# Design for Testability Techniques and Optimization Algorithms for Performance and Functional Testing of Multi-Chip Module Interconnections

A Doctoral Dissertation

Presented to

The Academic Faculty

by.

Rajesh Y. Pendurkar

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in Electrical & Computer Engineering

School of Electrical and Computer Engineering

Georgia Institute of Technology

March, 1999

Copyright © 1999 by Rajesh Pendurkar

# Design for Testability Techniques and Optimization Algorithms for Performance and Functional Testing of Multi-Chip Module Interconnections

Approved:

Prof. Abhijit Chatterjee

Prof. Joseph L. A. Hughes

Prof. David Keezer

Date Approved: 4/8/1999

# Dedicated to

mother Asha (Aai), lovely wife Shakalpi, brother Unmesh

&

the loving memory of my father Yashavant (Appa)

## Acknowledgments

I wish to thank my thesis advisor, Dr. Abhijit Chatterjee, for his guidance, inspiration, encouragement and support throughout the course of my graduate studies at Georgia Tech. His knowledge and enthusiasm have provided me with a constant challenge in completing my dissertation. I appreciate his open attitude which enabled me to focus on my research activities with greater freedom and collaborate with Dr. Craig Tovey of School of Industrial and Systems Engineering and Dr. Yervant Zorian of Logic Vision, Inc. Craig has been a source of tremendous inspiration to me and I am indebted to him for giving me an opportunity to work with him on the most celebrated problem in mathematics namely the traveling salesman problem. Throughout my Ph.D. work, he was educational in the process of learning and creativity. I wish to express my gratitude to Yervant for his continuous encouragement and remote technical discussions that laid solid foundations of my thesis. I am grateful to Dr. David Keezer for his insightful suggestions and comments throughout my research. My thanks go to Prof. Joseph Hughes and Dr. Keezer for devoting their precious time to serve on my thesis reading committee.

The establishment of the Packaging Research Center at Georgia Institute of Technology has helped me fulfil my dream of a getting a doctoral degree. I thank Dr. Rao Tummala, the PRC director, for this opportunity. His views on technology and interdisciplinary education have profoundly influenced me. I also thank PRC students for electing me as a president of graduate student executive council for 1997, the critical year of NSF review.

My Ph.D. research was greatly influenced by my summer internship at Strategic CAD Laboratory, Intel Corporation, Oregon. I would like to thank Prof. P. Pal Chaudhuri, Ken Stevens and Shai Rotem for giving me an opportunity to work on an industrial design and get hands-on experience. I wish to thank researchers at GTE Laboratories, Massachusetts

who inspired me to pursue my Ph.D. degree. Thanks also go to professors Dr. Mitch Kokar and Dr. Mark Staknis of Northeastern University, Boston for their recommendations. I also wish to thank Dr. Sham Navathe of College of Computing at Georgia Tech for creating an opportunity for me to study at this great institution. It has been a very fruitful experience at Georgia Tech campus and I will always cherish it for the rest of my life. Last, I wish to express my gratitude towards all my teachers, especially Mr. M. Nadkarni, Mr. N. Parab and Mr. B. Abreo.

I have benefited greatly from interacting with the members of dynamic MIST research group and many colleagues and friends at Georgia Tech. I would like to thank Sasidhar, Bruce, Huy, Pramod, Pankaj, Ramki, Sudip, Sasi, Gomes, Sreemala and Vijay.

I have been really fortunate to have a talented younger brother Unmesh and I cherished his endless love throughout my student life. Without his initiative, my doctoral studies would be just a distant dream.

Of course, my dream would not be a reality without Shakalpi, my lovely wife, for her unconditional love and sacrifice. She has been consistently providing me the mental energy necessary to overcome obstacles and to achieve my goal. While renowned physicist Stephen Hawking was my abstract inspiration, my mother has been my concrete inspiration. Likewise, Dr. Sharad Kanetkar has been my abstract motivation and Shakalpi has been my concrete motivation. I am grateful for her understanding, patience and encouragement, and for delivering our wonderful son, Parth just a month before my doctoral defense.

٧

## **Contents**

| Ack  | knowledg  | gments                                  | iv   |

|------|-----------|-----------------------------------------|------|

| List | t of Tabl | les                                     | X    |

| List | t of Figu | ires                                    | xi   |

| Glo  | ssary of  | Terms                                   | xiii |

|      |           |                                         |      |

| Abs  | tract     | *************************************** | xiv  |

|      |           |                                         |      |

|      |           |                                         |      |

| 1    | Intro     | oduction                                | 1    |

|      | 1.1       | Background                              | 1    |

|      | 1.2       | Background                              | 3    |

|      | 1.3       | Problem Statement                       | 5    |

|      | 1.4       | Dissertation Overview                   | 6    |

| 2    | Over      | rview of MCM Interconnect Testing       | 7    |

|      | 2.1       | Interconnect Fault Models               | 7    |

|      |           | 2.1.1 Stuck-at fault Model              | 8    |

|      |           | 2.1.2 Bridging Fault Model              | 8    |

|      |           | 2.1.3 Delay Fault Model                 | 9    |

|      | 2.2       | Interconnect Issues For MCMs            | 9    |

|      |           | 2.2.1 Interconnect Delay                |      |

|      |           | 0.00                                    |      |

|   | 2.3    | Fault Detection and Diagnosis Algorithms for Interconnects | 12 |

|---|--------|------------------------------------------------------------|----|

|   | 2.4    | Substrate Test Techniques for MCMs                         | 14 |

|   |        | 2.4.1 Flying Probe Testing                                 | 16 |

|   | 2.5    | Structured Testability Techniques for MCMs                 | 17 |

|   |        | 2.5.1 Boundary Scan Technique                              |    |

|   |        | 2.5.2 Built-In self-test                                   | 19 |

|   | 2.6    | Interconnect Testing for Yield and Throughput              | 20 |

| 3 | Single | e Probe Traversal Optimization                             | 22 |

|   | 3.1    | Probe Traversal Optimization Problem                       | 22 |

|   | 3.2    | Definitions, Notation, Assumptions                         | 24 |

|   | 3.3    | Theoretical Bounds on Test Cost                            | 26 |

|   | 3.4    | Integer Programming Formulation                            | 32 |

|   | 3.5    | Complexity Analysis                                        | 34 |

|   | 3.6    | Analysis for Practical MCM Substrate Testing               | 36 |

| 4 | Heur   | istic Algorithms for Single Probe Testing                  | 39 |

|   | 4.1    | Heuristic for Efficient Traversal of Single Probe          | 39 |

|   | 4.2    | Init_Tour Procedure                                        | 42 |

|   | 4.3    | Insert Procedure                                           | 42 |

|   | 4.4    | Shuffle Procedure                                          | 45 |

|   | 4.5    | Experimental results                                       | 47 |

| 5 | Distri | ibuted BIST Technique for Performance Test                 | 54 |

|   | 5.1    | BIST Preliminaries                                         | 54 |

|   | 5.2    | Proposed Approach                                          | 57 |

|   | 5.3    | Interconnect Test Model and Assumptions                    | 57 |

|   | 5.4    | Distributed BIST Architecture                              | 59 |

| 6 | Prech  | naracterized Test Pattern Generator                        | 63 |

|   | 6.1    | Proposed Approach                                          | 63 |

|   | 6.2   | Precharacterized TPG Architecture                          | 64  |

|---|-------|------------------------------------------------------------|-----|

|   | 6.3   | P-TPG Design Techniques                                    | 67  |

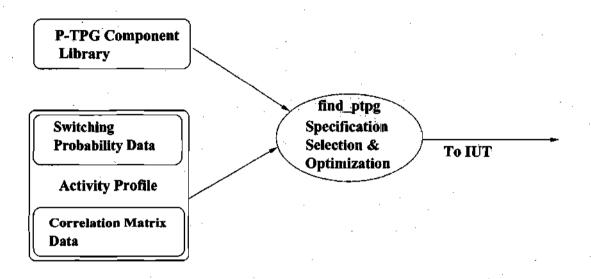

|   | 6.4   | P-TPG Design Specifications                                | 79  |

|   | 6.5   | P-TPG Design Optimization                                  | 81  |

|   | 6.6   | Activity Profile Generation Using P-TPG                    |     |

|   | 6.7   | Algorithm Description                                      | 83  |

| 7 | Disti | ributed Diagnosis Using MISR Reconfiguration               | 84  |

|   | 7.1   | Proposed Approach                                          | 84  |

|   | 7.2   | MISR Reconfiguration Technique                             | 90  |

|   | 7.3   | MISR Reconfiguration Under Single Fault                    | 92  |

|   | 7.4   | MISR reconfiguration Under Multiple Faults                 | 95  |

|   | 7.5   | Discussion                                                 | 99  |

|   | 7.6   | Experimental Results                                       | 102 |

|   | 7.7   | Hardware Cost                                              | 104 |

| 8 | DFT   | Tool for MCM Interconnect Test                             | 106 |

|   | 8.1   | Architectural Framework                                    | 106 |

|   | 8.2   | Discussion                                                 | 117 |

|   |       | 8.2.1 Interconnect Test Generation for Catastrophic Faults | 117 |

|   |       | 8.2.2 Interconnect Test Generation for Performance Faults  | 117 |

|   |       | 8.2.3 Test Compatibility with Boundary Scan Standard       | 118 |

|   |       | 8.2.4 Interconnect BIST Overhead Analysis                  | 118 |

|   | ;     | 8.2.5 Complexity Analysis of MatchProfile Algorithm        | 119 |

| 9 | Conc  | clusions and Future Work                                   | 120 |

|   | 9.1   | Single Probe Traversal Optimization                        | 120 |

|   |       | 9.1.1 Summary Of Contributions                             | 120 |

|   |       | 9.1.2 Future Research                                      | 121 |

|   | 9.2   | Precharacterized TPG Design                                | 121 |

|   |       | 9.2.1 Summary Of Contributions                             | 121 |

| •           | 9.2.2 Future Research                   | 122 |

|-------------|-----------------------------------------|-----|

| 9.3         | MISR Reconfiguration                    | 122 |

|             | 9.3.1 Summary Of Contributions          | 122 |

|             | 9.3.2 Future Research                   | 123 |

| Bibliograph | у                                       | 124 |

| VITA        | *************************************** | 134 |

# **List of Tables**

| 1.  | Technology Trends5                                                  |

|-----|---------------------------------------------------------------------|

| 2.  | Probe Route Cost Optimization With Different Heuristics43           |

| 3.  | Performance Comparison of Heuristics                                |

| 4.  | Effect of Variation of Number of Nets and Terminals on              |

|     | Probe Route Cost50                                                  |

| 5.  | Results on MCM Benchmark51                                          |

| 6.  | Moving Probe Tester Specifications52                                |

| 7.  | Comparison of Test Times: Single Probe Versus Double Probe Test53   |

| 8.  | Maximum Length Sequence for 4 bit external-XOR type LFSR68          |

| 9.  | Average of Total Number of Times P-TPG is in Given                  |

|     | Transient State76                                                   |

| 10. | Simulation Results for Distributed BIST Diagnosis Using R-MISR104   |

| 11. | Switching Profile Matching by Cascaded P-TPG Structure110           |

| 12. | IUT Profile Matching for Floating Point Multiplier111               |

| 13. | IUT Profile Matching for Cache-Processor Interface                  |

| 14. | Improved Profile Matching for Cache-Processor Interface             |

|     | Using XOR113                                                        |

| 15. | Analytical Computation of Cost Function Using Genetic Algorithm and |

|     | Markov Solver114                                                    |

| 16. | Comparison of Analytical Design and Simulated Design115             |

| 17. | Switching Profile Matching of Multiplier IUT Using Analytical and   |

|     | Simulation Design115                                                |

| 18. | Correlation Matrix Matching of Multiplier IUT Using Analytical and  |

|     | Simulation Design116                                                |

# **List of Figures**

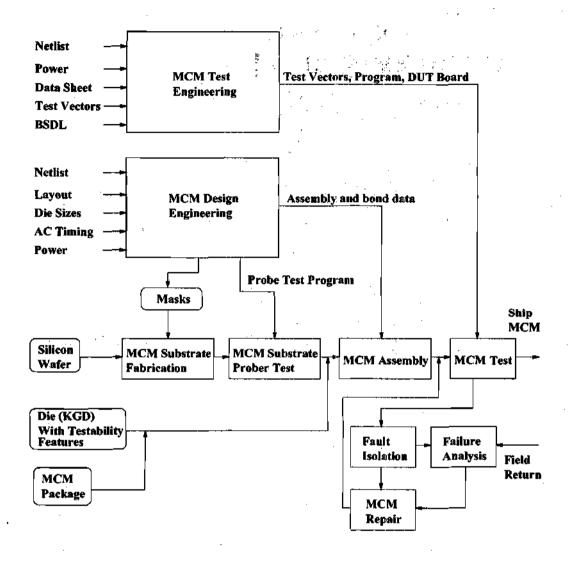

| 1.  | Integrated MCM Production Test Flow            | 4  |

|-----|------------------------------------------------|----|

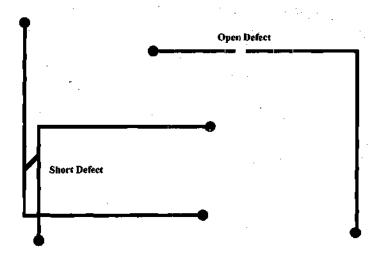

| 2.  | Short and Open Defects in MCM Interconnections | 9  |

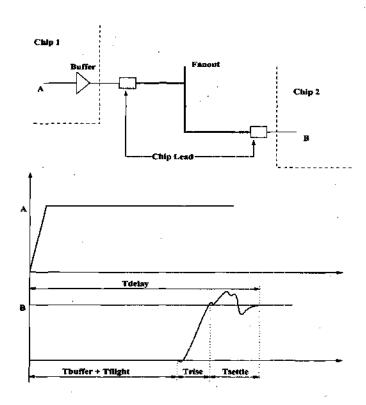

| 3.  | Interchip Signal Delay [12]                    | 10 |

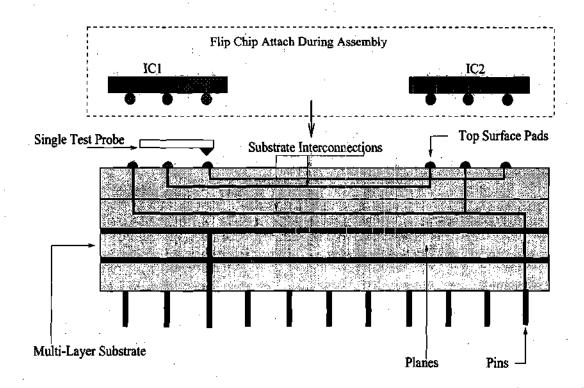

| 4.  | Multichip Module Substrate                     | 14 |

| 5.  | Boundary Scan standard compatible IC           | 18 |

| 6.  | Top Layer Interconnections With Terminal Pads  | 23 |

| 7.  | Comparison of SPTP and TSPTP                   | 27 |

| 8.  | SPTP for Unit Square                           | 28 |

| 9.  | Two Point Nets of Infinite Lengths             | 35 |

| 10. | An Example Substrate                           | 36 |

| 11. | Insertion Procedure                            | 44 |

| 12. | Shuffling of 5 Terminal Tour                   | 45 |

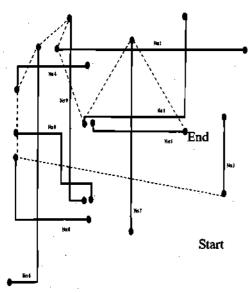

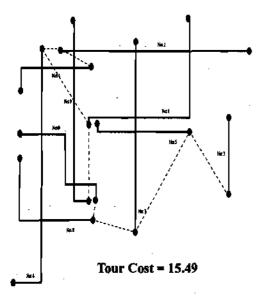

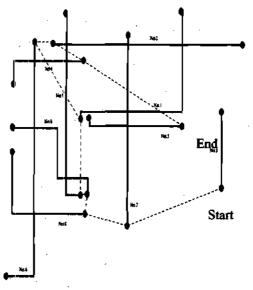

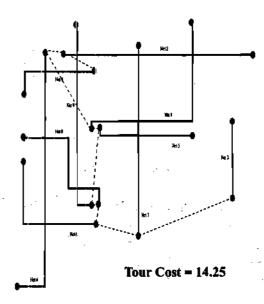

| 13. | Snapshots of Algorithm                         | 49 |

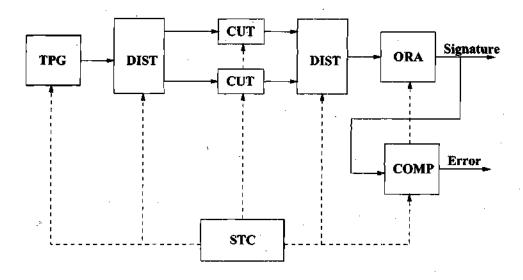

| 14. | Generalized BIST Architecture                  | 55 |

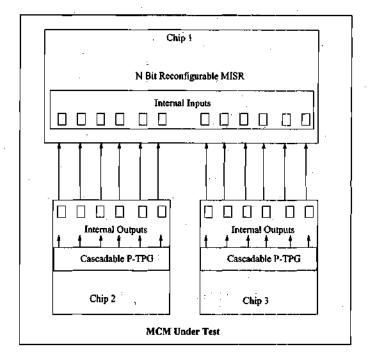

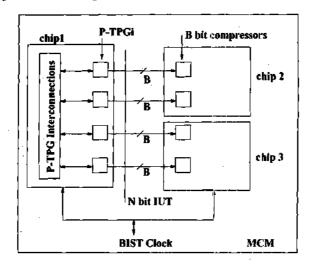

| 15. | Distributed BIST Architecture                  | 59 |

| 16. | Interconnect BIST Scheme                       | 63 |

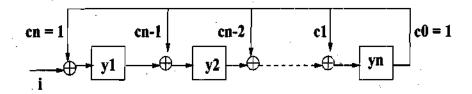

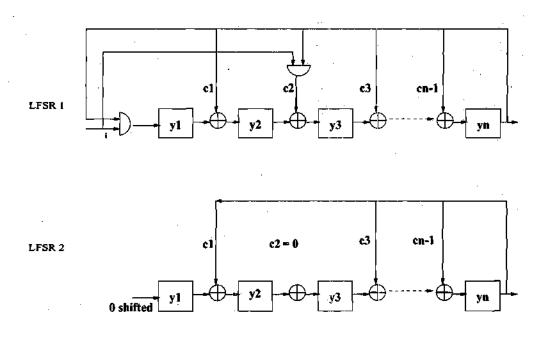

| 17. | Schematic of Internal-XOR LFSR                 | 64 |

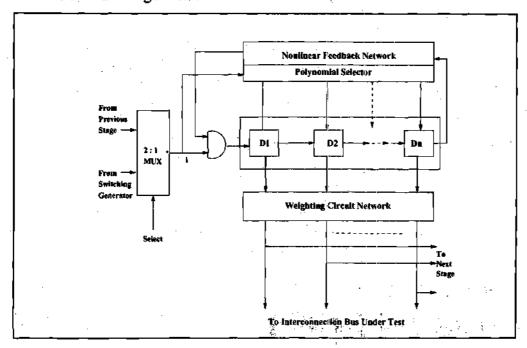

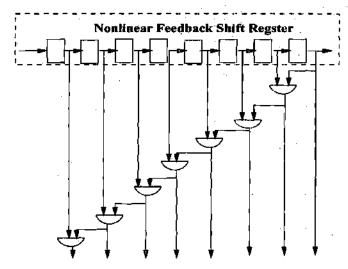

| 18. | Precharacterized TPG Component                 | 66 |

| 19. | Two LFSR Configurations                        | 67 |

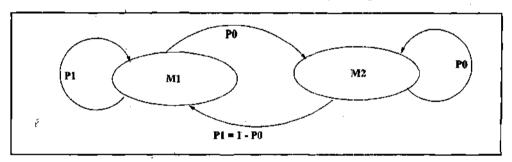

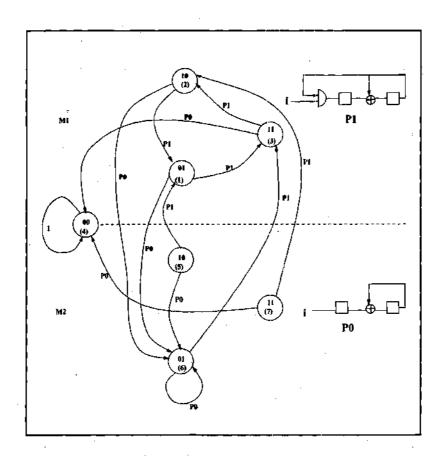

| 20. | Markov Model of P-TPG Component                | 70 |

| 21. | Markov Chain Model of 2-bit P-TPG                                  | 74         |

|-----|--------------------------------------------------------------------|------------|

| 22. | Transition Matrix of 2-bit P-TPG                                   | 75         |

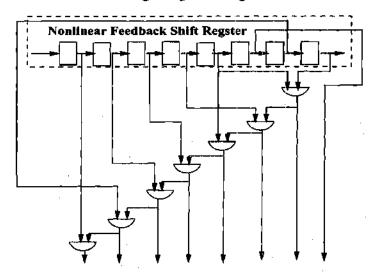

| 23. | Two Weight Circuit Configurations for Increasing Switching Profile | 77         |

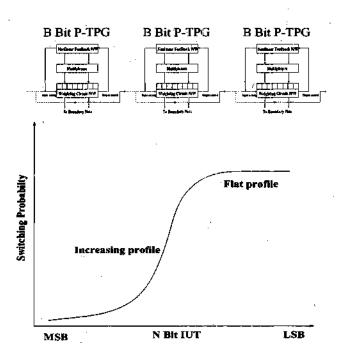

| 24. | Types of Switching Profiles                                        | 80         |

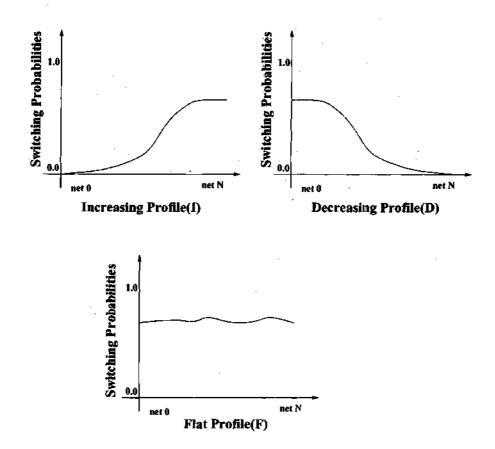

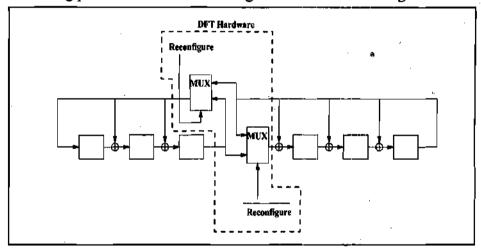

| 25. | DFT Architecture for Interconnect BIST                             | 81         |

| 26. | Cascaded P-TPG Structure and IUT Switching Profile                 |            |

| 27. | Dynamic Reconfiguration of LFSR                                    | 85         |

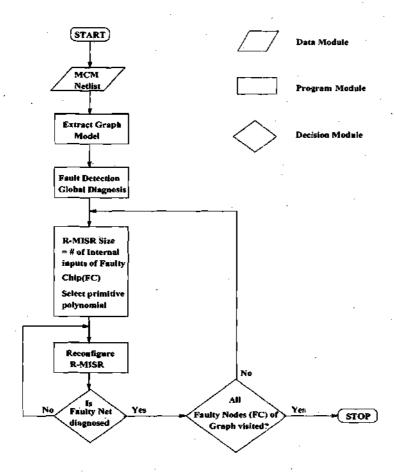

| 28. | MCM Interconnection Diagnosis Flowchart                            | 86         |

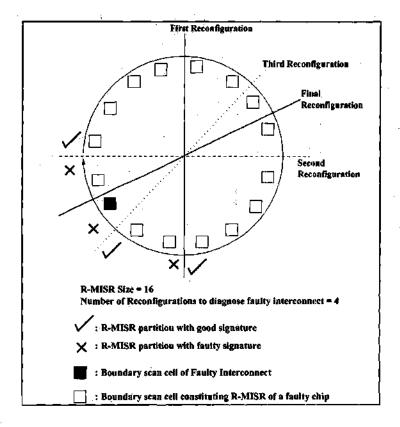

| 29. | Diagnosis Using R-MISR Reconfiguration                             | <b>9</b> 1 |

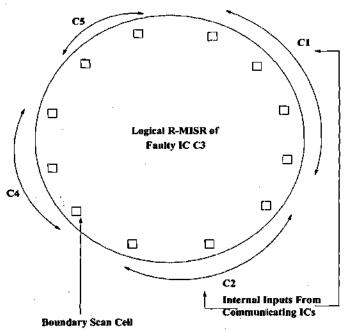

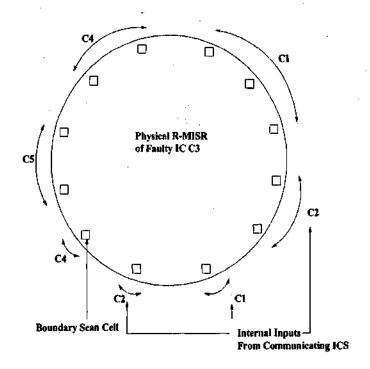

| 30. | Logical MISR                                                       |            |

| 31. | Physical MISR                                                      | 96         |

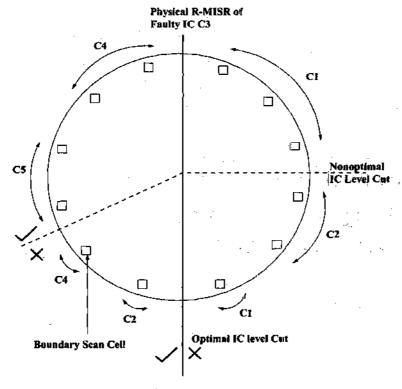

| 32. | Non-optimal MISR Reconfiguration at IC Level                       | 98         |

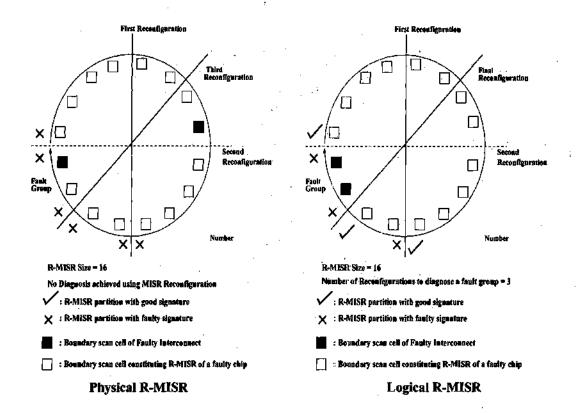

| 33. | Diagnosis Using Logical R-MISR v/s Physical R-MISR                 | 101        |

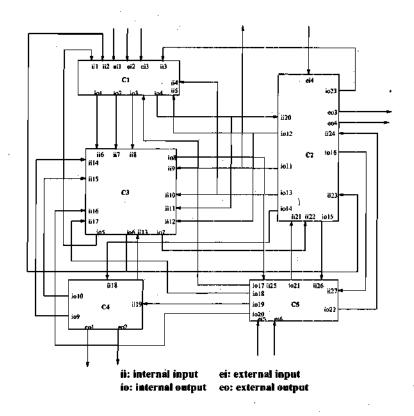

| 34. | Example MCM Under Test                                             | 103        |

| 35. | Graph Model of MCM Under Test                                      | 103        |

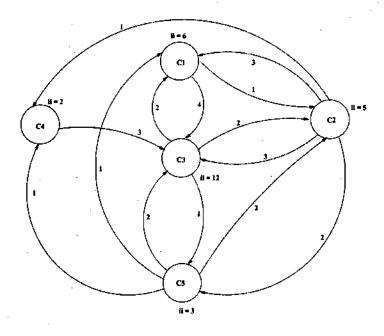

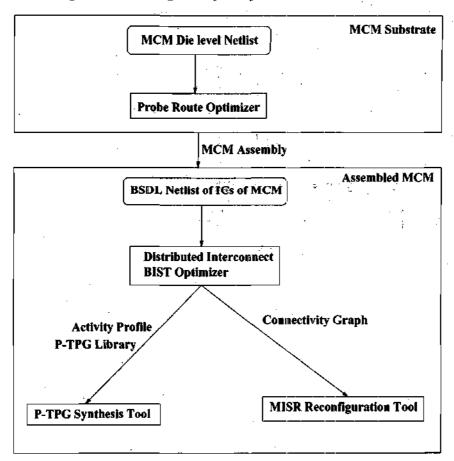

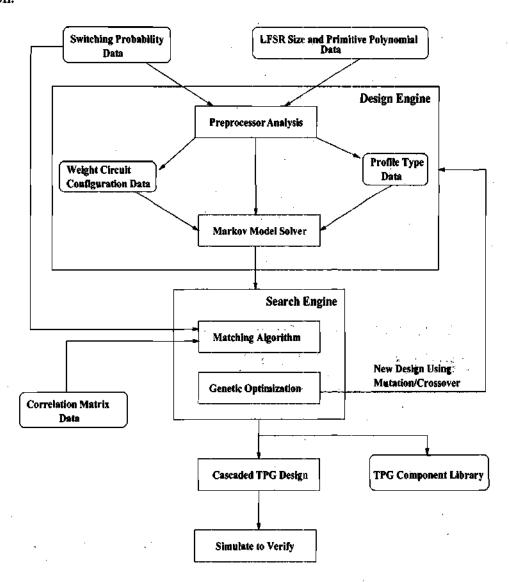

| 36. | Software Architecture of DFT Tool                                  | 107        |

| 37. | Structure of P-TPG Synthesis Tool                                  | 108        |

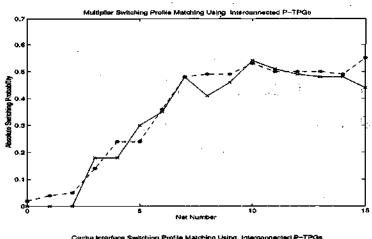

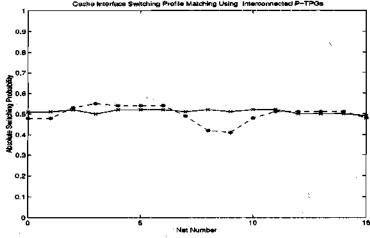

| 38  | Plots of Matched Switching Profiles                                | 112        |

## **Glossary of Terms**

SPTP Single Probe Traversal Problem

IUT Interconnect Under Test

LFSM Linear Finite State Machine

LFSR Linear Feedback Shift Register

MISR Multiple Input Signature Register

MUT MCM Under Test

ORA Output Response Analyzer

P-TPG Precharacterized Test Pattern Generator

R-MISR Reconfigurable MISR

TPG Test Pattern Generator

### **Abstract**

The objective of this research is to drive down the cost of functional testing of multi-chip module (MCM) interconnections before assembly of ICs using single probe test technique and to devise a formal design for testability (DFT) strategy for MCM interconnect performance test and diagnosis after assembly. Testing of MCM interconnections has become an activity of critical importance and considerable difficulty in the MCM design and test process in view of the demand for high performance and high density of packaging. First, electrical testing of a bare MCM substrate interconnections using a single probe is considered. A tight bound on single probe testing time is computed using rigorous theoretical analysis. Efficient and practical heuristic algorithm for finding an efficient probe route, to optimize the total test time of an MCM substrate, is presented. Experiments on the benchmark MCM netlist show that a up to 40% reduction in single test probe traversal time can be achieved by using the proposed algorithm. Secondly, a formal DFT methodology for comprehensive performance testing of assembled MCM interconnections is presented. A novel distributed BIST architecture is proposed to test and diagnose key performance issues such as the effects of cross-talk, ground bounce and simultaneous switching noise. The technique consists of specialized and reconfigurable on-chip precharacterized test pattern generators and multiple input signature registers. It is proved that interconnections switching activities can be effectively recreated and an accurate distributed diagnosis can be performed with low area overhead. The algorithms developed in this research are integrated into a CAD tool to automate MCM interconnections test flow.

## **CHAPTER I**

## INTRODUCTION

The purpose of this research is to develop a theoretical framework for comprehensive and efficient testing of multi-chip module (MCM) interconnections. This framework allows an efficient functional testing of MCM substrate interconnections before assembly using a single probe test technique. It also enables a comprehensive performance testing of assembled MCM interconnections after assembly using built-in self-test (BIST) techniques. This framework has been validated by software and hardware prototypes.

In this introductory chapter, the motivation and background behind this research are given. This is followed by a discussion on the economics of MCM testing. A high level description of the problem addressed in this research is given. Finally, the organization of the dissertation is outlined.

## 1.1 Background

Multi-chip module (MCM) technology is making its mark in high-volume markets such as consumer and automobile electronics, as well as in mission-critical applications

ı

such as avionics and communications [1]. By the end of this century, the worldwide MCM market is expected to reach \$2.3 billion out of which \$750 million is for smart cards and rest is for MCM-L, MCM-C and MCM-D [2]. The market in 2002 will reach \$3.3 billion. This increasing global trend of MCM applications is accompanied by increasing challenges resulting from shrinking dimensions of transistors, larger ICs, large I/O count resulting from high integration density and higher clock speeds. Some of the challenges are to increase the yield of MCM assembly, reduce the high cost of MCM manufacture and test, enhance the reliability of the assembled MCM and to overcome the limitations of high-cost external automatic test equipment (ATE).

The MCM technology involves the interconnection and assembly of bare dies on a substrate through metal interconnections. To achieve high volume, cost competitive MCMs, one must start with high yielding substrates and known good die. Due to the high cost of the semiconductor ICs involved, a testing scheme is necessary to ensure the functional integrity and performance of all the package interconnection paths. This promotes the reliability and quality of the end product. The test process consists of two steps. Initial testing of the interconnection paths prior to attachment of the active devices (ICs) must be performed and subsequently the assembled package must be tested. The testing of interconnections prior to die attachment is called *substrate testing* and is used to guarantee a defect-free substrate. The purpose of substrate testing is to test each interconnect for opens and/or shorts defects, thus assuring its functional integrity. This type of testing is essential because assembled MCM costs are high and repair of a substrate interconnect network is not always possible. A summary of electronic test methods for MCMs appears

in [3]. Functional /Performance testing is a follow-up step to the substrate testing and represents the testing of the package after die attachment. This testing step has two basic goals: 1) provide high quality detection of static and dynamic faults, in order to meet the expected defect rate at the module level, and 2) provide a high quality diagnosis of bad ICs and interconnects to allow potential repair at the module level. The module level testing of MCMs is described in [4].

The testing for dynamic faults is called *performance testing* which verifies that all the ICs on an MCM substrate can properly communicate with each other. Figure 1 shows the integrated MCM test flow. The detailed description of types of MCM test related activities is given in [5].

#### 1.2 Economics of MCM Test

Improvements in the design and test process are mandatory in view of the fact that economic factors, such as reducing the final product cost, are becoming increasingly important. The profitability of high performance MCMs are can only be achieved by improving two major components of the global cost namely minimum time to market and maximum end-of-product yield [6]. Therefore, the reduction in the test time for a single substrate has a significant impact over a large production run in terms of minimizing the production testing time. Maximizing the yield directly relates to the test strategies incorporated in the production flow. As a result of this increasing emphasis on testing, it is being considered a part of the design process.

FIGURE 1. Integrated MCM Production Test Flow

Test is becoming one of the parameters of a system design and employing design for testability strategies early in the design cycle effectively reduces test cost of the final product,

4

which is estimated to be about 30% of total production cost for MCMs [7]. Table 1 shows the typical technology and cost trends [8].

**TABLE 1. Technology Trends**

| 1970            | 1980                                        | 1990                                                                     | 2000                                                                                                              |

|-----------------|---------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| SSI             | LSI                                         | ULSI                                                                     | мсм                                                                                                               |

| 10              | 5k                                          | 200k                                                                     | 2000k                                                                                                             |

| 256             | 16k                                         | 16 Mb                                                                    | 10 Gb                                                                                                             |

| 10 <sup>2</sup> | 10 <sup>5</sup>                             | 10 <sup>9</sup>                                                          | 10 <sup>14</sup>                                                                                                  |

| 100k            | 10 <b>M</b>                                 | 100M                                                                     | 500M                                                                                                              |

| 14              | 44                                          | 356                                                                      | 1000                                                                                                              |

| 5               | 20                                          | 60                                                                       | 60                                                                                                                |

|                 | SSI<br>10<br>256<br>10 <sup>2</sup><br>100k | SSI LSI  10 5k  256 16k  10 <sup>2</sup> 10 <sup>5</sup> 100k 10M  14 44 | SSI LSI ULSI  10 5k 200k  256 16k 16 Mb  10 <sup>2</sup> 10 <sup>5</sup> 10 <sup>9</sup> 100k 10M 100M  14 44 356 |

#### 1.3 Problem Statement

Testing MCM substrate interconnections is necessary to assure the reliability and quality of the assembled MCM. Single probe test techniques are becoming increasingly popular for connectivity verification using high frequency test stimulus as well as for the capacitance testing of substrates. The objective of this research is two-fold. First, efficient traversal algorithms to optimize the total distance traveled by a single test probe on an MCM substrate are presented. These heuristic algorithms reduce the substrate testing time and associated test cost. Second, a novel design for testability(DFT) technique to address the issue of performance testing of MCM interconnections is developed. This issue is becoming very important because of the fact that hitherto "second-order" effects, such as ground bounce, crosstalk, and switching noise, play dominant roles in current design methods. Such effects are dominant causes of a low MCM yield. Built-in self-test techniques are devised to address these issues and enhance MCM testability.

#### 1.4 Dissertation Overview

Chapter 2 discusses the interconnect fault models and algorithms used currently for detection and diagnosis of interconnect related faults. A brief overview of structured DFT techniques for MCMs is given. An integer programing formulation of the single probe traversal optimization problem and a theoretical model for lower bound of a single probe test cost is described in Chapter 3. In Chapter 4, a heuristic algorithm designed for an efficient routing of a single test probe is discussed. A novel distributed BIST technique for performance testing of MCM interconnections is proposed in Chapter 5. Chapter 6 discusses in detail the test pattern generation part of the proposed distributed interconnect BIST technique. The distributed BIST diagnosis for performance related interconnect faults is described in Chapter 7. Chapter 8 provides an overview of a CAD tool and a hardware prototype developed based on this research. Chapter 9 summarizes the technical contributions and suggests directions for future research.

## **CHAPTER II**

# **OVERVIEW OF MCM**

# INTERCONNECT TESTING

In this chapter, a brief review of the interconnect fault models and the algorithms which are currently used by the test community is given. A general description of MCM substrate interconnections test techniques used in industry is given. Current design for testability (DFT) techniques, including a BIST concept, are discussed. This builds a foundation for the research presented in this dissertation.

#### 2.1 Interconnect Fault Models

The fault models of interest are based on the likely failures observed in MCM interconnections. The stuck-at fault model and the bridging fault model [9] are widely used in today's test and diagnosis activity for MCM interconnections. The delay fault model is becoming increasingly important in view of emerging deep submicron applications where the interconnect delays are dominating the gate delays. In the following subsections, each fault model is briefly described.

#### 2.1.1 Stuck-at fault Model

The stuck-at fault model, often referred to as a *classical* fault model [10], assumes that a fault in the interconnect results in logic value on that interconnect being fixed to either a logic 0 (stuck-at-0) or a logic 1 (stuck-at-1). This represents the most common types of failures, for example, short-circuit to ground plane or a power plane, in many technologies. A short results if not enough metal is removed by the photolithography, where as overremoval of metal results in an open circuit which is usually distinguished from a stuck-at fault.

#### 2.1.2 Bridging Fault Model

With the increasing density of ICs that are mounted on MCM substrate, the probability of shorts between two or more interconnects has been significantly increased. Unintended shorts between the interconnects form a class of permanent faults, known as *bridging faults*, which can not be modeled as stuck-at faults. There are two types of bridging faults: AND-bridging fault and OR-bridging fault [10]. In AND type of bridging fault, logic 0 dominates, while in OR type of bridging fault, logic 1 dominates.

#### 2.1.3 Delay Fault Model

The MCM interconnections are associated with resistance and capacitance which govern the RC-delay of that interconnect. The failure of the interconnect to meet its timing specification without alteration of its low-frequency functional behavior results in the delay fault. The defects such as near-opens and near-shorts have high probability of occurrence due to the statistical variations in the manufacturing process. These defects result in the violation of its timing specifications.

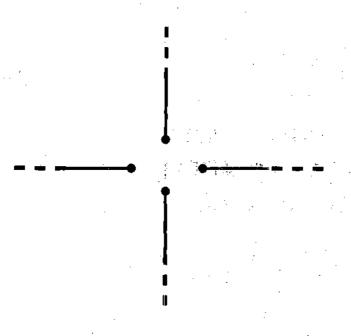

Examples of typical interconnect defects are shown in Figure 2.

FIGURE 2. Short and Open Defects in MCM Interconnections

#### 2.2 Interconnect Issues For MCMs

Interconnect refers to the medium used to connect any two or more circuit elements.

Interconnections include the package pins, lead frames, bonding wires, TAB frames, sol-

der bumps, metal layers inside chips, and wires on MCM substrates. Interconnections differ widely in their electrical performance. Typical interconnect models use lumped resistances and capacitances (R-C model) or distributed resistances and capacitances (Transmission line model) [11]. Two major interconnect performance factors are described below.

#### 2.2.1 Interconnect Delay

The total time taken for a signal to travel from chip 1 to chip 2 is given by the sum of the buffer delay, time of flight across interchip interconnection, rise time of the received signal and the settling time of the signal as shown in Figure 3.

FIGURE 3. Interchip Signal Delay [12]

The interconnect capacitance does not scale proportionately with device scaling. As more and more gates are integrated, die size increase and on-chip interconnect capacitance increases. Similarly, interchip interconnection capacitance, which is proportional to the wire length, increases as more and more chips are integrated on a single MCM. As a result of finer line widths and spacings, the resistance of the MCM interconnect becomes comparable to that of a driver circuit and causes increased time of flight for the signal.

#### 2.2.2 Interconnect Noise

The density of MCM substrates is higher compared to typical printed wiring boards.

Therefore, capacitive and inductive effects of the interconnects are also nonnegligible and lead to following types of noise [13].

Reflection noise: This is caused by unmatched loading and improper terminations of transmission lines of finite lengths. The reflections occur at discontinuities in the transmission lines, such as fanout branches, and can be minimized by interconnect design under controlled impedance environment.

Crosstalk noise: The mutual capacitance and inductance between neighboring electrical signal paths cause unwanted coupling between a active line (an interconnect with signal voltage switching from logic level 0 to logic level 1 or vice versa) and a passive line (an interconnect with no signal voltage switching). The detailed analysis and exact formulas for crosstalk noise voltages can be found in [11]. The methods for minimizing crosstalk noise are given in [14].

Power Distribution noise (Ground Bounce): Off-chip drivers used to drive package interconnections of an MCM have high drive strength. These high switching currents and transient currents flow through the power supply pin, substrate interconnections and substrate to package bonding and package parasitics. All these components have inductances which lead to voltage drops equal to  $L_{eff}(dI/dt)$  when these drivers switch, where  $L_{eff}$  is an effective inductance between the leads and dI/dt is the rate of change of current through the component leads. If many of the drivers switch simultaneously, the voltage may bounce below acceptable threshold, resulting in false logic level. This noise is referred to as simultaneous switching noise or ground bounce. Because of large number of drivers and the addition of MCM substrate interconnections, this type of noise becomes a critically important factor for the design and test of an MCM.

The combined effect of delay and noise contributes to performance degradation and is a major cause of lower MCM yield.

### 2.3 Fault Detection and Diagnosis Algorithms for Interconnects

The earliest work reported in this area was by Kautz [15]. He showed that  $\lceil \log_2 N \rceil$  parallel test vectors (PTV) are optimal for detecting all shorts in a network of N unconnected terminals. This method involved applying a unique sequential test vector(STV) to each net and could be generated by a simple counting sequence. This was extended to  $\lceil \log_2 (N+2) \rceil$  PTVs by Goel and McMahon [16] to enable detection of all possible stuck-at faults and all shorts. The modified counting sequence suggested allows stuck-at fault test-

ing in addition to detection of a short between any pair of nets. It is also extended to implement a two step diagnosis. Wagner [17] has proposed a diagnosis scheme which requires  $2\lceil \log_2(N+2) \rceil$  vectors. In this scheme,  $\lceil \log_2 N \rceil$  vectors used for shorts and stuck-at faults detection together with its complementary set forms the complete set of vectors for multiple fault diagnosis. A detection and diagnosis scheme which provides a minimal test vector set using the structure independent algorithm has been proposed in [18]. It also discusses a walking sequence scheme for the detection and diagnosis of shorts and stuck-ats. Jarwala and Yau [19] have discussed a theoretical framework for analyzing test generation and diagnosis algorithms for wiring interconnects. They define two types of diagnostic resolution. The first identifies, without ambiguity, a list of nets that have a fault. The second type further identifies the sets of nets affected by the same type of short, the nets that are stuck at zero or one, or the nets that are open. There are two types of test and diagnostic techniques. The first is One Step Test and Diagnosis where a set of test patterns are applied and the response is analyzed for fault detection and diagnosis. The second type is Adaptive Test and Diagnosis where the test is applied, response analyzed, and then one or more additional tests are applied depending on the response to aid diagnostics. The need for minimizing the test size while maintaining its diagnostic resolution is discussed in detail in [20]. It provides generalized, optimal or near-optimal algorithms for interconnect testing, providing the flexibility to trade-off test compactness and diagnostic accuracy.

## 2.4 Substrate Test Techniques for MCMs

Typical MCM substrates contain a large number of interconnections (nets) connecting different terminals (pads) on the topmost substrate layer. The ICs are attached to the substrate after it has been thoroughly tested for shorts and opens of its interconnections. Figure 4 shows the multilayer MCM substrate, buried interconnections, and top layer surface pads required to bond the ICs using a flip-chip attach technology.

FIGURE 4. Multichip Module Substrate

The typical interconnection testing process consists of application of the test stimulus to the interconnection under test through a probe which physically touches the top sub-

strate pads. The probe also receives the test response which can be evaluated by a tester [21] to decide whether the interconnection is faulty or fault-free. A moving probe tester physically moves the probe to another substrate pad to test another interconnection. This probe movement significantly impacts the total substrate test time since a typical MCM substrate consists of a large number of interconnections.

As the complexity of multi-chip module increases, the interconnect requirements will continue rising. A wiring density (total wire length per unit area) as well as the substrate size will keep increasing [22]. Before costly ICs are mounted on the package substrate, the substrate themselves need to be verified for electrical intergrity and probed for shorts and opens. The current techniques used by the industry are: flying probes for resistance, capacitance [23] and combined capacitance/resistance testing; voltage contrast electron beam [24]; electrical module test (EMT) and time domain network analysis (TDNA) [25]. The key elements that differentiate these test methods are equipment cost, test time, throughput (number of tests per second) and defect resolution and a detailed comparison can be found in [25].

Electron beam technology [24] measures the voltage present at each node of an interconnection network using an electron beam, after injecting a charge in the network at one node. Each node of the network should show the charge voltage present, verifying the electrical continuity. It is a highly accurate and high throughput testing technique and there is no mechanical contact with the substrate, but high cost and longer setup times limit its usefulness. Also, this technique is ideally suitable for shorts testing. TDNA has high test application time and high equipment cost. Although EMT has the capability of detecting near-opens, it can not detect near-shorts. Membrane probe cards [26] can detect open, short and high resistance faults. However, it is difficult to apply them to test cofired ceramic MCM substrates. Although parallel test vectors could be applied to the inputs, as would occur during the normal operation, the clock speed during probe card testing (TCK < 6 MHz) is usually much slower than that during normal operation [27]. A massively parallel test of large area substrate is presented in [28] as a low cost, high throughput method for substrate test. This approach uses digital signatures and claims an improved sensitivity to near failures such as resistive opens.

#### 2.4.1 Flying Probe Testing

Flying probe testers employ two or more single needle probes which are mounted on the mechanical systems moved by linear motors, positioning each probe at a programmed position and contacting the substrate at a bond pad for connection to an IC. By moving the probes to each bond pad in an interconnect network, this type of tester verifies the continuity of each interconnect network in a substrate. After a continuity check for the network, one of the probes may be moved to a ground connection, and then to the power connections(s), to check for isolation from ground and power planes.

Capacitance probing involves a single probe to contact each bond pad on the surface of the substrate and measure the capacitance with respect to the ground reference plane. This system is mechanically less complicated than the multiple flying probe systems. In addition, as the number of interconnection pads increases to even a moderate degree, this single probe technique becomes essential. This is because the number of two-probe measurements required to fully test a substrate for net to net shorts grows as the square of the number of pads while the number of single probe tests only grows linearly [23].

Recently, a new technique has been developed to detect interconnect faults by measuring the attenuation of the test stimulus applied through a tuned load using a single probe [21]. This technique reduces the total hardware cost of the test equipment and has a higher diagnostic resolution. It also has the potential to be faster and, therefore, cheaper compared with the multiple probe techniques. It also has the additional advantage of being able to detect latent defects such as near-open and near-shorts.

#### 2.5 Structured Testability Techniques for MCMs

Structured testability techniques improve controllability and observability of a circuit under design by making it more testable. The requirement of these techniques stems from two major problems faced by the MCM technology. First, the MCM pinouts allow limited access to internal nodes (isolation problem) and, second, the ICs mounted on an MCM do not undergo full functional testing after packaging (incomplete die testing problem) [29].

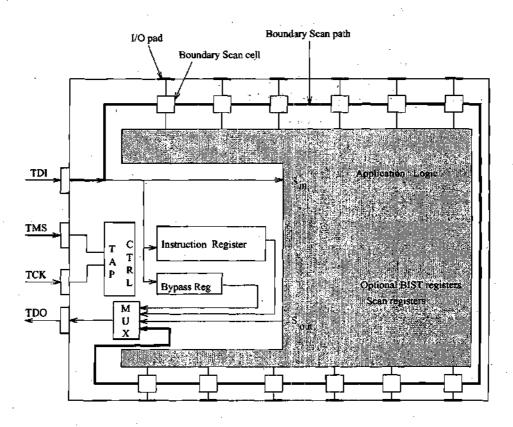

#### 2.5.1 Boundary Scan Technique

A boundary scan technique, which is standardized by IEEE 1149.1-1990, is a collection of design rules applied principally at the IC level [Figure 5] that allows test software to address these problems in a structured way. The architecture permits associating memory cells with each input and output pin of every chip so that known signals may be sent

across interconnections and captured for observation. It provides a single test access port (TAP) to each chip, through which all the test related instructions and data can be transferred. It is possible to execute an on-chip BIST using the "RUNBIST" instruction and test electrical interconnections functionally by transmitting data from a boundary scan cell (BSC) of one IC to the boundary scan cell of its neighboring IC using the "EXTEST" instruction. The application of the boundary scan technique [20] has opened up possibilities to access internal device test structures, such as internal scan, even though the device is now loaded on a board. This has caused an increased interest in adding BIST structures to devices and then re-using those structures at board or system level and particularly for field service.

FIGURE 5. Boundary Scan standard compatible IC

#### 2.5.2 Built-In self-test

Built-in self-test (BIST) [30][31] represents one of the embedded test (Design-For-Test) technologies that has finally been accepted by industry. Internal scan, boundary scan, level sensitive scan design (LSSD), random access scan, scan path, scan-set logic are some of the structured DFT techniques used in industry[32]. Built-in logic block observation(BILBO), syndrome testing, testing by verifying Walsh coefficients and autonomous testing are some of the self testing technologies[32]. Internal scan, was created to overcome fundamental implementation problems of Automatic Test-Pattern Generation based on the 1959 stuck-at model and path-sensitizing theory [10]. The motivation behind boundary scan, was to provide a virtual bed-of-nails to access boards containing surfacemount devices and MCMs. Typically, BIST is used at a device level to solve a variety of device-level test problems such as lack of direct pin access (especially for multiple instances of embedded RAMs), ability to carry out tests "at-speed", improved diagnostics and use for device burn-in. One of the problems encountered in the past was that BIST was seen to be an extra investment, i.e., once it had been used and the device had passed the tests, it would not be used any further. This makes an economic justification of BIST difficult. Boundary scan has changed this view. Access to the BIST resources through boundary scan means that the BIST can now be re-run at all stages of the product life cycle, particularly for the system-level diagnostic purposes such as MCM diagnostics [33].

## 2.6 Interconnect Testing for Yield and Throughput

Important issues of ATE capabilities, test/repair environment and board yield are discussed in [19]. Traditionally, manufacturers use two techniques to test boards: In-circuit test and functional test. The onset of deep sub-micron (now currently eluded to as nanometer) technology is changing the way chips are being designed and manufactured. New problems are arising that are driving design automation to integrate all the tools that are needed to successfully take a design from concept to reality. Test is one part of this process that is getting significant attention. An area once classified as a "back end" process in the design flow is moving closer to the "front end". Design methodologies are incorporating test related structures in the beginning of the design cycle. Manufacturability of the complex designs caused by the excess silicon available is a significant issue. The following is a quote from a leading technology magazine EE Times [34].

"But the industry has hit the wall in the quarter-micron generation. There are serious, serious problems with yields at quarter-micron..... The power signal-integrity and metal-migration challenges are exceeding the capability of the tools. Instead of 80% yields, crosstalk is cutting yields for quarter-micron designs down to 30 or 40 percent at some companies."

As yield becomes more of a problem, test and testability issues will get more focus. We are already observing a trend towards full scan designs. Deep sub-micron is challenging test in a number of areas. Capacity, performance, Iddq, pinouts, cores, power, and heat are issues that are stressing testing. The SIA roadmap [35] is predicting problems in the

Area of test. The roadmaps focus areas for test are: Testability, Testing and Testers, and Known Good Die. The roadmap sees "integrated circuit testing to be a major cost factor and must be done in prepackaged and packaged form, including future multi-chip packaging. Design productivity and performance improvement, cost-effective tools covering design verification from system design down to physical transistor, and interconnect design at clock frequencies greater than 1 GHz and 0.5 volts power supplies is a major challenge."

## **CHAPTER III**

## SINGLE PROBE TRAVERSAL

## **OPTIMIZATION**

In this chapter, a problem of finding an optimal route for a single probe for testing an MCM substrate, is formulated. An integer programing formulation of this optimization problem is given. A theoretical framework to analyze this problem is developed and a tight bound on the single probe traversal cost is computed.

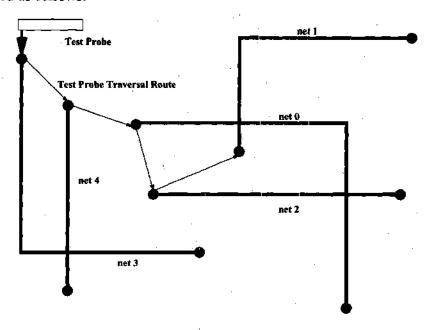

## 3.1 Probe Traversal Optimization Problem

An example of MCM interconnects, each having two terminals, as viewed from the top layer of an MCM substrate is shown in Figure 6. Each net may connect more than two terminals on the topmost substrate layer and is tested by probing only one of the terminals on the layer. The probe then traverses to a terminal of another net on the substrate and the test procedure is repeated. It is desired to find the optimal route for the probe so that the

total distance traveled, and thereby total test cost, is minimized. The generalized problem can be stated as follows.

FIGURE 6. Top Layer Interconnections With Terminal Pads

Generalized k-probe traversal problem: A k-probe tester contacts k terminal pads and simultaneously verifies the connectivity among  $\binom{k}{2}$  pairs of the k terminal pads. Given the netlist of a finite number of nets with fixed multiple terminals, find efficient and collision-free routes for the k-probes assuming that the probes move simultaneously. An algorithm for finding efficient routes is given in [36].

Single probe traversal problem: Given the netlist of a finite number of nets with fixed multiple terminals, identify the sequence of terminals of each net (one per net) such that the total traversal cost of the probe is minimized, thereby reducing the overall test time while ensuring that every net is probed once.

### 3.2 Definitions, Notation, Assumptions

For the sake of theoretical proof, it is assumed that the MCM substrate is a unit square. A net is a set of points on the substrate. Distances between points are either Euclidean (also called  $L_2$  norm) or the maximum of the absolute differences in x or y coordinates (called sup or  $L_{\infty}$  norm). Some machines used in MCM substrate testing can move probes simultaneously and independently in the x and y directions. The sup norm distances apply to this type of movement. Since the great majority of nets have 2 nodes, we focus on these cases. We analyze a substrate containing  $n_i$  nets of i nodes, i = 2 with  $n = n_2$ . Extensions could be easily carried out for more nodes per net but the results would be qualitatively the same.

The SPTP, or single probe traversal problem, is to visit one point from each net, so as to minimize the total distance traveled. Note that SPTP requires deciding which point from each net is to be visited, and in what sequence to visit the nets.

The two probe traversal problem, DPTP, involves a test procedure that uses a pair of probes. A probe is placed at each of two nodes of the net to test connectivity between the nodes. One such test is required for a 2-node net; depending on the internal wiring, either one or two such tests may be required for a 3-node net. After a pair of nodes is tested, the probes can move simultaneously to new locations for the next test. The effective travel distance between tests is therefore the maximum of the two distances that must be traveled by the probes. In DPTP one must decide on the sequence of tests, and decide which probe

will travel to which node, to minimize the total effective distance traveled. One efficient technique to find such a conflict-free route of a two probe tester is described in [37]. A 2-probe tester for substrate testing utilizing a bandsort algorithm to determine the route of one probe is discussed in [38]. In an optimal solution, it may be that two tests for the same net do not occur consecutively.

The SPTP is similar to the traveling salesman problem (TSP) which can be defined conceptually as follows: Given a set of N terminals, determine the shortest complete circuit that connects all terminals, so that every terminal is visited exactly once. There are various modifications and extensions to the basic TSP definition. These include the multiple traveling salesman problem [39], the vehicle routing problem [39], the capacitated are routing problem [40] and the multiple tour maximum collection problem [41]. The SPTP can be considered as a multiple choice TSP since a probe can contact any one of the terminals of the selected interconnect. Thus it has an added complexity that the set of terminals to be visited is not predetermined.

It is well known [39] that for every instance of TSP, the optimal solution has length  $\le 2\sqrt{n}$ . This is for the Euclidean metric, so it also holds for the sup norm metric. This result scales: for example if the points are in a square of side length 1/2, the optimal solution has length  $\le \sqrt{n}$ .

For the average case analysis, it is assumed that the location of every point in every net is identically independently distributed uniformly on the substrate. Under this distributional assumption, the Euclidean TSP is known to have expected optimal value tending to  $\alpha \sqrt{n} + o(\sqrt{n})$ . For the Euclidean norm,  $0.3 \le \alpha \le 2$  and the constant  $\alpha$  has been experimentally determined to have value approximately 0.71. This result scales just as the deterministic result discussed previously. Some of the results will involve the constant  $\alpha$ .

Let N denote the set of n net locations, which comprise an instance of SPTP or DPTP. N implicitly gives value of  $n_2$ . Let SPTP(N) (respectively DPTP(N)) denote the value of the optimum solution of SPTP (respectively DPTP) on the instance N. When the instance N is random, E[SPTP(N)] denotes the expected value of SPTP(N). For random N, the values  $n_2$  are treated as parameters rather than as data following some probabilistic distribution.

#### 3.3 Theoretical Bounds on Test Cost

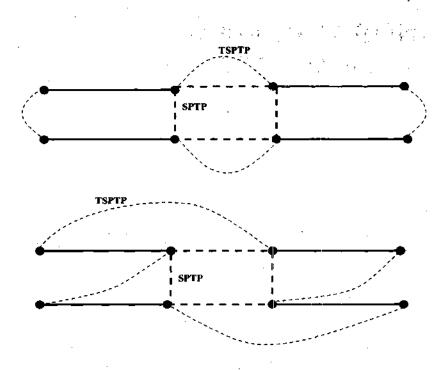

SPTP solution consists of n nodes (1 node per net) in sequenced tour. This problem can be related to the classical TSP by seeking an optimal solution to the related TSP instance on 2n nodes without any option of visiting one node per net. The optimal solution for tsp tour of all 2n nodes in the instance of N is denoted by TSPTP(N).

**Theorem 1:**  $SPTP(N) \leq TSPTP(N)$

**Proof:** The triangle inequality for an euclidean TSP is used. By triangle inequality, the shortest distance between any pair of cities is the direct route. For an instance of TSP over 2n nodes, all nodes of all nets are to be visited. There are 2n edges in the tour as shown in Figure 7. For the instance of SPTP, however there are only n edges in the tour. A step by

step solution to SPTP from the TSP tour over 2n nodes is constructed, starting from an arbitrary node say i. The next node j of the tsp tour is checked. If j belongs to the net different from that of node i, it is required to check whether the net to which node j belongs has been already visited. If not, the edge i-j in subtour leading to step by step construction of complete SPTP tour is preserved. Otherwise j is skipped and the next node k which belongs to the unvisited net in TSP tour, is considered. A new edge i-k is added to construct a subtour as a part of SPTP tour. Obviously by triangle inequality, length of the edge i-k is less than the path i-j-k in the TSP tour. Thus for any arbitrary new edge l-m added to construct SPTP tour, length edge (l-m) is always less than path (l-m) through intermediate nodes. Thus the optimal SPTP tour length can be no longer than optimal TSP tour length over 2n nodes. Q.E.D.

FIGURE 7. Comparison of SPTP and TSPTP

It is always interesting to find out the performance guarantee of the heuristic to solve computationally hard problem such as SPTP. In the following section we provide rigorous mathematical analysis to find out the lower bound on SPTP instance.

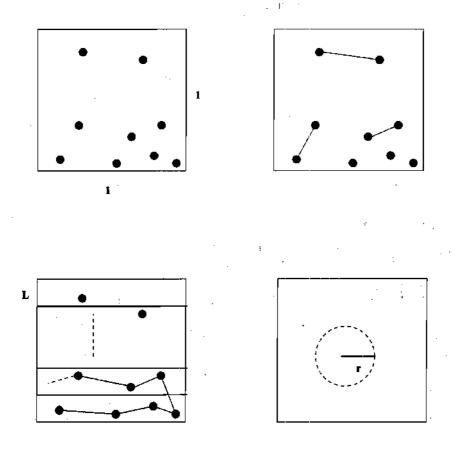

**Theorem 2:** Expected value of SPTP(N) is  $\theta(\sqrt{n})$

Proof: For the purpose of the proof, we restrict our attention in which all the nodes of the given instance of SPTP lie on the MCM substrate which is square of unit width as shown in Figure 8.

FIGURE 8. SPTP for Unit Square

Theoretical Analysis: We assume that all nodes of n nets on the substrate are uniformly distributed within the square. For the case of 2 nodes per net  $(n = n_2)$ , we randomly choose any 2 points from the given distribution of nodes and construct one net. Thus, we construct n 2-point nets out of given nodes in the unit square substrate. We compute theoretical bound on SPTP(N) in terms of general value of n as follows.

Upper Bound Analysis: We divide the unit square substrate into horizontal stripes  $S_1$ ,  $S_2$ ,....  $S_{1/L}$ . Clearly total number of stripes are 1/L. The probe traverses within odd numbered stripes from left to right and then visits nodes in the even numbered stripes from right to left, finally returning to the initial node from the last node of the final strip completely testing the unit square substrate. The worst case length of SPTP tour under the above constraints is  $SPTP(N) \le \sqrt{2} + 1/L + 2 + nL$ . The first component represents the diagonal jump to starting position. Second component is the number of bands of the square constituting to length due to X direction moment. Third component is  $2L \times 1/L$  where 2L denotes worst case moment in Y direction from one band to the other. The last component denotes the Y moment within the band. This bound from above is smallest for  $L = 1/(\sqrt{n})$ . Thus the SPTP(N)  $< \sqrt{2} + 2 + 2\sqrt{n}$ . This proves that SPTP(N) is bounded from above by  $\sqrt{n}$  as constant factors are ignored.

Lower Bound Analysis: Now we give rigorous proof for bound from below. This is estimated with probabilistic approach due to obvious bound of zero. We define  $d_{min}$  as the minimum distance between two nodes each belonging to separate nets. To bound SPTP(N) from below, we must find expected value of sum of  $d_{min}$  over all nets  $(n = n_2)$  for

2-point nets) in the unit square substrate. For this purpose we introduce probabilistic approach as shown in figure. The probability of random node falling in the circle of radius r is  $\pi r^2$ . Let  $d_{ij}$  be the distance from node i to node j. Let  $r = 1/(c\sqrt{n})$  for some constant c.

Let  $E[Min(d_{ij})i \neq j] \equiv E[D(i)]$ , D(i) are i.i.d. (identical and independent distribution) in the unit square. By definition of expectation, we have

$$E[D(i)] = Prob[D(i) \le r](E[D(i)|D(i) \le r]) + Prob[D(i) > r](E[D(i)|(D(i) > r)]) \tag{1}$$

First term is bounded by 0. We bound the second term using probability theory as follows.

$$D(i) > r = \bigcap_{i \neq j} (d_{ij} > r)$$

for all  $i$ ;

$$Prob[D(i) > r] \ge 1 - prob\left[\bigcap_{i \neq j} (d_{ij} > r)\right]$$

since  $p(A) = 1 - p(\overline{A})$

By De'Morgan's Law, complement of intersection is union of the complement, hence for independent events, we have

$$Prob[D(i) > r] \ge 1 - \sum_{i=1}^{n} prob[d_{ij} \le r]$$

, where N is number of nets.

$$Prob[D(i) > r] \ge 1 - \sum_{i=1}^{n} (\pi r^2) = 1 - n(\pi r^2)$$

(2)

Since E[D(i)|(D(i)>r)] is bounded by Nr, equation (1) becomes

$E[D(i)] \ge 0 + [1 - n(\pi r^2)](nr) = nr - n^2 r^3 = (n)(1/(c\sqrt{n})) + (n^2)(1/(c^3n^{3/2})) = c1\sqrt{n} + c2\sqrt{n}$

This proves that SPTP(N) is bounded from below by  $\sqrt{n}$  (ignoring constants) since SPTP(N) has to be at least equal to or greater than expected value of D(i) over all i where i is node of probed net.

Since for some constants  $C_1$  and  $C_2$ , from upper bound and lower bound analysis, we have

$$c_1 \sqrt{n} \le SPTP(N) \le c_2 \sqrt{n}$$

SPTP(N) =  $\theta(\sqrt{n})$ . Q.E.D.

**Lemma 1:** Given  $\rho\sqrt{2n}$  and  $\alpha\sqrt{n}$  as bounds on expected value of TSPTP(N) and SPTP(N) respectively,  $\alpha < \rho\sqrt{2}$ .

**Proof:** Obvious from upper bound analysis of theorem 2.

**Theorem 3:** Let  $\rho\sqrt{2n}$  be the expected value of TSPTP(S) and Let  $\alpha\sqrt{n}$  be expected value of SPTP(S). Then  $\rho\sqrt{2n} \le 2\alpha\sqrt{n}$

**Proof:** Consider TSPTP(N) and SPTP(N) for nets with 2 nodes each. The average saving per edge in constructing solution SPTP(N) from TSPTP(N) is  $(\rho\sqrt{2n})/(2n)$ . Since we remove n edges to construct solution SPTP(N), bound on expected value of SPTP(N) can

be obtained easily as  $\rho\sqrt{2n}-n(\rho\sqrt{2n})/(2n)=(\rho\sqrt{2n})/2$ . Since SPTP(N) must be at least  $((\rho\sqrt{2n})/2)$ , we have  $((\rho\sqrt{2n})/2) \le \alpha\sqrt{n}$ . Hence  $\rho\sqrt{2n} \le 2\alpha\sqrt{n}$ . Q.E.D.

The worst-case and average case behavior of SPTP and DPTP has been analyzed rigorously in [42] and it is shown that for substrates with 2 to 3 terminal pads in each of n nets, the expected travel time for a single test probe is shorter by a factor of order  $n^{1/4}$ .

#### 3.4 Integer Programming Formulation

The mathematical formulation of the single probe routing problem corresponding to the problem statement in Section 3.1 is described in [43] and restated below for completeness. An iteration t refers to the movements made by the single probe in the  $t^{th}$  step of the probe sequence, with t = 1 corresponding to the terminal from which the probe tour is started.

In this formulation the variables are defined as follows:

$Z_{iit} = 1$ , if terminal j of interconnect i is probed during iteration t

$Z_{iit} = 0$  , otherwise

$X_{ijkl} = 1$  , if probe moves from terminal j of interconnect i to terminal l of interconnect k

$X_{ijkl} = 0$  , otherwise

and the problem data are given by

$n_i = Number of terminals of interconnect i$

N = Number of interconnects of given substrate

$C_{ijkl}$  = Cost of moving from terminal j of interconnect i to terminal l of

interconnect k

$$minimize \qquad \sum_{ijkl} C_{ijkl} X_{ijkl} \tag{1}$$

subject to

$$\sum_{t=1}^{N} \sum_{i=1}^{n_i} Z_{ijt} = 1, \forall i$$

(2)

$$\sum_{j} \sum_{i} Z_{ijt} = 1, (t = 1, 2, ...N)$$

(3)

$$X_{iikl} \ge Z_{iit} + Z_{kl(t+1)} - 1, (t = 1, 2, ...(N-1))$$

(4)

All the variables are binary. Equation 1 states that the total cost of traveling from a terminal of an net to the terminal of the next net is to be minimized over all the terminals.

Equation 2 restricts each single probe to contact each net at one and only one terminal.

Equation 3 ensures that two nets can not be probed at the same time. Equation 4 links auxiliary variable X to main variable Z.

This formulation gives an exact solution technique for solving very small instances of

SPTP. However since SPTP is similar to the TSP (a well-known NP complete problem), SPTP must also be NP-Hard. We prove this in the following section.

#### 3.5 Complexity Analysis

Following theorem proves that SPTP and DPTP are computationally hard to solve.

**Theorem 4:** SPTP and DPTP are NP-Hard.

**Proof:** We assume that we have a deterministic polynomial time algorithm SPTP\_Solver to solve SPTP. Assume SPTP instance has N nets of 2 nodes each. By applying SPTP\_Solver, we get optimal tour of N nodes (one from each net). We shall use SPTP\_Solver to solve related euclidean TSP. Let X1, X2...Xn be an instance of TSP where each Xi is a node selected uniformly within a square unit of width. Let Xn+i = Xi for i = 1..n. Let an instance of SPTP be defined as net i  $\{Xi, Xn+i\}$  where i = 1..n. We give above stated TSP instance to the SPTP\_Solver. Obviously since for each net, both nodes are in the same location, an optimal solution to the instance of SPTP yields an optimal solution to the instance of TSP. It follows therefore that we can use SPTP\_Solver to solve TSP on N nodes. Alternatively if we consider each net of infinite length as shown in the Figure 9, we have a polynomial time algorithm for N node optimization version of TSP. But since optimization version of TSP has the same claim to intractability as any NP-Complete problem, there is no polynomial time algorithm to solve decision version TSP optimally unless P = NP. It follows consequently that we can not have deterministic polynomial time algorithm to solve SPTP unless P = NP. Q.E.D.

FIGURE 9. Two Point Nets of Infinite Lengths

For 2PTP, again consider instances with 2 nodes per net, where the first node of each net is located in the small square  $[0,.2]^2$ . Let  $\varepsilon$  denote the least distance between first nodes. Place all the second nodes in a circle of diameter  $\varepsilon$  centered at  $\{0.8, 0.8\}$ . Then one probe will visit all the first nodes, and its travel times will dominate the second probe's times. Solving 2PTP on these instances is equivalent to solving the TSP instance defined by the first nodes.

Q.E.D.

## 3.6 Analysis for Practical MCM Substrate Testing

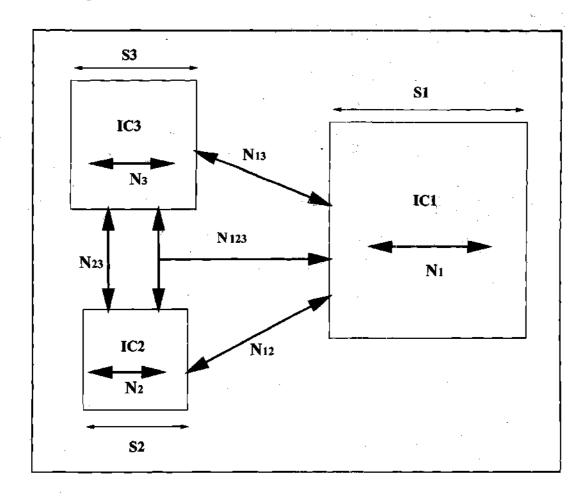

Application of the theoretical analysis to optimize test cost for connectivity verification of MCM Substrates is discussed is detail in this section. Typical MCM substrate is shown in Figure 10.

FIGURE 10. An Example Substrate

Our example substrate consists of three chips namely, IC1, IC2 and IC3, representing a typical microprocessor, a peripheral controller IC and a memory chip such as DRAM. We denote respective sizes of these chips by S1, S2 and S3. Let N<sub>i</sub> denote number of nets

completely within Chip i, Let  $N_{ij}$  denote number of nets between chips i and j and  $N_{ijk}$  denote number of nets that connect all three chips. where i, j belongs to  $\{1,2,3\}$ . Obviously  $N_{ij} = N_{ji}$ . We claim that the expected value of SPTP tour cost for net integrity test for a chip mounted on MCM substrate is proportional to the size of the chip. For our model we have all the chips with square footprints. Thus without loss of generality we can use the theorem 2 developed on unit square substrate to calculate bound on SPTP tour cost for a particular chip. Total SPTP tour cost for testing net integrity of chip i of size  $S_i$  with  $N_i$  nets is thus bounded by the product  $S_i \times \sqrt{N_i}$ . Total MCM substrate test cost can be modeled in many different ways depending on the choice of nodes selected for probing. For our example substrate, two options are described out of many different options available.

Option 1: Single probe testing is started at IC1. Testing of nets  $N_{123}$ ,  $N_{12}$ ,  $N_{13}$  and  $N_1$  is performed by probing the nodes terminating at IC1. Then the probe is moved to IC2 to test the nets  $N_2$  and finally the probe traverses to the IC3 and the nets  $N_{23}$  and  $N_3$  are tested. Then the probe traversal cost for the example substrate of is bounded by  $S_1 \times \sqrt{N_{123} + N_1 + N_{12} + N_{13}} + S_2 \times \sqrt{N_2} + S_3 \times \sqrt{N_3 + N_{23}}$ .

Option 2: Single probe testing of the example substrate can also be done by first probing nets  $N_1$  at IC1. Then the probe is moved to IC2 and nets  $N_{12}$  and  $N_2$  are tested by probing nodes terminating at IC2. Finally the probe traverses to IC3 and nets  $N_{123}$ ,  $N_{13}$ ,  $N_{23}$  and

N<sub>3</sub> are tested to complete the substrate test. With this option, the overall probe traversal cost for the example substrate of is bounded by

$$S_1 \times \sqrt{N_1} + S_2 \times \sqrt{N_2 + N_{12}} + S_3 \times \sqrt{N_3 + N_{23} + N_{13} + N_{123}} \,.$$

It is clear that these bounds give a way to select the best option from the physical netlist, so that substrate test time using the single probe can be optimized. The analysis shows that the traversal cost depends on the footprint sizes of the constituent ICs of an MCM as well as the die level netlist of the substrate which defines the interchip interconnections. For a substrate with an IC having maximum percentage of connectivity with other ICs, testing all the nets belonging to that IC at the location of that IC itself, might reduce the overall test time for single probe technique. Thus, the computation of theoretical bounds on the test cost proves to be effective tool in the CAD environment, especially for bigger MCM substrates.

# **CHAPTER IV**

# HEURISTIC ALGORITHMS FOR

# SINGLE PROBE TESTING

In this chapter, two practical heuristic algorithms to optimize traversal cost of a single probe for testing MCM substrate interconnects, are discussed in detail. Experimental results confirm the validity of these algorithms. The comparison of test times using single and double probe technique on a benchmark MCM netlist is presented.

#### 4.1 Heuristic for Efficient Traversal of Single Probe

Since SPTP is NP-hard, solving even a moderate size problem with the mathematical formulation is apt to be impractical. Considering the large number of interconnections on an MCM substrate any attempt at using an exact solution procedure will prove to be less practical. In view of the complexity of the problem, a heuristic procedure to solve the SPTP is proposed and is presented in the following sections. Below, some important definitions related to the problem are given.

- •A <u>net</u> represents a set of interconnected layers of substrate corresponding to a single electrical node. Each net has more than one terminal on the topmost layer of the substrate and is identified uniquely by a net identifier. A netlist is a list of all nets with their associated net identifiers and terminals each net connects.

- •A <u>terminal</u> is a pad on the topmost layer of substrate that is probed during substrate testing. Each terminal belongs to only one net. The terminals are used to provide electrical connections to the ICs that are bonded to the substrate during MCM assembly.

- •A <u>terminal tour</u> is the sequence of terminals to be probed. It consists of one terminal from each net in the netlist.

- •A <u>subtour</u> is defined to be a sequence of net terminals connected by edges (probe traversal paths), but not necessarily including a terminal from each net.

- •A net is <u>unprobed</u> if none of its terminals is in the current subtour.

- •The cost C(i, j) of an edge of a subtour is the Euclidean distance between the two terminals i and j on which that edge is incident.

- •The tour cost is the sum of costs of all the edges in the terminal tour.

A heuristic procedure for efficient single probe tour construction is described below. This procedure takes MCM netlist and Insert\_Mode as an input parameters along with other optional parameters such as Shuffle\_Mode and Improve\_Flag. The Insert\_Mode selects either an arbitrary insertion or a farthest insertion heuristic explained in Section 4.3. The Shuffle\_Mode activates or deactivates the shuffle procedure used for further optimization of the tour cost. Improve\_Flag is of type boolean which, when TRUE,

enables improved version of Insert and Shuffle procedures explained in Section 4.3 and Section 4.4 respectively.

```

Procedure Construct_Terminal_Tour

Input: Die level netlist of an MCM substrate, Inseit_Mode, Shuffle_Mode, Improve_Flag

Output: terminal tour to be probed using a single probe and corresponding tour cost.

Construct_Terminal_Tour {

subtour = Init_Tour(Insert_Mode);

While ( (there are unprobed nets) and (subtour is NOT equal to a terminal tour)) {

if (Insert_Mode == Arbitrary_Insertion)

Select an unprobed net randomly;

else /* Insert_Mode == Farthest_Insertion */

Select an unprobed net with maximum distance to the current subtour;

Insert (subtour, selected unprobed net, Improve Flag);

} /* end while */

if (Shuffle_Mode is activated)

Shuffle(terminal tour, Improve_Flag);

Compute terminal tour cost.

Return terminal tour;

```

#### 4.2 Init\_Tour Procedure

This procedure initializes the sequence of terminals to be probed by selecting the first terminal of the tour. The method of initialization depends on the Insert\_Mode.

```

Init_Tour (Insert_Mode) {

if (Insert_Mode == Arbitrary_Insertion) {

Randomly select a terminal of the arbitrarily selected net and initialize the terminal tour;

Find the nearest neighbor of the start terminal and construct a subtour;

}

else { /* Insert_Mode == Farthest_Insertion */

For every possible pair of nets S and T, compute

the distance D(S,T) = minimum over all nodes s in S, nodes t in T;

Select a pair of nets which are farthest from each other i.e. maximize D(S,T) to construct

a subtour;

}

return subtour;

```

#### 4.3 Insert Procedure

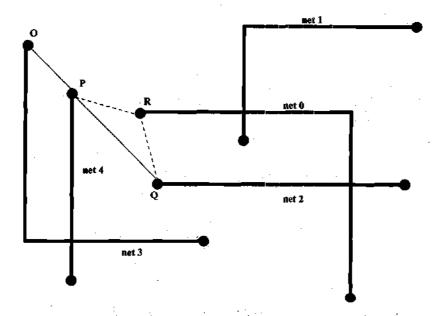

This procedure is based on the using either the arbitrary insertion or the farthest insertion heuristic to construct a TSP tour. For arbitrary insertion, an unprobed net is selected randomly. For farthest insertion, a distance of the net to a subtour is defined as the minimum of the distances of every node of the net from every member of the current subtour. For example suppose the current subtour has nodes a, b, c. Suppose net S contains nodes sI and sI. Then the distance from net S to the subtour is given by

$$min(d(a,s1),d(b,s1),d(c,s1),d(a,s2),d(b,s2),d(c,s2))$$

For this step, the unprobed net with maximum distance to the subtour is selected [44]. For each terminal r of the selected unprobed net using either of the insertion heuristic described above, the edge pq of the subtour is found such that Cpr + Crq - Cpq is minimized [45]. The terminal r is inserted between p and q. As an example in Figure 11, the current subtour consists of the terminals O, P, and Q of net 3, net 4, and net 2, respectively. Terminal R is to be inserted between P and Q to form a new subtour O-P-R-Q and compute the corresponding subtour cost. The *Improved Insertion* procedure consists of selecting the best terminal of the net with the best subtour cost and inserting that terminal and form a new subtour. This improvement procedure is repeated till an optimized terminal tour is constructed.

**FIGURE 11. Insertion Procedure**

The pseudo code for improved insertion is given below.

```

Insert (subtour, selected unprobed net, Improve_Flag) {

if (Improve_Flag is TRUE) { /* improved insert */

While (cost computations of all the terminals of the selected net are not complete) {

Select a terminal of the net.

Find minimum edge cost for insertion and insert the terminal in the current subtour.

Find the new subtour cost.

Select the terminal with minimum cost and insert in the current subtour.

}

else

Find minimum edge cost for insertion and insert the terminal in the current subtour.

}

```

The improved insertion gives a terminal tour with an improved tour cost. To further improve the tour cost, the shuffle procedure, below, is invoked.

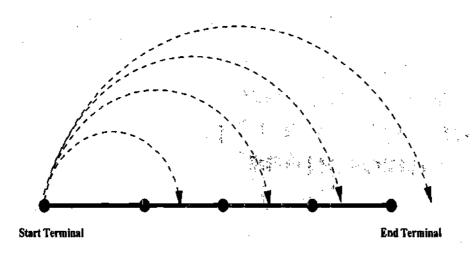

#### 4.4 Shuffle Procedure

FIGURE 12. Shuffling of 5 Terminal Tour

Given a terminal tour, sequentially drop every terminal in the tour out of its present position and insert it at every alternative position within the tour sequence and compute the total tour cost. This simple shuffling procedure is illustrated in Figure 12. The pseudo code for the procedure is also given.

When every terminal of the tour is selected, the shuffling procedure is repeated for all the terminals of the net to which the selected terminal belongs. In each cycle, we select the

best terminal of the respective net so that the total tour cost is minimized. This is an Improved Shuffling procedure.

```

Shuffle (terminal tour, selected unprobed net) {

for each terminal of the terminal tour {

find the corresponding net.

if (Improve_Flag is TRUE) { /* improved shuffle */

While (all the terminals of selected net are not effecked for minimum cost) {

Select a terminal of the net.

Delete the terminal from the tour and insert it at every alternative position in the tour.

Find out the terminal tour with minimum cost.

Select the terminal for which terminal tour cost is minimum and return terminal tour.

}

clse

{

Delete the terminal from the tour and insert it at every alternative position in the tour.

Find out the terminal from the tour and insert it at every alternative position in the tour.

Find out the terminal tour with minimum cost.

Select the terminal tour minimum cost and return that terminal tour.

}

```

Any heuristic offers a trade-off between computational complexity and performance. The performance of the probe routing optimization can be improved by including higher level shuffling (2 terminals at a time) but only at the expense of a substantial increase in computing cost. If there are m terminals per net and the total number of nets are n, then the complexity of the improved insertion procedure is  $O(m \cdot n)$  and the complexity of the improved shuffling procedure is  $O(m^2 \cdot n)$ . If there are m terminals per interconnection and the total number of interconnections is n, then the complexity of the selecting farthest

net is  $O(n^2 \cdot m)$ . This time complexity is justified since, to find the optimal route of a single probe, this algorithm is executed only once and then program the solution into the probe contoller scheme.

#### 4.5 Experimental results

The proposed heuristic algorithm was implemented in 'C' and tested on different test problems on a SUN Ultra-2 SPARCstation hardware platform. Table 2 shows the step by step improvement of the traversal cost by applying different heuristic procedures discussed in the previous section. First column lists the heuristic procedures applied. For improved insert heuristic, Construct\_Terminal\_Tour procedure is called with Improve Flag set to boolean value TRUE. For improved shuffle, Shuffle Mode in Construct Terminal Tour procedure is activated. Second column lists number of nets in the netlist. Corresponding terminals per net are shown in the third column. The tour costs which are obtained using different heuristics are noted in the fourth column. These tour costs are computed using Euclidean norm. The CPU time for executing Construct Terminal Tour procedure is computed using gprof utility in Unix and noted in the fifth column. The last column shows percentage improvement in the terminal tour cost over the tour cost obtained using insert procedure without improvement and shuffling. This tour cost improvement was calculated as follows. Let A be the tour cost for a given netlist with insert procedure without improvement. Let B be the tour cost for the same netlist with improved insert procedure. Then percentage improvement in the tour cost for

that netlist is given by  $\frac{A-B}{A} \times 100$ . A netlist consisting of 576 nets with four terminals per

TABLE 2. Probe Route Cost Optimization With Different Heuristics