# Modeling of Simultaneous Switching Noise in On-Chip and Package Power Distribution Networks Using Conformal Mapping, Finite Difference Time Domain and Cavity Resonator Methods

$\begin{array}{c} {\rm A~Thesis} \\ {\rm Presented~to} \end{array}$  The Academic Faculty

by

Jifeng Mao

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

School of Electrical and Computer Engineering Georgia Institute of Technology August 2004

# Modeling of Simultaneous Switching Noise in On-Chip and Package Power Distribution Networks Using Conformal Mapping, Finite Difference Time Domain and Cavity Resonator Methods

| Approved by:                  |              |

|-------------------------------|--------------|

| Madhavan Swaminathan, Advisor | Sung Kyu Lim |

| David C. Keezer               | C. P. Wong   |

| Abhijit Chatterjee            |              |

Date Approved: October 6th 2004

# Dedicated to 献给

my father, Liming Mao 我的父亲, 毛黎明

my mother, Zujuan Zhu 我的母亲, 朱祖娟

my sister, Yanling Mao 我的妹妹, 毛燕凌

for their love and support 为了他们对我的爱和支持

# ACKNOWLEDGEMENTS

First, I want to thank my advisor, Professor Madhavan Swaminathan, for his guidance and support during my graduate studies. He is an outstanding scientist, mentor, and a tremendous source of motivation. I will always be grateful for his valuable advice and insight. I would also like to extend my gratitude to the Ph.D. committee: Professor Abhijit Chatterjee, Professor David C. Keezer, Professor Sung Kyu Lim, and Professor C.P. Wong. I appreciate their time and effort in serving on my committee. I also thank Professor Zhengfan Li, who was the advisor of my master thesis in Shanghai Jiao-Tong University.

I extend special thanks to all current and graduated members of the research group. Your friendship, assistance, and opinions will always be appreciated. I would especially like to mention Nanju Na, Sungjun Chun, Sung-Hwan Min, Vinu Govind, Woopoung Kim, Erdem Matoglu, Jinwoo Choi, Jinseong Choi, Sidharth Dalmia, Bhyrav Mutnury, Prathap Muthana, Sujeet Vaidya, Rohan Mandrekar, Hideki Sasaki, Amit Bavisi, Tae Hong Kim, Wansuk Yun, Raghavan Madhavan, Di Qian, Joongho Kim, Krishna Srinivasan, Subramanian Natarajan Lalgudi, Souvik Mukherjee, Suna Choi and Lixi Wang.

I would like to thank James Libous and Daniel O'Connor at IBM for their support and encouragement for my studies.

I would like to thank my dear friends, Hang Chen and Yanfeng Chen, Yandong Su, Bao Mi for their friendship and encouragement.

Finally, I would like to thank my parents, Liming Mao and Zujuan Zhu, and my sister Yanling Mao for their love, support, guidance, and encouragement.

# TABLE OF CONTENTS

| DED  | OIC  | ATION   | 1                                                                       | iii |

|------|------|---------|-------------------------------------------------------------------------|-----|

| ACK  | NC   | WLE     | DGEMENTS                                                                | iv  |

| LIST | C OI | F TAB   | BLES                                                                    | ix  |

| LIST | OI   | F FIG   | URES                                                                    | x   |

| CHA  | PΤ   | ER I    | INTRODUCTION                                                            | 1   |

| 1    | 1.1  | Availa  | ble methods for modeling power distribution networks                    | 2   |

| 1    | 1.2  | Modeli  | ing of multilayered power and ground planes                             | 5   |

|      |      | 1.2.1   | Inductor network method                                                 | 5   |

|      |      | 1.2.2   | Transmission line method                                                | 9   |

|      |      | 1.2.3   | Transmission matrix method                                              | 13  |

|      |      | 1.2.4   | Modeling the power planes with FDTD method                              | 17  |

|      |      | 1.2.5   | Cavity resonator method                                                 | 18  |

| 1    | 1.3  | Modeli  | ing of on-chip power grid                                               | 21  |

|      |      | 1.3.1   | Modeling of on-chip interconnect                                        | 22  |

|      |      | 1.3.2   | Chip level simulation                                                   | 30  |

|      |      | 1.3.3   | Hierarchical analysis of on-chip power distribution networks            | 32  |

|      |      | 1.3.4   | Multigrid method                                                        | 34  |

|      |      | 1.3.5   | Latency insertion method and circuit based FDTD                         | 36  |

| 1    | 1.4  | Compl   | eted research                                                           | 39  |

| 1    | 1.5  | Dissert | tation Outline                                                          | 42  |

|      |      | ERII    | MODELING OF FIELD PENETRATION THROUGH PLAN                              |     |

|      |      |         | ILAYERED PACKAGES                                                       | 43  |

|      | 2.1  |         | ing of field penetration through planes in multi-layered packages       | 44  |

|      | 2.2  |         | to measurement correlation                                              | 51  |

|      | 2.3  |         | ation of a switching microprocessor in high speed computer applications |     |

|      | 2.4  |         | ession of power plane coupling between layers                           | 57  |

| 2    | 2.5  | Summa   | ary                                                                     | 59  |

| CF |     |         | II MODELING OF ON-CHIP POWER GRID ON LOSSY SUBSTRATE                             | 63                |

|----|-----|---------|----------------------------------------------------------------------------------|-------------------|

|    | 3.1 | Model   | ling of CPW on lossy silicon substrate                                           | 64                |

|    |     | 3.1.1   | Relationship between CPW and on-chip power grid                                  | 64                |

|    |     | 3.1.2   | Field pattern of CPW on silicon substrate                                        | 65                |

|    |     | 3.1.3   | Parasitic extraction of CPW over lossless substrate                              | 67                |

|    |     | 3.1.4   | Effect of lossy silicon substrate on CPW characteristics                         | 69                |

|    |     | 3.1.5   | Model to measurement correlation                                                 | 71                |

|    | 3.2 |         | itic extraction for coplanar multi-conductor lines in on-chip power grid rks     | 71                |

|    |     | 3.2.1   | Field distribution on M1 layer                                                   | 72                |

|    |     | 3.2.2   | Parasitic extraction                                                             | 75                |

|    |     | 3.2.3   | Accuracy of the extracted model                                                  | 79                |

|    |     | 3.2.4   | Comparison between CMC and CPW structure                                         | 80                |

|    |     | 3.2.5   | Effect of SiO <sub>2</sub> thickness                                             | 82                |

|    | 3.3 | FDTI    | O simulation for the on-chip power grid                                          | 83                |

|    |     | 3.3.1   | Representing an on-chip power grid using constant RLGC parameters                | 83                |

|    |     | 3.3.2   | Implementation of FDTD for constant RLGC circuit model of on-<br>chip power grid | 85                |

|    |     | 3.3.3   | Debye approximation for inclusion of frequency dependent RLGC circuit model      | 86                |

|    |     | 3.3.4   | Implementation of Debye model in FDTD algorithm                                  | 91                |

|    | 3.4 | Full-cl | hip power supply simulation                                                      | 92                |

|    | 3.5 | Simul   | ation for on-chip power grid with various power densities                        | 97                |

|    | 3.6 | Summ    | nary                                                                             | 102               |

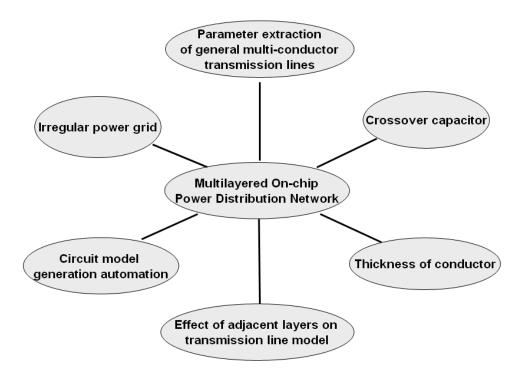

| CF |     |         | W MODELING OF MULTILAYERED ON-CHIP POWER DIS                                     | -<br>L <b>O</b> 3 |

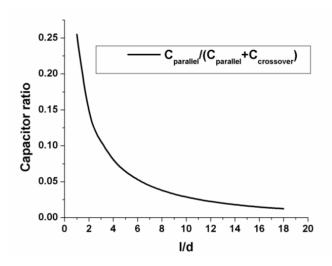

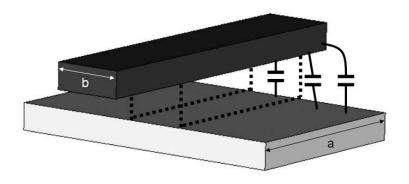

|    | 4.1 | Crosso  | over capacitance of power buses                                                  | 103               |

|    |     | 4.1.1   | Effect of coplanar neighboring interconnects                                     | 105               |

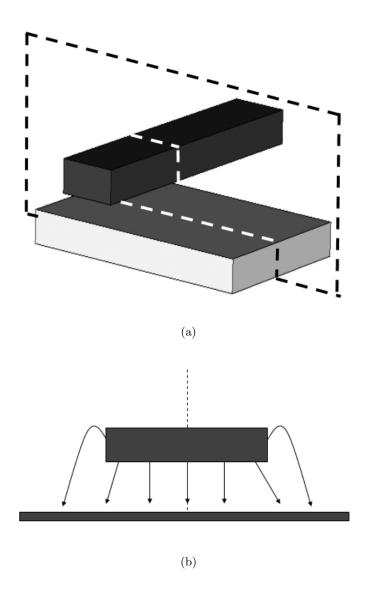

|    |     | 4.1.2   | Fringing distance                                                                | 106               |

|    |     | 4.1.3   | Conformal mapping for calculating crossover capacitance                          | 109               |

|    |     | 4.1.4   | Capacitor results                                                                | 114               |

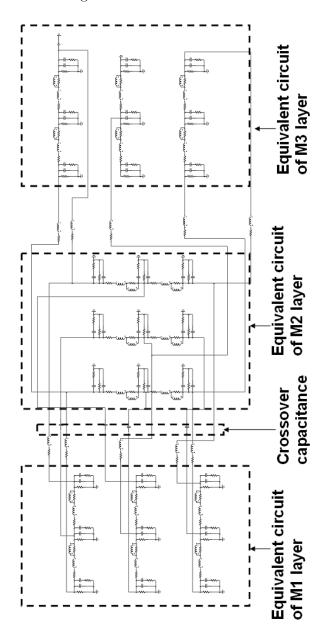

|     |      | 4.1.5   | FDTD implementation with crossover capacitance                                | 114 |

|-----|------|---------|-------------------------------------------------------------------------------|-----|

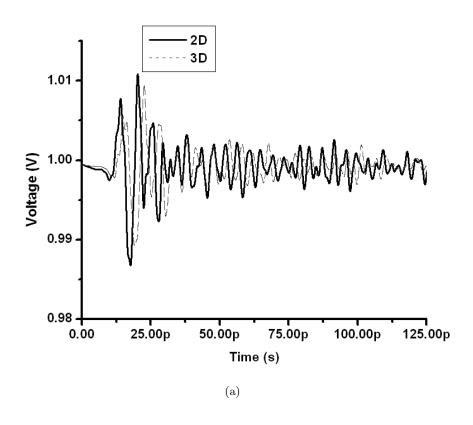

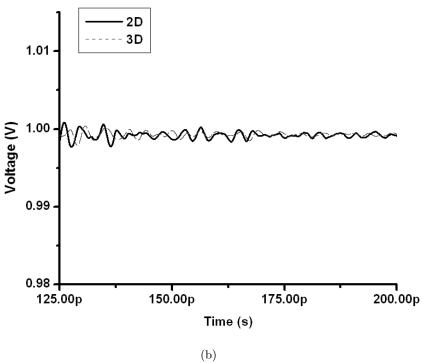

|     |      | 4.1.6   | Power grid simulation with crossover capacitance $\dots \dots$ .              | 118 |

|     | 4.2  | Param   | eter extraction for generic on-chip layout                                    | 121 |

|     |      | 4.2.1   | Acquiring the equivalent parameters from $N \times N$ matrices                | 126 |

|     |      | 4.2.2   | Inclusion of conductor thickness                                              | 128 |

|     |      | 4.2.3   | Parasitic extraction result                                                   | 128 |

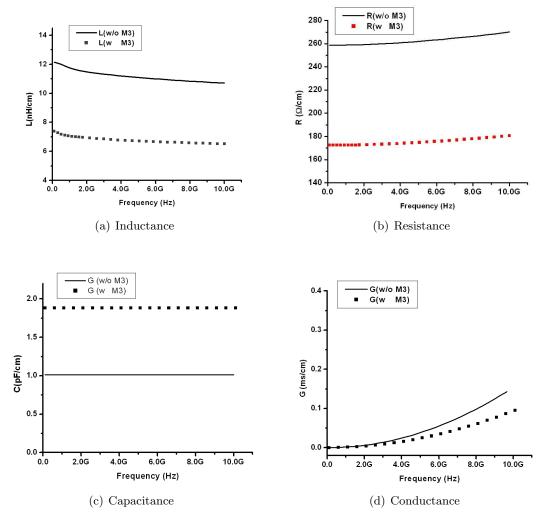

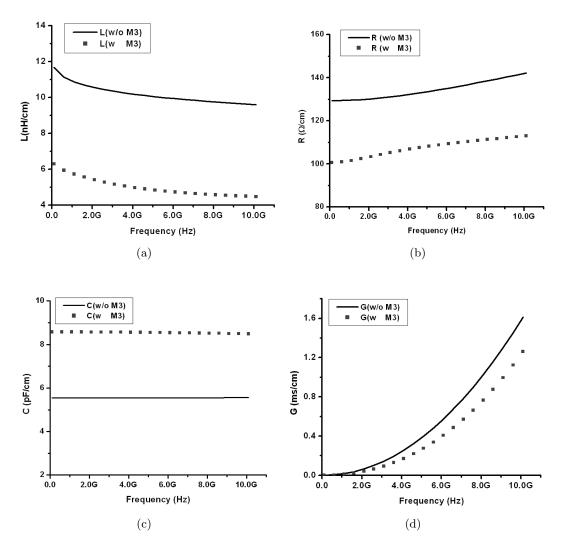

|     | 4.3  | Effect  | of adjacent layers in parasitic extraction                                    | 131 |

|     |      | 4.3.1   | Effect of M3 on the parasitics of interconnects on M1                         | 131 |

|     |      | 4.3.2   | Parasitic extraction for M3 layer                                             | 132 |

|     | 4.4  | Irregul | lar power grid                                                                | 137 |

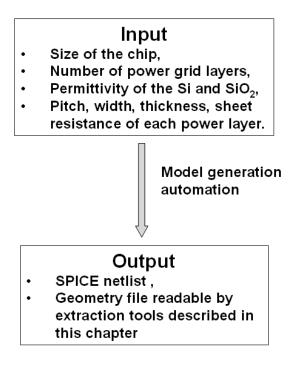

|     | 4.5  | Model   | generation and automation                                                     | 141 |

|     | 4.6  | Summ    | ary                                                                           | 143 |

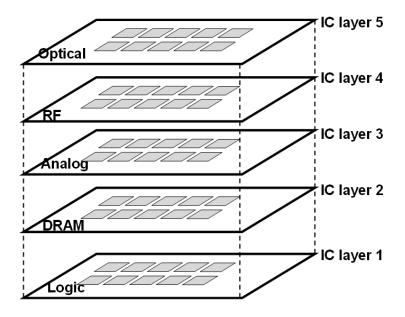

| СН  | APT  | ER V    | PRELIMINARY MODELING OF POWER GRIDS IN THE                                    | REE |

|     | DIM  | IENSI   | ONAL INTEGRATED CIRCUITS                                                      | 145 |

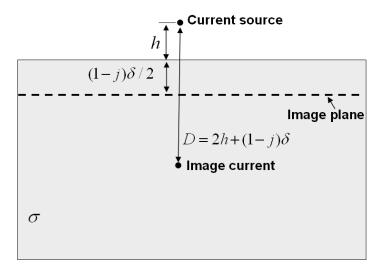

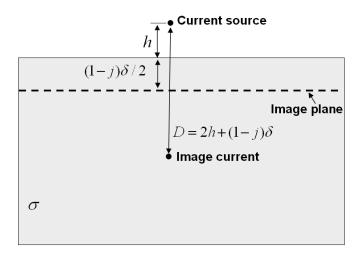

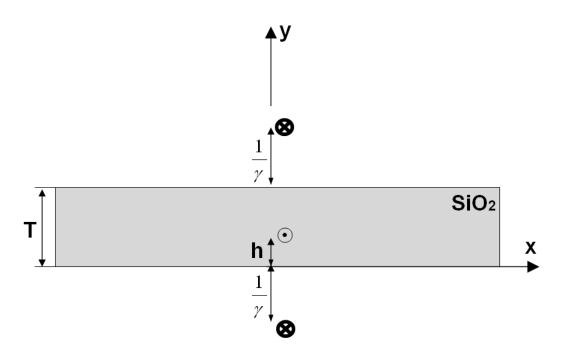

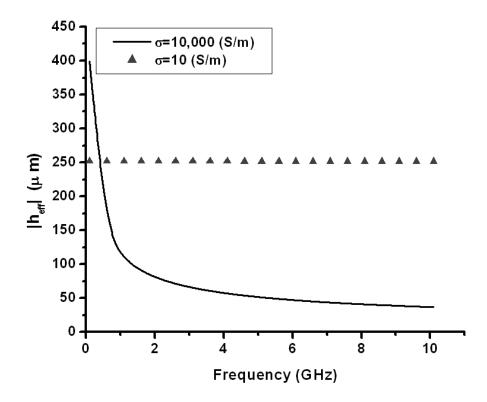

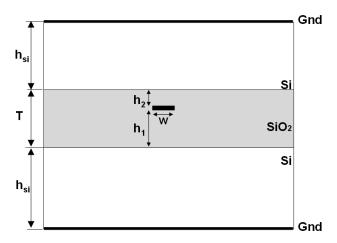

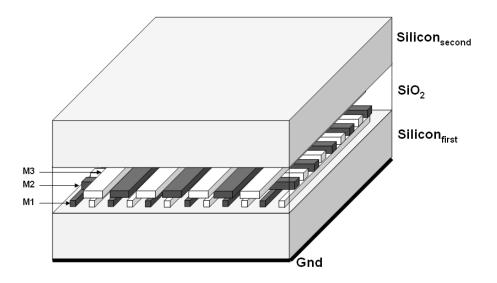

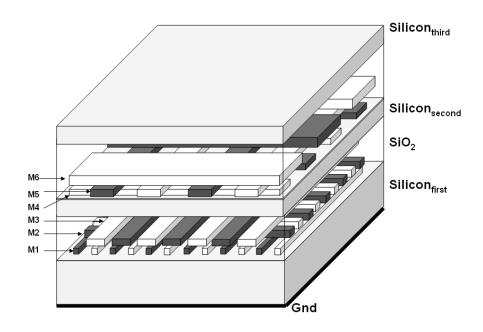

|     | 5.1  | Compl   | ex image for dual conductive substrate                                        | 146 |

|     |      | 5.1.1   | Complex image technique for modeling 2-D interconnects                        | 147 |

|     |      | 5.1.2   | Complex image technique for modeling interconnects in 3-D ICs $$ .            | 149 |

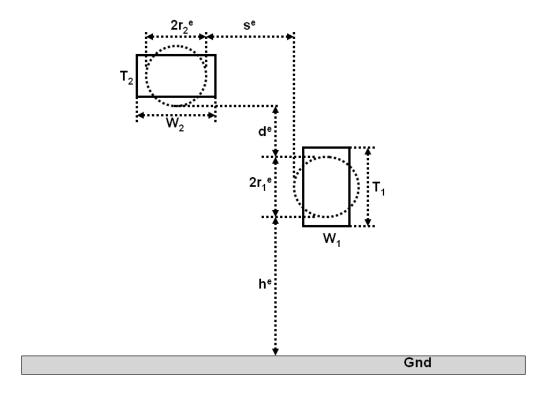

|     | 5.2  | Extrac  | ction of transmission line parameters for interconnects in 3-D ICs $$ .       | 157 |

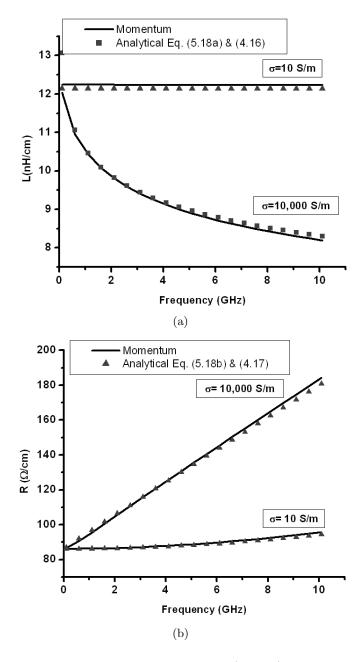

|     |      | 5.2.1   | Transmission line parameter extraction for symmetric interconnects in 3-D ICs | 158 |

|     |      | 5.2.2   | Parameter extraction for asymmetric transmission lines in 3-D ICs             | 164 |

|     |      | 5.2.3   | Parameter extraction for coupled transmission lines in 3-D ICs                | 166 |

|     |      | 5.2.4   | Effect of M3 metal layer on M1 metal layer parasitics in 3-D ICs $$ .         | 170 |

|     | 5.3  | Simula  | ation of power grid of 3-D IC                                                 | 171 |

|     | 5.4  | Simula  | ation of power grid of 3-D IC with various power densities                    | 178 |

|     | 5.5  | Summ    | ary                                                                           | 181 |

| СН  | APT  | ER V    | I CONCLUSION AND FUTURE WORK                                                  | 182 |

|     | 6.1  | Conclu  | isions                                                                        | 182 |

|     | 6.2  | Public  | ation                                                                         | 185 |

|     | 6.3  | Future  | e work                                                                        | 186 |

| DEI | PPD. | FNCF    | <b></b>                                                                       | 180 |

| VITA |  | 199 |

|------|--|-----|

|------|--|-----|

# LIST OF TABLES

| Table 1  | Capacitance result from conformal mapping and FEM                | 80  |

|----------|------------------------------------------------------------------|-----|

| Table 2  | Circuit elements in the first order Debye approximation          | 88  |

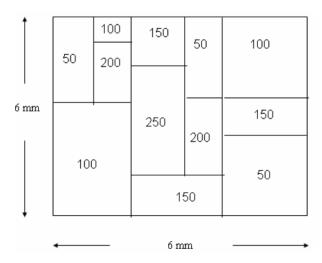

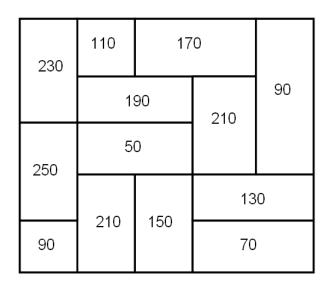

| Table 3  | Coordinates of the blocks with different power density           | 100 |

| Table 4  | Nodes on the boundary for calculating $C_{fringing}$             | 112 |

| Table 5  | Nodes on the boundary for calculating $C_{side\_pul}$            | 113 |

| Table 6  | Crossover capacitance comparison                                 | 114 |

| Table 7  | Parameters of a two-layer power grid                             | 120 |

| Table 8  | Inductance and capacitance of M3 layer                           | 136 |

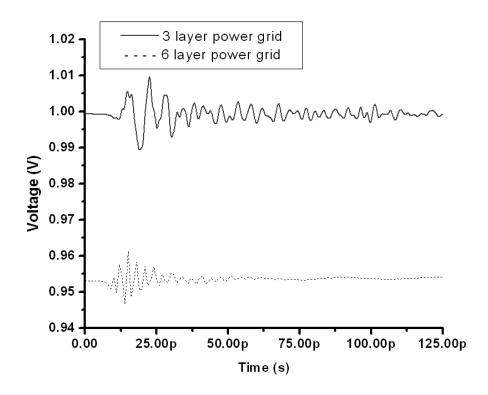

| Table 9  | Impedance parameters of a six-layer power grid                   | 139 |

| Table 10 | Admittance parameters of a six-layer power grid                  | 140 |

| Table 11 | Impedance parameters of a three-layer 3-D power grid             | 174 |

| Table 12 | Admittance parameters of a three-layer 3-D power grid            | 174 |

| Table 13 | Impedance parameters of M4, M5, and M6 metal layer               | 176 |

| Table 14 | Admittance parameters of M4, M5, and M6 metal layer              | 176 |

| Table 15 | Coordinates of the blocks with different power density in 3-D IC | 179 |

# LIST OF FIGURES

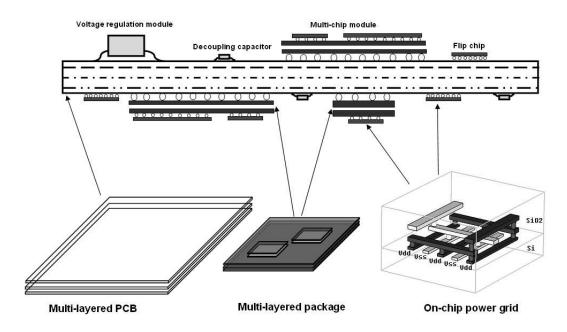

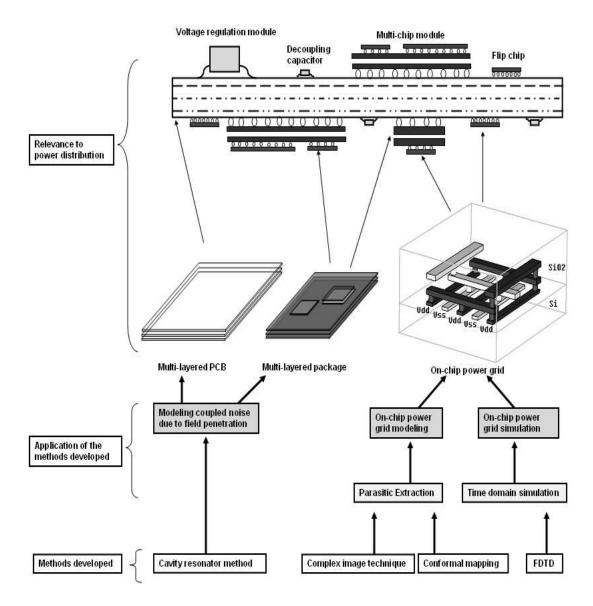

| Figure 1  | Power distribution network of electronic systems                                                                       | 2  |

|-----------|------------------------------------------------------------------------------------------------------------------------|----|

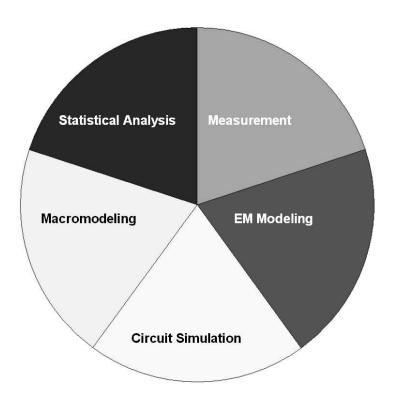

| Figure 2  | Different methods used for power integrity analysis                                                                    | 3  |

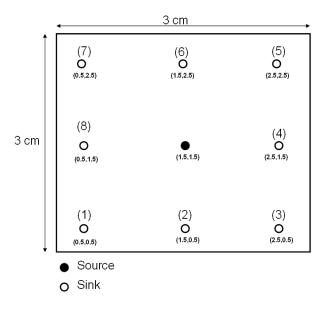

| Figure 3  | Solid plane with eight sink ports                                                                                      | 7  |

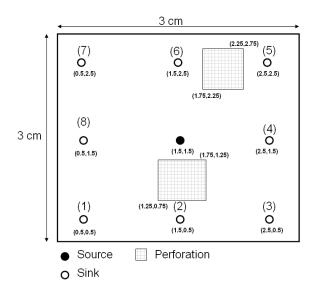

| Figure 4  | Perforated plane with eight sink ports                                                                                 | 8  |

| Figure 5  | Transmission line model for power planes                                                                               | 10 |

| Figure 6  | Transmission line model of (a)a rectangular plane, (b)an arbitrarily plane                                             | 10 |

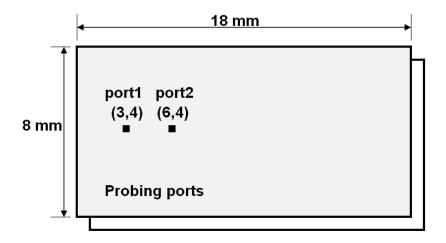

| Figure 7  | Test vehicle of transmission line method                                                                               | 11 |

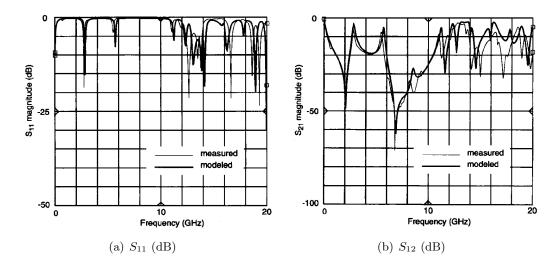

| Figure 8  | Measurement and TL model correlation (a) $S_{11}$ , (b) $S_{12}$                                                       | 12 |

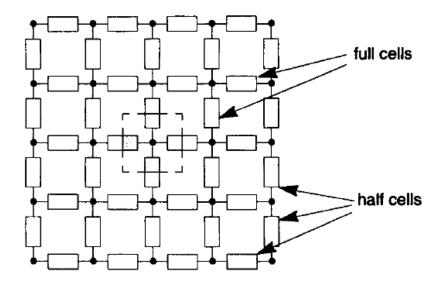

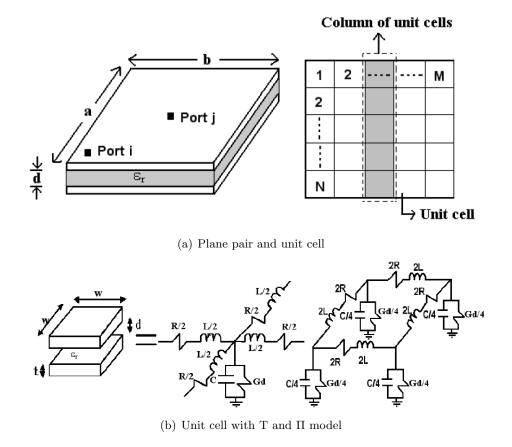

| Figure 9  | TMM model (a) Plane pair and unit cell, (b) T model and $\Pi$ model                                                    | 13 |

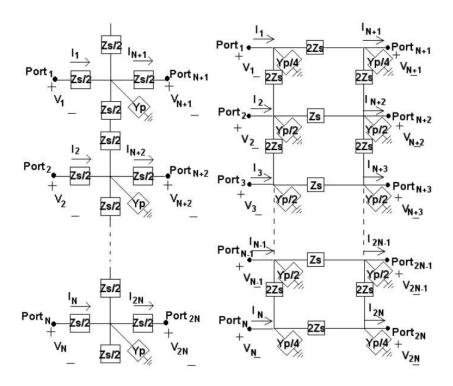

| Figure 10 | Equivalent circuit for a column of unit cells                                                                          | 15 |

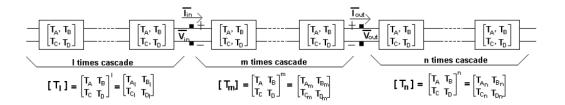

| Figure 11 | Cascading of columns of cells                                                                                          | 16 |

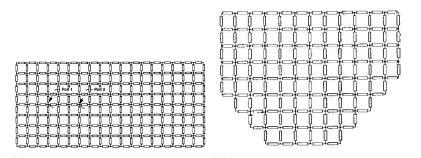

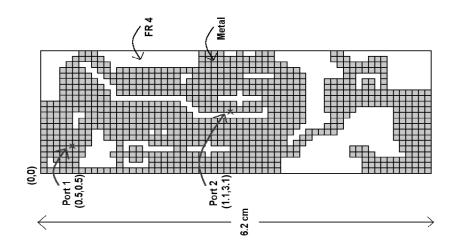

| Figure 12 | Top view of Motorola Bravo Plus pager power plane                                                                      | 16 |

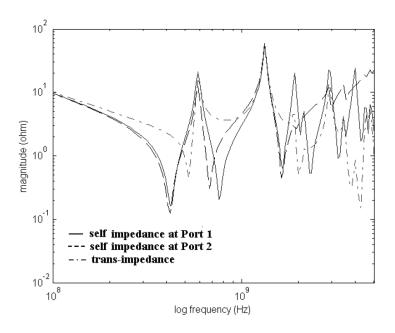

| Figure 13 | Impedance of Motorola pager                                                                                            | 17 |

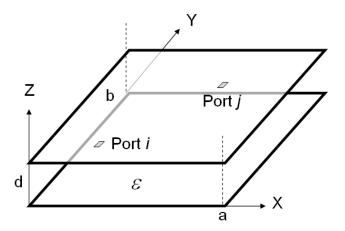

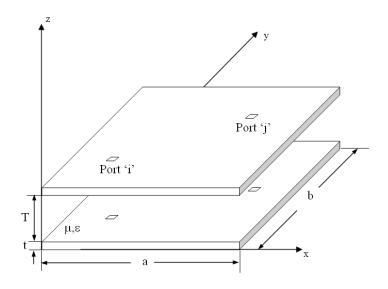

| Figure 14 | Plane pair structure                                                                                                   | 19 |

| Figure 15 | Modeling to hardware correlation for a functioning board                                                               | 21 |

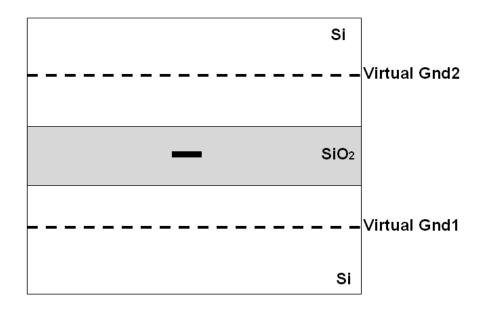

| Figure 16 | Side view of on-chip power grid                                                                                        | 22 |

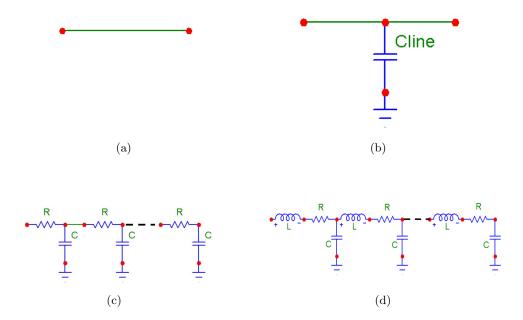

| Figure 17 | Transition of the interconnect model (a) Short circuit , (b) Capacitor model, (c) RC model, and (d) RLC model          | 24 |

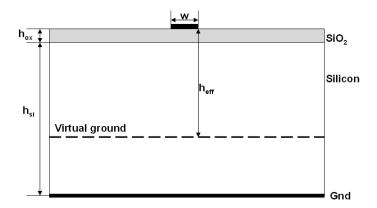

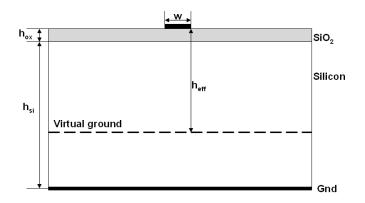

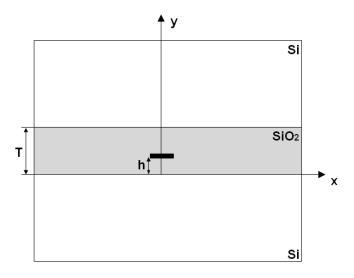

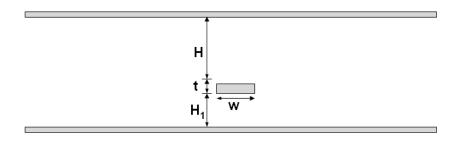

| Figure 18 | Microstrip over $Si$ - $SiO_2$ substrate                                                                               | 25 |

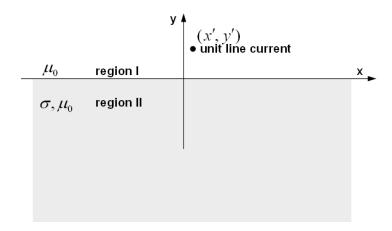

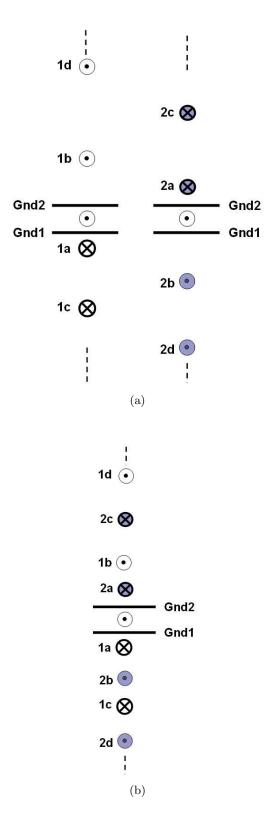

| Figure 19 | Current source over a semi-infinite lossy substrate                                                                    | 27 |

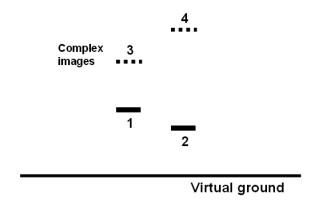

| Figure 20 | Virtual ground plane of current source over lossy substrate                                                            | 28 |

| Figure 21 | Complex image model of source over substrate with ground plane                                                         | 29 |

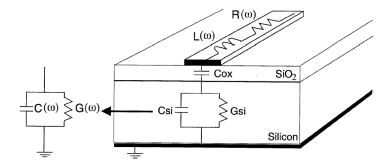

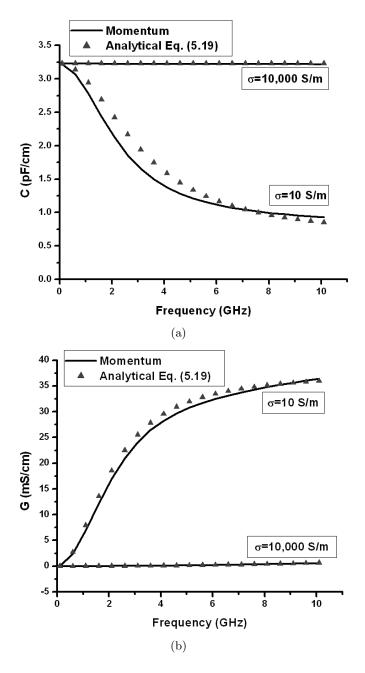

| Figure 22 | $\mathrm{C}(\varpi)$ and $\mathrm{G}(\varpi)$ of a microstrip on silicon substrate                                     | 30 |

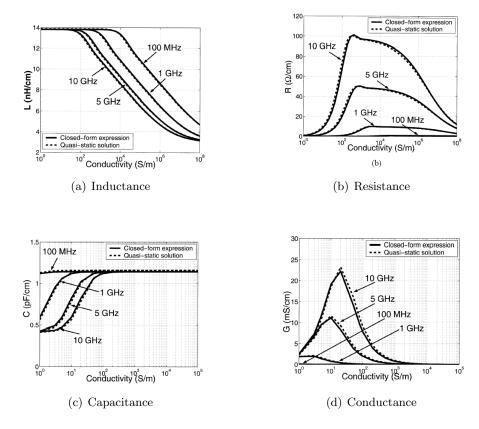

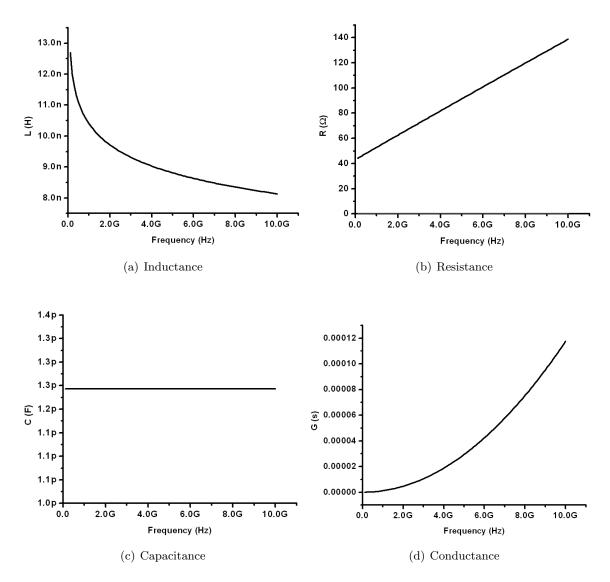

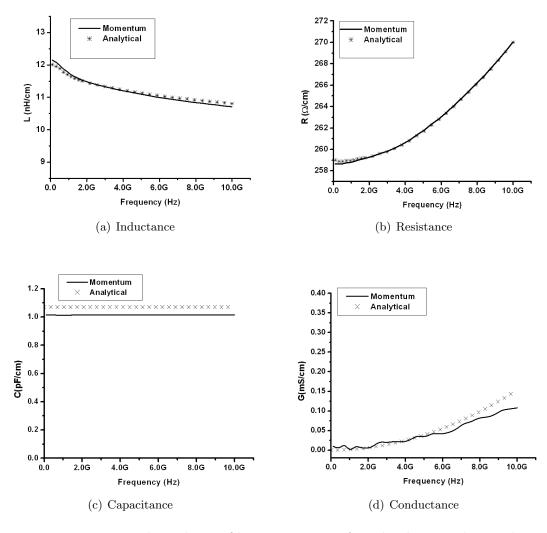

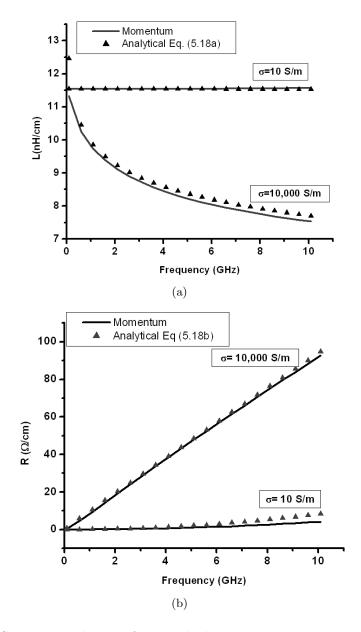

| Figure 23 | RLGC parameter for microstrip over lossy substrate (a) inductance, (b) resistance, (c) capacitance and (d) conductance | 31 |

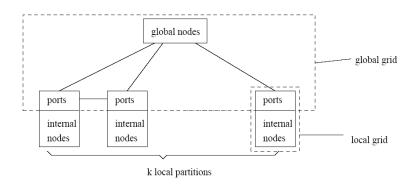

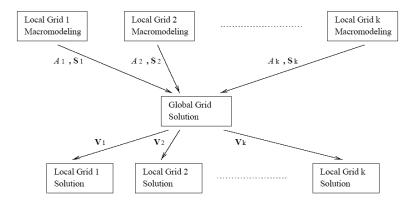

| Figure 24 | Partition for hierarchical analysis                                                                                    | 32 |

| Figure 25 | Data flow for hierarchial analysis                                                                                     | 33 |

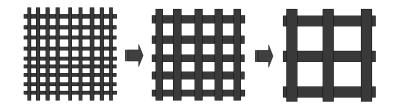

| Figure 26 | Grid reduction                                                                                                         | 35 |

| Figure 27 | Back-mapping process                                                                                                   | 36 |

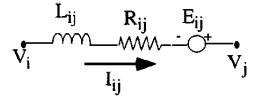

| Figure 28 | Branch equation derivation                                                                                                                                                                | 37         |

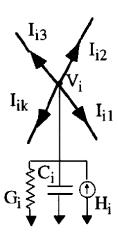

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 29 | Node equation derivation                                                                                                                                                                  | 37         |

| Figure 30 | Modeling and simulation methods developed and their relevance to power distribution                                                                                                       | 40         |

| Figure 31 | Plane pair structure                                                                                                                                                                      | 44         |

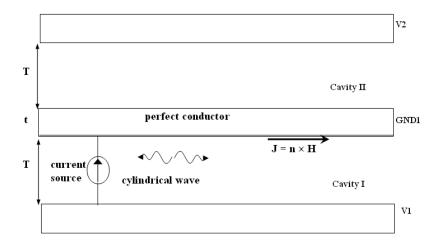

| Figure 32 | Three-layer package planes constructed with high conductivity metal (perfect conductor)                                                                                                   | 46         |

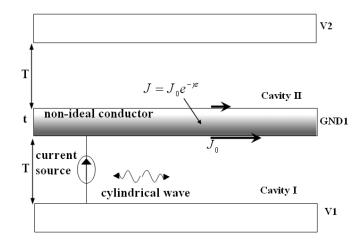

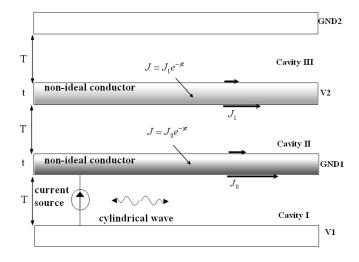

| Figure 33 | Three-layer package planes constructed with non-ideal conductor                                                                                                                           | 48         |

| Figure 34 | Four-layer package with non-ideal conductor                                                                                                                                               | 50         |

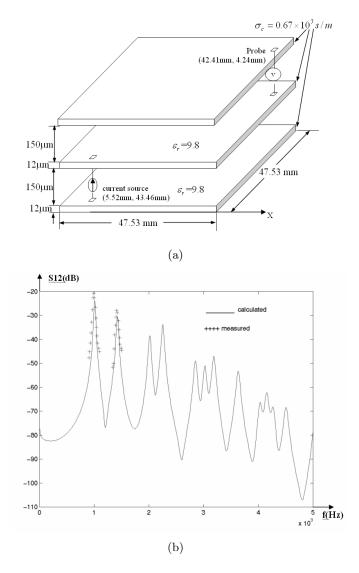

| Figure 35 | Measurement to model correlation (a) Cross section of test vehicle, (b) Comparison between simulation and measurement data                                                                | isor<br>52 |

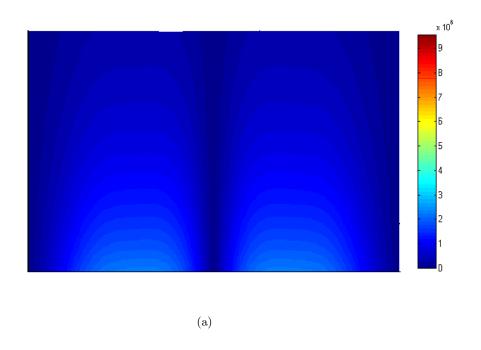

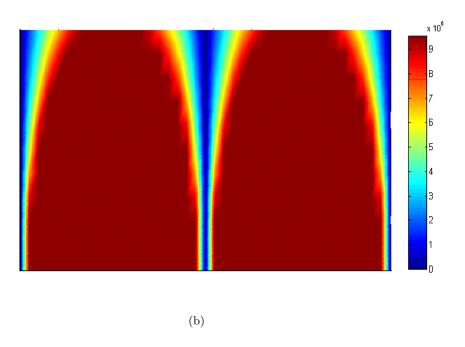

| Figure 36 | Current distribution in the cross section of GND1 plane: (a) $f=0.4$ GHz, (b) $f=2.0$ GHz                                                                                                 | 53         |

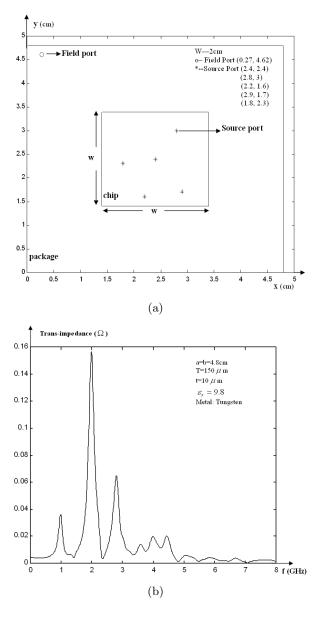

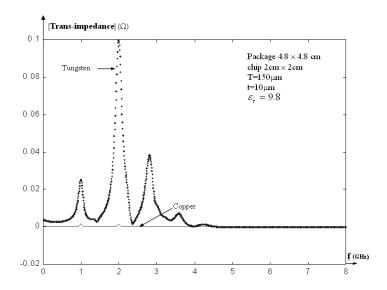

| Figure 37 | Microprocessor package: (a) top view of the single chip module and (b) trans-impedance $V_s$ frequency                                                                                    | 54         |

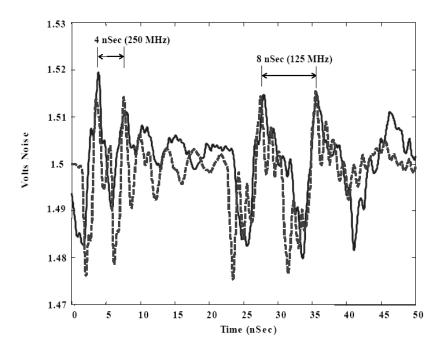

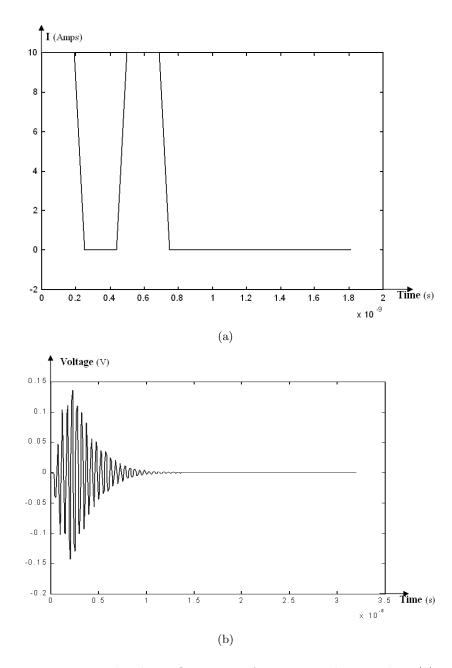

| Figure 38 | Excitation and voltage fluctuation for two switching cycles: (a)source waveform, (b)coupled voltage                                                                                       | 56         |

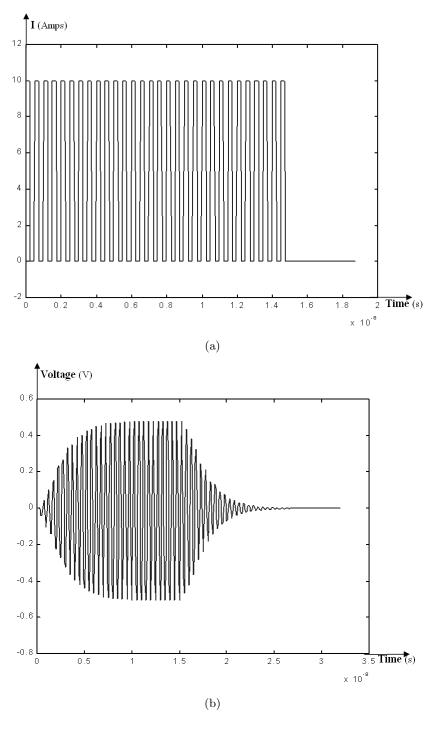

| Figure 39 | Excitation and voltage fluctuation for 30 switching cycles: (a)source waveform, (b)coupled voltage                                                                                        | 58         |

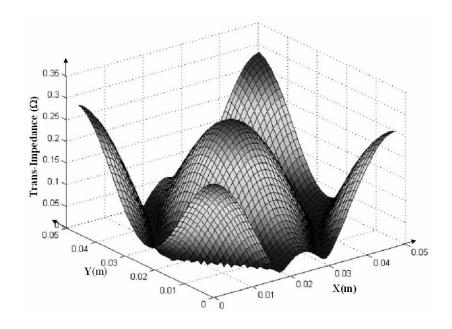

| Figure 40 | Coupling as a function of location                                                                                                                                                        | 59         |

| Figure 41 | Effect of metal conductivity on trans-impedance                                                                                                                                           | 60         |

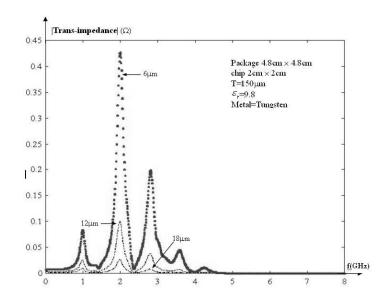

| Figure 42 | Effect of metal thickness on trans-impedance                                                                                                                                              | 61         |

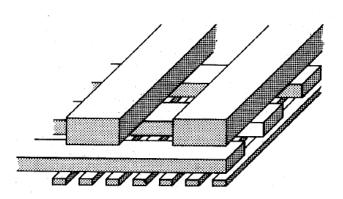

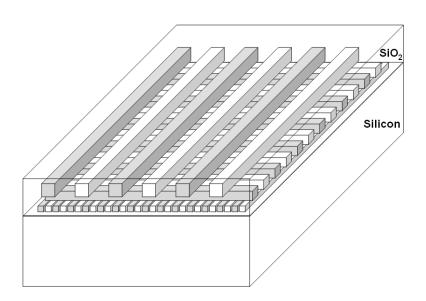

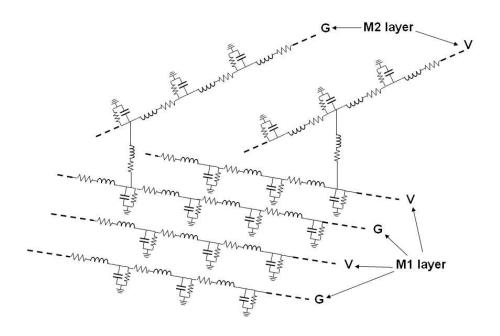

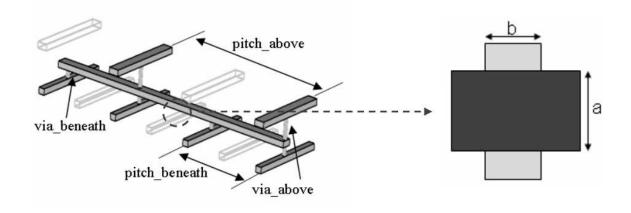

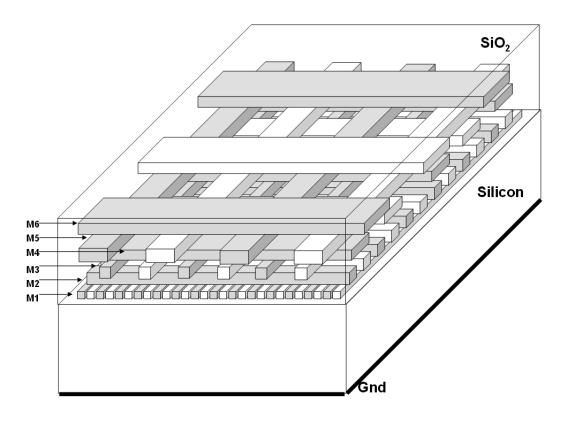

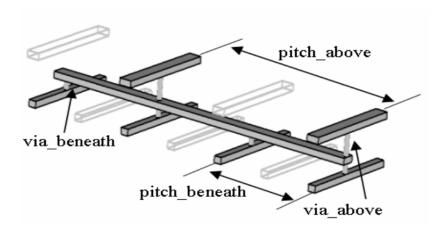

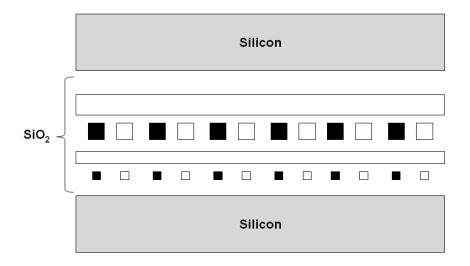

| Figure 43 | Multilayered on-chip power grid                                                                                                                                                           | 63         |

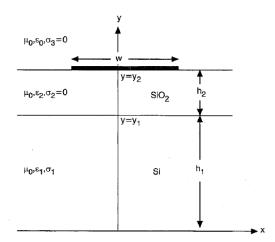

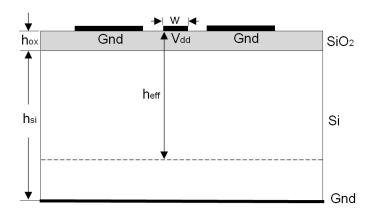

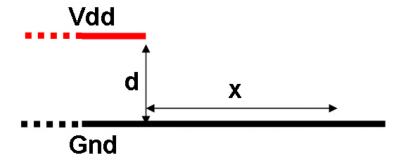

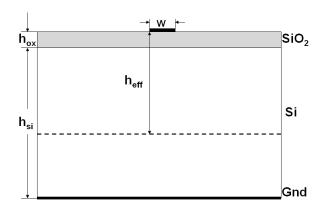

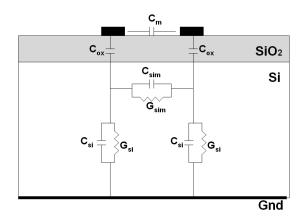

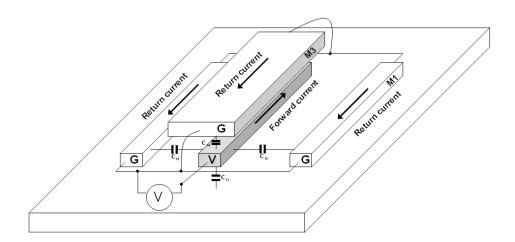

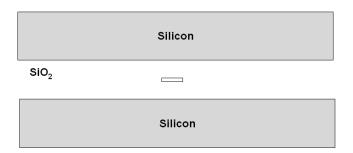

| Figure 44 | Side view of on-chip grid                                                                                                                                                                 | 65         |

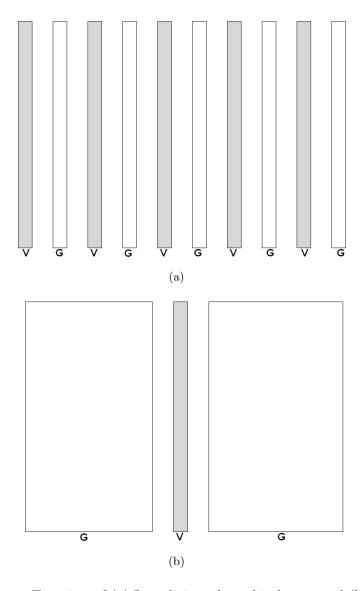

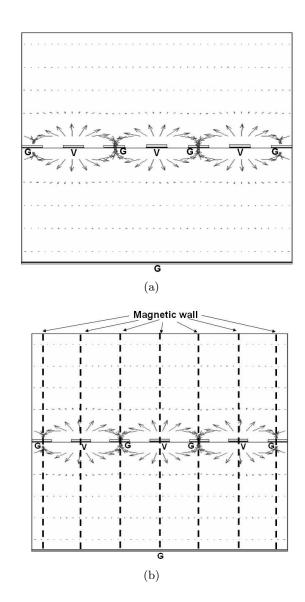

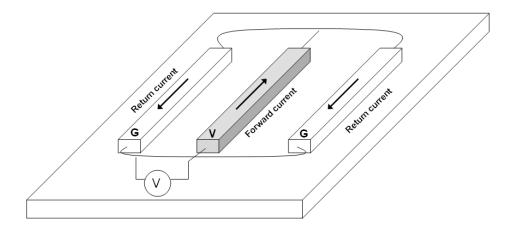

| Figure 45 | Top view of (a) Interdigitated on-chip buses, and (b) CPW $\ \ldots \ \ldots$                                                                                                             | 66         |

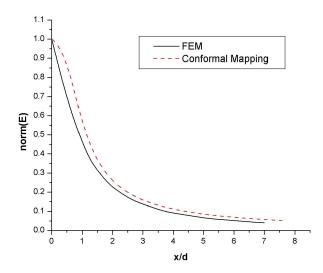

| Figure 46 | Field distribution of CPW                                                                                                                                                                 | 67         |

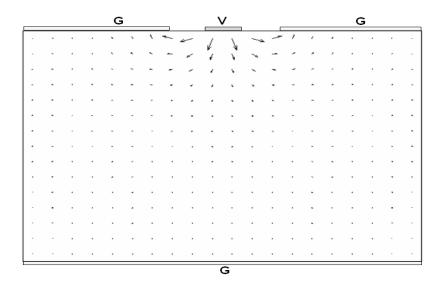

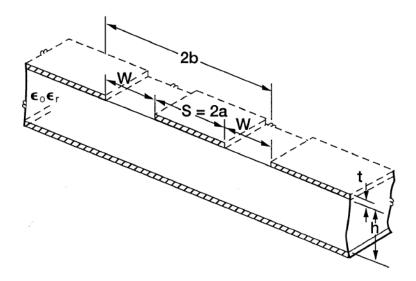

| Figure 47 | Conductor backed coplanar waveguide                                                                                                                                                       | 68         |

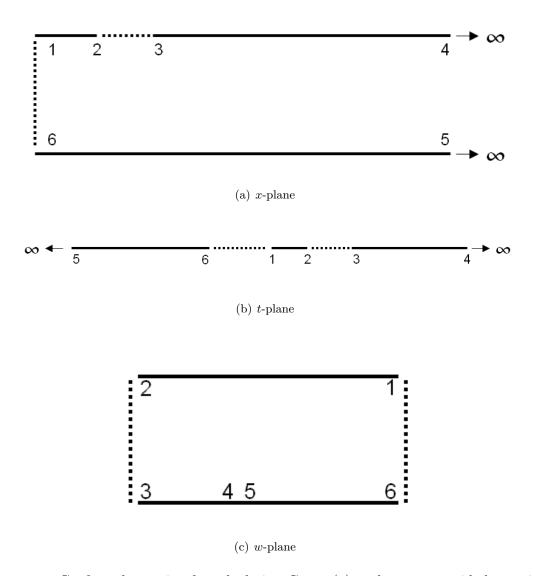

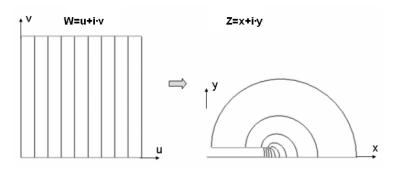

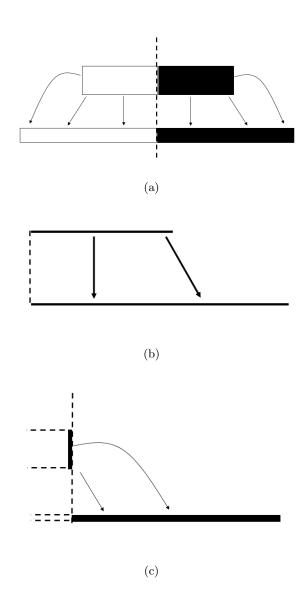

| Figure 48 | Conformal mapping for calculating $C_{CPW}$ (a) coplanar waveguide lower right quadrant, (b) intermediate transformed quadrant in $t$ -plane (c) final transformed geometry in $w$ -plane | 70         |

| Figure 49 | Conductor backed coplanar waveguide                                                                                                                                                       | 71         |

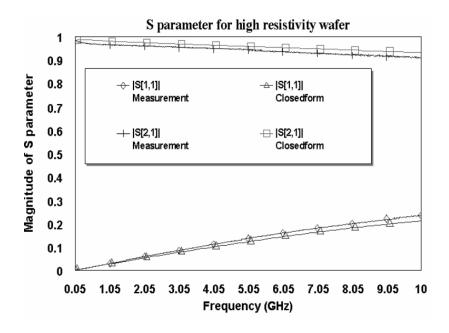

| Figure 50 | Measurement vs. analytical model for high resistivity wafer                                                                                                                               | 72         |

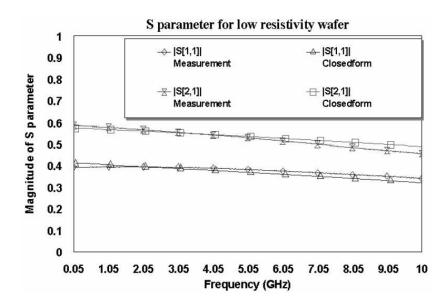

| Figure 51 | Measurement vs. analytical model for low resistivity wafer                                                                                                                                | 73         |

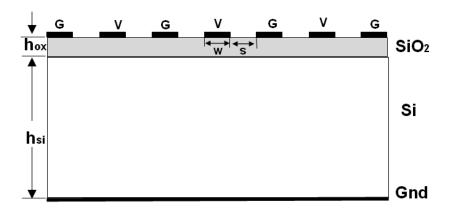

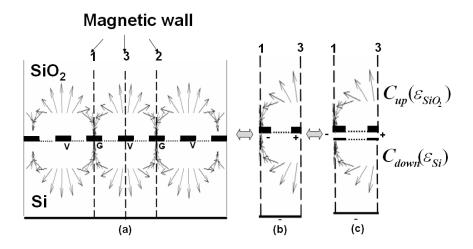

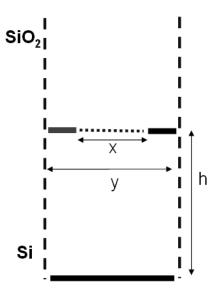

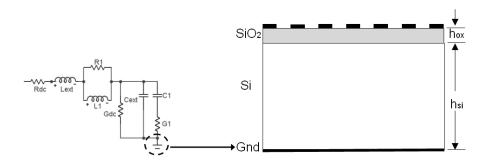

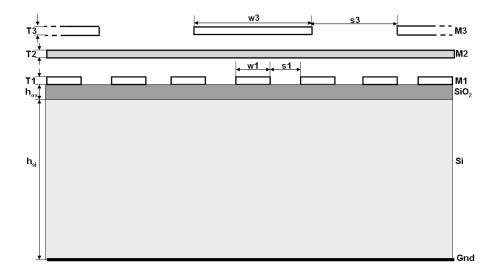

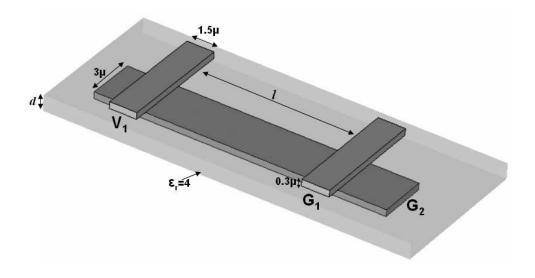

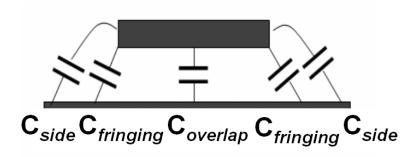

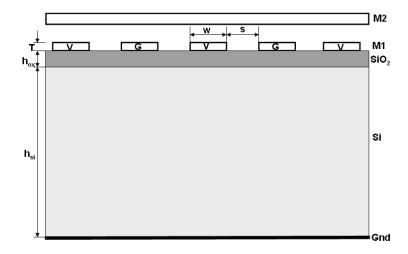

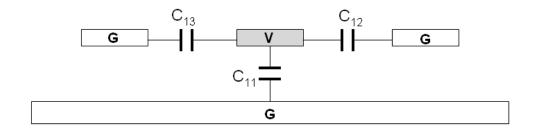

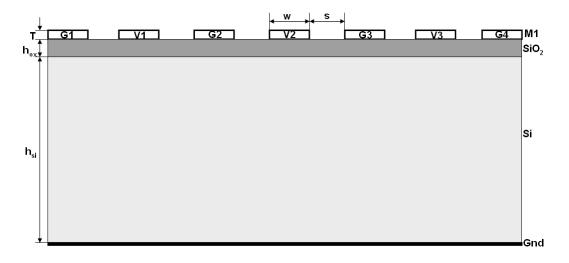

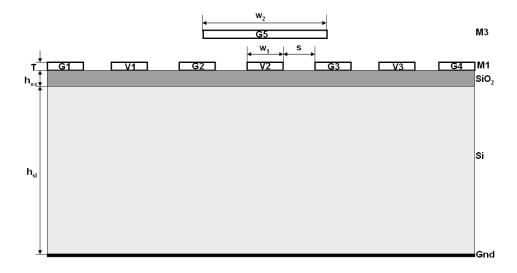

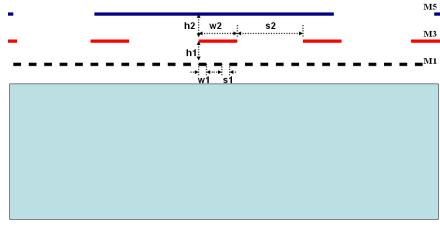

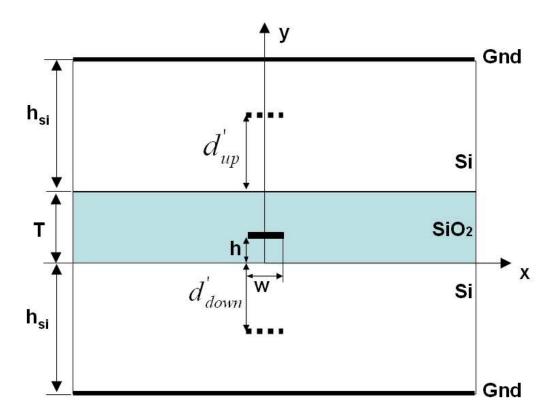

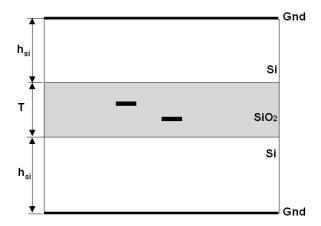

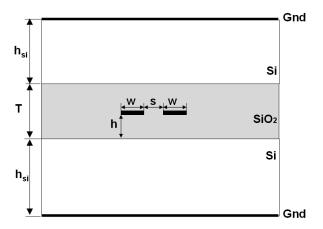

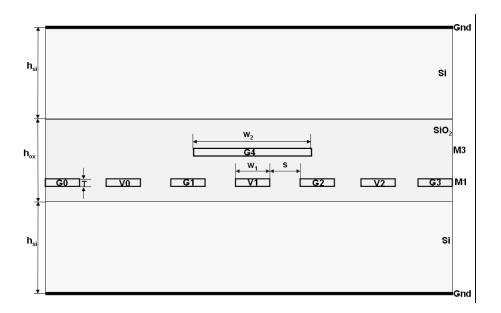

| Figure 52 | Cross section of first layer on-chip power bus (M1 layer)                                                                                                                                 | 73         |

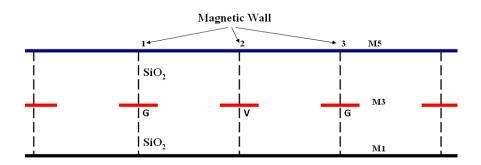

| Figure 53 | CMC lines (a) Electric field of CMC, and (b) Magnetic walls at the center of all buses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 74 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 54 | Electric field of CMC structure and capacitor calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75 |

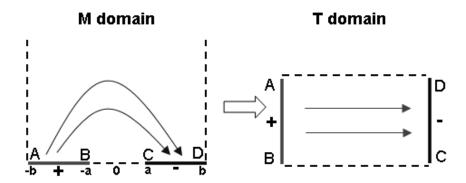

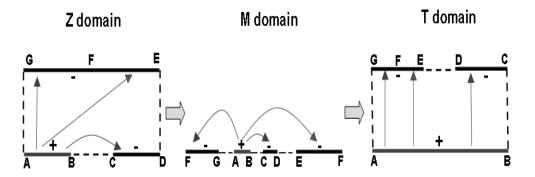

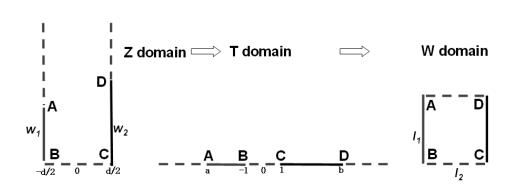

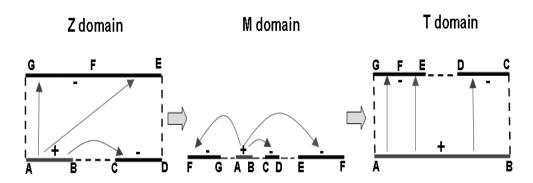

| Figure 55 | Conformal mapping of $C_{up}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76 |

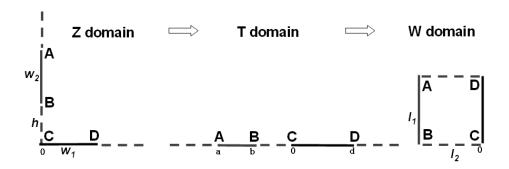

| Figure 56 | Conformal mapping of $C_{down}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 77 |

| Figure 57 | Test case of half CMC structure: $x = 5\mu m, y = 10\mu m, h = 250\mu m,$ $\varepsilon_{si} = 11.9\varepsilon_0$ and $\varepsilon_{sio_2} = 3.5\varepsilon_0 \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 79 |

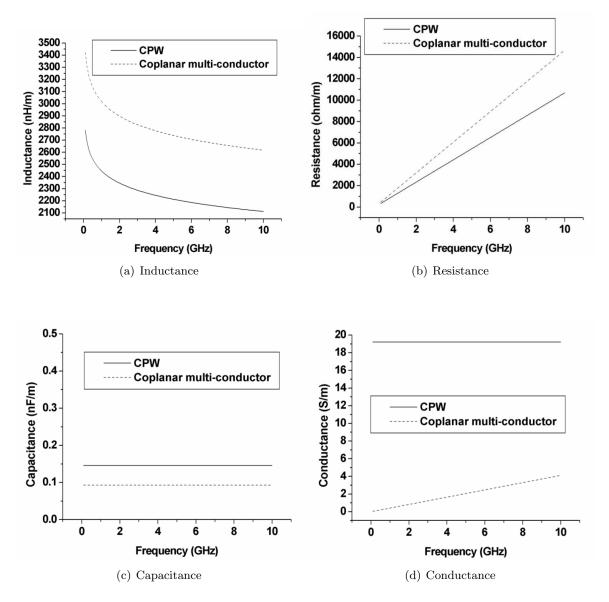

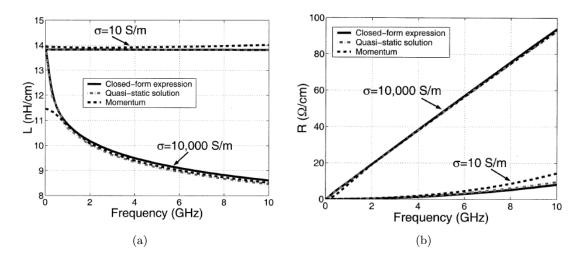

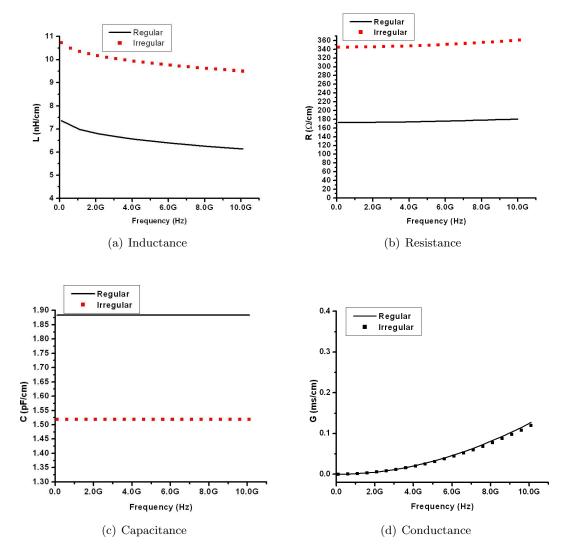

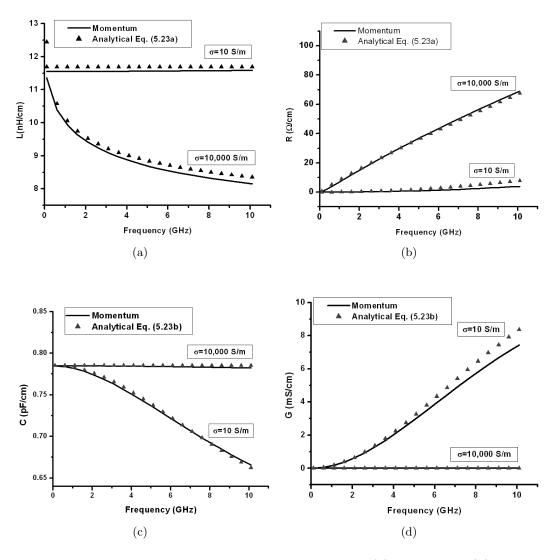

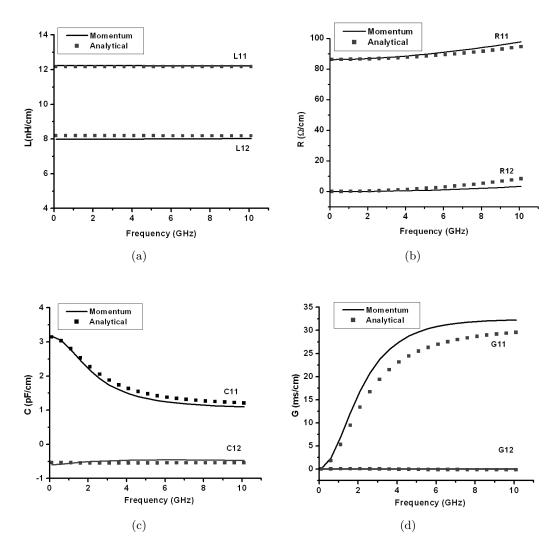

| Figure 58 | Comparison of parameters for CPW and CMC structure, (a) inductance, (b) resistance, (c) capacitance and (d) conductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 81 |

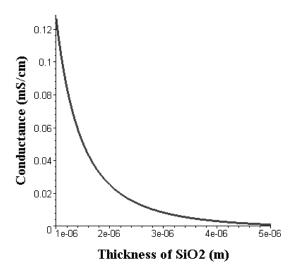

| Figure 59 | Conductance vs. SiO <sub>2</sub> thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83 |

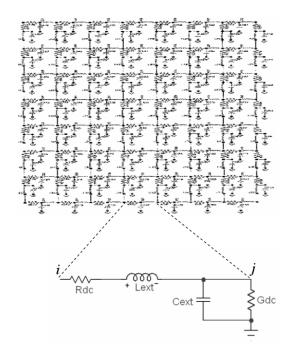

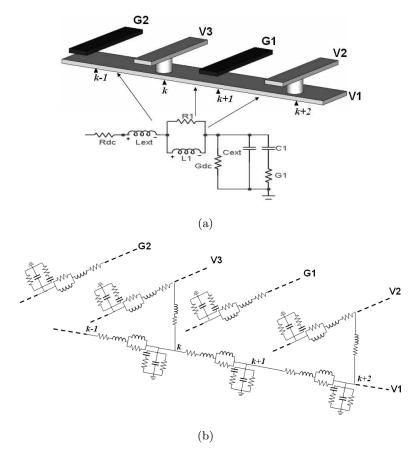

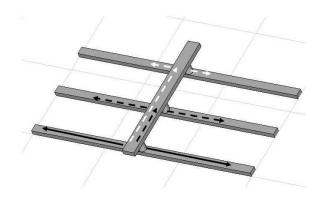

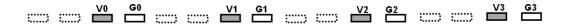

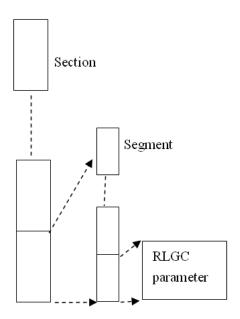

| Figure 60 | On-chip power grid with constant RLGC representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84 |

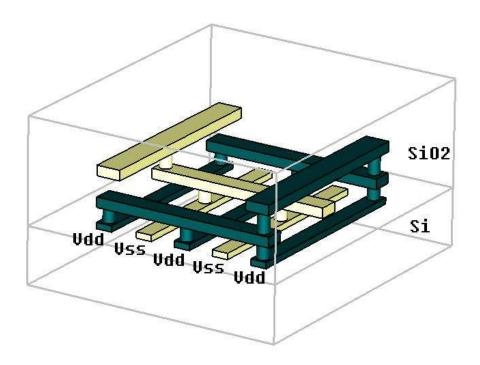

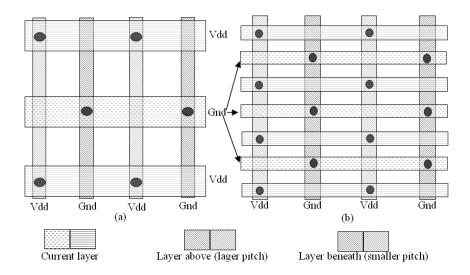

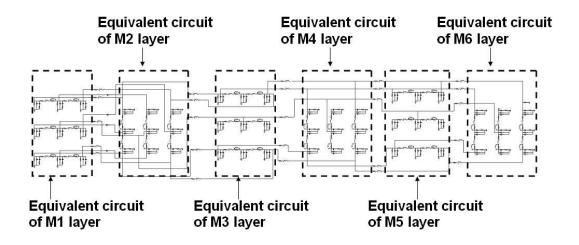

| Figure 61 | Constant RLGC representation of M1 and M2 layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 85 |

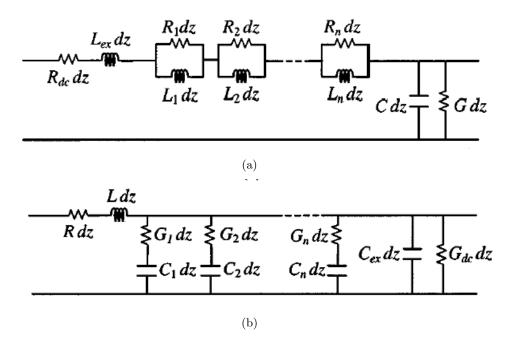

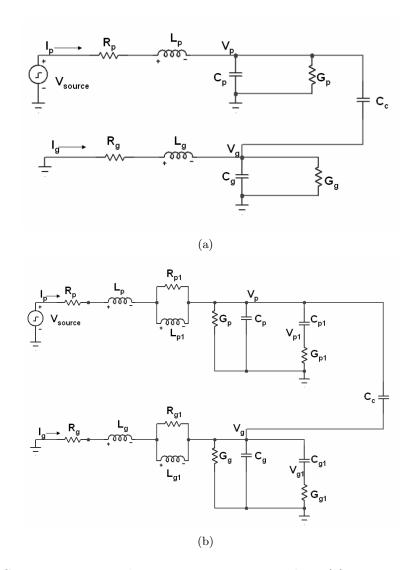

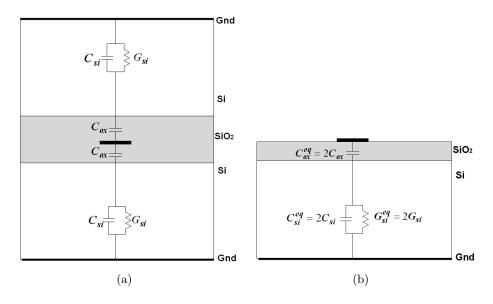

| Figure 62 | Equivalent circuit of unit length transmission line (a) Debye model for series $R$ and $L$ , (b) Debye model for shunt $G$ and $C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87 |

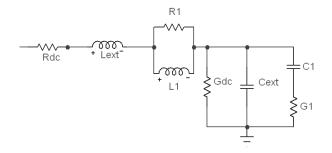

| Figure 63 | Circuit of first order Debye approximation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88 |

| Figure 64 | Example of using first order Debye model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88 |

| Figure 65 | Parameters of the test structure, (a) inductance, (b) resistance, (c) capacitance and (d) conductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 |

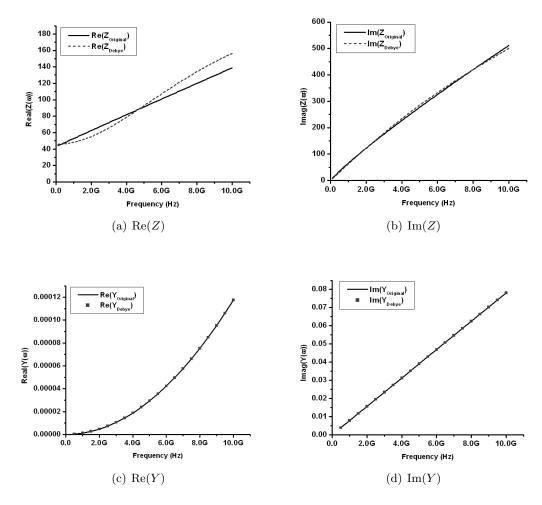

| Figure 66 | First order Debye approximation of frequency dependent impedance and admittance (a) $\text{Re}(Z)$ , (b) $\text{Im}(Z)$ , (c) $\text{Re}(Y)$ , (d) $\text{Im}(Y)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90 |

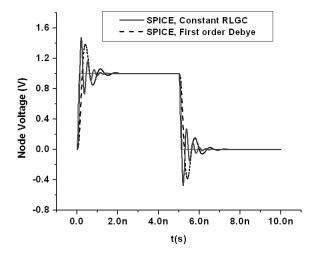

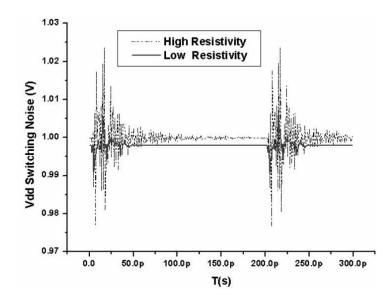

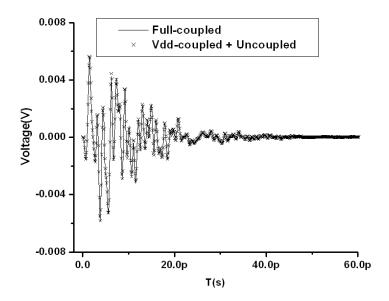

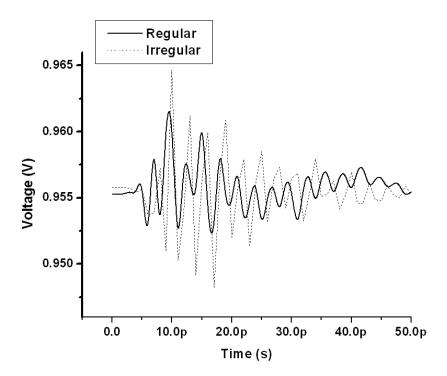

| Figure 67 | Comparison between constant RLGC model and first order Debye $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90 |

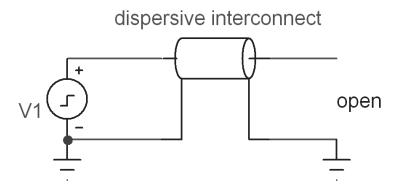

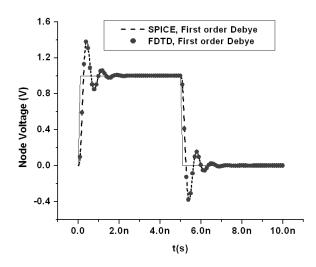

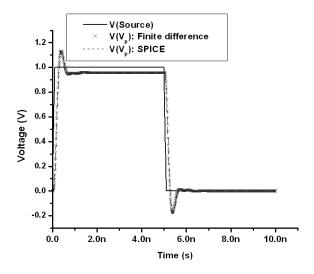

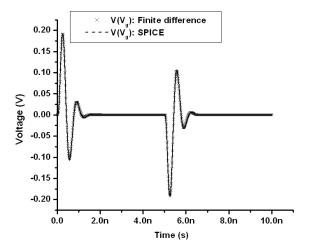

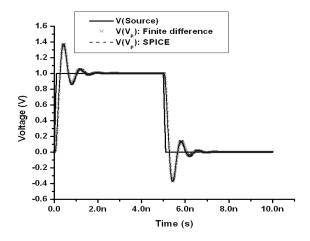

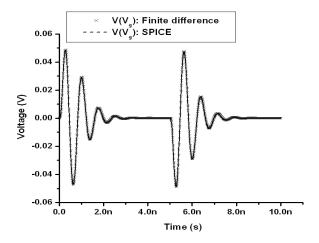

| Figure 68 | Correlation between SPICE and modified FDTD for first-order Debye model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93 |

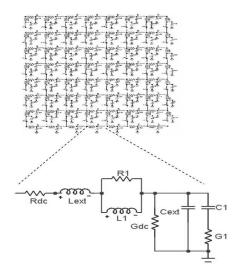

| Figure 69 | Power grid model (a) Debye model for each segment of the power/ground buses, and (b) the connection of M1 and M2 layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 94 |

| Figure 70 | Full-chip power model and Debye approximation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95 |

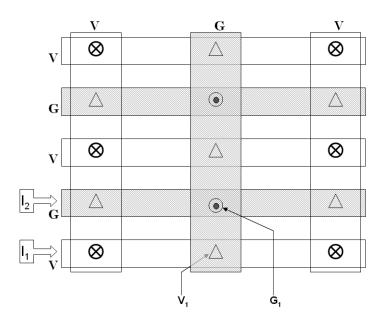

| Figure 71 | Ground node of an on-chip power grid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 95 |

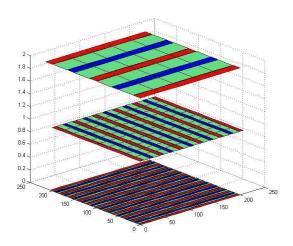

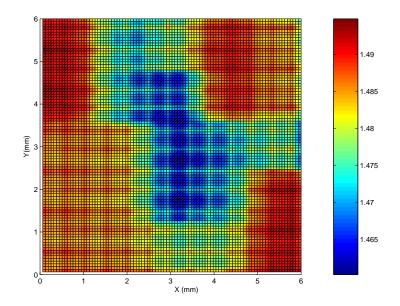

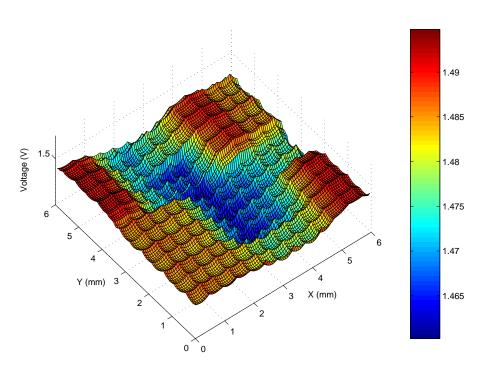

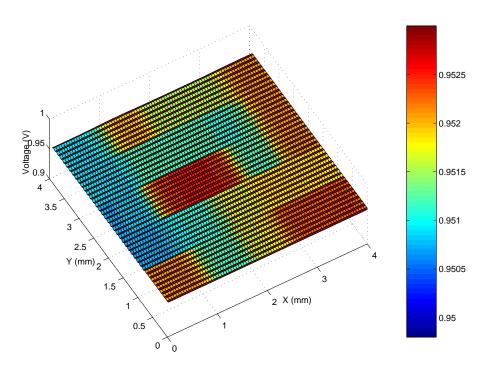

| Figure 72 | Steady state (DC) of on-chip power distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96 |

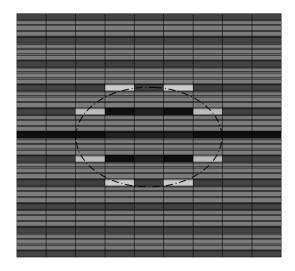

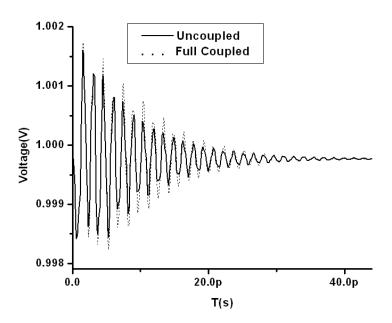

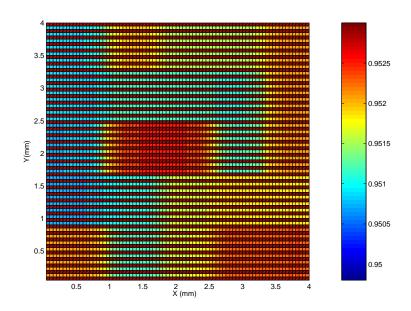

| Figure 73 | Elliptical pattern of the switching noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 97 |