# CHIP/PACKAGE CO-DESIGN METHODOLOGIES FOR RELIABLE 3D ICS

A Dissertation Presented to The Academic Faculty

by

Taigon Song

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2015

Copyright © 2015 by Taigon Song

# CHIP/PACKAGE CO-DESIGN METHODOLOGIES FOR RELIABLE 3D ICS

Approved by:

Dr. Sung Kyu Lim, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Arijit Raychowdhury School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Sudhakar Yalamanchili School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Suresh K. Sitaraman School of Mechanical Engineering *Georgia Institute of Technology*

Date Approved: October 22, 2015

To my wife Keeon Jung and our baby,

my parents,

and my family.

## ACKNOWLEDGEMENTS

Finishing my Ph.D. has been a journey with many surprises and challenges. It would not have been possible without many help. Everyone deserves proper appreciation, and I would like to use this section to thank all of those who helped me along the way.

Firstly, I would like to thank my advisor, Dr. Sung Kyu Lim, for guiding me and shaping my research. Changing my specialty from one to another was not easy, and without his guidance I would not have successfully made it. Thanks to him, my chance of pursuing the highest academic degree possible was a great success in one of the best schools in the world. I would like to thank Dr. Arijit Raychowdhury and Dr. Sudhakar Yalamanchili for guidance and suggestions on my research. In addition, I thank Dr. Saibal Mukhopadhyay and Dr. Suresh K. Sitaraman for their time and for the serving on my dissertation defense committee.

I thank Synopsys StarRC R&D group for the technical resources, discussion, and guidance regarding my face-to-face bonding research: Arthur Nieuwoudt, Ralph Iverson, and Alexander Mirgorodskiy. I also thank Beifang Qiu and Baribrata Biswas for giving me a wonderful opportunity to work at Synopsys Inc. In addition, I also thank Vivek Mishra, who was interning in Synopsys at that time with me, at the University of Minnesota for valuable discussions as well. I thank GTCAD members, Dr. Daehyun Kim, Dr. Xin Zhao, Dr. Young-Joon Lee, Dr. Krit Athikulwongse, Dr. Moongon Jung, Dr. Shreepad Panth, Chang Liu, Neela Lohith, Mohit Pathak, Yarui Peng, Sandeep Samal, Kyungwook Chang, Bon Woong Ku, Kartik Acharya, Kwangmin Kim, and Yoo-Jin Chae for their valuable comments and feedback. I would also not want to forget Pamela Halverson for her awesome help in all aspects of my office days for the last years.

I wish to thank my friends and roommates who supported me all the time: Dr. Sangkil

Kim, Jeewoong Kim, Junho Lee, Jonha Lee, Youngchul Park, Danny Kang, Yongmin Choi, Hyun Choi, and Sanggyu min. My church mentors and friends were also a big help to me: Joanna Jung, HK Bahk, Stella Song, Joohwan Kim, Michael Choi, Rachael Park, Michael Nam, Justin Cho, Letta Lee, Jinoh Yun, Mindy Yun, and Dongsik Chang. I would also like to extend my special thanks to Seung-ho Ok, Younsik Park, Daehyun Kim (my senior from Yonsei Univ.), and my mentor Jungwon Bae, who have always motivated me and helped me during my Ph.D. I thank my band, "Loveless" (Wonchul Kim, Juyoung Lee, Minjae Kang, Minkyung Hwang, Harum Chang, Eunjung Noh, Seungkyu Chang, Hwisuk Yang, Jiyoon Choi, Jihye Seo, Byunghwa Kim, and Jimin Park ), and my korean friends: Shawn Kim, Junyoung Jung, Eden Joo, Chan-Ho Kong, Ki-Joon Kim, and Seung-Ho Choi, who waited me in my home country, I thank them as well.

I am particularly thankful to wife, Keeon Jung, our little baby, and my parents, who have always been on my side, for their love and encouragement throughout my life. I also thank my sister, Hyunyoung Song, for the love and support. Last but not least, I thank God and all the professors, teachers, families, and friends who guided me to become the person that I am today.

# TABLE OF CONTENTS

| DE  | DICA  | TION    |                                                                                        | iii  |

|-----|-------|---------|----------------------------------------------------------------------------------------|------|

| AC  | KNOV  | WLEDO   | GEMENTS                                                                                | iv   |

| LIS | ST OF | TABLI   | ES                                                                                     | xi   |

| LIS | ST OF | FIGUE   | RES                                                                                    | xiii |

| SUI | MMA   | RY.     |                                                                                        | XX   |

| Ι   | INT   | RODU    | CTION                                                                                  | 1    |

|     | 1.1   |         | dimensional Integrated Circuits (3D ICs) and Silicon Interposers as ative Technologies | 2    |

|     | 1.2   | Challer | nges                                                                                   | 3    |

|     | 1.3   | Scope   | of This Dissertation                                                                   | 5    |

|     | 1.4   | Organi  | zation and Contributions                                                               | 5    |

| II  |       |         | SIS METHODOLOGIES IN CHIP, PACKAGE, AND PCBS IN<br>G TECHNOLOGIES                      | 8    |

|     | 2.1   | A Co-S  | Simulation Methodology for IR-drop Noise in Silicon Interposers .                      | 11   |

|     | 2.2   | Interpo | oser-3D IC Co-Simulation Methodology                                                   | 12   |

|     |       | 2.2.1   | PDN Design of the 3D IC                                                                | 13   |

|     |       | 2.2.2   | PDN Design of the Interposer and PCB                                                   | 13   |

|     |       | 2.2.3   | Co-Simulation Methodology                                                              | 15   |

|     | 2.3   | Experi  | mental Results                                                                         | 17   |

|     | 2.4   | Propos  | ed Thermal Analysis Flow                                                               | 22   |

|     |       | 2.4.1   | GDSII Level Thermal Analysis                                                           | 22   |

|     |       | 2.4.2   | Analog/Digital Mixed Thermal Analysis - Layout                                         | 25   |

|     |       | 2.4.3   | Analog/Digital Mixed Thermal Analysis - Power Analysis                                 | 25   |

|     |       | 2.4.4   | Analog/Digital Mixed Thermal Analysis - Material Density Library                       | 27   |

|     | 2.5   |         | ntegrated Voltage Regulator using Magnetic-Core Inductors on Sil-                      | 28   |

|     |       | 2.5.1   | Basic Structure of the Integrated Voltage Regulator                                    | 28   |

|   |     | 2.5.2                                                                                                                                              | Power Inductor inside the Integrated Voltage Regulator                                                                                                                                                | 29                                                                                                                                 |

|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 2.5.3                                                                                                                                              | Efficiency of the Integrated Voltage Regulator                                                                                                                                                        | 30                                                                                                                                 |

|   | 2.6 | Therm                                                                                                                                              | al Analysis of the 2.5D Integrated Voltage Regulator                                                                                                                                                  | 30                                                                                                                                 |

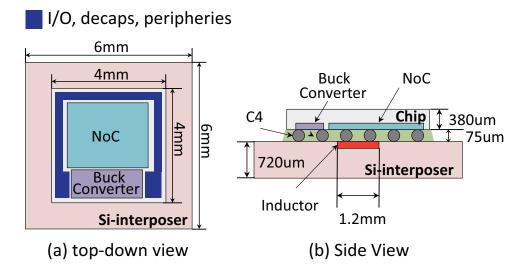

|   |     | 2.6.1                                                                                                                                              | Dimensions and Power Consumption of the Integrated Voltage<br>Regulator                                                                                                                               | 30                                                                                                                                 |

|   |     | 2.6.2                                                                                                                                              | Thermal Analysis of Essential Design Blocks                                                                                                                                                           | 32                                                                                                                                 |

|   |     | 2.6.3                                                                                                                                              | Factors Affecting Temperature Rise on Each Design Block                                                                                                                                               | 33                                                                                                                                 |

|   |     | 2.6.4                                                                                                                                              | Thermal Coupling Between NoC and the Buck Converter                                                                                                                                                   | 36                                                                                                                                 |

|   |     | 2.6.5                                                                                                                                              | Thermal Coupling Between NoC and the Inductor                                                                                                                                                         | 37                                                                                                                                 |

|   | 2.7 | Design                                                                                                                                             | Optimization of 2.5D Integrated Voltage Regulator                                                                                                                                                     | 40                                                                                                                                 |

|   |     | 2.7.1                                                                                                                                              | Design Block Relocation                                                                                                                                                                               | 40                                                                                                                                 |

|   |     | 2.7.2                                                                                                                                              | Inductor Spreading in Silicon Interposer                                                                                                                                                              | 40                                                                                                                                 |

|   | 2.8 | Summa                                                                                                                                              | ary                                                                                                                                                                                                   | 42                                                                                                                                 |

| ш |     |                                                                                                                                                    | P SIGNAL INTEGRITY ANALYSIS AND OPTIMIZATION OF                                                                                                                                                       | 45                                                                                                                                 |

|   | 3.1 | Electri                                                                                                                                            | cal Model of TSVs                                                                                                                                                                                     | 46                                                                                                                                 |

|   |     |                                                                                                                                                    |                                                                                                                                                                                                       |                                                                                                                                    |

|   | 3.2 | Analys                                                                                                                                             | is of TSV-to-TSV Crosstalk                                                                                                                                                                            | 49                                                                                                                                 |

|   | 3.2 | Analys<br>3.2.1                                                                                                                                    | is of TSV-to-TSV Crosstalk                                                                                                                                                                            | 49<br>49                                                                                                                           |

|   | 3.2 |                                                                                                                                                    |                                                                                                                                                                                                       | 49                                                                                                                                 |

|   | 3.2 | 3.2.1                                                                                                                                              | Crosstalk Equations Under High-Impedance Termination                                                                                                                                                  | 49<br>52                                                                                                                           |

|   | 3.2 | 3.2.1<br>3.2.2                                                                                                                                     | Crosstalk Equations Under High-Impedance Termination Comparison of Termination Conditions                                                                                                             | 49<br>52<br>53                                                                                                                     |

|   | 3.2 | <ul><li>3.2.1</li><li>3.2.2</li><li>3.2.3</li></ul>                                                                                                | Crosstalk Equations Under High-Impedance Termination Comparison of Termination Conditions                                                                                                             | 49<br>52<br>53<br>54                                                                                                               |

|   | 3.2 | <ul><li>3.2.1</li><li>3.2.2</li><li>3.2.3</li><li>3.2.4</li></ul>                                                                                  | Crosstalk Equations Under High-Impedance Termination                                                                                                                                                  | 49<br>52<br>53<br>54                                                                                                               |

|   | 3.2 | <ul> <li>3.2.1</li> <li>3.2.2</li> <li>3.2.3</li> <li>3.2.4</li> <li>3.2.5</li> </ul>                                                              | Crosstalk Equations Under High-Impedance Termination Comparison of Termination Conditions                                                                                                             | 49<br>52<br>53<br>54<br>55                                                                                                         |

|   | 3.2 | <ul> <li>3.2.1</li> <li>3.2.2</li> <li>3.2.3</li> <li>3.2.4</li> <li>3.2.5</li> <li>3.2.6</li> </ul>                                               | Crosstalk Equations Under High-Impedance Termination Comparison of Termination Conditions                                                                                                             | 49<br>52<br>53<br>54<br>55<br>58                                                                                                   |

|   | 3.2 | <ul> <li>3.2.1</li> <li>3.2.2</li> <li>3.2.3</li> <li>3.2.4</li> <li>3.2.5</li> <li>3.2.6</li> <li>3.2.7</li> <li>3.2.8</li> </ul>                 | Crosstalk Equations Under High-Impedance Termination <td< td=""><td><ol> <li>49</li> <li>52</li> <li>53</li> <li>54</li> <li>55</li> <li>58</li> <li>59</li> <li>61</li> </ol></td></td<>             | <ol> <li>49</li> <li>52</li> <li>53</li> <li>54</li> <li>55</li> <li>58</li> <li>59</li> <li>61</li> </ol>                         |

|   |     | <ul> <li>3.2.1</li> <li>3.2.2</li> <li>3.2.3</li> <li>3.2.4</li> <li>3.2.5</li> <li>3.2.6</li> <li>3.2.7</li> <li>3.2.8</li> </ul>                 | Crosstalk Equations Under High-Impedance Termination <td< td=""><td><ul> <li>49</li> <li>52</li> <li>53</li> <li>54</li> <li>55</li> <li>58</li> <li>59</li> <li>61</li> <li>64</li> </ul></td></td<> | <ul> <li>49</li> <li>52</li> <li>53</li> <li>54</li> <li>55</li> <li>58</li> <li>59</li> <li>61</li> <li>64</li> </ul>             |

|   |     | <ul> <li>3.2.1</li> <li>3.2.2</li> <li>3.2.3</li> <li>3.2.4</li> <li>3.2.5</li> <li>3.2.6</li> <li>3.2.7</li> <li>3.2.8</li> <li>Motiva</li> </ul> | Crosstalk Equations Under High-Impedance Termination                                                                                                                                                  | <ul> <li>49</li> <li>52</li> <li>53</li> <li>54</li> <li>55</li> <li>58</li> <li>59</li> <li>61</li> <li>64</li> <li>64</li> </ul> |

|    |     | 3.4.1   | Compact Multi-TSV Coupling Model                               | 69  |

|----|-----|---------|----------------------------------------------------------------|-----|

|    |     | 3.4.2   | Extraction Algorithm                                           | 75  |

|    | 3.5 | Full-cl | nip Analysis                                                   | 76  |

|    |     | 3.5.1   | Full Chip 3D SI Analysis Flow                                  | 76  |

|    |     | 3.5.2   | Design and Analysis Results                                    | 77  |

|    | 3.6 | Impact  | t of Process Parameters on TSV Coupling                        | 79  |

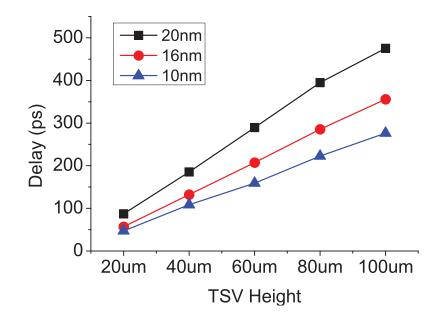

|    |     | 3.6.1   | TSV Height                                                     | 80  |

|    |     | 3.6.2   | Liner Thickness                                                | 81  |

|    |     | 3.6.3   | TSV Diameter                                                   | 82  |

|    | 3.7 | Impact  | t of Process Parameters on Delay                               | 83  |

|    |     | 3.7.1   | Analysis Structure for Single Net Delay Study                  | 83  |

|    |     | 3.7.2   | Impact of TSV Height, Liner Thickness, and TSV Radius          | 83  |

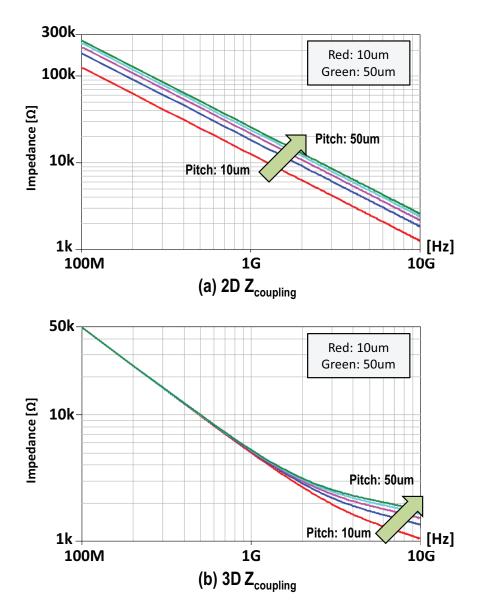

|    |     | 3.7.3   | Impact of TSV Pitch                                            | 84  |

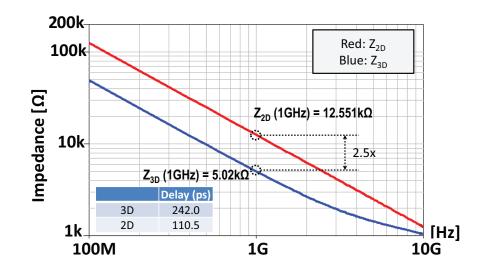

|    |     | 3.7.4   | The "Impedance Load" Analysis for Delay Estimation             | 86  |

|    |     | 3.7.5   | Technology Impact on 3D Delay                                  | 92  |

|    |     | 3.7.6   | Full-chip Impact on Timing and Power                           | 93  |

|    | 3.8 | TSV-to  | o-TSV Coupling Reduction                                       | 94  |

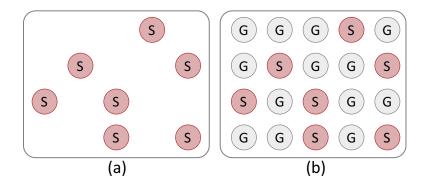

|    |     | 3.8.1   | TSV Path Blocking                                              | 95  |

|    |     | 3.8.2   | Optimization for Wide-I/O Design                               | 96  |

|    | 3.9 | Summ    | ary                                                            | 97  |

| IV |     |         | P DIE-TO-DIE PARASITIC EXTRACTION IN FACE-TO-FACE<br>DED 3D IC |     |

|    | 4.1 | Prelim  | inaries                                                        | 102 |

|    |     | 4.1.1   | Motivation                                                     | 102 |

|    |     | 4.1.2   | Limitations on the Top-Metal for F2F Structures                | 103 |

|    |     | 4.1.3   | Top Metal Candidates                                           | 104 |

|    |     | 4.1.4   | Test Structure                                                 | 106 |

|    | 4.2 | F2F Ca  | apacitance                                                     | 106 |

|    |     | 4.2.1   | F2F Bonding Impact on Thick Top Metal (TK)                     | 107 |

|   |     | 4.2.2   | F2F Bonding Impact on Thin Top Metal (TN)                                                         |

|---|-----|---------|---------------------------------------------------------------------------------------------------|

|   |     | 4.2.3   | Spacing-Height Relationship on F2F Capacitance                                                    |

|   |     | 4.2.4   | Impact of Offset Variation                                                                        |

|   |     | 4.2.5   | F2F Coupling in Different Top-metal Directions                                                    |

|   | 4.3 | Capaci  | itance Error Caused by F2F Bonding                                                                |

|   |     | 4.3.1   | Case Studies in Different Bump Sizes                                                              |

|   |     | 4.3.2   | F2F Bonding Impact on Capacitance Error                                                           |

|   | 4.4 | Full-cl | nip Extraction Analysis                                                                           |

|   |     | 4.4.1   | Technology Setup                                                                                  |

|   |     | 4.4.2   | Extraction Flow                                                                                   |

|   |     | 4.4.3   | New Capacitance in F2F Structure                                                                  |

|   |     | 4.4.4   | Comparison with Other Capacitances                                                                |

|   |     | 4.4.5   | F2F Capacitance Breakdown                                                                         |

|   |     | 4.4.6   | Error in Die-by-Die Extraction                                                                    |

|   |     | 4.4.7   | Impact of Chip-to-Chip Distance                                                                   |

|   | 4.5 | Full-cl | nip Timing/Noise Impact                                                                           |

|   |     | 4.5.1   | Holistic vs Die-by-Die Extraction                                                                 |

|   |     | 4.5.2   | Impact of PDN on F2F Capacitance                                                                  |

|   |     | 4.5.3   | Results on Other Benchmarks                                                                       |

|   | 4.6 | Summ    | ary                                                                                               |

| V | SOF | RS: TH  | WER REDUCTION IN 3D ICS FOR MULTI-CORE PROCES-<br>REE-TIER STRATEGIES IN CAD, DESIGN, AND BONDING |

|   | 5.1 |         | ation Settings                                                                                    |

|   | 5.1 | 5.1.1   | Benchmark                                                                                         |

|   |     | 5.1.2   | 3D Bonding Technology                                                                             |

|   | 5.2 |         | SD Bonding Technology         134           Fool for 3-Tier 3D ICs         136                    |

|   | 5.2 | 5.2.1   | Need for New Tools         137                                                                    |

|   |     | - · ·   |                                                                                                   |

|   |     | 5.2.2   | CAD Tool for F2B+F2F Bonding                                                                      |

|     |      | 5.2.3   | CAD Tool for B2B+F2F Bonding         |

|-----|------|---------|--------------------------------------|

|     |      | 5.2.4   | 3-Tier 3D IC Design Flow             |

|     | 5.3  | Benefit | ts of 3-Tier 3D IC                   |

|     |      | 5.3.1   | New Design Challenges                |

|     |      | 5.3.2   | 2D vs. 2-tier 3D vs. 3-tier 3D       |

|     | 5.4  | Block-  | Folding in 3-Tier 3D IC              |

|     |      | 5.4.1   | 3-Tier Block-Folding Challenges      |

|     |      | 5.4.2   | Block-Folding Strategies             |

|     | 5.5  | Bondin  | ng Style Impact Study                |

|     |      | 5.5.1   | Bonding Impact On Floorplan          |

|     |      | 5.5.2   | Bonding Impact On Block-Folding      |

|     |      | 5.5.3   | Overall Comparison                   |

|     | 5.6  | Design  | Challenges in Full-Chip              |

|     |      | 5.6.1   | Full-chip OpenSPARC T2 Design        |

|     |      | 5.6.2   | Area Management Challenges           |

|     |      | 5.6.3   | Block-Folding in Full-Chip           |

|     |      | 5.6.4   | Managing Bonding Styles in Full-Chip |

|     |      | 5.6.5   | Overall Comparison in Full-Chip      |

|     | 5.7  | Summa   | ary                                  |

| VI  | CON  | ICLUS   | IONS AND FUTURE DIRECTIONS           |

| PUI | BLIC | ATION   | <b>S</b>                             |

| RE  | FERE | NCES    |                                      |

# LIST OF TABLES

| 1  | Details of the circuits used in this paper 20                                                                                                                                                                                                                                                                                                                 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2  | IR-drop results comparison. PR stands for Synopsys PrimeRail 20                                                                                                                                                                                                                                                                                               |

| 3  | Power consumption numbers of some blocks from the measurement 32                                                                                                                                                                                                                                                                                              |

| 4  | Electrical parameters used in this paper 47                                                                                                                                                                                                                                                                                                                   |

| 5  | Model validation on general layouts                                                                                                                                                                                                                                                                                                                           |

| 6  | TSV coupling impact on crosstalk and timing. Coupling noise in (V), longest path delay in (ns), and total negative slack in (ns)                                                                                                                                                                                                                              |

| 7  | Full-chip 3D noise: Impact of TSV parameters                                                                                                                                                                                                                                                                                                                  |

| 8  | Full-chip timing report: Impact of TSV parameters                                                                                                                                                                                                                                                                                                             |

| 9  | Impact of TSV Path Blocking - block level design                                                                                                                                                                                                                                                                                                              |

| 10 | Impact of TSV Path Blocking - wide I/O design                                                                                                                                                                                                                                                                                                                 |

| 11 | Metal dimensions used in this study                                                                                                                                                                                                                                                                                                                           |

| 12 | Capacitance of test structure on different bump height                                                                                                                                                                                                                                                                                                        |

| 13 | Interconnect dimensions used in this design                                                                                                                                                                                                                                                                                                                   |

| 14 | F2F capacitance comparison to other capacitances. Total die cap and M6-M6 cap are averaged between Die 0 and Die 1. See Figure 94 (a) and (b) for definitions                                                                                                                                                                                                 |

| 15 | F2F capacitance breakdown: See Figure 94 (c) for definitions                                                                                                                                                                                                                                                                                                  |

| 16 | Capacitance overestimation in Die-by-Die extraction due to F2F cap in LDPC benchmark                                                                                                                                                                                                                                                                          |

| 17 | Full-chip timing and noise analysis in LDPC benchmark                                                                                                                                                                                                                                                                                                         |

| 18 | Results for all benchmarks. M6 $\Delta$ denote the the cap overestimation caused<br>by Die-by-Die extraction between M6-M6 in the same die as in Table 16.<br>Cap $\Delta$ , delay $\Delta$ , and noise $\Delta$ are worst case underestimation differences<br>caused in timing and noise analysis on a single net in Die-by-Die extraction<br>as in Table 17 |

| 19 | F2F capacitance reduction due to PDN                                                                                                                                                                                                                                                                                                                          |

| 20 | PDN specifications used in our 2D and 3D designs. # tracks show the maximum number of signal wires that can fit in between two adjacent P/G wires                                                                                                                                                                                                             |

| 21 | 3D interconnect settings                                                                                                                                                                |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22 | Area percentage of the functional unit blocks in T2 Core                                                                                                                                |

| 23 | 2D vs. 2-tier 3D vs. 3-tier 3D (non-folding, F2B-only) in T2 Core. All percentage values are with respect to 2D results                                                                 |

| 24 | Individual folded-block comparisons in F2B-only bonded T2 Core. % represents the reduction from 2D counterparts. (LSU not available for 3-tier folding)                                 |

| 25 | IFU 2-tier vs. 3-tier in F2B-only bonded T2 Core (see Figure 102 for illus-<br>tration)                                                                                                 |

| 26 | Comparison among 3-tier T2 Core designs built with various options in folding and bonding styles. All folded designs target 4 blocks (LSU, IFU, TLU, and FGU) to be folded              |

| 27 | Area comparison between 2D and 3D in full-chip level studies                                                                                                                            |

| 28 | Full-chip comparison among 3-tier 3D IC designs built with various op-<br>tions in folding and bonding styles. All folded designs target 4 blocks<br>(Core, RTX, CCX, L2D) to be folded |

# LIST OF FIGURES

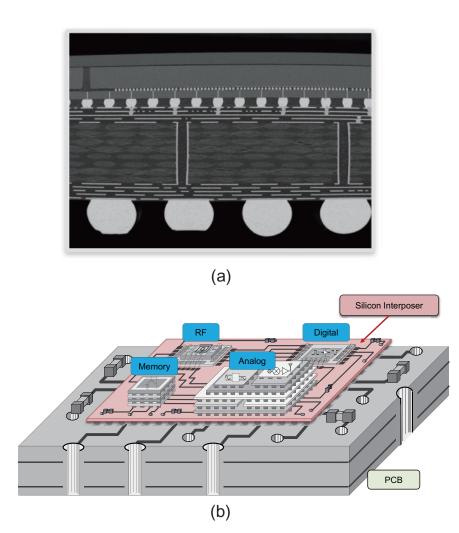

| 1  | (a) Silicon interposer in actual product [81] and (b) illustration of 3D ICs and silicon interposers for future ultra-miniaturized systems.                                                                                                                                                                          | 3     |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

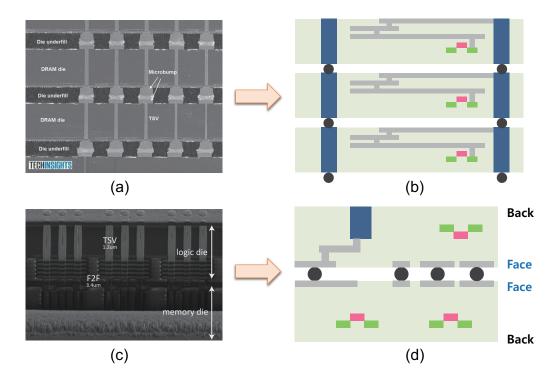

| 2  | 3D ICs using TSVs and F2F bumps: (a) Actual 3D IC product using TSVs [76], (b) illustration of a 3-tier 3D IC, (c) 3D IC designed in F2F bonded style [32], and (d) illustration of a F2F bonded 3D IC with F2F bumps                                                                                                | 4     |

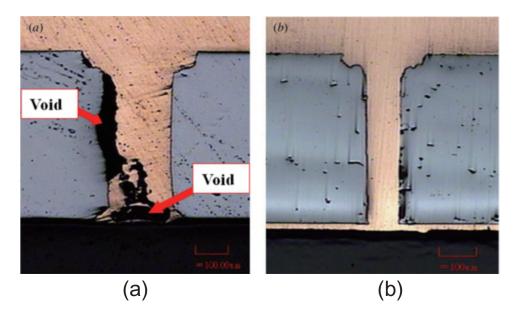

| 3  | (a) TSV manufactured with voids, (b) TSV manufactured with no voids [13].                                                                                                                                                                                                                                            | 5     |

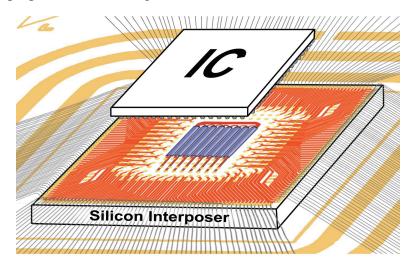

| 4  | Diagram of a 2.5D integrated voltage regulator (IVR) chip stack. The IC consists of buck converter and load circuitry, and the silicon interposer contains the power inductor. The IC is flip-chip mounted on the silicon interposer using ball grid array, and wirebonds connect the silicon interposer and the IO. | 10    |

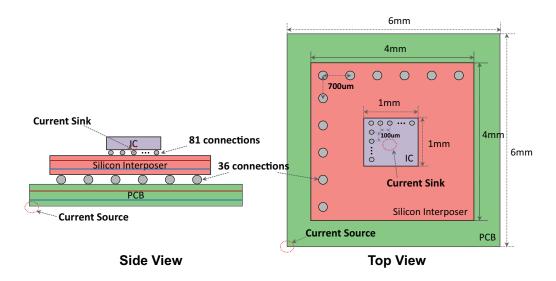

| 5  | Side view and top view of the system simulated for IR-drop noise                                                                                                                                                                                                                                                     | 12    |

| 6  | IR-drop Noise on (a): Si-interposer (17.08mV), (b): Organic package (2.24mV                                                                                                                                                                                                                                          | ). 12 |

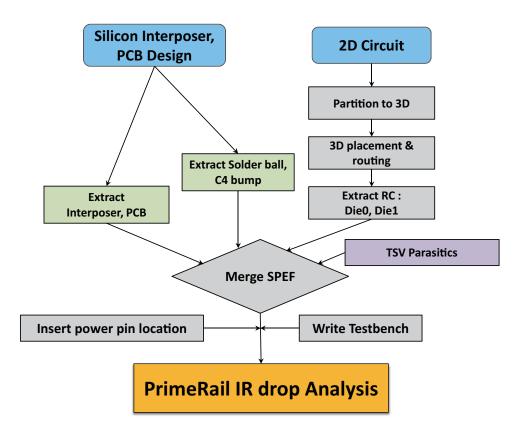

| 7  | The proposed co-analysis design flow for IR-drop noise                                                                                                                                                                                                                                                               | 13    |

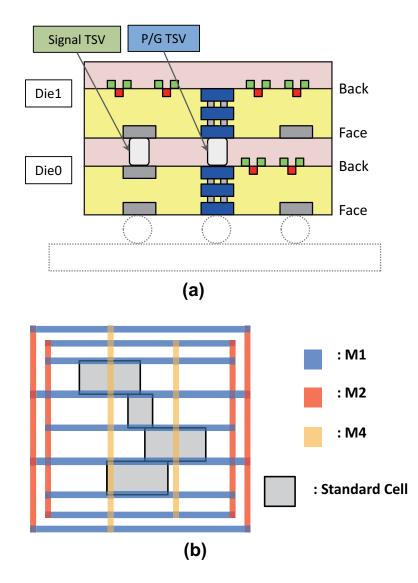

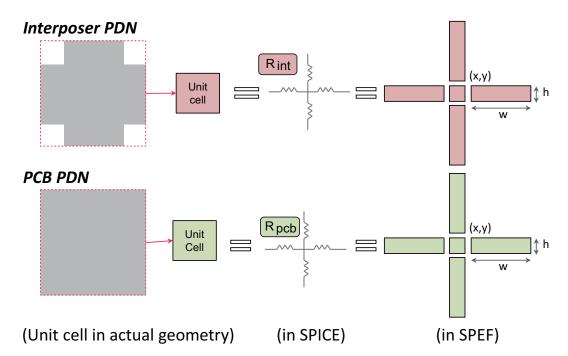

| 8  | Details of the 3D IC PDN design (a): Stack information of the two tier 3D IC, (b): PDN design on the 3D IC.                                                                                                                                                                                                          | 14    |

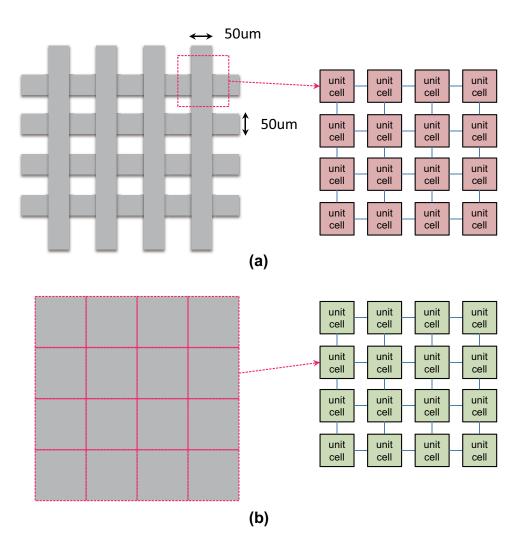

| 9  | PDN modeling using unit cell model (a): Silicon interposer, (b): PCB                                                                                                                                                                                                                                                 | 15    |

| 10 | PDN unit cell translation from physical model to SPEF netlist (a): Silicon interposer, (b): PCB                                                                                                                                                                                                                      | 16    |

| 11 | Metal layers used in Synopsys PrimeRail for IR-drop noise co-analysis                                                                                                                                                                                                                                                | 17    |

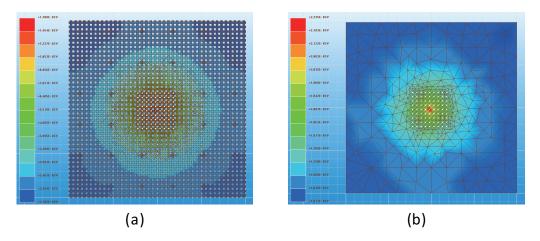

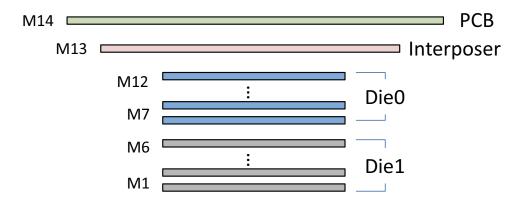

| 12 | Validation of the unit cell model in comparison with Ansys SiWave (a):<br>Keysight ADS (15.86mV, SPICE), (b): Ansys SiWave (17.08mV)                                                                                                                                                                                 | 18    |

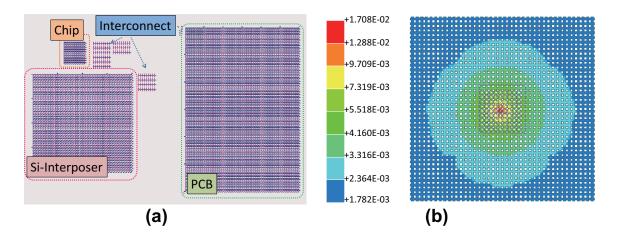

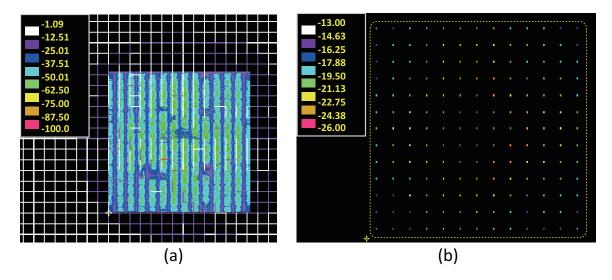

| 13 | Co-simulated IR-drop result of FFT3 circuit in Synopsys PrimeRail (a): IC<br>+ Si-Interposer + PCB (full system), (b): C4 bumps                                                                                                                                                                                      | 18    |

| 14 | IR-drop map of each layers on the co-simulated PDN (a): PCB, (b): Si-<br>interposer, (c): Die0, (d): Die1                                                                                                                                                                                                            | 19    |

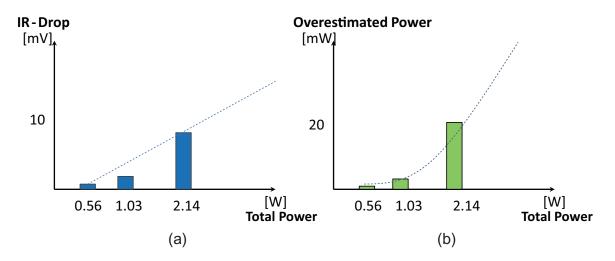

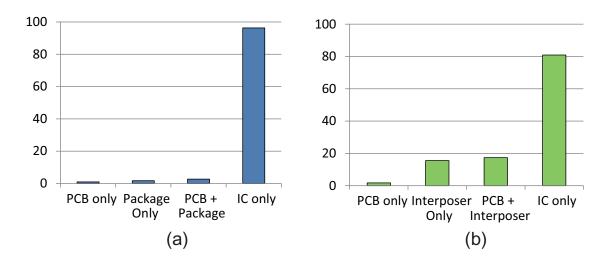

| 15 | Benefits anticipation of co-simulation on (a): IR-drop, (b): Power saving.                                                                                                                                                                                                                                           | 21    |

| 16 | Ratio of each system components on IR-drop generation (Average of three circuits used on Table 2) (a): System with organic package, (b): System with Si-interposer.                                                                                                                                                  | 21    |

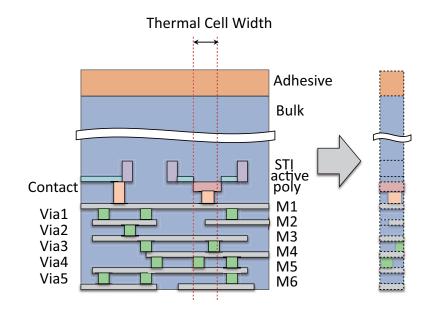

| 17 | Example of thermal cells in a 6 metal layer IC. Total 17 layers of thermal cells are inside the dotted lines.                                                                                                                                                                                                        | 22    |

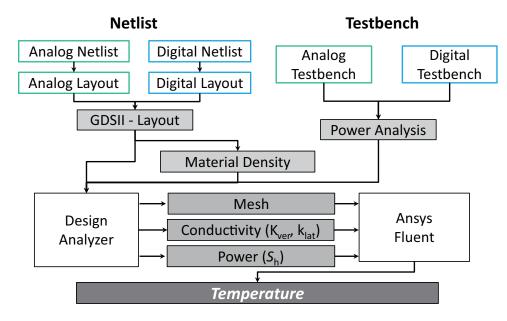

| 18 | Proposed thermal analysis flow for the GDSII-level analog/digital mixed design                                                                                                                         | 23 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

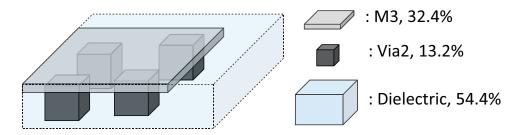

| 19 | A thermal cell (dotted cube) with different material composition                                                                                                                                       | 24 |

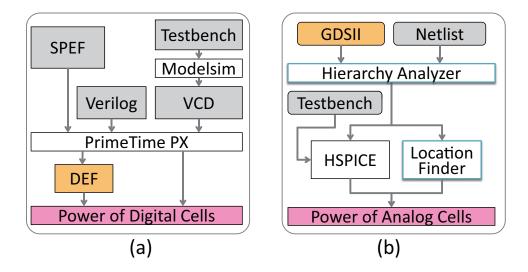

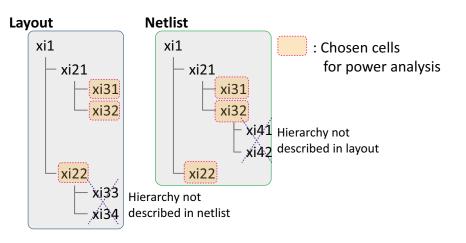

| 20 | Power analysis flow of (a) digital design, and (b) analog design                                                                                                                                       | 26 |

| 21 | An example of Hierarchy Analyzer on a netlist, choosing analog cells for power analysis.                                                                                                               | 27 |

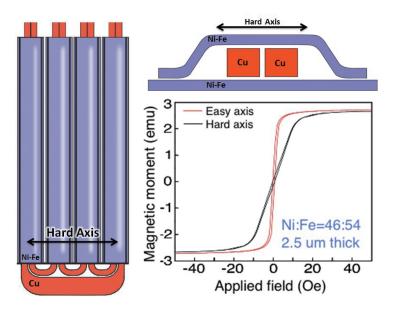

| 22 | Top view of a part of eight single-turn, coupled power inductors (left), cross-section of magnetic cores and windings (top right) and magnetization curves for the Ni-Fe core material (bottom right). | 29 |

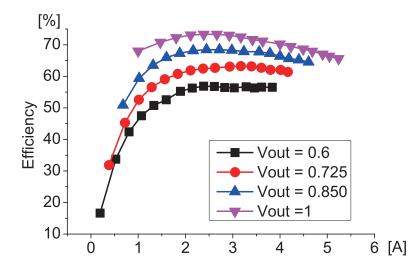

| 23 | IVR efficiency as a function of load current at 75MHz switching frequency.                                                                                                                             | 30 |

| 24 | (a) Top-down view, (b) side view of the IVR.                                                                                                                                                           | 31 |

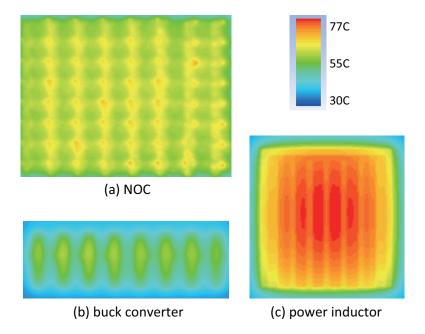

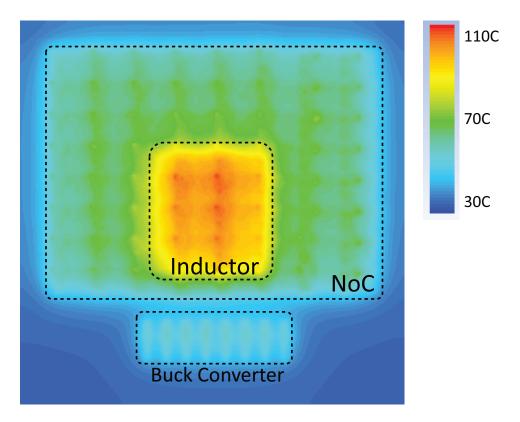

| 25 | Thermal maps. (a) NoC, (b) power inductor, (c) buck converter when generating (= consuming) 5W                                                                                                         | 33 |

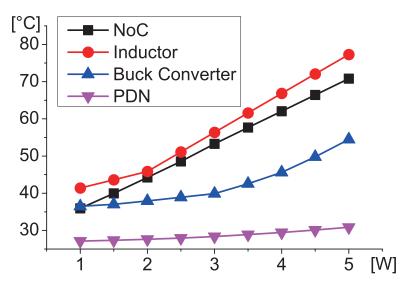

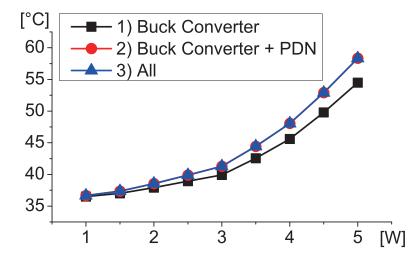

| 26 | Temperature of each blocks in the IVR                                                                                                                                                                  | 33 |

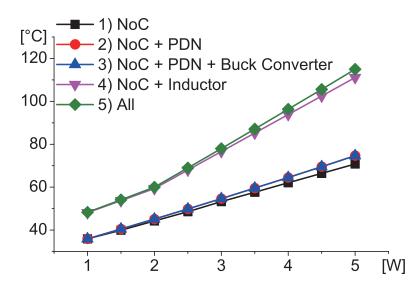

| 27 | Temperature of NoC on different analysis scenarios                                                                                                                                                     | 35 |

| 28 | 4 Scenarios for NoC temperature analysis                                                                                                                                                               | 35 |

| 29 | Thermal map of the IVR full chip when operating at 5W                                                                                                                                                  | 36 |

| 30 | Temperature of buck converter on different analysis scenarios                                                                                                                                          | 36 |

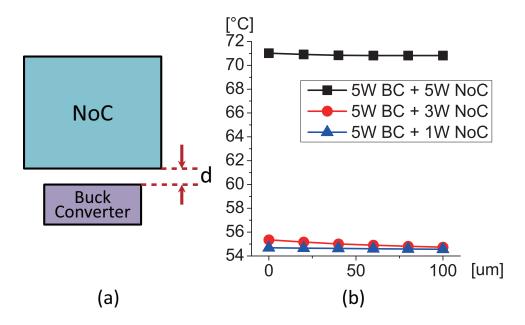

| 31 | Temperature when changing the distance between NoC and buck converter.<br>(a) Block diagram, (b) simulation results.                                                                                   | 38 |

| 32 | Temperature map when the distance between NoC and the buck converter is (a) 0um (max temp = $71.02^{\circ}$ C), (b) 100um, $70.82^{\circ}$ C                                                           | 38 |

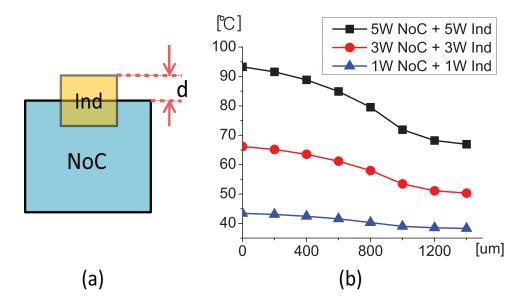

| 33 | Temperature when changing the overlap distance between NoC and the power inductor. (a) Block diagram, (b) simulation results                                                                           | 39 |

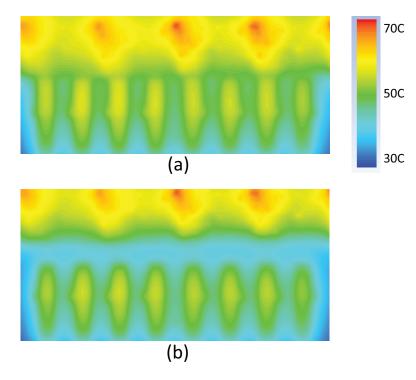

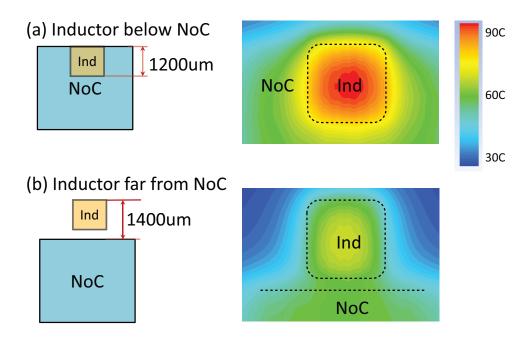

| 34 | Temperature change when (a) inductor is placed beneath the NoC, (b) in-<br>ductor is not overlapping the NoC                                                                                           | 39 |

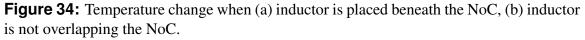

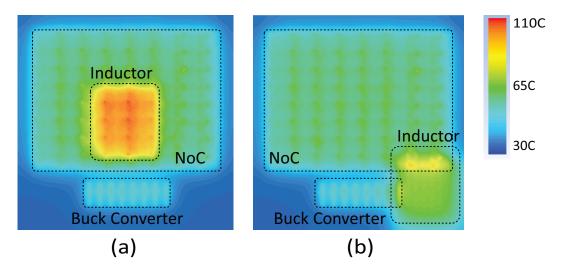

| 35 | Proposed design block relocation technique. (a) Inductor relocation to min-<br>imize the overlap, (b) design block relocation results                                                                  | 41 |

| 36 | Thermal map of the IVR. (a) Inductor placed in the middle of the chip, (b) inductor placed on the bottom right of the chip to reduce thermal coupling                                                  | 41 |

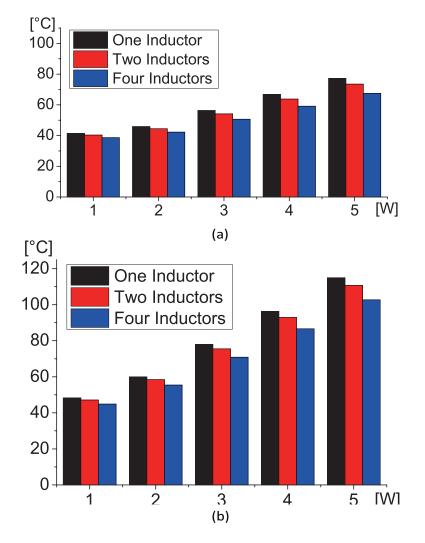

| 37 | Inductor spreading results: (a) temperature of each inductors, (b) full-chip temperature of the IVR using different inductors.                                                                         | 42 |

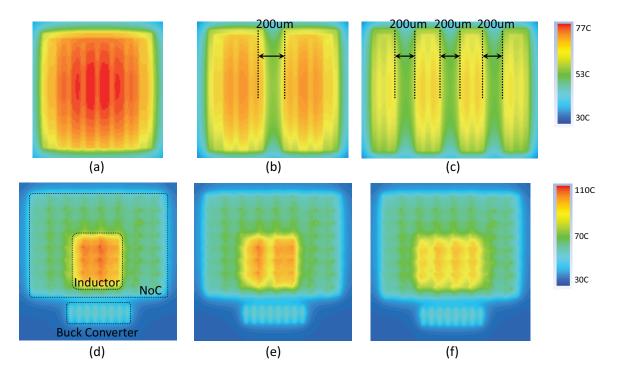

| 38 | Temperature map of inductor spreading: (a-c) temperature map of inductor with no other heat sources, (d-f) temperature map of the full chip. (a,d) one set of eight coupled inductor, (b,e) two sets of four coupled inductor, (c,f) four sets of two coupled inductor | 43 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

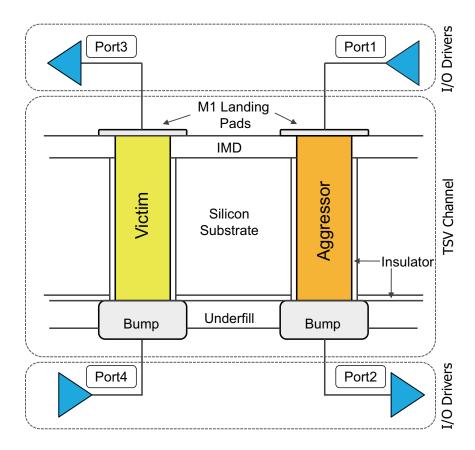

| 39 | A simplified model of TSVs and I/Os in 3D IC                                                                                                                                                                                                                           | 47 |

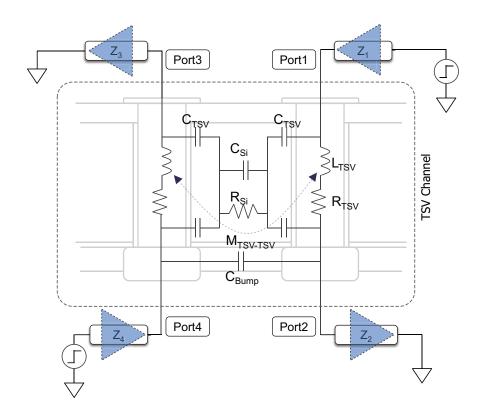

| 40 | Equivalent lumped circuit model for the TSV channel                                                                                                                                                                                                                    | 48 |

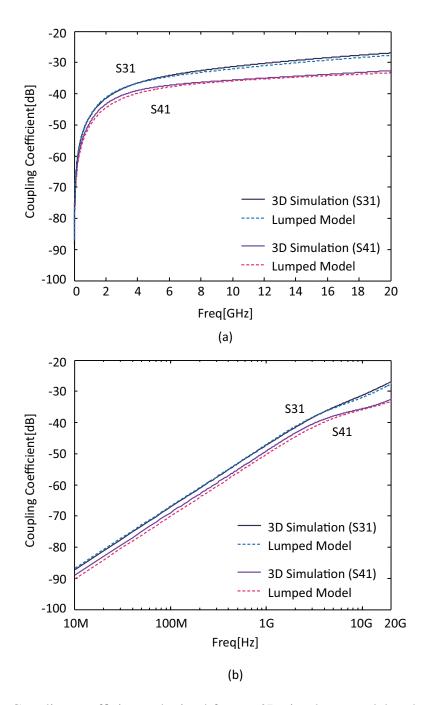

| 41 | Coupling coefficients obtained from a 3D simulator model and the proposed lumped circuit model when the TSV-to-TSV distance is $10\mu m$ . (a) Linear scale, (b) Log Scale                                                                                             | 50 |

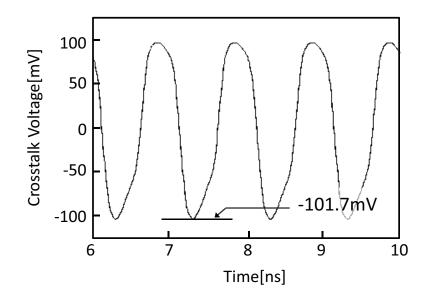

| 42 | Crosstalk voltage observed at port3 when 1.2V, 1GHz digital signal in-<br>serted to port1. (1× driver, TSV-to-TSV distance: $10\mu m$ .)                                                                                                                               | 51 |

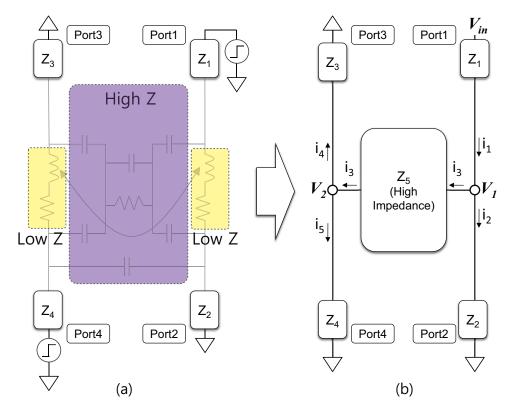

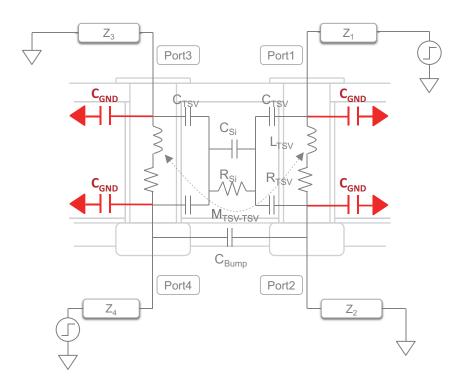

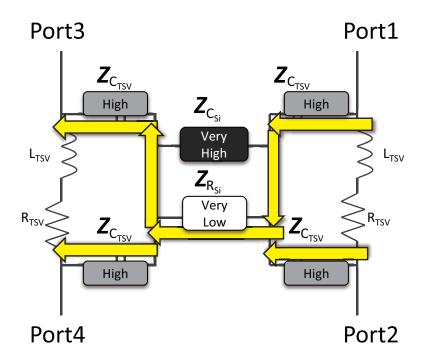

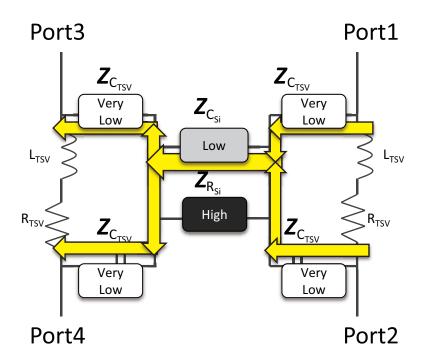

| 43 | (a) Impedance level of each component in the lumped circuit model, (b) Simplified model for coupling analysis.                                                                                                                                                         | 51 |

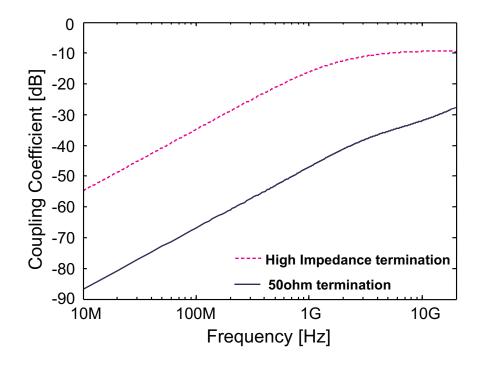

| 44 | Coupling coefficients of the $50\Omega$ termination condition (solid line) and the high impedance termination (1× driver, dotted line) condition                                                                                                                       | 52 |

| 45 | Impact of GND capacitance in TSV coupling channel.                                                                                                                                                                                                                     | 54 |

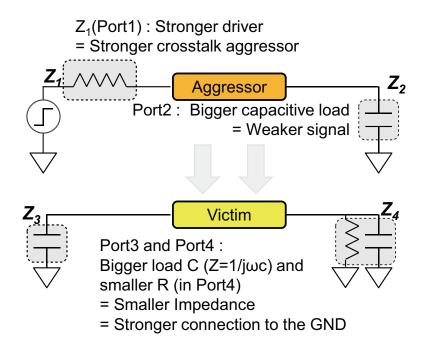

| 46 | Visualization of a driver strength, load impedance, and the relationship be-<br>tween the aggressor and the victim.                                                                                                                                                    | 55 |

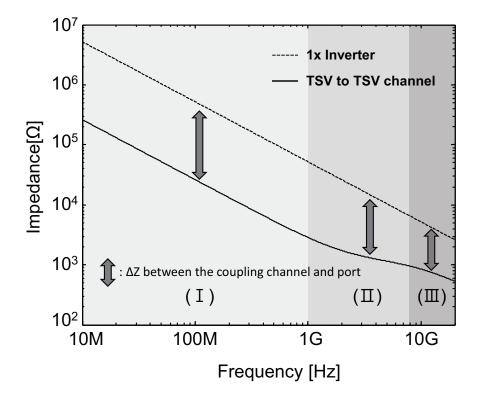

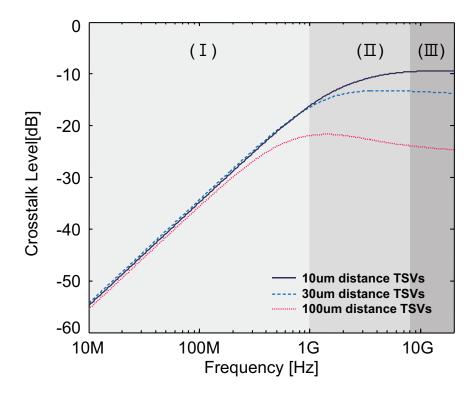

| 47 | Impedance difference between the silicon substrate channel, and the gate capacitance in different regions: (I) low frequency (< 1GHz), (II) middle frequency (1GHz to 8GHz), (III) high frequency (> 8GHz)                                                             | 56 |

| 48 | Coupling path in the low frequency region                                                                                                                                                                                                                              | 57 |

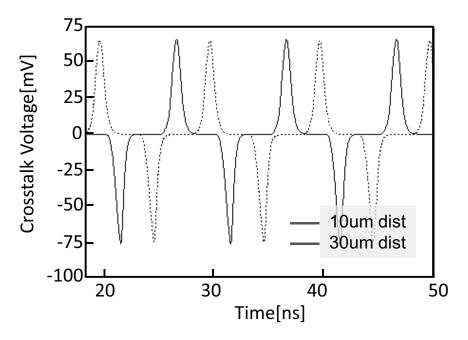

| 49 | Crosstalk voltage of 100MHz digital signal when the distance between TSV is 10um, and 30um ( $1 \times$ driver)                                                                                                                                                        | 58 |

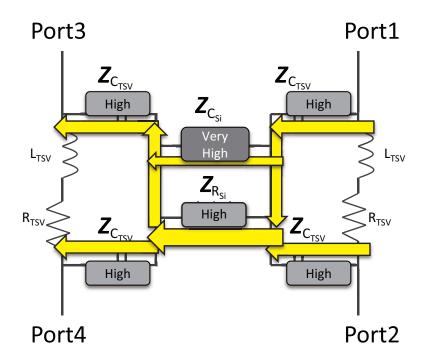

| 50 | Coupling path in the middle frequency region                                                                                                                                                                                                                           | 59 |

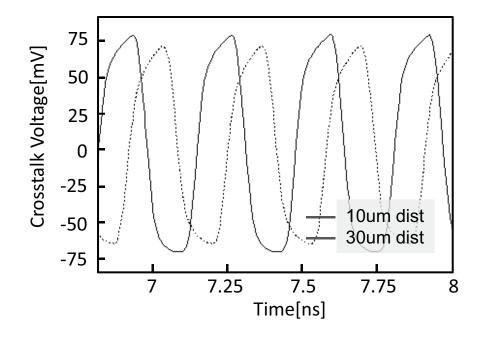

| 51 | Crosstalk voltage of 3GHz digital signal when the distance between TSV is 10um, and 30um ( $1 \times$ driver).                                                                                                                                                         | 60 |

| 52 | Coupling path in the high frequency region                                                                                                                                                                                                                             | 61 |

| 53 | Frequency dependency on TSV coupling to distance on high impedance termination: (I) low frequency, (II) middle frequency, (III) high frequency.                                                                                                                        | 62 |

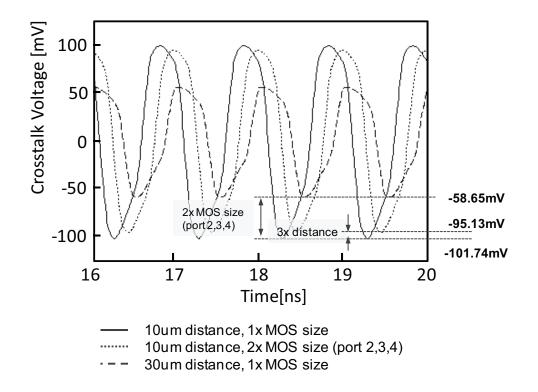

| 54 | Crosstalk voltage of 1GHz digital signal when distance and gate size have changed.                                                                                                                                                                                     | 63 |

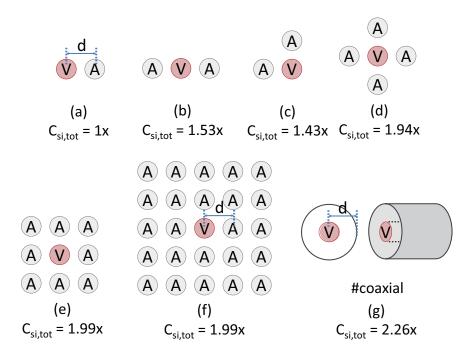

| 55 | Illustration showing non-linear capacitance increase when the number of aggressors increase, and (g) the maximum limit of coupling capacitance of a TSV.                                                                                                               | 65 |

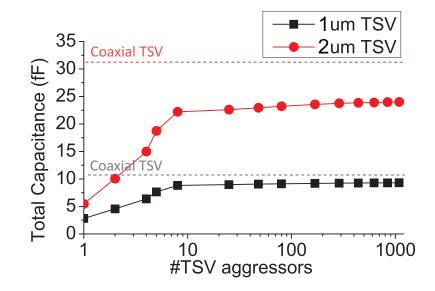

| 56 | Total capacitance of a victim when # of aggressors increase in two TSV technologies: $1/3/12\mu$ m and $2/5/20\mu$ m. (radius/pitch/height)                           | 66 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

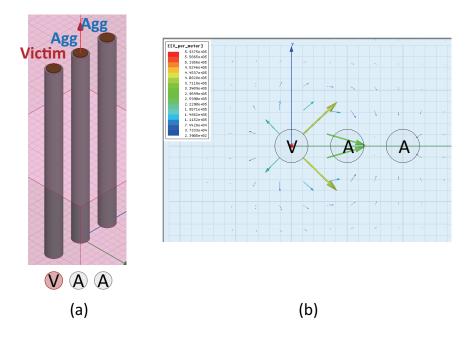

| 57 | Neighbor Effect. (a) Two aggressor model in HFSS, (b) the E-field distribution between the TSVs.                                                                      | 67 |

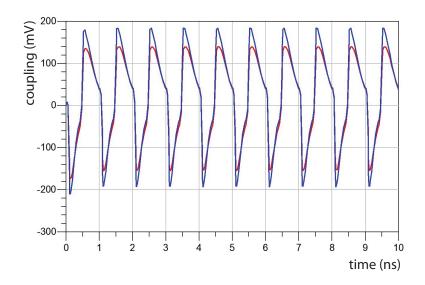

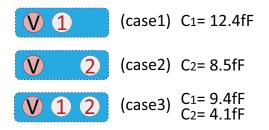

| 58 | Coupling voltage of the near (blue) and far (red) aggressors shown in Figure 57                                                                                       | 68 |

| 59 | Neighbor Effect case study on how neighbor TSVs affect other aggressors                                                                                               | 68 |

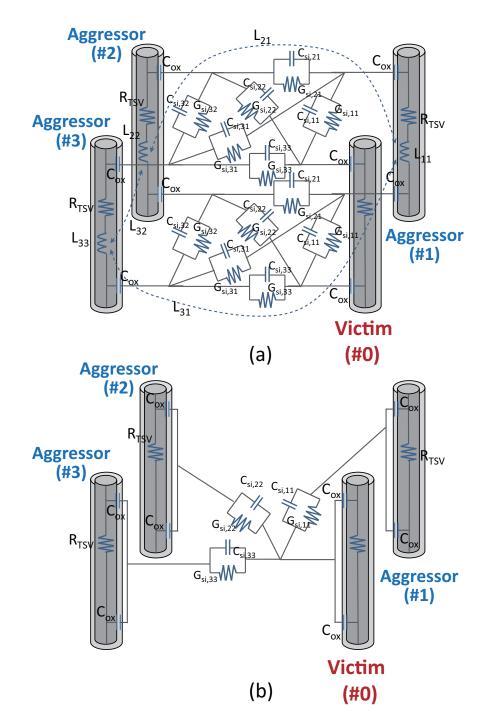

| 60 | (a) Original model proposed in [9], and (b) the proposed compact TSV model for full-chip analysis.                                                                    | 70 |

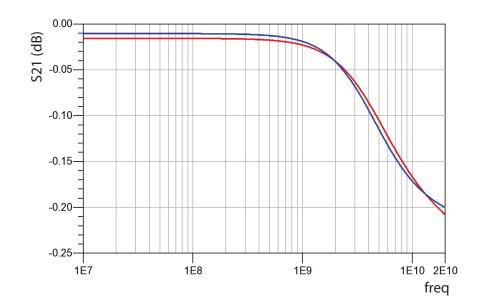

| 61 | S-parameter comparison between the proposed model and HFSS (red: HFSS, blue: proposed model)                                                                          | 74 |

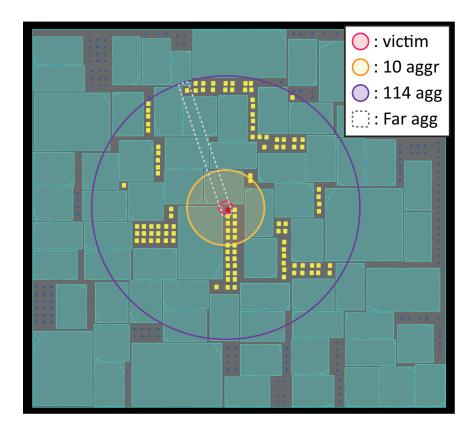

| 62 | Comparison between a small $N$ (10 aggressors) and a large $N$ (114 aggressors) in the proposed algorithm.                                                            | 77 |

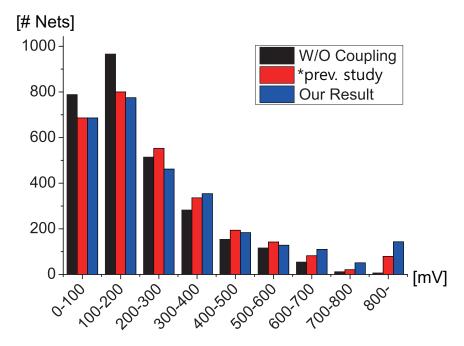

| 63 | Coupling analysis result. X axis denotes the noise voltage bins, and Y axis denotes the number of nets contained in the specific bin. Previous study refers to [45]   | 79 |

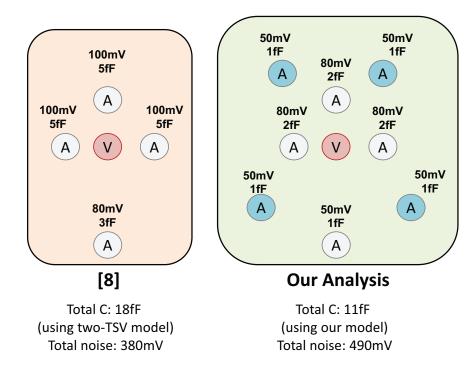

| 64 | Why delay and noise trend is different. Left shows the analysis in [45], and right shows analysis of this work.                                                       | 80 |

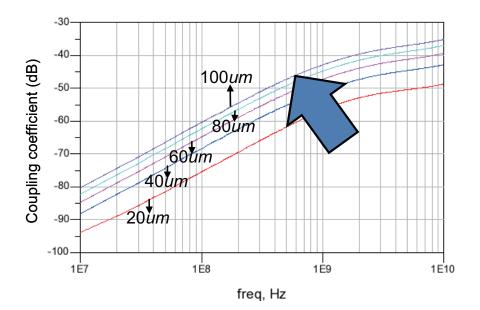

| 65 | S-parameter simulation of coupling coefficient with different TSV heights (20-100 $\mu m$ ).                                                                          | 81 |

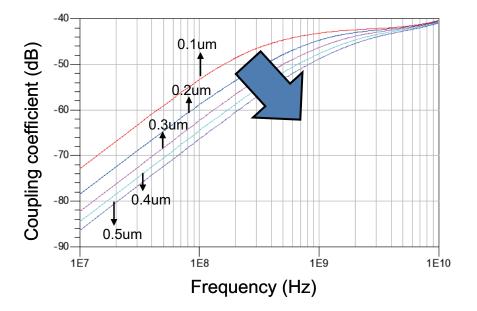

| 66 | S-parameter simulation of coupling coefficient with different liner thickness (0.1-0.5 $\mu$ m).                                                                      | 82 |

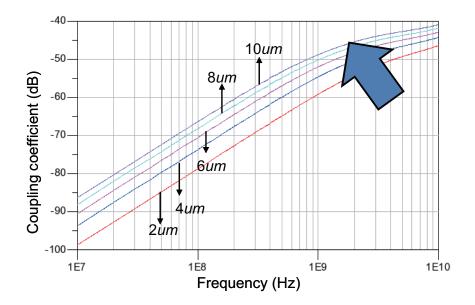

| 67 | S-parameter simulation of coupling coefficient with different TSV diameters $(2-10\mu m)$ .                                                                           | 83 |

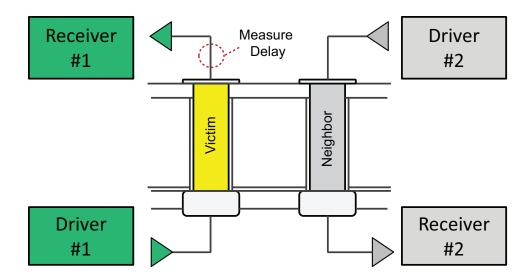

| 68 | Single net delay analysis model of a TSV having one neighbor TSV                                                                                                      | 84 |

| 69 | Delay impact on various TSV parameter change when driver (std. cell) size changes $(1x - 16x)$ : (a) TSV height, (b) Liner thickness, and (c) TSV radius.             | 85 |

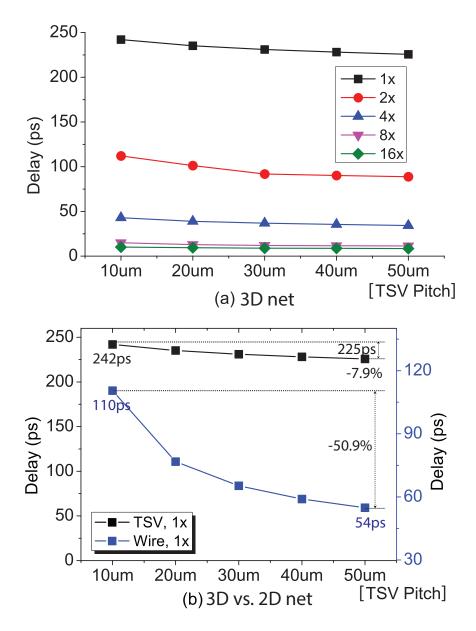

| 70 | Delay impact when TSV pitch changes: (a) Driver sizes from 1x to 16x, and (b) Comparison between 3D (black) and 2D (blue) when having same dimensions                 | 87 |

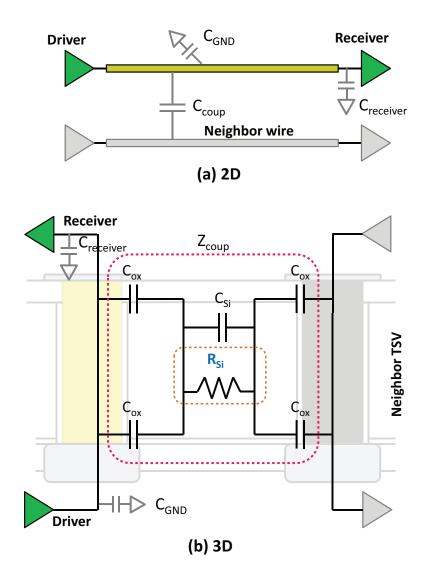

| 71 | All loads (GND, receiver, and coupling) in (a) 2D net and (b) 3D TSV net                                                                                              | 88 |

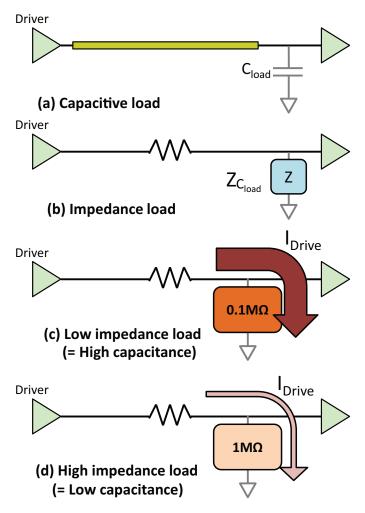

| 72 | The "Impedance Load" concept. A capacitive load (a), translates to an impedance load (b). Low-impedance load (c) suffers from more delay than high-impedance load (d) | 89 |

| 73 | Coupling load impedance $Z_{2D}$ and $Z_{3D}$ when TSV pitch is $10\mu m$                                                                                             | 91 |

| 74 | $Z_{\text{coup}}$ change when TSV pitch changes from $10\mu m$ to $50\mu m$ . (a): 2D, and (b): 3D                                                                                                                                                  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 75 | Delay impact when technology scales from 20nm to 10nm (driver size: 1x).<br>TSV height scales from $20\mu m$ to $100\mu m$                                                                                                                          |

| 76 | TSV Path Blocking in a layout: (a) Before TSV Path Blocking, (b) after<br>TSV Path Blocking                                                                                                                                                         |

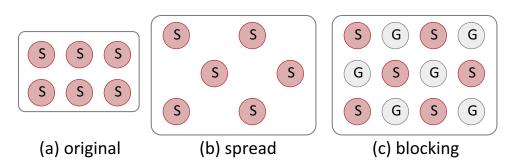

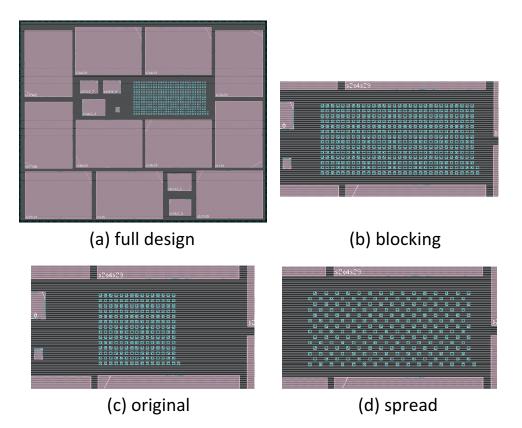

| 77 | (a) Initial wide-I/O design (b) wide I/O design with spread TSVs (c) wide-I/O design with TSV Path Blocking                                                                                                                                         |

| 78 | (a) TSV Path Blocking in Wide-I/O layout, (b) zoom-in photo of (a), (c) initial wide I/O design, (d) wide-I/O with spread TSVs                                                                                                                      |

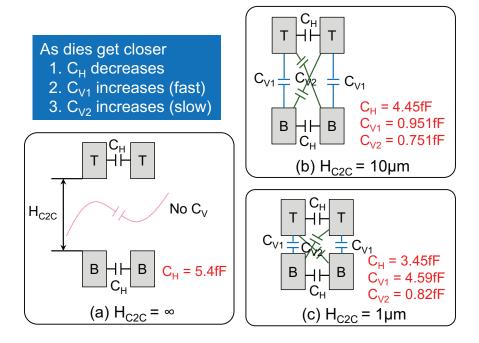

| 79 | How capacitance changes when chip-to-chip distance changes from $\infty$ to $1\mu$ m. Metal dimensions: width = $1.8\mu$ m, pitch = $1.8\mu$ m, thickness: $2.8\mu$ m. $C_H$ and $C_V$ respectively denotes horizonal and vertical capacitances 103 |

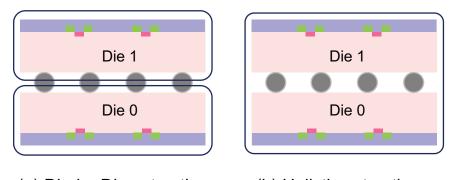

| 80 | Two capacitance extraction methodologies: (a) Die-by-Die extraction, and (b) the proposed Holistic extraction                                                                                                                                       |

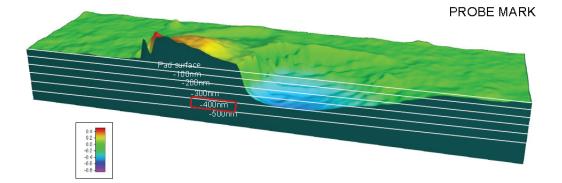

| 81 | Damage caused to the probe pad after testing [29]                                                                                                                                                                                                   |

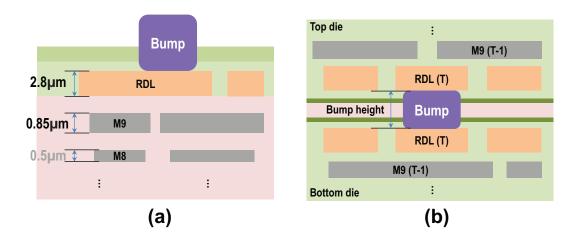

| 82 | Interconnect structure used in this study. (a) Top metal layers in an individual die. (b) Interconnect structure when two dies are stacked in F2F 3D IC. Bump height is the distance between two dies                                               |

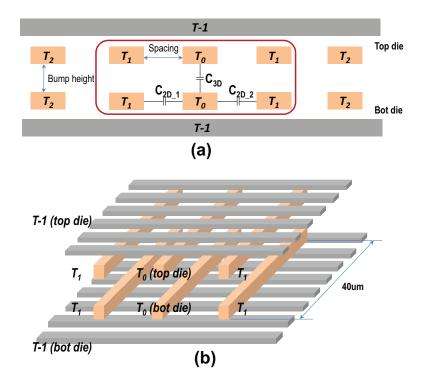

| 83 | General test structure used in this study. (a): Cross-sectional view, (b): 3D view showing the top-metals inside the red box of (a)                                                                                                                 |

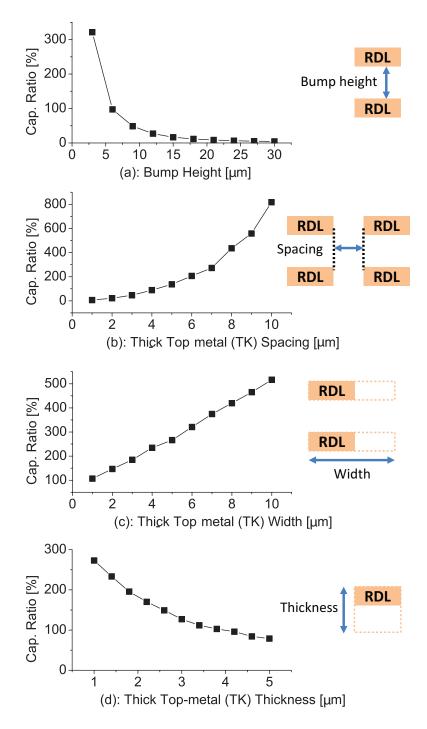

| 84 | <i>3D Cap. Ratio</i> change due to various parameter changes in thick top-metal (TK). (a): Bump height, (b): TK spacing, (c): TK width, (d): TK thickness 108                                                                                       |

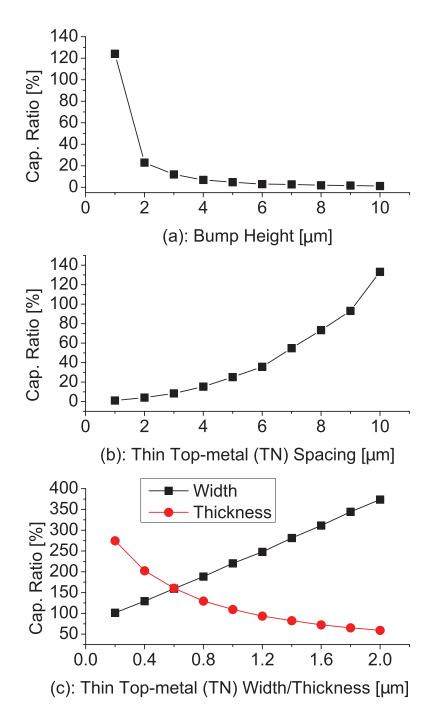

| 85 | <i>3D Cap. Ratio</i> change due to various parameter changes in thin top-metal (TN). (a): Bump height, (b): TN spacing, (c): TN width/thickness 111                                                                                                 |

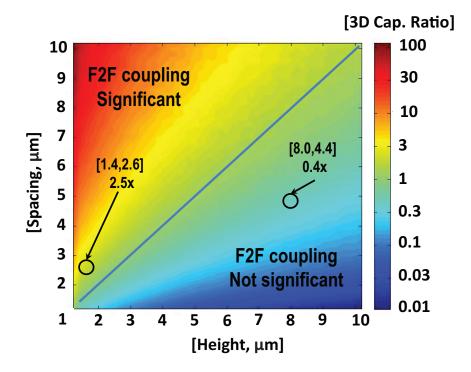

| 86 | Impact of metal-spacing/bump-height on 3D capacitance on TK 112                                                                                                                                                                                     |

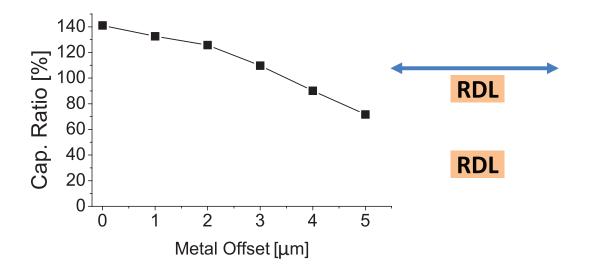

| 87 | 3D Cap. Ratio change when the offset of top-tier changes                                                                                                                                                                                            |

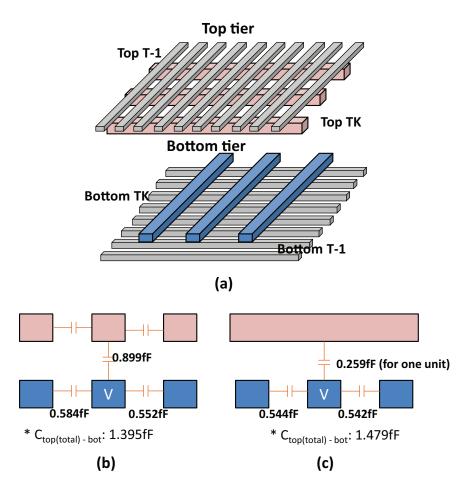

| 88 | Top die rotated by 90°. (a) 3D view of the 90° rotated test structure. (b)<br>Capacitance values in non-rotated structure. (c) Capacitance values in 90°<br>rotated structure                                                                       |

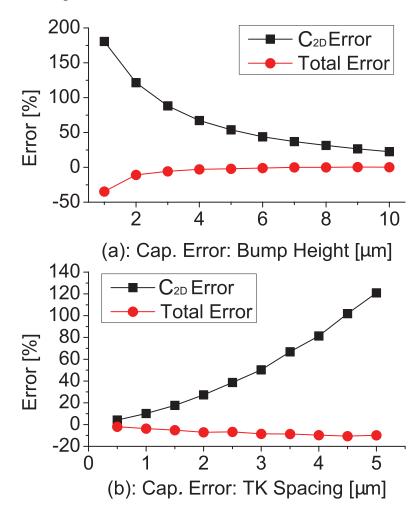

| 89 | Capacitance error variation when using Die-by-die Extraction scheme: (a)<br>Bump height, (b) TK spacing                                                                                                                                             |

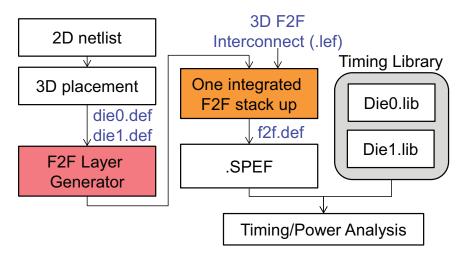

| 90 | Proposed extraction flow using the F2F Layer Generator                                                                                                                                                                                              |

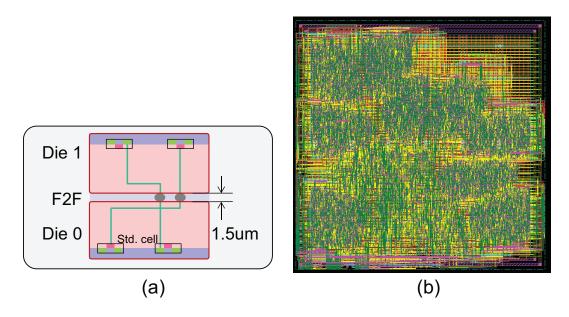

| 91  | <ul><li>(a): F2F stack-up created by the F2F Layer Generator. (b): One integrated full-chip layout in Cadence Encounter with power distribution network (PDN).</li></ul>                                                                                                             |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

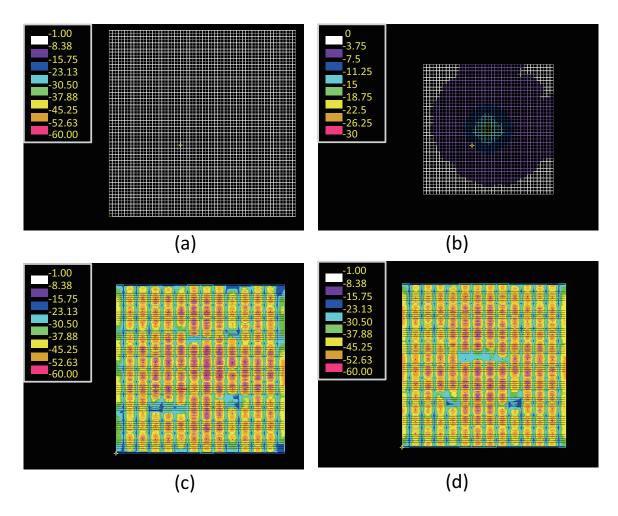

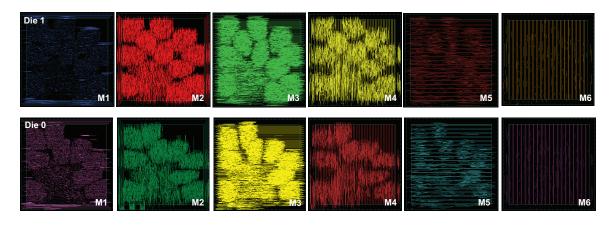

| 92  | Individual metal layer routing in F2F implementation of AES benchmark with PDN                                                                                                                                                                                                       |

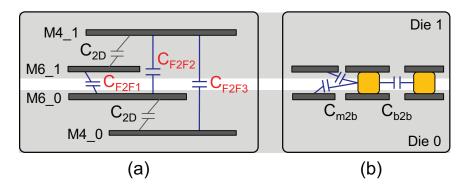

| 93  | F2F (3D) capacitances in F2F bonding. (a): Metal-to-metal capacitance<br>(b): Bump capacitances                                                                                                                                                                                      |

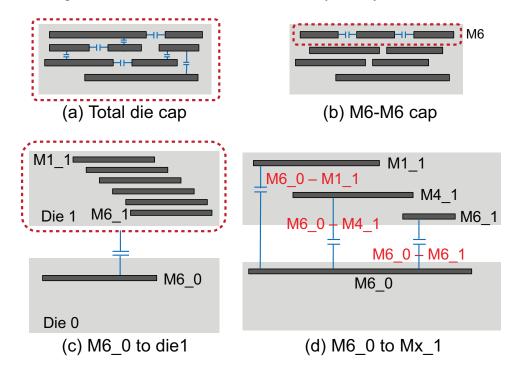

| 94  | Parasitic capacitance definitions. (a) Total die capacitance, (b) M6-M6 capacitance, (c) M6 (Die 0) to Die 1 capacitance, (d) M6_0 (Die 0) to $Mx_1$ (Die 1) capacitance                                                                                                             |

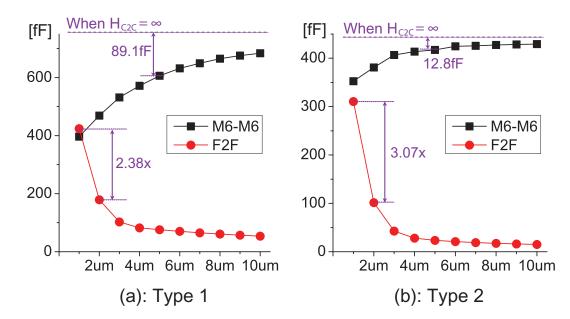

| 95  | F2F capacitance in different chip-to-chip distance. (a) Type 1, (b) Type 2.<br>See Table 13 for interconnect dimensions                                                                                                                                                              |

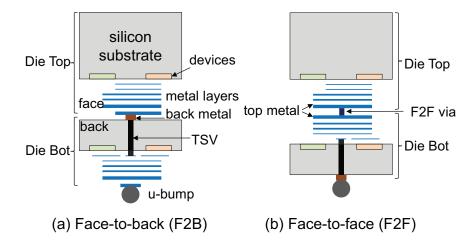

| 96  | Basic 2-tier die bonding styles: (a) Face-to-back (F2B), and (b) Face-to-<br>face (F2F)                                                                                                                                                                                              |

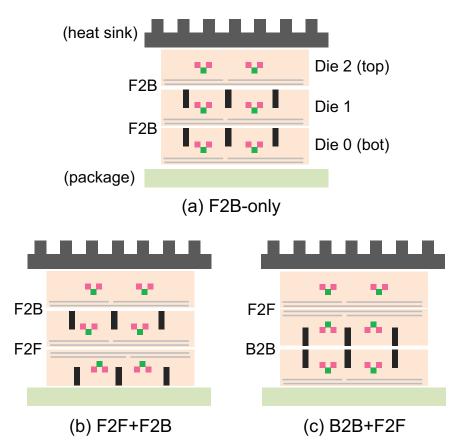

| 97  | 3-tier die bonding styles: (a) Face-to-back only (F2B-only), (b) Face-to-<br>face and face-to-back combined (F2F+F2B), and (c) Back-to-back and face-<br>to-face combined (B2B+F2F)                                                                                                  |

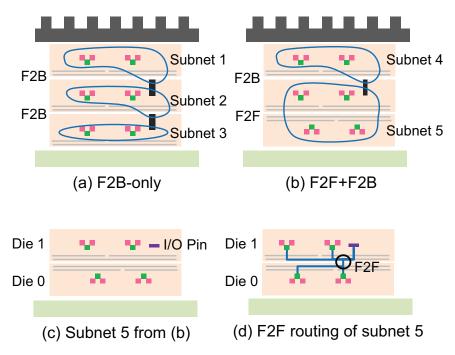

| 98  | Net handling and routing in 3-tier mixed bonding. (a) A 6-pin net with 2 TSVs is split into one subnet per tier in F2B-only case, (b) F2F bonding does not cause net splitting, (c) Subnet 5 from (b), where the TSV is defined as an I/O pin, (d) A sample routing topology for (c) |

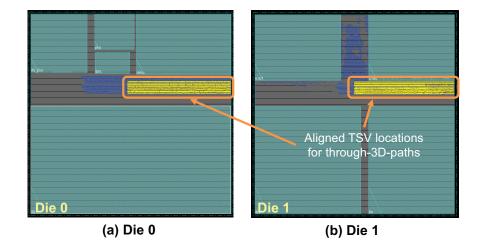

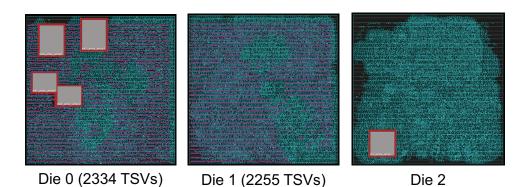

| 99  | TSV layers aligned in T2 Core to provide through path for Die 0–Die 2 connecting nets (Through-3D-Paths) in F2B-only (blue dots: regular TSVs, yellow dots: Through-3D-Path TSVs)                                                                                                    |

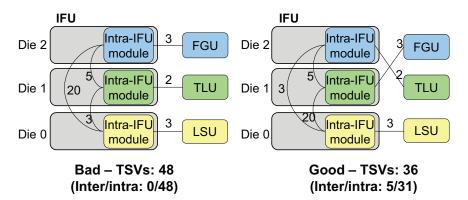

| 100 | 3-tier IFU folding impact on intra/inter-IFU TSV count                                                                                                                                                                                                                               |

| 101 | Many TSVs used in 3-tier TLU (in T2 Core) occupying a large area in F2B-only bonding. (purple dots: TSV)                                                                                                                                                                             |

| 102 | 2-tier vs 3-tier IFU (in T2 Core) folding impact on footprint in F2B-only bonding. (a) IFU 2-tier, (b) IFU 3-tier (footprint 10% reduced), (c) layouts. 147                                                                                                                          |

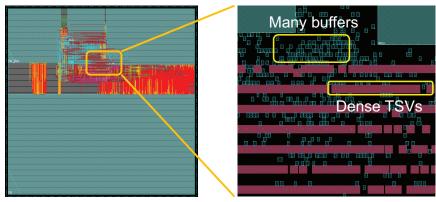

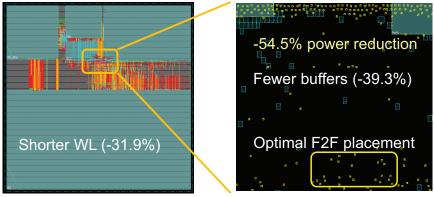

| 103 | F2F bumps for better design in F2F+F2B bonding under the same floorplan<br>in T2 Core: (a) F2B-only (TSVs for 3D connection), (b) F2F+F2B (F2F<br>bumps for 3D connection)                                                                                                           |

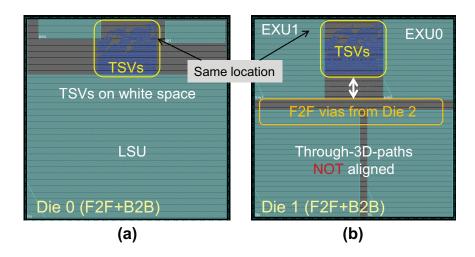

| 104 | Through-3D-paths between Die 1 TSV and Die 2 F2F bumps not aligned<br>in B2B+F2F bonded T2 Core because TSVs must be placed both in Die 1<br>and Die 2 (see Figure 99 for comparison)                                                                                                |

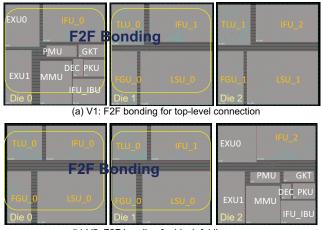

| 105 | F2F bonding choice for more power reduction in F2F+F2B bonded T2<br>Core. (a) F2F bonding for top-level, (b) F2F bonding for block-folding<br>(folded blocks in orange font)                                                                                                                                                                                                                       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

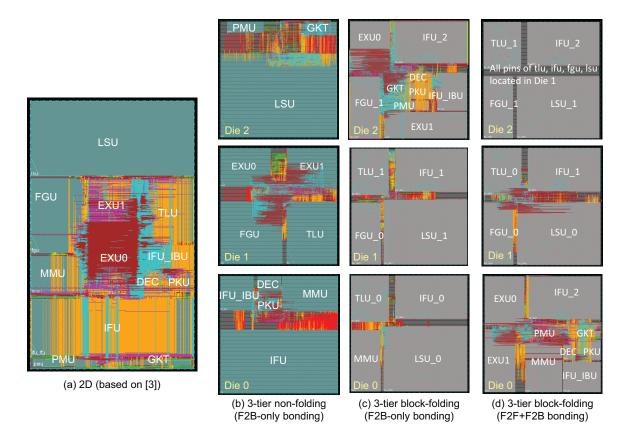

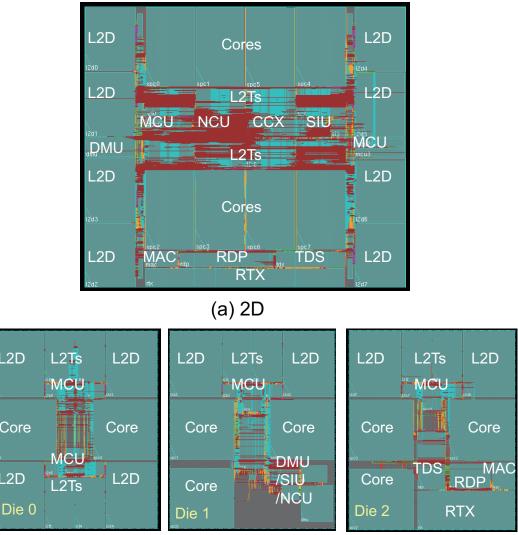

| 106 | GDSII layouts of various 3-tier T2 Core designs: (a) 2D based on [26], (b) 3-tier non-folding in F2B-only, (c) 3-tier block-folding in F2B-only, and (d) 3-tier block-folding in F2F+F2B                                                                                                                                                                                                           |

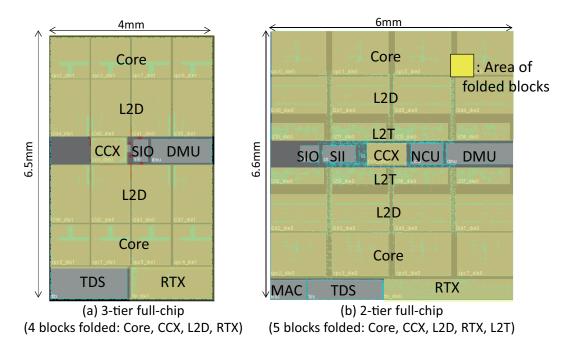

| 107 | White space (= gray area) in T2 full-chip. (a) 2D floorplan (9mm x 7.9mm),<br>(b) 3-tier 3D floorplan (4.5mm x 5.4mm). More silicon area used in 3D<br>remains as white space due to floorplanning challenges                                                                                                                                                                                      |

| 108 | How folding area reduces in 3-tier designs. Footprint reduction in 3-tier leads to less folded blocks. (a) Die 1 in 3-tier, (b) Die 1 in 2-tier [27] 159                                                                                                                                                                                                                                           |

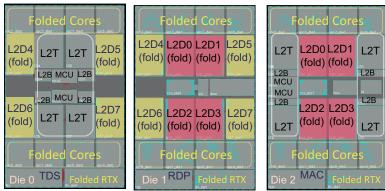

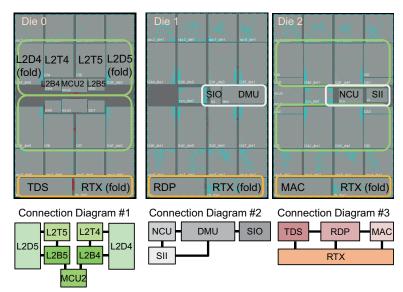

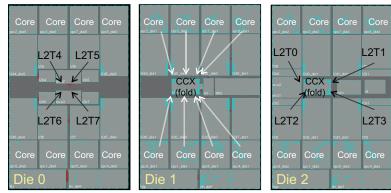

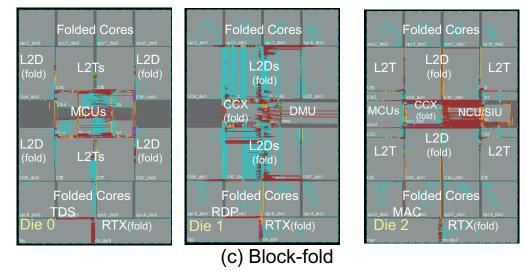

| 109 | Full-chip block-folding floorplan strategies: (a) 3-tier folded modules and L2\$ floorplan. Die 1 is utilized to place folded L2Ds, and other L2\$s are placed on Die 0 and Die 2. Corresponding L2D pins are placed on each dies. (b) How highly-connective modules are placed closely to each other and its connection diagram. (c) L2T-CCX and CCX-Core I/O pin assignment to reduce congestion |

| 110 | Full-chip block-folding floorplan strategy: L2T-CCX and CCX-Core I/O pin assignment to reduce congestion                                                                                                                                                                                                                                                                                           |

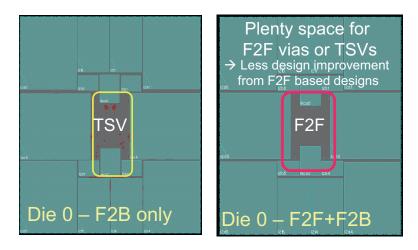

| 111 | TSV/F2F placement in full-chip. Because TSVs are placed in its optimal locations (left) due to less congestion and large whitespace, F2F bonding (right) do not provide significant benefits over TSVs                                                                                                                                                                                             |

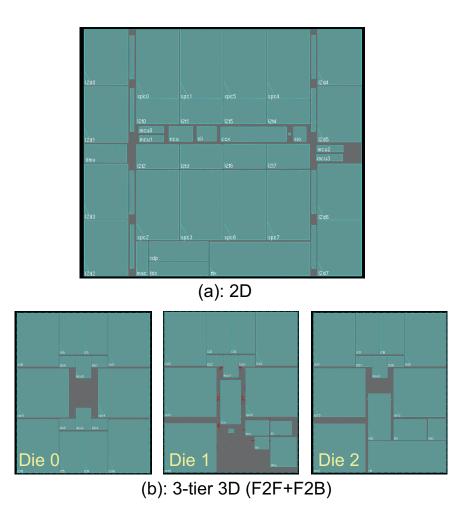

| 112 | GDSII layouts of various full-chip 3-tier 3D IC designs in F2F+F2B bond-<br>ing: (a) 2D based on [27], (b) 3-tier non-folding, and (c) 3-tier block-folding.167                                                                                                                                                                                                                                    |

#### SUMMARY

The objective of this research is to study and develop computer-aided-design (CAD) methodologies for reliability in chip-package co-designed three-dimensional integrated circuit (3D IC) systems. 3D IC technologies refer to many vertical integration methodologies (such as through-silicon vias and face-to-face bumps) that enable the stacking of ICs. By 3D IC stacking, various benefits in terms of power and performance can be gained. However, it is not only the 3D IC design itself but also the design of the package and its many connections that must be optimized to maximize the benefit of 3D IC technology. Therefore, this work proposes design methodologies that enable reliable 3D IC in terms of signal integrity, power integrity, and thermal optimization.

The first section of this dissertation presents chip/package/PCB co-analysis methodologies. In detail, two studies are presented: (1) a methodology of co-simulating IR-drop noise for 3D IC, silicon interposer, and PCB simultaneously, and (2) a thermal analysis methodology on integrated voltage regulators (IVRs) that are implemented in silicon interposers. By proposing co-analysis methodologies in two different domains, this section provides ideas for co-analysis that can be further extended to other analysis domains as well.

The second section investigates the impact of electric coupling between through-silicon vias (TSVs) in 3D ICs. TSV-to-TSV coupling is non-negligible, and the impact of coupling is different in ICs and interposer/package/PCBs. Therefore, the first part of this section investigates how TSV-to-TSV coupling is different in ICs compared to interposers/packages and PCBs. Then, the second part proposes a methodology of analyzing TSV-to-TSV coupling in full-chip scale.

The third section investigates the impact of parasitics in face-to-face (F2F) bonding. As technology scales in F2F bonded 3D ICs, the distance between the ICs becomes as small

as few microns. Due to this shorter distance, significant electric coupling occurs between these ICs. The impact of parasitics in F2F bonding in terms of capacitance is first investigated in various scenarios. Then, a holistic methodology of extracting F2F capacitance is proposed in full-chip scale. Based on the methodology, impact of F2F parasitics in timing and power are observed.

The final section presents power reduction methodologies and its benefits when 3-tier 3D ICs are designed in OpenSPARC T2 benchmark. It is shown that one additional tier available in 3-tier 3D ICs does offer more power saving compared with their 2-tier 3D IC counterparts, but more careful floorplanning, through-silicon via (TSV) management, and block folding considerations are required. This section develops effective CAD solutions that are seamlessly integrated into commercial CAD tools to handle 3-tier 3D IC power optimization under various bonding style options.

# **CHAPTER I**

#### INTRODUCTION

For the last fifty years, the semiconductor industry has been driven to double the number of transistors every two years by the "Moore's law", which motivates power/performance improvement by device scaling. This law has been used to set targets for research and development in the semiconductor industry to guide long-term planning [15]. Thanks to the Moore's law, in addition to the exponential growth in the transistor numbers by scaling, significant improvement has also been made to the performance of the transistors themselves. The development of new technologies and devices such as strained silicon [77], high-K metal gate [57], finFETs [6], and fully-depleted SOI [20] are some examples of the research done to follow this technology trend. However, doubts are rising that Moore's law may come to an end in the near future.

Recent studies are reporting challenges to the semiconductor scaling. First, studies indicate the physical limit of scaling. Current 14nm node transistors consist of countable number of atoms. Knowing that transistors would not be smaller than a few or less atoms, studies are predicting that scaling of transistors will eventually come to an end. Second, mask lithography is encountering its challenges. Mask lithography is currently based on 193nm lithography tools. Many technologies have been developed to extend the use of 193nm waves such as double patterning [17] and triple patterning [19]. However, a next generation lithography technology is required to follow up the mask generation in the scaling trend, and extreme ultraviolet (EUV) is a rising technology to break the lithography wall. Unfortunately, studies are still in progress to provide EUV for mass production and it suggests that EUV will come in long effort with high cost [47].

# 1.1 Three-dimensional Integrated Circuits (3D ICs) and Silicon Interposers as Alternative Technologies

Knowing that the forecasts on semiconductor scaling is not that bright, alternative technologies for scaling are rising up. Nanowire transistors are gaining attention as a future device to replace CMOS [22], and carbon-nanotube field-effect transistors also show its potential as an alternative to CMOS based on its 20x power-performance benefits [60]. In addition to these devices, Silicon interposers and three-dimensional integrated circuits (3D ICs) are gaining significant attention as alternative technologies.

Silicon interposer, a silicon die with no actives, is a technology developed to fill the gap between ICs and packages due to the smaller interconnect it can provide in low cost. Smaller interconnects in silicon interposers allow ICs to be placed side-by-side. Thus, high-bandwidth and low-latency designs are possible. In addition, products are already made in silicon interposer [81] proving the potential of this new technology [see Figure 1 (a)]. 3D IC is a technology of stacking two (or more) ICs in vertical (3D) dimension. Comparing to conventional 2D ICs, 3D ICs provide smaller footprint because we have multiple layers of transistors instead of one. Having the smaller footprint advantage, 3D ICs can be designed to provide higher performance on lower power. As in Figure 1 (b), future roadmap of 3D ICs and silicon interposers predict that these two technologies will be combined together for ultra-miniaturized high-performance and low-power systems. This will combine every electronic components such as digital, analog, RF, and memory in a small footprint for future systems such as mobile applications [2].

3D ICs can be bonded in two different bonding styles to realize the high-performance and low-power benefits: Using through-silicon-vias (TSVs) or using face-to-face (F2F) bumps. TSVs are metal pillars that penetrate through the silicon substrate. For 3D ICs that use TSVs, ICs are bonded using the back side (where the TSV is exposed) of one die and the face side (the side where top-metal is exposed) of another die. However, in F2F, the ICs are bonded by using both face sides as the bonding side using F2F bumps. Several studies

**Figure 1:** (a) Silicon interposer in actual product [81] and (b) illustration of 3D ICs and silicon interposers for future ultra-miniaturized systems.

indicates that F2F 3D ICs provide advantages over TSV-based 3D ICs in many applications since they do not use any silicon area [27]. F2F bonding can also be applied by using direct copper-to-copper (Cu-Cu) bonding [62]. When Cu-Cu bonding is applied, F2F dies do not have any space between them.

# 1.2 Challenges

Despite the advantages 3D ICs and silicon interposers can provide, many technical challenges exist in its manufacturing and design. In the manufacturing side, for example, manufacturing reliable TSVs is very important. However, faults during manufacturing such

**Figure 2:** 3D ICs using TSVs and F2F bumps: (a) Actual 3D IC product using TSVs [76], (b) illustration of a 3-tier 3D IC, (c) 3D IC designed in F2F bonded style [32], and (d) illustration of a F2F bonded 3D IC with F2F bumps.

as TSV voids and cracks reduce the production yield (see Figure 3). In addition, manufacturing TSVs inside chips require the silicon substrate to be thinned (less than 100um). Handling thinned dies are challenging, and it becomes more challenging when technology scales and requires manufacturers to handle even thinner substrates.