# ADVANCES IN PANEL GLASS PACKAGING OF MEMS AND SENSORS FOR LOW STRESS AND NEAR HERMETIC RELIABILITY

A Dissertation Presented to The Academic Faculty

by

Chintan Buch

In Partial Fulfillment

Of the Requirements for the Degree

Master of Science in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2018

**COPYRIGHT © 2018 BY CHINTAN BUCH**

# ADVANCES IN PANEL GLASS PACKAGING OF MEMS AND SENSORS FOR LOW STRESS AND NEAR HERMETIC RELIABILITY

#### Approved by:

Dr. Rao R. Tummala, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Venkatesh Sundaram School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Oliver Brand School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Peter J. Hesketh School of Mechanical Engineering Georgia Institute of Technology

Date Approved: January 29th, 2018

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to express my sincere gratitude to my advisor Professor Rao R. Tummala for giving me an opportunity to work on cutting edge advanced packaging research at the Georgia Tech 3D Systems Packaging Research Center (GT-PRC). His enthusiasm is inspirational and his experience, vision and guidance have greatly helped shape my thesis. Next, I would like to thank my mentor, Dr. Venkatesh Sundaram, for his guidance and inputs throughout my time as his student. His vast knowledge and experience helped me through several roadblocks in my research. I would also like to thank Dr. Klaus-Jergen Wolter for helping me build a foundation and kick-start my thesis.

Next, I would like to express my gratitude to my committee members Professor Peter J. Hesketh and Professor Oliver Brand for serving on my thesis committee and for their valuable feedback, which helped improve my thesis.

The research staff at PRC also played a critical role in my research with their knowledge, enthusiasm and constant availability. I would like to thank Dr. Fuhan Liu, Dr. Raj Pulugurtha, Dr. Himani Sharma and especially Dr. Vanessa Smet whose motivation and mentorship helped me tremendously. I would also like to thank the administrative staff at PRC including Karen May, Patricia Allen, Brian McGlade, Chris White and Jason Bishop, Dennis, Steven and Lila for all their help and support.

I would like to thank members of the GT-PRC Consortium and industry mentors for their technical support and guidance. I would particularly like to thank James Haley

and Gary Legerton at EMD Performance Materials for their help with conductive copper paste and through-package-via metallization process development.

My stay in Atlanta has been a fantastic experience, thanks to my friends at and outside of work. I'd like to thank Bart, Nithin, Rui, Brett, Bruce, Kaya, Atom, Shreya, Chandra, Tim, Ali, Abhishek, Fabian, Kashyap, Omkar, Vivek, Ninad, Haksun, Bhupender, Sukhada, Tailong, Siddharth, Nathan, Zihan, Teng, Grant, Hao, Shuhei, Yuya, and Jialing.

Lastly, I would like to thank my family for their unconditional love and support and for putting me on the path of education.

#### TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                   | iv                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                     | viii                                                     |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                    | ix                                                       |

| SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                            | xiii                                                     |

| CHAPTER 1: INTRODUCTION  1.1 Current Approaches to MEMS packaging and Their Limitations for Heterogeneous Package Integration (HPI)  1.1.1 Silicon Wafer Level Packaging  1.1.2 Low Temperature Co-Fired Ceramic (LTCC) Substrates and Laminates                                                                                                                                                                                   | 1<br>2<br>3<br>5                                         |

| 1.2 Panel Glass Embedding for HPI with MEMS 1.3 Research Objectives, Unique Approach and Technical Challenges 1.4 Research Tasks and Thesis Organization                                                                                                                                                                                                                                                                           | 9<br>10<br>12                                            |

| CHAPTER 2: LITERATURE REVIEW  2.1 Prior work in reliable cavity formation in thin glass  2.1.1 Wet etching  2.1.2 Sandblasting/powder blasting  2.2 Prior work in glass-glass bonding  2.2.1 Direct Glass-Glass Bonding  2.2.2 Indirect Bonding  2.3 Prior work in fully filled through-glass-via metallization  2.3.1 Copper Filled Through-Glass Vias  2.3.2 Alternate Through Via Metallization Techniques  2.4 Chapter Summary | 14<br>14<br>16<br>18<br>18<br>21<br>22<br>23<br>26<br>28 |

| CHAPTER 3: RELIABLE CAVITY FORMATION IN THIN GLASS PANELS  3.1 Glass Panel Embedding Architectures 3.2 Design Considerations for Glass Cavities 3.2.1 Sidewall roughness and defect size 3.2.2 Sidewall taper 3.2.3 Cavity Base Surface roughness 3.3 Laminated Glass Cavities vs Blind Cavities 3.3.1 Laminated Glass Cavities 3.3.2 Blind cavities                                                                               | 30<br>31<br>32<br>33<br>35<br>37<br>43                   |

| CHAPTER 4: LOW STRESS GLASS-GLASS BONDING 4.1 Adhesive bonding 4.2 Adhesive bonding mechanism, material selection and process advances 4.3 Glass-glass Bonding Characterization and Void Reduction                                                                                                                                                                                                                                 | <b>46</b> 46 47 54                                       |

| 4.3.1 | Void characterization                                                    | 55 |

|-------|--------------------------------------------------------------------------|----|

| 4.4   | Bond shear strength characterization                                     | 60 |

| 4.4.1 | Impact of BCB bonding process selection on shear strength                | 62 |

| 4.5   | Reliability studies                                                      | 63 |

| 4.6   | Summary                                                                  | 64 |

| СНАЕ  | PTER 5: HIGH THROUGHPUT, FULLY-FILLED THROUGH-PACKAO                     | GE |

| VIAS  | IN GLASS FOR CAVITY PACKAGES                                             | 66 |

| 5.1   | Need for Alternate Metallization Process for Fully Filled TPVs           | 66 |

| 5.2   | Transient Liquid Phase Sintering (TLPS) Pastes                           | 67 |

| 5.3   | TPV paste fill process                                                   | 71 |

| 5.4   | Hybrid TPV for improved electrical performance                           | 75 |

| 5.5   | Summary                                                                  | 80 |

| СНАЕ  | PTER 6: SUMMARY AND FUTURE WORK                                          | 82 |

| 6.1   | Summary                                                                  | 82 |

| 6.2   | Reliable Cavity Formation in Thin Glass Panels                           | 83 |

| 6.3   | Low Stress Glass-Glass Bonding                                           | 84 |

| 6.4   | High Throughput, Fully Filled Through-Package-Via Metallization in Glass | 84 |

| 6.5   | Key Contributions                                                        | 85 |

| 6.6   | Recommendations for Future Work                                          | 86 |

| 6.7   | Journal and Conference Publications                                      | 88 |

| REFE  | RENCES                                                                   | 89 |

#### LIST OF TABLES

| Table 1:  | Table showing research objectives, recent prior art and technical challenges                            | 11 |

|-----------|---------------------------------------------------------------------------------------------------------|----|

| Table 2:  | Comparison of various glass cavity formation techniques                                                 | 17 |

| Table 3:  | Summary of published literature in relevant tasks with references and technical contributions           | 28 |

| Table 4:  | Properties of polymer adhesive dry films used                                                           | 51 |

| Table 5:  | Lamination conditions used to polymer adhesive dry film lamination as well as glass-glass panel bonding | 53 |

| Table 6:  | Cure conditions for the polymer adhesive dry films used for glass-glass panel bonding                   | 53 |

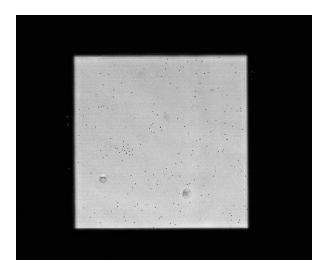

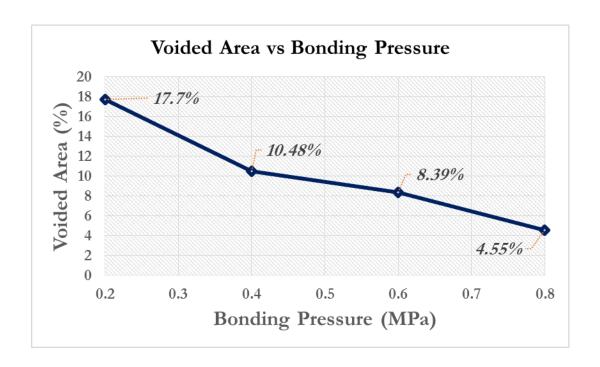

| Table 7:  | Impact of pressure on voided area and corresponding CSAM images                                         | 57 |

| Table 8:  | Optimized lamination conditions to reduce pre-cure surface roughness                                    | 59 |

| Table 9:  | Impact of optimized lamination conditions on pre-cure surface roughness                                 | 59 |

| Table 10: | Shear strength of glass-glass samples bonded using ABF GX-92 and BCB                                    | 61 |

| Table 11: | Post-cure matrix components of TLPS copper paste with their melting points and proportions              | 68 |

| Table 12: | Properties of TLPS copper paste vs bulk copper                                                          | 70 |

| Table 13: | Specifications of 3D model of dual via chain structure built in ANSYS HFSSTM                            | 77 |

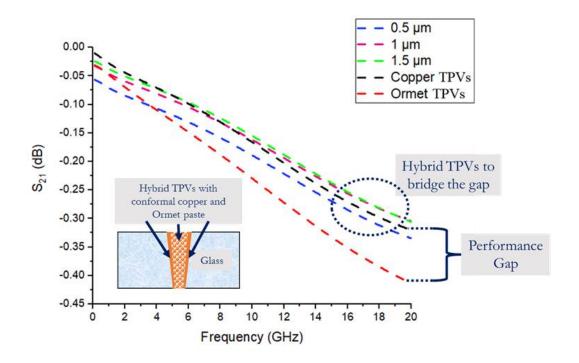

| Table 14: | Comparison of S21 parameters at 20GHz for electroplated copper TPVs and copper paste TPVs in glass      | 77 |

| Table 15: | Impact of conformal copper on S21 parameters of hybrid TPVs in glass                                    | 79 |

#### LIST OF FIGURES

| Figure 1  | Typical silicon wafer level packaging process flow [5]                                                                            | 3  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|----|

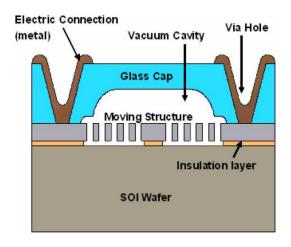

| Figure 2  | Typical cross section of a silicon wafer level packaged MEMS device [6]                                                           | 4  |

| Figure 3  | Manufacturing process of LTCC substrates [1]                                                                                      | 6  |

| Figure 4  | Sintering pastes used to form vertical and planar interconnections in LTCC substrates [2]                                         | 7  |

| Figure 5  | Concept image of a MEMS System-in-Package (SiP) using LTCC technology [3]                                                         | 7  |

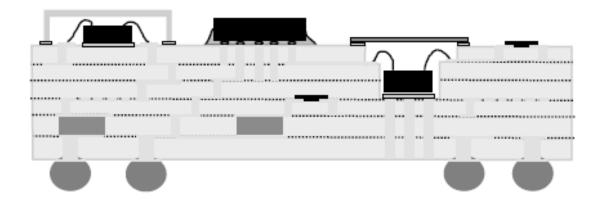

| Figure 6  | Amkor's laminate substrate based packaging to enable MEMS-ASIC integration                                                        | 8  |

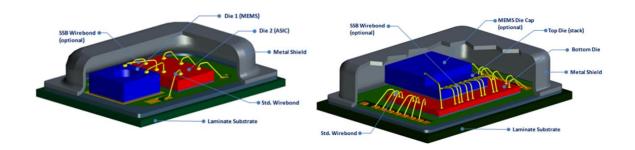

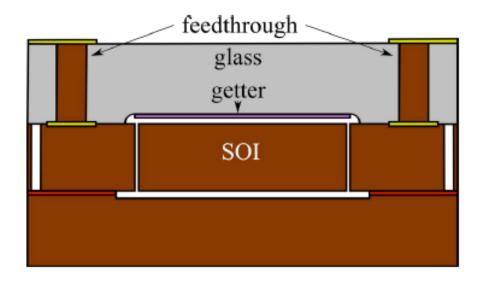

| Figure 7  | Conceptual cross-sectional image of glass cavity package                                                                          | 10 |

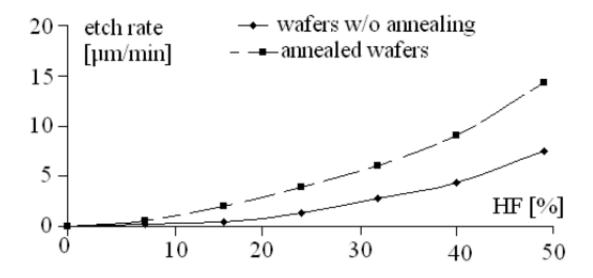

| Figure 8  | Variation of etch rates in glass with HF concentration [12]                                                                       | 15 |

| Figure 9  | Wet etched glass cavity for hermetic packaging of resonators [10]                                                                 | 16 |

| Figure 10 | Glass cavities formed by sandblasting technique [19]                                                                              | 16 |

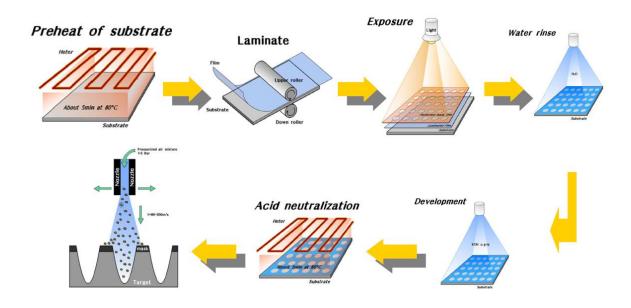

| Figure 11 | Image showing typical steps involved in sandblasting process [11]                                                                 | 17 |

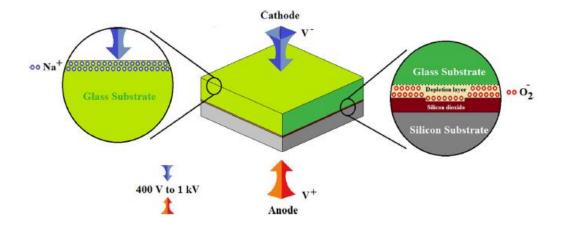

| Figure 12 | Conceptual image showing mechanism of Si-glass anodic bonding [22]                                                                | 19 |

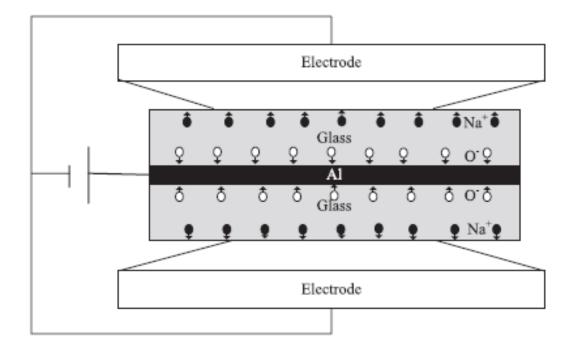

| Figure 13 | Conceptual image showing mechanism of glass-glass anodic bonding using common interfacial anode (here, Aluminum) [21]             | 19 |

| Figure 14 | Fabrication process flow of a wafer-level RF MEMS package [54].                                                                   | 23 |

| Figure 15 | SEM cross sections showing various stages of a Si interposer-<br>type fabrication process of filling glass vias with copper [55]. | 24 |

| Figure 16 | ALoT process for through-glass-via metallization [56]                                                                             | 25 |

| Figure 17 | (a) Debonded metallized glass wafer after Corning's a lot process and (b) SEM image showing good planarity [56]                   | 25 |

| Figure 18 | Asahi Glass' copper paste filled hermetic through vias [59]                                                                                              | 26 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 19 | Process flow for through glass vias filled with gold particles [61]                                                                                      | 27 |

| Figure 20 | Cross section showing interface between glass substrate and sintered gold particles [61]                                                                 | 27 |

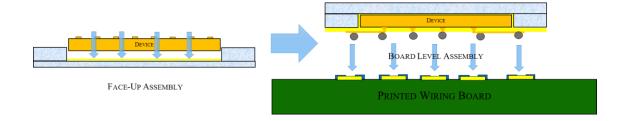

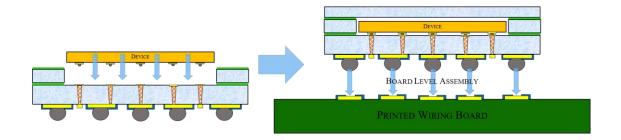

| Figure 21 | Concept image showing chip-first packaging architecture involving face-up die bonding followed by RDL fabrication and board level assembly               | 30 |

| Figure 22 | Concept image showing chip-last packaging architecture involving TGV metallization and RDL fabrication followed by die assembly and board level assembly | 31 |

| Figure 23 | Microdefects on rough glass sidewalls                                                                                                                    | 32 |

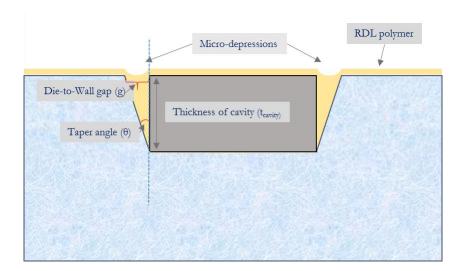

| Figure 24 | Cavity taper induced micro-depressions top RDL surface                                                                                                   | 33 |

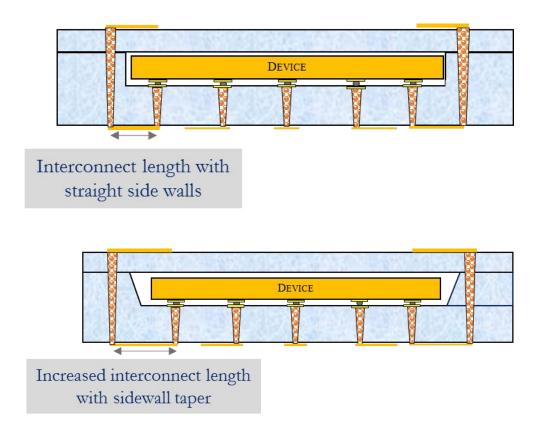

| Figure 25 | Image showing increased interconnect length from die to TGV due to tapered cavity sidewalls                                                              | 35 |

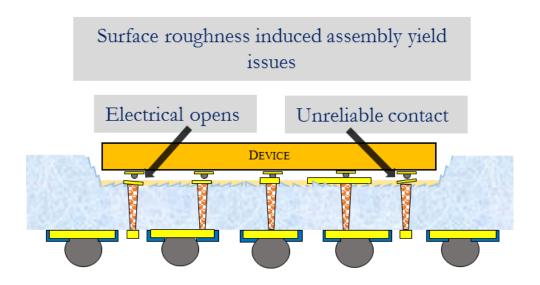

| Figure 26 | Cavity base surface roughness induced assembly yield challenges                                                                                          | 36 |

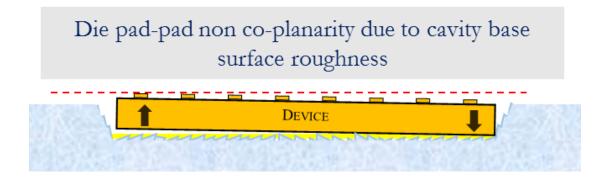

| Figure 27 | Die pad-pad non-co-planarity due to cavity base surface roughness                                                                                        | 36 |

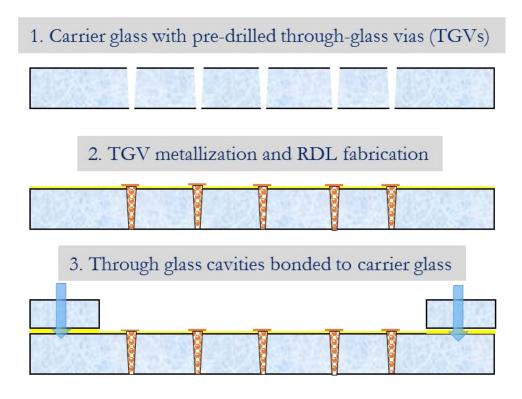

| Figure 28 | Process for formation of laminated glass cavities                                                                                                        | 38 |

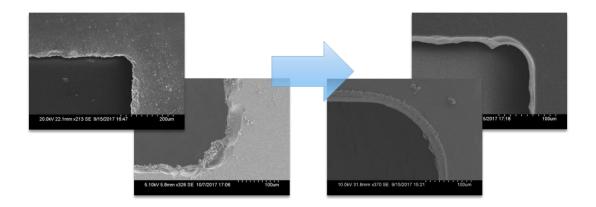

| Figure 29 | Cavity corners at right angles (left) vs rounded corners for reliable design (right)                                                                     | 39 |

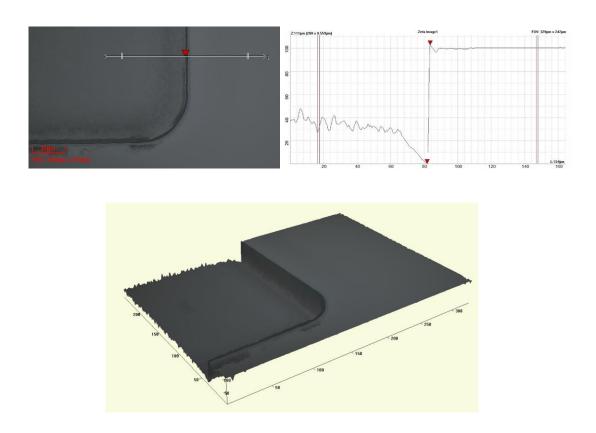

| Figure 30 | Advanced micromachining processes used to achieve low taper ( $<2\mu m$ )                                                                                | 40 |

| Figure 31 | Advanced micromachining processes used to achieve defect-<br>free, smooth cavity sidewalls                                                               | 41 |

| Figure 32 | Cavities micromachined in 300 µm thick glass                                                                                                             | 41 |

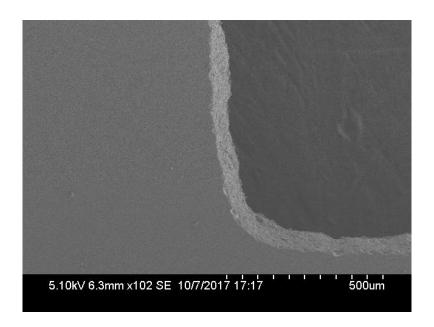

| Figure 33 | 60-70 µm taper in Applied Materials' proprietary wet etch process to form cavities in thin glass panels                                                  | 42 |

| Figure 34 | Blind cavities formed using advanced hybrid wet etch processes                                                                                           | 44 |

| Figure 35 | SEM image showing process induced taper of 155 μm – 175 μm                                                                                               | 45 |

| Figure 36 | Cavity base surface roughness profile shows roughness of about 0.5 µm                                                   | 45 |

|-----------|-------------------------------------------------------------------------------------------------------------------------|----|

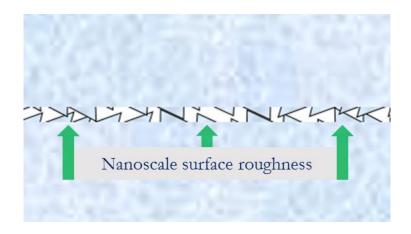

| Figure 37 | Concept image showing close up view of glass-glass contact interface with nano-scale roughness                          | 48 |

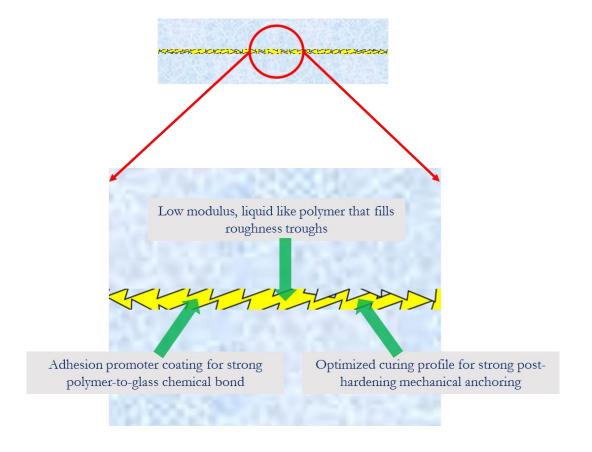

| Figure 38 | Concept image highlighting role of polymer adhesive dry films in glass-glass bonding                                    | 49 |

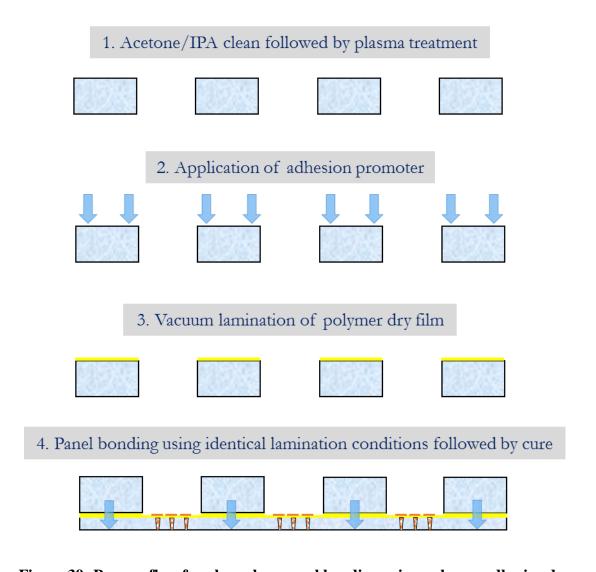

| Figure 39 | Process flow for glass-glass panel bonding using polymer adhesive dry films                                             | 50 |

| Figure 40 | Image showing sample sandwiched between two metal hotplates in the Meiki Laminator                                      | 51 |

| Figure 41 | Image showing role of silane-based adhesion promoter to<br>enhance adhesion of polymer adhesive dry films to glass [67] | 52 |

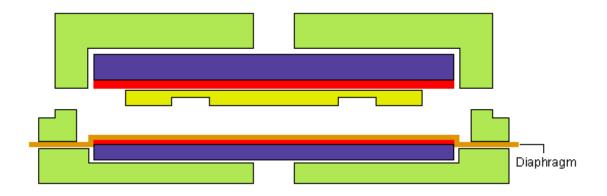

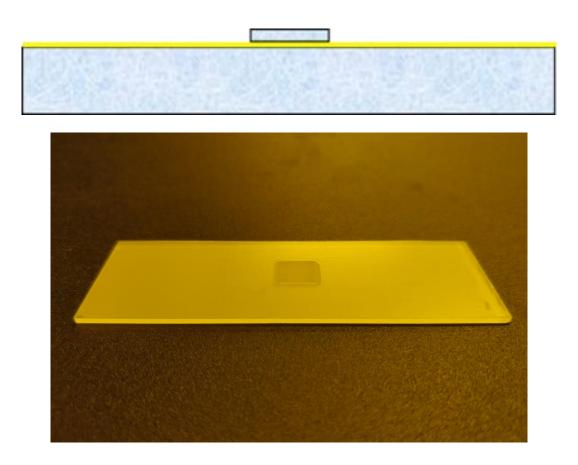

| Figure 42 | Cross section (top) and actual sample used for characterization of interfacial voids                                    | 55 |

| Figure 43 | CSAM image of ABF GX-92 bonded sample showing ~100% bonding efficiency                                                  | 56 |

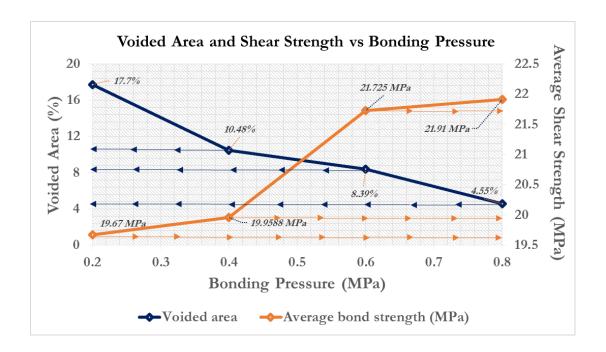

| Figure 44 | Graph showing reduction in voided area with an increase in bonding pressure                                             | 58 |

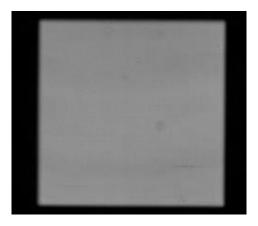

| Figure 45 | CSAM image of sample bonded using optimized conditions to achieve ~100% bonding efficiency                              | 60 |

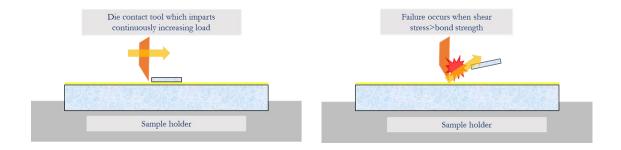

| Figure 46 | Bond strength characterization technique using die shear test tool                                                      | 60 |

| Figure 47 | Impact of pressure assisted bonding on bonding efficiency and corresponding impact on bond strength                     | 62 |

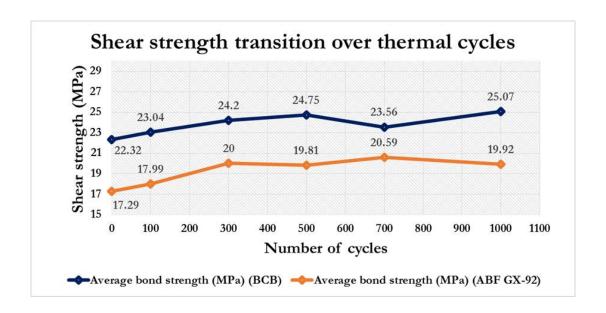

| Figure 48 | ABF GX-92 and BCB bond shear strength transition over 1000 thermal cycles                                               | 64 |

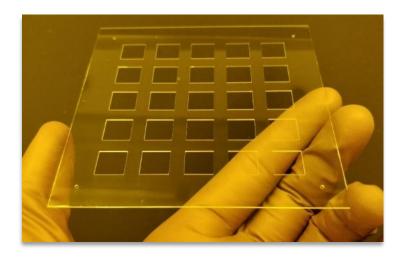

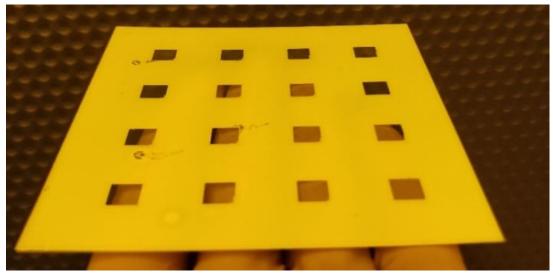

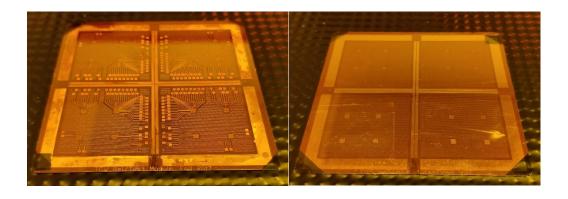

| Figure 49 | Glass cavity panel bonded to a glass carrier using BCB and ABF GX-92                                                    | 65 |

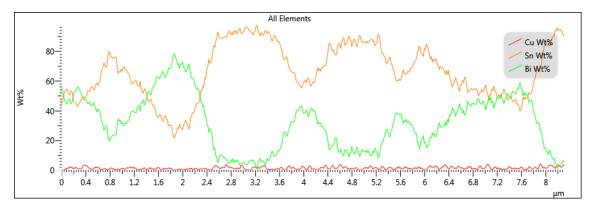

| Figure 50 | Line scan along a tin alloy particle showing presence of bismuth fillers                                                | 68 |

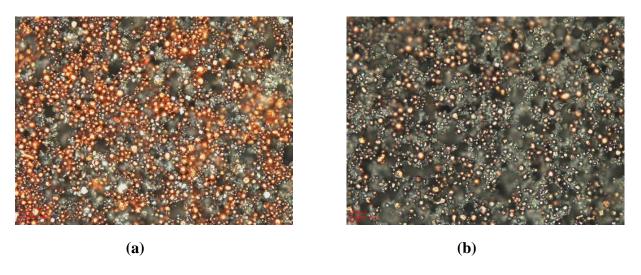

| Figure 51 | Paste cured at (a) 160 °C & (b) 175 °C                                                                                  | 69 |

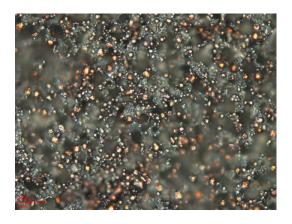

| Figure 52 | Paste cured at 191oC                                                                                                    | 70 |

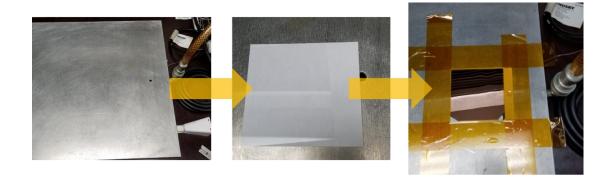

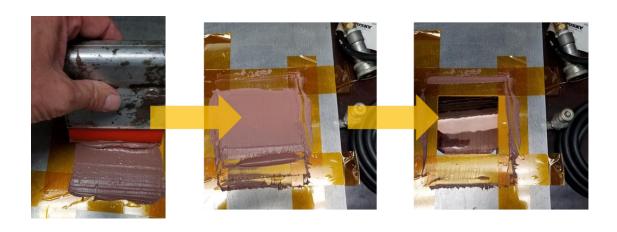

| Figure 53 | TPV paste fill process showing metal hotplate, bleeder paper and mounted substrate                                                            | 71 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 54 | TPV paste fill process showing copper paste dispensed using squeegee followed by surface cleaning                                             | 72 |

| Figure 55 | TPV paste fill process showing release of substrate and levelling the TPVs                                                                    | 73 |

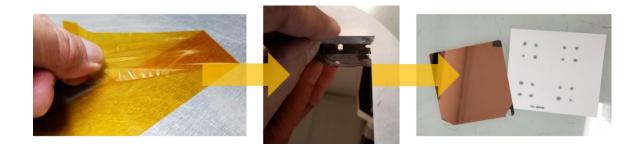

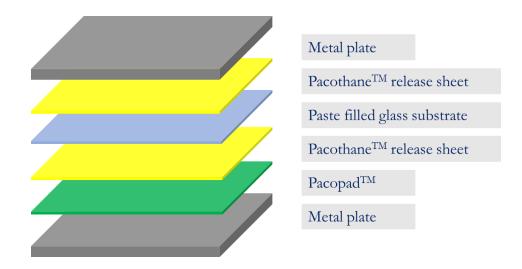

| Figure 56 | Stack-up used for paste curing step in lamination press                                                                                       | 73 |

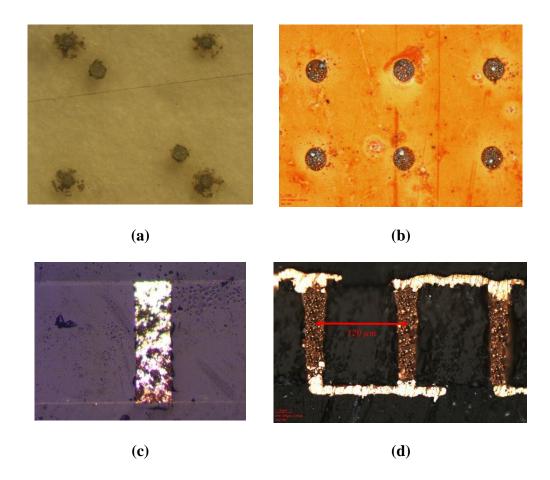

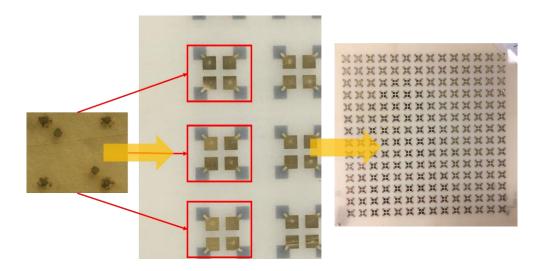

| Figure 57 | Top ((a) and (b)) and cross-sectional view ((c) and (d)) of paste filled TPVs of diameter 100 $\mu m$ and 30 $\mu m$ respectively             | 74 |

| Figure 58 | Top and 3D angular x-ray images of 30 µm paste filled TPVs in glass                                                                           | 75 |

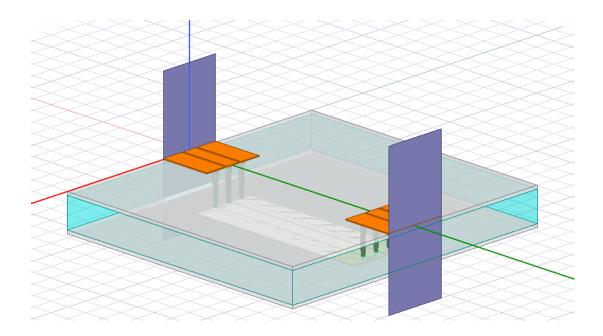

| Figure 59 | Dual-via chain structure                                                                                                                      | 76 |

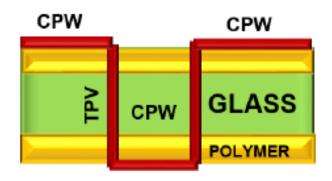

| Figure 60 | A dual-via chain model consisting of 2 sets of GSG vias and transmission lines                                                                | 76 |

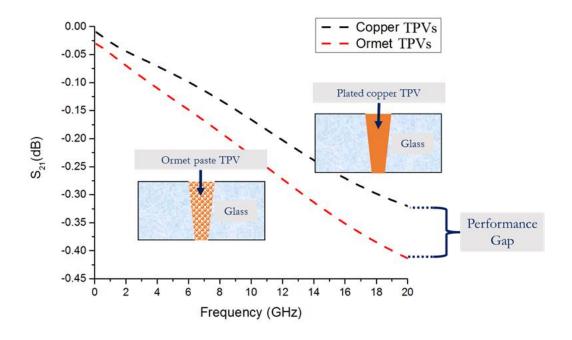

| Figure 61 | S21 plot showing performance gap between electroplated copper TPVs and copper paste TPVs in glass                                             | 78 |

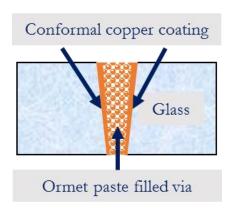

| Figure 62 | Concept image showing cross sectional view of hybrid TPV in glass                                                                             | 78 |

| Figure 63 | S21 plot showing impact of conformal copper in hybrid TPVs to improve high frequency performance of paste filled TPVs                         | 80 |

| Figure 64 | Test structures consisting of large paste filled TPVs in glass for sensor glass cavity package                                                | 81 |

| Figure 65 | Test vehicle with daisy chain structures to study thermomechanical reliability of small paste filled TPVs in bare glass                       | 81 |

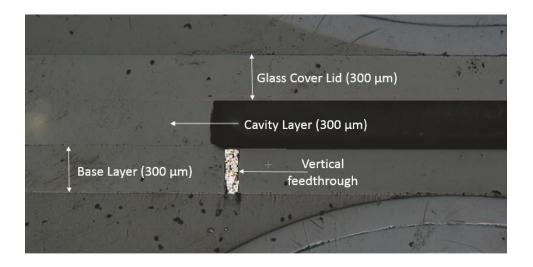

| Figure 66 | Cross sectional image showing glass cavity MEMS package with polymer-adhesive based glass-glass bonding and fully filled through-package-vias | 87 |

#### **SUMMARY**

MEMS based sensing is gaining widespread adoption in consumer electronics as well as the next generation Internet of Things (IoT) market. These applications serve as primary drivers towards miniaturization for increased component density, multi-chip integration, lower cost and better reliability. Existing MEMS packaging techniques like silicon wafer level packaging and laminate/ceramic substrate packaging either limit package level integration and miniaturization, are fabricated on small wafers or panels, or use materials that fail to decouple system level stress on the device, thereby risking its long-term reliability at board level. Besides, application specific packages take up the largest fraction of the total manufacturing cost. Therefore, advanced packaging of MEMS sensors for HPI plays a critical role in the short and long run towards the SOP vision.

This dissertation demonstrates a low stress, reliable, near-hermetic glass cavity MEMS package as a solution that combines the advantages of LTCC substrates and silicon wafer level packaging while also addressing their limitations. These glass based cavity packages can be scaled down to 2x smaller form factors (<500µm) and are fabricated out of large panel fabrication processes thereby addressing the cost and form factor requirements of MEMS packaging. Flexible cavity design, advances in through-glass via technologies and dimensional stability of thin glass also enable die stacking and 3D assembly for sensor-processor integration towards sensor fusion. The following building block technologies were explored: (a) reliable cavity formation in thin glass panels (b) low stress glass-glass bonding, and (c) high throughput, fully filled through-package-via metallization in glass. Three main technical challenges were overcome to realize the

objectives: (a) cavity corner cracking, side wall taper, side wall roughness and defects, (b) interfacial voids at glass-polymer-glass interface and (c) electrical opens and high frequency performance of copper paste filled through-package-vias in glass.

The first objective was to achieve cavities in thin glass panels with a focus on three main design metrics: a) side wall roughness for high reliability, b) side wall taper for RDL co-planarity and better electrical performance and c) surface roughness of cavity base for die pad-pad co-planarity and high assembly yield. Two types of cavity structures were explored: a) laminated glass cavities for excellent base surface smoothness, and b) blind cavities for easier integration of TPVs to enable 3D integration. These design metrics were optimized with the help of advanced, proprietary micromachining techniques from supply chain partners to achieve rounded cavity corners (100 µm corner diameter) to mitigate corner cracks, smooth side walls, low taper (< 2 µm) and smooth cavity base surfaces.

The second objective was low stress glass-to-glass bonding below 250°C, to achieve high reliability using ultra-thin 5-10 um special polymer adhesives. Glass to silicon or glass to glass bonding has been reported using anodic bonding which requires alkali-based glass with sufficient electrical conductivity, or by high temperature or high cost direct glass to glass bonding. This research explored low moisture uptake and ultra-thin polymers to achieve near-hermetic glass to glass bonding of alkali-free glasses with low stress due to the low modulus of the polymer materials. The interfacial bond strength was characterized by die shear testing, and bonding efficiency was enhanced by process variations. Bond reliability was demonstrated by characterizing bond strength degradation after thermal cycling.

The third objective was to achieve fully-filled through-package-vias with low stress and yet high enough electrical conductivity in thin glass. Via filling has been achieved in the past by electrolytic copper plating requiring thin polymer stress buffer liners for high reliability, especially for larger vias. Sintering pastes (Ag, Pt) and conductive adhesives have also been widely used for through-via metallization, requiring high temperatures and long curing cycles. This research explored and demonstrated a high-throughput, low stress through-via metallization process using screen printing of conductive paste cured at less than 200°C, as an alternative to copper plating. Direct copper plating on glass results in thermomechanical reliability failures due to CTE mismatch between glass (3-9 ppm/°C) and copper (17ppm/°C). The CTE of copper paste can be modified by binders and additives for reduced CTE mismatch with glass. Moreover, the transition alloys that partially re-melt in the copper paste matrix act as stress sinks during thermal cycling, thereby mitigating reliability issues like interfacial delamination and cohesive cracking that are posed by copper plating. The via fill process parameters were optimized to demonstrate void-free filling for small (30 µm) as well as large (100 µm) vias. Conductive paste filled vias have higher electrical resistance compared to copper filled vias, and via design rules were established using electromagnetic modeling (ANSYS HFSS<sup>TM</sup>) targeting Cu-via like performance at high frequencies. A hybrid structure involving conformal copper metallization followed by paste filling is being evaluated to achieve copper via like performance at high frequencies.

The following key engineering contributions were identified:

- i) Reliable, low defect, low taper cavity formation techniques in ultra-thin glass panels were explored, demonstrated and characterized.

- ii) Panel glass-glass bonding was demonstrated using ultra-thin, low moduli dry film polymer adhesives with low interfacial stress, ultra-high shear strength values and 100% bonding efficiency.

- iii) Thermal cycle reliability of polymer adhesives based glass-glass bonding was demonstrated and shear strength degradation was monitored and characterized.

- iv) A novel, low temperature cured conductive copper paste was used to fill small (30 μm) and large (100 μm) through-glass vias in 130 μm and 300 μm thick glass panels for lower stress and higher throughput compared to electroplated copper through-package-vias in glass.

- v) A hybrid through-package-via structure comprising of conformal coated sidewalls with copper paste filled via was explored and modeled using ANSYS HFSS<sup>TM</sup> to achieve copper-via like high frequency performance.

#### **CHAPTER 1**

#### INTRODUCTION

The objective of this dissertation is to model, design and demonstrate a near-hermetic glass package for low cost, highly reliable, ultra-thin (< 500 µm) MEMS and sensor device packaging at panel scale. Existing packaging schemes like panel laminate/ceramic cavity packaging and silicon wafer level packaging either limit package level integration and miniaturization, are fabricated on small wafers or panels, or use materials that fail to decouple system level stress on the device, thereby risking its long-term reliability at board level. Hence, there is a cost, reliability and form factor gap between existing MEMS and sensor packaging solutions and future heterogeneous package integration (HPI) requirements. This dissertation aims to bridge this gap by exploring ultra-thin panel glass embedding using low-cost materials and processes to enable low stress package structures with high system-level reliability.

MEMS and sensing electronics are seeing unprecedented growth, driven by smartphones as well as emerging IoT devices. Sensing devices need to be interconnected with RF connectivity, high bandwidth computing and analog/mixed signal processing ICs to form smart systems. MEMS devices are widely used for sensors due to existing CMOS fabrication infrastructure used to form 3D out-of-plane structures. There are several challenges in the packaging of MEMS sensors, especially when are co-packaged with logic, memory, RF and analog ICs to form heterogeneous systems. The main packaging challenges are cost, hermetic/near-hermetic sealing for board level stress decoupling and low stress through-package interconnections to enable miniaturization, all of which form

the focus of this dissertation. Current approaches to MEMS and ASIC integration in a package include wafer-level packaging in 2D and 3D stacking with TSV, and multi-chip system in package (SiP) in ceramic cavity substrates. Wafer level packaging involves expensive TSVs for 3D interconnections and anodic bonding of silicon-silicon or siliconglass wafers at high temperature and voltages which not only result in high residual stresses at the interface, but also fail to buffer external system level stresses. Ceramic cavity packages are limited by their high cost coming from small panel sizes, CTE mismatch induced stress on sensitive MEMS devices, and thick and bulky form factors. In contrast to these wafer or small ceramic substrates, this dissertation for the first time demonstrates a new cost-effective and low-stress, near-hermetic or hermetic package for MEMS devices using ultra-thin glass panel substrates and stacking multiple layers of thin glass with and without cavities.

## 1.1 Current Approaches to MEMS packaging and Their Limitations for Heterogeneous Package Integration (HPI)

MEMS sensors are currently packaged using a combination of two approaches: zero level packaging and first level packaging. Silicon Wafer Level Packaging is a necessary zero level packaging method used in which the fabricated MEMS and sensors devices are packaged before they are diced into individual coupons. These individual packaged dies are then further packaged on laminate/LTCC substrates with cavities for integration with other devices like ASICs.

#### 1.1.1 Silicon Wafer Level Packaging

Silicon wafer level packaging (WLP) refers to the practice of encapsulating MEMS structures fabricated on silicon chips between bonded wafers prior to the dicing step. WLP is a zero-level packaging technique or foundry based process which is low cost, high yield, provides protection from dust and water in saw dicing processes, shows superior long-term stability and reliability and provides robust mechanical protection, all of which are critical for fragile MEMS structures. Two main methods are used for wafer level encapsulation:

(a) use of bonded cap wafer and (b) deposition of encapsulation layer. Since thin film deposition involves complex processing steps, wafer level lids are more commonly used at the cost of increased form factor.

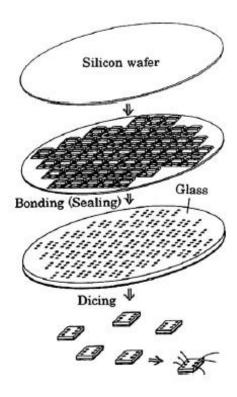

Figure 1: Typical silicon wafer level packaging process flow [5]

Figure 1 above shows the simplified process flow used in silicon wafer level packaging. MEMS devices with metallization and bond pads are fabricated using standard CMOS processing steps on a silicon wafer. Next, cavities are sacrificially etched on a lid wafer (silicon or Pyrex glass) which is then bonded to the device wafer using direct or indirect bonding techniques (anodic bonding, glass frit bonding and adhesive bonding). Finally, the devices are singulated to form packaged MEMS chips, cross section of which is shown in Figure 2 below.

Figure 2: Typical cross section of a silicon wafer level packaged MEMS device [6]

Recently, vertical feedthroughs to establish interconnections from inside the sealed cavity have gained popularity over complicated planar interconnections, leading to increased interest in through-silicon and through-glass via (TSV/TGV) technologies. Vertical feedthroughs can be used to assemble package on package (PoP) architectures which enable integration of the MEMS sensor with its ASIC circuitry in 3D fashion, thereby conserving silicon real estate for 2D miniaturization.

#### 1.1.1.1 Limitations of Silicon Wafer Level Packaging for HPI with MEMS

While wafer level packaging is gaining increased adoption due to its ability to provide hermetic vacuum encapsulation at foundry level that protects the delicate, sensitive device from dust, shocks, air dampening and humidity exposure, several challenges associated with WLP expose the technology gaps that need to be addressed. Wafer level packaging does not allow MEMS-ASIC integration. Cost scaling is limited due to lack of large panel availability and expensive processing steps like TSV formation and metallization. Form factor reduction made possible by back grinding the wafer to desired thickness may impart mechanical damage to the MEMS and high temperature anodic bonding techniques conventionally used to bond the lid wafer to device wafer generate residual stresses and stiction issues.

Despite these limitations, wafer level packaging is an essential part of the MEMS manufacturing process and cannot be avoided. To overcome the primary challenge of heterogeneous integration, first level packaging becomes critical and is the focus of worldwide research.

#### 1.1.2 Low Temperature Co-Fired Ceramic (LTCC) Substrates and Laminates

Low temperature co-fired ceramic (LTCC) substrates have been widely used for the last two decades to produce multi-chip ceramic modules, used as a multilayer substrate for IC packaging.

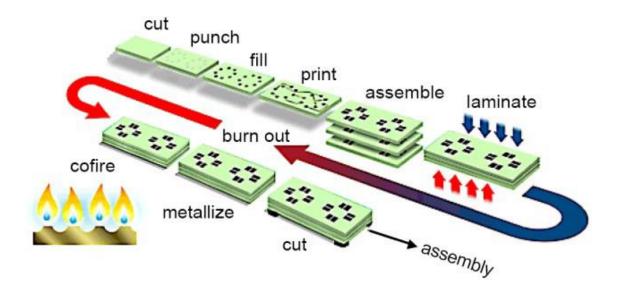

Figure 3: Manufacturing process of LTCC substrates [1]

A typical process flow for manufacturing LTCC substrates is shown in Figure 3 above. The starting point is the ceramic green tape sheets (usually >50 µm thick, 6 x 6 inch sheets) produced by tape casting method. Micromachining techniques are used to form through vias and other structures like cavities in the tape after which conducting material is screen printed to form vertical feedthroughs and horizontal traces that enable 2D and 3D integration. Successive green tapes are then registered, laminated using uniaxial or isostatic laminators (typically at 200 atm, 70°C for 10 minutes) and cofired in a single step in air at high temperatures, typically up to 875°C, simultaneously sintering the conductive ink to form interconnections, after which devices are assembled.

Figure 4: Sintering pastes used to form vertical and planar interconnections in LTCC substrates [2]

Figure 4 above shows the cross section of vertical and lateral electrical connections in an LTCC substrate and Figure 5 below shows the typical structure of a multilayer LTCC package with MEMS devices assembled and sealed in cavities.

Figure 5: Concept image of a MEMS System-in-Package (SiP) using LTCC technology [3]

Additionally, MEMS-ASIC integration is also made possible by die assembly in 2D or 3D stacked fashion using die attach followed by wire bonding/flip-chip assembly on laminate substrates, as shown in Figure 6 below. Once devices are assembled, metal/plastic lid structures, laminate based cavities and epoxy molding compound (EMC) are used for encapsulation and mechanical protection. Through-silicon-vias and face-to-face stacking

is used to interconnect stacked dies while through-mold-vias are used in cases where molding compounds are used.

Figure 6: Amkor's laminate substrate based packaging to enable MEMS-ASIC integration

## 1.1.2.1 Limitations of Low Temperature Co-Fired Ceramic (LTCC) Substrates and Laminates for HPI with MEMS

While LTCC substrates offer robust mechanical protection, high reliability through silicon CTE matching, device embedding and integration capabilities, there are several challenges that can limit its potential as an advanced MEMS packaging substrate. Since each green tape is at least 50 µm thick [4], high density, multilayer packages often exceed hundreds of microns in thickness. High density, fine line interconnections require smooth surfaces and precision micromachining capabilities but LTCC substrates are rough and are limited to a line width and via diameter of 50 µm and pitch of 150 µm, which may be insufficient for high density interconnections between MEMS and ASIC [2, 3]. Further, expensive processing tools and conductor materials typically used, like silver, gold and platinum pastes limit cost scaling. Finally, high temperature processing is often incompatible with certain MEMS whereas unequally distributed post-firing-shrinkage may lead to warpage induced stresses. Laminate based packaging enables MEMS-ASIC

integration in a system-in-package (SiP) fashion. Further, the large CTE mismatch between the dissimilar materials (EMC~30 ppm/°C, Silicon = 3 ppm/°C, die attach ~ 40 ppm/°C and laminate substrate = 17 ppm/°C) leads to reliability issues, particularly from molding compounds that impart compressive stresses often of the order of thousands of psi on the MEMS. Use of cavities and metal caps instead eliminates a source of stress. However, interfacial stresses at die-die attach-substrate interfaces and lid-substrate interface persist. Metal caps are also expensive and lead to bulky, heavy packages.

#### 1.2 Panel Glass Embedding for HPI with MEMS

In this dissertation, glass panel substrates are explored and demonstrated for first-level embedded packaging of MEMS sensors, scalable to heterogeneous integration with logic and other devices in the same package. Panel glass embedding combines the benefits of LTCC substrate and silicon wafer level packaging while addressing their limitations. There are several compelling reasons for the use of glass substrates for MEMS packaging:

- i) Large availability of **ultra-thin glass substrates** in panel form, engineered to thicknesses between  $30-300~\mu m$  to reduce form factor, eliminating the need for back grinding.

- ii) Affordability to form high-density through-package-vias in glass to enable **3D** integration and high density planar traces due to high modulus (50 90 GPa) and excellent surface finish with < 1 nm roughness.

- iii) Low package-induced stresses due to tailored CTE and high dimensional stability leading to higher reliability.

iv) Large area panel processing as opposed to wafer processing and use of inexpensive materials and processes for **lower cost**.

This dissertation demonstrates a new concept of low stress, reliable, near-hermetic ultra-thin glass based cavity packages for MEMS devices. These glass cavity packages can be scaled down to 2x smaller form factors (<500µm) and are fabricated out of large (up to 12 x 12 inch), ultra-thin (50 µm thick) glass panel based processes, thereby addressing the form factor and low-cost requirements of MEMS packaging. Flexibility in cavity design, advances in low temperature, low stress through-glass-vias (TGVs) and substrate bonding technologies, better CTE matching and dimensional stability of thin glass enable 3D integration with improved reliability. Figure 7 shows the conceptual representation of the glass cavity MEMS package.

# RELIABLE CAVITY FORMATION IN THIN GLASS PANELS LOW STRESS GLASS-GLASS BONDING PACKAGE-VIA METALLIZATION IN GLASS BOARD LEVEL STRESS DECOUPLING

ULTRA-THIN GLASS CAVITY PACKAGE

Figure 7: Conceptual cross-sectional image of glass cavity package

#### 1.3 Research Objectives, Unique Approach and Technical Challenges

The specific objectives of this dissertation research are to address the fundamental technical challenges in three key panel glass cavity MEMS package building blocks,

(a) reliable cavity formation in thin glass panels, (b) low stress glass-glass bonding, and (c) high-throughput, fully filled through-package-via metallization in glass. The fundamental challenges to achieve these objectives are: (a) cavity corner cracking, side wall taper, side wall roughness and defects, (b) interfacial voids at glass-polymer-glass interface and (c) electrical opens and high frequency performance of copper paste filled through-package-vias in glass.

The specific objectives, prior art, unique approach and associated technical challenges are summarized in Table 1, which forms the basis of this research.

Table 1: Table showing research objectives, recent prior art and technical challenges

| Objectives                                          | Prior Art                                                                                                                           | Unique Approach                                                                                                                          | Technical challenges                                                                 |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 1. Reliable Cavity  Formation in Thin  Glass Panels | <ul><li>Wet etch</li><li>Sandblasting</li></ul>                                                                                     | <ul> <li>Advanced         <ul> <li>machining</li> <li>technologies for</li> <li>laminated/blind</li> <li>cavities</li> </ul> </li> </ul> | Cavity corner     cracking, side wall     taper, side wall     roughness and defects |

| 2. Low Stress Glass-<br>Glass Bonding               | <ul> <li>Anodic bonding</li> <li>(400V-1000V,</li> <li>300 °C -500°C)</li> <li>Glass welding</li> <li>Glass frit bonding</li> </ul> | • Glass-glass near hermetic adhesive bonding @ <250°C using ultra-thin polymer adhesives                                                 | Interfacial voids at glass-polymer-glass interface                                   |

|                      | Copper plated    |                     |                        |

|----------------------|------------------|---------------------|------------------------|

|                      | fully filled     |                     | • Electrical opens and |

| 3. High Throughput,  | through-vias     | • Low temperature,  | •                      |

| Fully Filled         | • Electrically   | low stress          | high frequency         |

| Through-Package-     | conductive       | conductive paste    | performance of paste   |

| Via Metallization in | adhesives and    | filled through-vias | filled through-package |

| Glass                |                  | inica anough-vias   | vias in glass          |

|                      | high temperature |                     |                        |

|                      | sintering pastes |                     |                        |

#### 1.4 Research Tasks and Thesis Organization

The research tasks are consistent with the objectives and technical challenges mentioned above in. They are listed below:

- **Task 1**: Process development, demonstration and examination of reliable, defect free, low taper cavities in thin glass panels.

- **Task 2**: Shear strength characterization, void reduction and reliability studies of polymer adhesives against thermal cycling.

- **Task 3**: Process optimization and demonstration of metallization process for fully filled through-package-vias in glass using copper paste for high yield.

- **Task 4**: Evaluation of a novel hybrid via structure for improved high frequency performance of copper paste filled through-package-vias in glass.

This thesis is organized into six chapters. This chapter discussed the drivers for advanced MEMS packaging in the IoT era, reviewed the status of MEMS packaging and established a compelling case for the use of glass as a MEMS packaging substrate. Chapter 2 reviews published literature that studies glass cavity formation, glass-glass bonding and through-glass-via metallization technologies. In Chapter 3, various design considerations in formation of glass cavities in thin glass panels are discussed followed by process, characterization and analysis of reliable, defect free and low taper glass cavities. Chapter 4 discusses the theory of glass-glass bonding using ultra-thin polymer adhesives along with experimental characterization of bond strength, void reduction and bond reliability studies. Chapter 5 discusses the fundamental working principle of low temperature copper paste, process demonstration and optimization to achieve fully filled through-package-vias in glass. Hybrid via structures that exploit process versatility are explored for improved high frequency performance.

#### **CHAPTER 2**

#### LITERATURE REVIEW

The previous chapter described the dissertation objectives, technical challenges, and research tasks to address these challenges. The unique approach of panel scale device embedding in glass substrates for MEMS sensor packaging has three main challenges and tasks to achieve the research objectives, namely, (a) reliable cavity formation in thin glass panels, (b) low stress glass-glass bonding, and (c) high-throughput, fully filled throughpackage-via metallization in glass. This chapter will review published literature in addressing these challenges. The final section in this chapter will summarize these advances.

#### 2.1 Prior work in reliable cavity formation in thin glass

This section describes the prior work on cavity formation in glass using a variety of techniques. Due to its chemical inertness and brittleness, high throughput, defect free glass structuring is difficult. While cavity formation in glass has been demonstrated using a number of expensive, specialized techniques like deep reactive ion etching (DRIE) [7], glass reflow [8] and hot-forming [9], two main techniques are most widely used: wet etching and sandblasting (powder blasting).

#### 2.1.1 Wet etching

Wet etching is a method commonly used to machine structures in glass and silicon for MEMS wafer level packaging applications [7, 10] where HF based solutions of varying concentrations are used in combination with masking materials. Some of the main

drawbacks of this method are (a) isotropic nature of etching leading to irregular shapes, large taper and high surface roughness, (b) low etch rates and (c) selection of masking material. HCl and H<sub>3</sub>PO<sub>4</sub> used in appropriate ratios with HF are known to mitigate the challenge of roughness [11]. Etch rates can be controlled by varying the HF concentration and by controlling the temperature of the solution as shown in Figure 8 [12].

Figure 8: Variation of etch rates in glass with HF concentration [12]

Masking options and alternative solutions to overcome the roughness problem have been investigated in [11, 13, 14] and by the use of photosensitive glass [15-18]. Despite all these efforts, wet etching is limited by the fundamental challenge of isotropic etching resulting in tapered/curved side walls, as shown in Figure 9 below.

Figure 9: Wet etched glass cavity for hermetic packaging of resonators [10]

#### 2.1.2 Sandblasting/powder blasting

Sandblasting is one the earliest methods used for glass machining. Commonly used to fabricate large, coarse-pitched feedthroughs, this method, illustrated in Figure 11, has been recently extended to form glass cavities used as capping structures in MEMS packages, shown in Figure 10. [19]

Figure 10: Glass cavities formed by sandblasting technique [19]

Figure 11: Image showing typical steps involved in sandblasting process [11]

Table 2 summarizes the techniques used for glass cavity formation in the prior art. None of the existing methods meet all the requirements to achieve the research objectives and there is a need to explore and develop new processes to form high quality cavities in thin glass to match the throughput, reliability and form factor requirements of ultra-thin glass embedded packages.

Table 2: Comparison of various glass cavity formation techniques

| Parameter       | Sandblast      | Wet etch       | DRIE           | Glass reflow   |

|-----------------|----------------|----------------|----------------|----------------|

|                 |                |                |                |                |

| Lateral etching | No             | Yes            | No             | No             |

|                 |                |                |                |                |

| Taper           | V shaped taper | U shaped taper | Vertical walls | Vertical walls |

| _               |                |                |                |                |

| Aspect ratio    | Low            | Low            | High           | High           |

|                 |                |                |                |                |

| Surface quality | Rough          | Rough          | Smooth         | Smooth         |

|                 |                |                |                |                |

| Process time    | Short          | Long           | Long           | Long           |

|                 |                |                |                |                |

#### 2.2 Prior work in glass-glass bonding

Silicon-glass and glass-glass bonding have been developed for wafer level packaging of MEMS devices. Capping structures fabricated out of glass or silicon wafers are bonded to the MEMS wafer for mechanical protection, in the wafer fab and not in the package foundry, to prevent device contamination. While most of the published literature relates to glass-to-silicon wafer bonding, there has been a limited amount of prior work on glass-glass bonding. Bonding techniques can be broadly classified into two types described in this section: direct and indirect. Direct bonding uses no additional material at the interface whereas indirect bonding uses materials like polymer adhesives, frit paste and thin film metals.

#### 2.2.1 Direct Glass-Glass Bonding

#### 2.2.1.1 Anodic Bonding

Silicon-silicon, silicon-glass and glass-glass anodic bonding has been used extensively for hermetic sealing and protective encapsulation of various MEMS devices like accelerometers, RF switches, pressure sensors and gyroscopes [20]. In this technique, illustrated in Figure 12, alkali rich glass (borosilicate) is bonded to other borosilicate glasses, metals or semiconductor substrates, most commonly silicon by application of high temperatures (300°C – 500°C) and high voltages (400V – 1000V). A robust, permanent hermetic bond is achieved through formation of interfacial SiO<sub>2</sub>. Glass-glass anodic bonding has been demonstrated in [21] by use of thin film aluminum that acts as a common anode, illustrated in Figure 13. Other interfacial materials like silicon with similar CTEs can also be used as the common anode for more reliable bonding.

Figure 12: Conceptual image showing mechanism of Si-glass anodic bonding [22]

Figure 13: Conceptual image showing mechanism of glass-glass anodic bonding using common interfacial anode (here, Aluminum) [21]

Despite all its advantages, anodic bonding is only applicable to high-alkali content glasses with customized compositions. High voltages used in anodic bonding have shown to cause stiction between movable MEMS structures and the lid [2]. Additionally, the high temperatures involved in anodic bonding result in high residual thermal stresses [20],

which can be controlled by slow cooling resulting in increased processing time. Low temperature anodic bonding can result in weaker bonds and requires longer bonding times. A potential solution is to modify the glass composition to increase the bulk charge carrier density. This technique was employed in [23] and [24], where low temperature anodic bonding at 180°C was demonstrated using Li-containing glass-ceramic in which spodumene (β-LiAlSi<sub>2</sub>O<sub>6</sub>) provided mobile Li-ions at elevated temperatures. Another technique to achieve low temperature anodic bonding at 200°C - 300°C was demonstrated using plasma based surface activation techniques [25]. Most recently, electrode modifications have been shown to help reduce bonding temperatures to as low as 250°C with shorter bonding times [22].

#### 2.2.1.2 Low Temperature Direct Bonding

D. Hutt [26] and X. Cui [27] presented a preliminary process to fabricate laminated multilayer glass substrates built up from 50 μm - 100 μm thin glass sheets to address the demand for high density interconnect (HDI) packaging substrates. Glass sheets were micromachined to form vias, metallized to form electrical interconnections and then bonded using a Pressure Assisted Low Temperature Bonding method (PALTB) in a sequential process using metal plates and a clamping system which imparted high tensile stress and risk of glass cracking. M.M.R. Howlader's group [28] also explored direct bonding at room temperature using surface activation techniques, namely reactive ion etching O<sub>2</sub> RF plasma followed by nitrogen radical microwave plasma. The glass wafers were then bonded in a cold rolling process under a load of 20 kilograms.

# 2.2.2 Indirect Bonding

### 2.2.2.1 Adhesive Bonding

Adhesive bonding has been previously explored to bond silicon to silicon [29, 30] and silicon to glass [31-35] for MEMS WLP packaging applications but there is limited published work in detailed analysis of glass to glass adhesive bonding. Jourdain et al. demonstrated silicon-silicon bonding using BCB as the adhesive material for wafer level packaging and sealing of RF MEMS structures inside cavities fabricated in silicon to achieve low leak rates, high bond strength and reliability against harsh conditions [29]. Niklaus et al. used BCB, a photoresist (S1818) and two polyimides to investigate influence of process parameters on interfacial void formation to successfully demonstrate void-free silicon wafer-wafer interface [30]. In S. Ma's [31] and Polyakov's [33] work, BCB was explored to bond glass to silicon wafers where its photosensitivity and patternability was leveraged to avert MEMS intra-cavity contamination. Finally, adhesive bonding using a βstage epoxy was explored in Kim's work [32] where temperatures as low as 150°C with 30 to 60-minute cure times were shown to form robust silicon-glass bonds. However, since epoxies are weak in water, bond strength degradation was observed after a 40-hour water soak.

### 2.2.2.2 Laser Assisted Glass Frit Paste Bonding

Glass frit pastes have been used as an alternate to anodic bonding to for hermetic seals in MEMS packaging, especially gyroscopes. Detailed investigations on thermomechanical properties, process optimization, bond quality, bond reliability and hermeticity have been published in [36-38]. More recently, alternative techniques like laser

assisted frit bonding [39-44] have been explored to overcome the limitations of the traditional thermocompressive glass frit bonding, which cannot be applied for hermetic packaging of MEMS sensitive to high temperatures. Impact of laser processing on bond quality has been studied in [45] with a focus on further reduction of residual thermal stresses that initiate and propagate micro-cracks.

# 2.2.2.3 Ultrashort and Nanosecond Laser Welding with Interfacial Thin Films

Glass welding is a relatively new technology that is still under development. Many methods have been developed to bond glass substrates through use of expensive femtosecond [46], picosecond [47] and CO<sub>2</sub> lasers [48] while relatively cheap nanosecond lasers have also been explored [49]. A. Horn and A. de Pablos-Martin [49-53] have published detailed studies of glass-glass bonding mechanisms with and without intermediary absorber thin films like titanium, fresionite (BaSn0.15Ti0.85O3), and BaTiAl<sub>6</sub>O<sub>12</sub> using femto-, pico- and nanosecond lasers with research work in laser parameter dependence, interfacial microstructural analyses, bond strength and bond quality characterization.

### 2.3 Prior work in fully filled through-glass-via metallization

Metallization of through via interconnections in glass substrates is essential to enable x-y-z miniaturization and 3D integration. This section discusses the approaches that have been successfully used to demonstrate fully filled through vias metallized with different conductor materials.

### 2.3.1 Copper Filled Through-Glass Vias

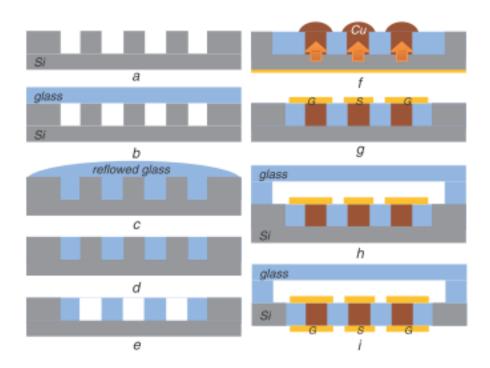

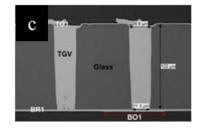

Fully filled copper vias offer improved electrical performance in 2.5D silicon and glass interposers. Lee et al. described an innovative approach which involves bottom-up plating of Cu into TGVs made by a wafer-level packaging approach (Figure 14) [54]. In this process shown in Figure 14, borosilicate glass is reflowed at 1025 °C into a silicon mold that contains inverse pillar structures formed by deep reactive ion etching (DRIE). The inverse pillar structures in the Si mold are etched by DRIE to reveal vias in the reflowed glass, which are filled with electroplated copper and then planarized by CMP. Finally, the bottom of the vias are revealed by CMP and then metallized.

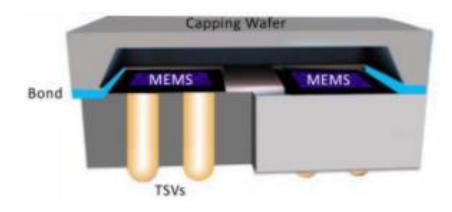

Figure 14. Fabrication process flow of a wafer-level RF MEMS package [54].

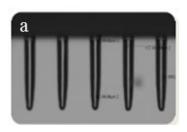

A more manufacturable approach was demonstrated by Corning Inc. in 2013 [55]. The process is similar to what is typically used for fabricating Si interposers. The process

begins with blind vias formed in a thick glass substrate (Figure 15a). The blind vias are drilled to a depth greater than the desired final substrate thickness. Ti/Cu is then deposited by physical vapor deposition (PVD), forming a seed layer for subsequent bottom-up filling of Cu and planarization (Figure 15b). Next, the glass substrate undergoes back grinding to reveal the bottom of the blind vias, and then another Cu metallization step is used to complete the metallized glass substrate (Figure 15c).

Figure 15. SEM cross sections showing various stages of a Si interposer-type fabrication process of filling glass vias with copper [55].

In 2016, Corning demonstrated an improved process for copper filled vias known as Advanced Lift-off Technology (ALoT) [56]. This technique obviates the back-grinding step and is also designed to be high temperature compatible. A carrier glass and a bonding layer is used to support thin glass wafers or panels with pre-drilled vias, as shown in Figure 16, followed by bottom-up metallization of vias using the standard process described in [57]. Finally, instead of back grinding, the carrier structure is mechanically debonded to release the metallized wafer/panel, shown in Figure 17. Chemical-mechanical-planarization (CMP) is required for planarity on top side, but no additional polishing is required on the bottom side.

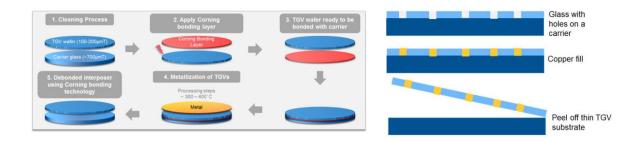

Figure 16: ALoT process for through-glass-via metallization [56]

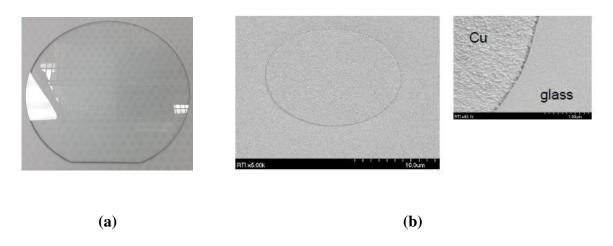

Figure 17: (a) Debonded metallized glass wafer after Corning's a lot process and (b) SEM image showing good planarity [56]

As discussed earlier, fully filled copper plated vias are highly beneficial for high frequency applications due to the high conductivity of copper. However, the fundamental challenges associated with copper plated through glass vias is the high CTE mismatch that lead interfacial stresses and subsequent thermomechanical reliability issues like interfacial delamination. Demir et al [58] proposed an alternative to fully-filled copper plated through

vias in bare glass by using thin polymer liners as barrier layers to buffer the stresses originating from glass-copper CTE mismatch for higher reliability.

# 2.3.2 Alternate Through Via Metallization Techniques

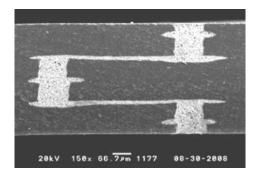

Asahi Glass Company reported on a process to metallize through vias in glass with copper paste filling for 2.5D and 3D glass interposers. TPVs with a minimum via pitch of 60µm in 100µm thick glass substrates were metallized using conductive metal paste, e.g., Cu paste shown in Figure 18. The study also reported that the CTE of the Cu-paste could be adjusted to match the CTE of the glass substrate to achieve higher reliability [59].

Figure 18: Asahi Glass' copper paste filled hermetic through vias [59]

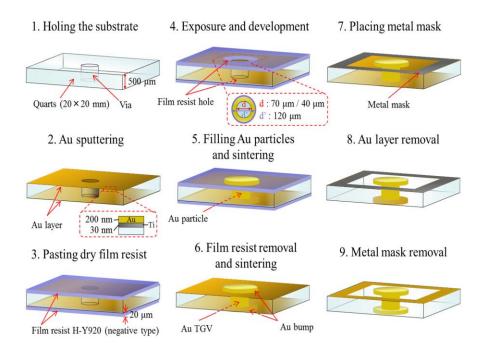

Another hermetic TGV filling technology named HERMES<sup>TM</sup> has been demonstrated by Schott/NEC [60] in which Tungsten (W) or FeNi is used as conductor materials in through glass vias for MEMS packaging applications. Glass is reflowed over W or FeNi plugs in an additive process to achieve hermetic, void free through glass vias 80 µm in diameter at 200 µm pitch in 350µm thick glass wafers. Nomura's work [61] demonstrated through glass via metallization with bumps using gold particles for hermetic sealing. Standard lithography steps were used to define bump patterns around the through-

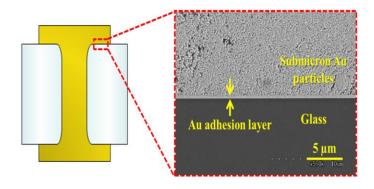

via opening, followed by vacuum-assisted stencil printing of Au slurry which comprises of submicron Au particles suspended in an organic solvent and surfactant. A pre-bake step at 110°C followed by a 200°C sintering step resulted in fully filled Au vias, shown in Figure 19 and Figure 20.

Figure 19: Process flow for through glass vias filled with gold particles [61]

Figure 20: Cross section showing interface between glass substrate and sintered gold particles [61]

# 2.4 Chapter Summary

This chapter discussed in detail the advances in addressing the three main technical challenges and tasks in this dissertation to enable miniaturized, low stress and near hermetic panel glass embedded packages: (a) reliable cavity formation in thin glass panels, (b) low stress glass-glass bonding and (c) high throughput, fully filled through-package-via metallization in glass. The table below summarizes published research discussed in previous sections of this chapter and highlights their technical contributions towards addressing challenges associated with each.

Table 3: Summary of published literature in relevant tasks with references and technical contributions

| Task                   |                | References | Technical contributions                                                                                                     |

|------------------------|----------------|------------|-----------------------------------------------------------------------------------------------------------------------------|

|                        | Wet Etching    | [11-12]    | Cavity sidewall roughness control by H <sub>3</sub> PO <sub>4</sub> addition and etch rate control by temperature variation |

| Glass Cavity Formation |                | [15-18]    | Use of photosensitive glass to overcome mask selectivity issues                                                             |

|                        | Sandblasting   | [19]       | Fabrication of tapered glass cavity for MEMS package capping structure for mechanical protection                            |

| Glass-Glass<br>Bonding | Anodic bonding | [22-25]    | Low temperature processing by electrode modification, increasing                                                            |

|                                 |                                |            | glass carrier concentration and                                               |

|---------------------------------|--------------------------------|------------|-------------------------------------------------------------------------------|

|                                 |                                |            | surface activation                                                            |

|                                 | Low temperature direct bonding | [26-28]    | Low temperature bonding using pressure and surface activation techniques      |

|                                 | Adhesive bonding               | [29-35]    | Silicon silicon/silicon-glass bonding for higher reliability                  |

|                                 | Glass frit bonding             | [39-45]    | Laser assisted bonding for localized heating                                  |

|                                 | Laser welding                  | [49-53]    | Laser welding using interfacial absorber thin films                           |

|                                 |                                | [54-58]    | Fully filled copper TGVs                                                      |

| Through glass via metallization | Copper Filled TGVs             | [58]       | Thin polymer liners for interfacial stress buffering and enhanced reliability |

|                                 | Schott HERMES®                 | [60]       | Hermetic fully filled tungsten TGVs                                           |

|                                 | Paste filled TGVs              | [59], [61] | Cu and Au paste hermetic TGVs                                                 |

#### **CHAPTER 3**

### RELIABLE CAVITY FORMATION IN THIN GLASS PANELS

The previous chapter reviewed literature describing recent approaches to address the three main research challenges. This chapter describes the dissertation research on the first task, namely, cavity formation in thin glass panels. The sections in this chapter discuss two main packaging architectures, metrics used to evaluate the formed cavities, methods to realize cavity structures with advances in micromachining processes and finally, the characterization results.

# 3.1 Glass Panel Embedding Architectures

Glass cavities can be integrated into two different device embedding architectures:

(a) chip last embedded glass cavity package, and (b) chip first embedded glass panel fanout package, shown in Figure 21 and Figure 22 below. The basic difference between the two is in the sequence of RDL formation and die placement in the cavity.

Figure 21: Concept image showing chip-first packaging architecture involving faceup die bonding followed by RDL fabrication and board level assembly

Figure 22: Concept image showing chip-last packaging architecture involving TGV metallization and RDL fabrication followed by die assembly and board level assembly

The chip-first packaging architecture shown in Figure 21 involves face up assembly of the device using ultra-thin polymer adhesives or standard die-attach films (DAFs) for die bonding to the base of the cavity, after which RDLs are fabricated directly on the die to form ultra-short die-to-package interconnections for the best possible electrical performance. The chip-last packaging architecture shown in Figure 22 is the main focus of this dissertation, since it enables the decoupling of board-level stresses from wafer level packaged MEMS devices, and provides ease of integration with other ICs.

# 3.2 Design Considerations for Glass Cavities

One of the fundamental barriers in realizing the above two packaging architectures is the formation of smooth and defect-free, small and large cavities with low taper angles in thin glass panels (50  $\mu m-300~\mu m$ ). For device capping in MEMS WLP applications, the specifications for these metrics are not very aggressive as these applications involve thick glass wafers, typically  $100~\mu m$  -  $500~\mu m$  [62] which are more stable and intrinsically more reliable to machine. Besides, their main role is to seal and protect the device from contamination and direct mechanical shocks. However, for device embedding in ultra-thin glass panels the demands on these metrics are relatively more aggressive to ensure high

reliability, small form factor (in the X, Y and Z domains) and provide planarity for RDL fabrication. The significance of each of these metrics is described below:

# 3.2.1 Sidewall roughness and defect size

Glass is a brittle material, and can fail under the influence of small elastic strains, especially in the presence of defects. The inherent strength of glass deteriorates during various processing steps as microcracks and other defects are introduced, especially during micro-structuring. Griffith's equation, stated below, states that the critical stress value for brittle failures is related to defect size.

$$\sigma_f = \sqrt{\frac{2E\gamma}{\pi a_c}} \tag{1}$$

Where  $\sigma_f$  is the failure stress, E is the Young's Modulus,  $\gamma$  is the specific free surface energy and  $a_c$  is the critical defect length for brittle failure. Small defects present on rough glass surfaces, illustrated in Figure 23 below, act as stress concentration sites which are vulnerable to crack initiation and propagation. Therefore, defect free cavity side walls are essential for reliability.

Figure 23: Microdefects on rough glass sidewalls

# 3.2.2 Sidewall taper

Side wall taper is an important design consideration while forming glass cavities.

Cavities with straight side walls enable overall package miniaturization in the x and y dimensions. Additionally, a low taper angle is desirable for the following reasons:

# a) RDL surface co-planarity

In the case of chip first glass embedded packages, redistribution layer circuitry is fabricated on top of the die that is assembled face-up. A high degree of planarity is needed to form small RDL traces and vias landing on die pads with good alignment accuracy. During fabrication, the inter-layer dielectric tends to flow into the gap between the die and cavity side wall, which creates micro-depressions on the top surface, as illustrated in Figure 24 below. Although these depressions can be planarized by further lamination steps or by planarization tools, this increases processing steps, complexity and cost. Therefore, a 90-degree cavity wall angle is desirable to reduce the gap volume.

Figure 24: Cavity taper induced micro-depressions top RDL surface

As illustrated in Figure 24 above, the die-cavity wall gap volume can be calculated by first calculating the two-dimensional gap area and then extending it in the third dimension. The gap area can be approximated as a triangle having base length equal to the thickness of the glass cavity ( $t_{cavity}$ ) and a height equal to the maximum dieto-cavity wall gap (g). If the taper angle is  $\theta$ , the gap area is defined by the following equation:

$$Gap\ Area = \frac{1}{2}\ x\ t_{cavity}\ x\ g$$

$$= \frac{1}{2} x t_{cavity} x \left( t_{cavity} x \tan \theta \right)$$

$$= \frac{1}{2} x t_{cavity}^2 x \tan \theta$$

Therefore, a relationship can be drawn between the gap volume and taper angle as shown below.

# $Gap\ Volume \propto (taper\ angle\ (\theta))^2$

To conclude, formation of micro-depressions and non-planarity on the cavity surface after die embedding can be controlled be minimizing the cavity side wall taper.

# b) Increased I/O density for 3D integration

Low taper angle is also desired for chip last glass embedded cavity packages to allow the integration of through-glass via structures in close vicinity to the active device placed in the cavity, thereby reducing total interconnect length in the x-y directions leading to better electrical performance for 3D packages. The taper-induced increase in lateral interconnect length is illustrated in the Figure 25 below.

Figure 25: Image showing increased interconnect length from die to TGV due to tapered cavity sidewalls

# 3.2.3 Cavity Base Surface roughness

Surface roughness of the cavity base is an important metric because the die is placed on the base of the cavity. Non-co-planar surfaces can lead to voids, unreliable contact between die bump and pad and other defects, as illustrated in Figure 26 below, and a smooth and planar surface is required to achieve high assembly yield.

Figure 26: Cavity base surface roughness induced assembly yield challenges

Surface roughness also impacts die pad-to-pad co-planarity in the case of panel glass fan-out packages, as illustrated in Figure 27. Landing of micro-vias on non-coplanar die pads/bumps can result in electrical opens and affect panel scale interconnection yield. Moreover, angular tilting of the die due to the non-uniform surface can lead to x-y axis misalignment.

Figure 27: Die pad-pad non-co-planarity due to cavity base surface roughness

#### 3.3 Laminated Glass Cavities vs Blind Cavities

Based on the cavity quality evaluation metrics discussed in the previous section, two glass cavity structures were explored: (a) forming through cavities in one layer of glass followed by glass-to-glass bonding to a base glass carrier, and (b) blind cavities formed in a one-step process.

### 3.3.1 Laminated Glass Cavities

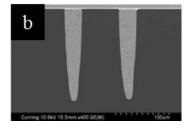

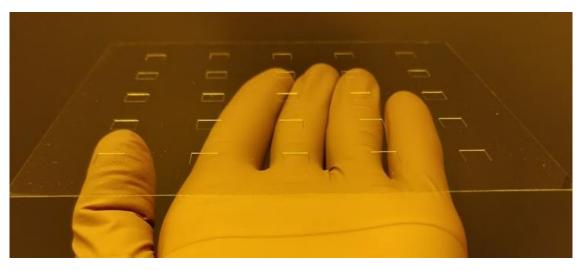

Cavity structures formed using a combination of through glass holes and a carrier substrate have numerous benefits and are the focus of this dissertation. Through-holes are micromachined through glass panels in a flexible process that allows custom designs in a range of glass thicknesses ( $50 \, \mu m - 500 \, \mu m$ ). Next, the carrier glass panel is bonded to the cavity panel to form the desired cavity structure. This two-step technique is used in cases where TGVs and RDL must be fabricated separately on the carrier glass before bonding of through-hole glass panel and chip assembly. Therefore, in this dissertation carrier glass is to demonstrate embedded glass cavity packages. Figure 28 below illustrates the concept of cavity formation using through glass holes and metallized carrier glass.

Figure 28: Process for formation of laminated glass cavities

This process enables cavity structures with excellent surface smoothness at the base, ensuring high yield during assembly. Step 3 shown in Figure 28 above involves formation of through-glass holes in glass panels which are then bonded to the carrier glass. To improve reliability of these through-holes, modifications in geometric design are needed. Cavity corners formed at right angles are vulnerable crack initiation sites due to stress concentration. Therefore, it is beneficial to have rounded corners as illustrated in Figure 29 below.

Figure 29: Cavity corners at right angles (left) vs rounded corners for reliable design (right)

Additionally, advancements in micromachining techniques enable formation of low taper, defect-free through glass holes which help meet the design metrics discussed in the previous section. Some of these advanced processes are described below:

### a) Advanced laser processes

Laser processes typically involve use of certain wavelengths of light (deep UV: <266 nm or IR: > 9 $\mu$ m) that glass absorbs. Photons of higher wavelength (IR regime) cannot break chemical bonds in glass due to insufficient photon energy; however, since absorptivity of glass is high at these wavelengths, the kinetic energy of photons is converted to vibrational energy, leading to thermal ablation by local melting and vaporization. Alternatively, low wavelength photons in the UV regime (<266nm) break chemical bonds in the glass matrix due to high incident energies. UV lasers avoid thermal damage and thus eliminate residual stresses. Ultra-short pulse lasers operating in the visible region are also used, where ablation is triggered by multi-photon initiated avalanche ionization [63]. These conventional laser processes lead to micro-cracking, glass chipping and rough surfaces.

Subsequent processing steps like grinding and polishing increase costs, reduce throughput and lead to low yields [64]

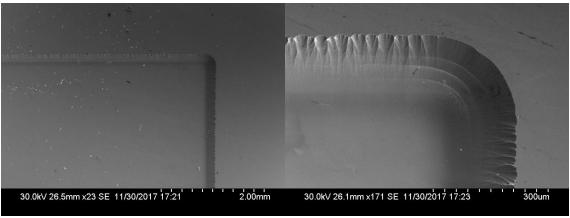

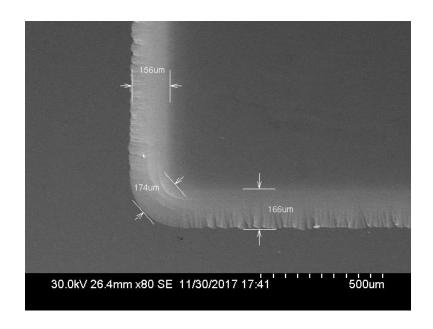

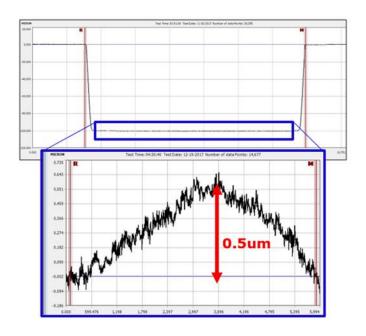

Figure 30: Advanced micromachining processes used to achieve low taper (<2µm)