# CMOS RF Power Amplifiers for Mobile Wireless Communications

A Dissertation Presented to The Academic Faculty

By

Kyu Hwan An

In Partial Fulfillment Of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2009

Copyright © Kyu Hwan An 2009

# CMOS RF Power Amplifiers for Mobile Wireless Communications

Approved by:

Dr. Joy Laskar, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. John D. Cressler School of Electrical & Computer Engineering *Georgia Institute of Technology*

Dr. Emmanouil M. Tentzeris School of Electrical & Computer Engineering *Georgia Institute of Technology*  Dr. Kevin T. Kornegay School of Electrical & Computer Engineering *Georgia Institute of Technology*

Dr. Paul A. Kohl School of Chemical & Biomolecular Engineering *Georgia Institute of Technology*

Date Approved: November 2, 2009

### ACKNOWLEDGEMENT

First of all, I would like to appreciate the monumental support and the invaluable opportunity that my advisor, Prof. Joy Laskar, gave me to work in this research. Without his inspiration and teaching, I certainly would not have achieved this goal.

I would also like to thank Prof. John D. Cressler, Prof. Emmanouil M. Tentzeris, Prof. Kevin T. Kornegay, and Prof. Paul A. Kohl, for their time in reviewing my dissertation and serving as my defense committee members.

I am very grateful to Dr. Chang-Ho Lee for his great support and guidance throughout this study. Furthermore, I am also indebted to Dr. Kyutae Lim for his efforts to provide the best research environment for all students.

Dr. Minsik Ahn and Dr. Dong Ho Lee deserve a special acknowledgement for their comments, help in the design, and their tremendous contributions in this research. I would like to acknowledge Samsung Design Center engineers, Dr. Jae Joon Chang, Dr. Woonyun Kim, Dr. Wangmyong Woo, Dr. Changhyuck Cho, Dr. Yunseo Park, Dr. Seongmo Yim, Dr. Ki Seok Yang, Dr. Jeonghu Han, and Michael Kroger for their assistance.

The support from members of power amplifier group has been invaluable: Hyungwook Kim, Jeongwon Cha, Eungjung Kim, Jihwan Kim, Youngchang Yoon, Hamhee Jeon, Michael Oakley, Hyunwoong Kim, Yan-Yu Huang, Kun Seok Lee, and Kwanyeob Chae. I would like to express my special gratitude to Ockgoo Lee for years of insightful feedback in my research. I would also like to acknowledge all my mates at the Microwave Application Group, Sang Min Lee, Jong Min Park, Kwan-Woo Kim, Taejoong Song, Sanghyun Woo, Joonhoi Hur, Jaehyouk Choi, Seungil Yoon, Michael Lee, Sungho Beck, Taejin Kim, Hyungsoo Kim, and Kilhoon Lee. I wish to thank Chris Evans, DeeDee Bennett, and Angelika Braig, for their continuous support.

And most of all, I can't express my love and gratitude enough to my wife, Min Jung Park, for her love and support throughout all my life. My daughter, Claire, and other one still waiting for her appearance in this world have also been a great source of joy. I am especially grateful to my parents, Jun Ho An and Cho Ja Kim, and my parents-in-law, Ki Soo Park and Soon Deuk Kim for their unconditional love. Without their encouragement and support, this dissertation would not have been possible. I would also like to recognize my brother, Kyu Cheol An, who also deserves a special thank you for his support.

## TABLE OF CONTENTS

| Acknowle    | dgement                                                | iii   |

|-------------|--------------------------------------------------------|-------|

| List of Ta  | bles                                                   | ix    |

| List of Fig | gures                                                  | X     |

| List of Ab  | breviations                                            | XV    |

| Summary     |                                                        | xviii |

| Chapter 1   | Introduction                                           | 1     |

| 1.1. Ba     | ickground                                              | 1     |

| 1.2. M      | otivation                                              | 4     |

| 1.3. Or     | ganization of the Thesis                               | 6     |

| Chapter 2   | <b>RF</b> Power Amplifiers for Wireless Communications | 9     |

| 2.1. In     | troduction                                             | 9     |

| 2.2. Cł     | naracteristics of RF Power Amplifiers                  | 10    |

| 2.2.1.      | Output Power, Gain, and Efficiency                     | 10    |

| 2.2.2.      | Linearity                                              | 14    |

| 2.2.3.      | Other Characteristics                                  | 24    |

| 2.3. W      | ireless Standards                                      | 28    |

| 2.3.1.      | Global System for Mobile Communications                | 29    |

| 2.3.2 | Wideband Code Division Multiple Access                           | 30 |

|-------|------------------------------------------------------------------|----|

| 2.3.3 | . Wireless Local Area Network and Worldwide Interoperability for |    |

| Mici  | owave Access                                                     | 31 |

| 2.4.  | Design of RF Power Amplifiers                                    | 32 |

| 2.4.1 | . Design Procedure                                               | 32 |

| 2.4.2 | Simulation Techniques                                            | 34 |

| 2.5.  | Measurement of RF Power Amplifiers                               | 36 |

| 2.6.  | Conclusion                                                       | 40 |

### Chapter 3 Challenges and Techniques of CMOS RF Power Amplifiers

41

| 3.1   | Introduction                                          | 41 |

|-------|-------------------------------------------------------|----|

| 3.2   | General Issues in Designing RF Power Amplifiers       | 42 |

| 3.3   | Challenges of CMOS Technology for RF Power Amplifiers | 44 |

| 3.3.  | Lossy Substrate and Thin Top Metal of Bulk CMOS       | 44 |

| 3.3.2 | 2 Reliability of Bulk CMOS                            | 51 |

| 3.3.3 | 3 Low Transconductance of Bulk CMOS                   | 53 |

| 3.3.4 | 4 Nonlinearity of Bulk CMOS                           | 54 |

| 3.4   | Techniques for CMOS RF Power Amplifiers               | 55 |

| 3.4.  | Output Power-Combining Techniques                     | 56 |

| 3.4.2 | 2 Linearity Enhancement Techniques                    | 58 |

| 3.4.3 | B Efficiency Enhancement Techniques                   | 60 |

| 3.5   | Conclusion                                            | 61 |

| Amplifier Design                                                 | 63  |

|------------------------------------------------------------------|-----|

| 4.1 Introduction                                                 | 63  |

| 4.2 Power-Combining Transformer                                  | 64  |

| 4.3 Switching Power Amplifier Design Using Parallel Power-Combin | ing |

| Transformer                                                      | 75  |

| 4.3.1 Transformer Design                                         | 75  |

| 4.3.2 Switching Power Amplifier Design                           | 80  |

| 4.3.3 Measurement Results                                        | 84  |

| 4.4 Fully-Integrated RF Front-End                                | 90  |

| 4.4.1 CMOS RF Power Amplifier Design                             | 90  |

| 4.4.2 CMOS Antenna Switch Design                                 | 92  |

| 4.4.3 Measurement Results                                        | 93  |

| 4.5 Conclusion                                                   | 96  |

| Chapter 5 Linear Power Amplifier Design for High Data-Ra         | ate |

| Applications                                                     | 98  |

| 5.1 Introduction                                                 | 98  |

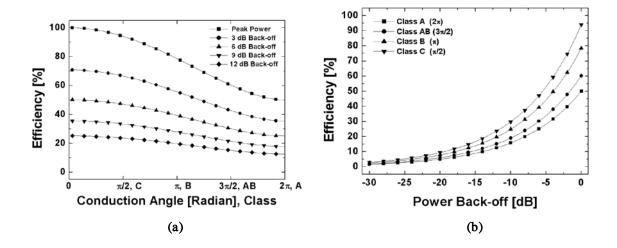

| 5.2 Efficiency at Power Back-off                                 | 99  |

| 5.2.1 Efficiencies of Linear Power Amplifiers                    | 99  |

### Chapter 4 Power-Combining Transformers and Class-E Power

Linear Power Amplifier Design Using Discrete Power Control

5.3.1 Discrete Power Control of Parallel Amplification

105

109

109

5.2.2 Efficiencies in the Back-off Area

5.3

| 5.3.2 Linear Power Amplifier Design           | 110 |

|-----------------------------------------------|-----|

| 5.3.3 Measurement Results                     | 112 |

| 5.4 Conclusion                                | 116 |

| Chapter 6 Conclusions and Future Work         | 117 |

| 6.1. Technical Contributions and Achievements | 117 |

| 6.2. Future Research Directions               | 119 |

| Publications                                  | 121 |

| References                                    | 123 |

| Vita                                          | 131 |

## LIST OF TABLES

| Table 1. Typical output power of PAs for some wireless applications                 | 4   |

|-------------------------------------------------------------------------------------|-----|

| Table 2. Commercial GSM PA specifications                                           | 30  |

| Table 3. Commercial WCDMA PA specifications                                         | 31  |

| Table 4. 802.11g WLAN transmitter specifications                                    | 32  |

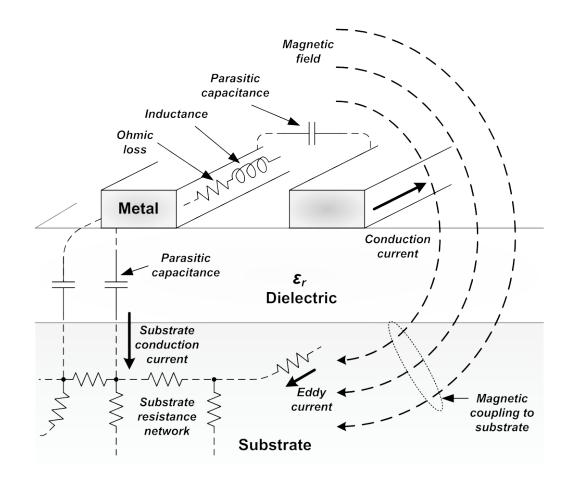

| Table 5. Loss mechanism of inductive structures in CMOS technologies                | 50  |

| Table 6. Breakdown mechanism of FETs                                                | 52  |

| Table 7. Simulated characteristics of the primary and secondary windings            | 78  |

| Table 8. Summary of measured and simulated PA performance                           | 88  |

| Table 9. Comparison of studies that dealt with output combining networks for fully- |     |

| integrated CMOS PAs based on the figure of merit                                    | 89  |

| Table 10. Performance summary and comparison with other fully-integrated CMOS I     | PAs |

|                                                                                     | 116 |

## LIST OF FIGURES

| Figure 1. A block diagram of a direct-conversion transceiver and its processes | s 2         |

|--------------------------------------------------------------------------------|-------------|

| Figure 2. Output power requirements of various standards                       | 3           |

| Figure 3. Scaling-down of CMOS technologies                                    | 5           |

| Figure 4. Cost advantages of CMOS technologies over other semiconductor to     | echnologies |

| for PA solutions in US\$/mm <sup>2</sup>                                       | 5           |

| Figure 5. Benefits of CMOS PAs in cellular markets                             | 6           |

| Figure 6. Outline of this research                                             | 7           |

| Figure 7. Definition of power and gain                                         | 10          |

| Figure 8. Efficiency calculation of a PA                                       | 13          |

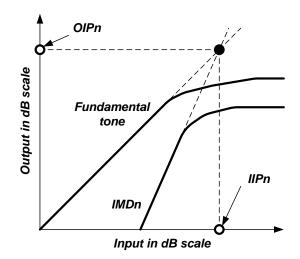

| Figure 9. Linearity indicators of a PA                                         | 14          |

| Figure 10. Distortion of a PA with one-tone input                              | 15          |

| Figure 11. 1dB compression point                                               | 16          |

| Figure 12. Distortion of a PA with two-tone input                              | 17          |

| Figure 13. IP3 and IMD                                                         | 18          |

| Figure 14. AM-AM and AM-PM distortion                                          | 19          |

| Figure 15. CCDF of a digitally modulated signal                                | 21          |

| Figure 16. Error vector of symbols                                             | 22          |

| Figure 17. EVM of a digitally-modulated signal                                 | 23          |

| Figure 18. ACLR of a digitally-modulated signal                                | 24          |

| Figure 19. Reflection at output node.                                          | 25          |

| Figure 20. Constant VSWR circles in the Smith chart                            | 26          |

| Figure 21. Reverse IMD generation                                                                               | 27 |

|-----------------------------------------------------------------------------------------------------------------|----|

| Figure 22. General design procedure of a PA                                                                     | 33 |

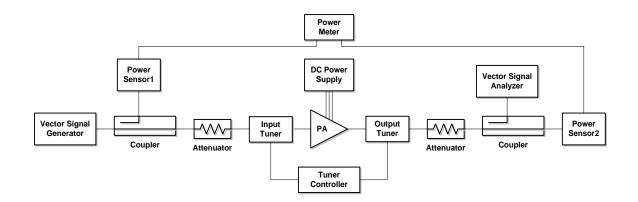

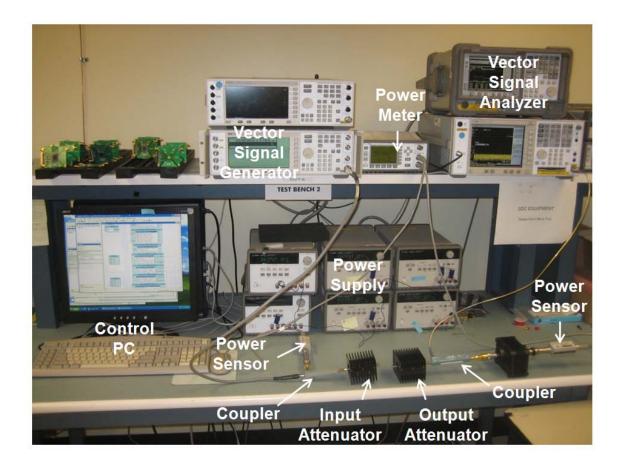

| Figure 23. Measurement setup of a PA                                                                            | 37 |

| Figure 24. Calibration procedure for a PA measurement setup: (a) offset calculation of                          | of |

| input and (b) offset calculation of output                                                                      | 38 |

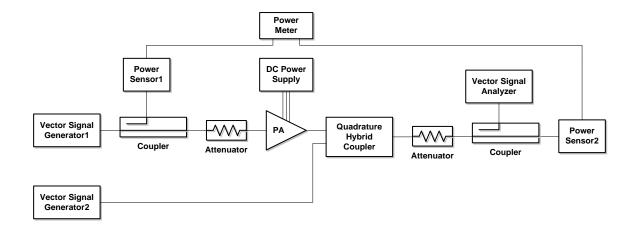

| Figure 25. Source/load-pull setup                                                                               | 39 |

| Figure 26. Reverse IMD test set up                                                                              | 39 |

| Figure 27. Block diagram of the PA output network                                                               | 42 |

| Figure 28. Loss mechanism of inductive structures in CMOS technologies.                                         | 45 |

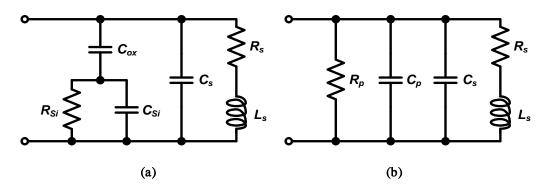

| Figure 29. Lumped model of a spiral inductor on silicon: (a) physical model and (b)                             |    |

| simplified equivalent model                                                                                     | 46 |

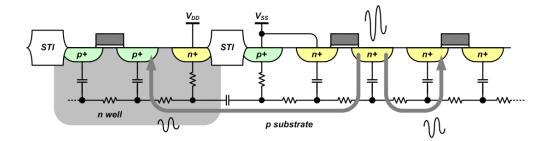

| Figure 30. Layer information of a standard CMOS process                                                         | 49 |

| Figure 31. Substrate coupling of a CMOS process                                                                 | 51 |

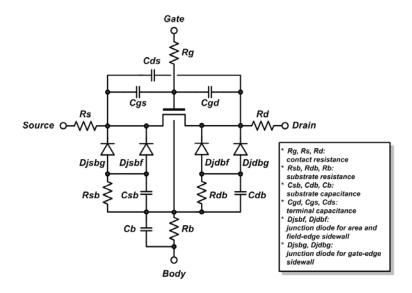

| Figure 32. Equivalent circuit model for RF NMOS transistor                                                      | 54 |

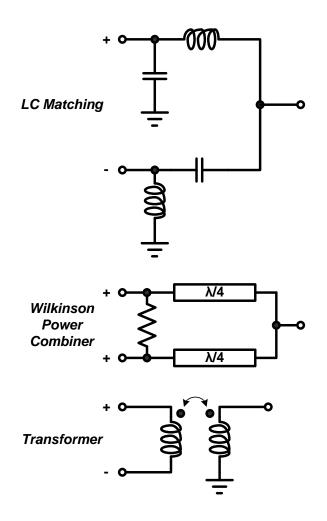

| Figure 33. Conventional power-combining techniques                                                              | 57 |

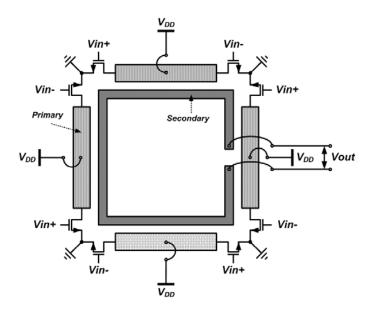

| Figure 34. Diagram of a DAT PA                                                                                  | 58 |

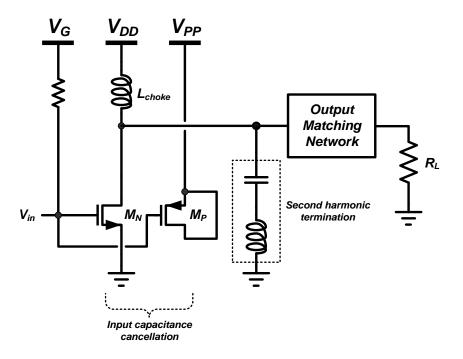

| Figure 35. Input capacitance cancellation technique                                                             | 59 |

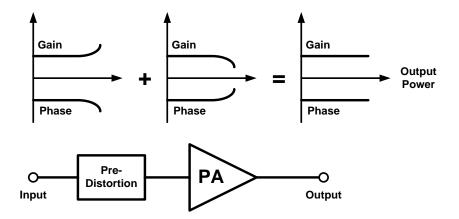

| Figure 36. Pre-distortion of a PA                                                                               | 60 |

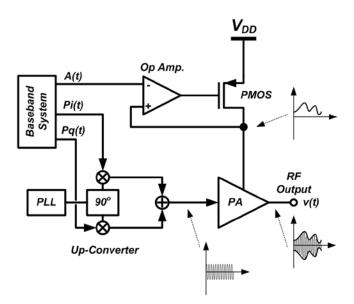

| Figure 37. Polar transmitter system                                                                             | 61 |

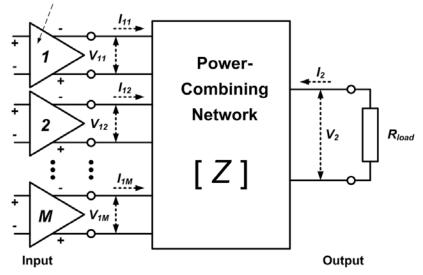

| Figure 38. Conceptual power-combining network.                                                                  | 65 |

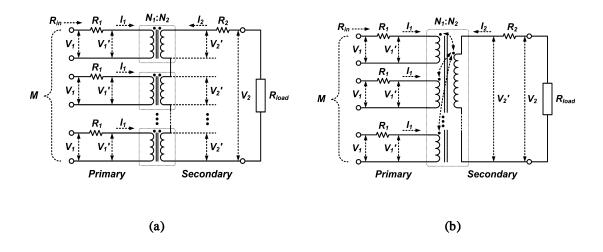

| Figure 39. Power-combining transformers (a) SCT and (b) PCT                                                     | 66 |

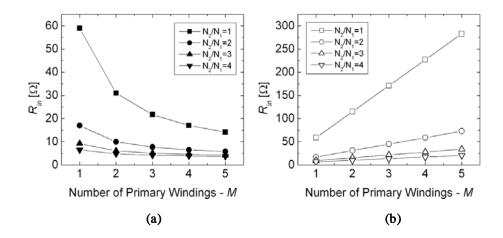

| Figure 40. Input impedance ( $R_1 = 3 \Omega$ , $R_2 = 6 \Omega$ , $R_{load} = 50 \Omega$ ) (a) SCT and (b) PCT | 69 |

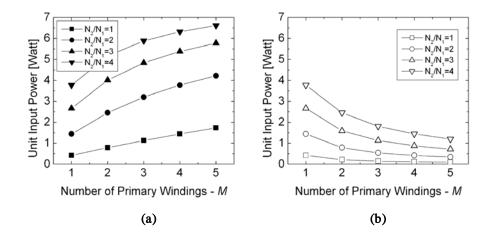

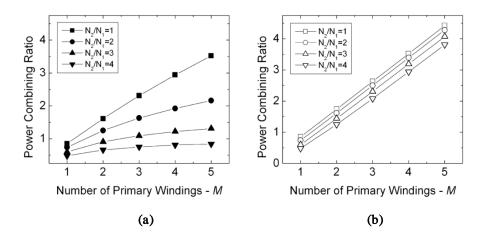

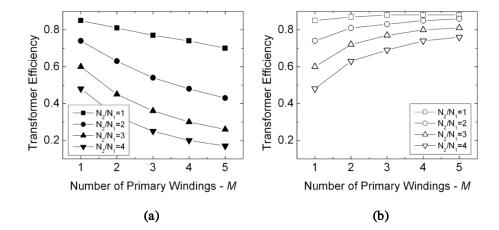

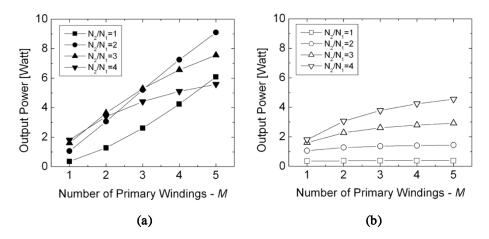

Figure 41. Power of unit power cell ( $R_1 = 3 \Omega$ ,  $R_2 = 6 \Omega$ ,  $R_{load} = 50 \Omega$ , differential class-A operation,  $V_1/2 = 3.5$  V) (a) SCT and (b) PCT 69

Figure 42. Power combining ratio ( $R_1 = 3 \Omega$ ,  $R_2 = 6 \Omega$ ,  $R_{load} = 50 \Omega$ ) (a) SCT and (b) PCT

86

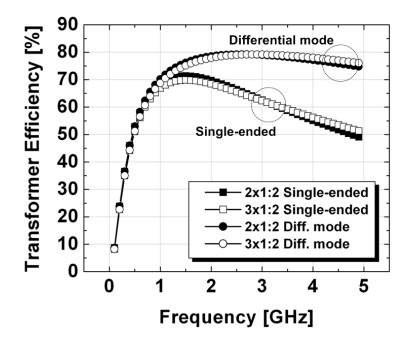

Figure 43. Transformer efficiency ( $R_1 = 3 \Omega$ ,  $R_2 = 6 \Omega$ ,  $R_{load} = 50 \Omega$ ) (a) SCT and (b) PCT 71

Figure 44. Output power (

$$R_1 = 3 \Omega$$

,  $R_2 = 6 \Omega$ ,  $R_{load} = 50 \Omega$ , differential class-A operation,

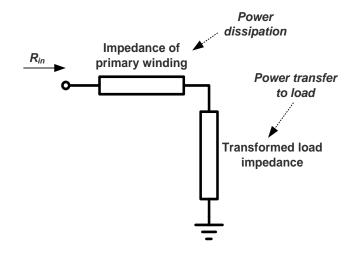

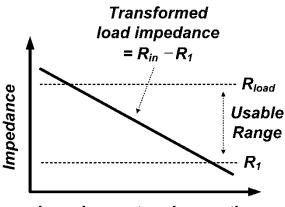

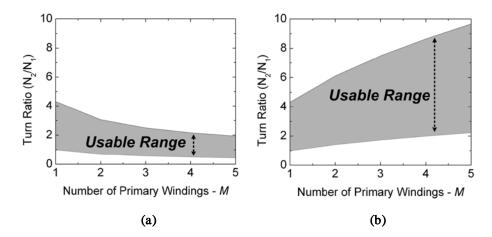

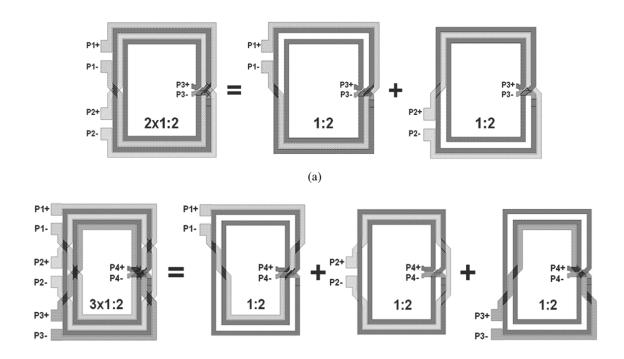

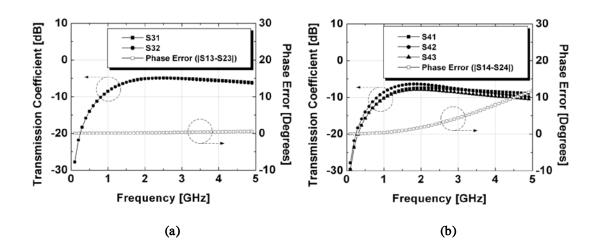

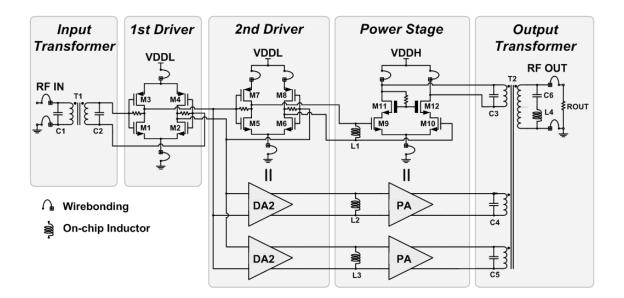

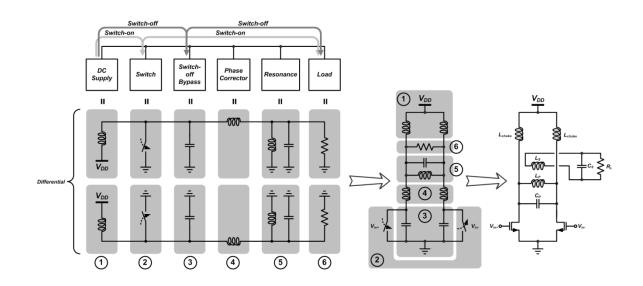

$V_1/2 = 3.5$  V) (a) SCT and (b) PCT 72 73 Figure 45. Input impedance looking into a transformer 73 Figure 46. Usable range of impedance transformation Figure 47. Usable range of turn ratio ( $R_1 = 3 \Omega$ ,  $R_2 = 6 \Omega$ ,  $R_{load} = 50 \Omega$ , differential class-74 A operation,  $V_1/2 = 3.5$  V) (a) SCT and (b) PCT Figure 48. Proposed transformers (a)  $2 \times 1:2$  PCT and (b)  $3 \times 1:2$  PCT 77 Figure 49. Simulated transmission coefficients and phase error (a)  $2 \times 1:2$  PCT and (b) 3×1:2 PCT 79 Figure 50. Simulated transformer efficiencies 80 81 Figure 51. Schematic diagram of a class-E PA Figure 52. Design of the class-E PA 82

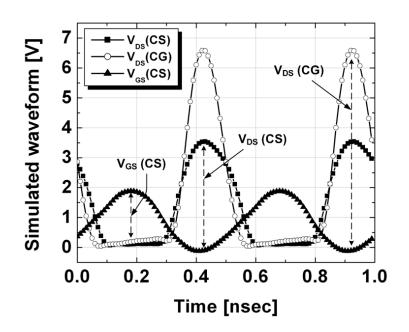

- Figure 53. Simulated waveform of the power stage83

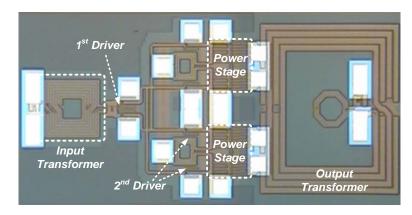

- Figure 54. Microphotographs of the class-E PAs (a) using 2×1:2 PCT and (b) using 3×1:2 PCT 85

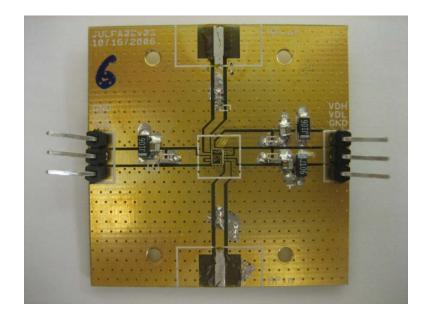

- Figure 56. Assembled measurement board  $(4\text{cm} \times 4\text{cm})$  86

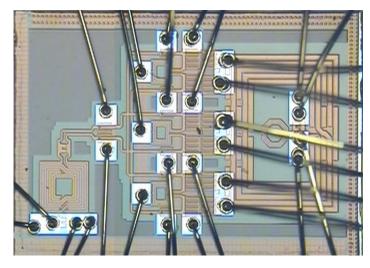

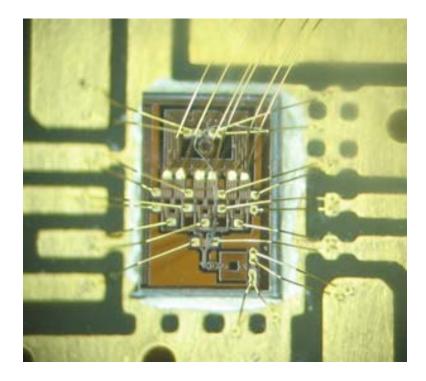

Figure 55. Microphotograph of the board assembly

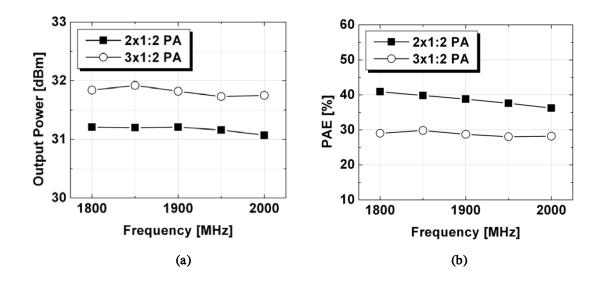

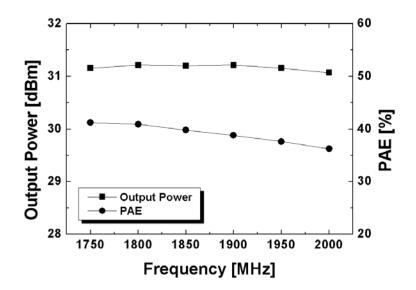

Figure 58. Measured results versus frequency (Input power of 5 dBm) (a) output power and (b) PAE 87

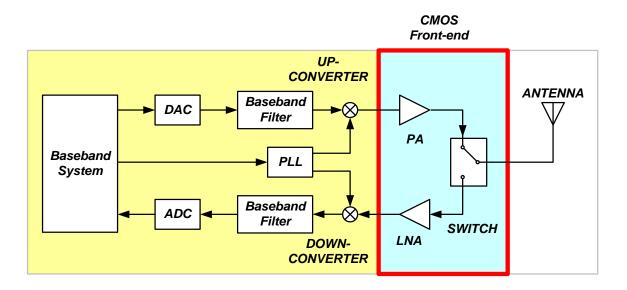

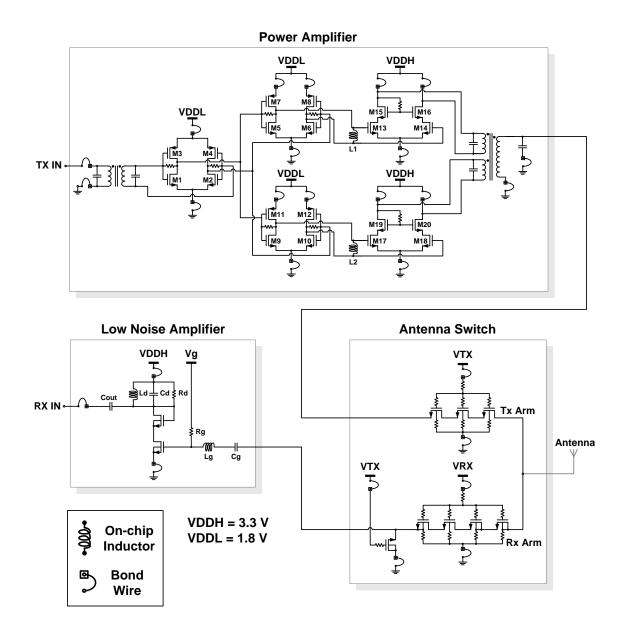

| Figure 59. Block diagram of RF front-end in a direct-conversion transceiver                       | 90        |

|---------------------------------------------------------------------------------------------------|-----------|

| Figure 60. Schematic diagram of the fully-integrated RF front-end                                 | 91        |

| Figure 61. Simulated PA performance in the front-end                                              | 92        |

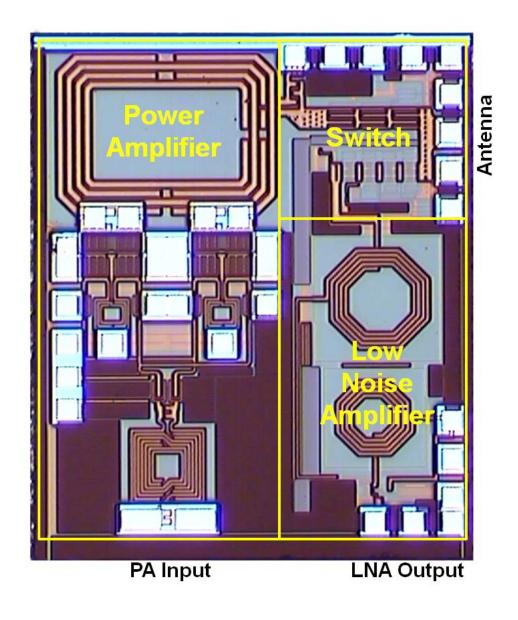

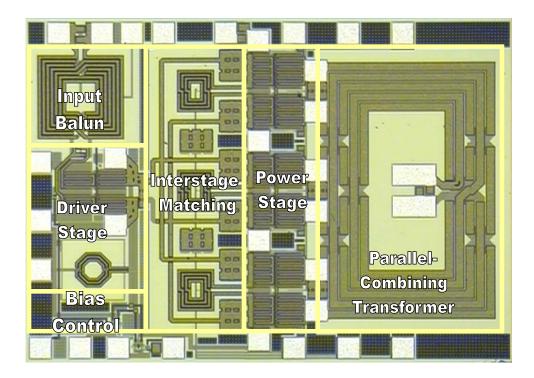

| Figure 62. Microphotographs of the fully-integrated RF front-end                                  | 94        |

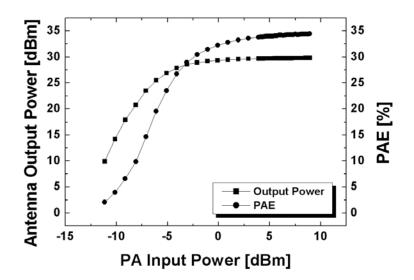

| Figure 63. Measured front-end performance vs. PA input power at 2 GHz                             | 95        |

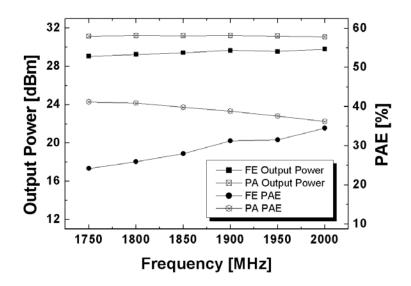

| Figure 64. Performance comparison between the simulated PA and measured from                      | nt-end 95 |

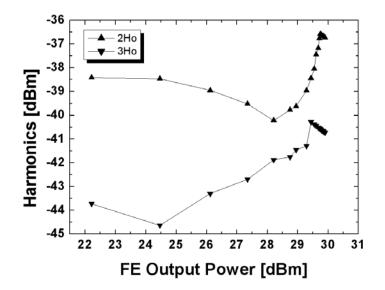

| Figure 65. Measured harmonic performance of the front-end at 2 GHz                                | 96        |

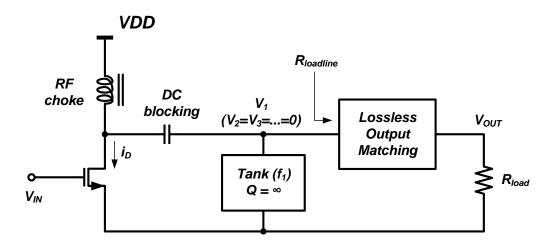

| Figure 66. A simplified linear PA topology                                                        | 99        |

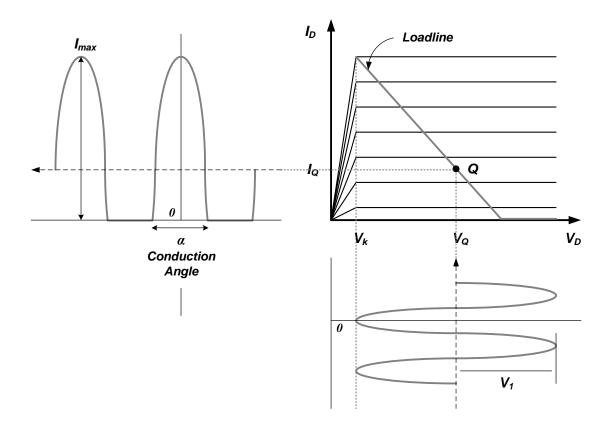

| Figure 67. Loadline analysis of a PA at a reduced conduction angle                                | 100       |

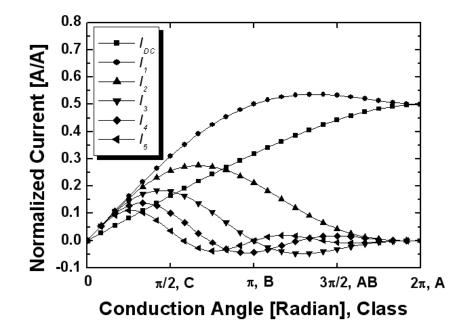

| Figure 68. Current waveforms of Fourier components as a function of the conduc                    | tion      |

| angle                                                                                             | 102       |

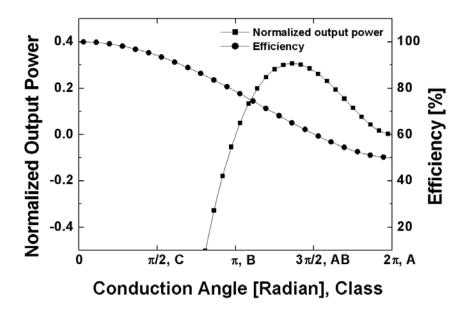

| Figure 69. Output power and efficiency capability as a function of the conduction                 | 1 angle   |

|                                                                                                   | 103       |

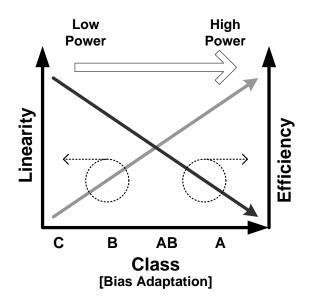

| Figure 70. Conceptual class shift by bias adaptation                                              | 104       |

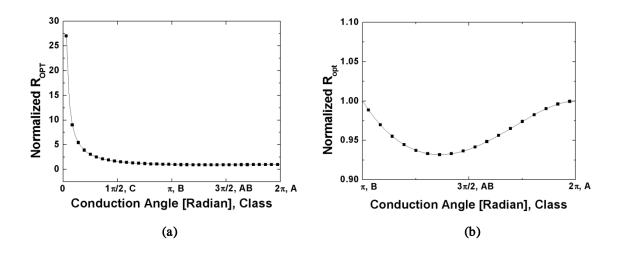

| Figure 71. Optimal loadline as a function of the conduction angle (a) the $0 \sim 2\pi$ range and |           |

| (b) zoomed view for the $\pi \sim 2\pi$ range                                                     | 105       |

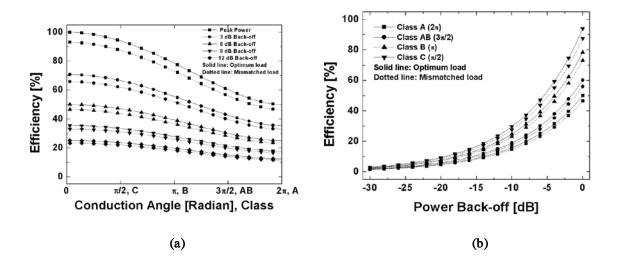

| Figure 72. Efficiency in the power back-off (a) efficiency as a function of the conduction        |           |

| angle and (b) efficiency as a function of the power back-off                                      | 106       |

| Figure 73. Efficiency degradation by a mismatched load ( $\Gamma_x$ =0.036) at the power          | back-off  |

|                                                                                                   | 108       |

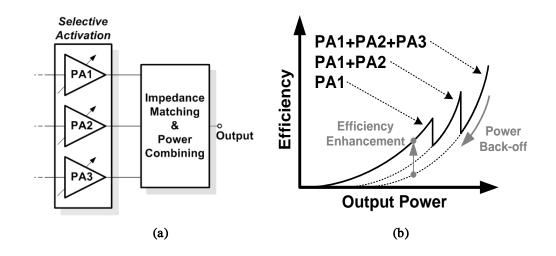

| Figure 74. Design concept of the proposed PA: (a) block diagram of the PA and (b) |     |

|-----------------------------------------------------------------------------------|-----|

| efficiency enhancement of the PA                                                  | 109 |

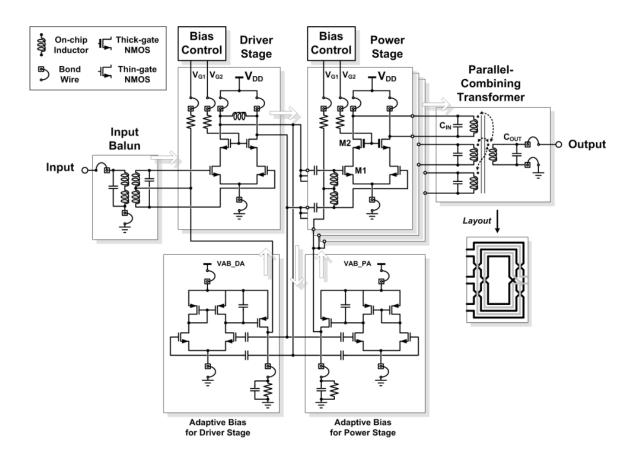

| Figure 75. Circuit schematic of the proposed PA                                   | 111 |

| Figure 76. Layout of the proposed PA.                                             | 112 |

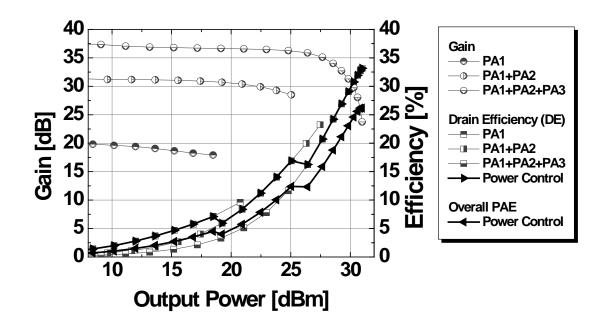

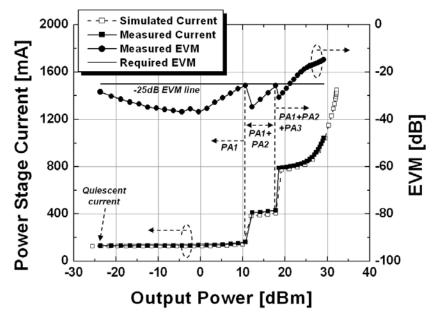

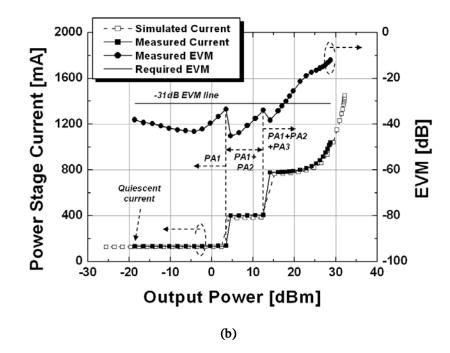

| Figure 77. Gain and efficiency variation according to discrete power control      | 113 |

| Figure 78. Discrete power control with EVM (2.4 GHz) (a) the 802.11g WLAN 54 Mbps |     |

| 64 QAM OFDM signal and (b) the 802.16e WiMAX 54 Mbps 64 QAM OFDM signa            | al  |

|                                                                                   | 115 |

## LIST OF ABBREVIATIONS

| ACLR                                  | adjacent channel leakage ratio                                                                                                                                           |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACPR                                  | adjacent channel power ratio                                                                                                                                             |

| AM-AM                                 | amplitude-amplitude modulation                                                                                                                                           |

| AM-PM                                 | amplitude-phase modulation                                                                                                                                               |

| AMPS                                  | advanced mobile phone service                                                                                                                                            |

| BJT                                   | bipolar junction transistor                                                                                                                                              |

| CCDF                                  | complementary cumulative density function                                                                                                                                |

| CDF                                   | cumulative density function                                                                                                                                              |

| CDMA                                  | code division multiple access                                                                                                                                            |

| CE                                    | collector efficiency                                                                                                                                                     |

|                                       |                                                                                                                                                                          |

| CG                                    | common gate                                                                                                                                                              |

| CG<br>CMOS                            | common gate<br>complementary metal oxide semiconductor                                                                                                                   |

|                                       |                                                                                                                                                                          |

| CMOS                                  | complementary metal oxide semiconductor                                                                                                                                  |

| CMOS<br>CS                            | complementary metal oxide semiconductor common source                                                                                                                    |

| CMOS<br>CS<br>DAT                     | complementary metal oxide semiconductor<br>common source<br>distributed active transformer                                                                               |

| CMOS<br>CS<br>DAT<br>DE               | complementary metal oxide semiconductor<br>common source<br>distributed active transformer<br>drain efficiency                                                           |

| CMOS<br>CS<br>DAT<br>DE<br>EVM        | complementary metal oxide semiconductor<br>common source<br>distributed active transformer<br>drain efficiency<br>error vector magnitude                                 |

| CMOS<br>CS<br>DAT<br>DE<br>EVM<br>FDD | complementary metal oxide semiconductor<br>common source<br>distributed active transformer<br>drain efficiency<br>error vector magnitude<br>frequency-division duplexing |

| GMSK  | Gaussian minimum shift keying              |

|-------|--------------------------------------------|

| GPRS  | general packet radio system                |

| GSM   | global system for mobile communications    |

| НВ    | harmonic balance                           |

| HBT   | hetero-junction bipolar transistors        |

| HSDPA | high-speed download packet access          |

| IC    | integrated circuit                         |

| IMD3  | third-order intermodulation distortion     |

| IP3   | third-order intercept point                |

| LNA   | low noise amplifier                        |

| LSSP  | large signal S-parameter                   |

| LTCC  | low-temperature co-fired ceramic           |

| NMT   | nordic mobile telephone                    |

| OFDM  | orthogonal frequency division multiplexing |

| PA    | power amplifier                            |

| PAE   | power-added efficiency                     |

| PAPR  | peak-to-average power ratio                |

| PAR   | peak-to-average ratio                      |

| PCB   | printed circuit board                      |

| PCR   | power-combining ratio                      |

| PCT   | parallel-combining transformer             |

| PDF   | probability density function               |

| PGS   | patterned ground shielding                 |

| P1dB  | 1dB compression point                           |  |

|-------|-------------------------------------------------|--|

| RF    | radio frequency                                 |  |

| SCT   | series-combining transformer                    |  |

| TDD   | time-division duplexing                         |  |

| TDMA  | time-division multiple access                   |  |

| UMTS  | universal mobile telecommunications system      |  |

| VCO   | voltage-controlled oscillator                   |  |

| VSWR  | voltage standing wave ratio                     |  |

| WCDMA | wideband code division multiple access          |  |

| WiMAX | worldwide interoperability for microwave access |  |

| WLAN  | local wireless area network                     |  |

### SUMMARY

The explosive growth of the wireless market has increased the demand for lowcost, highly-integrated CMOS wireless transceivers. However, the implementation of CMOS RF power amplifiers remains a formidable challenge. The objective of this research is to demonstrate the feasibility of CMOS RF power amplifiers by compensating for the RF performance disadvantages of CMOS technology. This dissertation proposes a parallel-combining transformer (PCT) as an impedance-matching and output-combining network. The results of a comprehensive analysis show that the PCT is a suitable solution for watt-level output power generation in cellular applications. To achieve high output power and high efficiency, the work presented here entailed the design of a class-E switching power amplifier in a 0.18-µm CMOS technology for GSM applications and, with the suggested power amplifier design technique, successfully demonstrated a fullyintegrated RF front-end consisting of a power amplifier and an antenna switch. This dissertation also proposed an efficiency enhancement technique at power back-off. In an effort to save current in the power back-off while satisfying the EVM requirements, a class-AB linear power amplifier was implemented in a 0.18- $\mu m$  CMOS technology for WLAN and WiMAX applications using a PCT as well as an operation class shift between class-A and class-B. Thus, the research in this dissertation provides low-cost CMOS RF power amplifier solutions for commercial products used in mobile wireless communications.

# CHAPTER 1 INTRODUCTION

#### 1.1. Background

Since the explosive growth of the wireless market took place in the late 1990s, just a decade ago, the top priority for manufacturers of mobile terminals has been to maximize their profits by lowering the cost of mobile terminals. However, to meet the demand for low-cost terminals in the ever-competitive wireless market, manufacturers must be able to facilitate their production of components to shorten the time to market. In the early era of mobile terminals, engineers spent a considerable amount of time assembling and matching components in the signal path to minimize loss. However, as the functions of wireless communication have proliferated and diversified, mobile terminal manufacturers are calling for easier solutions for modular integration, such as display, audio, and communication, in order to save time under pressure. As the wireless market trend continues to accelerate, integrated circuit (IC) manufacturers are taking on the burden of realizing modular functionality by attempting to provide a ready-made solution for cell-phone and wireless terminal designers.

Accordingly, the inevitable task and ultimate goal of the modern wireless communication industry is the full integration of digital, analog, and even radio frequency (RF) functions. To this end, the industry has devoted great effort to designing wireless terminals using a common semiconductor process that utilizes a single chip; thus, true single-chip radio is now within the grasp of manufacturers. To date, the most successful solution for such demands has been complementary metal oxide semiconductor (CMOS) technology, thanks to its cost-effective material and great versatility.

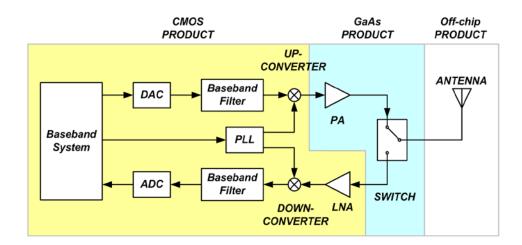

Lower  $f_{max}$  and  $f_T$  of CMOS devices are not serious problems at the frequencies used by cellular applications. However, because of the intrinsic drawbacks of standard CMOS processes from the RF perspective, several obstacles, especially low quality factor (*Q*) passive structures and lossy substrate [1] and low breakdown voltage of active devices [2], are hindering the realization of a fully-integrated CMOS radio. Thus, the implementation of CMOS RF front-ends, such as an RF switch [3] or a RF power amplifier (PA) [4], remains a challenging task. Accordingly, most commercial products are based on gallium arsenide (GaAs) technologies, as shown in Figure 1.

Figure 1. A block diagram of a direct-conversion transceiver and its processes

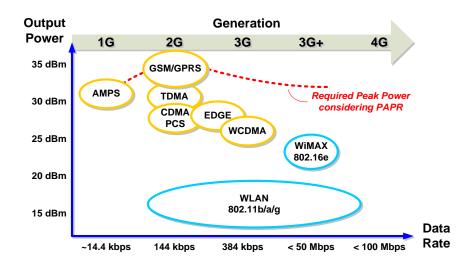

Today, the various demands from consumers have stoked the development of multiple standards. For example, global system for mobile communications (GSM), code

division multiple access (CDMA), and wideband CDMA (WCDMA) are now used for voice and relatively low data rate communications while local wireless area networks (WLANs) and worldwide interoperability for microwave access (WiMAX) mainly target high data rate communications with varying mobility. The typical output power levels of PAs for some wireless applications are listed in Table 1 and shown in Figure 2 along with their data rates. While many standards require different average output powers due to peak-to-average power ratio (PAPR), the general peak output power requirement for wireless communications is usually 30 dBm to 35 dBm as indicated in Figure 2. Due to the poor linearity performance of CMOS devices, satisfying the key specifications of commercial RF PA products (high output power, high efficiency, and high linearity) with CMOS devices poses a great challenge and even a greater one for emerging wireless communications [4] in which good linearity is a default requirement.

Figure 2. Output power requirements of various standards

| Application | Standard       | Frequency<br>(MHz) | Typical Output<br>Power (dBm) | Modulation |

|-------------|----------------|--------------------|-------------------------------|------------|

| Cellular    | GSM850         | 824-849            | 35                            | GMSK       |

|             | E-GSM900       | 880-915            | 35                            | GMSK       |

|             | DCS1800        | 1710-1785          | 33                            | GMSK       |

|             | PCS1900        | 1850-1910          | 33                            | GMSK       |

|             | CDMA (IS-95)   | 824-849            | 28                            | O-QPSK     |

|             | PCS (IS-98)    | 1750-1780          | 28                            | O-QPSK     |

|             |                | 1850-1910          |                               |            |

|             | WCDMA (UMTS)   | 1920-1980          | 27                            | HPSK       |

| WLAN        | IEEE 802.11b   | 2400-2484          | 16-20                         | PSK-CCK    |

|             | IEEE 802.11a   | 5150-5350          | 14-20                         | OFDM       |

|             | IEEE 802.11g   | 2400-2484          | 16-20                         | OFDM       |

| WiMAX       | IEEE 802.16d/e | 2300-2700          | 22-25                         | OFDM       |

|             | IEEE 802.16d/e | 3300-3700          | 22-25                         | OFDM       |

|             | IEEE 802.16d/e | 4900-5900          | 22-25                         | OFDM       |

Table 1. Typical output power of PAs for some wireless applications

#### **1.2.** Motivation

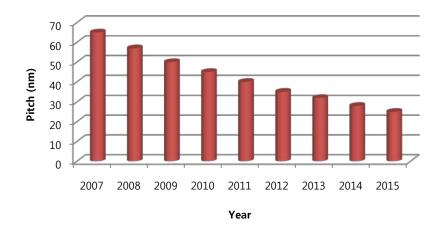

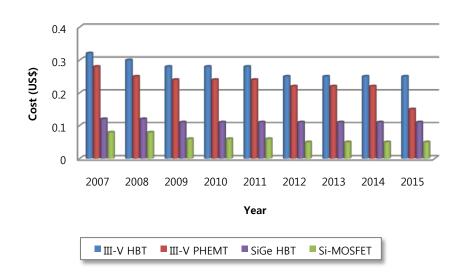

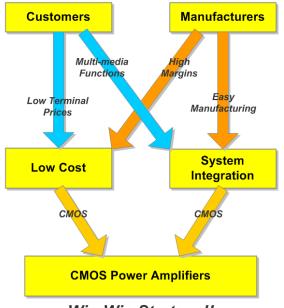

The difficulties of CMOS RF PAs have already been described in the previous section and will be revisited in Chapter III. From a purely performance-oriented standpoint, CMOS technologies are not a good solution. However, they follow an aggressive down-scaling roadmap, shown in Figure 3, that is unbeatable when compared to any other semiconductor technology; hence, the integrability and versatility of CMOS technologies will be welcomed for a long time down the road. Narrowing down the focus to the cost of PAs, CMOS technologies would be the cheapest among other candidates such as III-V HBT, III-V PHEMT, SiGe HBT, and Si-MOSFET technologies, as shown in Figure 4. Thus, it seems inevitable that both customers and manufacturers will choose

CMOS technologies over all others, as it represents a win-win strategy, depicted in Figure 5 [5].

Figure 3. Scaling-down of CMOS technologies

Figure 4. Cost advantages of CMOS technologies over other semiconductor technologies for PA solutions in US\$/mm<sup>2</sup>

Win-Win Strategy!!

Figure 5. Benefits of CMOS PAs in cellular markets

Currently, the atmosphere is ideal for an RF CMOS PA in the wireless market. One caveat, however, is how to achieve comparable performance using CMOS in implementing a PA. Therefore, in serious consideration of the implementation of CMOS RF PAs, this research will introduce and discuss various efforts at determining good PA solutions for their commercial application in wireless communications.

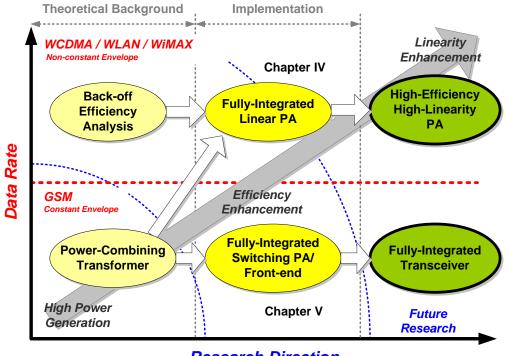

#### **1.3.** Organization of the Thesis

Based on the aforementioned technological background and motivation, the purpose of this work is to exploit CMOS technologies for developing RF PAs for current and future wireless communications as illustrated in Figure 6. In this work, research on a power-combining transformer technique is proposed for a fully-integrated switching PA that achieves both high output power and high efficiency for constant envelope communication. In addition, the analysis for power back-off efficiency is executed for the design of a fully-integrated linear PA that achieves both high output power and high efficiency in linear operation for non-constant envelope high data rate communication. The final and ultimate goal of this research is to identify the critical characteristics of an RF PA for high data rate communications: high output power, high efficiency, and high linearity.

**Research Direction**

Figure 6. Outline of this research

Chapter 1 contains an introduction to the wireless market and current trends, the requirements of RF PAs, and the motivation for this work. To provide some background,

Chapter 2 presents an explanation of the basic definitions of RF PAs for wireless communications and describes the key quantities, wireless standards, and measurement methods. Chapter 3 presents CMOS technology and its shortcomings from an RF PA design standpoint, and the information presented in this chapter serves as a basis for several PA designs discussed and illustrated in the following chapters. Chapter 4 presents a new power-combining method using a monolithic transformer for PA and the design of class-E PAs and an RF front-end design, and Chapter 5 introduces a CMOS linear PA for high data rate communications with an analysis of power back-off efficiency. Finally, Chapter 6 summarizes and concludes the work in this dissertation, and posits research trends for the future.

# CHAPTER 2 RF Power Amplifiers for Wireless Communications

#### 2.1. Introduction

Before advancing to the topic of CMOS RF PA, this dissertation will present an overview of PAs, which will serve as a guideline for the remainder of this research. A prerequisite for the design of PAs is a thorough understanding of the meaning and the significance of their key characteristics, such as output power, gain, efficiency, linearity, harmonic, stability, and so on. However, the complicated nature of these characteristics, particularly linearity, often hampers designers in their efforts to realize an efficient linear PA. Thus, the quantitative measures of linearity must first be understood. More importantly, for high data rate digital communications, such quantities, used to represent popular digital standards such as GSM, WCDMA, WLAN, and WiMAX must be known from the first phase of PA design.

Section 2.2 introduces the key characteristics of RF PAs such as output power, gain, efficiency, linearity, and other specifications, and Section 2.3 briefly summarizes several popular wireless standards from the PA standpoint. Section 2.4 then lists the general design procedures, and Section 2.5 lists the general measurement setups for various PA specifications.

#### 2.2. Characteristics of RF Power Amplifiers

The characteristics of RF PAs differ according to various standards. Once a PA is given, however, common specification parameters are used to evaluate its performance. The key specification items and their meanings follow.

#### 2.2.1. Output Power, Gain, and Efficiency

#### 2.2.1.1. Output Power

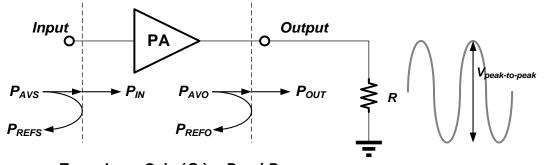

Output power is the most important design aspect of a PA. In one sense, if the PA generates low output power, it loses its identity, making it hard to define. When a supply voltage is given as a fixed value, only the amount of current that provides a required output power can be a design parameter. Assuming a normal output load with resistance, R, the PA in Figure 7 has an output power of the following expression:

$$P_{OUT} = \frac{\left(\frac{V_{\text{peak-to-peak}}}{2}\right)^2}{2 \cdot R}$$

(2.1)

Transducer Gain  $(G_T) = P_{OUT} / P_{AVS}$ Power Gain  $(G_P) = P_{OUT} / P_{IN}$ Available Gain  $(G_A) = P_{AVO} / P_{AVS}$

Figure 7. Definition of power and gain

In RF applications, the power level, usually defined as dBm, has a decibel value on a reference of 0.001 Watt (0 dBm). Assuming a general RF block with 50-Ohm terminations for the input and output, the voltage level can be derived. For a 30 dBm PA with 0 dBm input power (a gain of 30 dB), the peak-to-peak voltage swing for the input and output are 0.632 V and 20 V, respectively. Since an air-interface is not easily defined as fixed impedance, using a power interpretation instead of a voltage interpretation is preferable. Moreover, a link budget for a communication should be defined as a unit of power for the calculation of the dynamic range [2, 6].

#### 2.2.1.2. Gain

The gain of the PA in Figure 7 can be defined as follows. Using the definitions given in the figure,

Transducer Gain

$$(G_T) = \frac{P_{OUT}}{P_{AVS}},$$

(2.2)

Power Gain

$$(G_P) = \frac{P_{OUT}}{P_{IN}} = G_T \left( 1 + \frac{P_{REFS}}{P_{IN}} \right),$$

(2.3)

Available Gain

$$(G_A) = \frac{P_{AVO}}{P_{AVS}} = G_T \left( 1 + \frac{P_{REFO}}{P_{OUT}} \right).$$

(2.4)

In the gain definitions of a PA, the transducer gain of Equation (2.2) is handily used for general measurements. The power gain of Equation (2.3) is the gain considering the input and output matching conditions. This definition is useful when the matching condition is not well optimized and the reflection at the input and load are not negligible, which is often observed in source/load-pull tests. If the reflection at the input of the PA is eliminated, the definition is the same with the transducer gain. Finally, the available gain of Equation (2.4) is useful for the estimation of the maximum performance assuming perfect matching conditions for the input and the load of the PA. In reality, however, this gain is not feasible due to the unwanted mismatch in implementation. By ignoring the reflection at the output of the PA, the gain can be interpreted as the transducer gain, shown in Equation (2.4).

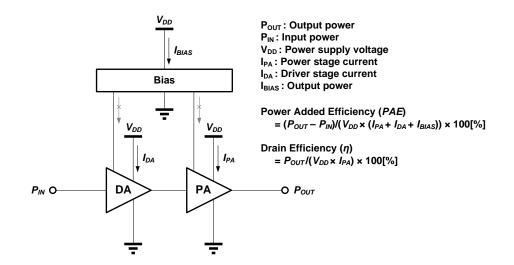

#### 2.2.1.3. *Efficiency*

To generate an output power, we need to supply energy that is higher than the required output power in advance. Since running a PA requires high current consumption, any careless control of the PA may cause power dissipation in the form of heat. While this is not a critical issue for fixed terminals, for mobile terminals with limited energy supplied by battery, the savings in current consumption would be critical for longer battery life and mobility. Thus, the efficiency of PAs is crucial to wireless applications. Even for fixed applications such as baseband station PAs, if the efficiency is too low, the heat generation by low efficiency may cause a problem with reliability.

For a typical PA, as shown in Figure 8, efficiency can be defined as the ratio between the output power and the sum of all supplied energy into the black box, including the input power and the DC supplied power. The most popular and accurate definition of an efficiency, referred to as power-added efficiency (PAE) is represented in Equation (2.5).

$$PAE = \frac{P_{OUT} - P_{IN}}{P_{DC}} = \left(1 - \frac{1}{G}\right) \cdot \frac{P_{OUT}}{V_{DD} \cdot (I_{PA} + I_{DA} + I_{BIAS})}$$

(2.5)

Figure 8. Efficiency calculation of a PA

Other definitions have been used for the same PA: in the case of field effect transistor (FET) circuits, it refers to drain efficiency (DE); and in the case of bipolar junction transistor (BJT) circuits, it refers to collector efficiency (CE). In this work, which assumes that all designs are FET circuits, only the term DE is used.

$$\eta(DE) = \frac{P_{OUT}}{P_{DC}} = \frac{P_{OUT}}{P_{DC} \cdot I_{PA}}$$

(2.6)

However, confusion may arise from this definition when dealing with a multi-stage PA in which more than one driver stage is used to drive the final stage. In some cases, DE is simply PAE without input power, but it includes driver current consumption. However, it is more intuitive to define DE as Equation (2.6), which includes only the drain bias current consumption. For a complete PA, the usage of DE can be misleading, because no information of gain is provided. If the gain is low, additional stages, which consume additional power, are needed to drive the final stage. Thus, this definition may be useful only for defining the quality of matching conditions for the output, but not for representing power consumption used for generating output power.

#### 2.2.2. Linearity

Linearity of a PA represents a criterion that represents how the quality of a given signal is maintained throughout the PA. However, myriad definitions and abbreviations for linearity specifications may confuse newcomers to this field who do not know which ones to use for characterization of linearity or how to interpret them. Specifically, the definition of linearity varies depending on viewpoints and modulation schemes.

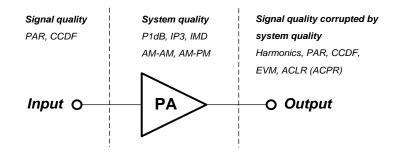

Figure 9. Linearity indicators of a PA

In Figure 9, the quality of a signal can be defined as a peak-to-average ratio (PAR) or a complimentary cumulative density function (CCDF). Moreover, the linearity of a system can be defined as a 1dB compression point (P1dB), a third-order intercept point (IP3), amplitude-amplitude modulation (AM-AM), amplitude-phase modulation (AM-PM), or third-order intermodulation distortion (IMD3). Such system qualities affect the quality of a signal, and the signal quality corrupted by the system quality can be defined by harmonics, PAR, CCDF, and the adjacent channel power ratio (ACPR), i.e., the adjacent channel leakage ratio (ACLR), error vector magnitude (EVM), and so on. Although the system qualities are not specified by communication standards, they are specifically defined in standards such that linear PAs should keep signals within a specified limit. The purpose of maintaining linearity is two-fold: to minimize signal distortion (PAR, CCDF, P1dB, AM-AM, AM-PM, EVM) so that users maintain good connectivity and to ensure co-existence with neighboring channels (harmonics, IP3, IMD, ACLR) so that other users can also maintain good connectivity.

#### 2.2.2.1. Harmonics, P1dB, IP3, and IMD

Equation (2.7) represents a polynomial expansion of the general PA model in Figure 10 truncated at the third-order term.

$$y(t) \approx \alpha_1 x(t) + \alpha_2 x(t)^2 + \alpha_3 x(t)^3$$

(2.7)

After input  $x(t) = A \cos \omega t$  is applied, then the system generates an output,

$$y(t) = \alpha_1 A \cos \omega t + \alpha_2 (A \cos \omega t)^2 + \alpha_3 (A \cos \omega t)^3$$

=  $\frac{1}{2} \alpha_2 A^2 + \left(\alpha_1 A + \frac{3}{4} \alpha_3 A^3\right) \cos \omega t + \frac{1}{2} \alpha_2 A^2 \cos 2\omega t + \frac{1}{4} \alpha_3 A^3 \cos 3\omega t$  (2.8)

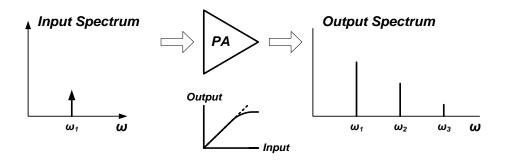

Figure 10. Distortion of a PA with one-tone input

The system generates higher-order harmonic components such as  $2\omega$  and  $3\omega$  as well as the fundamental frequency component at  $\omega$ . While the cause of harmonic generation is the nonlinearity of a PA, this specification is usually dealt with independently because it can be suppressed by filtering characteristics at the output. Thus, if we simply measure the harmonic levels, which designers have more freedom to control, at the output port [6], it can differ from the actual nonlinear performance of the PA.

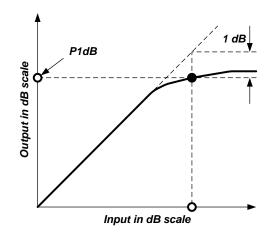

In the system, coefficient  $\alpha_3$  is assumed to be less than zero, or the system output expands with increased input to the system, violating a natural system in which new energy cannot be generated. Thus, with the increased input, the system suffers a compressive output. The point at which the original gain is compressed by 1 dB is defined as P1dB, illustrated in Figure 11, indicating a border between a reasonably linear region and a compression area.

Figure 11. 1dB compression point

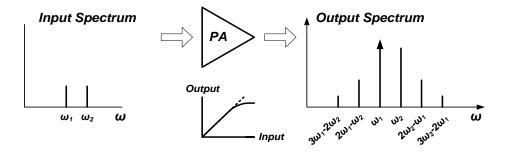

When two inputs with equal amplitudes are applied, as shown in Figure 12,  $x(t) = A \cos \omega_1 t + A \cos \omega_2 t$ , a different distortion mechanism, works through the same system,

such that not only harmonics but also inter-modulated signals appear very near the input frequency components at frequencies,  $2\omega_1 - \omega_2$ ,  $2\omega_2 - \omega_1$ ,  $3\omega_1 - 2\omega_2$ ,  $3\omega_2 - 2\omega_1$ , and so on.

$$y(t) = \left(\alpha_1 A + \frac{9}{4}\alpha_3 A^3\right)\cos\omega_1 t + \left(\alpha_1 A + \frac{9}{4}\alpha_3 A^3\right)\cos\omega_2 t + \frac{3}{4}\alpha_3 A^3\cos(2\omega_1 - \omega_2) t + \frac{3}{4}\alpha_3 A^3\cos(2\omega_2 - \omega_1) t + \cdots$$

(2.9)

Figure 12. Distortion of a PA with two-tone input

The generated third-order nonlinearities at frequencies  $2\omega_1 - \omega_2$  and  $2\omega_2 - \omega_1$  in Equation (2.9) are called IMD3. In Figure 12, as the input level increases, the intermodulation terms increase as well but follow a steeper slope (three times in IMD3 and in general, *n* times of the fundamental slope for IMD*n*, *n* = 2, 3, 4, ...), increases the fundamental level. At the imaginary intercept point at which the fundamental tone and the IMD*n* tone are equal, the *n*-th order intercept point (IP*n*, *n* = 2, 3, 4, ...) is defined in the black dot in the figure. The input and output of the point are called input *n*-th order intercept point (IIP*n*, *n* = 2, 3, 4, ...) is defined in the slack dot in the figure. The input and output *n*-th order intercept point (OIP*n*, *n* = 2, 3, 4, ...), respectively. Higher-order nonlinearities such as fifth-order intermodulation (IMD5) can also be generated at frequencies  $3\omega_1 - 2\omega_2$  and  $3\omega_2 - 2\omega_1$ , but the most

dominant intermodulation is still the third-order nonlinearities, so IMD3 and IP3 are usually used to indicate the linearity of a PA.

Figure 13. IP3 and IMD

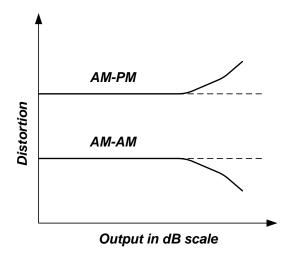

#### 2.2.2.2. *AM-AM and AM-PM*

AM-AM and AM-PM distortions represent the input-output relations of a PA excited by a sinusoidal input, depicted in Figure 14. AM-AM is distortion by the amplitude so that it has a strong connection with P1dB. However, this definition covers not only the compression by the P1dB but also the fluctuation of gain throughout the entire power range. In much the same way, the phase variation throughout the entire operational power range is quantified by AM-PM distortion. The quantities acquired by AM-AM and AM-PM are useful for characterizing EVM, in which distortions caused by the amplitude and the phase hinder the identification of the right constellation points. However, they are not very critical to the estimation of ACLR characteristics to which distinct frequency components generated by PA distortion are more relevant.

Figure 14. AM-AM and AM-PM distortion

# 2.2.2.3. *PAR and CCDF*

From the point of signal quality in a two-tone input test, the input can be rephrased as follows:

$$x(t) = A\cos\omega_1 t + A\cos\omega_2 t = 2A \cdot \cos\left(\frac{\omega_1 + \omega_2}{2}t\right) \cdot \cos\left(\frac{\omega_1 - \omega_2}{2}t\right), \quad (2.9)$$

$$P_{PEAK} = \left(\frac{2A}{\sqrt{2}}\right)^2 = 2A^2,$$

(2.10)

$$P_{AVG} = 2\left(\frac{A}{\sqrt{2}}\right)^2 = A^2,$$

(2.11)

$$P_{TONE} = \left(\frac{A}{\sqrt{2}}\right)^2 = \frac{A^2}{2}.$$

(2.12)

Thus, the ratio between the peak input signal over the average signal can be defined as PAR.

$$PAR \equiv 10 \log\left(\frac{P_{PEAK}}{P_{AVG}}\right) = 3 dB$$

(2.13)

For a linear operation without distortion, the input signal into the PA should be limited to a signal excursion equivalent to PAR at the output. Therefore, to guarantee that no distortion occurs, each tone of the two-tone test should be defined at the power back-off of 6 dB from the peak output power [6].

Back-off

$$\equiv 10 \log \left(\frac{P_{PEAK}}{P_{TONE}}\right) = 6 \, \mathrm{dB}$$

(2.14)

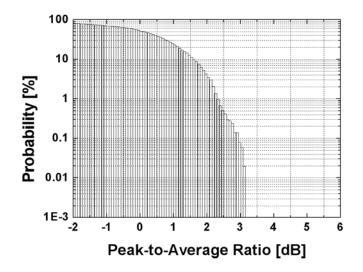

Digital modulations usually have statistical signal distribution showing dynamic behaviors according to modulation that differs from static linearity [7]. While either the one- or two-tone signal characterization of linearity can provide an intuitive understanding of linearity simplifying the relationship between the input and output, an accurate characterization of linearity can be attained only by including the dynamics of a modulated signal. Therefore, the definition of PAR for digital modulations cannot be derived from simple derivations, and only statistical accumulation of data can provide these definitions.

CCDF indicates that the PAR of a digital communication reflects the statistical distribution of signal amplitude. As represented in Equation (2.15), the probability density function (PDF) of a signal is determined by the low power level of the signal, resulting in a cumulative density function (CDF), which is depicted in a complimentary fashion that emphasizes the peak amplitude area. As an illustration, Figure 15 shows the CCDF of a digitally-modulated signal that has the PAR of 3.2 dB.

$$CCDF \equiv 1 - \int PDF(P) \cdot dP$$

(2.15)

where *P* represents the instantaneous power of a PA. Depending on modulation format, CCDF curves vary for different communication standards. A signal with a high CCDF near peak output range suffers more from distortion.

Figure 15. CCDF of a digitally modulated signal

Although PAR and CCDF determine the quality of a general signal, the signal can be distorted through a PA, which causes the PA to undergo amplitude compression; then the PAR and CCDF values may decrease. Thus, PA designers should maintain a sufficient signal excursion margin to minimize any reduction in these two linearity indicators.

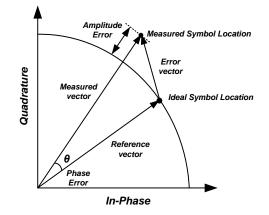

#### 2.2.2.4. *EVM and ACLR*

EVM is a metric of modulation or demodulation accuracy in a transmitting chain. Digital modulation requires a constellation diagram to identify each data point. Figure 16 shows that the ideal symbol location is often displaced by amplitude and phase error through a transmitting chain, and the measured symbol location is found in a different location by an amount of an error vector. The following calculated EVM Equations (2.16) and (2.17) can be formulation on either in a dB scale or a percent scale.

$$EVM(dB) \equiv 10 \log\left(\frac{Error vector}{Reference vector}\right)$$

(2.16)

$$EVM(\%) \equiv \sqrt{\frac{Error \, vector}{Reference \, vector}} \times 100(\%)$$

(2.17)

Figure 16. Error vector of symbols

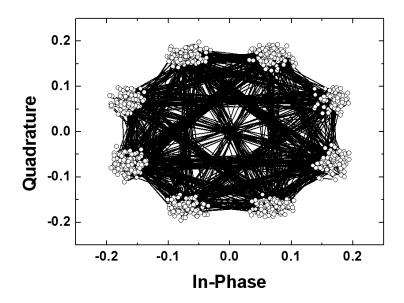

Figure 17 illustrates a constellation diagram in which a digitally-modulated signal is plotted. The white circles in the figure represent a data point with errors, and the lines between the white circles represent the movement of the amplitude information. As the group of white circles expands, the percentage vector displacement represented by EVM also degrades, increasing the likelihood that it will be incorrectly interpreted as a different data point.

Figure 17. EVM of a digitally-modulated signal

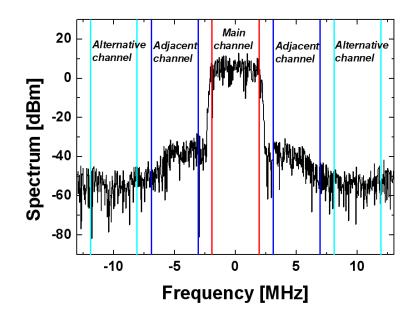

Another metric for linearity in digital communication is ACLR, which follows:

$$ACLR (dBc) \equiv 10 \log \left( \frac{Power in Adjacent or Alternative Channel in Watt}{Power in Main Channel in Watt} \right)$$

(2.18)

Intermodulation by the transmitter odd-order nonlinearities widens the signal spectrum, shown in Figure 18. A general term for this phenomenon is "spectral regrowth." The power of spectral regrowth in the adjacent channel acts as interference for other users in the cell using this channel.

Channel power adjacent to the main channel power is referred to as the "adjacent channel leakage ratio" while the channel power neighboring the adjacent channel is referred to as the "alternative channel leakage ratio" for the same abbreviation—ACLR.

Figure 18. ACLR of a digitally-modulated signal

While the definitions of EVM and ACLR are generally described in this section, the exact values are defined only by each standard characteristic. Since the two metrics are based on different nonlinearity mechanisms, the exact relationship between them cannot easily be identified.

#### 2.2.3. Other Characteristics

#### 2.2.3.1. Stability and Ruggedness

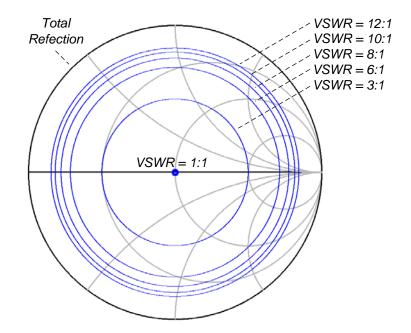

The usage environment of a general mobile terminal is very unpredictable due to the electromagnetic absorption or reflection of human bodies and other structures near the antenna of the mobile terminals. Thus, the usable range in such an environment, or mismatch, should be defined. VSWR is a measure of mismatch from the point of voltage reflection. In general cases, for low VSWR (e.g., less than 6:1), it is defined as the

guarantee of stability such that the PA is within a normal operating range. For high VSWR (e.g., about 10:1), it is defined as ruggedness that guarantees no damage to the PA, even in a high reflection environment.

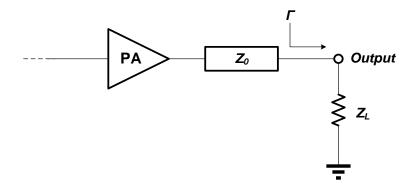

In Figure 19, the general reflection coefficient and the voltage standing wave ratio (VSWR) of a load can be defined as Equations (2.19) and (2.20), respectively.

$$\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0}$$

(2.19)

$$VSWR = \frac{1 + |\Gamma|}{1 - |\Gamma|}$$

(2.20)

Figure 19. Reflection at output node.

By combining Equations (2.21) and (2.22), the load with a constant reflection coefficient can be summarized as Equation (2.23):

$$|\Gamma| = \frac{VSWR - 1}{VSWR + 1},\tag{2.21}$$

$$\Gamma = \left| \frac{VSWR - 1}{VSWR + 1} \right| e^{j\theta}, \qquad (2.22)$$

$$Z_L = \left[ \frac{1 + \frac{VSWR - 1}{VSWR + 1} e^{j\varphi}}{1 - \frac{VSWR - 1}{VSWR + 1} e^{j\varphi}} \right] \cdot Z_0, \qquad (2.23)$$

where  $\theta$  represents the phase of  $\Gamma$ , and  $\varphi$  is the angle of VSWR. With  $\varphi$  in a range of 0 to  $2\pi$  radians, constant VSWR circles for some VSWR values can be plotted, depicted in Figure 20. As can be seen in the figure, the perfect matching point can be found at VSWR = 1:1, and the VSWR = 3:1 circle indicates the area in which half of the incident power is reflected at the load. The VSWR circle close to 10:1 is already close to the outer border of the Smith chart, indicating that most of the power will be reflected at the load.

Figure 20. Constant VSWR circles in the Smith chart

For a varying load, PAs should be stable; that is, they should generate neither spurious signals nor oscillation throughout the whole frequency band of interest. Stability is measured by the Rollet stability factor, can be defined in the following Equation (2.24) [8], [9] for any two-terminal device:

$$K \equiv \frac{1 + |\Delta|^2 - |S_{11}|^2 - |S_{22}|^2}{2|S_{21}||S_{12}|}$$

(2.24)

where  $\Delta = S_{11}S_{22} - S_{12}S_{21}$ , and K > 1 and  $\Delta > 0$  should be satisfied for unconditional stability.

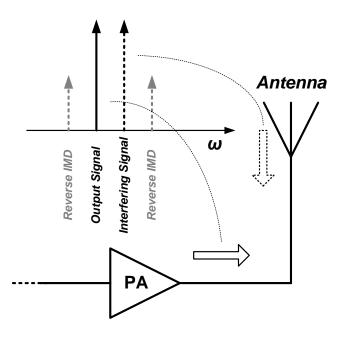

#### 2.2.3.2. Reverse Intermodulation Product

When a transmitting signal and an interfering signal from a co-located transmitter, which conducts back from an air-interface, are intermodulated at a PA output, a new distortion, shown in Figure 21, is generated. This IMD product, unlike the IMD product caused by the PA distortion, is called the "reverse intermodulation product." By adding an isolator after the PA, this IMD distortion can be suppressed. The measurement method for this phenomenon is described in detail in Section 2.5 of this chapter.

Figure 21. Reverse IMD generation

#### 2.2.3.3. Idle Current

The quantity of an idle current is defined for linear applications. In case of a timedivision duplexing (TDD) system, the transmitter of the system goes into an off state consuming no current. However, in a frequency-division duplexing (FDD) system, in which the transmitter should be ready to send a signal at all times, the PA in the system draws an idle current. Often this quantity is also called a "quiescent current." Since a quiescent current involves power dissipation that does not entail sending information, such unnecessary power dissipation should be suppressed as much as possible. If the idle state is statistically very long compared to the communication time, most of the battery power is simply wasted while the transmitter is waiting for usage.

$$I_{AVG} = T_{ON} \cdot I_{ON} + (1 - T_{ON}) \cdot I_{IDLE}$$

(2.25)

$$P_{AVG} = V_{DD} \cdot I_{AVG} \tag{2.26}$$

where

$I_{AVG}$  = Average current drain.

$T_{ON}$  = Fraction of time the PA is on.

$I_{ON}$  = Current drain from the battery when the PA is on.

$I_{IDLE}$  = Current drain from the battery when the PA is on standby.

$P_{AVG}$  = Average power consumption.

# 2.3. Wireless Standards

Among the many wireless standards, the most popular ones in the market that describe the specifications related to the design of PAs are introduced in this section. For 2G communications, the global system for mobile communications, used mostly for

voice communication is also described; and for 3G mobile communications, wideband code division multiple access, and specifically for dedicated data communications in 3G communications, WLAN and WiMAX standards are briefly introduced.

#### 2.3.1. Global System for Mobile Communications

Before GMS appeared in the market in the early 1990s, analog cellular communications such as advanced mobile phone service (AMPS) or Nordic mobile telephone (NMT) service, both introduced around 1980, were available. Evolving throughout the decades, GSM highlighted the need for and popularity of digital communication. Despite the advancement of new standards, GSM is currently the most popular cellular communication standard worldwide. The GSM standard is based on Gaussian minimum shift keying (GMSK) modulation in which time-division multiple access (TDMA) is used for user capacity in which one frame must be divided into eight slots. For a higher data rate, multiple slots can be assigned to one user, referred to as the "general packet radio system" (GPRS). By distinguishing the transmitting and receiving frequency bands, it is categorized as FDD, but instead of a duplexer at the antenna port, an RF switch can be used, owing to the nature of TDMA.

The design of a GSM PA does not demand a linearity requirement, so only output power and PAE are key design specifications to meet. High efficiency is the most important design target for this standard. The key specifications of GSM PAs are summarized in Table 2. Since the PA is turned on and off for each time slot, the PA should meet not only a spectral mask but also a time domain mask. The control of GSM PA is by a control port, not by input power requiring a good analog bias circuitry.

| Specification              | Value           |  |  |

|----------------------------|-----------------|--|--|

|                            | 824-849 MHz     |  |  |

| Operating frequency        | 880-915 MHz     |  |  |

|                            | 1710-1780 MHz   |  |  |

|                            | 1850-1910 MHz   |  |  |

| Transmission rate          | 270.833 kbps    |  |  |

| Maximum output power       | +33 dBm-+35 dBm |  |  |

| PAE @ Maximum output power | ~50%            |  |  |

#### Table 2. Commercial GSM PA specifications

#### 2.3.2. Wideband Code Division Multiple Access

Wideband CDMA is a standard for "3GPP" (Third Generation Partnership project), the so-called "UMTS" (Universal Mobile Telecommunications System), targeting high-speed mobile data communications over simple voice communications. A typical data rate is 3.84 Mbps, but by reducing a spreading factor in a high-speed download packet access (HSDPA), a higher data rate up to 14 Mbps is also possible. In the case of WCDMA PAs, the required specifications for class 3 (24 dBm output power at antenna port) are listed in Table 3. The usual products in the market deliver an output power of 28 dBm, a PAE of 40% and an ACLR of -40 dBc at 5 MHz offset [10], [11] while the standard specification is -33 dBc at this offset. ACLR at 10 MHz offset should be less than -43 dBc.

Using the minimum transmit power of -50dBm required for all power classes, it can say that a class 1 mobile station has a transmit power dynamic range of -50 dBm to +33 dBm, producing a total dynamic range of 83dB [12].

| Specification                     | Value                     |

|-----------------------------------|---------------------------|

| Operating frequency               | 1.92-1.98 GHz             |

| Bandwidth                         | 5 MHz                     |

| Chip rate                         | 3.84 Mcps                 |

| Maximum output power (class 3)    | +27 dBm - +28.5 dBm       |

| Dynamic range (class 3)           | 78 dB (-50 dBm - +28 dBm) |

| PAE @ Maximum linear output power | ~ 40%                     |

| ACLR (3.84 MHz integration)       | < -40 dBc @ 5 MHz offset  |

| NeLA (5.64 MHZ Integration)       | < -50 dBc @ 10 MHz offset |

| EVM                               | < 2.5%                    |

#### Table 3. Commercial WCDMA PA specifications

# 2.3.3. Wireless Local Area Network and Worldwide Interoperability for Microwave Access

Ever-increasing demands for a high data rate have not been successfully satisfied by mobile standards such as GSM, GPRS, EDGE, CDMA, and WCDMA. While the mobility of the standards is lower than those listed as mobile standards, an increased data rate could successfully be realized by WLAN and WiMAX due to their orthogonal frequency division multiplexing (OFDM) based on IEEE standards 802.11 and 802.16, respectively. In this multiplexing scheme, a set of carriers located individually and independently in close proximity allows frequency diversity.

Table 4 lists some commercial specifications of IEEE 802.11g.

So far, an IEEE 802.11 WLAN is considered the most suitable application for the CMOS PA. Since this application is operated at a comparably low power level with a low voltage swing, the burden of reliability and ruggedness is significantly reduced. In addition, the time division duplexing (TDD) mode of the 802.11 WLAN helps integration

with the transceiver since a TDD-based system does not concurrently operate both the receiver and transmitter parts. This confines the substrate coupling problem to the transmitter only [13].

| Specifications                  | Value                      |  |  |

|---------------------------------|----------------------------|--|--|

| Frequency band                  | 2.4-2.4835 GHz             |  |  |

| Number of carriers              | 52 (48 data and 4 pilots)  |  |  |

| Channel bandwidth               | 16.25 MHz                  |  |  |

| Data rate                       | 6 to 54 Mbps               |  |  |

| Carrier type                    | OFDM                       |  |  |

| Modulation                      | BPSK, QPSK, 16QAM or 64QAM |  |  |

| Max. instantaneous output power | 1 W (in USA)               |  |  |

| EVM                             | 2-3% or -25dB for 54 Mbps  |  |  |

|                                 | -20 dBc @ 11MHz offset     |  |  |

| Spectrum mask                   | -28 dBc @ 20MHz offset     |  |  |

|                                 | -40 dBc @ 30MHz offset     |  |  |

Table 4. 802.11g WLAN transmitter specifications

# 2.4. Design of RF Power Amplifiers

#### 2.4.1. Design Procedure

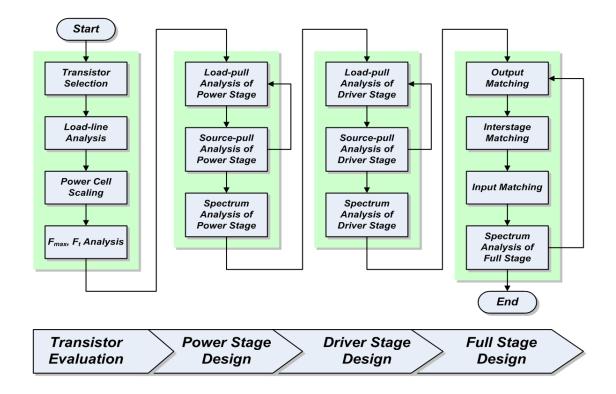

In the design of a PA with given specifications, a systematic approach can be helpful, so this research proposes the following design procedure. The first step of the procedure is to evaluate the transistor in light of the available semiconductor solutions and then to check the transistor characteristics from the perspective of the loadline, the determination of size, and finally the characteristics of a given size. The next step is to design a power stage in which both load-pull and source-pull analyses are repeated until the design optimization for output power, efficiency, and sometimes even linearity are complete. The final step is to evaluate the spectrum performance of the power stage. The same procedure can be applied to the driver stage. By securing the designed power stage and the driver stage, a complete PA that focuses on the output matching, interstage matching, and input matching can be designed. Since the performance should be optimized, even though each block is already characterized well, all design parameters should be readdressed from the perspective of the full stage design. Since all specifications are in trade-off relations, designers are required to spend considerable time optimizing and repeating the same procedure until all the specifications have sufficient margins.

Figure 22. General design procedure of a PA

In the abstract, this suggested design procedure is simple and clear. However, the actual design procedure often encounters more obstacles than expected, so designers should be prepared for long, tedious optimization procedure. Often, designers fall in a quagmire of going back-and-forth among all the trade-off relations that have deviated from the measured steps. Furthermore, the design procedure can vary according to different class operations. For example, if a class-E PA is designed, the required output impedance can be intentionally manipulated without regard to the optimal load-pull result. Such general guidelines can be helpful but not always the best approach for designers to take.

#### 2.4.2. Simulation Techniques

The characterization of RF PAs for digital communications requires computerassisted tools for calculating complicated signals. While transient analysis works in the time domain, harmonic balance, or Volterra series analysis, works in the frequency domain. To include the advantages of both domains, envelope simulation runs in the time domain and at each time point, harmonic simulation in the frequency domain works [14].

#### 2.4.2.1. Transient Analysis

Transient analysis is not easily applicable to digital domain signals, particularly for data-spreading spectrum techniques in which the PN code division of signals requires an impractically short time step. More importantly, the signal in the time domain should be converted to the frequency domain at a cost of the fast Fourier transformer (FFT) consuming computational time. Thus, this technique is rarely used in the design of a PA.

When the PA includes time-step input, the transient response of the PA can be checked for stability and settling time.

#### 2.4.2.2. Harmonic Balance Analysis

While harmonic balance (HB) is considered a technique in the frequency domain, it is a hybrid between the time and frequency domains. While the latter deals with the linear part of a signal, the former deals with the nonlinear part. This technique is applicable to strongly nonlinear systems with time-invariant coefficients for a Fourier series, representing only periodic and quasi-periodic responses. By simplifying a digitallymodulated signal with a few tones, it is widely used for RF simulation, including very nonlinear voltage-controlled oscillators (VCOs) and PAs. Some simulation techniques such as large signal S-parameter (LSSP) simulation or envelope simulation are also based on the HB. Since HB also consumes considerable computation time and memory, the smart matrix manipulation technique such as the Krylov solver has been widely adopted as an option. The phase information of each tone in HB should match to that of the envelope for an accurate modeling of digital signals.

#### 2.4.2.3. Volterra Series Analysis

Like HB, Volterra analysis also uses a multi-tone signal in a system expanded by the Volterra series, in which the memory effect of PAs is also included. It is good for a weakly nonlinear system below P1dB. Since most linear PAs are operated in the back-off region below P1dB, this technique is useful for a linear PA design.

#### 2.4.2.4. Envelope Analysis

Standard HB cannot handle a circuit with digitally-modulated signals or a multiple time-scale signal. Instead, in envelope analysis, different time rates are used for the sampling of the circuit variables [15]. By using time-variant phasors, this analytical technique can efficiently simulate complex regimes at low computational cost. Digitally-modulated signals can be modeled by one carrier with a time-varying complex envelope. Following the time step, the circuit is analyzed using single-tone HB, which calculates the instantaneous envelope at the point. Then another HB is executed during the next time step with the interval decided by the envelope bandwidth [14].

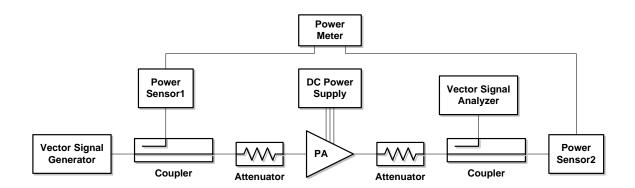

## **2.5.** Measurement of RF Power Amplifiers

The measurement setup of a PA requires a vector signal generator, a vector signal analyzer or a spectrum analyzer, a power meter, and several power suppliers. Attenuators for the input and output of the PA can help reduce reflection by mismatch. Since the allowable input power for the vector signal analyzer is usually less than 1 Watt, use of coupled output, shown in Figure 23, is recommended. While the loss is represented in dB (the power has a unit of dBm), it is often overlooked that the same 0.1 dB difference is actually a huge difference for peak output power and back-off output power. Therefore, the measurement setup must be calibrated with a particular focus on the output side, on which a slight calibration error could cause a significant percentage of efficiency miscalculation.

Figure 23. Measurement setup of a PA

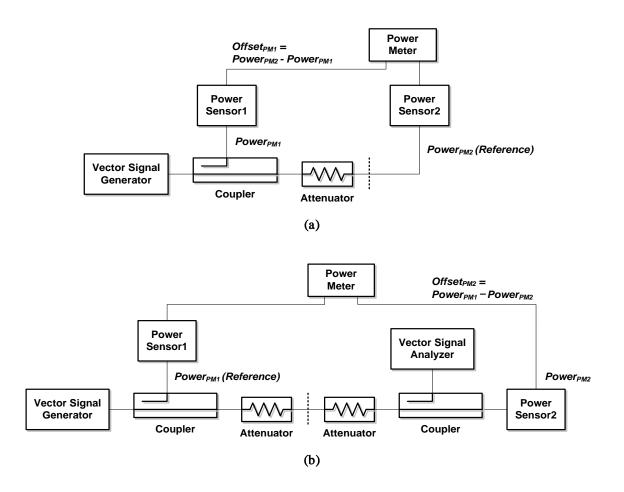

To minimize the error of the output power measurement, we must assure a power calibration condition. The calibration process, in which a power meter must have at least two independent sensors and readers or two separate power meters, consists of several steps. The first is to calculate the input offset for the first power meter by reading the power difference for the input part of the measurement setup. The next is to operate the measurement setup without a PA using a through component and then to record the difference as the offset of the second power meter. Figure 24 shows the setups for the calculation of offsets at the input and output, respectively, based on Equations (2.28) and (2.29).

$$Offset_{PM1} = Power_{PM2} - Power_{PM1}$$

(2.28)

$$Offset_{PM2} = Power_{PM1} - Power_{PM2}$$

(2.29)

Figure 24. Calibration procedure for a PA measurement setup: (a) offset calculation of input and (b) offset calculation of output

Figure 25 shows a typical source/load-pull setup for VSWR measurement. Under mismatched conditions, the operation of the PA is performed by controlling two tuners. A mismatch affects the load conditions of the matching network, causing the performance of the PA to deteriorate due to abnormal stress. Thus, in the evaluation process, such extreme cases should be verified as described in the previous section on VSWR specifications.

Figure 25. Source/load-pull setup

Figure 26 shows the setup for reverse IMD measurement. The figure shows that the two generators are used both at the input and output of the PA and that the IMD is measured at the output. The underlying mechanism of reverse IMD is briefly discussed in the previous section.

Figure 26. Reverse IMD test set up

## 2.6. Conclusion

This chapter provided general information that explains the design of RF PAs. The key quantities used to characterize a PA are output power, gain, efficiency, linearity, and so on. Each parameter has several different definitions according to a perspective within which the PA has been understood. In particular, the indicators of linearity can vary according to different standards and viewpoints, so the definitions of linearity such as P1dB, IP3, IMD, ACLR, and EVM can be selectively used for various digital standards. Once a standard is chosen as a target for PA design, proper design procedures and simulation techniques are used. For PA design, most design efforts go into the output matching of the last stage for maximum output and efficiency generation with high linearity. Estimating the correct behavior of PAs also entails the appropriate selection of a simulation tool from among the many time and frequency domain techniques. Accordingly, measurement setups for various PA specifications should also be properly understood and prepared to retrieve the accurate characteristics of a measured PA.

# **CHAPTER 3**

# CHALLENGES AND TECHNIQUES OF CMOS RF Power Amplifiers

# 3.1 Introduction

Designing PAs is often considered a very special field distinctive from other RF block designs because of the lack of well characterized models for large signal operations and high voltage and current stress. Thus, designers often rely more on their experience than simulation results when they characterize PAs. Moreover, guaranteeing a reliable operation is as important as achieving good performances such as high output power, high efficiency, and high linearity. In addition to these design difficulties of general PAs, a CMOS PAs are even harder to design. While CMOS technology is welcomed because of its cost-effective material and great versatility, as mentioned in Chapter I, the commercialization of CMOS PAs has not been easily achieved due to the intrinsic drawbacks of standard CMOS processes from RF perspectives: a low-quality factor (Q), the lossy substrate of passive structures, low breakdown voltage, and low transconductance of active devices. Thus, many efforts, including the development of high power generation techniques, linearity enhancement techniques, and efficiency enhancement techniques, have focused on overcoming the drawbacks of CMOS technology for PA designs. Thus, Section 3.2, introduces the structure and the difficulties of designing PAs. Section 3.3 follows with a discussion of the challenges of CMOS

technology in the design of PAs. In response to the challenges outlined in the previous sections, Section 3.4 introduces several state-of-art performance enhancement techniques for CMOS PAs.

# 3.2 General Issues in Designing RF Power Amplifiers

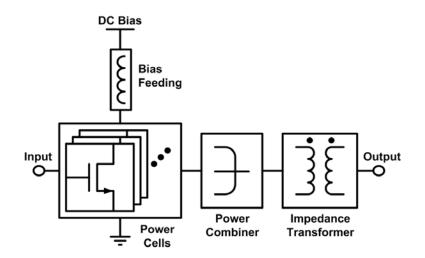

As shown in Figure 27, a PA consists of four important blocks: an active block that consists of power cells and three passive blocks that comprise bias feeding for the DC current, power combiners, and impedance transformers. Since the passive blocks usually contain inductive characteristics, they can be combined functionally.

Figure 27. Block diagram of the PA output network