## HARDWARE/SOFTWARE DEADLOCK DETECTION ALGORITHM AND IMPLEMENTATION

# $\begin{array}{c} \text{GIT-CC-02-46} \\ \text{SEPTEMBER 4, 2002} \end{array}$

#### PUN HANG SHIU

ABSTRACT. This report introduces a new theorem and its proof about the problem of deadlock detection. First, we examine how to represent the problem of deadlock with a directed graph. Then, translation from a directed graph into a matrix is elaborated. The theorem and its proof are based on this matrix representation. By applying this theorem, we present a novel parallel deadlock detection algorithm, which we hypothesize has a run-time complexity of  $O_{hw}(\min(m,n))$  in a parallel hardware implementation, where m, n are the number of processors and resources involved in deadlock detection respectively.

#### 1. The Deadlock Problem

Deadlock[1] is a system state when processors are waiting for resources held by other processors which, in turn, are also waiting for some resources held by the previous processors.

**Example 1.** We have two processors  $p_1$  and  $p_2$ . In addition, we have two resources  $q_1$  and  $q_2$ . Processor  $p_1$  is holding a resource  $q_1$  and makes a new request of resource  $q_2$ . At the same time, another processor  $p_2$  is holding  $q_2$  and makes a new request for resource  $q_1$ . Processor  $p_1$  needs both resources  $q_1$  and  $q_2$  to complete its task, thus processor  $p_1$  will not release resource  $q_1$  unless processor  $p_1$  obtains the resource  $q_2$ . The converse is true for processor  $p_2$ :  $p_2$  needs both resources  $q_1$  and  $q_2$  to proceed in its program before releasing any resource. Therefore, both  $p_1$  and  $p_2$  are waiting for a never-released resource from each other. At the end, neither processor  $p_1$  nor  $p_2$  are performing any useful work at all.

The situation of a system being in deadlock is also called a **deadlock state**[1]. In general, a "processor" can be any entity capable of requesting a resource; in this technical report, however, we will use "processor" to refer to either a standard Von Neumann style processor or to custom VLSI hardware able to request other hardware (or, in some cases, software) resources. A system in a deadlock state

1

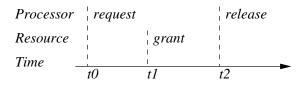

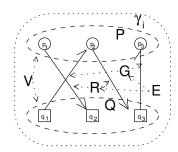

Figure 1. Some Terms

does not perform useful work because processors are blocked from either competing for other resources or communicating with other processors.

Resources can be classified into two groups. A **consumable resource** is characterized by (1) no fixed total number of units (units can be created or destroyed), (2) when the processor finishes using the acquired resource, the resource ceases to exist, and (3) an unblocked processor of the resource may release any number of units. These units then become immediately available to requesting processors. An example of a consumable resource is a message. A **reusable resource** is characterized by (1) fixed total inventory (units are neither created nor destroyed) and (2) units are requested and acquired by processors from a pool of available units. When the processor finishes using the acquired reusable resource, the resource is returned to the resource pool so that other processors can have a chance to use the resource. Note that in this technical report, we only consider reusable resources. Therefore, all further references to "resource" should be read as "reusable resource." The number of reusable resources can be classified into two classes. The first class is a **multiple-resource system** and has resources that have multiple units per resource type. The second class is a **single-resource system** and has resources that have one unit per resource type. This report will focus on a reusable single-resource systems which, we predict, will be commonly found in future System-on-a-Chip (SoC) designs.

In general, a system assumes the following guidelines when sharing resources among processors: (1) a processor must request a resource before using it; (2) a processor cannot proceed to use the resource until the processor's request is granted; (3) a processor must release the resource when the processor finishes using the resource; and (4) a processor may request as many resources as it likes as long as the requests do not exceed the total number of available resources.

From the hardware point of view, all the resources and processors are known to the system. Before using any resources exclusively, a processor must first ask for permission to obtain exclusive access to a particular resource. A processor is allowed to access a resource only after permission is given. A processor can give up the right of exclusive access to a particular resource by releasing the resource. In

Figure 1, there are three time stamps: t0, t1, and t2. The initial request for a resource begins at time t0. The resource is first granted at time t1. The moment of giving up exclusive access to the resource is time t2. The period from t0 to t1 is called **request**. The period from t1 to t2 is called grant of usage or **grant**.

From an Operating System (OS) point of view, request is an OS kernel routine, which enables processors to obtain shared resources. Also, the OS can keep track of availabilities of resources. Following the previously stated guidelines, a processor requests a resource and the OS schedules the resource to be given to the processor. When a processor requests a busy resource, the processor is constantly waiting for the busy resource to be assigned to the processor. During this time, the processor is unable to execute important task(s) which require the resource in order to be executed. During such a waiting period, we say that the processor is blocked. On the other hand, if the requested resource is available, a grant routine is called to update the resource allocation data structure internal to the operating system. Once the grant routine is completed, the processor can execute tasks requiring the obtained resource. Another OS kernel routine is release; release explicitly terminates the exclusive access of a shared resource.

#### 1.1. Motivation.

In a System-on-a-Chip (SoC), there may be several processors or processing elements on a single chip. Besides processing elements, there are also a lot of hardware units for various functions, such as telecommunication functions, image processing, and special hardware accelerators. deadlock detection in hardware will also enhance hardware/software debugging. Each processing element can have a different policy of using resources to meet a specific requirement.

Development of a real-time System-on-a-Chip (SoC) demands a deterministic and fast Real-Time Operating System (RTOS), which provides services and manages resources between software and hardware. However, the algorithms implementing RTOS services may be non-deterministic or may have long execution times. Since the RTOS also competes for the shared CPU on which the RTOS executes, RTOS services may be even less deterministic. For real-time systems, optimization beyond assembly code is desired, such as a custom hardware unit similar to FASTCHART[8]. Therefore, implementing deadlock detection in hardware can provide a better alternative which not only reduces the load of a shared CPU but also improves determinism of the overall SoC system.

Furthermore, moving deadlock detection out of the RTOS and into custom hardware gives more bandwidth to the rest of the RTOS services, allowing the RTOS to handle more services with faster run time, more concurrency, and better utilization of the underlying SoC.

Note that in the previous section we could have discussed a specific task on each processor which requests the resource(s); however, given our target architecture, we focus on a coarse level of granularity where we represent the request as coming from the processor, even though a specific task or set of tasks on the processor requires the resource(s).

### 1.2. Organization.

This report is organized as follows. A graph model applicable to deadlock detection is introduced in Section 2. Deadlock definition and properties are discussed in Section 3. A theorem and novel algorithm for parallel deadlock detection is presented in Section 4. Finally, this report is closed with an conclusion in Section 5.

#### 2. Graph Models

Before proceeding further to apply graph theory to a deadlock problem, basic terms are introduced next and then some properties are pointed out.

#### 2.1. Definitions of the Resource Allocation Graph.

**Definition 1.** Let  $P = \{p_1, p_2, \dots, p_m\}$  be a set of m requesters or processors which may request and/or hold a number of resources at any time.

If a processor needs to use a resource, the processor has to make a request first. Once a request is acknowledged by a grant, the processor can then safely use the resource exclusively.

**Definition 2.** Let  $Q = \{q_1, q_2, \dots, q_n\}$  be a set of n resources which provide a specific functions usable by the processors. Each resource  $q_i$  can serve only one processor at any given time.

Processors can obtain resources dynamically. Such an interaction between a processor and a resource is carried out by requests (Definition 3), grants (Definition 4), and release routines, which are denoted by various types of edges (except the releases, which only remove grant edges.).

**Definition 3.** Let R be the set of request edges. Let an ordered pair  $(p_i, q_j)$  be a request edge, where the first node is a processor  $p_i \in P$  and the second node is a resource  $q_j \in Q$ . Thus a set of request edges R can be written as follows:

$$R = \{(p_i, q_j) | | i \in \{1, 2, 3, \dots, m\}, j \in \{1, 2, 3, \dots, n\}, \text{ and processor } p_i \text{ is requesting resource } q_j\}.$$

An ordered pair  $(p_i, q_j)$  can also be represented by  $p_i \to q_j$ , where the arrow represents a request edge. Another notation for a request edge is  $r_{ij}$ , where the first index represents the processor  $p_i$  and the second index represents the resource  $q_i$ .

These three notations are used to facilitate interpretation. Notation  $(p_i, q_j)$  is used in a graph or set expression. Notation  $p_i \to q_j$  is used in diagrams illustrations. and square represents  $p_i$  and  $q_j$  respectively. Notation  $r_{ij}$  is used in a table or matrix, where the subindex ij is implicitly understood as determined by the location of r in row i and column j.

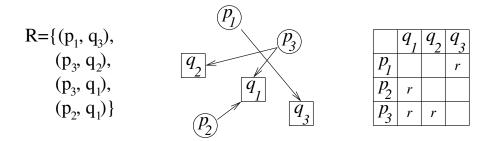

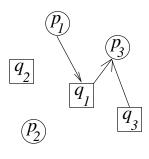

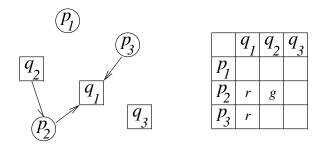

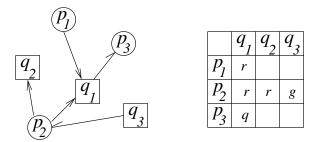

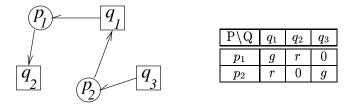

**Example 2.** Consider Figure 2. Processor  $p_2$  makes one request of resource  $q_1$ . This request is represented by an edge  $(p_2, q_1)$  in set R, arrow  $p_1 \to q_2$  shown in the graph of Figure 2, and  $r_{21}$  in the matrix on the right hand side of Figure 2. Note that  $r_{21}$  is the r located in row 2, column 1. Processor  $p_1$  makes one request of resource  $q_3$ . Such request is represented by an edge  $(p_1, q_3)$  in set R and by r in row 1, column 3 of the matrix. Processor  $p_3$  makes two requests of resource  $q_1$  and  $q_2$ . Such requests are represented by two edges  $(p_3, q_1)$  and  $(p_3, q_2)$  in the request set R, arrows in the graph of Figure 2, and r entries in the matrix of Figure 2. The final resulting request set R is also shown in Figure 2.

Figure 2. Example of Request

**Definition 4.** Let G be a set of grant edges. Let an ordered pair  $(q_j, p_i)$  be a grant edge, where the first node is a resource and the second node is a processor. Thus a set of grant edges G can be written as  $G = \{(q_j, p_i), \text{ such that } i \in \{1, 2, 3, ..., m\}$  and  $j \in \{1, 2, 3, ..., n\}\}$ . An ordered pair  $(q_j, p_i)$  can

also be represented by a  $p_i \leftarrow q_j$ , where the harpoon " $\leftarrow$ " represents a grant edge. Another notation is  $g_{ij}$ , where the first index represents the processor  $p_i$  and the second index represents the resource  $q_j$ .  $G = \{(q_j, p_i) \mid q \in Q \land p \in P \land (p, q) \notin R\}$

Several notations are used to facilitate interpretation. Notation  $(q_j, p_i)$  is used in graph or set expression. Notation  $p_i \leftarrow q_j$  is used in diagrams or figures illustration. Notation  $g_{ij}$  is used in a table or a matrix.

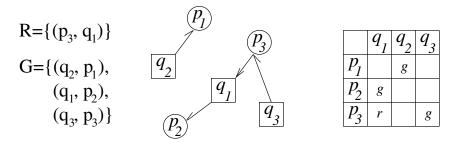

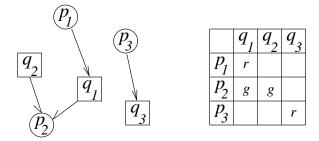

Figure 3. Example of Grant and Request edges

**Example 3.** Consider Figure 3. Resource  $q_1$  is granted to processor  $p_2$ . This case is represented by  $(q_1, p_2)$  in set G or  $g_{21}$  in the matrix (i.e., entry g in row 2, column 1 of the matrix in Figure 3). Resource  $q_2$  is granted to processor  $p_1$ ; this grant is represented by  $(q_2, p_1)$  in set G, a harpoon arrow in the graph of Figure 3, and g in row 1, column 2 of the matrix in Figure 3. Resource  $q_3$  is granted to processor  $p_3$ . Resource  $q_1$  is currently granted to processor  $p_2$ , thus processor  $p_3$  has to wait for resource  $q_1$  to be free. Such grant and request edges are represented by two edges  $(q_3, p_3)$  and  $(p_3, q_1)$  in the grant set G and request set R respectively. Therefore, the request set R contains  $\{(p_3, q_1), (q_1, p_2), (q_3, p_3)\}$ . The union of the request edge set and the grant edge set is  $\{(p_3, q_1), (q_2, p_1), (q_1, p_2), (q_1, p_3)\}$ .

Definition 5. If a grant edge ceases to exist in a graph, that we say that the grant edge is released.

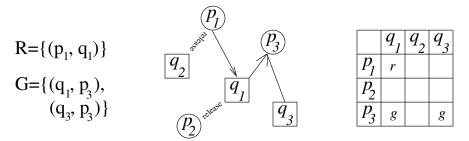

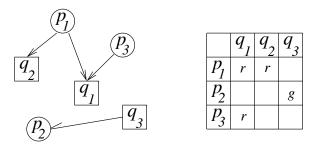

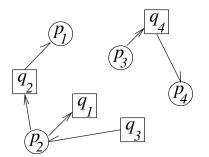

**Example 4.** In this example, we start with the system state shown in Figure 3. Processor  $p_2$  releases resource  $q_1$  which is immediately granted to processor  $p_3$ , as shown in Figure 4. The release of resource  $q_1$  is represented by the removal ("release") of grant edge  $(q_1, p_2)$  and the removal of  $g_{21}$  from the matrix of Figure 4. Furthermore, processor  $p_1$  releases resource  $q_2$ , which is now available to serve other processors. Thus grant edge  $(q_2, p_1)$  is removed ("released") from the grant set G. Processor  $p_1$  at the same time

makes a new request of resource  $q_1$ , which is being used by processor  $p_3$  exclusively, and thus processor  $p_1$  has to wait for resource  $q_1$  to be available. Overall, this case is represented by replacing a request edge  $(p_3, q_1)$  by a grant edge  $(q_1, p_3)$ , by adding a request edge  $(p_1, q_1)$ , and by eliminating ("releasing") two edges. Note that "release" in the middle diagram of Figure 4 represents a release of a resource by a processor.

FIGURE 4. Example of Release, Grant, and Request Edges

**Definition 6.** A given system with processors and resources can be abstracted by a Resource Allocation Graph (RAG). A RAG is a directed graph  $\gamma = \{V, E\}$ , such that V is a non-empty set of nodes and E is a set of ordered pairs or edges[10]. Note that the edge set E maybe empty. Using Definitions 1-5, a RAG can be described as a bipartite graph  $\gamma = \{V, E\}$ , where  $V = \{P \cup Q\}$  and  $E = \{R \cup G\}$ . The set V, the set of nodes in the RAG, can be divided into two disjoint subsets P and Q such that  $P \cap Q = \emptyset$ , where the processor subset is represented by  $P = \{p_1, p_2, p_3, \cdots, p_m\}$  (Definition 3) and the resource subset is represented by  $Q = \{q_1, q_2, q_3, \cdots, q_n\}$  (Definition 4). Therefore, graph  $\gamma$  is bipartite. The set E, the set of directed edges in the RAG, can be divided into two disjoint subsets R and G such that  $R \cap G = \emptyset$ , where the request subset is represented by  $R = \{(p_i, q_j) \mid 1 \le i \le m, 1 \le j \le n\}$  and the grant subset is represented by  $G = \{(q_j, p_i) \mid 1 \le i \le m, 1 \le j \le n\}$ . The total number of nodes V in a system  $\gamma_i$  is V = P + Q = m + n, where the subindex i represents a particular set V of a RAG  $\gamma$ .

**Definition 7.** The edge set E is equal to  $R \cup G$ . An edge is represented by  $(v_i, v_j)$  such that  $v_i, v_j \in V$  and either  $v_i \in P$  and  $v_j \in Q$ , or  $v_i \in Q$  and  $v_j \in P$ . An edge  $(v_i, v_j)$  denotes a request edge  $r_{ij}$  if the first node  $v_i$  is a processor node; e.g.,  $(p_i, q_j) = r_{ij}$ . On the other hand, an edge  $(v_i, v_j)$  denotes a grant edge  $g_{ij}$  if the first node is a resource node; e.g.,  $(q_i, p_j) = g_{ij}$ .

In the figures in this report, a circle represents a processor, while a square represents a resource. Hence, a group of circles forms a set P of processors and a group of boxes forms a set Q of resources.

Furthermore, as stated earlier, in the figures of this report, an arrow " $\rightarrow$ " represents a request edge while a harpoon " $\leftarrow$ " (or " $\rightarrow$ ") represents a grant edge.

**Definition 8.** Given RAG  $\gamma$ , let function  $E(\gamma)$  be defined as the set of edges E of RAG  $\gamma$ . Note that, from Definition 6, we know that  $E = \{R \cup G\}$ . The function  $R(\gamma)$  is defined as the set of request edges R of RAG  $\gamma$ . Similarly, the function  $G(\gamma)$  is defined as the set of grant edges G of a RAG  $\gamma$ . Let function  $V(\gamma)$  be defined as the set of nodes  $V = \{P \cup Q\}$  of RAG  $\gamma$ . The function  $P(\gamma)$  is defined as a set of processors P of RAG  $\gamma$ . The function  $Q(\gamma)$  is defined as a set of resources Q of RAG  $\gamma$ .

**Example 5.** Let the RAG in Figure 4 having three processors and three resources be system  $\gamma_i$ . The function  $E(\gamma_i)$  gives a set of edges  $\{(p_1, q_1), (q_1, p_3), (q_3, p_3)\}$ . The function  $R(\gamma_i)$  gives a set of request edges  $\{(p_1, q_1)\}$ . The function  $G(\gamma_i)$  gives a set of grant edges  $\{(p_1, q_1), (q_3, p_3)\}$ . The function  $V(\gamma_{ij})$  gives a set of nodes  $\{p_1, p_2, p_3, q_1, q_2, q_3\}$ . The function  $P(\gamma_{ij})$  gives a set of processor nodes  $\{p_1, p_2, p_3\}$ . The function  $Q(\gamma_{ij})$  gives a set of resource nodes  $\{q_1, q_2, q_3\}$ .

**Definition 9.** First of all, note that for a given (fabricated) SoC or Printed Circuit Board (PCB), the processors and resources are already decided upon and do not change. Therefore, a particular system  $\gamma_i = \{V, E\}$  representing this SoC or PCB will never change its set V of vertices (processors and resources). We define  $\gamma_{ij_1}, \gamma_{ij_2}, \gamma_{ij_3}, \ldots$  to be different instances or states of the same SoC or PCB (same set V). Note that the edge set  $E(\gamma_{ij})$  is different for each  $j \in \{1, 2, 3, \ldots\}$ . Since the node set  $V = \{P \cup Q\}$  is constant for a given system  $\gamma_i$ , the edge set E has enough information to represent a current state  $\gamma_{ij}$ , defined by the function  $E(\gamma_{ij})$  of a state  $\gamma_{ij}$  of a given system  $\gamma_i$ , where the second subindex j represents a particular set of E of a system  $\gamma_i$ . Thus a particular state  $\gamma_{ij}$  is uniquely defined relative to  $\gamma_i$  by  $E(\gamma_{ij}) = \{R \cup G\}$ . A system  $\gamma_i$  changes from one state  $\gamma_{ij}$  to another state  $\gamma_{ik}$  when handling requests, grants, and releases of resources[9].

**Example 6.** In Figure 5, a given system  $\gamma_i$  in a particular system state  $\gamma_{ij}$  is shown.  $V = \{P \cup Q\}$  is the set of nodes and  $E = \{R \cup G\}$  is the set of edges in  $\gamma_{ij}$ . A circle in Figure 5 represents a processor, while a box represents a resource. The set P of processors are shown by three circle nodes, which are  $\{p_1, p_2, p_3\}$ . The set Q of resources are shown by three box nodes, which are  $\{q_1, q_2, q_3\}$ . The set P of edges has two disjunct sets. The set P of edges are requests shown

FIGURE 5. An Example of RAG in Bipartite Graph.

by arrows from set P to set Q. The set  $G = \{(q_1, p_2), (q_3, p_3)\}$  of edges are grants shown by harpoons pointing from set Q to set P.

A SoC or PCB system is represented by a bipartite graph  $\gamma$ . A system  $\gamma_i$  defines a fixed set P of processors and a fixed set Q of resources, while a system state  $\gamma_{ij}$  represents the current actions (a set of requests R and a set of grants G).

An adjacency matrix  $M_{ij}$  is another representation of system state  $\gamma_{ij}$ . The dimension of matrix  $M_i$  is  $m \times n$ , m rows and n columns respectively. The set P of processors is mapped to the rows of matrix M. And the set Q of resources is mapped to the column of matrix M. In other words, the  $s^{th}$  row of matrix M represents all the edges (requests from or grants to) belonged to processor  $p_s$ . Similarly, The  $t^{th}$  column of matrix M represents all the edges (requests to or grants from) belonged to resource  $q_t$ . Each entry  $m_{st}$  (at  $s^{th}$  row and  $t^{th}$  column) in the matrix can be either request  $r_{st}$ , grant  $g_{st}$ , and available (as empty or release). For clarity in the matrix  $M_{ij}$ ,  $r_{st}$  is written as r in the row s and column t. Similarly, it is the same for  $g_{st}$ . If there is a grant edge  $(q_t, p_s) \in G$ , there is a  $g_{st}$  (or g at row g and column g in matrix g in the matrix

Definition 10. This definition aims to define matrices which correspond to graph  $\gamma$ , system  $\gamma_i$ , and state  $\gamma_{ij}$ . A RAG matrix M represents an arbitrary system with processors and resources. A system matrix  $M_i$  is defined as a matrix representation of system  $\gamma_i$  where the rows (fixed in size) of matrix  $M_i$  represent the fixed set P of processor nodes of  $\gamma_i$ , and the columns (fixed in size) of matrix  $M_i$  represent the fixed set Q of resource nodes of  $\gamma_i$ . A state matrix  $M_{ij}$  represents to a system state  $\gamma_{ij}$ . Edges in system state  $\gamma_{ij}$  are mapped into the array elements using the following rule:

Given

$$E = \{R \cup G\}$$

from  $\gamma_{ij}$ ,

for all rows  $0 \le s \le m$ , and for all columns  $0 \le t \le n$ :  $m_{st} = r_{st} \ (r \ for \ clarity), \ if \ there \ exists \ a \ request \ edge \ (p_s, q_t) \in R$   $m_{st} = g_{st} \ (g \ for \ clarity), \ if \ there \ exists \ a \ grant \ edge \ (q_t, p_s) \in G$   $m_{st} = 0_{st} \ (blank \ for \ clarity), \ otherwise$

**Example 7.** Example 4 shows an equivalent state matrix (on the right hand side of Figure 4) of the system state  $\gamma_{ij}$  described in Example 4. The system state  $\gamma_{ij}$  and state matrix  $M_{ij}$  corresponding to Example 4 are shown below in Figure 6. The request  $(p_1, q_1)$  from  $\gamma_{ij}$  is represented by  $m_{11} = r_{11} = r$  in the top left entry of the matrix as shown in Figure 6. Similarly, the grant  $(q_3, p_3)$  from  $\gamma_{ij}$  is represented by  $m_{33} = g_{33} = g$  in  $M_{ij}$  as shown in Figure 6.

(a) system state graph

| $M_{ij}$   | $q_{_I}$     | $q_{_2}$      | $q_{_{\!\scriptscriptstyle 3}}$ |

|------------|--------------|---------------|---------------------------------|

| $p_{_{I}}$ | $m_{II}=r$   | $m_{_{12}}=0$ | $m_{I3}=0$                      |

| $p_{_2}$   | $m_{2l} = 0$ | $m_{22} = 0$  | $m_{22} = 0$                    |

| $p_{_3}$   | $m_{3l}=g$   | $m_{32} = 0$  | $m_{33}=g$                      |

(b) system state matrix  $M_{ij}$

FIGURE 6. Example of a system state graph  $\gamma_{ij}$  and the corresponding system state matrix  $M_{ij}$ .

**Definition 11.** We overload the equality operator "=" in this technical report as follows: whenever an expression  $M_{ij} = \gamma_{ij}$  is seen, this means that matrix  $M_{ij}$  is created from  $\gamma_{ij}$  using Definition 10.

In summary, in this technical report, we use notation as follows. A RAG  $\gamma$ , as defined in Definition 6, represents a RAG, a directed bipartite graph with a set of nodes V and a set of edges E. A **system**  $\gamma_i$  represents a particular system, where the node set  $V = \{P, Q\}$  represents the system and does not change. A **state**  $\gamma_{ij}$  represents a particular instance of interactions (requests and grants) between processors and resources of a given system  $\gamma_i$ . Such interaction is captured in the edge set  $E = \{R \cup G\}$  which is used to represent formally the state  $\gamma_{ij}$  of a given system  $\gamma_i$ .

#### 2.2. Definitions of Types of Deadlock or Near-Deadlock States.

Note that for some state  $\gamma_{ij}$ , it may be possible to fulfill all requests in any arbitrary order without ever entering into a deadlock, and all requests are fulfilled in a timely fashion. Such states  $\{\gamma_{ij}\}$  are called **secure**.

**Definition 12.** For a particular system  $\gamma_i$ ,  $\Gamma^k = \{\gamma_{ij_1}, \gamma_{ij_2}, \gamma_{ij_3}, \ldots\}$  is a set of states, possibly empty, such that all states in  $\Gamma^k$  are secure.

Now, consider the case where there exists at least one request which is never fulfilled or is fulfilled so seldomly that the processor requesting the resource(s) is unable to perform its tasks in a timely fashion. Such a case does not lead to deadlock but is not a secure case either. This case is called **starvation**.

**Definition 13.** For a given system  $\gamma_i$ , we define  $\Gamma^h$  as to be a set of states  $\{\gamma_{ij_1}, \gamma_{ij_2}, \gamma_{ij_3}, \ldots\}$ , possibly empty, such that all states in  $\Gamma^h$  are starvation states.

In this report, we refer to a sequence of resource allocations via requests and grants as a **resource** scheduling. Now, consider a set of states  $\Gamma^j$  where there exists at least one resource scheduling that keeps a system out of deadlock. This case is called **safe**.

**Definition 14.** For a given system  $\gamma_i$ , we define  $\Gamma^j$  to be a set of states  $\{\gamma_{ij_1}, \gamma_{ij_2}, \gamma_{ij_3}, \ldots\}$ , non-empty, such that all states in  $\Gamma^j$  are safe states.

Note that all secure and starvation states are, by definition, safe states. More formally,  $\Gamma^k \subset \Gamma^j$  and  $\Gamma^h \subset \Gamma^j$ . Some authors also refer to safe states as **reducible**[1].

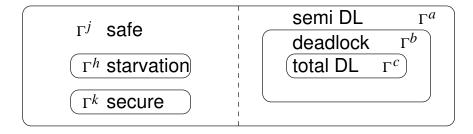

FIGURE 7. Sets of System States  $\Gamma^h, \Gamma^j, \Gamma^k, \Gamma^a, \Gamma^b, \Gamma^c$ .

Now, consider the case where a system will enter a deadlocked state regardless of in which order requests are granted due to new requests in the near future. Note that the system may or may not currently be deadlocked. This case is called **semi-deadlock**. Some authors also refer to semi-deadlock states as "non-safe" [1]. Clearly, absent knowledge of the future requests, it is not possible to detect if a system is in a semi-deadlock state.

**Definition 15.** For a given system  $\gamma_i$ , we define  $\Gamma^a$  to be a set of states  $\{\gamma_{ij_1}, \gamma_{ij_2}, \gamma_{ij_3}, \ldots\}$ , possibly empty, such that all states in  $\Gamma^a$  are semi-deadlock states.

Now, consider the case where there are some processors and resources deadlocked. There may also be some other processors or resources not part of the deadlock. This case is called **deadlock**.

**Definition 16.** For a given system  $\gamma_i$ , we define  $\Gamma^b$  to be a set of states  $\{\gamma_{ij_1}, \gamma_{ij_2}, \gamma_{ij_3}, \ldots\}$ , possibly empty, such that all states in  $\Gamma^a$  are deadlock states.

Now, consider the case where all processors and resources are deadlocked. This case is called **total-deadlock**.

**Definition 17.** For a given system  $\gamma_i$ , we define  $\Gamma^c$  to be a set of states  $\{\gamma_{ij_1}, \gamma_{ij_2}, \gamma_{ij_3}, \ldots\}$ , possibly empty, such that all states in  $\Gamma^c$  are total deadlock states.

Using Definitions 15, 16, and 17, note that  $\Gamma^c \subset \Gamma^b \subset \Gamma^a$ . We say that a state  $\gamma_{ij}$  is unsafe if state  $\gamma_{ij}$  is in one of the semi-deadlock states  $\Gamma^a$  – note that, by definition, state  $\gamma_{ij}$  could possibly also be in  $\Gamma^b$  or  $\Gamma^c$  as well. is a critical difference between deadlock and starvation. In a deadlock state, a processor waits for resources held by other processor(s) that will never be released, while in a starvation state, at least one processor never obtains enough to execute even though the resources periodically become available (only to be snatched up by other processors first).

The set  $\Gamma$  contains the union of the set of safe states and the set of semi-deadlock states. More formally,  $\Gamma = \Gamma^j \cup \Gamma^a$ .

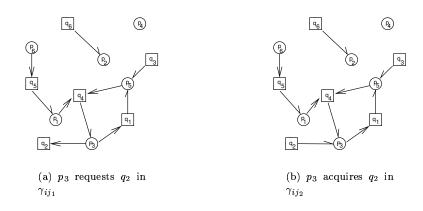

**Example 8.** Consider system  $\gamma_j$  as shown in Figure 8. In state  $\gamma_{ji_1}$ , processor  $p_3$  requests resource  $q_1$ , while at the same time  $p_2$  is using resource  $q_3$  which has been granted to  $p_2$ . State  $\gamma_{ji_1}$  is defined uniquely by  $P = \{p_1, p_2, p_3\}$ ,  $Q = \{q_1, q_2, q_3\}$ , and the edge set  $E = \{(p_3, q_1), (q_3, p_2)\}$ . Now consider what happens if processor  $p_1$  requests resource  $q_2$ , resource  $q_1$  is granted to processor  $p_3$ , and  $p_2$  releases resource  $q_3$ . The resulting state  $\gamma_{ji_2}$  is represented by the edge set  $E = \{(p_1, q_2), (q_1, p_3)\}$  and is shown in Figure 8(c).

Figure 8. Relationship between a State  $\gamma_{ji}$  (RAG) and edges E.

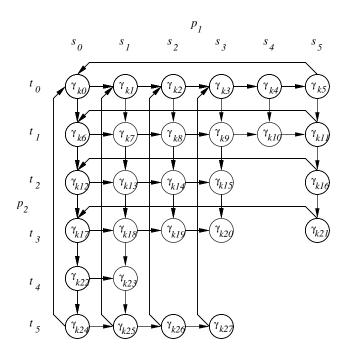

Now, let us put the previous definitions together and see the complexity of the deadlock detection problem as shown in Table 1 and Figure 9 for a system  $\gamma_k$  with two processors and two resources.

**Definition 18.** Note that at any point in time a processor may request or release a resource. Furthermore, at any point in time, an outstanding request for a resource may be granted. We refer to any such request, release, or grant as an **action**. Each action is associated with a **time-stamp**, which captures the relative timing among actions. Thus, the timing of a sequence of actions can be represented concisely by the sequence of time-stamps.

Example 9. Consider a system  $\gamma_k$  with two processors  $\{p_1, p_2\}$  and two resources  $\{q_1, q_2\}$ . At some point in time, each processor requires both resources at the same time to perform certain tasks. In this system, each processor performs the actions shown in Table 1 at the time-stamps shown in Table 1. The processor  $p_1$  will go from time-stamp  $s_0$  ( $p_1$  has no action) to  $s_1$ (an action that  $p_1$  requests  $q_1$ ) and then from time-stamp  $s_1$  to time-stamp  $s_2$ (an action that  $q_1$  is granted to  $p_1$ ). Finally, in our example, processor  $p_1$  goes from time-stamp  $s_4$ (an action that  $q_2$  is granted to  $p_1$ ) to time-stamp  $s_5$ (no action, but  $p_1$  is holding  $q_1$ ). When the processor  $p_1$  reaches time-stamp  $s_5$ , the processor  $p_1$  will go back to time-stamp  $s_0$  and will repeat the previous sequence of time-stamps. The processor  $p_2$  will go from time-stamp  $s_1$  to time-stamp  $s_2$ (an action that  $s_2$  is granted to  $s_2$ ). Finally, in our example, processor  $s_2$  goes from time-stamp  $s_2$ (an action that  $s_2$  is granted to  $s_2$ ). Finally, in our example, processor  $s_2$  goes from time-stamp  $s_2$ (an action that  $s_2$  is granted to  $s_2$ ) to time-stamp  $s_3$ (no action but  $s_2$  is holding  $s_2$ ). When the processor  $s_2$  reaches time-stamp  $s_3$ , the processor  $s_2$  will go back to time-stamp  $s_3$  and will repeat the previous sequence of time-stamps.

| multicolumn $2$ cActions of $p_1$ |                           | $\hbox{Actions of } p_2$ |               |  |

|-----------------------------------|---------------------------|--------------------------|---------------|--|

| Time-Stamp                        | Action                    | Time-Stamp               | Action        |  |

| $s_0$                             | no action                 | $t_0$                    | no action     |  |

| $s_1$                             | request $q_1$             | $t_1$                    | request $q_2$ |  |

| $s_2$                             | $\operatorname{grant}q_1$ | $t_2$                    | grant $q_2$   |  |

| $s_3$                             | request $q_2$             | $t_3$                    | request $q_1$ |  |

| $s_4$                             | $\operatorname{grant}q_2$ | $t_4$                    | grant $q_1$   |  |

|                                   | release $q_2$             |                          | release $q_1$ |  |

| $s_5$                             | no action                 | $t_5$                    | no action     |  |

|                                   | $release q_1$             |                          | release $q_2$ |  |

Table 1. Action Sequence for Processors  $p_1$  and  $p_2$

In Figure 9, both left and right horizontal arrows are action transitions due to actions by  $p_1$ . Furthermore, in Figure 9, both up and down vertical arrows are action transitions due to actions by  $p_2$ . In state  $\gamma_{k20}$  in Figure 9, processor  $p_1$  is at time-stamp  $s_3$ :  $p_1$  is holding  $q_1$  while requesting  $q_2$ . At the same time, in state  $\gamma_{k20}$  processor  $p_2$  is at time-stamp  $t_3$ :  $p_2$  is holding  $q_2$  while requesting  $q_1$ . Clearly, processors  $p_1$  and  $p_2$  are deadlocked in state  $\gamma_{k20}$ , which is also a total deadlock state in this system  $\gamma_k$  because all the processors and resources are involved. States  $\gamma_{k14}$ ,  $\gamma_{k19}$  and  $\gamma_{k15}$  are semi-deadlock states because  $p_2$  and  $p_1$  are going to deadlock in the future (given the known and unchanging execution patterns or action sequences we have described for  $p_1$  and  $p_2$ , we can prove that the system will definitely enter total deadlock state  $\gamma_{k20}$ ). Although there are no secure states in Figure 9, there are safe states: namely, the twenty-three states which are not total deadlock states ( $\gamma_{k20}$ ) nor semi-deadlock states ( $\gamma_{k14}$ ,  $\gamma_{k15}$  and  $\gamma_{k19}$ ).

In this report, we assume no knowledge about future execution patterns resulting in future requests and grants. Therefore, we are unable to detect semi-deadlock states. However, we can detect any any deadlock or total deadlock state. Similarly, we do not detect starvation states (note that starvation is typically due to a poor resource scheduling policy which can possibly be changed to avoid starvation). The scope of this report is limited to the fast detection of deadlock and total deadlock states.

## 2.3. Definitions and Properties of Various Edges.

This section further refines various relationships among edges. Such relationships of edges give the properties and definition of a deadlock. In other words, a particular set of edges corresponds to a particular system state, in which we would like to detect if there is a deadlocked scenario or not.

FIGURE 9. System States of Table 1

**Definition 19.** The out-degree of a node v is the number of directed edges going to other nodes from node v.

**Definition 20.** The *in-degree* of a node v is the number of directed edges coming in to node v from other nodes.

**Definition 21.** The degree of node v is the total number of directed edges connected to node v. Note that the sum of the out-degree of node v and the in-degree of node v equals the degree of node v. More formally, degree(v) = out-degree(v) + in-degree(v).

**Definition 22.** A isolated node  $v_{\epsilon}$  is a node that does not have any in-coming edges nor any out-going edges; more formally, node  $v_{\epsilon}$  is isolated if both  $E \cap \{(v, v_{\epsilon}) \mid v \in V\} = \emptyset$  and  $E \cap (v_{\epsilon}, v) \mid v \in V = \emptyset$ .

In other words, the number of edges of a isolated node is zero because the in-degree is zero and out-degree is zero.

**Definition 23.** Given a RAG in state  $\gamma_{ij}$  (see Definition 9), let  $\epsilon(\gamma_{ij})$  be a function which returns a set  $\{v_{\epsilon_1}, v_{\epsilon_2}, \dots, v_{\epsilon_p}\}$  of isolated vertices. Furthermore, let  $\Sigma_{\epsilon} = \{v_{\epsilon_1}, v_{\epsilon_2}, \dots, v_{\epsilon_p}\}$ . Note that it is possible for  $\Sigma_{\epsilon}$  to be empty, i.e., it may be the case that  $\Sigma_{\epsilon} = \emptyset$ .

Recall that a node in a RAG can be either a processor or a resource (Definition 6). If a processor does not request nor hold any resource, that processor is said to be an isolated processor. Obviously, an isolated processor cannot participate in any deadlock states. A resource is said to be isolated when that resource is not requested nor held by any processor. Such isolated nodes need not be considered by a deadlock detection algorithm. The advantage of identifying any isolated node(s) is that the problem space can be shrunk by ignoring the isolated node(s).

**Definition 24.** If a node is not isolated, it is called **non-isolated**. The set of non-isolated node is  $V - \Sigma_{\epsilon}$ .

When a resource is being requested by a processor, that resource and the processor are said to be non-isolated, because there is an action (interaction) between the processor and the resource. Specifically, the processor has an outgoing edge, while the resource has an incoming edge.

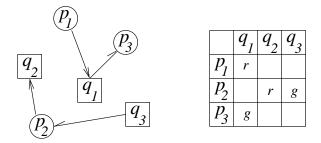

Example 10. Consider the left hand side of Figure 10. Processor  $p_1$  is not requesting nor holding any resource, thus processor  $p_1$  is an isolated processor node. Similarly, resource  $q_3$  is not being requested nor held by any processor, thus resource  $q_3$  is an isolated resource node. It is easy to identify any isolated node by checking either column j (for resource  $q_j$ ) or row i (for processor  $p_i$ ). On the right hand side of Figure 10, row 1 (for processor  $p_1$ ) is empty; thus, processor  $p_1$  is an isolated processor node. Again, consider the matrix on the right hand side of Figure 10: column 3 (for resource  $q_3$ ) is empty and thus resource  $q_3$  is an isolated node. Nodes  $p_2$ ,  $p_3$ ,  $q_1$ , and  $q_2$  are non-isolated nodes, because there are edges connected to or from each of these nodes. A non-isolated node is also easy to identify using the matrix: when a row or column is not empty, the corresponding processor or resource is non-isolated.

Figure 10. Isolated and non-isolated nodes

**Definition 25.** A node  $v_{\alpha}$  is a **sink** node if node  $v_{\alpha}$  both does not have any out going edges (out-degree( $v_{\alpha}$ ) = 0) and does have at least one incoming edge (in-degree( $v_{\alpha}$ )  $\geq$  1). More formally,  $v_{\alpha}$  is a sink node if both  $E \cap \{(v_{\alpha}, v) \mid v \in V\} = \emptyset$  and  $E \cap \{(v, v_{\alpha}) \mid v \in V\} \mid \geq 1$ .

**Definition 26.** Given a RAG in state  $\gamma_{ij}$  (see Definition 9), let  $\alpha(\gamma_{ij})$  be a function which returns a set  $\{v_{\alpha_1}, v_{\alpha_2}, \dots, v_{\alpha_p}\}$  of sink vertices. Furthermore, let  $\Sigma_{\alpha} = \{v_{\alpha_1}, v_{\alpha_2}, \dots, v_{\alpha_p}\}$ . Note that it is possible for  $\Sigma_{\alpha}$  to be empty, i.e., it may be the case that  $\Sigma_{\alpha} = \emptyset$ .  $\Sigma_{\alpha_{ij}}$  is used to denote the set of sink nodes in state  $\gamma_{ij}$ .

**Definition 27.** Given a RAG in state  $\gamma_{ij}$  and a set  $\alpha(\gamma_{ij})$  of sink vertices, let  $E_{\alpha_{ij}}$  be the set of edges connected to sink vertices  $v_{\alpha} \in \alpha(\gamma_{ij})$ . In other words,  $E_{\alpha_{ij}} = \{(v_x, v_y) \text{ such that } v_x \in \alpha(\gamma_{ij})\}$  – the tail of the edge is the sink vertex. (Recall that edge  $(v_x, v_y)$  was defined by Definition 7.)

FIGURE 11. Sink nodes and edges

Example 11. Let the left hand side of Figure 11 define state  $\gamma_{ij}$ . Processor  $p_2$  is a sink processor node  $(p_2 \in \alpha(\gamma_{ij}) = \Sigma_{\alpha_{ij}})$  with two grant edges:  $(q_2, p_2)$  and  $(q_1, p_2)$  both elements of  $E_{\alpha_{ij}}$ . Grant edges  $\{(q_2, p_2), (q_1, p_2)\}$  can be called sink edges with respect to the processor  $p_2$ . Resource  $q_3$  is a sink resource node  $(q_3 \in \alpha(\gamma_{ij}))$  with one request edge  $(p_3, q_3)$  which is in the set  $E_{\alpha_{ij}}$ . Request edge  $(p_3, q_3)$  can be called a sink edge with respect to resource  $q_3$ . One can easily identify a sink node using the matrix on the right hand side of Figure 11. If a row i for processor  $p_i$  contains only grant edges, then the processor  $p_i$  is a sink node and all the corresponding edges in that row i are called sink edges with respect to processor  $p_i$ . If a column j for resource  $q_j$  contains only one grant edge, then the resource  $q_j$  is a source node and the corresponding edge is called a source edge with respect to resource  $q_j$ .

**Definition 28.** A node  $v_{\beta}$  is a **source** node if  $v_{\beta}$  both has at least one outgoing edge (out-degree( $v_{\beta}$ )  $\geq 1$ ) and does not have any incoming edges (in-degree( $v_{\beta}$ ) = 0). More formally,  $v_{\beta}$  is a source node if both  $E \cap \{(v, v_{\beta}) \mid v \in V\} = \emptyset$  and  $E \cap \{(v_{\beta}, v) \mid v \in V\} \mid \geq 1$ .

**Definition 29.** Given a RAG in state  $\gamma_{ij}$  (see Definition 9), let  $\beta(\gamma_{ij})$  be a function which returns a set  $\{v_{\beta_1}, v_{\beta_2}, \dots, v_{\beta_p}\}$  of source vertices. Furthermore, let  $\Sigma_{\beta} = \{v_{\beta_1}, v_{\beta_2}, \dots, v_{\beta_p}\}$ . Note that it is possible for  $\Sigma_{\beta}$  to be empty, i.e., it may be the case that  $\Sigma_{\beta} = \emptyset$ .  $\Sigma_{\beta_{ij}}$  is used to denote the set of source nodes in state  $\gamma_{ij}$ .

**Definition 30.** Given a RAG in state  $\gamma_{ij}$  and a set  $\beta(\gamma_{ij})$  of source vertices, let  $E_{\beta_{ij}}$  be the set of edges connected to source vertices  $v_{\beta} \in \beta(\gamma_{ij})$ . In other words,  $E_{\beta_{ij}} = \{(v_x, v_y) \text{ such that } v_x \in \beta(\gamma_{ij})\}$  – the head of the edge is the source vertex.

Let us apply the sink and source definitions to an SoC scenario. A processor is a sink processor when the processor only has grant edges. Alternatively, a resource is a sink resource when the resource only has request edges. On the other hand, a processor is a source processor when the processor only has request edges. A resource is a source resource when the resource only has one edge, a grant edge. In such situations, sink or source processors or resources do not satisfy the four necessary conditions for deadlock to occur[1].

FIGURE 12. Source Nodes and Edges

**Example 12.** Let the RAG on the left of Figure 12 define  $\gamma_{ij}$ . Processor  $p_1$  is a source processor node  $(p_1 \in \beta(\gamma_{ij}) = \Sigma_{\beta_{ij}})$  because  $p_1$  has not been granted any resources and is making two requests: one request is for resource  $q_1$  and the other request is for resource  $q_2$ . The request edges are  $(p_1, q_2) = r_{12}$  and  $(p_1, q_1) = r_{11}$ . We find that  $r_{12} \in E_{\beta_{ij}}$  and  $r_{11} \in E_{\beta_{ij}}$ . Resource  $q_3$  is a source resource node  $(q_3 \in \beta(\gamma_{ij}))$  because  $q_3$  has only one edge: a grant edge  $(q_3, p_2)$  pointing to processor  $p_2$ . Grant edge

$(q_3, p_2) = g_{32}$  is an element of  $E_{\beta_{ij}}$ . Using Definition 25, resources  $q_2$  and  $q_1$  are both sink resource nodes because they only have incoming edges.

**Definition 31.** A node  $v_{\tau}$  is a terminal node, if node  $v_{\tau}$  is either a sink or a source node.

**Definition 32.** Given a RAG in state  $\gamma_{ij}$  (see Definition 9), let  $\tau(\gamma_{ij})$  be a function which returns a set  $\{v_{\tau_1}, v_{\tau_2}, \dots, v_{\tau_p}\}$  of terminal vertices. Furthermore, let  $\Sigma_{\tau} = \{v_{\tau_1}, v_{\tau_2}, \dots, v_{\tau_p}\}$ . Note that it is possible for  $\Sigma_{\tau}$  to be empty, i.e., it may be the case that  $\Sigma_{\tau} = \emptyset$ . Also note that  $\Sigma_{\tau} = \Sigma_{\alpha} \cup \Sigma_{\beta}$ . Finally,  $\Sigma_{\tau_{ij}}$  is used to denote the set of terminal nodes in state  $\gamma_{ij}$ .

**Definition 33.** Given a RAG in state  $\gamma_{ij}$  and a set  $\tau(\gamma_{ij})$  of terminal vertices, let  $E_{\tau_{ij}}$  be the set of edges connected to terminal vertices  $v_{\tau} \in \tau(\gamma_{ij})$ . In other words,  $E_{\tau_{ij}} = \{(v_x, v_y)\}$  such that either  $v_x \in \tau(\gamma_{ij})$  or  $v_y \in \tau(\gamma_{ij})$  (or both).

**Example 13.** In Figure 12, let the RAG shown define  $\gamma_{ij}$ . The node  $p_1$  in Figure 12 is a terminal node because  $p_1$  is a source node  $(p_1 \in \beta(\gamma_{ij}))$  and  $p_1 \in \tau(\gamma_{ij})$ . The node  $q_1$  is a terminal node because  $q_1$  is a sink node  $(q_1 \in \alpha(\gamma_{ij}))$  and  $q_1 \in \tau(\gamma_{ij})$ . The set of terminal nodes  $\Sigma_{\tau_{ij}}$  is  $\{p_1, p_2, p_3, q_1, q_2, q_3\}$ .

Now let the RAG in Figure 10 define  $\gamma_{ij}$ . In this case, the node  $p_2$  is not a terminal node because it is neither a sink nor a source node. Processor  $p_1$  and resource  $q_3$  are not terminal nodes because they are isolated nodes. The set of terminal nodes in Figure 10 is  $\Sigma_{\tau_{ij}}$  is  $\{p_3, q_1, q_2\}$ .

**Definition 34.** A link node  $v_{\lambda}$  is a node that has exactly one in-coming edge and one out-going edge, such that  $||E \cap \{(v, v_{\lambda}) \mid v \in V\}|| = 1$  and  $||E \cap \{(v_{\lambda}, v) \mid v \in V\}|| = 1$ . Clearly, the number of edges of a link node is two (degree $(v_{\lambda}) = 2$ ).

**Definition 35.** Given a RAG in state  $\gamma_{ij}$  (see Definition 9), let  $\lambda(\gamma_{ij})$  be a function which returns a set  $\{v_{\lambda_1}, v_{\lambda_2}, \dots, v_{\lambda_p}\}$  of link vertices. Furthermore, let  $\Sigma_{\lambda} = \{v_{\lambda_1}, v_{\lambda_2}, \dots, v_{\lambda_p}\}$ . Note that it is possible for  $\Sigma_{\lambda}$  to be empty, i.e., it may be the case that  $\Sigma_{\lambda} = \emptyset$ .

**Definition 36.** Given a RAG in state  $\gamma_{ij}$  and a set  $\lambda(\gamma_{ij})$  of link vertices, let  $E_{\lambda_{ij}}$  be the set of edges connected to link vertices  $v_{\lambda} \in \lambda(\gamma_{ij})$ . In other words,  $E_{\lambda_{ij}} = \{(v_x, v_y)\}$  such that either  $v_x \in \lambda(\gamma_{ij})$  or  $v_y \in \lambda(\gamma_{ij})$  (or both).

A resource is said to be a link resource when that resource is being used by one processor and at the same time is being requested by another processor. The concept of a link resource can also be applied to a processor. When a processor is holding a resource and at the same time requesting an additional resource, that processor is said to be link processor.

Figure 13. Link Nodes and Edges

Example 14. Let the system state shown in Figure 13 be  $\gamma_{ij}$ . Processor  $p_2$  is a link processor node  $(p_2 \in \lambda(\gamma_{ij}))$  because  $p_2$  is involved in both a request  $(p_2, q_2)$  and a grant  $(q_3, p_2)$ . With respect to processor  $p_2$ , edges  $(p_2, q_2)$  and  $(q_3, p_2)$  are link edges. Resource  $q_1$  is also another link node (link resource node) because there are a request edge from processor  $p_1$  and a grant edge to  $p_3$ . Processor  $p_1$  is not a link processor node: instead,  $p_1$  is a source processor node. Similarly, processor  $p_3$  is not a link processor node but instead is a sink processor node. Edges  $(p_1, q_1)$  and  $(q_1, p_3)$  are called link edges with respect to resource  $q_1$ . The result is as follows:  $\lambda(\gamma_{ij}) = \{p_2, q_1\}$  and  $E_{\lambda_{ij}} = \{(p_2, q_2), (q_3, p_2), (p_1, q_1), (q_1, p_3)\} = \{r_{22}, g_{32}, r_{11}, g_{13}\}$

It is easy to identify link nodes using the matrix in Figure 13. For processor  $p_2$ , row 2 contains requests  $r_{22}$  and grants  $g_{23}$ , therefore,  $p_2$  is a link node. For resource  $q_1$ , column 4 contains request  $r_{11}$  and grant  $g_{31}$ ; therefore,  $q_1$  is a link node. Resource  $q_2$  is a sink node. Similarly, resource  $q_3$  a sink node.

**Definition 37.** A branch node  $v_{\omega}$  has one or more incoming edges and one or more outgoing edges, such that the total number of edges is greater than or equal to three. More formally, three conditions must hold for  $v_{\omega}$  to be a branch node: (1) the in-degree of  $v_{\omega}$  must be one or more (in-degree( $v_{\omega}$ )  $\geq 1$ ); (2) the out-degree of  $v_{\omega}$  must be one or more (out-degree( $v_{\omega}$ )  $\geq 1$ ); and (3) the degree of  $v_{\omega}$  must be three or more (degree( $v_{\omega}$ )  $\geq 3$ ).

**Definition 38.** Given a RAG in state  $\gamma_{ij}$  (see Definition 9), let  $\omega(\gamma_{ij})$  be a function which returns a set  $\{v_{\omega_1}, v_{\omega_2}, \dots, v_{\omega_p}\}$  of branch vertices. Furthermore, let  $\Sigma_{\omega} = \{v_{\omega_1}, v_{\omega_2}, \dots, v_{\omega_p}\}$ . Note that it is possible for  $\Sigma_{\omega}$  to be empty, i.e., it may be the case that  $\Sigma_{\omega} = \emptyset$ .

**Definition 39.** Given a RAG in state  $\gamma_{ij}$  and a set  $\omega(\gamma_{ij})$  of branch vertices, let  $E_{\omega_{ij}}$  be the set of edges connected to branch vertices  $v_{\omega} \in \omega(\gamma_{ij})$ . In other words,  $E_{\omega_{ij}} = \{(v_x, v_y)\}$  such that either  $v_x \in \omega(\gamma_{ij})$  or  $v_y \in \omega(\gamma_{ij})$  (or both).

The difference between a branch node and a link node is that while a branch node must have three or more edges, a link node must have only two edges. A resource is said to be a branch resource if the resource is held by one processor and is being requested by two or more processors. A processor is said to be a branch processor if the processor either holds one or more resources while requesting two or more additional resources, or if the processor holds two or more resources while requesting one or more resources.

FIGURE 14. Branch Nodes and Edges

**Example 15.** Let the system state shown in Figure 14 be  $\gamma_{ij}$ . Processor  $p_2$  is a branch node because the number of edges to and from  $p_2$  is greater than two and there is at least one request edge and at least one grant edge. Similarly, resource  $q_1$  is also a branch node. The edges connected to a branch node are called branch edges with respect to the branch node. Thus,  $\{(p_2, q_2), (q_3, p_2), (p_2, q_1)\}$  are branch edges with respect to branch processor node  $p_2$ , and  $\{(p_2, q_1), (q_1, p_3), (p_1, q_1)\}$  are branch edges with respect to branch resource node  $q_1$ . We end up with the following for this example:  $\omega(\gamma_{ij}) = \{p_2, q_1\}$  and  $E_{\omega_{ij}} = E(\gamma_{ij})$  (since all edges connect to the two branch nodes).

It is also easy to identify a branch node by examining the matrix on the right hand side of Figure 14. A processor  $p_i$  is a branch node if row i has three or more entries with at least one r and one g entry. Similarly, a resource  $q_j$  is a branch node if the column j has three or more entries with at least one r entry and one g entry.

**Definition 40.** A node  $v_{\phi}$  is a **connect** node if node  $v_{\phi}$  is either a link node or a branch node.

**Definition 41.** Given a RAG in state  $\gamma_{ij}$  (see Definition 9), let  $\phi(\gamma_{ij})$  be a function which returns a set  $\{v_{\phi_1}, v_{\phi_2}, \dots, v_{\phi_p}\}$  of connect vertices. Furthermore, let  $\Sigma_{\phi} = \{v_{\phi_1}, v_{\phi_2}, \dots, v_{\phi_p}\}$ . Note that it is possible for  $\Sigma_{\phi}$  to be empty, i.e., it may be the case that  $\Sigma_{\phi} = \emptyset$ .

**Definition 42.** A path  $(v_1, v_2, v_3, \ldots, v_{k-1}, v_k)$ ,  $k \geq 2$ , is a consecutive ordered sequence of alternating request and grant edges  $(v_1, v_2)$ ,  $(v_2, v_3)$ , ...,  $(v_{k-1}, v_k)$  where every node in the path is distinct and where every other node belongs to the same set. In other words, every odd node along a path belongs to one node set of V (either P or Q) and every even node along the same path belongs to the other node set of V.

The "," between two nodes can represent either a request edge or a grant edge. The "," represents a request edge if the previous node is a processor node, while the "," represents a grant edge if the previous node is a resource node. To explicitly illustrate the action (interaction) between nodes, the arrow (request) and harpoon (grant) symbols can be used instead of the comma ",". Thus, a path  $v_1 \rightarrow v_2 \rightarrow v_3 \rightarrow \cdots \rightarrow v_{k-1} \rightarrow v_k$  can be another representation of a path  $(v_1, v_2, v_3, \ldots, v_{k-1}, v_k)$  where node  $v_1$  is a processor node in set P. Similarly, path  $v_1 \rightarrow v_2 \rightarrow v_3 \rightarrow \cdots \rightarrow v_{k-1} \rightarrow v_k$  can be used to represent a path  $(v_1, v_2, v_3, \ldots, v_{k-1}, v_k)$  where node  $v_1$  is a resource node in set Q.

**Example 16.** In Figure 5, resource  $q_1$  is granted to processor  $p_2$ . At the same time, processor  $p_2$  requests resource  $q_3$ , which is granted to processor  $p_3$ . Thus, Figure 5 has the path  $(q_1, p_2, q_3, p_3)$ . Resource  $q_1$  is a source node and processor  $p_3$  is a sink node. The processor  $p_2$  and resource  $q_3$  are link nodes in this path. In short, the paths in Figure 5 are  $(q_1, p_2, q_3, p_3)$ ,  $(q_1, p_2, q_3)$ ,  $(p_2, q_3, p_3)$ ,  $(q_1, p_2)$ ,  $(p_2, q_3)$ ,  $(q_3, p_3)$  and  $(p_1, q_2)$ .

**Definition 43.** A simple path is a path  $(v_i, v_{i+1}, \ldots, v_k)$  such that both  $v_i$  and  $v_k$  are terminal nodes and all other nodes are link nodes. Formally, a path  $(v_i, v_{i+1}, \ldots, v_k)$  is simple if both  $v_i, v_k \in \Sigma_{\tau}$  and  $v_{i+1}, \ldots, v_{k-1} \in \Sigma_{\lambda}$ .

**Definition 44.** A dangling path is a path  $(v_i, v_{i+1}, \ldots, v_j)$  such that either  $v_i$  is a terminal node and  $v_j$  is a branch node, or  $v_i$  is a branch node and  $v_j$  is a terminal node. Formally, a path  $(v_i, v_{i+1}, \ldots, v_j)$  is dangling if either  $(v_i \in \Sigma_{\tau}) \land (v_j \in \Sigma_{\phi})$  or  $(v_i \in \Sigma_{\phi}) \land (v_j \in \Sigma_{\tau})$ . In short, a dangling path either begins with a terminal node and ends with a branch node, or vice versa.

|                   | $q_{_{1}}$ | $q_{2}$ | $q_{3}$ | $q_{_{\!\!4}}$ |

|-------------------|------------|---------|---------|----------------|

| $p_{I}$           |            | g       |         |                |

| $p_2$             | r          | r       | g       |                |

| $\frac{p_2}{p_3}$ |            |         |         | r              |

| $p_{\!_{4}}$      |            |         |         | g              |

FIGURE 15. Nodes and Edges of Dangling and Simple Paths.

**Example 17.** Consider Figure 15. Processor  $p_2$  is a branch node, while resources  $q_2$  and  $q_4$  are link nodes. Resources  $q_1$  and  $q_3$  and processors  $p_1$ ,  $p_3$ , and  $p_4$  are terminal nodes. There are three dangling paths:  $(q_3, p_2)$ ,  $(p_2, q_1)$ , and  $(p_2, q_2, p_1)$ . There is one simple path  $(p_3, q_4, p_4)$

The reason for defining a dangling path will become clear later on when we use it in a proof.

**Definition 45.** The reachable set  $\Sigma_{v_{\pi}}$  of a node  $v_{\pi}$  is the set of nodes  $\{v_i \mid \exists (v_{\pi}, \ldots, v_i)\}$ , which means a set of nodes such that there exists a path from  $v_{\pi}$  to node  $v_i$ .

**Example 18.** In Figure 16 the reachable set  $\Sigma_{p_6}$  of node  $p_6$  is  $\{q_5, p_1, q_4, p_3, q_1, p_5, q_2\}$ . Note that although  $q_3$  is connected to the node  $p_5$ , nevertheless  $q_3$  is not reachable from  $p_6$ .

**Definition 46.** A cycle C is an ordered sequence of vertices  $(v_1, v_2, \ldots, v_k)$ ,  $k \geq 5$ , such that  $v_1$  and  $v_k$  are the same and no other in C are the same.  $\Sigma_c$  is the set of nodes involved in a path C.

**Example 19.** In Figure 16, nodes  $q_4$ ,  $q_1$ ,  $p_3$ , and  $p_5$  form a cycle C of  $(q_4, p_3, q_1, p_5, q_4)$ , starting and ending with node  $q_4$ . The set  $\Sigma_c$  is  $\{q_4, p_3, q_1, p_5\}$ .

Definition 47. A state  $\gamma_{ij}$  of a system  $\gamma_i$  is said to be an expedient state if  $\gamma_{ij}$  does not contain any sink resources. In other words, there are no resources which are unallocated and have pending requests: thus, all resources are either isolated (no requests) or are granted to some processors. In an expedient system, all satisfiable requests are granted without delay. As soon as there is one request of a resource which is an isolated resource, that resource will be granted to the requesting processor and will become a source resource. If a resource has two requests, the resource will be granted to one processor and become a link resource; the processor which was not granted the resource has to wait. If a resource has more than two requests, the resource will be granted to one processor only and become a branch resource.

## **Example 20.** Figure 16 shows a given system $\gamma_i$ in state $\gamma_{ij_1}$ .

FIGURE 16. An Example of RAG with Request(s), Grant(s), and Cycle(s).

In Figure 16, system  $\gamma_i$  has processors  $p_1$ ,  $p_2$ ,  $p_3$ ,  $p_4$ ,  $p_5$ , and  $p_6$ .  $\gamma_i$  also has resources  $q_1$ ,  $q_2$ ,  $q_3$ ,  $q_4$ ,  $q_5$ , and  $q_6$ . State  $\gamma_{ij_1}$  is not an expedient state, because the satisfiable request  $(p_3, q_2)$  has not been granted yet. However  $\gamma_{ij_1}$  can be transformed into expedient state  $\gamma_{ij_2}$  when the request edge  $(p_3, q_2)$  is turned into a grant edge  $(q_2, p_3)$ , which is possible since  $q_2$  is not allocated to any processor. In state  $\gamma_{ij_1}$ ,  $p_4$  is an isolated processor node, while the rest of the processor and resource nodes are either link, sink or source nodes.

**Example 21.** In Figure 17, the graph  $\gamma_{ij_1}$  is transformed into an expedient graph  $\gamma_{ij_2}$  by changing  $p_3 \to q_2$  into  $q_2 \rightharpoonup p_3$ . In Figure 17 (b), since  $p_2$  and  $q_6$  do not connect to the rest of the graph, the existence of path  $q_6 \rightharpoonup p_2$  will not affect the other subgraphs. Thus  $q_6 \rightharpoonup p_2$  can be safely ignored when searching for the deadlock condition.

FIGURE 17. RAG Reduction of Figure 16.

**Lemma 1.** The number of edges ||E|| in a system  $\gamma_i$  is less than or equal  $||E|| \leq m \times n$ ,

**Proof:** Since the graph  $\gamma_i$  is bipartite, each edge is permitted only to go from one set P of processor nodes to the other set Q of resource nodes or vice versa. A processor node  $p_i$  can have one edge to each resource,

thus a processor node  $p_i$  can have at most n = ||Q|| request edges  $\{(p_i, q_j) \mid q_j \in Q, j = 1, 2, 3, \dots, n\}$ . Since there are m = ||P|| processor nodes, the maximum number of request edges is  $m \times n$ . Since each grant edge replaces the corresponding request edge, the total number of request edges will be decreased by one whenever the total number of grant edges is increased by one. Thus, there is no change in the maximum total number of possible edges if the system is maintained in an expedient state. Overall, the total number of edges ||E|| is less than  $((m \times n - k) + k) = m \times n \mid k = 0, 1, 2, \dots, n$ , where k is the number of request edges that have been transformed into grant edges. Note that the maximum total number of grants at any given time is  $k \le n$ , since at most all n resources can be granted.

The above property give us the approximate computational complexity of an algorithm based on either edges or nodes. An edge based algorithm has O(e) run time complexity, where e is the number of edges. Also, the fact that there do not exist edges  $(p_i, p_j)$  from one processor to another and that there do not exist edges  $(q_i, q_j)$  from one resource to another is an important property for the hardware architecture. In short, a two dimensional adjacency matrix of edges is sufficient to represent all the possible different types of edges for the systems we consider. Such a two dimensional adjacency matrix provides an efficient hardware architecture implementation.

Therefore, OS routines and a RAG together can be used to model both system states and state transitions of an SoC or PCB with processors and resources. When a processor  $p_i$  makes a request for resource  $q_j$ , the OS inserts a request edge  $r_{ij} = (p_i, q_j)$  into the edge set R. When a processor  $p_i$  obtains a resource  $q_j$ , the OS removes the request edge  $r_{ij} = (p_i, q_j)$  from R and inserts a grant edge  $g_{ji} = (q_j, p_i)$  in the set G. When a processor  $p_i$  releases a resource  $q_j$ , the OS removes the grant edge  $g_{ji} = (q_j, p_i)$  from the set G.

#### 3. Deadlock Properties

This section describes various properties and theorems relating to deadlock. For a system  $\gamma_{ij}$ , these properties and theorems can be applied to the matrix representation  $M_{ij}$  of  $\gamma_{ij}$ . In the systems we consider – reusable single-resource systems (defined in Section 1) – a cycle is a sufficient condition for deadlock[1]. Generally speaking, it is desirable to identify if a system state is deadlocked or not as soon as possible. Finding and constructing a cycle is not computationally efficient because the run time complexity of a cycle-search algorithm is similar to that of depth-first-search or breath-first-search. A technique based on a reduction sequence applied to the RAG of the system has been shown previously[1].

In general, any algorithm based on a RAG has a computational complexity in software of  $O_{sw}(m \times n)$ , where the "sw" in " $O_{sw}$ " refers to the fact that the algorithm is run in software on a processor. We introduce a new technique – based on the notion of a matrix reduction sequence – which provides a better solution and can identify a deadlock state in linear time complexity in a hardware implementation.

**Theorem 1.** A cycle is a necessary and sufficient condition for deadlock in a reusable single-resource expedient system with  $m \ge 2$  requesters and  $n \ge 2$  resources..

**Proof:** The proof is available in Chapter 4 of Operating Systems - Advanced Concepts[1].

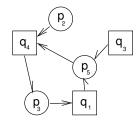

Example 22. A system with three processors and three resources is shown in Figure 18. The existence of a cycle C of path  $(p_5, q_4, p_3, q_1, p_5)$  is necessary and sufficient to indicate a deadlocked system. The set of nodes in cycle C is  $\Sigma_c = \{p_5, q_4, p_3, q_1\}$ . Processor  $p_5$  and resource  $q_4$  are branch nodes. The grant edge  $(q_3, p_5)$  and request edge  $(p_2, q_4)$  are dangling paths. The reachable set of  $p_5$  is  $\Sigma_{p_5} = \{p_5, p_3, q_1, q_4\} = \Sigma_c$ . The reachable sets  $\Sigma_{p_3}$ ,  $\Sigma_{q_1}$ , and  $\Sigma_{q_4}$  are equal to  $\Sigma_c$ . The reachable set  $\Sigma_{p_2}$  is  $\{\Sigma_c \cup p_2\}$  but processor  $p_2$  is not part of cycle C. Processor  $p_2$  is connected to the cycle C. The node  $q_3$  has a reachable set of  $\{\Sigma_c \cup q_3\}$  and resource  $q_3$  is not part of cycle C either. Since both processor  $p_2$  and resource  $q_3$  are not part of the  $\Sigma_c$ , the existence of the cycle C is not affected by the absence of edges  $p_2 \to q_4$  and  $q_3 \to p_5$ . In such a single-resource expedient system, a cycle is necessary and sufficient condition to identify a deadlocked state.

FIGURE 18. A Deadlock Cycle in RAG

Before formally defining the notion of a reduction step, we first give an informal description. One can consider a reduction step as emulating processor  $p_i$  either (i) releasing a held resource  $q_j$ , or (ii) releasing the resource  $q_j$ .

A processor  $p_i$  can complete its computation and then release all of the resources  $p_i$  holds only if the processor  $p_i$  has been granted access to all the resources  $p_i$  has requested. When a processor  $p_i$  does

release all of the resources which  $p_i$  holds, the processor  $p_i$  is said to be **reduced**. Clearly, a reduced processor which makes no more requests cannot participate in a deadlock. When a granted resource  $q_j$  is released by the last requester  $p_i$ , that resource  $q_j$  is said to be reduced. Clearly, a reduced resource which receives no more requests also cannot participate in deadlock. This is why we are interested in formally defining the notion of a reduction step.

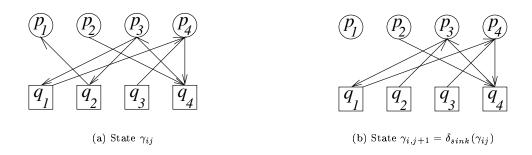

Definition 48. A sink reduction step  $\delta_{sink}$  is a unary operator  $\delta_{sink}: \gamma_{ij} \mapsto \gamma_{i,j+1}$ , where  $\delta_{sink}$  calculates the sink set  $\alpha(\gamma_{ij})$  of  $\gamma_{ij}$  and returns  $\gamma_{i,j+1}$  such that all sink edges  $E_{\alpha_{ij}}$  found are removed and do not appear in  $\gamma_{i,j+1}$ . To determine the sink set,  $\delta_{sink}$  uses Definition 25:  $\Sigma_{\alpha_{ij}} = \alpha(\gamma_{ij})$  which returns a set sink nodes. Next, the sink reduction step  $\delta_{sink}$  deletes all sink edges  $E_{\alpha_{ij}}$  found connected to vertices in the sink set  $\alpha(\gamma_{ij})$ . Such deletions reduce the number of edges. The formula for  $\delta_{sink}(\gamma_{ij})$  is shown in the second line of Equation 1:

(1)

$$\gamma_{i,j+1} = \delta_{sink}(\gamma_{ij}) \\

= (V, (E(\gamma_{ij}) - E_{\alpha_{ij}}))$$

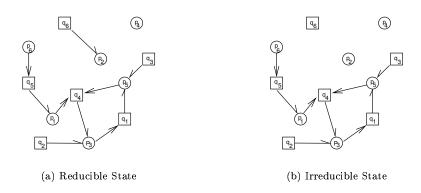

The function  $\delta_{sink}(\gamma_{ij})$  is called a sink reduction step because Equation 1 simply subtracts out (reduces) the set of sink edges. Note that the node set V is not changed. If the outgoing edge of a link node connects to a sink node in  $\gamma_{ij}$ , then that link node will become a sink node in  $\gamma_{i,j+1} = \delta_{sink}(\gamma_{ij})$ . If the outgoing edge of a branch node connects to a sink node, that branch node can become a link node when that edge is removed (if the degree of the branch node is three). If the outgoing edges of a branch node all connect to sink nodes, that branch node can become a sink node when those edges are removed. Thus, the removal of sink edges may make the set  $\Sigma_{\phi}$  of connect nodes smaller and may create new sink nodes. When  $\delta_{sink}$  is applied again to the next system state  $\gamma_{i,j+1}$ , any sink edges in  $\gamma_{i,j+1}$  must have been derived from the set of connect edges in  $\gamma_{ij}$ .

**Definition 49.** If a system state  $\gamma_{ij}$  can be transformed by a reduction step to another state  $\gamma_{i,j+1}$  resulting in  $\gamma_{i,j+1} \neq \gamma_{ij}$ , then the system state  $\gamma_{ij}$  is said to be **reducible**. If a system state  $\gamma_{ij}$  cannot be reduced to another different state  $\gamma_{i,j+1}$  (because the resulting  $\gamma_{i,j+1}$  is equal to  $\gamma_{ij}$ ), then system state  $\gamma_{ij}$  is said to be **irreducible**.

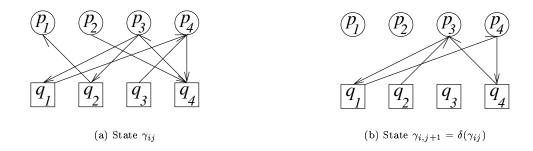

**Example 23.** Assume we are given a system state  $\gamma_{ij} = (V, E)$ , as shown in Figure 19(a), where  $V = \{P \cup Q\}$  and  $E = \{R \cup G\}$ :

FIGURE 19. Apply a Sink Reduction Step  $\delta_{sink}$  to State  $\gamma_{ij}$ .

$$\begin{split} P &= \{p_1, p_2, p_3, p_4\} \text{ and } Q = \{q_1, q_2, q_3, q_4\}. \\ R &= \{(p_2, q_4), (p_4, q_4), (p_3, q_1), (p_3, q_2)\} \text{ and } G = \{(q_2, p_1), (q_1, p_4), (q_4, p_3), (q_3, p_4)\}. \\ \Sigma_{\alpha_{ij}} &= \alpha(\gamma_{ij}) = \{p_1\} \text{ since } p_1 \text{ is a sink processor node.} \\ E_{\alpha_{ij}} &= \{(q_2, p_1)\} \text{ because there is only one edge into } p_1 = \alpha(\gamma_{ij}). \\ \text{Resource } q_2 \text{ is a link node in } \gamma_{ij} \text{ while } q_2 \text{ is a sink node in } \gamma_{i,j+1} \text{:} \end{split}$$

The result,  $\gamma_{i,j+1}$ , has a smaller set E because the sink reduction step  $\delta_{\text{sink}}$  removed an edge, as can be seen in Figure 19(b). Note that in state  $\gamma_{ij}$  there are no isolated nodes, while in state  $\gamma_{i,j+1} = \delta_{\text{sink}}(\gamma_{ij})$  the set of isolated nodes is  $\{p_1\}$ .

Definition 50. A sink reduction sequence  $\Delta_{sink}$  is defined as a finite sequence of sink reduction steps  $\delta_{sink}$ , such that (i)  $\gamma_{ij} \mapsto \gamma_{i,j+1} \mapsto \cdots \mapsto \gamma_{i,j+k}$ ; (ii)  $\gamma_{i,j+k}$  is irreducible; and (iii)  $\{\gamma_{i,j+h}, 0 \leq h < k\}$  are all reducible. An equation expression of sink reduction sequence  $\Delta_{sink}$  is  $\gamma_{i,j+k} = \Delta_{sink}(\gamma_{ij}) = \delta_{sink}(\cdots \delta_{sink}(\delta_{sink}(\gamma_{ij}))\cdots)$ , where the sink reduction step  $\delta_{sink}$  is applied recursively  $k \geq 0$  times until  $\gamma_{i,j+k}$  is irreducible. The formula  $\Delta_{sink}(\gamma_{ij})$  is shown in Algorithm 1.

#### Algorithm 1. Sink Reduction Sequence Algorithm

```

1

\Delta_{sink} (\gamma_{ij}) \{

2

k=0;

3

\gamma_{iterate} = \gamma_{ij};

while (\alpha(\gamma_{iterate}) \neq \emptyset) {

4

k = k + 1;

5

6

\gamma_{temp} = \delta_{sink}(\gamma_{iterate})

=(V(\gamma_{iterate}), E(\gamma_{iterate}) - E_{\alpha_{iterate}});

\gamma

\gamma_{iterate} = \gamma_{temp};

8

9

\gamma_{i,j+k} = \gamma_{iterate};

return \gamma_{i,j+k};

10

11

}

```

The right hand side of line 6 in Algorithm 1 is the core of the algorithm:  $\delta_{sink}(\gamma_{iterate})$  is calculated recursively on itself until there are no more sink edges left in  $\gamma_{iterate}$ . Equation 3 below shows another way of expressing the execution of Algorithm 1 to perform a sink reduction sequence, where each  $\gamma_{iterate}$  is replaced with  $\gamma_{i,j+h}$  where h has the appropriate value corresponding to the algorithm iteration step:

$$\operatorname{if} \alpha(\gamma_{ij}) \neq \{\emptyset\}, \qquad \gamma_{i,j+1} = \delta_{sink}(\gamma_{ij}) = (V, E(\gamma_{ij}) - E_{\alpha_{ij}}) \\

\operatorname{if} \alpha(\gamma_{i,j+1}) \neq \{\emptyset\}, \qquad \gamma_{i,j+2} = \delta_{sink}(\gamma_{i,j+1}) = (V, E(\gamma_{i,j+1}) - E_{\alpha_{i,j+1}}) \\

\vdots \qquad \vdots \\

\operatorname{if} \alpha(\gamma_{i,j+k-1}) \neq \{\emptyset\}, \quad \gamma_{i,j+k} = \delta_{sink}(\gamma_{i,j+k-1}) = (V, E(\gamma_{i,j+k-1}) - E_{\alpha_{i,j+k-1}}) \\

\alpha(\gamma_{i,j+k}) = \{\emptyset\}.$$

**Definition 51.** A system state  $\gamma_{i,j+k}$  is said to be completely reduced if  $E(\gamma_{i,j+k}) = \emptyset$ . Otherwise, a system state  $\gamma_{i,j+k}$  is said to be incompletely reduced if  $E(\gamma_{i,j+k}) \neq \emptyset$ .

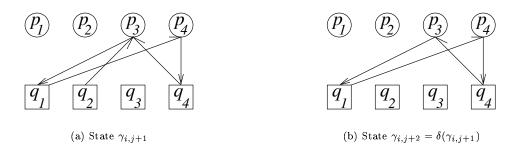

**Example 24.** Let us apply the sink reduction sequence  $\Delta_{sink}$  to two examples. We will consider a deadlocked example first and then a non-deadlocked case.

For the first example,  $\gamma_{ij}$  is the same as in Example 23:  $\gamma_{ij} = (V, E) = (\{P \cup Q\}, \{R \cup G\})$  as shown in Figure 19.

```

P = \{p_1, p_2, p_3, p_4\} \text{ and } Q = \{q_1, q_2, q_3, q_4\}. For the request set, we have R = \{(p_2, q_4), (p_4, q_4), (p_3, q_1), (p_3, q_2)\}, For the grant set, we have G = \{(q_2, p_1), (q_1, p_4), (q_4, p_3), (q_3, p_4), (q_3, p_4)\}.

```

The result is shown as follows:

$$\alpha(\gamma_{ij}) = \{p_1\}$$

$$E_{\alpha_{ij}} = \{(q_2, p_1)\}$$

$$\gamma_{i,j+1} = (V, \{(p_2, q_4), (p_4, q_4), (p_3, q_1), (p_3, q_2)\} \cup \{(q_2, p_1), (q_1, p_4), (q_4, p_3)\} - \{(q_2, p_1)\})$$

$$= (V, \{(p_2, q_4), (p_4, q_4), (p_3, q_1), (p_3, q_2)\} \cup \{(q_1, p_4), (q_4, p_3)\})$$

$$\alpha(\gamma_{i,j+1}) = \{\emptyset\}$$

Therefore, we stop and find that k = 1. Note that the result  $\gamma_{i,j+1}$  is incompletely reduced since  $E(\gamma_{i,j+1}) \neq \emptyset$ .

FIGURE 20. Apply Sink Reduction Sequence  $\Delta_{sink}$  to State  $\gamma_{ij}$ .

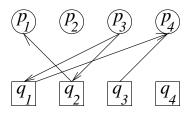

For the second example shown in Figure 20, the  $\gamma_{ij} = (V, E) = (\{P \cup Q\}, \{R \cup G\})$  is given as follows:

$$P = \{p_1, p_2, p_3, p_4\}$$

and  $Q = \{q_1, q_2, q_3, q_4\}.$

$$R = \{(p_3, q_1), (p_3, q_2)\}\$$

and  $G = \{(q_2, p_1), (q_1, p_4), (q_3, p_4)\}.$

The result of the first sink reduction step is shown as follows:

$$\alpha(\gamma_{ij}) = \{p_1, p_4\}$$

$$E_{\alpha_{ij}} = \{(q_2, p_1), (q_1, p_4), (q_3, p_4)\}$$

$$\gamma_{i,j+1} = (V, \{(p_3, q_1), (p_3, q_2), (q_2, p_1), (q_1, p_4), (q_3, p_4)\} - \{q_2, p_1), (q_1, p_4), (q_3, p_4)\}$$

$$\gamma_{i,j+1} = (V, \{(p_3, q_1), (p_3, q_2)\})$$

Figure 21 shows the result after one sink reduction step. Resources  $q_1$  and  $q_2$  have now become sink nodes. Therefore, they are removed by the next sink reduction step:

FIGURE 21. After one Sink Reduction Step  $\delta_{sink}$

$$\alpha(\gamma_{i,j+1}) = \{q_1, q_2\}$$

$$E_{\alpha_{i,j+1}} = \{(p_3, q_1), (p_3, q_2)\}$$

$$\gamma_{i,j+2} = (V, \{(p_3, q_1), (p_3, q_2)\} - \{(p_3, q_1), (p_3, q_2)\})$$

$$\gamma_{i,j+2} = (V, \emptyset)$$

$$\alpha(\gamma_{i,j+2}) = \emptyset$$

We stop and find that k = 2. Note that the result  $\gamma_{i,j+2}$  is completely reduced since  $E(\gamma_{i,j+2}) = \emptyset$ . Also note that the second sink reduction step assumes that resources  $q_1$  and  $q_2$  were both granted to and then released by processor  $p_3$ .

A sink reduction step  $\delta_{sink}$  of a state (thus removing edges to sink nodes) might unblock a waiting processor, e.g., as happened to processor  $p_3$  in the example above. Depending on which order requests are turned into grants, in fact deadlock could arise. Such an occurrence is equivalent to a safe state becoming a deadlock state (see Section 2.2). The sink reduction step as we have defined it takes an optimistic view about the future behavior of a system in state  $\gamma_{ij}$ ; in other words, if a safe sequence of requests and grants that keeps the system  $\gamma_i$  out of deadlock exists, then the sink reduction step assumes that this safe sequence is in fact the sequence that will be chosen.

**Theorem 2.** A processor  $p_i$  is not part of a deadlock cycle in state  $\gamma_{ij}$  iff there exists a sequence of sink reduction steps in  $\gamma_{ij}$  which allows processor  $p_i$  to be able to acquire all requested resources.

**Proof:** The proof is also available in Chapter 4 of Operating Systems - Advanced Concepts[1].

**Lemma 2.** A cycle C in system state  $\gamma_{ij}$  must contain alternating resource nodes and processor nodes.

**Proof:** By Definition 6,  $\gamma_{ij}$  cannot have any edge from processor  $p_i$  to processor  $p_j$  for any two processors  $p_i$ ,  $p_j \in V(\gamma_{ij})$ . Similarly, by Definition 6,  $\gamma_{ij}$  cannot have any edge from resource  $q_i$  to resource  $q_j$  for any two resources  $q_i$ ,  $q_j \in V(\gamma_{ij})$ . Therefore, since cycle C is composed of edges, any cycle C must contain alternating resource nodes and processor nodes connected by edged.

**Lemma 3.** In a system state  $\gamma_{ij}$ , the number of edges in a cycle must be a multiple of 2.

**Proof:** This lemma follows trivially from Lemma 2 and the definition of a cycle, Definition 46.

**Theorem 3.** Let  $\gamma_{ij}$  be an expedient state of a reusable resource system  $\gamma_i$ . Sink reduction sequence  $\Delta_{sink}(\gamma_{ij})$  reduces the state  $\gamma_{ij}$  to a state  $\gamma_{i,j+k}$  which is irreducible. State  $\gamma_{ij}$  is not a deadlock state if and only if  $\gamma_{i,j+k}$  is completely reduced  $(E(\gamma_{i,j+k}) = \emptyset)$ .

**Proof:** The proof is available as Theorem 4.3 in Chapter 4 of Operating Systems – Advanced Concepts[1]. By Theorem 3, if the state  $\gamma_{ij}$  is expedient, then detection of a cycle in  $\gamma_{ij}$  will be a sufficient condition for determining that  $\gamma_{ij}$  is a deadlock state.

Corollary 1. If state  $\gamma_{i,j+k} = \Delta_{sink}(\gamma_{ij})$  is completely reduced  $(E(\gamma_{i,j+k}) = \emptyset)$ , then  $\gamma_{ij}$  is not a deadlock state.

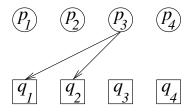

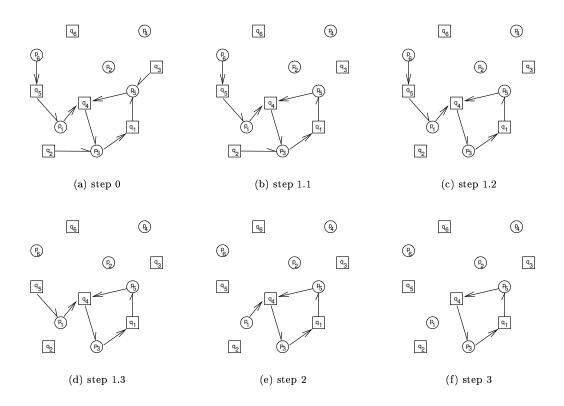

Example 25. In Figure 22 (a), the system state is expedient. The set of sink nodes is  $\Sigma_{\alpha} = \{p_2\}$ . The set of link nodes is  $\Sigma_{\lambda} = \{q_5, p_1, q_4, p_5, q_1, p_3\}$ , while the set of source nodes is  $\Sigma_{\beta} = \{q_3, q_6, q_2\}$ . Therefore, a sink reduction step  $\delta_{sink}$  removes an edge  $(q_6, p_2)$  incident to the sink node  $p_2$ . The reduced state is shown in Figure 22 (b). At that time, the sink set  $\Sigma_{\alpha} = \{\emptyset\}$ , and hence the state is irreducible. Since the state in Figure 22 (b) contains non-empty set of connect nodes,  $\Sigma_{\tau} \neq \emptyset$ , the original state shown in Figure 22 (a) is deadlocked. Note that Figure 22 (b) contains two dangling paths which do not participate in the deadlock cycle C.

## Algorithm 2. Deadlock Detection Algorithm Reducing Sink Nodes

```

\begin{array}{ll} 1 & Deadlock\_Detect\_Sink \; (\gamma_{ij}) \; \{ \\ 2 & \gamma_{i,j+k} = \Delta_{sink}(\gamma_{ij}); \\ 3 & if \; (E(\gamma_{i,j+k}) = \emptyset) \; \{ \\ 4 & return \; 0; \; / * \; no \; deadlock \; * / \\ 5 & \} \; else \; \{ \\ 6 & return \; 1; \; / * \; deadlock \; detected \; * / \\ 7 & \} \\ 8 & \} \end{array}

```

Figure 22. A System state that is Irreducible.

Algorithms 1 and 2 represent the classical solution for deadlock detection [2, 3, 1]. This solution and all other solutions known to the author take time  $O_{sw}(m \times n)$ , where the "sw" in " $O_{sw}$ " refers to the fact that the algorithm is run in software on a processor. Although other authors give their algorithm complexity in terms of e = ||E||,  $e \le m \times n$  so that  $O_{sw}(e) = O_{sw}(m \times n)$  [4, 6].

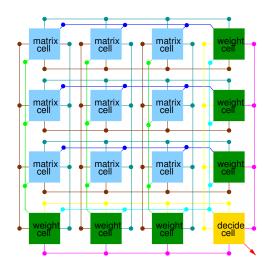

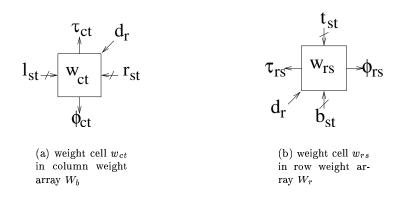

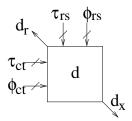

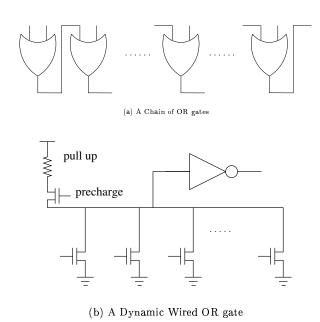

#### 4. Equivalent Deadlock Detection Theorem

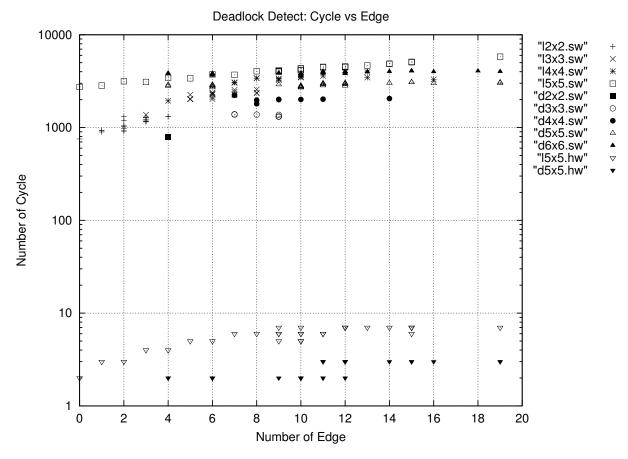

In this section we will define a new algorithm for deadlock detection with  $O_{sw}(m \times n)$ . The advantage of this new algorithm will not be seen until the next section when we show how to implement the algorithm in a matrix form. This matrix form can be implemented in hardware yielding complexity  $O_{hw}(min(m,n))$ , where the "hw" in " $O_{hw}$ " refers to the fact that the algorithm is run in a special hardware configuration (to be explained in detail in Section 6).