## RELIABLE FINE-PITCH CHIP-TO-SUBSTRATE COPPER INTERCONNECTIONS WITH HIGH-THROUGHPUT ASSEMBLY AND HIGH POWER-HANDLING

A Dissertation Presented to The Academic Faculty

by

Ninad Makarand Shahane

In Partial Fulfillment of the Requirements for the Degree Doctorate of Philosophy in the School of Material Science and Engineering

> Georgia Institute of Technology August 2018

## **COPYRIGHT © 2018 BY NINAD MAKARAND SHAHANE**

### RELIABLE FINE-PITCH CHIP-TO-SUBSTRATE COPPER INTERCONNECTIONS WITH HIGH-THROUGHPUT ASSEMBLY AND HIGH POWER-HANDLING

Approved by:

Dr. Rao R. Tummala, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Antonia Antoniou, Co-Advisor School of Mechanical Engineering *Georgia Institute of Technology*

Dr. Naresh Thadhani School of Material Science Engineering *Georgia Institute of Technology*  Dr. Pulugurtha Raj Markondeya School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Preet Singh School of Material Science Engineering Georgia Institute of Technology

Dr. Vanessa Smet School of Electrical and Computer Engineering *Georgia Institute of Technology*

Date Approved: June 18, 2018

Dedicated to my parents, Makarand and Seema

And to my love, Damini

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my advisor, Professor Rao R. Tummala for his vision and ambition, his close guidance towards interdisciplinary research, and for providing extraordinary opportunities of close cooperation with industry partners. I would also like to thank my co-advisor Prof. Antonia Antoniou for exceptional guidance. Her constant push towards deep scientific inquiry encouraged and inspired me towards completing this Ph.D. thesis. I also thank my committee members, Professor Naresh Thadhani, Professor Preet Singh, Dr. Vanessa Smet and Dr. P.M. Raj for their willing and valuable inputs. I would especially like to thank my mentors, Dr. Vanessa Smet and Dr. Raj Pulugurtha for their knowledgeable inputs, painstaking mentoring, and the creative flexibilities they afforded me throughout the course of my research.

I would like to extend my appreciation to all my research family at the Georgia Tech 3D System Research Center, especially Kashyap, Vidya, Siddharth, and Bhupender for their support in creating a happy and comfortable environment, through the ups and downs that we have shared together. I thank our visiting engineers, Satomi Kawamoto, Yutaka Takagi, and Hiroyuki Matsuura for their technical supports; and thank the interns, Laura Wambera, and Ramon Sosa who made direct contributions to this thesis. I would like to specially thank Scott McCann for ANSYS modeling and frequent discussions, and Chandrasekharan Nair for constructive discussions on materials processing.

I would like to thank my family for their unconditional love and support in helping me achieving my ambitions. Finally, I also thank my love and wife to be, Damini Gandham for being a pillar of faith and support and for encouraging me to always better myself.

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | iv                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | viii                                                                          |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ix                                                                            |

| LIST OF SYMBOLS AND ABBREVIATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | xvii                                                                          |

| SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | XX                                                                            |

| <ul> <li>CHAPTER 1. INTRODUCTION</li> <li>1.1 Research Motivation and Strategic Need <ol> <li>1.1 Pitch scaling for emerging systems</li> <li>1.2 Evolution of interconnection and assembly technologies</li> <li>1.3 State-of-the-art in all-Cu interconnections – the 'holy grail'</li> </ol> </li> <li>1.2 Research Objectives and Technical Challenges <ol> <li>1.2.1 High-throughput assembly</li> <li>2.2 Reliability of chip-to-substrate system (C2S) with CTE mismatch</li> </ol> </li> <li>1.3 Proposed Unique Approach <ol> <li>A Research Tasks</li> <li>1.4.1 Research Task 1: Modeling, design, and demonstration of copper interconnection system for improved reactivity and accommodation of non-coplanarities</li> <li>1.4.2 Research Task 2: Design and demonstration of high-speed assembly of Cu interconnections <ol> <li>A Research Task 3: Design and demonstration for reliability at interconnectior and IC level</li> </ol> </li> </ol></li></ul> | 1<br>2<br>7<br>11<br>14<br>15<br>17<br>18<br>20<br>20<br>20<br>21<br>22<br>23 |

| CHAPTER 2. LITERATURE REVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24                                                                            |

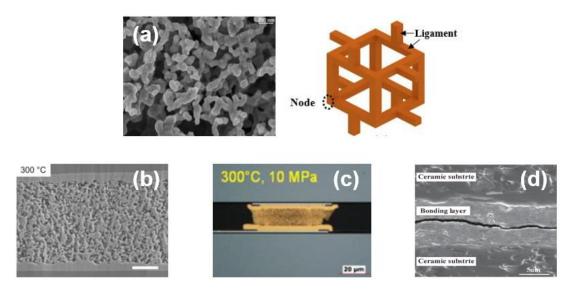

| 2.1 High-throughput Assembly<br>2.1.1 Improving interfacial reactivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>25</b><br>26                                                               |

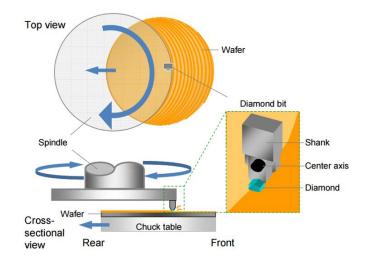

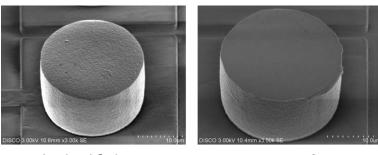

| <ul> <li>2.1.2 Achieving planar contact</li> <li>2.1.3 High-speed assembly</li> <li>2.1.4 Nano-sintering at low-temperature</li> <li><b>2.2 Reliability in chip-package architecture</b></li> <li>2.2.1 Failure modes in Cu pillar flip-chip packages</li> <li>2.2.2 Reliability challenges in stiff-interconnections</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30<br>35<br>38<br>46<br>46<br>47                                              |

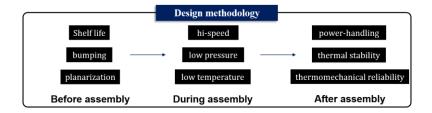

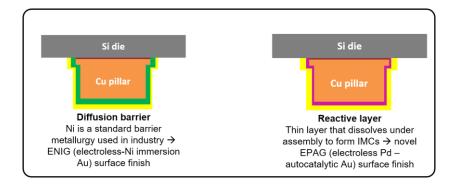

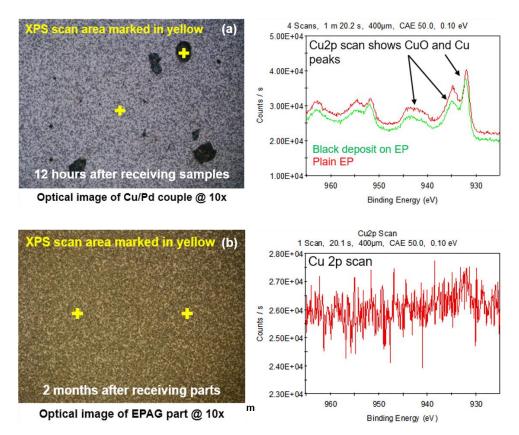

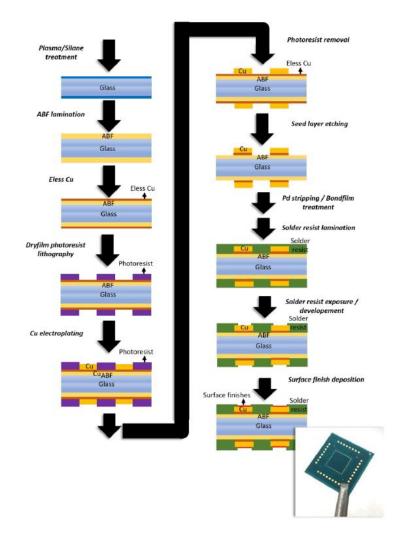

| <ul> <li>CHAPTER 3. CU INTERCONNECTIONS WITH METALLIC COATINGS</li> <li>3.1 Materials Design</li> <li>3.1.1 Design Methodology</li> <li>3.1.2 Design before assembly</li> <li>3.1.3 Design for assembly</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>50</b><br><b>50</b><br>50<br>52<br>58                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 61                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

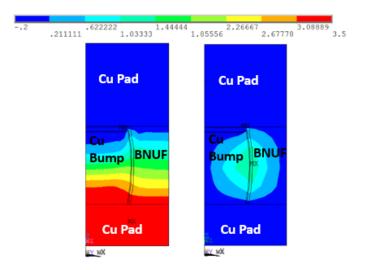

| 3.2 Thermomechanical Process Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65                                                                                                                                                                   |

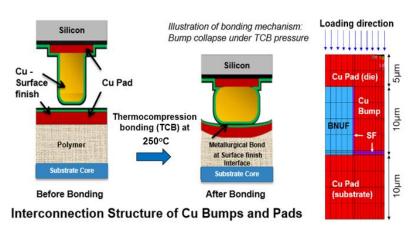

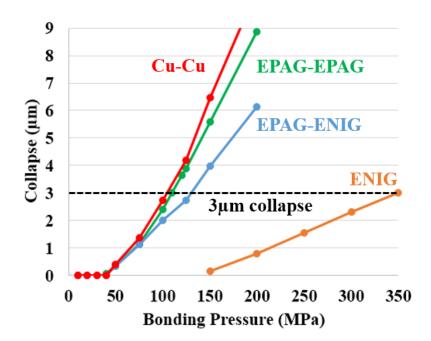

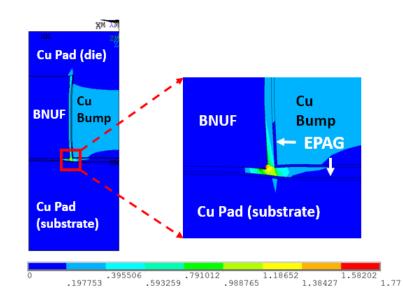

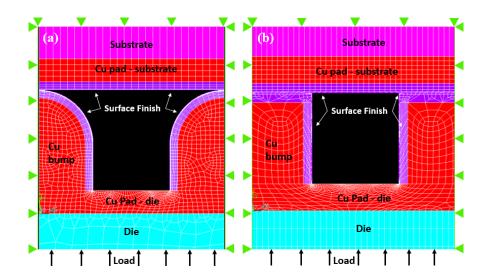

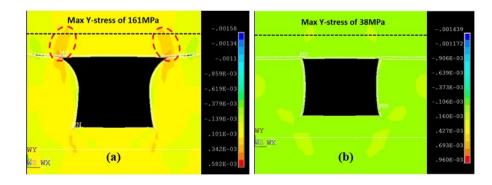

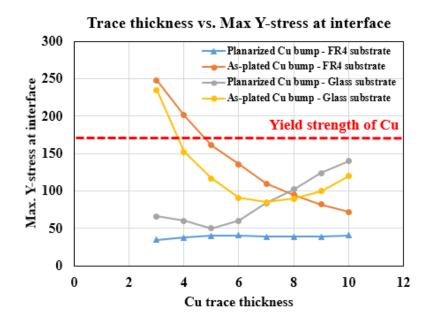

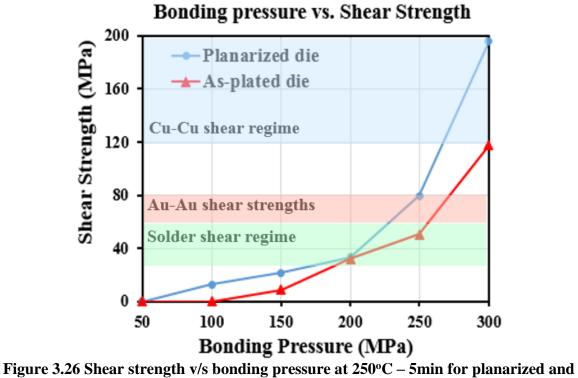

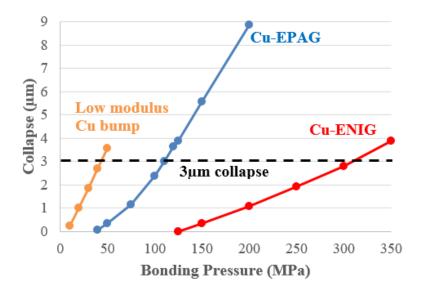

| 3.2.1 Effect of surface finish                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67                                                                                                                                                                   |

| 3.2.2 Effect of planarization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71                                                                                                                                                                   |

| 3.3 Test Vehicle Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>78</b>                                                                                                                                                            |

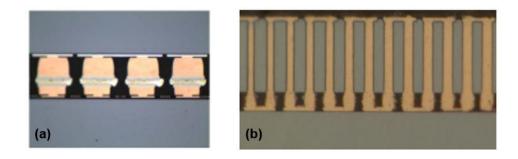

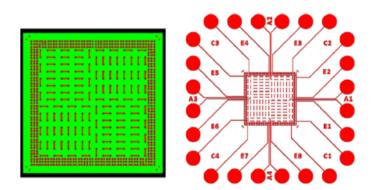

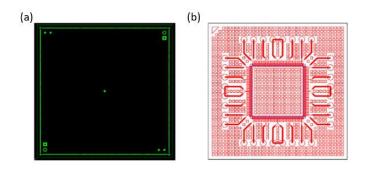

| 3.3.1 Test Vehicle 1 (TV1) at 100µm pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79                                                                                                                                                                   |

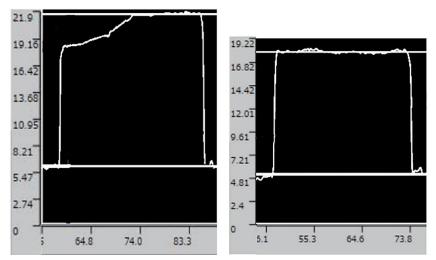

| 3.3.2 Test Vehicle 2 (TV2) at 40µm pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80                                                                                                                                                                   |

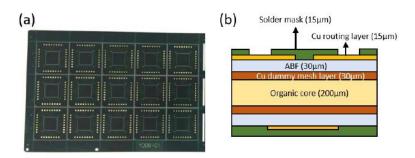

| 3.3.3 Test Vehicle 3 (TV3) at 50µm pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83                                                                                                                                                                   |

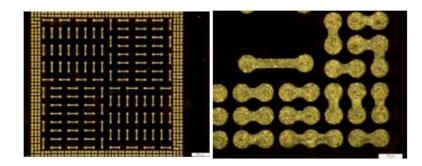

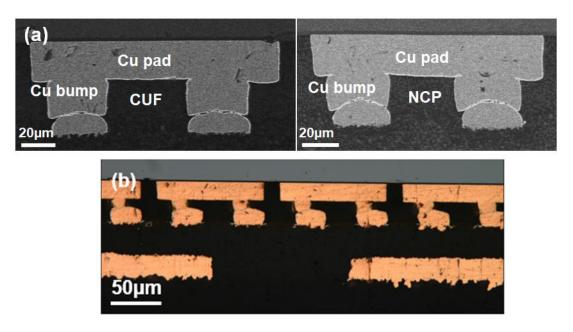

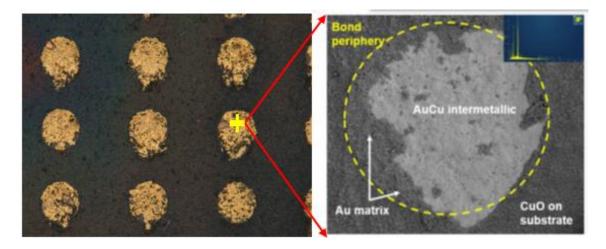

| 3.4 Assembly Demonstration and Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85                                                                                                                                                                   |

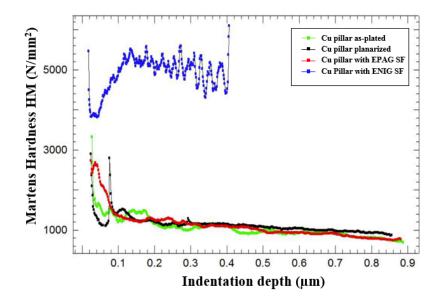

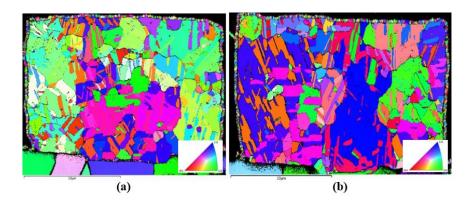

| 3.4.1 Material Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85                                                                                                                                                                   |

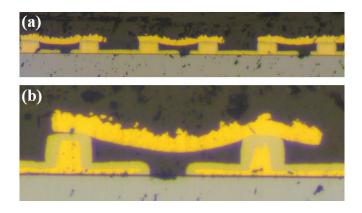

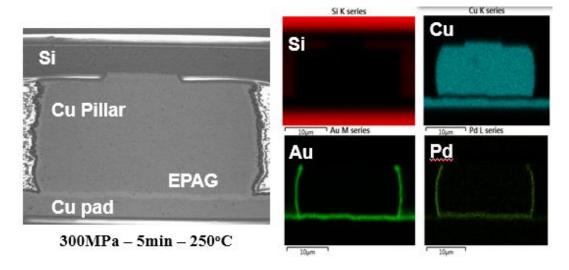

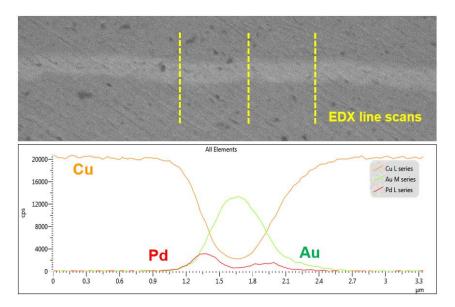

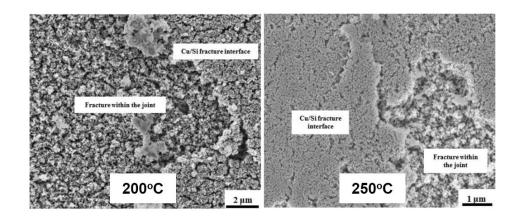

| 3.4.2 Validation of FEM models through assembly demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88                                                                                                                                                                   |

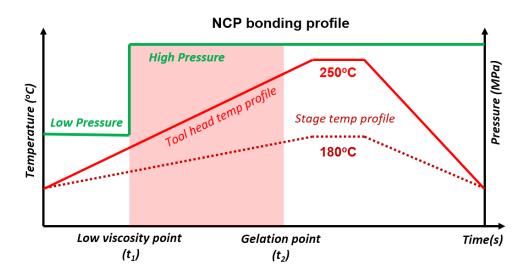

| 3.4.3 Hi-speed assembly with TC-NCP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 92                                                                                                                                                                   |

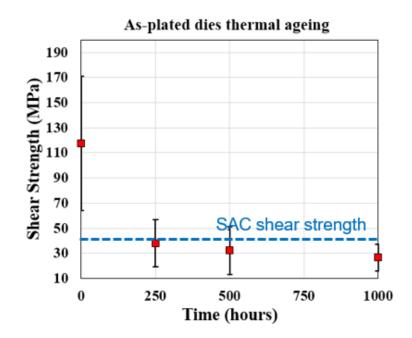

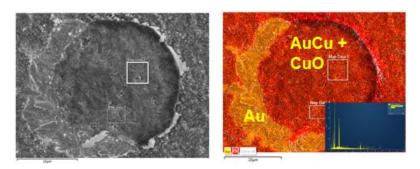

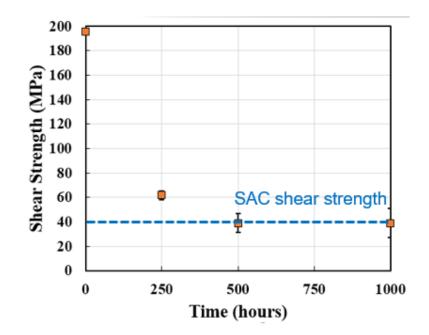

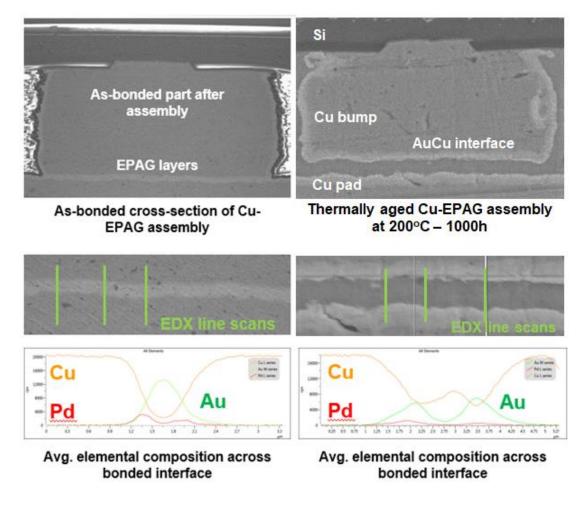

| 3.5 Thermal Ageing Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100                                                                                                                                                                  |

| 3.6 Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 104                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                      |

| CHAPTER 4. RELIABILITY OF CU-EPAG INTERCONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 106                                                                                                                                                                  |

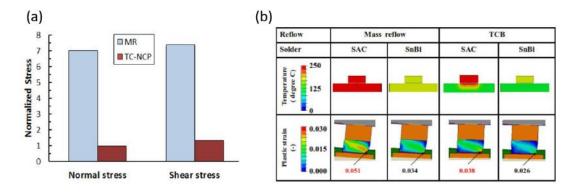

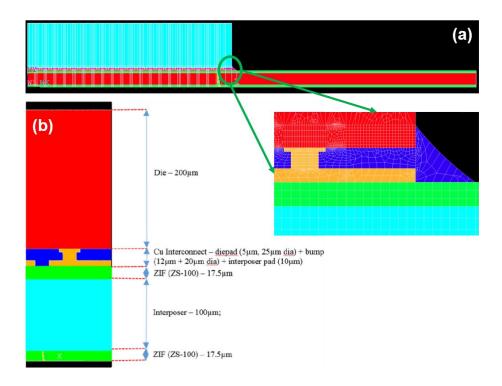

| 4.1 Reliability Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 106                                                                                                                                                                  |

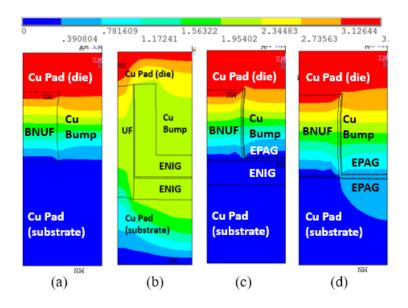

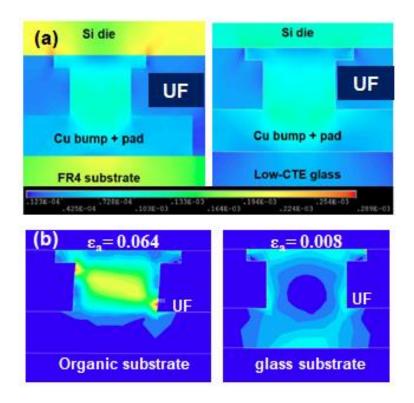

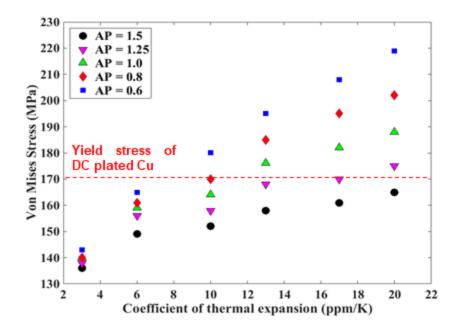

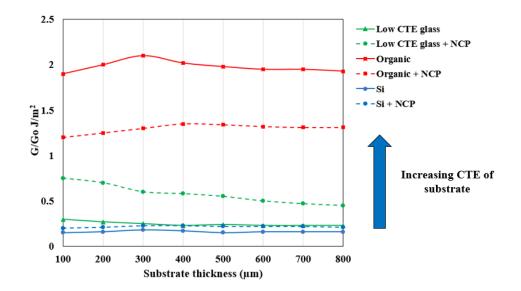

| 4.1.1 Thermomechanical reliability of Cu-EPAG interconnection system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 106                                                                                                                                                                  |

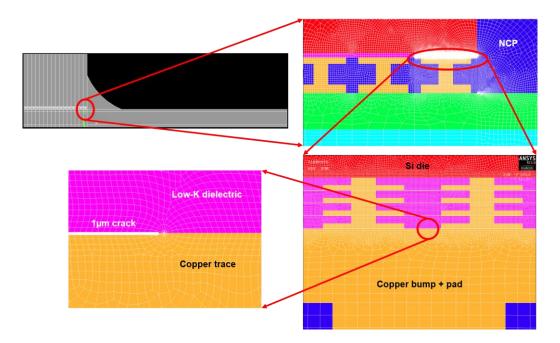

| 4.1.2 Low-K reliability at IC level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 112                                                                                                                                                                  |

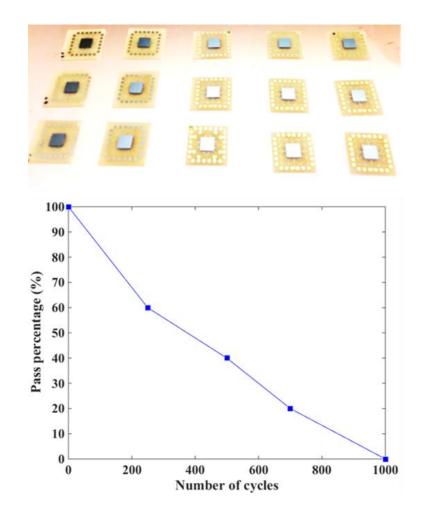

| 4.2 Thermomechanical Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 115                                                                                                                                                                  |

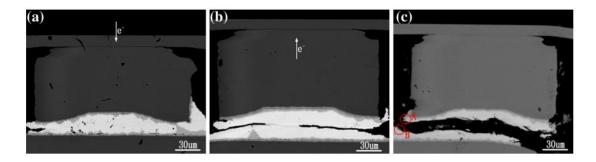

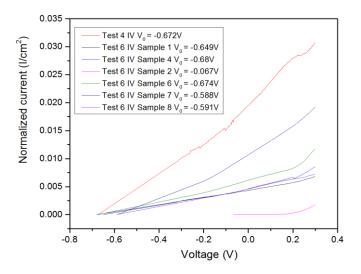

| 4.3 Electromigration Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 118                                                                                                                                                                  |

| 4.4 Summary of reliability characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 121                                                                                                                                                                  |

| CHADTED 5 CUDILLAD INTEDCONNECTIONS WITH NANOCODDED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

| CHAPTER 5. CU PILLAR INTERCONNECTIONS WITH NANOCOPPER<br>FOAM CAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 123                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 143                                                                                                                                                                  |

| S I Inforeonnoetion System Hostan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 123                                                                                                                                                                  |

| 5.1 Interconnection System Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

| 5.1.1 Motivation for low-modulus Cu interconnections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 123                                                                                                                                                                  |

| <ul><li>5.1.1 Motivation for low-modulus Cu interconnections</li><li>5.1.2 Design of precursor system for nano-Cu foams</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 123<br>128                                                                                                                                                           |

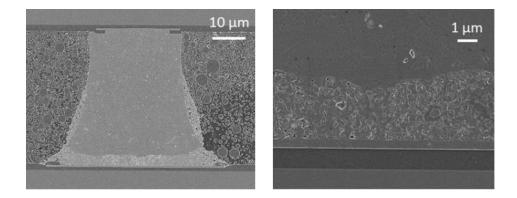

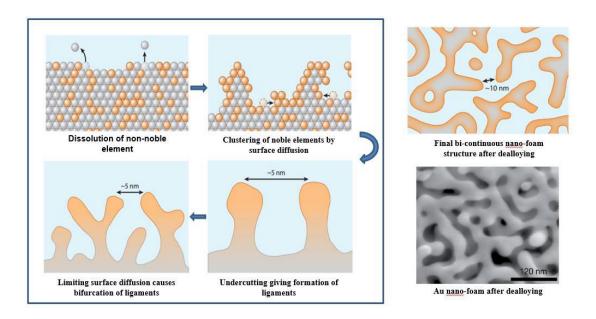

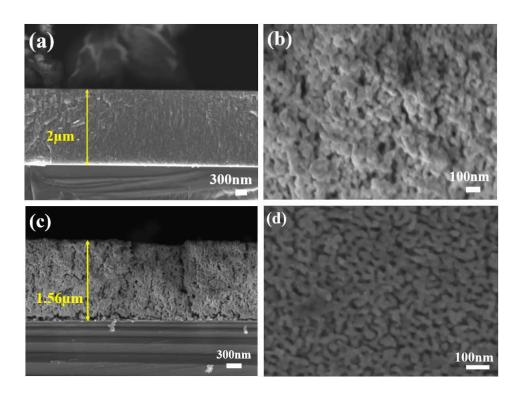

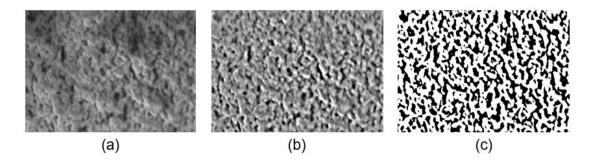

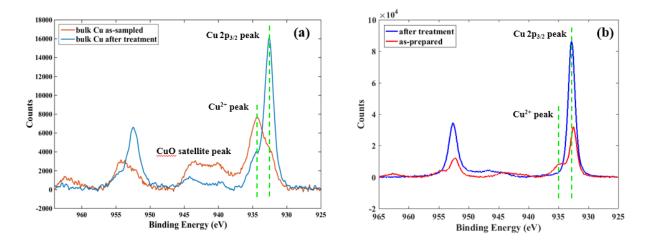

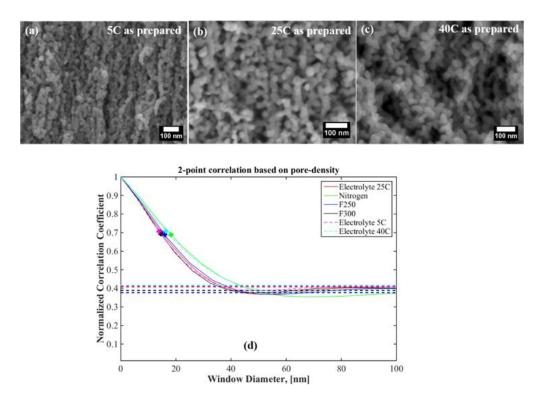

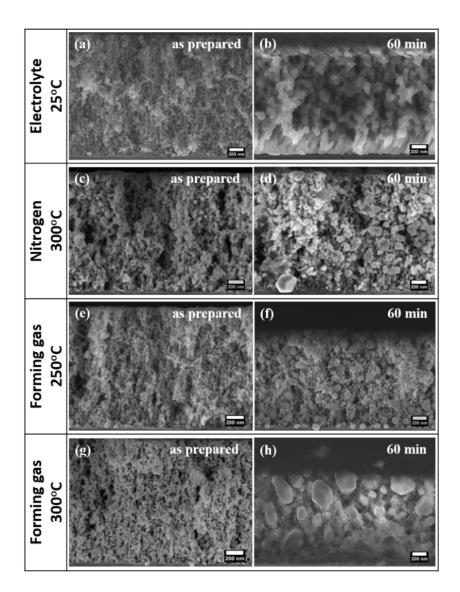

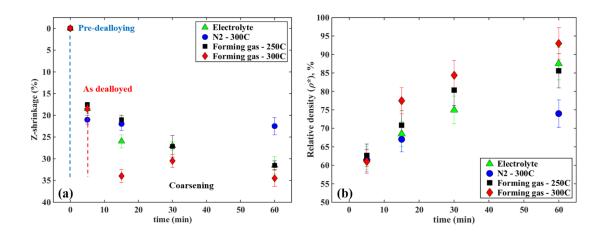

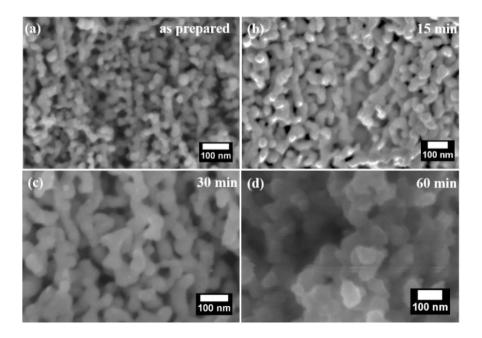

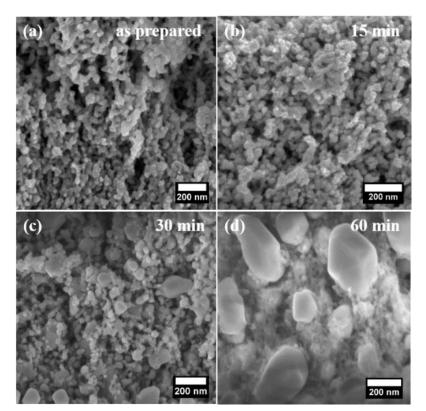

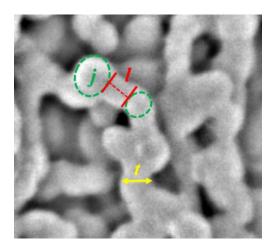

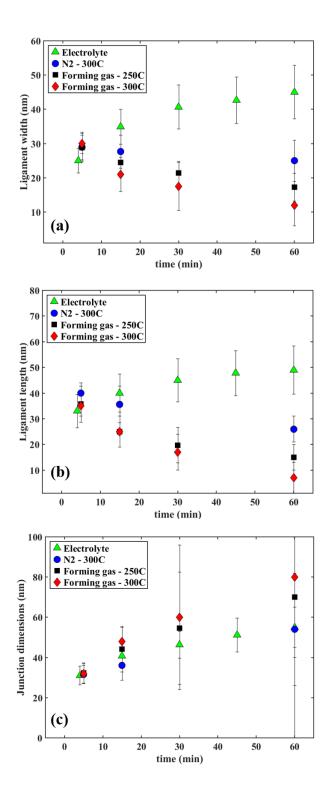

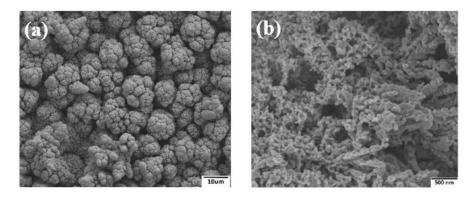

| <ul><li>5.1.1 Motivation for low-modulus Cu interconnections</li><li>5.1.2 Design of precursor system for nano-Cu foams</li><li>5.1.3 Dealloying and pre-assembly characterization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>123</b><br>123<br>128<br>130                                                                                                                                      |

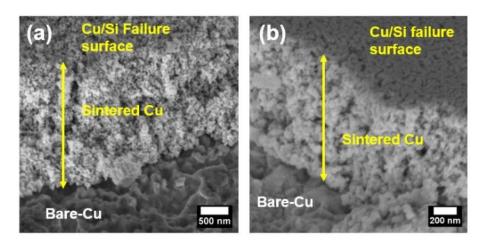

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 123<br>128<br>130<br>138                                                                                                                                             |

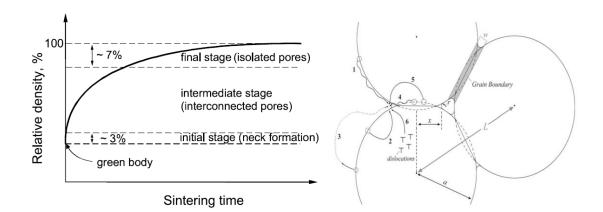

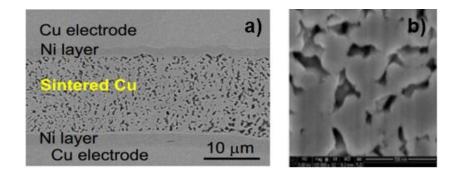

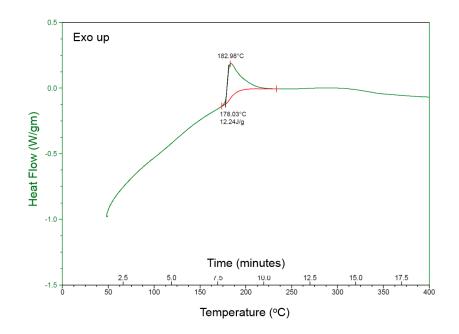

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 123<br>128<br>130<br>138<br>141                                                                                                                                      |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 123<br>128<br>130<br>138<br>141<br><b>163</b>                                                                                                                        |

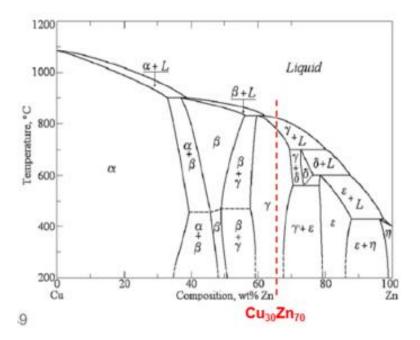

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164                                                                                                                 |

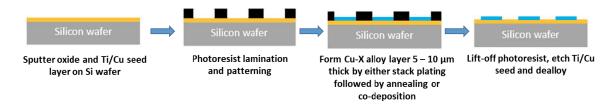

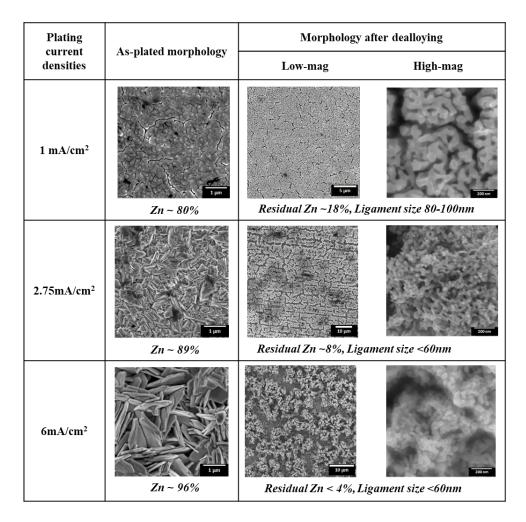

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165                                                                                                          |

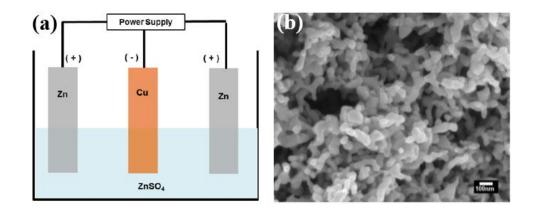

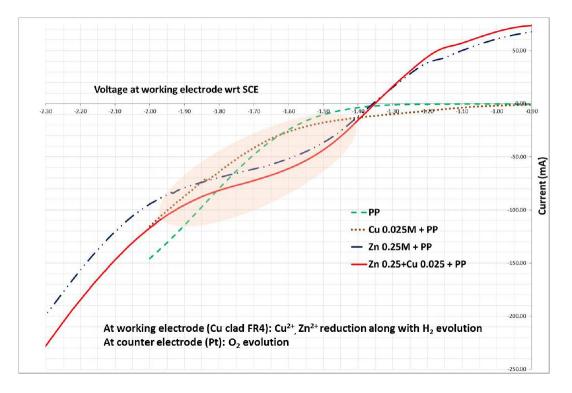

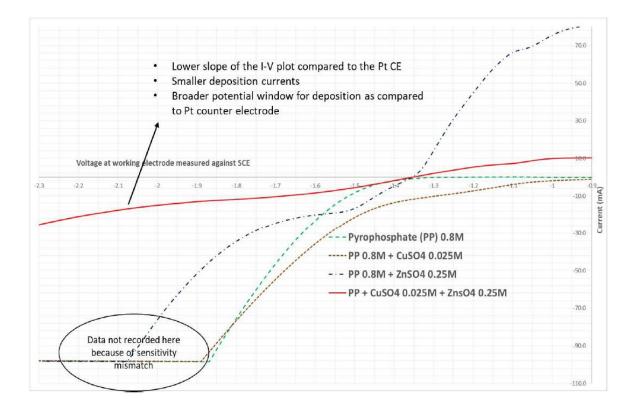

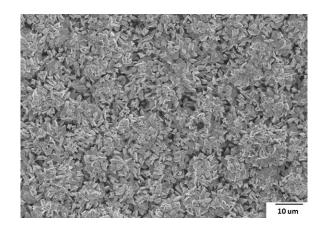

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                              | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166                                                                                                   |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> <li>5.2.4 Fine-pitch patternability</li> </ul>                                                                                                                                                                                                                                                                                                                                                     | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166<br>174                                                                                            |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> <li>5.2.4 Fine-pitch patternability</li> </ul>                                                                                                                                                                                                                                                                                                                                                     | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166<br>174<br><b>176</b>                                                                              |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> <li>5.2.4 Fine-pitch patternability</li> </ul>                                                                                                                                                                                                                                                                                                                                                     | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166<br>174                                                                                            |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> <li>5.2.4 Fine-pitch patternability</li> </ul>                                                                                                                                                                                                                                                                                                                                                     | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166<br>174<br><b>176</b><br><b>180</b>                                                                |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> <li>5.2.4 Fine-pitch patternability</li> <li>5.3 Fine-pitch Assembly Demonstration</li> <li>5.4 Chapter Summary</li> </ul>                                                                                                                                                                                                                                                                         | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166<br>174<br><b>176</b>                                                                              |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> <li>5.2.4 Fine-pitch patternability</li> <li>5.3 Fine-pitch Assembly Demonstration</li> <li>5.4 Chapter Summary</li> </ul>                                                                                                                                                                                                                                                                         | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166<br>174<br><b>176</b><br><b>180</b><br><b>181</b><br><b>181</b>                                    |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> <li>5.2.4 Fine-pitch patternability</li> <li>5.3 Fine-pitch Assembly Demonstration</li> <li>5.4 Chapter Summary</li> <li>CHAPTER 6. SUMMARY AND CONCLUSIONS</li> <li>6.1 Research Summary</li> <li>6.1.1 Modelling, design, and demonstration of copper interconnection system for</li> </ul>                                                                                                      | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166<br>174<br><b>176</b><br><b>180</b><br><b>181</b><br><b>181</b>                                    |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> <li>5.2.4 Fine-pitch patternability</li> <li>5.3 Fine-pitch Assembly Demonstration</li> <li>5.4 Chapter Summary</li> <li>CHAPTER 6. SUMMARY AND CONCLUSIONS</li> <li>6.1 Research Summary</li> <li>6.1.1 Modelling, design, and demonstration of copper interconnection system for improved reactivity and accommodation of non-coplanarities</li> </ul>                                           | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166<br>174<br><b>176</b><br><b>180</b><br><b>181</b><br><b>181</b>                                    |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> <li>5.2.4 Fine-pitch patternability</li> <li>5.3 Fine-pitch Assembly Demonstration</li> <li>5.4 Chapter Summary</li> <li>6.1 Research Summary</li> <li>6.1.1 Modelling, design, and demonstration of copper interconnection system for improved reactivity and accommodation of non-coplanarities</li> <li>6.1.2 Design and demonstration of high-speed assembly of Cu interconnections</li> </ul> | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166<br>174<br><b>176</b><br><b>180</b><br><b>181</b><br><b>181</b><br><b>181</b>                      |

| <ul> <li>5.1.1 Motivation for low-modulus Cu interconnections</li> <li>5.1.2 Design of precursor system for nano-Cu foams</li> <li>5.1.3 Dealloying and pre-assembly characterization</li> <li>5.1.4 Proof-of-Concept</li> <li>5.1.5 Sintering kinetics of nanoporous copper</li> <li>5.2 Manufacturable Synthesis with Co-electrodeposition</li> <li>5.2.1 Choosing precursor alloy system</li> <li>5.2.2 Stack-plating of Cu-Zn and dealloying</li> <li>5.2.3 Co-electrodeposition of Cu-Zn and dealloying</li> <li>5.2.4 Fine-pitch patternability</li> <li>5.3 Fine-pitch Assembly Demonstration</li> <li>5.4 Chapter Summary</li> <li>6.1 Research Summary</li> <li>6.1.1 Modelling, design, and demonstration of copper interconnection system for improved reactivity and accommodation of non-coplanarities</li> <li>6.1.2 Design and demonstration of high-speed assembly of Cu interconnections</li> </ul> | 123<br>128<br>130<br>138<br>141<br><b>163</b><br>164<br>165<br>166<br>174<br><b>176</b><br><b>180</b><br><b>181</b><br><b>181</b><br><b>181</b><br><b>182</b><br>185 |

| 6.3  | Technical and Scientific Contributions | 192 |

|------|----------------------------------------|-----|

| REFE | RENCES                                 | 194 |

# LIST OF TABLES

| Table 1  | Research objectives beyond prior art and associated technical challenges                                                                            | 15  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

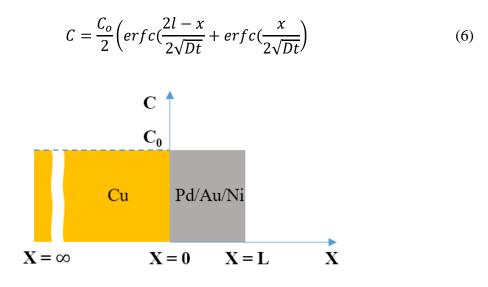

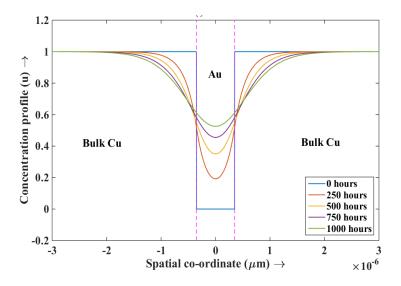

| Table 2  | Analytical diffusion modeling data                                                                                                                  | 61  |

| Table 3  | Isotropic elastic-plastic material properties for FEM model                                                                                         | 68  |

| Table 4  | Properties of materials within the substrate stack-up                                                                                               | 74  |

| Table 6  | Plain strain models for estimation of fatigure life                                                                                                 | 111 |

| Table 7  | Isotropic clastic-plastic material properties for low-modulus Cu                                                                                    | 125 |

| Table 8  | Comparison of thermal conductivity ( $\kappa$ ) and electrical resistivity ( $\rho$ ) between nanofoam and bulk system (at 300K).                   | 128 |

| Table 9  | Prior art on synthesis of nano-Cu foams                                                                                                             | 129 |

| Table 10 | Process parameters for Cu nanofoam-to-bulk Cu bonding                                                                                               | 139 |

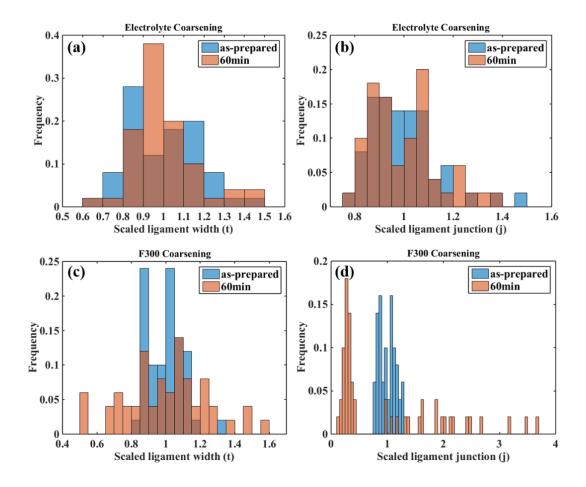

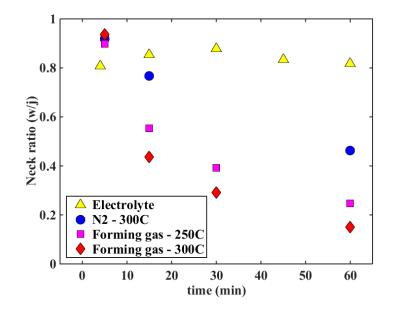

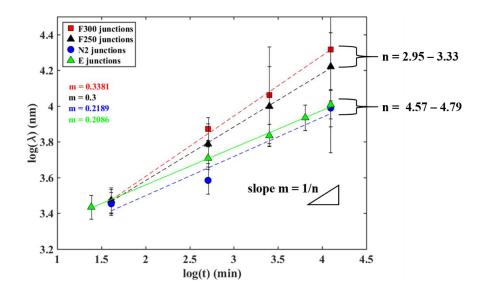

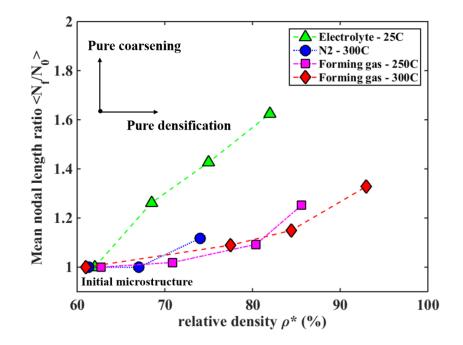

| Table 10 | Measured average ligament width (t) and junction dimensions (j) for Electrolyte and F300 samples across as-prepared and 60 min coarsened conditions | 155 |

## LIST OF FIGURES

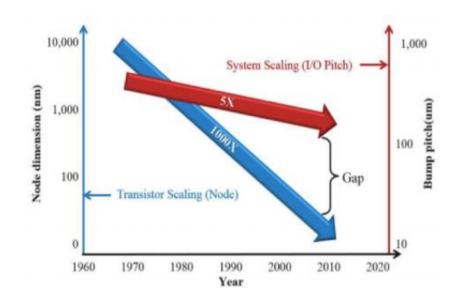

| Gap between transistor and system scaling (Courtesy Dr. S. Iyer, IBM)                                                                                                                   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

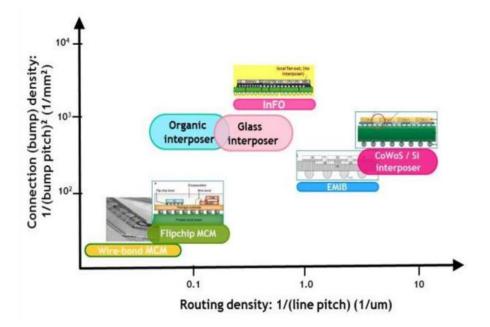

| Comparison of advanced packaging technologies: I/O density v/s routing density                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

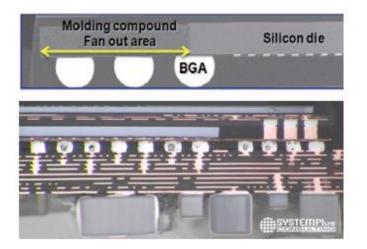

| (Top) TSMC's InFO package for processors and (bottom) TSMS processor-memory stacking                                                                                                    | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

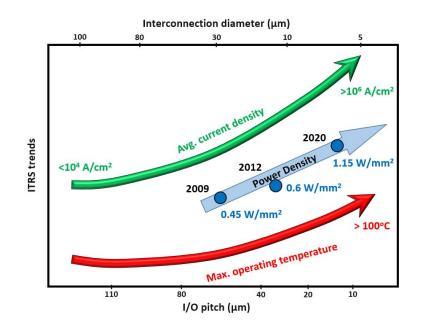

| ITRS roadmap predictions (arbitrary units) vs I/O pitch for high-<br>performance interconnections                                                                                       | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

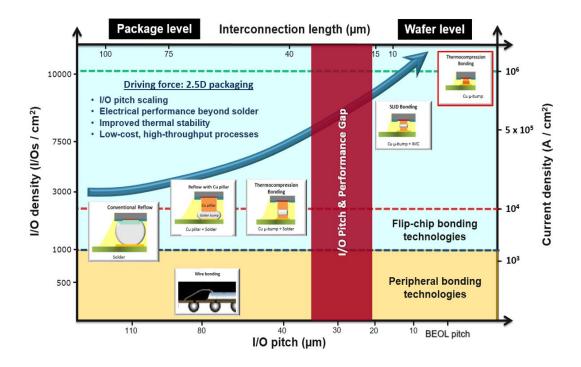

| Evolution of off-chip interconnection technologies for pitch and performance scaling                                                                                                    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Comparison of the most advanced industry-wide compatible technologies between the C2S and WLP applications                                                                              | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

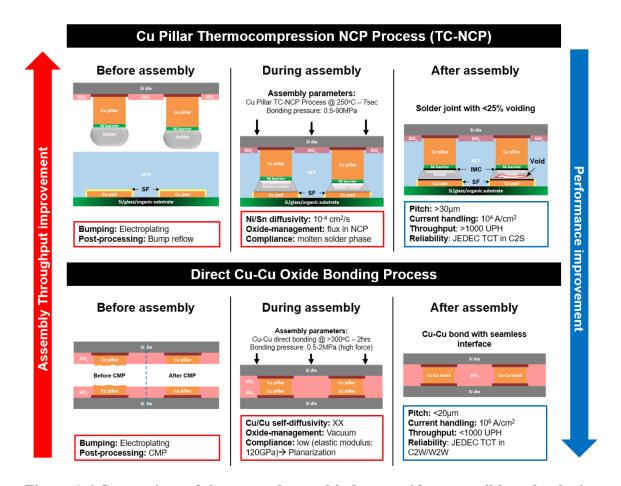

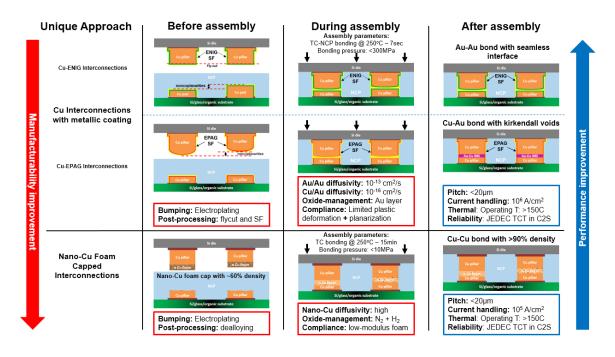

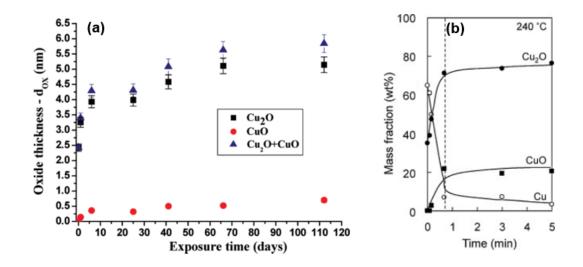

| Unique approaches beyond the current prior art for Cu interconnections without solders                                                                                                  | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |