## TECHNIQUES TO IMPROVE THE PERFORMANCE OF LARGE-SCALE DISCRETE-EVENT SIMULATION

A Dissertation Presented to The Academic Faculty

by

Brian Paul Swenson

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology August 2015

Copyright  $\bigodot$  2015 by Brian Paul Swenson

## TECHNIQUES TO IMPROVE THE PERFORMANCE OF LARGE-SCALE DISCRETE-EVENT SIMULATION

Approved by:

Professor George F. Riley, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Douglas M. Blough School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Aaron D. Lanterman School of Electrical and Computer Engineering Georgia Institute of Technology Professor Raheem A. Beyah School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Richard F. Fujimoto College of Computer Science Georgia Institute of Technology

Date Approved: April 30, 2015

## ACKNOWLEDGEMENTS

I would like to extend my gratitude to my advisor Dr. George Riley for his guidance and patience throughout my graduate study. Without his support I would have never been able to finish the program. I would also like to thank my dissertation committee members, Dr. Douglas M. Blough, Dr. Aaron D. Lanterman, Dr. Raheem A. Beyah, and Dr. Richard F. Fujimoto for their valuable advice and suggestions. I would also like to thank Dr. Tom Henderson for giving me many opportunities within the ns-3 community and for his support, guidance and patience.

Most importantly, I would like to thank my loving wife Jenni, and our two boys, Noah and Josh, for their unconditional love, encouragement, entertainment, understanding and support. Noah, I promise that I will have more free evenings to play Lego Marvel Universe now that this is done.

# TABLE OF CONTENTS

| AC            | KN(  | OWLE   | DGEMENTS                                                        | iii      |

|---------------|------|--------|-----------------------------------------------------------------|----------|

| LIS           | вт о | F TAE  | BLES                                                            | vii      |

| LIS           | бт о | F FIG  | URES                                                            | viii     |

| $\mathbf{SU}$ | MM.  | ARY .  |                                                                 | x        |

| Ι             | INT  | rod    | UCTION                                                          | 1        |

|               | 1.1  | Contri | ibutions                                                        | 2        |

|               | 1.2  | Disser | tation organization                                             | 4        |

| II            | OR   | IGIN . | AND HISTORY OF THE PROBLEM                                      | <b>5</b> |

|               | 2.1  | Discre | te-event simulation                                             | 5        |

|               | 2.2  | Parall | el discrete-event simulation                                    | 5        |

|               |      | 2.2.1  | Optimistic time-synchronization algorithms                      | 6        |

|               |      | 2.2.2  | Conservative time-synchronization algorithms                    | 7        |

|               |      | 2.2.3  | Maximizing lookahead                                            | 9        |

|               |      | 2.2.4  | Non-CPU hardware support for parallel discrete-event simulation | 10       |

| III           | AN   | NEW A  | APPROACH TO ZERO-COPY MESSAGE PASSING .                         | 12       |

|               | 3.1  | Tradit | ional message passing                                           | 14       |

|               | 3.2  | Zero-c | opy message passing                                             | 16       |

|               | 3.3  | Boost. | Interprocess C++ library                                        | 17       |

|               | 3.4  | Zero-c | opy message passing optimized for simulation                    | 19       |

|               |      | 3.4.1  | Custom smart pointer                                            | 19       |

|               |      | 3.4.2  | Shared heaps                                                    | 21       |

|               |      | 3.4.3  | Using zero-copy message passing in simulation                   | 25       |

|               | 3.5  | Evalua | ation                                                           | 28       |

|               | 3.6  | Discus | sion                                                            | 33       |

| IV  | CU    | RGE-SCALE DISCRETE-EVENT SIMULATION UTILIZINGDA WITH CONSERVATIVE TIME SYNCHRONIZATION TECHQUES34                                             |   |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|---|

|     | 4.1   | CUDA Overview                                                                                                                                 | 1 |

|     |       | 4.1.1 CUDA Execution Model                                                                                                                    | 1 |

|     |       | 4.1.2 Kernel Programming and Libraries                                                                                                        | 2 |

|     | 4.2   | Simulator Overview                                                                                                                            | 1 |

|     |       | 4.2.1 Memory Organization                                                                                                                     | 5 |

|     |       | 4.2.2 Simulator Execution                                                                                                                     | 3 |

|     | 4.3   | Evaluation                                                                                                                                    | ) |

|     | 4.4   | Discussion $\ldots \ldots 52$                             | 2 |

| V   |       | /IULATING LARGE TOPOLOGIES WITH BRITE AND CUDA<br>IVEN GLOBAL ROUTING                                                                         | 7 |

|     | 5.1   | BRITE                                                                                                                                         | 3 |

|     | 5.2   | BRITE integration with ns-3                                                                                                                   | ) |

|     | 5.3   | Floyd-Warshall and CUDA                                                                                                                       | 3 |

|     | 5.4   | Generation of routes                                                                                                                          | 5 |

|     | 5.5   | ns-3 routing implementation                                                                                                                   | ) |

|     | 5.6   | Evaluation $\ldots \ldots 69$ | ) |

|     | 5.7   | Discussion                                                                                                                                    | } |

| VI  | ME    | RFORMANCE OF CONSERVATIVE SYNCHRONIZATION<br>THODS FOR COMPLEX INTERCONNECTED CAMPUS NET-<br>ORKS IN NS-3                                     |   |

|     | 6.1   | ns-3's granted time window implementation                                                                                                     |   |

|     | 6.2   | ns-3's null message implementation                                                                                                            |   |

|     | 6.3   | Evaluation                                                                                                                                    |   |

|     | 6.4   | Discussion                                                                                                                                    | 3 |

| VII | [ CO] | NCLUSIONS AND FUTURE WORK                                                                                                                     | ) |

|     | 7.1   | Contributions                                                                                                                                 |   |

|     | 7.2   | Future work                                                                                                                                   | ) |

| REFERENCES . | • |  |  |  |  |  |  |  |  | • | • |  |  |  |  |  | 9 | 93 | 3 |

|--------------|---|--|--|--|--|--|--|--|--|---|---|--|--|--|--|--|---|----|---|

|              |   |  |  |  |  |  |  |  |  |   |   |  |  |  |  |  |   |    |   |

## LIST OF TABLES

| 1 | PHOLD: Total number of events processed | 54 |

|---|-----------------------------------------|----|

| 2 | PHOLD: Events per second                | 54 |

| 3 | Original Null Message Implementation    | 86 |

| 4 | Modified Null Message Implementation    | 87 |

# LIST OF FIGURES

| 1  | Bulk copy of serialized message between LPs                                | 15 |

|----|----------------------------------------------------------------------------|----|

| 2  | Difference between standard C/C++ pointer and offset pointer $\ .$ .       | 17 |

| 3  | Offset pointer with multiple shared memory segments                        | 18 |

| 4  | UML Diagram of BPtr, the offset pointer used in our implementation         | 20 |

| 5  | UML Diagram of a heap item which stores data to be shared between LPs      | 21 |

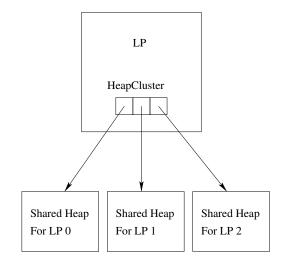

| 6  | Layout of Shared Heaps                                                     | 24 |

| 7  | Ordering of pointers in HeapCluster                                        | 25 |

| 8  | Transfer of message using zero-copy                                        | 27 |

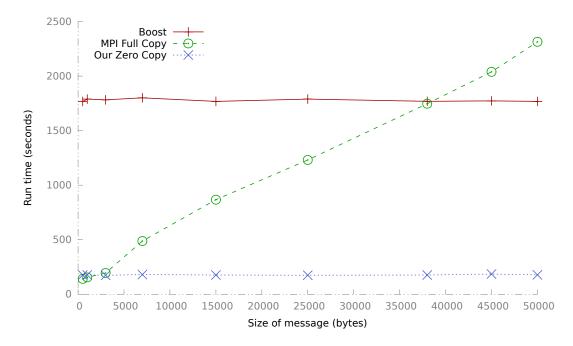

| 9  | SimpleSim results varying message size                                     | 30 |

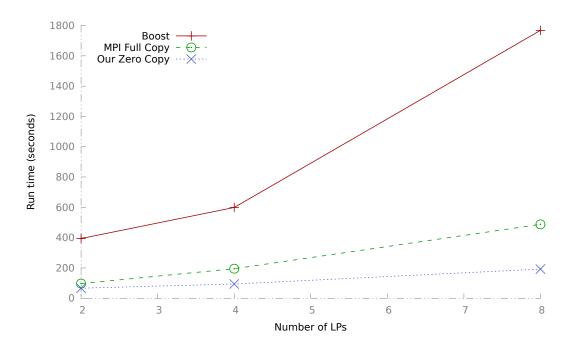

| 10 | SimpleSim results varying number of LPs                                    | 31 |

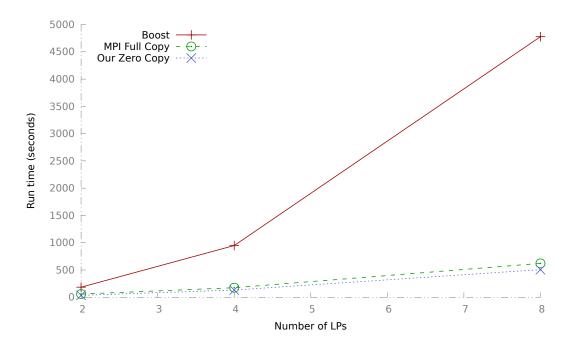

| 11 | GTNetS results varying number of LPs                                       | 32 |

| 12 | An example execution grid consisting of 6 blocks, each with 256 threads.   | 35 |

| 13 | Thread divergence example                                                  | 38 |

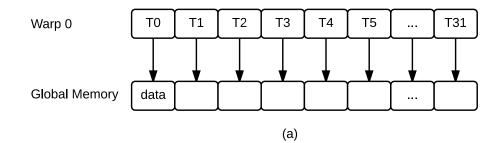

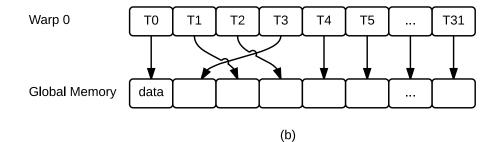

| 14 | Memory coalescing examples                                                 | 43 |

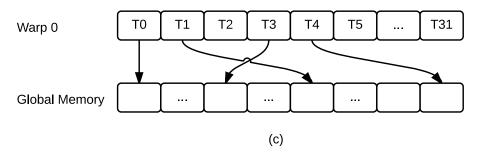

| 15 | SimpleSimulator event processing example                                   | 49 |

| 16 | ParitionSimulator event processing example                                 | 51 |

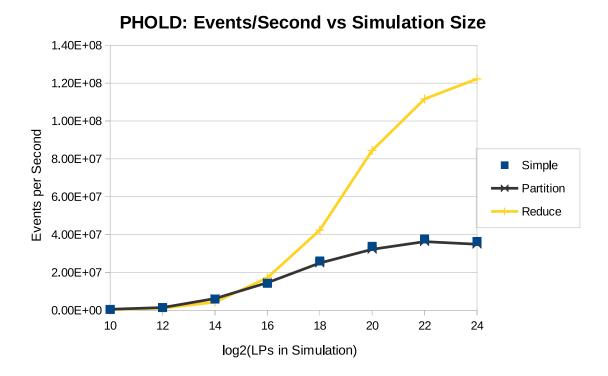

| 17 | Event processing rate by simulation size                                   | 53 |

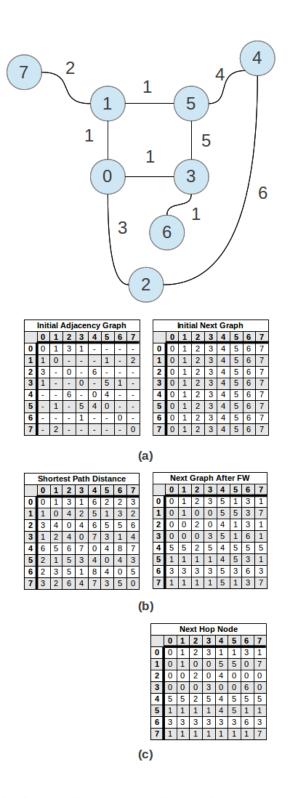

| 18 | Floyd-Warhsall routing example                                             | 66 |

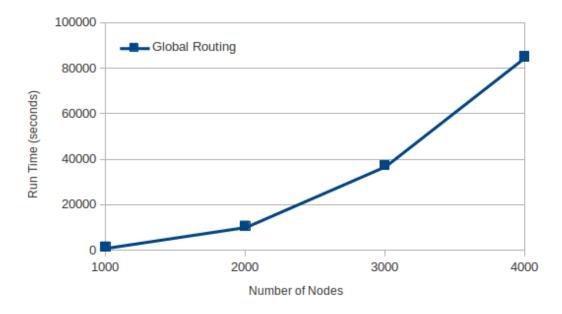

| 19 | ns-3's global routing runtimes                                             | 70 |

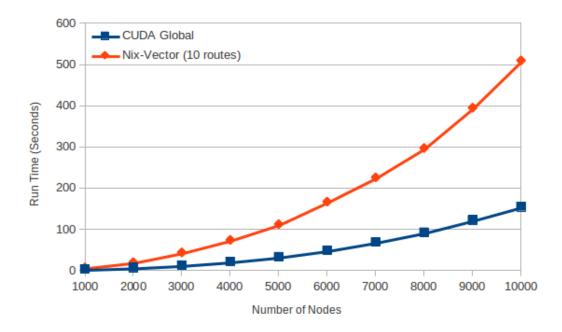

| 20 | Comparing nix-vector and CUDA routing varying number of nodes $\$ .        | 71 |

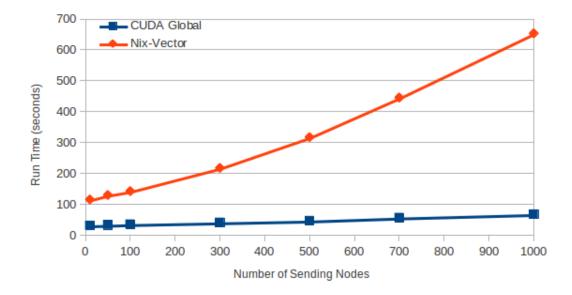

| 21 | Comparing nix-vector and CUDA routing varying number of traffic generators | 72 |

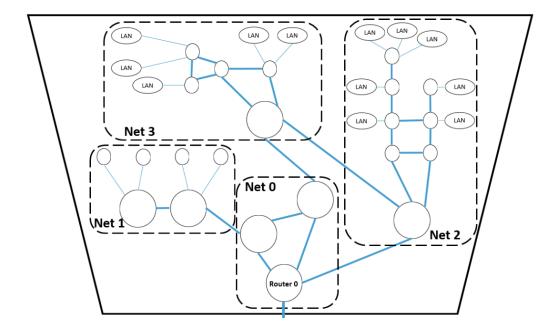

| 22 | The DARPA campus network topology                                          | 78 |

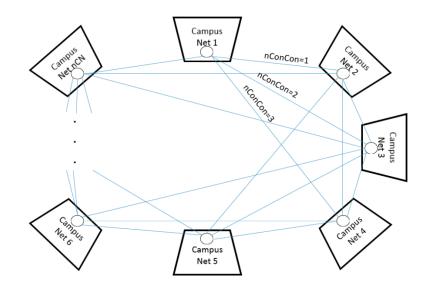

| 23 | Varying connectivity of individual DARPA campus networks                   | 79 |

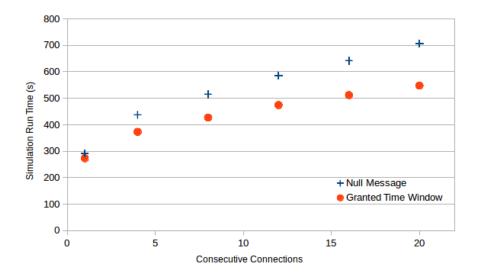

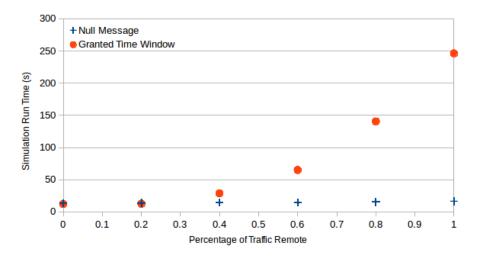

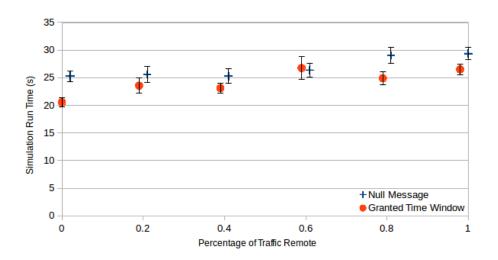

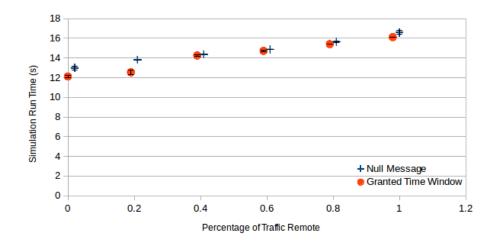

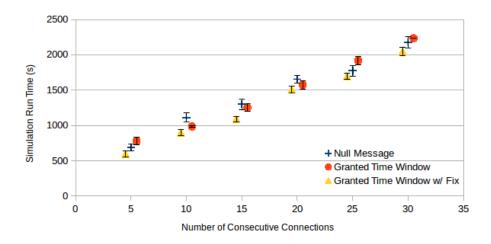

| 24 | Simulation runtime varying campus connectivity                             | 82 |

| 25 | Simulation runtime varying remote traffic percentage                       | 82 |

| 26 | Simulation runtime varying remote traffic percentage on cluster resource | 83 |

|----|--------------------------------------------------------------------------|----|

| 27 | Simulation runtime varying remote traffic percentage with fix            | 84 |

| 28 | Simulation runtime varying campus connectivity                           | 86 |

#### SUMMARY

Discrete-event simulation is a commonly used technique to model changes within a complex physical systems as a series of events that occur at discrete points of time. As the complexity of the physical system being modeled increases, the simulator can reach a point where it is no longer feasible for it to run efficiently on one computing resource. A common solution is to break the physical system into multiple logical processes. When breaking a simulation over multiple computing nodes, care must be taken to ensure the results obtained are the same as would be obtained from a non-distributed simulation. This is done by ensuring that the events processed in each individual logical process are processed in chronological order. The task is complicated by the fact that the computing nodes will be exchanging timestamped messages and will often be operating at different points of simulation time. Therefore, highly efficient synchronization methods must be used. It is also important that the logical processes have a capable means to transport messages among themselves or the benefits of parallelization will be lost.

The objective of this dissertation is to design, develop, test, and evaluate techniques to improve the performance of large-scale discrete-event simulations. The techniques include improvements in messaging passing, state management, and time synchronization. Along with specific implementation improvements, we also examine techniques on how to effectively make use of resources such as shared memory and graphical processing units.

#### Techniques to improve the performance of Large-Scale Discrete-Event Simulation

Brian Paul Swenson

#### 99 Pages

#### Directed by Professor George F. Riley

Discrete-event simulation is a commonly used technique to model changes within a complex physical systems as a series of events that occur at discrete points of time. As the complexity of the physical system being modeled increases, the simulator can reach a point where it is no longer feasible for it to run efficiently on one computing resource. A common solution is to break the physical system into multiple logical processes. When breaking a simulation over multiple computing nodes, care must be taken to ensure the results obtained are the same as would be obtained from a non-distributed simulation. This is done by ensuring that the events processed in each individual logical process are processed in chronological order. The task is complicated by the fact that the computing nodes will be exchanging timestamped messages and will often be operating at different points of simulation time. Therefore, highly efficient synchronization methods must be used. It is also important that the logical processes have a capable means to transport messages among themselves or the benefits of parallelization will be lost.

The objective of this dissertation is to design, develop, test, and evaluate techniques to improve the performance of large-scale discrete-event simulations. The techniques include improvements in messaging passing, state management, and time synchronization. Along with specific implementation improvements, we also examine techniques on how to effectively make use of resources such as shared memory and graphical processing units.

## CHAPTER I

## INTRODUCTION

Discrete-event simulation is a commonly used technique to model changes within a complex physical systems as a series of events that occur at discrete points of time. The events are processed in a time-stamp order and no changes to the state of the system can occur between consecutive events. The simulator is made up of a future event list, a simulation time, and the state of the physical system being modeled. When the simulator processes an event, it sets the the simulation time to the time within the timestamp of the earliest event in the future event list. Afterward the simulator updates the state of the physical system in response to the information contained within the event being processed. As an event is processed, the corresponding change in the physical state of the system may result in one or more new events to be generated in the future. The simulator will continue to run until it has completely exhausted the future-event list or until it processes an event with a stop request.

As the complexity of the physical system being modeled increases, the simulator can reach a point where it is no longer feasible for it to run efficiently on one computing resource. A common solution is to break the physical system into multiple logical processes. Each logical process is responsible for controlling a specific section of the overall system. Each logical process is made up of a local simulation time, a futureevent list for the events pertaining to the section of the system it is responsible for, and the state of the system it is responsible for. The logical processes communicate state changes to one another through the use of time-stamped messages.

When breaking a simulation over multiple computing nodes, care must be taken to

ensure the results obtained are the same as would be obtained from a non-distributed simulation. This is done by ensuring that the events processed in each individual logical process are processed in time-stamp order. The task is complicated by the fact that the computing nodes will be exchanging time-stamped messages and will often be operating at different points of simulation time. Therefore, highly efficient synchronization methods must be used. It is also important that the logical processes have a capable means to transport messages among themselves or the benefits of parallelization will be lost.

#### 1.1 Contributions

The objective of this dissertation is to design, develop, test, and evaluate techniques to improve the performance of large-scale discrete-event simulations. The techniques include improvements in messaging passing, state management, and time synchronization. Along with specific implementation improvements, we also examine techniques on how to effectively make use of resources such as shared memory and graphical processing units (GPUs). The primary contributions of this work are:

- To improve the message passing performance for simulators running on multicore systems with available shared memory, we developed a new zero-copy message passing approach specifically designed for the needs of distributed discreteevent simulators. This approach was compared to alternative available zerocopy approaches and to the traditional approach of serialization followed by a bulk memory copy. We show that our approach provides consistent performance, as would be expected of a zero-copy approach, and outperforms the traditional serialization and bulk copy approach in multiple simulation environments.

- We performed a study to determine if conservative time-synchronization techniques could be used to run large-scale distributed discrete-event simulations

entirely on a GPU designed for three-dimensional gaming. Three unique and different approaches for event list management were examined and compared. Using the PHOLD benchmark we were able to process events at a rate of approximately 122 million per second on a simulation containing over 16 million logical processes. Furthermore, specific discrete-event simulation considerations are discussed in relation to GPU architecture. This work lays the ground work for future research to fully utilize the massive parallel processing abilities on GPUs for large-scale discrete-event simulation.

- We demonstrated how GPUs can be used by CPU-based discrete-event simulators for increased performance. We developed an add-on to the popular ns-3 discrete-event network simulator that allows users to utilize the BRITE topology generator to generate highly-customizable, large-scale topologies in ns-3. We then developed another GPU-based module to perform global routing between all of the nodes in the network. We show that our routing module is substantially faster than the global-routing module included in ns-3 and can even outperform the highly-efficient nix-vector routing implementation also included in ns-3. This work has lead to numerous discussions on how other ns-3 modules can utilize GPUs for processing highly-parallel tasks such as propagation loss and even topology generation.

- We examined the two conservative-time synchronization implementations provided with ns-3 for distributed discrete-event simulation. The implementations were tested in a number of different topology configurations in order to provide simulation users insight into which implementation to use for running their large-scale simulations. Furthermore, after examining both of the implementations, we were able to propose improvements to each to significantly increase their performance in certain simulation scenarios. We discuss the improvements

and provide experimental results that demonstrate the improvement.

## 1.2 Dissertation organization

The remainder of this dissertation is organized as follows. Chapter 2 provides an overview of the background and related work in the area of distributed discreteevent simulation. Chapter 3 gives a description of our new approach to zero-copy message passing, designed specially for the demands of distributed discrete-event simulation, and compares its performance to other available methods. In chapter 4, we examine the feasibility of running large-scale simulations on GPUs as well as provide groundwork to support future research in this area. In chapter 5, we demonstrate how GPUs can be used in a supporting role to a CPU-based large-scale simulation. Here the GPU is used exclusively to quickly calculate routing information. Chapter 6 compares the conservative-time synchronization implementations in the network simulator ns-3 and provides enhancements to both that lead to significant performance increases in certain scenarios. Finally, chapter 7 concludes this dissertation.

## CHAPTER II

### ORIGIN AND HISTORY OF THE PROBLEM

#### 2.1 Discrete-event simulation

Discrete-event simulation is a technique to model the operation of a physical system as a discrete sequence of events. Changes to the state of the system are made by events that are processed in time-stamp order. Between consecutive events within the simulation, no change in state occurs. The events are stored in time-stamp order in an events list. The three main pieces of the simulator are the state, the event list, and the clock, which represents the current simulation time. Prior to processing each event, the simulator updates the current simulation time to the time within the timestamp of the event. As each event is processed, new events can be scheduled in the future. Ensuring that the events are processed in chronological order is known as enforcing the causality constraint. A discrete-event simulator will continue to run until it is stopped or it runs out of events in the event list.

#### 2.2 Parallel discrete-event simulation

As the size and the complexity of the models within the simulation grow, the simulation can reach a point where it is no longer feasible to run on one computing resource. In parallel discrete-event simulation (PDES), the standard solution is to parallelize the simulation by partitioning the model into multiple logical processes(LPs), each of which is run on a separate computing resource. Each LP has a local simulation time and an event list which will only contain the events that are to be processed on that particular LP. An LP will communicate an event impacting another LP through the transmission of a time-stamped message. It is mandatory that a distributed simulation produce the same results as a corresponding sequential simulation; therefore, causality must be enforced within the LPs. Specifically, an LP must be prevented from advancing too far ahead of other LPs, such that it receives an incoming event from another LP that contains a timestamp less than the current simulation time. To enforce the property of causality among LPs, distributed simulators make use of synchronization algorithms. These algorithms can be classified into two groups: optimistic and conservative.

#### 2.2.1 Optimistic time-synchronization algorithms

Optimistic synchronization allows LPs to progress independently of one another for short periods of time, which can result in possible causality violations. If an LP processes an event out-of-order, i.e., it later receives an event with an earlier timestamp than its current local time from another LP, the LP must undo, or rollback, its local state to its state prior to processing the out of order event. The newly received event with the earlier timestamp can then be processed, and the LP will resume processing events in its event list, possibly reprocessing events that were rolled back if they are still valid given the update to the state of the LP by the new message.

The Time Warp mechanism [32] is the most commonly implemented optimistic time-synchronization algorithm. In the original proposal, the LP saves a copy of its entire state prior to the processing of each event. Then, if the LP needs to rollback, it discards its local state and reloads the saved state prior to the processing of the outof-order event. In the original paper it was assumed that the state of the process was saved after the processing of every event. However, later works offered less demanding state-saving techniques [4] [74].

Regardless of the method used to save the state of the LP, over time this results in a large demand on memory resources. In order to minimize the amount of state storage for each LP, a global-virtual time (GVT) is maintained within the system. The GVT is a timestamp which contains the earliest timestamp of all of the unprocessed events in the system. Since no event with a timestamp earlier than the GVT will ever appear in the event list of a particular LP to cause a rollback, any state saved prior to the GVT can be removed. This procedure of reclaiming memory is referred to as fossil collection [24].

More recently, simulations using Time Warp have made use of reverse computation [60]. In reverse computation, the LP performs the inverse of events that have been processed out of order, effectively allowing the LP to run backwards in time to the point where it has processed an out-of-order event. However, for this process to succeed, reverse computation code must be written for each event type. Attempts have been made to create a compiler that automatically generates the reverse code for events. Perumalla [62] created source-to-source compiler for a subset of the C language that was demonstrated within the Georgia Tech Time Warp [16], an optimistic time synchronization simulator. Also work has begun on the development of a reversible C++ compiler [72]; however, frequently the generation of reverse execution code from a language that was designed for forward only computing.

Languages that have been from designed from the start to ensure correct and efficient reversibility do exist. One such example is Janus [40], and another is R [21]. However these languages are restrictive the operations they perform, for example in Janus all variables must be global integers, and often their use is not practical for large complex systems.

#### 2.2.2 Conservative time-synchronization algorithms

With conservative time-synchronization algorithms, each LP has to determine when an event is safe to process. An event is safe only when it can be guaranteed that the LP will not receive events from other LPs with timestamps less than the event being considered. In this way, the LP guarantees that all of its events are processed in order. These algorithms can be classified as being either *synchronous* or *asynchronous*. Synchronous algorithms require simultaneous participation from each of the LPs in the system. Asynchronous algorithms do not have the global communication requirement of synchronous algorithms instead synchronization is achieved by LP peer-to-peer communication. Conservative time synchronization algorithms must be sure to avoid deadlock, a situation where none of the LPs have a safe event to process and are waiting for updates from other LPs in order to continue.

One of the most popular conservative time synchronization algorithms is the Chandy-Misra-Bryant (CMB) algorithm. The CMB algorithm was developed independently by Chandy and Misra [12] and Bryant [9]. The CMB algorithm in an example of an asynchronous conservative time synchronization algorithm. The algorithm handles time synchronization and deadlock prevention by its use of *null messages*. The null message contains the the timestamp of the smallest unprocessed event on the sending LP plus the *lookahead* between the sending and receiving LP. The lookahead between two LPs is the minimum simulation time between the timestamp for an event on the sending LP and the timestamp on the subsequent event it generates on the receiving LP. The lookahead is closely related to the physical properties of the system being modeled. For example the lookahead between two communication nodes in a network simulator would be the speed of light delay between the two nodes. One important limitation of the CMB algorithm is that it cannot guarantee to prevent deadlocks if there are any cycles of logical processes with zero lookahead [24].

In the original algorithm proposal, after an LP processes an event, a null message is sent to each of its neighbors. Upon reception, the receiving LP knows that it can safely process the events in its event list up until the time in the null message without fear of receiving a message with an earlier timestamp from the sending LP. If the receivng LP has multiple neighbors it uses the minimum null message timestamp value as its safe time. The obvious problem with this approach is that this greatly increases the amount of cross LP traffic. An alternative approach, proposed later by Mirsa [45], allows LPs to process events until no more are safe. At that point the LP requests null messages from its neighbors.

The other class of conservative time-synchronization algorithms are considered to be synchronous. To determine if an event is safe, the LP finds the lowest-bound timestamp (LBTS) on all possible events that it may receive in the future. This process is similar to how the GVT is calculated for optimistic time-synchronization algorithms. How this bound is determined is dependent on the particular algorithm used. Several algorithms for finding LBTS values [66] [42] [38] [7] exist. Another important consideration for this type of conservative simulation algorithms is how they deal with *transient messages*. Transient messages are messages that have been sent by one LP, but have not yet been processed by the receiving LP. These need to be considered because the event with the lowest time stamp may be in one of these messages.

#### 2.2.3 Maximizing lookahead

For conservative time synchronization algorithms lookahead is an essential attribute for improved performance in parallel discrete-event simulation [22]. This value defines the amount of asynchrony among the distributed models in the system. Maximizing its value reduces the frequency of synchronization and increases the overall performance of the simulator by maximizing the amount of time each LP instance is processing internal events. A parallel simulation environment with minimal or no lookahead would essentially run as a non-parallel simulation with the additional overhead of LP communication. Due to its importance, there have been numerous studies that have examined techniques for maximizing lookahead values dynamically during simulation runtime, a technique referred to as dynamic lookahead extraction [59]. This technique has been shown to be vital in distributed wireless network simulation where the distances between communicating nodes is small, resulting in a minimal lookahead due solely to wireless propagation delay [39]. Researchers also have used information such as queuing delay to inflate the lookahead value higher than the static value assigned [76].

#### 2.2.4 Non-CPU hardware support for parallel discrete-event simulation

There has also been work examining how hardware can be used to increase the performance of parallel discrete-event simulation. This hardware can be optimized for particular functions, allowing it to perform them faster than can a CPU. The *Rollback Chip* [25] was proposed by Fujimoto to help optimistic Time Warp simulations by reducing the overhead of state saving and rollback. It was found that the use of this chip greatly improved the simulator's performance.

On the conservative side of time synchronization, a hardware supported global synchronization unit was proposed by Lynch and Riley [41]. The chip allows individual LPs to calculate LBTS as needed, without the overhead cost of global synchronization. The chip contains three sets of registers files, one for minimum outstanding event (MOE), one for minimum outstanding message (MOM) and finally one for transient message count (TMC). Each LP in the simulation has a register in each file. Both the MOE register file and the MOM register file have N-1 comparators that can compute the minimum value in the register file in lg(N) stages. To find the smallest outstanding timestamp in the system, a MinimumTimestamp instruction is provided which returns the minimum of the MOM and MOE register files. It was found that the use of this unit reduced runtime by as much as 50% in tests performed with GTNetS [64].

A new area of research that has become popular as of lately is utilizing general

purpose graphical processing units (GPGPU) within the realm of PDES. The first work on this was done by Perumalla [63] who used a GPGPU based discrete-event simulator to simulate a diffusion process. The work was done prior to the arrival of technologies such as CUDA and OpenCL and therefore used Brook and was executed on the DirectX 9 runtime. It was found that the GPGPU version of the simulator outperformed a similar simulator run on a CPU by almost two fold.

With the advent of GPGPU enabling technologies such as OpenCL and CUDA research into using GPGPUs for PDES has greatly increased. One example of a PDES simulator that makes extensive use of GPGPUs is Cunetsim [67]. Cunetsim [67] is a hybrid CPU-GPU network co-simulator where LPs process events using the GPU and time synchronization is done on the CPU. The authors use conservative time synchronization to ensure a casual ordering of events. The authors report substantial speedup [5] compared to non-GPGPU network simulators such as ns-3 and Singalo [17].

## CHAPTER III

# A NEW APPROACH TO ZERO-COPY MESSAGE PASSING

There are two main methods available to take advantage of the multiple cores on today's CPUs. The first is the thread model in which each logical process (LP) runs on its own thread within one operating system process. With multi-threaded applications, data can easily be passed between concurrently running threads using simple C type pointers. This allows the threads to communicate using messages of any size at the cost of passing a 32 or 64 bit pointer.

The alternative is the multi-process model where each logical process runs in its own individual operating system process. With multi-process applications, the process of passing messages becomes more complicated. The operating system runs each individual process in its own virtual address space, and any pointers created in a process will reference a virtual address, not a physical address. Since the mappings between virtual and physical addresses might be different for each process, pointers created by one process and passed to another might refer to a completely different physical location in memory for the receiver. Therefore, standard C type pointers can not be used as a means to pass messages between individual processes.

Both the multi-threaded and multi-process distributed simulation approaches are commonly used. In general, a distributed simulation using multiple threads will need all event handlers and the event scheduling engine to be aware of the need for multiple-access interlocking to prevent simultaneous updates and potential deadlocks. In contrast, when distributing the simulation in separate address spaces, only those portions of the simulation that send events and the portion that advances simulation time needs to be aware of the distributed execution. Further, if the original simulation package was not designed with distributed execution in mind, the multi-process approach is in general considerably easier to implement. ns-2 [48] is an example of a simulation environment that was not in fact designed originally to execute in a distributed fashion, but was later adapted to execute with multiple processes and disjointed address spaces.

A common API to use when working with multi-process simulations is the well– known Message Passing Interface (MPI) [20]. However, a significant overhead for MPI based applications is in message passing between the disjointed address spaces. Even in a tightly coupled, shared memory environment, the messages must be copied into a shared memory region. The copying of the entire message must be done because simple, C type pointers use virtual addresses which have no meaning once the pointer is passed to another process. Thus a common approach is to first serialize the message and its data and perform a memory copy of the serialized message to a shared memory location, where it then can be retrieved and deserialized by the receiving process. While this technique works and is in common use, a large processing cost can be incurred due to the amount of data being copied between processes. In the cases where these messages are large and must be passed frequently, this becomes a significant limiting factor in overall application performance.

An alternative approach is to use shared memory and smart pointers. With this method, data that needs to be shared with other processes can be created in a shared memory region that is accessible by every process. Then when a message needs to be passed, the owner can pass to the receiver a specialized smart pointer. These smart pointers allow the processes to pass only metadata for messages being exchanged, rather than the complete message. The receiving process can then access the original copy of the data stored in the shared memory using the smart pointer and normal dereferencing semantics. This greatly reduces the amount of data that needs to

be passed between applications. This technique is referred to as zero-copy message passing.

This chapter presented a new implementation for zero-copy message passing in introduced [69]. This is not the first work to implement a zero-copy message passing approach. Boost Interprocess offers a smart pointer design that allows shared memory usage. Also provided by Boost is a general purpose, shared-memory allocator. However, it will be shown that the implementation provided by Boost does not perform well in memory-intensive applications, like distributed simulators. Furthermore, Boost's implementation does not scale well to a large number of LPs. In contrast, the new zero-copy approach described is designed to function on a large number of LPs in a memory demanding environment.Using this new approach, performance of PDES applications on multi-core architectures is greatly improved, allowing for longer and more detailed simulations.

#### 3.1 Traditional message passing

Commonly, messages have been passed between individual processes by copying the entire content of the message to a shared memory region accessible by both the sender and the receiver. However the data to be transferred must first be formatted in a way that allows it to be meaningful to a receiver. This formatting, called serialization, or marshalling, generally copies each individual data item for all messages (and dereferencing pointers as needed) to a sequential array of bytes, which are then copied to the shared memory region.

In some cases, it is possible to marshall the data directly to the shared memory region, eliminating one of the memory copies needed. However this is rarely a trivial process because complex data objects generally make extensive use of pointers, references to other locations in memory. The data referenced from these pointers must also be copied into the buffer because, as mentioned previously, the pointer

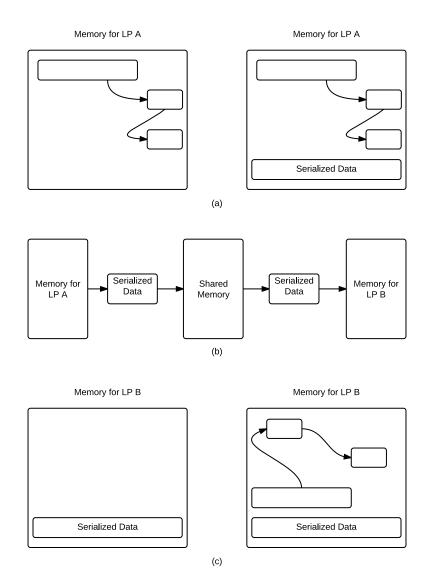

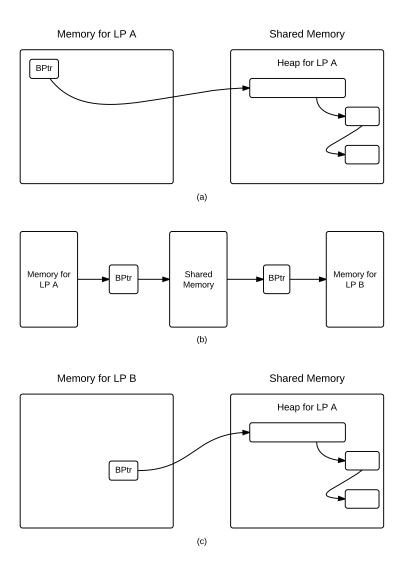

**Figure 1:** The transfer of a complex object between logical processes with disjoint address spaces. (a) The complex object is serialized. (b) The serialized data is first copied to shared memory and then copied into the memory space of LP B. (c) The data is finally deserialized and the object is ready to be used

will no longer be valid once the data is transferred to a different process. Thus the serialization process, in most cases, involves numerous and often recursive memory copies. Once the data to be sent has been serialized, it can then be transferred to the receiver. However, before the receiver can make use of what it has received, it must first deserialize, or unmarshall, the data. This is basically a reversal of the serialization process and therefore frequently requires multiple memory allocations to restructure complex objects back into their original form.

This process is depicted in Figure 1. While this procedure works as intended, the time to complete this marshalling and copying process is non-negligible and increases linearly with the size and complexity of the message.

### 3.2 Zero-copy message passing

Zero-copy message passing improves the performance of parallel simulations in a multi-process environment utilizing two main components: shared memory and smart pointers. First, rather than copying the data to shared memory, the data is created in shared memory, which can be accessed directly by the receiving process. As standard C type pointers cannot be utilized in this type of environment, zero-copy utilizes a smart pointer which is aware of the shared memory nature of the underlying data, and which has normal pointer semantics for dereferencing the pointer to access individual data items. Using the smart pointer eliminates the need for performing an expensive memory copy. Furthermore, the smart pointer can be equipped with reference counting semantics, which results in the underlying shared memory area being freed when all smart pointers pointing to the same area have gone out of scope. In this section we will describe our implementation of zero-copy and compare it to the implementation found in the Boost Interprocess C++ Library.

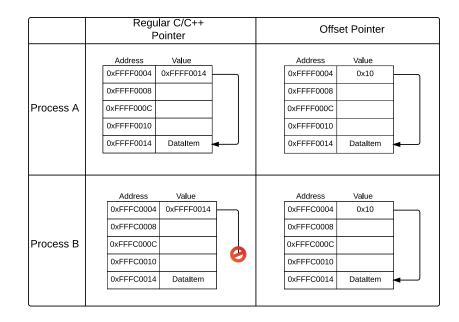

Figure 2: Difference between standard C/C++ pointer and offset pointer

## 3.3 Boost. Interprocess C++ library

Boost provides an extensive library for working with shared memory [26]. These classes can greatly simplify the task of working with shared memory. The following paragraphs discuss the Boost offset pointer and the Boost managed memory segment classes, which when used together can form a zero-copy implementation.

In Boost, the smart pointer that works with shared memory is the offset pointer. The offset pointer stores the distance from the offset pointers address to the object the pointer refers to. This allows objects created in shared memory to refer to each other regardless of which base address the shared memory segment is mapped into the processes address space. An example of this is shown in figure 2. Here you can see two processes have mapped a shared memory segment into their local address space. The regular pointer, create by process A, is not valid for process B since it mapped the shared memory segment to a different base address. Therefore the data to which the pointer should point is not at the address contained within the pointer. With the offset pointer, both processes can correctly address the referenced data regardless of

Figure 3: Offset pointer with multiple shared memory segments

where a process maps the shared memory segment. The only requirement is that the entire shared memory segment is mapped into a contiguous block of addresses.

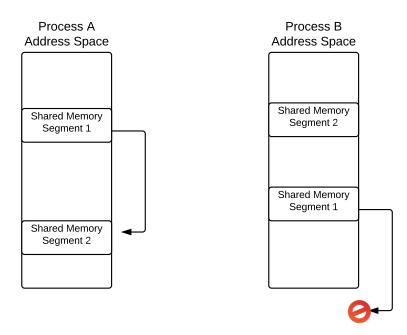

To the programmer, the pointer functions equivalently to a normal pointer and can be coupled with a reference counting pointer to supply automatic garbage collection. The problem with this design is that for it to work correctly, all of the objects have to be stored in the same shared memory segment. There is no guarantee that the difference in base addresses of two shared memory segments mapped into the address space of a process will be the same between processes. This issue is depicted in figure 3. Therefore, in most cases, only one shared memory segment can be used for all LPs.

A pool of shared memory is obtained in Boost using managed-memory segments. Once a pool is available, objects can be created using the segments allocator. The segments provide an allocate method that takes as a parameter a byte size and returns a void pointer to a chunk of memory that size if it is available in the segment. The segments also provide a templated construct method which will create an instance of the object specified in shared memory and return a pointer to it. Managed memory segments in Boost also allow the programmer to create named shared memory objects. A string name can be given to any object created in shared memory.

This name can then be used by any process that connects to the memory segment to find the object in shared memory. While the Boost shared memory segment offers many useful features, it is unable to perform satisfactorily in a memory intensive environment, as we will show. In addition, as mentioned above, due to how Boosts smart pointer interacts with memory segments, only one such segment can typically be used in an application.

This has two major consequences. First, access to critical sections of code in the segments allocator can become a major bottleneck as the number of LPs increase. Second, if the memory in the one shared memory segment is exhausted, the application has no choice but to terminate since shared memory segments are not dynamically expandable.

## 3.4 Zero-copy message passing optimized for simulation

We present a new implementation for zero-copy message passing that is optimized for the demands of PDES and addresses the shortcomings of the Boost Interprocess implementation. In our implementation, each LP is given its own shared memory segment which we refer to as a shared heap. We also provide a custom offset smart pointer to interact with these shared heaps. Our smart pointer also has reference counting semantics to ensure memory is deallocated once it is no longer in use. In the following sections we describe the pieces of our implementation and demonstrate its usage.

#### 3.4.1 Custom smart pointer

Similar to the Boost implementation, to reference items in shared memory, our zerocopy message passing technique utilizes smart pointers. These smart pointers are

| BPtr                                                 |

|------------------------------------------------------|

| heapItem: HeapItem*<br>lp:int<br>offset: int         |

| AddRef():void<br>DropRef():void<br>GetPointer():void |

Figure 4: UML Diagram of BPtr, the offset pointer used in our implementation

necessary because, as discussed previously, standard C type pointers contain a virtual address which may be meaningless when passed between process boundaries. The smart pointers used in the zero-copy approach get around this limitation by passing the metadata necessary for the receiving process to obtain the data that it was intended to receive. The smart pointer created for zero-copy message passing technique is called **BPtr** and its UML diagram is shown in figure 4.

The smart pointer is made up of three data items. The integer LP stores the heap number of the shared heap which contains the actual data being referenced. The offset stores the integer index of the heap item in the data owner's shared heap. Details of heap items will be presented in the next section. The smart pointer also contains a heap item pointer to the heap item referenced by the heap number and offset stored in the smart pointer. This heap item pointer is updated automatically by the smart pointer whenever the smart pointer is copied so it always points to the correct heap item, even when the pointer is passed across process boundaries.

The main difference between our pointer and the Boost offset pointer is that our pointer stores the heap number along with the offset. This offers two major advantages. First it allows our pointers to point to objects in separate shared memory segments. This eliminates many of the concurrency issues experienced with the Boost managed memory segment allocator. The second advantage is that new heaps can be created during runtime if shared memory resources are exhausted. A request is made

| HeapItem                                                             |

|----------------------------------------------------------------------|

| mutex: pthread_mutex_t<br>refcount: int                              |

| lp: int<br>offset: int<br>data: char[DATA_SIZE]<br>timeToZero: float |

| GetData(): char*                                                     |

Figure 5: UML Diagram of a heap item which stores data to be shared between LPs

to the kernel for more shared memory and once it is received the heap structure can be setup and be given a unique heap number. At that point the only thing left to be done is to notify all of the processes to connect to the new heap and add it into their heap cluster.

When a copy of the smart pointer is made, only the heap number and offset data items are copied. Then the **GetPointer** function is called, which gets the heap item pointer. It does this by indexing the **HeapCluster** array using the LP to acquire a reference to the correct heap and then using the offset to address it to the correct heap item. Another feature of the smart pointer class is that it automatically handles the reference counting for the heap item. The assignment operator and copy constructor have been overloaded to atomically increase the reference count of the appropriate heap item when a new reference to the heap item is made. Similarly, the virtual destructor for any **BPtr** object will decrement the reference count appropriately.

#### 3.4.2 Shared heaps

As previously mentioned, in our zero-copy implementation each LP is given its own shared heap for memory allocation. Each shared heap is made up of a group of heap items. It is in these heap items that the data to be shared is stored. The heap items are indexed according to the offset from the start of the heap. It is in these heap items that the data to be shared is stored. The heap items are indexed according to the offset from the start of the heap. A UML diagram of a heap item is shown in figure 5. The **Create** method returns a special templated pointer object called a **BPtr** which refers to an individual heap item.

The heap item is made up of multiple data items. It stores the number for the logical process it belongs to as well as its index number in the shared heap. The data field is where the actual data for the heap item is stored. The reference count specifies the number of smart pointers that are currently referencing the data in the heap item. This is used to determine when the heap item is no longer in use and can be recycled. This number is atomically incremented and atomically decremented whenever the heap item is copied or when it goes out of scope. Finally each heap item contains a timeToZero timestamp.

The timeToZero timestamp is used for simulators which use an optimistic time synchronization algorithm. As discussed previously, there are situations when optimistic simulators need to rollback due to the generation of a causality error. During this rollback, it may be necessary for the simulator to reacquire dynamically created objects that had previously been freed. This is true regardless of if the simulator is reverting to a previous saved state or performing reverse computation. In order to assist in this process, a heap item will not be immediately available for reuse once its reference count goes to zero. Instead the heap item will store the current simulation time for its LP in the time to zero field and will go into a dormant state, preserving itself and the data it contains. The heap item will stay in this state until the GVT of the system is greater than its stored timeToZero timestamp. Only after this happens will the heap item be made available for reuse. Because of this, it is necessary for the simulation to provide the shared heaps updated values for the GVT whenever they are calculated. For simulators that use a conservative time synchronization algorithm, the timeToZero timestamp is not used. It could either be removed or the GVT for all the heaps in the system could be set to infinity at startup. Either way, heap items that have their reference count go to zero will immediately be available for reuse. Since the concept of rollback does not exist in conservative time synchronization, there is no need to postpone garbage collection.

In our ZeroCopy implementation, the heap items are preallocated. The sizes for the heap items and the number to create can be configured by the user prior to runtime. For example, the user could setup heap items for small blocks (50 bytes), medium blocks (500 bytes), and large blocks (5,000 bytes). When an object is created, the heap will return the smallest size that the instance of the object will fit into. By preallocating the blocks, we can provide extremely efficient allocation and deallocation routines since the blocks are of a fixed size and are stored sequentially in memory. When a shared memory pool is requested from the linux kernel, the exact size must be specified and once it is allocated, it cannot be modified. Therefore we feel it makes sense to split the pool into blocks immediately, especially since the user of the simulator should have a general idea of the size of objects he/she needs to create prior to runtime.

Every logical process in the simulation has its own shared heap, which is initialized at initialization time. The heaps are created in shared memory and the permissions are set so every LP can access every other LP's shared heap as well as its own.

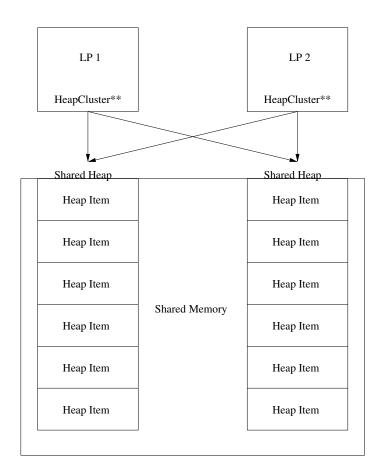

Once all of the logical processes finish creating their own shared heaps, all logical processes make attachments to all other shared heaps. Each LP stores pointers to each of these heaps in a global variable called HeapCluster. A diagram of this is shown in figure 6. Here two LPs have finished setting up their individual shared heaps and have stored pointers to both shared heaps in their HeapCluster, which is a global array of pointers to the heap object for all logical processes. In our implementation, each process maintains the array of virtual memory pointers to all shared memory regions in the order of the logical process number of the creating LP. This is shown in figure 7.

Figure 6: Layout of Shared Heaps

Figure 7: Ordering of pointers in HeapCluster

While both LPs have pointers to the same shared heap, the actual virtual address of the shared heap will typically be different. When a process attaches to a shared memory segment, the shared memory is mapped into the process's virtual address space and there is no guarantee that it will map to the same location for each process that attaches to it. This is why we cannot simply pass normal C/C++ pointers to data items in the shared memory across logical process address spaces.

#### 3.4.3 Using zero-copy message passing in simulation

In our zero-copy message passing design, when a new message is created (presumably to later be passed to another process), a special constructor method, called **Create**, is used rather than the normal C++ **new** operator. The **Create** method is functionally equivalent to **new**, excepting that the memory is allocated from a pre-existing shared memory we call the shared heap, rather than from the normal memory heap used by **new**.

Once created, the smart pointer behaves syntactically the same as any other pointer. When the smart pointer is dereferenced, it uses the stored LP to connect to the shared heap of the process that created the data and then uses the stored offset to obtain the heap item. The appropriate operators have been overloaded in

#### Listing 3.1: Smart Pointer example

//Create a new packet object using the smart pointer BPtr<Packet> packet = Create<Packet>();

//The pointer now functions syntactically the same as a regular pointer

packet->SetDestIP("192.168.1.5");

packet->SetSize("200kB");

cout << "My destination IP is: " << packet->GetDestIP() << endl;

cout << "My size is: " << packet->GetSize() << endl;</pre>

//The smart pointer class automatically handles reference counting. //Here the reference count is increased to 2. BPtr<Packet> anotherRef = packet;

//And now decreased back to 1

anotherRef = NULL;

//Below the reference count is decremented, which results in a zero refcount. //The current simulator time is saved into the HeapItem's time To Zero field . //If this isn't done explicitly, it will occur automatically when the smart pointer goes out of scope. packet = NULL;

**Figure 8:** The transfer of a complex object between logical processes using zero-copy. (a) The object is created in LP A's shared heap and is accessed by LP A via the smart pointer. (b) The smart pointer is copied to shared memory and then copied into the memory space of LP B. (c) Using the smart pointer, LP B can directly access the object in LP A's shared heap. The object itself is never moved or copied.

the smart pointer definition to allow access to all class member functions and data in the referenced class.

Listing 3.1 shows an example of creating a Packet object for a network-simulator using the smart pointer class. Figure 8 shows a message being passed using a smart pointer. Note that the actual object referenced by the pointer is neither moved nor copied.

### 3.5 Evaluation

The first evaluation of our new zero-copy implementation used a custom simulator which we named SimpleSim. SimpleSim is a simple distributed discrete-event simulator that functions similarly to the PHOLD PDES benchmark [23]. In our implementation, the simulator enforces causality using a conservative lower bound time stamp (LBTS) algorithm that exchanges timestamp and message count information between LPs in a common shared memory region. Each LP starts off with one event inserted into its event queue. The timestamp for the first event is chosen randomly within the first five simulation seconds.

When handling an event, SimpleSim always creates one new message and sends it to an LP chosen randomly from a uniform distribution. It then examines the size of its event queue. If the size is less than a predefined constant value, it creates another message which is also sent to a randomly chosen LP. It is possible that the LP can choose itself. Since the size of the event lists for the LPs will grow at approximately the same rate due to the random nature in which the recipients are selected, this prevents unbounded growth in the total number of events for any individual LP.

Included in the message sent to the recipient is a timestamp, a unique ID, and a pointer to an arbitrarily sized chunk of data, which represents the data to be passed to the receiving LP. The timestamps for the new events are chosen from a uniform distribution of 1 to 5 seconds in the future. Added to the timestamp is a predefined constant lookahead value. The unique ID was used mainly for testing purposes.

When SimpleSim receives a new message, it removes the message from the queue and schedules a new event in its event list for the timestamp specified in the message. The individual simulators continue to process and create events until a predefined stop time is reached.

Three versions of SimpleSim were created. The first version is an MPI implementation that copies the entire contents of the message to the receiving process. The other two versions both use a zero-copy technique. The second version uses the Boost Interprocess library and the third version uses our zero-copy implementation.

We created this simulation because it allowed us to easily vary the size of data being passed between processes. In most cases, the message being passed to the receiving process is a complex object with multiple nested pointers. However, in this simulation, the message that is being transferred is uninitialized memory. Thus, there is no serialization step prior to the memory being copied. This also means that there is no de-serialization step. Thus, any speedup observed is due only to the lack of a bulk-memory copy.

For the first experiment with SimpleSim, the number of LPs was held constant at eight and the size of the message was scaled from 500 to 50,000 bytes. The simulator was set to run for 25,000 simulator seconds. The maximum event-list size where LPs stopped sending a second message was set to 5,000 and the lookahead value was set to five seconds. All simulation configurations were run ten times and the average result was recorded. Figure 9 shows the run time of the three approaches for a variety of message sizes. As expected, for the two zero-copy approaches, the execution time is nearly constant regardless of data size. Again this is because the data is not being copied along with the message but instead is being referenced directly from the shared heap where it was created. By comparison, the execution time of the MPI full copy approach is growing approximately linearly with the size of the data being sent. The

**Figure 9:** The runtime of SimpleSim with 8 logical processes, varying message size using MPI, Boost Interprocess and our custom zero-copy approach

results also show that our approach outperforms MPI full copy when the message is larger than approximately 3,000 bytes and outperforms Boost's implementation by almost ten times.

For the second experiment with SimpleSim, we wanted to examine how each simulator instance scaled as the number of LPs participating in the experiment was increased. The size of the data being transferred was fixed to 7,000 bytes. Again the simulator was set to run for 25,000 seconds of simulator time and the maximum event list and lookahead values were set at 5,000 and 5 respectively. Figure 10 shows the results of our experiment. The data clearly shows that the Boost implementation scaled much more poorly than either of the other two. This is presumably because, as discussed previously, the Boost implementation is limited to only one shared memory segment. However even when the Boost version is performing at its peak, our implementation outperforms it by almost six times.

**Figure 10:** The runtime of SimpleSim with a message size of 7000 bytes, varying the number of logical processes using MPI, Boost Interprocess and our custom zero-copy approach. Data collected for 2, 4 and 8 LPs

#### 3.5.0.1 GTNetS

The Georgia Tech Network Simulator (GTNetS) [64] is a full-featured network simulator for modeling large-scale topologies. GTNetS offers packet level tracing and models packets with protocol data units (PDUs) that are added and removed as the packet moves up and down the protocol stack. Similar to SimpleSim, GTNetS also uses conservative time synchronization. We chose to test our zero-copy approach on GTNetS because the messages passed between processes in GTNetS are complex packet objects that contain multiple PDU objects that must be serialized prior to transfer.

For our GTNetS experiments we created a star topology for each LP. The hubs for each of the stars was then connected to form a clique. Each star was given N-1 nodes where N was the number of LPs participating in the simulation. Each node of a star was configured to send UDP traffic to a node in a different LP. Therefore each

**Figure 11:** The runtime of GTNetS varying the number of logical processes using MPI, Boost Interprocess and our custom zero-copy approach. Data collected for 2, 4 and 8 LPs.

LP was sending UDP traffic to every other LP using one of its nodes. Each node was also given a UDP sink to receive data being sent to it. Each UDP packet sent was configured to hold 1,024 bytes of data and each sender was configured with an On/Off Application to use approximately 20% of the available bandwidth. Senders were configured to start at a random time with the first half second of simulation and the simulation was configured to run for 5,000 simulation seconds. All simulation configurations were run ten times and the average value was recorded.

Figure 11 shows the results of this experiment. Again, the Boost version of the simulator scaled worse than the other two versions. Our version of zero-copy outperforms the MPI full copy version even though the message size is less than 1,100 bytes. This is due to the fact that the MPI version has to serialize/deserialize the complex packet hierarchy before and after transferring it. This demonstrates that the effectiveness of our approach improves as the complexity of the objects being transferred increases.

### 3.6 Discussion

This chapter presented a new approach to zero-copy message passing on a manycore architecture was presented. The effectiveness of this approach was demonstrated using distributed discrete-event simulation. While other approaches to zero-copy message passing exist, this new approach has been shown to achieve better performance, especially in the case where many processes are attempting to allocate memory. This approach requires little additional effort on the part of the software developer when creating a new message passing application. This only significant different that affects the software programmer is the use of a special custom smart pointer object instead of normal pointers. This smart pointer has been enhanced to include reference counting semantics which will automatically free shared heap memory once all references to a given object have gone out of scope. Finally, in order to be compatable with optimistic time synchronization algorithms, this zero-copy approach allows for retaining of freed memory contents until certain GVT values have been reached, allowing for freed memory to automatically be restored in the event of a rollback.

# CHAPTER IV

# LARGE-SCALE DISCRETE-EVENT SIMULATION UTILIZING CUDA WITH CONSERVATIVE TIME SYNCHRONIZATION TECHNIQUES

Parallel discrete-event simulation is a technique frequently used to speed up simulations by partitioning a simulation into logical processing units which are executed on separate processors. A large amount of research has gone into techniques and optimizations on how do this most efficiently on CPUs. However, significantly less research has gone into how this could be accomplished using the massive parallel processing abilities of GPUs. This chapter analyzed and compared three different techniques for running large-scale discrete-event simulators on GPUs using conservative time synchronization techniques and the NVIDIA CUDA [54] API.

# 4.1 CUDA Overview

This section provides an overview of CUDA and the underlying GPU architecture. The architecture discussion will cover the NVIDIA Kepler [51] GPU architecture since it was used exclusively for the testing of the simulators presented in this work, although some details may be true of other architectures as well. Knowledge of these topics is necessary to understand the design choices of the simulator.

#### 4.1.1 CUDA Execution Model

CUDA is a general purpose parallel computing platform and programming model that can be used to exploit the massive parallel execution abilities of NVIDIA GPUs. When using CUDA, the GPU can be viewed as a coprocessor with the ability to launch a large number of threads in parallel. Code written to execute on the GPU,

| Blo                          | ock 0            | Bloc                         | :k 1             | Block 2                      |                  |  |

|------------------------------|------------------|------------------------------|------------------|------------------------------|------------------|--|

| ТО                           | ···· )           | ТО                           |                  | ТО                           |                  |  |

| T1                           | T252             | T1                           | T252             | T1                           | T252             |  |

| T2                           | T253             | T2                           | T253             | T2                           | T253             |  |

| ТЗ                           | T254             | ТЗ                           | T254             | ТЗ                           | T254             |  |

|                              | T255             |                              | T255             |                              | T255             |  |

|                              |                  |                              |                  |                              |                  |  |

| ≻                            |                  | <b>\$</b>                    |                  | <b>}</b>                     |                  |  |

| Blo                          | ock 3            | Bloc                         | :k 4             | Blo                          | ck 5             |  |

| Blo<br>(T0)                  | ock 3            | Bloc<br>T0                   | ck 4             | Blo                          | ck 5             |  |

|                              | $\overline{}$    |                              |                  |                              |                  |  |

| ТО                           |                  | ТО                           |                  | ТО                           |                  |  |

| T0<br>T1                     | <br>T252         | T0<br>T1                     | <br>T252         | T0<br>T1                     | <br>T252         |  |

| T0           T1           T2 | <br>T252<br>T253 | T0           T1           T2 | <br>T252<br>T253 | T0           T1           T2 | <br>T252<br>T253 |  |

Figure 12: An example execution grid consisting of 6 blocks, each with 256 threads.

known as a kernel, is compiled to a GPU specific binary. During program execution, the compiled kernel and the data to be processed are uploaded to the GPU. After invoking a kernel, the CPU can either continue processing other tasks, including possibly launching other kernels, or wait until all kernel executions are complete.

Listing 4.1: Example grid creation

| nel parameters); |

|------------------|

|------------------|

Kernel launches from the CPU are accompanied by a programmer provided grid. A grid is comprised of a blockCount and a blockSize which refers to the number of threads in each block. The block size has a maximum value of 1024 in current hardware and should always be evenly divisible by 32 based on how the threads are executed on the hardware. The value is typically used as a tuning parameter since some workloads can be executed more efficiently with more blocks of a smaller block size. In C/C++, a grid is specified within triple angle brackets following the function name as shown in listing 4.1. In this example, a grid with 6 thread blocks, each containing 256 threads, is created as shown in figure 12.

#### 4.1.1.1 GPU Thread Execution

GPUs are comprised of an array of multi-threaded streaming multiprocessors (SM). In the Kepler architecture, each SM is made up of 192 single-precision cores and 64 double-precision cores. Each SM also contains 32 special function units and 32 load/store units. The special function units provide support for functions like sine, cosine and square root. During execution, each block of the grid is assigned to an SM and will stay with that SM until it has completed execution. Each SM is capable of holding up to 16 blocks or 2048 threads, based on whichever limit is reached first.

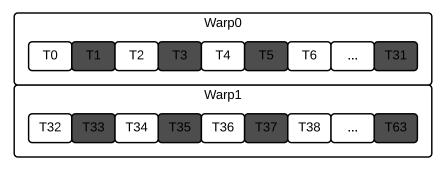

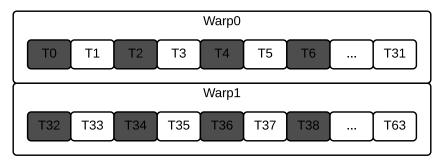

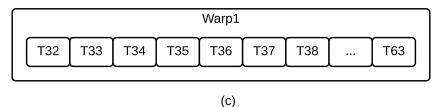

Thread execution within the SM occurs in groups of 32 threads, which is known as a warp. Based on this grouping scheme, all block sizes should be evenly divisible by 32. Otherwise, some warps will have unused threads. Threads are grouped into a warp sequentially by their thread identifier. For example, the 255 threads in block 0 from figure 12 will be split into eight warps: T0-T31, T32-T63, T64-T95, T96-T127, T128-T159, T160-T191, T192-T223, and T224-T255. The threads within the warp are executed in a pattern similar to the single instruction multiple data (SIMD) pattern in Flynn's taxonomy [19]. However, unlike standard SIMD where every thread executes every instruction, programmers using CUDA have the ability to insert divergent code paths into their CUDA kernels. NVIDIA refers to this execution pattern as single instruction multiple thread (SIMT). It is handled at the hardware level by enabling and disabling certain threads within the warp during execution. While this design provides the programmer with greater flexibility in kernel design, care must be taken to avoid potentially large performance consequences.

#### Listing 4.2: Example of thread divergence

\\obtain threadId in block

int myId = threadIdx.x;

if(myId % 2 == 0)

doMethodA();

else

```

doMethodB();

```

Listing 4.2 shows a classical example of thread divergence. In this listing, the threads with an even identifier execute doMethodA while the threads with an odd identifier execute doMethodB. Since the warp executes in a SIMD fashion and consists of threads with sequential thread identifiers, the warp must execute both doMethodA and doMethodB. During the execution of doMethodA, the threads with an odd thread identifier are disabled as shown in figure 13a. During the execution of doMethodB, the threads with an even thread identifier are disabled as shown in figure 13b. Assuming both methods are of equal size, the throughput of the kernel is effectively halved. In cases where there is a deep nesting of conditional statements, the situation becomes even worse. The warp has to sequentially step through every execution path taken by any of its threads, disabling and enabling threads as needed. Given its potential for severely limiting kernel performance, there has been a good deal of research on techniques to limit thread divergence [27] [68] [75] [15] [8].

#### Listing 4.3: Kernel with no divergence penalty

Frequently, the cost of conditional branches within a kernel can be mitigated by thoughtful algorithm selection. In listing 4.2, the intent of the kernel was to have half of the threads within a block perform one function and have half of the threads

# doMethodA()

(a)

# doMethodB()

(b)

doMethodA()

| Warp0 |    |    |    |    |    |    |  |     |

|-------|----|----|----|----|----|----|--|-----|

| ТО    | T1 | Т2 | ТЗ | Т4 | Т5 | Т6 |  | Т31 |

# doMethodB()

**Figure 13:** The cost of thread divergence within a warp. (a), (b) Show the result of a naive conditional statement within a warp. The darker threads are disabled. (c) Results of a modified conditional statement where there is no thread divergence within a warp

perform another. If the author was using a block size that would produce an even number of warps, the kernel shown in listing 4.3 would be a better option. In this listing, the condition is based on the identifier of the warp which can be obtained by the provided thread identifier. By making this change, all of the threads within a warp will execute only one of the functions and none of the warps will be forced to step through both, as shown in figure 13c.

The example kernels above are intentionally trivial to demonstrate the basic issue of branch divergence. The CUDA compiler, nvcc, will attempt to minimize the cost of divergent branches in areas where it is able. One area where this type of optimization would play a role in the context of discrete-event simulation would be in event handling code. A kernel that is tasked with updating the state of a large number of LPs based on the next event type of a particular LP would benefit by grouping each event type in a separate group of warps. This implementation would prevent warps from sequentially executing each and every event handler.

### 4.1.1.2 GPU Memory

To do anything useful, most kernels are going to have to access memory. This fact presents another area where care must be taken to avoid potentially large performance degradation. There are six different types of memory within the CUDA API: global memory, texture memory, constant memory, shared memory, local memory, and registers. The memory types vary in scope, size, and optimal usage patterns. Not all of the types will be covered in this section; however, a full description of each can be found here [56].

When a thread block has been assigned to an SM, the threads within that block are considered to be "in-flight." An "in-flight" thread has its own private copy of the non-shared variables used within the kernel. These private copies are stored in the block registers. If the registers overflow, the excess is moved to local memory. In the Kepler architecture, each SM is supplied with 65,536 32-bit registers, and each thread is capable of addressing up to 255.

Constant memory provides fast read-only memory that can be cached at each SM. It is best used when every thread within a warp is reading from the same address because the results of each read are broadcast to each thread within the warp [13]. If every thread in a warp were to read a separate address from constant memory, the accesses would be serialized, i.e. not done in parallel. If this type of memory access pattern is needed, a better choice would be shared or global memory.