# APPLICATION-LEVEL MODELING AND ANALYSIS OF TIME AND ENERGY FOR OPTIMIZING POWER-CONSTRAINED EXTREME-SCALE APPLICATIONS

A Dissertation Presented to The Academic Faculty

By

Eric Anger

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology December 2016

Copyright © 2016 by Eric Anger

# APPLICATION-LEVEL MODELING AND ANALYSIS OF TIME AND ENERGY FOR OPTIMIZING POWER-CONSTRAINED EXTREME-SCALE APPLICATIONS

Approved by:

Dr. Sudhakar Yalamanchili, Advisor Professor, School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Richard Vuduc Professor, School of Computational Science and Engineering Georgia Institute of Technology Dr. Ada Gavrilovska Professor, School of Computer Science Georgia Institute of Technology

Dr. Linda M. Wills Professor, School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. George F. Riley Professor, School of Computational Science and Engineering Georgia Institute of Technology

Date Approved: December 2016

# ACKNOWLEDGMENTS

This thesis would not be possible without the concerted effort of many people. Foremost is my adviser Dr. Sudhakar Yalamanchili, who took me under his wing and taught me not only the technical aspects of my work, but also how to conduct myself in formal research and with my colleagues. Thank you for guiding me on how to be a better researcher. I would also like to thank Dr. George Riley and Dr. Rich Vuduc for their feedback and insight as my reading committee members, as well as Dr. Ada Gavrilovska and Dr. Linda Wills for their input on my thesis and during the defense.

Through the years I have had the great fortune to work with individuals not associated with the university. I would like to thank Dr. Curtis Janssen and Dr. Gilbert Hendry for mentoring me at Sandia National Labs in California, and especially Dr. Jeremiah Wilke for his advice and leadership for the many research projects I undertook in conjunction with him. I am grateful as well for the mentorship of Dr. Kevin Barker and Dr. Darren Kerbyson at Pacific Northwest National Lab and Patrick McCormick and Dr. Scott Pakin at Los Alamos National Lab. These internships were invaluable in exposing me to the outside world of academic research.

Many, many thanks to my friends in the CASL lab; Andrew Kerr, Jeffrey Young, Chad Kersey, Will Song, Si Li, Minhaj Hassan, Jin Wang, Haicheng Wu, Hugh Xiao, Xinwei Chen, Karthik Rao, and all the rest were there when I needed information, advice, commiseration, sympathy, motivation, and cheer. I could not have gotten through it without you all.

Last, I would like to thank my close friends and family. You are all my rock, giving me nothing but encouragement and support through this process. This is as much your creation as mine.

# TABLE OF CONTENTS

| ACKNO   | WLEDGMENTS                                                  | iii |

|---------|-------------------------------------------------------------|-----|

| LIST OF | TABLES                                                      | vi  |

| LIST OI | FIGURES                                                     | vii |

| SUMMA   | <b>RY</b>                                                   | ix  |

| CHAPT   | ER 1 INTRODUCTION                                           | 1   |

| 1.1     | Contributions                                               | 3   |

| 1.2     | Organization                                                | 8   |

| CHAPT   | ER 2 RELATED WORK                                           | 10  |

| 2.1     | Performance and Energy Estimation                           | 10  |

|         | 2.1.1 Large-scale Simulation Techniques                     | 10  |

|         | 2.1.2 Performance Prediction Using Models                   | 12  |

|         | 2.1.3 Statistical Modeling of Performance                   | 13  |

|         | 2.1.4 Power Measurement Facilities                          | 14  |

| 2.2     | Analytical Models of Time and Energy Scaling                | 14  |

| 2.3     | Optimizing Performance Under Power Limitations              | 15  |

| 2.4     | Power-Aware Parallelism for Task-Based Applications         | 16  |

| 2.5     | Concluding Remarks                                          | 17  |

| CHAPT   | ER 3 APPLICATION-LEVEL MODELING OF TIME AND ENERGY          | 19  |

| 3.1     | Statistical Models of Application Execution Time and Energy | 20  |

|         | 3.1.1 Model Generation Procedure                            | 24  |

|         | 3.1.2 Formal Specification                                  | 29  |

| 3.2     | Modeling Performance of Applications at Scale               | 31  |

|         | 3.2.1 Data-Dependent Computation                            | 35  |

|         | 3.2.2 Compute Modeling                                      | 35  |

|         | 3.2.3 Skeletonization Procedure                             | 36  |

| 3.3     | Experimental Results                                        | 39  |

|         | 3.3.1 Experimental Setup                                    | 39  |

|         | 3.3.2 Model Fit                                             | 41  |

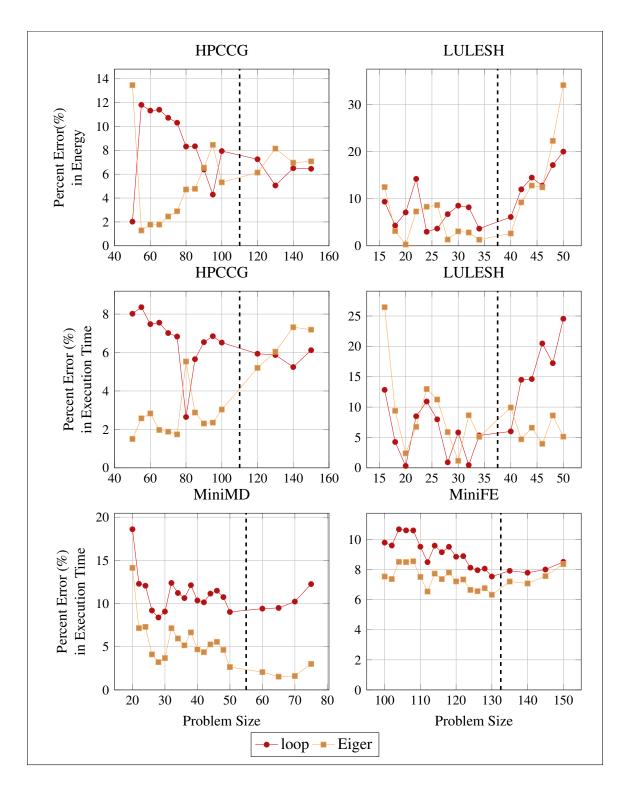

|         | 3.3.3 Simulation Accuracy                                   | 42  |

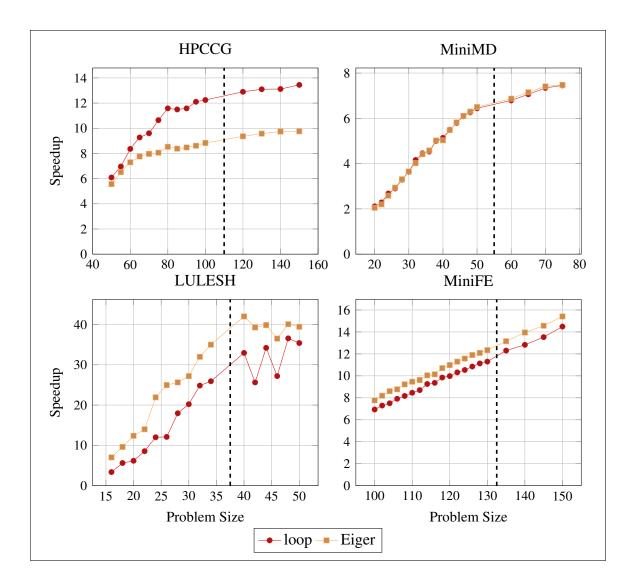

|         | 3.3.4 Simulation Speedup                                    | 44  |

| 3.4     | Concluding Remarks                                          | 47  |

| CHAPT   | ER 4 CHARACTERIZING RELATIONSHIPS BETWEEN TIME AND          | )   |

|         | ENERGY SCALING                                              | 49  |

| 4.1     | Theoretical Energy Scaling                                  | 50  |

|         | 4.1.1 The Baseline Energy Scaling Model                     | 52  |

|         | 4.1.2 The Effect of Processor Idle States on the Model      | 53  |

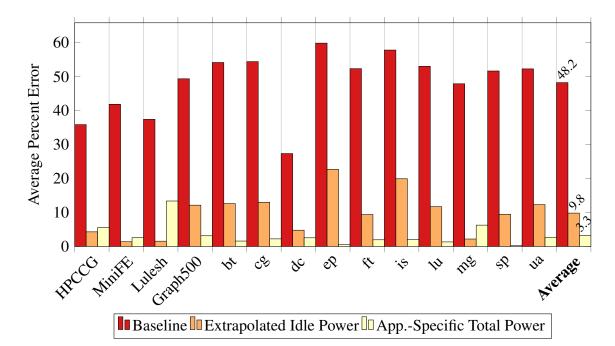

|                   | 4.1.3        | Application-Dependent Active Power                    | 56 |  |  |

|-------------------|--------------|-------------------------------------------------------|----|--|--|

|                   | 4.1.4        | Experimental Results                                  | 57 |  |  |

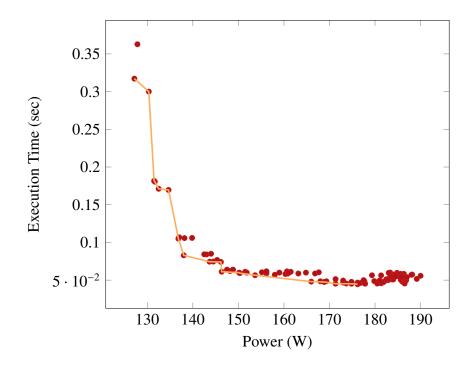

| 4.2               | Pareto       | o-Optimal Scaling in Time and Power                   | 60 |  |  |

|                   | 4.2.1        | Machine Model                                         | 61 |  |  |

|                   | 4.2.2        | Frontier Construction                                 | 62 |  |  |

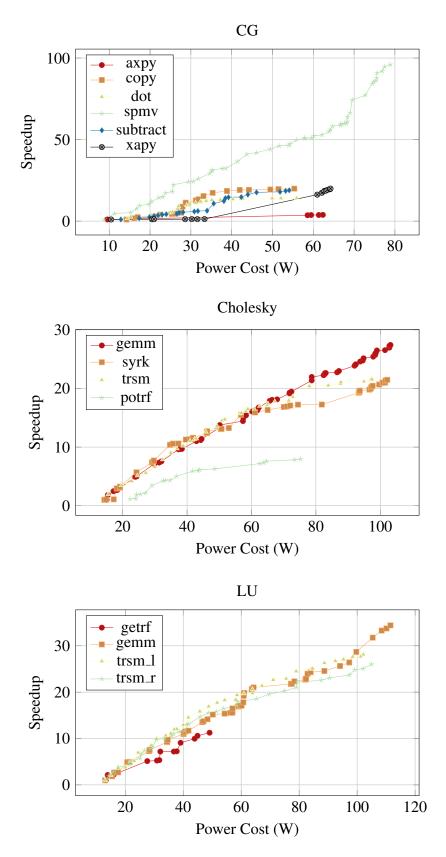

|                   | 4.2.3        | Power–Performance Pareto Frontiers                    | 66 |  |  |

| 4.3               | Concl        | luding Remarks                                        | 66 |  |  |

| CHAPTI            | E <b>R 5</b> | POWER-CONSTRAINED PERFORMANCE SCHEDULING .            | 68 |  |  |

| 5.1               | Dyna         | mic Power Steering For Bulk-Synchronous Applications  | 70 |  |  |

|                   | 5.1.1        | Power Assignment to Processor Cores                   | 71 |  |  |

|                   | 5.1.2        | Workload Case Studies                                 | 73 |  |  |

|                   | 5.1.3        | Experimental Setup                                    | 76 |  |  |

|                   | 5.1.4        | Results and Discussion                                | 78 |  |  |

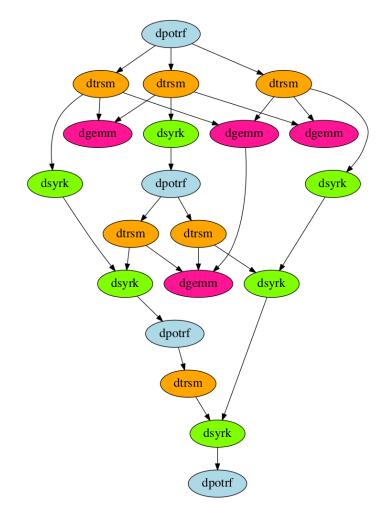

| 5.2               | Power        | r-Constrained Scheduling for Asynchronous Task Graphs | 80 |  |  |

|                   | 5.2.1        | Power-Efficient Scheduling                            | 81 |  |  |

|                   | 5.2.2        | Scheduling Heuristics                                 | 81 |  |  |

|                   | 5.2.3        | Results                                               | 84 |  |  |

| 5.3               | Concl        | luding Remarks                                        | 87 |  |  |

| CHAPTI            | ER 6         | CONCLUSION                                            | 89 |  |  |

| <b>REFERENCES</b> |              |                                                       |    |  |  |

# LIST OF TABLES

| 1 | Model pool                                                                                    | 27 |

|---|-----------------------------------------------------------------------------------------------|----|

| 2 | Machine configurations for collecting time and energy training data                           | 41 |

| 3 | Configuration of Intel Sandy Bridge-EP platform used for experimental data collection.        | 57 |

| 4 | Descriptions of the applications examined in this work, along with their input configuration. | 58 |

| 5 | Machine configuration used for experimental evaluation.                                       | 62 |

# LIST OF FIGURES

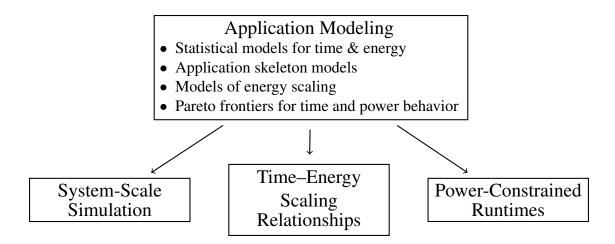

| 1  | Application-level models provide a foundation for the three challenges addressed in this thesis.                                                                                                                                                                                           | 2                                                     |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

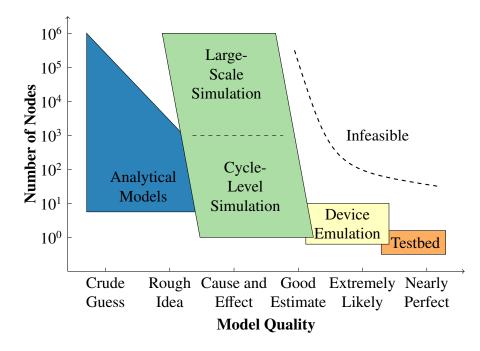

| 2  | Spectrum of different modeling granularity and the associated quality                                                                                                                                                                                                                      | 11                                                    |

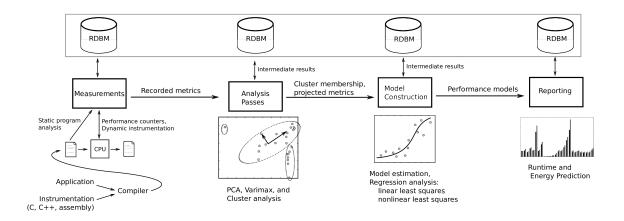

| 3  | Implementation details of Eiger Statistical Model Creation framework.                                                                                                                                                                                                                      | 22                                                    |

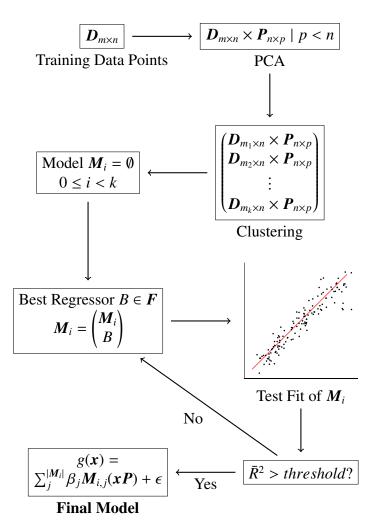

| 4  | The steps of model construction                                                                                                                                                                                                                                                            | 25                                                    |

| 5  | The structure of the SST/macro simulator                                                                                                                                                                                                                                                   | 32                                                    |

| 6  | Creation of a compete application skeleton from its original.aOriginal application.bSkeleton application with communication calls replaced with a model,<br>while retaining correct control flow.cSkeleton application with the inclusion of both communication and<br>computation models. | <ul><li>34</li><li>34</li><li>34</li><li>34</li></ul> |

| 7  | Transformation of a simple function into a compute model. The original application is transformed into data collection and skeleton versions during compilation.aAnnotated OriginalbData CollectioncSkeleton                                                                               | 38<br>38<br>38<br>38                                  |

| 8  | Example function (a) and the same function where the computation is replacedby the loop model (b)aExample function performing computation.bComputation replaced with model.                                                                                                                | 40<br>40<br>40                                        |

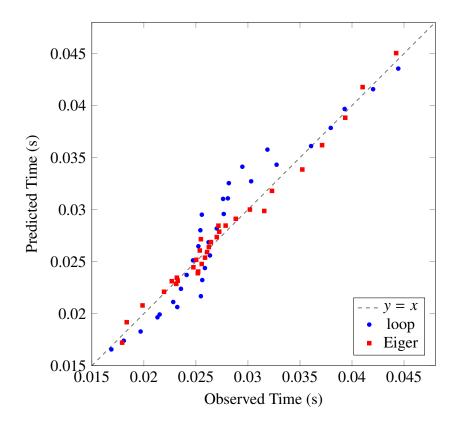

| 9  | Observed training values and their associated loop model predictions for MiniFE Dirichlet boundary condition region of computation.                                                                                                                                                        |                                                       |

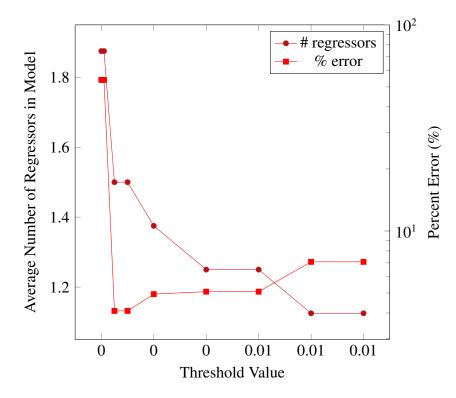

| 10 | Effect of threshold value on overfitting for HPCCG.                                                                                                                                                                                                                                        |                                                       |

| 11 | Error in simulation predictions of application runtime.                                                                                                                                                                                                                                    | 45                                                    |

| 12 | Speedup of simulator runtime over native execution.                                                                                                                                                                                                                                        | 46                                                    |

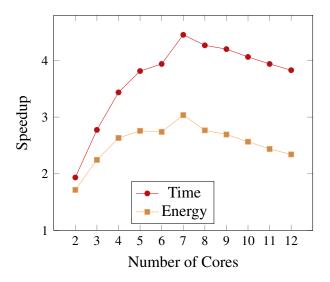

| 13 | Energy and time speedup for strong-scaling study of HPCCG mini-app on a Sandy Bridge-EP platform.                                                                                                                                                                                          |                                                       |

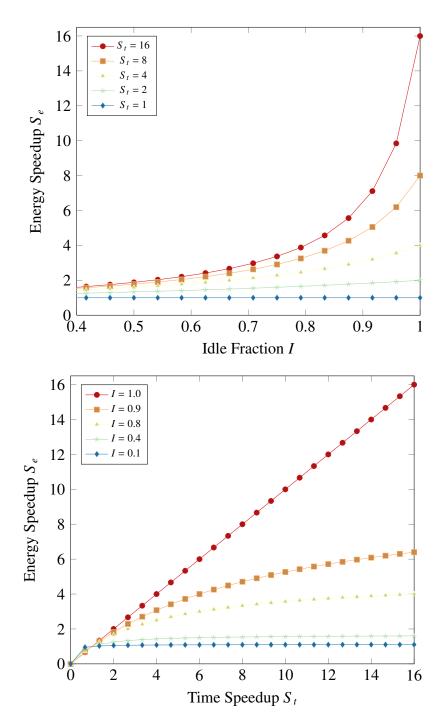

| 14 | Achievable energy speedup as a function of: a idle fraction of energy for dif-<br>ferent time speedup values, and b time speedup for different idle fractions of<br>energy.                                                                                                                | 54                                                    |

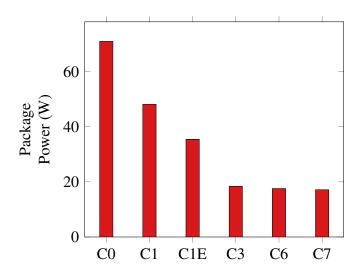

| 15 | Idle power for each core C-state on the Sandy Bridge-EP platform when running a stress microbenchmark.                                                                                                    | 55                   |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

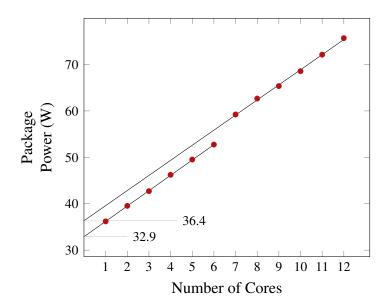

| 16 | Sandy Bridge-EP platform power as the number of compute tasks increases, extrapolating the idle power.                                                                                                    | 56                   |

| 17 | Error between measured energy speedup for the baseline model and progressive improvements due to extrapolated idle power and per-application active power.                                                | 59                   |

| 18 | Task configuration points and resulting Pareto frontier for the DPOTRF task from<br>Cholesky factorization.                                                                                               | 60                   |

| 19 | Task graph showing task dependencies for a 4×4 tile-base right-looking Cholesky decomposition.                                                                                                            |                      |

| 20 | Pareto frontiers for each task in CG, Cholesky, and LU task graphs                                                                                                                                        | 65                   |

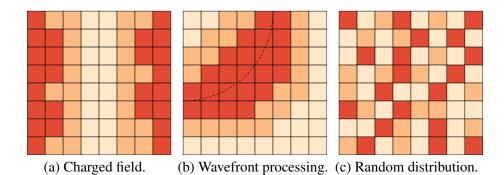

| 21 | Load levels for the three workloads on an 8 × 8 processor configuration. Colorindicates relative processor load from light (low) to dark (high)aCharged field.bWavefront processing.cRandom distribution. | 74<br>74<br>74<br>74 |

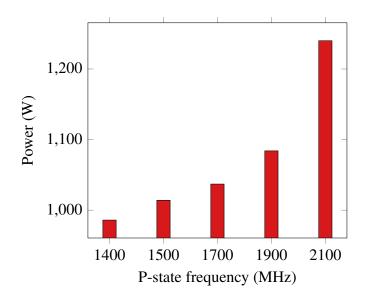

| 22 | Measured power states for an AMD Interlagos quad-node on the PAL system running a stress microbenchmark at the given frequency state.                                                                     | 77                   |

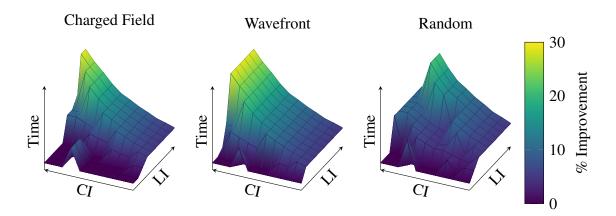

| 23 | Relative runtime improvement for three workload types when using Dynamic Power Steering as a function of compute intensity and load imbalance.                                                            |                      |

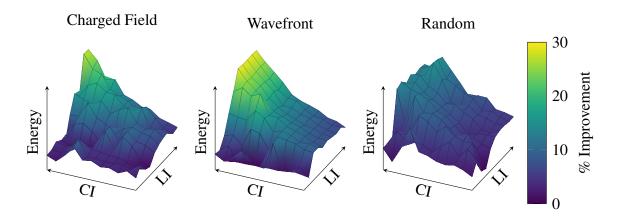

| 24 | Relative energy improvement for three workload types when using Dynamic Power Steering as a function of compute intensity and load imbalance                                                              |                      |

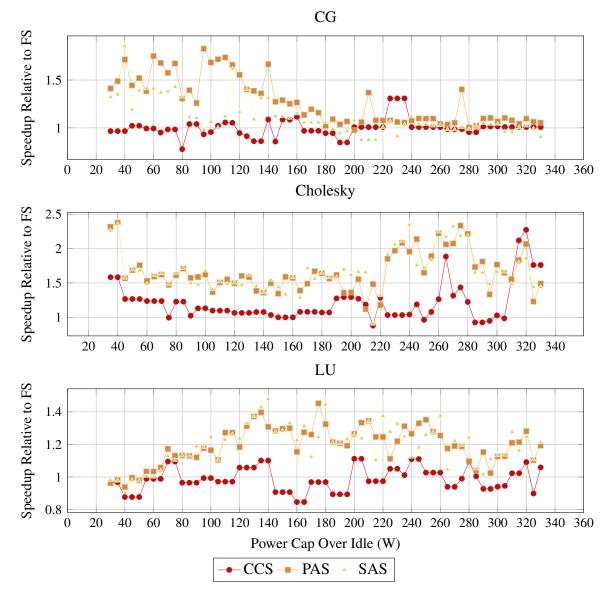

| 25 | Relative performance of the CCS, PAS, and SAS schedulers over the Fair Sched-<br>uler for the three task graphs as a function of the power cap                                                            | 85                   |

## SUMMARY

The objective of the proposed research is to create a methodology for the modeling and characterization of extreme-scale applications operating within power limitations in order to guide optimization. While extreme scale systems get larger, the amount of power they may draw at one time is changing very little. This places immense pressure on ensuring that the design is energy-efficient. To combat this pressure, the hardware is being designed to expose unprecedented degrees of parallelism and complexity, necessitating new programming models. However, efficient hardware is not enough to reach exascale performance goals; it is necessary to understand the energy behaviors of applications to guide their development. Optimizing extreme-scale applications to operate within power limitations will require new techniques for understanding the relationships between application characterization, performance, and energy. The main contributions of this work are:

- A method for modeling execution time and energy for regions within applications.

- Models of energy scaling and the trade-off between performance and power.

- Power-constrained performance scheduling of synchronous and asynchronous applications.

The foundation for addressing these problems is the modeling of time and energy consumption of applications. The different forms these models take provide the necessary insight to approach these challenges. The first challenge is addressed with the development of automated techniques for the construction of fast models of time and energy parameterized by application-level information. These models are used to drive macro-scale simulations, giving developers feedback on the performance of their applications on future large-scale systems. The second challenge is addressed by improving existing analytical energy scaling models to show how time and energy are related as the system scales. This leads into the use of Pareto frontiers to describe a reduced set of configurations that achieve the highest performance for a given power. The third challenge is addressed with a set of runtime heuristics, guided by performance and power models, for driving the configuration selection of tasks in both bulk-synchronous parallel and asynchronous, task-based programming models. Collectively, these techniques provide the necessary insight into the energy consumption behavior of applications to ensure that they are designed in a way that achieves the highest performance when constrained by power limitations.

This thesis illustrates how the appropriate application of models for energy can help ensure the energy-efficient design of next-generation extreme scale systems.

# CHAPTER 1 INTRODUCTION

High-performance computing is trending towards extreme scale where the quantity of data operated on is growing dramatically [11]. In order to reach exascale— $10^{18}$  operations per second—it is projected that machines will need millions of execution cores. It is likely that these new machines will operate with stringent power caps [80] where the amount of power the systems may draw at one time is fixed. Likely this will manifest as an overprovisioning of compute resources (e.g., processor cores, memory channels, clock frequency states) that cannot be used concurrently [31]. This imposes a new challenge for balancing performance and energy consumption in the design of these next-generation systems as the performance of the systems is tied to their energy-efficiency. These new architectures require that applications be written with new programming models to ensure efficiency gains, particularly as the development of future exascale systems is driven in large part by the rapid feedback cycle termed *codesign* [75]. In the codesign regime the hardware and software communities work together, communicating design trade-offs across the entire system stack. It is founded upon effective methods for describing the requirements and effects of design decisions as they pertain to the performance of the system. As a result, it is necessary to understand the energy behaviors of applications and the trade-offs imposed by future systems. This is synthesized in the following problem statement: performance optimization of extreme-scale systems that operate within power limitations require new techniques for understanding the relationships between platform characterization, performance, and energy consumption as a function of the applications being executed.

Existing techniques at the architecture level to address this problem have focused on hardware design, presenting mechanisms for observing their energy behaviors and tuning their architectures to provide the highest performance per watt. However, these techniques are insufficient to address the rigorous energy-efficiency demands of exascale systems. The

Figure 1: Application-level models provide a foundation for the three challenges addressed in this thesis.

increased synergism between the hardware and software created through the codesign process necessitates explicit consideration of the specific applications used when designing energy-efficient systems. Writing energy-efficient applications is itself a challenge, especially as the industry shifts to more dynamic programming models such as asynchronous task-based models. In order to fully address the problem of energy-efficient exascale systems, there needs to be a methodology for characterizing the relationships between energy and performance of the application's component parts, as well as how to quickly iterate over application designs to converge on a design that fits within the power constraints for a target system. This characterization is necessary to guide the developer to ensure energy efficient applications.

To that end, this dissertation presents a methodology for modeling and characterizing applications in order to both steer the design of energy-efficient applications as well as improve the energy consumption and performance of applications at runtime. At a high level, this thesis addresses the following challenges:

1. How can system-level models for the execution time and energy behavior of applications be developed?

- 2. What is the relationship between time and energy scaling and how does configuration (i.e., number of cores, clock frequency) affect performance and power scaling behaviors?

- 3. How can these models of time and energy drive the decision-making process during execution to speed up applications under a power cap?

The relationships between the contributions of this work are shown in Figure 1. The foundation for addressing these problems is the modeling of time and energy consumption of applications. The different forms these models take provide the necessary insight to approach these challenges. The first challenge is addressed with the development of automated techniques for the construction of fast models of time and energy parameterized by application-level information. These models are used to drive macro-scale simulations, giving developers feedback on the performance of their applications on future large-scale systems. The second challenge is addressed by improving existing analytical energy scaling models to show how time and energy are related as the system scales. This leads into the use of Pareto frontiers to describe a reduced set of configurations that achieve the highest performance for a given power. The third challenge is addressed with a set of runtime heuristics, guided by performance and power models, for driving the configuration selection of tasks in both bulk-synchronous parallel and asynchronous, task-based programming models. Collectively, these techniques provide the necessary insight into the energy consumption behavior of applications to ensure that they are designed in a way that achieves the highest performance when constrained by power limitations.

The next section describes the key contributions of this work, followed by a summary of the structure of this document. The key contributions have also been presented in several publications [53, 15, 9, 10, 8].

# **1.1 Contributions**

This thesis makes the following major contributions.

#### 1. Modeling of execution time and energy for regions within applications

The first contribution of this thesis approaches the problem of creating time and energy models of scientific applications that can scale to a large number of nodes. Traditional high-accuracy modeling techniques such as cycle-level simulation can take hours to days of time to run. However, moving towards exascale will require system-level simulations which is only achievable with composable models that can be evaluated quickly. This thesis addresses this concern with a method for constructing models of applications based on profiling data. In leveraging profiling data, this technique generates statistical models for behaviors of applications as a function of the program parameters. The model generation procedure is customizable, allowing for domain-specific knowledge about the behavior of the application or the architecture to inform the modeling process. These models are much faster to evaluate than cycle-level simulations, providing a mechanism to replace regions of computations within large-scale applications for fast large-scale simulation. Application skeletons, stripped-down versions of applications originally used for network studies [88], are used as the vehicle for these simulations. By replacing the time-intensive computation within these skeletons with analytic models of time and energy behaviors, the accuracy of the simulation is maintained while reducing simulation execution time.

In order to evaluate this modeling methodology, this work contributes *Eiger*, a framework for the creation of statistical models of execution time and energy for regions of computation [53]. These models represent execution behavior based on empirical data, parameterized by source code-level information. The Eiger framework has three main components: reading in instrumentation data, iterative model generation, and output of the model for use in large scale simulation. The first step is achieved with the Lightweight Performance Data Collectors (lwperf) tool to facilitate the collection of performance data. This tool is robust in the instrumentation

sources it can draw from; it has been used with real hardware, simulators, and emulators. This data is then fed into Eiger for model generation. This model generation procedure is semi-automated, learning an appropriate model from the input data, but able to leverage domain-specific information. It uses stepwise regression to adaptively add terms to the model so long as they improve the model's fit. As well, the instrumentation data can be passed on to the R programming language [68] for more complex model generation. Once the model has been constructed, it is output into a structured format for use in external tools. The use of these models have been shown to accelerate simulation of high-performance applications on both CPUs and GPUs with minimal error, when predicting both execution time and energy consumption [9].

#### 2. Models of energy scaling and the trade-off between performance and power

While the prior work demonstrated the ability to estimate energy consumption for regions of applications, it does not address how energy consumption scales with parallelism. In the pursuit of high performance, computer systems are being developed with an increasing degree of parallelism. While time behavior under parallelization is well studied, energy behavior has received significantly less attention. While existing analytical models of energy scaling have been presented [90], they have been used almost exclusively as high level estimates with little corroborating measurement data.

This thesis presents the key observation that although execution time can be overlapped in time through the use of parallelization, energy cannot; energy is the cumulative cost for all the *work* performed, regardless of whether that work happens sequentially or in parallel. Total energy consumption does have a time-dependent portion, relating to the time a system has to be powered on. In general, total energy consumption is decomposed into two parts: the *idle energy*, which is the energy cost associated with running an inactive system, and the *dynamic energy*, which is all energy that is consumed by the application performing computation. Breaking down total energy into its two parts forms the basis for the energy scaling model. For this model, idle energy scales proportionally to time speedup, where as the work (dynamic energy) remains constant. This thesis shows how characterizing the platform and the application are necessary to determine the ratio of idle to dynamic energy. Experimental data on modern shared memory multicore architectures demonstrates how this model accurately represents the energy scaling behavior of an application as a function of time scaling behavior.

The selection of degree of parallelism is just one way in which the configuration of an application affects performance and energy behaviors. Other features, such as dynamic voltage and frequency scaling (DVFS), can also be used to present different trade-offs between performance and power for a target platform. However, the combinatorial explosion in the number of configurations makes selecting the appropriate configuration challenging. This thesis proposes reducing the state space with the use of *Pareto frontiers* to identify those configurations that achieve the highest performance for a given amount of power. Importantly, these frontiers are dependent on the application and platform. This thesis proposes the identification of Paretooptimal configurations to describe the trade-offs between performance and power. These frontiers are used as the model for time and power behaviors as a function of configuration. An experimental analysis of Pareto frontiers is performed on a set of tasks taken from HPC applications run on a large shared memory multicore system.

# 3. Power-constrained performance scheduling of synchronous and asynchronous applications

The prediction of application execution time and energy behaviors can also be

leveraged to make decisions at runtime for systems constrained to operating under a power cap. This thesis presents two complimentary techniques for increasing performance of applications both across nodes and within a node. First, this thesis presents Dynamic Power Steering, a method for optimizing execution of loadimbalanced bulk-synchronous applications in power-limited environments [15]. In the bulk-synchronous programming model, computation is periodically synchronized at global barriers. However, there may be imbalance in the amount of work assigned to the nodes in the system, which may change over time. Because of this, some nodes may finish their work and reach the barrier before others. This idle time is called slack [50]. The Dynamic Power Steering approach uses DVFS to slow down nodes that would reach the barrier too quickly and speeds up nodes that are the last to reach the barrier, so long as the system remains under the power cap. This technique uses system-level models of node power and performance to direct the application of the available power. This work explores the effect of Dynamic Power Steering for three synthetic workloads that represent typical workload imbalance in BSP applications. Experimental results are shown for a power-instrumented cluster.

The second technique presented in this thesis addresses the power-constrained scheduling of applications on shared memory, high core count multicore processors. An important programming model is the task graph-based application, which mixes coarse-grained, asynchronous tasks with fine-grained intra-task data parallelism. A major challenge with this application model is dynamically selecting which tasks to schedule and how many cores to assign to each task. This decision is further complicated when a power cap is imposed, since there is a non-trivial relationship between number of threads and power consumption.

This thesis contributes a set of scheduling heuristics that determine which of the available tasks should run as well as how to configure their execution. In order to make this decision, the heuristics leverage the previously described Pareto-optimal configuration information to evaluate the trade-offs between performance and power consumption. This work demonstrates the benefits of power-aware scheduling over baseline static techniques across a wide range of power caps on a high core count, shared memory system.

# **1.2 Organization**

This dissertation is organized as follows.

Chapter 2 describes the landscape for application modeling and power-constrained optimization. It contains an overview of techniques used to model the behavior of applications, both as it pertains to simulation at scale as well as modeling energy consumption. In addition, this chapter includes a description of analytical modeling techniques for applications as they scale, and the major existing methods for optimizing the performance of both bulk-synchronous parallel and asynchronous task-based programming models. Additional related work is included toward the beginning of each chapter as appropriate.

Chapter 3 presents the method for constructing models of time and energy behaviors of applications as a function of program parameters. These techniques, encapsulated in the Eiger and lwperf tools, are used to construct statistical models of execution time and energy from instrumentation data. These models replace regions of computation within *Application skeletons*, the vehicles for macro-scale simulations, which are shown to increase the accuracy of system-level energy and performance models while reducing simulator execution time.

Chapter 4 examines the creation of energy scaling models and formulating the tradeoffs between performance and power as Pareto frontiers. These models describe the increasing energy cost for executing applications in parallel as a function of the execution time speedup as well as a characterization of application and platform. This chapter then describes some methods for improving the fidelity of the energy scaling model, as well as an evaluation of the model for HPC workloads on a server-grade system. Additionally, this chapter presents the characterization of system configurations into Pareto-optimal points in the performance–power space. By providing this formulation, Pareto frontiers represent the configurations of the application, such as the degree of parallelism or DVFS state, as a trade-off between performance and power.

Chapter 5 builds on the energy and performance modeling work to provide heuristics for improving performance of applications when power constrained. This begins with a description of the Dynamic Power Steering technique for bulk-synchronous applications, with experimental evaluation on a test bed cluster system. This chapter then expands on this methodology for asynchronous task-based application scheduling. Several heuristics are presented which leverage the Pareto frontier formulation of power–performance trade-offs to increase performance while remaining under a power cap. Several task graphbased HPC applications are demonstrated to achieve greater performance while power constrained compared to baseline static limiting techniques.

Finally, Chapter 6 summarizes the contributions and conclusions from this thesis as well as contemplating future areas of research.

# CHAPTER 2 RELATED WORK

This chapter documents the important research that frames the work in this thesis. It is broken down into several parts, broadly broken into the three main themes from this dissertation: performance and energy estimation applications, modeling of time and energy, and methods for optimizing performance of parallel applications in the face of power limitations. These prior works lay out the framework for the thesis, outlining current trends in application modeling. The sections below will walk through the relationships between existing works, as well as indicating the gaps in those works, questions left open, and how the goals of those works are different from those presented in the subsequent chapters of this thesis.

# 2.1 Performance and Energy Estimation

In high performance computing, a wide range of performance prediction techniques are used depending on the quality of estimate desired, as shown in Figure 2. Simulators range from high-fidelity and computationally expensive simulators for measuring performance between two nodes [85] to lower-fidelity and lower-cost simulators that can estimate performance on large-scale machines[88]. Often emphasis is on MPI emulation or simulation, with prominent simulators including BigSim [93] and SIMGRID [20] in addition to SST/macro [71]. There are notable examples of simulators that fit application runtime to analytical models [40]. The following sections describe key efforts in the literature that address energy and performance modeling across the fidelity–cost spectrum.

# 2.1.1 Large-scale Simulation Techniques

Three well-known approaches have been investigated for estimating performance at scale. The most common approach is direct execution of the full application on the target system [66, 70]. This simulation approach uses virtual time unlike normal benchmarking that

Figure 2: Spectrum of different modeling granularity and the associated quality.

uses real time. Another approach requires tracing the program in order to collect information about how it communicates and executes [93]. The resulting trace file contains computation time and actual network traffic. Still, tracing does not scale to a different number of processors or new problem sizes. A third approach is to implement a model skeleton program as a simple, curtailed version of the full application but complete enough to simulate realistic activity [5]. This approach has the advantage that the bulk of the complex computation can be replaced by simple timing information. The skeleton application provides a powerful method for evaluating the scalability and efficiency over various architectures of moderate or extreme scales.

Some approaches investigate automatically synthesizing skeletons from communication traces [4], but this requires extensive trace collection and may not capture behavior produced with extrapolated application parameters outside the calibration range. Static analysis techniques have been used to identify computations that have no impact on control flow or communication and replace them with symbolic estimates for time [5]. Automated methods have been demonstrated for transforming scientific codes through the use of both static analysis and runtime information in the form of MPI communication patterns [67, 77].

The use of application kernels in performance analysis is well established. Two widelyused collections of kernels are the NAS Parallel Benchmarks (NPB) [12] and the PARK-BENCH suite [30]. The kernels in these suites represent common computational patterns that are found in many full-scale applications. While these suites provide simpler implementations of important algorithms than full scientific codes, they represent generic algorithms that lack any nuances that would be found in specific application implementations.

#### 2.1.2 Performance Prediction Using Models

While simulation can give accurate predictions of execution behavior, it is a tool used late in the design stage. Instead, approximate behavior is encapsulated into models that provide a reasonable estimate while remaining intuitive and fast to evaluate. The most general of these models, known as *analytical models*, provide a mathematical expression to describe performance. These models have been used to predict network performance [25] and to describe how Amdahl's Law can be extended to energy in multicore processors [90]. Another example is the roofline model which relates the computational intensity of a workload the ratio of computation to memory demand—to performance [89] and energy [23]. The roofline model focuses only on the characterization of the application under the fixed behavior of the platform, under the goal of energy optimization. A more nuanced approach is to examine the energy behavior of individual instructions [76]; this modeling technique allows for individual characterization of the hardware and software, which can be combined orthogonally.

In addition to predicting execution behavior, models have been used to quickly search large design spaces. Jia et al. [46] present such a technique which simulates a random subset of GPU designs from a very large design space then applies a stepwise regression modeling algorithm to construct a performance estimator. These models tend to be powerful but hard to introspect. Cook et al. [24] describe a Monte Carlo method for design space exploration and performance prediction using sampling and statistical methods. Automated regression analysis [33] constructs an analytic model determined from a set of training samples. In order to manage model complexity and optimize training error rate, a forward-stepwise procedure is used to aggregate basis functions based upon adjusted coefficient of determination, a modification of the coefficient of determination that adjusts for the number of terms in the model [55].

#### 2.1.3 Statistical Modeling of Performance

Various techniques from the field of machine learning have been used to predict the performance of applications, rather than to select an optimal design from a large design space. Statistical techniques are often used to characterize the behavior of applications; Genbrugge et al. [35] describe a method for constructing a synthetic trace of a program execution bearing the same statistical properties as a complete execution but of much shorter overall length. These techniques provide methods for reducing design space, but struggle to disclose why one particular design may be better than others, providing little insight to the application developers.

Applications have been characterized using principal component analysis [42] and hierarchical clustering [37] in order to describe the differences between applications in benchmark suites as well as to indicate how applications stress different parts of the hardware pipeline. One technique used to predict execution time, power, and energy consumption is Artificial Neural Networks (ANNs) [43, 83]. While this method provides high quality predictions, it obscures the meaning and interpretation of the model while prohibiting the designers from informing the modeling process. Some works [81] use linear regression models to predict performance and energy for the entire execution of the application. Hong et al. [41] propose a predictive analytical performance model for GPUs along these lines.

In addition to performance prediction, other techniques explore how to estimate the performance of applications by collecting data from existing architectures to predict for previously unseen architectures. Kerr et al. [54] explore an approach based on Principal

Component Analysis [47] to automatically select the correct metrics to model GPU workloads executing on either GPUs or CPUs. This method provides a good framework for understanding the execution behavior of kernels of execution, setting the stage for adding statistical models to skeleton applications presented in this work.

#### 2.1.4 Power Measurement Facilities

The previous subsections describe estimation techniques that rely on accurate input data. While measuring performance for these systems is typically straight forward, the ability to measure power draw has only been recently added as a feature. CPU-specific methods have lead the way, such as the model-specific registers provided by recent Intel parts through the Running Average Power Limit (RAPL) infrastructure [1] and corresponding AMD tools [6]. Accelerators are often the goal of power-measurement, with tools like NVIDIA's NVML library for accessing GPU power information [63], or Intel's libmicmgmt library for accessing information about the Xeon Phi coprocessor cards [2]. Cray has provided an system for monitoring and measuring the power consumption of their clusters [59]. Other methods for energy measurements leverage external meters [34]. These measurement tools have been aggregated by wrapping libraries such as PAPI [61] and the PowerAPI specification [18].

# 2.2 Analytical Models of Time and Energy Scaling

The majority of scalability work has focused on understanding performance behaviors, both in predicting scaling behavior as well as determining performance bottlenecks. The energy scaling model has been explored from the perspective of clock frequency [22], giving a measure for the relationship between scaling and energy. This has been extrapolated to an optimization function for selecting configurations given die area constraints [21]. The Amdahl's Law-style model for performance and power have motivated exploring energy scaling on multicore processors, concluding that with current trends it is untenable to keep all devices powered up at the same time, known as *dark silicon* [31]. Rather than purely

analytical models, several simulation frameworks have been used to predict both performance and energy [78, 82] under scaling. This includes work that adds models of energy consumed during regions of computation to large-scale simulations [9].

# **2.3 Optimizing Performance Under Power Limitations**

Going forward, not all computing resources will be active at any one time as insufficient power will be available. In the HPC space, power constraints limit the extent to which large-scale systems can grow. To combat this, several techniques have been developed to increase energy efficiency, resulting in better performance. Recent work includes designing energy efficient runtimes for hybrid programming models [57], and graph algorithms [73]. The Adagio runtime system predicts execution 'slack' to provide energy optimization for applications [72]. However, the approach assumes Bulk Synchronous Parallelism (BSP) in which the model of execution consists of multiple steps each containing a compute followed by communication that is often global [36]. This does not provide the best energy efficiency for applications with complex and time- dependent processing patterns including those in wavefront applications that have benefited from the Energy Template approach [52].

The work by Etinski et al. [32] optimizes job scheduling to make best use of an available power budget. A framework that exploits barriers for energy efficiency has also been explored [58]. Green building blocks and methodologies for hybrid execution for providing energy efficiency in the runtime system was proposed in [56]. Several techniques that use Dynamic Voltage Scaling, including a just-in-time method [50], enable a processor-core to slow down if the assigned computation is lower than on others. Methods for designing energy efficient collective communication primitives using MPI have been studied for a range of applications [49].

Tackling the problem of power limits for HPC systems has presented many techniques for increased energy efficiency. Understanding when imbalance occurs in an application in order to reduce energy when executing some applications under a power cap has been demonstrated [15]. These works apply to only bulk-synchronous programming models, whereas the work presented in this thesis is more general, presenting techniques that work for both bulk-synchronous as well as the more complex asynchronous task graphs.

Zhang [92] provides a survey of methods for enforcing a power limit, both by the hardware and software. However, the surveyed techniques are viewed from the perspective of administration, ensuring that limits are met within a timely manner. Methods for increasing energy efficiency by adjusting the configuration either of the number of threads given to each task [79] or the configuration of the hardware, tweaking either the frequency states or number of available cores for use [13] have been demonstrated. Additionally, work by Patki et al. [64] shows the effect of power-aware job scheduling depending on user behavior. While not focused on executing task graphs, that work provides a foundation for applying power limitations to entire clusters, ensuring fast task turnaround time based upon user requirements.

# 2.4 Power-Aware Parallelism for Task-Based Applications

The problem of effectively scheduling task graphs has been shown to be difficult, particularly when additional constraints, such as limited power or number of cores, need to be considered. The work by Buttari et al. [19] describes the formulation of linear algebra algorithms including Cholesky and LU decompositions into tasks and describing their performance improvements over more traditional algorithms. The DAGuE runtime [17] provides a programming model and framework for the execution of task graphs for the HPC domain, focusing on scale and speed of execution for large problem sizes, and has been used to implement the DPLASMA library of dense linear algebra functions for distributed systems [16]. This formulation of asynchronous DAGs has been expanded by Wu [91] to add an additional layer of hierarchy, distinguishing between the coarse-grained task parallelism and the fine-grained data parallelism within a task which has been termed *elastic* or *parallel* tasks [74, 86]. To address the scheduling of graphs when constrained by the number of cores available, Barbosa el al. [14] present a static method and Vydyanathan et al. [87] present a dynamic method for assigning cores to tasks to minimize execution time. These works use analytical performance models based on the task workload. In contrast, this thesis focuses on the empirical behavior of tasks to classify their execution.

Recent work has explored measuring the power behavior of task-based applications [60], paving the way for appropriately scheduling individual tasks so as to optimize performance under power caps [13]. One large focus of work in this area is to understand the way parallelism affects time and energy. Cho et al. [22] examine the theoretical relationship between these three built off of Amdahl's Law-style analysis. The technique proposed by Curtis-Maury et al. [26] leverages machine learning to select the degree of parallelism that optimizes performance and power consumption. Work by Vydyanathan et al. [87] expands upon this notion, providing a method for optimizing the runtime assignment of parallelism either within a task or across tasks.

Research has been shown to estimate the performance, power, or energy behavior of application tasks as a function of frequency state [27]. The models in Chapter 5 leverage Pareto frontiers to describe the power and performance for each of the tasks. Pareto-optimal configurations have been used to characterize system designs across multiple cores [31].

# 2.5 Concluding Remarks

The evolving landscape of HPC application and system development has created a large corpus of work addressing the issues of performance and energy modeling, operating under a power cap, and scheduling task graphs. Moving forward into the exascale regime, the demands for understanding the behaviors of applications, particularly as they scale, will become necessary. While existing work has isolated key issues within these domains, this thesis focuses on treating energy consumption as a first-class resource, which has so far been typically considered only secondarily. By providing an understanding of the energy behaviors of applications, new models can be constructed to help estimate behaviors at

scale, as described in Chapter 3, easily describe the trade offs between performance and energy efficiency, as in Chapter 4, and provide a mechanism for making runtime decisions to increase performance under a power cap, discussed in Chapter 5.

### CHAPTER 3

# **APPLICATION-LEVEL MODELING OF TIME AND ENERGY**

Both the scientific and enterprise computing domains are seeing the rise of extreme scale systems to handle explosive growth in problem sizes. These systems will need to be designed without the luxury of prototyping to fit within the tightening constraints of power, heat dissipation, memory bandwidth, and processor speed as discussed in Chapter 2. Hardware–software codesign will play a key role in their development. The power constraints of future systems will place greater emphasis on quickly evaluating the energy consumption of applications in addition to their execution time.

Developing accurate models of the time and energy consumption of applications is a complex task [11]. Cycle-level hardware simulation is infeasible at scale motivating the need for more abstract models of the *effects* of computation on the system rather than the *mechanism*. A key contribution of this work is the use of statistical modeling to learn the relationships between application-level parameters and the time and energy behaviors on the target platform through analysis of instrumentation data taken from the application running on real hardware. This modeling technique can flexibly handle model construction for complex architectures and applications while reducing domain expertise required by users building the application skeletons. This method is used across execution models and language selection to predict both execution time and energy. This work presents the Eiger Statistical Modeling Framework [53] as a tool for reading instrumentation data, iteratively constructing models, and emitting them for use.

This chapter proposes a large-scale modeling methodology based on the notion of *application skeletons*. These are application implementations where regions of code (such as compute-intensive loop nests) can be replaced by analytic models of their physical properties (e.g., execution time and energy). A second contribution of this work is a method for the creation of these skeletons, collecting instrumentation data, and feeding it into the

Eiger framework to generate models. After the models are generated, calls are inserted to replace the computation with queries to the models. This instrumentation functionality is encapsulated in the lwperf instrumentation infrastructure.

These skeletons form the vehicle for *macro-scale simulation*, where candidate applications and hardware configurations can be simulated at the scale of hundreds or thousands of cores to understand the impact of system design at scale. Inter-node communication is modeled as flows on the network, which is analyzed for congestion behavior and its impact on system performance. Such simulations have demonstrated high scalability [88], capable of reaching tens of thousands of nodes. However to ensure high-fidelity simulations, these abstracted communication models must be coupled with fast, accurate end-point computation models. This work contributes an analysis of the use of Eiger models in application skeletons for macro-scale simulation. Included is a demonstration of the increased accuracy of the application skeleton, as well as the trade-offs in simulator overhead.

The main contributions described in this chapter are:

- The generation and use of statistical models to predict how different input parameters translate into execution time and energy for regions of computation.

- A technique for converting an application into a skeleton.

- The application of computation models in application skeletons to permitting high-fidelity simulation at scale.

# 3.1 Statistical Models of Application Execution Time and Energy

This section describes an automated statistical approach for modeling program behaviors on diverse architectures. The objective is to *design and implement a methodology* for discovering and synthesizing analytic performance models of the execution time and energy consumption of applications running on target heterogeneous processors.

This approach discovers analytic relationships between the static and dynamic parameters of an application and performance metrics. For example, one may wish to capture the impact of the sparsity of input data structures, dynamic execution count, and number of function calls on the execution time. Or one may wish to discover a relationship between the number of double precision load operations, number of DMA calls, and occurrence of unconditional branches on energy consumption. These are usually complex relationships that elude manual discovery or effective application of off-the-shelf models. This complexity is magnified in modern and emerging heterogeneous processors. Broadly, this methodology is comprised of 1) experimental data acquisition and database construction, 2) data analysis passes over the database (possibly creating new higher order data), and 3) model selection and construction. The analysis passes can utilize existing data analytics techniques. The last phase automates the creation of model files for use with external tools.

Eiger is a methodology for constructing statistical models from instrumentation data. Eiger provides a standardized infrastructure and API for adding instrumentation to applications, a relational data store for collecting and managing that data, and a workflow for the creation and analysis of models. The original version of the Eiger tool was used to estimate performance across GPU models [54]. The main goal of this second generation of the Eiger project is to facilitate intelligent, semi-automated model construction without requiring expert knowledge of hardware or software. Instead of meticulous domain analysis, the models are learned from the measurement data. The infrastructure is designed for flexibility in adding new parameters controlling model construction and trading accuracy for performance.

The current implementation achieves these goals via statistical methods for dimensionality reduction and automated model selection. Eiger constructs coarse-grain predictive models when trained with results of similar applications on similar machines. The regression models may be as simple or complex as desired using metrics ranging from fine grained counts of instruction distributions to coarse grain estimates of computation working set size. The infrastructure is easily extensible to new sources of measurement data and supports the incremental addition of new experimental data. Its modular structure supports

Figure 3: Implementation details of Eiger Statistical Model Creation framework.

the easy addition of new analysis and model construction passes. Consequently, the infrastructure will benefit from other explorations in the community by lowering the barriers to entry in performance model generation or synthesis.

A detailed illustration of the Eiger framework is provided in Figure 3. The framework encompasses an automated process in which application profiling data is collected via a standardized interface and ultimately used to construct a model of execution time, energy, or any other dependent result metric. The resulting statistical model may be then composed with other tools and applications such as simulation environments, heterogeneity-aware process schedulers, and reporting tools. The following are the key components of this infrastructure.

#### 1. Measurements

Eiger uses a relational database to manage the storage of all data accumulated during profiling runs as it allows asynchronous insertions while allowing for rigorous relational specifications. Additionally, Eiger provides support for the scenario where execution runs of multiple tools are required to construct a single data point (trial). This data can be drawn from many sources, including real hardware, simulators, and emulators. This data is internally stored within the Eiger framework for the subsequent analysis and construction passes.

#### 2. Analysis

After the measurement process, the data is fed through a flexible series of analysis passes to prepare it for model generation. An analysis may in turn generate new data that is also stored within the Eiger framework to be the candidate for future analyses or model construction passes. One example of an analysis pass is Principal Component Analysis (PCA) which is a well-known dimensionality reduction technique. Benefits of reducing the dimensionality of the input dataset are manifold; it speeds up the model generation process, improves the clarity of the resulting model, and allows for intuition into the correlations between input metrics. A more in-depth examination of the entire modeling process is described below.

It is important to note that PCA is an *unsupervised* learning technique in that it does not take the performance metric into account when choosing dimensions to eliminate. It is entirely possible that a dimension with low variance may have a larger affect on application performance than one with high variance. For example, number of cores may not have as large a variance as memory bandwidth for a range of machines but a greater impact on runtime for compute-bounded applications. PCA does not explicitly specify how many dimensions to retain; rather it relies upon the user to make the final decision.

#### 3. Model Construction

After initial analyses are performed, the data is ready to move into the model construction pass. This pass provides a built-in method for constructing statistical models to show how a general technique can be used to generate models of application execution time and energy. This modeling process is outlined in the following subsection.

As well, an interface to the R programming language [68] is available, allowing for data to move back and forth between the two environments. R is a powerful language for performing sophisticated data analysis and modeling; making this interface available enables more modeling techniques from the domain of machine learning and data science to be applied to execution data.

#### 4. Reporting

Completed models consist of a set of transformation matrices from dimensionality reduction and cluster analysis as well as a vector of functions and their associated weights. Reporting passes over this data will format the information in a method easily consumed by the user, including plotting and statistical results. This phase also allows for the serialization and memoization of the finished models for later consumption. Finally, this phase produces model descriptions in a format that can be imported by system simulation tools and software modules such as run-time schedulers.

#### 3.1.1 Model Generation Procedure

The framework does not predefine what should constitute an input parameter or a performance metric. Input parameters may include hardware (e.g., cache size, cache line size, register file size) and software features (e.g., input data size, stencil size, DMA block size) while performance metrics are any measurable metric (e.g., execution time, energy, failure rates). The general procedure for model construction can be seen in Figure 4 and consists of three main components: Principal Component Analysis, Clustering, and Forward Model Selection.

### 3.1.1.1 Principal Component Analysis

Before any modeling takes place, Eiger constructs a single, large matrix  $D_{m\times n}$  representing all instrumentation data. Each column is a different input parameter and each row is a separate data point corresponding to a unique application execution. In its effort to minimize domain expertise to construct models, Eiger recommends liberally including input parameters, even if they ultimately will not be used in the model. This step, Principal Component Analysis (PCA) [47], aims to compress the number of columns, eliminating unnecessary

Figure 4: The steps of model construction.

data and simplifying model generation. A linear transformation  $P_{n\times p}$  is produced, converting the set of possibly correlated input parameters into a derived set of uncorrelated parameters. Derived parameters with low variance can be eliminated. A concern [48] with this technique is that even parameters exhibiting low variance may relate strongly to the dependent variable, and would be valuable information to discard. For this reason, PCA is leveraged to eliminate parameters with *zero* variance, simplifying the data set without throwing away information.

#### 3.1.1.2 Clustering

The next modeling step is Clustering, where similar data points (i.e., rows of the output matrix from the PCA step) are grouped together. Designing processors to accelerate general sets of workloads would be significantly simpler if all workloads exhibited similar performance characteristics. In contrast, real applications demonstrate varied performance behavior. Dense linear algebra workloads with regular control properties and compute-intensive inner loops differ significantly from irregular workloads with data-dependent branch behavior and load imbalance across threads. Goswami et al. [37] analyze the diversity of CUDA workloads and present a prioritized tree of benchmark applications sorted by how much each increases total variance of a given set of metrics.

Rather than using all the data points in the model fitting step, each cluster goes through fitting separately, under the assumption that this composite of fits will perform better. Applications exhibiting high correlation among principal components are clustered together. A single model trained from profiling data from all applications in a comprehensive benchmark is unlikely to yield high accuracy. Rather, the best model is likely to be obtained from training data gathered by a set of applications that are "similar" to the experimental application. Kerr et al. [54] provide empirical evidence that clustering and partitioning improves model accuracy.

Eiger uses *k*-means clustering, where a data point belongs to the nearest of k clusters. The center point of the cluster is defined as the mean of the input parameter values for all

Table 1: Model pool.

| Functions  |            |              |               |             |         |         |             |

|------------|------------|--------------|---------------|-------------|---------|---------|-------------|

| $x_i^{-2}$ | $x_i^{-1}$ | $x_i^{-1/2}$ | $\log_2(x_i)$ | $x_i^{1/2}$ | $x_i^1$ | $x_i^2$ | $x_i * x_j$ |

the data points in that cluster. Eiger performs the next step of model construction for each of the clusters, creating k different analytical expressions. When evaluating the model, the closest cluster must be found and its associated analytical expression used. Choosing the value for k is left to the user.

# 3.1.1.3 Forward Model Selection

The last transformation fits an analytical expression of the input parameters in a cluster to calculate the result metric. This is achieved with a linear combination of functions, called *regressors*, that are applied to the input parameters. These regressors come from a pool F of candidates. The model pool defines a set of possible basis functions which may be mapped to principal components and whose linear combination yields the resulting performance model. The model pool must be selected by the experimenter and should offer sufficient variety for maximizing goodness of fit of the resulting model. The model pool should include functions that closely model the space and time complexity of dominant algorithms within the applications of interest as well as non-linear combinations of several metrics. For example, compute-bound applications may demonstrate a very strong correlation between the product of clock frequency and dynamic instruction counts. Table 1 describes the basis functions used for this work.

In the Eiger framework a selection approach is taken to progressively include regressors in the final model only if they improve the quality of the fit. This approach is *forward* in the sense that it begins with an empty model and adds regressors to it, in contrast with a *backward* approach in which the model starts out with every possible function and unsatisfying elements are removed.

The stepwise procedure is outlined in Algorithm 1. Beginning with an empty model,

Algorithm 1 Selects a model that minimizes error over a cluster

- 1: profile, performance, modelPool = ... // initialize training data

- 2: threshold = ... // specification from user

- 3: finalModel = [] // empty set

- 4: currentRsquaredAdj =  $-\infty$

- 5: while not done do

- 6: maximum =  $-\infty$

- 7: for each each function left in modelPool do

- 8: add function to finalModel

- 9: U = apply finalModel to profile

- 10: beta = leastSquares(U, performance)

- 11: RsquaredAdj =  $\dots$  // calculate adjusted rsquared

- 12: **if** RsquaredAdj > maximum **then**

- 13: maximum = RsquaredAdj

- 14: newFunction = function

- 15: newBeta = beta

- 16: **end if**

- 17: remove current function from finalModel

- 18: **end for**

- 19: **if** maximum currentRsquaredAdj > threshold **then**

- 20: add newFunction to finalModel

- 21: remove newFunction from modelPool

- 22: currentRsquaredAdj = maximum

- 23: **else**

- 24: done = True // there are no more useful functions

```

25: end if

```

- 26: end while

- 27: return finalModel, beta, currentRsquaredAdj

regressors are chosen from the pool and added one by one to select the one that increases the quality of the fit the most. The coefficient of determination ( $R^2$ ) gives a measure of how well a model is able to map predicted values to their associated training value; it ranges from 0, indicating no correlation between the prediction and the observed valued, to 1, indicating exact replication by the model. Eiger uses the adjusted coefficient of determination ( $\bar{R}^2$ ), a modification of  $R^2$  taking into consideration the number of terms in the model [55].  $\bar{R}^2$  will decrease if the added regressor results in a model that performs worse than would be expected by adding a random regressor. To control over-fitting, in which the predictability of new data points is sacrificed in order to ensure the model approaches the training data as closely as possible, the winning regressor is only added if the amount by which it increases the fit is larger than a user-provided threshold. In this work, selecting the threshold value is an empirical procedure. Model construction finishes when there are no more models left in the pool or when the winning regressor *F*<sub>i</sub> and an associated weight  $\beta_i$ , plus an error term  $\epsilon$ .

There are instances where the user has some intuition about the relationship between input parameters and performance and wish to generate a model based on this intuition, (i.e., based on a specific set of regressors and input parameters). For example, the user may wish to construct a linear model or a model that is logarithmic in the input data set size. Consequently, Eiger enables the user to a) specify the set of regressors to be used, and b) specify the set of input parameters to be used. For example, even though the set of input parameters is quite extensive, the user may wish to construct a model based on two input parameters and two specific regressors.

# **3.1.2 Formal Specification**

Let  $m \in \mathbb{Z}$  refer to the number of *trials* executed for a multiplicity of applications, datasets, and machine configurations. Let  $n \in \mathbb{Z}$  refer to the total number of metrics (measurements) acquired per trial. These may include static application metrics, dynamic metrics acquired during the execution of the trial, and machine configuration parameters.

Define  $X \in \mathbb{R}^{m \times n}$  as an input dataset and  $R \in \mathbb{R}^{m \times 1}$  as a result set. Each row in X corresponds to a trial instance with result (e.g., execution time) in the corresponding row of the column vector R. Together, (X, R) captures sufficient data describing the application, machine, and performance characteristics to construct a model for R.

$$X = \begin{bmatrix} \vdots \\ m \text{ trials} \\ \vdots \\ \dots & n \text{ metrics} & \dots \end{bmatrix} \qquad R = \begin{bmatrix} \vdots \\ m \text{ results} \\ \vdots \end{bmatrix}$$

Principle component analysis (PCA) yields a projection P from X onto  $U \in \mathbb{R}^{m \times p}$ , where  $p \in \mathbb{Z}$ ,  $p \le n$  is the number of principle components, such that all axes are orthogonal and are sorted in decreasing amount of variance.

Clustering analysis enables a down-selection of trials used in model computation. This analysis yields a subset of rows such that U' = SU where  $U' \in R^{m' \times p}, m' \leq m$  and S is a selection matrix. This work applies *k*-means clustering which partitions a set of points into *k* clusters such that each point in a cluster  $k_i$  is closest to the mean of  $k_i$  than any other mean. The distance metric used in this work is *squared Euclidean distance*, which gives increasingly greater weight to the distance between two elements.

Model selection yields a function  $f : \mathbb{R}^{1 \times p} \to \mathbb{R}$  that maps individual trials onto a predicted result value. f is the performance model, and this work yields one model per cluster. Model selection leverages linear regression, a commonly-used and well-behaved form of regression that evaluates the dependent variable y as the weighted linear combination of independent variables x plus an error term  $\epsilon$ , representing any deviation of the expected value of the model from the real value.

$$y = \beta_0 + \sum_{i=1}^n \beta_i x_i + \epsilon \tag{1}$$

The method of model estimation is least squares, in which the set of coefficients  $\beta$  is chosen to minimize the residual sum of squares

$$RSS(\beta) = \sum_{i=1}^{n} (y_i - \beta_0 - \sum_{j=1}^{p} x_{ij}\beta_j)^2$$

(2)

Model selection itself composes a performance model as the linear combination of a set of non-linear functions on the projected profiling data. The set of possible functions is known as a *model pool*, which can include basis expansions, mathematical transformations, and varaible interactions, among others. To allow for greater generalizability, this work can iterate over a set of model pools and select the one that minimizes squared error.

In order to manage model complexity and optimize training error rate, a forwardstepwise procedure is used to aggregate basis functions based upon adjusted coefficient of determination, a modification of the coefficient of determination that adjusts for the number of terms in the model [55].

$$AdjustedR^{2} = \bar{R}^{2} = 1 - (1 - R^{2})\frac{n - 1}{n - p - 1}$$

(3)

It is important to note that  $\bar{R}^2$  does not have the same interpretation as  $R^2$ ; while  $R^2$  is in the range  $0 \rightarrow 1$ ,  $\bar{R}^2$  is in the range  $-\infty \rightarrow 1$ . The intuition is that any value of  $\bar{R}^2$  less than zero implies a fit worse than could be expected by chance.

# 3.2 Modeling Performance of Applications at Scale

While existing techniques for performance prediction such as cycle-level simulation provide an accurate mechanism for estimating execution behavior, they are typically too slow and too fine-grained to observe the system-level phenomenon of extreme scale applications. By composing fast approximations of behavior for regions of computation, full systems can be simulated quickly, estimating both time and energy. The following sections describe the process of creating application skeletons and the tools developed to facilitate this process. Simulating the execution of applications on a large number of cores requires the abstraction of application software with minimal compromises in simulation accuracy. A recent development is *macro-scale simulation* models, which contrasts with cycle-level or micro-scale simulation models. The macro-scale simulation models are driven by *application skeletons*: a full application, modified to retain its control flow and structure, but with code segments replaced by analytic models to compute the resources consumed by the corresponding code segment. In general the *effect* of execution characteristics are modeled rather than the *mechanism*, i.e., the procedure a code goes through during execution. The use of application skeletons enables modeling to be applied at a larger scale that otherwise feasible. In principal, this technique can be used to model any resource consumed by the system; this thesis applies this technique to execution time and energy, but the methodology is general enough to model resources such as memory or network bandwidth.

Figure 5: The structure of the SST/macro simulator.