# AUTOMATED GENERATION OF ROUND-ROBIN ARBITRATION AND CROSSBAR SWITCH LOGIC

A Thesis Presented to The Academic Faculty

by

## Eung S. Shin

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

School of Electrical and Computer Engineering Georgia Institute of Technology November 2003

# AUTOMATED GENERATION OF ROUND-ROBIN ARBITRATION AND CROSSBAR SWITCH LOGIC

Approved by:

Professor Vincent J. Mooney III, Adviser

Professor George F. Riley

Professor Sung Kyu Lim

Professor Mary Ann Ingram

Professor Santosh Pande

Date Approved: 11/05/2003

# "In his heart a man plans his course, but the LORD determines his steps...."

- Proverbs 16:9

To my parents

#### ACKNOWLEDGMENTS

During my Ph. D. study, there are many people in Georgia Tech to whom I am thankful. First of all, I would like to express enormous appreciation to my adviser, Dr. Vincent J. Mooney III, from the bottom of the heart. In addition to his enthusiasm and professionalism dedicated to all members of our Codesign group, Dr. Mooney has been supporting and encouraging me to develop my thesis. With our weekly regular meeting, he has been listening to my idea patiently, and we have been brainstorming by short question and answer session. He has been also helping me improve my writing with logical reasoning and has been correcting my English pronunciation. His technical acumen, integrity and concern for all members of Codesign are remarkable and exemplary.

Second of all, I am also grateful to all my committee members, Dr. George F. Riley, Dr. Sung Kyu Lim, Dr. Mary Ann Ingram and Dr. Santosh Pande. Especially, Dr. Riley is the coauthor of two of my papers and has been supportive to enhance our paper quality by developing a switch arbiter simulator.

Also, I have to express thank to all members of the Codesign group. Mohamed Shalan, the coauthor of one of my papers, has been helpful me with productive discussion of our research interest and the provision of constructive advice for simulations. Pramote Kuacharoen, Tankut Akgul and his wife Bilge Saglam Akgul have been encouraging me with helpful advice and hilarious joke and have been broadened my research interest. Jun Cheol Park and Kyeong-Keol Ryu have been supportive for every aspect besides the power estimation and debugging my design.

Finally, I wish to thank my parents who gave me a birth and have been supportive for my entire life. Without their encourage and support, I doubt that I have could bring my thesis into final form. They have believed in my ability to complete my thesis and have made me confident in pursuing my goal. I also thank to my brother, Eung Seok Shin and my sister, You Yong Shin, for their encouragement.

# TABLE OF CONTENTS

| DE                 | DIC  | ATION   | N                                                             | iii  |

|--------------------|------|---------|---------------------------------------------------------------|------|

| ACKNOWLEDGMENTS in |      |         |                                                               | iv   |

| LIST OF TABLES vii |      |         |                                                               | viii |

| LIS                | вт о | F FIG   | URES                                                          | ix   |

| LIS                | бт о | F ABE   | BREBIATIONS                                                   | xii  |

| $\mathbf{SU}$      | MM   | ARY .   |                                                               | xiv  |

| I                  | IN   | TROE    | OUCTION                                                       | 1    |

|                    | 1.1  | Proble  | em Statement                                                  | 1    |

|                    | 1.2  | Thesis  | Contributions                                                 | 2    |

|                    | 1.3  | Motiva  | ation                                                         | 3    |

| II                 | TI   | ERMIN   | NOLOGY FOR AN ARBITER                                         | 6    |

| III                | RI   | ELATE   | D WORK                                                        | 15   |

|                    | 3.1  | Arbite  | rs                                                            | 15   |

|                    |      | 3.1.1   | Arbitration for Network Packet Switching: PPA, PPE and others | 15   |

|                    |      | 3.1.2   | Logic Synthesis                                               | 21   |

|                    |      | 3.1.3   | Token Rings                                                   | 22   |

|                    | 3.2  | On-chi  | ip Communication                                              | 22   |

| IV                 | R    | OUND    | -ROBIN ARBITER DESIGN                                         | 26   |

|                    | 4.1  | 2x2, 32 | x3 and 4x4 Bus Arbiter Design                                 | 26   |

|                    | 4.2  | Switch  | Arbiter Design                                                | 31   |

|                    | 4.3  | Hierar  | chical Bus Arbiter Design                                     | 46   |

|                    | 4.4  | Impac   | t on Logic Synthesis: Priority Logic Specification            | 48   |

|                    |      | 4.4.1   | Hierarchical SA versus PPE                                    | 49   |

|                    |      | 4.4.2   | Hierarchical SA versus PPA                                    | 51   |

| 4.5             | Fairne | ess in Arbitration                                         | 53        |

|-----------------|--------|------------------------------------------------------------|-----------|

| V R             | AG: R  | OUND-ROBIN ARBITER GENERATOR                               | 58        |

|                 |        | CROSSBAR SWITCH GENERATOR FOR MULTIPRO                     | - 66      |

| 6.1             | The X  | Kbar                                                       | 67        |

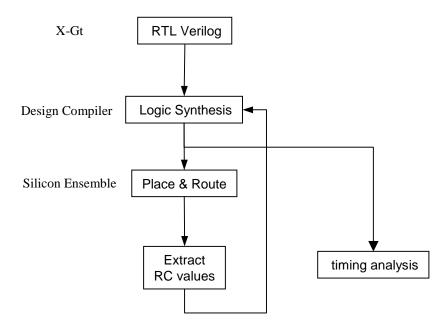

| 6.2             | Metho  | odology                                                    | 69        |

| 6.3             | Integr | ration with DMMU and its generation tool                   | 72        |

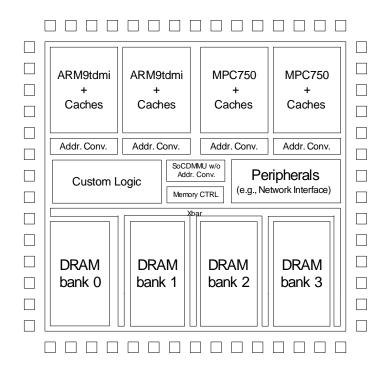

|                 | 6.3.1  | Target Architecture                                        | 73        |

|                 | 6.3.2  | Tool Integration                                           | 75        |

| VII E           | XPER   | IMENTAL RESULTS                                            | <b>79</b> |

| 7.1             | Arbite | er Experiment                                              | 79        |

|                 | 7.1.1  | BA Area and Delay Considerations                           | 80        |

|                 | 7.1.2  | SA Area and Delay Comparisons                              | 80        |

|                 | 7.1.3  | Power Dissipation of the Arbiters                          | 84        |

|                 | 7.1.4  | Speedup for a Chip Implementing a $32x32$ Network Switch . | 92        |

|                 | 7.1.5  | Fairness Simulation for Hierarchical SAs                   | 100       |

| 7.2             | Xbar   | Synthesis                                                  | 104       |

|                 | 7.2.1  | Xbar Area                                                  | 104       |

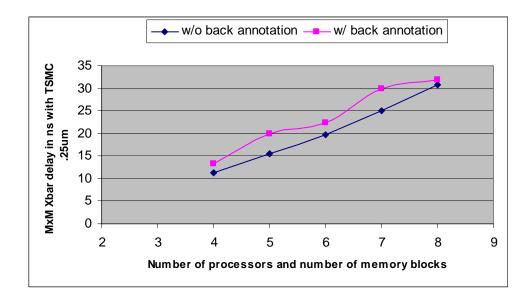

|                 | 7.2.2  | Xbar Delay                                                 | 105       |

|                 | 7.2.3  | MP-SoC with Xbar and DMMU                                  | 109       |

| VIII CONCLUSION |        |                                                            | 111       |

| REFERENCES      |        |                                                            |           |

## LIST OF TABLES

| Table 1 | Truth table of a 4x4 priority logic block                 | 29  |

|---------|-----------------------------------------------------------|-----|

| Table 2 | Simulation results, continuous requests                   | 101 |

| Table 3 | Simulation results, bursty on-off traffic                 | 101 |

| Table 4 | Simulation results, TCP traffic using the GTNets log file | 103 |

# LIST OF FIGURES

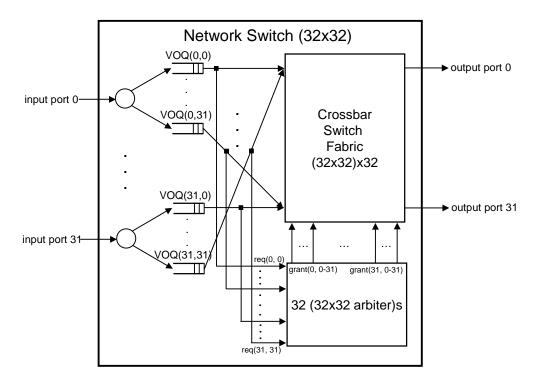

| Figure 1  | Internal structure of $(32x32)x32$ crossbar switch fabric and thirty-<br>two 32x32 SAs of 32x32 network switch   | 6  |

|-----------|------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | HOL blocking example: without VOQs and with VOQs $\ldots \ldots$                                                 | 8  |

| Figure 3  | 32x32 network switch architecture                                                                                | 9  |

| Figure 4  | (3x2)x2 crossbar switch fabric and two 3x3 SAs (Note: reset signals for the SAs not shown)                       | 10 |

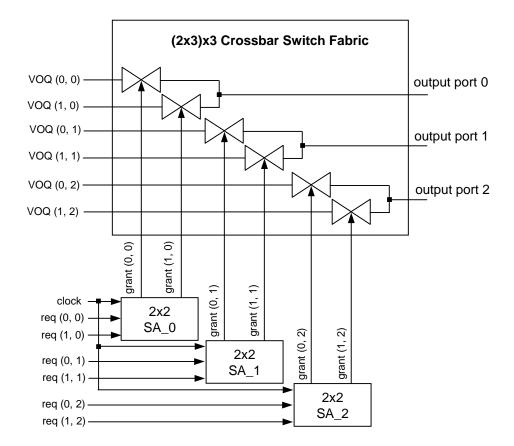

| Figure 5  | (2x3)x3 crossbar switch fabric and three 2x2 SAs (Note: reset signals for the SAs not shown)                     | 12 |

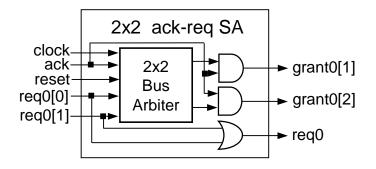

| Figure 6  | 2x2 ack-req SA block                                                                                             | 13 |

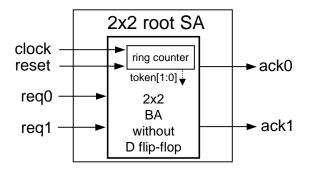

| Figure 7  | 2x2 root SA                                                                                                      | 13 |

| Figure 8  | 32x32 network switch architecture (Note: Figure 8 is exactly same as Figure 3)                                   | 16 |

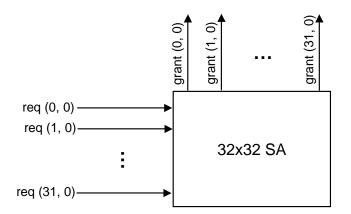

| Figure 9  | 32x32 Switch Arbiter (SA)                                                                                        | 17 |

| Figure 10 | AR2: 2-input PPA and its internal logic                                                                          | 20 |

| Figure 11 | A binary tree structured PPA                                                                                     | 21 |

| Figure 12 | Octagon bus                                                                                                      | 23 |

| Figure 13 | A processing tile with crossbar interconnect                                                                     | 24 |

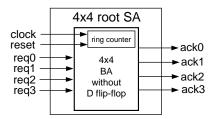

| Figure 14 | Block diagram and logic diagram of a 4x4 Bus Arbiter                                                             | 27 |

| Figure 15 | 4x4 Bus Arbiter (BA) architecture                                                                                | 28 |

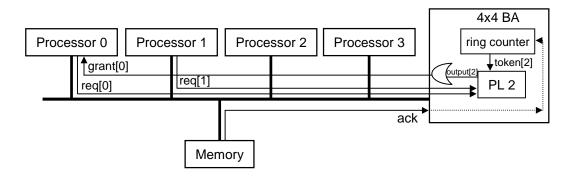

| Figure 16 | Four processors with a shared memory system (Note: bus and 4x4 BA details shown only as needed for Example 4.1.) | 31 |

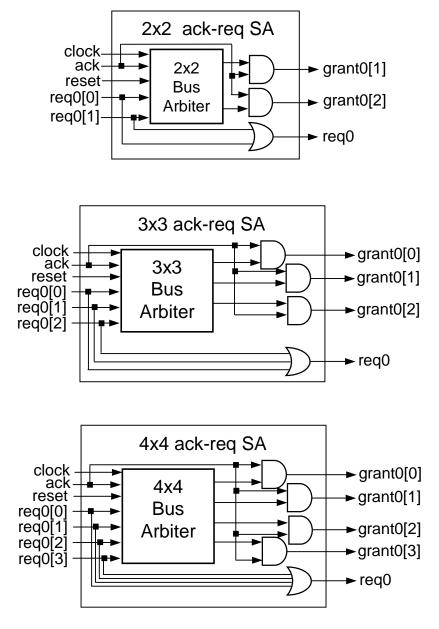

| Figure 17 | Ack-req SA blocks                                                                                                | 32 |

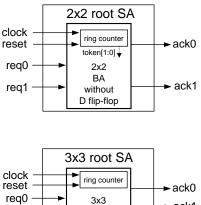

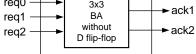

| Figure 18 | Root SA blocks                                                                                                   | 34 |

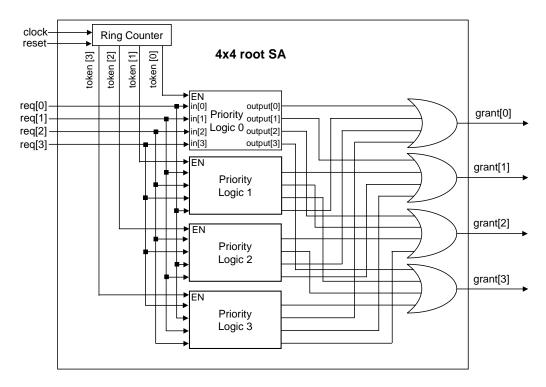

| Figure 19 | Detailed view of a 4x4 root Switch Arbiter                                                                       | 34 |

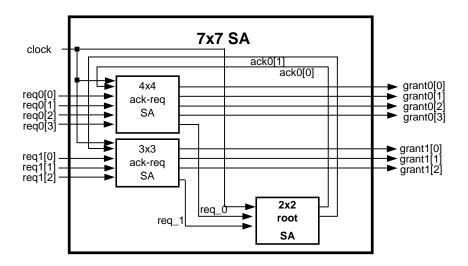

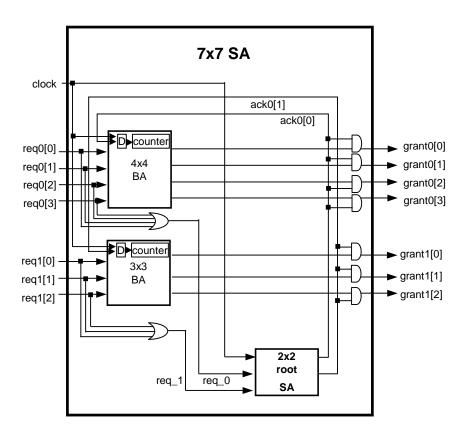

| Figure 20 | A 7x7 SA configuration (Note: reset signal not shown) $\ \ldots \ \ldots \ \ldots$                               | 35 |

| Figure 21 | A 7x7 SA with a different placement of the AND gates (Note: reset signal not shown)                              | 35 |

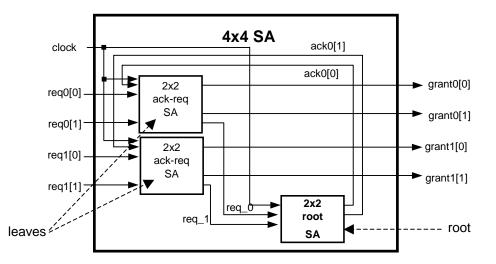

| Figure 22 | A 4x4 SA implemented by three 2x2 switch arbiter blocks (Note: reset signal not shown)                           | 36 |

| Figure 23 | Hierarchical Switch Arbiter for 32 x 32 switch (Note: reset signal not shown)                | 38 |

|-----------|----------------------------------------------------------------------------------------------|----|

| Figure 24 | The critical path of Figure 23                                                               | 39 |

| Figure 25 | Switch Arbiter algorithm                                                                     | 42 |

| Figure 26 | Flowchart of Switch Arbiter algorithm                                                        | 44 |

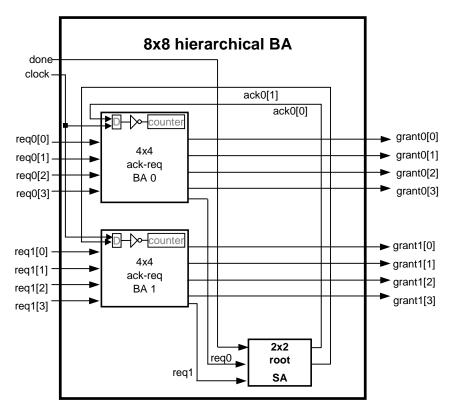

| Figure 27 | 8x8 hierarchical BA                                                                          | 46 |

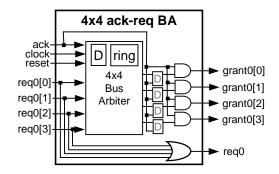

| Figure 28 | 4x4 ack-req BA                                                                               | 47 |

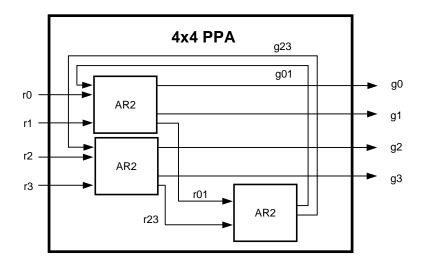

| Figure 29 | 4x4 PPA                                                                                      | 51 |

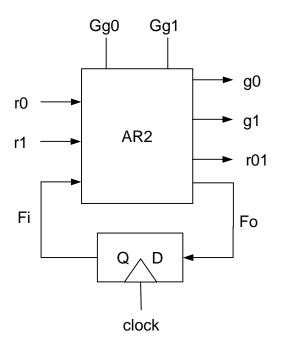

| Figure 30 | AR2 block diagram                                                                            | 52 |

| Figure 31 | 4x4 Bus Arbiter (BA) architecture (Note: Figure 31 is exactly same as Figure 15)             | 53 |

| Figure 32 | The pointer update scheme of PEE                                                             | 55 |

| Figure 33 | Flow of RAG tool                                                                             | 59 |

| Figure 34 | Flowchart of Algorithm 2                                                                     | 62 |

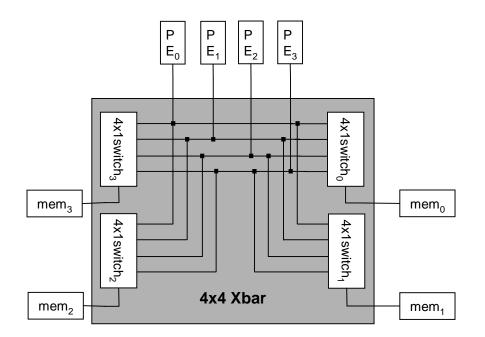

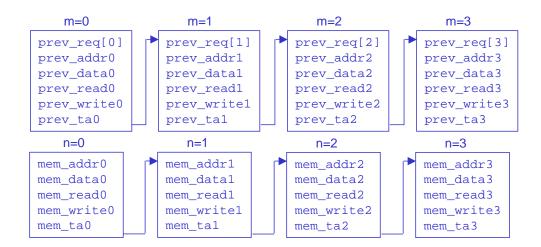

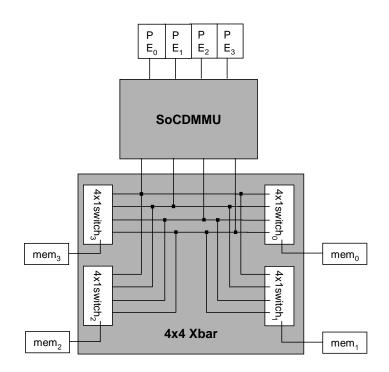

| Figure 35 | The example of 4x4 Xbar with four processors and four memory blocks each with a single port  | 66 |

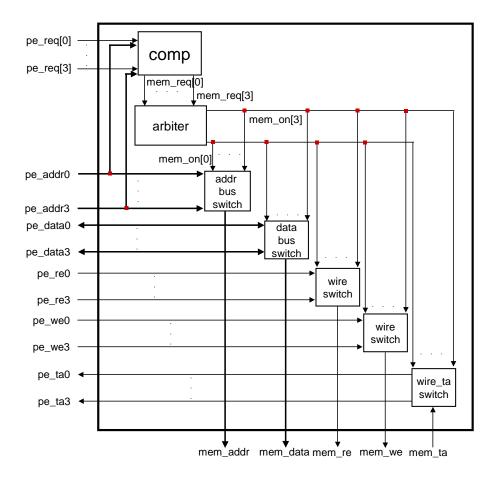

| Figure 36 | Internal structure of a $4x1$ switch $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$   | 68 |

| Figure 37 | Linked-list data structure for Example 6.2                                                   | 70 |

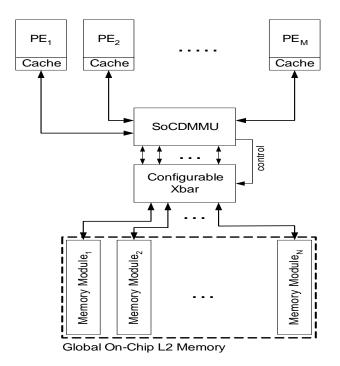

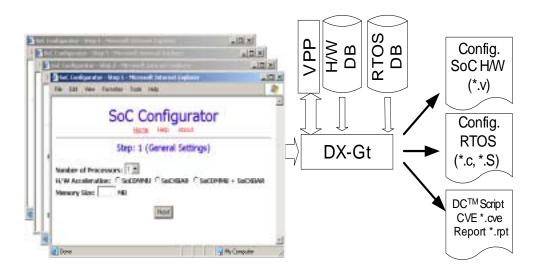

| Figure 38 | The SoC target architecture                                                                  | 74 |

| Figure 39 | The target architecture of four processors and four memory blocks<br>each with a single port | 75 |

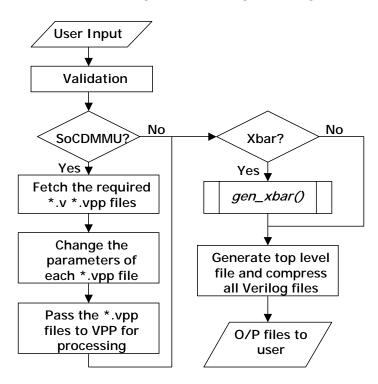

| Figure 40 | The SoC configuration tool flow                                                              | 76 |

| Figure 41 | Flowchart of DX-Gt                                                                           | 77 |

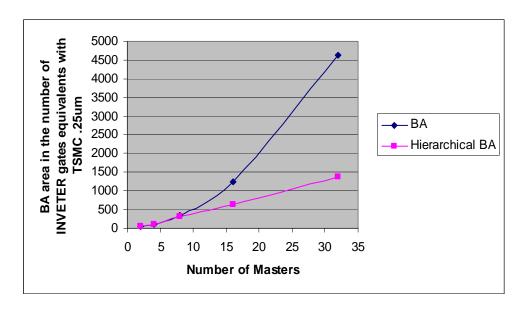

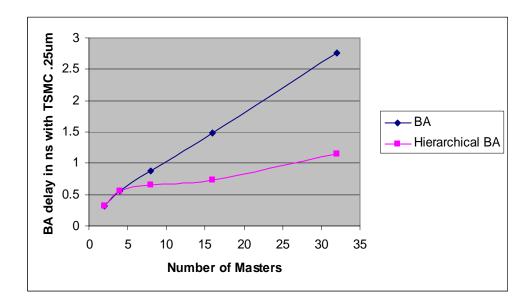

| Figure 42 | MxM Bus Arbiter area                                                                         | 81 |

| Figure 43 | MxM Bus Arbiter delay                                                                        | 81 |

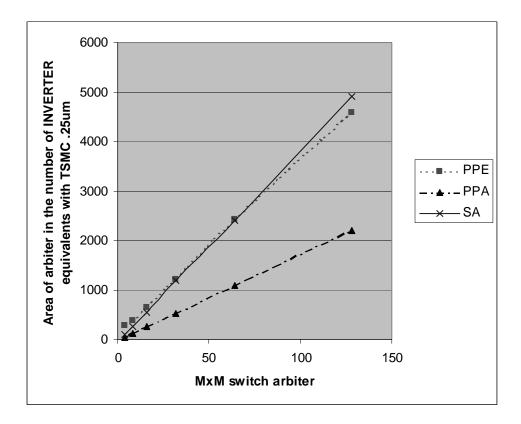

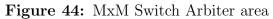

| Figure 44 | MxM Switch Arbiter area                                                                      | 83 |

| Figure 45 | MxM Switch Arbiter longest delay                                                             | 83 |

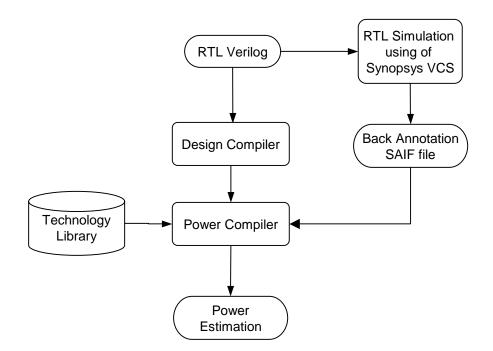

| Figure 46 | Methodology of power estimation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$    | 85 |

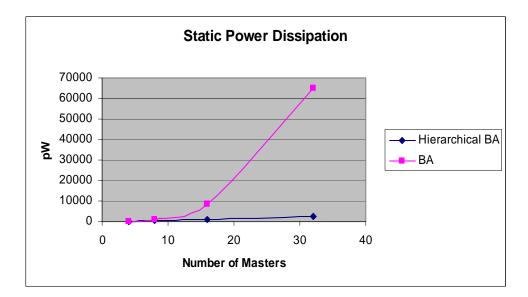

| Figure 47 | MxM hierarchical BA and BA static power dissipation $\ . \ . \ .$ .                          | 86 |

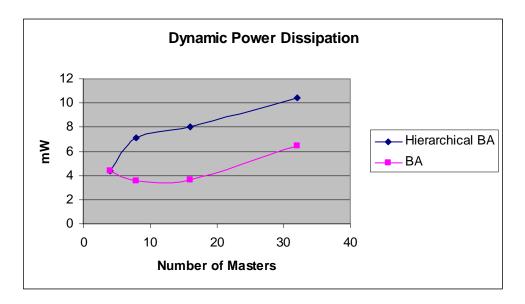

| Figure 48 | MxM hierarchical BA and BA dynamic power dissipation                                         | 87 |

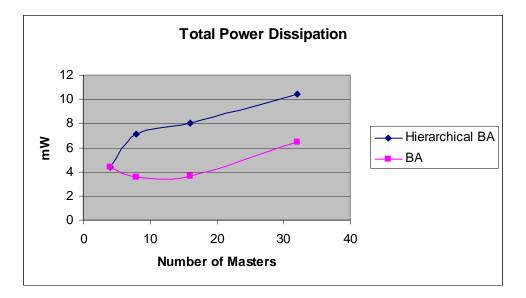

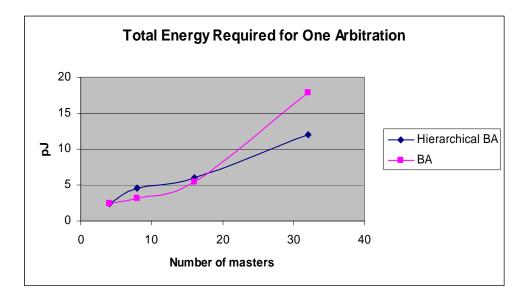

| Figure 49 | Total power dissipation of BA versus hierarchical BA                                    | 87  |

|-----------|-----------------------------------------------------------------------------------------|-----|

| Figure 50 | Total energy required for one arbitration of BA versus hierarchical BA                  | 88  |

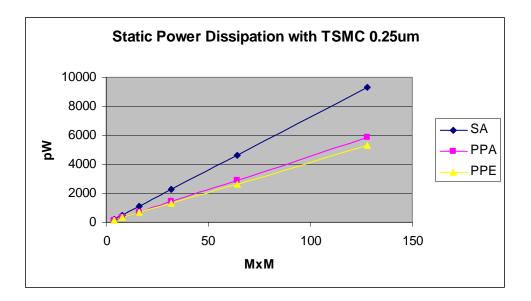

| Figure 51 | MxM hierarchical SA, PPE and PPA static power dissipation $\ .$ .                       | 90  |

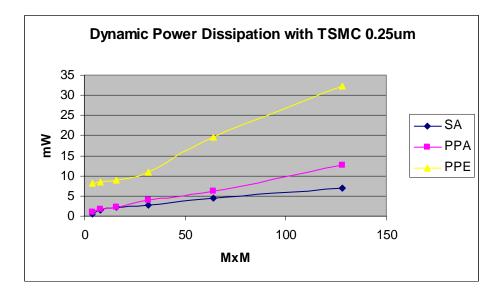

| Figure 52 | MxM hierarchical SA, PPE and PPA dynamic power dissipation                              | 90  |

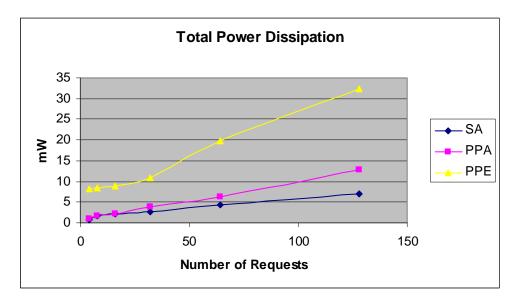

| Figure 53 | Total power dissipation of hierarchical SA, PPE and PPA $\ . \ . \ .$                   | 91  |

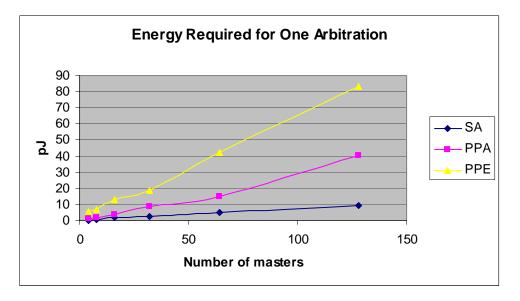

| Figure 54 | Energy required for one arbitration of MxM hierarchical SA, PPE and PPA                 | 91  |

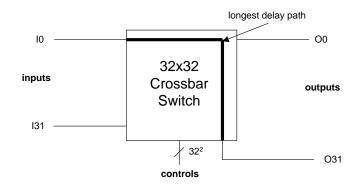

| Figure 55 | 32x32 crossbar switch and its longest delay path                                        | 94  |

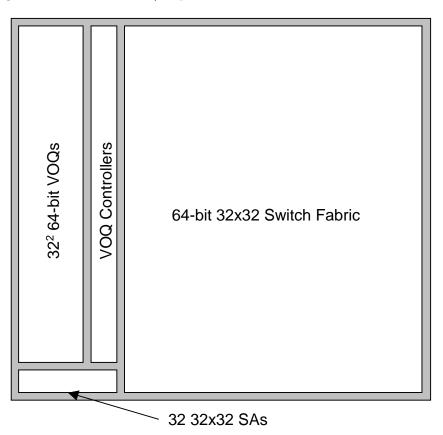

| Figure 56 | The floorplan of the 64-bit 32x32 switch fabric, VOQs, controllers and SAs              | 95  |

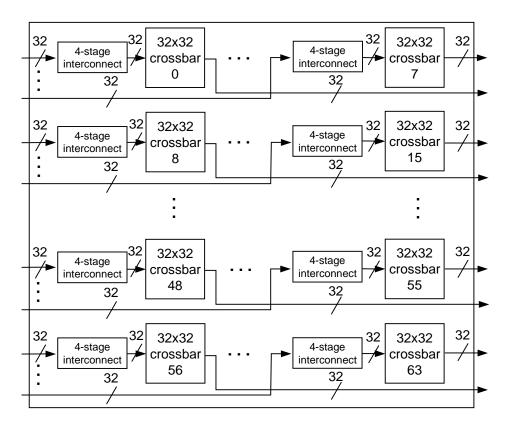

| Figure 57 | The internals of the 64-bit $32x32$ switch fabric                                       | 97  |

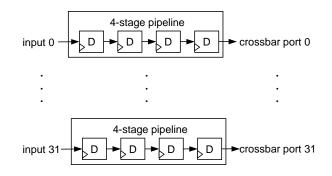

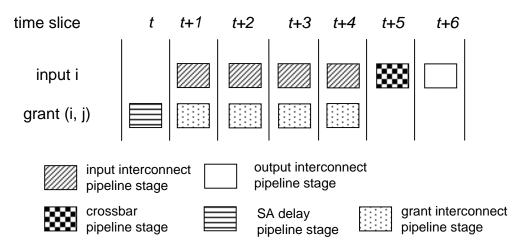

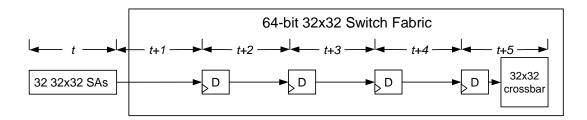

| Figure 58 | The internals of the 4-stage interconnect box                                           | 97  |

| Figure 59 | The grant-connect pipeline including an input interconnect and a control wire pipelines | 98  |

| Figure 60 | The 4-stage pipeline of a control wire                                                  | 99  |

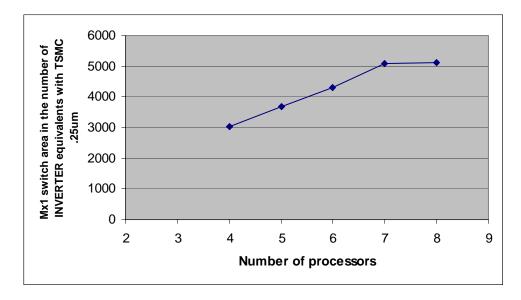

| Figure 61 | Area of Mx1 switch                                                                      | 106 |

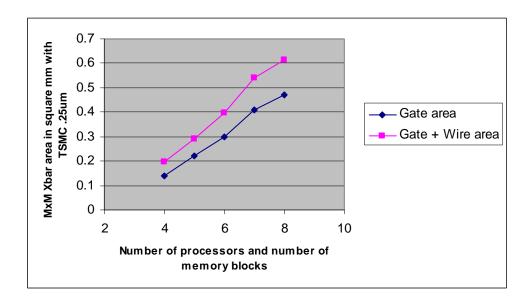

| Figure 62 | Area of MxM Xbar                                                                        | 106 |

| Figure 63 | Back-annotation Flow                                                                    | 107 |

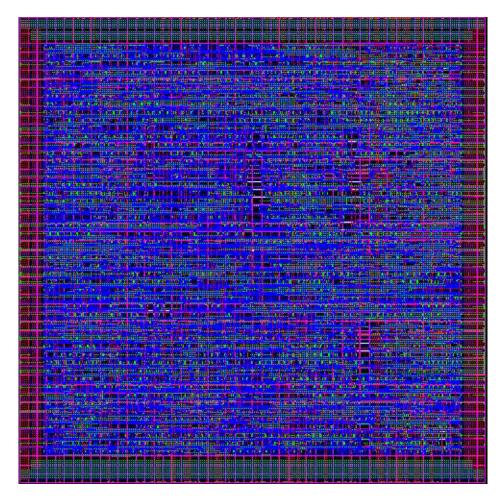

| Figure 64 | The snapshot of 4x4 Xbar layout                                                         | 108 |

| Figure 65 | Delay of MxM Xbar                                                                       | 108 |

| Figure 66 | The floorplan of an SoC that utilizes the SoCDMMU and the Xbar                          | 110 |

# LIST OF ABBREBIATIONS

| ASIC          | Application Specific Integrated Circuit                                                                                                                                                                                                                                   |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BA            | Bus Arbiter                                                                                                                                                                                                                                                               |

| CAD           | Computer-Aided Design                                                                                                                                                                                                                                                     |

| CSMA/CD       | Carrier Sense Multiple Access with Collision Detection                                                                                                                                                                                                                    |

| DMMU          | Dynamic Memory Management Unit                                                                                                                                                                                                                                            |

| DX-Gt         | $\mathbf{D} \mathbf{y} \mathbf{n} \mathbf{a} \mathbf{m} \mathbf{m} \mathbf{c} \mathbf{m} \mathbf{n} \mathbf{n} \mathbf{d} \mathbf{x} \mathbf{b} \mathbf{a} \mathbf{r} \mathbf{G} \mathbf{e} \mathbf{n} \mathbf{e} \mathbf{r} \mathbf{a} \mathbf{t} \mathbf{o} \mathbf{r}$ |

| GUI           | Graphical User Interface                                                                                                                                                                                                                                                  |

| HOL           | Head-of-Line                                                                                                                                                                                                                                                              |

| IP            | Internet Protocol                                                                                                                                                                                                                                                         |

| LAN           | Local Area Network                                                                                                                                                                                                                                                        |

| MAC           | Medium Access Control                                                                                                                                                                                                                                                     |

| NoC           | Network-on-a-Chip                                                                                                                                                                                                                                                         |

| PCB           | Printed Circuit Board                                                                                                                                                                                                                                                     |

| $\mathbf{PE}$ | Processing Element                                                                                                                                                                                                                                                        |

| PPA           | Ping-Pong Arbiter                                                                                                                                                                                                                                                         |

| PPE           | Programmable Priority Encoder                                                                                                                                                                                                                                             |

| RAG           | Round-robin Arbiter Generator                                                                                                                                                                                                                                             |

| RTL           | Register Transfer Level                                                                                                                                                                                                                                                   |

- SA Switch Arbiter

- SAIF Switching Activity Interchange Format

- SASim Switch Arbiter Simulator

- **SDF** Standard Delay Format

- SIP Silicon Intellectual Property

- SoC System-on-a-Chip

- TCP Transport Control Protocol

- **VOQ** Virtual Output Queue

- X-Gt Xbar Generator

#### SUMMARY

The objective of this thesis is to automate the design of round-robin arbiter logic. The resulting arbitration logic is more than 1.8X times faster than the fastest prior state-of-the-art arbitration logic the author could find reported in the literature. The generated arbiter implemented in a single chip is fast enough in 0.25  $\mu$ m CMOS technology to achieve terabit switching with a single chip computer network switch. Moreover, this arbiter is applicable to crossbar (Xbar) arbitration logic. The generated Xbar, customized according to user specifications, provides multiple communication paths among masters and slaves.

As the number of transistors on a single chip increases rapidly, there is a productivity gap between the number of transistors available in a chip and the number of transistors per hour a chip designer designs. One solution to reduce this productivity gap is to increase the use of Silicon Intellectual Property (SIP) cores. However, a SIP core should be customized before being used in a system different than the one for which it was designed. Thus, to reconfigure the SIP core, either an engineer must spend significant effort altering the core by hand or else an enhanced CAD tool can automatically customize the core according to customer specifications. In this thesis, we present SIP generator tools for arbiter and Xbar generation.

First, we introduce a Round-robin Arbiter Generator (RAG). The RAG can generate a hierarchical Bus Arbiter (BA) which is faster than all known previous approaches. RAG can also generate a hierarchical Switch Arbiter (SA) which is faster than all known previous approaches. Using a 0.25  $\mu$ m TSMC standard cell library from LEDA Systems, we show the arbitration time of a 32x32 SA and demonstrate that our SA meets the time constraint to achieve terabit throughput. Furthermore, using a novel token-passing hierarchical arbitration scheme, our 32x32 SA performs better than the Ping-Pong Arbiter and Programmable Priority Encoder by factors of 1.8X and 2.3X, respectively, with less power dissipation.

Finally, we present an Xbar switch Generator (X-Gt) tool that automatically configures a crossbar for a multiprocessor System-on-a-Chip (SoC). An Xbar is generated in Register Transfer Level (RTL) Verilog HDL.

## CHAPTER I

## INTRODUCTION

#### 1.1 Problem Statement

In a multiprocessor System-on-a-Chip (SoC) environment, a silicon CMOS chip designer typically uses an arbiter to resolve conflicts on shared resources (i.e., bus or equivalent communication channels) among multiple bus masters (e.g, processors). In a bus-based system, processors could be stalled because of bus conflicts. Thus, a highperformance arbiter is needed to resolve bus contentions among bus masters; such a fast arbiter can also reduce processor stall time by shortening arbitration delays.

In computer networks, such a fast and efficient arbiter commands more attention to resolve contention for crossbar switch(es) of a fast network switch as the amount of user traffic continues to double every year [35]. If the network switch capacity fails to increase with user traffic, then internet service providers may have to increase the number of switches in their network each year. Alternatively, the capacity of a single network switch needs to increase instead, and a fast and efficient arbiter plays a key role in increasing such switch capacity. Considering power consumption, such an arbiter is also preferably implemented in a single chip since the power budget of a network switch is about 10 kW per rack. A recent single rack of network switches, which aims at terabit switching, have already reached this limit [20]. As mentioned in [7, 20, 26, 29, 66], arbitration delay is one of the major obstacles to achieving terabit switching.

In the era of billion transistor chips, reducing the productivity gap between the number of transistors available in a chip and the number of transistors per hour that a designer can design is a challenging issue to a silicon CMOS chip designer. The productivity gap can be reduced by enhancing Silicon Intellectual Property (SIP) core reusability, e.g., by developing CAD tools that can automatically configure and customize a core according to customer specifications.

Primarily, this thesis focuses on round-robin arbiter design and automatic arbiter generation. Secondarily, we extend automatic arbiter generation to CAD tool development for a crossbar (Xbar) switch that employs our generated arbiter for its arbitration logic.

## 1.2 Thesis Contributions

The contributions of this thesis are summarized as follows.

- In the era of multiprocessor SoC, the importance of fast and powerful arbiters commands more attention. We have designed a fast hierarchical round-robin arbiter, which can also be employed for a high-speed network switch. Our fast arbiter addresses arbitration delay, one major obstacle in the drive to achieve terabit switching in a single chip [7, 20, 26, 29, 66].

- As billion transistor chips begin to appear, the customization of Silicon Intellectual Property (SIP) cores by chip designers becomes much more complicated and difficult, resulting in longer time-to-market. Thus, the automatic generation of a hierarchical round-robin arbiter can reduce the time required to properly customize the arbiter. Also, to the best of our knowledge, we present the first published work on the automatic generation of a round-robin arbiter.

- We also developed a crossbar (Xbar) switch generator for on-chip communication. Since the generated Xbar is orthogonal to processor types, the Xbar is valuable in the sense that it can easily be integrated into a heterogeneous multiprocessor SoC. The automated customization of an Xbar according to customer specifications is presented in a tool called Xbar Generator (X-Gt).

#### 1.3 Motivation

In a year or so integrated circuits will appear with more than one billion transistors on a single chip [42]. Such chips give designers the opportunity to integrate many functionalities, each of which used to be implemented on different chips, into the same chip. In other words, a digital system that was previously implemented on a Printed Circuit Board (PCB) will be integrated into a single chip, i.e., System-ona-Chip (SoC). One opportunity for such chips is building an SoC that has multiple processors of different types, large memory, custom digital logic and interfaces connected by one or more on-chip buses.

Most Processing Elements (PEs) in an SoC communicate with each other via buses and memory. As the number of bus masters increases in a single chip, the importance of fast and powerful arbiters commands more attention to achieve a highspeed on-chip bus. Especially, a fast arbiter is one of the more dominant factors for high-performance network switches [7, 20, 26, 29, 66]. Also, fast and efficient switch arbiters are needed to switch packets in a Network-on-Chip (NoC) [11, 18]. However, to design with high performance and fairness in arbitration is a very tedious and error-prone task for designers.

Fast arbitration schemes are intensively studied in computer networks. A major concern in computer networks today is the design of ultra high-speed switches, which provide a high speed and cost-effective contention resolution scheme when multiple packets from different input ports compete for the same output port. This issue is extremely important in order to provide multimedia services for future Broadband Integrated Services Digital Networks (B-ISDN) [48, 59]. We will show how our Roundrobin Arbiter Generator (RAG) can help in the design of a terabit switch.

Most of the current prevailing buses such as VME [63] and PCI [38] were designed for system level buses. While VME connects PCBs in large systems, PCI connects discrete devices on a PCB. A System-on-a-Chip (SoC) allows designers to overcome the drawbacks of PCBs by implementing many or most chips of a PCB onto a single silicon chip. SoC technology allows one to take advantage of increased bus speed and decreased area compared with a PCB.

In the implementation of a multiprocessor SoC, an on-chip network comes to the forefront because the performance of the system is not dependent only on the CPU speed but also on the on-chip network, which may cause system degradation resulting from communication bottlenecks in the system. An efficient bus architecture and arbitration for reducing contention plays an important role in maximizing the performance of the system. We predict that in next five years multiprocessor SoCs will be dominated by designs with four to eight processors and on-chip SRAM or DRAM of 16Mbytes to 128Mbytes. In such multiprocessor SoCs, multiple communication channels may be desired so that communication among processors does not become a system bottleneck. We utilize a crossbar (Xbar) switch for an efficient on-chip network solution.

As the number of transistors on a single chip increases rapidly, there is a productivity gap between the number of transistors available in a chip and the number of transistors per hour a designer can design. In other words, it is almost impossible for human designers to cope with number of available transistors in a chip which doubles every 18 months by Moore's Law [65], while the number of transistors per hour that a designer designs increases 21% per year [42]. One solution to reduce this productivity gap is to increase the reusability of Silicon Intellectual Property (SIP) cores. However, an SIP core should be customized/configured before being used in a system different than the one for which it was designed. Thus, to reconfigure the SIP core, either an engineer must spend significant effort altering the core by hand or an enhanced CAD tool (SIP generator) can automatically configure and customize the core according to customer specifications. For example, memory and I/O generators by Artisan [2] and processor generators by ARC [1] and Tensilica [57] supply application-specific SIP cores that can be highly tuned for specific applications.

To the best of this author's knowledge, this thesis presents the first published work on automatic generation of an Xbar switch coupled with a round-robin arbiter. More specifically, reconfiguring an Xbar is more than reconfiguring bus parameters such as address bus width and data bus width. An MxN Xbar must be configured to support an exact number of masters (processors), M, and an exact number of slaves (memory), N. Thus, to configure an MxN Xbar, one must generate (i) an arbiter able to handle the exact number of requests in an Xbar and (ii) wires (address bus, data bus and some control lines) between masters and slaves.

#### CHAPTER II

## TERMINOLOGY FOR AN ARBITER

In this chapter, we define terms that we use in this thesis. A reader who is already very familiar with computer network switch terminology may skip this chapter.

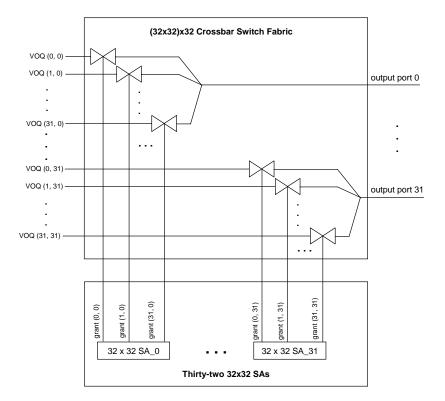

**Figure 1:** Internal structure of (32x32)x32 crossbar switch fabric and thirty-two 32x32 SAs of 32x32 network switch

We define terms to describe Figure 1. Figure 1 shows the inputs and outputs of the crossbar switch fabric in a 32x32 network switch. We briefly describe the network switch structure in order to later show how our generated arbiter is applied to a network switch. Note that we use the terms "switch" and "network switch" interchangeably throughout this thesis. Also, note that this thesis focuses only on an arbiter (equivalently, a scheduler) for a network switch or for a bus.

- 1. An **MxN switch** is an M-input by N-output switch. For example, a 32-input by 32-output device is a "**32x32**" device. Thus, there are 1024 (32<sup>2</sup>) different possible connections where a "connection" is between a particular input port and a particular output port. A switch is able to pass data (packets) from any of the M inputs to any of the N outputs. A network switch is a switch that implements packet passing via a specific network protocol, e.g., the Internet Protocol (IP). All the switches we consider in this thesis are network switches.

- 2. Virtual Output Queues (VOQs) are typically employed in a packet switch to mitigate the head-of-line (HOL) blocking problem. HOL blocking occurs when a single FIFO input queue is used for each input port, and the packet at the head of the queue is blocked from being forwarded to its corresponding output port because of port contention, thereby blocking the entire FIFO. By using separate input queues for each input/output port pair, the HOL blocking problem can be solved [56].

- 3. VOQ (m, n): m is the input port index, and n is the output port index. VOQ (1, 0), for example, is VOQ of input port 1 and queues packets destined to output port 0 as shown in Figure 1.

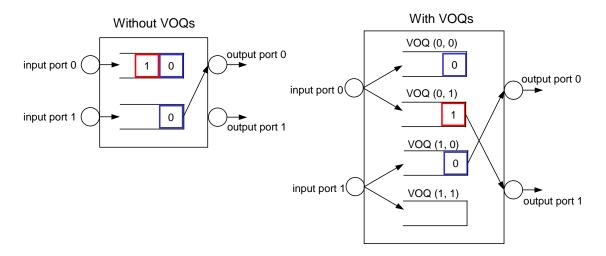

**Example 2.1** Figure 2 describes HOL blocking problem (*Without VOQs*) and the solution of this problem (*With VOQs*). For this example, assume that *input port 1* is granted when output port contentions occur. A numbered rectangle in Figure 2 corresponds to a packet with the destination specified by the number. Thus, the packet numbered '1' indicates that this packet is destined to *output port 1*. For the *Without VOQs* case, *packet 1* in the queue at *input port 0* is blocked by *packet 0*

Figure 2: HOL blocking example: without VOQs and with VOQs

located at the head of the queue, even though *output port 1* is available at this point. Therefore, only *packet*  $\theta$  is sent to *output port 1* in the current cycle. To remove HOL blocking, multiple VOQs are placed at input ports. In the *With VOQs* case, *packet 1* at *VOQ (0, 1)* is forwarded to *output port 1* simultaneously as *packet 0* at *VOQ (1, 0)* is delivered to *output port 0*. Consequently, multiple packets can be delivered to the appropriate unique destinations by employing VOQs.  $\Box$

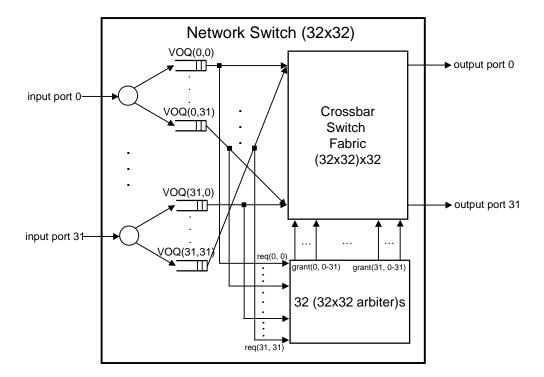

4. (MxV)xN: M is the number of input ports of an MxN switch. V is the number of VOQs per input port, and N is the number of output ports of an MxN switch. Note that the number of VOQs per input port (V) is typically equal to the total number of output ports (N) that can be requested from one input port - i.e., typically V equals N. The multiplicative product of M multiplied by V is the total number of VOQs in an MxN switch. As the name of Virtual Output Queue (VOQ) implies, an input port considers its V VOQs as output ports. Also, the VOQs dedicated to a certain input port have the same input port index as shown in Figure 3. For example, input port 0 as shown in Figure 3 has thirty-two VOQs with the same input port index: from VOQ (0, 0) to VOQ (0, 0)

31). Theoretically, to completely remove the HOL block problem, each input port requires N dedicated VOQs.

Figure 3: 32x32 network switch architecture

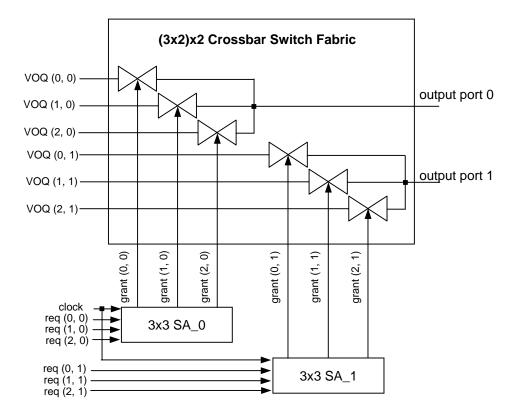

**Example 2.2** Suppose we design a 3x2 network switch. Each input port is allocated two VOQs since there are two output ports. The VOQs for *input port* 0 are VOQ(0, 0) and VOQ(0, 1); the VOQs for *input port* 1 are VOQ(1, 0) and VOQ(1, 1); and the VOQs for *input port* 2 are VOQ(2, 0) and VOQ(2, 1). Thus, the total number of VOQs for this 3x2 switch is equal to 6 (= 3 \* 2). If we group VOQs based on the output port index as shown in Figure 1, VOQ(0, 0), VOQ(1, 0) and VOQ(2, 0) are grouped together for output port 0 as shown in Figure 4.  $\Box$

5. (MxV)xN crossbar switch fabric: There are connections between M \* V inputs (from VOQ (0, 0) to VOQ (M-1, V-1)) and N outputs, the number of output ports in the switch fabric. Again, VOQ (l, m) implies a VOQ at the

**Figure 4:** (3x2)x2 crossbar switch fabric and two 3x3 SAs (Note: reset signals for the SAs not shown)

$l^{th}$  input port destined to  $m^{th}$  output port. As an example, Figure 1 shows a (32x32)x32 crossbar switch fabric<sup>1</sup>.

6. An MxM Switch Arbiter (SA) is a part of an (MxV)xN switch with V=N. An MxM SA controls M specific transmission gates between M VOQs and a particular output port in an (MxN)xN switch. Thus, the number of requests is typically equal to the number of input ports, M. At most one transmission gate is turned on out of M transmission gates at a time. Hence, the number of grant signals controlling the M transmission gates to a particular output port is always equal to M. In Figure 1, for example, signal grant (0, 31) from

<sup>&</sup>lt;sup>1</sup>The crossbar switch fabric shown in Figure 1 might be different from the switch fabric of a real network switch. We assume that control signals are required to turn on a connection between a specific VOQ and a particular output port.

$SA\_31$  turns on or off the transmission gate between VOQ~(0, 31) and output port 31. Signals grant (1, 31) through grant (31, 31) control the other thirtyone transmission gates. The inputs of an MxM SA are req[M-1:0], clock and reset signals, and the outputs of an MxM SA are grant[M-1:0] signals. The clock input is employed to rotate, in round-robin fashion, which request out of the M request signals (req[M-1:0]) receives the highest priority in a given clock cycle. The total number of MxM SAs needed for an (MxN)xN switch is equal to the number of output ports, N.

**Example 2.3** (Continued from Example 2.2) There are six (= 3 \* 2) inputs (equivalently, the total number of VOQs in the switch) to the crossbar switch fabric in our 3x2 network switch. To resolve conflicts among VOQ (0, 0), VOQ (1, 0) and VOQ (2, 0) in the case that all three request output port 0 (by req (0, 0), req (1, 0) and req (2, 0), respectively) in the same cycle, a 3x3 SA controls the connections as shown in Figure 4. Note that 3 (= M) is equal to the number of input ports of a 3x2 switch. The grant signals from the SA are concatenated as follows: grant (2, 0), grant (1, 0), grant (0, 0). In Figure 4, if a grant signal from the 3x3 SA\_0 is 3'b010, only the transmission gate between VOQ (1, 0) and vOQ (2, 1), another 3x3 SA (3x3 SA\_1) is required for output port 1 as shown in Figure 4. Thus, a total number of two 3x3 SAs are needed for this 3x2 switch.  $\Box$

**Example 2.4** For a 2x3 network switch, one 2x2 SA is needed per output port. In Figure 5,  $2x2 SA_0$  is used to resolve contentions between VOQ(0, 0) and VOQ(1, 0) in the case that both request *output port* 0 in the same cycle. Again, 2 (= M) is equal to the number of input ports of a 2x3 switch.  $\Box$

7. An MxM distributed SA, equivalently an MxM hierarchical SA, fulfills the same role as and has exactly the same inputs and outputs as an MxM SA.

**Figure 5:** (2x3)x3 crossbar switch fabric and three 2x2 SAs (Note: reset signals for the SAs not shown)

However, an MxM hierarchical SA is composed of smaller SAs in the form of a hierarchical tree structure. We call smaller SAs switch arbiter blocks.

- 8. An ack-req SA block has an extra request ("req") output and an extra acknowledgment ("ack") input, as shown in Figure 6. We only use 2x2, 3x3 and 4x4 ack-req SA blocks in this thesis.

- 9. A root SA can be a 2x2, 3x3 or 4x4 SA. We call the 2x2 (3x3 or 4x4) SA a 2x2 (3x3 or 4x4) root SA for two reasons: (i) a root SA is built directly from logic gates (no hierarchy) as shown in Figure 7 for the 2x2 case, and (ii) a root SA is used as the "root" SA in the tree structure of an MxM hierarchical SA; this use will become more clear later in Section 4.2.

Figure 6: 2x2 ack-req SA block

Figure 7: 2x2 root SA

- 10. We use a **switch arbiter block** as a superset of an ack-req SA, ack-req BA and a root SA.

- 11. A **Bus Arbiter (BA)** resolves bus conflicts when multiple bus masters request a bus in the same cycle. A BA allows access to a bus for the bus master whose request is granted. The input/output logic function of a BA and an ack-req SA block are the same except that an ack-req SA block has an extra "request" output. The use of this extra "request" output will become clear later in Section 4.2. The main difference between a BA and an ack-req SA block is in typical use: a BA typically arbitrates buses, while an ack-req SA block is a component of an MxM hierarchical SA that typically resolves conflicts between input ports and output ports in a switch.

- 12. A hierarchical BA is nearly the same as a hierarchical SA. The only difference is that a hierarchical BA has an extra *ack* input, taking the *ack* input from the owner of the bus (the bus master). In short, while a hierarchical SA rotates priorities every clock cycle, a hierarchical BA rotates priorities (which include rotating the highest priority among the potential bus requestors) only after a rising edge seen on the *ack* input. Thus, the bus requestor given control over the bus may use the bus for multiple bus clock cycles.

- 13. An **ack-req BA**, a component of a hierarchical BA, has the same functionality as an ack-req SA. However, the logic of an ack-req BA has extra gates to guarantee the possession of multiple bus clock cycles to the granted bus master.

In addition to an (MxV)xN crossbar switch fabric, the internal structure of an MxN network switch consists of VOQs and arbiters (there may be additional hardware components such as memory at the input port in case of the occurrence of VOQ overflows). In Figure 1, we intentionally delete request connections to the 32x32 Switch Arbiters (SAs) from VOQs to present a more compact and easy-to-read diagram. In Figure 9in Chapter 3, however, we show request connections to the SAs in more detail.

#### CHAPTER III

#### **RELATED WORK**

In this chapter, we present some of previous work in arbiter design and crossbar switch customization. For the arbiter design, we emphasize the Ping-Pong Arbiter (PPA) [7] and the Programmable Priority Encoder (PPE) [13] which implements the iSLIP algorithm [29]. The iSLIP algorithm is arguably the best current state-of-the-art arbitration algorithm in computer network theory and, from the author's informal search of the literature, seems to be the most referenced arbitration algorithm in recent network switch papers, including [7, 8, 66]. In Section 3.2, we focus on Smart Memory which is the closest related work in terms of the customized Xbar.

#### 3.1 Arbiters

#### 3.1.1 Arbitration for Network Packet Switching: PPA, PPE and others

Current designs in Network-on-Chip (NoC) typically use standard round-robin token passing schemes for bus arbitration [11]. In computer network packet switching, previous research in round-robin algorithms have reported results on an iterative round-robin algorithm (iSLIP) [29] and a dual round-robin matching (DRRM) algorithm [8]. Furthermore, Chao *et al.* describe a design of a round-robin arbiter for a packet switch [7]. Chao *et al.* refer to their hardware design as a Ping Pong Arbiter (PPA).

In general, the goal of a switch arbiter in a packet switch is to provide control signals to the crossbar switch fabric as shown in Figure 3. In a packet switch design, one must keep in mind that each input port can potentially request connections to all output ports (e.g., in the case of broadcast). Theoretically, to avoid the HOL blocking problem in a packet switch with M input ports and N output ports, each input is allocated N VOQs (one per output) for a total of the multiplicative product of M times N VOQs in the packet switch [27, 56]. By employing VOQs, it is reported that the throughput of an input-queued switch increases from 58.6% to 100% [27, 30]. In general, an MxN switch can have fewer VOQs than N per input port to save cost and area at some slight cost of occasional HOL blocking. However, we assume V = NVOQs per input port in an MxN switch in this thesis.

**Figure 8:** 32x32 network switch architecture (Note: Figure 8 is exactly same as Figure 3)

Figure 3 is repeated here as Figure 8: Figure 8 shows a 32x32 network switch with 32 input ports and 32 output ports. Each input port can request between zero (none) and thirty-two (all) connections to output ports. To accomplish this, thirty-two 32x32 Switch Arbiters (SAs), as shown in the bottom right hand side of Figure 3, take as input  $32^2$  requests (req (0, 0), req (0, 1), ..., req (31, 30), req (31, 31) – 32 requests per input port, or one request per VOQ) and translates those requests into

$32^2$  (=4096) grant signals (one grant signal per possible VOQ to output connection) where at most one grant signal per output port is set to '1' on each clock cycle (thus, of the  $32^2$  grant signals, at most 32 are set to '1' each clock cycle).

Figure 9 shows one 32x32 SA out of the thirty-two 32x32 SAs in Figure 3. Each SA grants one request out of at most thirty-two requests from thirty-two VOQs. Each input of the 32x32 SA in Figure 9 is connected to a specific VOQ (one per input port) which may request *output port 0*. The thirty-two outputs of the 32x32 SA are grant signals indicating which of the 32 VOQs is granted *output port 0* (note that if no VOQ requests the output port, then all grant signals will be '0' in this case). For example, grant (31, 0) can signal the crossbar switch fabric in Figure 3 to connect VOQ (31, 0) to output port 0.

Figure 9: 32x32 Switch Arbiter (SA)

#### 3.1.1.1 Network Packet Switching Arbitration: PPE

The iSLIP algorithm [29] uses in its implementation MxM SAs. The iSLIP algorithm focuses on the efficient and fast scheduling of *best-effort* traffic and is developed to satisfy the following properties:

• High throughput for a network switch: an algorithm should keep the backlog low in the VOQs.

- Starvation-free VOQs: a nonempty VOQ should not remain unserved indefinitely.

- Fast arbitration scheme: to achieve a high speed network switch, an arbitration algorithm should not be a performance bottleneck.

- Simplicity of implementation: an arbiter plus some network switch components (e.g., VOQs and crossbar switch fabric) are preferably implemented in a single chip.

The iSLIP authors implement an MxM SA in hardware that they call a Programmable Priority Encoder (PPE) [13]. PPE was used in the Tiny Tera prototype [28]. Tiny Tera employs an input queued 32-port crossbar switch and a centralized scheduler, PPE. PPE is composed of an M-input simple Priority Encoder [64] and a thermometer encoding logic [13] which rotate priority levels of inputs. The thermometer encoding logic eliminates the long critical path resulting from the programmable priority level. A log<sub>2</sub>M-bit-wide vector  $\mathbf{x}$  is translated into an M-bit-wide vector  $\mathbf{y}$  by a thermometer encoding according to the following equation.

$$y[i] = 1$$

iff  $i < value(x)$  for all  $0 < i < M$ , otherwise  $y[i] = 0$

Since the area and delay of an M-input priority encoder rapidly increases as M increases, the authors of PPE propose a recursive decomposition of PPE for large M. An M-input PPE can be decomposed into two M/2-input subblocks. One subblock takes care of inputs 0 through (M/2)-1, while the other serves inputs M/2 through and M-1. This idea can be extended to further decompose an (M/2)-input subblock into two (M/4)-input subblocks. Each decomposition adds one stage of multiplexers to combine final output. However, the authors do not show their detailed design nor area and delay comparison in [13]. Please note that after [13], subsequent papers from the authors of [13] do not have a logic diagram of PPE. Instead, subsequent publications

of the authors of [13] focus on routing and packet classification algorithms [12, 14, 16, 17, 21, 36].

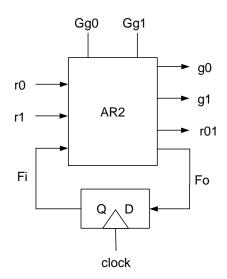

#### 3.1.1.2 Network Packet Switching Arbitration: PPA

Chao *et al.* observe that a traditional arbiter (centralized arbiter) handles all request inputs together with arbitration delay increasing proportionally to the number of requests [7]. Consequently, a fixed amount of allowable arbitration delay limits the network switch capacity for large M. Therefore, in PPA, inputs are divided into groups and each group has its own arbiter. An arbiter in a group is named as AR2. Figure 10 shows the block diagram of AR2 and its internal logic. AR2 handles two request inputs ( $r\theta$  and r1) with two external grant inputs ( $Gg\theta$  and Gg1). The outputs of AR2 are two grant signals ( $g\theta$  and g1), a request output ( $r\theta1$ ) and a flag signal ( $F\theta$ ) which is fed back to AR2 (Fi) via the D flip flop.

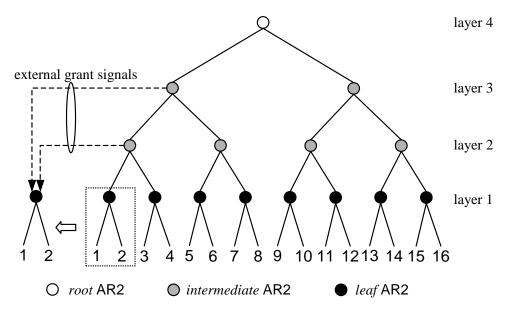

The request signals of each AR2 are summed as a group request signal by use of an OR gate (r01 in Figure 10). PPA is binary tree structured as shown in Figure 11 and is composed of AR2 in each layer of hierarchy.

Under the assumption of  $M = 2^k$ , Figure 11 describes a k-layer complete binary tree with each group handling two requests. In an AR2, an internal feedback signal indicates which input has a higher priority in the current cycle. If an input is granted in the current cycle, the other input has a higher priority in the next cycle. The priority is indicated by 1-bit flag; if flag is '0', input 0 of AR2 (left input of AR2) in Figure 11 has a higher priority. There are  $2^{k-1}$  leaf AR2s. The arbiter at the highest layer is called the root AR2. Other arbiters placed other than the first and the last layers are called *intermediate* AR2s.

The grant signal from an AR2 in a location other than the lowest layer is fed back to the corresponding AR2 located at the lower layer. Thus, each intermediate and leaf AR2 has external grant inputs from an upper layer (Gg0 and Gg1 in Figure 10)

Figure 10: AR2: 2-input PPA and its internal logic

Figure 11: A binary tree structured PPA

which is ANDed with an AR2's internal grant signal to reflect the arbitration result of an upper layer. The other important usage of an external grant is for a flag update. If an AR2 receives a valid external grant, the AR2's group request is granted from upper layers. Thus, the flag of the AR2 must be updated (toggled). However, the flag should be unchanged if the external grant is invalid to maintain the current priority.

The PPA structure shown in Figure 11 is for the case of k = 4. If all inputs request a grant, request inputs are granted in the order of  $1 \rightarrow 3 \rightarrow 5 \rightarrow 7 \rightarrow 9 \rightarrow 11 \rightarrow 13 \rightarrow 15 \rightarrow 2 \rightarrow 4$ and so on which is in round-robin fashion.

Additional details of PPE and PPA will be described in Chapter 4 in the context of comparing PPE and PPA with our approach.

#### 3.1.2 Logic Synthesis

Logic synthesis transforms a logic level description of a digital circuit into a gate level specification [3]. For large varieties of logic designs, logic synthesis provides fast design of logic at area and performance suitable for many Application-Specific Integrated Circuit (ASIC) designs [3, 15, 32]. For some classes of designs, such as multipliers and dividers, chip designers have devised custom logic structures that are much faster with much lower area, when compared to what a logic synthesis tool can deliver given the boolean description of the design.

The author could not find any prior research in logic synthesis focusing on arbitration logic or using token-passing in a multi-level logic network. Thus, while this thesis only presents a small focused tool able to generate custom arbitration logic and is not a general-purpose logic synthesis tool, nevertheless no prior work on logic synthesis known to the author focuses on synthesis of specialized arbitration logic using token-passing.

#### 3.1.3 Token Rings

Since the 1970s, Local Area Networks (LANs) [24, 48] have been developed using a token ring networks. In a token ring, there are many stations which are connected by point-to-point links in a ring topology. Transmission links in a ring topology shared by many stations require Medium Access Control (MAC) which coordinates access to the shared medium in order to prevent collisions. Only the station which has possession of the token has the privilege to transmit at any given time. A "token," the key idea used in a token ring, is used for the token ring MAC and travels around the ring-topology network.

We apply the "token" concept to our hierarchical BA and SA designs in order to rotate the priority level among input request signals. The token enables a particular logic block in our design, which specifying the priority order in request signals. The details of exactly how we use a "token" are discussed in Chapter 4.

## 3.2 On-chip Communication

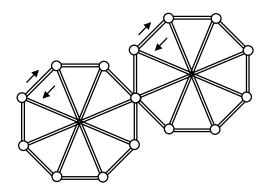

Considering multiple paths for on-chip communication, Karim *et al.* propose the "Octagon" bus which provides multiple on-chip communication channels for a multiprocessor SoC [19]. The octagon bus can support up to eight PEs and is scalable by sharing one port with another octagon bus as shown in Figure 12. There are bidirectional channels between ports, and each port has three queues: one for the route to cross, another for the route to the left and a third for the route to the right. Utilizing three queues is analogous to the VOQ concept in order to remove the HOL blocking problem. For applications whose communication patterns map closely to the Octagon bus structure, the Octagon bus can be an attractive and lower area alternative when compared to a full crossbar switch network.

Figure 12: Octagon bus

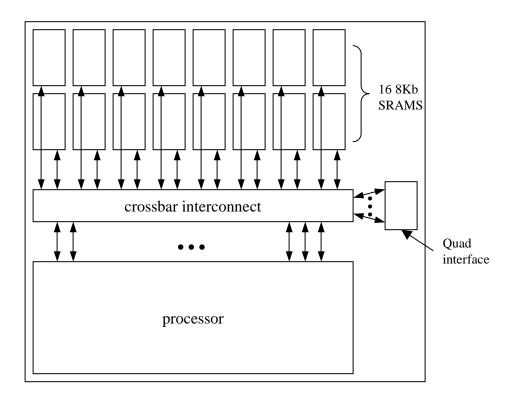

There are few approaches to reduce design time for an SoC crossbar switch. Mai *et al.* propose reconfigurable crossbar switch and memory blocks [25]. In [25], a processing tile consists of a processor, crossbar interconnect and sixteen 8Kbytes SRAM blocks as shown in Figure 13. The processor is composed of two integer clusters and a floating point cluster. The processor block is connected to sixteen SRAMs via a crossbar switch such that a different number of SRAMs can be remapped to two integer clusters and a floating point cluster depending on an application. A *quad* has four processing tiles, and each processing tile communicates via a quad network. There are many 2.5  $mm \ge 2.5 mm$  processing tiles with 0.1 $\mu$ m CMOS technology. However, the authors do not give details about their crossbar switch design.

Dally *et al.* propose a Network-on-Chip (NoC) in [11] which consists of network logic and tiles (similar to Mai *et al.* [28]). Dally *et al.* propose a tile structured NoC:

Figure 13: A processing tile with crossbar interconnect

sixteen 3  $mm \ge 3 mm$  tiles in a 12  $mm \ge 12 mm$  chip using 0.1µm CMOS technology with a 0.5µm minimum wire pitch. A tile can have client logic such as processors, DSPs, peripheral controllers and memory subsystems. With no top level connections other than the network logic, tiles communicate to one another by sending packets over the network logic. Each tile has one input controller at the west edge of a tile and four output controllers: one for the other directions (North, East and South) and one for the tile. The area overhead resulting from the on-chip network is estimated to be 6.6%. The arbitration scheme for a router is not explicitly mentioned in [11].

All literature discussed above present approaches to efficiently communicate onchip. Compared with [25], which appears to be designed by hand, our MxN crossbar (Xbar) switch is automatically generated with bus parameters specified by a user to support an exact number of masters and an exact number of slaves. Also, our generated Verilog code for an Xbar is synthesizable, resulting in a reduction of design time. Thus, from the above discussion, an Xbar switch Generator (X-Gt: the subset of DX-Gt described in Chapter 6) provides the first automated approach to Xbar switch generation.

In this chapter we showed previous arbiter designs and approaches to on-chip communication with multiple channels from Karim *et al.* [19] and from Mai *et al.* [25]. In Chapter 4, we will show how our arbiter design is different from others, especially PPE and PPA. We will present how our arbiter is automatically generated in Chapter 5. In Chapter 6, we will describe how our Xbar is customized according to customer specifications.

## CHAPTER IV

## **ROUND-ROBIN ARBITER DESIGN**

A round-robin token passing bus or switch arbiter guarantees avoidance of starvation among masters and allows any unused time slot to be allocated to a master whose round-robin turn is later but who is ready now. The protocol of a round-robin token passing bus or switch arbiter works as follows. In each cycle, one of the masters (in round-robin order) has the highest priority (i.e., owns the token) for access to a shared resource. If the token-holding master does not need the resource in this cycle, the master with the next highest priority who sends a request can be granted the resource. At the end of the cycle, the highest priority master then passes (in roundrobin order) the token to the next master which then will have the highest priority for the next time slot.

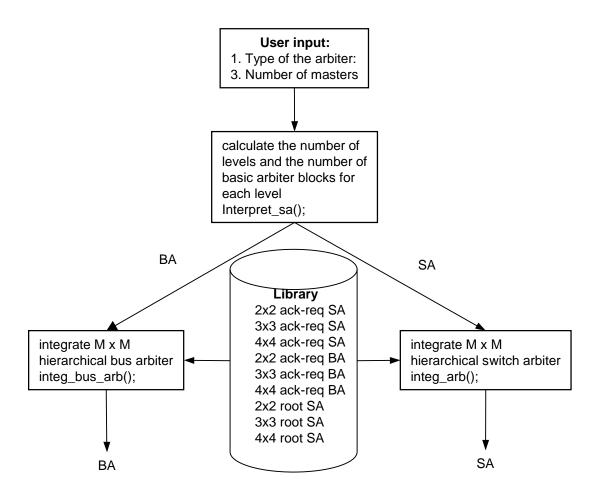

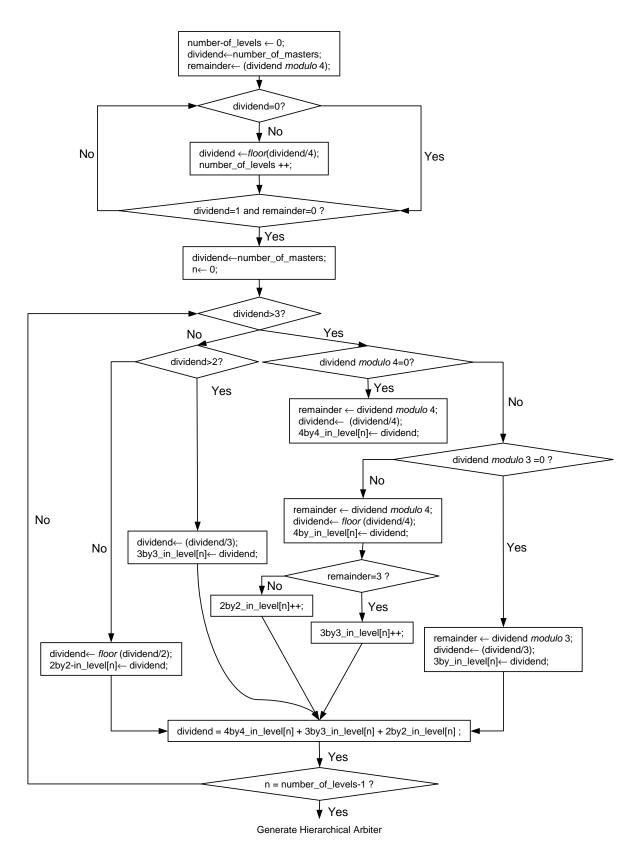

Section 4.1 (the next section) shows the design of 2x2, 3x3 and 4x4 Bus Arbiters (BAs) generated by our tool. In Section 4.2, we present a sample design of a 32x32 hierarchical SA generated by our tool. In Section 4.3, we describe how a hierarchical SA is modified to become a hierarchical BA. We discuss how our arbiter design approach impacts on logic synthesis in Section 4.4. Finally, we discuss the fairness issue in arbitration in Section 4.5. MxM hierarchical SAs and BAs generated by our Round-robin Arbiter Generator (RAG) have a hierarchical structure for values of M greater than four.

# 4.1 2x2, 3x3 and 4x4 Bus Arbiter Design

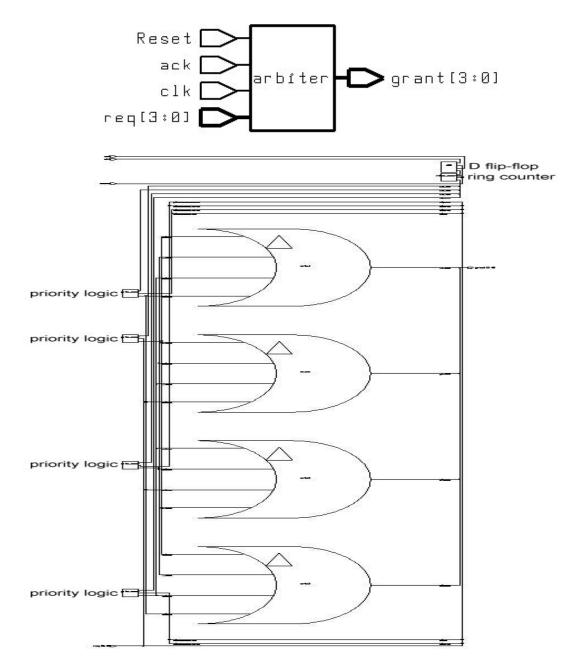

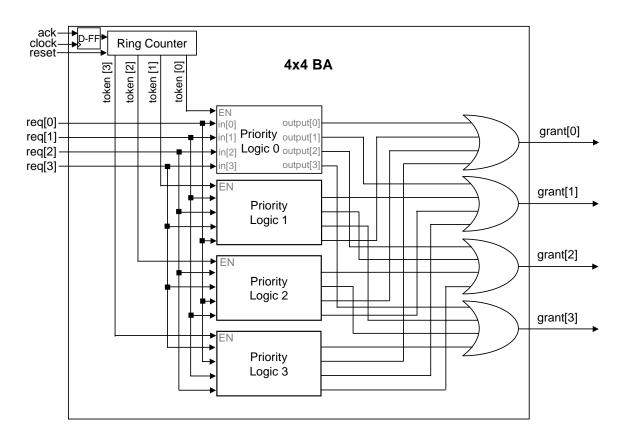

Figure 14 show a BA generated to handle four requests. The top figure of Figure 14 shows a BA block diagram for bus arbitration among four masters. To generate a

Figure 14: Block diagram and logic diagram of a 4x4 Bus Arbiter

hierarchical BA, RAG takes as input the number of masters and produces synthesizable Register Transfer Level (RTL) Verilog code. For synthesis of the logic for a four-master BA, the bottom of Figure 14 shows the logic synthesized by the Synopsys Design Compiler [51] with a TSMC  $0.25\mu$ m standard cell library [60] from LEDA Systems [23] (now Qualcore Logic).

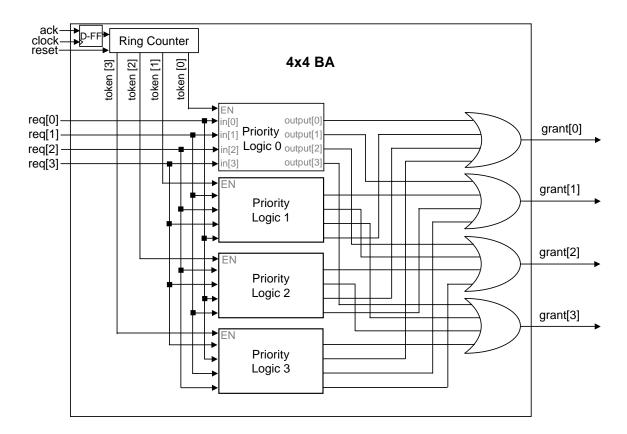

The four small blocks on the left side of the logic diagram in Figure 14 are the four "priority logic" blocks in Figure 15, and the block on the top right side of the logic diagram in Figure 14 is a ring counter. The functionality of a priority logic block is the same as that of a priority encoder [64] without output encoding; please see Table 1 for a truth table for a priority logic block for a 4x4 case.

The BA consists of a D flip-fop, priority logic blocks, an M-bit ring counter and M M-input OR gates as shown in Figure 15 where M=4. A 4x4 priority logic block is

Figure 15: 4x4 Bus Arbiter (BA) architecture

| EN | in[0] | in[1] | in[2] | in[3] | output[0] | output[1] | output[2] | output[3] |

|----|-------|-------|-------|-------|-----------|-----------|-----------|-----------|

| 0  | Х     | Х     | Х     | Х     | 0         | 0         | 0         | 0         |

| 1  | 1     | Х     | Х     | Х     | 1         | 0         | 0         | 0         |

| 1  | 0     | 1     | Х     | Х     | 0         | 1         | 0         | 0         |

| 1  | 0     | 0     | 1     | Х     | 0         | 0         | 1         | 0         |

| 1  | 0     | 0     | 0     | 1     | 0         | 0         | 0         | 1         |

**Table 1:** Truth table of a 4x4 priority logic block

implemented incombinational logic implementing the logic function of Table 1. The priority of inputs is placed in descending order from in[0] to in[3] in the priority logic blocks (*Priority Logic 0* through 3) shown in Figure 15. Thus, in[0] has the highest priority, in[1] has the next priority, and so on. To implement a BA, we employ the token concept from a token ring in a network. The possession of the token allows a priority logic block to be enabled. Since each priority logic block has a different order of inputs (request signals), the priority of request signals varies with the chosen priority logic block. The token is implemented in a 4-bit ring counter as shown in Figure 15.

**Example 4.1** When token = 4'b0100, processor 2 (req[2]) has the token and thus has the highest priority in this arbitration cycle. In other words, *Priority Logic 2* in Figure 15 is enabled and req[2] has the highest priority because req[2] is connected to in[0] of the priority logic block, *Priority Logic 2*.  $\Box$

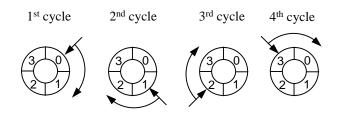

The outputs (four bits) of the ring counter act as the enable signals to the priority logic blocks. Thus, only the single enabled priority logic block can assert a grant signal. The *ack* signal to the bus arbiter is clocked by a D flip-flop as shown in Figure 15. The *ack* signal pulls a trigger to the ring counter so that the content of the ring counter is rotated one bit for the next arbitration cycle. Thus, the token bit is rotated left each cycle with 4'b1000 rotating to 4'b0001 in Figure 15, and the token is initialized to one at the reset phase (e.g., 4'b0001 for a four-bit ring counter) so that there is exactly one '1' output by the ring counter. In the round-robin algorithm, each master must wait no longer than (M - 1) time slots, where a time slot is the period of time allocated to the chosen master, until the next time it receives the token (i.e., highest priority). The assigned time slot can also be yielded to another master if the owner of the time slot has nothing to send [47]. This round-robin protocol guarantees a dynamic priority assignment to bus masters (requestors) without starvation.

In Figure 15, request inputs are connected with different levels of priority so that the priority levels are equally distributed over all request signals. In other words, the probability of being the highest priority is 0.25 for all request signals (req[0] - req[3]). Likewise the probability of being the second highest priority is also 0.25, and so on.

**Example 4.2** In Figure 15, req[0] has the highest priority in the top priority logic block (*Priority Logic 0*) and has the lowest priority in the next priority logic block (*Priority Logic 1*). Also, req[1] has the second highest priority in the top priority logic block and has the highest priority in the next priority logic block. The outputs of priority logic blocks are ORed together in the same order of the request inputs to priority logic blocks. In other words, for example, grant[0] is the output of a 4-input OR gate whose four inputs are *output*[0] (corresponding to req[0] input to in[0] of *Priority Logic 0*), output[3] (corresponding to req[0] input to in[2] of *Priority Logic 2*) and output[1] (corresponding to req[0] input to in[1] of *Priority Logic 3*).  $\Box$

**Example 4.3** Consider a scenario with four processors as bus masters connected to the same bus with one large shared memory as a slave on the bus as shown in Figure 16. Suppose the token is 4 (token = 4'b0100, which means processor 2 has the token), and only processor 0 (which uses req[0]) and processor 1 (req[1]) want to access the memory at this cycle. Token=4'b0100 enables only Priority Logic 2 in Figure 15. In Priority Logic 2, the connection to in[0] (req[2] from processor 2) indicates the highest priority. Since req[3]

Figure 16: Four processors with a shared memory system (Note: bus and 4x4 BA details shown only as needed for Example 4.1.)

is connected to in[1] of Priority Logic 2 in Figure 15, processor 3 has the next highest priority. However, since neither processor 2 nor processor 3 makes a request, in[2] which is connected to req[0] is next in line in priority. Thus, processor 0 is granted access to the memory. After processor 0 finishes, the memory controller of the accessed memory sends an ack signal, whose connection to the BA is shown in Figure 15, indicating when the memory transaction is successfully completed. Next, which could be several processor clock cycles later, the token is passed to processor 3 (the 4-bit ring counter is rotated left when the acksignal is received) in which case the token is 4'b1000. Note that only the asserted signals of this example are shown in Figure 16.  $\Box$

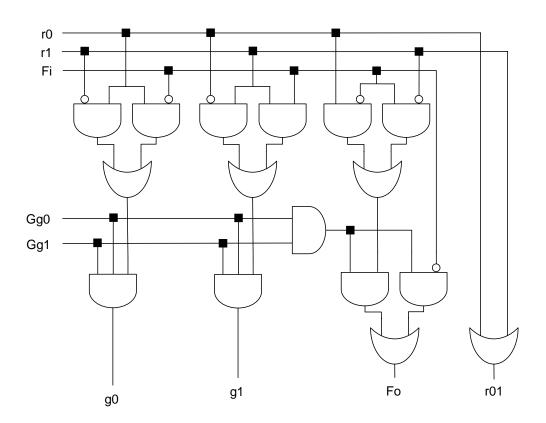

## 4.2 Switch Arbiter Design

We use 2x2, 3x3 and 4x4 switch arbiter blocks as basic modules to implement an MxM hierarchical Switch Arbiter (SA). Figure 17 shows how 2x2, 3x3 and 4x4 bus arbiters are modified to implement 2x2, 3x3 and 4x4 ack-req SAs by adding some AND and OR gates to a BA (note that the  $2x2 \ ack-req \ SA$  in Figure 17 is exactly the same as Figure 6). In Figure 17, request input signals are ORed together to generate a single request output (whose use will become clear later), and grant signals are ANDed

Figure 17: Ack-req SA blocks

together with an *ack* input (active high) which indicates that the corresponding ackreq SA is acknowledged in order to be enabled. Finally, the ack-req SA grants a master only if the *ack* input is asserted.

A root SA is placed at the top level of the hierarchy in a hierarchical SA. Specifically, a root SA is placed on the top of the hierarchical tree structure (an example of which will be shown in Figure 20). A root SA has no *ack* input nor *req* output. The input/output logic of a 2x2 root SA, a 3x3 root SA and a 4x4 root SA are the same as that of a 2x2 BA and a 4x4 BA except that there is no *ack* input and no D flip-flop in front of the ring counter as shown in Figure 18: thus, the *clock* input is used to rotate the content (the token bits) of the ring counter as shown in detail in Figure 19 for the case of a 4x4 root SA.

With the 2x2, 3x3 and 4x4 switch arbiter blocks shown in Figures 17 and 18, we can design an MxM hierarchical SA. Figure 20 shows how a 7x7 hierarchical SA is implemented and demonstrates a tree structure rotated clockwise by 90 degree. We call the 4x4 ack-req SA placed on the left side a "leaf" arbiter, and the final switch arbiter placed on the right side we call the "root" SA. We consider the "level" of a switch arbiter block to increase or go up moving toward the right. Thus, a "leaf" arbiter is always located at the lowest level. As shown in Figure 20,  $req_{-0}$  and  $req_{-1}$  signals act as request inputs to a switch arbiter block at the next highest level (in the case of Figure 20, the 2x2 root SA is the next highest level). The grant signals output by the higher level switch arbiter block(s) – in Figure 20, the 2x2 root SA is the only case – are used as inputs to the ack signals for lower level switch arbiter blocks – in Figure 20, ack0[0] and ack0[1]. Intuitively, the higher-level switch arbiter blocks.

We can redraw Figure 20 with 4x4 BAs by placing AND gates and OR gates as shown in Figure 21 (the AND gates and OR gates shown explicitly in Figure 21 were previously contained in the 4x4 ack-req SAs in Figure 20). Note in Figure 21 that

Figure 18: Root SA blocks

Figure 19: Detailed view of a 4x4 root Switch Arbiter

Figure 20: A 7x7 SA configuration (Note: reset signal not shown)

Figure 21: A 7x7 SA with a different placement of the AND gates (Note: reset signal not shown)

ack0[0] and ack0[1] are fed back to a D flip-flop for the next arbitration cycle to rotate the ring counter. However, the grant signals grant0[3:0] and grant1[3:0] are not fed back but instead are outputs in Figure 21.

Considering Figure 21, the two critical path candidates for the 7x7 SA are (i) a 4-input OR gate, a 2x2 root SA and an AND gate, or (ii) a 4x4 BA followed by a 2-input AND gate. It turns out that the critical path when using a TSMC  $0.25\mu$ m standard cell library from LEDA Systems is (i) a 4-input OR gate followed by a 2x2 root SA followed by an AND gate. Note that *ack0* signals from the 2x2 root SA feed into D flip-flops in the 4x4 BAs and thus do not affect the present arbitration cycle.

In Chapter 5, we will give a formal algorithm to design a hierarchical SA. For now note that to reduce the number of levels in the hierarchical SA, we use as many 4x4 switch arbiter blocks as possible because both the speed and area of a 4x4 switch arbiter block are less than the speed and area of employing two levels of 2x2 switch arbiter blocks to handle four requests, for a total of three 2x2 switch arbiter blocks: two leaves and one root as shown in Figure 22. For example, the delay of a 4x4 switch arbiter block is 0.34 ns in a TSMC  $0.25\mu$ m library [60] from LEDA Systems [23] which

Figure 22: A 4x4 SA implemented by three 2x2 switch arbiter blocks (Note: reset signal not shown)

is less than the delay of two levels of 2x2 switch arbiters implementing Figure 22: 0.46 ns using the same TSMC 0.25 $\mu$ m library from LEDA Systems. Also, comparing a 16x16 SA versus a combination of 4x4 switch arbiter blocks implementing a 16x16 hierarchical SA yields the following: a 16x16 SA with a 16-input priority logic block synthesized using the Synopsys Design Compiler leads to 1.49 ns gate delay using a TSMC 0.25 $\mu$ m library from LEDA Systems, while a 16x16 hierarchical SA yields only 0.76 ns gate delay using the same standard cell library. So, apparently, for fast implementation, it is best to keep MxM hierarchical SAs built out of 2x2, 3x3 and 4x4 switch arbiter blocks, with a preference for 4x4 switch arbiter blocks. This will be discussed in more detail in Chapter 5.

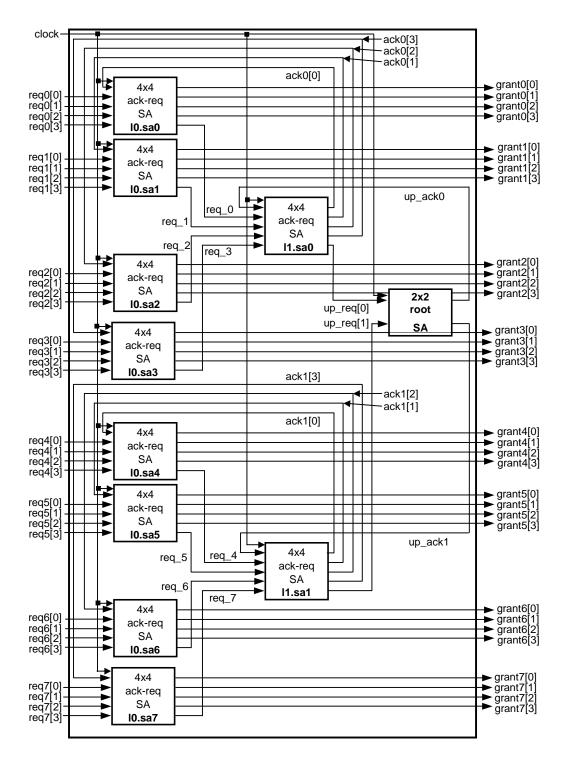

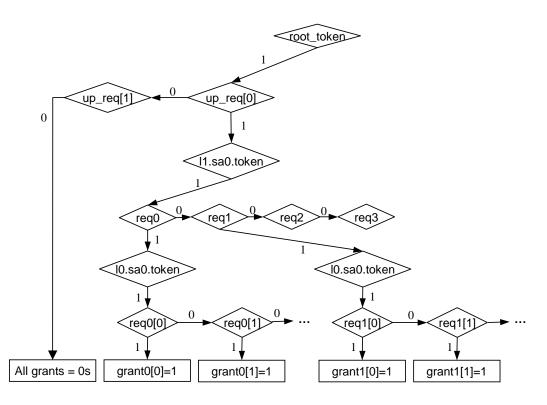

For a larger example, consider the 32x32 hierarchical SA shown in Figure 23. The 2x2 and 4x4 switch arbiter blocks are composed into a tree structure in Figure 23 (the leftmost blocks are the leaves and the rightmost block is the root). Non-root 2x2 and 4x4 ack-req SA blocks receive an acknowledgment from a switch arbiter block at the next higher level (which translates to being further toward the right hand side of Figure 23) for the next arbitration cycle. Since the root switch arbiter block in the hierarchy does not receive an acknowledgment (because there is no higher level switch arbiter block), the root arbiter uses the clock input to pass the token (i.e., highest priority) to the next master in every arbitration cycle in round-robin order.

In Figure 23, "l0.sa0" denotes switch arbiter ("sa") 0 in level 0 (the lowest level in the hierarchy where the left hand side of Figure 23 is the lowest). The 4x4 ack-req SAs placed on the left side of Figure 23 are the lowest level (l0.sa0 through l0.sa7) in the hierarchy, and the level goes up moving toward the right. At most one grant out of the 32 grants (outputs) is allowed to be set to logic '1' at a time. This hierarchical SA is a distributed switch arbiter whose individual 2x2 and 4x4 switch arbiter blocks operate in parallel with one another. In other words, the upper level switch arbiters (l1.sa0, l1.sa2 and the root arbiter) only arbitrate their own ORed requests (for example,

**Figure 23:** Hierarchical Switch Arbiter for 32 x 32 switch (Note: reset signal not shown)

$req_0$  through  $req_3$  for l1.sa0 from the lower level switch arbiters (l0.sa0 through l0.sa3) regardless of the *ack* signals from the higher level. Note that, for example, the ORed request  $req_0$  indicates whether any of req0[3:0] is currently making a request; thus,  $req_0$  indicates to l1.sa0 that l0.sa0 has at least one active request which l0.sa0 can grant if ack0[0] is set high, enabling l0.sa0. Also, ack signals from higher levels are fed back to D flip-flops in each ack-req SA in order to potentially rotate the token bit in the next arbitration cycle.

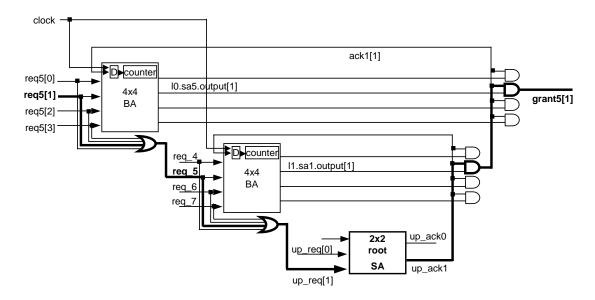

Figure 24: The critical path of Figure 23

For critical path considerations, we synthesized an RTL Verilog description of Figure 23 using the Synopsys Design Compiler [51] with a 0.25  $\mu$ m TSMC standard cell library [60] from LEDA Systems [23]. The longest logic delay in Figure 23 given by the Synopsys Design Compiler [51] is shown in Figure 24: two levels of ORed requests req\_5 (ORed req5[0] through req5[3]) and up\_req[1] (ORed req\_4 through req\_7), the gate delay of the 2x2 root arbiter, up\_ack1 ANDed with l1.sa1.output[1] finishing with ack1[1] ANDed with l0.sa5.output[1] which produces signal grant5[1]. This critical path is indicated by the bold line in Figure 24. This scheme of Figure 23 results in area savings and delay savings compared with a centralized arbiter. Even more, the design of a class of hierarchical SAs similar to Figure 23 is automated by our RAG tool, which will be described in Chapter 5.

We compare the performance and the area of our SA with those of the Programmable Priority Encoder (PPE), implementing iSLIP, and Ping-Pong Arbiter (PPA) in Chapter 7. We do not compare our SA with dual round-robin matching (DRRM). As mentioned in [7] by Chao, who is the first author of both DRRM [8] and PPA [7], PPA is proposed to reduce complexities due to the centralized arbitration algorithms like DRRM and iSLIP; thus, Chao claims that the arbitration of PPA is faster than that of DRRM. Hence, we do not compare our solution to DRRM but only to PPA, since, presumably according to Chao [7], if our solution is faster than PPA, then our solution is also faster than DRRM by the same or greater margin of speedup.

We chose to design our hierarchical SAs in the way shown in the previous two examples (Figure 20 and Figure 23) for two reasons. First, we want to reduce the number of levels in a hierarchical SA. As we showed in the comparison of a 4x4 SA with a 4x4 hierarchical SA composed of three 2x2 switch arbiter blocks as shown in Figure 22, a hierarchical 4x4 SA has longer logic delay than a 4x4 SA made using a single 4x4 BA (i.e., without any hierarchy). However, since PPA uses only 2x2 switch arbiters, PPA has more levels in its hierarchy resulting in longer logic delay than our SA. Hence, we prefer to use as many as 4x4 switch arbiter blocks possible in our hierarchical SA in order to reduce delay.

Employing priority encoders is one way of implementing an arbiter. However, the number of gates and the logic stages in a priority encoder rapidly increases as the number of masters increases, which leads to the longer critical path delay. Thus, we found that overall delay was the smallest when we limit the size of priority logic blocks to 2-input, 3-input or 4-input blocks to avoid the rapid increase in gate delay and area for PPE (which uses a single large priority encoder) as shown in Figure 45 of

# Algorithm 1 Pseudo code for token passing of the 2x2 root SA and a 4x4 switch

```

arbiter blocks

2x2 root token

begin

1: /*Initialization*/

2: root token = 2'b01;

3: if (positive edge of clock) then

rotate token;

4:

5: end if

end

4x4 ack-req SA token

begin

1: /*Initialization*/

2: ack-req token = 4'b0001;

3: if (positive edge of clock) then

if (ack) then

4:

5:

rotate token;

6:

end if

```

```

7: end if

end

```

Chapter 7. Furthermore, we use 2x2, 3x3 and 4x4 switch arbiter blocks to implement an MxM SA. Note that 3x3 switch arbiter blocks are utilized only when M is not a power of two.

Algorithm 1 presents in pseudo code how the 2x2 root SA and an 4x4 ack-req SA tokens are passed. The 2x2 root token is rotated every clock cycle using a 2-bit ring counter, while the token of a 4x4 ack-req SA is rotated using a 4-bit ring counter whenever the 4x4 ack-req SA is acknowledged from the higher level.

**Example 4.4** If the current token state of *l1.sa1* (the ring counter outputs token[3:0], see Figure 15 which shows the 4x4 Bus Arbiter of 4x4 ack-req SA in Figure 17) in Figure 23 equals 4'b1000 implying that  $req_{7}$  has the highest priority, the token will be rotated to give  $req_4$  the highest priority in the next arbitration cycle if  $up\_ack1$  is asserted.  $\Box$