### ASSESSING THE PERFORMANCE AND RELIABILITY OF GALLIUM NITRIDE BASED ELECTRONICS VIA OPTICAL AND ELECTRICAL METHODS

A Dissertation Presented to The Academic Faculty

by

Georges Pavlidis

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the George W. Woodruff School of Mechanical Engineering

> Georgia Institute of Technology MAY 2018

## **COPYRIGHT © 2018 BY GEORGES PAVLIDIS**

### ASSESSING THE PERFORMANCE AND RELIABILITY OF GALLIUM NITRIDE BASED ELECTRONICS VIA OPTICAL AND ELECTRICAL METHODS

Approved by:

Dr. Samuel Graham, Advisor School of Mechanical Engineering *Georgia Institute of Technology*

Dr. Eric Heller Materials and Manufacturing Directorate *Airforce Research Laboratory*

Dr. Peter Hesketh School of Mechanical Engineering *Georgia Institute of Technology*  Dr. Satish Kumar School of Mechanical Engineering *Georgia Institute of Technology*

Dr. Shyh-Chiang Shen School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. John D. Cressler School of Electrical and Computer Engineering *Georgia Institute of Technology*

Date Approved: April 5th, 2018

[To the graduate students of the Georgia Institute of Technology]

#### ACKNOWLEDGEMENTS

Throughout my PhD, I have gained an enormous amount of knowledge and learned several valuable lessons. I first would like to acknowledge and thank my advisor Professor Samuel Graham for his constant support, patience and encouragement to explore new areas of research. You have inspired me to become a better researcher and communicator and have always spent the time to solve any obstacles that I encountered throughout my PhD.

I would also like to thank Dr. Eric Heller (AFRL) for spending the time to discuss with me on a biweekly basis about my research. The knowledge he has provided to me as well as the research questions he has pushed me to answer, have contributed significantly to results presented in this thesis. I am also sincerely grateful to the Materials and Manufacturing Directorate at AFRL for their financial support for which I would not have been able to complete my PhD without this. I would also like to thank Dr. Donald Dorsey and Dr. Elizabeth Moore for participating in fruitful conversations about my research.

I would also like to extend my sincere thanks to Professor Peter Hesketh, Professor Satish Kumar, Professor John Cressler and Professor Shyh-Chiang Shen for serving on my thesis committee. I am grateful for their time taken to carefully review my work and provide me with advice. Several collaborators have made this thesis possible by either providing high quality devices or materials for analysis. I would like to acknowledge the following collaborators: Dr. Ramakrishna Vetury for providing me with RFMD GaN/SiC gate resistance Transistors; Dr. Farid Medjdoub (IEMN) for providing me with GaN/Si HEMTs with the etched substrate technology; Professor Shyh-Chiang Shen for providing me with vertical GaN PIN diodes; Professor Hiroshi Amano for hosting me in his lab at Nagoya University and continuing to provide high quality epitaxial GaN films and cross sectional PIN diodes; Jason Barrett, John Atherton, Wayne Struble and Shamit Som from MACOM for hosting me for an internship and allowing me to conduct RF GRT measurements on their GaN/Si technology. Albert Hilton (AFRL) for providing me with Cross Sectional GaN/Si HEMTs. IQE for providing with strain engineered superlattice HEMTs. Professor Sukwon Choi for his deep knowledge in thermal characterization of GaN electronics and continuing collaborations. I would also like to thank Spyros Pavlidis and Saurabh Gupta for their wirebonding skills.

I next would like to thank all the Graham Group lab members who made my time here at Georgia Tech more enjoyable and were always available to help me when needed. This includes Luke Yates, Dr. Wale Odukomaiya, Dr. Ankit Kumar, Dr. Minseok Ha, Dr. Hyungchul Kim, Dr. Nazli Donmezer, Dr. Anne Mallow, Jason Jones, Samuel Kim, Yvette Chen, Kenechi Agbim, Kirkland Malcolm, Nicholas Hines, Kyungjin Kim, Waylon Puckett, Cole Skinker, Michael Sulkis, Gabe Cahn, Jason Hirschey. Special thanks is also given to Dr. Brian Foley and Dr. Darshan Pahinkar. I would also like to thank the visiting scholars Dr. Ting Cheng, Dr. David Mele and Dr. Enes Tamdogan for their productive research collaborations. The staff at Georgia Tech have also been instrumental in the development of my PhD. I would like to thank Regina Neequaye, Joyce Lowe, Segried Winfrey, Kenneth Garrick, Darryl Williams, Cary Ogletree, Cynthia Pickett, Glenda Johnson and the staff at the manufacturing workshop. Having spent the majority of my time in the Love building, I would like to thank the cleaning facilities for making the building a more enjoyable place to work in. Keeping myself busy outside the lab, I have been fortunate enough to develop new friendships that will last for a lifetime. I would like to thank British Calloway for always being there for me and helping me get through any obstacle I faced. I would like to thank my lunchtime buddies: Abdalla, Pietro, Joaquin, Giovanni, Matias, Sourabh, Shekaib, Stefano, Alessandro and Pietro 2.0. My soccer buddies: Domenic, Noris, Esteban, Camilo, Lucas, Sebastian, Diego, Sam, Brian, goalie Mike and Mike. And I cannot forget my basketball buddies: Dimitris and David who helped me win an intramurals championship together. Thank you very much to all the other graduate students who have also provide me with quality experiences.

My family has played an instrumental role throughout my PhD providing me with unlimited guidance and support to achieve my goals. I would like to thank my older brother Spyros for not only helping me with my research and giving me tips on how to get through my PhD but also always being there to talk. My younger sister Despina, for coming to Georgia Tech for undergrad and helping me get through my final years of my PhD. My sister in law Stef for always trying to cheer up my day. I cannot quantify how thankful I am to my parents, Dimitris and Vasso, who have ensured my success and provided me with unconditional support and love to me.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                | iv    |

|-----------------------------------------------------------------|-------|

| LIST OF TABLES                                                  | X     |

| LIST OF FIGURES                                                 | xi    |

| NOMENCLATURE                                                    | xviii |

| SUMMARY                                                         | XX    |

| CHAPTER 1. Introduction                                         | 1     |

| 1.1 Background and Motivation                                   | 1     |

| 1.2 Review of Thermometry Techniques                            | 4     |

| 1.2.1 IR Thermography                                           | 4     |

| 1.2.2 Thermo-Sensitive Electrical Parameters                    | 5     |

| 1.2.3 Raman Thermometry                                         | 7     |

| 1.2.4 Thermoreflectance                                         | 9     |

| <b>1.3 Research Objectives</b>                                  | 11    |

| 1.4 Dissertation Outline                                        | 13    |

| CHAPTER 2. Gate Resistance Thermometry for AlGaN/GaN HEMTs      | 15    |

| 2.1 Overview and Approach                                       | 15    |

| 2.1.1 Experimental Setup and Calibration                        | 15    |

| 2.1.2 Experimental Validation                                   | 17    |

| 2.1.3 Numerical Validation                                      | 19    |

| 2.2 Steady State Analysis                                       | 22    |

| 2.2.1 Fully Open Channel                                        | 22    |

| 2.2.2 High Drain Bias Operation                                 | 24    |

| 2.3 Transient Thermal Analysis under Pulsed Bias                | 27    |

| 2.3.1 Effect of Gate Leakage                                    | 27    |

| 2.3.2 Effect of Probe Current                                   | 29    |

| 2.3.3 Effect of Duty Cycle                                      | 32    |

| 2.4 Summary and Conclusions                                     | 36    |

| CHAPTER 3. Comparison of RF to DC Thermal Performance in GaN HE | MTs   |

| Using Gate Resistance Thermometry                               | 38    |

| 3.1 Overview and Approach                                       | 39    |

| 3.1.1 Removing the Uncertainty due to Gate Leakage              | 40    |

| 3.1.2 Temperature Coefficient of Resistance (TCR)               | 42    |

| 3.1.3 Steady State Thermal Analysis                             | 44    |

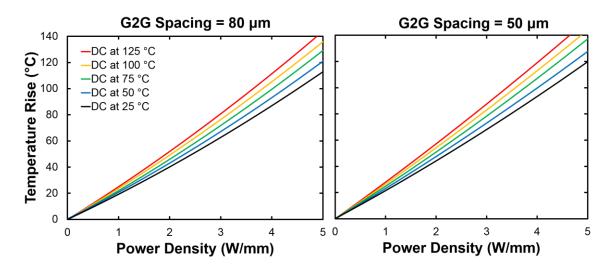

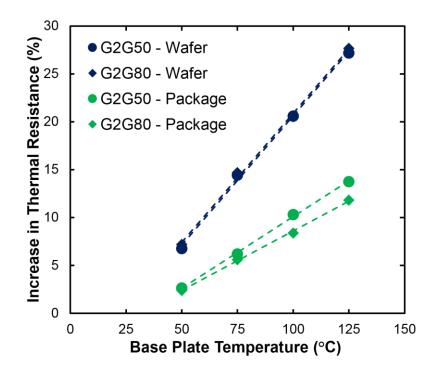

| <b>3.2 Effect of Baseplate Temperature</b>                      | 45    |

| 3.2.1 DC Biasing                                                | 45    |

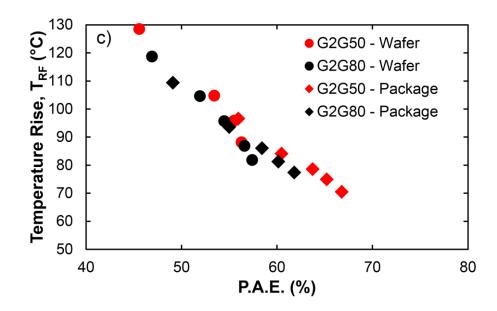

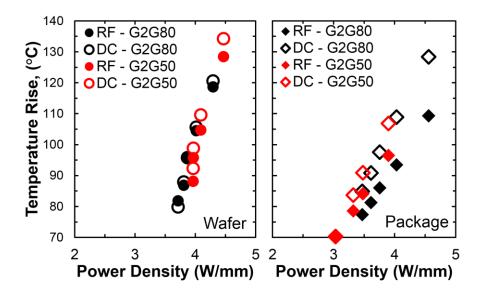

| 3.2.2 RF Operation                                              | 47    |

| <b>3.3 RF vs DC Operation</b>                                   | 48    |

| 3.4 Transient Analysis                                                | 50  |

|-----------------------------------------------------------------------|-----|

| 3.5 Summary and Conclusions                                           | 52  |

| CHAPTER 4. Development of Optical Thermal Metrology Techniques for Ga | N   |

| HEMT Reliability                                                      | 53  |

| 4.1 Raman Active Nanoparticles for Surface Temperature Measurements   | 53  |

| 4.1.1 Sample Preparation and Calibration                              | 54  |

| 4.1.2 Effect of Nanoparticles on Electrical Performance               | 61  |

| 4.1.3 Channel Temperature Mapping                                     | 62  |

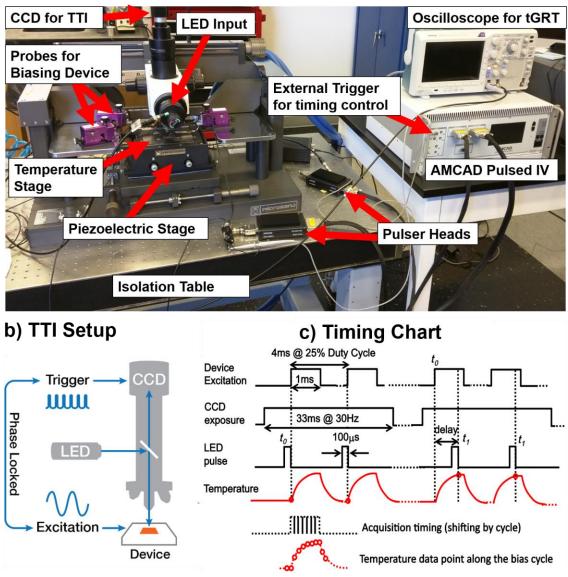

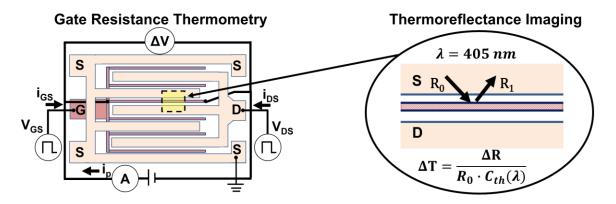

| 4.2 Transient Thermoreflectance Imaging                               | 64  |

| 4.2.1 Theory and Experimental Setup                                   | 64  |

| 4.2.2 Design Specifications and Considerations                        | 66  |

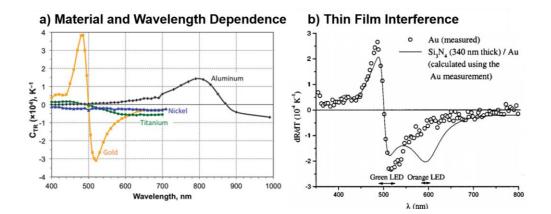

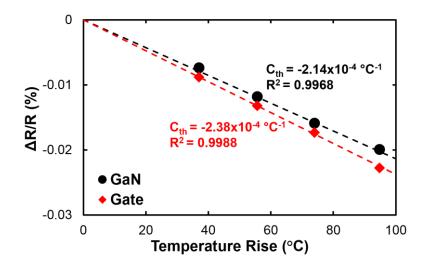

| 4.2.3 Understanding the Thermoreflectance Coefficient                 | 67  |

| 4.2.4 Experimental Validation                                         | 68  |

| 4.2.5 Development of UV Thermoreflectance Imaging                     | 75  |

| 4.2.6 Improvement of Transient Thermoreflectance Imaging              | 79  |

| 4.2.7 Thin Film Interference                                          | 83  |

| 4.3 Summary and Conclusions                                           | 87  |

| CHAPTER 5. Understanding The Vertical Temperature Gradient in GaN Ba  | sed |

| Electronics                                                           | 88  |

| 5.1 Overview and Approach                                             | 88  |

| 5.2 Cross Sectioned GaN/SiC HEMTs                                     | 89  |

| 5.2.1 Plan View TTI                                                   | 89  |

| 5.2.2 Cross Sectional TTI                                             | 92  |

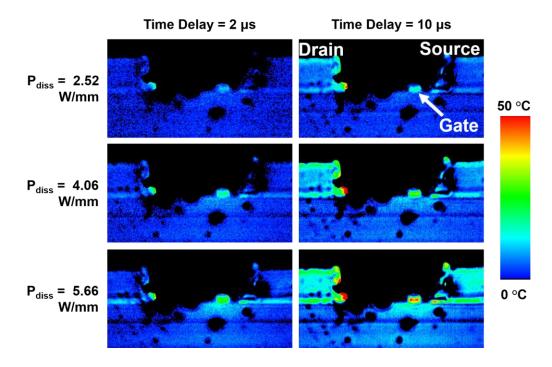

| 5.2.3 Power Dependence                                                | 93  |

| 5.2.4 Bias Dependence                                                 | 98  |

| 5.2.5 Cross Sectional Raman Thermometry                               | 100 |

| 5.3 Vertical GaN PIN Diodes                                           | 103 |

| 5.3.1 Assessing the thermal distribution via Raman Thermometry        | 104 |

| 5.3.2 Transient Comparison via Transient Thermoreflectance Imaging    | 108 |

| 5.3.3 Cross Sectional Temperature Mappings of Vertical GaN PN Diodes  | 110 |

| 5.4 Summary and Conclusions                                           | 114 |

| CHAPTER 6. The Impact of Strain Relief Layers on Power Electronics    | 116 |

| 6.1 Overview and Approach                                             | 116 |

| 6.2 Thermal Analysis                                                  | 117 |

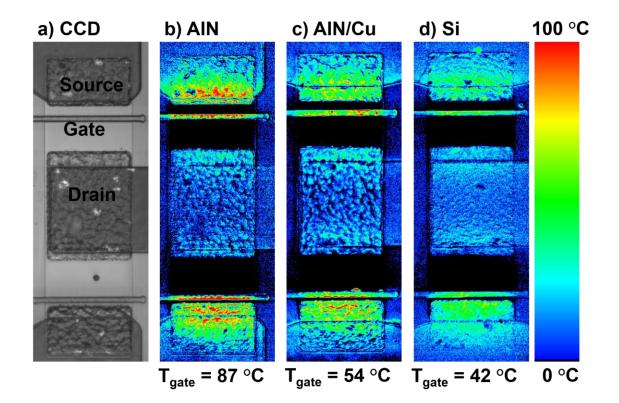

| 6.2.1 Comparison of Gate Metal Temperatures                           | 117 |

| 6.2.2 Bandgap Dependence UV Thermoreflectance Imaging                 | 119 |

| 6.2.3 Above Bandgap UV Thermoreflectance Imaging                      | 122 |

| 6.3 Electroluminescence                                               | 123 |

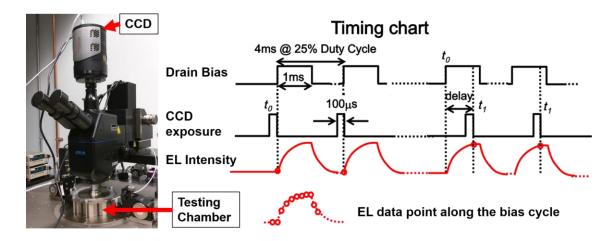

| 6.3.1 Experimental Setup and Methods                                  | 124 |

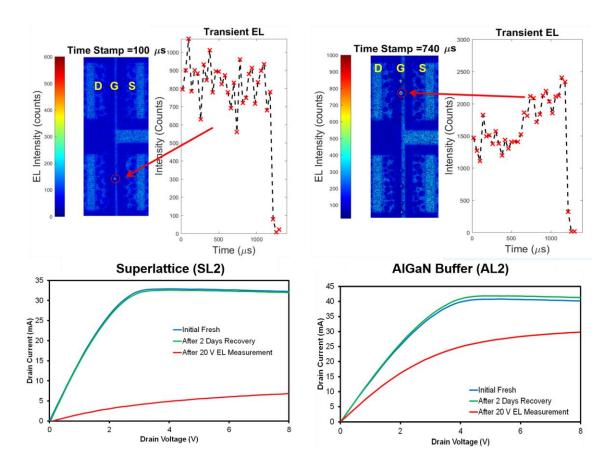

| 6.3.2 Transient Electroluminescence                                   | 127 |

| 6.3.3 Design Considerations                                           | 128 |

| 6.4 Summary and Conclusions                                           | 130 |

| CHAPTER 7. THE Impact of Substrate Removal on Power Electronics       | 132 |

|   | ٠ | ٠ | ٠ |

|---|---|---|---|

| V | 1 | 1 | 1 |

| 7.1 Overview and Approach                                        | 132 |

|------------------------------------------------------------------|-----|

| 7.2 Device Description and Electrical Characterization           | 133 |

| 7.3 Application of Raman Active Nanoparticles                    | 136 |

| 7.4 Thickness Dependent Vertical Temperature Gradient            | 137 |

| 7.5 Effect of Substrate of Removal                               | 139 |

| 7.6 Improvement of Thermal Performance by AlN/Cu Layer Insertion | 140 |

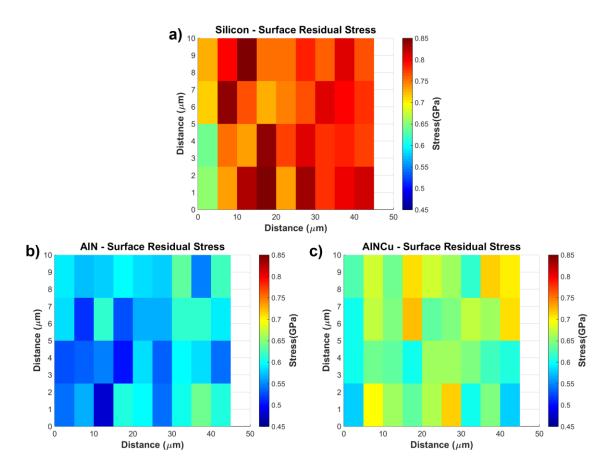

| 7.7 Residual Stress Analysis                                     | 144 |

| 7.8 Summary and Conclusions                                      | 146 |

| CHAPTER 8. Conclusions                                           | 148 |

| 8.1 Summary of Contributions                                     | 149 |

| 8.1.1 Electrical Methods                                         | 149 |

| 8.1.2 Optical Methods                                            | 150 |

| 8.2 Future Work                                                  | 151 |

| REFERENCES                                                       | 156 |

## LIST OF TABLES

| Table 1 Temperature dependent thermal conductivities applied to initial model. Ta | ken from |

|-----------------------------------------------------------------------------------|----------|

| [75]                                                                              |          |

| Table 2 Comparison of GRT to IR thermometry.                                      |          |

| Table 3 Material properties of nanoparticles under investigation.                 |          |

## LIST OF FIGURES

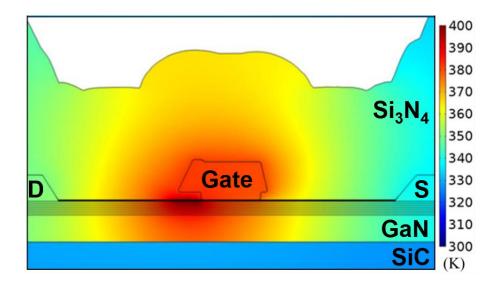

| Figure 1: Hotspot formation in GaN HEMT (adapted from [7])2                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

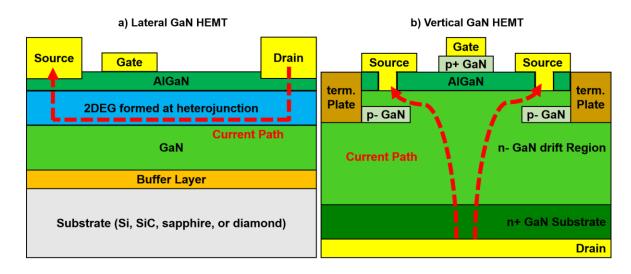

| Figure 2: Current path in a) Lateral GaN HEMT and b) Vertical GaN HEMTs                                                                                                                                                                                                                                                                                           |

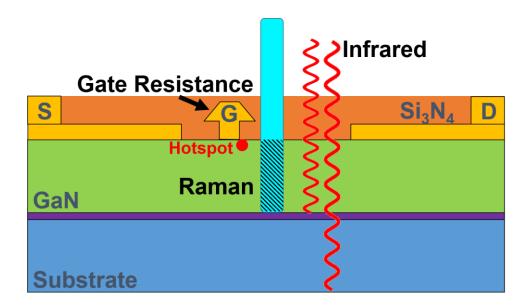

| Figure 3: Schematic of different thermometry techniques for lateral GaN devices                                                                                                                                                                                                                                                                                   |

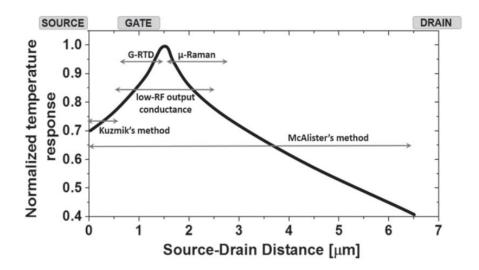

| Figure 4: Comparison of location of TSEPs across GaN HEMT [42]                                                                                                                                                                                                                                                                                                    |

| Figure 5: a) Overview of experimental setup designed for the verification of Gate Resistance Thermometry (GRT) b) Detailed description of different parts used to perform GRT simultaneously to biasing the device                                                                                                                                                |

| Figure 6: a) Device layout and configuration of four terminal sensing to measure the gate resistance over a single finger for 6 finger devices with gate widths of 370 $\mu$ m and 1000 $\mu$ m. b) Linear calibration fit used to measure the thermal response of the gate metal resistance of a 6 x 1000 $\mu$ m device for a temperature range of 30 to 120 °C |

| Figure 7: Schematic of layer configuration implemented in the 3D FEM thermal model including the SiC substrate. The gate resistance probed area is highlighted in red while the GaN probed volume is circled in black                                                                                                                                             |

| Figure 8: Comparison of Raman (Black) and GRT (Red) measured temperatures to respective FEM probed temperatures for 6 x 370 $\mu$ m devices at power densities up to 3.5 W/mm.                                                                                                                                                                                    |

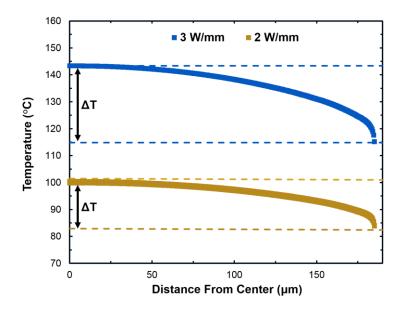

| Figure 9: FEM temperature distribution from the center of the gate finger to the edge of the 6 x 370 $\mu$ m device. The temperature difference at 3 W/mm (blue) results in a larger temperature difference, $\Delta$ T, when compared to the 2 W/mm (gold) powering condition.23                                                                                 |

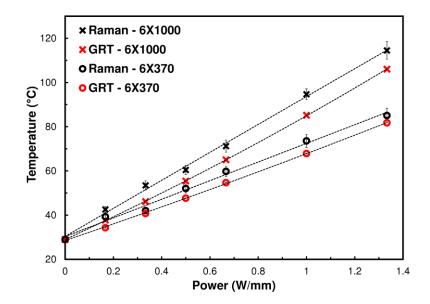

| Figure 10: Comparison of Raman (Black) and GRT (Red) measured temperatures at 28 V drain bias for bot 6 x 370 $\mu$ m and 1000 $\mu$ m devices at power densities up to 1.33 W/mm. 25                                                                                                                                                                             |

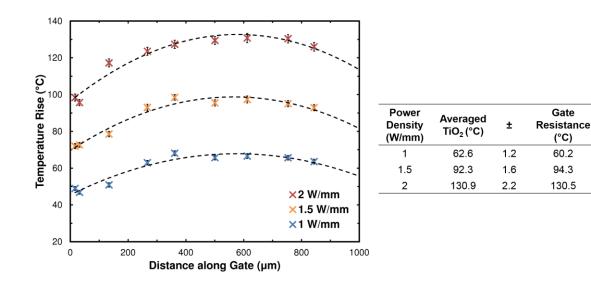

| Figure 11: Temperature distributions along the gate width of the 6 x1000 $\mu$ m device at different power densities using TiO <sub>2</sub> nanoparticles to directly measure the gate metal surface temperature. Second order polynomials were fitted to each set of measurements and then averaged to directly compare to GRT values                            |

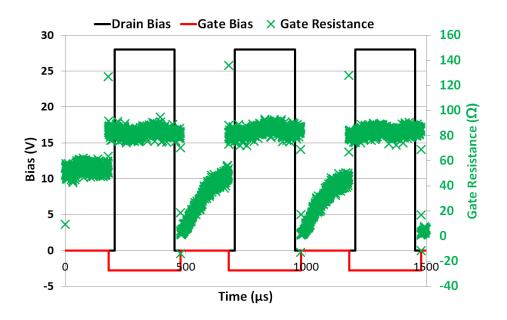

| Figure 12: Attempt to pulse both drain and gate while monitoring the gate resistance 28                                                                                                                                                                                                                                                                           |

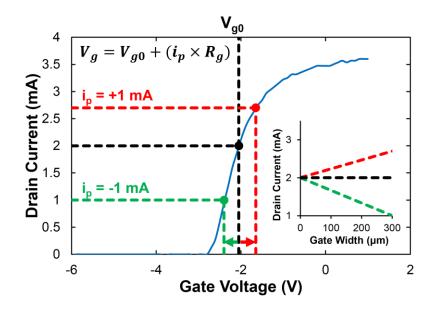

| Figure 13: Effect of probe current's magnitude and direction on drain current, $I_{ds}$ . Inset shows $I_{ds}$ distribution along gate when probe current is applied                                                                                                                                                                                              |

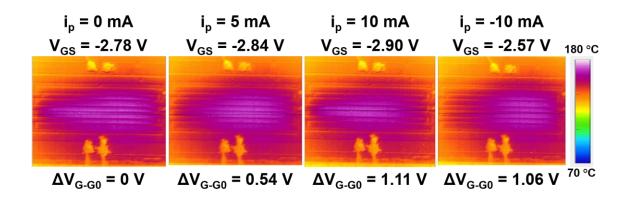

| Figure 14: Effect of probe current on overall thermal distribution. 6x1000 µm GRT devices were biased at 0.8 W/mm                                                                                                                                                                                                                                                 |

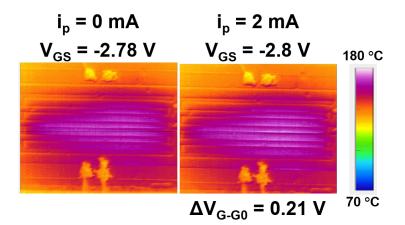

| Figure 15 Effect of 2 mA probe current on thermal distribution was determined minimal and was thus used for the remainder of measurements                                                                                                                                                                                                                         |

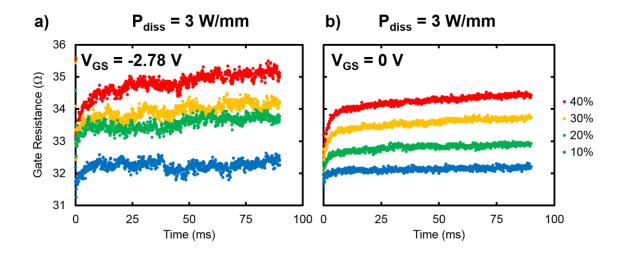

| Figure 16: Transient response of gate resistance for $6x370 \mu m$ device under pulsed biasing when a constant gate voltage of a) -2.78 V and b) 0 V is applied. Drain bias was adjusted to match power densities of 3 W/mm                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

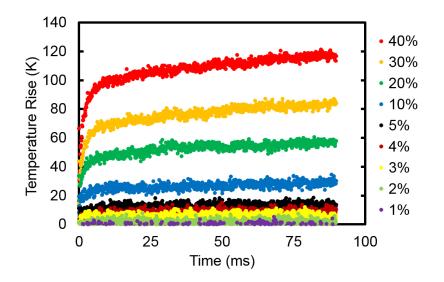

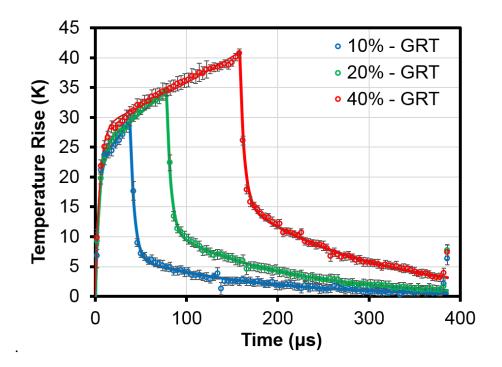

| Figure 17: Transient device temperature response for varying duty cycle at a power density of 3 W/mm                                                                                                                                                                           |

| Figure 18: Transient thermal response of GaN HEMT under various duty cycles                                                                                                                                                                                                    |

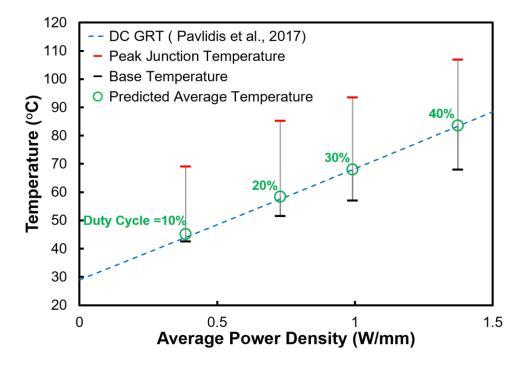

| Figure 19: Absolute base and peak temperature measured by GRT for varying duty cycle from 10% to 40% with a time period of 400 us. A calculated average gate temperature is compared to DC GRT results measured for the same device                                            |

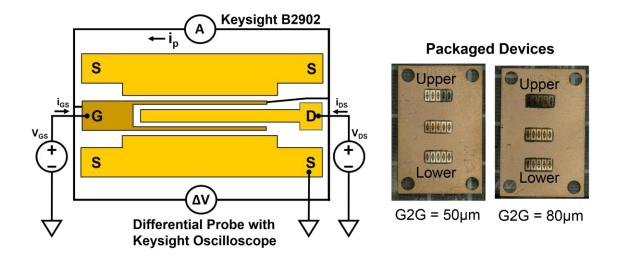

| Figure 20: Experimental setup for gate resistance thermometry (GRT). A four-point measurement across a single finger of a $2x300 \ \mu m \ GaN/Si \ HEMTs$ was performed. Both on wafer and packaged measurements were. The devices were packaged on a CuW die.40              |

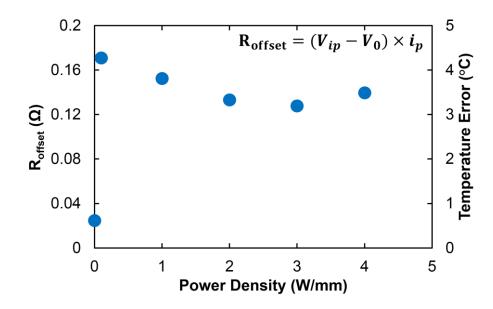

| Figure 21: Effect of power density on the uncertainty of gate resistance thermometry. During operation, significant gate leakage causes an offset in the probe current, i <sub>p</sub> , which results in a change in the measured gate resistance that is not due temperature |

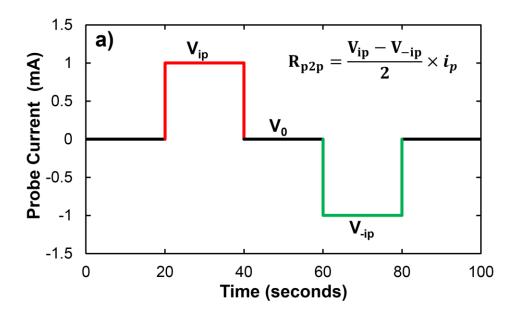

| Figure 22: Peak to peak timing diagram of the probe current direction applied to the GRT device. 42                                                                                                                                                                            |

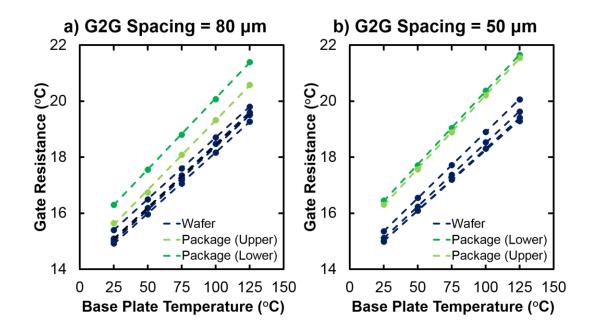

| Figure 23: Linear calibration fit used to extract the temperature coefficient of resistance (TCR) for both on wafer and packaged devices with a gate pitch of a) 80 µm and b) 50 µm.                                                                                           |

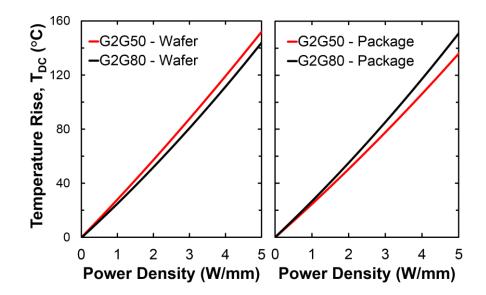

| Figure 24: Steady state thermal response of GaN/Si HEMTs at 125 °C base plate temperature a) on wafer b) mounted on CuW package                                                                                                                                                |

| Figure 25: Effect of base plate temperature on DC thermal performance for a gate to gate spacing (G2G) of a) 80 µm and b) 50 µm                                                                                                                                                |

| Figure 26: Effect of base plate temperature on thermal resistance of effective stack. Percentage change is relative to thermal resistance calculate at 25 °C                                                                                                                   |

| Figure 27: RF Thermal performance of GaN/Si HEMTs at different Power Added Efficiencies (P.A.E.) evaluated using GRT at different base plate temperatures from 25 to 125 °C                                                                                                    |

| Figure 28: Comparison of junction temperature measured under RF operation to DC steady state biasing. Temperatures were compared for identical base plate temperatures and power dissipated                                                                                    |

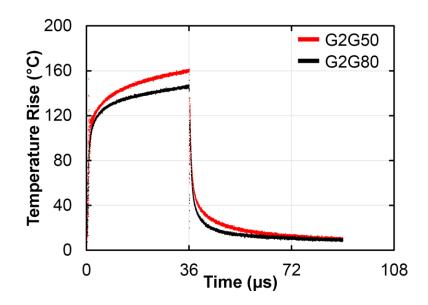

| Figure 29: Transient thermal response of packaged GaN/Si HEMTs with different gate to gate spacings. A 50 V drain bias was applied for a 10% duty cycle                                                                                                                        |

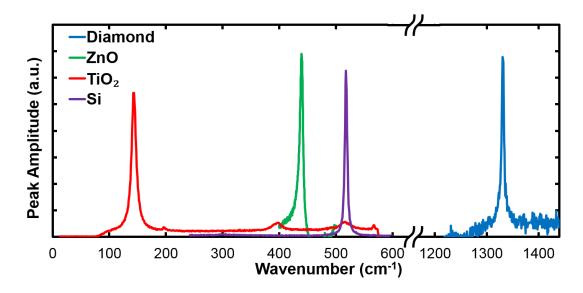

| Figure 30: Raman spectra of nanoparticles under investigation using a 488 nm laser 56                                                                                                                                                                                          |

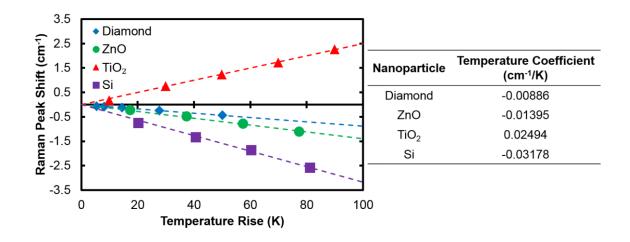

| Figure 31: Temperature dependence of different nanoparticle phonon frequencies. Linear regression was applied to extract the temperature coefficients                                                                                                                          |

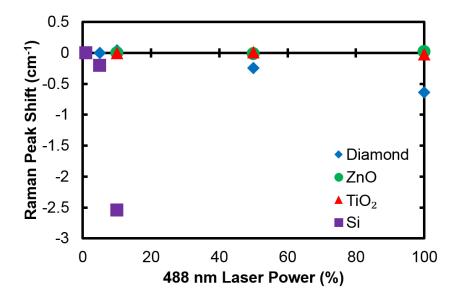

| Figure 32 Effects of laser self-heating on Raman nanoparticles phonon frequency 58                                                                                                                                                                                             |

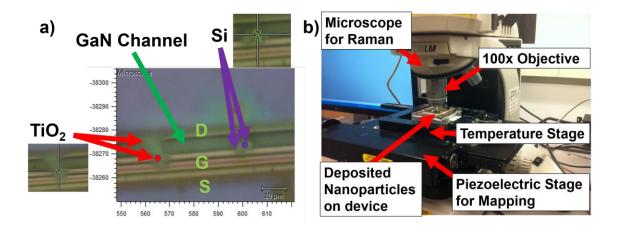

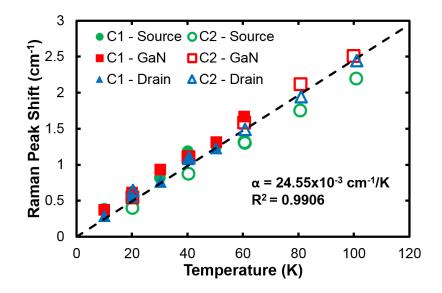

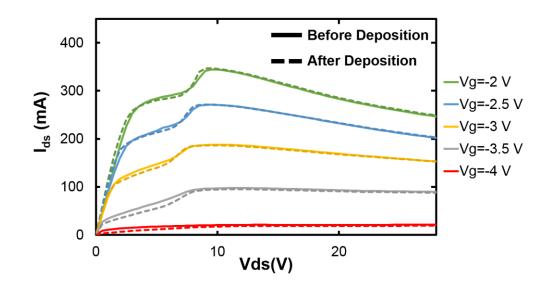

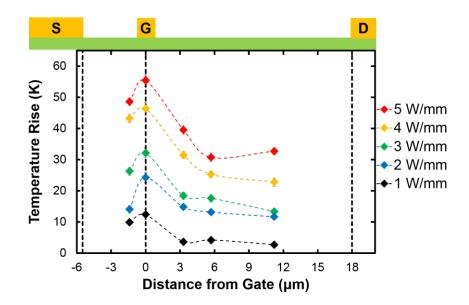

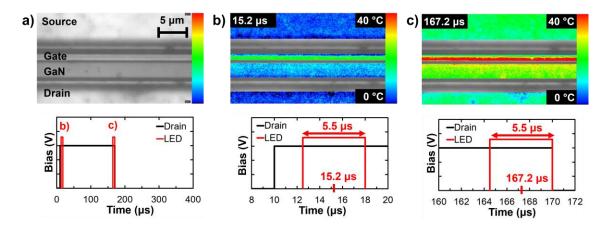

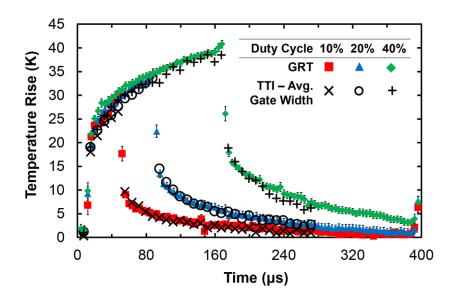

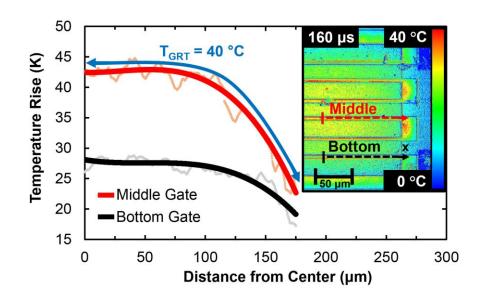

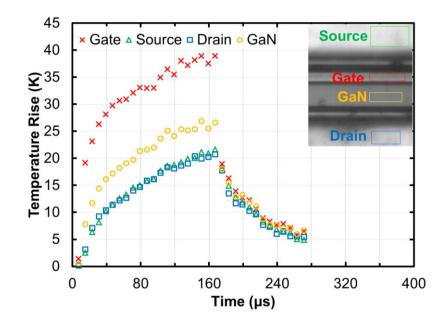

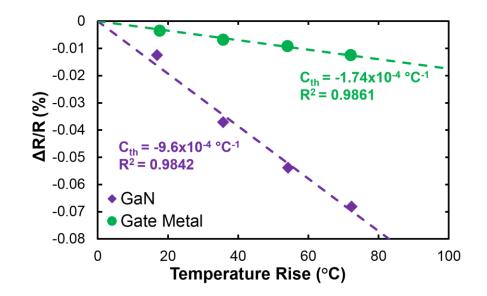

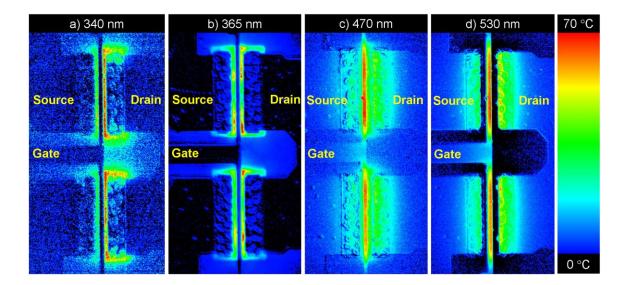

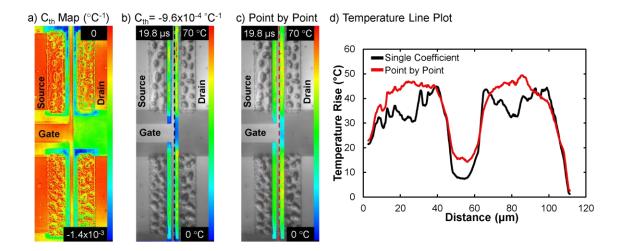

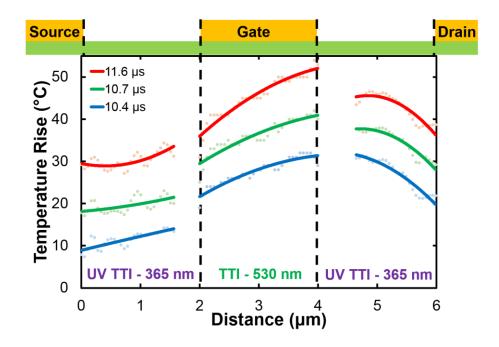

Figure 33: a) Location of nanoparticles when deposited on GaN HEMT b) Description of Figure 34: Uniformity of temperature calibration coefficient of TiO<sub>2</sub> nanoparticles across Figure 35: Effect of TiO<sub>2</sub> nanoparticle deposition on GaN HEMT IV characteristics..... 61 Figure 36: Lateral surface channel temperature mappings of GaN/SiC HEMT using TiO<sub>2</sub> Figure 37: a) Experimental setup of Microsani thermoreflectance system b) Schematic describing the different components used in thermoreflectance imaging c) Schematic Figure 38: a) Thermoreflectance coefficient (CTR) vs. illumination wavelength for various materials [95] b) Spectrum of dR/dT measured in the case of bare gold (circles), and calculated in the case of Si<sub>3</sub>N<sub>4</sub>-coated gold (line). The arrows indicate the FWHM spectral width of two of the LEDs [69].....67 Figure 39: Four terminal sensing gate resistance thermometry device in pulsed bias configuration. For direct comparison to transient thermoreflectance imaging, simultaneous thermoreflectance mapping of the device gate width was performed. A 405 nm LED Figure 40: Linear temperature dependence of the thermoreflectance signal detected from the gate and GaN channel region using a 405 nm LED source. Linear thermoreflectance Figure 41: a) CCD image of 6x370 µm GaN HEMT including timing synchronization between device bias and LED pulse. LED pulse widths of 5.5 µs were applied at time delays of b) 15.2 µs and c) 167.2 µs. The corresponding CCD based thermoreflectance image highlights the area of localized Joule heating along the gate width during pulsing. Figure 42: Comparison of transient thermal response of a GaN HEMT under various duty cycles measured by transient thermoreflectance imaging, TTI (markers) and gate resistance Figure 43: Temperature profile along gate width of middle gate finger and bottom gate finger. Temperature profiles were extracted from thermal image measured by Transient Thermoreflectance Imaging using a 20x lens. The blue line represents the averaged area Figure 44: Temperature profile monitored by transient thermoreflectance imaging, TTI, of different regions across device for a duty cycle of 40%......74 Figure 45: Linear temperature dependence of the gate metal thermoreflectance signal using Figure 46: Transient thermoreflectance imaging of 2x42 µm GaN/Si HEMT using different wavelength LED excitation sources. Near UV wavelengths: a) 340nm and b) 365 nm resulted in strong temperature mappings of the GaN Channel region while longer

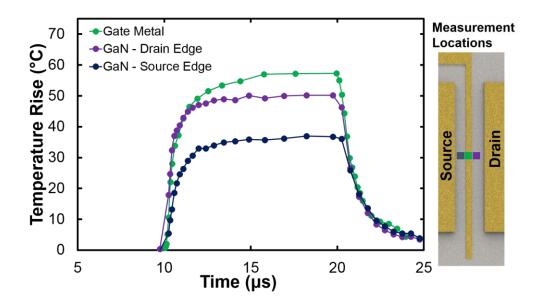

Figure 48: Transient thermal response of GaN/Si measured by thermoreflectance imaging. Gate metal temperature was monitored using a 530 nm LED and GaN channel temperatures were measured using 365 nm LED. Temperatures represent averaged temperature over 0.8 x 0.8  $\mu$ m square in the center of the device. 81

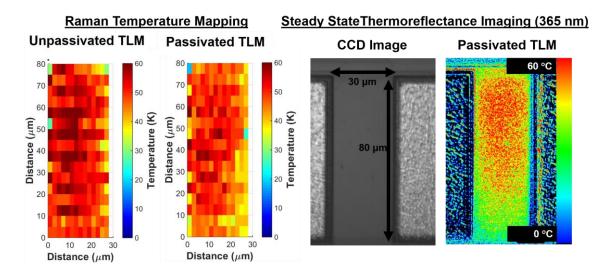

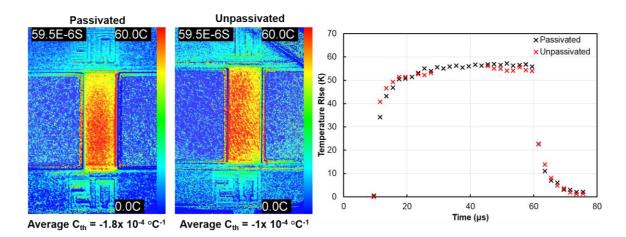

Figure 50: Comparison of steady state temperature mapping of GaN/SiC TLM performed by Raman thermometry and thermoreflectance imaging. Unpassivated device was fabricated by etching the passivation. Both devices were bias at approximately 1.1 W. No steady state thermoreflectance imaging of the unpassivated device could be measured.. 84

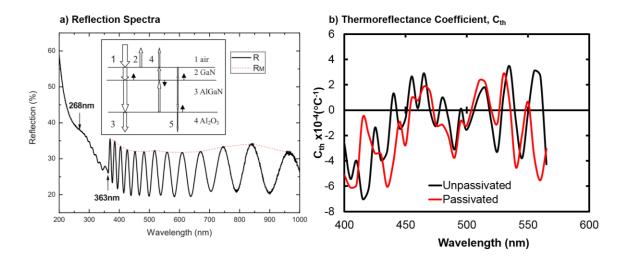

Figure 52: a) Reflection spectrum and envelope of maxima wavelengths of GaN/AlGaN bilayer on Sapphire (adapted from [99]) b) Thermoreflectance coefficient, C<sub>th</sub>, measured at different wavelengths for both GaN/SiC TLMs with and with and without passivation.

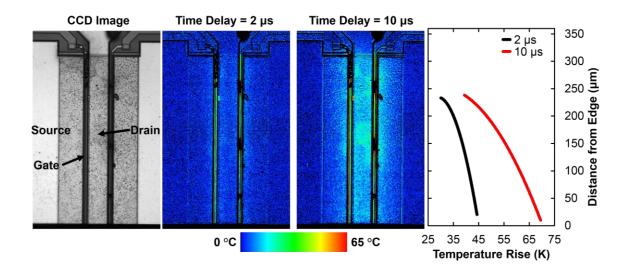

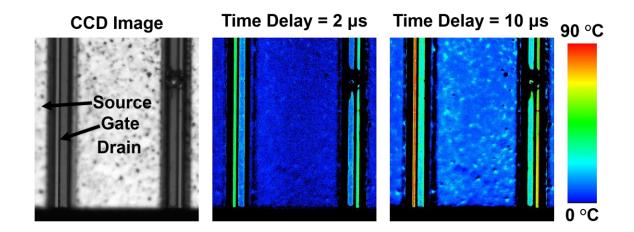

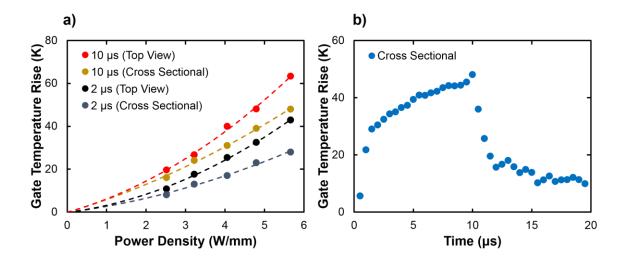

Figure 57: a) Comparison of temperature response with varying power density of gate metal temperature in HEMT measured by TTI from two different orientations: top side and cross sectional side b) Transient temperature profile measured from cross sectional view.

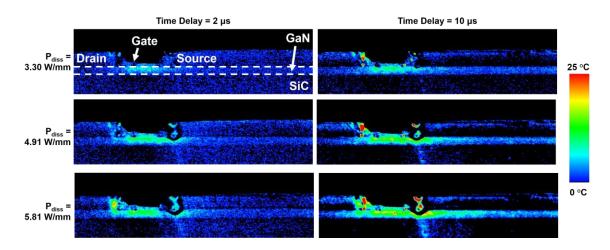

| Figure 58: Cross sectional UV TTI images of a GaN/SiC at varying power densities and time delay. A 365 nm LED was used as an the excitation source                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

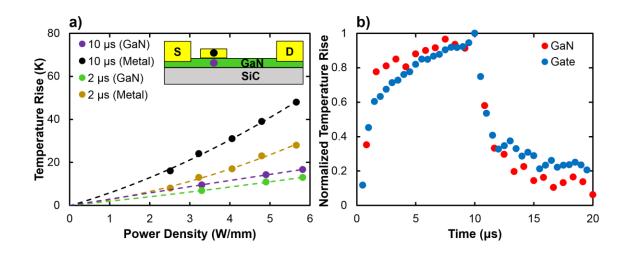

| Figure 59: a) Comparison of temperature response with varying power density of gate metal temperature to GaN channel side b) Transient temperature profile measured from cross sectional view                                                                                                                                                                                                                                                                                            |

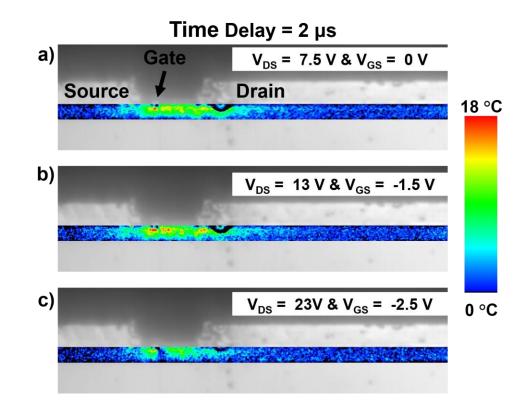

| Figure 60: Bias dependence of temperature distribution across GaN layer in GaN/SiC HEMT                                                                                                                                                                                                                                                                                                                                                                                                  |

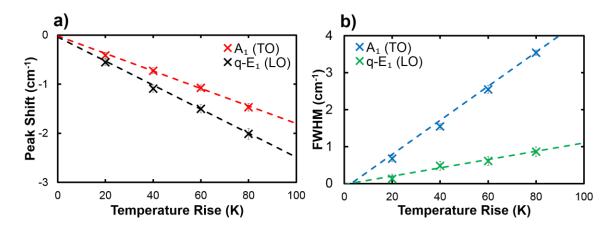

| Figure 61: Temperature dependence of GaN's vibrational modes $A_1$ (TO) and q-E <sub>1</sub> (LO) a) peak position and b) full width half max (FWHM). Thermal stage temperature was varied from 30 °C to 110 °C                                                                                                                                                                                                                                                                          |

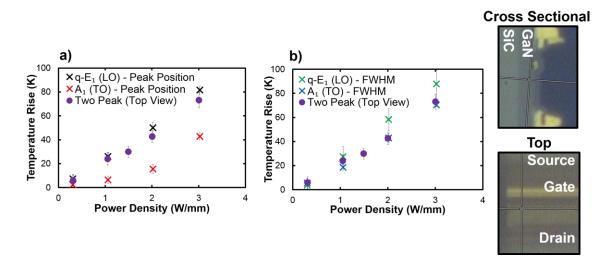

| Figure 62: Comparison of plan view Raman thermometry to cross sectional view thermometry using a) Shift in peak position and b) Shift in FWHM                                                                                                                                                                                                                                                                                                                                            |

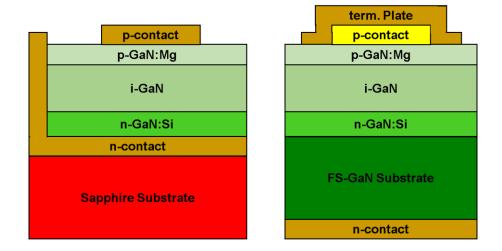

| Figure 63: Schematic of layer of a) GaN/Sapphire PIN Diodes b) Free-Standing (FS) GaN PIN diode                                                                                                                                                                                                                                                                                                                                                                                          |

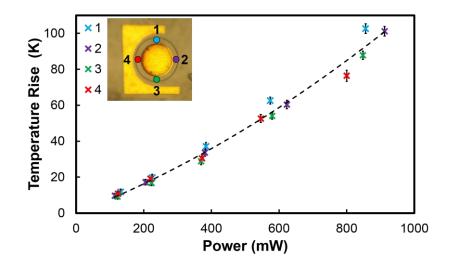

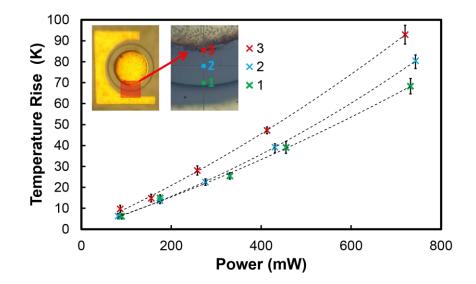

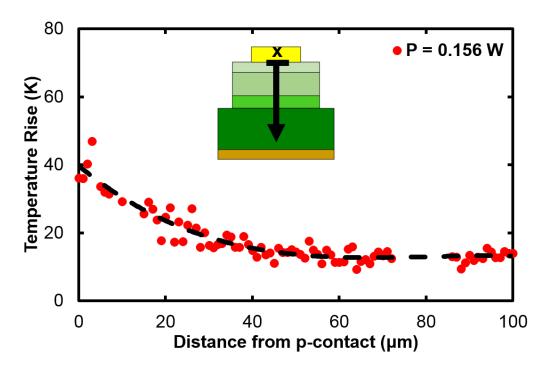

| Figure 64: Temperature rises measured by Raman thermometry of GaN on Sapphire PIN diodes at varying power dissipations. Locations were probed at the edge of the p-type contacts to estimate the temperature rise in the GaN as close as possible to the heat generation. Locations of the four different probed areas are shown in the top left image. 105                                                                                                                              |

| Figure 65: Lateral temperature distribution across GaN on Sapphire PIN diodes at varying power dissipations measured by Raman thermometry. Locations of the three different probed areas are shown in the top left image                                                                                                                                                                                                                                                                 |

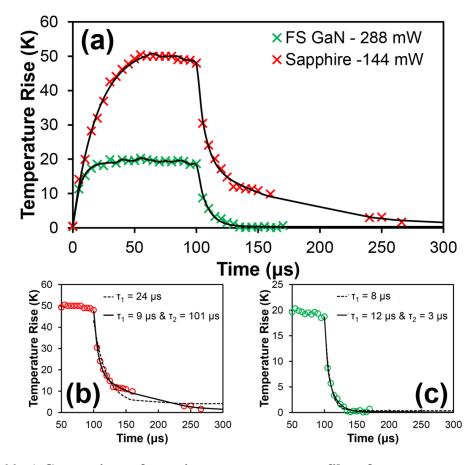

| Figure 66: a) Comparison of transient temperature profiles of p-contact metal of FS-GaN diode (green) and GaN on sapphire diode (red). Devices were biased with 8 V for a period of 400 µs and a duty cycle of 25%. Exponential rise and decay fittings were performed and plotted in solid black lines. Exponential decay fittings to TTI results (circles) using a single time constant (dashed line) and multiple time constants (solid) for b) GaN on Sapphire diode c) FS-GaN diode |

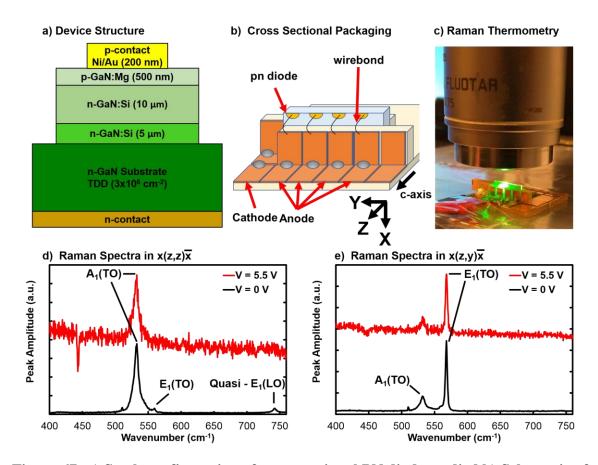

| Figure 67: a) Stack configuration of cross sectional PN diode studied b) Schematic of packaging method for cross section PN diode (figure and package designed by Shiyegoshi Usami) c) Package mounted on Raman thermometry system                                                                                                                                                                                                                                                       |

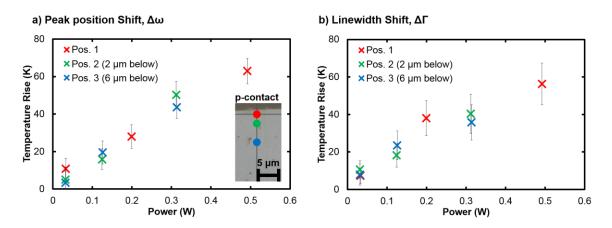

| Figure 68: Temperature distribution in a cross sectional GaN PN diode monitored via a) A <sub>1</sub> (TO) peak shift and b) A <sub>1</sub> (TO) line width shift                                                                                                                                                                                                                                                                                                                        |

| Figure 69: Temperature depth mapping across the GaN PN Diode at a constant power dissipation                                                                                                                                                                                                                                                                                                                                                                                             |

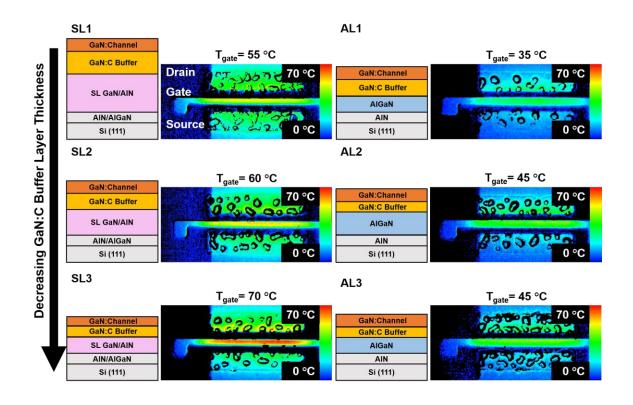

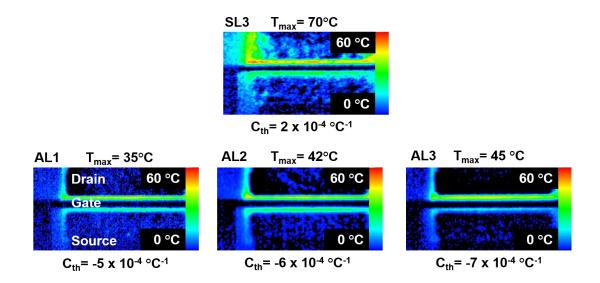

| Figure 70: Comparison of gate metal temperature for three different GaN HEMTs on Superlattice (SL) structures and three additional GaN HEMTs on AlGaN buffer layers (AL). TTI was performed with a 530 nm LED excitation source. Devices were biased at the same power conditions                                                                                                                                                                                                        |

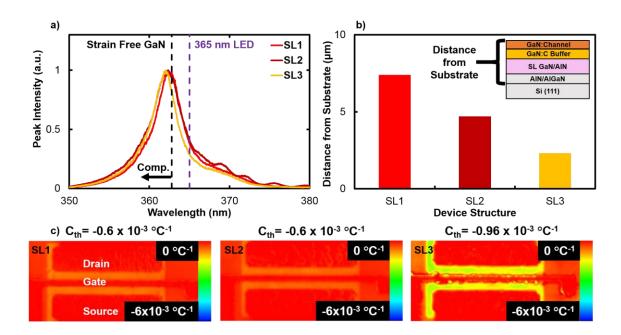

| Figure 71: a) Photoluminescence (PL) spectra of the Superlattice (SL) structured GaN HEMTs b) The distance from the top of the device to the substrate is plotted and the c) thermoreflectance coefficient, $C_{th}$ , for all three devices is mapped                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

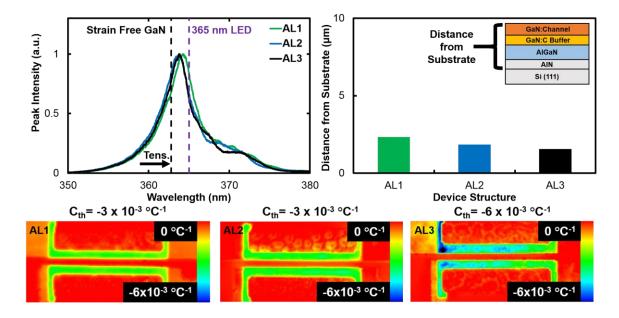

| Figure 72: a) Photoluminescence (PL) spectra of the AlGaN buffer layer (AL) GaN HEMTs b) The distance from the top of the device to the substrate is plotted and the c) thermoreflectance coefficient, $C_{th}$ , for all three devices is mapped                                                                                                               |

| Figure 73: UV TTI Results using 340 nm LED excitation source. No thermoreflectance imaged of the SL1 and SL2 device structures could be obtained. Devices were biased at the same power conditions                                                                                                                                                              |

| Figure 74: Experimental setup for electroluminescence (EL). Timing diagram explained for transient EL analysis                                                                                                                                                                                                                                                  |

| Figure 75: Transient electroluminescence analysis of superlattice (SL) structured GaN HEMT on Si and AlGaN buffer layer (AL) devices. The change in IV characteristics are compared to the number of EL spots and EL intensity                                                                                                                                  |

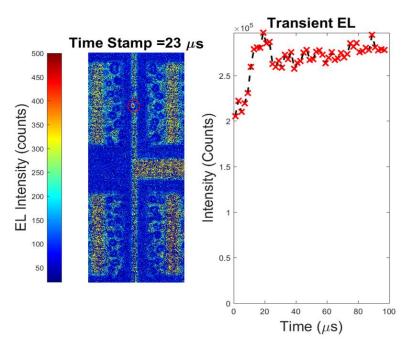

| Figure 76: Improvement of temporal resolution in transient EL analysis when using a near IR 100x objective                                                                                                                                                                                                                                                      |

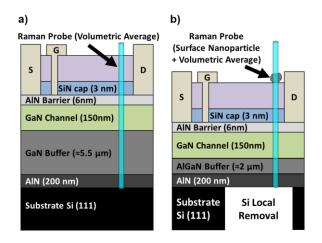

| Figure 77: Cross section of layers of AlGaN/GaN HEMTs with a) 5.5 $\mu$ m thick GaN buffer layer and b) 2 $\mu$ m thin AlGaN buffer layer with silicon locally removed region. A 488 nm laser was used to probe a volumetric average temperature across the device (left) as well as a surface temperature using ZnO/TiO <sub>2</sub> nanoparticles (right)     |

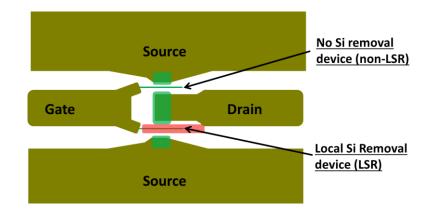

| Figure 78: Position of locally removed silicon on Device. Upper device has no silicon removed between the gate and drain (non-LSR) while the silicon is removed lower device.                                                                                                                                                                                   |

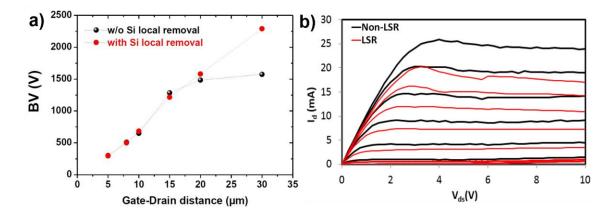

| Figure 79: a) Improvement of breakdown voltage when locally removing the substrate [131] b) Comparison of IV Characteristics of local silicon removed device (red line) and no silicon removed (black line). Drain bias ( $V_{ds}$ ) was swept from 0 to 10 V while the gate bias ( $V_{gs}$ ) was held constant at biases from -1.5 to 1 V in 0.5 V increments |

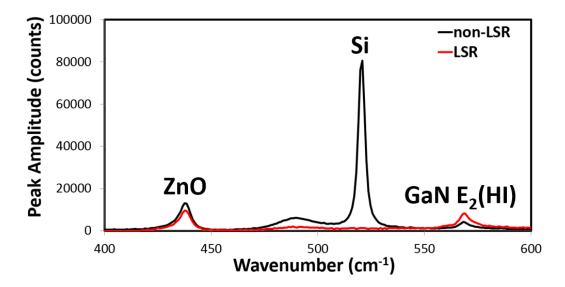

| Figure 80: Example of Raman spectra obtained when probing locally silicon removed channel (LSR) and no silicon removed channel (non-LSR). The Raman peak of ZnO shows the potential of simultaneously probing the surface temperature as well as the average volumetric averaged temperature                                                                    |

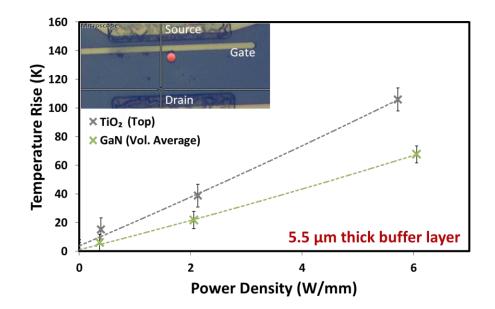

| Figure 81: Thermal response of 5.5 $\mu$ m GaN buffer layer HEMT. Comparison of TiO <sub>2</sub> surface temperatures (grey) and volumetric averaged GaN temperature (green). Image of location where Raman measurements were taken (top-left)                                                                                                                  |

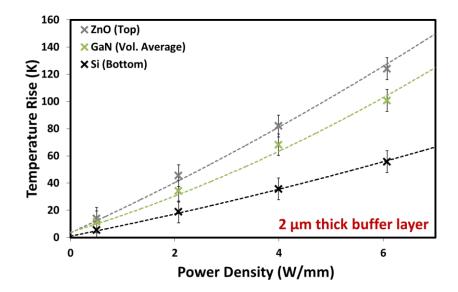

| Figure 82: Thermal response of 2 µm AlGaN buffer layer HEMT. Comparison of ZnO surface temperatures (grey), volumetric averaged GaN temperature (green) and silicon base temperatures (black)                                                                                                                                                                   |

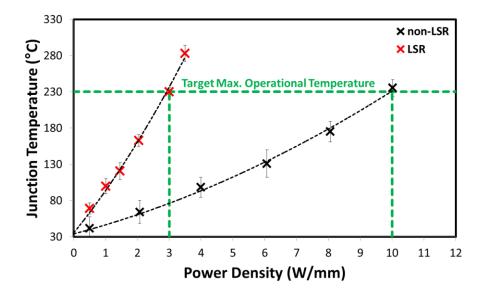

| Figure 83: Comparison of thermal performance between local silicon removed device (red) and non-LSR device (black). Temperature rises were computed using ZnO particles. The non-LSR device shows to achieve a maximum power density of 10 W/mm while LSR device can only perform up to 3 W/mm                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                 |

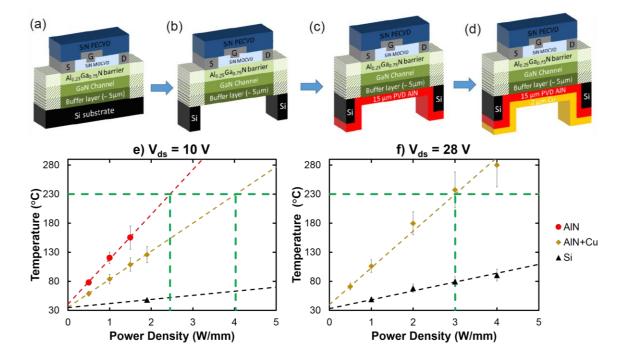

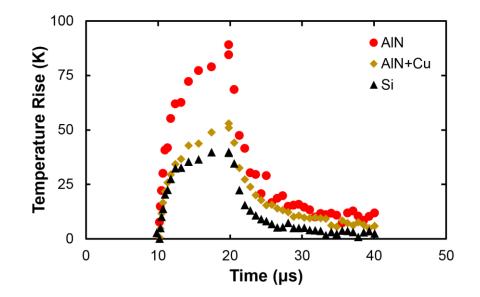

Figure 85: Comparison of TTI maps representing the temperature rise of the metal contacts. A 365 nm LED excitation was used. Devices were pulsed biased for a 100  $\mu$ s period with a 10% duty cycle. A drain bias of 28 V was applied corresponding to a peak power density of 5.6 W/mm. 143

Figure 86: Transient thermal profiles of gate metal temperature rise using UV TTL..... 144

### NOMENCLATURE

- AL AlGaN Buffer Transition Layer

- CCD Charge-coupled Device

- G Gate

- D Drain

- EL Electroluminescence

- FEM Finite Element Method

- GaN Gallium Nitride

- GRT Gate Resistance Thermometry

- HEMT High Electron Mobility Transistor

- IPA Isopropyl Alcohol

- LED Light-emitting Diode

- MTTF Mean Time To Failure

- NA Numerical Aperture

- P<sub>diss</sub> Power Dissipated

- RF Radio Frequency

- S Source

- SL Superlattice Transition Layer

- TLM Transmission Line Measurement

- TSEP Temperature Sensitive Electric Parameters

- TTI Transient Thermoreflectance Imaging

- T<sub>base</sub> Baseplate Temperature

- V<sub>ds</sub> Drain Source Voltage

- $V_{gs}$  Gate Source Voltage

- $\Delta T$  Temperature Rise

#### SUMMARY

Gallium nitride (GaN) based electronics have shown great potential for RF devices and power electronics. Its superior material properties have enabled the fabrication of high frequency and high voltage devices. Under high power operational conditions, significant localized Joule heating occurs near the drain side edge of the gate which can have detrimental effects on the device. The quantification of performance parameters such as the gate junction temperature is thus necessary to accurately assess the device's quality and lifetime. Until now Raman thermometry has shown to be the most accurate method to estimate the junction temperature. This method, however, is limited to a point measurement and sometimes may be limited by its optical access. Furthermore, the ability to monitor the transient temperature rise under pulsed conditions has not been yet fully developed. This thesis presents advanced methods for *in-situ* transient temperature measurements, using gate resistance thermometry, and temperature mappings across GaN based electronics via transient thermoreflectance imaging (TTI). A combination of experimental and numerical analysis is used to achieve this. The methods are applied to lateral HEMTs, vertical PIN diodes and cross sectional HEMTs. The limitations of the current techniques are discussed and contrasted.

#### CHAPTER 1. INTRODUCTION

#### **1.1 Background and Motivation**

Gallium Nitride (GaN) based high electron mobility transistors (HEMTs) have proven to have great potential for RF devices and power electronics [1]. Compared to GaAs based devices, GaN has a higher break down voltage (10 times greater than silicon [2]), higher power densities [3] and lower on-resistance [4]. These attractive features have pushed GaN based electronics to the forefront of developing high power RF electronics for communications such as base stations, satellites, and for radar applications [5]. In the area of power electronics, currently lateral GaN HEMTs are being developed on Si substrates in order to lower the cost for inverters and converters for battery chargers in electronics, industrial motor controllers, and automotive or aircraft applications [6]. For the case of RF and power HEMTs, a similar geometry as shown in Figure 1 is utilized where different parameters such as the electrode spacing, GaN thickness, and buffer layers are varied to maximize performance. However, in both cases, temperature related concerns arise when biasing the device. In normally on HEMTs, at high drain bias and negative gate bias conditions, electrons are accelerated locally between the gate and the drain and dissipate thermal energy in the region of high electric field at the edge of the gate [7]. The thermal energy from electrons is primarily dissipated through the emission of longitudinal optical (LO) phonons [8] which remain in the active region until they convert into other vibrations to be able to transport the Joule heating [9]. This results in significant localized Joule heating near the drain side edge of the gate (Figure 1) which can have detrimental effects on the device such as metal contact degradation [10] and hot electron induced trap

generation [11]. The generated heat is often dissipated by spreading through the GaN layer and diffusing across the interfacial layers required for heteroepitaxial growth and then into the growth substrate [12]. This makes the dissipation of heat very complicated due to the impact of dislocations near the GaN interface on thermal transport [13], the impact of interfacial layers [14], and the device substrate as well as the stresses induced in the device which can also lead to degradation [15].

Figure 1: Hotspot formation in GaN HEMT (adapted from [7]).

In more recent technology developments, the creation of vertical GaN devices are especially appealing for power electronics [16]. The use of vertical devices will allow the creation of efficient high voltage and high power switches which are needed to advance the state of power electronics [17]. While the development of these devices is in their infancy, the understanding of thermal effects in vertical GaN devices is a relatively unexplored topics and necessary due to its potential impact on device reliability. Overall, several methods have been developed to monitor and characterize the lateral temperature distribution across a device. These established methods are suitable for lateral devices such as GaN HEMTs where the path of heat travels horizontally through the device (Figure 2a). The transition to fabricating devices on GaN substrates removes the necessity for buffer layers enabling vertical devices where the path of current flow and heat will travel predominantly in the vertical direction (Figure 2b). New characterization techniques must therefore be established to understand the temperature distribution across vertical devices such as PIN diodes.

Figure 2: Current path in a) Lateral GaN HEMT and b) Vertical GaN HEMTs.

Upon review of previous technology such as Si and GaAs, the thermal time constants associated with the materials were estimated to be on the order of tens of microseconds or longer [18]. In contrast, the thermal time constants associated with GaN have been measured to be on the order of microseconds [19]. Additionally, GaN is typically grown on a Si or SiC substrate with very different thermal diffusivity, unlike Si and GaAs for discrete power FETs. To obtain the full potential out of these devices, understanding and controlling the device's transient thermal dynamics is important to characterizing the nanoscale thermal transport [20, 21]. Accurately predicting the device temperature during biasing is thus necessary for predicting the device's lifetime and reliability [22, 23].

Currently, several thermometry techniques have been developed to estimate the peak temperature (Figure 3) which include IR Thermography [24], Raman Spectroscopy [25], and Gate Resistance Thermometry [26]. However, there are several issues that are seen in the application of accurate thermometry methods to GaN devices, especially lateral and vertical structures in combination with transient operation, which must still be addressed. There is also a desire to understand the vertical temperature gradients in these devices which is often not measured by current techniques [27]. Some of these techniques are reviewed in the next sections and their specific challenges for application to temporal measurements of temperature in GaN devices are explained.

#### **1.2** Review of Thermometry Techniques

#### 1.2.1 IR Thermography

One of the most commonly utilized methods for measuring the temperature in electronics is Infrared (IR) thermography [28-30]. A CCD is used to detect the change in

emitted radiation in the infrared range from a surface. Since IR wavelengths are transparent to most wideband gap materials, the radiation detected will originate from the multiple layers present and thus be a convolution of the temperature rise across all layers and possibly the layers underneath the device (Figure 3). Consequently for GaN electronics, the inability to monitor the change in radiation in the GaN layer has shown to greatly under predict the junction temperature [31, 32]. Performing calibrations to measure the change in radiation of metal is possible in spite of its low emissivity, but due to the technique's low lateral resolution (~10  $\mu$ m), it is very difficult to capture the temperature rise across the gate metal which is closest to the localized Joule heating. In addition to its limited spatial resolution, transient IR thermal imaging has only been achieved on the millisecond restricting itself from being able to monitor the temperature of devices under normal pulsed biasing conditions [33, 34].

#### 1.2.2 Thermo-Sensitive Electrical Parameters

Another method that can be used in the measurement of electrical devices are characteristics of the electrical response that are temperature sensitive. By monitoring the temperature dependence of electrical characteristics in semiconductor devices such as voltage [35] or current [36], thermo-sensitive electrical parameters (TSEP) can be extracted to estimate the device temperature rise. A common example is the use of the forward voltage temperature measurement in LEDs for junction temperature assessment [37]. In general, the advantage of using TSEPs is the minimal addition of equipment required to conduct the measurement, the operation of the electronic device and its response itself is used as a temperature sensor [38]. Requiring no optical access or material deposition, TSEPs provide a low-cost option for estimating the device temperature rise. Specifically,

for HEMTs, several different DC I-V characteristics have been employed to measure temperature. Using Schottky diode forward characteristics, the gate-diode forward resistance and threshold voltage have been found to have a linear temperature dependence [39]. Similarly, monitoring the change in saturated drain current has also shown to be used to estimate the channel temperature (McAlister's method in Figure 4 [40]). While these techniques have been found to give a quick approximation of the channel temperature, significant error has been found to be associated with the degradation of the Schottky barrier during operation and current collapse. Furthermore, when performing DC measurements, the device must be switched briefly off to perform the IV sweeps. This method limits these DC characterization techniques from performing *in-situ* measurements. Further studies, using Pulsed-IV, have shown to shorten these acquisition times to sub-microseconds when attempting to monitor the change in ON-resistance and drain current [41]. These methods, however, still incur and error associated with fast switching and leakage currents.

Figure 4: Comparison of location of TSEPs across GaN HEMT [42].

An electrical method that has shown the potential to estimate the channel temperature rise in HEMTs is the monitoring of the gate end-to-end resistance [43]. Using a 4-point setup, the resistance of the gate metal has shown to be strongly linearly dependent with temperature [44]. Previous work using Gate Resistance Thermometry (GRT) under DC biasing has been applied to single finger AlGaN/GaN-on-Si HEMTs [45] as well as GaAs pHEMTs [46, 47]. It has been suggested that GRT tends to under predict the junction temperature when a large temperature gradient exists across the channel [48]. The effects of bias conditions and device geometry on the accuracy of estimating the channel peak temperature have not yet been fully investigated. Altering the drain bias can impact the electric field distribution and consequently change the area of localized Joule heating. Elongating the gate width may develop larger temperature gradient along the device [49, 50]. Overall, there is a need to verify the accuracy of GRT and understand exactly the origin of the temperature rise it captures. In addition to being able to conduct this technique without having to switch off the device, the technique also has the potential to transiently monitor the channel temperature [51] which could then be used to characterize the device's transient thermal dynamics.

#### 1.2.3 Raman Thermometry

Of the thermal techniques most widely applied to GaN HEMTs is the use of Raman thermography [25, 52, 53]. Raman thermography can be used to estimate the temperature rise in HEMTs by tracking the temperature dependent peak position of Raman active phonon modes [54]. This technique requires specialized equipment including a monochromatic laser, sensitive CCD and most of all it requires optical access to probe crystalline Raman active materials. Due to the fact, the hotspot is predicted to be in the

GaN, Raman Spectroscopy has proven to estimate accurately the temperature change in the GaN. Either the GaN  $E_2$ (high) or  $A_1$ (LO) phonon modes can be used [55]. The phonon frequency, however, is also dependent on stress and thus, errors in temperature measurements can arise due to thermoelastic stresses that occur during operation when using a single phonon mode [56]. To address this problem, it is possible to measure both the shift in the E<sub>2</sub> (high) and A1 (LO) mode peak positions to decouple stress and temperature effects [56]. To avoid self-heating sub band gap lasers are typically used to measure the Raman shift in GaN. The Raman temperature shift therefore measures a volumetric average across the depth (tens of microns) of the GaN layer (Figure 3) with approximately a 1 µm diameter in the lateral direction. If thick GaN layers are present in the device, the Raman volumetric averaged temperature will not capture the temperature gradient across the GaN and will result in under predicting the hotspot temperature. Few studies have shown the applicability of UV Raman to capture the surface temperature rise in the GaN [57, 58] but this method may result in exciting electrons into the channel which can affect the electrical performance of the device. Another drawback to using Raman Spectroscopy is its limitation due to optical access. The 'hot spot' is typically formed underneath and near the edge of the gate. Raman Spectroscopy is not able to directly probe the desired area unless probed from the back side of the device. Employing a back-side measurement, however, removes the possibility of any heat-sinking effect which would be present during normal operation.

While Raman thermometry has proven to have high spatial resolution compared to TSEPs the technique requires long acquisition periods (several minutes) which makes it unfavorable for temperature mappings [59]. Furthermore, regarding its temporal

resolution, Raman thermometry has shown to capability to capture temperature rises on the order of microseconds during continuous pulsed biasing [60]. This fine time resolution permits thermal time constants to be extracted for a device to understand and better model the device's transient thermal dynamics [61]. The ability to capture both a mapping and transient temperature rise across the device however is not possible with Raman. Developing a technique to achieve this will allow for better thermal characterization of devices providing validation when attempting to build accurate numerical models.

Overall, current Raman thermometry studies have shown its suitability for lateral devices where the path of heat follows the current and travels horizontally through the device (Figure 2a). The transition to fabricating devices on GaN substrates removes the necessity for buffer layers enabling vertical devices where the path of heat will travel predominantly in the vertical direction (Figure 2b) [16].

New methods of using Raman thermometry must therefore be established to understand the temperature distribution across vertical devices such as PIN diodes. Recent developments in Raman surface thermometry using nanoparticles such as diamond [62] or  $TiO_2$  [63] permit temperature measurements of non-crystalline surfaces such as the top metal plates of vertical devices to be conducted. While a depth mapping is not possible unless the laser wavelength used is transparent to all the different layers [64], further research is necessary to fully characterize the heat dissipation through vertical devices.

#### 1.2.4 Thermoreflectance

While Raman thermometry and TSEPs have been used frequently over the past decade, no single acquisition temperature mapping technique has yet been fully developed

apart from IR thermometry which the drawbacks have been already discussed. In a manner similar to temperature dependent electrical parameters, temperature dependent optical properties can also be used to quantify temperature in electronics. Recent studies have shown the feasibility of measuring the change in the optical reflectance (thermoreflectance) of the gate metal in HEMTs to monitor the temperature rise in devices [65]. Thermoreflectance is typically used in a pump probe setup known as Time Domain Thermoreflectance (TDTR) in which thermal properties of different materials are extracted [66]. Replacing the photodiode detector with a CCD, thermoreflectance can be used as a thermal imaging tool to monitor the change in thermoreflectance of every pixel in the CCD. To estimate the surface temperature rise,  $\Delta T$ , via Thermoreflectance Transient Imaging (TTI) the correct thermoreflectance coefficient, C<sub>th</sub>, must be applied to the thermally induced optical reflectivity variation detected,  $\Delta R$ , as shown in the equation:

$$\Delta T = C_{th} \times \frac{\Delta R}{R} \tag{1}$$

The  $C_{th}$  is both material and excitation source wavelength dependent [67]. With the addition of passivation layers, the  $C_{th}$  of GaN and the gate metal can change significantly [68, 69] leading to significant errors in the estimated temperature rise via TTI.

The accuracy of this technique is thus based on how well the thermoreflectance coefficient,  $C_{th}$ , of the surface studied can be estimated. Due to thermal expansion effects, using a thermal stage and a thermocouple to determine the thermoreflectance coefficient can introduce error in the measurement of reflectivity. Previous studies have used a combination of electro-thermal modelling and Raman thermometry to adjust the

thermoreflectance coefficient of the metal to match the expected results [65, 70, 71]. While this methodology for validating transient thermoreflectance is accurate, the procedure requires additional complex equipment and long acquisition times. With recent advancements in the development of transient thermoreflectance imaging (TTI) technology, a piezoelectric stage can be used to account for thermal expansion during the extraction the thermoreflectance coefficient [72].

#### **1.3 Research Objectives**

The thermography methods discussed in the previous sections show that several techniques have been employed to thermally characterize GaN HEMTs and vertical GaN electronics. Although some techniques have been extensively studied, there are clear shortcomings in trying to provide both high resolution temporal measurements as well as temperature gradient information that can exist in these structures. Often time, such information is obtained through electro-thermal numerical modeling of the devices with limited validation from experiments [73]. Regarding the monitoring of the gate resistance, until now this technique has not been proven to be used as a true in-situ measurement. The device typically must be briefly switched off to avoid any impact of leakage current on the temperature estimation. Furthermore, the technique has shown the potential to transiently monitor the channel temperature under pulsed biasing but has so far only been proven to obtain a time resolution on the order of milliseconds.

In contrast Raman thermometry, has been shown to be an ideal candidate for DC measurements when there are no optical barriers restricting access to the region next to the hot spot such as a field plate. Some extensions to high temporal resolution transient analysis

have been pioneered [60, 61] but this has not been widely adopted. In addition to optical restriction, Raman thermometry is also limited to a spectral point measurement and requires multiple acquisitions to plot a temperature mapping of a device. Comparing its time-resolved capabilities, it can detect temperature changes in the microsecond regime but requires several accumulations making it a time averaged technique instead of *in-situ* and does not provide a full field analysis of temperature.

To address need for high spatial and temporal resolution thermal measurements, thermoreflectance imaging is a potential solution where a pixel by pixel map is acquired during every measurement. Until now, this technique has only been applied to monitoring the surface temperature rise of unpassivated metal. To find a solution to monitor both the temperature rise in the GaN channel region as well as passivated metal requires a better understanding of the effects of thin film interference on the thermoreflectance coefficient. For vertical temperature gradients, the use of nanoparticles on the surface of GaN devices may allow measurement of the GaN surface temperature along with the average temperature in GaN. Vertical gradients in AlGaN LEDs have shown the potential of doing this [74] but this was done based on tracking the Raman signatures of different materials in the LED. By using Raman active nanoparticles added to the device, it may be possible to perform a similar characterization in both vertical and lateral GaN devices.

The primary research objectives of this work are:

• To develop experimental thermal metrology methods that can accurately measure the insitu transient temperature rise in GaN based electronics under high frequency pulsed biasing and map the temperature distribution across the device both laterally and vertically. • To develop an electrical characterization method to determine the channel temperature in GaN HEMTs by continuous monitoring the gate metal resistance (Gate Resistance Thermometry).

• To implement gate resistance thermometry under RF operating conditions and determine any differences in the device thermal performance when compared to DC operation.

• To determine the applicability of transient thermoreflectance imaging for transient thermal measurements in GaN HEMTs, exploring both the gate metal and GaN channel regions.

• To investigate the use of Raman active nanoparticles for the characterization of vertical temperature gradients in GaN devices such GaN Si HEMTs with thick buffer layers.

• To establish a method to thermally map the Joule heating profile across GaN HEMTs using transient thermoreflectance imaging and show the bias dependence on the Joule heating profile.

• To investigate the effects of thin film interference on thermoreflectance imaging and determine the suitability of this technique for fully passivated devices and devices multiple thin film layers such as superlattices.

#### **1.4 Dissertation Outline**

The present work aims to address the mentioned problems in the following chapters. Chapter 2 discusses the development and verification of gate resistance thermometry (GRT) for both steady state and transient analysis. The errors associated with

the technique are investigated. Chapter 3 highlights the applicability of GRT to GaN/Si HEMTs showing for the first-time gate temperature measurements under RF operating conditions. A direct comparison between the junction temperature achieved via DC and RF operation is presented. Chapter 4 explains the development of advanced optical techniques used for thermometry of GaN based electronics. First the development of Raman active nanoparticles for surface temperature measurements is discussed and its accuracy is verified. Subsequently, a detailed analysis of transient thermoreflectance imaging (TTI) is conducted and its accuracy is verified via GRT. Chapter 5 demonstrates the first ever thermoreflectance imaging of a cross sectional GaN/SiC HEMTs showing the effect of bias conditions on Joule heating. The challenges with measuring the vertical temperature gradient in GaN PIN diodes is also presented. Chapter 6 focuses on quantifying the effects of thin film interference on TTI's accuracy and demonstrates the applicability of TTI to benchmark the thermal performance of GaN/Si HEMTs with strain engineered layers. Chapter 7 discusses the applicability of Raman active nanoparticles and TTI to assess the vertical temperature gradient in GaN/Si HEMTs with thick buffer layers and compare their thermal performance to HEMTs with locally removed Si substrate. The techniques are used to quantify the thermal penalty when removing the substrate and assess the viability of additional thin film layers to improve the thermal performance.

# CHAPTER 2. GATE RESISTANCE THERMOMETRY FOR ALGAN/GAN HEMTS

Content in this chapter (figures and text) adapted from:

1. Pavlidis, G., *et al.*, "Characterization of AlGaN/GaN HEMTs Using Gate Resistance Thermometry," IEEE Transactions on Electron Devices, vol. 64, pp. 78-83, Jan 2017. [26]

#### 2.1 Overview and Approach

This chapter introduces the gate resistance thermometry (GRT) technique developed for GaN HEMTs. This method provides a fast and low-cost technique to determine the average temperature of the gate metal. Previous attempts to use electrical methods for thermometry show significant differences in temperature rises measured with different techniques [48]. However, GRT is the most desirable of the electrical methods, if it can be shown to be accurate. The initial feasibility of this technique has been applied to single finger AlGaN/GaN HEMTs. Particular focus is given on verifying the technique's accuracy technique via other experimental methods (Raman) and numerical simulations. The viability is of this technique under different modes of operation (DC and pulsed biasing) is presented and the errors associated with the measurements are quantified.

#### 2.1.1 Experimental Setup and Calibration

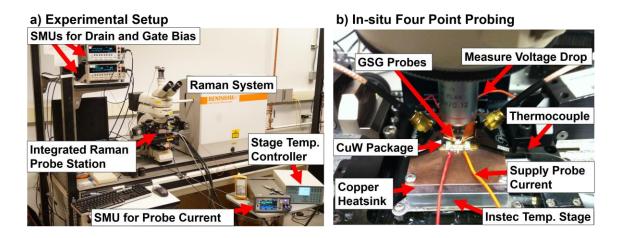

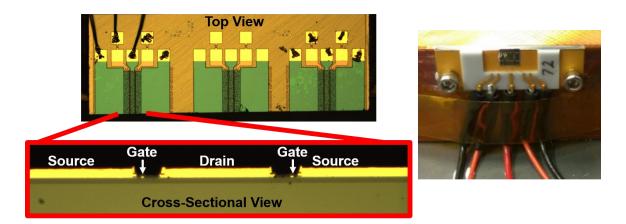

Six finger AlGaN/GaN-on-SiC HEMTs were tested and modelled with two different gate widths, 370  $\mu$ m and 1000  $\mu$ m. As shown in Figure 5, ground-signal-ground probes connected to bias tees with the RF signal routed to 50 Ohm terminations were used to make

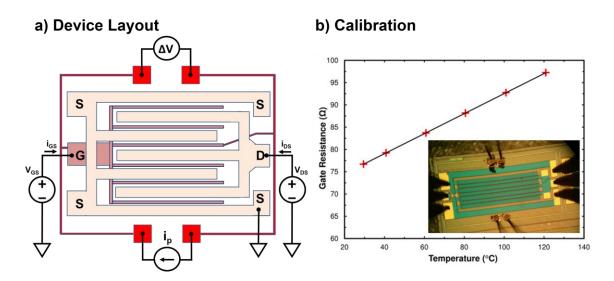

electrical contact with the devices. All power sourcing and electrical measurements were conducted with a Keithley 2410 SMU for biasing the gate and a 2425 SMU for biasing the drain where high current and high voltage are needed. Four terminal sensing was used to measure the gate resistance over a single finger (see Figure 6a). A probe current,  $i_p$ , was supplied through a metal pad to one end of the finger and was returned directly to the SMU. The voltage drop,  $\Delta V$ , was then measured across the finger by the additional two pads. All measurements were conducted using a Keithley SMU controlled digitally by the software Test Script Builder.

Figure 5: a) Overview of experimental setup designed for the verification of Gate Resistance Thermometry (GRT) b) Detailed description of different parts used to perform GRT simultaneously to biasing the device.

To estimate the uncertainty of the measurement, an average of 50 measurements over a time period of 3.4 seconds was conducted at each powering condition. A calibration was performed prior to measuring the Gate Resistance to ensure a consistent relationship between gate resistance and temperature for each device. Resistance was measured at fixed temperatures between 30 - 120 °C which was controlled by a thermal stage (Instec HCP302 shown in Figure 5b). Calibrations were performed on four different devices for both gate widths. The TCR was estimated to be in between 0.28-0.31 %/K for both devices. To obtain a more accurate representation of the device temperature, a thermocouple was placed below the Stratedge LPA580274 CuW package where the device was attached using Ag-epoxy (H20E). Linear regression was applied to determine the slope between resistance and temperature that was then used to estimate the gate temperature (see Figure 6b). Uncertainty analysis was performed to estimate the error of the slope.

Figure 6: a) Device layout and configuration of four terminal sensing to measure the gate resistance over a single finger for 6 finger devices with gate widths of 370  $\mu$ m and 1000  $\mu$ m. b) Linear calibration fit used to measure the thermal response of the gate metal resistance of a 6 x 1000  $\mu$ m device for a temperature range of 30 to 120 °C.

## 2.1.2 Experimental Validation

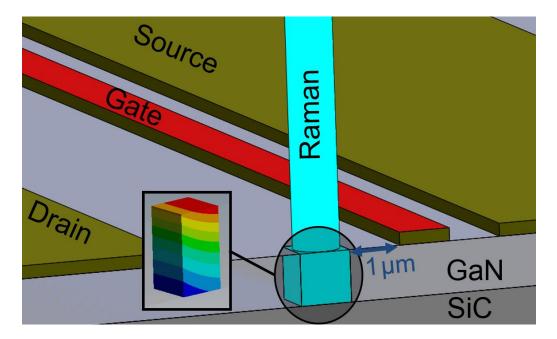

Micro-Raman spectroscopy was performed using a Renishaw InVia Raman microscope with a 0.25 m focal length spectrometer and a 488 nm laser as the excitation source. The laser beam diameter was approximated to be 1  $\mu$ m. The use of sub-band gap laser wavelengths prevented localized heating of the GaN and TiO<sub>2</sub> by laser light absorption. A charge coupled device (CCD) camera was integrated into the system to

image the collected Raman signals. Experiments were carried out with the laser light perpendicular to the basal plane of GaN in a  $180^{\circ}$  backscattering configuration and unpolarized detection with a 100X objective. A 3000 l/mm grating was used with a slit width of 65 µm for all measurements. To estimate the uncertainty in the temperature measurements with 95% confidence intervals, an average of at least 20 measurements was made at all power conditions.

The measurement steps for the Raman thermometry measurements were done with the temperature controlled stage set at 303 K. Silicone thermal grease was used between the backside of the package and the thermal stage to reduce the interface thermal resistance. The resulting Raman spectrum was analyzed with a Gaussian-Lorentzian (Voigt) fit to find peak parameters of the Stokes peaks of GaN and TiO<sub>2</sub>. For GaN, the temperature of the devices was estimated using the two-peak fit method [56]. For TiO<sub>2</sub>, the  $E_g$  phonon frequency was measured at fixed temperatures between 303 and 393 K. Raman measurements were taken at the middle of the center finger with the center of the Raman laser 1 µm away from the gate edge as shown in Figure 7 (edge of the beam 0.5 µm away from gate). For a direct comparison between the two experimental techniques, the gate resistance was recorded simultaneously with the Raman measurements at various power densities.

Figure 7: Schematic of layer configuration implemented in the 3D FEM thermal model including the SiC substrate. The gate resistance probed area is highlighted in red while the GaN probed volume is circled in black.

# 2.1.3 Numerical Validation

A 3D finite element model was developed using ANSYS to model the heat dissipation throughout the devices. A schematic of the different material layers included in the model is shown in Figure 7. Applying quarter symmetry, the material properties of the different layers including temperature dependent thermal conductivities were taken from [75] and shown in Table. To ensure close approximation of the device structure, channel dimensions were determined from optical microscope images. The gate-to-drain spacing was measured to be 4.5  $\mu$ m while the gate-to-source spacing was set to 1  $\mu$ m. The gate was modelled as a rectangle with nominal length of 1  $\mu$ m.

| Material      | Thermal Conductivity (W/m-K)               |  |  |

|---------------|--------------------------------------------|--|--|

| GaN           | $150 * \left(\frac{T}{300}\right)^{-1.4}$  |  |  |

| SiC           | $387 * \left(\frac{T}{293}\right)^{-1.49}$ |  |  |

| Cu            | 387                                        |  |  |

| CuW           | $204 - 0.0251 * T - 0.0000762 * T^2$       |  |  |

| AuSn Solder   | 57                                         |  |  |

| Thermal Paste | 0.757                                      |  |  |

Table 1 Temperature dependent thermal conductivities applied to initial model.Taken from [75].

Under high drain bias operation conditions with a negative gate bias such that the device is nearly pinched off, the temperature distribution across the channel from source to drain is known to be asymmetric due to localized Joule heating mostly occurring in the depletion region and requiring the need for electro-thermal simulations [9]. In contrast, if the gate is opened fully so that the channel is not significantly modulated by the additional gate bias, Joule heating will then be much more uniform over the entire channel from source to drain without a significant depletion region [76]. Even though the devices had a T-gate configuration, the gate metal layers were modelled as a rectangle with nominal length of 1  $\mu$ m. Since the model was created to simulate fully open channel conditions, the temperature distribution across the gate length will be parabolic and therefore the effect of the gate structure will be minimal. Based on the channel length, constant heat fluxes were applied to an area of 6.5  $\mu$ m by the gate width. The bottom face of the CuW package was

constrained to 303 K to simulate a constant thermal stage temperature applied during the experiments. All other boundaries were assumed adiabatic.

Since GRT provides a surface average temperature while Raman provides a volume average temperature, different analysis regions were defined in the model in order to extract temperatures that could be compared to the experimental results obtained from Raman and GRT (Figure 7). When performing Raman Spectroscopy, a volumetric average across the depth of the GaN layer (1.8  $\mu$ m) is probed with an approximated laser diameter of 1  $\mu$ m. A cube of 1 x 1 x 1.8  $\mu$ m was therefore created to model the Raman probed temperature. The gate resistance represented an average over the full cross section of the gate metallization and was thus modelled as a 1  $\mu$ m long rectangle across the gate width.

The packaging of the devices required the addition of multiple layers other than the GaN and SiC layer. This includes the silver epoxy material, thermal paste, CuW package and mounting plate. To avoid rough approximations of these layers, an effective thermal resistance was applied below the SiC layer to represent the effect of combining these layers. This value was determined by varying the effective thermal resistance and matching the measured and calculated gate resistance and Raman temperatures for a single operating condition. This value was then held constant for all other predictions of temperature versus power response of the device. The passivation layer was not included in the model. The minimum difference between the average temperatures measured by the TiO<sub>2</sub> particles to the gate resistance temperatures, showed an insignificant temperature gradient across the passivation layer.

# 2.2 Steady State Analysis

#### 2.2.1 Fully Open Channel

The devices were operated under fully open channel conditions by applying a positive gate bias between 1 and 2 volts. To ensure a fully open channel, the gate current,  $I_{gs}$ , was maintained at approximately 0.12 mA for each power density. The experimental results obtained for the 370 µm gate width device are shown in Figure 8 and are compared to the numerical model.

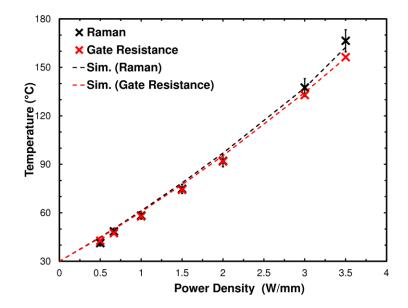

Figure 8: Comparison of Raman (Black) and GRT (Red) measured temperatures to respective FEM probed temperatures for 6 x 370 µm devices at power densities up to 3.5 W/mm.

Good agreement was shown between the GRT and Raman data for power densities from 0.5 - 3.5 W/mm. The close agreement of the numerical and experimental data at different power densities validates the implementation of the effective resistance. The data also shows that for the majority of the power densities studied, the GRT and Raman values are very similar, in spite of one being a volume average and one being a surface average temperature. At higher power densities (e.g., greater than 3 W/mm), the Raman temperature is shown to be higher than the GRT measured temperature. A maximum difference of 10  $^{\circ}$ C (6  $^{\circ}$ ) is shown for the power densities tested, and this is expected to increase as the power density increases.

The numerical solutions exhibit a similar trend with the Raman numerical temperature shown to be 2 °C higher than the GRT numerical solution. As shown in Figure 7, the location of the probed Raman temperature and the GRT temperature can explain the higher temperatures obtained by Raman. A constant heat flux applied across the channel creates a parabolic temperature profile between the source and the drain and between the ends of the device channel (Figure 9).

Figure 9: FEM temperature distribution from the center of the gate finger to the edge of the 6 x 370  $\mu$ m device. The temperature difference at 3 W/mm (blue) results in a larger temperature difference,  $\Delta$ T, when compared to the 2 W/mm (gold) powering condition.