# **EFFICIENT SIMULATION TECHNIQUES FOR**

# LARGE-SCALE APPLICATIONS

A Dissertation Presented to The Academic Faculty

By

Jen-Cheng Huang

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology August 2015

Copyright © 2015 by Jen-Cheng Huang

# EFFICIENT SIMULATION TECHNIQUES FOR LARGE-SCALE APPLICATIONS

Approved by:

Dr. Hyesoon Kim, Advisor Associate Professor, School of Computer Science Georgia Institute of Technology

Dr. Moinuddin K. Qureshi Associate Professor, School of ECE Georgia Institute of Technology

Dr. Sudhakar Yalamanchili Professor, School of ECE Georgia Institute of Technology Dr. Hsien-Hsin S. Lee Adjunct Professor, School of ECE Georgia Institute of Technology

Dr. Karsten Schwan Professor, School of Computer Science Georgia Institute of Technology

Date Approved: June 2015

Dedicated to my parents

# ACKNOWLEDGMENTS

With the support and help from my mentors and friends, I finally finished my Ph.D. journey. I would like to take this opportunity to thank them.

First of all, I thank my advisor, Prof. Hyesoon Kim. In the summer of 2012, she provided guidance me when I was desperately looking for help. Over these years, she has provided valuable advice on all aspects of a research project: identifying a research problem, forming my ideas, writing a conference paper, making presentation slides, and so on. Her advice was always sharp and directly pointed out the deficiencies I needed to improve. She kept helping me improve my research skills. Honestly, I could not have finished my dissertation without her advice. Her attitude at work always motivates me. To her, she is very persistent, focused, and hard working. To me, she is very caring. She gave me the freedom to work on the research projects that I am interested in. Whenever I was in trouble, she is generous with her help. All the things that I learned from her will continue to influence me for the rest of my life.

I thank my former advisor Prof. Hsien-Hsin S. Lee for introducing me to the computer architecture field. I am grateful that he guided me through the early years of my graduate study. I would like to thank my mentors from HP Labs: Matteo Monchiero and Yoshio Turner. Even after my internship, they still spent time talking with me every week to help me finish the project. Without their guidance, I would never have been able to finish my first research project. I thank my mentor Ching-Tsun Chou from Intel Labs. He has provided a lot of technical help so that I could finish my intern project on time. I would also like to thank all my committee members: Prof. Hyesoon Kim, Prof. Hsien-Hsin S. Lee, Prof. Moinuddin K. Qureshi , Prof. Sudhakar Yalamanchili, and Prof. Karsten Schwan for serving on my committee and providing me valuable comments to improve my dissertation.

I thank my colleagues from HPArch: Nagesh Lakshminarayana, Sunpyo Hong, Jaekyu Lee, Pranith Kumar, Jaewoong Sim, Dilan Manatunga, Joo Hwan Lee, Hyojong Kim, Nimit Nigania, Prasun Gera, Lifeng Nai, and Ramyad Hadidi for their feedback on improving my papers and the discussions during the weekly meetings. Lifeng Nai, Joo Hwan Lee, and Hyojong Kim, coauthored the papers with me and helped me develop research ideas. Dilan Manatunga helped me improve the writing quality of my papers and introduced me to the world of anime. Nagesh Lakshminarayana, Prasun Gera, and Pranith Kumar provided me much technical support on simulation and system issues. Jaewoong Sim challenged me with insightful feedback to improve my projects. I thank my colleagues from MARS: Sungkap Yeo, Mohammad Hossain, Tzu-Wei Lin, Guanhao Shen, Dong Hyuk Woo, Dean Lewis, Eric Fontaine, Manoj Athreya, Andrei Bersatti, Nak Hee Seong. I thank Sungkap Yeo and Mohammad Hossain for letting me co-author their work. Sungkap and I joined the lab at the same time. I am grateful for his encouragement over the years. I thank Dong Hyuk Woo gave me research suggestions and a valuable opportunity to intern in the Intel lab.

I thank all my friends who have helped me over these years. You-Chi Cheng, Hwa-You Hsu and Chieh-Yu Lee are my closest friends in Atlanta. I will not forget the happy times we had hiking and grocery shopping. I would like to thank Chi-Ti Hsieh, Ping-Chang Shih, Yu-Hsien Hsu and Cheng-Lin Tsao who helped me resolve many issues during my early years in the graduate school. I thank Yuejian Xie, Tzu-Han Hung and Chun-Ming Chen for providing numerous suggestions on research and life issues. I thank Xinwei Chen and He Xiao for spending many coffee breaks with me. I thank Tricia Grindel for helping me edit my papers to improve the readability.

Finally, I would like to thank my parents: Chiung-Tang Huang and Hsiu-Min Weng. They have never given me any pressure to finish the degree and always let me choose the path that I wanted. My younger brother, Yu-Cheng Huang, has shared many life tips in the U.S. with me. My girlfriend, Hsiao-Ling Lin, has been supporting me and gone through many ups and downs with me. They always believe in me and give me unconditional love and support for which I am very grateful.

# **TABLE OF CONTENTS**

| ACKNOWLEDGMENTS |                                                                       |     |  |  |

|-----------------|-----------------------------------------------------------------------|-----|--|--|

| LIST OF         | TABLES                                                                | ix  |  |  |

| LIST OF         | FIGURES                                                               | X   |  |  |

| SUMMA           | <b>RY</b>                                                             | iii |  |  |

| СНАРТЕ          | <b>ER 1</b> INTRODUCTION                                              | 1   |  |  |

| 1.1             | The Problem: Reducing the simulation time of large-scale applications | 1   |  |  |

| 1.2             | The Solution: Domain-specific simulation mechanisms                   | 3   |  |  |

|                 | 1.2.1 Sampling technique for GPGPU kernels                            | 3   |  |  |

|                 | 1.2.2 Hybrid modeling technique for GPGPU kernels                     | 3   |  |  |

|                 | 1.2.3 Sampling technique for data analytic workloads                  | 4   |  |  |

| 1.3             | Thesis Statement                                                      | 4   |  |  |

| 1.4             | Organization of This Thesis                                           | 5   |  |  |

| СНАРТЕ          | <b>CR 2 RELATED WORK</b>                                              | 6   |  |  |

| 2.1             | Simulation Sampling                                                   | 6   |  |  |

|                 | 2.1.1 Statistical Sampling                                            | 6   |  |  |

|                 | 2.1.2 Profile-driven Sampling                                         | 7   |  |  |

| 2.2             | Statistical Simulation                                                | 9   |  |  |

| 2.3             | Parallel Simulation                                                   | 10  |  |  |

| 2.4             | Analytical Modeling                                                   | 11  |  |  |

|                 | 2.4.1 Analytical Models of Single-threaded Cores                      | 11  |  |  |

|                 | 2.4.2 Analytical Models of Multi-threaded Cores                       | 12  |  |  |

| 2.5             | Input Set Selection                                                   | 14  |  |  |

| СНАРТЕ          | <b>CR 3</b> TBPOINT: REDUCING SIMULATION TIME FOR LARGE-SCA           | LE  |  |  |

|                 | GPGPU KERNELS                                                         | 15  |  |  |

| 3.1             | Introduction                                                          | 15  |  |  |

| 3.2             | Background and Motivation                                             | 16  |  |  |

|                 | 3.2.1 Target Platform and Terminology                                 | 16  |  |  |

|                 | 3.2.2 Motivation                                                      | 17  |  |  |

| 3.3             | Inter-Launch Sampling                                                 | 20  |  |  |

| 3.4             | Intra-Launch Sampling                                                 | 23  |  |  |

|                 |                                                                       | 24  |  |  |

|                 | 3.4.2 Implementation of Intra-Launch Sampling                         | 27  |  |  |

|                 | 3.4.3 Homogeneous Region Identification                               | 27  |  |  |

|                 | 3.4.4 Homogeneous Region Sampling                                     | 31  |  |  |

| 3.5             |                                                                       | 33  |  |  |

|                 | 3.5.1 Evaluation Configurations                                       | 33  |  |  |

|     |      | 3.5.2  | Comparisons                                       | 36 |

|-----|------|--------|---------------------------------------------------|----|

|     |      | 3.5.3  | Sensitivity Analysis                              | 38 |

|     | 3.6  | Sumn   | nary                                              | 39 |

| CHA | APTH | ER 4   | GPUMECH: GPU PERFORMANCE MODELING TECHNIQU        | E  |

|     |      |        | BASED ON INTERVAL ANALYSIS                        | 40 |

|     | 4.1  | Introd | luction                                           | 40 |

|     | 4.2  | Backg  | ground and Motivation                             | 42 |

|     |      | 4.2.1  | Motivation                                        | 42 |

|     | 4.3  | Single | e-Warp Model                                      | 45 |

|     |      | 4.3.1  | GPUMech Overview                                  | 45 |

|     |      | 4.3.2  | Interval Algorithm                                | 46 |

|     |      | 4.3.3  | Selecting Representative Warp                     | 47 |

|     | 4.4  | Multi  | -Warp Model                                       | 48 |

|     |      | 4.4.1  | Modeling Multithreading                           | 48 |

|     |      | 4.4.2  | Modeling Resource Contention                      | 53 |

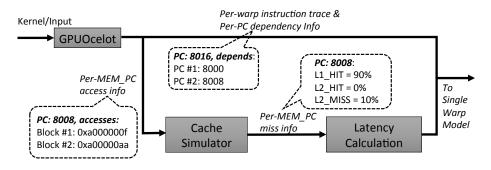

|     | 4.5  | Input  | Collector                                         | 57 |

|     |      | 4.5.1  | Overview                                          | 57 |

|     |      | 4.5.2  | Instruction Latency per PC                        | 58 |

|     | 4.6  | Evalu  | ation                                             | 59 |

|     |      | 4.6.1  | Methodology                                       |    |

|     |      | 4.6.2  | Model Accuracies of Different Scheduling Policies |    |

|     |      | 4.6.3  | Varying Hardware Configurations                   |    |

|     |      | 4.6.4  | Accuracy of Cache Simulation                      |    |

|     |      | 4.6.5  | Discussions on Timing Overhead                    |    |

|     | 4.7  | Use C  | Case                                              | 66 |

|     |      | 4.7.1  | Identify the Scaling Bottlenecks                  |    |

|     | 4.8  | Sumn   | nary                                              | 69 |

| CHA | APTH | ER 5   | SIMPROF: A SAMPLING FRAMEWORK FOR DATA ANA        |    |

|     |      |        | LYTIC WORKLOADS                                   |    |

|     |      |        | luction                                           |    |

|     | 5.2  | •      | ground and Motivation                             | 73 |

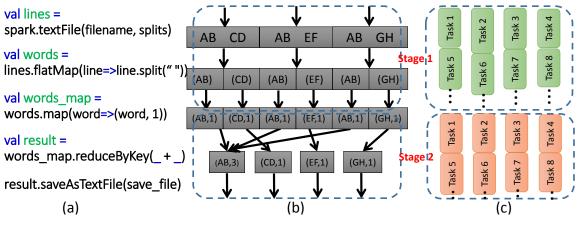

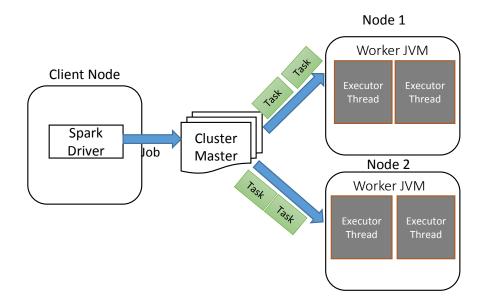

|     |      | 5.2.1  | Apache Spark                                      |    |

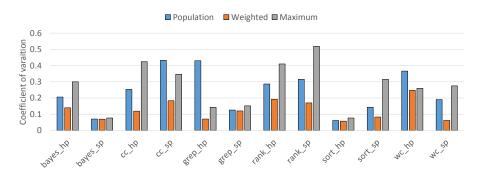

|     |      | 5.2.2  | Phase Behaviors                                   | 75 |

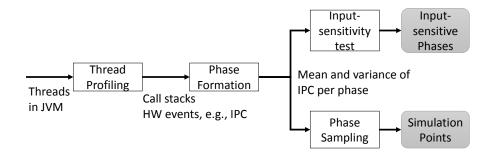

|     | 5.3  | SimP   |                                                   | 77 |

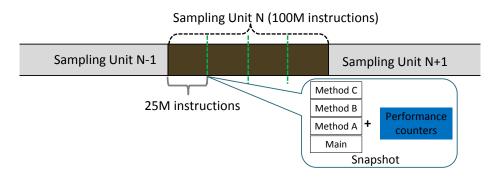

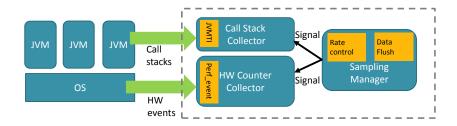

|     |      | 5.3.1  | Thread Profiling                                  | 78 |

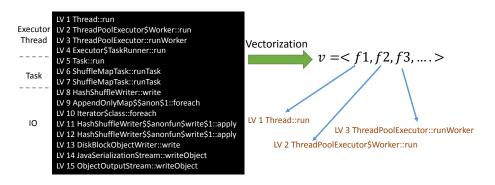

|     |      | 5.3.2  | Phase Formation                                   | 79 |

|     |      | 5.3.3  | Phase Sampling                                    | 83 |

|     |      | 5.3.4  | Input Sensitivity Test                            | 85 |

|     | 5.4  | Evalu  |                                                   | 87 |

|     |      | 5.4.1  | Platform and Benchmarks                           | 87 |

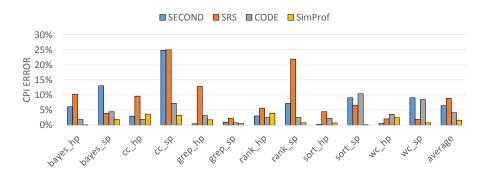

|     |      | 5.4.2  | Accuracy and Sample Size Results                  | 88 |

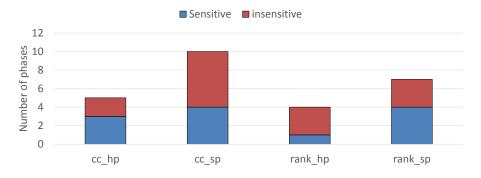

|     |      | 5.4.3  | Phase Analysis                                    |    |

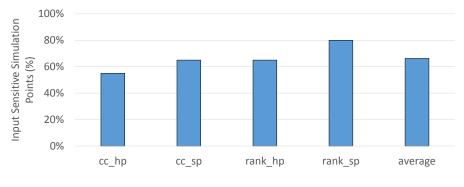

|     |      | 5.4.4  | Input Sensitivity Analysis                        | 92 |

| 5.4.6      | Framework Comparisons9Architecture-level Analysis9ary10 | 6 |

|------------|---------------------------------------------------------|---|

| CHAPTER 6  | CONCLUSION                                              | 3 |

| REFERENCES |                                                         | 5 |

# LIST OF TABLES

| Table 1  | Comparison of GPGPU execution time and Simulation Time. GPU time is for NVIDIA Quadro 6000. | 16 |

|----------|---------------------------------------------------------------------------------------------|----|

| Table 2  | Comparisons of profiling-based sampling techniques                                          | 19 |

| Table 3  | Example of Homogeneous Region Table                                                         | 30 |

| Table 4  | IPCs of Inter-Launch and Intra-Launch Sampling                                              | 32 |

| Table 5  | Simulation Configuration.                                                                   | 33 |

| Table 6  | Evaluated Benchmarks (Type I: irregular kernel, Type II: regular kernel) .                  | 34 |

| Table 7  | Simulation Configuration.                                                                   | 59 |

| Table 8  | Evaluated models.                                                                           | 60 |

| Table 9  | Stall types of CPI stacks.                                                                  | 67 |

| Table 10 | Evaluated benchmarks                                                                        | 87 |

| Table 11 | Evaluated Inputs                                                                            | 93 |

# LIST OF FIGURES

| Figure 1  | Simpoint overview [1]                                                                                                                                                                                                                                                                                                                                       | 7                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

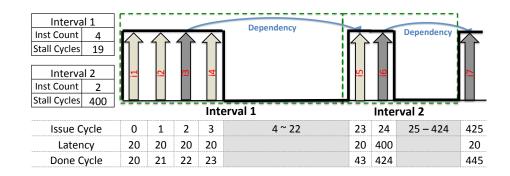

| Figure 2  | Example of interval analysis. (i: instruction.)                                                                                                                                                                                                                                                                                                             | 12                                          |

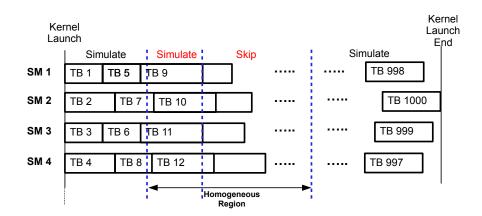

| Figure 3  | GPGPU Simulation Overview                                                                                                                                                                                                                                                                                                                                   | 17                                          |

| Figure 4  | Procedure of Inter-Launch Sampling.                                                                                                                                                                                                                                                                                                                         | 20                                          |

| Figure 5  | Intra-Launch Sampling                                                                                                                                                                                                                                                                                                                                       | 23                                          |

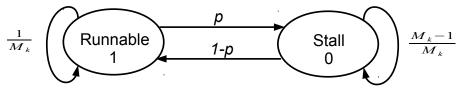

| Figure 6  | The State Diagram of a Warp. $p = \frac{mem\_insts}{total\_insts}, M_k \sim N(\mu, \sigma^2) \dots \dots \dots$                                                                                                                                                                                                                                             | 24                                          |

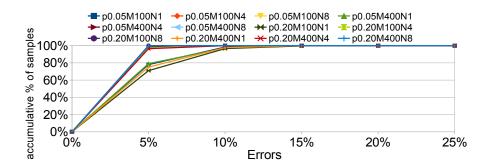

| Figure 7  | IPC Variation (Each legend shows the $p$ , $M$ , and $N$ values. For example, $p0.05M100N4$ means $p = 0.05$ , $M = 100$ and $N = 4$ )                                                                                                                                                                                                                      | 26                                          |

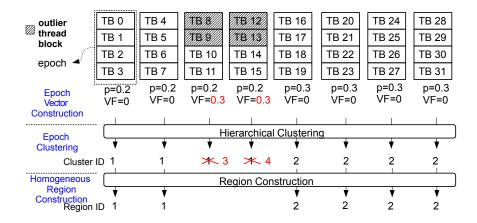

| Figure 8  | Example of Homogeneous Region Identification                                                                                                                                                                                                                                                                                                                | 28                                          |

| Figure 9  | Example of Homogeneous Region Sampling. SU = sampling unit ID.<br>RID = homogeneous region ID.                                                                                                                                                                                                                                                              | 30                                          |

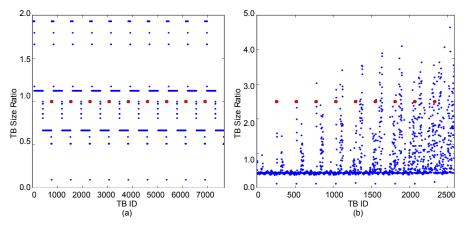

| Figure 10 | Different Kernel Types. (a) Regular. (b) Irregular kernel. A red dot in-<br>dicates the start of a kernel launch while a blue dot indicates a thread<br>block. Thread block size ratio is the thread block size, which is the num-<br>ber of thread instructions in a thread block, normalized by the average<br>thread block size across all thread blocks | 34                                          |

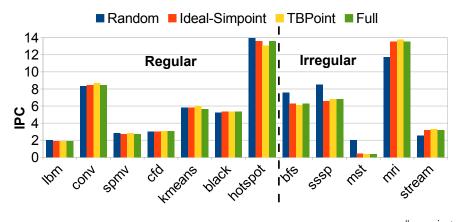

| Figure 11 | Overall IPC. (The overall IPC is defined as $\sum_{k \in SMS} \frac{\#warp\_insts_k}{\#cycles_k}$ )                                                                                                                                                                                                                                                         | 35                                          |

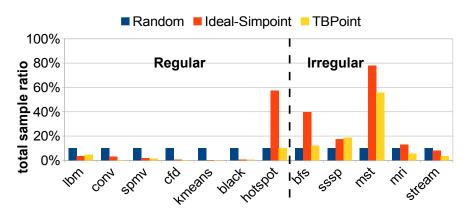

| Figure 12 | Total Sample Size (Ratio). (The total sample size is defined as $\sum_{k \in SMS} \frac{\#_{simulat}}{\#_{WA}}$                                                                                                                                                                                                                                             | $\frac{ed_warp_insts_k}{arp_insts_k}$ ). 35 |

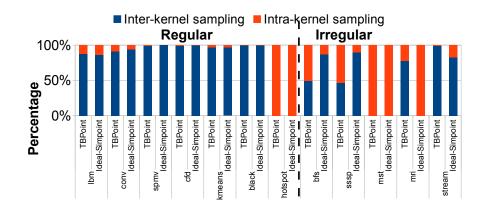

| Figure 13 | Breakdown of the Relative Percentage of Skipped Instructions from Inter-<br>Launch and Intra-Launch Sampling.                                                                                                                                                                                                                                               | 36                                          |

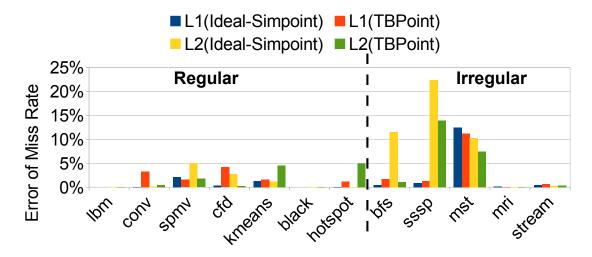

| Figure 14 | Errors of L1/L2 cache miss rates.                                                                                                                                                                                                                                                                                                                           | 37                                          |

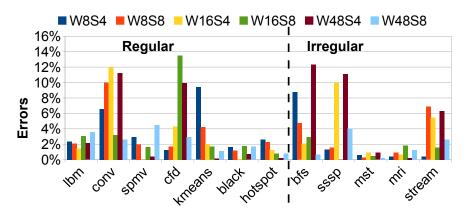

| Figure 15 | Sampling Errors of Different Hardware Configurations. W is the number of warps in an SM, and S is the number of SMs                                                                                                                                                                                                                                         | 38                                          |

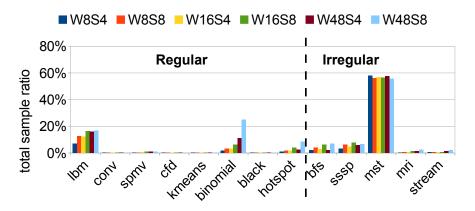

| Figure 16 | Total Sample Sizes (Ratios) of Different Hardware Configurations                                                                                                                                                                                                                                                                                            | 38                                          |

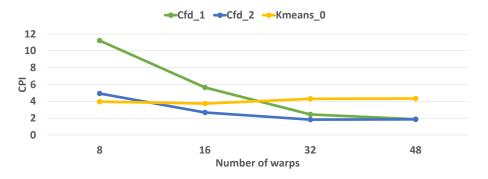

| Figure 17 | The CPIs of different number of warps in an SM                                                                                                                                                                                                                                                                                                              | 41                                          |

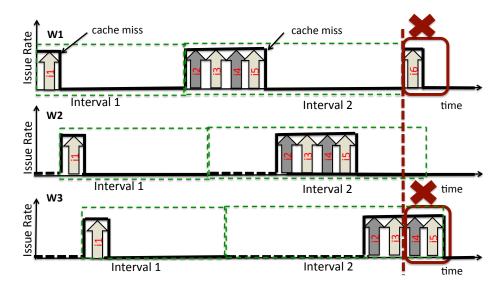

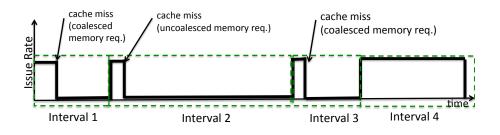

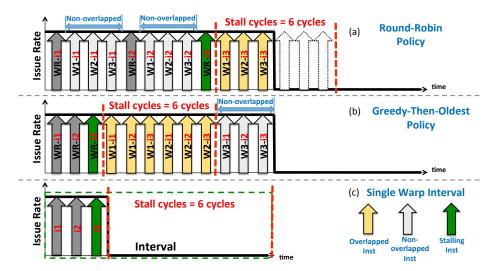

| Figure 18 | The case of interval analysis with multiple warps. A green box represents an interval. The red boxes contain the instructions that do not overlap with the stall cycles. (W: warp, i: instruction.)                                                                                                                                                         | 43                                          |

| Figure 19 | Interval analysis with different degrees of memory divergences                                                                                                                                                                                                                                                                                              | 44                                          |

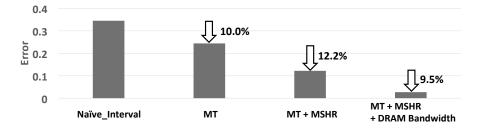

| Figure 20 | The errors of a kernel from the SRAD benchmark. The arrows represent the error reduction from its left-side configuration.                                                    | 44 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

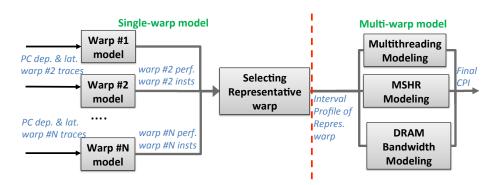

| Figure 21 | GPUMech Overview                                                                                                                                                              | 45 |

| Figure 22 | Intervals of a warp. (The shaded boxes indicate the stall cycles in which no instructions are issued. The instructions in dark gray are the ones that lead to stall cycles.)  | 46 |

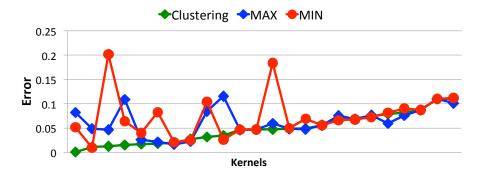

| Figure 23 | Errors from different representative warp selection methods. Each tick represents a control divergent kernel and data points are sorted by the errors of Clustering approach. | 48 |

| Figure 24 | The cases of non-overlapped instructions of RR and GTO policies. (WR: representative warp.)                                                                                   | 49 |

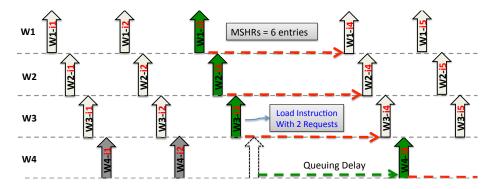

| Figure 25 | The queuing delays caused by a limited number of MSHR                                                                                                                         | 54 |

| Figure 26 | The input collector                                                                                                                                                           | 57 |

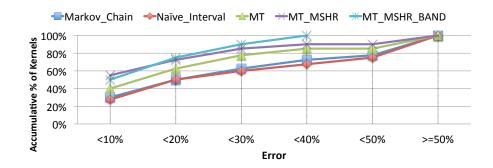

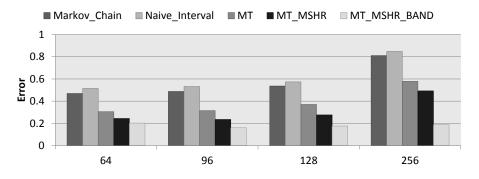

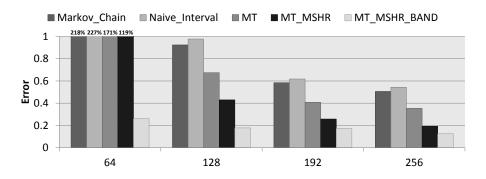

| Figure 27 | Model comparisons for round-robin policy                                                                                                                                      | 60 |

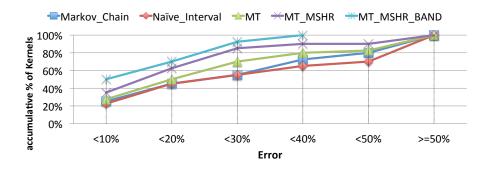

| Figure 28 | Model comparisons for greedy-then-oldest policy                                                                                                                               | 61 |

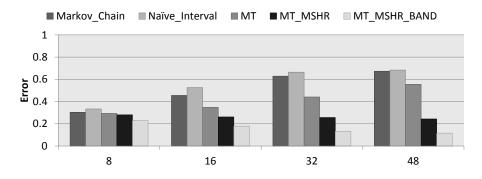

| Figure 29 | Errors with different number of warps per core                                                                                                                                | 62 |

| Figure 30 | Errors with different number of MSHR entries                                                                                                                                  | 63 |

| Figure 31 | Errors with different DRAM bandwidth (the unit of X-axis is GB/s)                                                                                                             | 63 |

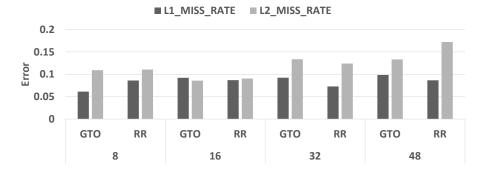

| Figure 32 | Error of L1/L2 cache miss rates compared against detailed simulations .                                                                                                       | 64 |

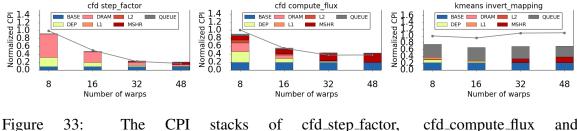

| Figure 33 | The CPI stacks of cfd_step_factor, cfd_compute_flux and kmeans_invert_map kernels.                                                                                            |    |

| Figure 34 | WordCount Example                                                                                                                                                             | 74 |

| Figure 35 | Spark Infrastructure [2]                                                                                                                                                      | 75 |

| Figure 36 | SimProf Overview                                                                                                                                                              | 77 |

| Figure 37 | Snapshots in a sampling unit                                                                                                                                                  | 78 |

| Figure 38 | Thread profiler in SimProf                                                                                                                                                    | 79 |

| Figure 39 | Convert call stacks into a feature vector                                                                                                                                     | 80 |

| Figure 40 | Coefficient of variation of CPIs                                                                                                                                              | 81 |

| Figure 41 | The sampling errors of CPI of different sampling approaches                                                                                                                   | 89 |

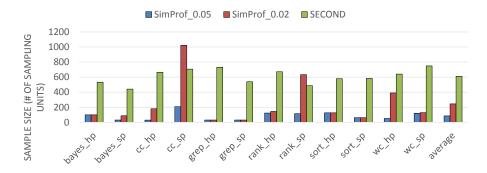

| Figure 42 | The comparison of the sample size (number of sampling units) between SimProf and SECOND.                                            | 90  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

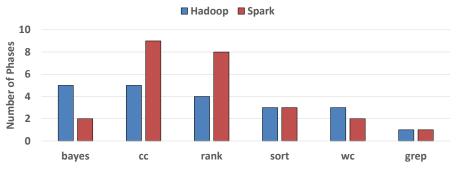

| Figure 43 | Number of phases                                                                                                                    | 90  |

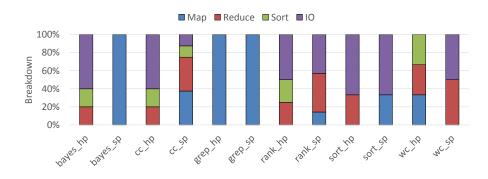

| Figure 44 | Phase type distribution                                                                                                             | 91  |

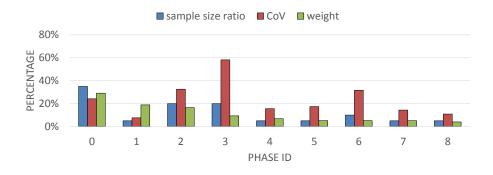

| Figure 45 | The sample size ratio of each phase of $cc_{sp}$ distributed based on the optimal allocation. (The phases are sorted by the weight) | 92  |

| Figure 46 | The input-sensitive sample size                                                                                                     | 93  |

| Figure 47 | The number of input-sensitive and input-insensitive phases                                                                          | 94  |

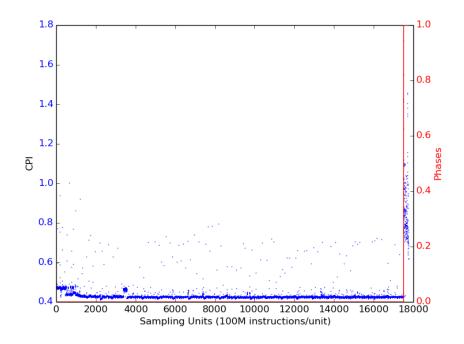

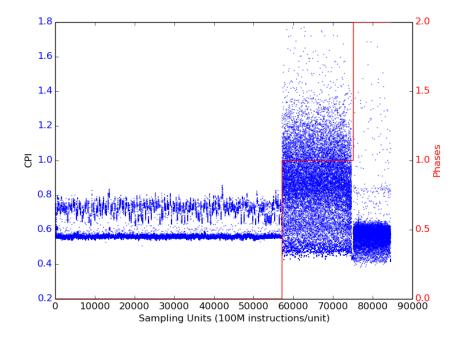

| Figure 48 | WordCount - Spark implementation                                                                                                    | 95  |

| Figure 49 | WordCount - Hadoop implementation                                                                                                   | 96  |

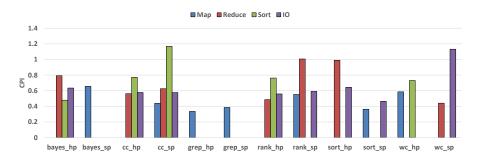

| Figure 50 | The CPI of each type of phases                                                                                                      | 97  |

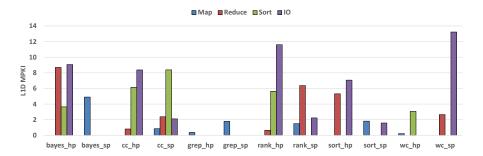

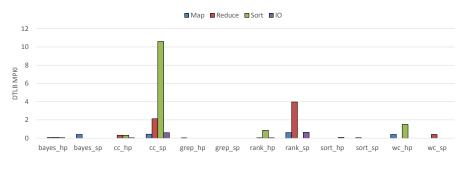

| Figure 51 | L1D MPKI of each type of phase                                                                                                      | 98  |

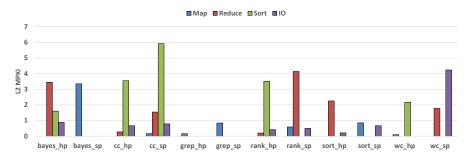

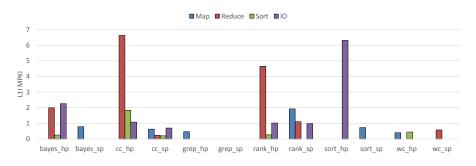

| Figure 52 | L2 MPKI of each type of phase                                                                                                       | 99  |

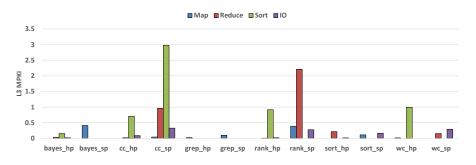

| Figure 53 | L3 MPKI of each type of phase                                                                                                       | 99  |

| Figure 54 | DTLB MPKI of each type of phases                                                                                                    | 100 |

| Figure 55 | L1I MPKI of each type of phases                                                                                                     | 101 |

### SUMMARY

Architectural simulation is one of the most important performance modeling approaches for architecture design. Compared to the native execution speed, the simulation speed has 10,000x times slowdown. Therefore, the techniques that reduce the simulation time are required. Prior techniques target for the conventional benchmark suites, which are either single-threaded or having limited parallelism. However, the emerging workloads, such as GPGPU kernels and data analytic workloads, feature massive parallelism and huge data volume. Prior simulation techniques are not applicable to these workloads or could still incur long simulation time. In this dissertation, three simulation techniques were proposed to simulate these large-scale applications accurately and efficiently.

First, this dissertation presents the sampling techniques, inter-launch and intra-launch sampling, for reducing the simulation time of GPGPU kernels. In inter-launch sampling, a new feature vector is proposed to capture the control and memory divergence, which are the unique characteristics of GPGPU kernels. In intra-launch sampling, the dynamic sampling approach is proposed to sample the instruction intervals that are non-deterministic due to warp scheduling effect.

Second, even with sampling, the number of simulated instructions is proportional to the number of threads in the system. The longer simulation time is expected with more hardware threads integrated onto the GPU. To further reduce the simulation time, an abstracted simulation technique were proposed. Instead of using detailed timing simulation, the simulation model is abstracted using functional simulation and analytical modeling. This technique models the performance of a multithreaded GPU core using the execution behaviors of a single warp. It achieves low modeling error of performance compared to a detailed timing simulation while achieving two orders of magnitude speedup.

Finally, to reduce the simulation time of data analytic workloads, a sampling framework were proposed to select the simulation points. Prior sampling approaches focused on capturing the performance difference caused by code changes. However, because of the data diversity of the data analytic workloads, the sampling approach needs to take the data impact on performance into account. The framework profiles the workloads with negligible overhead on a real machine for fast analysis of phase behaviors. It uses stratified random sampling, a statistical sampling technique, to account not only the performance impact of code, but also other factors, such as data access patterns. Furthermore, it provides the input sensitivity test to further reduce the simulation time when simulating multiple inputs.

### **CHAPTER 1**

# **INTRODUCTION**

# **1.1 The Problem: Reducing the simulation time of large-scale applications**

Architecture simulation is an important performance modeling technique. Modeling the hardware components with sufficient detail helps developers to identify both hardware and software bottlenecks. It is more flexible than hardware counters because it can be modified to provide some program statistics that hardware counters may not provide, such as instruction-level parallelism (ILP). In addition, simulation is a required tool for designing future processors before they are implemented in the hardware.

However, the major issue of architectural simulation is the huge simulation time. Since architecture simulation uses software to model hardware behavior, its speed is several order of magnitude slower than real hardware. For example, the typical speed of an architecture simulator is from 10,000 instructions per second up to several million instructions per second while the slowdown compared to the actual execution is around 10,000x. Thus, it is important to reduce the simulation time in order to make simulation a feasible solution for performance study.

The speed gap between simulation and real hardware is growing wider and wider for the following reasons: (1) hardware complexity, (2) massive parallelism and (3) massive data.

In terms of hardware complexity, the future processor will become more complex and accommodate more hardware components to improve performance. For example, the network-on-chip (NoC) design will be more complex to reduce the communication overhead between cores. Memory hierarchy will become deeper to avoid off-chip memory accesses. Since more complex hardware designs require more lines-of-code to model their behaviors, the cost of simulating one instruction becomes higher. In terms of massive parallelism, the technology trend is to integrate more cores into a chip to increase performance. Furthermore, the new computing platform, GPGPU, executes thousands of threads concurrently using a large number of simple cores. To match the hardware parallelism, a straightforward approach is to parallelize the simulator. However, the speedup is still limited since memory system is shared creating a single point of bottleneck. To accurately model the memory contention between threads, synchronization is required to ensure the correctness of their access orders. In addition, periodic synchronization, e.g., every 1000 cycles, is required to make sure the threads progress at the same speed. The synchronization overhead negates the benefits of parallelization, especially when the number of cores is high.

In terms of massive data, the data analytic workloads, which are the services deployed in data centers, process a huge amount of data on multiple nodes. For such workloads, more extensive resources are required to simulate because of the involvement of multinode simulation and the large input set. Another challenge of simulating the data analytic workloads is to deal with the managed runtime, e.g., Java, applications, since the workloads are usually written in high-level languages to achieve platform independence.

Prior studies have proposed various techniques to reduce the simulation time, such as sampling [3, 1] and simulation abstraction [4]. However, they all focus on traditional applications or hardware without accounting for the existence of higher parallelisms in the modern hardware and software. From a hardware perspective, they target platforms with a small number of out-of-order cores (up to 8 cores [5, 6]), that are very different from some modern platforms, e.g., GPGPU, featuring a large number of simpler in-order multithreaded cores. From a software perspective, the emerging workloads, GPGPU kernels and the data analytic workloads, have very different characteristics from the conventional benchmarks, e.g., SPEC [7] and PARSEC [8]. The conventional benchmarks are purely

CPU-bound, native executed without managed runtimes and have limited thread-level parallelism. In this dissertation, several mechanisms have been innovated to efficiently simulate the GPGPU kernels and data analytic workloads, which have massive thread and data parallelism, with small modeling errors.

### **1.2** The Solution: Domain-specific simulation mechanisms

The solution to the emerging large scale workloads is to design domain-specific simulation techniques. Based on the characteristics of the applications and the execution model of the platform, we design a set of simulation-based modeling techniques for GPGPU kernels and data analytic workloads. They are based on mathematical theory to provide trustworthy simulation results. The highlights of the proposed techniques are as follows.

#### **1.2.1** Sampling technique for GPGPU kernels

To reduce the simulation time of GPGPU simulation, we have developed TBPoint, the sampling technique that can deal with the massive thread-level parallelism (TLP). Simulating the GPGPU kernels may incur a huge overhead since GPUs typically have a large number of threads and high throughput. However, since the prior sampling techniques do not account for massive parallelism, the sample size is likely to be more than required.

The proposed sampling technique, TBPoint, contains inter-launch sampling and intralaunch sampling. Inter-launch sampling selects the representative kernel launches to be simulated while the performances of the remaining kernel launches are predicted as the same as the representative ones. Then, intra-launch sampling selects and simulates the instructions within a kernel launch. The proposed sampling technique can quickly adapt to different levels of thread-level parallelism incurring little overhead.

#### 1.2.2 Hybrid modeling technique for GPGPU kernels

Even though the simulation time can be reduced through sampling, the number of simulated instructions of each simulation point may be high depending on the number of threads in

the system. By contrast, to quickly model the performance, analytical modeling is likely to have higher errors.

The proposed technique, GPUMech, leverages both functional simulation and analytical modeling to balance the accuracy and the modeling speed. Based on the concept of interval analysis [9, 10], an analytical model of multithreaded core is developed to model the performance while the cache simulation is used to identify the stall events of a thread. The proposed technique balances the speed and accuracy. In addition, it provides the CPI stack for analyzing the performance bottlenecks in a GPGPU kernel.

#### **1.2.3** Sampling technique for data analytic workloads

Because of the era of big data, the data analytic workloads, which have the computations scale out to multiple nodes, have growing importance. Even though many frameworks have been developed for those workloads, it is still a challenge in the architecture community to simulate those workloads. Although some sampling tools exist, they are inadequate for those workloads that are implemented using high-level languages and that have long running time.

The proposed technique, SimProf, is a profiling tool for analyzing the phase behaviors and selecting the representative simulation points. It profiles the Java applications using Java call stacks and the hardware counter values. To select the simulation points, SimProf uses the stratified random sampling approach to deal with the non-homogeneous phase behaviors.

#### **1.3** Thesis Statement

The modern software and hardware that feature massive parallelism can be simulated efficiently without sacrificing much accuracy by designing mechanisms based on their execution characteristics.

# 1.4 Organization of This Thesis

Chapter 2 provides the related work of different categories of simulation techniques. Chapter 3 presents the sampling technique for GPGPU kernels. Chapter 4 presents the hybrid modeling technique that combines functional simulation and analytical modeling for GPGPU kernels. Chapter 5 presents a sampling framework for data analytic workloads based on modern computing platform, e.g., Hadoop and Spark. Chapter 6 concludes this document.

# CHAPTER 2 RELATED WORK

Multiple techniques have been proposed to reduce simulation time including simulation sampling, statistical simulation and parallel simulation, each of which is explained as follows.

# 2.1 Simulation Sampling

Simulation sampling, one of the most popular techniques to reduce the simulation time, selects the sampling units to be simulated in detail while "fast-forwarding" the other sampling units. During fast-forwarding, the detailed timing simulation is not performed, but the functional simulation is still required to guarantee the functional correctness. The sampling unit size is a variable depending on the sampling technique. Sampling techniques can be classified into statistical sampling and profile-driven sampling described as follows.

#### 2.1.1 Statistical Sampling

Statistical sampling takes samples based on statistical theories. Two sampling techniques have been proposed for statistical sampling: random sampling and systematic sampling (periodic sampling). Conte et al. [11] proposed random sampling which selects the sampling units at random. This approach provides the confidence interval and error bounds, but it is based on unrealistic assumptions about the micro-architecture, e.g., perfect cache hierarchy or branch prediction. Wunderlich et al. [3] proposed SMARTS, which chooses systematic sampling over random sampling to take samples since it is more intuitive to be implemented in an event-driven simulator. In addition, SMARTS uses the z-score of the central limit theorem to estimate the required sample size to achieve the specified confidence interval without assuming the target population. SMARTS uses a small sampling unit size, 1000 instructions, to minimize the instructions simulated in detail. For such a

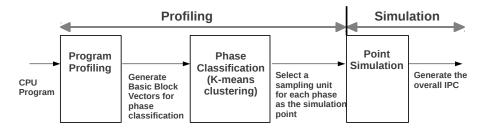

Figure 1: Simpoint overview [1]

small sampling unit size, the requirement of the reconstruction of cache and branch predictor states is more important compared to a large sampling unit size. Thus, SMARTS applies "functional warming," which continuously warms the components with long history to guarantee correct micro-architecture states at all times. The major bottleneck of SMARTS is the speed of functional warming since the authors found that the required instructions for detailed simulation are relatively small (< 1%).

Carlson et al. [6] and Ardestani et al. [5] extend SMARTS to support multithreaded applications on multi-core platforms. The challenge of sampling multithreaded applications is to decide the relative speed of each thread during fast-forwarding. The IPC of a thread in the previous period is used as the IPC of the fast-forwarding period of the thread. In addition, the authors adopt systematic sampling but take samples based on cycles instead of instructions and claim better accuracy than instruction-based sampling like SMARTS.

#### 2.1.2 Profile-driven Sampling

Profile-driven sampling takes samples based on the profiled information. The idea is to pick a sampling unit from each program phase as the simulation point. Since other sampling units in the same phase are predicted to have the same behavior as the selected point, the overall IPC can be predicted. The profiling is used to cluster sampling units into phases. Thus, the key to good accuracy is to extract the features of each sampling unit that can accurately cluster the sampling units with similar behaviors into phases. Sherwood et al. [1] developed Simpoint, the most popular profile-driven sampling technique. Because they found that the instructions being executed have a strong correlation with performance [12],

Basic Block Vector (BBV) is used as the feature vector of each sampling unit. Equation 5 shows the representation of a BBV. BBV characterizes the basic blocks executed in a sampling unit and their execution counts. By clustering the BBVs using k-means, a clustering algorithm, the sampling units are grouped into clusters, while each cluster is a phase. For each cluster, a sampling unit closest to the centroid of the cluster is selected as the simulation point of the phase. Equation 3 shows the overall CPI. The weight of a phase is determined by the number of sampling units in the phase, as shown in Equation 2.

$$BBV =$$

(1)

$$phase\_weight_i = \frac{\#sampling\_units_i}{total\_sampling\_units}$$

(2)

$$Total\_CPI = \sum_{i \in phases} (simulation\_point\_CPI_i \times phase\_weight_i)$$

(3)

Pinpoint [13] leverages the Pin tool [14], a dynamic instrumentation tool, to collect BBVs. Sherwood et al. proposed a processor architecture based on the concept of BBV with online phase detection. Perelman et al. [15] extended Simpoint to provide statistically valid simulation points with confidence interval analysis. Biesbrouck et al. [16] proposed co-phase matrix, which detects phases when multi-programmed workloads are running. Lau et al. [17] extended Simpoint to support variable-length sampling units so that the sampling unit size is better matched with the period of a phase. In addition to BBV, Eeckhout et al. [18] consider several micro-architecture independent metrics to find simulation points. They also explored picking simulation points. Similarly, Lau et al. [19] use program semantics, called graph and loop graph, to identify the phase changes in the software level. For multi-threaded benchmarks with barriers, Carlson et al. [20] consider each inter-barrier region as a sampling unit and use BBV to pick the inter-barrier regions needed to be simulated.

SMARTS and Simpoint can be compared based on (1) implementation easiness, (2) accuracy and (3) efficiency. From an implementation easiness standpoint, the simulation

points selected by Simpoint are easier to be used by simulators since no warming techniques need to be implemented while SMARTS requires functional warming integrated into simulators and statistical analysis to be performed. From an accuracy perspective, Yi et al. [21] concluded that SMARTS is slightly more accurate than Simpoint. The reason is that Simpoint determines the similarity between sampling units using code signature (BBV) without considering micro-architecture states. On the other hand, SMARTS determines required sample size based on the central limit theorem using the actual CPI variation. Wunderlich et al. [22] applied stratified random sampling using BBVs and found that it does not provide much benefit over simple random sampling when the sampling unit size is small. From an efficiency perspective, SMARTS is slower than Simpoint due to the overhead of functional warming. In addition, SMARTS requires running the entire benchmark, while in Simpoint, the simulation can be terminated early once all simulation points have been simulated.

### 2.2 Statistical Simulation

Different from sampling, statistical simulation reduces the simulation time by generating and simulating synthetic traces rather than simulating the original programs. To generate synthetic traces, a set of program characteristics is profiled and represented as distributions. This process is called statistical profiling. Then, statistical simulation used a simple simulator to simulate the synthetic traces to get performance numbers. Because the length of a synthetic trace is much shorter than the original program, the simulation time can be greatly reduced.

Statistical profiling characterizes the program statistics into micro-architecture dependent and independent statistics. The micro-architecture independent statistics include instruction mix and dependency distance distribution. Statistical profiling also needs to consider control flow behaviors. Oskin et al. [23] propose using control flow graph tagged with transition probabilities. Eeckhout et al. [24] propose the statistical flow graph (SFG), which uses a Markov chain to further improve the accuracy. Using SFG, the execution paths caused by different control flows are better captured. The micro-architecture dependent statistics include the locality events, such as cache and branch predictor behaviors. The initial designs of statistical simulation [25, 26] to capture the locality events do not consider the delayed hits and the memory level parallelism (MLP). Genbrugge et al. model the delayed hits by collecting the cache line reuse distributions and model MLP through the global history of cache events. Functionality-wise, the synthetic trace simulator is similar to the full blown simulator but it is less complex since it only needs to simulate the information encoded in the traces.

## 2.3 Parallel Simulation

Eeckhout [27] categorizes parallel simulation into (1) parallel sampled simulation and (2) parallel simulation, explained as follows.

Parallel sampled simulation divides a simulation into multiple time chunks. Simflex [28] speeds up SMARTS using checkpoints. According to Simflex, 99% of the overhead of SMARTS comes from functional warming. Thus, the authors proposed "live points" to store the micro-architecture states in addition to the functional states. Instead of checkpointing the whole micro-architecture states, only the states of cache hierarchy and branch predictor need to be stored since most of micro-architecture states can be reconstructed through a few thousand instructions of warming. The simulation can be parallelized by running different checkpoints in parallel. One limitation of this approach is that the stored micro-architecture states are not flexible and may not be used in different hardware configurations, e.g., different cache sizes. Using checkpoints to parallelize the simulation. Parallelizing simulations using checkpoints has been used in other work [29].

Parallel simulation is becoming popular for simulating multi-core platforms. It is natural to parallelize by cores because of the independence between core executions. The intuitive way is to synchronize between cores every cycle. Although this approach incurs no errors, the synchronization overhead outweighs the benefits of parallelization. The cycle-by-cycle synchronization can be relaxed using quantum-based synchronization [30], which synchronizes between threads every quantum size, e.g. N cycles. If the quantum size is smaller than the latency of propagating an event from one thread to another, the accuracy is the same as the cycle-by-cycle synchronization. For multicore processors, since the communication latency between threads is small, the quantum size needs to be in the range of tens of cycles without losing accuracy [31]. Similarly, the small quantum size limits the benefit of parallelization. To address this limitation, some studies trade accuracy for speed by further relaxing the synchronization. Slacksim [32] uses the concept of "slack" defined as the cycle count difference between threads. The simulation can tolerate a certain amount of slack without barrier synchronization. Zsim [33] uses the "bound-weave" approach, which divides the synchronization into two steps. In the first step, the threads run in parallel to determine the interaction between threads on shared resources. In the second step, since the interaction between threads is known from the first step, the synchronization can incur much lower overhead. Zsim also uses Pin tool [34], a binary instrumentation tool, to speed up the functional simulation and applies an instruction-driven timing model, which moves the timing model to the instrumentation stage for low-overhead timing simulation.

### 2.4 Analytical Modeling

#### 2.4.1 Analytical Models of Single-threaded Cores

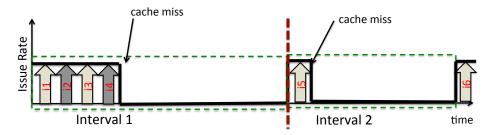

The foundation of interval analysis was proposed by Karkhanis et al. [9] and Eyerman et al. [10]. The basic idea is that the performance of a processor is equal to the issue rate of a processor (a sustained performance) unless disruptive miss events occur such as branch mispredictions or cache misses. Performance is then estimated by subtracting the stall cycles due to different stall events from the maximum issue rate. Figure 2 illustrates interval analysis. An *interval* is defined as a sequence of instructions with the maximum issue rate followed by stall cycles. Functional simulators are used to detect stall events.

Figure 2: Example of interval analysis. (i: instruction.)

Several studies improved or applied the interval analysis technique. Genbrugge et al. [35]. proposed "interval simulation," which improves the simulation speed by abstracting the out-of-order execution using interval analysis. Eyerman et al. [36, 37] proposed performance counter architectures for out-of-order processors and SMT processors based on interval analysis. Chen et al. [38] improved the accuracy of the technique considering pending cache hits, prefetching, and MSHRs. Breughe et al. [39] applied the technique to in-order processors.

#### 2.4.2 Analytical Models of Multi-threaded Cores

Chen and Aamodt proposed a first-order performance model of a multithreaded core [40]. They performed a Markov chain analysis to predict the performance of a multithreaded core similar to a GPU core except with vector processing. To begin with, a single thread is modeled as a random variable with two states: *activated* and *suspended*. Activated means that the thread can issue an instruction at the cycle. Otherwise, it is stalled. The transition probability from activated to suspended is *p*, while the probability from suspended to activated is  $\frac{1}{M}$ , where *M* is the number of cycles of a thread being suspended. By performing the Markov chain analysis, the probability of being in any state at any cycle can be known.

In the past few years, several GPU performance models have been proposed. Baghsorkhi et al. [41] proposed using a work flow graph (WFG), an extension of the control flow graph, to estimate the performance. Zhang and Owens [42] proposed a model to measure the execution time of the instruction pipeline, shared memory, and global memory respectively using micro-benchmarking. However, these prior works did not model the cache hierarchy that is equipped in all modern GPUs.

GPUPerf [43] is a performance analysis framework used to predict the performance bottlenecks of GPGPU kernels. The authors use benefit metrics to indicate the relative importance of different performance bottlenecks:  $B_{fp}$ ,  $B_{itilp}$ ,  $B_{memlp}$ , and  $B_{serial}$ . They model the benefits of removing the inefficient computation, increasing TLP and MLP, and removing the synchronization and resource contention.  $B_{fp}$  represents the benefits of removing the inefficient computation;  $B_{itilp}$  represents the benefits of increasing the thread-level parallelism;  $B_{memlp}$  represents the benefits of increasing the memory-level parallelism; and  $B_{serial}$  represents the benefits of removing the synchronization and resource contention. The benefit metrics are generated by the performance model extended from the MWP-CWP model [44]. But, similar to the model for a multithreaded core, they do not model the queuing delay due to resource contention in the memory system nor do they model the scheduling policy. This affects not only the modeling accuracy, but also the reported benefit metrics. For example, the model may suggest increasing the memory-level parallelism (MLP), but it may instead hurt the performance due to increased queuing delays. In addition, the proposed benefit metrics do not show the performance bottlenecks in detail, e.g., micro-architecture level.

Eq. 4 shows that the total execution time is composed of  $T_{comp}$ ,  $T_{mem}$  and  $T_{overlap}$ .  $T_{comp}$  is the execution time to excute compute instruction. First, the total exeuction cycles of a single warp is counted. Because the execution cycles from multiple warps can overlap, such effect can be modeled by estimating the TLP. Similarly, to compute  $T_{mem}$ , the overlapping effect can be modeled by estimating the memory-level parallelism (MLP).  $T_{overlap}$  represents the degree of how much the memory access cost can be hidden by warped execution.  $T_{overlap}$  is equal to  $min(T_{comp} \times, T_{mem})$ .

$$T_{exec} = T_{comp} + T_{mem} - T_{overlap} \tag{4}$$

In addition to performance models, several GPU cache models have been proposed.

Baghsorkhi et al. [45] applied Monte Carlo simulation for a finite number of times to mimic the non-deterministic schedule deviation between thread blocks. Tang et al. [46] applied the reuse distance theory on a single thread block to model the cache miss rate without considering MSHRs. Nugteren et al. [47] proposed a cache model for L1 cache based on the reuse distance theory. They emulate per-warp memory traces with the round-robin scheduling policy. In addition, they modeled MSHRs accounting for a limited number of outstanding misses.

# 2.5 Input Set Selection

Prior work on input sets focused on selecting the representative input sets. Eeckhout et al. [48] used principle component analysis (PCA) to select the representative programinput pairs. They characterize each program-input pair using 20 program characteristics, such as instruction mix and cache miss rates. Breughe et al. [49] used BBV to select the representative inputs for microprocessor design space exploration. Hsu et al. [50] found that procedure coverage and microarchitecture behaviors are different between the training and reference sets of SPEC 2000.

## **CHAPTER 3**

# TBPOINT: REDUCING SIMULATION TIME FOR LARGE-SCALE GPGPU KERNELS

This chapter first describes the problem of long simulation time of GPGPU kernels. To reduce the simulation time, this chapter introduces TBPoint [51], which is an infrastructure that reduces the instructions to be simulated by sampling GPGPU kernel launches and thread blocks. On average, the solution leads to 1.74% of sampling error compared to full simulation while simulating only 2.6% of total instructions.

### 3.1 Introduction

Recently, one of the main scientific computing paradigms in addition to Titan [52] and CSCS (Swiss National Super- computing Center) [53] is General-purpose graphics processing units(GPGPU), which has large-scale computing power. To take advantage of this computing power, a wider range of algorithms have been converted to GPGPU kernels. Future workloads of GPGPU kernels will be much more complex and much larger scale.

To design new architectures optimized for GPGPU kernels, computer architects use a cycle-level simulator to gain insights into kernel behaviors. Using cycle-level simulation can help not only architects but also application developers to understand the performance bottleneck in applications and architectures.

However, because GPGPU architectures have many cores to simulate, cycle-level simulation takes a significant amount of execution time. Table 1 shows comparisons of GPGPU execution times and expected simulation times of a cycle-level GPGPU simulator. The GPGPU execution times are from Burtscher et al. [54], and we used the Macsim simulator for the GPGPU simulations [55]. The slowdown of Macsim running on the Intel Ivy-bridge is around 80,000x compared to native NVIDIA Quadro processors. Even for kernels with

| Time       | NB    | SP    | SSSP | PTA  | TSP  | DMR  | MM    |

|------------|-------|-------|------|------|------|------|-------|

| GPU        | 28557 | 18779 | 7067 | 4485 | 4456 | 3391 | 881   |

| (msec)     |       |       |      |      |      |      |       |

| Simulation | 3.78  | 2.48  | 6.54 | 4.15 | 4.13 | 3.14 | 19.58 |

|            | weeks | weeks | days | days | days | days | hours |

Table 1: Comparison of GPGPU execution time and Simulation Time. GPU time is for NVIDIA Quadro 6000.

a few seconds of running time, the simulation time takes days. As a result of this slowdown, simulation is an unattractive approach. Although most GPGPU kernels have short kernel sizes, the overhead comes from simulating a massive number of threads. Because of the computing power of GPU processors, an 80,000x slowdown is reasonable. GPGPU applications can easily have 1GFLOPS or even higher performance. If a simulator can simulate 1,000FLOPS/sec (which is similar to 10K instructions per sec in typical cycle-level simulators), a 10<sup>6</sup> slowdown is typical. To accelerate simulation time, one can parallelize a cycle-level GPGPU simulator, but when large-scale GPGPU systems are simulated, the required resources for such simulations become significant.

In this chapter, we first introduce the GPGPU simulation model and the terminology. Then, we discuss the existing sampling techniques on reducing simulation time.

## **3.2 Background and Motivation**

#### 3.2.1 Target Platform and Terminology

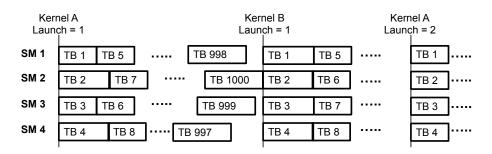

Figure 3 illustrates GPGPU simulations and the following terminology used throughout the chapter.

- Occupancy: For a kernel, "system occupancy" refers to the maximum number of concurrent thread blocks, while "SM occupancy" refers to the maximum number of concurrent thread blocks on one SM. For example, Figure 3 shows that SM occupancy is 1 and system occupancy is 4 for both Kernels A and B.

- **Kernel Launch (Launch):** A "kernel launch" is an instance of a GPGPU kernel that can be executed multiple times. For each kernel launch, thread blocks are dispatched

Figure 3: GPGPU Simulation Overview

in a sequence based on their thread block IDs. The global thread block scheduler dispatches the thread blocks in a greedy fashion. All thread blocks of the kernel launch need to be executed before the next kernel launch.

- Warp/Thread Instruction: "Warp instructions" or "instructions" are those executed by a warp, and "thread instructions" are those executed by a thread within a warp.

- Interval: An interval is a series of contiguously executed instructions.

#### 3.2.2 Motivation

In profiling-based sampling, the idea is to profile a program and find the instruction intervals likely to have homogeneous behaviors based on the program characteristics. The simulation time can be reduced by simulating one interval to represent the performance of the other intervals with homogeneous behaviors.

The requirements of profiling-based sampling are as follows.

- **Hardware independence:** The profiling should have no constraints on the platform where the profiling can be performed.

- **One-time profiling:** The profiling needs to be executed only once for each program/input combination, and the results can be used in different hardware configurations.

• Mathematical model support: The sampling approach should be supported by detailed mathematical modeling to confirm its accuracy.

The most popular profiling-based sampling technique targeting single-threaded CPU applications is Simpoint [1], the functionality of which is described as follows.

- At profile time, the program is divided into sampling units that contain a fixed number of instructions, such as one million instructions. Then, the profiler collects a basic block vector (BBV) for each sampling unit. A dimension of the vector represents a basic block in the program. The value of a dimension is the executed instruction counts of the basic block normalized by the total instruction counts, as shown in Equation 5. The BBVs, used as feature vectors, are fed into the clustering algorithm, k-means, to group the sampling units into clusters. For each cluster, a sampling unit that is selected as the simulation point represents the performance of the other units in the cluster.

- At simulation time, only the sampling units selected as simulation points need to be simulated. The other sampling units can be skipped by fast-forwarding. Each simulation point could have different weights, depending on the number of sampling units in the cluster. The overall CPI can be predicted by Equation 5.

$$BBV = \langle BB1 : \frac{\#BB1\_insts}{\#insts}, BB2 : \frac{\#BB2\_insts}{\#insts}...BBN : \frac{\#BBN\_insts}{\#insts} \rangle$$

$$Total\_CPI = \sum_{i \in phases} (representative\_unit\_CPI_i \times phase\_weight_i)$$

$$phase\_weight_i = \frac{\#sampling\_units_i}{total\_sampling\_units}$$

(5)

Since GPGPU kernels can be considered as multithreaded applications, Pinpoint [14], an extension of Simpoint for sampling multi-threaded applications, could be applicable to GPGPU kernels. In Pinpoint, BBVs are collected on a per-thread basis by actually executing all threads on a real system. However, it does not meet the requirements of profiling-based sampling for the following reasons.

- The profiling needs to be redone for different hardware configurations since the profiling results (simulation points) can only be applied to the simulated platform, which has the same hardware configurations as the profiling platform.

- Although the BBV has a strong correlation with performance in single-thread applications [12], it is uncertain whether the same would be true for GPGPU kernels because of the warp scheduling effect.

Table 2 summarizes the comparisons of different profiling-based sampling techniques. To satisfy all of the requirements of profiling-based sampling, we propose a sampling approach, TBPoint. In terms of hardware independence, TBPoint uses GPUOcelot [56] as the profiling tool, which performs the functional simulations of GPGPU kernels and collects the information about each thread block. In terms of one-time profiling, for different hardware configurations, such as a different number of warps and SMs, TBPoint simply needs to re-perform clustering while reusing the profiling results, incurring low overhead. To model the warp scheduling effect, we use a Markov Chain model that accounts for the performance impact of the effect.

|               | -             |                |           | -          |

|---------------|---------------|----------------|-----------|------------|

|               | applicability | hardware inde- | one-time  | math model |

|               | to GPGPU      | pendence       | profiling | support    |

| Simpoint [1]  | Ν             | Y              | Y         | Y          |

| Pinpoint [14] | Y             | N              | N         | Ν          |

| TBPoint       | Y             | Y              | Y         | Y          |

Table 2: Comparisons of profiling-based sampling techniques

To reduce the GPGPU simulation time, inter-launch sampling and intra-launch sampling are proposed. To reduce the number of kernel launches, the former selects the kernel launches that need to be simulated. If different kernel launches have homogeneous behaviors, only one of them needs to be simulated to represent the others. To reduce the simulation time of a kernel launch, intra-launch sampling selects the thread blocks that need to be simulated within a kernel launch. inter-launch sampling and intra-launch sampling are explained in the following sections.

## **3.3 Inter-Launch Sampling**

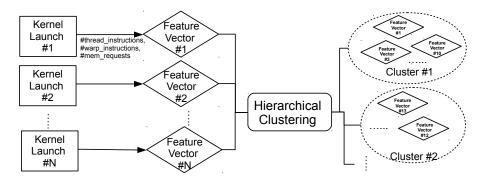

Using hierarchical clustering, inter-launch sampling groups the kernel launches with homogeneous performance. We simulate only one kernel launch within each cluster and predict that the performance of the other kernel launches within each cluster will be the same as the simulated launch, thus reducing simulating time.

Figure 4: Procedure of Inter-Launch Sampling.

Figure 4 shows the procedure of inter-launch sampling. First, each kernel launch is represented as a feature vector, which is the input to the clustering algorithm. A feature vector describes the characteristics of a kernel launch that contains four features (described below), each of which belongs to one dimension of the vector. Then, hierarchical clustering processes the feature vectors and groups them into clusters. Since each feature vector represents a kernel launch, the kernel launches within the same cluster are believed to have homogeneous performance (IPCs).

The design of feature vectors is important since a feature vector should correctly describe the characteristics of a kernel launch so that the hierarchical clustering can group the kernel launches with homogeneous performance into a cluster. The features with which we chose to compose a feature vector and their performance impact are shown as follows.

• **Kernel launch size**: The number of *thread instructions* of a kernel launch is used as a feature to capture the size of a kernel launch.

- **Control flow divergence**: Because simply capturing the number of thread instructions of a kernel launch does not reflect its degree of control flow divergence, the number of *warp instructions* of a kernel launch is used as a feature to capture the degree of control flow divergence. Even if two kernel launches have the same number of thread instructions, they may have different IPCs due to different degrees of control flow divergence. For example, Kernel Launch 1 executes 32 thread instructions in one warp instruction, while Kernel Launch 2 executes 32 thread instructions in 32 warp instructions.

- Memory divergence: Because kernel launches with different numbers of memory requests are likely to have different IPCs, the number of *memory requests* of a kernel launch is used as a feature to capture the degree of memory divergence. The degree of memory divergence is independent of the number of thread blocks and the control flow divergence. For example, a warp instruction that contains 32 thread instructions can issue at least one and up to 32 memory requests if none of the accesses can be coalesced.

- Thread block variations: The coefficient of variations (CoV) of thread block sizes of a kernel launch is used as a feature to capture the variations of thread block sizes. Thread block size is defined as the number of thread instructions in a thread block. All the above features are designed as if only one thread block were running per kernel launch. However, a kernel launch typically has multiple thread blocks, and different thread blocks may have a different number of instructions. For example, let's assume that kernel launch 1 has two thread blocks with the number of thread instructions 100 and 100, respectively, and that kernel launch 2 has two thread blocks with the number of thread instructions 160 and 40, respectively. Even though both kernel launches may have the same size (200 thread instructions), they may perform differently because of distinct thread block interleaving situations.

Equation 6 shows the inter-feature vector composed of the above features, each of which is normalized with its average value across all kernel launches so that they have the same order of magnitude.

For kernel launch i,

$$Memory\_Divergence, Thread\_Block\_Variations >$$

$$= < \frac{\#thread\_insts_i}{avg\_thread\_insts}, \frac{\#warp\_insts_i}{avg\_warp\_insts},$$

$$\frac{\#mem\_reqs_i}{avg\_mem\_reqs}, CV\_TB\_size >$$

$$(6)$$

Hierarchical clustering takes all inter-feature vectors and groups them into clusters. For each cluster, the kernel launch with the inter-feature vector closest to the center of the cluster is selected as a simulation point that will be sampled by intra-launch sampling.

We chose hierarchical clustering instead of the k-means algorithm used by Simpoint for the following reason. The number of clusters can be determined automatically by setting the *distance threshold*  $\sigma$ , which is the maximum distance between any two points in a cluster. The higher threshold results in fewer clusters, which decreases the total sample size, but the variations within each cluster could be higher, which increases the sampling errors. The appropriate value of the distance threshold depends on the required accuracy and hardware configurations. On the other hand, the k-means algorithm requires a pre-defined number of clusters as an input, which needs another index, such as Bayesian information criterion (BIC) score, to set. In addition, while the results of hierarchical clustering are deterministic, the results of k-means could be affected by the selection of the initial seeds. For all hardware configurations that we tested, the distance threshold = 0.1 for inter-launch sampling can minimize the sampling errors to less than 10% on average.

The proposed inter-feature vector has the following advantages over BBVs, which were used in Simpoint. First, it provides more insight into performance behavior. We found that BBVs are less correlated with performance on GPGPU programs. GPGPU kernels often have very few basic blocks and even the same basic blocks show very distinct performance

Figure 5: Intra-Launch Sampling

behaviors because of memory divergence, thread block variations, and other behaviors. Furthermore, the same kernel can be launched multiple times but each invocation of the kernel shows particular behaviors, e.g., reduction kernel. Hence, although BBVs can be useful to detect program behavior, the sources of performance variations cannot be solely obtained through BBVs. On the other hand, the proposed vector is also more computationally efficient since it has only four dimensions, while the BBV has a number of dimensions equal to the number of basic blocks in the kernel launch. <sup>1</sup>

# 3.4 Intra-Launch Sampling

Once inter-launch sampling selects a kernel launch from each cluster for simulation, intralaunch sampling can further reduce the simulation time by sampling the selected kernel launch.

Figure 5 shows a high-level view of intra-launch sampling. Within a kernel launch, our goal is to sample *homogeneous regions*, which have homogeneous performance across multiple thread blocks. In a homogeneous region, a few thread blocks are simulated while the others are skipped so as to reduce the simulation time. The IPC collected from the simulated thread blocks is predicted to be the IPC of the entire homogeneous region. The

<sup>&</sup>lt;sup>1</sup>The BBV can be added as another feature for improving accuracy with the cost of increased total sample size. The study of such extension is left for our future work.

Figure 6: The State Diagram of a Warp.  $p = \frac{mem\_insts}{total\_insts}, M_k \sim N(\mu, \sigma^2)$

thread blocks not in any homogeneous regions are simulated as usual.

The design presents the following challenges.

- How do we define a homogeneous region? (Section 3.4.1)

- During profiling, how do we identify the location of a homogeneous region? (Section 3.4.3)

- During simulation, how do we sample a homogeneous region? (Section 3.4.4)

#### 3.4.1 The Design of Intra-Launch Sampling

Our design of intra-launch sampling identifies a homogeneous region through the mathematical model that quantifies the IPC variations under different warp interleaving situations that we assume are caused by variable memory latencies due to resource contention and/or queuing delay. Based on our model, such IPC variation has proven to be small. The IPC of a homogeneous region can be predicted as equal to one of its homogeneous intervals. The definitions and proofs are as follows.

Definition 1:

- *p* is the **stall probability** that is the probability of a warp being stalled, and *M* is the **average stall cycles** consumed by a stall event. *p* is modeled as a constant while *M* is modeled as a random variable following Gaussian distribution. *N* is the number of warps in an SM.

- A homogeneous interval is a sequence of executed instructions from concurrent warps, and each warp has the same *p* and *M*.

• A homogeneous region is the region with consecutive homogeneous intervals with the same *p* and *M*.

**Lemma 1** The IPC variation of a homogeneous interval under different warp interleaving situations caused by random variable M is within a 10% difference of the average IPC.

Definition 1 shows all definitions that are required for the model. As an example of the input parameter p and M, let us assume that 10% of the instructions of a warp are long latency instructions, and each of which consumes 400 cycles on average. Then, p is a constant equal to 0.1. M is a random variable following  $N(\mu, \sigma^2)$  where the  $\sigma = \frac{0.1 \times \mu}{1.96}$  so that 95% of randomly picked Ms is within ±10% of  $\mu$  (400 cycles). Figure 6 shows the state diagram of a warp, which is the basic building block of the model.

Lemma 1 is proven by modeling the IPC variation of a homogeneous interval that includes two steps. First, the IPC of a homogeneous interval is predicted by the Markov chain, which considers the warp interleaving effect. Second, the IPC variation caused by variable M can be predicted by the Monte Carlo method, which performs the Markov chain analysis a finite number of times.

$$S_{i,j} = \prod_{x=1}^{N} f(A_i[x], A_j[x]), A_i[x], A_j[y] \in \{0, 1\}, \ 0 \le i, j < 2^N - 1$$

$$f(A_i[x], A_j[x]) = \begin{cases} A_i[x] \times p + (1 - A_i[x]) \times \frac{1}{M_x}, & A_i[x] \neq A_j[x] \\ A_i[x] \times (1 - p) + (1 - A_i[x]) \times (1 - \frac{1}{M_x}), & A_i[x] = A_j[x] \end{cases}$$

$$V_i = < R_0, R_1, R_2 \dots R_{2^N - 1} > = < 0, 0, 0, \dots 1 >$$

$$V_s = \lim_{n \to \infty} V_i T^n \qquad (7)$$

$$T = \begin{bmatrix} S_{0,0} & S_{0,1} & \dots & S_{0,2^N - 1} \\ S_{1,0} & S_{1,1} & \dots & S_{1,2^N - 1} \\ \dots & \dots & \dots & \dots \\ S_{2^N - 1,0} & S_{2^N - 1,1} & \dots & S_{2^N - 1,2^N - 1} \end{bmatrix}$$

$$IPC = 1.0 \times (1 - R_0)$$

Figure 7: IPC Variation (Each legend shows the *p*, *M*, and *N* values. For example, p0.05M100N4 means p = 0.05, M = 100 and N = 4)