### ELECTRONIC DESIGN AUTOMATION TOOLS AND DESIGN STUDY FOR HETEROGENEOUS MONOLITHIC 3D INTEGRATED CIRCUITS

A Dissertation Presented to The Academic Faculty

By

Sai Surya Kiran Pentapati

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology

May 2022

© Sai Surya Kiran Pentapati 2022

### ELECTRONIC DESIGN AUTOMATION TOOLS AND DESIGN STUDY FOR HETEROGENEOUS MONOLITHIC 3D INTEGRATED CIRCUITS

Thesis committee:

Dr. Sung Kyu Lim Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Saibal Mukhopadhyay Electrical and Computer Engineering Georgia Institute of Technology

Dr. Shimeng Yu Electrical and Computer Engineering Georgia Institute of Technology Dr. Callie Hao Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Hyesoon Kim College of Computing Georgia Institute of Technology

Date approved: April 1, 2021

#### ACKNOWLEDGMENTS

As I approach the end of my journey as a doctoral student, I would like to take this opportunity and thank everyone who have helped me to reach this point of my journey.

First of all, I like to thank Dr. Sung Kyu Lim who has been an integral part of my Ph.D. guiding me along and helping me gain my footing in my first year. He has been a great mentor and taught me some invaluable lessons. I would also like to thank the members of the proposal and dissertation committees – Dr. Arijit Raychowdary and Dr. Shimeng Yu for their great advice during the proposal exam, and Dr. Saibal Mukhopadhyay, Dr. Hyesoon Kim, and Dr. Callie Hao for taking their time and effort in serving as part of my dissertation committee.

I'm also grateful for all the great mentors, collaborators, managers, and colleagues from the industry: Dr. Asif Khan, Nick Samra, Vassilios Gerousis, Rwik Sengupta, Harsono Simka, Dr. Gary Yeap, Nick Lafrenz, Dr. Xiaoqing Xu, Dr. Thorlindur Thorolfsson, Kurian Abraham for their technical discussions and industry insights. I also like to show my sincere appreciation to all the GTCAD members with whom I had many fruitful discussions: Dr. Sandeep Samal, Dr. Kyungwook Chang, Dr. Bonwoong Ku, Rakesh Perumal, Dr. Heechun Park, Lennart Bamberg, Jinwoo Kim, Anthony Agnesina, Da Eun Shim, Dr. Junsik Yoon, Lingjun Zhu, Yi-Chen Lu, Gauthaman Murali, Pruek Vanna-Iampikul

I am also very grateful for all my friends and family whose conversations and chats always make me more cheerful, especially, all the great times I had with my cousins, and my brother, Kaushik, who is the best friend I could ask for (although I'm scared to show this to him as he would never let it go).

Lastly, but most importantly, I want to show my heartfelt gratitude towards my parents, Sai Murali and Venkata Lakshmi, who have been very supportive of my decisions ever since I was capable of making informed decisions, and being with me every step of the way. I can never thank them enough and hope this is at least a drop in the ocean.

## TABLE OF CONTENTS

| Acknow    | vledgme  | nts                                                               |

|-----------|----------|-------------------------------------------------------------------|

| List of ' | Tables . | x                                                                 |

| List of ] | Figures  | xiv                                                               |

| Summa     | nry      |                                                                   |

| Chapte    | r 1: Int | roduction                                                         |

| 1.1       | Fabrica  | ation and Packaging Techniques for 3D ICs                         |

| 1.2       | Electro  | onic Design Automation Flows for 3D ICs                           |

|           | 1.2.1    | Placement in the Three Dimensional space                          |

|           | 1.2.2    | Pseudo-3D Place and Route Flows                                   |

| 1.3       | Organi   | zation                                                            |

| Chapte    | r 2: Ma  | chine Learning Integrated Pseudo-3D Flow for Monolithic 3D ICs 10 |

| 2.1       | RC An    | alysis                                                            |

|           | 2.1.1    | RC breakdown of a net                                             |

|           | 2.1.2    | RC Evolution from Pseudo-3D to Final-3D designs                   |

| 2.2       | Design   | and Learning Model Implementation                                 |

|           | 2.2.1    | Design Implementation                                             |

|        | 2.2.2    | Machine Learning Model                                       | 23 |

|--------|----------|--------------------------------------------------------------|----|

| 2.3    | Result   | s                                                            | 24 |

|        | 2.3.1    | Training and Inference                                       | 24 |

|        | 2.3.2    | Full-chip PPA                                                | 25 |

| 2.4    | Conclu   | usion                                                        | 29 |

| Chanta | r 3. Din | a-3D: An Effective Multi-Die Co-Optimization Methodology for |    |

| Chapte |          | IC Design                                                    | 30 |

| 3.1    | Backg    | round                                                        | 30 |

| 3.2    | Pin-3E   | D Flow Enablement                                            | 33 |

|        | 3.2.1    | Key Idea                                                     | 33 |

|        | 3.2.2    | Creating the 3D BEOL and FEOL files                          | 34 |

| 3.3    | Pin-3E   | D Design Flow                                                | 37 |

|        | 3.3.1    | Incremental Placement with Global Routing                    | 37 |

|        | 3.3.2    | Clock Tree Optimization                                      | 38 |

|        | 3.3.3    | Routing                                                      | 40 |

|        | 3.3.4    | Timing Closure                                               | 40 |

|        | 3.3.5    | ECO                                                          | 41 |

| 3.4    | Experi   | imental Setup                                                | 43 |

|        | 3.4.1    | Homogeneous 3D ICs                                           | 43 |

|        | 3.4.2    | Heterogeneous 3D ICs                                         | 43 |

| 3.5    | PPA b    | enefits of the Pin-3D stages                                 | 44 |

| 3.6    | PPA R    | esults and Analysis                                          | 51 |

|        | 3.6.1    | Homogeneous 3D IC Design                                     | 51 |

|        | 3.6.2   | Routing Analysis and Metal Layer Savings                                     | 56 |

|--------|---------|------------------------------------------------------------------------------|----|

|        | 3.6.3   | Heterogeneous 3D IC Design                                                   | 56 |

| 3.7    | Conclu  | usion                                                                        | 58 |

| Chapte |         | etal Layer Sharing: A Routing Optimization Technique for Mono-<br>nic 3D ICs | 65 |

| 4.1    | Charae  | cteristics of Routing                                                        | 65 |

|        | 4.1.1   | 2D IC Routing Characteristics                                                | 66 |

|        | 4.1.2   | 3D IC Routing Characteristics                                                | 67 |

| 4.2    | Experi  | imental Setup                                                                | 70 |

|        | 4.2.1   | 3D PnR and Controlling the Metal Layer Sharing                               | 70 |

|        | 4.2.2   | Benchmarks and Technology Setup                                              | 71 |

| 4.3    | Metal   | Layer Sharing Scenarios                                                      | 71 |

|        | 4.3.1   | Metal Layer Sharing with Different 3D Bonding Styles                         | 72 |

|        | 4.3.2   | Metal Layer Sharing with Different 3D Partitioning                           | 75 |

|        | 4.3.3   | Impact of Pitch on the Metal Layer Sharing                                   | 77 |

| 4.4    | Result  | s                                                                            | 81 |

|        | 4.4.1   | Baseline Experiments                                                         | 81 |

|        | 4.4.2   | Metal Layer Sharing and Cost Saving                                          | 86 |

|        | 4.4.3   | Full-Chip Timing Improvements                                                | 91 |

| 4.5    | Conclu  | usion                                                                        | 97 |

| Chapte | r 5: On | Legalization of Die Bonding Bumps and Pads for 3D ICs                        | 98 |

| 5.1    | Motiva  | ation                                                                        | 98 |

|        | 5.1.1                                                                                 | Via Overlaps with State-of-the-Art 3D flows |  |  |  |

|--------|---------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|

|        | 5.1.2                                                                                 | Source of Via Overlaps                      |  |  |  |

| 5.2    | Bump                                                                                  | /Pad Legalization Flow                      |  |  |  |

| 5.3    | Force-                                                                                | Based Via Legalization                      |  |  |  |

|        | 5.3.1                                                                                 | Forces Utilized                             |  |  |  |

|        | 5.3.2                                                                                 | Overall Execution                           |  |  |  |

| 5.4    | Bipart                                                                                | ite-Matching Grid Assignment                |  |  |  |

|        | 5.4.1                                                                                 | Algorithm                                   |  |  |  |

|        | 5.4.2                                                                                 | Machine Learning Tuning                     |  |  |  |

| 5.5    | Result                                                                                | s And Analysis                              |  |  |  |

|        | 5.5.1                                                                                 | Experimental and Technology Setup           |  |  |  |

|        | 5.5.2                                                                                 | Application in different types of 3D ICs    |  |  |  |

| 5.6    | Conclu                                                                                | usion                                       |  |  |  |

| Chapte | Chapter 6: A Logic-on-Memory Processor-System Design with Monolithic 3D<br>Technology |                                             |  |  |  |

| 6.1    | Mono                                                                                  | lithic 3D Integration                       |  |  |  |

|        | 6.1.1                                                                                 | Logic-on-Memory Monolithic 3D Partitioning  |  |  |  |

|        | 6.1.2                                                                                 | RTL-to-GDS Tool Flow For Monolithic 3D ICs  |  |  |  |

| 6.2    | Experi                                                                                | imental Setup                               |  |  |  |

|        | 6.2.1                                                                                 | Benchmark Architecture                      |  |  |  |

|        | 6.2.2                                                                                 | Design Setup                                |  |  |  |

|        | 6.2.3                                                                                 | Technology Setup                            |  |  |  |

| 6.3    | Design                                                                                | n and Simulation Results                    |  |  |  |

|        | 6.3.1 GDS Layouts                                                                                |

|--------|--------------------------------------------------------------------------------------------------|

|        | 6.3.2 Analysis                                                                                   |

| 6.4    | Conclusion                                                                                       |

| Chapte | r 7: Heterogeneous Monolithic 3D ICs: EDA Solutions, and Power, Per-<br>formance, Cost Tradeoffs |

| 7.1    | Technology Setup                                                                                 |

|        | 7.1.1 Cost Trends                                                                                |

|        | 7.1.2 Quirks of Heterogeneity                                                                    |

| 7.2    | Heterogeneous 3D IC Design Flow                                                                  |

|        | 7.2.1 Enhancing the Pin-3D Flow                                                                  |

|        | 7.2.2 Re-partitioning Using ECO                                                                  |

| 7.3    | Experimental Results                                                                             |

|        | 7.3.1 Methodology                                                                                |

|        | 7.3.2 Full-Chip PPAC                                                                             |

|        | 7.3.3 Analysis of clock, critical path, and memory connections 141                               |

| 7.4    | Conclusion                                                                                       |

| Chapte | <b>r 8: Conclusions</b>                                                                          |

| 8.1    | Machine Learning Integrated Pseudo-3D Flow for Monolithic 3D ICs 147                             |

| 8.2    | Pin-3D: An Effective Multi-Die Co-Optimization Methodology for 3D IC<br>Design                   |

| 8.3    | Metal Layer Sharing: A Routing Optimization Technique for Monolithic<br>3D ICs                   |

| 8.4    | On Legalization of Die Bonding Bumps and Pads for 3D ICs                                         |

| 8.5     | A Logic-on-Memory Processor-System Design with Monolithic 3D Tech-<br>nology           |

|---------|----------------------------------------------------------------------------------------|

| 8.6     | Heterogeneous Monolithic 3D ICs: EDA Solutions, and Power, Performance, Cost Tradeoffs |

| Referen | nces                                                                                   |

| Publica | <b>tions</b>                                                                           |

| Vita .  |                                                                                        |

## LIST OF TABLES

| 2.1 | Routing statistics of the Pseudo-3D and the final 3D routed designs 13                                                                                                                                                                                      | į |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2.2 | Input Features used to train the XGBoost model, and their importance and/or explanation                                                                                                                                                                     |   |

| 2.3 | R2 Scores and Mean Squared Error of Compact-2D (C2D) scaling and the best model for capacitance training                                                                                                                                                    |   |

| 2.4 | Permutation importance using RMSE loss of the 8 most important features per model. The RMSE loss of resistance model is $7.31 \times 10^{-2} \Omega$ , and capacitance model loss is $9.22 \times 10^{-4}$ fF                                               |   |

| 2.5 | Overall PPA of the test netlists with Circuit Agnostic ML Scaling, Compact-<br>2D Scaling, Circuit Specific ML Scaling Models                                                                                                                               | , |

| 3.1 | Qualitative comparison among state-of-the-art "Pseudo-3D" physical de-<br>sign tools for monolithic 3D ICs and this work. "enhanced die-by-die"<br>means the pins from both dies are visible during die-by-die optimization on<br>a complete 3D metal stack |   |

| 3.2 | Worst and Total Negative Slack Trend in Pin-3D, and the effect of the clock optimization stage for Cortex-A7. All slacks are normalized w.r.t the clock period                                                                                              | , |

| 3.3 | Pin-3D vs. Compact-2D [24] on different aspects of the 3D design. We useCortex-A7 in 28 nm.44                                                                                                                                                               | Ļ |

| 3.4 | Clock Tree structure and other related metrics of a netlist designed with and without fixing clock combinational cells on top-die                                                                                                                           | , |

| 3.5 | Efficiency of the Pin-3D optimization in timing closure. Critical parameters for Cortex-A7 are normalized w.r.t the 2D design                                                                                                                               | ) |

| 3.6  | 3D ECO optimization result on register-to-register paths using Pin-3D ECO.<br>We use Cortex-A7 in 28 nm.                                                                                                                                                                                              | 61 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7  | TSMC 28nm benchmark PPA comparisons among commercial 2D, Compact-2D [24], and Pin-3D optimized designs.                                                                                                                                                                                               | 62 |

| 3.8  | Cell Distribution by threshold voltage types in Cortex-A7 2D and Pin-3D designs. The threshold voltage types are labelled 1 (lowest $V_{th}$ ) — 4 (highest $V_{th}$ )                                                                                                                                | 63 |

| 3.9  | Top 100 critical path averages of register-to-register path group. The Cortex-<br>A metrics are normalized w.r.t the clock period.                                                                                                                                                                    | 63 |

| 3.10 | Impact on PPA with one metal layer removed                                                                                                                                                                                                                                                            | 63 |

| 3.11 | PPA results of our 45 nm+15 nm heterogeneous 3D IC design of 128-bit AES benchmark using Pin-3D. We use 2GHz as the target frequency of the whole design.                                                                                                                                             | 64 |

| 4.1  | Inter-cell routing layer usage in OpenPiton 2D IC used as a reference. A wire segment is a single continuous piece of metal routed in a straight line.                                                                                                                                                | 67 |

| 4.2  | Metal layer sharing in different 3D orientations using OpenPiton RTL.<br>#MIVs on 2D nets shows the amount of metal layer sharing                                                                                                                                                                     | 72 |

| 4.3  | Metal layer sharing in 3D partitioning options: Logic+Memory, Logic+Logic.<br>#MIVs on 2D nets shows the abundance of metal sharing in the designs                                                                                                                                                    | 78 |

| 4.4  | Metal layer sharing with F2B oriented Logic+Memory partitioning at dif-<br>ferent pitch values                                                                                                                                                                                                        | 80 |

| 4.5  | Metal Layer Usage of signal and power networks in the baseline 3D metal stack. Usage is calculated as the % of available tracks used for routing. Blocked Tracks is the % tracks blocked compared to total possible tracks in the footprint. Industry-A design is used for the following calculations | 83 |

| 4.6  | Design metrics of the three RTLs considered in our work. The designs are implemented in a F2B 3D fashion. These are the baseline designs for further comparisons                                                                                                                                      | 85 |

| 4.7  | Metal Layer Usage of signal and power networks with the reduced metal<br>layer stack with metal layer sharing. Industry-A design is used for the<br>following calculation. All the calculations are done same as from Table 4.5                                                                       | 86 |

| 4.8  | Routing Summary of the Industry-A design with different metal layer shar-<br>ing options. The two columns correspond to the Industry-A columns in Ta-<br>ble 4.9                                                                                                                                                                                                      | 89 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.9  | Max-performing design metrics of the three Industry RTLs with one fewer metal layer. For metrics reported as a $\Delta\%$ , the absolute value is calculated w.r.t. the baseline designs in Table 4.6. A negative value for $\Delta\%$ implies the current design (one metal layer removed, and metal layers shared) performs worse than the baseline and vice versa. | 92 |

| 4.10 | Timing Analysis of the Critical Paths and Clock Tree Results of Industry-A design                                                                                                                                                                                                                                                                                     | 93 |

| 4.11 | Energy Consumption per unit clock period at maximum frequencies for Industry-B design                                                                                                                                                                                                                                                                                 | 95 |

| 5.1  | 3D Via Overlaps using the two state-of-the-art 3D flows and varying pitches.                                                                                                                                                                                                                                                                                          | 99 |

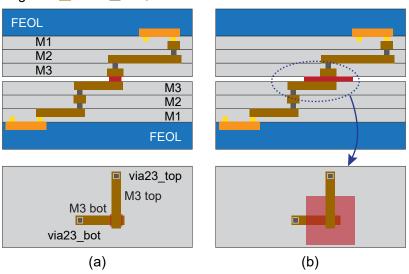

| 5.2  | Comparing BEOL dimensions in the 28 and 16 nm nodes. The metal (Mx) layer is directly beneath the 3D via                                                                                                                                                                                                                                                              | 01 |

| 5.3  | The six windowing parameters tuned with machine learning. The 3D via pitches are noted as $p_x, p_y$                                                                                                                                                                                                                                                                  | 07 |

| 5.4  | Displacement metrics before and after ten Bayesian optimization iterations.<br>The design has $\sim 6000$ vias to be legalized on a 5 µm pitch grid. The weights are $w_C=20$ , $w_D=10$                                                                                                                                                                              | 09 |

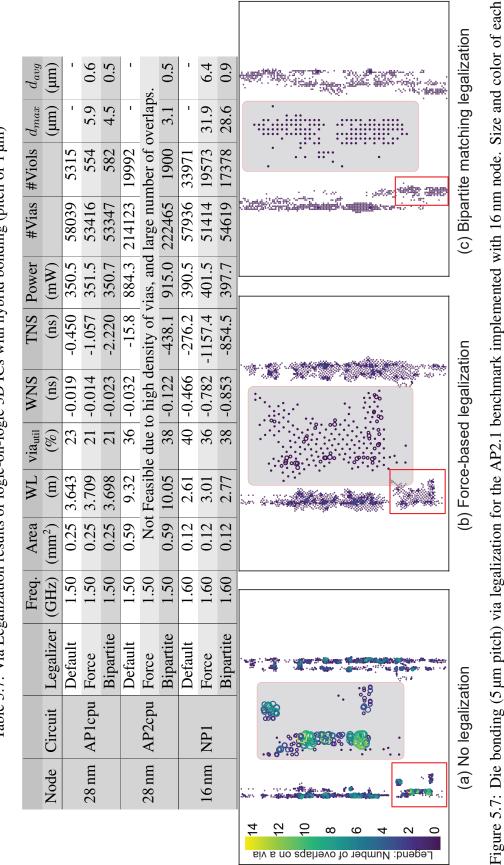

| 5.5  | Via Legalization results of memory-on-logic 3D ICs with hybrid bonding (pitch of $5 \mu m$ )                                                                                                                                                                                                                                                                          | 13 |

| 5.6  | Via Legalization results of memory-on-logic 3D ICs with micro bumping (10 µm pitch for AP2, 2.1; 20 µm for AP1)                                                                                                                                                                                                                                                       | 13 |

| 5.7  | Via Legalization results of logic-on-logic 3D ICs with hybrid bonding (pitch of 1 µm)                                                                                                                                                                                                                                                                                 | 14 |

| 6.1  | Max-performance comparison of the 2D and M3D designs of OpenPiton 1                                                                                                                                                                                                                                                                                                   | 22 |

| 6.2  | Iso-performance comparison of the Case-II (small memory architecture) 2D and M3D designs of single-tile OpenPiton                                                                                                                                                                                                                                                     | 23 |

| 7.1 | Cost Model Parameters and Assumptions [40]                                                                                                                                                                                                                                         |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.2 | "Qualitative" comparisons of expected PPAC behavior of the 5 technology<br>and design configurations at their expected maximum frequencies. 1 means<br>the worst, and 5 the best                                                                                                   |

| 7.3 | Impact of heterogeneous technology when input to driver of an FO4 is from different tier (see Figure 7.2(b)). Time is in ns, Power is in $\mu$ W, Voltage is in V                                                                                                                  |

| 7.4 | Improvements obtained with our heterogeneous version of Pin-3D flow [13] for the commercial CPU design                                                                                                                                                                             |

| 7.5 | PPAC results of our 3D Heterogeneous Designs (raw data based on a commercial foundry 28 nm technology)                                                                                                                                                                             |

| 7.6 | PPAC percentage delta (= $(3D \text{ hetero } - \text{ config}) / \text{ config} \times 100)$ of 3D heterogeneous design w.r.t. different homogeneous configurations. A -ve (+ve for PPC) value implies that heterogeneous implementation outperforms the particular configuration |

| 7.7 | Clock Network, Critical Path, Memory Interconnect analyses of the com-<br>mercial CPU design                                                                                                                                                                                       |

## LIST OF FIGURES

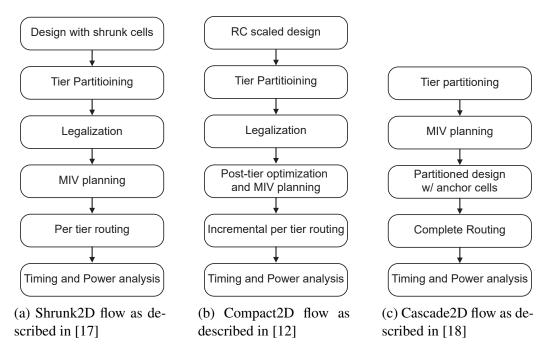

| 1.1 | Various Pseudo-3D Flows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Routing overhead of a 3D net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5  |

| 2.1 | Pseudo-3D flow and training from the corresponding features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10 |

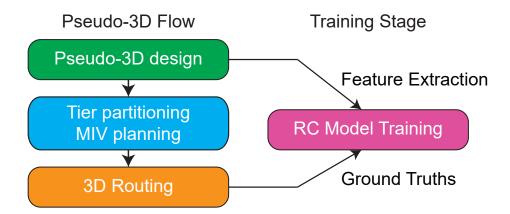

| 2.2 | (a) Capacitance, (b) Resistance of nets in the AES-128 design w.r.t. routed wirelength of the net. The data points are color coded according to the number of vias on each net.                                                                                                                                                                                                                                                                                                                                                                                                      | 14 |

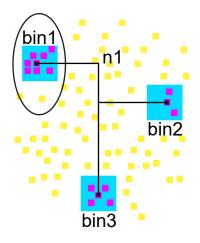

| 2.3 | Net and its connected cells (smaller squares). The local regions at each end point of the net are shaded in blue (larger squares). bin1 has a high cell density and the contained cell will be displaced during legalization after tier partitioning                                                                                                                                                                                                                                                                                                                                 | 15 |

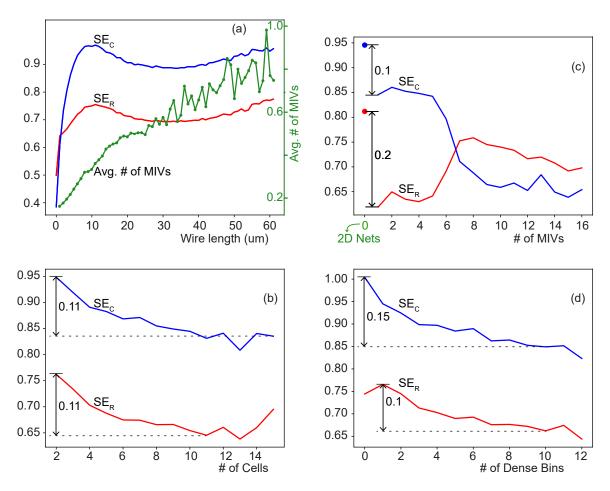

| 2.4 | Average RC scaling errors w.r.t. various net features. (a) Wire length, (b)<br>Number of MIVs on the net, (c) Number of cells connected to the net, (d)<br>Number of dense bins of the net                                                                                                                                                                                                                                                                                                                                                                                           | 17 |

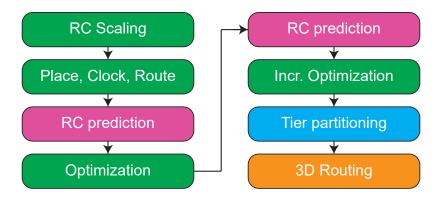

| 2.5 | Pseudo-3D flow with integrated RC prediction results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21 |

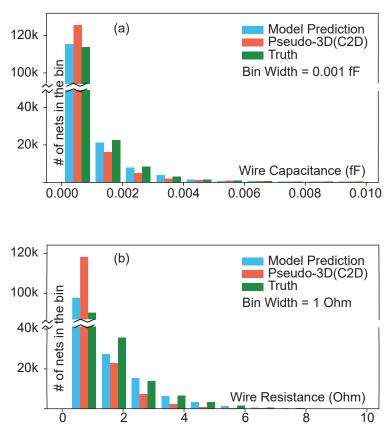

| 2.6 | RC Histograms of ML based implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 |

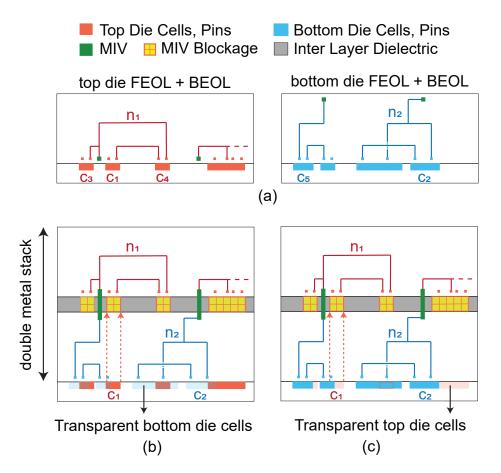

| 3.1 | The key idea of Pin-3D: die merging and pin projection. (a) top and the bot-<br>tom dies separately, (b) merged dies for the top die optimization, (c) merged<br>dies for the bottom die optimization. Our double metal stack contains pins<br>from both dies to provide the entire 3D context during die-by-die legaliza-<br>tion, routing, and timing closure. Top die cells are also projected to the<br>MIV layer to ensure no overlap between MIV and routed nets. Moreover,<br>Pin-3D allows design with two different technology nodes as demonstrated<br>in subsection 3.6.3 | 36 |

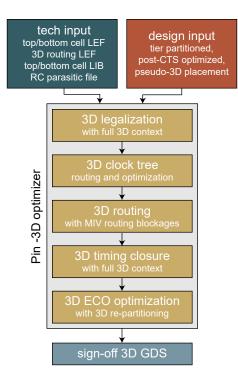

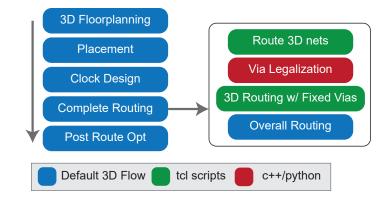

| 3.2 | Our Pin-3D optimizer design flow.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37 |

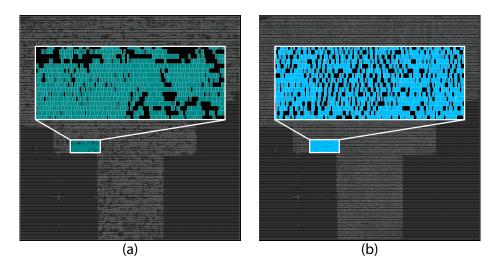

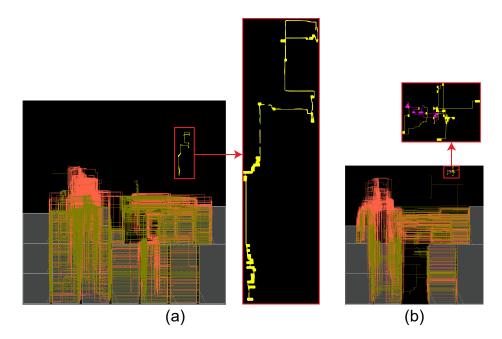

| 3.3 | Standard cell placement of Cortex-A7 and zoom-in at a specific location<br>using (a) Compact-2D legalization; (b) Pin-3D legalization. Dense cell<br>clusters is bad for M3D routing. Tier-partitioning and pre-legalized cell<br>placement is the same between the two.                   | 38 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

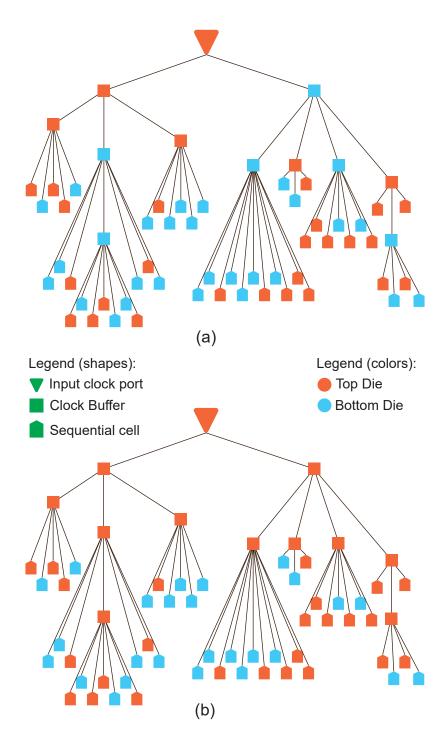

| 3.4 | Example Clock Tree Network showing input clock, clock buffers, and sequential cells. (a) Clock Buffers allowed to be placed on both tiers. (b) Clock Buffers moved to the top-tier                                                                                                         | 46 |

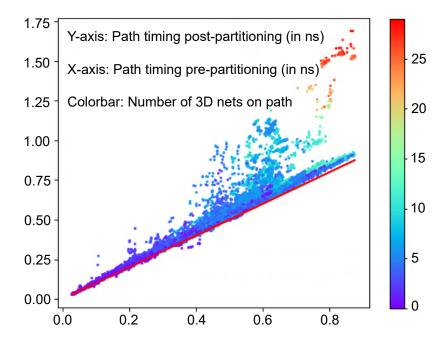

| 3.5 | Path delays of a design before and after tier partitioning. The red line represents the line along which the delays are equal i.e., the path timing does not change after partitioning                                                                                                     | 48 |

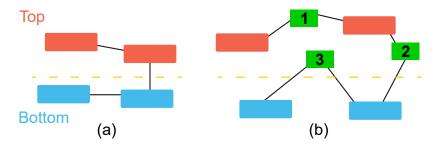

| 3.6 | Example logical connectivity of netlist (a) Before top die optimization, (b)<br>After top die optimization showing three different types (1, 2, 3) of buffer<br>insertions shown in green                                                                                                  | 49 |

| 3.7 | (a) Worst Negative Slack and (b) Total Negative Slack Trends during the three stages of Pin-3D optimization                                                                                                                                                                                | 50 |

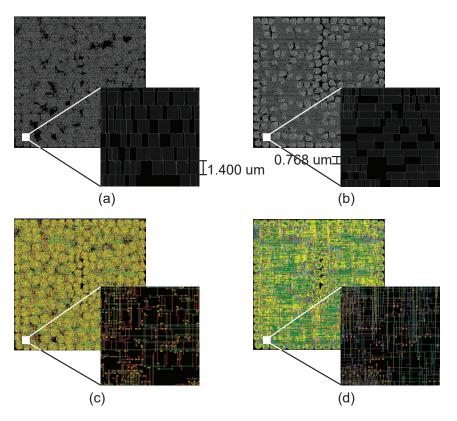

| 3.9 | Layout of our 45 nm+15 nm heterogeneous 3D IC design of 128-bit AES benchmark using Pin-3D. (a), (b) Full placement in top and bottom dies respectively along with standard row height (c), (d) Full routing of the top and bottom dies respectively with zoom-in windows for each         | 59 |

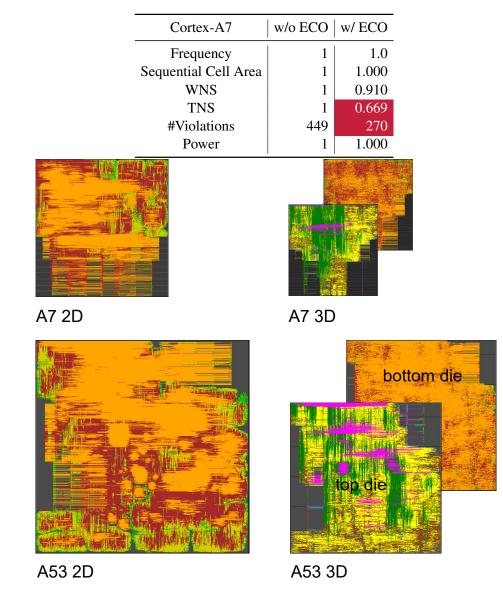

| 3.8 | GDS layouts of our Cortex-A7 and Cortex-A53 designs. For 3D designs, we show the placement for the top die, and the routing for the bottom die. We use a TSMC 28nm technology in all designs.                                                                                              | 61 |

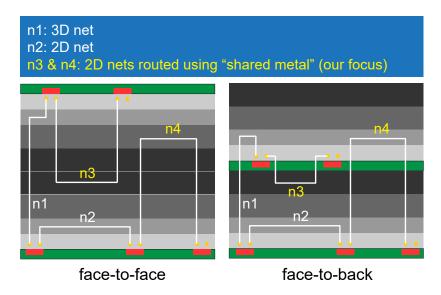

| 4.1 | Routing layer sharing in face-to-face and face-to-back 3D ICs. Green por-<br>tion represent the active FEOL layers, Gray represents the dielectric and<br>various routing layers. The darker shade corresponding to higher thickness,<br>pitch, and lower parasitic values of metal layers | 66 |

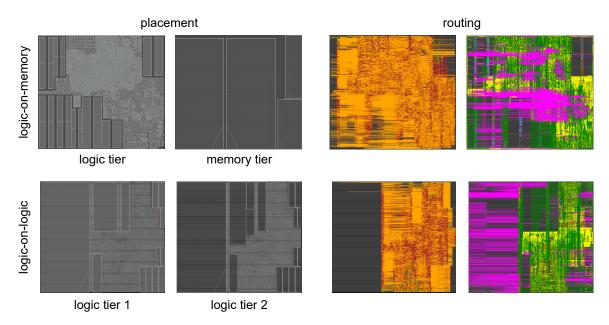

| 4.2 | Comparing tier partitioning impact on routing in OpenPiton. The place-<br>ment and routing layouts in the two tiers are provided for the two styles of<br>partitioning. Memory tier and Logic tier 2 are the bottom FEOL in their<br>corresponding designs.                                | 73 |

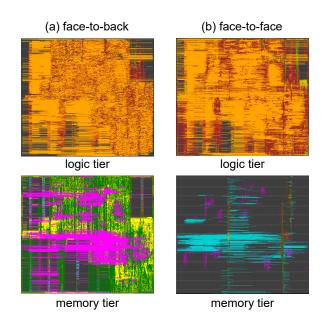

| 4.3 | Routing comparison between two bonding styles of Logic-On-Memory 3D ICs. (a) F2B, (b) F2F. The logic tier BEOL layouts are on the top, and memory tier BEOL layouts the bottom. Each color corresponds to a routing layer.                                                                 | 73 |

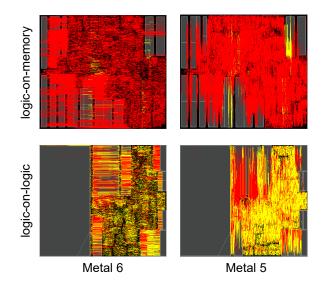

| 4.4 | Routing in shared metal layers of 3D OpenPiton design with F2B bonding style. We show M5 and M6 of the memory tier and logic tier 2. Red are routing with metal sharing, and yellow is everything else                                              | . 79  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

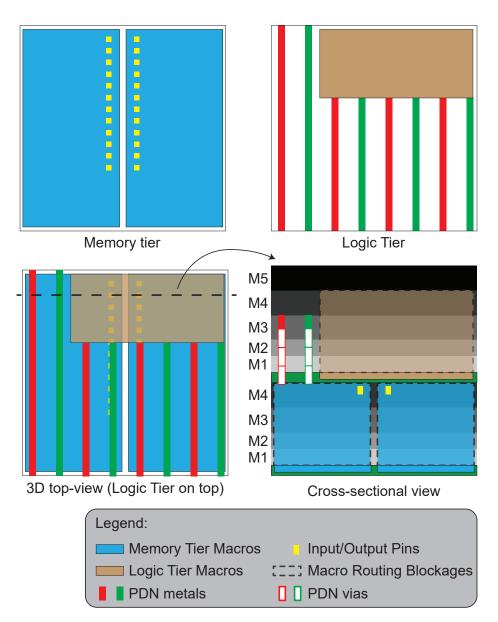

| 4.5 | Partitioning scenario showing the obstructions caused by memory macros with just 4 layers in the bottom BEOL. The Cross-sectional view is shown at the cut-line of the 3D view                                                                      | . 84  |

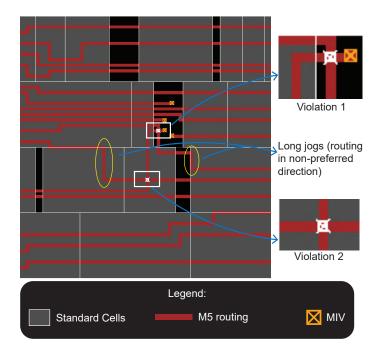

| 4.6 | Zoom-in shot of M5 routing in the metal layer sharing design. We can see the routing jogs and shorts in this layer                                                                                                                                  | . 90  |

| 5.1 | Using a commercial router to place face-to-face pads [13, 14]. (a) small F2F bond pad pitch, (b) large F2F pitch. The top-down views of the die interface are shown on the bottom.                                                                  | . 99  |

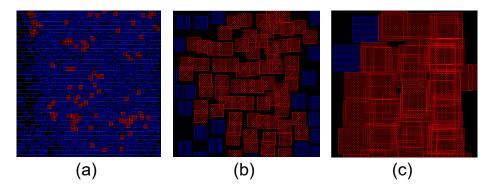

| 5.2 | 3D Via overlaps (shown in red) with different flows and pitch values from Table 5.1. (a) Pin-3D [13] 1 $\mu$ m pitch, (b) Macro-3D [14] 5 $\mu$ m pitch, (c) Macro-3D [14] 10 $\mu$ m pitch                                                         | . 100 |

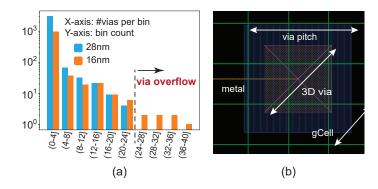

| 5.3 | (a) Via distribution of a design in two different process nodes. Each bin is $25 \mu m \times 25 \mu m$ , (b) Global cell grid (in green), 3D via, and metal layer in a 28 nm design.                                                               | . 101 |

| 5.4 | Design flow of a typical 3D IC design, and our modifications for inter-die pad/bump management.                                                                                                                                                     | . 102 |

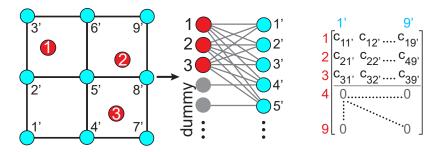

| 5.5 | Our high-level grid assignment formulation. Vias (in red) and manufac-<br>turing grid points (in blue) are transformed into a bipartite graph, whose<br>pairwise distances form the weight matrix, input to the LAP solver                          | . 104 |

| 5.6 | Divide-and-conquer using a sliding window. In each window, the grid as-<br>signment problem is solved optimally.                                                                                                                                    | . 107 |

| 5.7 | Die bonding (5 µm pitch) via legalization for the AP2.1 benchmark imple-<br>mented with 16 nm node. Size and color of each via represent the number<br>of overlaps. The gray rectangle shows the zoom-in of the highlighted vias<br>in the red box. | . 114 |

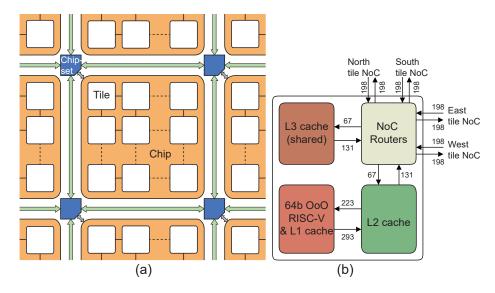

| 6.1 | OpenPiton architecture (a) full system (adopted from [30]), (b) single tile with data-flow width.                                                                                                                                                   | . 118 |

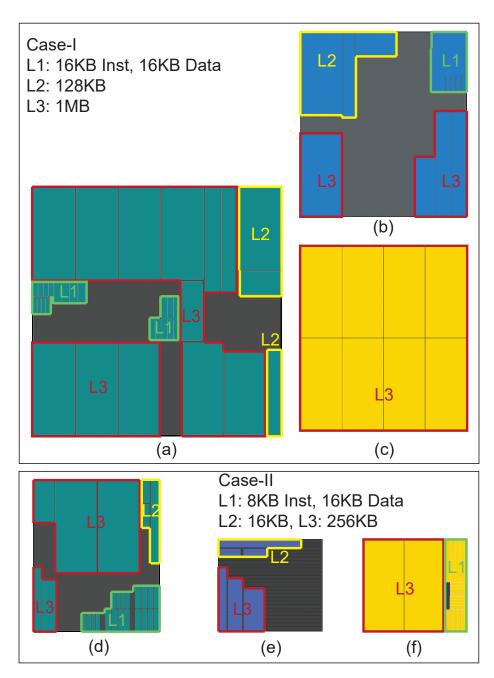

| 6.2 | Physical layout of the memory modules. Case-I designs: (a) 2D, (b) M3D top-die, (c) M3D bottom-die; Case-II designs: (d) 2D, (e) M3D top-die, (f) M3D bottom-die                                                                                                           |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.3 | GDS layouts of single-tile OpenPiton Case-I (= large) memory architecture.<br>(a) 2D, (b) M3D                                                                                                                                                                              |

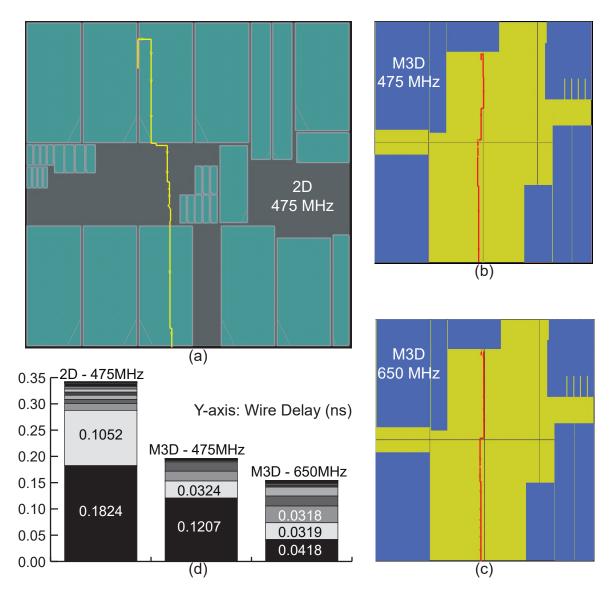

| 6.4 | Timing critical path of Case-I 2D memory architecture design in: (a) 2D at 475 MHz, (b) M3D at 475 MHz (iso-performance), (c) M3D at 650 MHz (max-performance). (d) Detailed delay breakdown of the path in the designs. 128                                               |

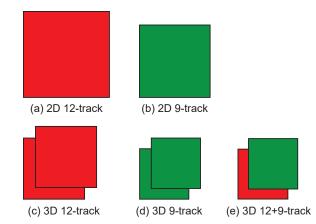

| 7.1 | 5 different configurations (to scale, assuming equal number of cells) of 2D and 3D using 9-track and 12-track cells studied in this work. We use commercial 28nm libraries                                                                                                 |

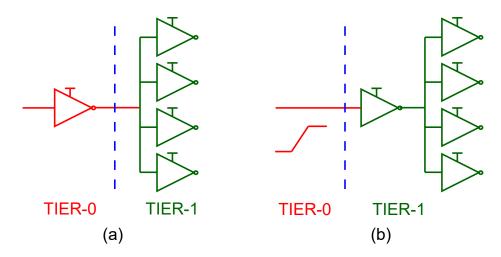

| 7.2 | The two types of boundary conditions due to heterogeneity in a FO-4 inverter. (a) Heterogeneity at driver output, (b) Heterogeneity at driver input. 133                                                                                                                   |

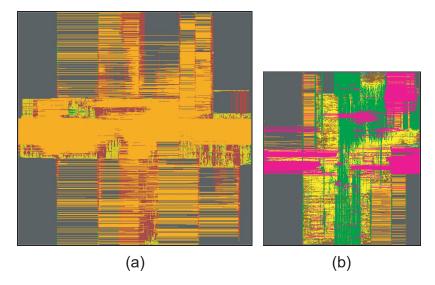

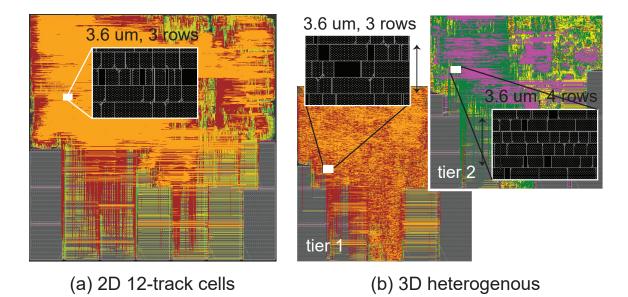

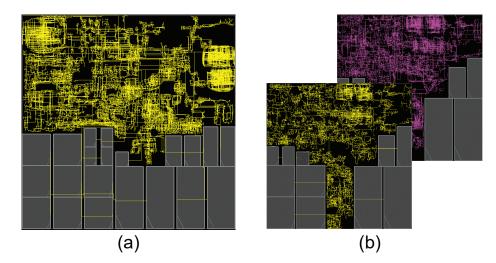

| 7.3 | Routing and zoomed placement GDS layouts of our commercial CPU. (a) 2D 12-track, (b) 3D heterogeneous, where tier 1 is using 12-track cells and tier 2 9 track cells                                                                                                       |

| 7.4 | Timing critical paths and memory nets of (a) 12-track 2D, (b) Heteroge-<br>neous 3D implementations of the CPU design. Yellow: 12-Track tier wires<br>and cells, Magenta: 9-Track tier wires and cells, Dark Red: memory output<br>nets, and Dark Green: memory input nets |

| 7.5 | Clock tree layouts of (a) 12-track 2D, (b) Heterogeneous 3D implemen-<br>tations of the CPU design. Yellow: 12-Track tier clock wires, Magenta:<br>9-Track tier clock wires                                                                                                |

#### **SUMMARY**

The objective of this research is to explore and exploit novel design configurations possible with 3D ICs. Furthermore, several tool flows and algorithms were developed to augment and capitalize on the commercially available Electronic Design Automation (EDA) tool flows to support our exploration. While most of the technological assumptions made in our work were in early stages of research, we also develop new flows to refine the 3D IC routing with commercially available 3D IC fabrication techniques.

# CHAPTER 1 INTRODUCTION

Technology scaling predicted by Moore's law [1] is gradually slowing down and new alternatives to silicon-based transistors are being explored. Some of the most promising solutions make use of materials such as carbon nanotubes [2] or ferroelectrics with negative capacitance effects [3]. While these materials bring improvements to the actual transistor structure, Three Dimensional (3D) Integrated Circuit (IC) Design is another such alternative [4] for going beyond the Moore's Law that operates orthogonally to the transistor material improvements. 3D integration improves power, performance, and area (PPA) by stacking multiple smaller 2D dies vertically instead of using a single 2D die with a larger footprint. This leads to shorter interconnects and adds an extra degree of placement freedom in the z-direction along with the traditional x,y-directions.

#### 1.1 Fabrication and Packaging Techniques for 3D ICs

There are three main types of 3D ICs based on the fabrication or bonding techniques [5]: Monolithic 3D ICs (M3D IC), hybrid bonded 3D IC, micro-bump 3D IC.

**Micro-bumping** is a die-level 3D packaging technique where two known good dies are bonded together using micro-bumps usually in the order of  $10 \,\mu\text{m}$  or larger. The large size of the bumps limits the number of bumps that can be used to connect the two dies and the high resistance and capacitance of the micro-bumps also limits the maximum connection speed achievable. While this is commercially most feasible, it can only be helpful in specific designs due to their limitations. **Hybrid bonding** uses direct Cu-Cu bonds with pitch values around 1  $\mu$ m at a wafer level to create the 3D IC. The smaller pitch significantly increases the allowed bandwidth between the two dies of the 3D design and is also quickly becoming a commercially available option. The fine-pitch for hybrid bonding at wafer level is still hard to accomplish with current technology processes and not many foundries offer this at present. But more research is being done into enabling sub-micron pitch for hybrid bonding [6] which can bring it to consumer electronics in the near future.

**Monolithic 3D IC** design is the most advanced technique for creating 3D ICs where the 3D ICs are directly fabricated unlike the packaging techniques of Micro-bumping and Hybrid-bonding. The different tiers of the 3D IC are sequentially fabricated on top of each other, removing the need for alignment of bumps/bonds. This can achieve an extremely fine via pitch of  $\approx 0.1 \,\mu\text{m}$ . While this shows the best-case scenario for 3D ICs, the process of fabricating dies on top of each other is extremely challenging with many limitations related to the thermal budget and the materials that could be used in the fabrication. In recent years, CEA-LETI showcased a significant breakthrough in low temperature fabrication of the devices that shows potential for M3D IC manufacturing to lead the 'More than Moore' era of computing [7]. This sequential fabrication allows for a nanometer scale pitch for 3D vias that can unlock a variety of 3D IC designs.

#### 1.2 Electronic Design Automation Flows for 3D ICs

To study the benefits and different characteristics of 3D ICs, Electronics Design Automation (EDA) tools are necessary for the placement, routing, and timing optimization of the 3D ICs. The commercially available tools such as Innovus from Cadence and IC Compiler from Synopsys do not natively support PnR for 3D ICs. As a result, two ways of tackling this issue have appeared. First is a more ground-level 3D implementation with placers such as [8, 9, 10, 11] that are mainly focused on improving the placement without regards to routing or the final Power, Performance, Area (PPA) results. On the other hand, tool flows such as [12, 13, 14] are used to develop a more holistic 3D IC design with Place and Route (PnR), and timing optimization using tweaks to the available commercial 2D PnR tools. Partitioning algorithms such as [15, 16] help to consider the 3D nature of the placement in such tool flows.

#### 1.2.1 Placement in the Three Dimensional space

The academic placers take several heuristics to create the 3D IC placement. The authors in [11] perform 3D placement using a force-based algorithm that models connecting wires as a springs, and local cell density as a repelling force. The 3D placement in [9] is done based on partitioning based algorithms, that recursively partition the netlist structure and assign them to ever smaller areas, until the size of a partition makes the placement trivial. In [10], analytical solvers are employed for the 3D placement that minimize the wirelength while satisfying some density and overlap constraints. And finally, the authors in [8] perform placement by treating cells as charged particles and employing electrostatic field solvers to find the least placement of standard cells in a 3D space that has the least electric potential. While these placements might preform better at metrics like wirelength or the number of 3D-vias, they fail in terms of PPA when compared to the routing or timing driven placement of commercial tools.

#### 1.2.2 Pseudo-3D Place and Route Flows

A tight integration between placement and routing, timing optimization is required to achieve good Power, Performance, and Area (PPA) of any IC. "Pseudo-3D flows" such as [17, 12, 18] have been proposed that utilize the commercial 2D EDA capabilities to 3D ICs. In a pseudo-3D flow, 3D designs are built using an "intermediate 2D design" and then partitioned into multiple tiers and routed to obtain the final 3D design. The placement in such flows transforms a 2D optimized placement into a placement for 3D IC designs.

Figure 1.1: Various Pseudo-3D Flows

**Shrunk2D** [17] is the first RTL-to-GDSII tool flow that creates near-optimal M3D designs using 2D EDA tools. The width and height of the standard cells are first shrunk by a factor of  $1/\sqrt{2} = 0.707$  thereby halving the area of standard cells (Hence the name Shrunk2D). With the shrunk dimensions, all the cells fit in a floorplan half the area of a 2D floorplan with the same cell density of a normal 2D design. With the halved footprint, the distance between cells in an M3D design is approximately  $0.707 \times$  of 2D designs which gives a theoretical wirelength savings of  $\sim 30\%$ . The shrunk design can be treated as a proxy for M3D design because the cell distances are almost equal to that of the M3D design is still considered 2D and all the optimization capabilities of a commercial EDA tool such as cell sizing, buffer insertion, removal, routing, power optimization, timing closure etc., can be leveraged. This concludes the 'pseudo-3D' stage of the flow.

The intermediate shrunk2D design falls short as a proxy for 3D designs in some key aspects. In the original shrunk2D flow presented in the paper [17], the wire widths and pitches are scaled by a factor of 0.707 to allow for routing on a smaller footprint. In

Figure 1.2: Routing overhead of a 3D net

this case, the authors did not consider the change in wire parasitics due to the geometry scaling. In [19] the authors address this issue to create better RC-lookup tables so that the parasitics in the shrunk2D stage mirror the parasitics in the M3D design. Correct parasitic estimation is necessary for EDA engines to optimize M3D designs. Another drawback is that the shrunk2D flow does not provide optimization after tier partitioning meaning that the cell movement during legalization and the routing overhead of 3D nets(Figure 1.2) are not considered.

**Compact2D** [12] is another RTL-to-GDSII tool flow. Compact2D simply scales the RC parasitics of the wires linearly without shrinking any geometry. This RC shrinking is a proxy for the 3D parasitics to be represented in the 2D footprint. Once the design is optimized, the cells are then mapped to a halved footprint by linearly scaling the x, y coordinates. The 3D cell placement is then achieved in the same fashion as shrunk2D using bin-based FM min-cut partitioning.

The second big improvement of compact2D is its post-partitioning optimization, as it re-optimizes the whole design after tier-partitioning to consider the cell movement during legalization and the 3D net overhead. The design is therefore optimized with 3D overhead and 3D metal layer structure in consideration. There still remain a few drawbacks in Compact2D as the linear scaling of parasitics is inaccurate as the scaling depends on characteristics of the net. While the post-partitioning optimization helps fix the timing and power, the representation of the design at this stage leaves some design rule violations in the routing, and does not fully support a 3D clock tree optimization.

**Cascade2D** [18, 20] is a different type of 3D RTL-to-GDSII flow where the z-location(tier assignment) of the cells are determined before performing x-y optimization unlike the previous two flows. The 3D connections are treated as special kind of cells, and a co-iterative placement of the standard cells and the 3D cells in the two dies create the placement. Unlike Shrunk2D or Compact2D flows, the availability of z-location allows the authors to create a better pseudo-3D stage that considers the different peculiarities of 3D connections. The drawback here is that the partitioning cannot be dense as it can negatively impact the pseudo-3D representation, limiting its usage in densely connected designs. Additionally, the PPA quality is significantly affected by the partitioning which needs to be done based on the detailed micro-architecture and data-flow analysis.

#### 1.3 Organization

The main contributions of this dissertation encompass three different themes. The first theme corresponds to *the design of better EDA design flow and heuristics* in chapter 3 and chapter 2. Here we tackle the issues of current pseudo-3D flows to create a more robust and efficient 3D IC. The second theme comprises of chapter 4 and chapter 5 where we specifically deal with the *routing in 3D IC designs*. We thoroughly analyze the different routing structures in 3D, identify potential issues with routing in advanced nodes and propose refinements to address such problems. Finally, the last theme corresponds to *the exploration of 3D IC arrangements* in chapter 6 and chapter 7. A specific partitioning type that can immensely benefit from 3D ICs is discussed in chapter 6, and a novel heterogeneous technology scheme for 3D ICs is discussed in chapter 7.

While the different chapters can be treated as a part of an encompassing theme, they are self-contained as follows:

- In chapter 2, for the design of better EDA design flow: we propose a Machine Learning based prediction algorithm to decrease the discrepancy between the pre and post partitioned 3D design using regression models. Our proposed model is circuit-agnostic and its performance with respect to a circuit dependent model is also studied. Furthermore, more details on the behavior and analysis of the model is considered. Overall, we achieve significant reduction in the total negative slack of the test design (3x 16x) using the machine learning model integrated pseudo-3D flow at the expense of just -1 to 4 % increase in total power.

- In chapter 3, *for the design of better EDA design flow*: we present incremental placement, clock optimization, complete routing, and timing optimization flows for 3D ICs. Using technology file hacks, we load the complete 3D design at once including the physical and logical connectivity of the netlist and library cell timing without causing cell overlaps. This helps with better 3D optimization, as well as 3D ECO for manual changes to the design. With Pin-3D, we were able to achieve a 10× smaller total negative slack compared to the recent flows that do not support 3D timing closure. The improved placement and routing flows also produce up to a 9% further reduction in wirelength in 3D. Compared to 2D IC designs, the 3D designs with Pin-3D flow have 9-32% power reduction due to 3D wirelength savings of 24-38% including a 17-33% reduction in the leakage power. Overall compared to 2D, the reduction in Energy Delay Product of 3D ICs is between 18% to 28% depending on the design.

- In chapter 4, *for the analysis and enhancement of routing in 3D IC designs*: we analyze and quantify a specific kind of routing novel to 3D ICs. While many recent studies have shown the benefits of 3D IC design on timing and power consumption

of circuits, routing in 3D is solely done with the automatic commercial routers and has not been well studied. In this paper, we show that 3D routing is far from simple and discuss the various routing scenarios in 3D that arise from the cell partitioning and the 3D metal layer stack. Unlike 2D, the metal layer configuration in 3D depends on the orientation of the dies that are bonded together. Due to this, depending on the 3D configuration, cells in one tier tend to use routing layers from the other tier. This is referred to as Metal Layer (or) Routing Sharing which depends on the metal layer stack and the cell partitioning in 3D, as well as the via pitch used for 3D connections. By analyzing metal layer sharing in detail, we see that it can help reduce metal layer costs in 3D, as well as improve the power consumption, and in some cases, the maximum achievable performance of the circuits. Overall, the 3D BEOL cost can decrease by 9% along with an improved Power Delay Product of up to 7.5% just from the routing sharing in Monolithic 3D ICs.

- In chapter 5, *for the analysis and enhancement of routing in 3D IC designs*: we identify the problem of routing in 3D IC designs with commercially viable bonding types and/or advanced technology nodes. State-of-the-art 3D IC Place-and-Route flows fail to honor the 3D via spacing rules when realistic pitch values are used. Here, we propose an added 3D via legalization stage during routing to reduce such violations. A force-based solver, and an ML-guided bipartite-matching algorithm are presented as viable legalizers compatible with various process nodes, bonding technologies, and partitioning types. With the modified 3D routing stage, we reduce the via overlap violations by more than 10x without any performance, power, or area impact.

- In chapter 6, *for the exploration of 3D IC arrangements*: we present the benefits of M3D ICs using OpenPiton, a scalable open-source RISC-V based multi-core SoC.

With a logic-on-memory 3D integration, we analyze the power and performance

benefits of two OpenPiton single-tile systems with smaller and larger memory architectures. The logic-on-memory M3D design shows 37% performance improvement compared to the corresponding tile design in 2D. And at iso-performance, M3D shows 14% total power saving.

- In chapter 7, *for the exploration of 3D IC arrangements*: we explore a novel heterogeneous design of Monolithic 3D ICs along with crucial design flow enhancements and better partitioning methods. The heterogeneous M3D ICs are designed with a combination of low-cost, low-power, and low-performance cells on one die and a higher-cost, power, and performance technology variant on the tier, for heterogeneity. These heterogeneous designs out-perform most 2D, 3D variants in Power-Delay Product and Cost metrics. Using 4 different netlists, we see up-to 23% improvement in Performance per Cost, and 16% improvement of Power Delay Product with heterogeneous M3D compared to the best 2D designs.

- Finally, in chapter 8, we summarize all of our results and benefits from each chapter.

#### **CHAPTER 2**

# MACHINE LEARNING INTEGRATED PSEUDO-3D FLOW FOR MONOLITHIC 3D ICS

In this chapter, we present a machine learning integration framework for pseudo-3D flows such as [12, 17]. Better estimations of RCs early in the design stage will improve the final PPA in general. In the pseudo-3D flows for 3D ICs in particular, this RC estimation becomes more important as the timing optimization is exclusively done in the pseudo-3D stage. The 3D parasitics depend on a lot of variables as will be discussed later in subsection 2.1.2, and so a machine learning framework is well suited to learn the different interactions of the net features to estimate the 3D R and C values.

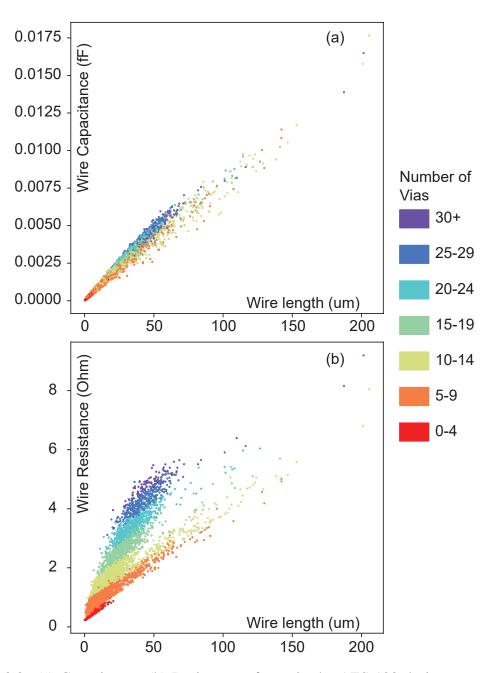

We use a total of 12 memoryless logic RTL downloaded from opencores, ISPD contests [21, 22, 23]. These are designed with a 28 nm commercial technology node. For all the 2D designs, 6 metal layers are used for signal routing. 3D designs have two tiers and a total of 12 signal routing layers (6 per each die). All the machine learning implementation are done with python3.6.

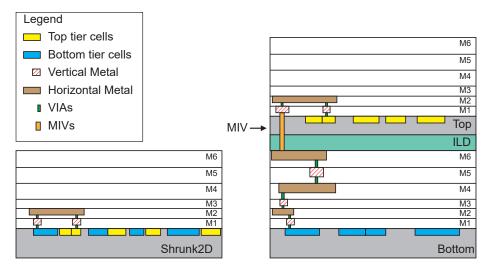

Figure 2.1: Pseudo-3D flow and training from the corresponding features

#### 2.1 RC Analysis

#### 2.1.1 RC breakdown of a net

In a GDS layout of an RTL, the nets are complex 3D structures whose parasitics depend on the exact shape of the net as well as the overall BEOL(Bottom-End-of-Line) dielectrics, neighboring nets. But such detailed analysis require a significant amount of time for 3D extractions and spice simulations. So the commercial EDA tools use several assumptions and simplifications to achieve a trade-off between accuracy and run-time.

Consider a rectangular wire of width W, thickness T, length L, at a distance H from the ground plane. The resistance and ground capacitance are given by  $C_{wire} = \frac{\epsilon_d WL}{H}$ ;  $R_{wire} = \frac{\rho L}{WT}$ , where  $\epsilon_d$  is the dielectric constant of the dielectric between the wire and the ground plane. While the resistance model is fairly simple, the total capacitance is much more complex with contributions from fringing effect of the ground capacitance, and coupling capacitance. Modern day IC designs also use multiple layers of metals and the  $W, T, H, \epsilon_d, \rho$  can be different for the different metal layers. In an EDA tool, it is not feasible to calculate these capacitances from just the physical dimensions, and material properties. So, an RC look-up table is provided by the technology foundry containing pre-calculated unit length ground capacitance, coupling capacitance, and resistance values of the wires (denoted by lower-case c, r in this paper), and the vias at different scenarios (width, thickness, spacing, temperature, etc.) for each metal layer. The total resistance, and capacitance of a net with wires of length  $l_{M_i}$  on metal layer  $M_i$ , and  $n_{V_i}$  number of vias of type  $V_i$  is given by:

$$C_{net} = \sum_{M_i} c_{M_i} l_{M_i} + \sum_{V_i} c_{V_i} n_{V_i} + XCap$$

(2.1)

$$R_{net} = \sum_{M_i} r_{M_i} l_{M_i} + \sum_{V_i} r_{V_i} n_{V_i}$$

(2.2)

where X cap is the cross coupling capacitance between the *net* and the neighboring nets in the design.  $c(r)_{M_i}$  is the capacitance (resistance) of a wire of length 1 µm, and  $c(r)_{V_i}$  is the capacitance (resistance) of a via of type  $V_i$ . Note that there can be multiple types of vias from metal layer  $M_i$  to  $M_{i+1}$ . Coupling capacitance of the net is dependent on the final routing. While most of the nets have a negligible coupling capacitance, the nets that are routed in congested areas can have majority of the total capacitance as the coupling capacitance.

#### 2.1.2 RC Evolution from Pseudo-3D to Final-3D designs

As Compact-2D's pseudo-3D stage works under the assumption that the wire RCs scale down by a factor a  $\frac{1}{\sqrt{2}}$  when the design is converted from pseudo-3D to 3D stage. So, the scaling factor is applied in the pseudo-3D stage. This assumption is true in an ideal case, but the discrete row placement of cells and complex routing algorithms of commercial tools create variations in the scaling factor. Even in a global sense, the overall RC reduction is rarely as expected. Furthermore, the global scaling is applied only considering the length reduction portion in (Equation 2.1), (Equation 2.2). Number of vias on a net is much harder to predict as the routing in pseudo-3D (6 metal layers total) and final-3D (12 metal layers total) is very different. The contact resistance of vias keep increasing in smaller technology nodes, and ignoring the via resistance on the overall resistance can cause inconsistencies in the resistance of nets from the pseudo-3D to final-3D stages. In the technology node considered here, the unit values for metal layer 4 are as follows:  $c_{M_4} \approx 0.20 \text{ fF}/\mu\text{m}$ ,  $c_{V_4} \approx$  $0.02 \text{ fF}/\mu\text{m}$ ,  $r_{M_4} \approx 10.0 \Omega/\mu\text{m}$ ,  $r_{V_4} \approx 8.0 \Omega/\mu\text{m}$ . It is clear that the contact resistance is significant even in the relatively older 28 nm node, considering the total wirelength and via count in Table 2.1

To further analyze the RC evolution in a design implementation, we design AES-128 circuit in pseudo-3D and final-3D stages. Some of the useful metrics from this implementation is shown in Table 2.1. Note that the wire length, ground capacitance, wire resistance are considerably underestimated in the pseudo-3D stage. Via Count increases by ~ 17.5%, but the global scaling  $(\frac{1}{\sqrt{2}})$  performed is suitable for a ~ 30% reduction in the via count.

|                                            | Pseudo-3D | Final-3D  |

|--------------------------------------------|-----------|-----------|

| Footprint (mm <sup>2</sup> )               | 0.228     | 0.114     |

| Metal Stack                                | 6 Layers  | 12 Layers |

| Wire length <sup>†</sup> ( $\mu$ m)        | 1,141,179 | 1,234,332 |

| Via Count                                  | 872,931   | 1,028,040 |

| Ground Capacitance <sup>†</sup> (pF)       | 119.34    | 140.83    |

| Coupling Capacitance <sup>†</sup> (pF)     | 35.20     | 31.71     |

| Wire Resistance <sup>†</sup> (M $\Omega$ ) | 15.26     | 21.23     |

Table 2.1: Routing statistics of the Pseudo-3D and the final 3D routed designs

<sup>†</sup> Wire length, Capacitance, Resistance values of pseudo-3D are scaled by  $\frac{1}{\sqrt{2}}$  to show a clear representation of the estimations

This increase in 3D is due to the halved footprint (or number of tracks per layer) and twice the number of vertical layers compared to a 2D or pseudo-3D implementation.

The scatter plot of the wire parasitics as a function of the routed wire length are in Figure 2.2 visualizes a couple of trends. One, the wire resistance can be given by a set of linear functions of the wire length, whose slope is fixed and intercept increases with the number of vias on the net. Two, the via capacitance has a negligible impact on the total wire capacitance. Three, the resistance and capacitance are linear functions of the total routing on separate metal layers. This is due to the fact that the unit RC values for the 1–6 metal layers in the considered commercial technology node are very close to each other. The difference between routing in pseudo-3D and final-3D means that the via count in pseudo-3D cannot be directly used as a proxy for the final-3D via count. But it provides a new point of information for the machine learning algorithm. In later sections, we show that via count indeed has useful information regarding final 3D parasitics by verifying the null hypothesis probability.

From the stages shown in Figure 2.1, the tier partitioning and 3D routing changes layout after the pseudo-3D stage. Within tier partitioning, cell legalization is performed to get a clean placement solution in two tiers. As the location mapping from a larger 2D footprint to an halved 3D footprint in compact-2D creates cell overlaps. Additionally in this work,

Figure 2.2: (a) Capacitance, (b) Resistance of nets in the AES-128 design w.r.t. routed wirelength of the net. The data points are color coded according to the number of vias on each net.

Figure 2.3: Net and its connected cells (smaller squares). The local regions at each end point of the net are shaded in blue (larger squares). bin1 has a high cell density and the contained cell will be displaced during legalization after tier partitioning

instead of legalizing the cells independently in each tier, we perform an incremental placement similar to the proposed solution in [13]. This allows for a better placement quality as die by die legalization does not consider the PPA impact. Based on cell placement and net connectivity, nets undergo different amounts of cell movement during the tier partitioning. Figure 2.3 shows an example of a net and neighboring cells. Features such as the local density in a small neighborhood to the end-points of nets can be used to learn the extent of cell movement each net undergoes.

During 3D routing, the nets are fully modified. Based on the routing, nets can be grouped into three categories as follows:

- Single-tier nets are the ones where the 3D routing is done entirely within top or bottom tier. These are expected to undergo the least amount of change from pseudo-3D stage as they are still routed within the 6 signal routing layers.

- **Multi-tier nets** are the nets connecting cells from different tiers after the partitioning. These have the highest difference in routing between the two design stages, as they need to be routed vertically for a proper connectivity. These would have increased wirelength and number of vias that will affect capacitance and the resistance of the nets.

• Finally, the last group are the **nets that use metal-borrowing**. Consider a net that is connecting to cells entirely within the top tier. When performing 3D routing, some of these nets can use metal layers belonging to a different tier. This is called metal layer borrowing, and such nets would have a medium variation in the parasitics in 3D.

To quantify the impact the tier partitioning and 3D routing have on the nets and to understand the extent of this impact from different net features, the following metric is useful:

$$\frac{\text{res}(\text{cap}) \text{ of net}(s) \text{ in pseudo-3D}}{\text{res}(\text{cap}) \text{ of the net}(s) \text{ in final-3D}} = \text{Scaling Error of R, C}$$

represented as  $SE_{R(C)}$ . This shows how well the scaling in pseudo-3D corresponds with the final 3D RCs.

Scaling error can also be defined for a group of nets by using the sum of R, C values in the numerator and denominator of the fraction.  $SE_{R(C)} \approx 1$  of a group of nets implies that the scaling done in the pseudo-3D stage is close to accurate for the group.

$SE_{R(C)} \ll 1$  for a group of nets means that the estimation in pseudo-3D is much lower than the final 3D for this group. This results in worse timing after the design is 3D routed. Identifying such group of nets using combination of net is useful in properly applying scaling factor. Most of the nets in a design would fall in this group as the pseudo-3D is usually optimistic.

$SE_{R(C)} \gg 1$  occurs when the parasitic value in pseudo-3D is over-estimated. Cells on these nets would be over-sized in pseudo-3D. These cells not only consume additional but also manifests as an additional capacitance load to the connected cells.

Grouping the nets using net metrics like routed wirelength, fan-out/number of connected cells, number of MIVs, local cell density near the cells, we plot the scaling error variation of these groups in Figure 2.4.

In Figure 2.4(a), the nets are grouped based on the routed wire length. All the nets with

Figure 2.4: Average RC scaling errors w.r.t. various net features. (a) Wire length, (b) Number of MIVs on the net, (c) Number of cells connected to the net, (d) Number of dense bins of the net

wire length  $[x, x + 1)\mu m$  are put into group x. Based on this, the average scaling error of R, C, and the MIV counts are plotted. Number of MIVs is dependent on many different features such as cell count, overall connectivity graph, bin size chosen etc. In order to observe the impact of just wirelength, the other features are kept constant for this plot by only considering nets with fan-out 2 in the implementation of aes-128 with fixed bin-size. This shows how wirelength can impact the 3D routing (specifically the average number of MIVs). The average number of MIVs in each group increases as the pseudo-3D wirelength keeps getting higher. Net groups with at least a 1000 nets are considered to reduce volatility in the plot.

More importantly, we observe the scaling error of resistance and capacitance of these groups. This follows a slightly more complex trajectory. The scaling error plots are much smoother by the virtue of central limit theorem as we consider significantly more number of nets. It is interesting to note that none of the groups have an average scaling error > 1 in line with our claim that pseudo-3D under-represents the final RC values. Misrepresenting the via calculation causes the resistance to be significantly under valued. Overall, the scaling error vs. wire length plots have two main trends: a steep increase at lower values  $0 \le x < 10$  followed by a saddle-like shape for 10 < x < 60.

At  $0 \le x < 10$ , the scaling error values are the most i.1. Since these nets are smaller, small perturbation during legalization and routing changes can cause a relatively significant increase in the final parasitics and so the SE < 1. As the nets become relatively large, the net are more likely to be partitioned (as evident from the avg. MIV count plot) and 3D routing is now going to have a higher impact adding more RCs in final 3D that were unaccounted for. This shows us up as the decrease in SE. And as the net length keeps on increasing, the pseudo-3D RCs increase at a rate higher than the impact of 3D routing, so the SE increases again. This interaction between the pseudo-3D RCs and the additional 3D touring manifests as the saddle shape. With a relatively low noise, this allows us to learn a scaling model as a function of routed wirelength.

Extending a similar analysis to the number of cells connected to a net vs.  $SE_{R(C)}$  gives us the plot in Figure 2.4(b). These plots are close to monotonically decreasing. This shows that a highly connected net is more likely to have higher discrepancy between the pseudo-3D and final-3D stages. This is a direct result of the bin-based Fiduccia-Mattheyses partitioning done in pseudo-3D flow.

**Bin-based Fiduccia-Mattheyses partitioning** In this partitioning, placement layout is first divided into smaller rectangular bins and then each bin is partitioned into two tiers such that the area of cells in the two tiers is the same within a tolerance threshold. In any hypergraph partitioning, the nets with high fanout are more likely to be partitioned. For example, a net with c' cells connected has  $2^c$  ways being split into two partitions. Apart from the two solutions where all the cells in either of the partitions, the other  $2^c - 2$  solutions have a cut-size of 1 net. So, once such a net is forced to not be partitioned leaves the solution space almost unchanged with different configurations achieving same result. So, it is not a good move to keep a highly partitioned net constrained to a single partition as we might miss the chance of finding a better cut-size solution. So, a highly connected cell is more likely to be partitioned under hyper-graph partitioning.

With this knowledge of hyper-graph partitioning, it is easy to see the reason for the monotonically decreasing plots in Figure 2.4(b). As discussed in the wirelength analysis, a partitioned net will have increased parasitics in 3D and since the groups are not directly dependent on wirelength, the numerator (pseudo-3D parasitic value) cannot compensate for the increase in the 3D parasitics unlike in Figure 2.4(a).