# DESIGN OF BALUNS AND LOW NOISE AMPLIFIERS IN INTEGRATED MIXED-SIGNAL ORGANIC SUBSTRATES

A Dissertation Presented to The Academic Faculty

by

Vinu Govind

In Partial Fulfillment Of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

Georgia Institute of Technology

August 2005

#### Design of Baluns and Low Noise Amplifiers in Mixed-Signal Organic Substrates

Approved by:

Dr. Madhavan Swaminathan, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Rao R. Tummala School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. James S. Kenney School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Abhijit Chatterjee School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Suresh K. Sitaraman School of Mechanical Engineering *Georgia Institute of Technology*

Date Approved: July 18, 2005

To Achan & Amma

### **ACKNOWLEDGEMENTS**

As an old Malayalam song goes, "*Karmam cheyyuka nammude lakshyam*, *Karma phalam tharum Eeshvaranallo*" ("Act, for it is man's duty to act, but seek not the results of the action, for that is God's will alone"). I'd like to thank the Almighty for all his blessings so far, and pray for his continued benevolence.

It is with great gratitude that I thank Prof. Swaminathan, for guiding me through the intricacies of graduate research and for instilling in me the importance of hard work and long-term vision. Being part of his group has exposed me to the values of teamwork, as well as provided opportunities to attend various conferences and workshops. I would also like to thank my Committee members Dr. Tummala, Dr. Kenney, Dr. Chatterjee and Dr. Sitaraman, for being patient with me and providing support when I needed it the most.

I would like to thank members of the Epsilon group, the Packaging Research Center and Dept. of ECE for their friendship and for the valuable contributions they made towards this work. Jinwoo, Sung Hwan, Nanju, Souvik, Wan Suk, Amit, Hideki-san, Jifeng, Bhyrav, Rohan, Prathap, Sung Jun, Woopoung, Joe, Raghavan, Sandeep, Dev, Dr. Raj, Krishna, Erdem, Jinseong and Joongho, you guys made graduate life a lot of fun with your friendship. Thank You! Dr. Sid Dalmia provided much help and guidance over the last four years, both professionally and personally. Thank you! Dr. Marshall Leach and Ms. Gail Palmer ended up being more friends than tutors. Thank you! Good friends are hard to find. I would like to thank Swami, Arvind and Anand. Without your help and support, this could have been quite a difficult journey. Thanks are also due to members of the JMD team, who encouraged and helped me complete this work - Dr. White, Venky, Winston, Jim, Andy, Jeff, Jack, Charlie, Larry, Semyon, Camil, Chris, Fred, Jim, James, Ramsay and Trish.

I count it a privilege to have known Mr. K. P. P. Nambiar. Growing up in Kalliasseri, it felt good to know that people from similar backgrounds had gone out and made a difference in the world. And without his guidance at critical points in my life, who knows how things might have turned out. Thank you, Sir.

Finally, family. To Achan and Amma, who taught me the virtues of hard work and dedication, who worked hard to provide for me what they themselves never had, who made sacrifices that I only later appreciated, who gave me the confidence to reach for the stars, Thank you! To Cheriyammon and Kunjammon, who had more faith in my abilities than I myself did at times, Thank you! To Sneha, Abhijith and little Arya, who in one way or another bore the brunt of having a brother/brother-in-law/uncle who did not have much time for socializing, Thank you! To Bilsi, who tolerated seven months of solitude as I finished up this thesis, Thank you! And to everyone else from Kannapuram/Ezhome/Palakkad whose support I could always count on, Thank you!

# TABLE OF CONTENTS

| Acknowledgements                                          | iv   |

|-----------------------------------------------------------|------|

| List of Tables                                            | X    |

| List of Figures                                           | xi   |

| Summary                                                   | xvii |

| Chapter 1: Introduction                                   | 1    |

| 1.1. Multiband Radio Architectures                        | 4    |

| 1.2. Mixed-Signal Integration                             | 8    |

| 1.2.1. Low Temperature Co-fired Ceramic (LTCC) Technology | 13   |

| 1.2.2. Organic Technology                                 | 16   |

| 1.3. Organic SOP-Based Mixed-Signal System Integration    | 21   |

| 1.3.1. Design of Multiband RF Components                  | 23   |

| 1.3.2. Design Partitioning                                | 24   |

| 1.3.3. Measurement and Analysis of Signal Coupling        | 26   |

| 1.3.4. Research Objectives                                | 27   |

| 1.4. Research Accomplishments                             | 32   |

| 1.4.1. Original Contributions                             | 34   |

| Chapter 2: Design of Baluns for Multiband Radios                     | 37 |

|----------------------------------------------------------------------|----|

| 2.1. Multiband Baluns                                                | 38 |

| 2.1.1. Theory                                                        | 43 |

| 2.1.2. Design                                                        | 48 |

| 2.1.3. LCP Based SOP Technology for Large Area Manufacturing         | 49 |

| 2.1.4. Fabrication and Measurements                                  | 52 |

| 2.2. Extension of the Theory of Multiband Marchand Baluns – Wideband |    |

| Singleband Baluns                                                    | 57 |

| 2.2.1. Design, Fabrication and Measurements                          | 57 |

| 2.3. Narrowband Lumped-Element Baluns                                | 64 |

| 2.3.1. Design                                                        | 65 |

| 2.3.2. Fabrication and Measurements                                  | 66 |

| 2.4. Summary                                                         | 71 |

|                                                                      |    |

| Chapter 3: Design of Filter-Balun Networks                           | 73 |

| 3.1. Baluns with Frequency Rejection                                 | 74 |

| 3.2. Cascaded Filter-Baluns                                          | 82 |

| 3.2.1. Implementation                                                | 83 |

| 3.3. Summary                                                         | 87 |

|                                                                      |    |

35

| Chapter 4: Design of Low Noise Amplifiers Using Embedded Passives | 88 |

|-------------------------------------------------------------------|----|

|-------------------------------------------------------------------|----|

| 4.1. Chip-Package Co-Design of CMOS LNAs                       | 91  |

|----------------------------------------------------------------|-----|

| 4.1.1. Noise Analysis                                          | 94  |

| 4.1.2. Inductor Optimization                                   | 97  |

| 4.2. Multiple Embedded Passives: Analog-Analog Signal Coupling | 103 |

| 4.2.1. Modeling – Using Field Solvers                          | 107 |

| 4.2.2. Modeling – Using Transmission Lines                     | 110 |

| Chapter 5: Digital-Analog Coupling in Mixed Signal Integration | 115 |

| 5.1. EMI Based Noise Coupling                                  | 119 |

| 5.1.1. Indirect Coupling                                       | 121 |

| 5.1.2. Direct Coupling                                         | 124 |

| 5.2. Power Supply Based Noise Coupling                         | 128 |

| 5.3. Electromagnetic Isolation                                 | 132 |

| 5.4. Mixed-Signal System Integration Using EBG-Based Power     |     |

| Distribution                                                   | 137 |

| 5.5. Wideband Noise Suppression                                | 142 |

| 5.6. Summary                                                   | 143 |

| Chapter 6: Conclusions and Future Work                         | 145 |

| 6.1. Future Work                                               | 147 |

|                                                                |     |

### Appendix A: Publications Resulting from this Research149

**Appendix B: Patents and Invention Disclosures Resulting from this**

| Research | 152 |

|----------|-----|

|          |     |

References

153

# LIST OF TABLES

| Table 1.1  | Comparison of discrete, SOC, LTCC, MCM-D/TFOS and SOP-L integration technologies.                                                                                                                                                                                                                                                                                                                         | 20  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1. | Measured performance of the balun.                                                                                                                                                                                                                                                                                                                                                                        | 55  |

| Table 2.2. | Performance summary of the balun, with a comparison with a commercially available Marchand balun from Anaren, Inc.                                                                                                                                                                                                                                                                                        | 63  |

| Table 2.3. | Performance summary of the balun, with a comparison with a commercially available LTCC balun (*Note: The Murata balun was chosen for comparison because it specs the lowest loss for an 0805 balun in the market today. However, the amplitude and phase imbalance information was not available for the LDB21G410C-001. Typical industry standard numbers have been used for the imbalance comparisons). | 70  |

| Table 3.1. | Measured performance of the filter-balun, with a comparison with<br>a commercially available LTCC filter-balun from Soshin.                                                                                                                                                                                                                                                                               | 86  |

| Table 4.1. | Survey of past work done on CMOS LNAs for long-distance communication protocols.                                                                                                                                                                                                                                                                                                                          | 91  |

| Table 4.2. | Variation of inductor Q with area.                                                                                                                                                                                                                                                                                                                                                                        | 100 |

# LIST OF FIGURES

. .

. .

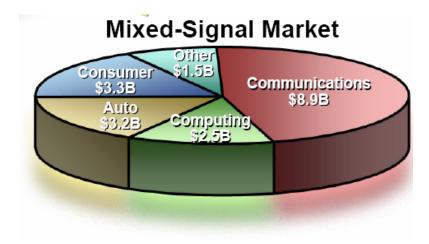

| Figure 1.1. | Global mixed-signal market, and its composition                                                                                                                                                                                                                                                                                                                                                              | 2  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

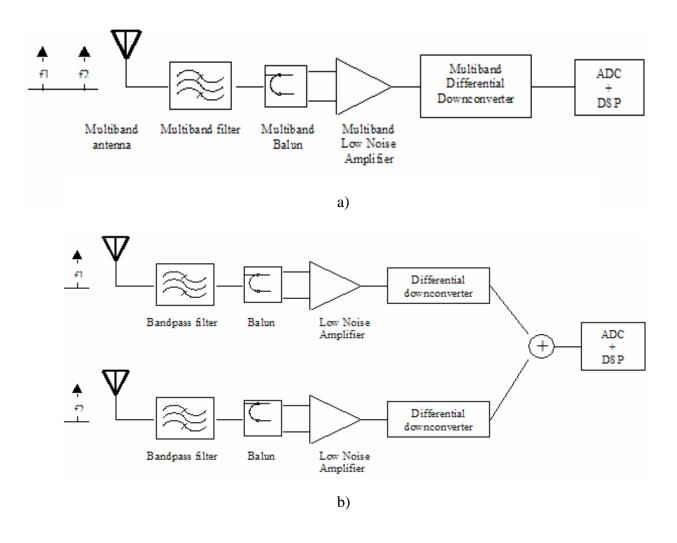

| Figure 1.2. | a) Multiband architecture, with each device operational at a single<br>band, and switching between frequency bands in the baseband. b)<br>Concurrent multiband architecture, with each component<br>functional at multiple frequency bands.                                                                                                                                                                  | 5  |

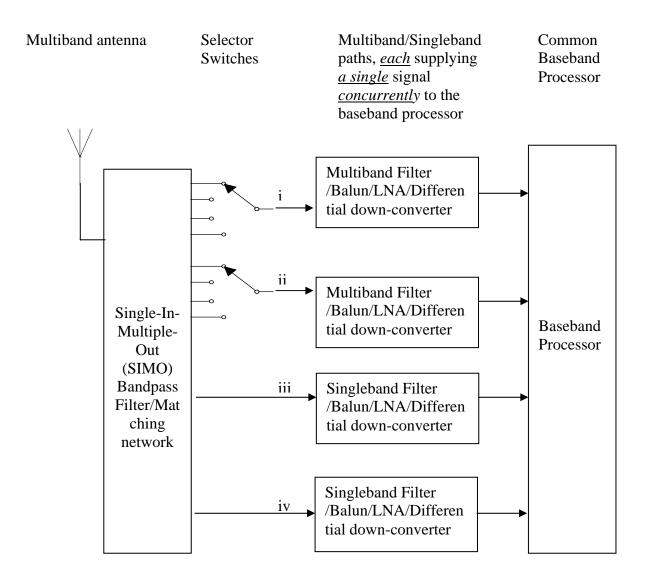

| Figure 1.3. | Switched semi-concurrent multiband receiver architecture, showing four paths with each path supplying one signal concurrently to the baseband processor. Paths (i) and (ii) are multiband in functionality, with the selector switch between the SIMO filter and the rest of the front-end circuitry determining the choice of signal to pass-through. Paths (iii) and (iv) are singleband in functionality. | 7  |

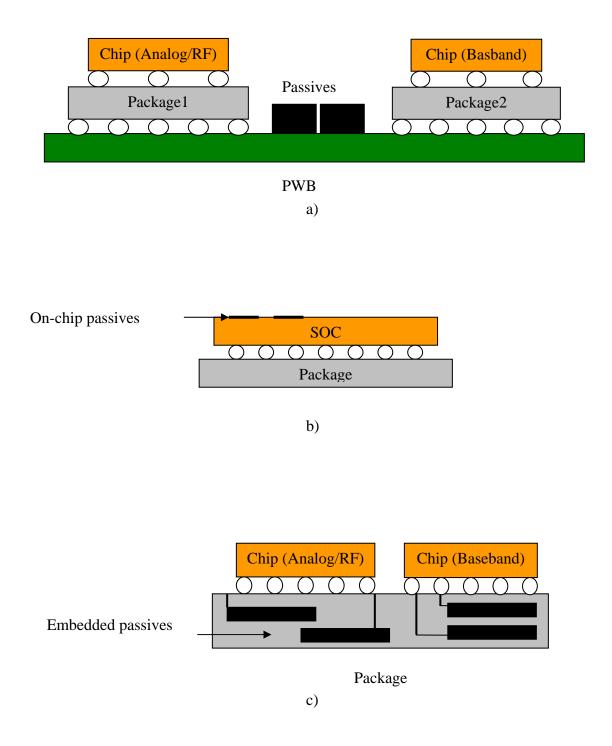

| Figure 1.4. | a) Printed Wiring Board (PWB) based integration, with packaged chips and passives assembled onto a PWB substrate b) SOC-based integration, with on-chip passives c) SOP-based integration, with embedded passives in the package.                                                                                                                                                                            | 12 |

| Figure 1.5. | LTCC based integrated Bluetooth transceiver module from Kyocera.                                                                                                                                                                                                                                                                                                                                             | 14 |

| Figure 1.6  | Embedded passives on <b>a</b> ) MCM-D substrate. b) TFOS substrate. c) SOP-L (Vialux <sup>TM</sup> ) substrate.                                                                                                                                                                                                                                                                                              | 17 |

| Figure 1.7. | Mixed-signal SOP-based test vehicle, with integration of semi-<br>concurrent multiband RF front-end and high-speed digital<br>computing.                                                                                                                                                                                                                                                                     | 28 |

| Figure 1.8. | SOP implementation, with heterogenous MCM-L substrate.<br>Multiple chips, some low-profile passive components and a few<br>discrete passives are attached to the top, and the whole structure is<br>overmolded.                                                                                                                                                                                              | 29 |

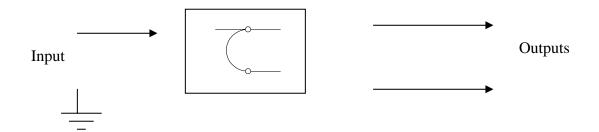

| Figure 2.1. | Functional representation of a balun.                                                                                                                                                                                                                                                                                                                                                                        | 37 |

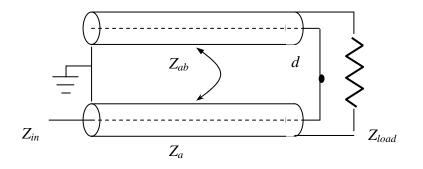

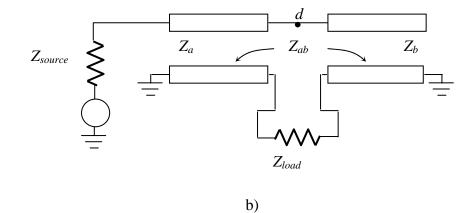

| Figure 2.2. | a) Coaxial balun b) Simplified schematic                                                                                                                                                                                                                                                                                                                                                                     | 39 |

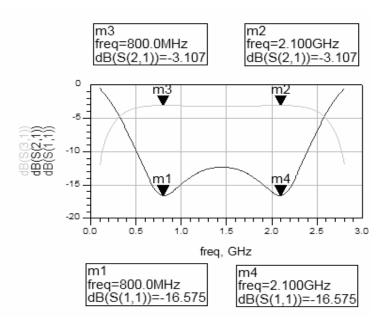

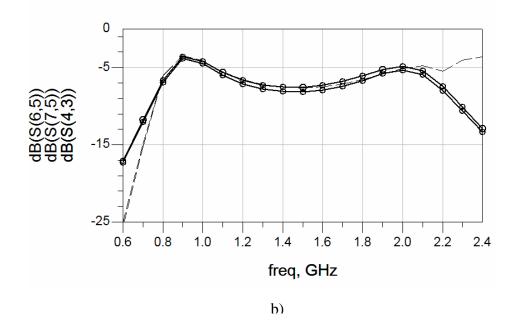

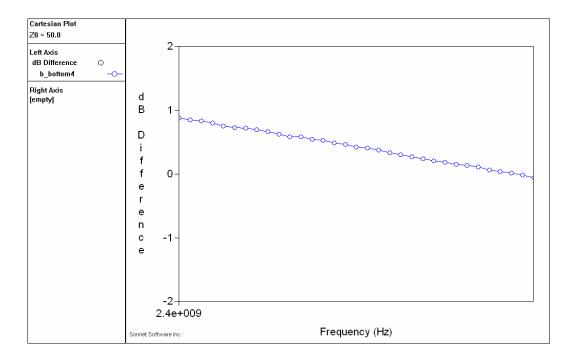

| Figure 2.3.  | S-parameter simulation of the balun showing input match (S11) and power loss (S21 and S31) in the 800 MHz and 2.1 GHz frequency bands.                                                                                    | 42 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

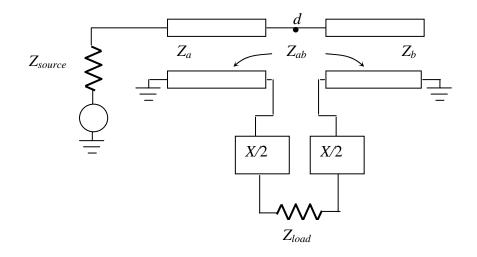

| Figure 2.4.  | Schematic of the new balun, with two frequency dependent impedances ( $X/2$ ) added in series with the load.                                                                                                              | 43 |

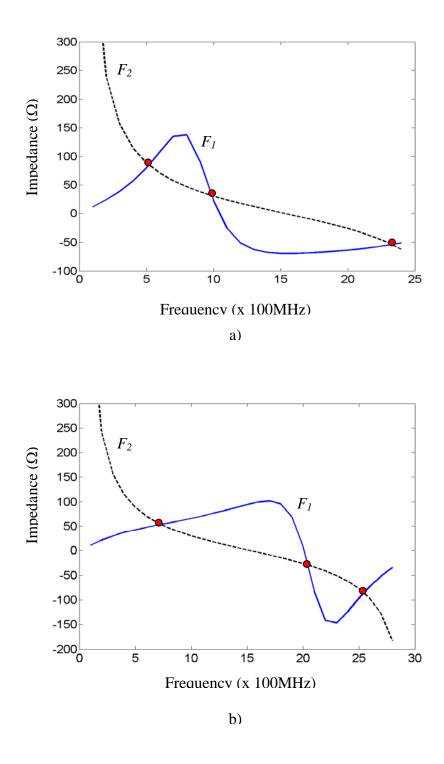

| Figure 2.5.  | Plot of $F_1(\theta)$ and $F_2(\theta)$ with respect to frequency a) X=1.5pF b) X=10nH                                                                                                                                    | 46 |

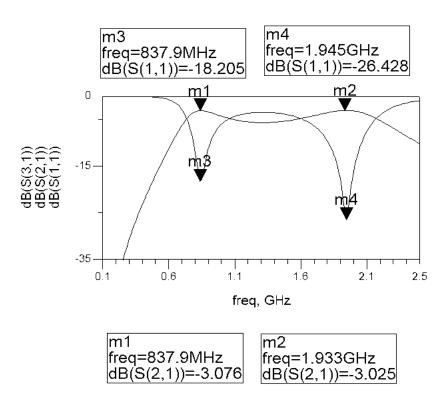

| Figure 2.6.  | S-parameter simulation of the balun, showing input match (S11) and power loss (S21 and S31) in the 830 MHz and 1.93 GHz frequency bands.                                                                                  | 49 |

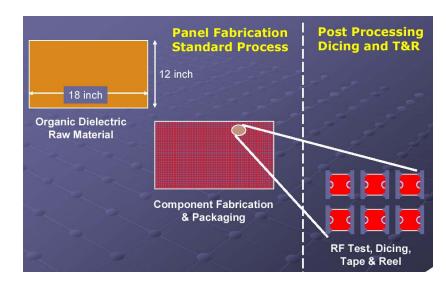

| Figure 2.7.  | Large area manufacturing process.                                                                                                                                                                                         | 50 |

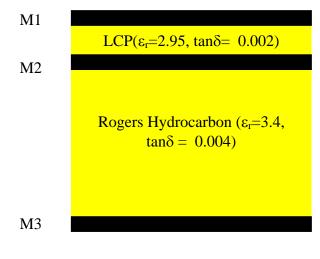

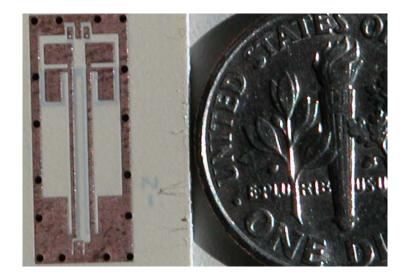

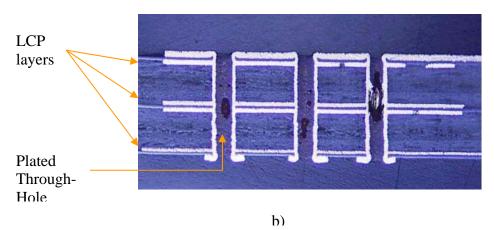

| Figure 2.8.  | a) 3-metal layer organic stack-up and b) photograph of the balun fabricated on LCP substrate. The device measures $1.5 \text{ cm x } 0.6 \text{ cm}$ , including the CPW ground rings and probe-pads.                     | 53 |

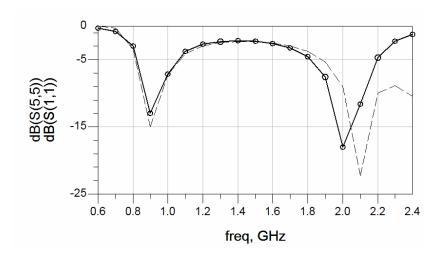

| Figure 2.9.  | Simulated (Sonnet) and measured results for the fabricated balun<br>a) Input match (S11) b) Power transfer (S21 and S31). Solid line<br>with dots represent measured values, dashed line represents<br>simulated results. | 54 |

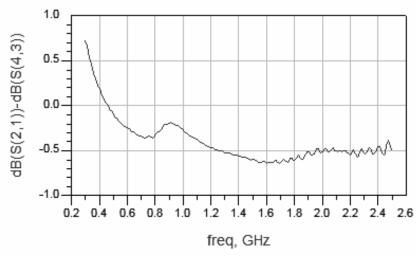

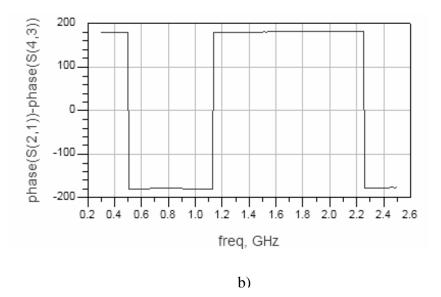

| Figure 2.10. | Measured a) amplitude and b) phase imbalance for the balun.                                                                                                                                                               | 56 |

| Figure 2.11. | a) Cross-section of the substrate. b) Photograph of a cross-section.                                                                                                                                                      | 58 |

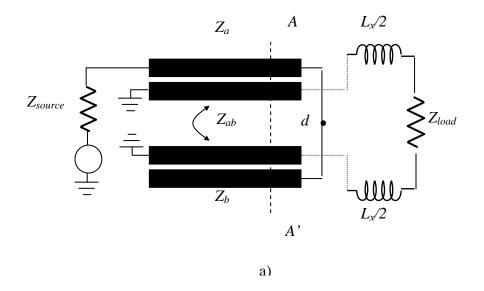

| Figure 2.12. | a) Layout of the planar balun, and b) the cross-section of the device cut along the A-A' axis.                                                                                                                            | 59 |

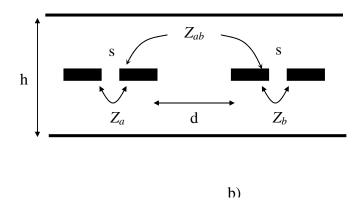

| Figure 2.13. | a) Plot of $\text{Im}(Z_d)$ vs. frequency showing the zero crossings (using the optimized values for $L_x$ and $Z_{ab}$ ) b) Variation of $S_{11}$ with frequency, calculated using (2).                                  | 60 |

| Figure 2.14. | Photograph of the balun.                                                                                                                                                                                                  | 61 |

| Figure 2.15. | Measured balun response a) $S_{11}$ , $S_{21}$ and $S_{31}$ b) amplitude and phase imbalance.                                                                                                                             | 62 |

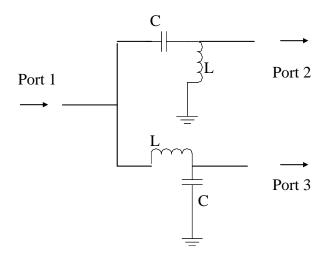

| Figure 2.16. | Lattice balun schematic.                                                                                                                                                                                                  | 66 |

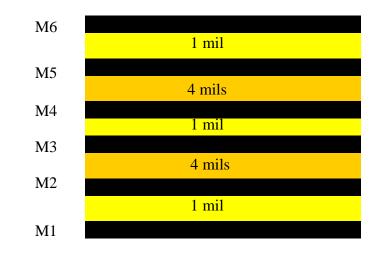

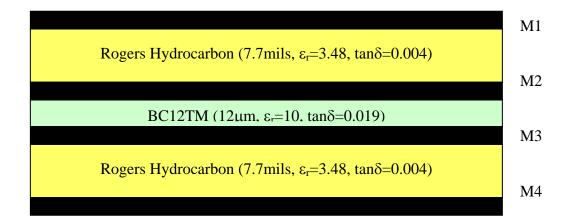

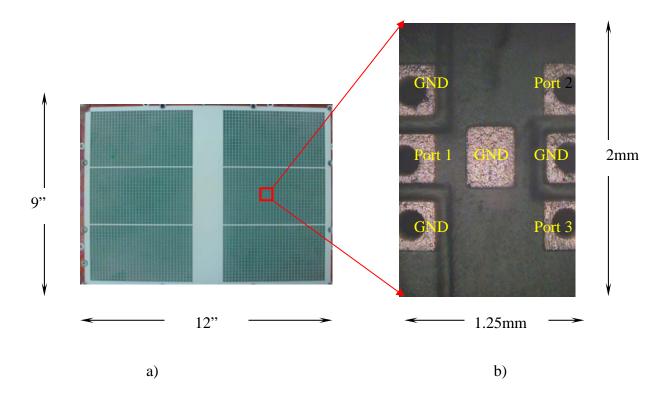

| Figure 2.17. | 4-metal layer stack-up with high-K dielectric layer.                                                                                                                                                                      | 67 |

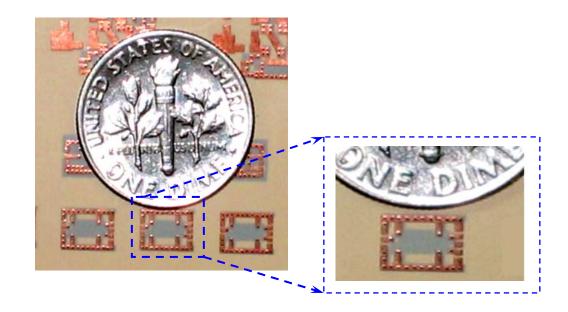

| Figure 2.18. | a) Photograph of the fabricated 9'x12' panel showing the baluns laid out in six coupons, and b) close-up of the device after dicing, showing the input and output ports. | 67 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

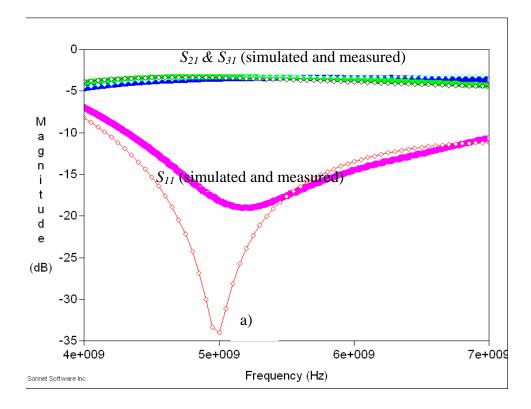

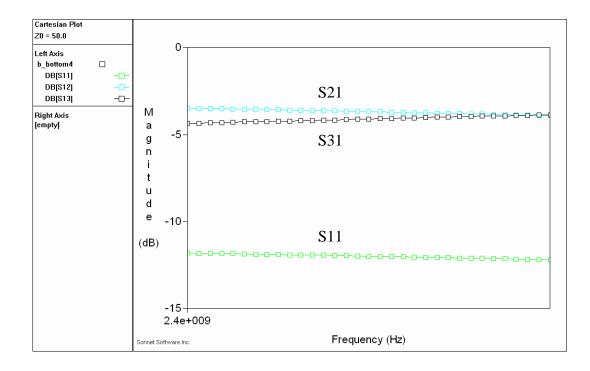

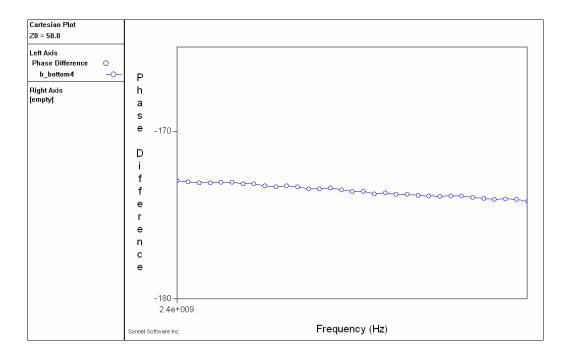

| Figure 2.19. | Measured values for S11, S21 and S31.                                                                                                                                    | 68 |

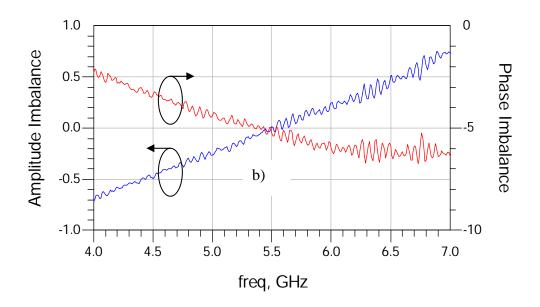

| Figure 2.20. | Measured values for a) Amplitude imbalance and b) Phase imbalance.                                                                                                       | 69 |

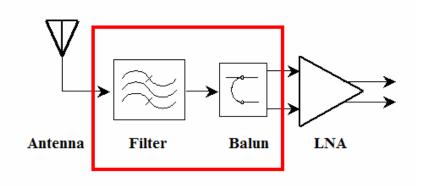

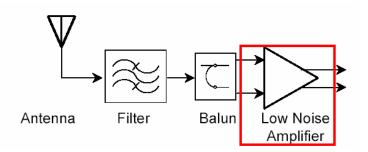

| Figure 3.1.  | Functional block diagram of a receiver showing the filter and balun.                                                                                                     | 73 |

| Figure 3.2.  | Lumped-element model of a capacitor.                                                                                                                                     | 75 |

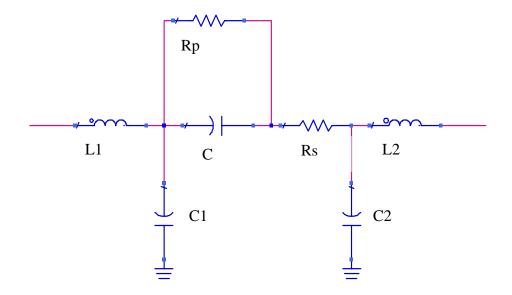

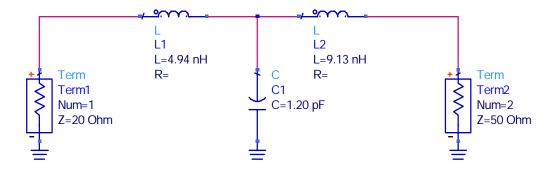

| Figure 3.3.  | Matching network schematic.                                                                                                                                              | 76 |

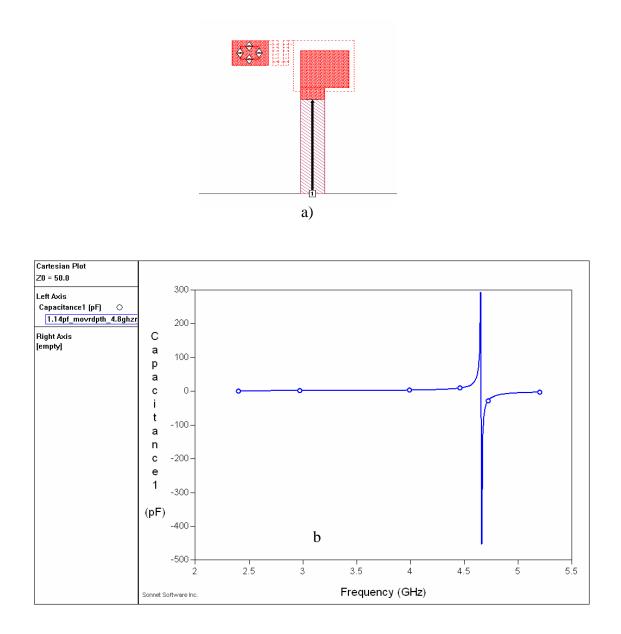

| Figure 3.4.  | a) 1.2pF capacitor layout, and b) simulated response                                                                                                                     | 77 |

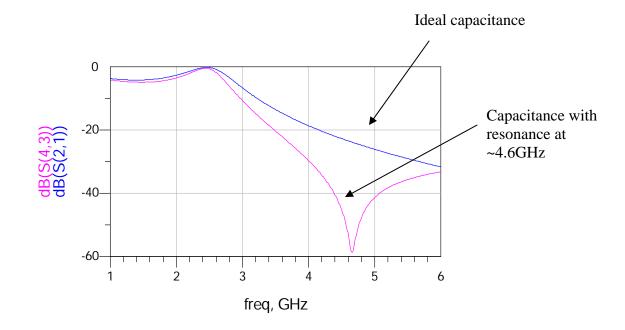

| Figure 3.5.  | Simulated response of the matching network, with without the capacitor resonance                                                                                         | 78 |

| Figure 3.6.  | Lattice balun with inductors and capacitors replaced with resonators.                                                                                                    | 79 |

| Figure 3.7.  | Simulated response of the balun.                                                                                                                                         | 79 |

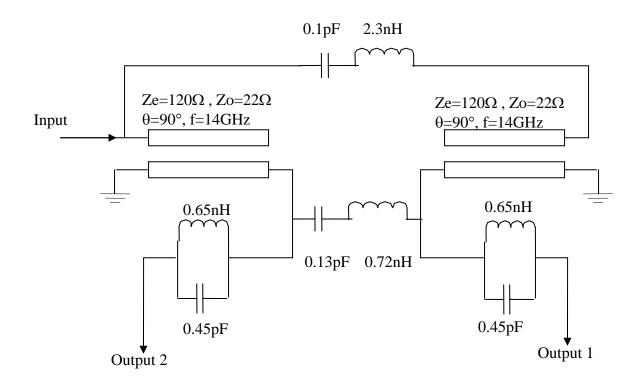

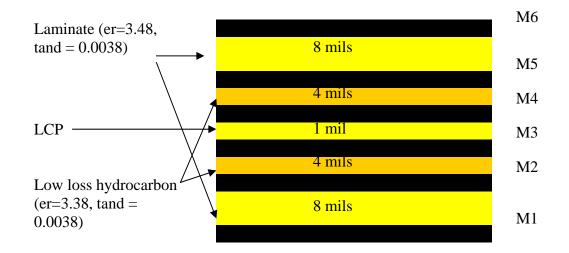

| Figure 3.8.  | Modified Marchand balun for operation in the 5-6GHz, with resonators for frequency selection.                                                                            | 80 |

| Figure 3.9.  | Simulated response (S21) of the balun.                                                                                                                                   | 81 |

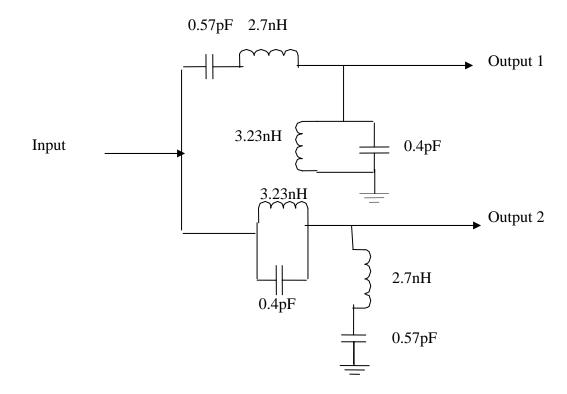

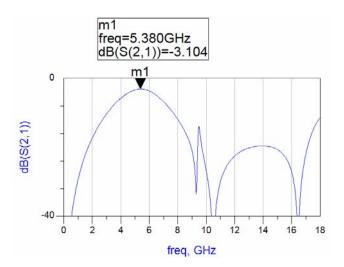

| Figure 3.10. | Filter-balun schematic.                                                                                                                                                  | 82 |

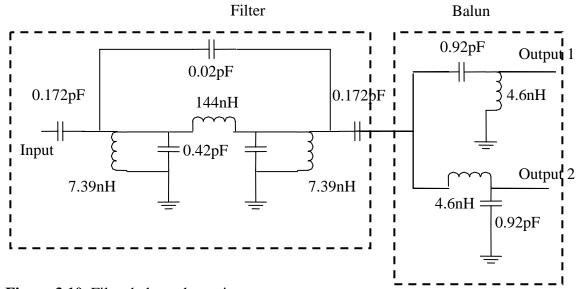

| Figure 3.11. | LCP stack-up used to implement the filter-baluns.                                                                                                                        | 83 |

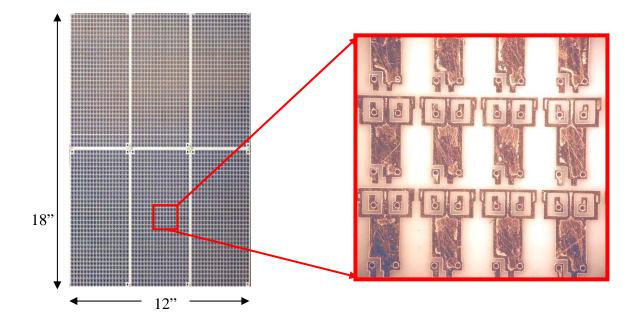

| Figure 3.12. | Photograph of the fabricated 12"x18" panel showing the devices laid out in six coupons, and close-up of the devices showing probe pads.                                  | 84 |

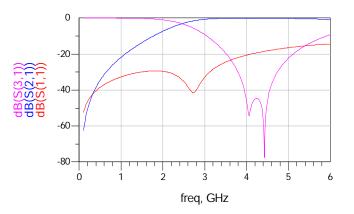

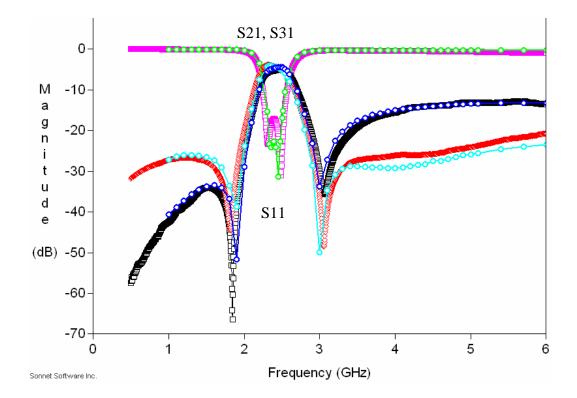

| Figure 3.13. | Measured and modeled values of S11, S21 and S31. Dotted line shows Sonnet simulations while continuous line shows the measured data                                      | 85 |

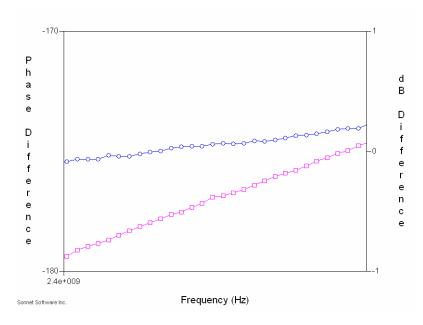

| Figure 3.14. | Measured amplitude and phase imbalance.                                                                                                                                  | 85 |

| Figure 4.1.  | Functional block diagram of a receiver showing the LNA.                                                                                                                  | 88 |

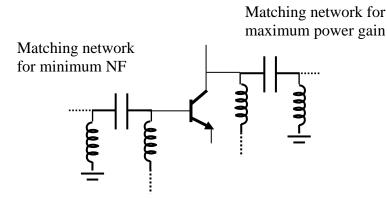

| Figure 4.2.  | Classical LNA design, showing matching networks.                                                                                                                                                                                                | 90  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

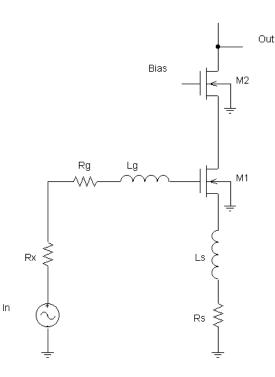

| Figure 4.3.  | LNA with inductive degeneration. $R_g$ and $R_s$ are parasitic<br>resistances of the inductors $L_g$ and $L_s$ . The bias circuitry has not<br>been shown for simplicity's sake.                                                                | 90  |

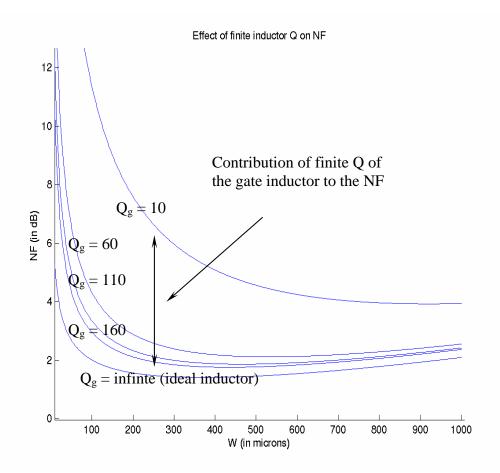

| Figure 4.4.  | Variation of <i>NF</i> with transistor width (for different values of $Q_g$ ), for a 1.9 GHz CMOS LNA designed for the AMI 0.5 $\mu$ process.                                                                                                   | 95  |

| Figure 4.5.  | Variation of <i>NF</i> with Qg, for a 1.9 GHz CMOS LNA designed for the AMI $0.5\mu$ process.                                                                                                                                                   | 96  |

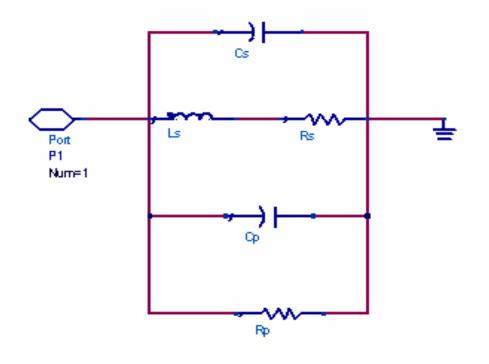

| Figure 4.6.  | Inductor lumped-element model.                                                                                                                                                                                                                  | 97  |

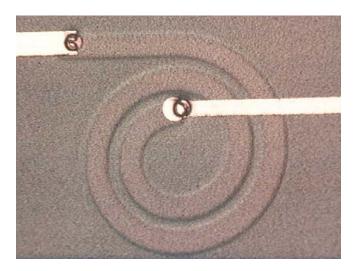

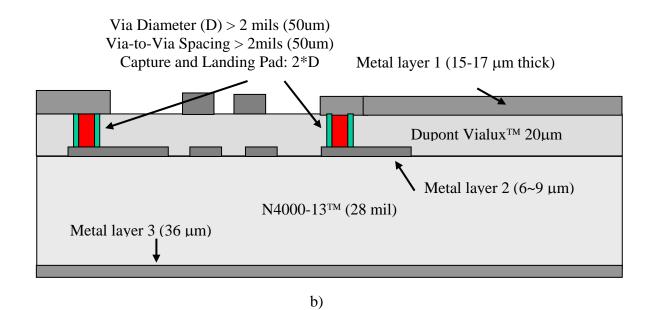

| Figure 4.7.  | a) Photograph of the fabricated inductor (the CPW ground ring around the inductor is not shown) b) Cross-section of the substrate.                                                                                                              | 99  |

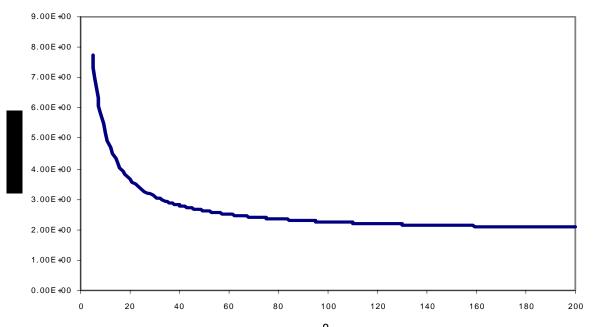

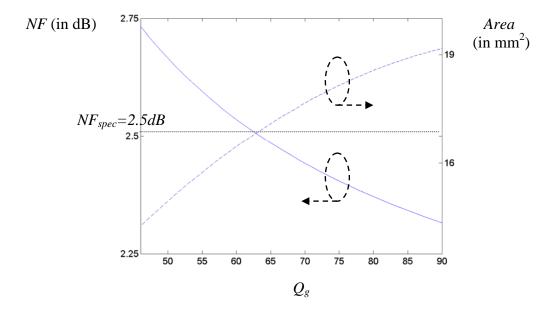

| Figure 4.8.  | Variation of inductor area and NF with $Q_g$ .                                                                                                                                                                                                  | 100 |

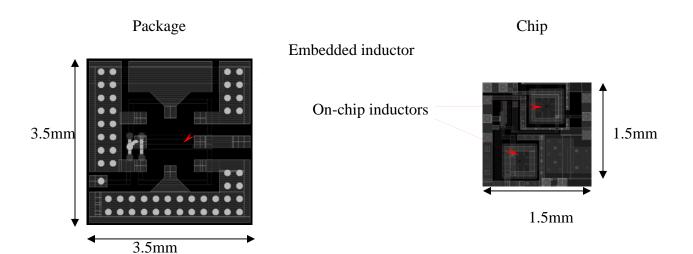

| Figure 4.9.  | Chip and package layouts of the proposed integrated LNA.                                                                                                                                                                                        | 101 |

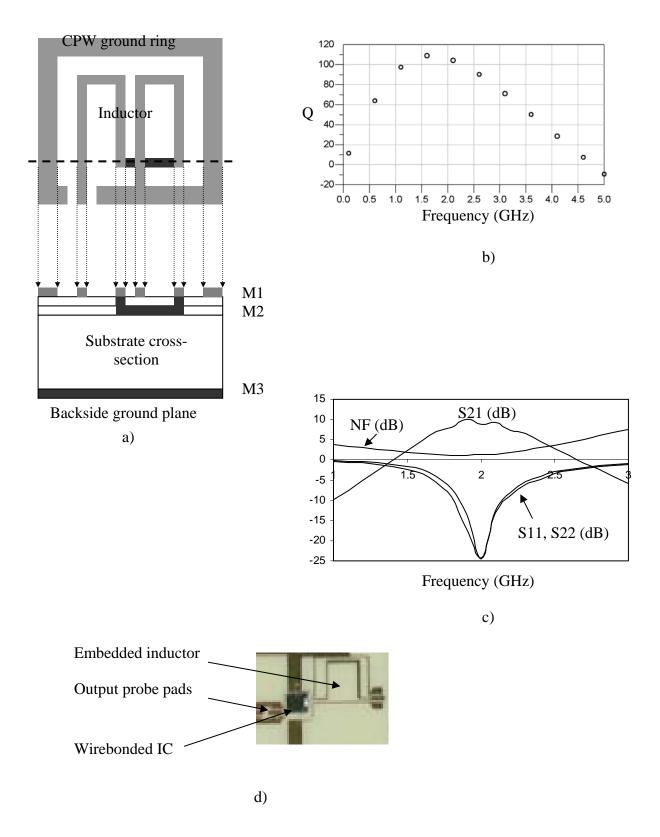

| Figure 4.10. | a) Layout and cross-section of the inductor used (9 nH CPW topology) with b) measured Q values, c) simulated gain and NF numbers, and d) photograph of an initial prototype showing the embedded inductor in the package and the wirebonded IC. | 102 |

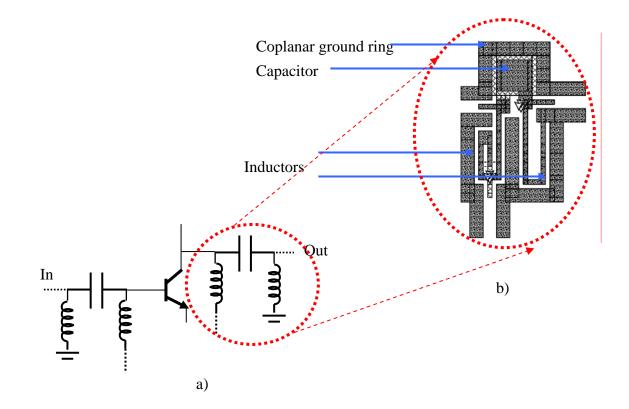

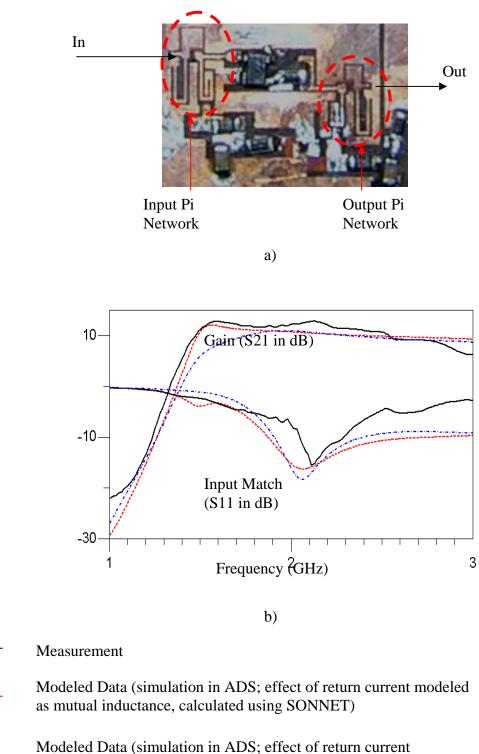

| Figure 4.11. | a) LNA with impedance transformation networks (pi networks)<br>and implementation of the output pi using embedded passives. b)<br>Actual layout of the output pi, showing the embedded inductors<br>and capacitor.                              | 105 |

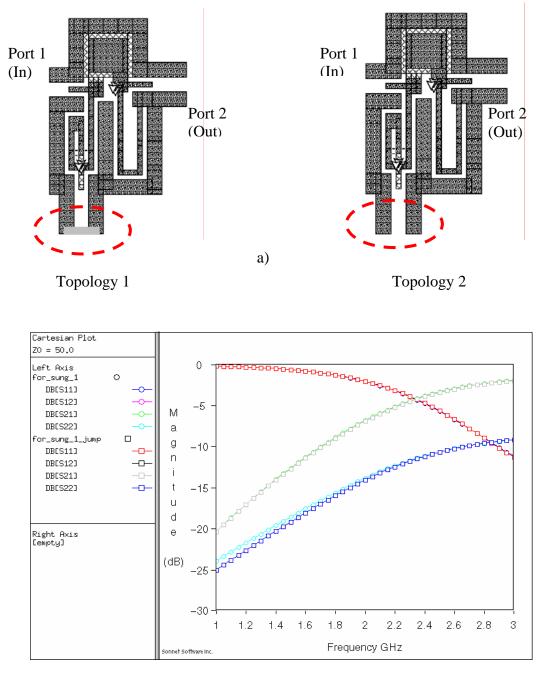

| Figure 4.12. | a) Two reference ground layout topologies for the output pi. b) SONNET simulations for both layouts.                                                                                                                                            | 106 |

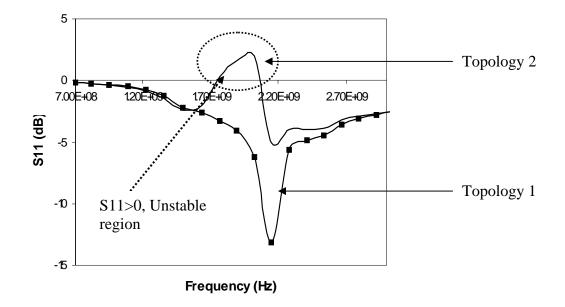

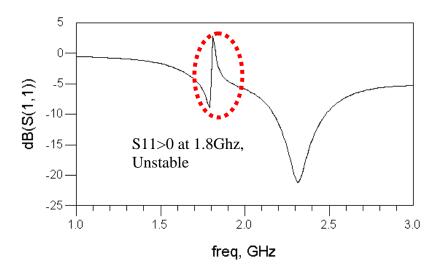

| Figure 4.13. | Measured S11 values for amplifiers using the two pi topologies of Figure 4.11a, showing the effect of the reference ground layout on LNA performance.                                                                                           | 107 |

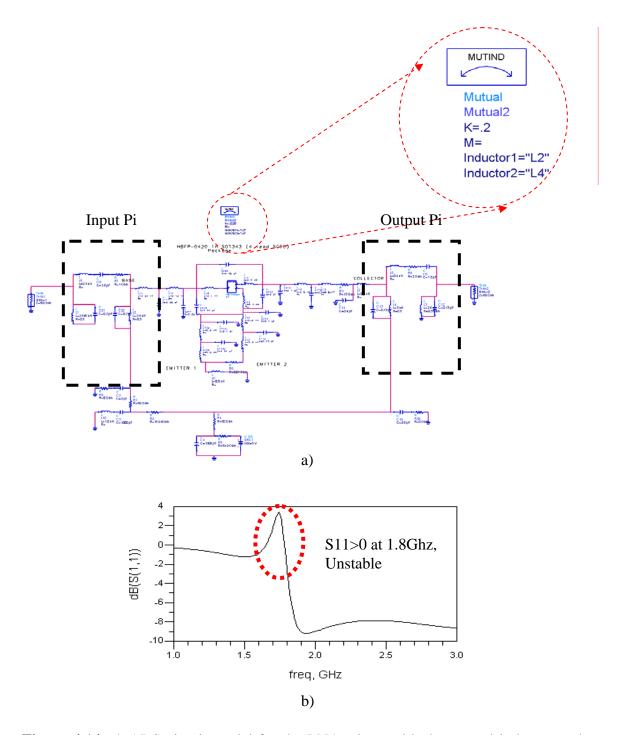

| Figure 4.14. | a) ADS circuit model for the LNA, along with the mutual inductance that was necessary to model the instability. b) Modeled (ADS) S11 results showing instability                                                                                | 108 |

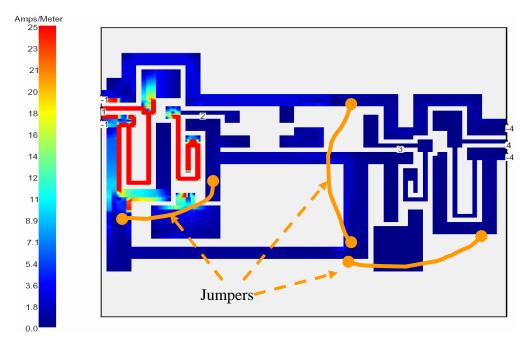

| Figure 4.15. | Sonnet simulations of the unstable LNA layout, with the use of jumpers for current re-routing.                                                                                                                                                  | 109 |

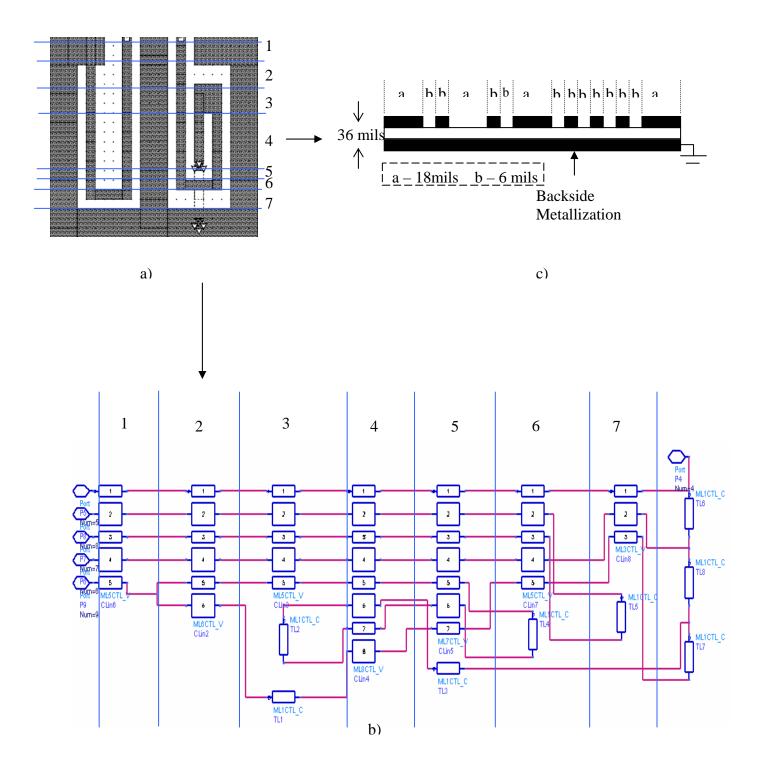

| Figure 4.16. | Coupled-line modeling of two inductors a) Layout and segmentation of the inductors b) ADS multilayer coupled line model of the inductors c) Cross-section of one of the segment    |     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | (Segment 4).                                                                                                                                                                       | 111 |

| Figure 4.17. | Modeled (ADS) S11 results showing instability.                                                                                                                                     | 112 |

| Figure 4.18. | a) Photograph of the fabricated device. b) Modeled and measurement data.                                                                                                           | 113 |

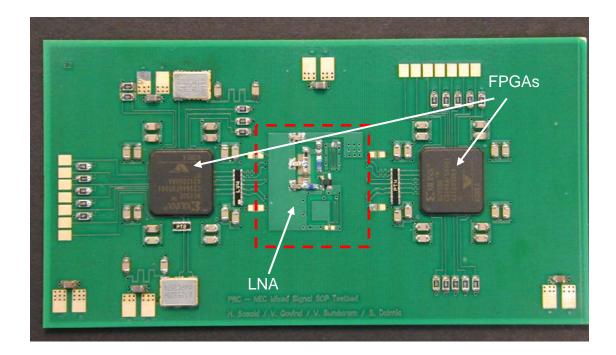

| Figure 5.1.  | Mixed-signal test-vehicle showing an RF circuit (LNA) in close proximity to digital circuits (FPGAs)                                                                               | 117 |

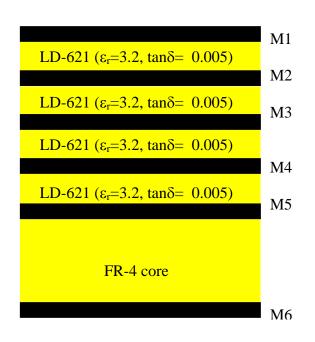

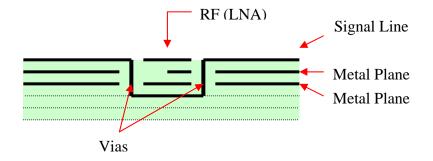

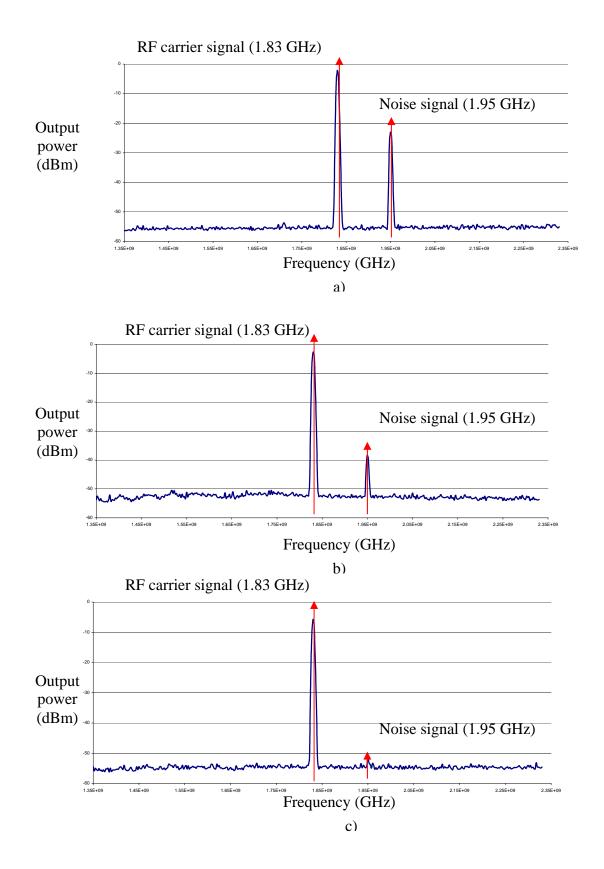

| Figure 5.2.  | Board stack-up.                                                                                                                                                                    | 119 |

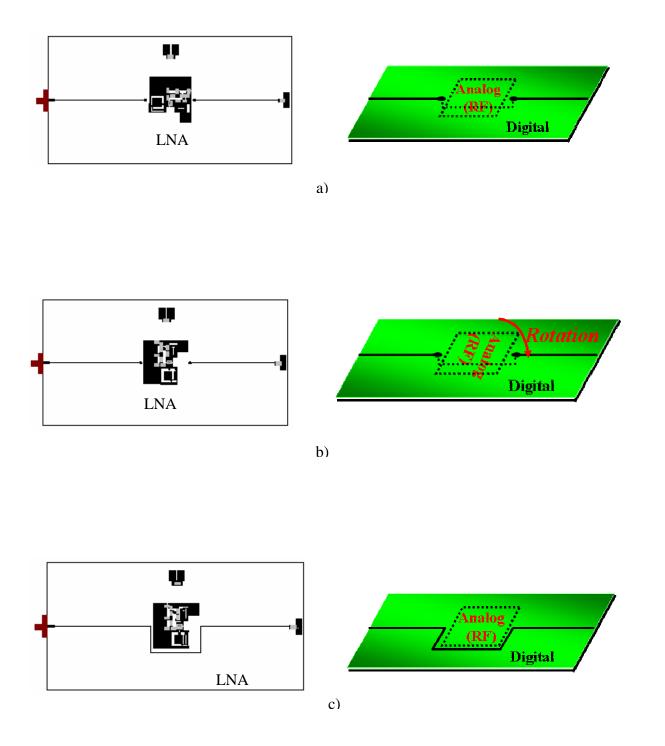

| Figure 5.3.  | a) Test vehicle A. b) Test vehicle B. c) Test vehicle C.                                                                                                                           | 120 |

| Figure 5.4.  | Cross-section of the 6-metal layer board substrate, showing the routing of the signal line beneath the LNA (for boards A and B).                                                   | 121 |

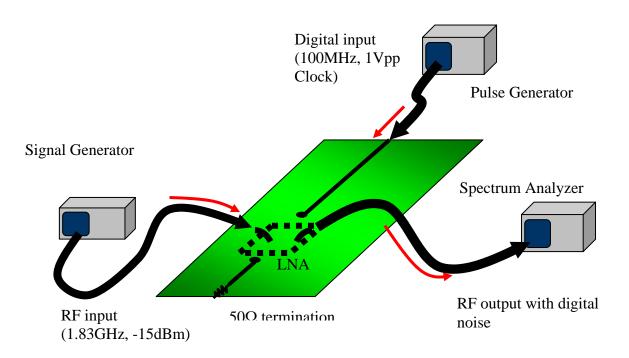

| Figure 5.5.  | Measurement setup.                                                                                                                                                                 | 122 |

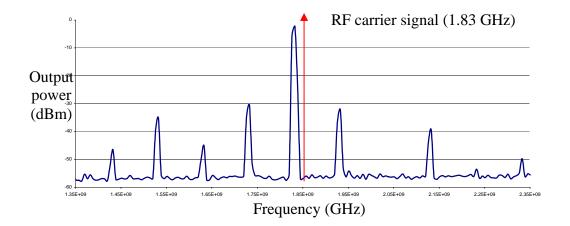

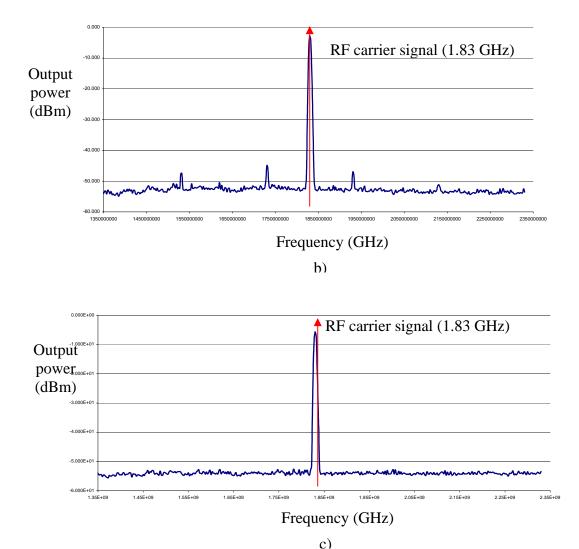

| Figure 5.6.  | LNA output spectrum of Test vehicle A                                                                                                                                              | 122 |

| Figure 5.7.  | LNA output spectrum a) Test vehicle B. b) Test vehicle C.                                                                                                                          | 123 |

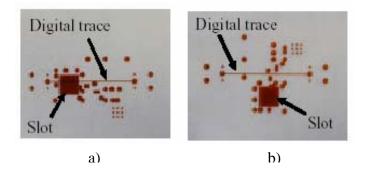

| Figure 5.8.  | Routing of the digital trace (metal layer 4) with respect to the LNA layout (metal layers 1 & 2; not shown) and the corresponding slot (metal layer 3). a) Test vehicle A. b) Test |     |

|              | vehicle B.                                                                                                                                                                         | 124 |

| Figure 5.9.  | Via transition in the signal path, showing the discontinuity in the return current path.                                                                                           | 125 |

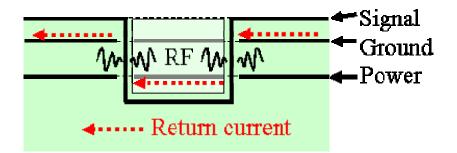

| Figure 5.10. | LNA output spectrum a) Test vehicle A. b) Test vehicle B. c) Test vehicle C.                                                                                                       | 126 |

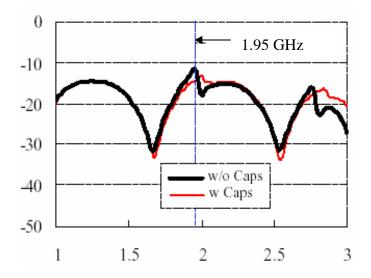

| Figure 5.11. | S11 measurements at the input of the 50 $\Omega$ microstrip signal line (on Testbed A), with and without capacitors.                                                               | 127 |

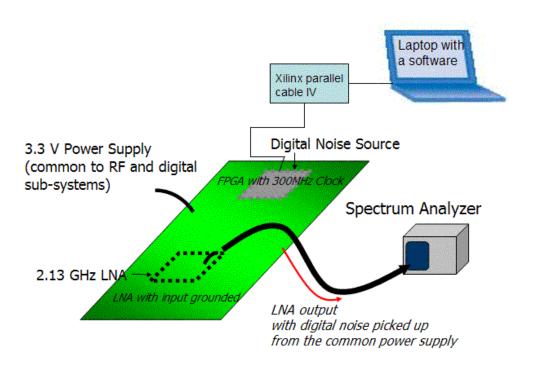

| Figure 5.12. | Measurement setup.                                                                                                                                                                 | 129 |

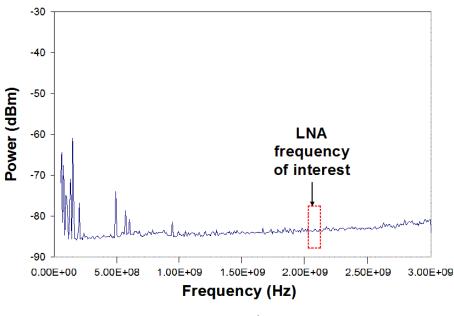

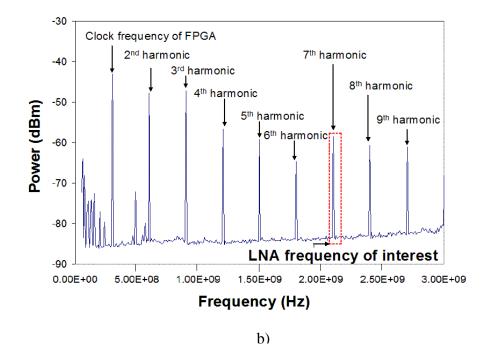

| Figure 5.13. | Measured frequency spectrum at the output of the LNA, with the input shorted to ground and a) system powered on, but with                                                          |     |

|              | FPGA quite (not switching) b) system powered on and the FPGA driving the bus with a 300MHz clock.                                                                                                                                                                                                                                                                      | 131 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

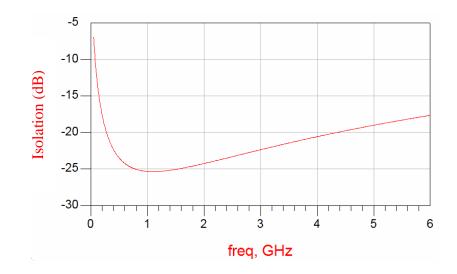

| Figure 5.14. | Simulated isolation of the Murata ferrite bead.                                                                                                                                                                                                                                                                                                                        | 133 |

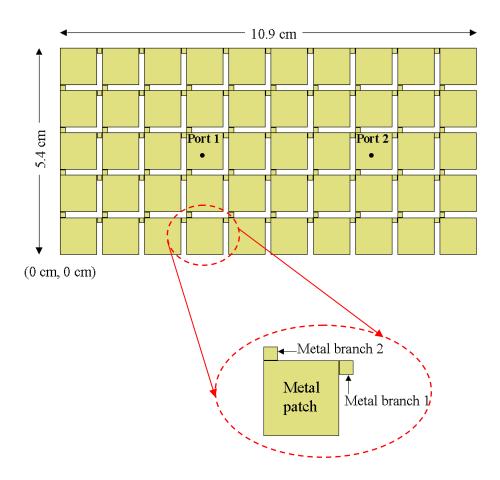

| Figure 5.15. | a) AI-EBG implementation b) Unit cell of the EBG structure.                                                                                                                                                                                                                                                                                                            | 135 |

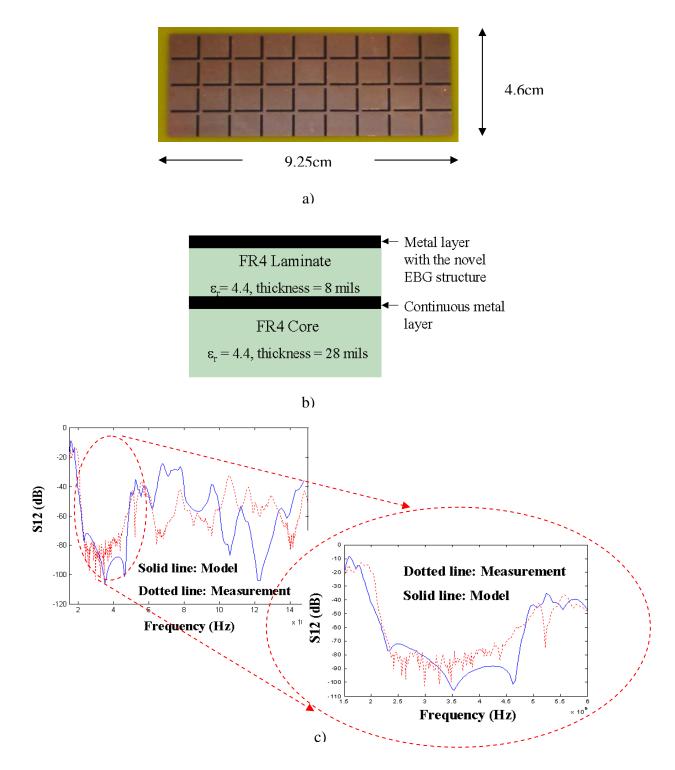

| Figure 5.16. | a) Photograph of an AI-EBG implementation. b) FR-4 stackup used. c) Model-to-hardware correlation for isolation (S21) in the structure.                                                                                                                                                                                                                                | 136 |

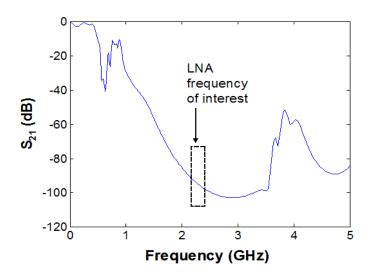

| Figure 5.17. | Simulated transmission coefficient of the EBG.                                                                                                                                                                                                                                                                                                                         | 137 |

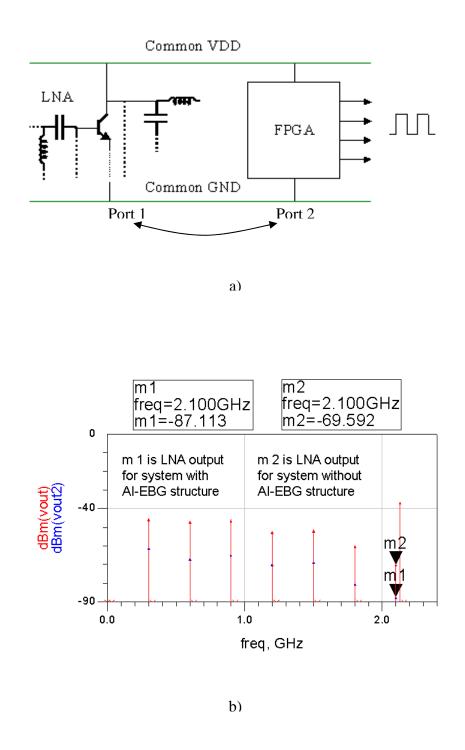

| Figure 5.18. | a) Frequency domain simulation of the mixed-signal system.<br>Figure shows the definition of the two ports. b) Simulated LNA<br>output spectrum. The red lines (and marker m2 at 2.1GHz) show<br>the noise coupled through an ordinary plane pair, while the blue<br>lines (and marker m1 at 2.1GHz) represent noise coupled through<br>the AI-EBG-based power system. | 139 |

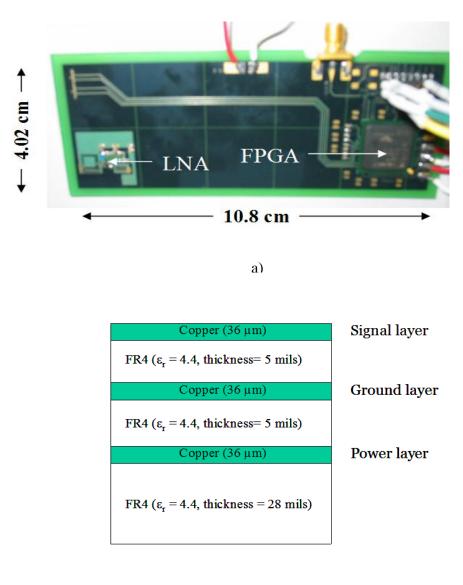

| Figure 5.19. | a) Photograph of the test-vehicle b) 3-metal layer FR-4 stack-up used to implement the system.                                                                                                                                                                                                                                                                         | 140 |

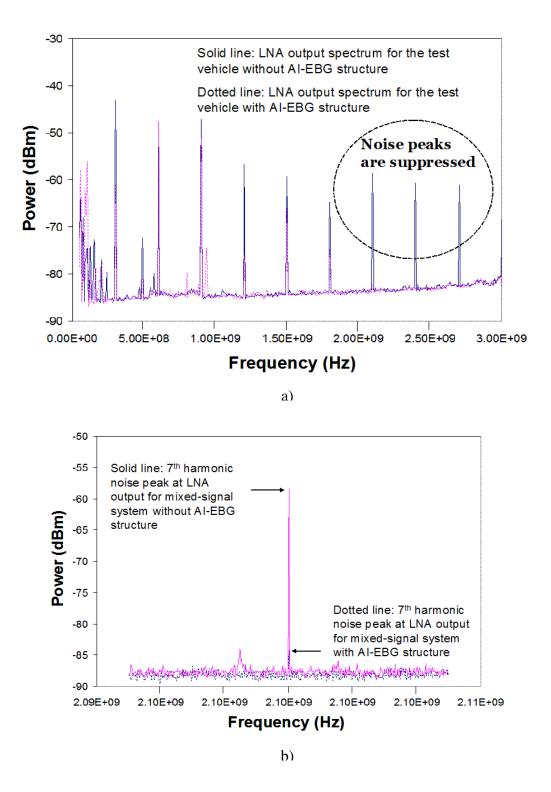

| Figure 5.20. | a) Comparison of LNA output spectrum, with and without the AI-EBG–based power distribution scheme. b) Comparison of 7 <sup>th</sup> harmonic noise peak at 2.1 GHz for the mixed-signal systems with and without the AI-EBG AI-EBG–based power distribution scheme.                                                                                                    | 141 |

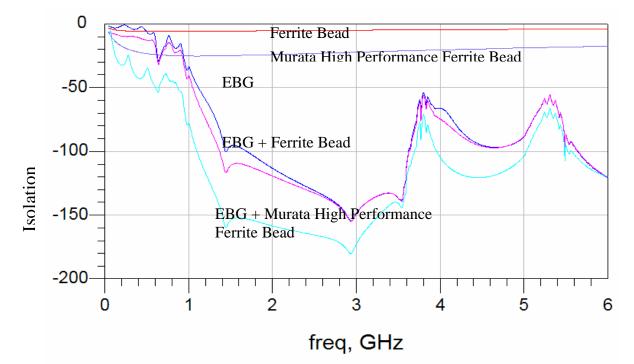

| Figure 5.21. | Simulated performance comparison of different combinations of EBG-based structures and ferrite beads.                                                                                                                                                                                                                                                                  | 143 |

### **SUMMARY**

The integration of mixed-signal systems has long been a problem in the semiconductor industry. CMOS System-on-Chip (SOC), the traditional means for integration, fails mixed-signal systems on two fronts; the lack of on-chip passives with high quality (Q) factors inhibits the design of completely integrated wireless circuits, and the noise coupling from digital to analog circuitry through the conductive silicon substrate degrades the performance of the analog circuits.

Advancements in semiconductor packaging have resulted in a second option for integration, the System-On-Package (SOP) approach. Unlike SOC where the package exists just for the thermal and mechanical protection of the ICs, SOP provides for an increase in the functionality of the IC package by supporting multiple chips and embedded passives. However, integration at the package level also comes with its set of hurdles, with significant research required in areas like design of circuits using embedded passives and isolation of noise between analog and digital sub-systems.

The key contributions of this work are envisioned to be the development of novel RF circuit topologies utilizing embedded passives, and an advancement in the understanding and suppression of signal coupling mechanisms in mixed-signal SOP-based systems. The former will result in compact and highly integrated solutions for RF front-ends, while the latter is expected to have a significant impact in the integration of these communication devices with high performance computing.

### **CHAPTER 1**

### **INTRODUCTION**

In recent years, the marriage of high-speed computing and wireless communication has emerged as a formidable driving force in the global electronics industry. This has resulted in products with both computing and communication capabilities, and has engineered a tremendous surge of interest in the mixed-signal market [1]. Figure 1.1 shows the global mixed-signal market and its composition [2].

For example, Intel, Corp. has announced a "Radio Free Intel<sup>®</sup>" initiative, adding communication capability to high-performance computing by the merger of CMOS wireless radios and microprocessor chip-sets [3]. Intel envisages a future where a user with a mobile computer can seamlessly move between different wireless networks (longdistance as well as short-distance), achieving "ubiquitous wireless connectivity" for a computing device. At the same time, Nokia Corp., the world's largest manufacturer of cell-phones, has announced the "N-Gage" gaming device platform where customers all over the world can compete with each other wirelessly [4]. With the processing power in these gaming consoles expected to be equal to or more than a consumer laptop, this would represent an unprecedented increase in the computing power of a commercial wireless communication device.

Figure 1.1. Global mixed-signal market, and its composition.

Although the term "mixed-signal" is a generic one and deals with the integration of multiple signal domains, in the particular context of today's commercial applications, it has come to represent the blurring of the hitherto concrete lines separating digital and analog/RF domains.

As shown in the examples mentioned above, the next-generation mixed-signal systems will be expected to provide high-performance computing and wireless connectivity to a mobile user. But with a proliferation of communication standards geared towards different applications, these computing-communicating-hybrids will need to support multiple communication protocols at multiple frequency bands [5] to achieve this goal of ubiquitous connectivity. As an e.g. (a rather futuristic one), a mobile user engaging in a video-conference via his cell phone can expect his call to be routed over a Wideband CDMA (WCDMA) network as he walks across the parking lot, with a

seamless hand-off to a Wireless LAN (WLAN) based network as he enters his office. At the same time, a GPS signal from his cell phone continuously communicates his position to a satellite, while the Bluetooth protocol is used to synchronize the contents of his phone-based calendar with the one in his office computer.

Ever since the invention of the Integrated Circuit (IC), miniaturization and integration have been key drivers in the growth of the semiconductor industry. Consumer-driven devices like the computing-communicating-hybrids (described in the previous section) also need miniaturization (through integration), to achieve goals of lowcost and high performance. In fact, with wireless mobility as a key distinguishing feature, these mixed-signal systems impose additional constraints of size, thickness and weight on the integration technologies.

An integrated multi-frequency mixed-signal system can lead to a number of design complexities, primary of which are the suppression of signal coupling between the different signal domains and the design of the multiband radio architecture. Suppression of digital switching noise is very much dependent on the level of integration in the system, and is thus tightly coupled to the technology used for integration. It will therefore be dealt with later in this chapter, after looking at the different integration technologies available for mixed-signal systems.

#### 1.1. Multiband Radio Architectures

Figure 1.2 shows two possible multiband receiver implementation schemes, based on functionality. Figure 1.2a shows multiple parallel paths (each of which is single-band in nature) stacked together. Each path is a complete receiver chain, with a single-band antenna, single-band filter, single-band balun, single-band Low Noise Amplifier (LNA) and a single-band differential down-converter (with a single-frequency Voltage Controlled Oscillator (VCO)). A common back-end baseband unit contains the Analogto-Digital Converter (ADC) (Digital-to-Analog Converter (DAC) in case of a transmit chain) and the Digital Signal Processor (DSP). The multiple receiver paths provides the baseband circuit with signals at multiple frequencies simultaneously, but the choice of the signal to be processed (and by extension, the receiver path to be used) is made at the baseband level. This is a viable architecture in a scenario where the multiband radio is expected to receive signals at multiple frequencies, but process only one at any single instance of time. A good example is a multiband "world-phone" which is operational at the 850MHz, 900MHz, 1800MHz and 1900MHZ to service the GSM-USA, EGSM, DCS and PCS protocols. Although the RF front-end is capable of processing signals in any of these frequency bands, the baseband chooses only one at any instance of time based on availability of service and/or signal strength.

Figure 1.2b shows an alternate architecture, where each device in the receiver path is functional at multiple frequency bands. The receiver consists of a multiband antenna, a multiband filter, a multiband LNA, a multiband differential down-converter (with a multiband VCO) and a baseband unit, and can thus *process multiple signals at different frequencies simultaneously*. As an example, a receiver functional at 1900MHz and 2.4GHz concurrently can enable the user to make a phone call using the PCS protocol even as he receives data from the WLAN router simultaneously.

Figure 1.2. a) Multiband architecture, with each device operational at a single band, and switching between frequency bands in the baseband. b) Concurrent multiband architecture, with each component functional at multiple frequency bands.

The "multiple single-band" architecture of Figure 2a suffers from high power consumption and large size, due to the multiplicity of receiver paths. The concurrent architecture of Figure 2b, meanwhile, can result in saturation of the active circuitry in the presence of a high power signal in *any* of the bands it is designed for. This can degrade the sensitivity of the receiver for signals in the other operating frequency bands, limiting its concurrent functionality.

In practice, a combination of the two architectures, with multiple receiver paths each involving singleband/multiband devices, will offer the optimum performance and size. Figure 1.3 shows one such implementation, where switches have been used in the receiver chain to ensure that high-power out-of-band signals do not saturate the active circuitry. The frequencies/protocols have been divided based on concurrent and nonconcurrent functionality requirements, and have been allocated distinct receiver paths. For each receiver path (after the switch), the components have been designed for multiband functionality, resulting in optimized sizes and power consumption.

As an example, consider a quad-band (850MHz, 900MHz, 1800MHz and 1900MHz) cell-phone with dual-band (2.4GHz and 5GHz) WLAN capability. As only one of the four bands available for voice communications need to be used at any instance, they can all be grouped into one multiband receiver path operational at all four frequencies. Similarly, the two WLAN bands can also be grouped into one multiband path. However, since a user needs to make a phone call *and* receive signals from the WLAN router *simultaneously*, the two paths can be classified as concurrent, and can be designed such that the baseband processor receives *one* signal from each path *concurrently*.

**Figure 1.3.** Switched semi-concurrent multiband receiver architecture, showing four paths with each path supplying one signal concurrently to the baseband processor. Paths (i) and (ii) are multiband in functionality, with the selector switch between the SIMO filter and the rest of the front-end circuitry determining the choice of signal to pass-through. Paths (iii) and (iv) are singleband in functionality.

The design methodology for the switched architecture can thus be summarized as follows:

- Functional division of the frequency spectrum under consideration, based on concurrent or non-concurrent operation.

- 2) Design of each path using multiband components for concurrent operation.

The first step in the implementation of mixed-signal systems with multiband radios is the design of multiband front-end components (comprising of antennas, band-pass filters, baluns, LNAs, VCOs and mixers). As in the case of the suppression of noise coupling between the digital and analog signal domains, this is highly dependant on the level of integration required in the system. A solution for implementing multiband components in a mixed-signal environment would therefore be incomplete (and inappropriate) without looking at the various integration technologies available for such a solution.

#### 1.2. Mixed-Signal Integration

Traditionally, mixed-signal systems have been implemented at the Printed Wiring Board (PWB) level, by simply soldering multiple ICs and discrete passives onto a lowcost epoxy-based board. With improvements in semiconductor technology, the number of transistor per die has increased, leading to a scenario where entire systems can be implemented in a single chip. This approach, also called the System-On-Chip (SOC) implementation, has been particularly successful in the case of CMOS digital circuit design, where single-chip solutions with millions of transistors have become very common (E.g. [6]).

However, the single-chip integration methodology of SOC has been singularly unsuccessful in the integration of the mixed-signal computing-communicating-hybrids described in the previous section. Although several system-level examples (E. g. [3], [7]) have been reported on high-performance mixed-signal (analog/RF and digital) functionality, none of them are single-chip solutions. The SOC-based examples that *do* exist tend to be low-performance applications. For example, Broadcom has announced a single-chip transceiver solution for wireless audio processing, the BCM 2037 IC. However the Bluetooth protocol that it uses for communication reduces the range of operation, and the meager 120kB of memory that it contains is insufficient for any meaningful computing functionality. It is important to note that Broadcom's own BCM2004 IC, a single-chip Bluetooth solution designed for use in a Qualcomm cellphone, still requires an external filter to function in the multiband environment. SOC thus fails in the integration of high-performance computing and long-range communication protocols like WiMax and WCDMA.

By its very nature of bringing together computing and communication, mixedsignal systems require a wide range of technological capabilities. For example, the power amplifier (PA) of a radio transmitter needs the high rail-to-rail power supplies of Gallium Arsenide (GaAs) technology while the baseband circuits require the reduction in size and power consumption afforded by CMOS technology. Unlike digital integration where any possible function can be implemented using standard transistors in a standard CMOS technology, mixed-signal integration thus calls for multiple technological capabilities. And studying the previous published examples ([3], [7]), it becomes clear that one of the main impediments to CMOS SOC based mixed-signal integration schemes is the inability to pick and choose the correct technology required for a particular application [8].

Another problem in SOC based integration is the lack of high Quality (Q) on-chip passives. The thin metal layers and the lossy nature of the silicon substrate lead to higher parasitics for on-chip inductors and capacitors (E.g. [9]). This is primarily a concern in RF/analog circuit design, where the low-Q passives make design of completely integrated filters and LNAs for high sensitivity applications like long-distance communication protocols next to impossible ([10]-[13]).

A third impediment to mixed-signal on-chip integration is noise coupling from digital circuitry to components of the wireless receiver chain ([14]-[17]). As the incoming RF signals are in the order of microvolts, any in-band noise reaching the receiver corrupts the signal. The switching of digital circuits couples with package parasitics to produce power supply noise, as well as directly coupling to the analog circuitry through the conductive silicon substrate. The LNA is the first active device in any receiver chain, and is particularly susceptible to this noise.

Developments in packaging technology have led to a second option for integration, the System-on-Package (SOP) approach. Unlike SOC where the package exists just for the thermal and mechanical protection of the ICs, SOP provides for an increase in the functionality of the IC package by supporting multiple chips and embedded passives [18]. Depending on the packaging technology used, there are two main approaches for SOP integration; namely 1) Low-Temperature Co-fired Ceramic (LTCC) technology [19] and 2) Organic technology ([20]-[22]). The dielectric materials and highly conductive copper layers of these packaging substrates makes high-Q embedded inductors and capacitors possible ([19]-[22]). These passives can be used to design RF front-end components like antennas, filters and baluns embedded in the packaging substrate, which combined with the on-chip circuitry, leads to completely integrated modules. The use of multiple chips for the RF transceiver and the digital baseband processor also reduces the noise that would have otherwise coupled through a common silicon substrate, along with opening up the possibility of using multiple technology ICs for implementing multiple functions.

Figure 1.4 summarizes the various integration options available to the mixedsignal system designer today.

**Figure 1.4. a)** Printed Wiring Board (PWB) based integration, with packaged chips and passives assembled onto a PWB substrate **b**) SOC-based integration, with on-chip passives **c**) SOP-based integration, with embedded passives in the package.

Conceptually, SOP offers the best solution possible for a mixed-signal environment. As such, it makes sense to go more into the details of the two main SOPbased technologies, so as to determine the optimum solution for mixed-signal integration.

#### 1.2.1. Low-Temperature Co-fired Ceramic (LTCC) Technology

LTCC technology (also known as Multi-Chip Module – Ceramic (MCM-C)) is a multi-layer ceramic process, where the ceramic layers are tape-cast in their pre-fired "green state" and the tape is then cut to the required size [23]. Registration holes, via holes and cavities are then punched or drilled into the different tape layers. Via holes are normally filled (often with silver), and then thick-film processing is used to print metallization patterns on the tapes. The layers are then registered and laminated to each other, and then co-fired at about 850°C.

The main electrical properties of LTCC can be summarized as follows [23]:

- Low loss tangent ( $0.003 < tan \delta < 0.009$  from 1-10GHz)

- Dielectric constants ranging from 5-20, enabling the integration of a widerange of functionalities

- High dielectric layer count (as high as 50)

These characteristics have propelled the development of LTCC into the "technology of choice for RF integration" [23]. Inductors ranging from 1nH to 25nH and capacitors ranging from 1pF to 30pF have been demonstrated on LTCC substrates [24]. Depending on topology, these passives exhibit a Q of 50-150 for inductors and 50-200 for the capacitors. They can then be used for the design of circuits like filters and baluns

that are completely integrated in the substrate. Several modules involving active circuits attached to these LTCC substrates (via flip-chip or wire-bond or simply soldering prepackaged components) are available in the commercial market today. Although PA modules remain the single-largest application for LTCC substrates, Antenna Switch Modules (ASM) used to isolate RF signals so that they may share one antenna patch, VCOs to provide stable reference frequencies for down-conversion and Surface Acoustic Wave (SAW) filter based high-Q filtering modules have also proved to be major LTCC applications. In addition, completely integrated RF transceivers in module forms have also been implemented using LTCC (Figure 1.5).

Figure 1.5. LTCC based integrated Bluetooth transceiver module from Kyocera.

Although significant advancements have been made in the use of LTCC for microwave applications, the question still arises as to whether they are truly the technology of choice to meet the integration needs of next-generation computingcommunication-hybrids. And the answer is a resounding no, due to the following reasons:

- 1. Although LTCC has been commercially proven for *today's* RF modules and components, fundamental processing issues place limits on the amount of future integration possible. This can be described as follows:

- The screen-printing process in LTCC limits via size to 0.1mm and 1:1 aspect ratio. Combined with limitations on minimum line-widths possible (due to the screen-printing process), this results in low component-density substrates. Although per-volume component count can be increased today by stacking multiple dielectric layers, future trends in wireless packaging points to low-profile devices, making such a multi-layer LTCC platform non-competitive with regards to thickness.

- LTCC process starts with "green-sheet", resulting in 10-25% shrinkage during fabrication. This affects the yield of the devices.

- The screen-printed conductor profile results in rough interfaces. At microwave frequencies, this results in higher metal losses due to Skin Effect.

- 2. Processing limitations results in poor yields for large metal planes in LTCC substrates, which are very important for use as power distribution planes in digital systems. This results in poor signal and power integrity in the system, ultimately resulting in failure of high-speed digital systems.

- 3. Finally, LTCC is a high-temperature (800°C) process. Combined with the fact that current commercial manufacturers are set-up for processing "green" sheets in lot-sizes of 8"x8", it makes LTCC a high-cost process.

#### 1.2.2. Organic Technology

Integrated organic technology can be further classified as Multi Chip Module-Deposition (MCM-D) and SOP-Laminate (SOP-L), depending on whether the organic films are deposited or laminated onto the mechanical substrate to form functional layers.

MCM-D consists of deposition of thin (<15 $\mu$ m) polymer dielectric films deposited onto a stable base substrate such as silicon/glass or alumina. Thin (2-5 $\mu$ m) conductor film, usually copper, is then deposited and processed photolithographically. Benzo Cyclo Butene (BCB) ( $\epsilon_r$ =2.65 and tan $\delta$ =0.0008) is a polymer that has been widely used for such applications (e.g. [25], Figure 1.6a). The ability to have microvias as well as very thin line-widths increases the component density of the technology. However, it is also important to note that it is difficult to fabricate multilayer substrates with large number of layers in this process. Combined with the fact that it is a high-temperature process (450°C) and can only be processed on wafers with 4-6" diameter makes MCM-D a comparatively high-cost technology for high-volume manufacturing.

A variation of MCM-D is the Thin-Film-On-Glass (TFOG) or Thin-Film-On-Silicon (TFOS) process (Figure 1.6b). Copper metal (10µm thick) is deposited onto an insulated surface if silicon (with 25µm silica (SiO<sub>2</sub>) layer on top). Low-loss low dielectric constant materials like BCB are spun onto this layer to add two more metal layers. Microvias are available between all three metal layers. Further, the technology also offers precision Nickel-Chromium (NiCr) resistors and Silicon Nitride (SiN) capacitors. Like MCM-D, these processes provide high component density with the possibility of integration with CMOS active circuitry. But again, like MCM-D, they also have the drawbacks of high-temperature processing and fabrication in lots of 6" wafers. The technology also limits the number of metal layers possible (currently three).

SOP-L is based on technology developed for the fabrication of PWBs. A thick copper-cladded (9-35µm) FR-4 organic substrate (epoxy-glass fiber composite) is used as the mechanical core [26]. Further layers are formed by laminating copper-clad dielectric layers onto the core, with the multiple copper layers insulated from each other using thin-film epoxy-glass composites (25-100µm thick). Patterns are formed on the copper layers using photolithographic techniques, resulting in minimum line-width and minimum line-spacing as low as 25µm (Figure 1.6c).

**Band Pass Filter**

c)

**Figure 1.6.** Embedded passives on **a**) MCM-D substrate. **b**) TFOS substrate. c) SOP-L (Vialux<sup>TM</sup>) substrate.

Some of the processing and electrical advantages of this technology are as follows:

- 1) Heterogeneous stack-ups with different electrical properties ( $\varepsilon_r$  and tan $\delta$ ) and thickness (4µm-1mm) for each layer allows for fulfilling the disparate needs of different signal domains. For example, it is possible to realize a multilayer stack-up with a high-loss high dielectric constant (K) layer for power-supply decoupling, low-loss low-K layer for high-speed digital signal routing and a low-loss high-K layer for the design of RF passives.

- Availability of microvias as small as 1mil in diameter combined with minimum line-width/line-spacing of 1mil and thin dielectric layers (as low as 4µm) allows for component densities higher than that of LTCC and comparable to that of MCM-D.

- High conductivity copper metallization (12-36µm) helps reduce losses in transmission lines and passive devices compared to the losses in deposition and ceramic processes.

- 4) It is a low-temperature process (<250°C) that can be processed in lot-sizes as large as 18"x24" making SOP-L a low-cost technology for high-volume production.

A wide variety of organic laminates (with a wide range of electrical properties) are available today, for use in heterogeneous SOP-L stack-ups for mixed-signal integration. Low-cost epoxy based laminates used in traditional PWB industries form the bottom of the heap. They have high tan $\delta$  (0.015-0.025) and high coefficient of moisture absorption, which results in a variation of their electrical properties with temperature. As a result, embedded passives designed on these substrates have low Q-factors and also

change their electrical properties with temperature. Their usage is thus limited to routing of low-speed digital signals.

Thin high-K laminates such as Oak-Mitsui's FaradFlex<sup>TM</sup> ( $\varepsilon_r$  ranging from 4.4 to 30 and thickness ranging from 24µm to 8µm) and 3M's C-Ply<sup>TM</sup> ( $\varepsilon_r$  of 16 and thickness ranging from 8µm to 16µm) comes next. The high capacitance density that a combination of high  $\varepsilon_r$  and low thickness provides (as high as 11nF/inch<sup>2</sup>) allows the use of these laminates for embedded power supply decoupling applications. A comparatively high tanδ and coefficient of moisture absorption limits their application in the design of high-precision low-loss embedded passive circuits; however, by packaging the layers in such a way that they are not exposed to the outside air, they can still be useful for the realization of specific miniature RF circuits where dielectric loss is really not a concern (e.g. low-pass or high-pass filter structures for baluns).

At the top of the pyramid comes the new breed of high performance laminate solutions like Asahi-PPE<sup>™</sup>, Rogers 4350, Liquid Crystalline Polymers (LCP) and Teflon. Boasting low tanδ and low moisture absorption coefficient, these materials can be used in the realization of precision RF circuitry with virtually no change in frequency characteristics with temperature variation. Although Teflon is comparatively higher cost and harder to fabricate, the others are usable within a standard PWB-based processing flow, reducing their cost structure. With high line densities and the availability of small microvias, their component densities are comparable to that of LTCC and MCM-D.

It can be seen that a combination of the above materials, in a heterogeneous multilayer stack-up, can meet all the packaging needs of mixed-signal computing-

19

communication-systems. It is thus clear that laminate-based SOP could be the technology of choice for mixed signal integration.

Table 1.1 summarizes the characteristics of the various integration technologies covered so far.

**Table 1.1.** Comparison of discrete, SOC, LTCC, MCM-D/TFOS and SOP-L integration technologies.

| Technology       | Advantages                                                                                                                                                        | Concerns                                                                                                                       |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Discretes on PWB | <ul><li>Low-to-mid Q passives</li><li>Readily available</li></ul>                                                                                                 | <ul><li>Low density, large size</li><li>Component variation</li></ul>                                                          |  |

| SOC              | <ul> <li>Compact</li> <li>High integration in digital circuits</li> </ul>                                                                                         | <ul> <li>Low-Q passives</li> <li>No single technology<br/>platform covers all mixed-<br/>signal system requirements</li> </ul> |  |

| LTCC             | <ul> <li>High-Q passives</li> <li>High integration</li> <li>High density</li> </ul>                                                                               | <ul> <li>CTE mismatch</li> <li>Shrinkage</li> <li>Future scalability</li> <li>Lack of metal planes</li> </ul>                  |  |

| MCM-D/TFOS       | • High density                                                                                                                                                    | <ul><li>Low-Q passives</li><li>Low integration</li></ul>                                                                       |  |

| SOP-L            | <ul> <li>High Q passives</li> <li>High integration</li> <li>High density</li> <li>Availability of large metal planes</li> <li>Large area manufacturing</li> </ul> | • Hermiticity                                                                                                                  |  |

(Note: In addition to the above-mentioned technologies, Micro-Electro-Mechanical-System (MEMS) (where passive physical structures including inductors and capacitors are realized on SOC-based silicon wafers using conventional and non-conventional semiconductor processing steps) has also emerged as a technology candidate to implement mixed-signal systems. In fact, a few devices incorporating a CMOS digital IC with a MEMS-based gyroscope has appeared on the commercial market for automotive and cellular application [27]. However, these are niche devices at best, with several problems such as packaging the moveable physical components and integrating the nonconventional processing steps with conventional CMOS SOC manufacturing procedures preventing across-the-board adoption of a MEMS-based platform for mixed-signal integration. As such, it is perceived that MEMS (along with other exotic technologies like piezoelectric Surface Acoustic Wave (SAW) and Bulk Acoustic Wave (BAW) resonators) will become a part of an SOP-based system integration scheme. In such a scenario, each component will provide its own niche functionality, acting in a complementary fashion rather than competing with the laminate-based SOP base process).

## 1.3. Organic SOP-Based Mixed-Signal System Integration

Given the choice of technology for mixed-signal integration, it is important to revisit the two main concerns that were raised and set-aside earlier – design of multiband

components for multiband radio architectures, and the analysis of noise coupling between the digital and analog/RF sub-sections. In addition, the parasitic inductance and capacitance of chip-package interconnects become significant and can result in signal degradation at high frequencies. This becomes significant for circuits like LNAs, VCOs and Power Amplifiers (PA), which reside at the interface between the package and chip domains. The back-and-forth transfer of signals between the package and chip domains necessitate a design partitioning methodology to decide the distribution of circuit components within the package or within the chip. The use of multiple embedded passives in the substrate can also generate undesirable resonance and feedback, jeopardizing the functionality of the system [28].

Integration at the package level leads to changes in priority at the design phase. With the availability of high-Q passives embedded in the package, the *number* of lumped components becomes less important than the *value* of each of these components. (In contrast, designs utilizing discrete passives are more concerned with the total number of passives and not the individual values of each; the cost of assembly depends only on the number of discrete elements to be soldered on board, and the packaged size for different values of capacitance or inductance usually remains the same for commercially available discrete devices). This requires novel designs for RF components using these embedded passives, with priorities shifting from reducing the component count to keeping the value of the passives low.

Noise coupling between digital and analog circuits remains a problematic issue even in SOP-based implementations. Although coupling through the silicon substrate of an SOC chip is now eliminated, new noise sources like Electromagnetic Interference (EMI) from high-speed signal lines, fluctuations in power plane etc. arise, which have to be dealt with through careful modeling and analysis.

### 1.3.1. Design of Multiband RF Components

Multiband functionality in components can be achieved in the following ways:

- Devices with wide bandwidths capable of operating at different frequency bands.

- 2) Multiple single-band devices with matching networks at input and output producing a Single-Input-Single-Output (SISO) component. Each singleband device has narrow operating bandwidth, and multiband operation is achieved for the component by switching between the different singleband circuits (i.e. the component outputs only a single frequency at any given time) [29]

- Concurrent devices that achieve simultaneous multiband functionality (sampling one or more frequencies at a time depending on application)

[30].

Option 1 is difficult to implement due to technological concerns and the presence of large blocker signals close to the frequency bands of interest. Option 2 is a componentscale replica of the multiband architecture discussed in Figure 2a, and as such exhibits problems such as large size and high power consumption. In contrast, Option 3 (the use of true multiband devices) leads to lower power consumption and a vastly reduced footprint. Research is replete with examples of multiband antennas ([30]-[33]). Multiband band-pass filters using varactor diodes have also been reported [34]. As these diodes exhibit Q-factors of the order of 30 and results in an increase in the noise figure (NF) of the device, solutions like stacking separate single-band passive filters on a single package has also been attempted [35]. Further, a multiple frequency generator using high-Q embedded passives on an organic substrate, where two clock signals are generated concurrently, has been proposed recently [36]. Finally, multiband LNAs (through the use of resonant passive networks [5] or by stacking multiple single-band devices [37]) have also been reported.

All of the above examples have either been demonstrated directly using SOP based packaging technologies, or can easily be ported to one. From a design perspective, the only new RF device required to implement a completely integrated multiband receiver (like the one shown in Figure 1.2b or Figure 1.3) is a balun that is functional at multiple frequency bands.

### **1.3.2.** Design Partitioning

The passive devices like antennas, filters and baluns are completely embedded in the package. For the circuit components lying at the interface of the chip and package domains (the LNA, the VCO and the PA), design partitioning and optimization is required, to take into account the parasitics involved in a chip-package signal transition. Examples of PAs with the output matching networks implemented using embedded passives and VCOs with high-Q embedded inductors for improvement in phase noise has been reported in the literature ([38]-[40]).

It would be a relatively simple process to achieve complete integration by embedding passives in the package. However, this approach neglects the fact that compared to on-chip inductors with low Q values and discrete passives with fixed Q's, the use of embedded passives leads to the development of the passive Q as a new variable in circuit design. With Q values ranging from 20-200 (E.g. [21]), designers now have a choice in the value of Q they want for a particular component. Higher Q values result in new tradeoffs, particularly with respect to device size, and a design partitioning and optimization strategy is thus required to ensure efficient use of the packaging substrate. This has to be incorporated into the design methodology of each circuit, for optimal system performance. Although [39] has mentioned that there is very little reduction in VCO phase noise with improvement in inductor Q beyond a certain value for Q, the implication of this with respect to module size has not been fully investigated.

References [10]-[13] reports LNAs for long-distance communication protocols; none of these devices are completely integrated solutions, and an external discrete inductor is used in each case to make the circuit functional. The multiband LNA reported by Hashemi et al. [5] also relies on external discrete passives to implement the input resonant network. Design of completely integrated CMOS LNAs is possible by using embedded passives in the package. However, the common CMOS LNA design methodology of [10] has to be updated to take into account the tradeoff of higher inductor size for higher Q.

### **1.3.3.** Measurement and Analysis of Signal Coupling

With the high sensitivity requirements for radio circuits necessitating the handling of microwatts of input signal power, noise coupling from digital to analog domains has become a major impediment to mixed-signal integration. Noise is generated in digital circuits when many static gates change state simultaneously, causing a spike in current flow through parasitic resistances and inductances in the circuit [16]. This results in a spike in the power supply, which can couple into the analog circuits through a common power distribution system. The noise can also appear in analog circuits through capacitive coupling to and from the highly doped silicon substrates used in SOC systems. [14-17, 41-47].

However, with the use of SOP based schemes, new noise coupling and propagation mechanisms come into play. With the use of power planes in the package for power distribution, ground bounce and simultaneous switching noise (SSN) become important factors in mixed-signal design. High speed signal lines also end up radiating energy, resulting in Electro-Magnetic Interference (EMI) acting as a major source of noise.

The main digital-analog noise coupling mechanisms in mixed-signal SOP based systems can thus be summarized as follows:

- Through a common power supply

- Through EMI from high-speed signal lines

In addition, coupling within the analog signal domain through closely spaced multiple embedded passives also results in performance degradation of the RF circuitry.

26

The low-loss power-distribution networks used in SOP-based systems produces sharp resonances that do not exist in a higher-loss SOC-based power system [48]. The modeling of noise propagation through power planes has been extensively covered for printed wiring boards (PWB) [49-52]. Many of these methodologies are directly applicable to SOP based integration schemes. The analysis of EMI has also been analyzed from a PWB perspective [53-54]. However, the effect of this noise on a practical RF circuit, using multiple embedded passives and a package-based power supply scheme, has not been fully analyzed yet.

### **1.3.4. Research Objectives**

The main research objectives of SOP based mixed-signal system integration can be summarized as follows:

- 1) *Design* of novel integrated RF front-end components using embedded passives

- 2) *Optimization* and *Design Partitioning*

- 3) *Modeling and Analysis* of analog-analog and analog-digital signal coupling.

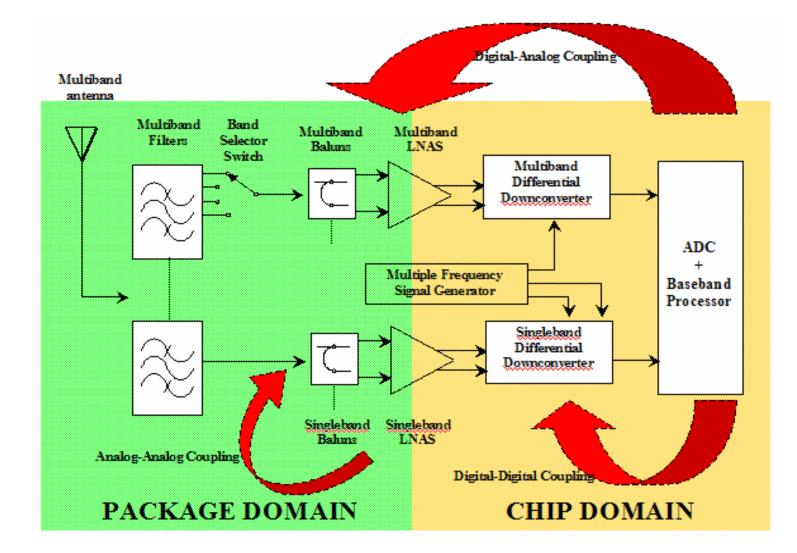

Figure 1.7 shows a test-vehicle highlighting these issues, comprising of a multiband wireless receiver supporting multiple communication protocols, and a high-speed baseband (digital) processor.

Figure 1.7. Mixed-signal SOP-based test vehicle, with integration of semi-concurrent multiband RF front-end and high-speed digital computing.

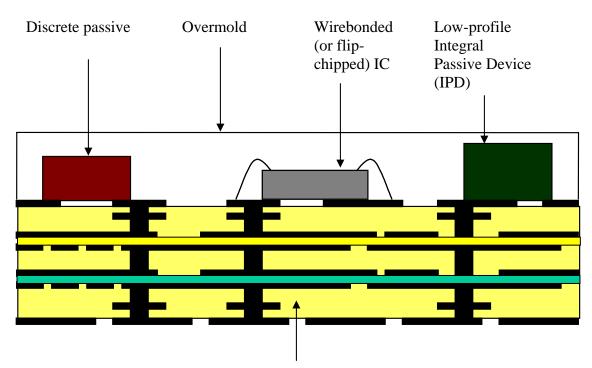

Figure 1.8 shows a possible SOP-based integration scheme, showing a heterogeneous SOP-L substrate with ICs and some passive components mounted on the surface. The assembled substrate is then overmolded, making the SOP integration invisible to the end-user.

Organic substrate, with multiple dielectric layers having multiple electrical properties

**Figure 1.8.** SOP implementation, with heterogenous MCM-L substrate. Multiple chips, some low-profile passive components and a few discrete passives are attached to the top, and the whole structure is overmolded.

In such an implementation scheme, the passive functionality is divided between embedded circuits in the substrate and low-profile soldered-on components on the top surface. Capacitance or inductance values that are very much higher than the SOP component densities are automatically implemented as surface mount devices (SMD) soldered on top of the substrate surface. For example, RF bypass and/or power-supply decoupling capacitors have values in the range of  $0.1-10\mu$ F, and are implemented by soldering on 0402 or 0201 chip capacitors to the substrate surface. For implementing passive circuits with values of inductance and capacitance lower than or approaching the SOP component density, there exist two options:

- 1) <u>Substrate</u>:

- Passive functionality embedded in the packaging substrate.

- ICs and SMDs attached on the top surface.

- Internal routing and redistribution layers.

- *Custom designs*, with pin-outs, foot-prints and land-patterns varying with each chip-set and application.

- 2) <u>Integral Passive Device (IPD)</u>:

- Passive circuits fabricated on a low-profile stack-up. They are then singulated and attached on top of the module substrate like any other SMD.

- Complete or partial shielding based on application.

- *Standard designs*, with standard pin-outs and land-patterns that can be used in multiple applications with multiple chip-sets.