## MODELING, DESIGN AND DEMONSTRATION OF LARGE 2.5D GLASS BGA PACKAGES FOR BALANCED CHIP- AND BOARD-LEVEL RELIABILITY

A Thesis Presented to The Academic Faculty

by

Vidya Jayaram Mythly

In Partial Fulfillment of the Requirements for the Degree Master of Science in the School of Material Science and Engineering

Georgia Institute of Technology

May 2017

Copyright © Vidya Jayaram Mythly 2017

## MODELING, DESIGN AND DEMONSTRATION OF LARGE 2.5D GLASS BGA PACKAGES FOR BALANCED CHIP- AND BOARD-LEVEL RELIABILITY

Approved by:

Prof. Rao Tummala, Advisor School of Material Science and Engineering *Georgia Institute of Technology*

Prof. Suresh Sitaraman School of Mechanical Engineering *Georgia Institute of Technology*

Dr. Vanessa Smet School of Electrical and Computer Engineering *Georgia Institute of Technology*

Date Approved: April 20, 2017

To my Amma and Appa

#### ACKNOWLEDGEMENTS

By submitting this thesis, my long and delightful journey of being a student is officially over. This journey would have not been possible without having the guidance, friendship, help, and support of many wonderful people to whom I will always be grateful.

I would like to express my sincere gratitude to my advisor, Prof. Rao Tummala, for giving me the opportunity to join his team and work under his supervision. His passion and enthusiasm for research, his distinct personality and leadership skills have constantly inspired me throughout my studies as a Master's student. I have always felt I am a fortunate graduate student to have him as my advisor, not only because he is a great professor who provides enormous number of research opportunities for his students, but also because he is an extraordinary human being and a great teacher.

Next, I would like to thank my mentor, Dr. Vanessa Smet. Her encouragements, patience, and continuous support of my work have made my 2 years of working with her an exceptional experience for me and I am deeply grateful. She has stood by me through both my professional and personal difficulties, and I always say with confidence that I can go to war with Vanessa by my side.I could not have asked for a better mentor and a friend.

I am also very grateful to Dr. Raj Pulugurtha and Dr. Venky Sundaram for sharing with me their knowledge and guiding me throughout the course of my research. I would like to thank Prof. Suresh Sitaraman for being on my thesis defense committee and for providing insightful comments about my work.

Being part of an active research group of motivated and knowledgeable members is significantly important to the success of every graduate student. I feel very fortunate to have been part of such a team at the 3D Systems Packaging Research Center with hard-working students who selflessly helped me out with different aspects of my research. I would specially like to mention Dr. Scott McCann for his expertise and relentless help on ANSYS modeling - without which my progress on that front would be impossible. His

training sessions on tools for warpage and reliability analysis helped me a long way. Many thanks to my colleagues from the Interconnections & Assembly team: Bhupender Singh for mentoring me, Nathan for his guidance on assembly with Kulicke and Soffa bonder and underfill processes, Siddharth Ravichandran for assisting me with fabrication and assembly processes, Ninad Shahane and Kashyap Mohan for their constant encouragement and moral support. I would also like to thank Zihan Wu, Jialing Tong, Bruce Chao, Karan Bhangaonkar, Shreya Dwarakanath, Chandrasekharan Nair, Omkar Gupte and all other fellow GRAs. My past two years at PRC have been filled with a lot of good memories because of these wonderful people. I will definitely miss our group meetings, conference trips, coffee breaks and I will always be grateful for their friendship. I am grateful to the visiting engineers - Satomi Kawamoto for help with underfill processes, Hiroyuki Matsuura and Yuya Suzuki for their help on fabrication. I would like to specially thank Chris White and Jason Bishop for their assistance with lab equipment. I would also like to thank Karen May, Brian McGlade, Patricia Allen and Kimberly Purvis for their great support of my administrative needs.

I am indebted to my parents, Mythly and Jayaram, for their unconditional love and support throughout my life. My father has always been an example to follow my mother has been a continuous source of love and moral support. They taught me to never give up and have continuously provided me not only great hopes and strong motivations but everything I need in the world to build myself a better future. Many thanks to my wonderful grandparents for their love over the years. This thesis would have not been possible without the support of my friends and family.

## TABLE OF CONTENTS

| Acknov    | vledgments                                                                   | iv |

|-----------|------------------------------------------------------------------------------|----|

| List of ' | Tables                                                                       | x  |

| List of ] | Figures                                                                      | xi |

| Chapte    | r 1: Introduction                                                            | 1  |

| 1.1       | Evolution in electronics packaging from transistor scaling to system scaling | 2  |

| 1.2       | Emergence of 2.5D technology                                                 | 4  |

| 1.3       | Research objectives                                                          | 6  |

| 1.4       | Technical challenges                                                         | 7  |

| 1.5       | Unique approach addressing technical challenges                              | 10 |

| 1.6       | Research tasks and thesis organization                                       | 13 |

| Chapte    | r 2: Literature Review                                                       | 15 |

| 2.1       | Recent advances in multi-chip packaging                                      | 15 |

| 2.2       | Material developments in interconnections for board-level reliability        | 20 |

|           | 2.2.1 Advances in surface finishes and doped solders                         | 21 |

|           | 2.2.2 Advances in underfill materials at board-level                         | 22 |

|           | 2.2.3 Compliant interconnections                                             | 24 |

| 2.3     | Warpage mitigation in assembly |                                                                                               |    |

|---------|--------------------------------|-----------------------------------------------------------------------------------------------|----|

| 2.4     | Summ                           | ary                                                                                           | 32 |

| Chapter |                                | deling and design of a 2.5D glass package for balanced chip- and ard-level reliability        | 34 |

| 3.1     | Test ve                        | chicle design of a 2.5D glass BGA package                                                     | 34 |

|         | 3.1.1                          | Daisy chain test dies                                                                         | 34 |

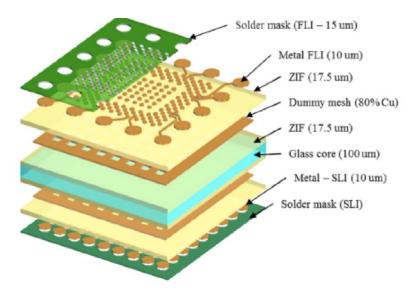

|         | 3.1.2                          | Test vehicle substrate stack up                                                               | 35 |

| 3.2     | Desigr                         | n methodology                                                                                 | 35 |

| 3.3     |                                | element modeling for system-level reliability and minimum warpage 5D glass BGA package        | 38 |

|         | 3.3.1                          | Geometric model                                                                               | 38 |

|         | 3.3.2                          | Material modes and stress free temperatures                                                   | 39 |

|         | 3.3.3                          | Thermal loading conditions for thermomechanical and warpage sim-<br>ulations                  | 41 |

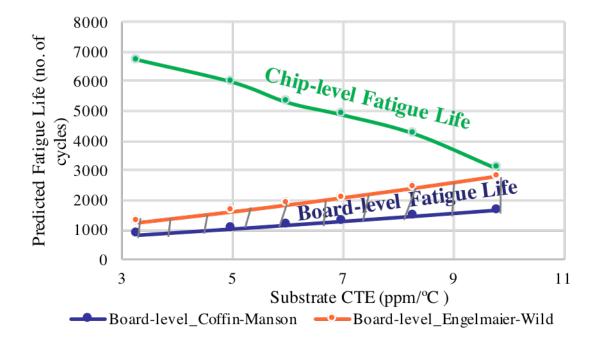

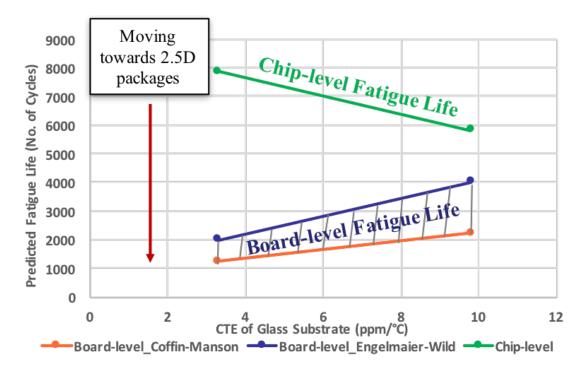

|         | 3.3.4                          | Effect of coefficient of thermal expansion of substrate on fatigue life of solders            | 42 |

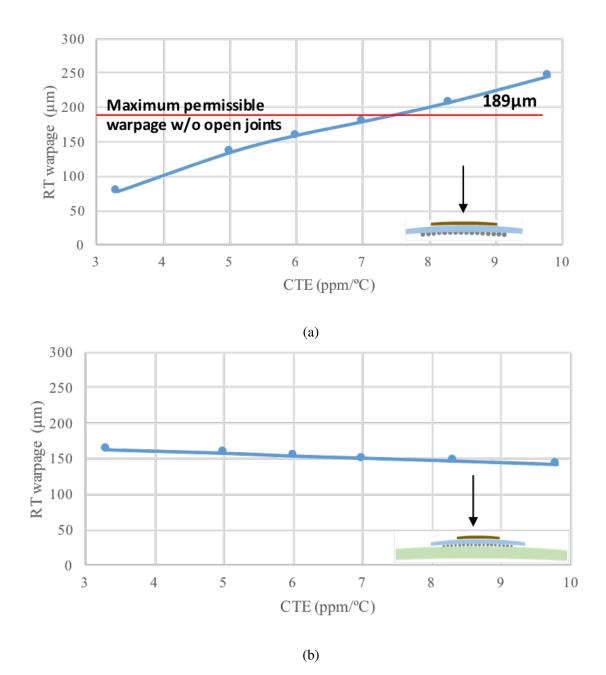

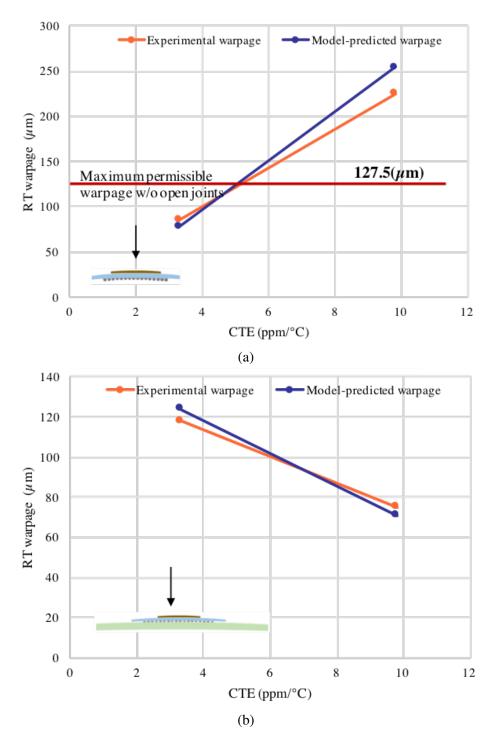

|         | 3.3.5                          | Effect of coefficient of thermal expansion of substrate on warpage behavior                   | 44 |

| 3.4     | Summ                           | ary                                                                                           | 47 |

| Chapter |                                | deling, design and demonstration of board-level reliability for<br>ain relief and reliability | 50 |

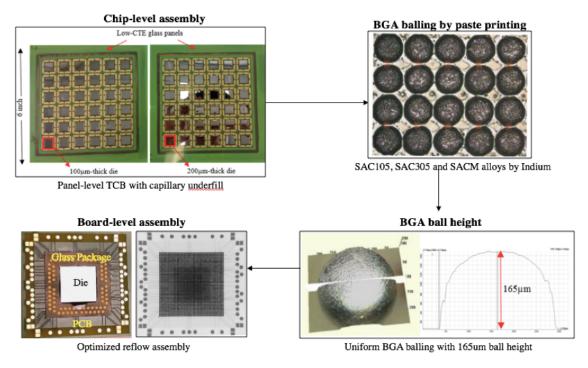

| 4.1     | Test ve                        | chicle design and fabrication of a single-chip glass BGA package                              | 50 |

|         | 4.1.1                          | Daisy chain test die                                                                          | 50 |

|         | 4.1.2                          | Glass substrate fabrication                                                                   | 51 |

|         | 4.1.3                          | PCB board design                                                                              | 53 |

| 4.   | .2 Finite-element modeling for analysis of system-level reliability and room temperature warpage |         | 53                                                                              |    |

|------|--------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------|----|

|      |                                                                                                  | 4.2.1   | Geometric model                                                                 | 53 |

| 4.   | .3                                                                                               | Assem   | bly and yield evalutation                                                       | 59 |

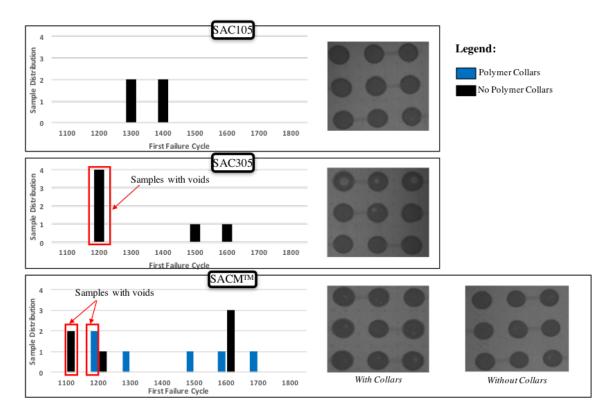

| 4.   | .4                                                                                               | Therm   | al cycling reliability test                                                     | 62 |

|      |                                                                                                  | 4.4.1   | Failure distribution                                                            | 62 |

|      |                                                                                                  | 4.4.2   | Optical inspection                                                              | 64 |

| 4.   | .5                                                                                               | Summ    | ary                                                                             | 65 |

| Chap | oter                                                                                             |         | ermocompression bonding process design and optimization for page mitigation     | 67 |

| 5.   | .1                                                                                               | Test ve | chicle design and fabrication of a low-CTE single-chip package                  | 67 |

| 5.   | .2                                                                                               |         | element modeling for warpage mitigation in thermocompression bond-              | 68 |

|      |                                                                                                  | 5.2.1   | Geometric model                                                                 | 68 |

|      |                                                                                                  | 5.2.2   | Thermal loading conditions and model-predicted warpage analysis                 | 71 |

| 5.   | .3                                                                                               | Therm   | ocompression bonding assembly process and parameters                            | 73 |

| 5.   | .4                                                                                               | Analys  | is of warpage during assembly                                                   | 75 |

|      |                                                                                                  | 5.4.1   | Experimental warpage measurements                                               | 75 |

|      |                                                                                                  | 5.4.2   | Effect of TCB stage temperature on warpage without substrate-<br>stage coupling | 76 |

|      |                                                                                                  | 5.4.3   | Effect of stage temperature on substrate-stage coupling                         | 77 |

| 5.   | .5                                                                                               | Conclu  | isions                                                                          | 79 |

| Char | oter                                                                                             | 6: Sur  | nmary and conclusions                                                           | 80 |

| 6    | .1                                                                                               | Summ    | ary of task 1 results                                                           | 81 |

| Referen | ices                      | 92 |

|---------|---------------------------|----|

| 6.4     | Conclusions               | 85 |

| 6.3     | Summary of task 3 results | 83 |

| 6.2     | Summary of task 2 results | 82 |

# LIST OF TABLES

| 1.1 | Research objectives beyond prior art, technical challenges and associated research tasks                      | 7  |

|-----|---------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Physical properties of materials in modeling                                                                  | 40 |

| 3.2 | Anand's model parameters for SAC105                                                                           | 41 |

| 3.3 | Maximum plastic strain range values at chip- and- board-level solder joints .                                 | 43 |

| 3.4 | Material constants in the Engelmaier-Wild model                                                               | 44 |

| 3.5 | Predicted number of cycles to thermomechanical failure                                                        | 44 |

| 4.1 | Summary of stack-up materials and design rules                                                                | 53 |

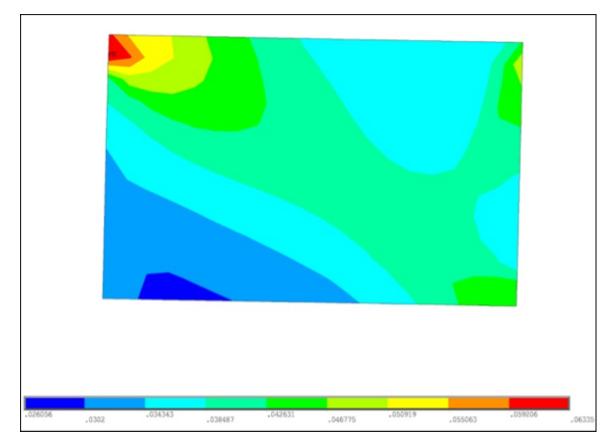

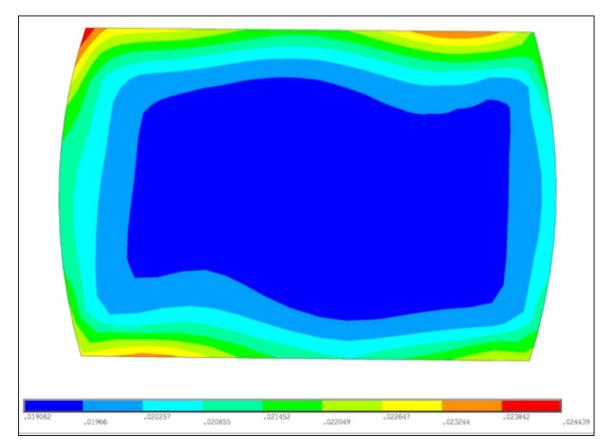

| 4.2 | Maximum plastic strain range values at chip- and- board-level solder joint .                                  | 56 |

| 4.3 | Predicted fatigue life for chip- and- board-level assembly using Coffin-<br>Manson and Engelmaier-Wild models | 57 |

| 4.4 | Preliminary evaluation of number of samples in test for thermal cycling reliability.                          | 61 |

| 5.1 | Material properties used in modeling                                                                          | 71 |

| 6.1 | Summary of the technical challenges addressed through associated research tasks                               | 81 |

# LIST OF FIGURES

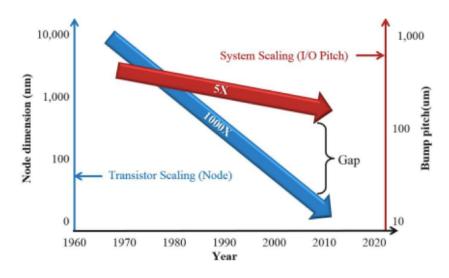

| 1.1 | Gap between transistor and system scaling (Courtesy Dr. S. Iyer, IBM)                                                                                                                          | 3        |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

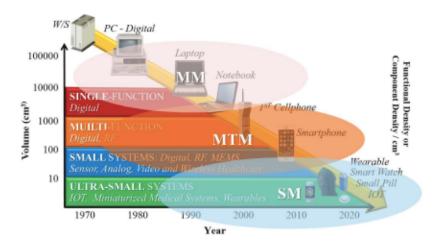

| 1.2 | Increasing functional densities for next-generation ultra-small systems: system scaling by System Moore (SM) for heterogeneous integration beyond More of Moore (MM) and More than Moore (MTM) | 4        |

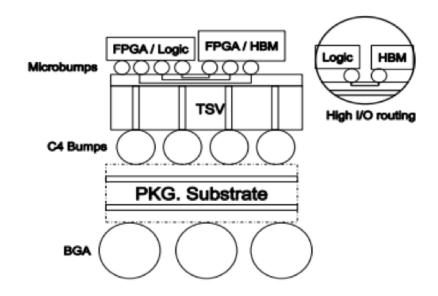

| 1.3 | 2.5D approach with lateral I/O connections using passive Si interposers. $\therefore$                                                                                                          | 5        |

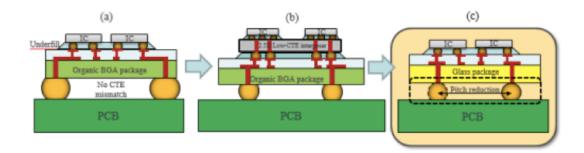

| 1.4 | Traditional package approach (a) IC organic BGA PCB, current package (b) IC low-CTE interposer organic BGA PCB, and new package approach (c) IC large and thin glass package PCB.              | 6        |

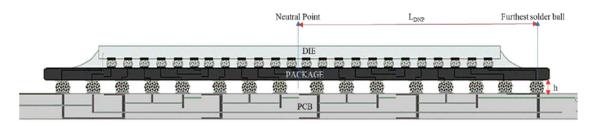

| 1.5 | Die-package-board interconnections with large LDNP and low stand-off height.                                                                                                                   | 9        |

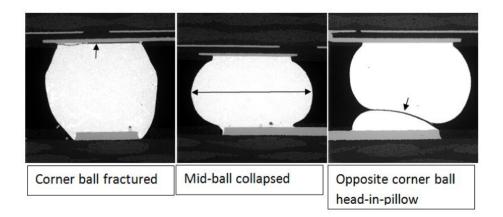

| 1.6 | Typical defects in solder balls due to assembly-induced package warpage (Courtesy of SEM Lab, Inc.)                                                                                            | 10       |

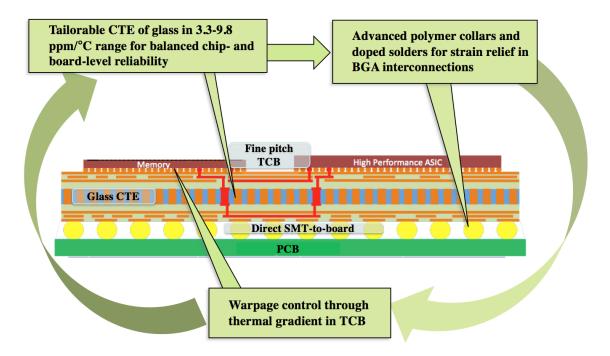

| 1.7 | Unique approach for balanced- chip and- board-level reliability of a large, 2.5D glass package with direct SMT-to-board                                                                        | 11       |

| 2.1 | 3-level hierarchical 2.5D integration with two 28 nm FPGAs and one transceive die placed side by side on a 20 mm x 25 mm silicon interposer assembled on high-CTE ceramic substrate (Xilinx).  | er<br>17 |

| 2.2 | High-bandwidth memory stacks with a center GPU on a silicon interposer assembled on an organic laminate (SK Hynix).                                                                            | 17       |

| 2.3 | 2.5D FLI assembly at 100 $\mu$ m die-to-die spacing (a.) top view of 25 mm x 30 mm six-metal-layer glass interposer (b) cross-section (c) FLI detailed cross-section.                          | 18       |

| 2.4 | Parametric effects on the maximum principle stress of glass                                                                                                                                    | 19       |

| 2.5  | Von Mises stress in volume average at the corner solder ball                                                                   |    |  |

|------|--------------------------------------------------------------------------------------------------------------------------------|----|--|

| 2.6  | Intel's EMIB assembly, Process flow to achieve FOWLP - Courtesy of Beth Keser, Amkor Technology Inc's SLIM and SWIFT.          | 20 |  |

| 2.7  | Microstructures of (a) SAC305, (b) SAC105, (c) SAC105 + 0.15Mn, (d) SAC105 + 0.5Mn, (e) SAC105 + 0.15Ti and (f) SAC105 + 0.5Ti | 23 |  |

| 2.8  | Drop test reliability of SAC solder with dopants                                                                               | 24 |  |

| 2.9  | Thermal cycling results for SnPb, SAC105, SAC305 and SACm <sup>TM</sup>                                                        | 24 |  |

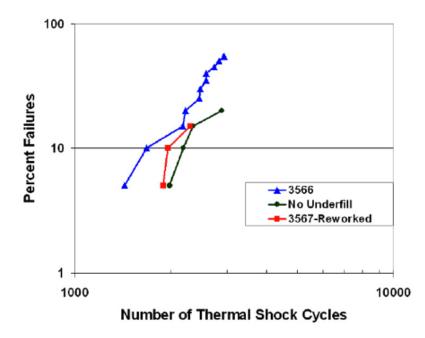

| 2.10 | Percent failures for different underfill types.                                                                                | 25 |  |

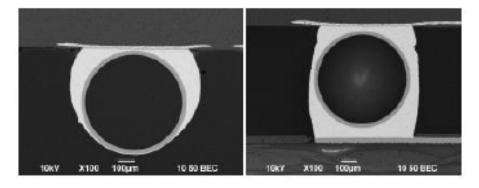

| 2.11 | Cross-section of polymer core solder ball after balling and assembly                                                           | 25 |  |

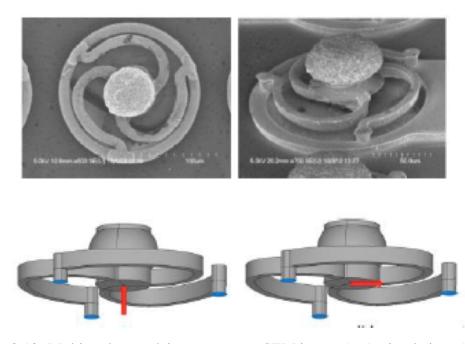

| 2.12 | Multi-path complaint structures - SEM image, simulations                                                                       | 26 |  |

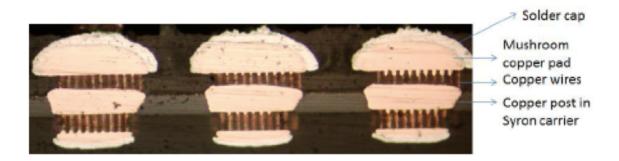

| 2.13 | Cross section of MWA interconnections.                                                                                         | 27 |  |

| 2.14 | Cross-section of an 18.4 mm interposer with uniform collar formation achieved after spin-coating profile optimization.         |    |  |

| 2.15 | Comparison of warpage during thermocompression bonding and mass reflow.                                                        | 29 |  |

| 2.16 | Vacuum fixture with carrier during mass reflow, uniform ball height cross-<br>section, warpage with and without vacuum fixture | 29 |  |

| 2.17 | Interposer warpage as a function of TCB stage temperature                                                                      | 30 |  |

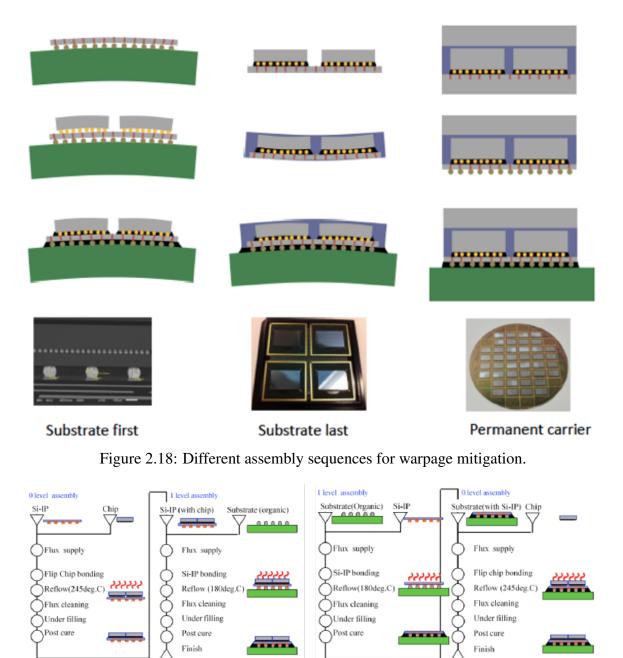

| 2.18 | Different assembly sequences for warpage mitigation                                                                            | 31 |  |

| 2.19 | Assembly sequence process flow with chip-first and chip-last                                                                   | 31 |  |

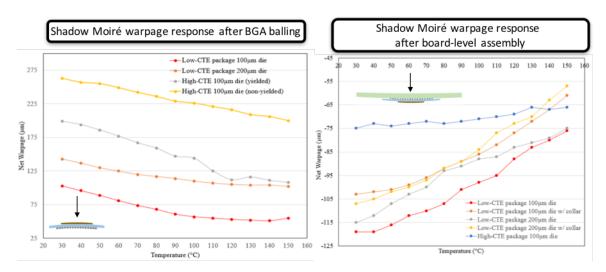

| 2.20 | Shadow Moire warpage response after BGA balling and after package-to-<br>board assembly                                        | 32 |  |

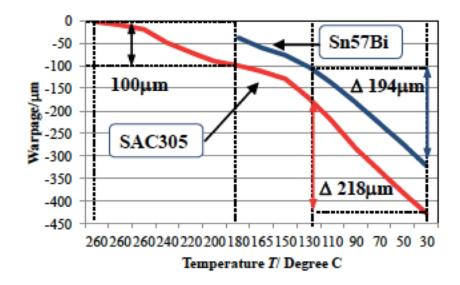

| 2.21 | Warpage response of standard SAC305 vs low-melting Sn57Bi solder                                                               | 33 |  |

| 3.1  | Assembly test vehicle layout of 2.5D glass BGA package with center logic emulator and 4 stacked HBMs on the periphery.         | 35 |  |

| 3.2  | Logic emulator with exterior and interior array design parameters; high-<br>bandwidth memory emulator die design.              | 36 |  |

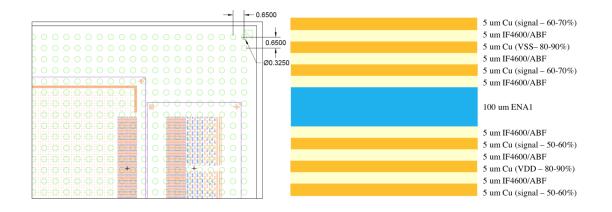

| 3.3  | Substrate design and substrate stack-up.                                                                                            | 36 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

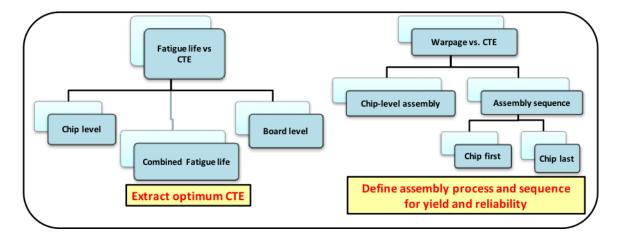

| 3.4  | Assembly design methodology for balanced reliability of 2.5D packages                                                               | 37 |

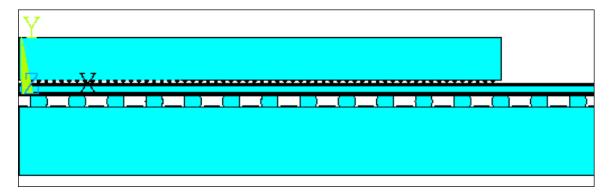

| 3.5  | Example geometry in modeling.                                                                                                       | 39 |

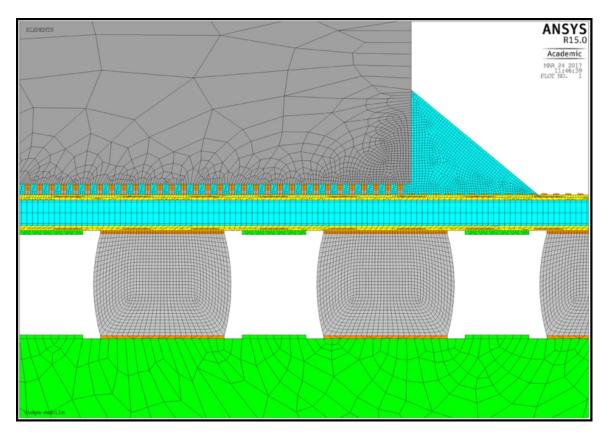

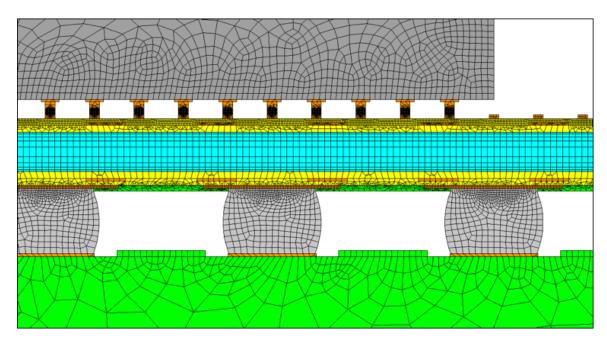

| 3.6  | Example mesh in modeling refined at solder and thin layers                                                                          | 39 |

| 3.7  | Two numerical solutions                                                                                                             | 45 |

| 3.8  | Model-predicted chip- and- board-level fatigue life for a 2.5D glass BGA package.                                                   | 46 |

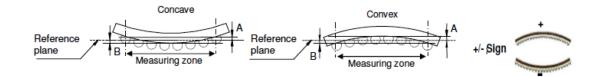

| 3.9  | JEDEC-defined package warpage convention.                                                                                           | 46 |

| 3.10 | Example warpage at room temperature after chip-level assembly                                                                       | 47 |

| 3.11 | Two numerical solutions                                                                                                             | 48 |

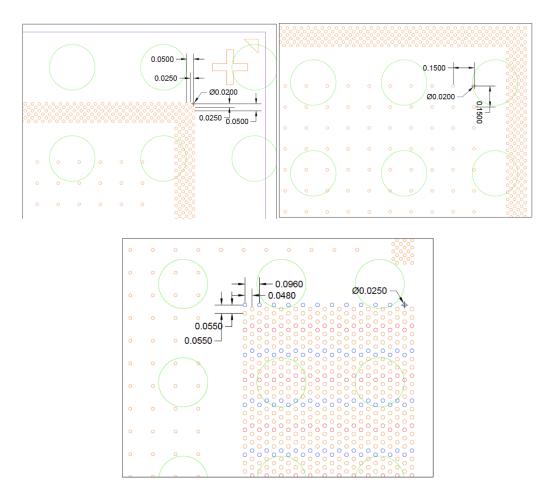

| 4.1  | Daisy-chain test die: a) design and b) optical image of a bumped corner (Image courtesy of ASE).                                    | 51 |

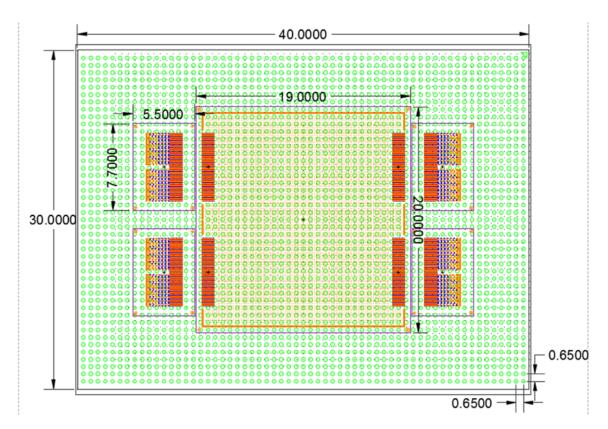

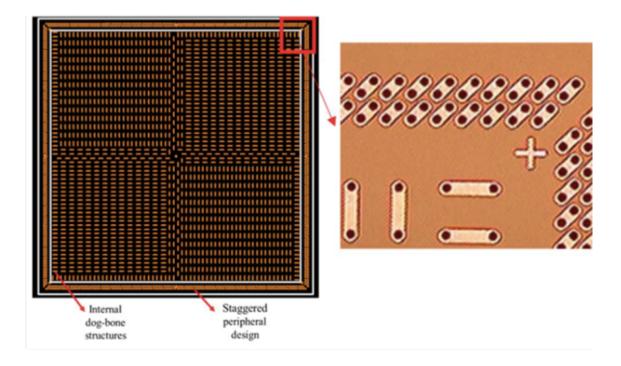

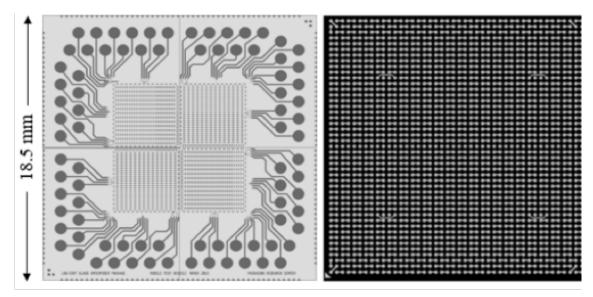

| 4.2  | Glass substrate test vehicle design on the die side, and the BGA side                                                               | 52 |

| 4.3  | Schematic of 18.5 mm x 18.5 mm 4-metal layer glass substrate                                                                        | 52 |

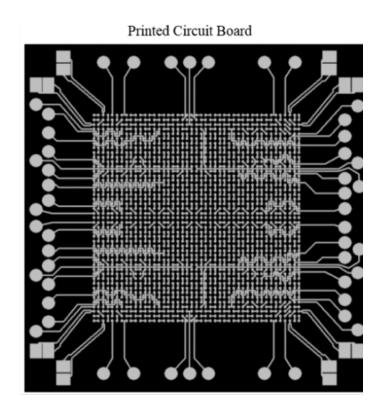

| 4.4  | Daisy-chain interconnection design of PCB with probing pads                                                                         | 54 |

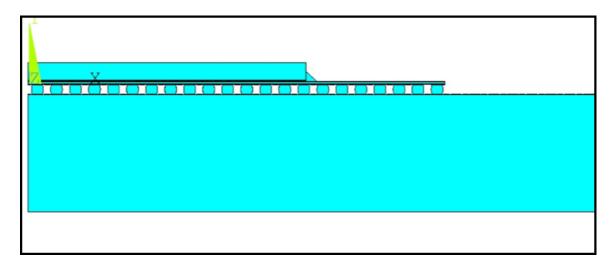

| 4.5  | Example geometry in modeling. Two-dimensional geometry represents a cut along the diagonal of the package with symmetry at the left | 54 |

| 4.6  | Example mesh used in modeling for thermal and mechanical analysis                                                                   | 55 |

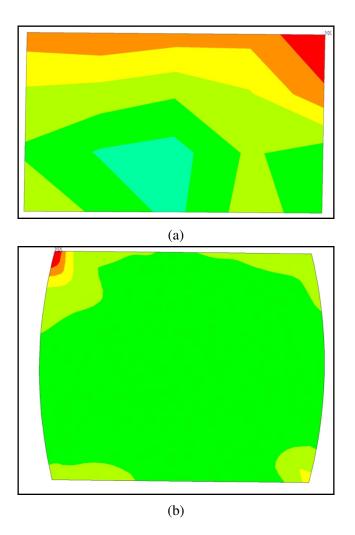

| 4.7  | Plastic strain distribution of outermost solder joint at chip-level                                                                 | 56 |

| 4.8  | Plastic strain distribution of outermost solder joint at board-level                                                                | 57 |

| 4.9  | Fatigue life vs. CTE using Coffin-Manson and Engelmaier-Wild models                                                                 | 58 |

| 4.10 | Two numerical solutions                                                                                                             | 60 |

| 4.11 | Summary of test vehicle assembly of low-CTE glass panels with 100 $\mu$ m and 200 $\mu$ m dies.                                     | 62 |

| 4.12 | Failure distribution for low-CTE glass packages with 200 $\mu \rm m$ thick die                                                                      | 63 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.13 | Failure distribution for low-CTE glass packages with 100 $\mu \rm m$ thick die. $~$ .                                                               | 64 |

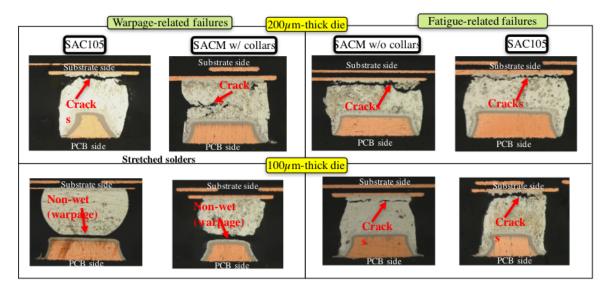

| 4.14 | Optical characterization of cross-sections of failed assemblies with SAC105, SAC305 and SACm <sup>TM</sup> BGAs for identification of failure modes | 65 |

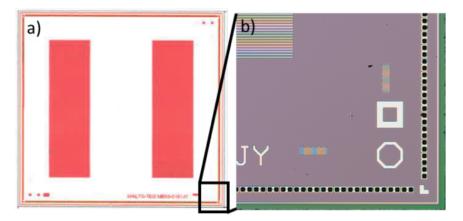

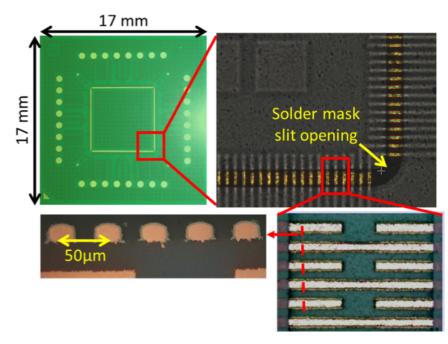

| 5.1  | Daisy chain test die at 50 $\mu$ m pitch: a) design and b) optical image of a bumped corner (Walts Co. LTD)                                         | 68 |

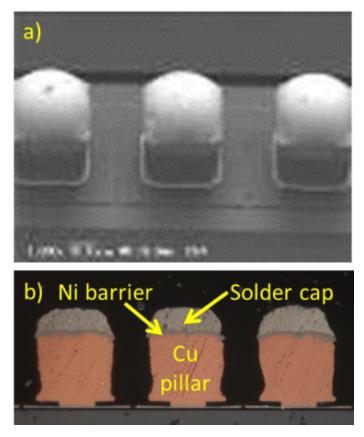

| 5.2  | Cu pillar interconnections at 50 $\mu$ m pitch: a) top view, and b) cross-section.                                                                  | 69 |

| 5.3  | Low-CTE organic substrate with bump-on-trace wiring (Walts Co. LTD).                                                                                | 69 |

| 5.4  | Substrate stack-up design (Courtesy of Walts)                                                                                                       | 70 |

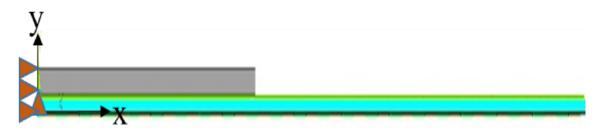

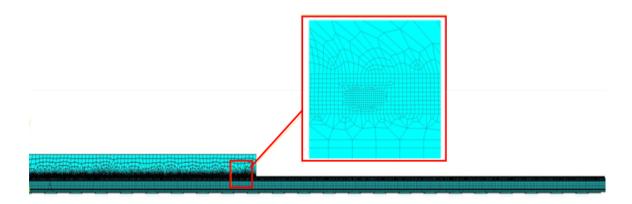

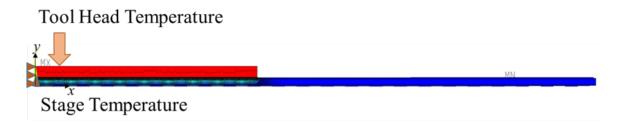

| 5.5  | Example geometry in modeling. Two-dimensional geometry represents a cut along the diagonal of the package with symmetry at the left                 | 70 |

| 5.6  | Example mesh used in modeling for thermal and mechanical analysis                                                                                   | 71 |

| 5.7  | Example of thermal gradient in the package during TCB                                                                                               | 72 |

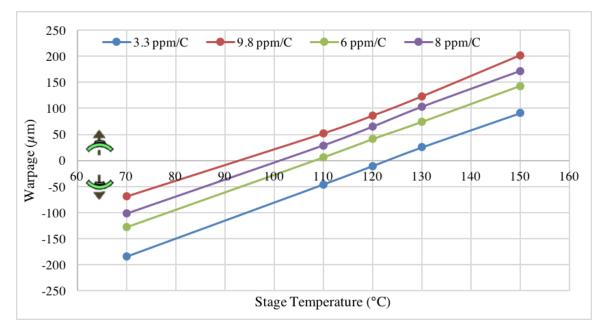

| 5.8  | Predicted warpage as a function of stage temperature for a range of sub-<br>strate CTEs                                                             | 72 |

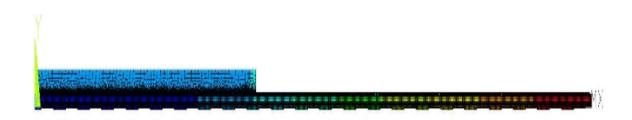

| 5.9  | Predicted warpage of low-CTE package assembled using 70 °C stage temperature conditions.                                                            | 73 |

| 5.10 | Minimum warpage stage temperature as a function of substrate CTE                                                                                    | 73 |

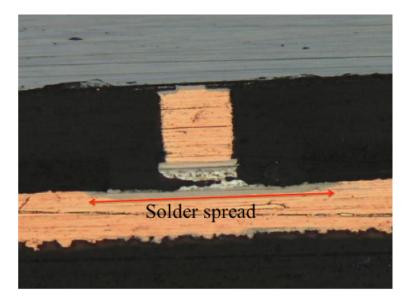

| 5.11 | Cross-section of a non-yielded assembly with excessive solder lateral spread.                                                                       | 75 |

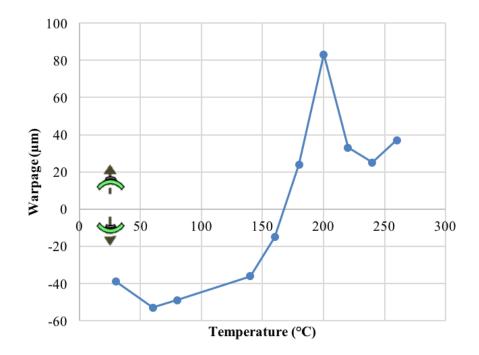

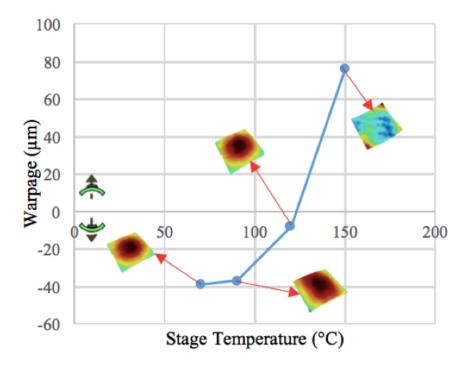

| 5.12 | Package warpage as a function of temperature for TCB profile with 70 °C stage temperature.                                                          | 76 |

| 5.13 | Room temperature package warpage as a function of stage temperature without coupling the substrate to the stage                                     | 77 |

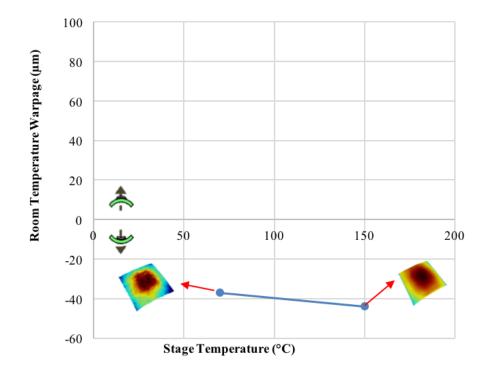

| 5.14 | Room temperature package as a function of stage temperature warpage with coupling the substrate to the stage.                                       | 78 |

#### SUMMARY

Transistor scaling, driven by Moores Law, has enabled the integration of billions of transistors on a single integrated chip (IC); thereby enabling rapid miniaturization of microprocessor devices such as smartphones, servers and personal computers. However, silicon integration following Moore's law is now reaching its limits due to increasing design complexity and cost, bringing the need for a new "System Scaling" approachfor further miniaturization and performance improvements. The System-on-Package (SOP) approach, pioneered by Georgia Tech PRC, relies on co-integration of multiple electronic functions on a package substrate, as opposed to on-chip. Packaging, therefore, becomes key in enabling higher functional densities. An example of this new approach to system design is the recent trend of "split dies" where large devices is broken down into smaller devices at finer I/O pitches that are interconnected on a substrate using high-density wiring. These advanced package architectures such as 2.5D interposer packages now rely on packaging to improve performance and miniaturize the system as a whole.

Silicon interposers are particularly attractive in such split-die applications due to their outstanding lithographic capability enabling high-density, high-speed die-to-die interconnections. Such 2.5D interposers tend to be fairly large with body sizes exceeding 30 mm x 40 mm, bringing unprecedented board-level reliability challenges due to large mismatch in coefficients of thermal expansion (CTE) between silicon and mother boards. These challenges are typically addressed by introducing an additional organic BGA package between interposer and board to accommodate for the CTE mismatch and decrease in pitch. However, this degrades electrical performance with longer interconnection lengths, and adds to the overall cost.

Glass has emerged as an alternative substrate technology to overcome the shortcomings of silicon. Glass has been demonstrated to have superior electrical properties than silicon with lower losses and can accommodate high-density wiring owing to micron-scale lithographic design rules. Further, glass can be tailored for a wide CTE range of 3.3 to 9.8 ppm/K. This unique property brings design flexibility to address board-level reliability challenges and directly assemble large glass interposer packages to boards without the need for an intermediate organic package.

The primary objective of this research is to model, design and demonstrate a large, 2.5D glass BGA package with 1) direct SMT-to-board interconnection; and 2) balanced chip- and- board-level reliability. The ultimate goal is to provide guidelines for the design of 2.5D glass BGA packages, optimizing the glass CTE to mitigate warpage and achieve system-level reliability, and subsequently the assembly process and sequence.

Finite-element models were built to assess the reliability of 2.5D glass packages with direct SMT assembly to the board. The methodology for achieving balanced chip- and-board-level reliability was validated through focused modeling and experimental results for a single-chip package. Board-level reliability was recognized as the most critical challenge and enhanced byusing innovative doped solder materials such as Indium's Mn-doped SACm<sup>TM</sup> alloy and strain-relief mechanisms to give more design flexibility. Failure distribution analysis and optical characterization was performed to evaluate thermal cycling reliability. A process design approach was demonstrated for mitigating warpage induced by thermocompression bonding on ultra-thin, low- and- high-CTE substrates at I/O pitches below 50  $\mu$ m. By selecting optimum thermal profiles for mitigating chip-level assembly warpage, board-level assembly is enabled at larger package sizes, and system-level reliability is thereby enhanced.

# CHAPTER 1 INTRODUCTION

Modern consumer electronics industry is being driven by size, cost and performance. With Moore's Law reaching its physical limits, the need for advanced microelectronics packaging is being recognized. The recent split die trend is an example of this new System Scaling approach to system design, in which a large die is divided in multiple smaller dies at finer pitch. Functionality is then reconstituted through high-density fine-pitch wiring on the substrate. Silicon interposers have gained strong momentum in such 2.5D package architecture as they, unlike organic substrates, can support the required interconnect density. However, such interposers tend to be thin and large, averaging 30 mm 40 mm in body size, which brings unprecedented yield and reliability challenges at board level due to the large mismatch in coefficient of thermal expansion (CTE) between silicon and motherboard. To address these challenges, an additional organic BGA package is typically introduced between interposer and board, which degrades electrical performance and adds to the system's cost. A two-level hierarchy with direct surface-mount (SMT) assembly of the interposer on the motherboard is, therefore, desirable to meet the performance and miniaturization needs of future high-performance systems. Georgia Tech has recently pioneered glass as an alternative substrate technology overcoming the shortcomings of silicon. Glass has superior electrical properties with low losses, is capable of 5  $\mu$ m lithographic design rules giving high-density multi-layered wiring, and has unique mechanical properties such as high modulus and tailorable CTE in the 3.2-9.8 ppm/K range, giving design flexibility to balance chip- and board-level reliability. Thus, 2.5D glass interposer packages where the interposer also acts as a package can comprehensively address the aforementioned challenges.

#### 1.1 Evolution in electronics packaging from transistor scaling to system scaling

Transistor scaling, driven by Moore's Law, has enabled the integration of billions of transistors on a single integrated chip (IC); thereby reducing cost and enhancing the performance in addition to rapid miniaturization of microprocessor devices such as smartphones, servers and personal computers. It gave rise to on-chip integration also known as system-on-chip (SOC). This technology aims at combining multiple heterogeneous functions such as processor, memory, wireless and graphics by integrating the required components on a single chip. Although SOC aims at providing highest performance at a compact system level, it faces cost, design, fabrication and integration challenges. These challenges act as drivers for considering other ways to integrate at system level such as system-in-package (SIP) and multi-chip modules (MCM). To achieve the expected performance with the SOC approach, larger multi-functional dies are required. However, such large and complex dies face major yield limitations at wafer scale. MCMs were sought as an approach to functionally integrate smaller dies interconnected horizontally in addition to providing design flexibility for each functional component. They evolved from HTCCs that included multilayer ceramics interconnected with multiple wiring layers to LTCCs with dielectric layer build ups and sputtered or electroplated copper conductors with better electrical conductivity. In parallel to MCMs, the SIP approach was also pursued. SIPs are defined as three dimensional or vertical stacking of ICs that may or may not be similar in functionality. This approach leads to miniaturization if the size and thickness of stacked components are reduced. In the process of integrating all system components and power sources on the system board, this technology faces processing challenges at nanoscale, and integration thus becomes difficult. In addition, SIP only aims at silicon integration that accounts for barely 10% of the overall system. However, due to their benefits, a wide range of SIP-based modules has been implemented in high-volume production, with the following classification: (a) SIP by wire bonding, (b) SIP by flip chip and wire bonding, (c) SIP by flip chip-on-chip, (d) 3D

integration by through-silicon-via technology and (e) SIP by package stacking. Although SOC, MCM and SIP seek to ultimately increase functionality while following Moore's Law, they fail to achieve miniaturization at system level. The performance of ICs depends on transistor density which is now being limited by constraints on Moore's Law. The gap between transistor scaling (based on the gate length of a transistor) and system scaling (based on off-chip interconnection pitch) illustrated in Figure 1.1 indicates the need for a new paradigm for system integration and miniaturization.

Figure 1.1: Gap between transistor and system scaling (Courtesy Dr. S. Iyer, IBM).

Georgia Tech's 3D Systems Packaging Research Center (3D-PRC) has been pioneering System-on-Package (SOP) to address the fundamental challenges of existing technologies [1]. System on package (SOP) is a novel concept based on miniaturization of the device, package and system board into a single package that includes all system functions. The two main criteria governing SOP are size reduction and increased functionality. SOP reduces the size of 80-90% of the non-IC part of the system through ultra-high wiring densities with less that 5  $\mu$ m lines and spaces, use of RDLs and embedded ultrathin film components. Additionally, it also reduces cost and provides technical advantages in digital, wireless and optoelectronic-based systems. SOP provides a balance between IC and package integration that overcomes the shortcomings of the technologies stated above. Advanced packaging so-

Figure 1.2: Increasing functional densities for next-generation ultra-small systems: system scaling by System Moore (SM) for heterogeneous integration beyond More of Moore (MM) and More than Moore (MTM) [1].

lutions, realizing the SOP concept, are therefore necessary to achieve ultra-miniaturization and increased functionality, with tomorrows smartphones having the same functions as that of todays supercomputers, tomorrows smart-watches with the same performance as that of todays smartphones and so on (Figure 1.2).

#### 1.2 Emergence of 2.5D technology

Smart systems of today require high logic-to-memory bandwidth with high signal switching speeds. The system bandwidth for high-performance applications is expected to double every year [2] and estimated to increase to 512 GB/s to 1 TB/s in the near future. Such systems continue to follow the trend of ultra-miniaturization. This introduces additional demands to achieve higher bandwidths at reduced form factor, besides the need to reduce cost and power consumption. To meet the demands, new technologies were introduced with ultra-fine pitch interconnections between logic and memory devices through 3D stacking with vertical through-silicon-vias (TSV) interconnections or horizontal 2.5D interconnections. The 3D vertical stacking of logic and memory chips, interconnected by TSVs is shown in Figure 1.3 [3]. This approach stacks memory chips on top of the logic die at the bottom and requires TSVs in the logic dies. This creates several challenges such as

Figure 1.3: 2.5D approach with lateral I/O connections using passive Si interposers.

complex co-design between logic and memory dies, large thermomechanical stresses on active devices from TSVs, high electrical losses and yield loss due to lack of testability of known-good-dies (KGD).

To address these challenges, a new approach of high-density horizontal interconnections was introduced between logic and memory dies. It follows a similar concept as that of multichip modules (MCMs), but with higher I/O densities, known as 2.5D technology. To maintain high functional densities, chip-level interconnections of logic and memory dies are moving towards finer pitches of less than 35  $\mu$ m. This, in turn, imposes finer die-to-die interconnect pitches below 10  $\mu$ m. Silicon-based 2.5D interposers were subsequently considered due to their high-density sub-5  $\mu$ m wiring capability. AMDs Fury and Xilinxs FPGAs are some of the commercial implementations of the silicon interposer technology. However, the dielectric losses associated with silicon is a limiting factor. Also, an additional organic layer was introduced in 2.5D packages, to address the challenge of board-level thermomechanical reliability. Nevertheless, this resulted in additional concerns of increased parasitics, larger thicknesses and higher costs. An ideal solution would be to have a package that can be directly mounted on to the board with a 2-level hierarchy, with

Figure 1.4: Traditional package approach (a) IC organic BGA PCB, current package (b) IC low-CTE interposer organic BGA PCB, and new package approach (c) IC large and thin glass package PCB.

lowered costs and increased bandwidths (Figure 1.4).

Glass substrates have emerged as a promising alternative to silicon interposers for 2.5D applications owing to their superior electrical properties including low loss tangent, low dielectric constant. Glass also exhibits superior thermal and dimensional stability and low surface roughness giving micron-scale lithographic capability. Glass also exhibits superior thermal and dimensional stability and low surface roughness. Additionally, glass can be processed at a large panel scale, resulting in higher throughput and lower cost. Further, glass has tailorable CTE (3.8-9.8 ppm/K) and high modulus, hence can mitigate warpage introduced by thickness reduction. The tailorable CTE also provides design flexibility to optimize chip- and board-level reliabilities. With glass, the desired 2-level hierarchy can therefore become possible, bridging the technology gap between the high-performance needs of the market at low form factor and the challenges associated with achieving them.

#### **1.3 Research objectives**

The primary objective of this work is to model, design and demonstrate a large, 2.5D glass BGA package with 1) direct SMT-to-board; 2) minimum warpage; and 3) balanced chipand- board-level reliability. This work also aims at providing guidelines for the design of chip-level assembly processes for minimum warpage with considerations of CTE and package thickness. The metrics required to achieve the desired goals along with related

| Table 1.1: Research obj | jectives beyond prior a | art, technical challenges | and associated re- |

|-------------------------|-------------------------|---------------------------|--------------------|

| search tasks            |                         |                           |                    |

| Parameters               | Objectives                                    | Prior Art                                                             | Technical<br>Challenges                                                                                                                                                         | Research Tasks                                                                     |                                                                 |

|--------------------------|-----------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Interposer size          | Glass package:<br>~30mm x 40mm                | Si interposer:<br>30mm x 38mm                                         | <ol> <li>Balanced<br/>chip- and-<br/>board-level<br/>reliability</li> <li>Aggravated<br/>plastic strains in<br/>BGAs</li> <li>Warpage<br/>mitigation in<br/>assembly</li> </ol> | design of g<br>package                                                             | 1. Modeling and<br>design of glass<br>package for<br>chip- and- |

| Interposer<br>technology | Low- & high-<br>CTE glass: 3.3-<br>9.8 ppm/°C | Si: 2.5 ppm/°C                                                        |                                                                                                                                                                                 | board-level<br>reliability<br>2. Design and<br>demonstration of                    |                                                                 |

| Chip-level<br>assembly   | Optimized TCB<br>for min warpage              | 3D ICs with<br>TSV                                                    |                                                                                                                                                                                 | board-level<br>interconnections<br>for strain relief<br>and reliability            |                                                                 |

| Board-level<br>assembly  | Direct SMT of<br>glass package to<br>PCB      | 3-level hierarchy<br>with Si<br>interposer,<br>organic BGA<br>and PCB |                                                                                                                                                                                 | 3. Modeling and<br>design of<br>assembly<br>processes for<br>controlled<br>warpage |                                                                 |

prior art, main technical challenges and their associated research tasks are summarized in Table 1.1.

### **1.4 Technical challenges**

The gap between transistor scaling and system scaling led to System Moore as the frontier for system scaling, beyond Moore's law. Emerging high-performance computing systems have been aggressively driving advances in packaging technologies to meet their escalating performance and miniaturization needs. Three main challenges have been identified in realizing a 2.5D glass BGA package with direct SMT assembly to the board:

1. Balanced chip- and board-level reliability:

Due to the large CTE mismatch between Si and organic boards, chip- and board-level reliability are driving conflicting requirements on the mechanical properties of glass,

in particular its CTE. While lower CTEs of glass are preferred to achieve reliable chip-level interconnections at pitches below 35m, higher CTEs are critical for board-level reliability. The glass CTE, therefore, needs to be optimized to mitigate chip- and board-level reliability.

2. Aggravated plastic strains in BGAs:

The large package size of 30 mm x 40 mm and reduced thickness of the glass substrate in the 100 - 300  $\mu$ m range result in severe plastic strains in BGA interconnections, with board-level reliability identified as the most critical challenge in this package configuration. For the past 2 decades, solder alloys have been used as the primary interconnection technology for SMT assembly of packages onto printed circuit boards (PCBs). These interconnections are required to meet thermomechanical reliability requirements defined by JEDEC standards. Thermomechanical reliability is dependent on the plastic strain experienced in the solder joints. These cyclic strains are due to the mismatch in the coefficients of thermal expansion (CTE) between the package and the board and the applied temperature gradient, as given by the equation below [4]:

$$\Delta \gamma \alpha \frac{L_{DNP}(\alpha_{PWB} - \alpha_{pack}) \Delta T}{h} \tag{1.1}$$

where  $L_{DNP}$  is the distance to the neutral point (DNP), between solder joint and the center of the package; h is the solder height;  $\Delta T$  is the temperature change during each loading cycle; and  $\alpha_{pack}$  and  $\alpha_{PWB}$  are the CTEs of the package and PCB, respectively, as illustrated in Figure 1.5.

Accumulation of cyclic strains results in crack initiation and propagation in the solder joints leading to fatigue failures. The use of underfills to lessen plastic deformation in the joints, while widely adopted at chip level, is limited at board level by the need for reworkability. Innovations in materials and stress-relief mechanisms are, therefore,

Figure 1.5: Die-package-board interconnections with large LDNP and low stand-off height.

required to address this challenge with minimum system-level impact.

3. Warpage mitigation in assembly:

Warpage control is critical for board-level assembly yield and system-level reliability. Warpage is aggravated as the package size increases while its thickness is reduced, as is the trend in consumer electronics. Warpage occurs as a result of differential thermal expansion between mechanically coupled materials. While package substrates typically feature some residual warpage build through different fabrication processes with thermal steps such as dielectric curing or electroplating, chip-level assembly contributes for most of the package warpage experienced in board-assembly. In conventional reflow, the assembled package is isothermally heated and cooled with a uniform temperature established through the structure. Package warpage originates during the cool-down phase as solder solidifies and creates mechanical coupling between die and substrate, typically around 150 °C for standard lead-free SAC alloys. Consequently, package warpage induced in reflow is primarily governed by the CTE mismatch between die and glass substrate. This warpage can lead to defects in the solder joints like head-in-pillow defects, stretched solders, collapsed center balls etc. resulting in early failures (Figure 1.6). On the other hand, in emerging thermocompression bonding, heat is applied from the die side only, while the substrate is maintained at a constant stage temperature. A thermal gradient is therefore established in the package assembly giving independent control over the thermal expansion of die and substrate. Consequently, careful design of thermocompression thermal profiles

Figure 1.6: Typical defects in solder balls due to assembly-induced package warpage (Courtesy of SEM Lab, Inc.)

can enable minimum warpage when die and substrate expands by the same amount. The conditions giving minimum warpage, therefore, are defined as a function of the CTE of the package. As fundamental understanding of thermal gradients in thermocompression bonding is still relatively limited, with no existing standards for process design, warpage control in assembly remains a grand challenge that is addressed in this work.

#### 1.5 Unique approach addressing technical challenges

The technical challenges in achieving balanced chip- and- board-level reliability and mitigating package warpage as described in the above section need to be addressed to realize the desired objectives. Direct SMT assembly of a large, 2.5D glass BGA package to the board with system-level reliability is achieved through the following innovations: 1) optimization of the CTE of glass for balanced chip- and board-level reliability; 2) advanced polymer collars and doped solder alloys to further improve thermal cycling performance at board level; and 3) optimization of chip-level assembly processes for warpage mitigation with modeling and empirical correlation (Figure 1.7).

Glass has emerged as a promising solution to enable, for the first time, direct SMT assembly to the printed wiring board of a large 2.5D interposer package, as opposed to

Figure 1.7: Unique approach for balanced- chip and- board-level reliability of a large, 2.5D glass package with direct SMT-to-board.

the conventional Si interposer organic BGA PWB 3-level hierarchy. Benefitting from the unique properties of glass such as tailorable CTE, high-density wiring capability, high modules and mechanical stability, this additional organic BGA package layer can be removed. A parametric thermomechanical model of the 2.5D package was built to identify the optimal glass substrate CTE and thickness. Additionally, the glass CTE greatly impacts package warpage and, subsequently, yield of the SMT assembly and board-level reliability. Further, package warpage after chip-level assembly defines the stress build up in the interconnections as well as the flatness of the package prior to assembly on board. Excessive package warpage can result in yield loss in SMT assembly. Thus, the ideal CTE range for minimum package warpage and system-level reliability is extracted from the models to provide guidelines for design of the glass package to meet the JEDEC reliability and warpage standards.

Even though the board-level interconnection pitch is targeted to be coarser (>500  $\mu$ m) for 2.5D applications in comparison to single-chip packages, the increase in package size

and decrease in chip-level interconnection pitch, driving towards lower glass CTEs, will adversely impact the board-level fatigue life. It is thus critical to independently improve board-level reliability to meet the reliability requirements. Board-level reliability will be enhanced further by introduction of innovative strain relief mechanisms to improve the thermal cycling performances with minimum change to current processes. These strain relief mechanisms include advanced interconnection materials like doped solders and circumferential polymer collars. Georgia Tech PRC, along with its industry partner Namics Corporation Inc. have recently demonstrated the benefits of circumferential polymer collars. These filler-free epoxies with high-CTE and low modulus act as partial underfills, increasing fatigue life by up to 30%. Since solder properties are greatly dependent on their alloy composition and microstructure, they can be tuned to achieve desired properties without affecting its processability. Recently, solders doped with Mn (SACm<sup>TM</sup>) developed by Indium Corporation have enabled superior thermal cycling performance by constraining the intermetallics (IMCs) growth and stabilizing the microstructure. However, SACm<sup>™</sup> alloy is limited in its applicability only to pitches above 500  $\mu$ m since it is available only in paste form. Bhupender et al. have previously initiated single-chip glass BGA packages with SACm<sup>TM</sup> alloys as package-to-board interconnections at 400  $\mu$ m pitches. This work will focus on extending board-level reliability through the aforementioned strain relief mechanisms and performing thermal cycling studies of standard solders in comparison to the innovative novel doped SACm<sup>TM</sup> solder alloy.

Package warpage after chip-level assembly affects the board-level assembly yield. Hence, it is essential to mitigate warpage to improve yield and system-level reliability. There is little control of package warpage with the traditional mass reflow as opposed to TCB, which enables better process control. Thus, the package warpage can be minimized to obtain a zero net warpage point through optimization of the TCB conditions based on the ideal substrate CTE.

The proposed unique approach realizes the research objectives with parametric model-

ing for providing design guidelines for balanced reliability, improving board-level reliability through novel strain relief mechanisms and optimizing the TCB conditions to minimize assembly warpage at chip-level to prevent yield loss and enhance reliability.

#### **1.6 Research tasks and thesis organization**

This thesis document is divided into six main chapters. Chapter 1 introduces the transistor and system scaling trends, objectives, challenges and unique approach to address the technical challenges. Chapter 2 reviews literature of state-of-the-art technologies used to address the aforementioned challenges. The target objectives are achieved through the unique approach proposed above with associated research tasks, organized as the next 3 chapters, respectively addressing the respective technical challenges.

Chapter 3 introduces the design of a novel 2.5D glass BGA package architecture directly mounted on to the board with SMT-compatibility to obtain balanced reliability. This is achieved through finite element modeling for warpage mitigation and enhanced systemlevel reliability using a parametric approach. This work investigates the effect of glass CTE on the chip- and- board-level reliability thereby extracting the optimum CTE to pass reliability standards.

Chapter 4 evaluates the thermomechanical reliability of a large, single-chip glass BGA package with direct SMT-mount-on-board through a) finite element analysis of fatigue life at chip and board levels as well as warpage mitigation at chip level as a function of glass CTE; b) validating the models with focused reliability studies of low- and high-CTE glass package assemblies; and c) using innovative doped solder materials such as Indium's Mn-doped SACm<sup>™</sup> alloy and strain-relief mechanisms to extend board-level reliability to larger body sizes and give more design flexibility.

Chapter 5 investigates the effect of package warpage due to chip-level assembly and minimizes it through a) accurate thermomechanical finite element modeling of TCB process, focusing on the effect of the thermal profiles on warpage and long-term reliability, b)

using these models to estimate substrate warpage at package level, c) validating the models with focused experimental results, and d) mitigating assembly warpage based on these models to achieve superior system-level reliability.

Chapter 6 summarizes the overall research, aligning the results with the research objectives. It finally concludes on the inferences and suggestions for future work, towards achieving balanced reliability.

# CHAPTER 2 LITERATURE REVIEW

This chapter provides a background on the recent advancements in IC packaging leading to multi-chip packaging technologies for high-performance computing applications with fine pitch and high I/O densities. The materials and processes needed to achieve such high performance present several challenges along the way. This chapter discusses the innovative solutions proposed by researchers to address the challenges related to the mechanical design of 2.5D packaging, with warpage and reliability considerations.

#### 2.1 Recent advances in multi-chip packaging

Emerging high-performance systems drive the need for high-bandwidth between application processors and memory ICs. The bandwidth demand is predicted to increase exponentially in the next decade [2, 5]. These systems continue to shrink in size forcing the need for such bandwidths to be achieved at smaller form factors, at lower costs with least power consumption. Advances in transistor scaling and miniaturization has led to continuous improvements in electronics systems resulting in further advances in SOC packaging. SOC aims at combining multiple functions on to a single chip. However, SOC poses cost and fabrication limitations in integrating certain IC function's such as DRAMs, RF and MEMS. Further, increase in functional densities are driving the need for larger die sizes at finer pitches. To meet these demands of high bandwidth, 3D architectures with vertical staking of logic and memory dies interconnected by through-silicon-vias (TSVs) were considered. TSVs in such large logic dies requires complex co-design between logic and memory dies and results in high thermomechanical stresses and testability issues without the known-good-dies (KGDs) in the stack. The above cost, thermal and fabrication challenges associated with 3D packaging created a need to explore alternate approaches to enable high logic-to-memory bandwidth.

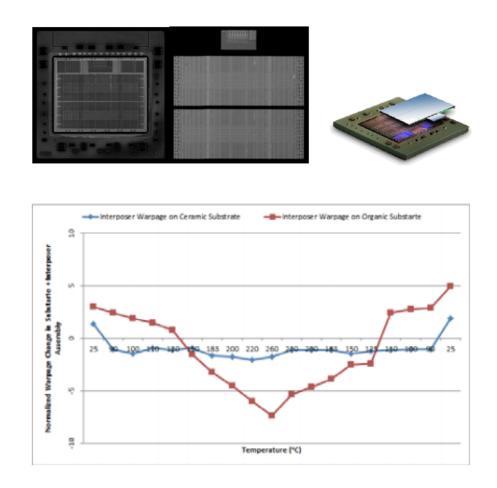

To overcome the above challenges due to TSVs in logic dies, another approach was developed involving split-dies with side-by-side interconnections between the logic and 3D memory stacked dies. This 2.5D packaging technology can integrate multi-functional chips at high I/O densities for large, thin package sizes. Logic-to-memory interconnections are achieved through ultra-fine re-distribution layers (RDL) on silicon interposers. It eliminates the need for TSVs in the logic die and employs TSVs only in the passive silicon interposer to connect to the organic BGA package. It also provides design flexibility, scalability, testability and thermal management. However, this 2.5D package present several challenges associated with the mechanical and electrical design for balancing reliability at chip- and- board-level. Xilinx has demonstrated successful 3-level hierarchical 2.5D integration with two 28 nm FPGAs and one transceiver die placed side by side on a 20 mm x 25 mm silicon interposer with minimal heat flux issues [6]. The TSV interposer is connected to a 35 mm x 35 mm large, high-CTE ceramic substrate through optimized thermocompression bonding process to mitigate the warpage (Figure 2.1) and the dies are stacked horizontally through traditional mass reflow process. The importance of assembly process conditions to mitigate warpage and the reliability challenges associated with high-CTE ceramic substrates were evaluated.

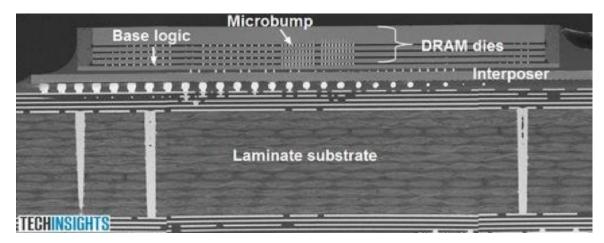

SK Hynix's HBM as shown in Figure 2.2 also illustrate a 3-level hierarchy with four HBM stacks and a GPU assembled on a 30 mm x 38 mm Si interposer [7]. The additional organic package layer in both of the above systems adds to the system cost apart from inducing a large CTE mismatch at package level. This CTE mismatch leads to warpage and yield issues adversely impacting the reliability of the system.

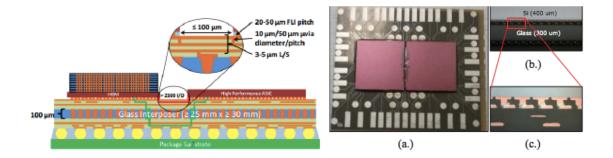

Glass as a substrate platform is extensively being researched due to its tunable CTE, dimensional stability and high-density wiring capabilities. Using glass, a 2-level hierarchy can be built to overcome the challenges of the additional package layer. Georgia Tech's PRC successfully demonstrated a 2-level 2.5D glass BGA package that can be directly

Figure 2.1: 3-level hierarchical 2.5D integration with two 28 nm FPGAs and one transceiver die placed side by side on a 20 mm x 25 mm silicon interposer assembled on high-CTE ceramic substrate (Xilinx).

Figure 2.2: High-bandwidth memory stacks with a center GPU on a silicon interposer assembled on an organic laminate (SK Hynix).

SMT-mounted on the board (Figure 2.3).

Figure 2.3: 2.5D FLI assembly at 100  $\mu$ m die-to-die spacing (a.) top view of 25 mm x 30 mm six-metal-layer glass interposer (b) cross-section (c) FLI detailed cross-section.

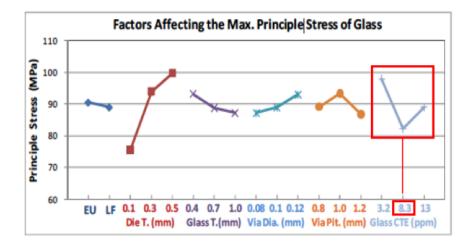

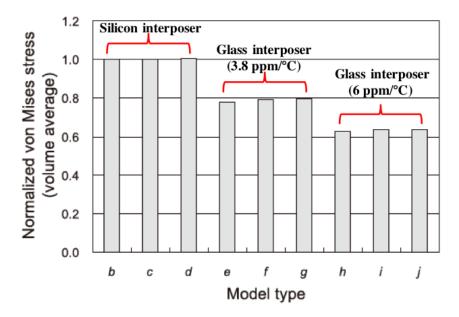

Glass with low- and- high-CTE are readily available today in large panel sizes or roll-toroll form. However, in order to balance chip- and- board-level reliability as well as mitigate warpage, the glass CTE needs to be tuned. Low-CTE glass creates a large CTE mismatch at board-level, thus degrading its reliability. On the other hand, high-CTE glass induces high warpage at chip-level, subsequently resulting in yield loss and chip-level reliability concerns. TSMC performed a finite element analysis of a glass interposer for a highperformance flip-chip BGA (HP-fcBGA), varying the glass CTE to obtain a middle CTE for least stress build-up [8]. They evaluated the effect of glass CTE on different stresses experienced by the BGAs. Based on their analysis, a middle CTE of 8.3 ppm/K generated least stress because of the CTE mismatch between the glass and die and PCB were close, which relieved the thermomechanical stresses accordingly. Further, IBM recognized the importance of minimizing stress based on the effect of interposer material, CTE, size for mechanical design of the package [9]. Similar to TSMC, IBM also conducted a finite element analysis with a parametric approach, evaluating the glass substrate CTE on warpage and the Von Mises stress at the solder joint. Glass CTE of 6 ppm/K was found to have least Z-displacement and the von Mises stress reduced by 18% when the CTE was increased from 3.8 ppm/K to 6 ppm/K (Figure 2.4 and Figure 2.5).

The packaging industry has been innovating several materials, fabrication and intercon-

Figure 2.4: Parametric effects on the maximum principle stress of glass.

Figure 2.5: Von Mises stress in volume average at the corner solder ball.

nection techniques to address the warpage and reliability challenges held by 2.5D packaging that will be discussed in detail in the following sections.

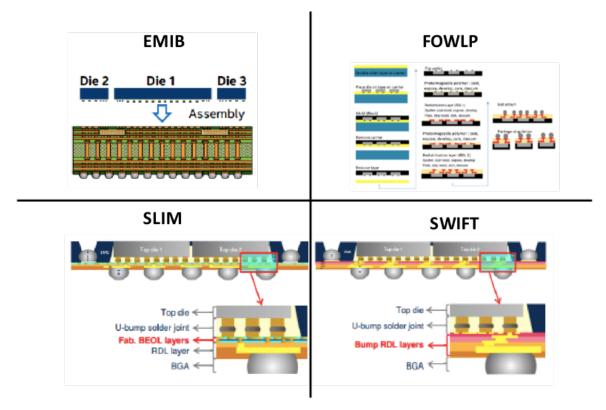

In addition to the 2.5D technology, researchers have also been looking at other approaches for high-density interconnections between heterogenous dies on a single package including (a) Intel's Embedded Multi-die Interconnect Bridge (EMIB) [10], (b) fan-out wafer-level packaging platform (FOWLP) [11], (c) Amkor's Silicon-Less Integrated Module (SLIM) [12] and (d) Silicon Wafer Integrated Fan-out Technology (SWIFT) [13]. These different technologies are as shown in Figure 2.6.

Figure 2.6: Intel's EMIB assembly (top left), Process flow to achieve FOWLP - Courtesy of Beth Keser (top right), Amkor Technology Inc's SLIM (bottom left) and SWIFT (bottom right).

#### 2.2 Material developments in interconnections for board-level reliability

In emerging high-performance systems, the split-die trend is driving high-density interconnections at sub-5  $\mu$ m pitch at large body sizes. Thus, improving board-level reliability without adversely impacting chip-level reliability has become a major concern. Additionally, due to reduction in pitch at board-level to below 400  $\mu$ m, higher strains and warpage is experienced in BGAs, further degrading reliability. Advances in materials development used to enhance board-level reliability are discussed in this section.

#### 2.2.1 Advances in surface finishes and doped solders

Standard solders used in BGAs are called SAC alloys that comprise of tin, silver and copper that are used to form metallurgical bonds between the copper pad on the package and the board. These copper pads are coated with a thin layer of surface finish in order to provide least surface tension for the solder to wet the pads effectively. The surface finish also takes part in intermetallics (IMCs) formation and forms the interface between the pad and bulk solder. After reflow, the solder melts and partially dissolves in the surface finish, forming IMCs due to diffusion phenomena. These IMCs are brittle in nature and their composition, thickness and microstructure greatly affect the strength and reliability of the joint. Pad surface finishes play an important role in determining the reliability of the solder joint. Traditional surface finishes include hot air solder leveling (HASL), organic solderability preservative (OSP), immersion Sn (ImSn) and immersion Ag (ImAg) [14]. Due to their limitations like non-uniformity, cost, solderability, shelf-life, surface oxidation, etc., advanced in surface finishes have been made. The most popular amongst these are electroless nickel immersion gold (ENIG) and electroless nickel electroless palladium gold (ENEPIG). Literature studies have been made on the effect of ENIG and ENEPIG on reliability based on their IMC formation. Even though they address the challenges posed by traditional surface finishes, they impede pitch scalability with sub-10  $\mu$ m gaps between traces. Another novel surface finish technology developed by Atotech GmBH known as electroless Pd autocatalytic Au (EPAG) enables high-density wiring at finer pitches. The thickness of IMC depends on the reflow time and number of reflow cycles [15]. The IMCs grow further during thermal ageing and the presence of these brittle IMCs act as crack initiation points leading to interfacial failure [16]. Control of IMC growth and consequent control of microstructure is critical in enhancing board-level reliability.

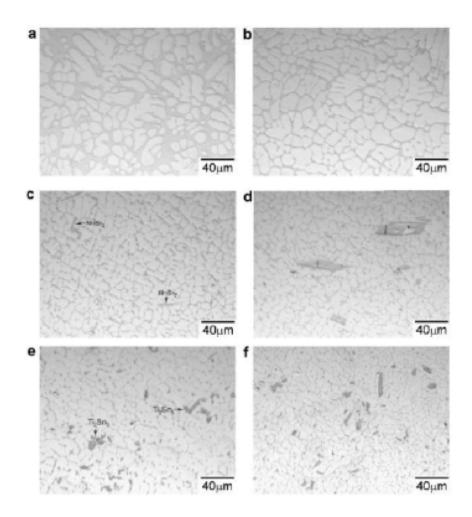

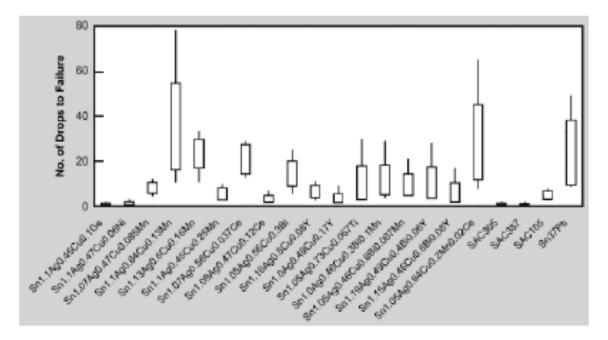

Apart from advances in surface finish, development in solders by refining their microstructure have also been researched. As mentioned in Chapter 1, with current standard solders, higher drop performances can be achieved only at the cost of thermomechanical fatigue life. Doping these standard SAC alloys with Nickel (Ni), Manganese (Mn), Cerium (Ce), Bismuth (Bi), Titanium (Ti), Germanium (Ge) and Yttrium (Y) have been studied [17]. Due to their low solubility and low melting points, they refine the solder microstructure upon reflow. During solidification, they make the grains finer and limit the growth of IMCs, improving the tensile and creep resistance. Among the various dopants, it was found that Mn and Ti doped SAC alloy reduced the undercooling required for the initiation of crystal nucleation and also hindered the formation of detrimental intermetallics like Ag3Sn and suppressed the thickness of Cu6Sn5. Microstructures of SAC305, SAC105 and SAC105 doped with different compositions of Mn and Ti are observed in Figure 2.7 [18]. With different variations of dopants, Liu and Lee (Indium Corporation) found that SAC105 + 0.13% Mn displayed the best composition for balanced thermal cycling and drop test reliability.

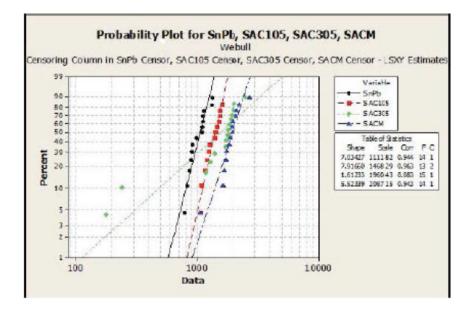

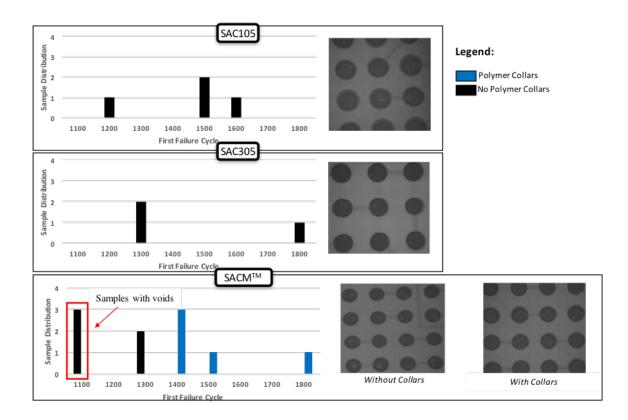

The drop test and thermal cycling results are shown in Figure 2.8 and Figure 2.9 respectively. Indium corporation commercialized SACm<sup>TM</sup> based on their experimental findings on the Mn dopant as an alternative to SAC105, bridging the gap between drop and thermal fatigue performance [19]. The superior thermal cycling reliability of SACm<sup>TM</sup> was attributed to the refinement of microstructure, suppression of IMC growth and improved joint strength. Currently, SACm<sup>TM</sup> is only available in paste form which limits its applicability to pitches above 500  $\mu$ m.

#### 2.2.2 Advances in underfill materials at board-level

Underfills are generally used at chip-level to enhance the reliability by absorbing and redistributing the stresses away from the solder joints. Reworkability is an important factor in board-level assembly. However, underfills prevent reworkability and are not widely used for board-level interconnections. Thermally reworkable underfills are being developed to improve reliability to the flip-chip package while allowing the chip to be easily removed at elevated temperatures. Wong et al used two approaches being development of thermally-

Figure 2.7: Microstructures of (a) SAC305, (b) SAC105, (c) SAC105 + 0.15Mn, (d) SAC105 + 0.5Mn, (e) SAC105 + 0.15Ti and (f) SAC105 + 0.5Ti.

cleavable-block-containing epoxies and additive-modified epoxies. They observed that by combining the two approaches, both die removal and underfill removal were achieved [20]. Peng et al studied the effects of snap cure underfill and reworkable underfill. They showed that reworked underfill had least percentage of failures when compared to snap cure and no underfill packages as shown in Figure 2.10 [21]. However, reworkable underfill takes longer to cure and causes reliability issues. Thus, their reliability concerns need to be addressed by reducing curing time, increasing molecular weight and extending their application at wafer-level.

Figure 2.8: Drop test reliability of SAC solder with dopants.

Figure 2.9: Thermal cycling results for SnPb, SAC105, SAC305 and SACm<sup>™</sup>.

#### 2.2.3 Compliant interconnections

Standard solders and interconnection techniques are reaching their limits to achieve advanced computing and high-performance application needs. A variety of compliant interconnections have been investigated to mitigate the stresses induced by such high-functional

Figure 2.10: Percent failures for different underfill types.

requirements. Compliant solder balls have been reported consisting of a polymer core instead of the bulk metal to reduce the effective elastic modulus of the joint (Figure 2.11). This also increases the CTE and redistributes the stress uniformly. A 2x - 3x improvement in thermal cycling was observed as compared to SAC305 [22]. The complex fabrication and cost limitations prevent this approach from being adopted commercially.

Figure 2.11: Cross-section of polymer core solder ball after balling (left) and assembly (right).

Another compliant interconnection technique developed by [23] involves differential displacement that mechanically decouples the die and substrate. It accommodates the CTE mismatch between the die and substrate during thermal cycling by easily deforming in

the x, y and z directions to provide stress relief in the interconnections as shown in the Figure 2.12.

Figure 2.12: Multi-path complaint structures - SEM image (top), simulations (bottom).

Other metal-based compliant interconnections have also been reported including the micro-spring [24], stress-engineered [25] interconnections, double-ball wafer-level pack-aging (WLP) [26], bed of nails [27] etc.

Previous work on board-level compliant interconnections carried out at Georgia Tech's Packaging Research Center includes compliant micro-wire arrays and circumferential polymer collars. Copper micro-wire arrays eliminated the need for board-level underfill. They were pre-fabricated in ultra-thin carriers and then assembled as a stress-relief interlayer between the package and board [28] (Figure 2.13).

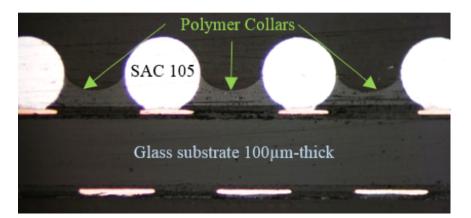

Addition of low-modulus dielectric build up layers on either side of the glass substrate further enhance the thermomechanical reliability by increasing the effective CTE of the substrate, reducing the CTE mismatch to the board. Circumferential polymer collars were used as to relieve stress by spin-coating on to the BGAs after balling (Figure 2.14). They act as partial underfills by redistributing the stress while maintaining reworkability [29].

Figure 2.13: Cross section of MWA interconnections.

Figure 2.14: Cross-section of an 18.4 mm interposer with uniform collar formation achieved after spin-coating profile optimization.

#### 2.3 Warpage mitigation in assembly

The trend to meet low cost, high density, speed and bandwidth at low power for emerging smart mobile and high performance systems is driving package sizes towards large, ultrathin architectures. High-CTE organic packages are currently being used as the substrate core. Traditional organic laminates such as FR-4 or BT, with build-up epoxy dielectric based re-distribution layers (RDL) are the main substrates used for fine pitch BGA packages [30, 31]. But the drawbacks associated with it are limiting its use for high performance needs. The demand for thinner packages for ultra-thin substrates leads to substrate warpage before and after assembly. A major substrate parameter affecting warpage of the package is the substrate coefficient of thermal expansion (CTE). This CTE mismatch between the die and substrate causes warpage. High-CTE organic packages are often thick with a core

thickness ranging from 500  $\mu$ m to 1 mm and are not sufficiently rigid to meet the JEDEC warpage standards. Therefore, it can be assumed that by lowering the CTE mismatch, package warpage can be reduced. Low-CTE silicon core substrates have become increasingly popular due to their high elastic modulus, high stiffness at high temperatures and their ability to be manufactured at high-wiring densities. They are shown to display good performance and high interconnection reliability to achieve excellent mounting capability of semiconductor devices [32]. It has been shown that low CTE core substrates have lower warpage than high CTE core substrates [33]. However, these low CTE substrates transfer the CTE mismatch to board inducing large stresses at the BGAs, interfacial delamination and adversely affecting the solder joint reliability. To overcome this issue, interposers are being developed. For interposers with ultra-high I/O density and 2  $\mu$ m lines and spaces RDL, silicon wafers fabricated in the back end of line (BEOL) have been demonstrated [34, 35, 36]. These interposers are then mounted on to an organic substrate and connected to the board. This involves an additional assembly step and aggravates warpage, making it critical to optimize process conditions to minimize assembly warpage. Mass reflow is the most common process used in assembly at chip level. The other process that are being developed is the thermocompression bonding (TCB) process. Mass reflow technology cannot be controlled as efficiently as TCB, since the latter can be optimized on the basis of various parameters like force, ramp rate, temperature profile (heating and cooling rates) [37]. Mass reflow is generally used with capillary underfill (CUF) while TCB can be used with CUF or pre-applied underfill materials. Satomi et al. have demonstrated that the warpage induced by traditional mass reflow is higher than that through an optimized TCB process for an organic substrate package as seen in Figure 2.15 [38].

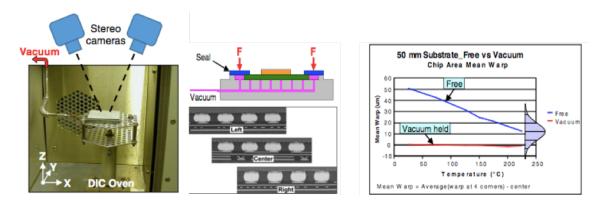

Researchers have also studied ways to minimize warpage during the reflow process. IBM has successfully demonstrated warpage mitigation in mass reflow through the use of a vacuum fixture with a carrier on which the package is placed. The carrier has holes as depicted in Figure 2.16 through which the vacuum permeates to minimize concave warpage.

| Temperature | 30°C | 150°C | 220*C | 260°C |

|-------------|------|-------|-------|-------|

| ТСВ         |      |       |       |       |

| reflow      |      |       |       |       |

Figure 2.15: Comparison of warpage during thermocompression bonding and mass reflow.

Atmospheric pressure is applied from the top that pushes down the top surface uniformly to prevent convex warpage. Cross sections in Figure 2.16 show the uniformity in the C4 bump height throughout the package with minimum warpage. However, as we move towards 2.5D packages, the chip-level pitches reduce drastically, making it harder to assemble via mass reflow process.

Figure 2.16: Vacuum fixture with carrier during mass reflow (left), uniform ball height cross-section (middle), warpage with and without vacuum fixture (right).

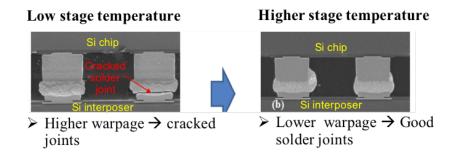

Thermocompression bonding process is typically used at such fine pitches. Even TCB is shown to mitigate warpage better as compared to reflow, it is still extremely critical to optimize the conditions based on the package type and pitch to achieve yield and system-level reliability. Liang Wang et al. have investigated the effect of TCB conditions on warpage [39] and demonstrated that the stage temperature and subsequent peak temperature has a strong effect on assembly-induced warpage. For a 2.5D package with silicon interposer, it was shown that a lower stage temperature resulted in higher warpage and cracked solder joints (Figure 2.17). On the other hand, higher stage temperatures warped lesser than 12  $\mu$ m and formed good solder joints. Precise and dynamic control of thermal gradient in TCB is critical in achieving reliable solder joints.

Figure 2.17: Interposer warpage as a function of TCB stage temperature.