# Methods for Extending High-Performance Automated Test Equipment (ATE) using Multi-Gigahertz FPGA Technologies

A Dissertation Presented to The Academic Faculty

by

Ashraf M. Majid

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology May 2011

Copyright © Ashraf M. Majid 2011

# Methods for Extending High-Performance Automated Test Equipment (ATE) using Multi-Gigahertz FPGA Technologies

Approved by:

Dr. David C. Keezer, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Abhijit Chatterjee School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Linda S. Milor School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. James O. Hamblen School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Shijie Deng School of Industrial and Systems Engineering *Georgia Institute of Technology*

Date Approved: March 29th, 2011

As no man is born an artist, so no man is born an angler. -Izaak Walton – The Compleat Angler To my mother, Shahida Majid, and my family, for their endless love, encouragement and support, without which, this work would not have been possible.

## ACKNOWLEDGEMENTS

My career at Georgia Tech started as I first stepped through the halls of this great institution in 1998. As an eager undergraduate student during the ramp-up to the dot-com era, my only plan was to graduate and enter the high-tech industry as quickly as possible. I had no clue that this institution had a lot more planned for me over the next 13 years. Fortunately, along the way, I was able to meet wonderful people whose guidance, support, and above all friendship have enabled this achievement.

First of all, I would like to express my deepest gratitude to my advisor Dr. David Keeezer for all his support throughout my graduate career at Georgia Tech. If it were not for his willingness to take a gamble on a young student, with no experience in digital testing, this research would not have been possible. His guidance and wisdom have proven to be invaluable in the development of my career. Also, his encouragement and patience throughout the years have made this entire experience joyful. I would also like to give a special thanks to my lab mate Carl Grey who has been instrumental in much of our work and who has always been willing to provide his technical expertise.

I would like to thank both my reading committee members Dr. Abhijeet Chatterjee and Dr. Linda Milor, who have been highly supportive of this research and available for guidance and advice. Dr. Chatterjee has helped our research group with numerous publications and industry liaisons throughout the years and deserves a special acknowledgement. I would like to express my gratitude to Dr. James Hamblen for serving on my proposal and dissertation defense committees. Furthermore, I would like to thank Dr. Shije Deng for his assistance and guidance during my time in the quantitative finance program, and also for serving on my dissertation defense committee.

I would also like to acknowledge of my undergraduate professors at Georgia Tech. I was fortunate enough to take courses throughout various schools at Georgia Tech and able to meet many wonderful professors, each of whom contributed to my development. I would especially like to thank Dr. David Anderson who introduced me to this intriguing world of research. Allowing me to join his Digital Signal Processing lab as an undergraduate, he helped sow the seeds for my desire of research and further studies.

Over the last three years, I have been working full time at SunTrust Bank's capital markets division while finishing this research. This would not have been possible without the support and patience of my entire team at SunTrust. I would especially like to thank my manager Al Kolesar, who has proven to be a great mentor over the years and pivotal in developing my newfound career in investment banking.

Finally, I am eternally indebted to my family, without whose support, this work would have been impossible, if not meaningless. This entire journey was not only made bearable, but pleasurable and fun by the never ending love and support of my mother and sister. My father's own academic achievements, and hard work ethic, inspired and drove me to endeavors I attempt today. Their understanding and patience has been vital in this entire process. Furthermore, this section would not be complete without acknowledging the wonderful lifelong friendships I have developed during my tenure at Georgia Tech and in Atlanta. These friendships have proven to be an essential support structure providing the encouragement required for completing this research. I have come to value all these relationships very very dearly.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                           | V    |

|------------------------------------------------------------|------|

| LIST OF TABLES                                             | X    |

| LIST OF FIGURES                                            | xi   |

| LIST OF SYMBOLS AND ABBREVIATIONS                          | xvii |

| SUMMARY                                                    | xxii |

| CHAPTER 1: INTRODUCTION                                    |      |

| CHAPTER 2: BACKGROUND AND HISTORY                          |      |

| 2.1 TECHNOLOGY ROADMAPS                                    |      |

| 2.1 TECHNOLOGY KOADMAPS<br>2.2 AUTOMATIC TEST EQUIPMENT    |      |

| 2.2 AUTOMATIC TEST EQUIPMENT                               |      |

| 2.3 Design For restrability (DFT)                          |      |

| 2.3.1 Additional Wodule based DT1                          |      |

| 2.3.2 Enfocaded Would Access based DTT                     |      |

|                                                            |      |

| CHAPTER 3: MODULAR EXTENSION OF ATE TO MULTI-GHZ SPEEDS    | 22   |

| 3.1 HIGH SPEED SIGNAL GENERATION                           | 23   |

| 3.2 LOOPBACK TESTING                                       | 29   |

| 3.3 TIMING SKEW ADJUSTMENT                                 | 32   |

| 3.4 JITTER MANIPULATION                                    | 35   |

| 3.5 Switching                                              | 39   |

| CHAPTER 4: STAND-ALONE MINIATURE TESTER                    | 44   |

| 4.1 WAFER-LEVEL TESTING                                    | 45   |

| 4.2 WAFER-LEVEL PROBING                                    | 47   |

| 4.2.1 Interposer                                           | 49   |

| 4.2.2 Bare-die test Socket                                 | 52   |

| 4.3 MINIATURE TESTER                                       | 55   |

| 4.3.1 Digital Logic Core (DLC)                             | 57   |

| 4.3.2 High Speed Signal Generation                         | 59   |

| 4.3.3 High Speed Signal Sampling                           |      |

| 4.4 EXPERIMENTAL DEMONSTRATION OF THE MINI-TESTER          |      |

| 4.5 EXPERIMENTAL DEMONSTRATION OF THE BARE-DIE TEST SYSTEM | 65   |

| CHAPTER 5: ENHANCED TEST MODULE USING MULTI-GIGAHERTZ FPG  | βA   |

| TECHNOLOGIES                                               | 69   |

| 5.1 Concept                                                | 70   |

| 5.2 Methodology                                            |      |

| 5.3 Test Module Design                                     | 74   |

| 5.3.1 Core Logic Block                                     | 75   |

| 5.3.2 Application Specific Block                           | 78   |

| 5.4 APPLICATIONS                                               | 79    |

|----------------------------------------------------------------|-------|

| 5.4.1 High Speed Signal Multiplexing                           | 80    |

| 5.4.2 Loopback Testing                                         |       |

| 5.4.3 Amplitude/Voltage Adjustment                             | 84    |

| 5.4.4 Timing Skew Adjustment                                   | 86    |

| 5.4.5 Jitter Injection                                         | 90    |

| 5.4.6 Low Speed/Parametric/ATE Testing                         | 91    |

| CHAPTER 6: FPGA DESIGN AND IMPLEMENTATION                      | 93    |

| 6.1 FGPA Selection                                             | 94    |

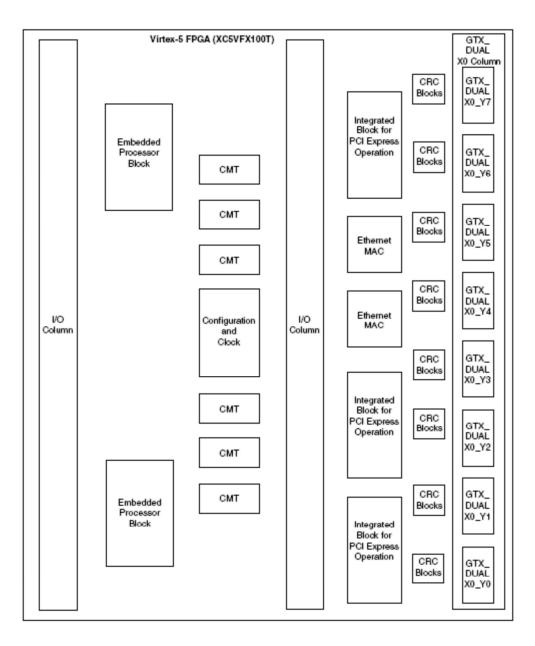

| 6.1.1 Xilinx Virtex 5                                          |       |

| 6.1.1.1 RocketIO GTX Transceivers                              | 98    |

| 6.2 FPGA IMPLEMENTATION                                        | 104   |

| 6.2.1 Communication                                            | 105   |

| 6.2.2 FPGA Firmware                                            | 110   |

| 6.2.3 Software Client                                          | 116   |

| CHAPTER 7: PHYSICAL DESIGN AND BOARD LAYOUT                    | 119   |

| 7.1 Physical Design Considerations                             | 119   |

| 7.2 TEST MODULE PHYSICAL LAYOUT                                |       |

| <b>CHAPTER 8:</b> TEST MODULE PERFORMANCE AND CHARACTERIZATION | N 135 |

| 8.1 CORE LOGIC BLOCK – CHARACTERIZATION                        | 135   |

| 8.2 HIGH-SPEED SIGNAL MULTIPLEXING –CHARACTERIZATION           |       |

| 8.3 LOOPBACK PATH – CHARACTERIZATION                           |       |

| 8.4 AMPLITUDE ADJUSTMENT – CHARACTERIZATION                    |       |

| 8.5 TIMING/SKEW ADJUSTMENT – CHARACTERIZATION                  |       |

| 8.6 JITTER INJECTION – CHARACTERIZATION                        |       |

| 8.7 LOW-SPEED/PARAMETRIC TESTING - CHARACTERIZATION            |       |

| 8.8 RESULTS SUMMARY                                            |       |

| CHAPTER 9: CONCLUSIONS                                         |       |

| 9.1 SUMMARY                                                    | 164   |

| 9.2 CONTRIBUTIONS                                              |       |

| 9.2 CONTRIBUTIONS                                              |       |

| 9.2.2 Communication and control architecture for test modules  |       |

| 9.2.3 High-speed signal multiplexing                           |       |

| 9.2.4 High-speed Loopback path                                 |       |

| 9.2.5 Jitter Injection                                         |       |

| 9.2.6 Low-speed/parametric testing path                        |       |

| 9.2.7 Physical design guidelines for high-speed test module    |       |

| 9.3 Conclusions                                                |       |

| 9.4 FUTURE WORK                                                |       |

| APPENDIX A: FPGA Firmware                                      |       |

| APPENDIX B: Communication Firmware and Software                | 212   |

| APPENDIX C: Physical Board Design and Layout                   | 246   |

| REFEREN | ICES |

|---------|------|

| VITA    |      |

## LIST OF TABLES

| Table 2.1 Test Cost Drivers [1]                          | 9  |

|----------------------------------------------------------|----|

| Table 2.2 ITRS Test and Test Technology Roadmap 2005 [2] | 9  |

| Table 6.1 Virtex-5 Family supported I/O standards [100]  | 97 |

## LIST OF FIGURES

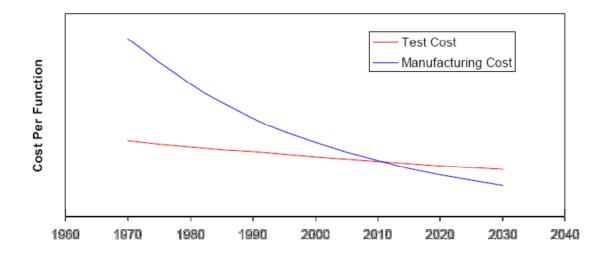

| Figure 2.1 Semiconductor test cost vs. manufacturing cost [17].                                          | 8        |

|----------------------------------------------------------------------------------------------------------|----------|

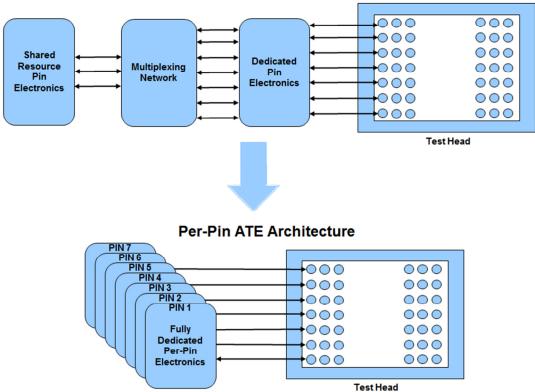

| Figure 2.2 ATE Architecture Change                                                                       | 13       |

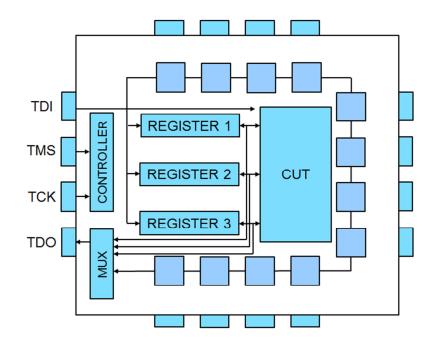

| Figure 2.3 Serial Scan Architecture                                                                      | 18       |

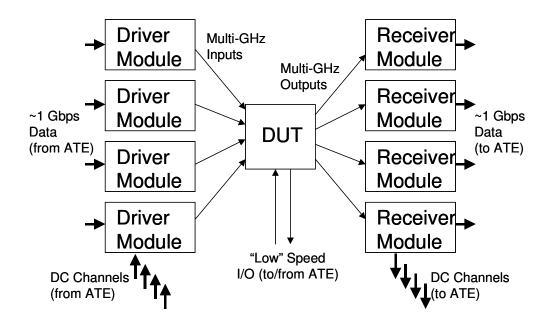

| Figure 3.1. Top-level system view of modular extension approach to ATE[44]                               | 25       |

| Figure 3.2 Typical application test configuration [44].                                                  | 26       |

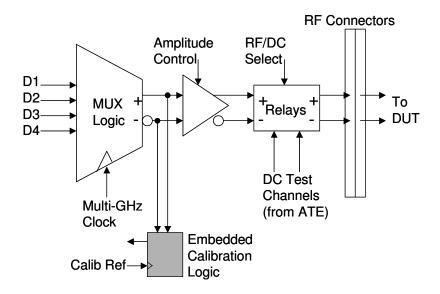

| Figure 3.3. Multi-GHz driver module logic [44].                                                          | 27       |

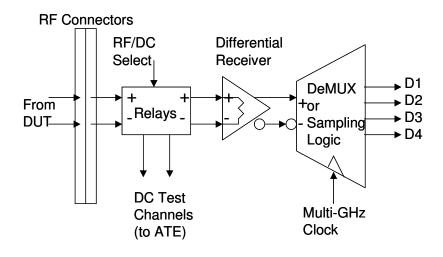

| Figure 3.4. Multi-GHz receiver module logic [44].                                                        | 28       |

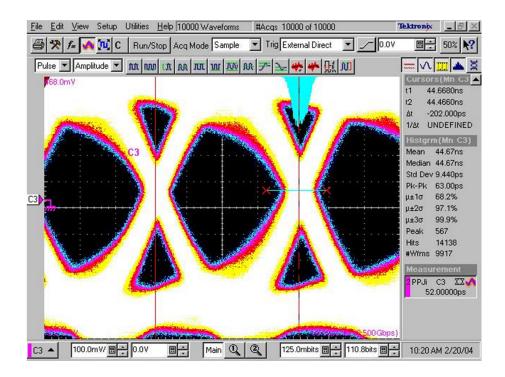

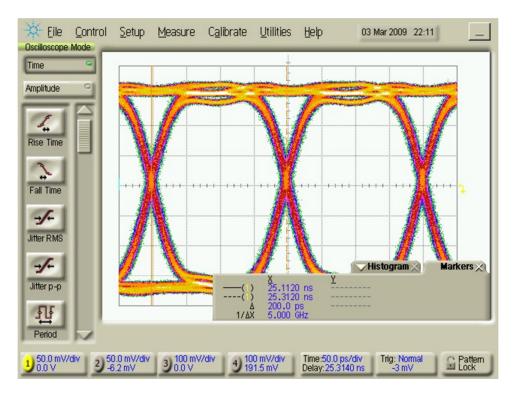

| Figure 3.5. High-speed data signal from driver module at 5.0Gbps [44].                                   | 28       |

| Figure 3.6. Overview of minimal loopback testing [52]                                                    | 30       |

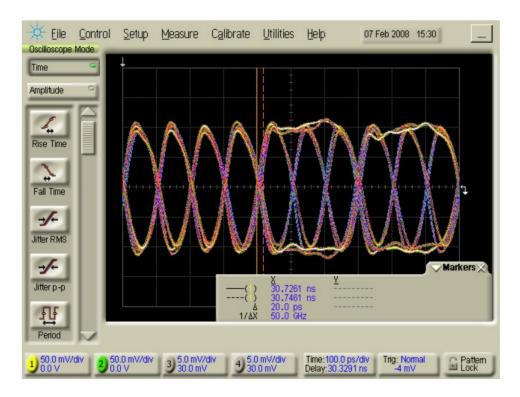

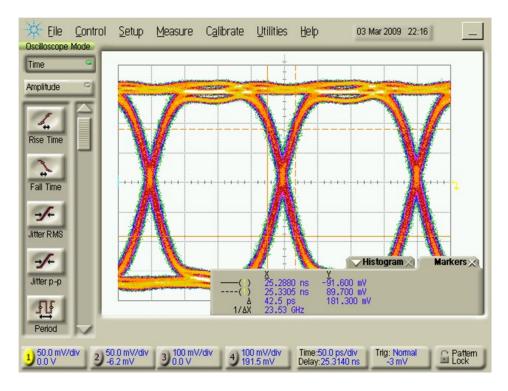

| Figure 3.7 Active loopback path measured at 10.0Gbps [53]                                                | 31       |

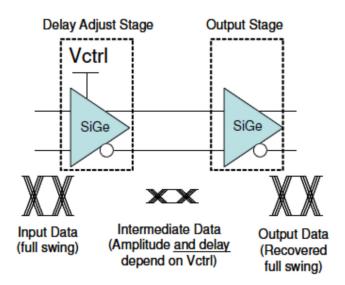

| Figure 3.8 One stage variable delay circuit [59]                                                         | 34       |

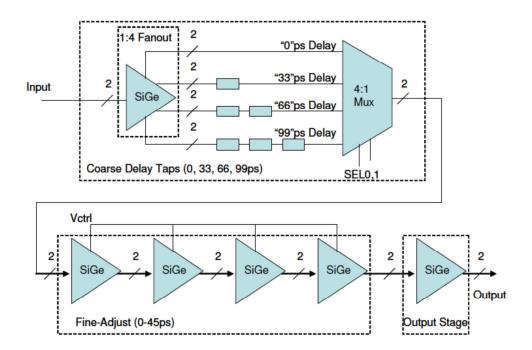

| Figure 3.9 4-stage fine delay circuit with finite delay circuit [59]                                     | 34       |

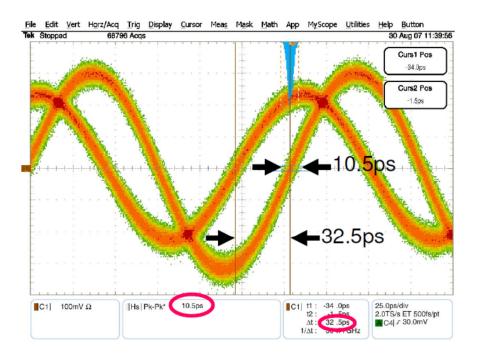

| Figure 3.10 Output from delay circuit at 6.0 GHz showing a delay of 32.5ps [59]                          | 35       |

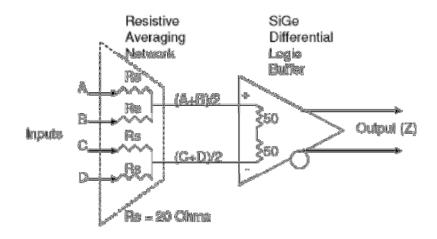

| Figure 3.11. Simple jitter reduction circuit [61]                                                        | 36       |

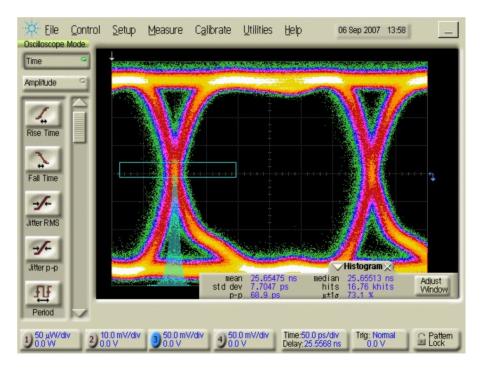

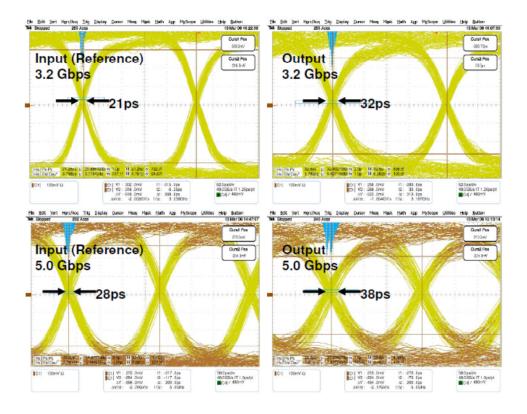

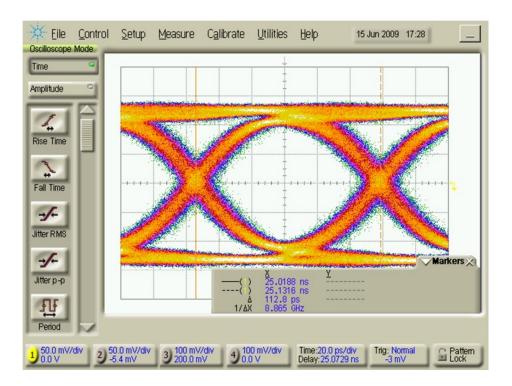

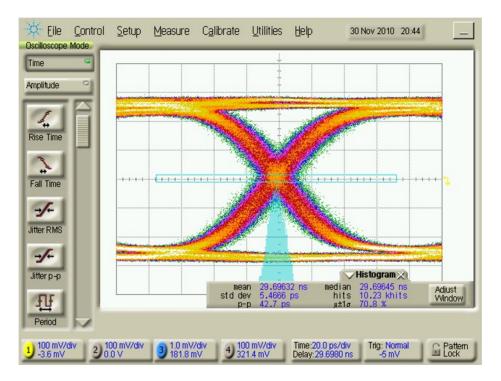

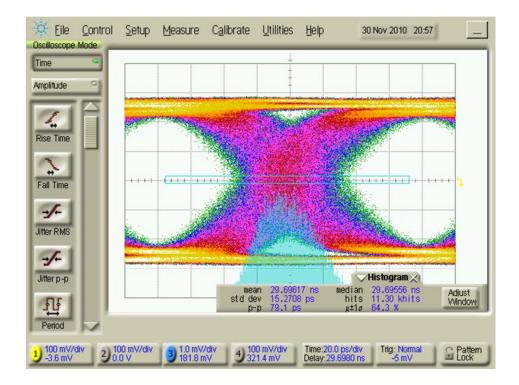

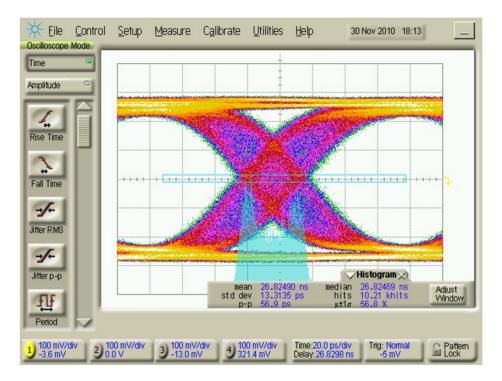

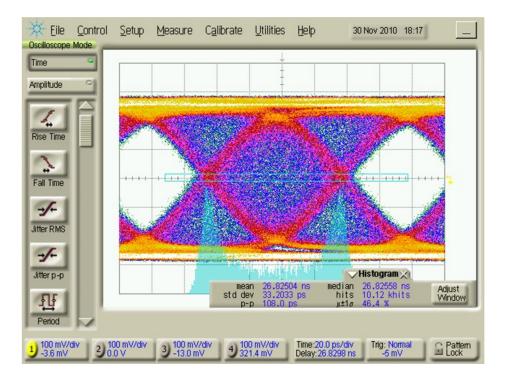

| Figure 3.12 Input signal into jitter injection circuit at 3.2Gbps with 29ps of total jitter [59]         | 38       |

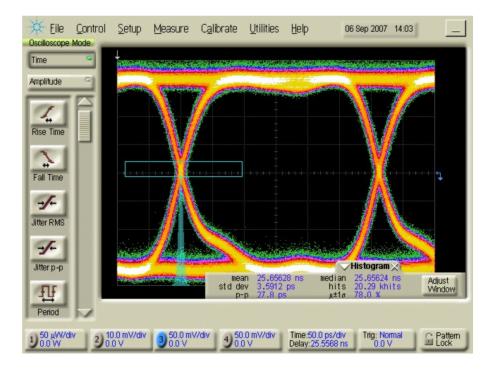

| Figure 3.13 Output signal from jitter injection circuit at 3.2Gbps with 69ps of total jitte [59]         | er<br>38 |

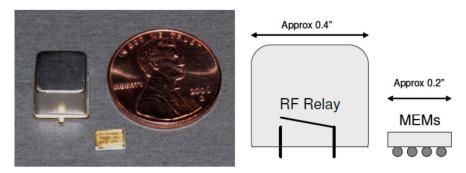

| Figure 3.14 Mechanical relay performance [52]                                                            | 41       |

| Figure 3.15 Size comparison of mechanical relay and MEMS relay [52]                                      | 42       |

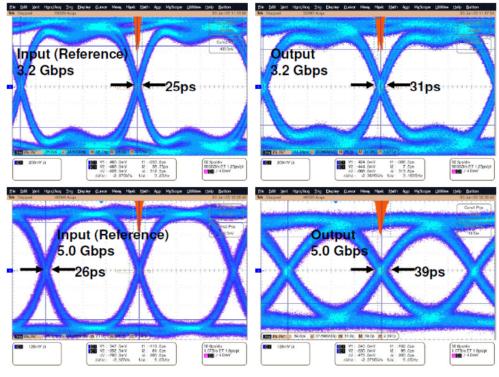

| Figure 3.16 MEMS switch performance [52]                                                                 | 43       |

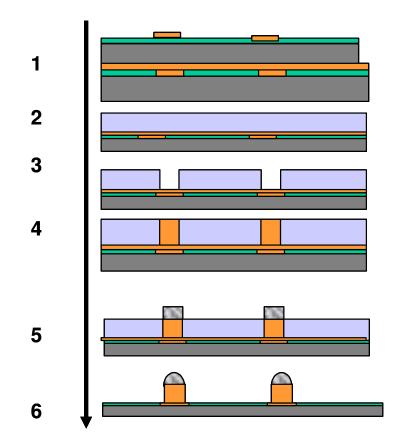

| Figure 4.1 Process flow of bed of nails wafer level interconnects by photo resist method                 | d<br>49  |

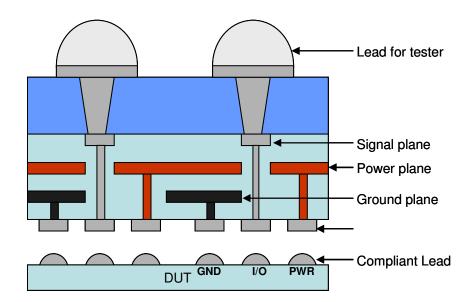

| Figure 4.2 Interposer incorporating vertically connected signal traces created using through wafer vias. | 49<br>50 |

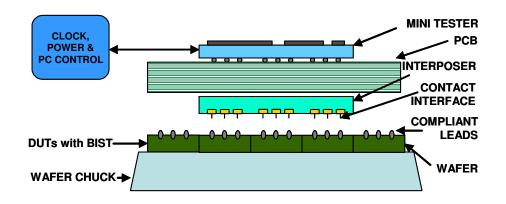

| Figure 4.3 Testing of wafer-level packaged (WLP) devices using a "miniature tester" and a high-density interposer.                | nd<br>51 |

|-----------------------------------------------------------------------------------------------------------------------------------|----------|

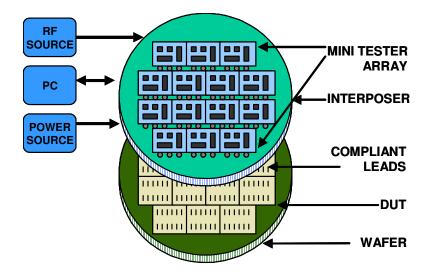

| Figure 4.4 Parallel high-speed wafer probing using multiple miniature testers.                                                    | 52       |

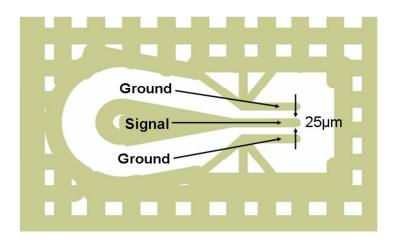

| Figure 4.5 Layout of elastomer coplanar contact probe.                                                                            | 53       |

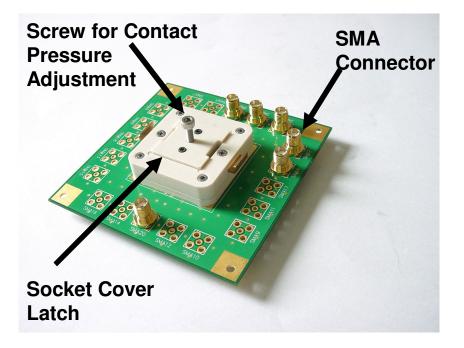

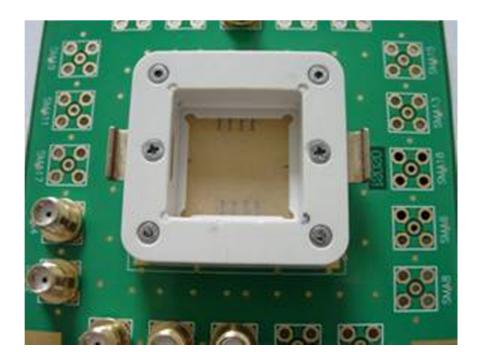

| Figure 4.6. Prototype Test Socket                                                                                                 | 54       |

| Figure 4.7. Elastomer Coplanar Contact probes inside test socket.                                                                 | 54       |

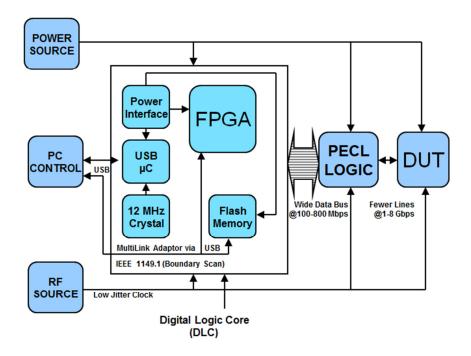

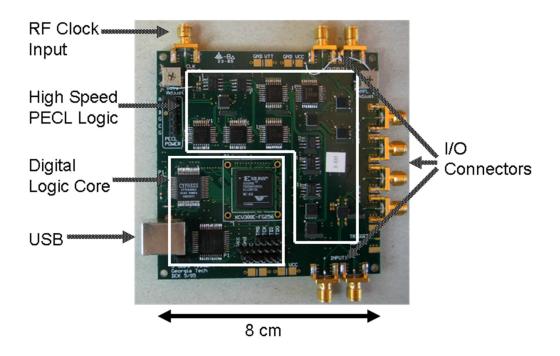

| Figure 4.8. Miniature tester with high-speed PECL for testing multi-GHz DUTs (DLC enlarged).                                      | 58       |

| Figure 4.9. Prototype miniature tester with embedded DLC.                                                                         | 58       |

| Figure 4.10. PECL logic used in mini-tester for high speed signal generation.                                                     | 60       |

| Figure 4.11. Logic used in mini-tester for high speed signal sampling.                                                            | 61       |

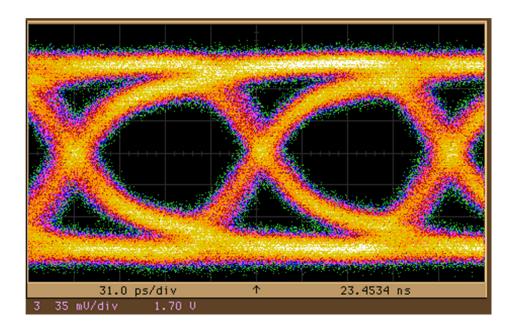

| Figure 4.12. 5.0Gbps eye diagram produced by mini-tester.                                                                         | 62       |

| Figure 4.13. 6.4Gbps eye diagram produced by mini-tester.                                                                         | 62       |

| Figure 4.14. 8.0Gbps eye diagram produced by mini-tester.                                                                         | 63       |

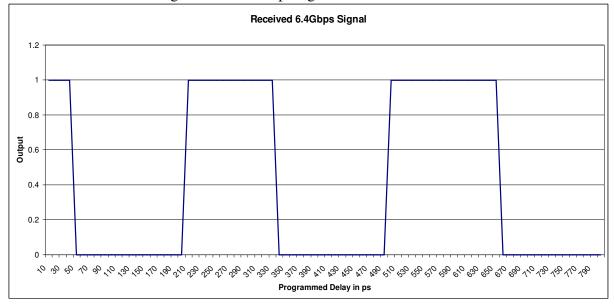

| Figure 4.15. 6.4Gbps signal to be received.                                                                                       | 64       |

| Figure 4.16. Bit pattern plotted with sampled data.                                                                               | 64       |

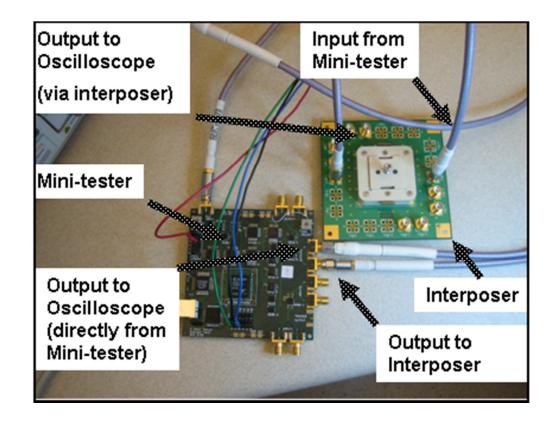

| Figure 4.17. Lab setup showing high-speed signal from mini-tester prototype passing through interposer prototype to oscilloscope. | 65       |

| Figure 4.18. 5.0Gbps eye diagrams. Bottom signal directly from mini-tester, top signal via interposer.                            | 66       |

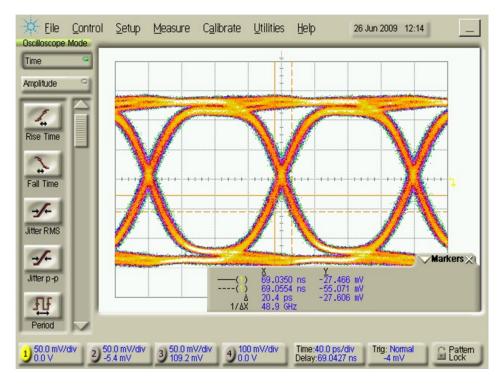

| Figure 4.19. 6.4Gbps eye diagrams. Bottom signal directly from mini-tester, top signal via interposer.                            | 67       |

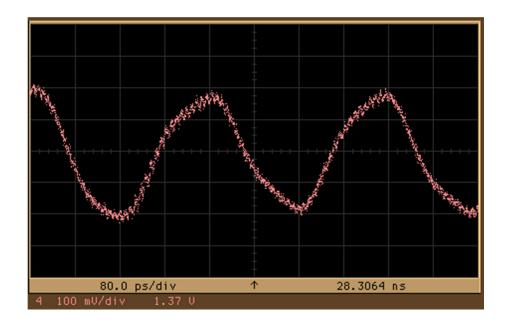

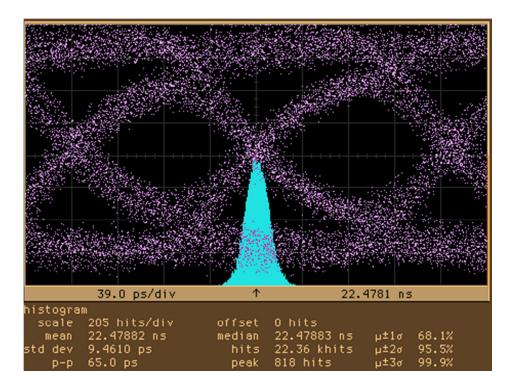

| Figure 4.20. Jitter measurement of 6.4Gbps through interposer.                                                                    | 68       |

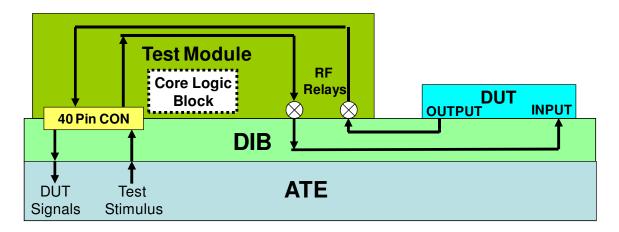

| Figure 5.1 ATE test head shown with device interface board. Test modules are designed to plug into DIB.                           | d<br>72  |

| Figure 5.2 Block diagram of test module design with DIB and ATE.                                                                  | 73       |

| Figure 5.3 Photograph of the FPGA 5/10Gbps Module.                                                                                                                                                 | 78         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 5.4 Multiplexing high-speed signals from core logic block to produce a double date rate signal. (a) shows a timing diagram to generate a double date rate. (b) shows logic components used. |            |

| Figure 5.5 Typical loopback path for external loopback test.                                                                                                                                       | 83         |

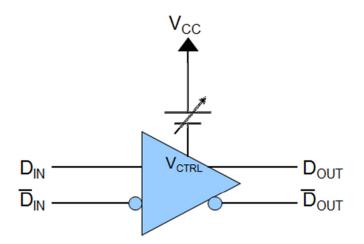

| Figure 5.6 Variable-gain output buffer.                                                                                                                                                            | 84         |

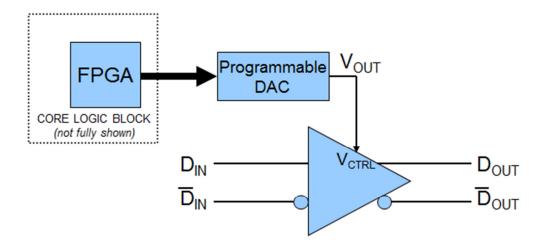

| Figure 5.7 Variable-gain output buffer controlled by a DAC.                                                                                                                                        | 85         |

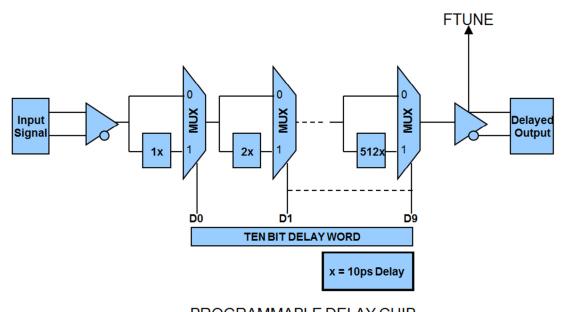

| Figure 5.8 Schematic of 10-stage delay chip                                                                                                                                                        | 87         |

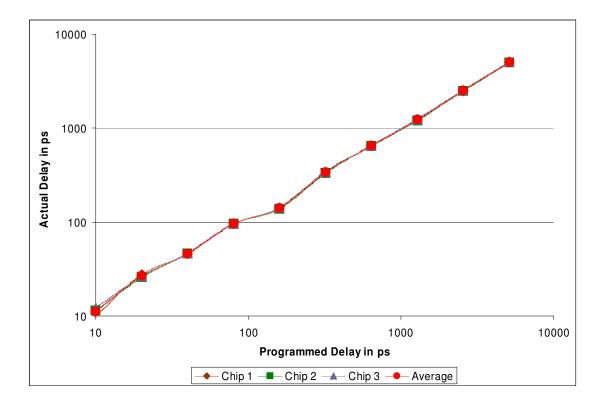

| Figure 5.9 Measured delay plotted against programmed delay for three delay chips.                                                                                                                  | 88         |

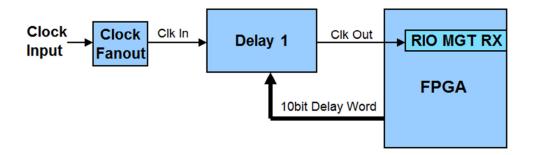

| Figure 5.10 Delay Chip used with clock input for RIO MGT                                                                                                                                           | 89         |

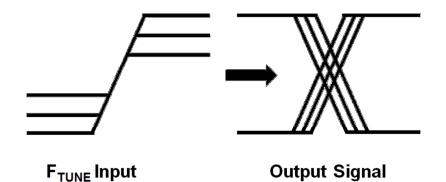

| Figure 5.11 Jitter injection using FTUNE pin                                                                                                                                                       | 91         |

| Figure 5.12 Low speed/ATE testing                                                                                                                                                                  | 92         |

| Figure 6.1 Example of GTX Transceiver Tile column in a Virtex-5 FXT device [102]                                                                                                                   | ] 100      |

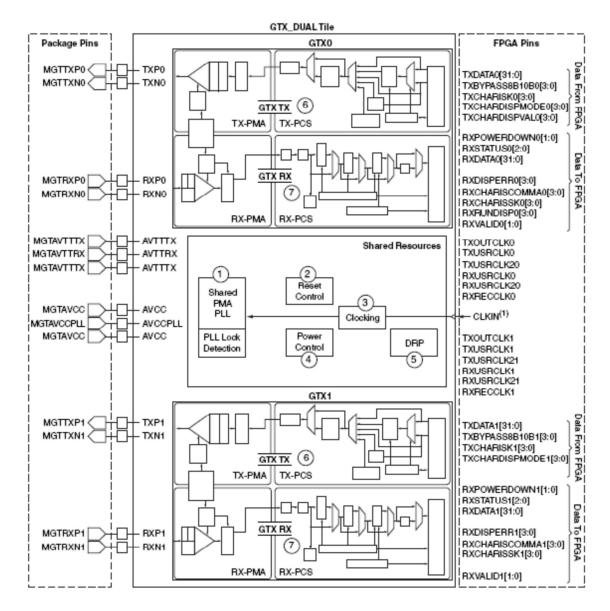

| Figure 6.2 GTX_DUAL Tile block diagram [102]                                                                                                                                                       | 101        |

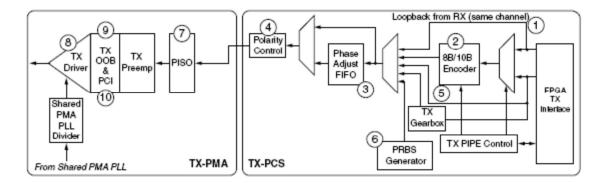

| Figure 6.3 GTX TX block diagram [102]                                                                                                                                                              | 102        |

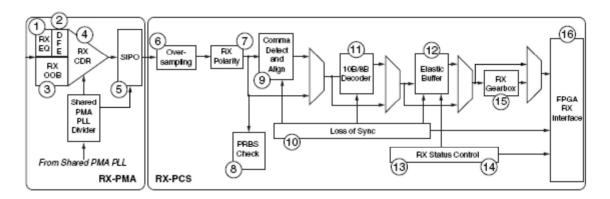

| Figure 6.4 GTX RX block diagram [102]                                                                                                                                                              | 103        |

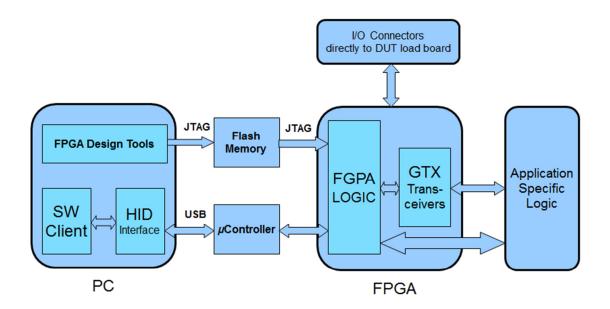

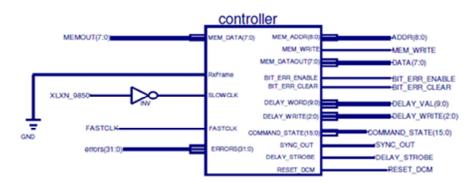

| Figure 6.5 Logical overview of FPGA in core logic block and surrounding componer                                                                                                                   |            |

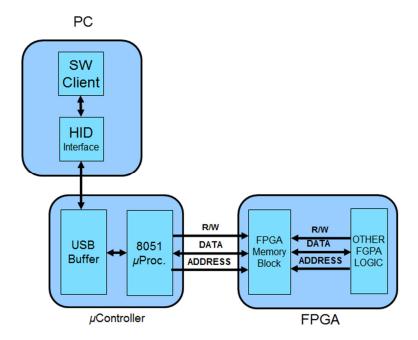

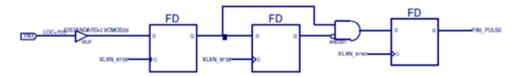

| Figure 6.6 Logical overview of communication to test module                                                                                                                                        | 105<br>109 |

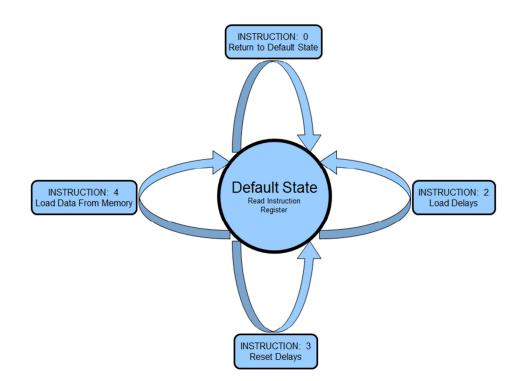

| Figure 6.7 State machine implemented in FGPA firmware to execute instructions                                                                                                                      | 111        |

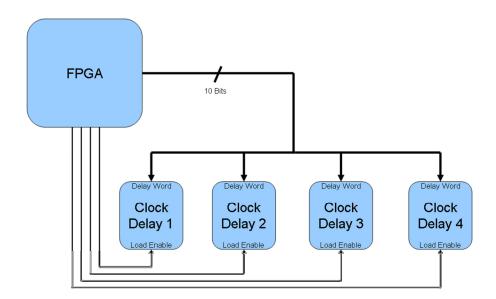

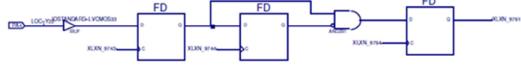

| Figure 6.8 FPGA clock delay control logic overview                                                                                                                                                 | 113        |

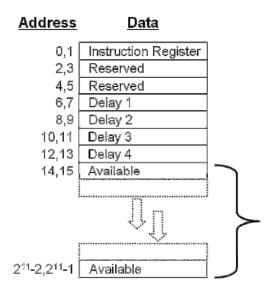

| Figure 6.9 FPGA firmware memory map                                                                                                                                                                | 115        |

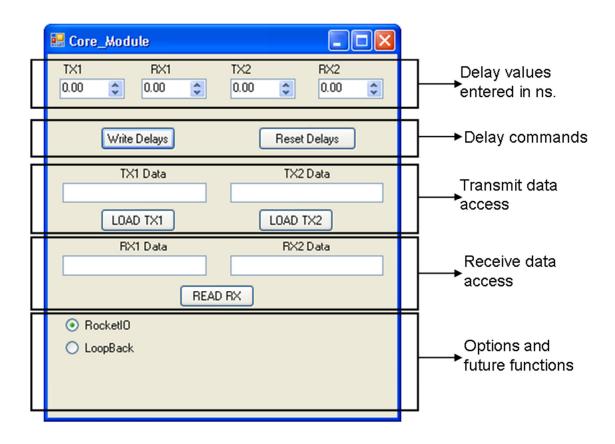

| Figure 6.10 Client software screen                                                                                                                                                                 | 116        |

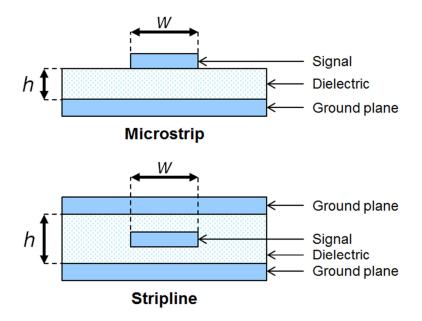

| Figure 7.1 Microstrip and stripline configurations                                                                                                                                                 | 124        |

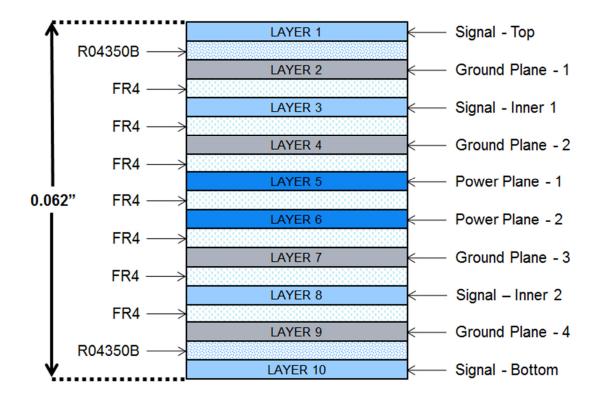

| Figure 7.2 Test module PCB stack up                                                                                                                                                                | 127        |

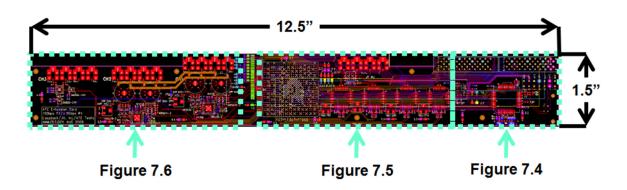

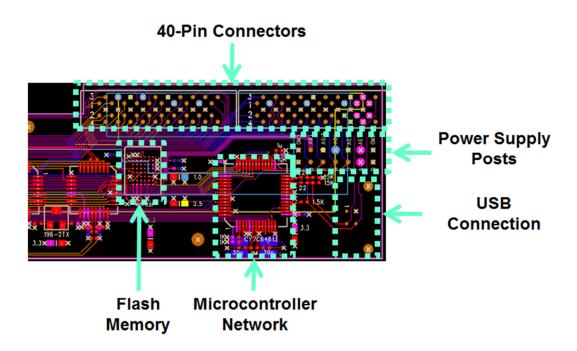

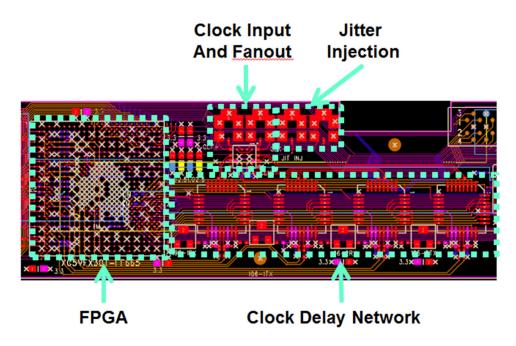

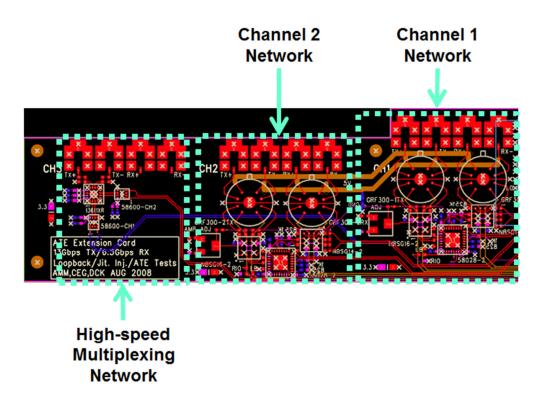

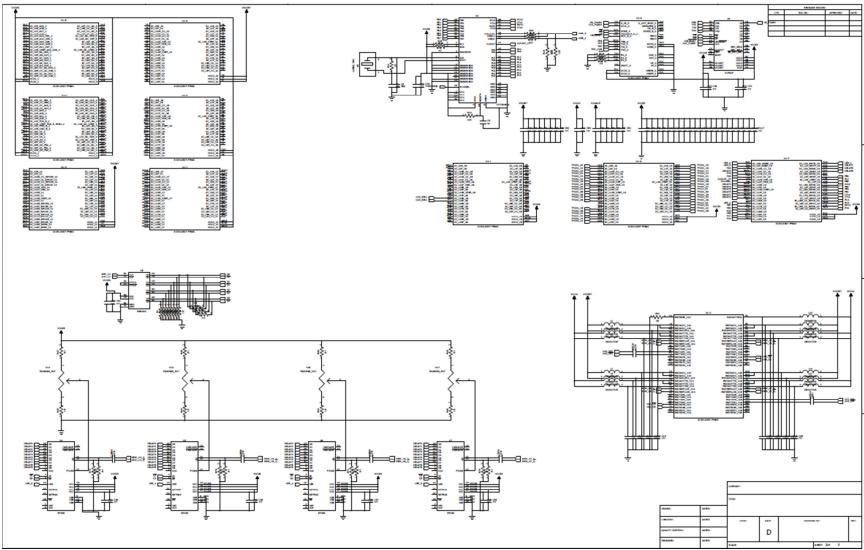

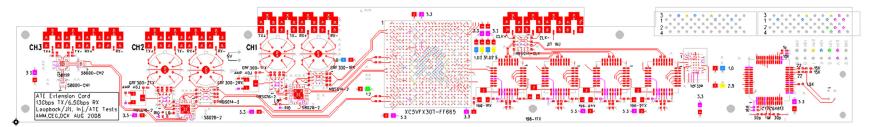

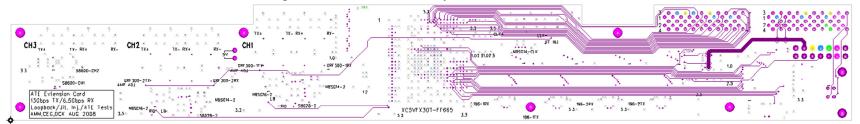

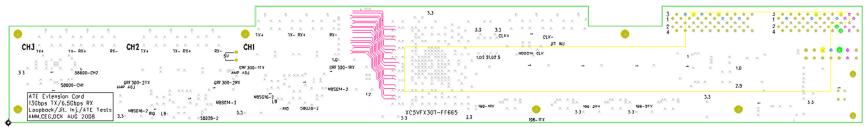

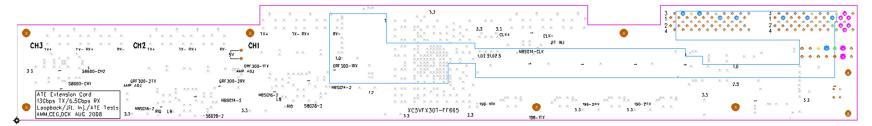

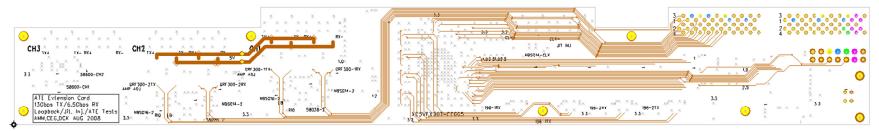

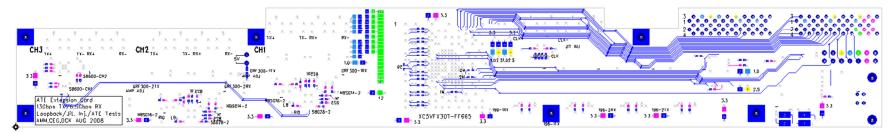

| Figure 7.3 Test module PCB layout using CAD software.                                       | 130 |

|---------------------------------------------------------------------------------------------|-----|

| Figure 7.4 Right-most section of test module layout                                         | 131 |

| Figure 7.5 Mid-section of test module layout                                                | 131 |

| Figure 7.6 Left-most section of test module layout                                          | 132 |

| Figure 8.1 Test setup to measure core logic block performance.                              | 136 |

| Figure 8.2. Core logic block output @ 5Gbps                                                 | 137 |

| Figure 8.3 Core logic block output rise time measurement @ 5Gbps                            | 138 |

| Figure 8.4 Core logic block output @ 6.25Gbps                                               | 138 |

| Figure 8.5 Core logic block output @ 9.00Gbps                                               | 139 |

| Figure 8.6 Core logic block jitter measurement @ 9.00Gbps                                   | 140 |

| Figure 8.7 Core logic block output @ 10.00Gbps                                              | 141 |

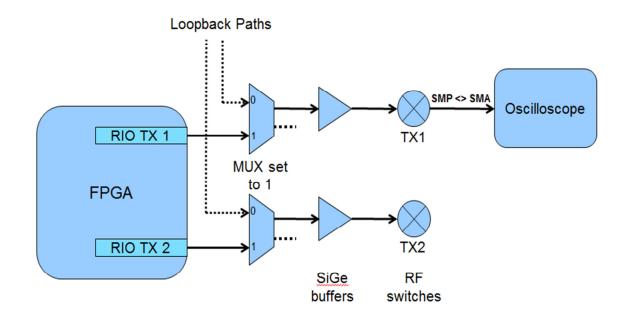

| Figure 8.8 Test setup to measure high-speed signal multiplexing performance                 | 142 |

| Figure 8.9 High-speed signal multiplexing output @ 10.00Gbps                                | 143 |

| Figure 8.10 High-speed signal multiplexing rise-time measurement @ 10.00Gbps                | 144 |

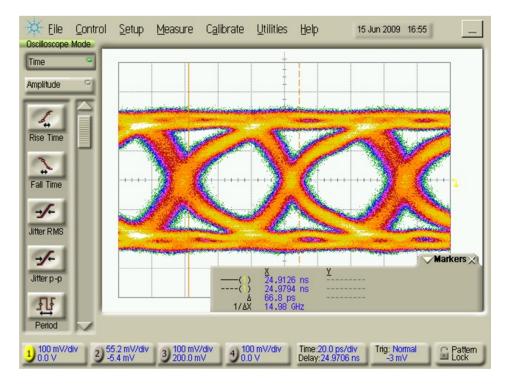

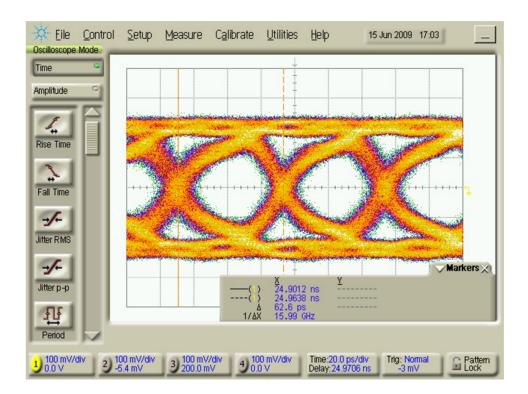

| Figure 8.11 High-speed signal multiplexing output @ 15.00Gbps                               | 144 |

| Figure 8.12 High-speed signal multiplexing output @ 16.00Gbps                               | 145 |

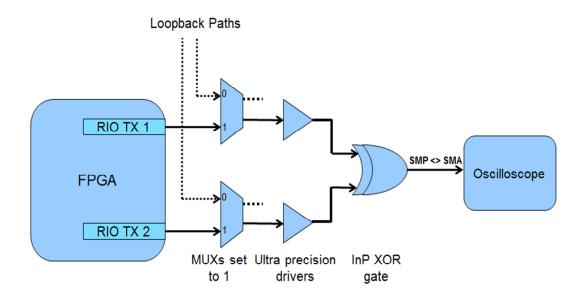

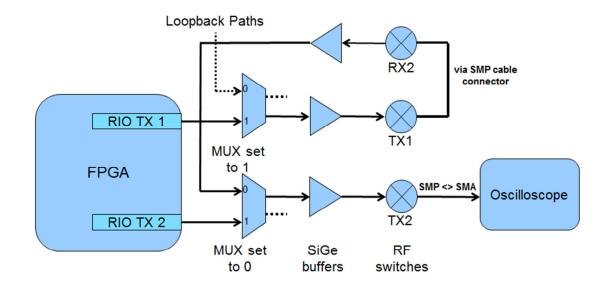

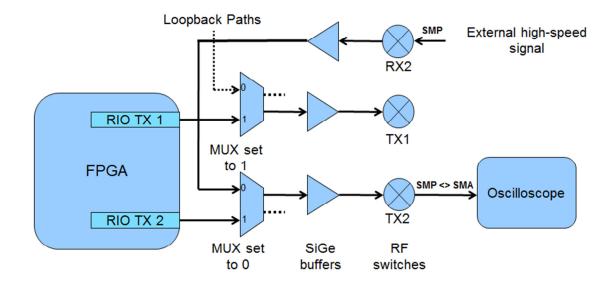

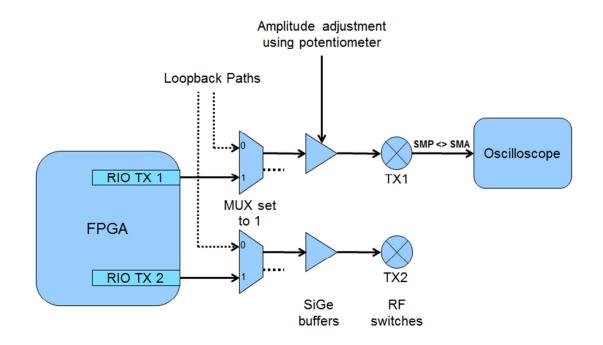

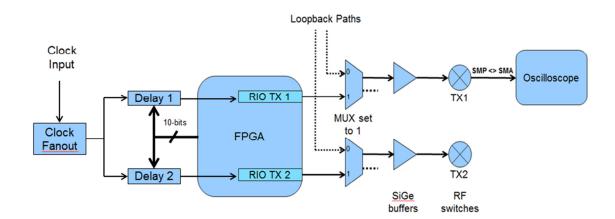

| Figure 8.13 Test setup to measure loopback path using RIO MGT signals.                      | 146 |

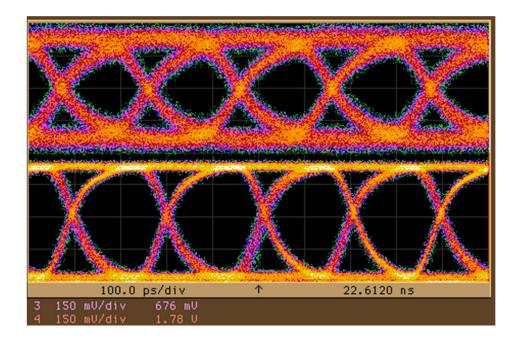

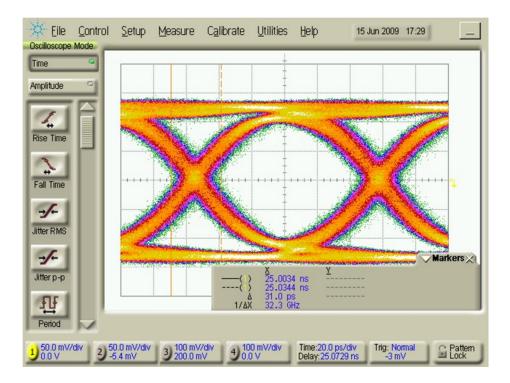

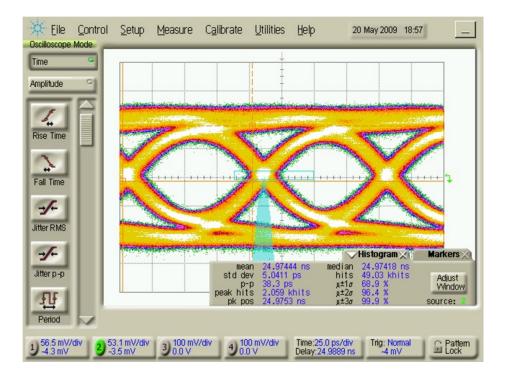

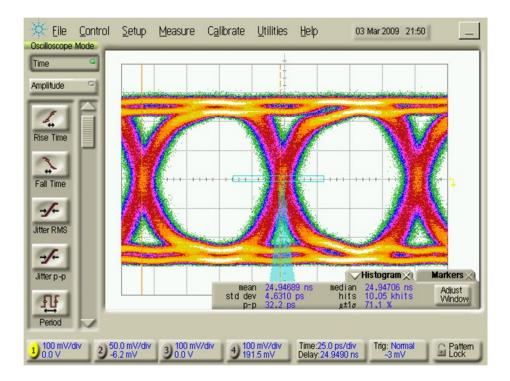

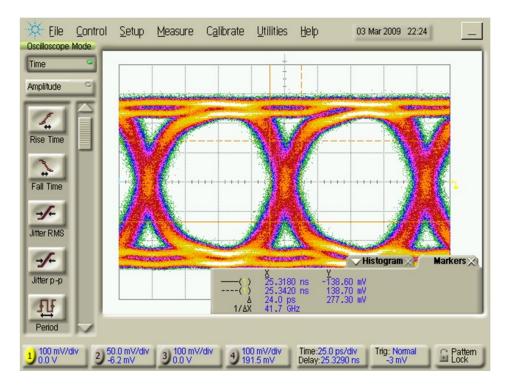

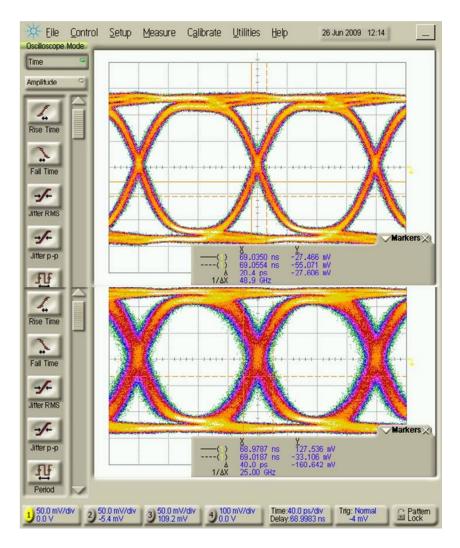

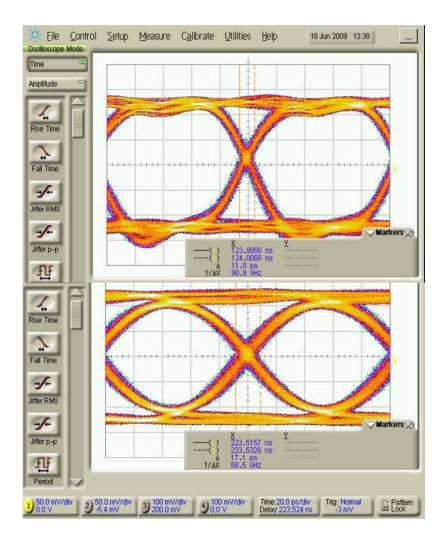

| Figure 8.14 Loopback path results using RIO MGT @ 6.25Gbps                                  | 147 |

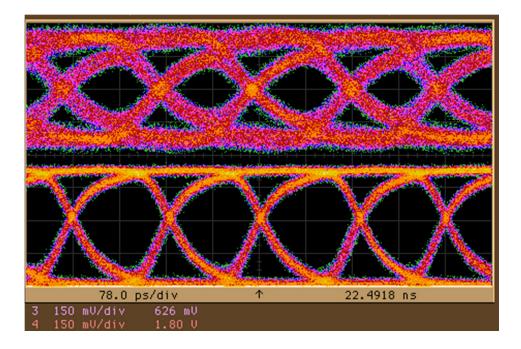

| Figure 8.15 Loopback path results using RIO MGT @ 9.00Gbps                                  | 148 |

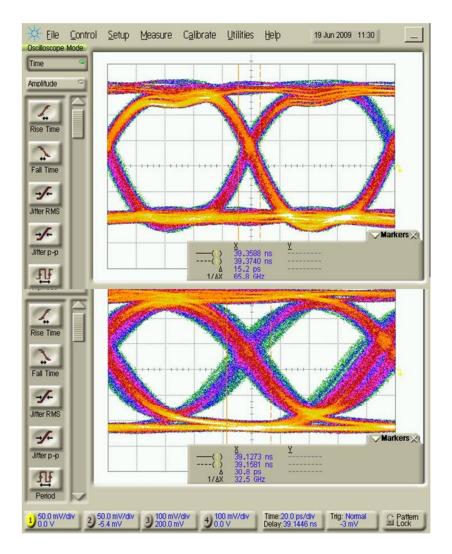

| Figure 8.16 Loopback path results using RIO MGT @ 10.00Gbps                                 | 149 |

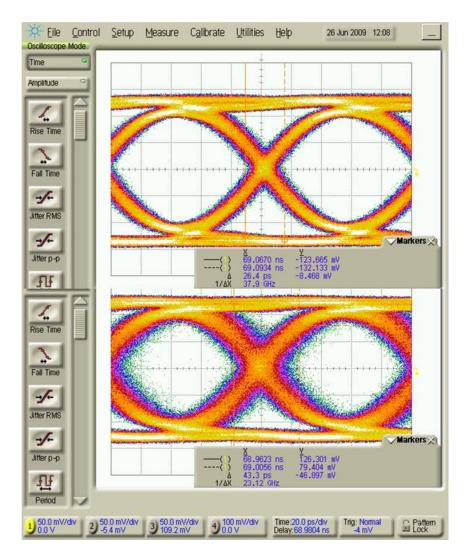

| Figure 8.17 Test setup to measure loopback path using an external high-speed signal source. | 150 |

| Figure 8.18 Loopback path results using external source @ 9.28Gbps                          | 151 |

| Figure 8.19 Loopback path results using external source @ 10.0Gbps                 | 152 |

|------------------------------------------------------------------------------------|-----|

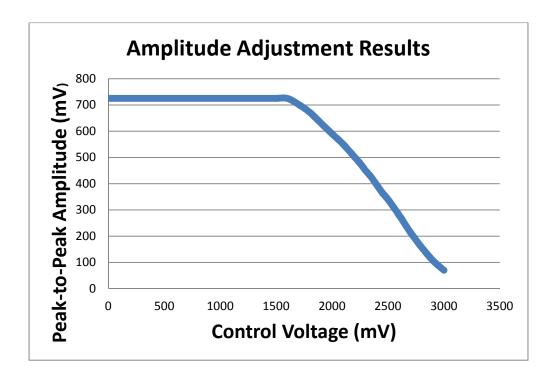

| Figure 8.20 Test setup to measure amplitude adjustment performance of test module. | 153 |

| Figure 8.21 Amplitude adjustment results from TX1                                  | 154 |

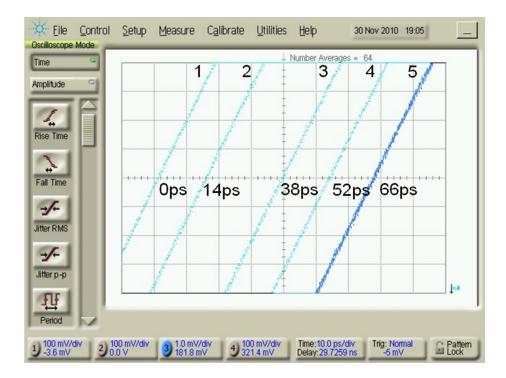

| Figure 8.22 Test setup to measure timing/skew adjustment.                          | 155 |

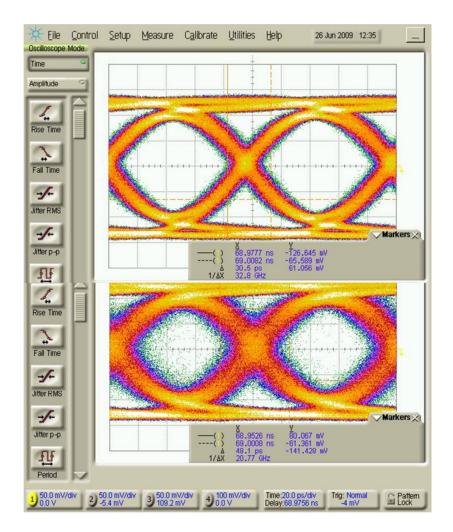

| Figure 8.23 Finite timing adjustment with delay chip                               | 156 |

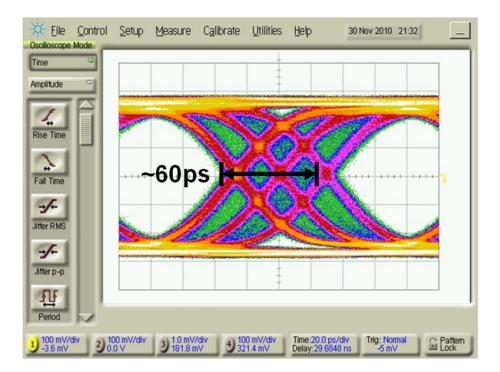

| Figure 8.24 Timing adjustment using analog FTUNE input on delay chip               | 157 |

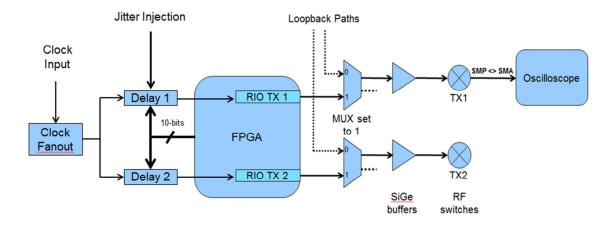

| Figure 8.25 Test setup to demonstrate jitter injection.                            | 158 |

| Figure 8.26 0.5V noise signal injecting 16ps (p-p) of jitter                       | 159 |

| Figure 8.27 2.0V noise signal injecting 52ps (p-p) of jitter                       | 159 |

| Figure 8.28 0.5V 20MHz sine signal injecting 30ps (p-p) of jitter                  | 160 |

| Figure 8.29 2.0V 20MHz sine signal injecting 81ps (p-p) of jitter                  | 160 |

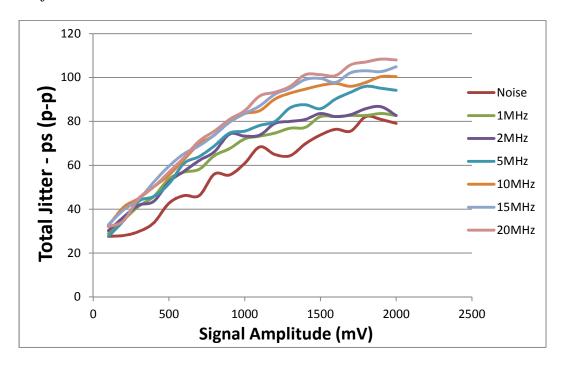

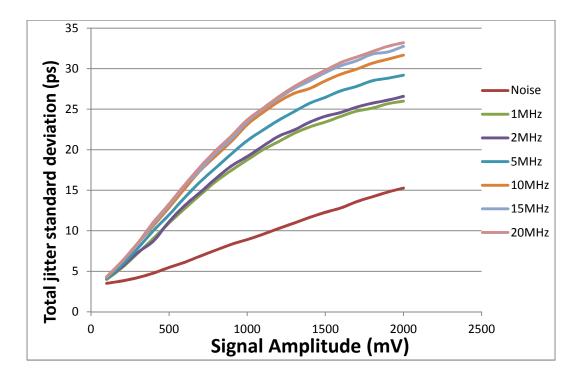

| Figure 8.30 Jitter injection measurements (p-p)                                    | 161 |

| Figure 8.31 Jitter injection measurements (standard deviation)                     | 162 |

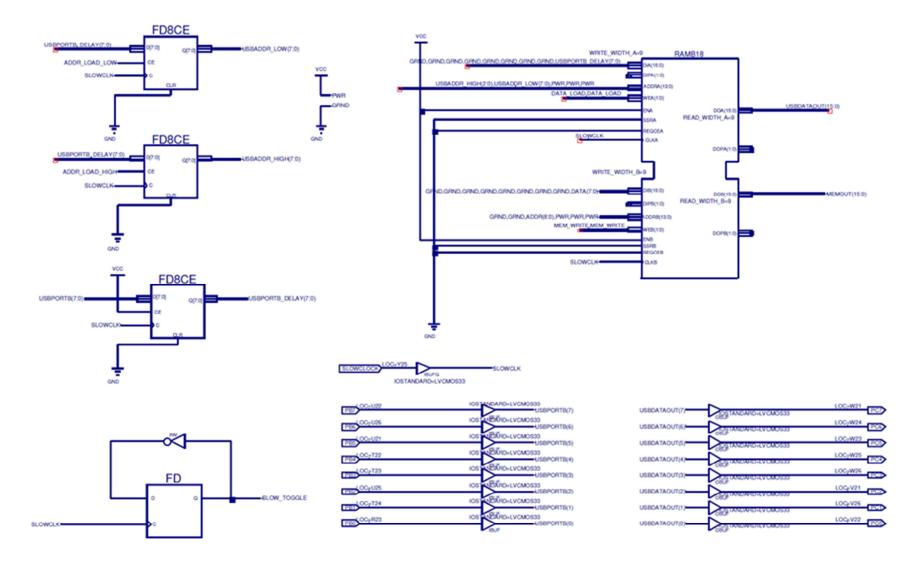

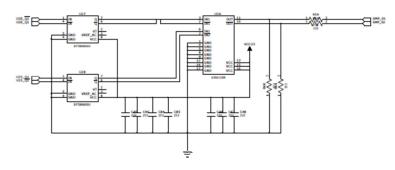

| Figure A.1 USB Communication logic                                                 | 176 |

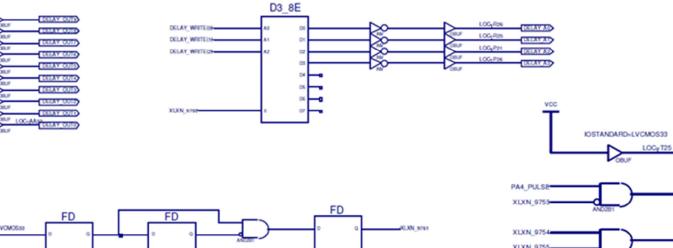

| Figure A.2 Delay load logic                                                        | 177 |

| Figure B.1 DLC software interface                                                  | 230 |

| Figure B.2 Test module software interface                                          | 244 |

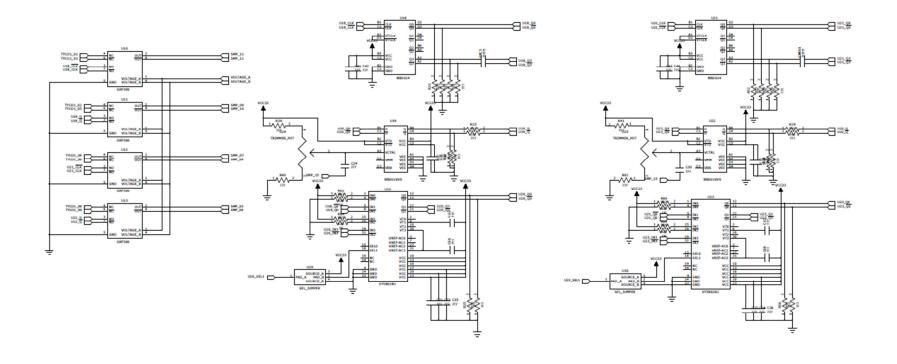

| Figure C.1 Core logic block schematic                                              | 248 |

| Figure C.2 Application specific logic schematic                                    | 248 |

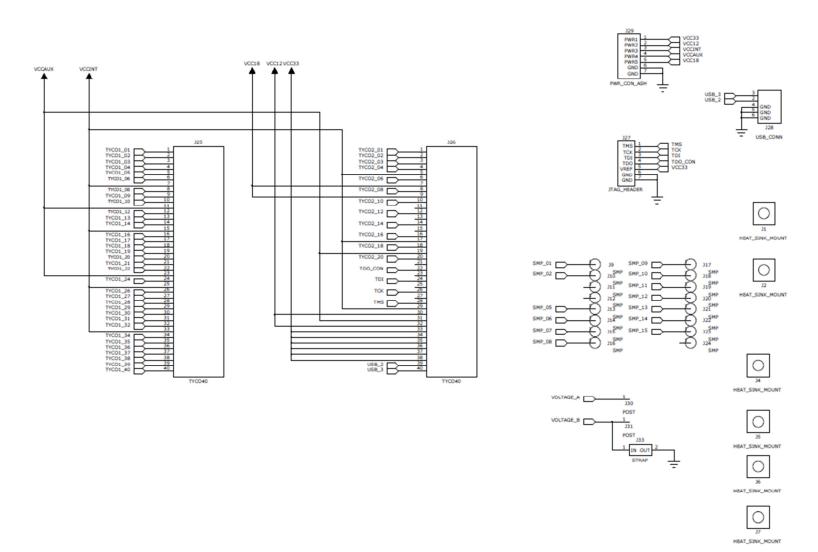

| Figure C.3 Test Module connectors schematic                                        | 249 |

| Figure C.4 Test Module Layer 1: Signal – Top                                       | 250 |

| Figure C.5 Test Module Layer 2: Ground Plane - 1                                   | 250 |

| Figure C.6 Test Module Layer 3: Signal – Inner 1                                   | 250 |

| Figure C.7 Test Module Layer 4: Ground Plane - 2  | 251 |

|---------------------------------------------------|-----|

| Figure C.8 Test Module Layer 5: Power Plane – 1   | 251 |

| Figure C.9 Test Module Layer 6: Power Plane - 2   | 251 |

| Figure C.10 Test Module Layer 7: Ground Plane - 3 | 252 |

| Figure C.11 Test Module Layer 8: Signal – Inner 2 | 252 |

| Figure C.12 Test Module Layer 9: Ground Plane - 4 | 252 |

| Figure C.13 Test Module Layer 10: Signal - Bottom | 253 |

## LIST OF SYMBOLS AND ABBREVIATIONS

| Automated Test Equipment                | ATE   |

|-----------------------------------------|-------|

| Alternating Current                     | AC    |

| Application-Specific Integrated Circuit | ASIC  |

| Automatic Test Pattern Generator        | ATPG  |

| Benzocyclobutene                        | BCB   |

| Ball Grid Array                         | BGA   |

| Built-In Self-Test                      | BIST  |

| Bus Low-Voltage Differential Signaling  | BLVDS |

| Bed of Nails                            | BoN   |

| Built-Off Self-Test                     | BOST  |

| Computer-Aided Design                   | CAD   |

| Clock Management Tiles                  | СМТ   |

| Central Processing Unit                 | CPU   |

| Cyclical Redundancy Check               | CRC   |

| Chip Scale Package                      | CSP   |

| Circuit Under Test                      | CUT   |

| Digital-to-Analog Converter             | DAC   |

| Direct Current                          | DC    |

| Data Dependent Jitter                   | DDJ   |

| Double Data Rate                        | DDR   |

| Design for Testability                  | DFT   |

| Device Interface Board                  | DIB   |

| Digital Logic Core                      | DLC   |

| DLL    | Delay-Locked Loop                                   |

|--------|-----------------------------------------------------|

| DRAM   | Dynamic Random-Access Memory                        |

| DSP    | Digital Signal Processing                           |

| DUT    | Device Under Test                                   |

| FIFO   | First In, First Out                                 |

| GaAs   | Gallium Arsenide                                    |

| GPS    | Global Positioning System                           |

| GSG    | Ground-Signal-Ground                                |

| GTL    | Gunning Transceiver Logic                           |

| GTLP   | Gunning Transceiver Logic Plus                      |

| HDL    | Hardware Description Language                       |

| HID    | Human Interface Device                              |

| HSTL   | High-speed Transceiver Logic                        |

| I/O    | Input and Output                                    |

| IC     | Integrated Circuit                                  |

| IEEE   | Institute of Electrical and Electronics Engineers   |

| InP    | Indium Phosphide                                    |

| IP     | Intellectual Property                               |

| ISA    | Instruction Set Architecture                        |

| ITRS   | International Technology Roadmap for Semiconductors |

| JTAG   | Joint Test Action Group                             |

| LFSR   | Linear Feedback Shift Register                      |

| LVCMOS | Low-Voltage Complementary Metal Oxide Semiconductor |

| LVDS   | Low-Voltage Differential Signaling                  |

| LVTTL  | Low-Voltage Transistor-Transitor Logic              |

| MAC     | Media Access Control                 |

|---------|--------------------------------------|

| MCC     | Multiple Copper Columns              |

| МСМ     | Multi-Chip Module                    |

| МСР     | Multi-Chip Package                   |

| MEMS    | Microelectromechanical Systems       |

| MUX     | Multiplexor                          |

| ORA     | Output Response Analyzers            |

| PA ATE  | Protocol Aware ATE                   |

| PC      | Personal Computer                    |

| РСВ     | Printed Circuit Board                |

| PCI     | Peripheral Component Interconnect    |

| PCIE    | PCI Express                          |

| PCI-X   | PCI eXtended                         |

| PEC     | Pin Electronic Card                  |

| PECL    | Positive Emitter-Coupled Logic       |

| PISO    | Parallel In, Serial Out              |

| PLL     | Phase-Locked Loop                    |

| PMU     | Parametric Measurement Unit          |

| PRBS    | Pseudorandom Binary Sequence         |

| PROM    | Programmable Read-Only Memory        |

| RAM     | Random Access Memory                 |

| RF      | Radio Frequency                      |

| RIO MGT | RocketIOTM Multi-Gigabit Transceiver |

| RSDS    | Reduced Swing Differential Signaling |

| RX      | Receive                              |

|         |                                      |

| SATA   | Serial Advanced Technology Attachment    |

|--------|------------------------------------------|

| SB     | Solder Bumps                             |

| SECT   | Standard For Embedded Core Test          |

| SerDes | Serializer/Deserializer                  |

| SIE    | Serial Interface Engine                  |

| SiGe   | Silicon-Germanium                        |

| SiP    | System-in-a-Package                      |

| SIPO   | Serial In, Parallel Out                  |

| SMA    | SubMiniature version A                   |

| SoC    | System-on-a-Chip                         |

| SoL    | Sea of Leads                             |

| SRAM   | Static Random-Access Memory              |

| SSC    | Stretched Solder Column                  |

| SSTL   | Stub Series Transceiver Logic            |

| SW     | Software                                 |

| TAM    | Test Access Mechanism                    |

| ТСК    | Test Clock                               |

| TDI    | Test Data In                             |

| TDO    | Test Data Out                            |

| TMS    | Test Mode Select                         |

| TPG    | Test Pattern Generator                   |

| TSP    | Test Support Processor                   |

| TX     | Transmit                                 |

| UBM    | Under Bump Metallization                 |

| ULVDS  | Ultra Low-Voltage Differential Signaling |

| Universal Serial Bus                | USB  |

|-------------------------------------|------|

| Ultra-Violet                        | UV   |

| Voltage-Controlled Oscillator       | VCO  |

| VHSIC Hardware Description Language | VHDL |

| Wafer-Level Package                 | WLP  |

|                                     |      |

#### SUMMARY

This thesis presents methods for developing multi-function, multi-GHz, FPGAbased test modules designed to enhance the performance capabilities of automated test equipment (ATE). In recent years technological advancements in semiconductor technology have outpaced advances in ATE testing capabilities, thereby causing significant challenges for new high-speed device testing. The main motivation of this research was to develop solutions that address these challenges.

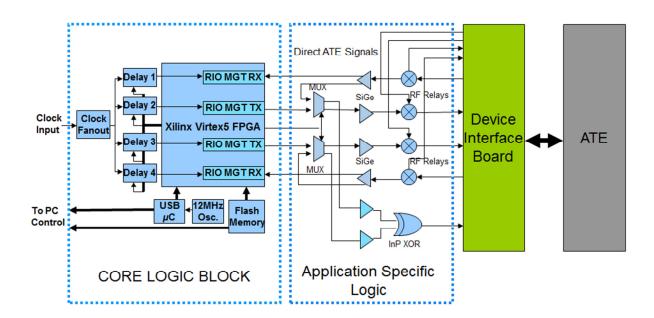

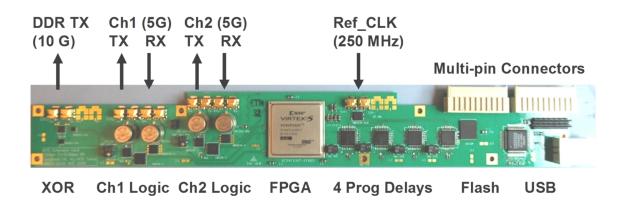

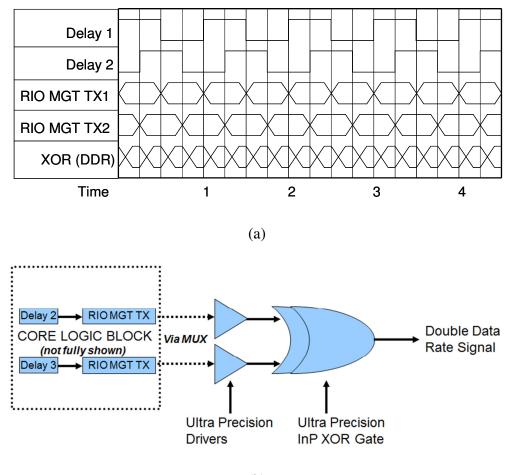

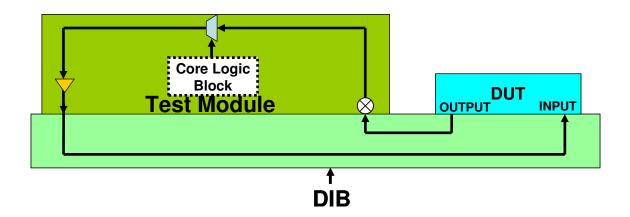

The methods shown in this thesis are used to develop a design approach that utilizes a test module structure in two blocks. A core logic block is designed using a multi-GHz FPGA that provides control functions. Another block called the "application specific" logic block includes components required for specific test functions. Six test functions are demonstrated in this research: high-speed signal multiplexing, loopback testing, jitter injection, amplitude adjustment, timing adjustment. Furthermore, the test module is designed to be compatible with existing ATE infrastructure, thus retaining full ATE capabilities for standard tests. Experimental results produced by this research provide evidence that the methods are sufficiently capable of enhancing the multi-GHz testing capabilities of ATE and are extendable into future ATE development.

The modular approach employed by the methods in this thesis allow for flexibility and future upgradability to even higher frequencies. The methods allow a next-generation FPGA to be quickly integrated into a test module to increase performance. Similarly, new components can be designed into the "application specific" block for additional test functionality. Therefore the contributions made in this thesis have the potential to be used into the foreseeable future for enhancements to semiconductor test capabilities.

xxii

#### CHAPTER 1

## **INTRODUCTION**

The objective of this research is to develop feasible and economical solutions to testing high-speed digital devices at multi-GHz rates. Testing high-speed digital devices at full speeds is essential to assure that manufactured devices meet design specifications and function properly throughout the entire range of intended operation. Increases in device performance and functionality have resulted in challenging problems pertaining to testing them effectively. Many current methods of testing are either inefficient or prohibitively expensive. This research presents methods to develop an efficient test system to cost-effectively test high-speed semiconductor devices.

Technology roadmaps have accurately predicted rapidly increasing clock and data rates of electronic devices [1]. Current roadmaps indicate this trend will continue into the foreseeable future [2]. Gordon Moore states in his famous 1965 article [3] – the basis for the well-known "Moore's Law"- that the number of components that can be placed into a device nearly doubles every two years. This "law" has been upheld for nearly half a century, despite meeting many physical limitations on the way. Furthermore, this trend is expected to continue without major obstacles until at least the year 2015 or perhaps later [4], thereby producing exponentially complex, higher-performance devices.

Automated Test Equipment (ATE) has generally been used to test high-volume semiconductor devices over the last four decades. Over this period, ATE performance has improved and new capabilities have been added. However, the advances in many ATE performance measures and capabilities have not kept up with the advances in semiconductor technology [1][2]. One commercially available system can run up to 12.8Gbps after installing add-on instrumentation [5]. Typical base systems are limited to lower speeds [6]. This situation has resulted in the production of advanced, complex devices, but not a feasible way to test their complete functionality. This problem has become so critical to the development of higher performance devices, that the paradigm in which design is associated with research and development and testing is associated with manufacturing no longer stands [7]. Design and test can no longer be dealt with as separate issues – they must be approached hand in hand in order to efficiently develop next generation high-performance devices.

Design for Testability (DFT) incorporates certain testability features into the design stage of semiconductor devices. These improvements typically include design modifications and enhancements such as serial scan, boundary scan, and built-in self-test (BIST) [7]. Most DFT and BIST methods can be used to verify internal logic and structural connectivity, thereby simplifying external testing required.

As the complexity of devices increase, testing the entire device globally becomes inefficient and complex. Incorporating DFT techniques into various components of devices produces substantial benefits [8][9]. This has caused most semiconductor manufacturers to incorporate DFT features into complex device design. Assuming there is a practical degree of DFT and BIST methods on the device, its testing complexity can be reduced to a subset of traditional testing [10]. However, functional testing at full clock speeds remains as one of the most critical tests required as DFT and BIST generally do not operate at these speeds. Furthermore, environmental and parametric testing is still required, as these tests are not covered by DFT and BIST methods. Therefore, although the required external tests are reduced by incorporating DFT, high-performance devices still require high-speed functional tests and traditional testing such as environmental and parametric testing.

ATE have traditionally been able to perform most semiconductor testing requirements mentioned above. Parametric tests are performed by elaborate parametric measurement units (PMUs) within an ATE. Reliability tests are performed by an ATE's full suite of sophisticated instrumentation and software. These tests do not fundamentally change with increasing clock and data rates. Functional testing, on the other hand, is limited by an ATE's performance capabilities. Purchasing new ATE systems when higher-performance testing is required can be cost prohibitive (historical ATE buy rates have been reduced by a factor of two since 1981 [11]). Upgrading existing ATE performance with additional pin electronics cards (PECs) from its manufacturer is a cheaper option when available. Therefore there is a need for a test system that can perform functional tests beyond the performance capabilities of available ATE. Based on technology road maps, test systems will be required to test devices running at speeds in excess of 10Gbps.

To approach the problem of increasing test performance requirements, a modular test system is presented in this thesis. The test system is used to enhance specific ATE performance criteria such as high-speed signal generation, high-speed loop-back testing, etc. The test system is designed with a core component that aims to exploit state-of-theart field programmable gate array (FPGA) technologies. Current FPGA performance exceeds many performance criteria of ATE [6][12]. Furthermore the use of an FPGA allows the test system to operate independently of the ATE and without any of its resources which tend to be relatively expensive. With the FPGA, the core component controls and generates many test functions itself. However, for comprehensive testing, test functions such as parametric measurement and reliability testing are required. As discussed above, these traditional, lower-speed parametric tests are better handled by and ATE. Hence, to retain full testing functionality, the designed solutions must be compatible with existing ATE infrastructure.

In addition to a core component, the test system can be designed with logic to enhance ATE capabilities based upon specific test application requirements. For instance, typical ATE are limited in signal speeds up to 3.2Gbps. If higher speed test signals are required for the test application, logic can be added to the test module to increase signal speeds to above 3.2Gbps. Similarly, if other test capabilities are required such as jitter injection, additional logic can be added to the test module.

Therefore the objective of the research presented in this thesis is to develop feasible methodologies for extending ATE performance capabilities using multi-GHz FPGAs. The research develops an approach that can be adapted as new functionalities are required and further technological advances take place. The approach consists of the design of a test system in separate blocks, specifically a core logic block and an application specific block. When higher performance is required of the test system, the core logic block can be redesigned independently of the application specific logic. Similarly, the application specific logic can be redesigned or additional logic added to accommodate new or improved test applications. By limiting the solution to focus on specific enhancements, the methods presented in this thesis allow ATE performance to be extended in a feasible, timely and cost-effective manner. The organization of this thesis is as follows. In Chapter 2, technology roadmaps are presented and discussed. Also the history of ATE is given and the evolution of testing with concepts such as DFT and BIST is described. Two different methods of previous work done in the area to enhance high-speed digital testing capabilities are presented in Chapters 3 & 4. Chapter 3 presents modular extension techniques of ATE to accommodate high-speed digital testing. This method of test enhancement extends resources from the ATE to produce higher performance test capabilities. Chapter 4 presents a FPGA-based stand-alone test system that is capable of operating independently of an ATE and providing high-performance test capabilities.

The reaming research presented in this thesis uses the lessons learned in both Chapters 3 and 4 and develops an FPGA-based modular extension test system designed to work within existing ATE infrastructure, but not to use ATE resources. The test system can be operated with the FPGA, thus allowing operation independent of an ATE. Chapter 5 discusses in detail the concept and design of the test system. As the FPGA in the test system is a critical component of it, the selection, design, and use of the FPGA is discussed in Chapter 6. Designing high-speed digital systems requires additional considerations versus designing at-speed systems. At higher speeds, passive system elements can cause undesirable effects, essentially altering system performance. These additional considerations are discussed in Chapter 7 and the physical design of the test system is presented. In Chapter 8, the experimental results of this thesis are presented and the developed test system is characterized. Finally in Chapter 9, conclusions of this work are presented and future work discussed.

## CHAPTER 2

### **BACKGROUND AND HISTORY**

In the semiconductor industry, specialized computers are used to test devices. Over the past 50 years or so, these specialized computers, or ATE as they are formally known as, have become bigger, faster and offer more functionality than ever before. This chapter aims to present a background on testing and the history of ATE evolution.

Semiconductor testing is largely driven by the technological trends of the semiconductor industry. Various technologies, such as digital, optical, MEMS, RF, etc. require different testing methodologies. Furthermore, technological advancements in these fields merit different methodologies of test techniques due to the complexities imposed by these advancements. Therefore it is relevant to discuss these technological advancements to fully understand the nature of modern day semiconductor testing. Due to this reason, in this chapter, technology roadmaps are discussed first. ATE are the primary tools used in testing semiconductor devices, thus after presenting technology roadmaps, the history and development of ATE is discussed. The last section of this chapter discusses general testing methods and how they have been developed along with ever increasing semiconductor device functionality.

#### 2.1 Technology Roadmaps

Over the past few decades, the ever increasing performance and transistor count of semiconductor devices has caused a phenomenal change in semiconductor test requirements. Consumer demand during the 80s and 90s focused mainly on increased performance of electronics. However the last decade witnessed a fundamental shift in market demand, as technological advancements allowed the integration of various semiconductor technologies. These technological advancements include technologies such as Multi-chip modules (MCM), Multi-chip package (MCP), System-on-a-Chip (SoC), System-in-a-Package (SiP) and 3D packaging, which have allowed the integration of various semiconductor technologies such as digital, RF, optical, MEMS, etc. devices into one system [13]. Based on these capabilites, consumer demand has shifted from not only higher performance from electronic devices, but more functionality as well.

The demand growth of simple one function devices has been steadily declining. In many cases, such as the point-and-shoot digital camera, sales have actually been declining since 2008 [14]. Current market demand indicates that consumers prefer to use their smartphone devices, and demand that a smartphone also function as a highresolution camera, GPS device, motion sensor, etc. This level of integration has caused significant challenges in testing as it is ultimately the application requirements or specifications that determine test requirements. Furthermore, each technology requires different test methodologies. Along with testing requirements for various technologies, increased device complexity has increased test complexity, which further translates to increased test cost. The cost of testing a device is now a large part of its total manufacturing cost [15]. Fabrication costs per function have generally decreased 25-30% annually, while test cost per function has decreased only 5-10% annually [16]. Given that test costs are already a large part of the total manufacturing cost; the statistics indicate that testing costs will soon be the majority of a device's final cost. Figure 2.1 shows a plot of manufacturing and test costs per function over the past 40 years and predicted for the next 20 years. It is expected that the cost of testing a device will become the majority of a device's cost shortly within this decade [17].

Figure 2.1 Semiconductor test cost vs. manufacturing cost [17].

According to the International Technology Roadmap for Semiconductors (ITRS), the capital cost for a test cell is the following:

$C_{CELL} = C_{BASE} + C_{INTERFACE} + C_{POWER-SUPPLIES} + C_{TEST-CHANNELS} + C_{OTHER}$

Where  $C_{BASE}$  is the cost of the base system (channels not included),  $C_{INTERFACE}$  is the cost of interfacing devices,  $C_{POWER-SUPPLIES}$  is the cost of power supplies,  $C_{TEST-}$ CHANNELS is the cost of channels, and  $C_{OTHER}$  is the remaining costs such as floor space, cooling systems, etc.[1]. The total cost of a test cell can be broken down into more meaningful figures by dividing costs by testing throughput, to result in a per device test cost. The current top drivers of test cost and future test cost drivers according to the ITRS are shown in Table 2.1.

| Current Top Test Cost Drivers    | Future Test Cost Drivers             |  |  |  |  |  |  |

|----------------------------------|--------------------------------------|--|--|--|--|--|--|

| ATE Capital Expenditures         | Device Performance Metrics           |  |  |  |  |  |  |

| ATE Interface Expenditures       | New Defects and Reliability Problems |  |  |  |  |  |  |

| Cost of Test Program Development | Known Good Die Requirement           |  |  |  |  |  |  |

| Test Time an Test Coverage       | Test Requirements of Packaging       |  |  |  |  |  |  |

Table 2.1 Test Cost Drivers [1]

Device performance metrics will be one of the main future test cost drivers. The cost of testing high-speed I/O has become very significant [1]. High frequency I/O technology continues to show significant growth in speed and port count. Trends such as these are expected to continue as technology roadmaps clearly predict rapidly increasing clock and data rates into the foreseeable future. Table 2.2 shows the ITRS Test and Test Technology Roadmap from 2005. It can be noted from the table that not only are the data rates for future semiconductors expected to increase, but their feature sizes are expected to decrease.

|                     |       |       |       |       | 8, -  |       |       |       |       |

|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Year                | 2005  | 2006  | 2007  | 2008  | 2009  | 2010  | 2011  | 2012  | 2013  |

| Wafer Test -        |       |       |       |       |       |       |       |       |       |

| number of Sites     | 8     | 8     | 8     | 16    | 16    | 16    | 16    | 32    | 32    |

| Half Pitch size     |       |       |       |       |       |       |       |       |       |

| (nm)                | 90    | 78    | 68    | 59    | 52    | 45    | 40    | 36    | 32    |

| Chip-to-board (off- |       |       |       |       |       |       |       |       |       |

| chip) speed (high-  |       |       |       |       |       |       |       |       |       |

| performance, for    |       |       |       |       |       |       |       |       |       |

| peripheral buses)   |       |       |       |       |       |       |       |       |       |

| (MHz)               | 3125  | 3906  | 4883  | 6103  | 7629  | 9536  | TBD   | 14901 | 18626 |

| I/O data rate       | 0.1 - | 0.1 - | 0.1 - | 0.1 - | 0.2 - | 0.2 - | 0.2 - | 0.2 - | 0.2 - |

| (GT/s)              | 3     | 6     | 6     | 6     | 12    | 12    | 12    | 15    | 15    |

Table 2.2 ITRS Test and Test Technology Roadmap 2005 [2]

Based on this roadmap and technology trends, there are a few important areas of concern regarding test. The first is the rampant data rate increase. Due to higher data rates, test systems must be capable of such high-speed data rates. Second, test systems must be able to accommodate the increase in pin counts enabled by the lower feature sizes. In 2009, up to 250 pairs of 7Gbps backplane style SerDes channels were found in some applications [1], however most applications will have 32 channels or less. The third area of concern is test system bandwidth. At 10Gbps, the bandwidth requirement becomes 20GHz or higher and providing such an interface including connections through PCB, cables, connectors, etc. becomes a monumental engineering task. The fourth area of concern is jitter, and this becomes a significant concern at multi-GHz data rates. At a 10Gbps speed, bit periods are 100ps and only 50ps of jitter can render half that bit period useless. Dealing with such high-speed signals and introducing low amounts of jitter is not a trivial task. The final area of concern is the cost factor. Traditionally high-speed devices were designed as high-performance high-priced devices. This has been rapidly changing as the thirst for high-speed data in commoditized hand-held devices has been insatiable. Furthermore, with accelerating technology improvements, product lifecycles have become shortened, which has made cost savings from "mature" technologies very difficult to achieve.

The concerns discussed above indicate a need for a test system that:

- i) is capable of multi-GHz I/O

- ii) is capable of accommodating multiple data channels

- iii) is capable of high bandwidth through all components

- iv) adds low jitter to the test signal

#### v) feasibly and economically tests devices

In addition to the new requirements for a test system discussed above, a comprehensive test system should always be capable of standard tests functions such as timing adjustment, voltage adjustment, parametric tests, etc. Taking all these concerns into consideration, multi-dimensional challenges arise when developing new test instrumentation. Semiconductor testing is generally done using ATE. The next section discusses the history and development of ATE systems.

### **2.2 Automated Test Equipment**

The roots of modern ATE were developed in the 1960s by Nick DeWolf, a wellknown test engineer during that era, and often referred to as the father of ATE [18]. DeWolf and Alex d'Arbeloff together founded a company called Teradyne whose business plan was to manufacture and design semiconductor test equipment. In 1966, Teradyne introduced an integrated circuit tester, the J259, which was the first tester to use a minicomputer for control, thus launching the first ATE [19].

The first generation of ATE was comparatively primitive to modern day ATE. It wasn't until the late 70s and early 80s that ATE started to achieve complex functionality and the use of automatic handlers and probers. During this time multi-function ATE were being introduced that could test mixed-signal, RF, optical as well as digital components.

In the mid-to late 80s digital devices were rapidly evolving into the GHz range. This required test systems capable of testing at GHz rates. Many manufacturers developed systems using various techniques to increase speeds. For instance, the Megatest MegaOne and the Tektronix S-3295 used multiplexing concepts on adjacent pins to double output frequencies [20]. However these systems could operate at only a few hundred MHz, with timing accuracy of only 0.5-1ns, and above all, cost nearly \$3M for a 256-pin system. Therefore around this time, ATE functionality could not keep pace with the rapid advancements of semiconductor technologies. In order to achieve GHz speeds and keep up with technological trends, test engineers either developed custom test heads for existing ATE or developed extension systems to produce GHz signals. These enhancements are the topic of the next chapter.

Despite the lack of performance during this period, a significant shift did occur in ATE architecture. Up to this point, most ATE systems used a "shared resource" architecture, where a few dedicated "per-pin" electronics, such as formatter or comparator served as an interface to the device under test (DUT). When lower pin counts were required, this allowed a cost advantage. However as more and more switching and multiplexing techniques were employed, issues such as test calibration and programming became very tedious due to signal routing. Also, at higher speeds bandwidth limitations produced undesirable results. To overcome these issues, manufacturers introduced "perpin" architecture [20]. Under this architecture, each tester pin included its own dedicated pin electronics such as pattern generation, timing control, etc. This eliminated the complex switching algorithms and timing issue between pins, and created a more simplistic, efficient and easy to use system as each channel could be controlled independently. This architecture in turn reduced the cost of the base system, and allowed users to purchase additional channels when required. An overview of the shift from shared resource architecture to per-pin architecture is shown in Figure 2.2.

Shared Resource ATE Architecture

Figure 2.2 ATE Architecture Change

Hewlett Packard released its first series of testers based on this new "per-pin" architecture in the 90s. The 83000-F660 was the state-of-the-art tester at the time. However, it could not reach 1GHz; its highest speed was 666MHz. The cost of the system ranged between \$1-3M and despite the cost and performance limitations, these systems were the industry leader and quite popular.

Other players in the market included Teradyne, Advantest and Credence systems. All had their own custom systems, but none running above 1GHz. However around this time, a new standard for modern ATE architecture did evolve which included a test mainframe/test head, a development workstation, and power supplies. Much of the testing done on ATE was power intensive and generated much heat. Thus most ATE were equipped with efficient cooling systems, for example the HP8300 was equipped with water cooling features.

Despite the fact that tester performance could not keep pace with device performance, many additional functions were added and improved. These included elaborate parametric measurement units, sophisticated test pattern generation algorithms, large amounts of memory, etc. Adding such additional functions to ATE have kept their costs around the same level. ATE cost per pin for high-end systems still hovers around \$3,000-\$10,000 per channel. Therefore a 256 channel ATE can easily range from \$1M to above \$5M.

In order to lower ATE costs, manufacturers pushed the concept of openarchitecture test platforms in the early 2000s [13]. The concept of open-architecture testers is similar to that of building a custom PC, in which one can purchase a motherboard, a processor, a video card, etc. separately in order to build one system. Similarly ATE manufacturers developed base test systems to which PECs could be added to. The idea was that consumers could purchase a base system and only the cards they required, thus keeping costs down [21]. Furthermore this allowed the design of higher end cards that could be sold to consumers that required high-performance testing. For example Verigy (formerly HP's Test Systems division) develops a base system called V93000 SOC (the latest system evolved from the HP83000). The system can accept cards with functions such as digital nano-electronics testing, high-speed digital testing, highend consumer mixed-signal testing, etc. [5]. Despite this new model, the demand for higher-performance, greater accuracy and increased vector memory have offset most cost savings achieved. The base system for the V93000 costs well over \$1M, and adding PECs for required high-speed testing can create a total price tag well into the \$3-5M range. Furthermore, there haven't been significant third-party efforts to develop PECs for ATE due to their complexity and performance requirements. Independent PEC development by third-parties could have lowered costs. Therefore the ATE industry is yet to experience significant cost reductions.

The latest development in the ATE industry is what has been termed Protocol Aware ATE (PA ATE). PA ATE came into prominence in 2007 and was formally debuted in [22]. The concept for PA ATE arose as higher levels of integration allowed the manufacture of diverse devices using technologies such as SoC. Device manufacturers with substantial IP libraries could develop an entire true system with diverse IP blocks in a single process on a single die with minimal development time. Each IP block could have different protocols such as JTAG, PCI, PCI-E, USB, SATA, serial flash, SRAM/DRAM, etc. And each protocol would require its own test strategy, thus testing the entire device on a global level would be high inefficient if not impossible. PA ATE aims to solve this problem by essentially natively emulating, in real time, chip I/O at the protocol level. Programmable interfaces in PA ATE are used to perform realtime state detection to handshake with a device using its native protocol. Test strategies are developed for each protocol, and once a communication link to the device is established, testing is performed in a more efficient manner.

PA ATE enables cooperative test between an ATE and a DUT with realistic device activity, thus improving the quality of test [23]. The ATE provides a suitable test environment with infrastructure such as power supplies, cooling systems, DUT

15

interfaces, probe cards, etc. Furthermore, the ATE controls overall test flow, I/O levels, I/O timing, etc. and manages results.

PA ATE is most effective when used with DFT techniques. DFT is used to provide access to internal chip resources and allows the ATE to perform low-level structural tests using the required protocol. Low-level structural tests require less ATE complexity and simpler use, which results in lower cost and higher reliability [24]. In fact much of the cost savings in testing have been afforded by DFT techniques. Therefore the next section discusses the evolution of DFT standards and usage in detail.

### **2.3 Design for testability (DFT)**

In the semiconductor industry, testing is the process by which stimuli is applied to a circuit in order to demonstrate its correct operation [25]. Traditional testing of semiconductor devices can generally be divided into three broad categories [26]:

- i) Functional tests: these tests comprise of testing input/output pins on the device, its timing characteristics, proper logic handling, behavior, etc.

- Environmental testing: tests include operation characteristics under various power and temperature conditions.

- Reliability testing: these tests characterize a device's quality, reliability, life

expectancy, failure rates, etc.

Out of the above three categories, functional tests are the most involved as they are required to test the proper logic functioning of the device. Comprehensive functional tests should be able to verify the proper function of all components in a device. A typical modern semiconductor device can contain hundreds of millions of transistors and wires. Every one of these transistors and wires can contain defects that manifest themselves as incorrect opens or shorts. These defects can only be tested via device I/O pins, which there are only a few hundred of. Therefore there is a gap between the large number of on-chip components that need to be tested and the relatively small number of pins through which these test can be performed. This gap necessitates design modifications to improve accessibility from external pins to all internal logic. DFT addresses this problem and is the design of additional on-chip hardware to improve accessibility to internal logic. Improving accessibility is used as a generic term here, as DFT techniques can provide accessibility in a variety of ways from physically providing access to internal logic to generating tests on internal logic and providing access to results.

Modern trends in DFT techniques can be distinguished into three general roles [27]. The first role of DFT is to enable high-quality testing, through the use of additional internal modules designed on-chip. The second role is to provide access to embedded modules within a DUT. The third role is the on-chip generation of stimuli and/or the evaluation of test responses. These roles are discussed further below.

#### 2.3.1 Additional Module based DFT

This technique of DFT requires the inclusion of additional modules into devices to enable external testing. The most common methods of this style of DFT are scan-based designs which allow the access and control of device components connected to internal registers through scan chains. Various types of scans exist based on the depth of the testing required such as full serial scan, partial serial scan, non-serial san, and system level scan [28]. The most popular scan-based design is the Joint Test Action Group (JTAG) Boundary Scan Standard (IEEE Standard 1149.1) [29]. A serial scan architecture is shown in Figure 2.3.

Figure 2.3 Serial Scan Architecture

As shown in the figure, the architecture requires four additional pins. In the JTAG standard these signals are defined as Test Data In (TDI), Test Data Out (TDO), Test Clock (TCK) and Test Mode Select (TMS). Test data and instructions are sent through the TDI pin to internal registers in the device. Each register has certain test functions implemented in it, and the TMS pin is used to select these registers. Once tests are performed, results are sent back over the TDO pin. A clock input is required for the internal logic and provided through the TCK pin. The advantage of using the JTAG

standard is that is allows the scan of multiple circuits. For example a flash memory device connected to eight FPGAs can be scanned at once using this standard.

#### 2.3.2 Embedded Module Access based DFT

Complex devices can be composed of multiple logic modules. Testing these modules in a similar fashion, i.e. modular testing, is an efficient approach to testing as it reduces test generation time through reuse and concurrent engineering [27]. Modular testing requires an on-chip test infrastructure in the form of test wrappers and Test Access Mechanisms (TAMs) [30]. The test wrappers are used to provide access to the targeted module and the TAMs are used to transport data to and from external pins. Therefore, a small number of external pins can access a much larger number of internal signals, thus allowing testing to be performed using external test equipment. The IEEE describes a standard for test wrappers called the Standard for Embedded Core Test (SECT – IEEE Std. 1500) [31]. The standard is similar to the JTAG standard, however slightly different and allows for some customization. This makes SECT a better standard for use with various TAMs.

#### 2.3.3 Self-Test

Test stimuli and response evaluation has traditionally been performed by an external tester. As devices became more complex and access to embedded components became more difficult, external testers could not perform comprehensive testing. To solve this problem, internal test modules are designed onto the device itself in a technique called BIST. This technique was first applied to memory devices in the late 80s [32]. Additional on-chip circuitry is added on to devices that generate test stimuli and evaluate responses to verify operation.

BIST is generally of two types, online and offline. Online BIST is designed to function when a device is in normal operation, thus being able to detect errors in realtime. Offline BIST is designed to perform testing functions when the device is not in operation mode, such as on power up [28]. Both types of BIST require similar architecture. The main components of BIST are test pattern generators (TPGs) and output response analyzers (ORAs). A BIST controller component controls operation of the TPGs and reads output from the ORA to determine test results. These components can be built using registers and finite state machines.

The complexity of BIST depends on the amount of test patterns required and the number of circuits under test (CUTs). BIST has been an efficient method of DFT for the last 20 years [27]. Miniaturization of transistor features has allowed additional circuitry to be built into devices without much imposition on the devices performance. However as device complexity increased exponentially, employing BIST has become more challenging. Therefore in 1999, Credence Systems Corp. introduced the concept of built-off self-test (BOST) [33]. In this DFT technique, additional self-test circuitry is added to a device, but built off of the device such as on a load board, test fixture, etc. Typically a FPGA is used to control the test circuitry and generate test patterns. This technique permits tremendous flexibility, as it removes physical limitations of BIST. Furthermore, the use of high-performance FPGAs can develop elaborate, high-performance testing solutions.

The three techniques of DFT can be mixed according to testing needs to design optimal results. Using any form of DFT techniques does add additional costs to a semiconductor device. However there are definite economic benefits that justify the use of DFT [8]-[10]. Therefore most semiconductor manufactures employ some level of DFT. While DFT can do a variety of testing, it cannot replace all traditional required testing functions. Environmental and reliability testing still needs to be handled by an external tester. External functional testing can be reduced, but not eliminated by using DFT. For example at-speed tests and characterization may not be handled by DFT. Therefore DFT is often designed to complement the use of an ATE. This has led to the development of low-cost testers by ATE manufacturers [34]. These low-cost testers work adequately provided one is willing to rely on DFT to compensate for reduced tester capability. Although, this solution addresses the concerns of cost, it does not address the concerns of higher performance test requirements. By relying on DFT, a similar argument can be made to develop higher-performance test systems. The development of higher performance test systems is presented in the following chapters.

### **CHAPTER 3**

# MODULAR EXTENSION OF ATE TO MULTI-GHZ SPEEDS

Testing electronic devices has been challenging due to their exponential growth in complexity [3]. When next generation devices are developed, a test engineer may only have current generation technologies available for devising test strategies. For instance, when the first generation of GHz capable devices are developed, the only resources available to test may be limited to MHz speeds. In terms of clock and data speeds, this issue was first addressed in the 80s. During that era, standard ATE had testing capabilities up to 200 Mbps [35], however many GaAs devices and high-end application-specific integrated circuits (ASIC) were developed to operate above 1000 Mbps, thus creating a need for multi-GHz testing equipment. Therefore, the first substantial attempts to enable testing capabilities into the Gbps range were seen in the late 80s [35]-[43].

The need for high-speed testing has typically been limited to newer devices and ASICs. Furthermore, these devices may require high-speed testing limited to only a few pins. These new devices are often manufactured in smaller quantities. In the fast paced technology industry, new devices have a limited a "window of opportunity" in which to make an impact, thus requiring a shorter testing turnaround time. As such, purchasing an entire new test system is difficult to justify from a business point of view. Also developing a custom platform to test these devices is not feasible in order to take advantage of the window of opportunity. Taking these concerns into consideration, test engineers have developed solutions extending ATE resources. These solutions involved

developing test electronics that used ATE resources to produce higher-performance tests. In [36]-[40], high-speed ATE extension is demonstrated using custom design test heads. Although this approach is certainly a possibility, designing custom test heads for today's complex ATE systems is a more challenging task. Furthermore, developing custom test heads for specific ATE does not allow portability of the solution to other ATE systems. Building on this approach, [35] & [41]-[43] demonstrate extension of ATE through the development of modular electronic cards using similar principles. These modules are compatible with the existing ATE test head - through a device interface board (DIB) or similar interface; thus allowing portability to other ATE systems. Initial modular extensions developed for GHz speeds included drivers/receivers [35][41], pattern generators [42], clock distribution networks [43], and others. Essentially, these works laid the foundations of using modular electronics card to extend ATE performance.

In this chapter, a number of selected modular ATE extension methods pertinent to this research are presented. In the first section high-speed signal generation using driver and receiver modules is presented. The next section discusses loopback modules, followed by jitter manipulation modules. Modules capable of timing and skew control of high-speed signals are presented and finally high-speed signal switching modules presented.

### **3.1 High speed signal generation**

ATE systems may not have a single signal running in the multi-GHz range, however many have multiple signals running in the GHz range. It is not uncommon for an ATE to have 64 channels or more, each capable of producing up to 1Gbps. The sheer aggregate bandwidth of these signals can be awesome, however available only in parallel format. Harnessing a few of these signals into one high-speed signal using careful techniques is an approach to generating high-speed data. In this approach a large number of low-speed signals are taken from the ATE and interleaved or multiplexed into a smaller number of high-speed signals. Although not a trivial task by any means, this becomes especially challenging when attempting to generate multi-GHz speeds. For instance, the bit period of a 5Gbps is 200ps. This requires the ATE to maintain very tight timing accuracies across very long test sequences and over multiple channels. Further the electronics used to multiplex these signals must be capable of producing high-speeds without significantly distorting the signal by adding unwanted elements such as jitter, noise, etc.

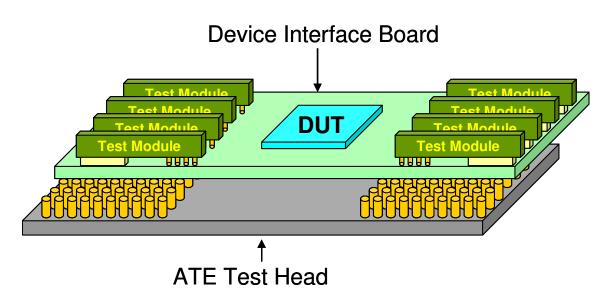

In [44] and [45], Keezer et al demonstrate the extension of ATE using test-support modules. The modules are designed to work with a DIB. The DIB is an interface between the test-support module and the ATE. DIBs are designed to fit a specific ATE test head. Since DIBs do not have any active components, they can be quickly designed for another test system, thus allowing a test extension module to be ported to another test system. Figure 3.1 illustrates how these test-support modules are used with the DIB. In this research, an Agilent 93000-P1000 ATE with about 900 channels was used.

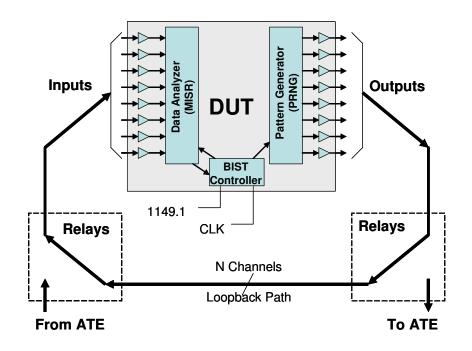

Figure 3.1. Top-level system view of modular extension approach to ATE[44]

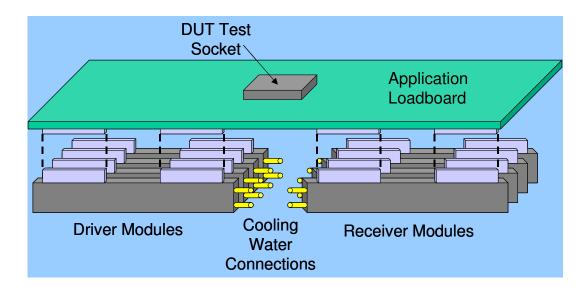

To generate and receive high-speed signals from existing ATE signals, typically a driver and receiver module is required. The driver module synthesizes low-speed signals from the ATE into high-speed signals through multiplexing using various logic and control functions from the ATE. These signals are delivered to the DUT. The receiver card performs the opposite function; it takes high-speed signals from the DUT and demultiplexes them into a larger number of slow speed signals which the ATE can handle. Depending on the application requirements, numerous driver and receiver modules can be used. However care must be taken to order to maintain tight timing accuracy across the ATE and the modules. For temperature stability, the driver and receiver modules have water-cooled plates sandwiched around them as shown in the figure.

A typical application test configuration is shown in Figure 3.2. A DUT may require several multi-GHz test signals. To produce these signals, several high-speed signals are synthesized by the driver modules from incoming low-speed ATE signals and delivered to the DUT. The DUT performs its designed function with the signals and produces output signals, which are also running at multi-GHz. These high-speed outputs from the DUT are then input into the receiver modules. Since the ATE is also not capable of receiving high-speed signals, the DUT output is de-multiplexed by the receiver module in multiple lower speed signals and relayed back to the ATE. This approach provides a low-cost solution to obtaining high-speed signals from an ATE using little or no external instrumentation. The benefits of this approach include flexibility, customization, and compatibility [44].

Figure 3.2 Typical application test configuration [44].

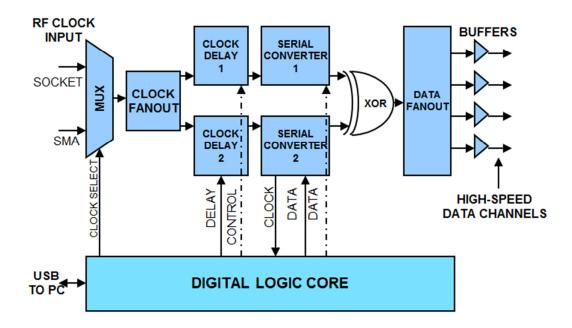

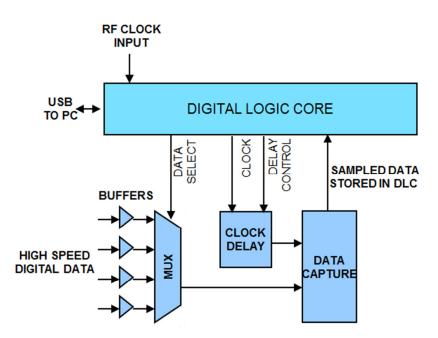

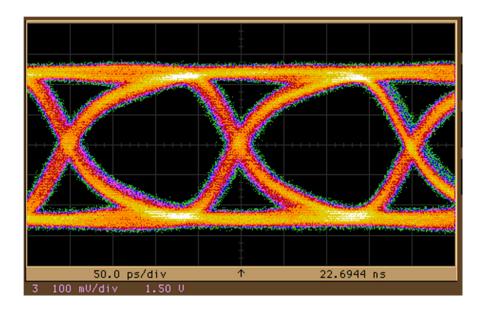

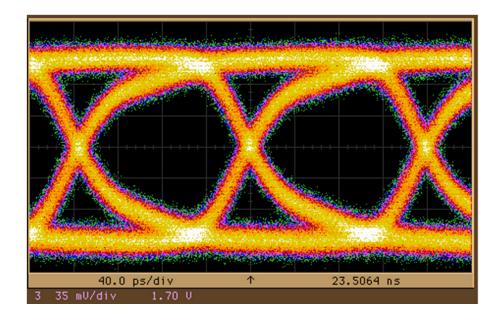

Basic driver and receiver modules are designed using multiplexing logic with additional ancillary logic devices. Figure 3.3 shows a logical overview of a basic driver. Multiple data channels from the ATE are supplied to multiplexing logic in the driver module. A multi-GHz clock is used as the select signal on the MUX and multiplexes the input signals into a higher-speed signal. The signal then passes through a buffer where it is re-clocked; and also allows for amplitude control. Relays are present on this driver module which allow for switching between high-speed and low speed signals (switching is discussed further in Section 3.5). Figure 3.4 shows a basic receiver module designed in a similar fashion. High-speed data from the DUT passes through relays and a buffer after which it enters de-multiplexing logic. Similar, but opposite to the driver module, a multi-GHz clock is used to de-multiplex the signals into multiple lower speed signals which can then be received by the ATE.