## Issues in the Design of Distributed Shared Memory Systems

A Thesis Presented to The Faculty of the Division of Graduate Studies

#### By

Ajay Mohindra

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Computer Science

Georgia Institute of Technology May 1993

Copyright © 1993 by Ajay Mohindra

## Issues in the Design of Distributed Shared Memory Systems

Approved:

Dr. Umakishore Ramachandran, Chairman

Dr. Mustaque Ahamad

Dr. Richard LeBlanc Jr.

Dr. Karsten Schwan

Dr. Murthy Devarakonda (IBM)

5/26/93 Date Approved by Chairman \_

## Acknowledgements

First, I would like thank Dr. Kishore Ramachandran for enduring me for the past six years, and seeing me through the Ph.D. program. Without his guidance, I may not have seen the end of the tunnel. I would also like to thank all the members of my reading committee, who provided guidance and constructive criticisms, and ensured that what I did was worthwhile. Thank you Dr. Richard LeBlanc Jr., Dr. Mustaque Ahamad, Dr. Karsten Schwan, and Dr. Murthy Devarakonda. I would also like to thank Dr. Sudhakar Yalamanchili and Dr. H. Venkateswaran for their advice and guidance.

Special thanks go to folks in the CLOUDS Lab who kept the lab alive. Thanks to Sathis Menon, Mark Pearson, Gautam Shah, Ranjit John, M. Chelliah, Vibby Gottemukkala, Sreenivas Gukal, L. Gunaseelan, and Ross D'Souza. I would also like to thank Dr. Martin Davis Jr. for being a good friend. Special thanks go to Deeptendu Majumder, with whom I checked out numerous ethnic restaurants, and movies during my stay at Georgia Tech.

My Ph.D. would not have been possible without the love and support of my parents; I dedicate my dissertation to them. I would also like to thank my brother Vivek, and my sister Deepali, for their "long distance" support. And last, but not the least, I would like to thank my wife Reena, for her support and understanding, and for providing me with motivation to graduate.

## Contents

| A          | Acknowledgements iii |                                 |    |  |  |

|------------|----------------------|---------------------------------|----|--|--|

| Li         | List of Tables viii  |                                 |    |  |  |

| Li         | List of Figures x    |                                 |    |  |  |

| Summary xi |                      |                                 |    |  |  |

| 1          | Intr                 | oduction                        | 1  |  |  |

| 2          | Issu                 | es in the design of DSM systems | 5  |  |  |

|            | 2.1                  | Virtual Memory and DSM          | 5  |  |  |

|            | 2.2                  | Granularity                     | 6  |  |  |

|            | 2.3                  | Memory Model                    | 8  |  |  |

|            | 2.4                  | Choice of Protocol              | 10 |  |  |

|            | 2.5                  | Synchronization                 | 13 |  |  |

|            | 2.6                  | Hardware Technology             | 14 |  |  |

| 3          | Rela                 | ated Work                       | 15 |  |  |

|            | 3.1                  | Apollo Domain                   | 15 |  |  |

|            | 3.2                  | Ivy                             | 17 |  |  |

|            | 3.3                  | CLOUDS                          | 20 |  |  |

|   | 3.4  | Mach and Agora                                      | 22 |

|---|------|-----------------------------------------------------|----|

|   | 3.5  | Memnet                                              | 24 |

|   | 3.6  | Choices                                             | 26 |

|   | 3.7  | Mether                                              | 27 |

|   | 3.8  | Munin                                               | 28 |

|   | 3.9  | Hardware assisted distributed shared memory systems | 29 |

|   | 3.10 | Discussion                                          | 31 |

|   | 3.11 | Other Work                                          | 35 |

| 4 | Dist | ributed Shared Memory in CLOUDS: A Case Study       | 38 |

|   | 4.1  | DSM Primitives                                      | 39 |

|   | 4.2  | Methodology                                         | 41 |

|   | 4.3  | Performance Measurements                            | 42 |

|   | 4.4  | Analysis                                            | 44 |

| 5 | Imp  | lementation and Analysis of Benchmarks              | 49 |

|   | 5.1  | System Architecture                                 | 50 |

|   | 5.2  | Embarrassingly Parallel Benchmark                   | 52 |

|   | 5.3  | Integer Sort Benchmark                              | 53 |

|   | 5.4  | Matrix Multiplication Benchmark                     | 58 |

|   | 5.5  | Conjugate Gradient Benchmark                        | 59 |

|   | 5.6  | SCAN Benchmark                                      | 61 |

|   | 5.7  | Traveling Salesman Problem                          | 63 |

| 6 | Sim  | ulation Studies                                     | 66 |

|   | 6.1  | Simulator $\ldots \ldots 6'$ | 7       |

|---|------|-------------------------------------------------------------------------------------------------------------------------|---------|

|   | 6.2  | The Workload Model                                                                                                      | 9       |

|   |      | 6.2.1 Structure of the Workload Model                                                                                   | 1       |

|   |      | 6.2.2 Domain Specific Models                                                                                            | 3       |

|   |      | 6.2.3 Validation of the Workload Model                                                                                  | 5       |

|   |      | 6.2.4 Parameters for the Simulation                                                                                     | )       |

|   | 6.3  | Simulation Results and Discussion                                                                                       | l       |

|   |      | 6.3.1 Transaction Model                                                                                                 | i.<br>L |

|   |      | 6.3.2 Iterative Model                                                                                                   | 5       |

|   |      | 6.3.3 Asynchronous Model                                                                                                | )       |

|   |      | 6.3.4 Hardware Technology                                                                                               | )       |

| 7 | Dise | cussion 96                                                                                                              | 5       |

|   | 7.1  | Virtual Memory and DSM                                                                                                  | ;       |

|   | 7.2  | Granularity                                                                                                             |         |

|   | 7.3  | Memory Model and Coherence Protocol                                                                                     | Ē       |

|   | 7.4  | Synchronization                                                                                                         | 1       |

|   | 7.5  | Hardware Technology                                                                                                     |         |

|   | 7.6  | Conclusions                                                                                                             | ł       |

| 8 | Con  | clusions and Future Work 115                                                                                            |         |

|   | 8.1  | Concluding Remarks                                                                                                      |         |

|   | 8.2  | Future Work                                                                                                             |         |

|   | -    |                                                                                                                         |         |

| Α | Inte | eger Sort and SCAN benchmarks 119                                                                                       | ٤.      |

|   | A.1                             | Integer Sort (version $\mathcal{V}1$ ) Benchmark                                                                                                                                                                                 | 9                |

|---|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|   |                                 | A.1.1 Source Listing of the Integer Sort Benchmark                                                                                                                                                                               | C                |

|   | A.2                             | SCAN Benchmark                                                                                                                                                                                                                   | 3                |

|   |                                 | A.2.1 Source Listing of the SCAN Benchmark                                                                                                                                                                                       | 7                |

| в | Des                             | ign and Implementation of Buffered Consistency based DSM                                                                                                                                                                         |                  |

|   | on                              | CLOUDS 132                                                                                                                                                                                                                       | 2                |

|   | B.1                             | The Buffered Consistency Memory Model                                                                                                                                                                                            | 2                |

|   | B.2                             | Implementation of BC-DSM on CLOUDS                                                                                                                                                                                               | 3                |

|   | B.3                             | Performance of BC-DSM on CLOUDS                                                                                                                                                                                                  | 5                |

|   |                                 |                                                                                                                                                                                                                                  |                  |

| С | Har                             | dware Support for Distributed Shared Memory 139                                                                                                                                                                                  | )                |

| С | <b>Har</b><br>C.1               | dware Support for Distributed Shared Memory139Hardware Design of the Controller Board140                                                                                                                                         |                  |

| C |                                 |                                                                                                                                                                                                                                  | )                |

| С | C.1                             | Hardware Design of the Controller Board                                                                                                                                                                                          | )                |

| С | C.1<br>C.2<br>C.3               | Hardware Design of the Controller Board                                                                                                                                                                                          | )<br>2<br>7      |

|   | C.1<br>C.2<br>C.3<br>C.4        | Hardware Design of the Controller Board                                                                                                                                                                                          | )<br>2<br>7      |

| D | C.1<br>C.2<br>C.3<br>C.4<br>Nur | Hardware Design of the Controller Board       140         Software Design for the Controller Board       142         Functional Description of the Controller       147         Expected Performance of the Controller       150 | )<br>2<br>7<br>) |

## List of Tables

| 1  | Comparison of DSM systems                                                 | 37 |

|----|---------------------------------------------------------------------------|----|

| 2  | Basic system timings on CLOUDS                                            | 44 |

| 3  | Basic system timings on CLOUDS (contd.)                                   | 45 |

| 4  | Basic system timings on CLOUDS (contd.)                                   | 46 |

| 5  | DSM timings on CLOUDS                                                     | 47 |

| 6  | Page-fault service times on CLOUDS                                        | 48 |

| 7  | Completion times and speedups for the Embarrassingly Parallel             |    |

|    | benchmark, $\mathcal{N} = 2^{16}$ iterations                              | 53 |

| 8  | Breakdown of times for the Integer Sort algorithm version $\mathcal{V}2.$ | 58 |

| 9  | Completion times and speedups for the Matrix Multiplication bench-        |    |

|    | mark for $\mathcal{N}=256$ rows                                           | 59 |

| 10 | Completion times and speedups for the Traveling Salesman Prob-            |    |

|    | lem, 11 city tour                                                         | 64 |

| 11 | List of parameters for domain specific workload models                    | 74 |

| 12 | List of parameters for the simulator along with the default values $\ .$  | 78 |

| 13 | Comparison of results obtained via simulation with actual measure-        |    |

|    | ments for the Integer Sort benchmark for $2^{18}$ elements                | 79 |

| 14 | Comparison of results obtained via simulation with actual measure-        |    |

|    | ments for the SCAN benchmark for 10000 records                            | 79 |

| 15 | List of alternatives evaluated using simulation                           | 79 |

|    |                                                                           |    |

| 16                         | Integrated vs Library: Comparison of the two approaches 98                                      |

|----------------------------|-------------------------------------------------------------------------------------------------|

| 17                         | Computation granularity requirements                                                            |

| 18                         | Classification of the applications based on the $CGRatio$ 100                                   |

| 19                         | Optimal value of page-size for different system configurations $102$                            |

| 20                         | Ranking of the three memory models                                                              |

| 21                         | Number of messages generated in the three coherence protocols $\therefore$ . 108                |

| 22                         | Scalability of the three coherence protocols without multi-cast $\ldots$ 109                    |

| 23                         | Characteristics of three types of DSM systems                                                   |

| 24                         | Number of nodes that can efficiently execute an application based                               |

|                            | on the CGRatio                                                                                  |

| 25                         | Approximate shared memory requirements for the integer sort bench-                              |

|                            | mark for $\mathcal{N}=2^{18}$ elements, Bmax = 2048, MAX_PROCS=6 120                            |

| 26                         | Number of references made by each task for the integer sort bench-                              |

|                            |                                                                                                 |

|                            | mark for $\mathcal{N} = 2^{18}$ elements, Bmax = 2048                                           |

| 27                         | mark for $\mathcal{N} = 2^{18}$ elements, Bmax = 2048                                           |

| 27                         |                                                                                                 |

| 27<br>28                   | Approximate shared memory requirements for the SCAN bench-                                      |

|                            | Approximate shared memory requirements for the SCAN bench-<br>mark for MAXRECORDS=10000 records |

| 28                         | Approximate shared memory requirements for the SCAN bench-<br>mark for MAXRECORDS=10000 records |

| 28<br>29                   | Approximate shared memory requirements for the SCAN bench-<br>mark for MAXRECORDS=10000 records |

| 28<br>29<br>30             | Approximate shared memory requirements for the SCAN bench-<br>mark for MAXRECORDS=10000 records |

| 28<br>29<br>30<br>31       | Approximate shared memory requirements for the SCAN bench-<br>mark for MAXRECORDS=10000 records |

| 28<br>29<br>30<br>31<br>32 | Approximate shared memory requirements for the SCAN bench-<br>mark for MAXRECORDS=10000 records |

# List of Figures

| 1  | Distributed Shared Memory Abstraction                                                                                          | <b>2</b> |

|----|--------------------------------------------------------------------------------------------------------------------------------|----------|

| 2  | Memnet Architecture                                                                                                            | 25       |

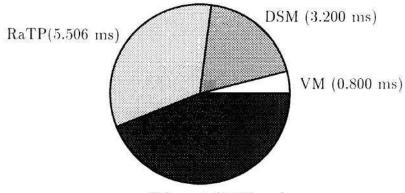

| 3  | Cost associated with each subsystem in servicing a DSM page-fault.                                                             |          |

|    | $Total = 16.3 ms \dots $ | 44       |

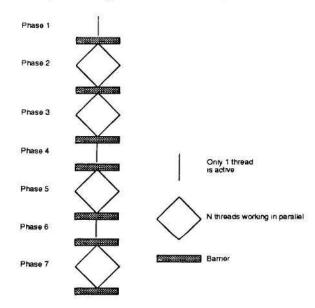

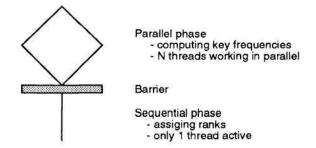

| 4  | High level structure of the Integer sort benchmark, Version $\mathcal{V}1$                                                     | 56       |

| 5  | High level structure of the Integer sort benchmark, Version $\mathcal{V}2$                                                     | 56       |

| 6  | Completion times for the Integer Sort benchmark, Version $\mathcal{V}1, \mathcal{N}=$                                          |          |

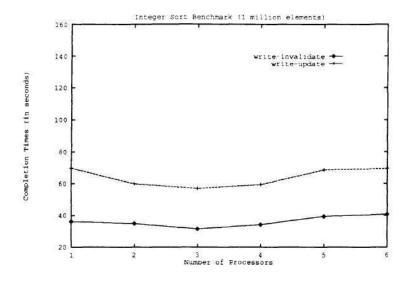

|    | 2 <sup>20</sup> keys                                                                                                           | 57       |

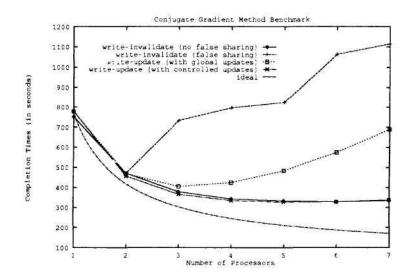

| 7  | Completion times for the Conjugate Gradient benchmark                                                                          | 61       |

| 8  | Pseudo code for the SCAN benchmark                                                                                             | 62       |

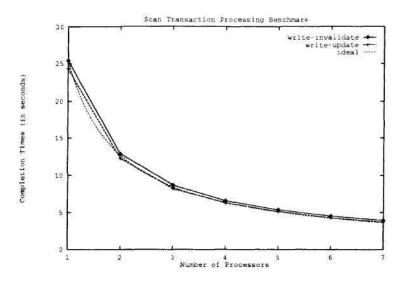

| 9  | Completion times for the SCAN benchmark                                                                                        | 63       |

| 10 | Conceptual picture of the simulator                                                                                            | 68       |

| 11 | Reference parameters within a task                                                                                             | 73       |

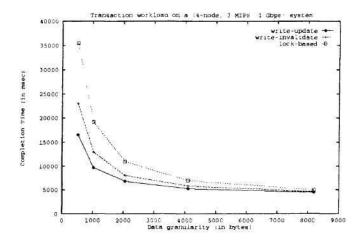

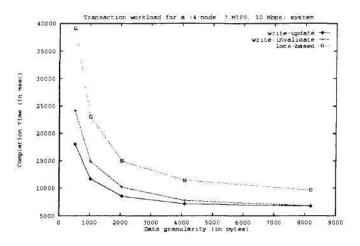

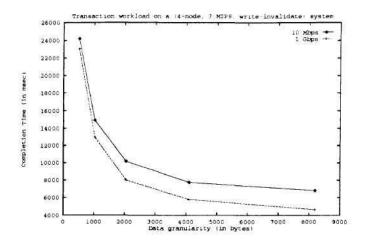

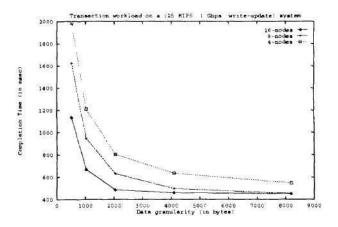

| 12 | Transaction workload model's performance on 4 nodes on fiber                                                                   | 82       |

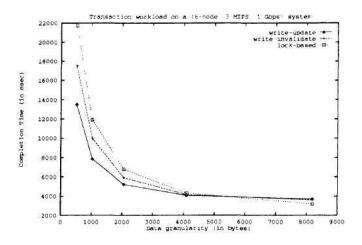

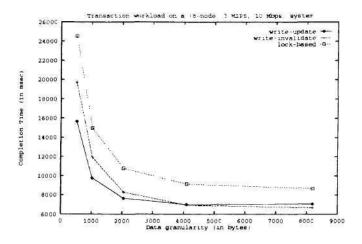

| 13 | Transaction workload model's performance on 8 nodes on fiber                                                                   | 83       |

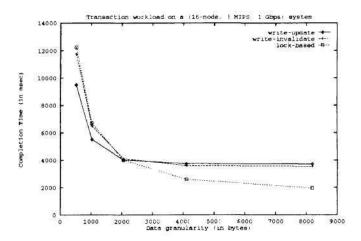

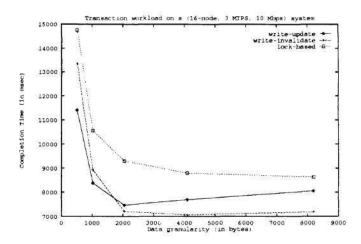

| 14 | Transaction workload model's performance on 16 nodes on fiber $\ . \ .$                                                        | 83       |

| 15 | Transaction workload model's performance on 4 nodes on Ethernet                                                                | 85       |

| 16 | Transaction workload model's performance on 8 nodes on Ethernet                                                                | 86       |

| 17 | Transaction workload model's performance on 16 nodes on Ethernet                                                               | 86       |

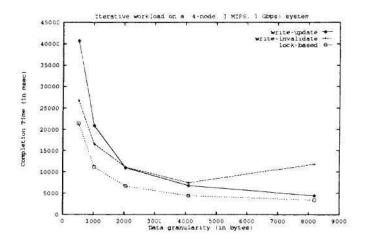

| 18 | Iterative workload model's performance on 4 nodes on fiber                                                                     | 87       |

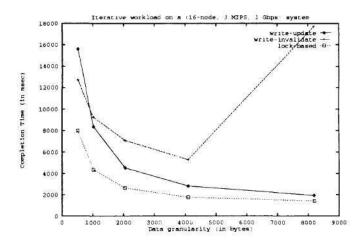

| 19 | Iterative workload model's performance on 16 nodes on fiber $87$             |

|----|------------------------------------------------------------------------------|

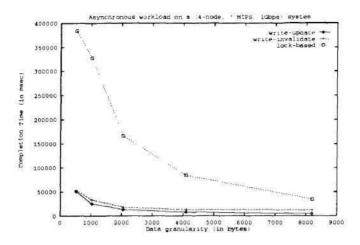

| 20 | Asynchronous workload model's performance on 4 nodes on fiber $90$           |

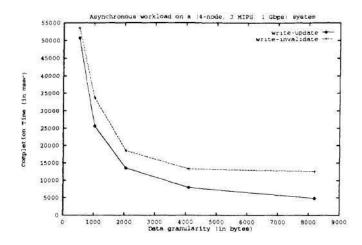

| 21 | Asynchronous workload model's performance on 4 nodes on fiber.               |

|    | Comparing write-update and write-invalidate                                  |

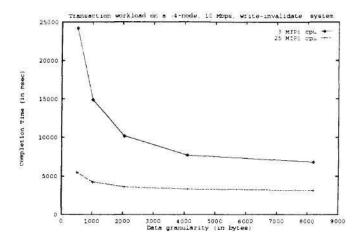

| 22 | Effect of processor speed on performance                                     |

| 23 | Effect of communication speed on performance                                 |

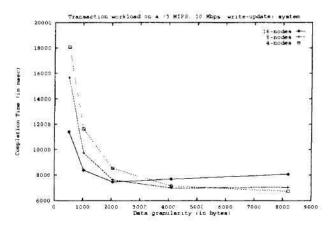

| 24 | System scalability with 3 MIPS CPU and 10 Mbps network 94                    |

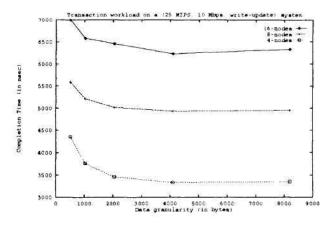

| 25 | System scalability with 25 MIPS CPU and 10 Mbps network 94 $$                |

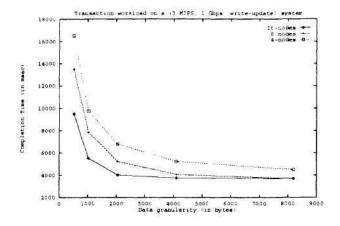

| 26 | System scalability with 3 MIPS CPU and 1 Gbps network $\ldots$ 95            |

| 27 | System scalability with 25 MIPS CPU and 1 Gbps network 95 $$                 |

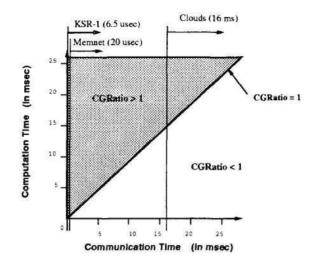

| 28 | Computation to communication ratio requirements                              |

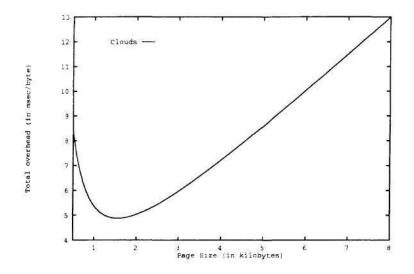

| 29 | Total overhead per byte for DSM on CLOUDS                                    |

| 30 | Structure of the <i>dtable</i> entry                                         |

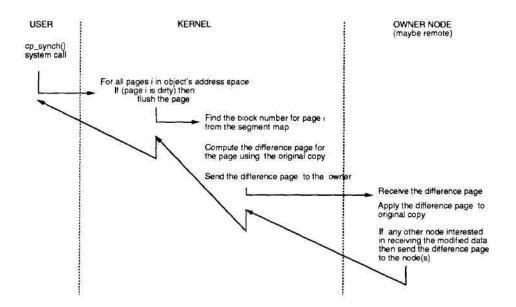

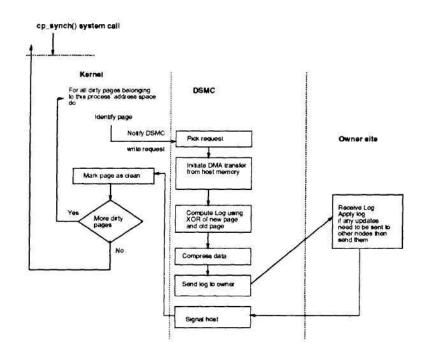

| 31 | Flow of control for the cp_synch() system call                               |

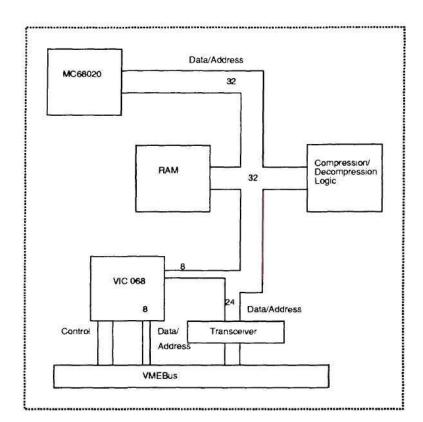

| 32 | Layout of the DSMC coprocessor board                                         |

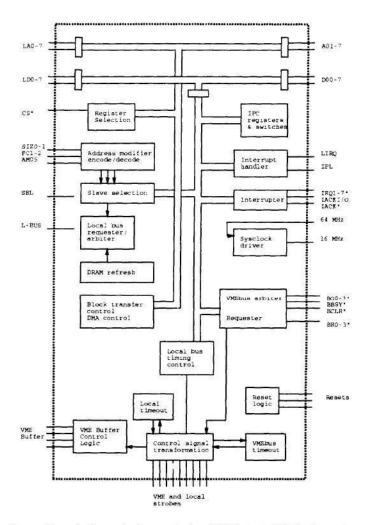

| 33 | Functional description of the VIC 068 VME bus interface chip $\ . \ . \ 142$ |

| 34 | Structure of a buffer entry                                                  |

| 35 | Structure of a state table entry                                             |

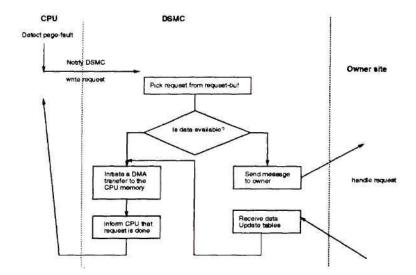

| 36 | Page-fault servicing by the controller                                       |

| 37 | Schematic of DSMC actions subsequent to a cp_synch() system call 153         |

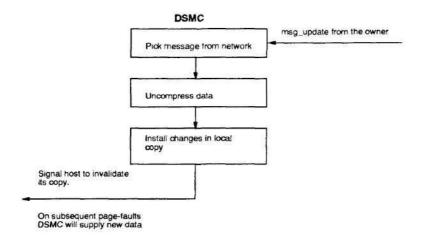

| 38 | Schematic of DSMC actions subsequent to the receipt of a msg_update          |

|    | message                                                                      |

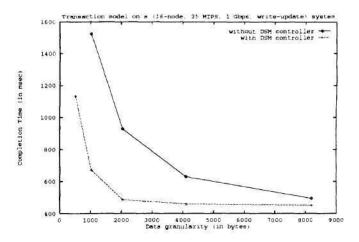

| 39 | Effect of using a DSM controller on the performance                          |

### Summary

This thesis examines the various system issues that arise in the design of distributed shared memory (DSM) systems. This work has been motivated by the observation that distributed systems will continue to become popular, and will be increasingly used for solving large computational problems. To this effect, shared memory paradigm is attractive for programming large distributed systems because it offers a natural transition for a programmer from the world of uniprocessors. The goal of this work is to identify a set of system issues, such as integration of DSM with virtual memory management, choice of memory model, choice of coherence protocol, and technology factors; and evaluate the effects of the design alternatives on the performance of DSM systems. The specific question that we are trying to answer is, "Can we determine a set of system design parameters that defines an efficient realization of a distributed shared memory system?". The design alternatives have been evaluated in three steps. First, we do a detailed performance study of a distributed shared memory implementation on the CLOUDS<sup>1</sup> distributed operating system. Second, we implement and analyze the performance of several applications on a distributed shared memory system. Third, the system issues that could not be evaluated via the experimental study, are evaluated using a simulation-based approach. The simulation model is developed from our experience with the CLOUDS distributed system. A new workload model that captures the salient features of

<sup>&</sup>lt;sup>1</sup>CLOUDS is a distributed object-based operating system developed at Georgia Tech.

parallel and distributed programs is developed and used to drive the simulator. The key results of the thesis are: DSM mechanisms have to be integrated with the virtual memory management for providing high performance distributed shared memory systems; the choice of the memory model and coherence protocol does not significantly influence the system performance for applications exhibiting high computation granularity and low state-sharing; and an efficient implementation of DSM requires a careful design of miscellaneous system services (such as synchronization and data servers). The thesis also enumerates several questions related to future research directions.

۰.

## Chapter 1

## Introduction

Technological advances in recent years have spurred a trend towards workstationoriented computing environments. Each workstation has computing power comparable to the mini-mainframes of the past. Availability of powerful computers connected via local (wide) area network has sparked interest in the area of distributed computing systems. Current research is targeting its efforts in utilizing the available computation power on the network in solving large problems through co-operative computing.

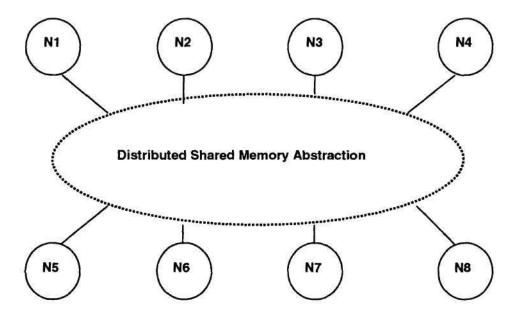

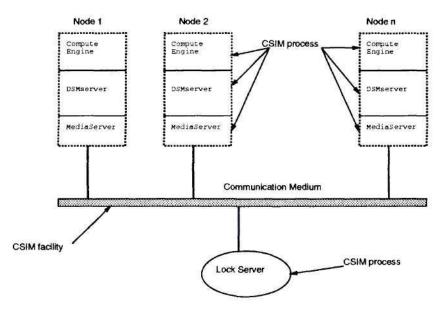

To facilitate programming of distributed systems, two basic paradigms exist: shared memory, and message-passing. These two paradigms have been used for interprocess communication and synchronization in multi-process computations. The duality between the two paradigms for structuring computations is well-known [21]. Nevertheless, shared memory has been an appealing paradigm from the point of view programming ease even in distributed systems. It is no surprise that several researchers [28, 30, 17, 7] have proposed system architectures that provide the abstraction of shared memory in a physically non-shared (distributed) architecture. We refer to this abstraction as *Distributed Shared Memory* (DSM). Figure 1 shows the conceptual representation of a distributed shared memory system. In the system, a set of nodes (computers) are connected via an interconnection network, and do not physically share memory. The DSM mechanisms allow an application to access shared data not physically resident at that node. These mechanisms are usually provided as a software layer either integrated with or on top of the operating system.

Figure 1: Distributed Shared Memory Abstraction

Another motivation for DSM arises from the structure of current distributed computing environments. A typical distributed computing environment consists of *compute servers*<sup>1</sup> and *data servers*<sup>2</sup> interconnected by a local area network. In such an environment, there are two tasks to be performed to execute a computation. The first task involves selecting a compute server, and the second task involves bringing the code and data from the data server to the selected compute server before executing the computation. The second task requires a remote paging facility. If

<sup>&</sup>lt;sup>1</sup>Nodes where computation is performed.

<sup>&</sup>lt;sup>2</sup>Nodes that serve as repositories for data.

sharing of data is coupled with this remote paging, it could be seen that DSM presents itself as a natural facility for combining the two.

Previous work in the area of distributed shared memory, as will be elaborated in Chapter 3, has been concerned with the design and implementation of distributed shared systems, and evaluation of algorithms for enforcing coherence of shared data. Some researchers have also focussed their efforts on designing fault-tolerant algorithms for distributed shared memory systems. Previous work, however, has ignored the study of system issues that need to be addressed in the design of distributed shared memory systems. The specific question that the research is trying to answer is:

"Can we determine a set of system design parameters that defines an efficient realization of a distributed shared memory system?".

In this thesis, we identify and evaluate the system issues (see Chapter 2) that need to be addressed for designing distributed shared memory systems. The issues relate to questions such as, whether to integrate DSM with virtual memory management, what type of memory model to provide, which coherence protocol to use for maintaining coherence of shared data, and what kind of impact do technology factors have on the DSM system performance. We evaluate these issues with respect to the available design alternatives. The evaluation is done in three steps. First, we do a performance study of an implementation of DSM (see Chapter 4). The performance study has provided us with an insight into the functioning of a distributed shared memory system. Second, we have implemented and studied the performance of several applications on a distributed shared memory system

(see Chapter 5). Finally, aspects of the study that could not be evaluated via experimental studies are evaluated using simulation. In Chapter 6, we describe the design of a simulator that models a distributed shared memory system. The costs obtained from the performance study are used to assign costs to different components of the simulator. A new workload model is developed and used to drive the simulator. The workload model captures the salient features of distributed and parallel programs. In Chapter 7, we discuss the results of the research. The conclusions and contributions of the research are presented in Chapter 8.

The key contribution of this thesis is that it enumerates the systems issues and specifies the design parameters for addressing system issues for an efficient realization of a DSM system. The key results of the thesis are: DSM mechanisms have to be integrated with the virtual memory management for providing high performance distributed shared memory systems; the choice of the memory model and coherence protocol does not significantly influence the system performance for applications exhibiting high computation granularity and low state-sharing; and an efficient implementation of DSM requires a careful design of miscellaneous system services (such as synchronization and data servers).

## Chapter 2

## Issues in the design of DSM systems

As mentioned in Chapter 1, a designer needs to address several system issues during the design of a distributed shared memory system. These issues form the core of a DSM system design, and choice of solutions to these issues can significantly influence the overall system performance. In this chapter, we enumerate these issues and discuss the alternatives available for addressing these issues.

### 2.1 Virtual Memory and DSM

DSM is not true shared memory as is the case in shared memory multiprocessors (SMM). Thus remote memory accesses have to be reconciled with the memory management at each node. Of course, if the basic machine architecture does not support virtual memory then the solution could perhaps be simpler. However, if the basic architecture supports virtual memory then the DSM management and Virtual Memory (VM) management have to be integrated. In particular, the local memory at each node may be considered simply a cache of a global address space that spans the entire network. The DSM and VM management at each node would have to cooperate to ensure that the semantics implemented by the DSM manager and the VM manager are not compromised. The normal VM chores such

as page replacement, swapping, and flushing have to be done in consideration with the DSM algorithms. Similarly, in satisfying a remote memory request, the DSM would have to consult the VM manager to get a page frame, etc. Upon release of a page, the DSM has to instruct the VM manager to invalidate page table entries and take other related actions.

The effectiveness of the DSM paradigm depends crucially on how quickly a remote memory access request is serviced, and the computation is allowed to continue, which in turn depends on several factors:

- the speed at which the VM system detects that a memory access fault (i.e. a page-fault) or a pre-fetching request entails a remote access

- the software overhead involved in the DSM protocol (i.e. coherence mechanism) for servicing a remote memory access request

- the software overhead involved in the communication subsystem (i.e. the basic transport protocol) for effecting the inter-node message communication to service the request

- the speed of the communication medium (i.e. hardware).

#### 2.2 Granularity

There are two dimensions to granularity: computation granularity and data granularity. The former deals with the amount of computation a process has to do between synchronization or communication points in a multi-process computation. The latter deals with the amount of shared information processed during this computation phase.

Eggers and Katz [14] define "write-run" as a sequence of reads and writes by a given processor following an initial write executed by the same processor to a given shared memory location before an external read by a different processor to that shared memory location occurs. In a shared memory multiprocessor system, write-runs of representative applications may range from a few to a few tens of references. However, in a DSM system, write-runs of a few hundred instructions would be more appropriate given the latency for remote accesses.

Another distinction between the SMM and the DSM is in the data granularities of accesses that are practical in the two. In a uniprocessor memory hierarchy, the processor-to-cache transfer time is in the tens of nanoseconds, the cache-to-main memory transfer time is in the hundreds of nanoseconds, and the main memory-to-disk transfer time is in the order of milliseconds. Correspondingly, the granularity of transfer that makes feasible sense are: byte or word between the processor and the cache, a block of several bytes between the main memory and the cache, and a page ranging from 512 bytes to a several kilobytes between the main memory and the disk. DSM systems add a new dimension to the memory hierarchy, namely remote memory access across the network. The choice of the network plays a big role in determining the latency. Nevertheless, independent of this choice, there is a fixed software overhead to be incurred depending on the choice of the data transfer protocol on the network. Moreover, such remote memory accesses need to be integrated somehow with the memory management at each node. This requirement often forces the granularity of access to be an integral multiple of the fundamental unit of memory management (usually a page). However,

it is possible to reduce the network latency by transferring the page partially. The key point to note is that the data granularity has to be sufficiently high to make the DSM paradigm viable.

#### 2.3 Memory Model

In a uniprocessor, correctness of execution is ensured by preserving the order of memory references generated by a processor. Lamport [20] has proposed *sequential consistency* as a memory model for ordering shared memory accesses to ensure correct multiprocessor execution. In this model, the order of memory references generated by an individual processor is preserved, while the global order of memory references from all the processors is an arbitrary interleaving of the individual processors' reference streams that preserves the order of references emanating from each processor. Essentially, sequential consistency ensures that the view of the memory is consistent at all times from all the processors.

Insofar as correctness of multiprocessor execution is concerned, only the ordering of the shared memory references is of interest. Shared memory accesses may be categorized into three types:

- shared code,

- synchronization variables, and

- shared data variables.

Shared code is always read-only, and hence is always consistent. On the other hand, synchronization variables require that memory consistency be strictly

preserved. Shared data variables normally require strict consistency as well. However, several applications exist wherein the program correctness would not be compromised even if there are temporary inconsistencies in the view of the shared memory as seen by distinct processes. Examples of such applications include asynchronous and iterative algorithms. Moreover, if the programs are written to obey some synchronization paradigm such as lock/unlock, and semaphore P/V, then ensuring a consistent view of shared data may be deferred to synchronization points in the program without compromising program correctness. Thus, sequential consistency is an overly restrictive memory model. This fact was first observed by Dubois, Scheurich and Briggs [13], who proposed weak ordering as an alternative to sequential consistency. Weak ordering requires that memory accesses from a process are performed in program order; synchronization operations are globally performed before allowing a process to continue; and all shared data accesses from a process are globally performed before issuing a synchronization operation. Several weaker memory models have been proposed. One such memory model is the causal memory model [1]. This model is based on the notion of causality [20], which is the fundamental event ordering mechanism in distributed systems. Similar to a message-passing system, the causal order is used to relate operations based on the program (local) order at processes and a reads-from order that is established between a write and its subsequent reads. This is similar to the happens-before relation defined in message-passing systems between an operation that sends a message and the operation that receives it. The causal memory model only guarantees that read operations do not return *causally overwritten* values. Another

memory model weakens the ordering constraints by distinguishing between synchronization operations that acquire and release rights to access shared data [25]. Of course, all such weakening of the memory model assumes that it is possible to distinguish between two types of memory accesses: synchronization and read-write data. If such a distinction cannot be made then a conservative approach (such as sequential consistency) may be the only way to assure program correctness. Recently, there have been proposals for hardware support to make this distinction possible in SMMs [23, 33, 18]. DSM, on the other hand, is usually a software abstraction. Therefore, it is quite straightforward (with support from the compiler and/or operating system) to make this distinction possible and weaken the memory model.

#### 2.4 Choice of Protocol

DSM assumes that all memory is globally shared. This assumption requires that independent computations started at different nodes see a consistent view of the shared memory. To facilitate this view would require a coherence scheme. Consistency maintenance of distributed shared memory is similar to cache coherence in multiprocessors. Shared memory multiprocessors such as Encore's Multimax, consist of several processors connected to a common shared memory via a system bus. A main memory cache is associated with each processor to help reduce the traffic to the shared memory. Multiprocessor cache consistency protocols ensure the following memory coherence constraint: a read operation performed by a processor returns the most recent value written into that location (by any processor). This criterion is appropriate in a shared memory multiprocessor since the system bus (a broadcast medium) serializes the memory operations of all the processors. The cache coherence algorithms that have been proposed for multiprocessors are viable since the cost (measured in circuit complexity as well as time) of implementing them in hardware is a small fraction of the total system cost. Further, bus-based multiprocessors usually have the ability to invalidate (or update) all cached copies in one atomic bus cycle.

It is possible to devise distributed versions of cache coherence protocols to maintain the consistency of distributed shared memory. However, such implementations would suffer to some degree due to the mismatch in the capabilities of their intended environments and distributed systems. The definition of coherence that works well for shared memory multiprocessors is not appropriate in a distributed environment since there is no "system bus" to impose a total order on the memory operations that are performed by all the processors. Further, while invalidation of cached copies of data is a viable approach in multiprocessors (with a system bus) it is expensive in a distributed system due to the cost of the invalidation messages. Invalidation involves at least sending a multi-cast message to all the nodes that have a read-copy of the data. Achieving reliable delivery of such multi-cast messages is expensive in a distributed system.

In reality, memory coherence and process synchronization are closely intertwined. A process acquires permission to read or write shared data invariably through some synchronization method. Absence of synchronization implies that any arbitrary ordering of simultaneous accesses to a shared location should yield valid results for a given computation. Therefore, in such cases there is no coherence requirement. In fact, it would be reasonable to argue that memory coherence should be defined in conjunction with process synchronization.

Not surprisingly, the solutions that have been suggested in the DSM environment are similar to the ones in the SMM caches. Broadly, these solutions may be classified into three categories:

- 1. Write-invalidate policy: In this protocol the writer acquires exclusive ownership by invalidating all copies before performing the write.

- 2. Lock-based policy: In this protocol lock requests (exclusive and shared) result in the data associated with the lock being sent to the requester along with the granting of the lock. Upon release of a lock, the associated data is sent back (if modified) to the server. Reads or writes to shared data without explicit locking follow single-copy semantics that does not allow multiple-readers or writers. A weaker form of read allows multiple-readers to shared data (without locking) but does not guarantee consistency.

- 3. Write-update policy: This protocol differentiates between two types of accesses: normal read/write and synchronization. Writes to shared data are buffered and consistency is enforced at synchronization points.

These three categories of cache protocols may be likened to deadlock prevention in an operating system, in that they prevent memory consistency violations from ever happening. It is possible to take a more liberal approach (similar to deadlock detection) and allow memory consistency violations to occur but have mechanisms in the system to detect such violations and take corrective action when they occur (see section 3.1).

In distributed systems, the number of messages is a measure of protocol performance. From this standpoint, the lock-based policy is expected to out-perform the other two, since coherence is maintained commensurate with the semantics of sharing in the computation. Moreover, since locking could be integrated with the data transfer, there is no need for any additional mechanisms for providing mutual exclusion for shared write accesses. In both write-update and write-invalidate policies there is a need to provide synchronization mechanisms on top of the coherence policy to assure mutual exclusion for multiple nodes requesting to write to the same page. However, lock-based policy has its drawbacks: In particular it does not have the generality of the other two policies. By decoupling memory coherence and synchronization, it is possible to devise synchronization mechanisms independent of the coherence policy. The lock-based policy requires explicit directives from the system software to know the semantics of sharing, while the other two do not require any such directives.

#### 2.5 Synchronization

Another issue is the way interprocess synchronization is achieved in such systems. Extending the analogy of shared memory multiprocessors to DSM, it would seem that shared-memory style of synchronization would be expected in DSM systems as well. However, the granularity of accesses in DSM systems precludes using true shared memory style of synchronization such as Test-and-Set on arbitrary memory locations. One possibility is to combine synchronization with sharing as has been suggested in some multiprocessor cache protocols [23]. Another possibility is to have an orthogonal set of primitives to achieve synchronization. This latter approach is attractive since there could be situations where there may be very little sharing of data but independent computation may have to synchronize with one another. For example, in compute-intensive applications, such as the embarrassingly parallel kernel and matrix multiplication, interprocess synchronization is used only to indicate completion of computation. Some systems provide semaphore operations or lock operations in addition to the shared memory primitives.

#### 2.6 Hardware Technology

There are two sources of overhead in a DSM system: the first is the communication overhead associated with the data transfer on the communication medium; and the second is the computational overhead associated with servicing remote memory requests. The choice of the communication medium (Ethernet, optical fiber, etc.) directly impacts the former, while the speed of the processor and any additional hardware support for DSM affects the latter.

In this chapter, we enumerated a set of issues that need to be addressed in the design of a distributed shared memory system. These issues form the basis of the work described in this thesis. In the next chapter, we present the work that has been previously done in the area of distributed shared memory.

## Chapter 3

### **Related Work**

Over the past decade, several systems have been developed and implemented that provide a shared memory abstraction in a physically distributed environment. However, the emphasis of the research has been restricted to the design, analysis, and implementation of algorithms for maintaining coherence of shared data. Some research has also been done to investigate the issues in providing reliable and recoverable distributed shared memory. In this chapter, we briefly summarize the work that has been done in the area of distributed shared memory, and qualitatively discuss these systems with respect to the issues outlined in chapter 2.

#### 3.1 Apollo Domain

Apollo Domain [22] system is one of the earliest systems that employs DSM paradigm to assure consistency of shared objects in a local area network of personal workstations and data servers. It provides an integrated distributed environment with each node possessing a high degree of autonomy with additional system mechanisms that permit cooperation and sharing among the nodes. The Domain system allows users to name and access all objects in a transparent manner by having a distributed object storage system (OSS). The OSS is a flat address space of objects addressed by unique identifiers (UID's). The distributed OSS allows objects to be accessed from any node in the network. Processes could potentially access all objects by presenting their UID's and mapping the object into their respective address spaces.

The OSS is implemented in two layers. The first layer provides access to local objects that reside on the same node as the faulting process. The second layer provides access to remote objects in a transparent manner. On a page-fault, the OSS determines if the access is to a local object. If so then the object is read from the local disk and mapped into the process' address space. If the object is not locally available then it is located using an object locating service. After the object is located, the specific page is requested and mapped into the process' address space.

To assure consistency of replicated copies of an object a two-level approach is adopted. The lower level detects concurrency violations using a time-stamp based version number scheme for each object. The time-stamp corresponds to the time the object was last modified. Every node remembers the version number for all remote objects whose pages it has encached in its main memory. Every time an object is read from another node, its version number is returned with it. If it is the only page of the object encached in this node, its version number is remembered. If not, the returned version number must match the remembered version number for the object; otherwise a read concurrency violation has occurred. Every time a page of an object is written back to its home node, the current version number is sent with the write request and an updated version number is returned. The home node only accepts the page if the write occurs on a current version of the page; otherwise a write concurrency violation has occurred. A write request to a page updates both the home node's and the requesting node's time stamp for the object. The system also provides primitives to flush stale pages of cached object, inquiring current version number of an object, and sending back modified pages of a cached object.

The higher level provides an object locking mechanism. Several types of lock modes are provided including a multiple-readers/single-writer lock. Lock and unlock requests for remote objects are always sent to the home node. A lock request that is granted returns the current version number of the lock. This information is used to remove stale pages from the requesting node's main memory. The unlock operation forces modified pages back to the home node before the lock is released. In Domain, lock requests are not enqueued; if the lock is currently in use, then the requester is denied access to the lock and would have to retry later.

#### 3.2 Ivy

Ivy [28] is a distributed shared memory system implemented on Apollo workstations interconnected by a token-ring network. It provides a shared virtual address space similar in concept to the Domain system with the difference that the granularity of access is a physical page in Ivy as opposed to an object in Domain.

In Ivy, a process address space is divided into two parts: a private part and a shared part. The private part is local to a process and cannot be accessed by any other process. The shared part is implemented using shared virtual memory. A process may access any memory location of the shared virtual memory through the shared part of its address space. To manage the shared virtual memory, each node has a memory mapping manager. The memory mapping manager implements the mapping between the physical memory of the processor and the shared virtual memory address space. The memory mapping manager at each node treats the physical memory as a cache for the shared virtual memory, and is responsible for maintaining the shared virtual memory coherent at all times. The shared virtual memory is implemented at the processor-level: Thus, once a page of the shared virtual memory is made available at a node by its memory mapping manager, it becomes accessible to all processes that execute at this node.

Ivy uses a write-invalidate type of coherence protocol to manage its shared virtual memory. The virtual memory is partitioned into pages. Individual pages can exist in read-only, write, or nil mode. Ivy uses multiple-readers/single-writer memory semantics. In this approach, all read-only copies of a page are invalidated when any processor attempts to write to the page. Three different flavors of the invalidation scheme have been implemented in Ivy. In the central scheme, a central manager maintains a table to keep track of the locations for all the pages. On a page-fault, the faulting processor asks the central manager for a copy of the page. The central manager then asks the *owner* of the page to send a copy of the page to the faulting processor. A node is said to be the owner of a page if it was the last node that modified the page. The second approach, fixed distribution scheme, is similar to the centralized scheme except that each node is assigned a pre-determined set of pages to manage. A mapping function is used to perform this distribution. This scheme avoids the single site bottleneck of the centralized scheme. The third scheme is the dynamic distributed manager algorithm that keeps track of the ownership for all the pages. This is done by adding a field called *probOwner* in each page table entry at all the processors. The probOwner field is used as a hint to locate the true owner of a page. A processor sends the request for a page to the node indicated in the probOwner field of the page. If the node that receives the page request is not the current owner of the page, it forwards the request to the node indicated in its page table. Initially, the probOwner field is set to some default value in all the processors. The probOwner field is updated whenever a processor receives an invalidation request, a processor relinquishes the ownership of a page on a read or write page-fault, or a processor forwards the page-fault request to another node.

On a read page-fault, the processor locates the owner of a page and sends a request to the owner of the page. The owner maintains a set of all nodes that have a read-only copy of the page in a *copyset*. The owner adds the faulting processor to the copyset of the page and sends a copy of the page to the faulting processor. On a write page-fault, the processor locates the owner of the page and sends a request to the owner of the page. The owner of the page sends the page and its copyset to the faulting processor. The faulting processor sends an invalidation message to all the processors in the copyset of the page. When all the invalidation requests have been acknowledged, the faulting processor restarts the blocked process.

Ivy provides synchronization mechanisms based on the primitives (eventcounts) provided by the underlying operating system. An event-count supports four operations: *init*(count), *read*(count), *await*(count, value), and *advance*(count). Init primitive initializes an event-count. Read primitive returns the value of the event-count. Await primitive suspends the calling process until the event-count value reaches a specified value. Advance primitive increments the value of the event-count by one and wakes up any sleeping processes. Any process may use an event-count after the event-count has been initialized.

An extension of Ivy's memory coherence protocol has been implemented in the Mirage system at UCLA [17]. It allows a reader or a writer of a page to retain access to the page for a fixed duration of time regardless of the pending requests. This is done to guarantee forward progress of the computation by reducing thrashing of heavily shared data pages.

#### 3.3 CLOUDS

CLOUDS [9] is a distributed operating system developed at Georgia Tech. One of the distinctive features of CLOUDS is its separation of two notions that have been traditionally inter-twined in most operating systems, namely, address space and computation. The former is specified by objects and the latter by threads in CLOUDS. An object is a passive entity (i.e. there is no process associated with it) that is part of a global name space. It specifies a distinct virtual space that is unique in the entire distributed system. The object encapsulates data that can be manipulated only from within the object. There are *entry points* in the object that are invocable from other objects. The entry points contain code for manipulating the data in the object, and may themselves invoke entry points in other objects. To allow concurrent execution of more than one computation in the same object, shared-memory style synchronization primitives are provided by the operating system.

A thread is an active entity that provides the notion of a computation. It executes in the context of an object. During the course of execution. a thread may invoke entry points in other objects. Thus, a thread is not associated with a single address space. Further, since these objects may not all be at the same node, a thread may span machine boundaries during the course of execution.

The collection of objects in CLOUDS represents a distributed shared virtual space. A thread traverses the address spaces of the objects that it invokes during its execution. Objects are composed of segments that form the basic unit of sharing. Each segment may be composed of one or more pages. Pages are the units of distribution. There is an entity, Distributed Shared Memory Controller (DSMC) [30] at each node that owns and maintains the segments that are created in the node. The DSMC provides a set of primitives for segment access and transport, and is responsible for preserving the consistency of the segments that it owns. DSMC uses a lock-based protocol for coherence maintenance that unifies synchronization and transport of data. It supports both exclusive (readwrite) locks as well as shared (read-only) locks for segment access. Upon a lock request, the owner DSMC encloses the requested segment (parts thereof) in the message that grants the lock request, thus providing synchronization for free. A segment may be requested by a thread in one of the four modes: read-only, readwrite, weak-read, and none. Read-only mode provides a non-exclusive lock on the segment while read-write mode provides an exclusive lock on the segment. Mode none gives exclusive access to the segment without locking the segment, i.e., any new request would result in the segment being yanked away to service the request.

These three modes provide sequentially consistent memory semantics for the nodes accessing the segments. However, there are situations where such strong memory coherence may not be required (e.g. a monitoring thread that wants to "inspect" the contents of a segment). For such purposes, the weak-read mode is provided. In this mode a current copy of the segment is sent to the requester. The thread would continue to receive updates to the segment if it had specified the *update* option on the weak-read request. A thread explicitly relinquishes a lock that it has acquired for a segment by using the *discard* primitive.

#### 3.4 Mach and Agora

Mach [32] is a multiprocessor operating system kernel developed at CMU. It provides five basic abstractions: *task*, *thread*, *port*, *message* and *memory object*. A task is an execution environment that includes a virtual address space and an access list to system resources. A thread is a basic unit of CPU scheduling and it executes in the environment provided by a task; a port is a communication channel; and a message is a typed collection of data objects. Inter-thread communication is effected using messages on the ports. A memory object is a collection of data that may be mapped into the address space of any task. It is a structured mechanism for managing virtual memory independent of the underlying architecture.

An address space consists of a collection of memory mappings between a task and memory objects. A task may modify its address space by allocating and de-allocating a region of virtual memory. A task may also set protection attributes and specify inheritance of a region of virtual memory. It could create and manage a memory object that maybe mapped into the address space of another task. There are two ways of sharing memory between tasks in Mach: *copy-on-write* and *readwrite*. In copy-on-write sharing, unrelated tasks share an address space without the actual data being copied. The first task that tries to write gets a copy of the shared address space. The copies become distinct and different from this point on. Read-write shared memory is created by allocating a memory region and setting its inheritance attributes to *shared*, *copy*, or *none*. Subsequent child task creation obeys the inheritance attributes specified by the parent. Pages specified as shared are physically shared between the parent and the children, i.e., there is exactly one copy of the page in the multiprocessor system. A child gets a logical copy of a page that is marked copy. Pages marked as none are not shared between the parent and the children.

Note that memory objects may be shared across the network. In this case, the physical memory is considered to be a cache for the memory objects. Associated with each memory object is a server called *pager* that manages the memory object. The pager handles any request for the memory object through a communication port. On a page-fault, the Mach page-fault handler checks whether the faulting thread has the access permissions for the page. If the permissions are correct then the page request is sent to the pager for the memory object. The pager services the request and sends back the page from the memory object. Mach provides sequentially consistent memory coherence semantics using a write-invalidate approach for sharing of pages across the network.

Although Mach's shared memory semantics are geared towards managing shared memory in a tightly-coupled multiprocessor, there is nothing in the design

that precludes its use in a loosely-coupled system. In fact, Agora [5] is a system that is built on top of Mach with the specific intent of providing shared memory semantics in a loosely-coupled system. The Agora system allows processes to share structured data, e.g., abstract data types across heterogeneous architectures over a local area network. Agora uses the shared memory abstraction of the Mach operating system to share data structures among processes on the same machine. It also provides simple locks to synchronize access to shared data. To provide sharing across the network, the shared data structures are stored in the shared memory of the process that created the data structure. This copy of data is called the *master* copy while a copy of the data at another node is called a *cache copy*. Data is shared using copy-on-write semantics with updates to the cache copies. Writes to shared data are done on the master copy while data is read from the cache copy. A server process running on the node with the master copy is responsible for updating the copies of the data at other nodes. A read may potentially return stale data if the read occurs after the write is complete on the master copy and before the updates are propagated to the cache copies. The system expects that synchronization is implemented orthogonally using semaphores to guard against such stale accesses.

### 3.5 Memnet

Memnet [12] is a shared local area token-ring network being developed at the University of Delaware. It provides close coupling to the processors of a distributed multiprocessor system. There are three distinctive features of this project: first, it allows a granularity of access (32-byte chunks) finer than a page; second, it employs

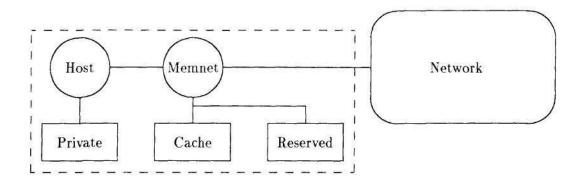

Figure 2: Memnet Architecture

dedicated hardware (Memnet device) to service remote memory accesses; third, it exploits the features of a special-purpose token ring network to implement a writeinvalidate style of cache protocol. Given that there is an appreciable software overhead for remote access, dedicated hardware is almost a necessity to assure acceptable performance in DSM systems. The Memnet system does not support virtual memory. Therefore, the way DSM is managed on Memnet is very similar to cache management in a shared memory multiprocessor.

Each node in the system consists of a host and a Memnet device (Figure 2). The host has access to its private memory, which is inaccessible to other nodes. There is a large shared memory that is accessible from any node in the system. This shared memory is divided into 32-byte chunks and distributed among all the Memnet devices. The hardware address space seen by each host has two parts: private and shared. References to the shared part are passed to the associated Memnet device, which coordinates with other devices to resolve the references.

The physical memory associated with each Memnet is divided into two parts: *reserved* and *cache*. The reserved part is the permanent residence for the portion of the global shared memory that is managed by this Memnet device, while the cache is a temporary store for chunks that have been brought from remote Memnet devices. There is a chunk status table with each Memnet device that contains an entry for the chunks that are present in its physical memory. Memnet uses a write-invalidate style of cache protocol. A chunk may be in one of three states: valid (readable but not writable), exclusive (readable and writable), and invalid.

When a reference is generated for a chunk that is not locally available, then this request is sent around the token-ring. The first node that has valid copy of this chunk responds to this request. In case the reference is a "write", all other valid copies are invalidated before the chunk is written. In this sense, Memnet treats the token-ring as a logical broadcast bus. When a chunk has to be replaced from the cache, it is written back to its designated reserved area in the appropriate Memnet device. Since the system does not explicitly provide synchronization mechanisms, they have to be implemented at the user level to protect shared accesses.

## 3.6 Choices

Choices [34] is an operating system architecture developed at the University of Illinois at Urbana-Champaign. It uses class hierarchies and object-oriented programming to support the building of customized operating systems for shared memory and networked multiprocessors.

The virtual memory management system of Choices is similar to that of Mach. Choices uses the idea of a memory object that is cached in physical memory. The memory object abstraction is provided by the *MemoryObject* class while the virtual memory abstraction is provided by the *Domain* class. The Domain class maintains information about the association between the virtual memory of an application and the memory objects. It provides methods to bind and release a virtual address to a memory location. Sharing of memory is achieved by mapping the same memory object into multiple Domains. Sharing across the network is achieved via the *DistributedMemoryObjectCache* class. This class is responsible for servicing page-faults on a node for shared data residing on a remote node. It communicates with its peers to maintain the consistency of shared data using a write-invalidate style of protocol similar to the distributed manager protocol of Ivy. The granularity of remote access is a page. Choices also provides for locking a page similar to the read-write mode of CLOUDS (see section 3.3) to guarantee atomic updates to a memory object by denying access until the lock is removed. Another variant (similar to Mirage) that Choices allows is retaining access to a page for a fixed duration of time regardless of other pending requests.

# 3.7 Mether

Mether [29] provides a set of mechanisms for sharing memory across the network on top of SunOS 4.0. Mether differs from most other distributed shared memory systems in that it does not provide sequentially consistent memory coherence. A process can continue to write on a page without the changes being reflected in other copies of the page. The other copies of the page may be updated in one of the following three ways: The process with the consistent copy of the page may initiate the updates to be propagated to all the other copies; a process holding an inconsistent copy of the page may invalidate its copy, resulting in a page-fault the next time it tries to access that page; a process holding an inconsistent copy of the page may explicitly request a consistent copy of the page. As should be evident, the user is responsible for tailoring the consistency requirements commensurate with the needs of the application. Mether provides a set of system calls to facilitate customizing the coherence requirements.

Mether provides for data driven page-faults. In a data driven page-fault, the process that caused the page-fault is blocked. No request for servicing the page-fault is sent by the server across the network. The page-fault is serviced when another process actively sends out an update for the page that caused the fault. Thus, the page-faults are completely passive. Mether defines two types of pages: a short page (32-bytes) and a full page (8192 bytes). A short page, referred to as a *subset*, corresponds to the first 32-bytes of a full page, while a full page is referred to as a *superset*. A process is ready to resume execution following a page-fault, as soon as the subset of the page is made available to this node.

# 3.8 Munin

Munin [7] is a distributed shared memory system that allows shared memory parallel programs to be executed on distributed memory multiprocessors. It differs from other distributed shared memory systems in that it uses multiple consistency protocols, and its use of a weaker memory model based on release consistency<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>In release consistency, memory consistency is enforced at a release synchronization point.

In Munin, shared program variables are annotated with their expected access pattern, and these annotations are then used by the runtime system to choose a consistency protocol best suited to that access pattern. At present, Munin supports seven different types of annotations: read-only, migratory, write-shared, producerconsumer, reduction, result, and conventional. These annotations are then used by the runtime system to select appropriate consistency protocol for sharing. Munin uses weaker sharing semantics (using release consistency) to mask network latency and reduce the number of messages required to keep memory consistent.

# 3.9 Hardware assisted distributed shared memory systems

In recent years, several systems have been proposed that implement the distributed shared memory abstraction in hardware. Two examples are the DASH multiprocessor [26], and KSR-1 [33].

The DASH architecture consists of processing nodes connected to an interconnection network. It uses a distributed directory-based cache coherence protocol. Each processing node consists of a small number of processors, called a cluster; a small portion of the shared memory; and a directory controller interfacing the cluster to the network. The memory hierarchy consists of two levels: cluster memory, and global memory. The cluster memory consists of the memory available with the processors of the cluster, while the global memory consists of memory available in all the clusters. On an access miss, an attempt is made to service the data request by the processors within a cluster. If the request cannot be serviced then it is sent to other processors outside the cluster. Each processing node has a directory memory corresponding to its portion of the shared physical memory. For each memory block, the directory memory stores the identities of all remote nodes caching that block. Using the directory memory, a node can send either invalidation or update messages to those processors that are caching the block. DASH uses an invalidation-based ownership protocol for maintaining consistency of shared data. Data consistency is maintained at the granularity of a cache line within a cluster, and at the granularity of a memory block between clusters.

KSR-1 is a 64-bit cache only memory architecture based on an interconnection of a hierarchy of rings. It implements a system virtual address (SVA) space that is global to the entire system. The SVA consists of the union of all the memory available with the individual processor caches. Each cache is subdivided in 16-Kbyte pages, which are further divided into 128-byte sub-pages. A data item on KSR-1 does not have any home associated with it. The data item moves from one cache to another cache as dictated by the memory access pattern of the application. An invalidation-based cache coherence protocol is used to maintain consistency of shared data. The unit of cache consistency is a sub-page. Access miss on a data item is sent on the local ring. If another cache is able to service the data request, it does so by sending the sub-page to the requesting cache. If no cache on the local ring has the data item, the request is propagated to the next level of the ring.

# 3.10 Discussion

In this section we compare the features of the DSM systems surveyed in this chapter with respect to the issues enumerated in chapter 2 (see Table 1). All the DSM systems presented in this chapter, with the exception of Agora and Munin have integrated the DSM management with the VM management, i.e., the DSM manager co-operates with the VM manager to service page-faults. Accesses to remote memory are referred to the DSM manager by the VM manager, which in turn satisfies the request using its own coherence protocol. Thus, a page-fault to local memory is indistinguishable from a page-fault to remote memory, insofar as a process is concerned. The difference may only be in the latency of service. Memnet does not support virtual memory. The shared memory in Memnet is at the physical address level and its management is similar to private caches in an SMM. References to shared memory are serviced by a Memnet device without the software overhead associated with the VM management. A similar approach is used in DASH and KSR-1 systems. CLOUDS provides a tighter integration of the VM system and the DSM system than any of the other systems by maintaining sharing information at the thread (process) level as opposed to processor level. In fact, such an integration is essential for a system that uses a lock-based coherence protocol to assure mutual exclusion (when needed) for a thread from all other threads, including ones that execute on the same processor. On the other hand, Agora and Munin use the library-approach. Both systems require the user to specify which data structures in the program are shared. This information is used by the DSM at runtime for maintaining coherence for shared data. Due

to the additional overhead for processing shared memory requests in the libraryapproach, the library approach is expected to perform poorly as compared to the integrated-approach.

Data granularity (see section 2.2) has two aspects: unit of transfer and unit of access and locking. Unit of transfer refers to the amount of information shipped across the network to satisfy a remote request, while the unit of access and locking is self explanatory. One disadvantage of integrating DSM management with VM management is that the data granularity of shared memory may be dictated by the underlying VM architecture. Most VM architectures provide address mapping and protection attributes at the level of a page or multiples of a page. This feature could constrain the unit of transfer between the DSM managers to be a page, and could lead to inefficiencies if the size of the shared data structure is less than a page. For example, suppose the size of a data object is 512 bytes. In a DSM system with a page size of 8192 bytes, an access to this data object would result in the transfer of 8192 bytes, an unnecessary overhead of 1500%. This overhead could be reduced with some simple optimizations. One such optimization is implemented in Mether, where each access to shared data results in the transfer of the first 32-bytes of the page. A process may decide to fetch the entire page if it so desires by examining the first 32-bytes of the page.

Another disadvantage of such an integration (between VM and DSM) could be that the unit of access and locking may be constrained to be a page (or multiples thereof). If multiple data structures are allocated on the same page, then this constraint could lead to *false sharing*, wherein distinct private data structures appear shared due to co-location on the same page. However, the advantage of such an integration is that the hardware memory management facilities in the underlying architecture could be exploited to efficiently implement access control and locking of the shared data structures.