# SYSTEM-LEVEL MODELING AND RELIABILITY ANALYSIS OF MICROPROCESSOR SYSTEMS

A Dissertation Presented to The Academic Faculty

by

Chang-Chih Chen

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology December 2014

Copyright © 2014 by Chang-Chih Chen

# SYSTEM-LEVEL MODELING AND RELIABILITY ANALYSIS OF MICROPROCESSOR SYSTEMS

# Approved by:

Dr. Linda Milor, Advisor

School of Electrical and Computer

Engineering

Georgia Institute of Technology

Dr. Abhijit Chatterjee

School of Electrical and Computer

Engineering

Georgia Institute of Technology

Dr. David Keezer

School of Electrical and Computer

Engineering

Georgia Institute of Technology

Dr. Hyesoon Kim College of Computing

Georgia Institute of Technology

Dr. Azad Naeemi

School of Electrical and Computer

Engineering

Georgia Institute of Technology

Date Approved: August 19, 2014

#### **ACKNOWLEDGEMENTS**

I would like to extend special thanks to my advisor, Professor Linda S. Milor, for her guidance and advice during my Ph.D. study. I would also like to thank Professor David Keezer and Professor Azad Naeemi for their helpful suggestions. I would like to express my thanks to Professor Abhijit Chatterjee and Professor Hyesoon Kim, both of whom have agreed to serve on my dissertation committee. I am also grateful to Professor Sung Kyu Lim.

I would like to express my deepest thanks to Dr. Dae Hyun Kim, for developing the layout extractor for the reliability simulator from the GTCAD lab. I am also grateful to Dr. Muhammad Bashir for his collaboration.

I thank all the lab members, Dr. Fahad Ahmed, Soonyoung Cha, Taizhi Liu and Woongrae Kim for their collaboration, and valuable comments and feedback.

I would also like to extend special thanks to my best friend, Anshuman Goswami, who have always supported and motivated me.

I am particularly thankful to my parents, Lo-Wen Chen and Shu-Yuan Tang, who have always been on my side, for their love and encouragement throughout my life. I also thank my grandfather, grandmothers, brother, Hsuan-Chih Chen, and sister, Jou-Chou Chen, for their love and support. Last but not least, I would like to thank all the professors, teachers, families, and friends who guided me to become the person that I am today.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                                       | iv  |

|----------------------------------------------------------------------------------------|-----|

| LIST OF FIGURES                                                                        | vii |

| LIST OF SYMBOLS AND ABBREVIATIONS                                                      | xi  |

| SUMMARY                                                                                | xiv |

| <u>CHAPTER</u>                                                                         |     |

| 1. INTRODUCTION                                                                        | 1   |

| 2. BACKGROUND                                                                          | 8   |

| 3. DEVICE-LEVEL WEAROUT MODELS                                                         | 14  |

| 3.1 Backend Time-Dependent Dielectric Breakdown (BTDDB)                                | 15  |

| 3.1.1 Vulnerable Dielectric Area and Test Structures                                   | 18  |

| 3.1.2 Test Results                                                                     | 22  |

| 3.1.3 Model Constructions for Irregular Geometries                                     | 25  |

| 3.1.4 Vulnerable Length and Feature Extraction                                         | 29  |

| 3.2 Electromigration (EM)                                                              | 34  |

| 3.3 Stress-Induced Voiding (SIV)                                                       | 37  |

| 3.4 Negative/Positive Bias Temperature Instability (NBTI/PBTI)                         | 39  |

| 3.5 Hot Carrier Injection (HCI)                                                        | 41  |

| 3.6 Gate Oxide Breakdown (GOBD)                                                        | 44  |

| 4. AGING ASSESSMENT FRAMEWORK                                                          | 47  |

| 5. LIFETIME AND RELIABILITY ANALYSIS DUE TO BACKEND WAROUT MECHANISMS (BTDDB, EM, SIV) | 59  |

| 5.1 Microprocessor Lifetime Models                                                     | 59  |

| 5.2 Lifetime Estimations for The Systems                                               | 65  |

| 5.2.1 Case Study 1: LEON3 microprocessor                                                        | 65  |

|-------------------------------------------------------------------------------------------------|-----|

| 5.2.2 Case Study 2: 32-bit RISC microprocessor                                                  | 75  |

| 5.3 Impact of Irregular Geometries on System Lifetimes under BTDDB                              | 77  |

| 5.3.1 Case Study 1: FFT Circuits                                                                | 77  |

| 5.3.2 Case Study 2: LEON3 microprocessor                                                        | 80  |

| 6. LIFETIME AND RELIABILITY ANALYSIS DUE TO FRONTEND WEAROUT MECHANISMS (NBTI, PBTI, HCI, GOBD) | 83  |

| 6.1 Impact of Frontend Wearout Mechanisms on Microprocessor Logic Block Reliability             | 83  |

| 6.1.1 Performance Degradation Analysis Flow                                                     | 83  |

| 6.1.2 Logic Wearout Simulation Results                                                          | 85  |

| 6.1.2.1 Case Study 1: LEON3 microprocessor                                                      | 86  |

| 6.1.2.2 Case Study 2: 32-bit RISC microprocessor                                                | 91  |

| 6.2 Performance Degradation Analysis for Memory Blocks                                          | 93  |

| 6.2.1 SRAM Circuit                                                                              | 93  |

| 6.2.2 Memory Wearout Simulation Results                                                         | 94  |

| 7. CONCLUSIONS                                                                                  | 103 |

| 7.1 Conclusions of the Research                                                                 | 103 |

| 7.2 Future Work                                                                                 | 104 |

| APPENDIX A: LIFETIME WITH RECONFIGURATION THROUGH REDUNDANCY ALLOCATION                         | 105 |

| REFERENCES                                                                                      | 107 |

# LIST OF FIGURES

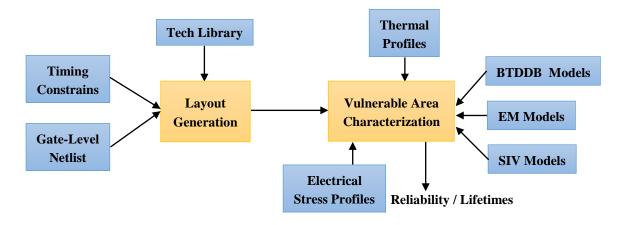

| 1.1  | The flow of system-level modeling for backend wearout mechanisms                                                                                                                                                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

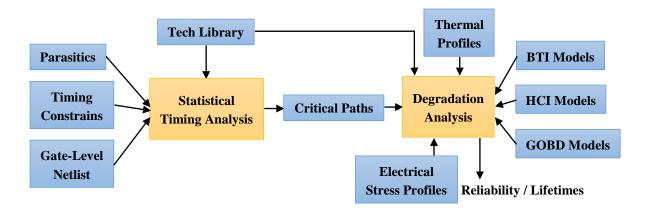

| 1.2  | The flow of system-level modeling for frontend wearout mechanisms                                                                                                                                                                                                                                                                         |

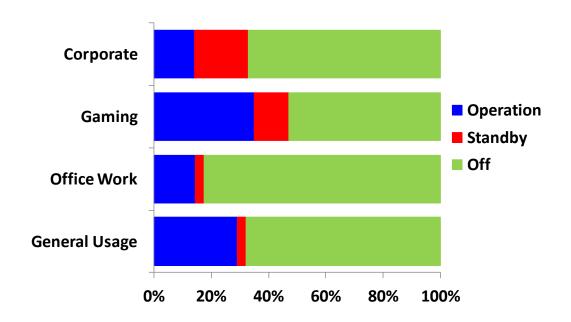

| 1.3  | The use scenarios provided by Intel are shown.                                                                                                                                                                                                                                                                                            |

| 3.1  | Cross section of an example dual-damascene Cu/Low-k interconnect under BTDDB.                                                                                                                                                                                                                                                             |

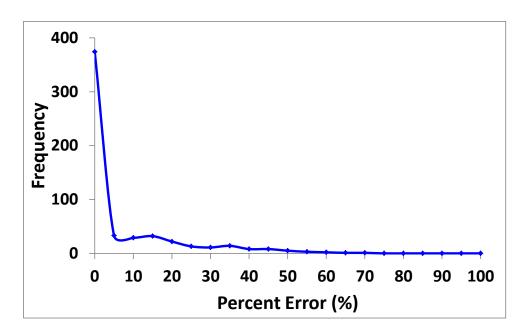

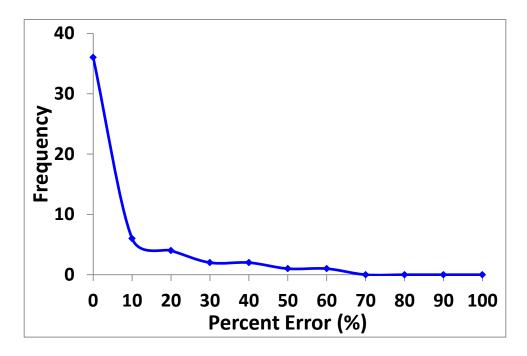

| 3.2  | Percent error distribution of the random-selected dielectric segments                                                                                                                                                                                                                                                                     |

| 3.3  | The vulnerable length associated with a linespace is shown. The rectangles are copper wires, surrounded by the backend dielectric.                                                                                                                                                                                                        |

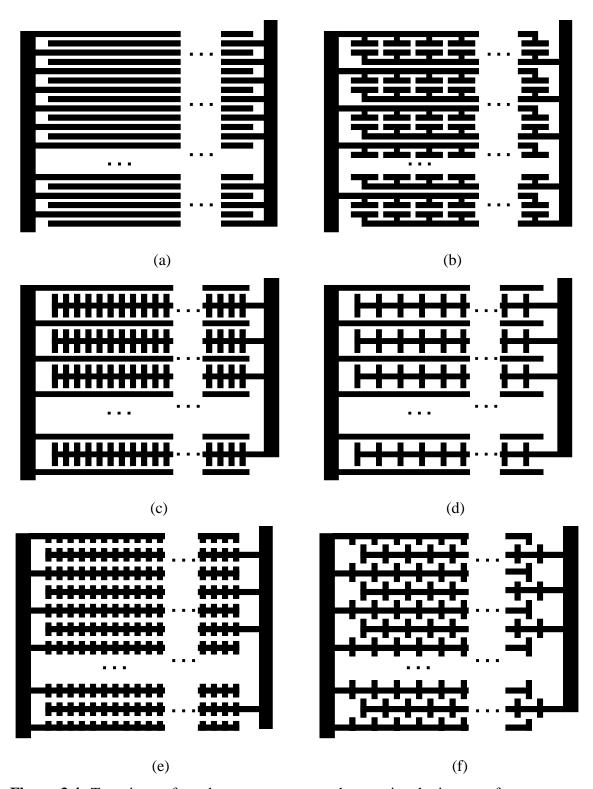

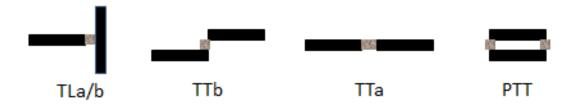

| 3.4  | Top views of comb test structures to characterize the impact of geometry on time-dependent dielectric breakdown. (a) Standard comb structure, (b) PTT, (c) TLa, (d) TLb, (e) TTa, and (f) TTb.                                                                                                                                            |

| 3.5  | Vulnerable line ends that need to be extracted from a layout.                                                                                                                                                                                                                                                                             |

| 3.6  | Data collected from (a) PTT vs. the reference structure, (b) TLa, TLb, and TTa vs. the reference structure, and (c) TTb. $2\sigma$ confidence bounds are included for the area scaled reference test structure.                                                                                                                           |

| 3.7  | Vulnerable length and line ends extracted from test structure TLa/b and PTT. The vulnerable length is indicated with arrows and the line ends are indicated with circles.                                                                                                                                                                 |

| 3.8  | Data collected from TLa/b vs. the reference structure. The models for the data from the test structure and the line ends, after subtracting the effect of area are nearly indistinguishable.                                                                                                                                              |

| 3.9  | Data collected from PTT vs. the reference structure. The graph shows the models for the data from the test structure vs. the line ends, after subtracting the effect of area.                                                                                                                                                             |

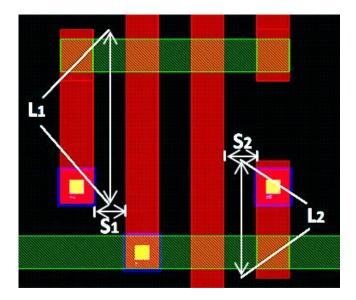

| 3.10 | (a) Initial line structure. (b) PTT is extracted from S1 and S2. (c) Vulnerable length between S1 and S2 is extracted. (d) Postpocessing after vulnerable area extraction. (e) TTb does not exist between S1_1 and S2. (f) TTb is extracted from S1_1 and S3. (g) TLa/b is extracted from S2 and S4. (h) TTa is extracted from S2 and S3. |

| 3.11 | An example vulnerable interconnect/via interface under EM                                                                                                                                                                                                                                                                                 |

| 3.12 | Percent error distribution of the random-selected via current densities                                                                                                                                                                                                       | 37 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

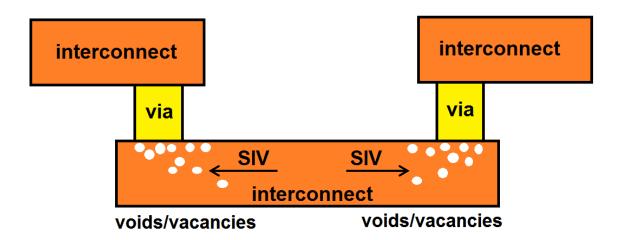

| 3.13 | An example vulnerable interconnect/via interface under SIV                                                                                                                                                                                                                    | 38 |

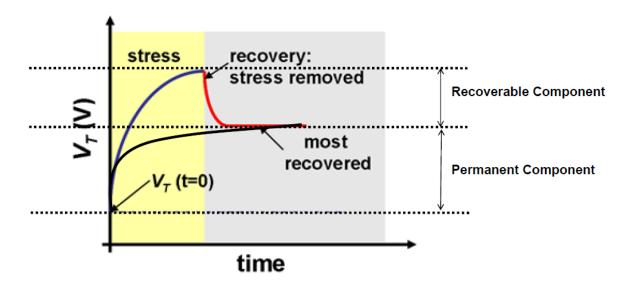

| 3.14 | The threshold voltage drift caused by BTI is a function of stress time and recovery (non-stress) time.                                                                                                                                                                        | 40 |

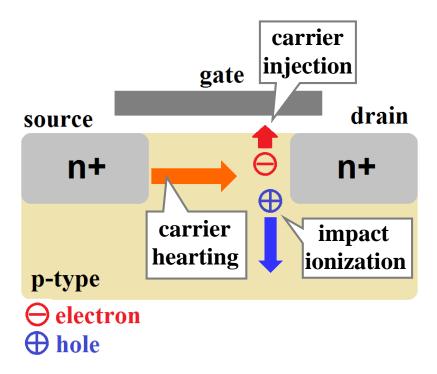

| 3.15 | Carriers shoot out from the source of a NMOS, accelerate in the channel, and experience impact ionization near the drain end of the device.                                                                                                                                   | 42 |

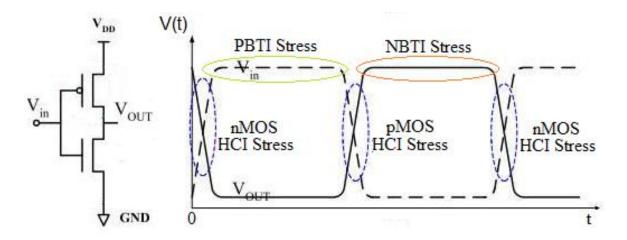

| 3.16 | Stress-time windows of NBTI, PBTI and HCI for an inverter.                                                                                                                                                                                                                    | 43 |

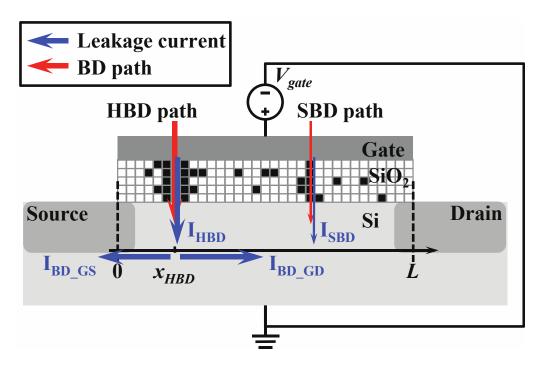

| 3.17 | Defect generation in the SiO <sub>2</sub> layer based on a 2D percolation model for SBD and HBD paths.                                                                                                                                                                        | 45 |

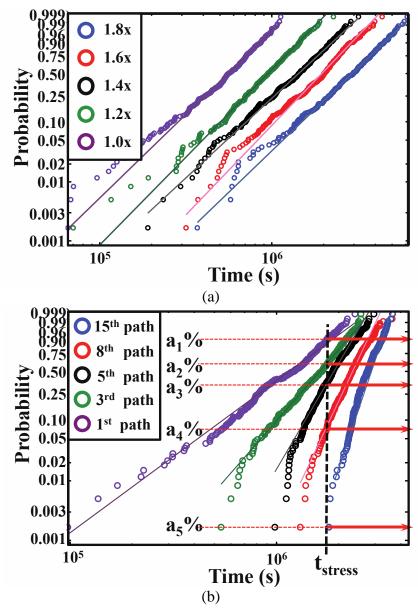

| 3.18 | Time distribution of defect generation in SiO2. (a) The probability distribution of the time of occurrence of the k <sup>th</sup> SBD path for different gate sizes. (b) The probability distribution of the number of SBD paths for a fixed gate size as a function of time. | 46 |

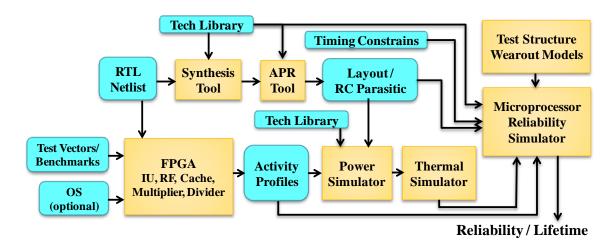

| 4.1  | The schematic of the proposed electrical/thermal aging assessment framework is shown. Yellow blocks indicate tools, while blue blocks indicate data.                                                                                                                          | 47 |

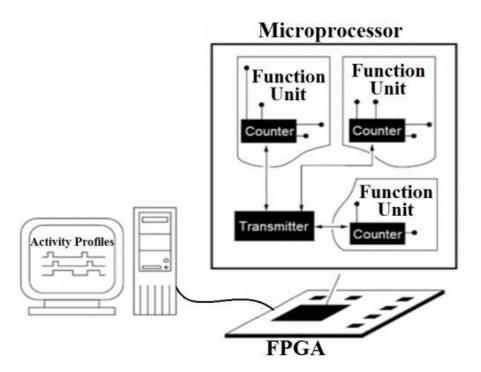

| 4.2  | The system used to collect activity profile of microprocessor contains an FPGA board that implements the microprocessor system and exports data on the activity profile to a PC.                                                                                              | 49 |

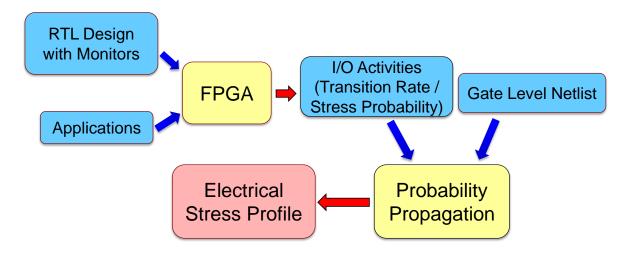

| 4.3  | The flow of Acquisition of electrical stress profile is shown.                                                                                                                                                                                                                | 50 |

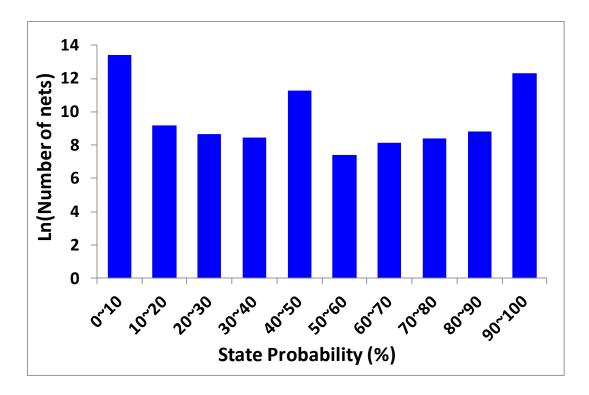

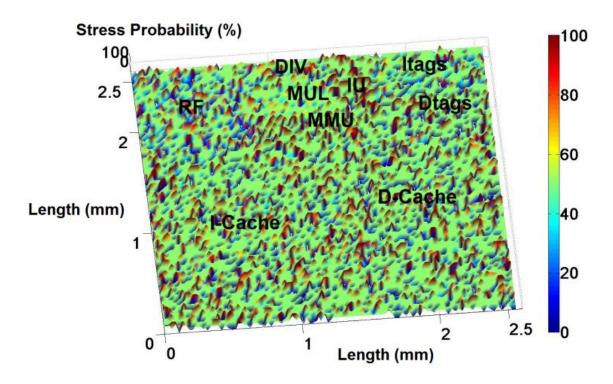

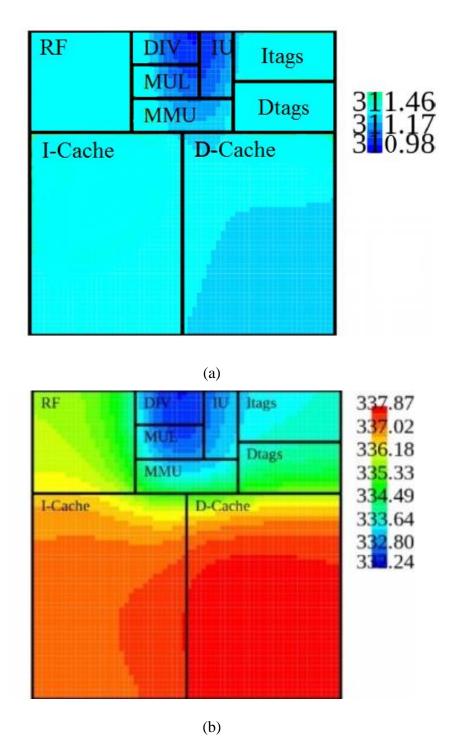

| 4.4  | The spatial distribution of the state probability for an example microprocessor is shown while running a set of standard benchmarks                                                                                                                                           | 51 |

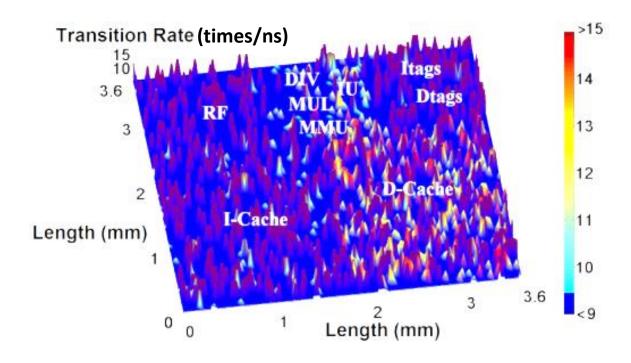

| 4.5  | The spatial distribution of the transition rate for an example microprocessor is shown while running a set of standard benchmarks.                                                                                                                                            | 52 |

| 4.6  | The spatial distribution of the dielectric stress probability for an example microprocessor is shown while running a set of standard benchmarks                                                                                                                               | 53 |

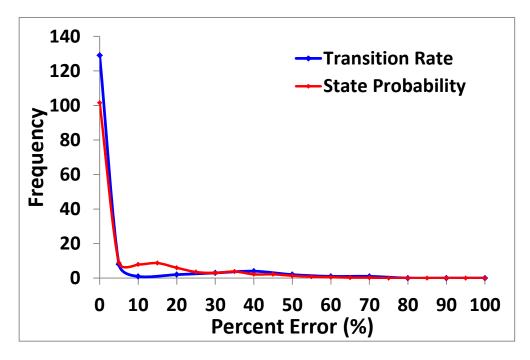

| 4.7  | Percent error distribution of the random-selected interconnects.                                                                                                                                                                                                              | 54 |

| 4.8  | The flow of RC parasitic extraction is shown.                                                                                                                                                                                                                                 | 56 |

| 4.9  | The flow of acquisition of power and thermal profiles is shown.                                                                                                                                                                                                               | 56 |

| 4.10 | The static temperature distribution for an example microprocessor is shown while running a set of standard benchmarks.                                                                                                                                                        | 57 |

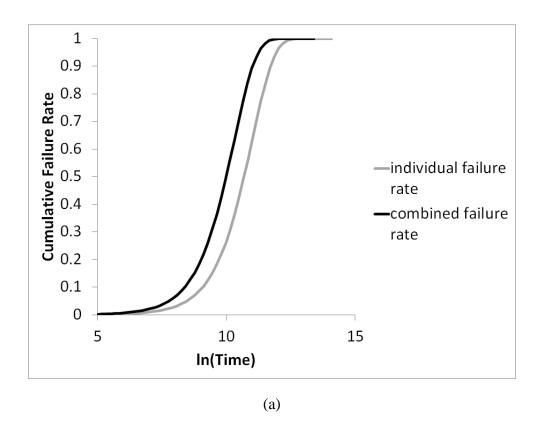

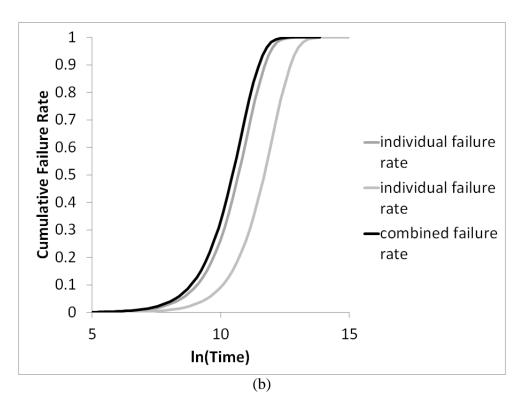

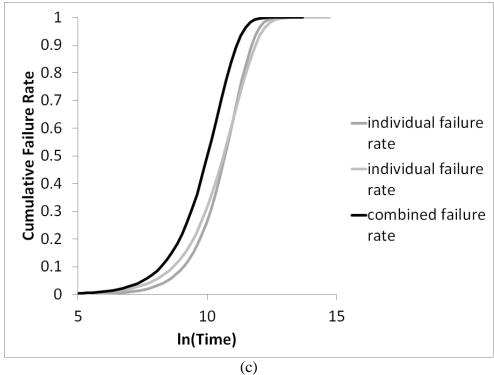

| 5.1  | (a) Impact of combining two Weibull distributions with the same parameters.  (b) Impact of combining two Weibull distributions with different characteristic lifetimes. (c) Impact of combining two Weibull distributions with different shape parameters. | 62 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

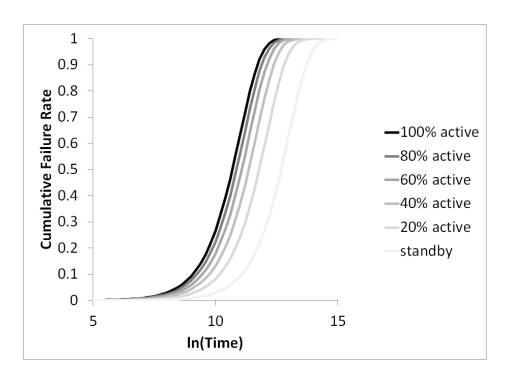

| 5.2  | Impact of combining two Weibull distributions with different failure rates                                                                                                                                                                                 | 65 |

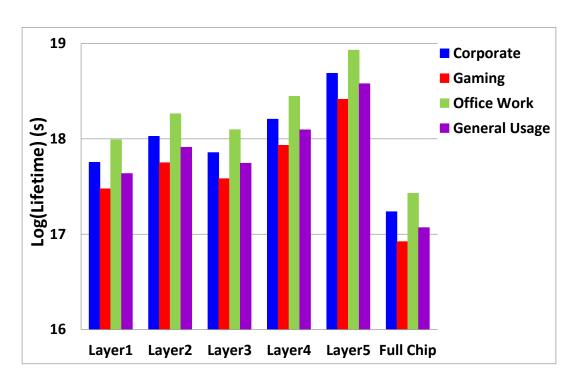

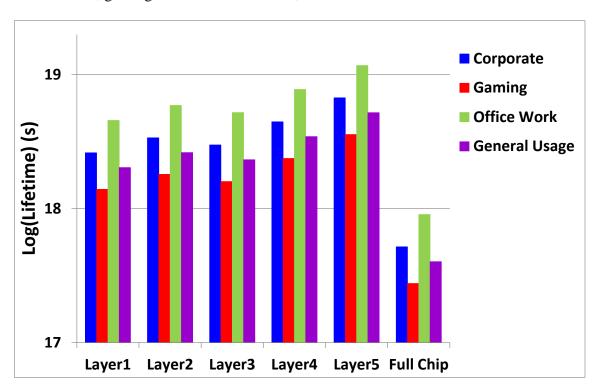

| 5.3  | Characteristic lifetimes under different scenarios for each layer of LEON3 microprocessor due to BTDDB indicate the most vulnerable layer.                                                                                                                 | 67 |

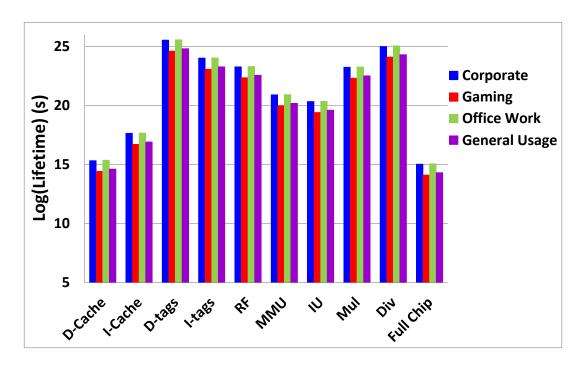

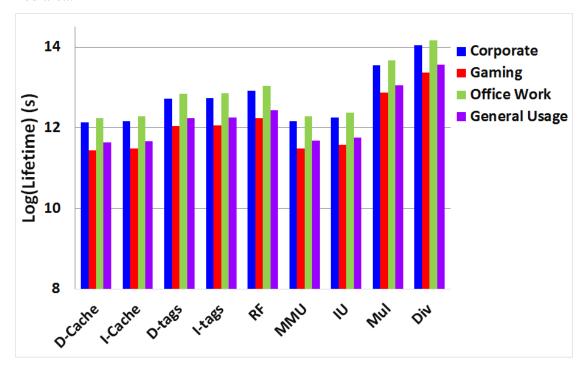

| 5.4  | Characteristic lifetime results under different use scenarios for each unit in LEON3 microprocessor due to BTDDB indicate the most vulnerable blocks.                                                                                                      | 67 |

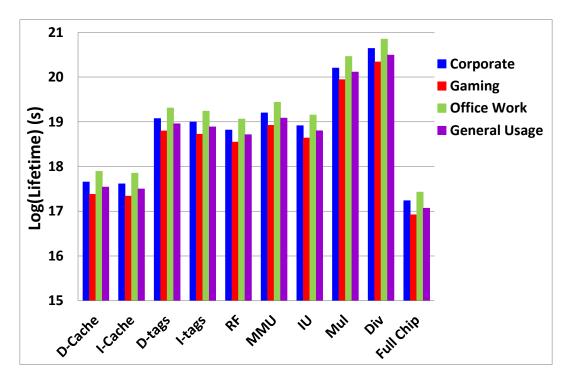

| 5.5  | Characteristic lifetime results under different use scenarios for each unit in the microprocessor system due to EM indicate the most vulnerable blocks                                                                                                     | 69 |

| 5.6  | Characteristic lifetime results under different use scenarios for each unit in the microprocessor system due to SIV indicate the most vulnerable blocks                                                                                                    | 70 |

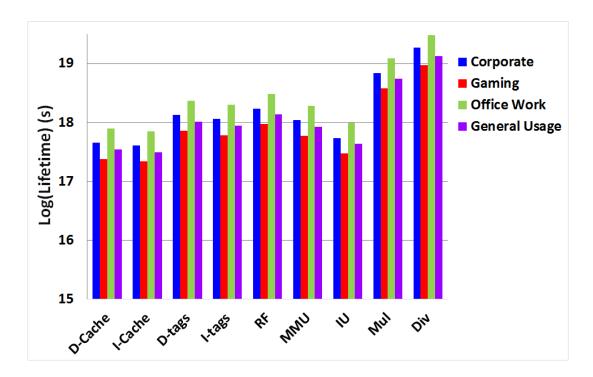

| 5.7  | Characteristic lifetime results under different use scenarios due to BTDDB for each unit in LEON3 microprocessor where each unit is expanded so that each unit has a fixed area.                                                                           | 71 |

| 5.8  | Characteristic lifetime results under different use scenarios due to EM for each unit in LEON3 microprocessor where each unit is expanded so that each unit has a fixed area.                                                                              | 72 |

| 5.9  | Characteristic lifetime results under different use scenarios due to SIV for each unit in LEON3 microprocessor where each unit is expanded so that each unit has a fixed area.                                                                             | 72 |

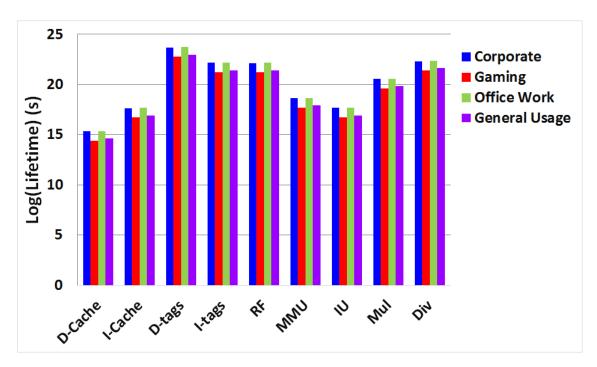

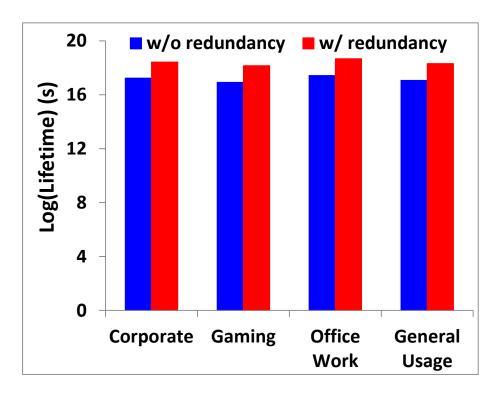

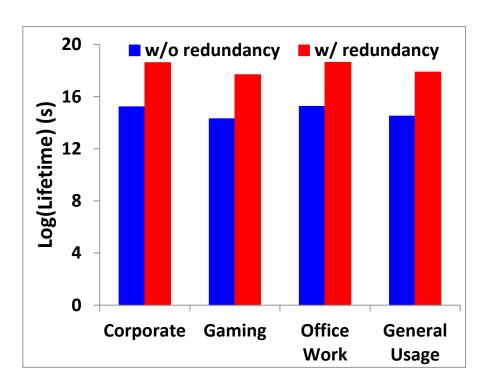

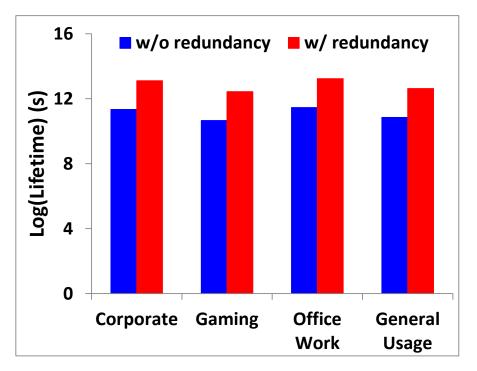

| 5.10 | Characteristic lifetime results under different use scenarios of LEON3 microprocessor due to BTDDB with and without redundancy is shown                                                                                                                    | 73 |

| 5.11 | Characteristic lifetime results under different use scenarios of LEON3 microprocessor due to EM with and without redundancy is shown.                                                                                                                      | 74 |

| 5.12 | Characteristic lifetime results under different use scenarios of LEON3 microprocessor due to SIV with and without redundancy is shown.                                                                                                                     | 74 |

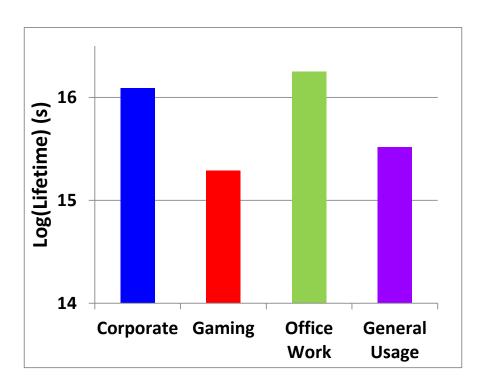

| 5.13 | Characteristic lifetimes under different scenarios for each layer of RISC microprocessor due to BTDDB indicate the most vulnerable layer.                                                                                                                  | 75 |

| 5.14 | Characteristic lifetimes under different scenarios of RISC microprocessor due to EM indicate the most vulnerable layer.                                                                                                                                    | 76 |

| 5.15 | Characteristic lifetimes under different scenarios of RISC microprocessor due to SIV indicate the most vulnerable layer.                                                                       | 76 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

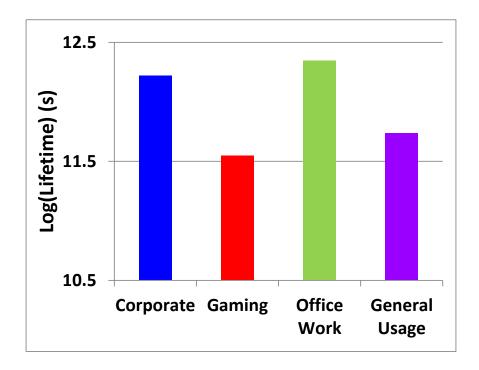

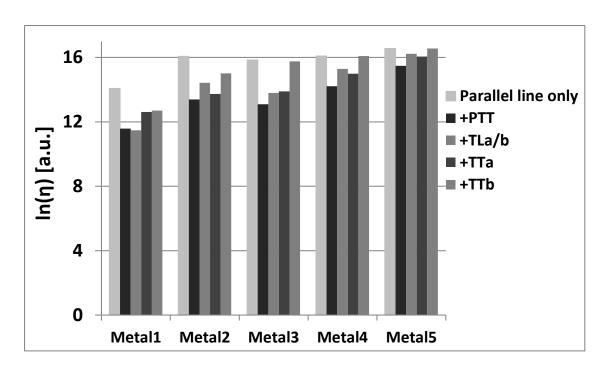

| 5.16 | Characteristic lifetimes for individual layers of an FFT circuit considering only the dielectric between parallel lines and considering the impact of each irregular geometry separately.      | 78 |

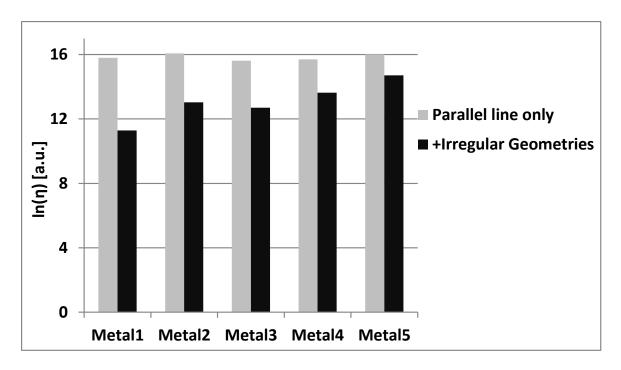

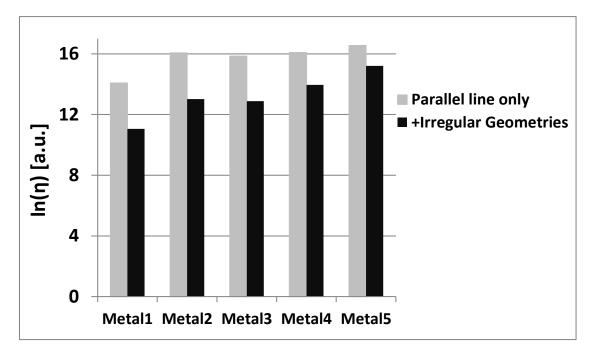

| 5.17 | Lifetimes for individual layers of an FFT circuit considering only the dielectric between parallel lines (gray) and also considering the irregular features (black).                           | 79 |

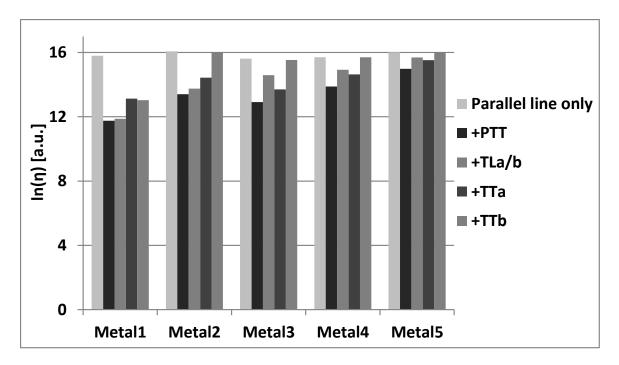

| 5.18 | Microprocessor characteristic lifetimes for each layer considering only the dielectric between parallel lines and considering the impact of each irregular feature geometry.                   | 81 |

| 5.19 | Microprocessor characteristic lifetimes for each layer considering only the dielectric between parallel lines (gray) and considering also the dielectric involved in irregular geometries.     | 81 |

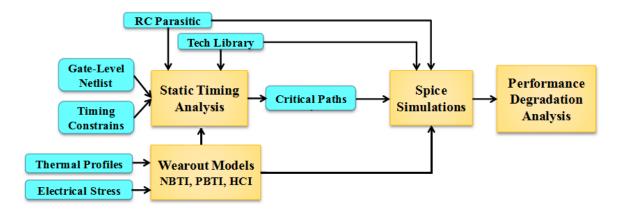

| 6.1  | The schematic of the proposed flow for performance degradation analysis is shown. Yellow blocks indicate tools, while blue blocks indicate data                                                | 83 |

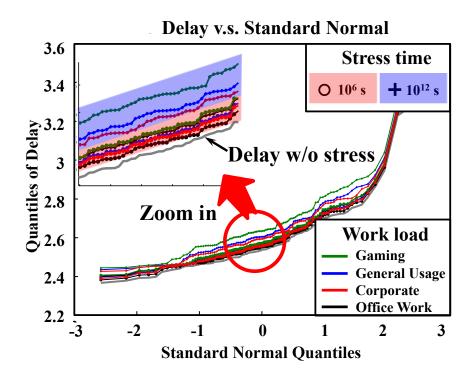

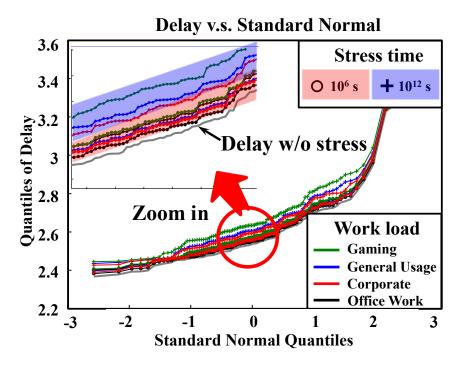

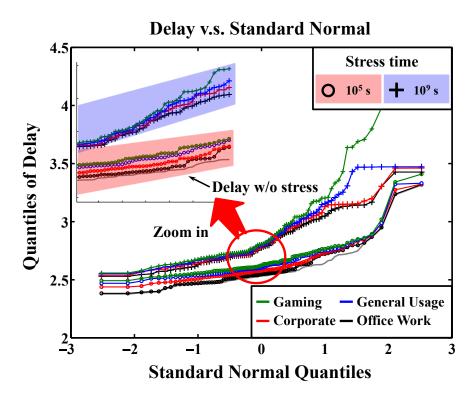

| 6.2  | The latency distributions of the critical paths of the microprocessor due to BTI for different use scenarios and for different stress time.                                                    | 87 |

| 6.3  | The latency distributions of the critical paths of the microprocessor due to HCI for different use scenarios and for different stress time.                                                    | 87 |

| 6.4  | The latency distributions of the critical paths of the microprocessor due to GOBD for different use scenarios and for different stress time                                                    | 88 |

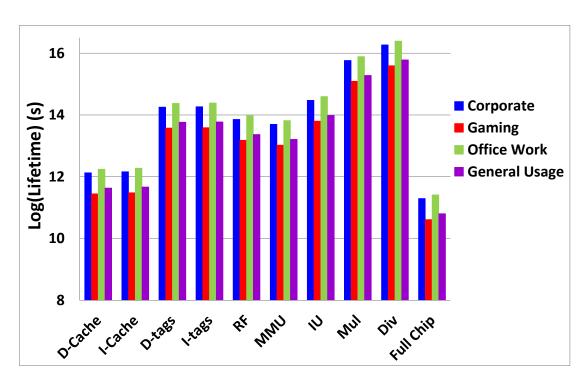

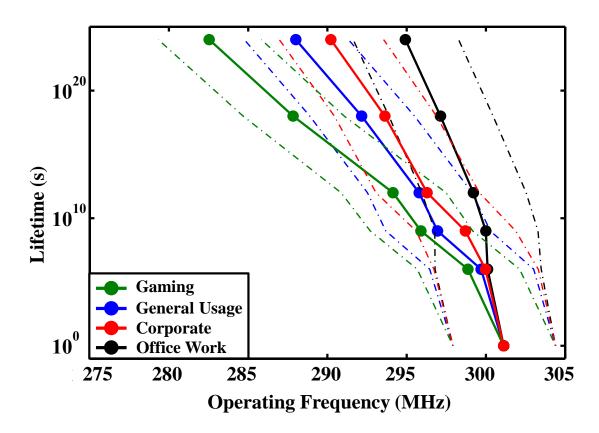

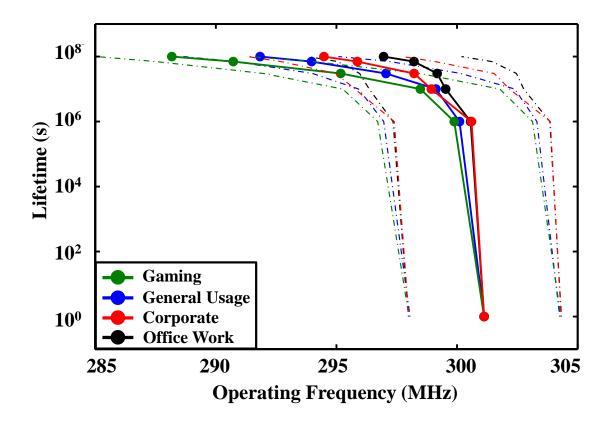

| 6.5  | The estimated lifetimes of LEON3 microprocessor due to BTI for different use scenarios and different system frequencies. Dotted lines show the boundaries when considering process variation.  | 89 |

| 6.6  | The estimated lifetimes of LEON3 microprocessor due to HCI for different use scenarios and different system frequencies. Dotted lines show the boundaries when considering process variation.  | 90 |

| 6.7  | The estimated lifetimes of LEON3 microprocessor due to GOBD for different use scenarios and different system frequencies. Dotted lines show the boundaries when considering process variation. | 91 |

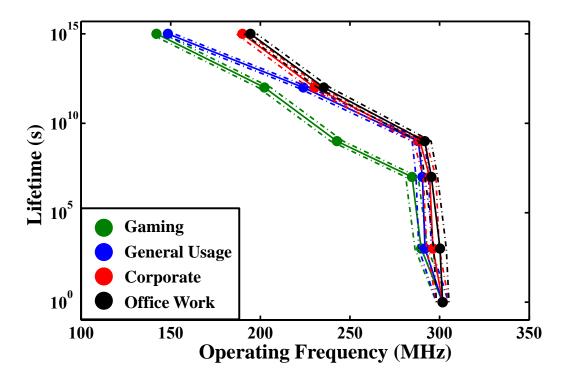

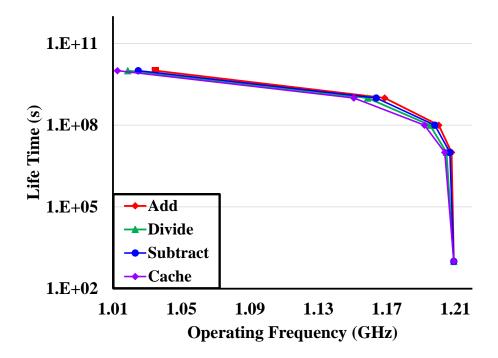

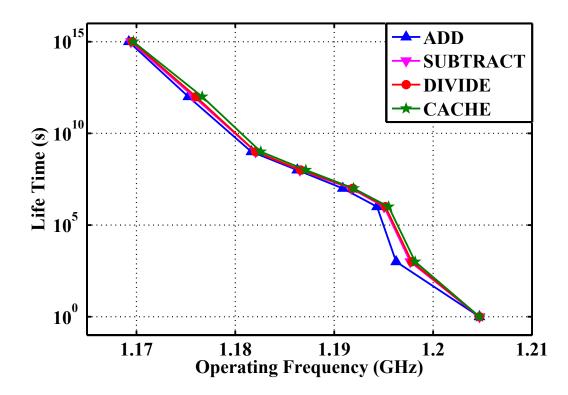

| 6.8  | The estimated lifetimes of the RISC microprocessor due to BTI for different benchmarks and different system frequencies.                                                                       | 92 |

| 6.9  | The estimated lifetimes of the RISC microprocessor due to HCI for different benchmarks and different system frequencies.                    | 92  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.10 | The estimated lifetimes of the RISC microprocessor due to GOBD for different benchmarks and different system frequencies.                   | 93  |

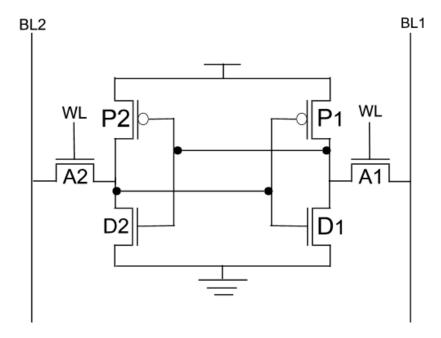

| 6.11 | A typical 6T SRAM cell is shown.                                                                                                            | 94  |

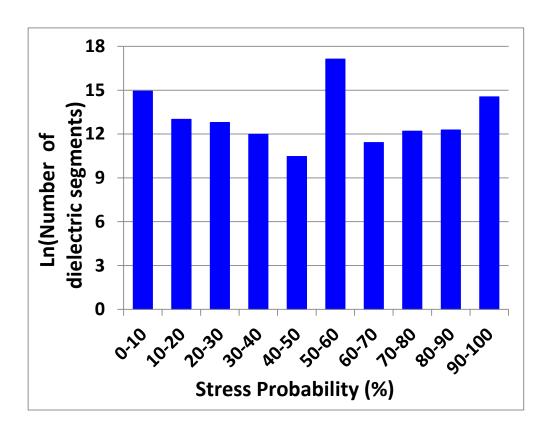

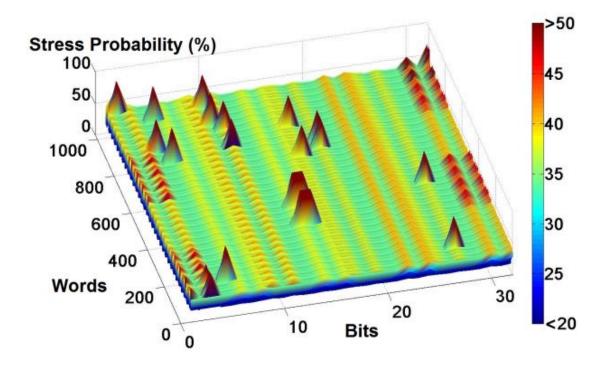

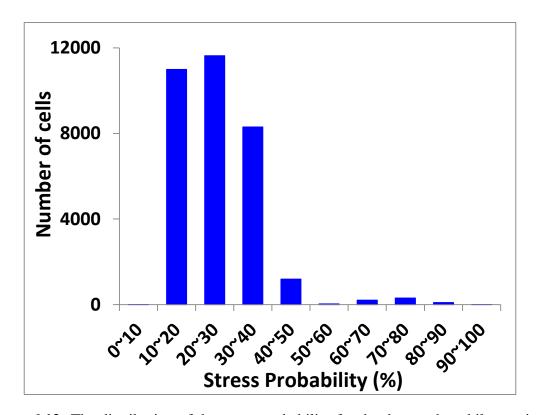

| 6.12 | The distribution of the stress probability for the data cache while running a set of standard benchmarks.                                   | 96  |

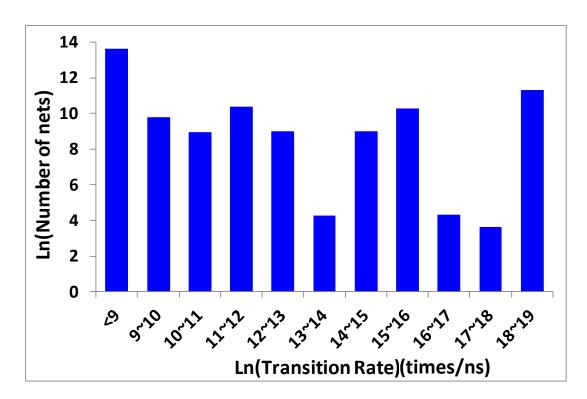

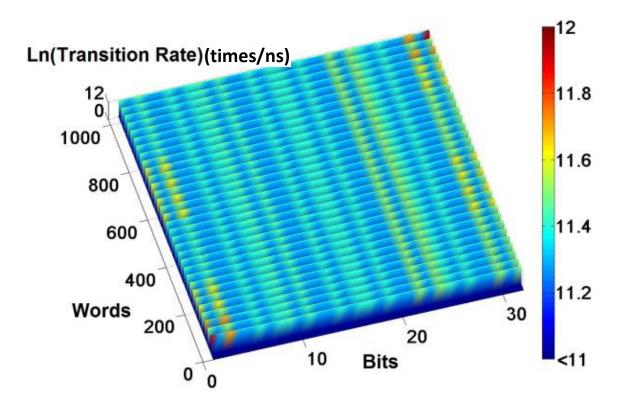

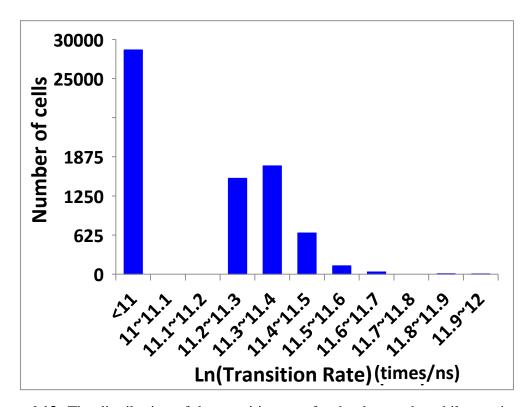

| 6.13 | The distribution of the transition rate for the data cache while running a set of standard benchmarks.                                      | 97  |

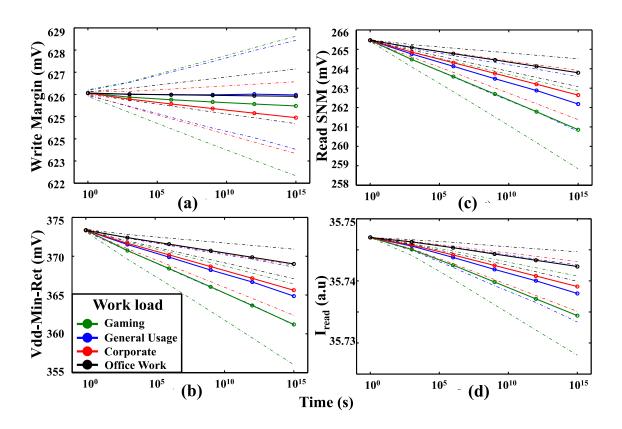

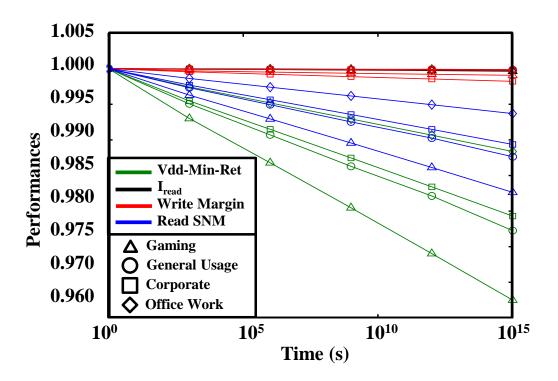

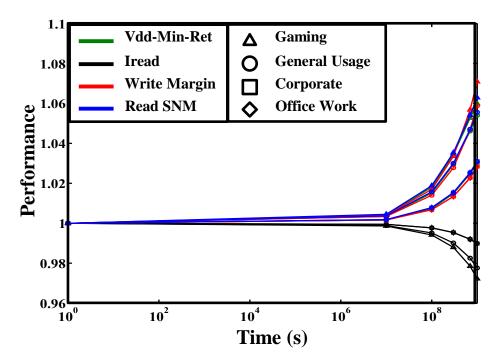

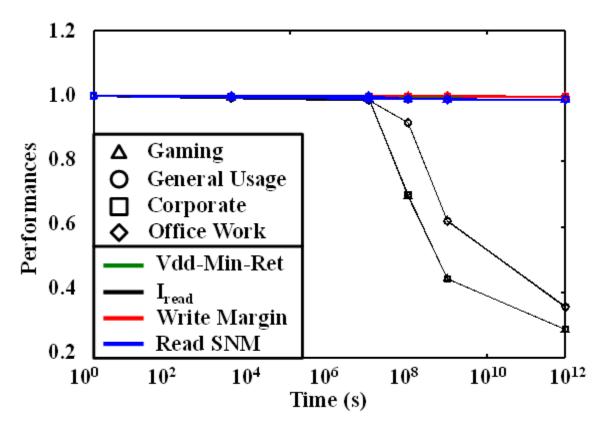

| 6.14 | The degradation of (a) write margin, (b) vdd-min, (c) read SNM, and (d) read current of the memory due to BTI for different use scenarios.  | 98  |

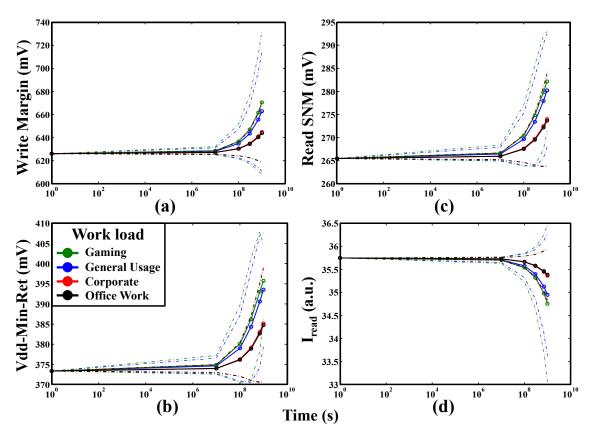

| 6.15 | The degradation of (a) write margin, (b) vdd-min, (c) read SNM, and (d) read current of the memory due to HCI for different use scenarios.  | 99  |

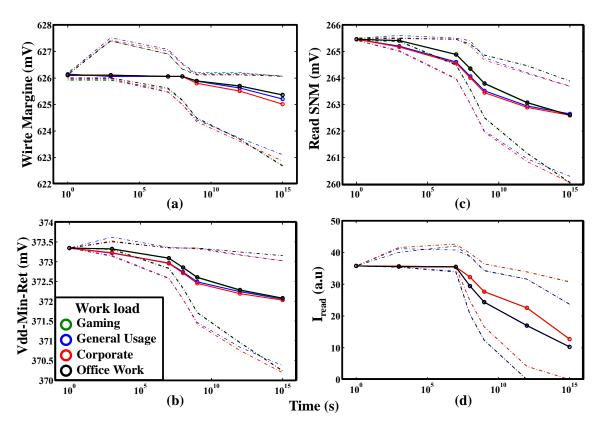

| 6.16 | The degradation of (a) write margin, (b) vdd-min, (c) read SNM, and (d) read current of the memory due to GOBD for different use scenarios. | 100 |

| 6.17 | The performance metrics of the memory for different use scenarios under BTI.                                                                | 101 |

| 6.18 | The performance metrics of the memory for different use scenarios under HCI.                                                                | 101 |

| 6.19 | The performance metrics of the memory for different use scenarios under GOBD.                                                               | 102 |

# LIST OF SYMBOLS AND ABBREVIATIONS

AC Alternating Current

BTDDB Backend Time-Dependent Dielectric Breakdown

BTI Bias Temperature Instability

Cu Copper

DC Direct Current

D-Cache Data Cache

DIV Divider

Dtags Data tags

EM Electromigration

FPGA Field-Programmable Gate Array

GOBD Gate Oxide Breakdown

HBD Hard Breakdown

HCI Hot Carrier Injection

I/O Input/Output

IC Integrated Circuit

I-Cache Instruction Cache

IP Intellectual Property

Itags Instruction tags

IU Integer Unit

MMU Memory Management Unit

MTTF Mean-Time-To-Failure

MUL Multiplier

NBTI Negative Bias Temperature Instability

NMOS N-Channel MOSFET

PBTI Positive Bias Temperature Instability

PM Percolation Model

PMOS P-Channel MOSFET

QPC Quantum Point Contact

RC Resistance and Capacitance

RF Register File

RISC Reduced Instruction Set Computing

SBD Soft Breakdown

SILC Stress Induced Leakage Current

SIV Stress-Induced Voiding

SNM Static Noise Margin

SPICE Simulation Program with Integrated Circuit Emphasis

SRAM Static Random-Access Memory

STA Static Timing Analysis

TF Time-to-Failure

#### **SUMMARY**

The object of the research is to develop a methodology to assess microprocessor lifetimes for a variety of wearout mechanisms by building the link between the device-level wearout models and the system level. This research has focused on seven critical wearout mechanisms, namely negative bias temperature instability (NBTI), positive bias temperature instability (PBTI), hot carrier injection (HCI), transistor gate oxide breakdown (GOBD), electromigration (EM), stress-induced voiding (SIV) and backend time-dependent dielectric breakdown (BTDDB), and has demonstrated the feasibility of the proposed methodology by presenting results from a lifetime simulator based on the proposed methodology.

We have developed an emulation framework for each of these failure mechanisms. It uses an FPGA based platform to determine the activity and state profiles. The activity and state profiles are needed to determine the thermal profiles and electrical stress of each feature in a system [1]-[8]. Taking into account the detailed thermal and electrical stress profiles, a methodology was developed to accurately assess state-of-art microprocessor reliability due to different wearout mechanisms. Backend wearout mechanisms are handled differently than frontend wearout mechanisms.

Analysis of lifetime due to the backend wearout mechanisms (BTDDB, EM, SIV) is based on layout analysis, layout feature extraction, where the wearout of each feature is computed and the distributions are combined analytically to estimate the lifetime of the full system [1]-[5],[9],[10].

Frontend wearout mechanisms (NBTI, PBTI, GOBD, HCI) first degrade transistor characteristics as a function of stress, which in turn degrades circuit performances. Hence, analysis of lifetime due to frontend wearout mechansms must take into account the use conditions and the circuit performance requirements [5]-[8]. Moreover, memory performances are different than logic performances and must be handled appropriately, taking into account the memory specifications, such as the static noise margin and minimum Vdd retention voltage [6]-[8].

This work presents a way to establish the link between the device-level wearout models and the architecture level. Combining the wearout models, the thermal profiles, and the electrical stress profiles, this work provides insight into lifetime-limiting wearout mechanisms, along with the reliability-critical microprocessor functional units for a system while taking into account a variety of use scenarios, composed of a fraction of time in operation, a fraction of time in standby, and a fraction of time when the system is off. This enables circuit designers to know if their designs will achieve an adequate lifetime and further make any updates in the designs to enhance reliability prior to committing the designs to manufacture.

#### **CHAPTER 1**

#### INTRODUCTION

Although constant technology scaling has resulted in considerable benefits, including smaller device dimensions, higher operating temperatures and electric fields have also contributed to faster device and interconnect aging due to wearout. Not only does this result in the shortening of microprocessor lifetimes, it leads to faster wearout resultant performance degradation with operating time. Microprocessor lifetime is a function of both device and backend wearout.

The analysis of frontend mechanisms is different than backend mechanisms. Backend mechanisms result in open and short circuits, which result in system failure directly, and hence it is sufficient to model the time-to-failure of components of the system and to combine them statistically. Frontend wearout mechanisms, on the other hand, cause a gradual weakening of the devices. The weakening is both random and a function of stress and temperature. However, unlike backend mechanisms, the relationship between the degradation and the circuit performances must be taken into account to determine the lifetime distribution.

Device lifetime is a function of two kinds of stress: electrical and thermal. An increase in either of the two results in decreased device reliability. The increase in device densities has been achieved through reduction in device dimensions, which means that the devices undergo increased electrical stresses during their lifetime. The resulting increase in operating frequency, as well as device densities, had led to greater thermal stress, which also increases with each new generation. A decrease in device reliability

and the increase in system complexity translate into systems whose lifetime characterization is both challenging due to the large number of devices that degrade simultaneously in modern systems and extremely critical because each device fails more quickly than in previous technologies. This work considers frontend wearout due to negative bias temperature instability (NBTI), positive bias temperature instability (PBTI), hot carrier injection (HCI), and transistor gate oxide breakdown (GOBD).

Besides wearout due to devices, each technology generation reduces the interconnect dimensions without always reducing the supply voltage in proportion, resulting in higher electric fields within the backend dielectric and within the metal lines, increasing wearout in the backend geometries. At the same time, as the dielectric constant (k) decreases to reduce parasitics, the porosity of materials must increase, at the possible cost of increasing the vulnerability of materials to breakdown. Additionally, the faster operating frequencies of processors result in decreased interconnect reliability, due to increases in both electrical current and operating temperature, increasing the risk of failure of chips due to backend wearout for the newer technology nodes. This work considers backend wearout due to electromigration (EM), stress-induced voiding (SIV) and backend time-dependent dielectric breakdown (BTDDB).

The physics describing IC failure mechanisms both in the frontend and in the backend has matured as a result of years of refinement to existing theories. However, the extension of these models to large and complex microprocessor systems has not proven to be straightforward and is complex. Microprocessor system reliability analysis requires techniques to extend the results gathered from small test structures to large complex microprocessors. Such an endeavor requires methods to manage the deluge of data that

comes with analyzing large numbers of complex layouts and devices degrading at different rates.

The purpose of this research is to present a methodology to assess microprocessor lifetimes and circuit performances due to NBTI, PBTI, HCI, GOBD, BTDDB, EM and SIV by developing the link between the device-level wearout models and the architecture level while taking into account realistic use scenarios [11]. This enables a designer to make any updates in the design to enhance reliability prior to committing a design to manufacture.

Since the wearout mechanisms being studied are activity and temperature dependent, the proposed framework determines the detailed thermal profiles of the systems under study, as well as the electrical stress of each net/device in the systems by running a variety of standard benchmarks. Microprocessors contain both logic and SRAM components. Hence, both types of blocks are considered in this work. Backend wearout mechanisms are handled differently than frontend wearout mechanisms.

Backend wearout mechanisms impact circuits by causing short circuits (for BTDDB) and open circuits (for EM and SIV). It is assumed that these open and short circuit failures cause the system to fail, except when the failure happens in a memory block utilizing error correction codes and/or reconfiguration through redundancy. Hence, backend wearout models involve combining the time-to-failure distributions of large numbers of components and the determination of whether a component failure causes a system to fail is not required. Analysis of lifetime due to the backend wearout mechanisms is based on layout analysis, layout feature extraction, where the wearout of

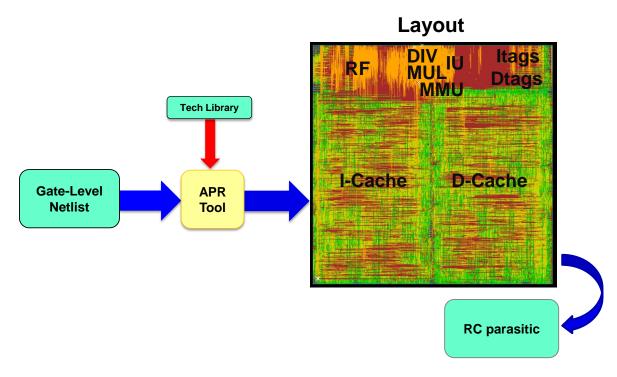

each feature is computed and the distributions are combined analytically to estimate the lifetime of the full system [1]-[5],[9],[10], as illustrated in Figure 1.1.

**Figure 1.1:** The flow of system-level modeling for backend wearout mechanisms.

Frontend wearout mechanisms, namely NBTI, PBTI, HCI, and GOBD, result in threshold voltage drifts and gate current leakage that impact circuit timing for logic blocks and SRAM performances. When studying logic blocks, we combine the electrical stress profiles, thermal profiles and device-level models, and apply statistical timing analysis (incorporating process variations) to identify the critical paths of the microprocessors and to characterize microprocessor performance degradation due to NBTI, PBTI, HCI and GOBD, as illustrated in Figure 1.2. Similarly, DC noise margins of SRAM cells are also analyzed due to NBTI, PBTI, HCI and GOBD degradation.

**Figure 1.2:** The flow of system-level modeling for frontend wearout mechanisms.

The impact of NBTI and PBTI on circuits has been previously studied with the older reaction diffusion theory ([12]-[17] for logic and [18],[19] for SRAMs) and the current trapping/detrapping theory ([20],[21] for logic and [22] for memory), which is also implemented in this work. Only simple ring oscillators are considered in [20], while providing evidence to validate trapping/detrapping theory over reaction diffusion theory.

In this work, as in prior work [23], oxide breakdown is modeled by inserting a gate-to-source resistance (R<sub>G2S</sub>) or gate-to-drain resistance (R<sub>G2D</sub>) in a target gate in order to create the current leakage path in the circuit. A percolation model is used to count the number of conduction paths and the time to soft breakdown (SBD) and hard breakdown (HBD) in the thin oxide layer, and a quantum point contact (QPC) model is used to calculate the SBD and HBD resistances.

Timing analysis is implemented in [21], including the updating of path selection throughout the aging process. However, prior work has involved smaller circuits and assumptions about stress distributions for each device [21],[22]. In this work we have used emulation to handle large systems running actual benchmarks to determine the actual activity of circuits and memory cells while running benchmarks. The results from

emulation are used to update timing analysis and analysis of memory performances based on actual usage patterns.

This work not only accounts for activity and temperature, but also accounts for the fact that processors are not in operation at all times. Realistic use conditions include operation modes, standby, and periods of time when the processor is turned off, as illustrated in Figure 1.3. This research presents a method to take these use scenarios into account.

**Figure 1.3:** The use scenarios provided by Intel are shown [11].

The rest of the thesis is organized as follows. Chapter 2 gives a brief overview of the related work and recent trends. Chapter 3 presents the device-level wearout models we have used in this research. Chapter 4 gives the overview of our system-level aging assessment framework. The methodology to determine model parameters through FPGA emulation is described. In Chapter 5, we study the lifetimes for the systems from our

simulator and present a comparison based on our results for backend wearout mechanisms. Chapter 6 describes our methodology to evaluate performance degradation of a microprocessor due to frontend wearout mechanisms and presents the degradation and lifetime results for logic blocks of the microprocessors. We also present analysis of SRAM noise margins under BTI, HCI and GOBD degradation. Chapter 7 concludes this work.

### **CHAPTER 2**

#### **BACKGROUND**

Aggressive technology scaling, resulting in higher operating temperatures, electric fields, and smaller device dimensions, has contributed to faster device aging. Historically, the major causes of wearout in the field have been electromigration (EM), gate oxide breakdown (GOBD), and hot carrier injection (HCI) [24]. EM [25]-[28] refers to the dislocation of metal atoms caused by momentum imparted by electrical current in interconnects and vias. The dislocation of metal atoms further causes interconnects to have increased resistance over time. The increase in resistance is design dependent, since it is a function of current density and temperature. Failure happens at joints between interconnect lines and vias, most often under the vias, where a void can form. Specifically, vias are damaged by downstream electron flow, from the via to the metal below it. GOBD [29]-[35] is detected by leakage currents through gate oxides. These leakage currents are a cumulative function of the local electric field over time and temperature. Failures in the gate oxide are caused by local thinning of the oxide due to lattice problems, such as the dislocation of an atom or the generation of traps. HCI [36]-[40] degrades device saturation current, threshold voltage, and the maximum transconductance over time, and it is due to velocity saturation effects and the reduction of charged interface states. Historically, HCI was only a major concern for NMOS devices, with PMOS devices showing comparatively negligible degradation because (a) holes have a smaller impact ionization rate and (b) holes face a higher  $S_i - S_i O_2$  barrier than electrons. However, subsequent reports have revealed that HCI effects on PMOS

devices is also observed [41]. The rate of degradation due to HCI is sensitive to operating conditions.

More recently, because of the introduction of new materials (copper, low-k intra and inter-layer dielectrics, high-k gate dielectrics), the increase in the number of interconnect layers with smaller geometries and higher current densities, and the concomitant increase in on-chip temperatures, new failure mechanisms have emerged, including bias temperature instability in PMOS and NMOS transistors, backend timedependent dielectric breakdown (BTDDB), and stress-induced voiding (SIV). Negative bias temperature instability (NBTI) in PMOS devices [42]-[45] is caused by the generation of interface traps under high temperature and negative gate bias and results in shifts in device parameters, such as threshold voltage, transconductance, device mobility, etc., but is generally identified by shifts in the threshold voltage [43]. Positive bias temperature instability (PBTI) has the same effect on NMOS transistors. Failures in the backend dielectric [46]-[53] are due to the alignment of trap sites which provide a low impedance path through the oxide that enables copper drift. Breakdown is detected by leakage current through the oxide. Finally, the impact of stress migration is high resistivity and opens at via sites. Stress migration is a function of interconnect geometry and is caused by the directionally biased motion of atoms in interconnects due to mechanical stress caused by thermal mismatch between metal and dielectric materials [54]-[56].

All of these wearout mechanisms cause parametric variation as a function of time. They degrade interconnect resistance, device saturation currents and/or threshold voltages, and increase the current through thin and thick oxides as a function of operating

conditions and temperature. All of these wearout mechanisms are accelerated with temperature, depend on thermal cycles (which can induce recovery for some mechanisms), and are exacerbated by thermomechanical mismatch of materials (which is degrading with the use of lower-k dielectrics in the backend).

System-level reliability analysis under realistic workloads has been studied for many years. The existing state-of-the-art is summarized in [57],[58]. In both approaches, the system is assumed to be a series combination of the components for reliability estimates, where if any component fails due to any wearout mechansism, the system fails.

In order to evaluate system-level behavior and insure reliable system operation, the gap between the established device-level wearout models and system behavior at the architecture level need to be bridged. In [59], a so-called RAMP model which conducts dynamic reliability management for analyzing microprocessor lifetime and reliability was proposed. The model assumes the device density throughout the chip is uniform and each device is identically vulnerable to failure mechanism. Later, the work proposed in [60] introduces a structure-aware model that takes into account the vulnerability of basic structures of the microarchitecture to different failure mechanisms. For the approaches to analyze system level reliability in [57]-[60], an exponential failure rate distribution is assumed. In this case the mean-time-to-failure of the chip,  $MTTF_{chip}$ , is a combination of the mean-time-to-failures due to each of the wearout mechanisms,  $MTTF_i$ . It is assumed that a MTTF can be computed for each wearout mechanism. Under these conditions,

$$MTTF_{chip} = 1/\sum_{i} (1/MTTF_{i}). \tag{2.1}$$

This distribution does not take into account randomness in the rates of wearout for the same failure mechanism for multiple components undergoing the same stress. Moreover,

it is unrealistic to use a *MTTF* to represent chip lifetime for each wearout mechanism since a chip is composed of a large number of elements, all failing at different rates, based on their temperature, electrical stress, and geometry. To account for variation in the wearout rate, the standard distribution used in industry is the two-parameter Weibull distribution, described by a characteristic lifetime,  $\eta$ , and a shape parameter,  $\beta$ . When probabilities of failure are combined with realistic failure rate distributions, as in [58], the formulas for the time-to-failure for a chip are less straightforward. Specifically, as illustrated in [61], for each wearout mechanism, i, let the characteristic lifetimes and shape parameters be  $\eta_i$  and  $\beta_i$ , respectively. The characteristic lifetime of the chip does not have a closed form solution, unless  $\beta_i$  is constant for all wearout mechanisms. Otherwise, the characteristic lifetime,  $\eta_{chip}$ , is the solution of [61]-[63]

$$1 = \sum_{i} (\eta_{chip} / \eta_i)^{\beta_i}. \tag{2.2}$$

The shape parameter for the chip is

$$\beta_{chip} = \sum_{i} \beta_{i} (\eta_{chip}/\eta_{i})^{\beta_{i}}. \qquad (2.3)$$

The lifetime at probability point, P, is

$$-\ln(1-P) = \sum_{i=1}^{n} (t/\eta_i)^{\beta_i} . \tag{2.4}$$

All prior work begins with device-level models of each wearout mechanism. For instance, NBTI is a function of the build-up of interface traps, which increases as a power low function of the time under stress. When stress is removed there is a recovery, which reduced the interface traps as a function of time. The number of interface traps translates directly into a shift in the threshold voltage. However, prior work does not say much about how much of a threshold voltage shift can be tolerated by the system, and when a specific threshold voltage shift results in hard failure. The hard breakdown point is a

function of the circuit design and type of component. Similarly, GOBD is a function of stress of the oxide, which causes the formation of traps in the oxide. When the traps increase to a critical level, the leakage current through the oxide increases. When the leakage current exceeds a limit, hard breakdown occurs, and the circuit no longer functions correctly. The limit at which hard failure occurs is a function of the type of circuit and circuit specifications.

The long-term threshold voltage drifts induced by NBTI, PBTI and GOBD degrade SRAM cell stability, margin, and performance, and lead to eventual functional failure. During SRAM design, it is important to build in design margins to achieve an adequate lifetime [64],[65]. As this has become more challenging, several authors have proposed methods to improve SRAM reliability in the presence of NBTI/PBTI and GOBD degradation. These approaches include circuitry that periodically flips the data in an SRAM cell to reduce failure rates [66], the use of redundancy [67]-[69], error correcting codes [70],[71], and both [72]. Evaluation of these methods requires a model of cell stress. Assumptions are usually made about the stress distribution among cells. This is because characterizing each SRAM cell based on actual operating conditions is not straightforward.

All prior work relies on system-level benchmarks, and realistic workload models. But, little is said about the simulation method and limitations. In [73], a system-level reliability simulator was developed that includes EM, SIV, GOBD, and thermal cycling based on process-level models. However, the implementation is limited to 50,000 or fewer devices. Benchmarks for architicture evaluation are complex, and it is not possible to model system operation in software only. Hardware/software emulation is required.

Even with hardware/software emulation, a simulation of a standard benchmark can take several days. Such simulations are inadequate for analyzing product lifetimes. Hence, sampling of system activity, in combination with hardware/software emulation is required to estimate system wearout for each sample, associated with specific variation in process parameters and wearout parameters.

### **CHAPTER 3**

#### DEVICE-LEVEL WEAROUT MODELS

The first step in insuring reliable system operation is to bridge the gap between the established device level wearout models and system behavior at the architecture level. The current mean time to failure (MTTF) based high level reliability models, such as [74],[75], only provide us with crude, single point, reliability estimates based on the assumption that the system is a series failure system.

These methods assume an exponential failure rate distribution and that we can compute a MTTF for each mechanism and each block. However, each block is composed of a large number of elements, all failing at different rates, based on their temperature, electrical stress, and geometry.

Moreover, component failure rates are typically modeled with a Weibull or Lognormal distributions, rather than exponential distributions. Hence, the methodology to determine the MTTF for each block, as required in [74],[75], is not clear. Instead, we work with process-level models directly, and propagate these models to system-level models.

In this chapter we begin by presenting the detailed wearout models for microprocessor system components. Incorporating accurate electrical stress distributions for whole systems and functional units, accounting for the operating temperature and all vulnerable areas in layouts, our methodology establishes a link between the device level wearout models and the architecture level to estimate lifetimes more accurately for different wearout mechanisms.

Wearout mechanisms can be divided into two broad categories, the voltage (or E-field) dependent wearout mechanisms, such as NBTI, PBTI, GOBD, and BTDDB etc., and the current-stress dependent wearout mechanisms, such as EM and HCI. Due to the lack of higher level models for the progressive effect of these mechanisms, it is necessary to first model their effects at the device level and then abstract the models to the systeme level.

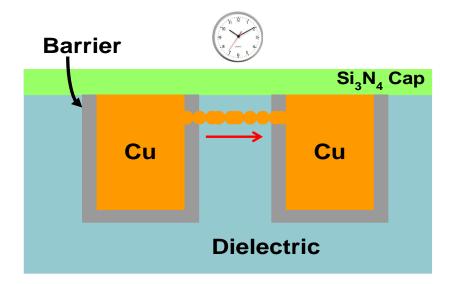

# 3.1 Backend Time-Dependent Dielectric Breakdown (BTDDB)

Dielectric breakdown is the irreversible local breakdown of a dielectric's insulation property. Time-dependent dielectric breakdown (TDDB) is dielectric breakdown that takes place after a constant application of an electric field (E), lower than the breakdown field, to the dielectric, as illustrated in Figure 3.1. TDDB results in the local development of a very small spot with increased conductivity compared to the rest of the dielectric, resulting in a change in the electrical characteristics of the dielectric [76]. In interconnects, TDDB of the low-k dielectric leads to catastrophic breakdown of the system.

**Figure 3.1:** Cross section of an example dual-damascene Cu/Low-k interconnect under BTDDB.

The characteristic lifetime of a dielectric segment of the microprocessor, with vulnerable length,  $L_i$ , associated with linespace,  $S_i$ , is [61]-[63]

$$\eta = A_{BTDDB} L_i^{-1/\beta_i} exp(-\gamma E^m - E_a/kT), \tag{3.1}$$

where  $A_{BTDDB}$  is a constant that depends on the material properties of the dielectric,  $\gamma$ , is the field acceleration factor, m is one for the E model [77] and 1/2 for the  $\sqrt{E}$  model [78]. The electric field is a function of voltage, V, and the linespace, S, between the two lines surrounding a dielectric segment, i.e., E=V/S. The electric field, temperature (T), and geometry  $(L_i)$  determine the characteristic lifetime,  $\eta$ . The temperature dependence is modeled with the Arrhenius relationship [79], where k is the Boltzmann constant.

It should be noted that process data comes from test structures that are stressed with DC stress, while the microprocessor dielectrics undergo AC stress. Since BTDDB is most often (but not always) manifested as an abrupt and irreversible increase in the

leakage current when a dielectric segment is under constant bias stress at elevated temperature [80]-[83], the impact of switching on the dielectric segment is negligible. Hence, for segments of the microprocessor, it is sufficient to determine the time that each dielectric segment is under stress. To translate the DC stress of the test structure to the AC stress of the circuit, we compute the probability that each adjacent net has opposite voltages,  $\alpha$ . To do this, we collect the electrical state profiles of each net within the microprocessor while running standard benchmarks [84] using FPGA emulation described in Section 4. First, we find the probability,  $p_i$ , that each net is at logic "1". We then compute the stress probability of a dielectric segment as the probability that the two adjacent nets are at different logic states. If the adjacent state probabilities are  $p_i$  and  $p_2$ , then

$$\alpha = p_1(1 - p_2) + p_2(1 - p_1). \tag{3.2}$$

Equation (3.2) has been verified by comparing the exact stress durations of random-selected vulnerable dielectric segments from an example system layout with the ones calculated. The result, as illustrated in Figure 3.2, shows the percent errors are less than 15% for more than 80% of the selected samples. The high errors are mostly from the dielectric segments in deeper locations of the circuit. Since errors are accumulative, more activity propagation due to deeper stages leads to a bigger difference between real stress probabilities and calculated ones.

Figure 3.2: Percent error distribution of the random-selected dielectric segments.

#### 3.1.1 Vulnerable Dielectric Area and Test Structures

In order to calculate the vulnerability of a layout to BTDDB, the BTDDB simulator operates by breaking down the dielectric in each layer and each block into dielectric segments. Each dielectric segment is characterized by a vulnerable length,  $L_i$ , and a linespace,  $S_i$ . The vulnerable length,  $L_i$ , is defined as the length of a block of dielectric between two copper lines separated by linespace  $S_i$ , illustrated in Figure 3.3. A given layout is analyzed by determining the pairs  $(S_i, L_i)$  for each layer for all linespaces.

**Figure 3.3:** The vulnerable length associated with a linespace is shown. The rectangles are copper wires, surrounded by the backend dielectric.

Test structures have been designed to assess the impact of linespace and area on Cu/low-k TDDB. The details of the test structures, their design and results, are given in [9]. The test structure in Figure 3.4(a) is used to determine the lifetime of the dielectric between parallel tracks with a specific line spacing. This test structure has a fixed linespace, S, and vulnerable length, L. The vulnerable area is LS. To test the lifetime of such a feature, a voltage difference is applied between the two combs. The current between the combs is monitored to determine the time-to-failure. The data set from several samples is fit with a Weibull distribution to estimate  $\eta_t$  and  $\beta_t$ .

**Figure 3.4:** Top views of comb test structures to characterize the impact of geometry on time-dependent dielectric breakdown. (a) Standard comb structure, (b) PTT, (c) TLa, (d) TLb, (e) TTa, and (f) TTb.

Because the features on a chip differ from a test structure layout, area scaling must be performed to adjust the lifetime to take into account the difference in vulnerable area between the chip and the test structure. To do this, let  $L_t$  and  $L_i$  be vulnerable lengths of the test structure and chip, i.e. the length of the lines that run in parallel in the test structure and chip, respectively, with the same linespace, S.  $\eta_t$  is determined by stressing a test structure with linespace S and vulnerable length  $L_t$ . Then the corresponding characteristic lifetime for that feature in the chip is

$$\eta_i = \eta_t \left(\frac{L_t}{L_i}\right)^{1/\beta}.\tag{3.3}$$

Test structures that have several irregular features have been designed in order to determine any impact of field enhancement. Figure 3.4(b)-(f) shows the top views of these test structures and the fragments of these test structures are shown in Figure 3.5. PTT emphasizes the electric field between parallel routing tracks that end at the same point. TLa and TLb emphasize the electric field between line ends and perpendicular lines. TLb includes additional fringing fields, since the line ends are more widely spaced. TTa and TTb emphasize electric fields between line ends. In TTa, the line ends abut, and in TTb the line ends are in parallel tracks. TLa, TLb, TTa, and TTb have 528 line ends each. The separation between line ends is the same for all test structures.

Figure 3.5: Vulnerable line ends that need to be extracted from a layout.

All test structures in Figure 3.3 have the same minimum line space, 140nm. If the drawn line space is consistent with the printed line space, then the relative influence of each geometry would be the same. Moreover, the number of vulnerable line ends for each geometry in Figure 3.4(c)-(f) is constant, i.e. 528 line ends each. Hence, when comparing the test structure in Figure 3.4(c)-(f), no area scaling is required (using equation (3.3)) when comparing the results. On the other hand, we require area scaling to determine if the test structures in Figure 3.4(b)-(f) result in an increase failure rate in comparison with parallel lines, as in Figure 3.4(a). The test structures were tested at 3.6MV/cm and at 150°C, and the current between the lines was monitored. A current limit of 10 µA was set to detect dielectric breakdown.

To account for irregular features, the counts of the features are extracted from the layout. Each add additional parameters,  $\eta_{PTT}$ ,  $\beta_{PTT}$ ,  $\eta_{TLa/b}$ ,  $\beta_{TLa/b}$ ,  $\eta_{TTa}$ ,  $\beta_{TTa}$ ,  $\eta_{TTb}$ , and  $\beta_{TTb}$  to (2.2) and (2.3). These parameters depend on the number of minimally spaced line ends in each category of the layout. Let's consider the computation of  $\eta_{TLa/b}$  for the sake of illustration. Let's suppose the test structure has  $N_{test}$  minimally spaced line ends, from which  $\eta_{test}$  and  $\beta_{TLa/b}$  are computed. Then, for a layout with  $N_{chip}$  similar line ends, by area scaling

$$\eta_{TLa/b} = \eta_{test} \left( \frac{N_{test}}{N_{chip}} \right)^{1/\beta_{TLa/b}}.$$

(3.4)

#### 3.1.2 Test Results

Let's suppose that there is no field enhancement due to any of the features in Figure 3.4(b)-(f). Then the lifetime data from the test structure in Figure 3.4(a) would be sufficient to predict the lifetimes of the test structures in Figure 3.4(b)-(f). We make this

assumption and extract the vulnerable length, L, and linespace, S, for the test structures in Figure 3.4(a)-(f).

Next, we compare the measured Weibull curves for the test structures in Figure 3.4(b)-(f) with the Weibull curve from the standard comb test structure with the same linespace, *S*, in Figure 3.4(a), area scaled [36] – by using the Poisson area scaling invariance of the Weibull distribution – to match the vulnerable length of the test structures in Figure 3.4(b)-(f).

Specifically, let  $N = L_t/L_i$  be the ratio of vulnerable length, where  $L_t$  corresponds to the vulnerable length of the standard comb structure in Figure 3.4(a) and  $L_i$  corresponds to the vulnerable length in one of Figure 3.4(b)-(f). To area-scale the standard comb structure to give us the lifetime distribution for a different (smaller) vulnerable area, we plot

$$\ln \eta_t = \ln TF - \frac{1}{\beta} \ln \left( -\frac{1}{N} \ln (1 - P(TF)) \right) . \tag{3.5}$$

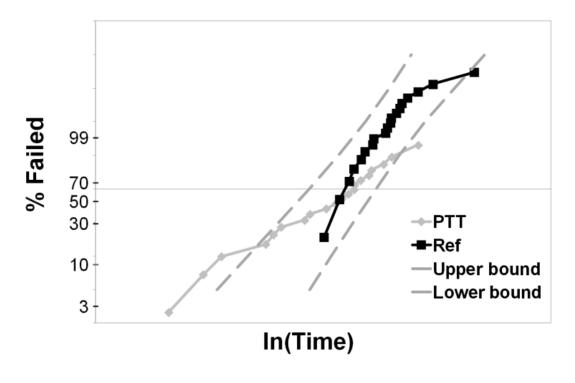

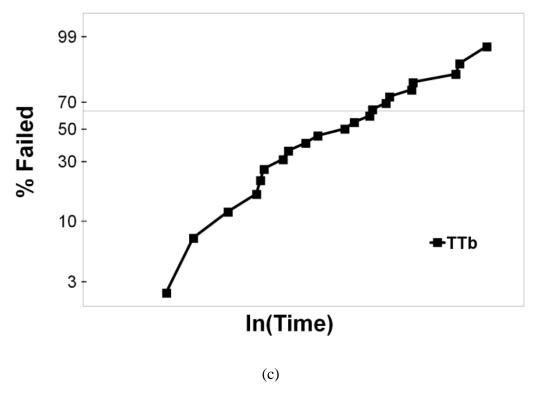

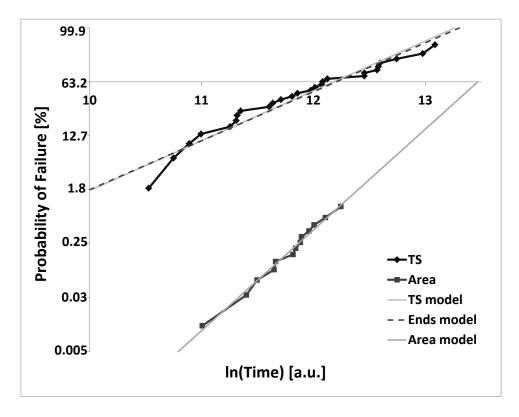

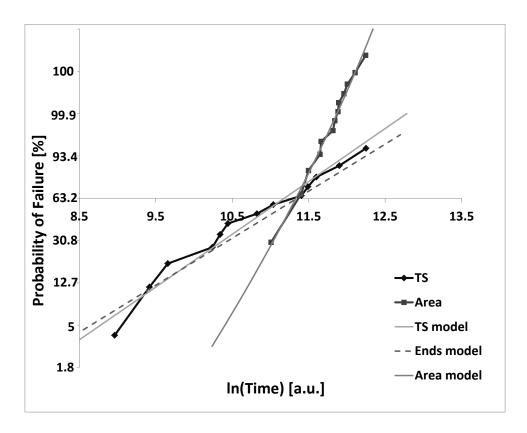

The line end features in Figure 3.5 were found to have a significant impact on lifetime. The data collected from the test structures is presented in Figure 3.6. An area scaled version of a standard comb test structure is included for comparison. It can be seen that all test structures (PTT, TLa, TLb, TTa, and TTb) result in a significantly reduced lifetime in comparison with the reference test structure. The data also indicate that TLa and TLb fail at the same rate, showing that fringing fields are not significant. The data from these two test structures can be merged to determine a single model. TTa has an improved lifetime, in comparison with TLa/b. No reference curve is included for comparison for TTb because TTb has no vulnerable length.

(a)

(b)

**Figure 3.6:** Data collected from (a) PTT vs. the reference structure, (b) TLa, TLb, and TTa vs. the reference structure, and (c) TTb.  $2\sigma$  confidence bounds are included for the area scaled reference test structure.

Since the test results indicate all of the line ends create an increased vulnerability for PTT, TLa, TLb, TTa, and TTb and fail more rapidly, the counts of the vulnerable line ends with these geometries need to be incorporated separately from the vulnerable length in the simulator when estimating the wear-out of a full chip.

## 3.1.3 Model Constructions for Irregular Geometries

A model was extracted for PTT, TLa/b, TTa, and TTb. The model for TTa and TTb was found with the standard method, involving fitting a linear function to the data to find  $\eta_{TTa}$ ,  $\beta_{TTa}$ ,  $\eta_{TTb}$ , and  $\beta_{TTb}$ .

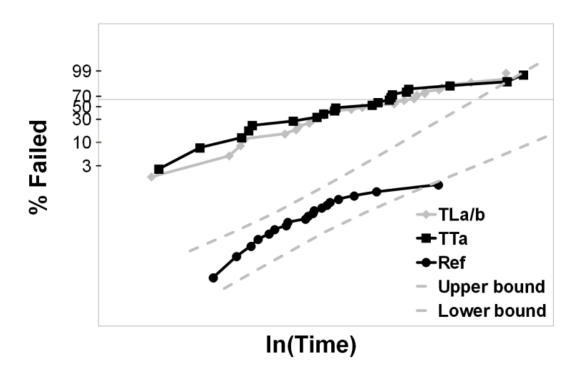

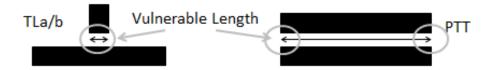

Extraction of the model for TLa/b and PTT is more complex, since these structures combine both line ends and vulnerable length. Figure 3.7 shows one TTa/b line end and two PTT line ends, together with the vulnerable length extracted. If one finds  $\eta_{TLa/b}$ ,  $\beta_{TLa/b}$ ,  $\eta_{PTT}$ , and  $\beta_{PTT}$  by fitting a linear function, then the model would include both the impact of the line ends and the vulnerable length. For circuit analysis purposes, it is necessary to eliminate the effect of vulnerable length to create a model for line ends only. To find the model for line ends, it is necessary to subtract the effect of vulnerable length. Let  $\eta_{TS}$  and  $\beta_{TS}$  be the measured data from the test structures TLa/b and PTT. For each of these test structures we need to determine  $\eta_{ends}$  and  $\beta_{ends}$ , after eliminating the component due to vulnerable area,  $\eta_{area}$  and  $\beta_{area}$ . The parameters,  $\eta_{area}$  and  $\beta_{area}$ , are determined from the area scaled data from the reference test structure.

**Figure 3.7:** Vulnerable length and line ends extracted from test structure TLa/b and PTT. The vulnerable length is indicated with arrows and the line ends are indicated with circles.

Relying on equations (2.2) and (2.3), we have that

$$1 = \left(\frac{\eta_{TS}}{\eta_{ends}}\right)^{\beta_{ends}} + \left(\frac{\eta_{TS}}{\eta_{area}}\right)^{\beta_{area}} \tag{3.6}$$

and

$$\beta_{TS} = \beta_{ends} \left( \frac{\eta_{TS}}{\eta_{ends}} \right)^{\beta_{ends}} + \beta_{area} \left( \frac{\eta_{TS}}{\eta_{area}} \right)^{\beta_{area}}.$$

(3.7)

Rearranging the equations results in

$$\beta_{ends} = \frac{\beta_{TS} - \beta_{area} \left(\frac{\eta_{TS}}{\eta_{area}}\right)^{\beta_{area}}}{1 - \left(\frac{\eta_{TS}}{\eta_{area}}\right)^{\beta_{area}}}$$

(3.8)

and

$$\eta_{ends} = \eta_{TS} \left( 1 - \left( \frac{\eta_{TS}}{\eta_{area}} \right)^{\beta_{area}} \right)^{-1/\beta_{ends}}.$$

(3.9)

These equations were used to extract the model for TLa/b. Because of the large separation between the data and the reference, the shift in  $\eta$  and  $\beta$  due to subtracting the impact of vulnerable area is less than 0.1% and 1%, respectively. This is illustrated in Figure 3.8.

**Figure 3.8:** Data collected from TLa/b vs. the reference structure. The models for the data from the test structure and the line ends, after subtracting the effect of area are nearly indistinguishable.

Equations (3.8) and (3.9) cannot be used for PTT. This is because equations (2.3) and (3.7) were derived by finding the probability density function of the combined failure rate as a function of the underlying parameters, converting to the Weibull probability scale (i.e.  $\ln(-\ln(1-P))$ ), and evaluating the slope at the characteristic lifetime,  $\eta$ . As can be seen from Figure 3.5(a), PTT impacts lower probabilities, and the slope is not well defined at the x-intercept of the Weibull plot.

Instead, we need to find  $\eta_{ends}$  and  $\beta_{ends}$  by defining the probability density function for the test structure as a function of TF, for any value of TF, i.e.,

$$P(TF) = 1 - exp\left(-\left(\frac{TF}{\eta_{TS}}\right)^{\beta_{TS}}\right). \tag{3.10}$$

Since this probability density function results from two independent mechanisms, we also have that

$$P(TF) = 1 - exp\left(-\left(\frac{TF}{\eta_{ends}}\right)^{\beta_{ends}} - \left(\frac{TF}{\eta_{area}}\right)^{\beta_{area}}\right). \tag{3.11}$$

Hence,

$$\left(\frac{TF}{\eta_{ends}}\right)^{\beta_{ends}} + \left(\frac{TF}{\eta_{area}}\right)^{\beta_{area}} = \left(\frac{TF}{\eta_{TS}}\right)^{\beta_{TS}}.$$

(3.12)

We solve for the unknowns,  $\eta_{ends}$  and  $\beta_{ends}$ , by finding the best fit to the data in the range where end failures are dominant, through linear regression. The results are shown in Figure 3.9.

**Figure 3.9:** Data collected from PTT vs. the reference structure. The graph shows the models for the data from the test structure vs. the line ends, after subtracting the effect of area.

### 3.1.4 Vulnerable Length and Feature Extraction

BTDDB requires the determination of the vulnerable length of the dielectric segments as a function of linespace. A layout extraction tool has been developed using the standard object oriented programming languages. A detailed description of the algorithm is given in Algorithm 3.1.

```

Input: The maximum line spacing S_{max} and a layout L

Output: Tables of vulnerable lengths (VulnerableLengthTable) and new features (TLab, TTa,

TTb, PTT)

for each metal layer m do

LineDataX (m) \leftarrow \text{ReadLines } (L); // BucketSort

LineDataY (m) \leftarrow \text{ReadLines } (L); // BucketSort

TTa (m) \leftarrow 0; TTb (m) \leftarrow 0; PTT (m) \leftarrow 0; TLab (m) \leftarrow 0;

c \leftarrow 1;

n \leftarrow 2:

while c < N_{line} do // N_{line}: # lines in LineDataY

L_1 \leftarrow \text{LineDataY } (m,c); // c\text{-th line}

L_2 \leftarrow \text{LineDataY } (m,n); // n\text{-th line}

if Spacing (L_1, L_2) <= S_{max} then

TLab (m) += CheckTLab (L_1, L_2); // check TLab between L_1 and L_2

TTa (m) += CheckTTa (L_1, L_2); // check TTa between L_1 and L_2

end

n \leftarrow \text{Adjust } (c, n);

L_2 \leftarrow \text{LineDataX}(m,n);

if Spacing (L_1, L_2) <= S_{max} then

TLab (m) += CheckTLab (L_1, L_2); // check TLab between L_1 and L_2

end

n \leftarrow \text{Adjust}(c, n);

L_2 \leftarrow \text{LineDataY}(m,n);

if Spacing (L_1, L_2) <= S_{max} then

PTT (m) += CheckPTT (L_1, L_2); // check PTT between L_1 and L_2

TTb (m) += CheckTTb (L_1, L_2); // check TTb between L_1 and L_2

VulnerableLengthTable (m) \leftarrow VulnerableLength (L_1, L_2);

LineDataY (m) \leftarrow Split(L_1, L_2);

n \leftarrow \text{Adjust}(c, n);

end

n \leftarrow \text{Adjust } (c, n);

end

end

```

**Algorithm 3.1**: Layout extraction flow

Vulnerable area and features are extracted by comparing two lines in a given layout. Since tens of millions of lines exist in each metal layer in a layout, it is necessary to find two adjacent lines forming a vulnerable area or a feature in a short time. Therefore, vulnerable area and features are extracted as follows. First of all, lines are read from a

given layout, sorted by the bucket sort algorithm, and stored in two separate data variables, LineDataX and LineDataY. The lines in LineDataX (or LineDataY) are sorted in the ascending order of the x-coordinates (or y-coordinates) of the bottom left corner of the lines. If two lines have the same x-coordinate (or y-coordinate), they are sorted in the ascending order of the y-coordinates (or x-coordinates) of the bottom left corner of the lines. Then, the extraction process starts by comparing the first  $(L_1)$  and the second  $(L_2)$ lines in the first bucket of LineDataY. Since each metal layer has a preferred routing direction (horizontal or vertical), the preferred routing direction is assumed to be horizontal in this explanation. Then, the y-coordinates of the two lines in the same bucket are the same, so they can form TTa or TLa/b depending on the distance between them and the direction (horizontal or vertical) of the lines. Whether or not they form TTa (or TLa/b) or not, the first line does not form any features with other lines in the same bucket because the second line lies between the first and the other lines in the bucket. Then the index of the second line is adjusted to find TLa/b between  $L_1$  and other vertical lines. If  $L_1$  is horizontal,  $L_2$  should be vertical to form TLa/b with  $L_1$ , so LineDataX is searched based on the x-coordinate of the bottom right corner of  $L_1$  to find  $L_2$  that can form TLa/b with  $L_1$ .

TTb or PTT is extracted by comparing two lines in different buckets (lines in different buckets have different y-coordinates) in LineDataY. Therefore, the index of  $L_2$  is adjusted and whether they form TTb or PTT is checked. If TTb or PTT is found, the flag of the edge of  $L_1$  forming TTb or PTT with  $L_2$  is set. By setting the flag, counting TTb or PTT formed by  $L_1$  and  $L_3$  is avoided when the x-coordinate of  $L_3$  is the same as that of  $L_2$  and the distance between  $L_1$  and  $L_3$  is less than the maximum line spacing.

After extracting irregular features formed by  $L_1$  and its adjacent lines, the vulnerable length between  $L_1$  and  $L_2$  is extracted. If the vertical spacing is less than or equal to the maximum line spacing, a vulnerable area surrounded by these two lines exists, so the vulnerable length is added to the vulnerable length table. Then,  $L_1$  is split into one or two new lines, they are inserted into LineDataY, and  $L_1$  is removed from LineDataY.

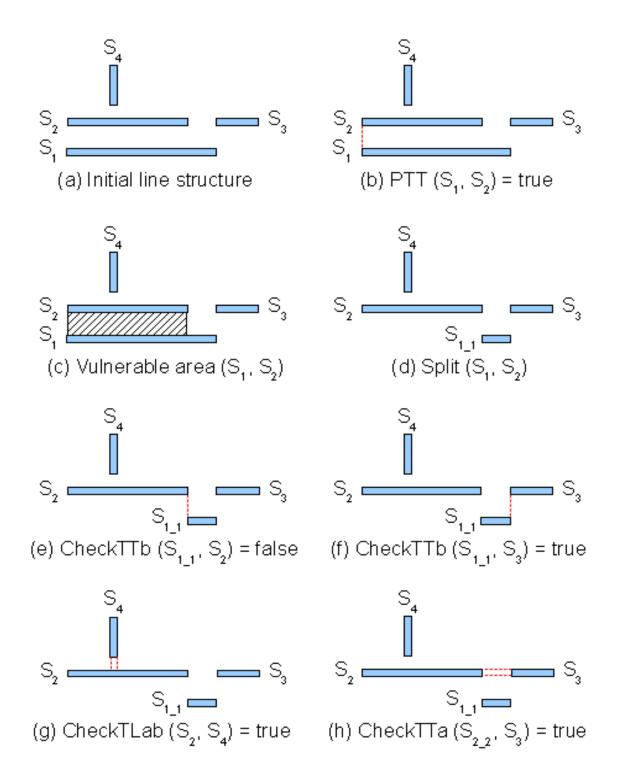

Figure 3.10 shows an example with four lines,  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ . The algorithm starts with the first line segment,  $S_1$ .  $S_1$  forms PTT with  $S_2$  (when the distance between them is smaller than the maximum line spacing) as shown in Figure 3.10(b). They also form a vulnerable area as shown in Figure 3.10(c), so the vulnerable length is added to the vulnerable line table. Then,  $S_1$  is split into new lines. In this example, only one new line  $(S_{1-1})$  is created because the left boundaries of  $S_1$  and  $S_2$  are aligned as shown in Figure 3.10(d). After inserting  $S_{1-1}$  into LineDataY,  $S_1$  is set to  $S_2$ , and the extraction process is repeated between them. TTb exists between  $S_{1-1}$  and  $S_2$  as shown in Figure 3.10(e). Similarly, TTb exists between  $S_{1-1}$  and  $S_3$  in Figure 3.10(f). Since  $S_{1-1}$  does not overlap with other lines,  $S_1$  is set to  $S_2$  and  $S_3$  in Figure 3.10(g), and TTa is extracted between  $S_2$  and  $S_3$  in Figure 3.10(h).

**Figure 3.10:** (a) Initial line structure. (b) PTT is extracted from S1 and S2. (c) Vulnerable length between S1 and S2 is extracted. (d) Postpocessing after vulnerable area extraction. (e) TTb does not exist between S1\_1 and S2. (f) TTb is extracted from S1\_1 and S3. (g) TLa/b is extracted from S2 and S4. (h) TTa is extracted from S2 and S3.

Complexity of vulnerable feature extraction is O(n), where n is the number of features, since bucket-sort algorithm is used. Complexity of extracting statistics from features is also O(n), because the bucket is scanned from the bottom most element, and the maximum number of features within a fixed distance from an element is constant. Hence, layout feature extraction is linear in terms of the number of geometries analyzed and is linear as a function of the area of a chip.

After extraction of the dielectric segments' length and linespace, each dielectric segment is linked to its thermal and stress profile in order to compute its characteristic lifetime with equation (3.1). Temperature is a function of the location of the segment in the layout, and stress is a function of the state probabilities of the adjacent nets.

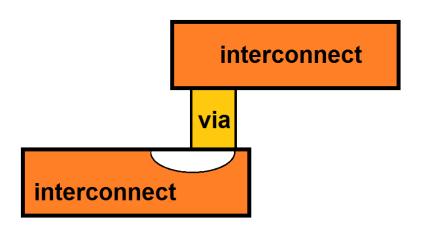

## 3.2 Electromigration (EM)

EM refers to the dislocation of metal atoms caused by momentum imparted by electrical current in interconnects and vias. The vulnerable location is the interconnect/via interface, where a void can form, as illustrated in Figure 3.11. Specifically, vias are damaged by downstream electron flow, from the via to the metal below it. This is because the via and the line below it are formed by separate deposition steps, which creates a vulnerable interface. Hence, although EM can be observed in interconnect lines, it is much more likely to be seen at via interfaces [85],[86]. Therefore, this work focuses on EM in vias, rather than in the significantly less vulnerable interconnect lines. The characteristic lifetime,  $\eta$ , of a via due to EM can be modeled as [87]-[90]:

$$\eta = A_{EM} T/j, \tag{3.13}$$

where T is temperature, j is the current density, and  $A_{EM}$  is a technology dependent constant that takes into account the velocity of the void, the resistivity of the metal, surface diffusivity, surface thickness, the thickness of the line, and the via size. The data on EM used in this study comes from Choi's experimental data [87].

**Figure 3.11:** An example vulnerable interconnect/via interface under EM.

In order to calculate the vulnerability of a layout to EM, the EM simulator operates by determining the characteristic lifetime of each via within each interconnect segment in the microprocessor layout. To do this, we find the current density of each interconnect, by collecting the switching activity profiles of each interconnect segment while running standard benchmarks [84] using FPGA emulation. When calculating the corresponding current density for each via on an interconnect, since the current always flows from a via on one end of an interconnect to the vias on the other end, we assume that one of the vias on an interconnect segment experiences EM degradation during the rising/falling transitions and the rest of the vias experience degradation during the opposite transition for signal nets. On the other hand, only one of the vias in each power

supply/ground net experiences degradation, because current flow in power supply/ground nets is unidirectional.

The Automatic Place and Route (APR) tool [91] has been used to collect the via locations and total number of vias connected to each interconnect segment,  $v_i$ , when the system layouts are generated. The computational cost is O(1). One via is assumed to be impacted by rising/falling transitions and the rest,  $(v_i - 1)$  are assumed to be impacted by the opposite transition. The corresponding current density,  $j_{interconnect}$ , for rising or falling transitions, is averaged over each via at each end of an interconnect, to give us the average via current densities,  $j_{via}=j_{interconnect}$  and  $j_{via}=j_{interconnect}/(v_i - 1)$ , respectively. To verify average via current densities, the actual current densities of randomly-selected vias are calculated based on the real interconnect geometries and compared with their average via current densities. The result, as illustrated in Figure 3.12, shows the percent errors are less than 10% for more than 80% of the selected samples.

**Figure 3.12:** Percent error distribution of the random-selected via current densities.

The location of each via/interconnect segment is determined to provide a link to its thermal profile, to find the characteristic lifetime of each via with equation (3.13).

# 3.3 Stress-Induced Voiding (SIV)

SIV damage is caused by the directionally biased motion of atoms in interconnects due to mechanical stress caused by thermal mismatch between metal and dielectric materials, as illustrated in Figure 3.13. As with EM, the failure site is at the via interfaces. This interface is vulnerable because the via and the line below it are formed by separate deposition steps. SIV depends on the geometry above a via, because larger geometries result in more material expansion and contraction with temperature, which in turn creates greater stress at the vulnerable via interface. Based on the SIV dependence

on both temperature and geometric linewidth of the interconnect above a via, the characteristic lifetime,  $\eta$ , of a via under SIV is given by [92],[93]:

$$\eta = A_{SIV}W^{-M}(T_0 - T)^{-N}exp(E_a/kT)$$

(3.14)

where W is the linewidth, M is the geometry stress component,  $T_0$  is the stress-free temperature, N is the thermal stress component, and  $A_{SIV}$  is a constant. SIV depends on switching activity to the extent that switching activity increases temperature. The data used in our study of SIV comes from Yao's experimental data [92].

Figure 3.13: An example vulnerable interconnect/via interface under SIV.

In order to find the lifetime of each via with equation (3.14), the width of the interconnect segment above each via is extracted from the layout, and the location of each via is determined, to provide a link to the thermal profile.

# 3.4 Negative/Positive Bias Temperature Instability (NBTI/PBTI)

Bias temperature instability, as the name suggests, causes instability in device behavior and is a result of the bias stress applied to it. NBTI is the degradation of a PMOS device under negative gate stress, and PBTI is the degradation of an NMOS device under positive gate stress. NBTI and PBTI result in shifts in device parameters, such as threshold voltage, transconductance, device mobility, etc., but are generally identified by shifts in the threshold voltage.