# SYSTEMS AND APPLICATIONS FOR PERSISTENT MEMORY

A Thesis Presented to The Academic Faculty

by

Subramanya R. Dulloor

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the College of Computing

Georgia Institute of Technology December 2015

Copyright  $\bigodot$  2016 by Subramanya R. Dulloor

## SYSTEMS AND APPLICATIONS FOR PERSISTENT MEMORY

Approved by:

Prof. Karsten Schwan, Committee Chair College of Computing Georgia Institute of Technology

Prof. Karsten Schwan, Adviser College of Computing Georgia Institute of Technology

Prof. Ada Gavrilovska College of Computing Georgia Institute of Technology

Prof. Umakishore Ramachandran College of Computing Georgia Institute of Technology Prof. Moinuddin Qureshi School of Electrical and Computer Engineering Georgia Institute of Technology

Prof. Sudhakar Yalamanchili School of Electrical and Computer Engineering Georgia Institute of Technology

Prof. Ling Liu College of Computing Georgia Institute of Technology

Date Approved: 27 October 2015

To the memory of my daughter, Rhea Anand Dulloor To my wife (Ruchi Anand) and my parents (Mohan and Suguna) To the memory of my advisor, Karsten Schwan

## ACKNOWLEDGEMENTS

It has been quite a journey reaching this point; one that would not have been possible without the support of numerous people in my life.

First of all, I would like to thank my advisor Prof. Karsten Schwan. Prof. Schwan was the most supportive advisor one could ever hope for. He was there for me during the toughest times of my life, not only as an advisor but also as a mentor and as a symbol of strength. I would have never reached this stage without him and I will miss him. I would also like to thank Dr. Ada Gavrilovska and Dr. Mustaque Ahamad for mentoring and advising me at various points in my research.

My mentors at Intel (Rajesh Sankaran, Jeff Jackson, and Rich Uhlig) deserve special gratitude for their unwavering support over the last 5 years. Without their guidance and patience, I would have given up a long time ago.

The one thing that this journey has taught me is the importance of a good support system. I will forever be grateful to all my friends and colleagues who helped me stay motivated through the years. Vaibhav Dubey, Seema Dubey, Sanjay Kumar, Priyalee Kushwaha, Abhishek Dhanotia, Sabina Grover, Reagan Lopez, Bhavani Krishnan, Dheeraj Reddy, and Amitabha Roy deserve special mention.

Finally, I would like to thank my parents (Mohan and Suguna), my grandparents (Shyamala and Gauri), and my sisters (Pratima, Shalini, and Lakshmi) for their love and support. Above all, I would like to thank my wife Ruchi Anand, the most important person in my life. She has been a source of strength through the ups and downs of life for the last 10 years. We look forward to making up for the lost time.

# TABLE OF CONTENTS

| DED  | ICAT       | TON .   |                                                                 | iii  |

|------|------------|---------|-----------------------------------------------------------------|------|

| ACK  | NOW        | LEDG    | EMENTS                                                          | iv   |

| LIST | OF         | TABLE   | SS                                                              | viii |

| LIST | OF         | FIGUR   | ES                                                              | ix   |

| SUM  | MAR        | Υ       |                                                                 | xi   |

| Ι    | INT        | RODU    | CTION                                                           | 1    |

|      | 1.1        |         | Statement                                                       | 4    |

|      | 1.2        |         | butions                                                         | 5    |

|      | 1.3        |         | ization                                                         | 6    |

| II   | тнғ        | 0       | RID MEMORY EMULATOR                                             | 7    |

| 11   | 2.1        |         | round                                                           | 7    |

|      | 2.1<br>2.2 | 0       | mulator Platform                                                | 8    |

|      |            |         |                                                                 |      |

| III  |            |         | OFTWARE FOR PERSISTENT MEMORY                                   | 13   |

|      | 3.1        |         | round                                                           | 13   |

|      | 3.2        | System  | a Architecture                                                  | 18   |

|      | 3.3        | PMFS    | Design and Implementation                                       | 20   |

|      |            | 3.3.1   | Optimizations for memory-mapped I/O $\ . \ . \ . \ . \ . \ .$ . | 21   |

|      |            | 3.3.2   | Consistency                                                     | 24   |

|      |            | 3.3.3   | Write Protection                                                | 29   |

|      |            | 3.3.4   | Implementation                                                  | 31   |

|      | 3.4        | Testing | g and Validation                                                | 33   |

|      | 3.5        | Evalua  | ation                                                           | 35   |

|      |            | 3.5.1   | Experimental Setup                                              | 35   |

|      |            | 3.5.2   | File-based Access                                               | 37   |

|      |            | 3.5.3   | Memory-mapped I/O                                               | 42   |

|      |            | 3.5.4   | Write Protection                                                | 45   |

|      | 3.6        | Summ    | ary                                                             | 46   |

| IV | DAT  | TA TIEI      | RING IN HYBRID MEMORY SYSTEMS 4                                                                                                             | 7 |  |

|----|------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|---|--|

|    | 4.1  | 1 Background |                                                                                                                                             |   |  |

|    | 4.2  | The ca       | se for X-Mem                                                                                                                                | 0 |  |

|    | 4.3  | X-Men        | n Allocator                                                                                                                                 | 2 |  |

|    |      | 4.3.1        | Allocator API                                                                                                                               | 2 |  |

|    |      | 4.3.2        | Allocator Internals                                                                                                                         | 3 |  |

|    |      | 4.3.3        | Mapping Regions to Memory Types                                                                                                             | 3 |  |

|    |      | 4.3.4        | Implementation                                                                                                                              | 5 |  |

|    | 4.4  | Memor        | ry Access Time Model                                                                                                                        | 5 |  |

|    | 4.5  | Profile      | Guided Placement                                                                                                                            | 7 |  |

|    |      | 4.5.1        | Profiler                                                                                                                                    | 7 |  |

|    |      | 4.5.2        | Runtime                                                                                                                                     | 9 |  |

|    |      | 4.5.3        | Loaded Latency                                                                                                                              | 0 |  |

|    | 4.6  | Evalua       | tion $\ldots \ldots \ldots$ | 0 |  |

|    |      | 4.6.1        | Hybrid Memory Emulator                                                                                                                      | 1 |  |

|    |      | 4.6.2        | Modifications to use the X-Mem API                                                                                                          | 2 |  |

|    | 4.7  | Graph        | Mat                                                                                                                                         | 3 |  |

|    |      | 4.7.1        | Data Structures and Placement                                                                                                               | 4 |  |

|    | 4.8  | VoltDI       | 3                                                                                                                                           | 6 |  |

|    |      | 4.8.1        | Data Structures and Placement                                                                                                               | 7 |  |

|    | 4.9  | MemC         | 3                                                                                                                                           | 8 |  |

|    |      | 4.9.1        | Data Structures and Placement                                                                                                               | 9 |  |

|    | 4.10 | Practic      | cal Deployment                                                                                                                              | 1 |  |

|    |      | 4.10.1       | Human Overhead                                                                                                                              | 1 |  |

|    |      | 4.10.2       | Profiling Overhead                                                                                                                          | 2 |  |

|    |      | 4.10.3       | Device Wear                                                                                                                                 | 2 |  |

|    |      | 4.10.4       | Migration Overhead                                                                                                                          | 2 |  |

|    |      | 4.10.5       | Choosing the right implementation                                                                                                           | 3 |  |

|    | 4.11 | Summa        | ary                                                                                                                                         | 4 |  |

| V  | REI  | ATED         | WORK                                                                                                                                        | 6 |  |

|    | 5.1  | PM as        | fast storage                                                                                                                                | 6 |  |

|      | 5.2 PM as scalable memory     | 78 |

|------|-------------------------------|----|

| VI   | SUMMARY AND FUTURE DIRECTIONS | 83 |

| REF  | ERENCES                       | 85 |

| VITA | A                             | 93 |

# LIST OF TABLES

| 1 | Comparison of Memory Technologies $[90, 18]$                                                                                                                                                                                                                                                                                               | 15 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | Overview of PM Write Protection                                                                                                                                                                                                                                                                                                            | 29 |

| 3 | Metadata CoW or Logging overhead (in bytes)                                                                                                                                                                                                                                                                                                | 40 |

| 4 | Comparison of new memory technologies [90, 18]. NVM technologies include<br>PCM and RRAM [90, 18]. Cost is derived from the estimates for PCM based<br>SSDs in [67]. Since writes to write-back cacheable memory are posted, the<br>effect of NVM's slower writes is lower bandwidth to NVM. For reads, latency<br>is the critical metric. | 48 |

| 5 | An overview of memory tiering techniques.                                                                                                                                                                                                                                                                                                  | 51 |

| 6 | Memory tiering in GraphMat with the X-Mem API                                                                                                                                                                                                                                                                                              | 63 |

| 7 | Memory tiering in VoltDB with the X-Mem API.                                                                                                                                                                                                                                                                                               | 66 |

| 8 | Memory tiering in MemC3 with the X-Mem API.                                                                                                                                                                                                                                                                                                | 70 |

| 9 | Time taken to migrate one gigabyte of application data from DRAM to NVM (at 600-5). $S$ and $L$ denote the use of 4K pages and 1G pages respectively.                                                                                                                                                                                      | 73 |

# LIST OF FIGURES

| 1  | A comparison of traditional vs. PM storage architecture                                                  | 2  |

|----|----------------------------------------------------------------------------------------------------------|----|

| 2  | An overview of the PM (and hybrid memory) software stack. $\ldots$                                       | 5  |

| 3  | Memory read latency for various access patterns                                                          | 8  |

| 4  | Bandwidth of HMEP configurations                                                                         | 11 |

| 5  | Read latency-bandwidth plots for several HMEP configurations and all access patterns                     | 12 |

| 6  | PM System Architecture                                                                                   | 14 |

| 7  | PMFS vs. Traditional File Systems                                                                        | 16 |

| 8  | PMFS data layout                                                                                         | 22 |

| 9  | PMFS journaling data structures                                                                          | 23 |

| 10 | Write Protection in PMFS                                                                                 | 30 |

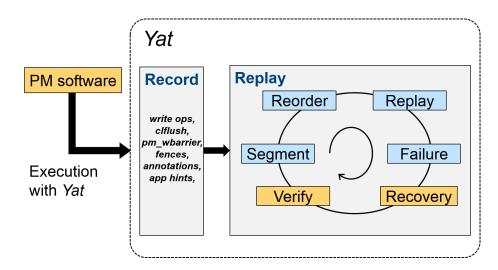

| 11 | PM software flow                                                                                         | 34 |

| 12 | Overview of Yat's operation                                                                              | 35 |

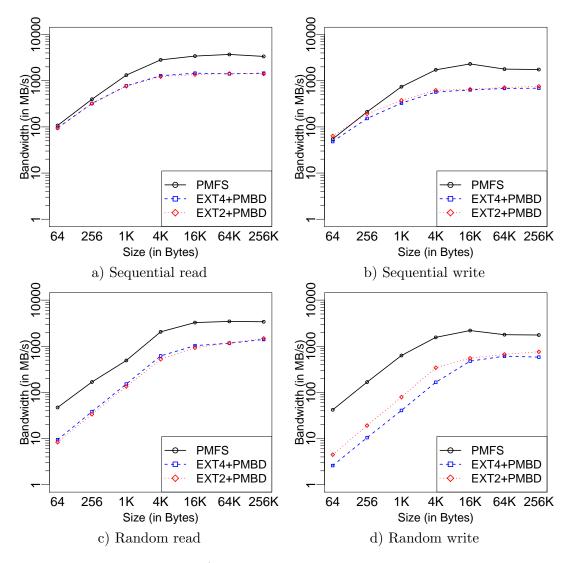

| 13 | Evaluation of File I/O performance; X-axis is the size of the operation; Y-axis is the bandwidth in MB/s | 36 |

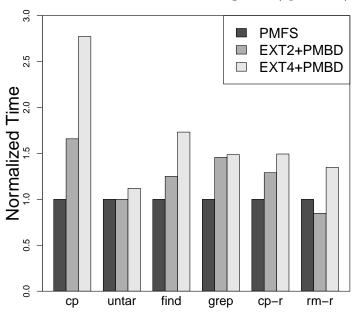

| 14 | Evaluation of File utilities                                                                             | 38 |

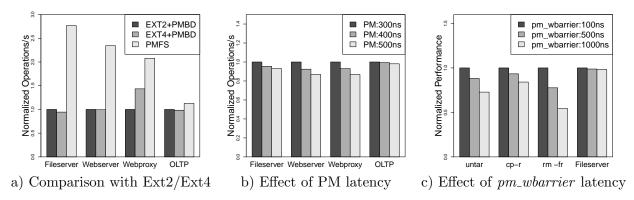

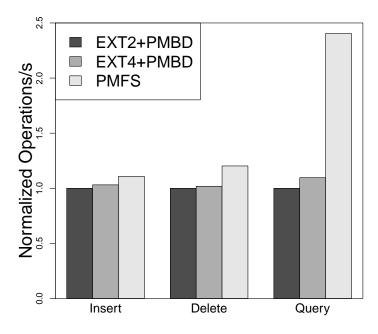

| 15 | Evaluation of Filebench performance                                                                      | 39 |

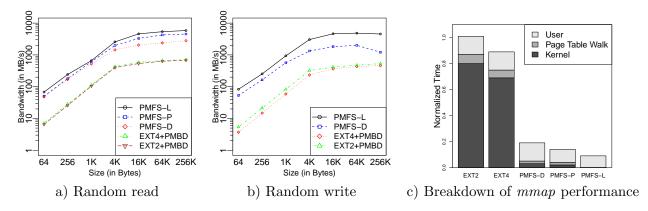

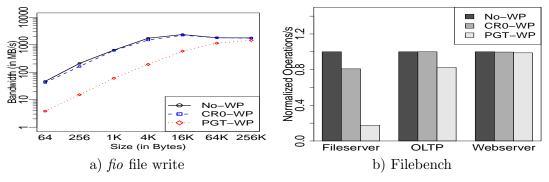

| 16 | Evaluation of memory-mapped I/O performance $\ldots \ldots \ldots \ldots \ldots$                         | 42 |

| 17 | Evaluation of Neo4j performance                                                                          | 45 |

| 18 | Evaluation of PMFS write protection overhead                                                             | 45 |

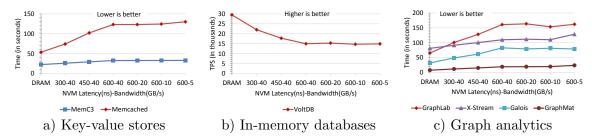

| 19 | Effect of memory latency and bandwidth on the performance of large in-<br>memory applications            | 49 |

| 20 | X-Mem API                                                                                                | 52 |

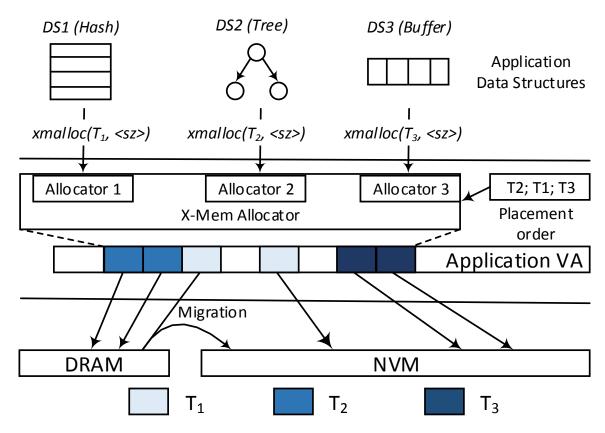

| 21 | X-Mem design                                                                                             | 54 |

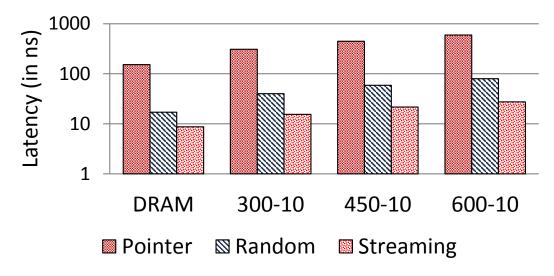

| 22 | Memory read latency for various access patterns                                                          | 57 |

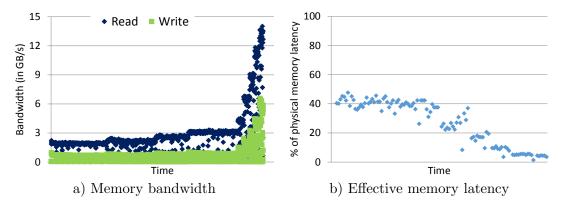

| 23 | Classifying Access Type                                                                                  | 59 |

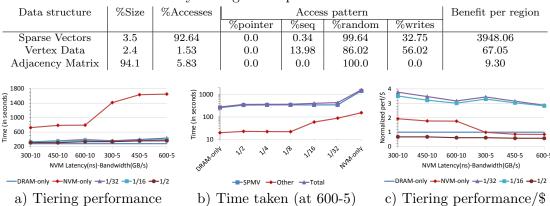

| 24 | Evaluation of memory tiering in GraphMat                                                                 | 63 |

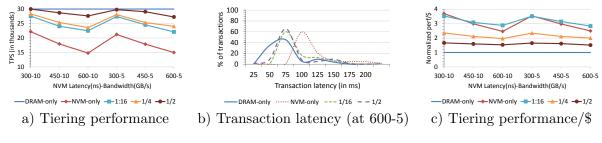

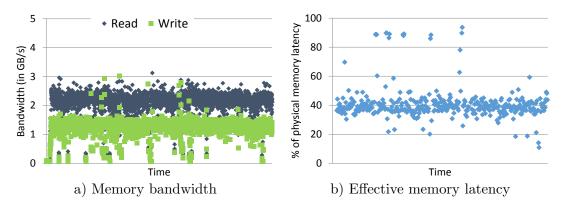

| 25 | Memory usage in GraphMat (Pagerank algorithm)                                                            | 64 |

| 26 | Evaluation of memory tiering in VoltDB                                                                   | 66 |

| 27 | Memory usage in VoltDB (TPC-C workload)                                                                  | 67 |

| 28 | Memory usage in MemC3 (Facebook-like workload). | 69 |

|----|-------------------------------------------------|----|

| 29 | Evaluation of memory tiering in MemC3           | 70 |

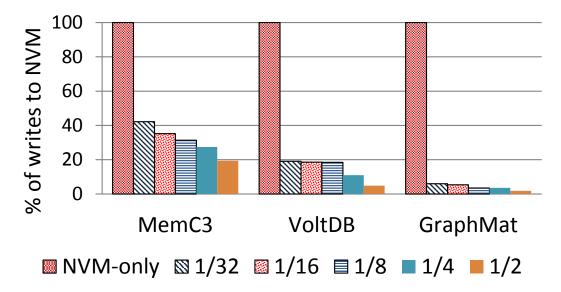

| 30 | Writes to NVM as a percentage of total writes   | 73 |

### SUMMARY

Performance-hungry data center applications demand increasingly higher performance from their storage in addition to larger capacity memory at lower cost. While the existing storage technologies (e.g., HDD and flash-based SSD) are limited in their performance, the most prevalent memory technology (DRAM) is unable to address the capacity and cost requirements of these applications. Emerging byte-addressable, non-volatile memory technologies (such as PCM and RRAM) offer performance within an order of magnitude of DRAM, prompting their inclusion in the processor memory subsystem. Such load/store accessible non-volatile or persistent memory (referred to as NVM or PM) introduces an interesting new tier that bridges the performance gap between DRAM and PM, and serves the role of fast storage or slower memory. However, PM has several implications on system design, both hardware and software: (i) the hardware caching mechanisms, while necessary for acceptable performance, complicate the ordering and durability of stores to PM, (ii) the high performance of PM (compared to NAND) and the fact that it is byte-addressable necessitate rethinking of the system software to manage PM and the interfaces to expose PM to the applications, and (iii) the future memory-based applications that will likely employ systems coupling PM with DRAM (for cost and capacity reasons) must be extremely conscious of the performance characteristics of PM and the challenges of using fast vs. slow memory in ways that best meet their performance demands.

The key contribution of our research is a set of technologies that addresses these challenges in a bottom-up fashion. Since the real hardware is not yet available, we first implement a hardware emulator that can faithfully emulate the relative performance characteristics of DRAM and PM in a system with separate DRAM and emulated PM regions. We use this emulator to perform all of our evaluations. Next we explore system software support to enable low-overhead PM access by new and legacy applications. Towards this end, we implement PMFS, an optimized light-weight POSIX file system that exploits PM's byte-addressability to avoid overheads of block-oriented storage and enable direct PM access by applications (with memory-mapped I/O). To provide strong consistency guarantees, PMFS requires only a simple hardware primitive that provides software enforceable guarantees of durability and ordering of stores to PM. We demonstrate that PMFS achieves significant (up to an order of magnitude) gains over traditional file systems (such as ext4) on a RAMDISK-like PM block device.

Finally, we address the problem of designing memory-based applications for systems with both DRAM and PM by extending our system software to manage both the tiers. We demonstrate for several representative large in-memory applications that it is possible to use a small amount of fast DRAM and large amounts of slower PM without a proportional impact to an application.s performance, provided the placement of data structures is done in a careful fashion. To simplify the application programming, we implement a set of libraries and automatic tools (called X-Mem) that enables programmers to achieve optimal data placement with minimal effort on their part. Finally, we demonstrate the potentially large benefits of application-driven memory tiering with X-Mem across a range of applications.

#### CHAPTER I

## **INTRODUCTION**

The computing industry in undergoing a major transformation due to the emergence of "big data" problems that necessitate data-intensive processing at a scale not seen before [53, 107, 75]. Data center applications require increasingly more compute, memory, and storage performance to process this deluge of data in a timely manner. A parallel trend that is engendering the demand for performance is the rise of virtualized (cloud) infrastructures that are reaping the economic benefits of server consolidation [56, 100] by sharing platform resources among multiple applications.

While the compute power has been improving steadily over the years, the storage and memory performance have languished up until recently. On the storage side, while NAND flash has recently helped bring down the high performance gap between traditional storage and memory [65, 62, 106], it has hit the performance wall and is still up to three orders of magnitude slower than DRAM. In addition, the fact that NAND flash is suited only for use as block devices (i.e., SSDs attached to the IO interfaces) means additional overheads associated with the traditional block-oriented storage stacks [105].

On the other hand, memory-based data center applications like key-value stores, inmemory databases, and data analytics require servers with increasingly larger memory capacities. However, scaling the performance or capacity of DDR-based DRAM memory (DDR-DRAM) is becoming challenging due to physical limitations [73, 90].

To address these challenges, industry is exploring new memory technologies. non-volatile DIMMs (*NVDIMMs*), for instance, attach storage directly to the scalable memory (DDR) interface [94, 19]. NVDIMMs are gaining popularity due to their ability to provide low-latency predictable performance at high rated IOPS [62, 94]. But, despite being attached to the CPU, large capacity NAND-based NVDIMMs are still accessed as block devices [94] in a separate address space, due to the inherent properties of NAND [90]. Battery-backed

DRAM is a high performance (and more expensive) alternative with some adoption in data centers [55], but the capacity of the technology is still subject to the challenges to scaling DRAM [90].

On-package stacked DRAM (3D-DRAM) [73, 26] addresses the performance limitations of DDR-DRAM with vertically stacked DRAM modules that are attached to high-density on-package (or on-chip) interconnects. It has lower latency and much higher bandwidth compared to DDR-DRAM, but its capacity is limited to a few gigabytes vs. the hundreds of gigabytes to terabytes possible with DDR-DRAM [26].

The most promising of these technologies – expected to provide large capacity, byteaddressable, persistent memory – are the storage class memories such as PCM and RRAM [63, 90, 35]. These non-volatile memory (NVM) technologies are positioned between DRAM and secondary storage (such as NAND flash), both in terms of performance and cost. Further, unlike NAND based devices, NVM can be attached directly to the CPU and addressed by regular load/store instructions. In other words, NVM (also referred to as persistent memory or PM) can be used as either fast storage, or as high capacity and low cost (but slower) memory.

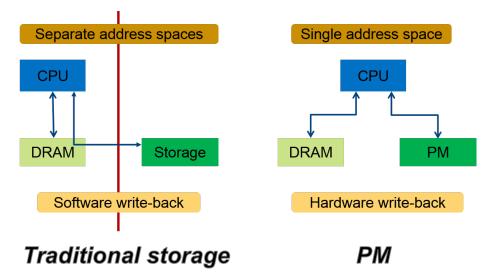

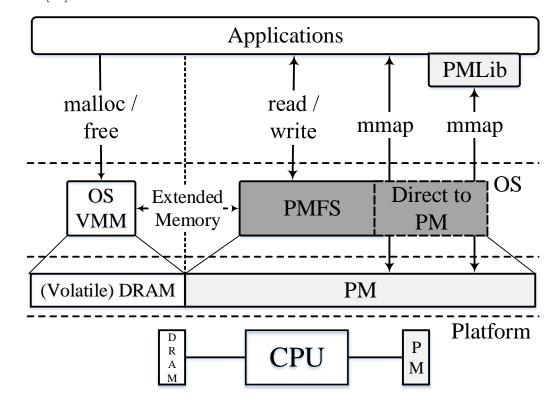

Figure 1: A comparison of traditional vs. PM storage architecture.

PM has several implications on system architecture, system software, libraries, and applications [90, 52, 101, 51]. This dissertation addresses some of the opportunities and challenges arising from the advent of fast load/store accessible storage that can also be used as high capacity, slower memory coupled with DRAM in a hybrid memory system. The main requirement of our research is that both DRAM and PM in a hybrid memory system are managed completely in software, and not by transparent hardware mechanisms [90]. We explore the use of PM as both fast storage and scalable (but slower) memory, and address the following key research problems:

• Architectural support: PM's byte-addressability and the fact that PM can be used as regular (write-back) cacheable memory introduces new challenges to software that must ensure consistency (i.e., ordering and durability) of stores to PM. Traditionally, the storage has always resided in a different address space from memory (Figure 1). For software to access the storage, it has to first copy the data to DRAM and then access the data. Similarly, to flush the data back to the storage, software has to explicitly initiate the flush operation. Software is always in control of when and how the data becomes persistent.

With PM, the storage resides in the same address space as memory, and is part of the cpu's memory hierarchy. Software can access PM directly using regular load/store instructions. Exploiting this capability, we can eliminate many layers of software overhead by optimizing the software stack for PM (discussed next). And, for performance reasons, software would also want to map PM as (write-back) cacheable. But, in doing so, software no longer has control over when the dirty data is flushed to the PM. The dirty data in the CPU caches could be evicted anytime by the hardware, and the writes to PM can be reordered at several places in the hardware. This complicates the ordering, durability, and therefore consistency mechanisms in the software, and necessitates additional architectural support.

• Low overhead access to PM: PM is orders of magnitude faster than traditional storage (HDDs and even NAND flash based SSDs). Research has shown that, as storage becomes faster, software overheads tend to become the most dominant source of wasted effort, therefore necessitating rethinking of the software stacks [105]. As discussed earlier, traditional storage stacks assume that storage is in a different address space, and operate on a block device abstraction. They implement intermediate layers such as page cache to stage the data. When using PM, such a layered design results in unnecessary copies and translations in the software. It is possible to eliminate these overheads by completely avoiding the page cache and the block layer abstraction. Providing low overhead (but managed) access to PM is critical to ensure that applications harness the full potential of PM, and one of the key problems addressed in this dissertation.

• Application design in hybrid systems: The likely deployment of PM in systems coupling DRAM and PM is interesting to memory-based data center applications that require scalable, cost-effective main memory. In such scenarios, PM is used mainly for its low cost and high capacity (persistence is secondary), and can therefore be expected to constitute the majority memory in such hybrid memory systems. The main concern then would be the performance overheads with the memory-intensive applications (with limited locality), particularly if PM is used in a transparent manner. As a result, hybrid memory places the burden on applications to use fast vs. slow memory in ways that best meet their performance demands. The research problem is to develop principled tiering techniques for matching application data with the underlying memory types.

## 1.1 Thesis Statement

Emerging non-volatile (or persistent) memories bridge the performance and capacity gap between memory and storage, thereby introducing a new tier. To harness the full potential of future hybrid memory systems coupling DRAM with PM, we must build new system software and application mechanisms that enable the optimal use of PM as both fast storage and scalable low cost (but slower) memory.

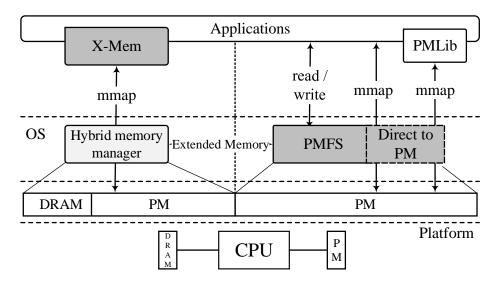

Figure 2: An overview of the PM (and hybrid memory) software stack.

## 1.2 Contributions

The key contribution of our research is a set of technologies (Figure 2) that addresses the aforementioned challenges. Specifically, this dissertation makes the following contributions:

- *Hybrid memory emulator*: Since the real hardware is not yet available, we implement a hardware emulator that can faithfully emulate the relative performance characteristics of DRAM and PM in a system with distinct DRAM and emulated PM regions. In addition, we emulate the performance of the proposed hardware primitives necessary to ensure consistency of the PM software. We use this emulator to perform all of our evaluations.

- System software for PM: To enable low overhead access to PM for legacy and new applications, we implement PMFS, a light-weight POSIX-compliant file system that is optimized for byte-addressable PM. By avoiding the block layer and eliminating the copy and translation overheads from maintaining a separate address space, PMFS improves the performance of several legacy applications by an order of magnitude. In addition, PMFS provides applications with direct access to PM via the memory-mapped interface, and implements features such as transparent large page support [23] to further optimize memory-mapped I/O. Finally, PMFS exploits PM's byte-addressability

yet again to optimize consistency using a combination of atomic in-place updates, logging at cacheline granularity (fine-grained journaling), and copy-on-write (CoW).

• Data tiering in hybrid memory systems: We present a case for application data tiering in hybrid memory systems by demonstrating that a large portion of the overheads from using slower memory can by removed by judiciously placing some application data structures in the small amount of available DRAM. The selection of these data structures of course depends on their access pattern. We implement a memory management infrastructure (called X-Mem) to help programmers automatically identify the properties of application data structures and to enable automatic data placement at run time. The resulting system supports a standard allocator API with minor extensions (hence the name "extended memory" or X-Mem), and requires minimal modifications to the application code.

## 1.3 Organization

The remainder of this dissertation is organized as follows.

Chapter 2 describes the hybrid memory emulator and presents a detailed performance characterization of the platform.

Chapter 3 describes the design and implementation of PMFS, along with an evaluation of the system on the emulator platform.

Chapter 4 motivates the importance of data tiering in hybrid memory systems and presents the design, implementation, and a thorough evaluation of X-Mem.

Chapter 5 discusses related work, including brief architectural specifics of future hybrid memory systems and their impact on software design.

Chapter 6 concludes the dissertation and presents ideas for future research.

### CHAPTER II

#### THE HYBRID MEMORY EMULATOR

#### 2.1 Background

Modern processors like the Intel Xeon processor used in this study support muliple features aimed at hiding the memory latency for various access patterns [27]. These features can be summarized as follows:

(a) Out-of-order execution: The execution cores in modern processors are massively (and increasingly) out-of-order. For example, the out-of-order engine in Intel  $3^{rd}$  generation Core processors (used for all the experiments in this paper) can handle 168  $\mu$ ops (or instructions) in flight, with the number increasing to 192  $\mu$ ops in Intel  $4^{th}$  generation Core processors [27]. Large out-of-order windows enable speculative execution and aggressive reordering of  $\mu$ ops. The improvements in the front end (particularly branch prediction) and the increasingly large load buffers enable a large number of in-flight loads (up to 64 in our test processor).

(b) *Hardware prefetchers*: Modern processors implement several hardware cache prefetchers ers that monitor the pattern of the downstream memory accesses to predict the data program is likely to consume and bring it from the lower levels of cache hierarchy and memory. The prefetchers are very effective for sequential accesses, and are increasingly aggressive. In our test processor, the streamer prefetcher of the second level cache tracks up to 32 streams of data accesses and brings in data up to 20 cachelines ahead of the load request [27].

Depending on the actual implementation and the memory access pattern, mitigating factors to the high memory latency are modern processors' (e.g.,  $Intel^{\textcircled{R}} Xeon^{\textcircled{R}}$ ) extensive use of out-of-order execution and aggressive hardware prefetching [27]. These features can successfully reduce the average latency of memory reads, for certain access patterns, by reducing the number of cache misses and increasing memory-level parallelism (MLP) [50].

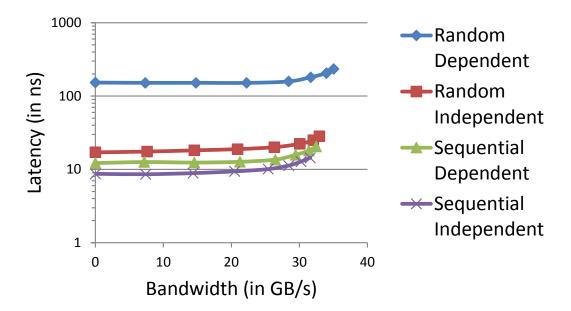

These effects are demonstrated in Figure 3, which shows the average latency of memory reads (for various access patterns) on an Intel Xeon E5-4620 system. In these experiments,

Figure 3: Memory read latency for various access patterns.

one thread reads memory (in the specified pattern) and measures average latency while other threads consume memory bandwidth by accessing their private memory. For *dependent* accesses, the latency thread's memory is initialized for pointer chasing. The locations for *independent* accesses are generated on the fly without any dependencies. Dependent can have only one memory load waiting for execution, and therefore does not benefit from out-of-order execution. Independent can have many in-flight loads.

Random dependent represents the worst case scenario, with every load experiencing the entire memory latency. In comparison, random independent is an order of magnitude faster due only to MLP. Similarly, sequential dependent is an order of magnitude faster than random dependent, but entirely due to hardware prefetchers. Sequential independent, which benefits from both MLP and prefetchers, shows the best performance of all.

The key observation from this experiment is that the performance of memory-intensive applications depends heavily on the pattern of their memory accesses.

### 2.2 The Emulator Platform

The hybrid memory emulation platform (HMEP) enables the study of hybrid memory with real-world applications by implementing – (i) separate physical memory ranges for DRAM and emulated NVM, and (ii) fine-grained emulation of their relative latency and bandwidth characteristics.

HMEP is based on a dual-socket Intel Xeon E5-4620 platform, with each processor containing eight 2.6 GHz cores. Hyperthreading is disabled. Each CPU supports four DDR3 channels and memory is interleaved across the CPUs.

Separate DRAM and NVM physical ranges: Using custom BIOS firmware, HMEP partitions the four memory channels of a CPU equally between DRAM and emulated NVM. The NVM region is available to software either as a separate NUMA node (managed by the OS) or as a reserved memory region (managed by PMFS) [57].

**Read latency emulation:** Memory read latency is often critical to the performance of memory-intensive applications. If there is a dependency in the program flow, then the CPU execution core stalls waiting for the data to be read. Since NVM has higher read latency than DRAM, these stalls are longer, resulting in worse performance. On the other hand, if there are no dependencies, CPU's MLP results in lower average read latency and fewer wasteful core stalls. HMEP emulates read latency on the NVM physical range using special CPU microcode, which uses debug hooks in the CPU to implement a performance model for latency emulation. The model monitors a set of hardware counters over very small intervals, and for each interval estimates (and applies) the additional cycles that the core would have stalled if the underlying memory was slower than DRAM. A naive method of calculating *stall cycles* would be to count the number of actual memory accesses (i.e., last level cache misses) to NVM and multiply it by the desired extra latency. This method, however, is suited only for simple in-order processors and highly inaccurate for modern out-of-order CPUs (§2.1).

We implement a model based on the observation that the number of cycles that the core stalls waiting for the memory reads to complete is proportional to the actual memory latency. If Lp is the target latency to emulated NVM, then the additional (proportional) stalls that the model applies for the time interval is:

$\delta_{stall} = S \times \frac{L_p - L_d}{L_d}$ , where S is the actual number of stall cycles due to accesses to the emulated NVM range,  $L_p$  is the desired NVM latency, and  $L_d$  is the actual latency to DRAM.

In calculating S, we are limited to the following available counters on our test processor:

- Core execution stall cycles due to second level cache (L2) misses  $(S_{L2})$ .

- Number of hits in LLC  $(H_{LLC})$ .

- Number of last level cache (LLC) misses to DRAM  $(M_{dram})$  and NVM  $(M_{nvm})$  ranges.

Using these counters, the model first computes the execution stalls due to LLC misses  $(S_{LLC})$  as follows:

$S_{LLC} = S_{L2} - (H_{LLC} \times K)$ , where K is the difference in latency of a LLC hit and a L2 hit.

Finally, the model computes S as:

$$S = S_{LLC} \times \frac{M_{nvm}}{M_{dram} + M_{nvm}}.$$

*Validation*: To validate the model, we emulate the latency of slower NUMA memories in multi-processor platforms and compare the performance of several application on emulated NVM vs. actual NUMA memory. Following this approach, we validated the latency emulation model for a large number of applications – including several microbenchmarks (e.g., various sort algorithms) and benchmarks from SPEC CPU2006. Performance with NVM (emulating remote memory latency) is always within 7% of the performance with actual remote memory.

**Limitations:** NVM device characteristics are very different from that of DRAM. For instance, reads and writes to a PCM device have to wait for the preceding writes to the same memory line to complete [87]. The HMEP latency emulation model emulates only the average latencies and not NVM's device-specific characteristics. This restriction is primarily due to the limited internal CPU resources available for NVM latency emulation.

CPU hardware prefetchers can drastically improve the performance of sequential and strided memory accesses. HMEP assumes that the prefetchers will continue to be at least as effective with NVM as they are today with slow remote memory (of comparable latency) on large NUMA platforms. This assumption is reasonable even if we ignore the fact that, if needed, CPU prefetchers could be assisted by some form of prefetching on the NVM modules as well. **Bandwidth emulation:** NVM has lower sustained bandwidth than DRAM, particularly for writes (Table 1), though that could be improved using ample scale-out of NVM devices and buffers. <sup>1</sup> HMEP emulates read and write bandwidths by programming the memory controller to limit the maximum number of DDR transactions per  $\mu$ sec. This throttling feature can be programmed on a per-DIMM basis [20], and is applied only to the NVM range.

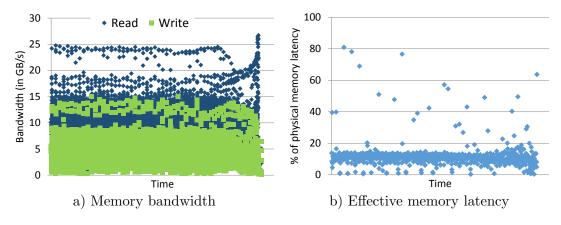

Figure 4: Bandwidth of HMEP configurations

*Limitations*: The bandwidth throttling feature in the memory controller is a single knob that limits the rate of all DDR transactions. Therefore, HMEP is unable to vary the read and write bandwidths independently.

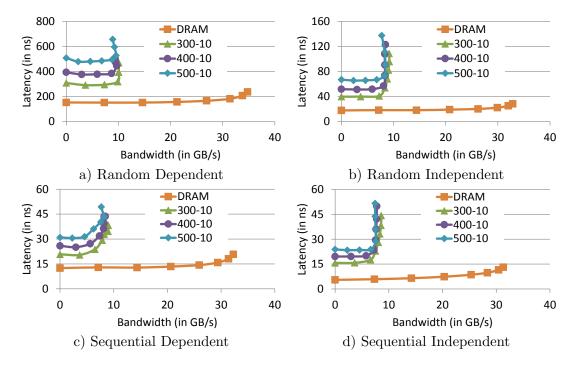

**Characterization:** Figure 5 shows latency and bandwidth characteristics for memory reads to the NVM range in various HMEP configurations. These configurations are denoted by x-y, where x is the emulated NVM read latency (in ns) and y represents the peak bandwidth (in GB/s) to the NVM range. Access patterns are as described earlier (§2.1). Read latency to NVM depends heavily on the access pattern (as with DRAM) – sequential and independent reads are much faster than random and dependent reads.

<sup>&</sup>lt;sup>1</sup>Since writes to write-back caches are posted, NVM's slower writes result in lower bandwidth and not higher latency on every write.

Figure 5: Read latency-bandwidth plots for several HMEP configurations and all access patterns

Figure 4 shows the measured sustained bandwidth to NVM for various HMEP configurations and access patterns. As expected, sequential accesses achieve higher bandwidth than random accesses, and read bandwidth is higher than write bandwidth.

To summarize, despite the stated limitations, HMEP adequately emulates the relative characteristics of DRAM and NVM in a hybrid memory system, and also the performance behavior of various memory access patterns. During the course of this dissertation, HEMP is alternatively referred to as Persistent Memory Emulator Platform (or PMEP).

### CHAPTER III

## SYSTEM SOFTWARE FOR PERSISTENT MEMORY

Emerging byte-addressable, non-volatile memory technologies offer performance within an order of magnitude of DRAM, prompting their inclusion in the processor memory subsystem. However, such load/store accessible Persistent Memory (PM) has implications on system design, both hardware and software. In this chapter, we explore system software support to enable low-overhead PM access by new and legacy applications. To this end, we implement PMFS, a light-weight POSIX file system that exploits PM's byte-addressability to avoid overheads of block-oriented storage and enable direct PM access by applications (with memory-mapped I/O). PMFS exploits the processor's paging and memory ordering features for optimizations such as fine-grained logging (for consistency) and transparent large page support (for faster memory-mapped I/O). To provide strong consistency guarantees, PMFS requires only a simple hardware primitive that provides software enforceable guarantees of durability and ordering of stores to PM. Finally, PMFS uses the processor's existing features to protect PM from stray writes, thereby improving reliability.

Using the PM hardware emulator, we evaluate PMFS's performance with several workloads over a range of PM performance characteristics. PMFS shows significant (up to an order of magnitude) gains over traditional file systems (such as ext4) on a RAMDISK-like PM block device, demonstrating the benefits of optimizing system software for PM.

#### 3.1 Background

In recent years, NAND flash has helped bring down the historically high performance gap between storage and memory [65]. As storage gets faster, the trend is to move it closer to the CPU. Non-Volatile DIMMs (*NVDIMMs*), for instance, attach storage directly to the scalable memory (DDR) interface [94, 19]. NVDIMMs are gaining popularity due to their ability to provide low-latency predictable performance at high rated IOPS [62, 94] But, despite being attached to the CPU, large capacity NAND-based NVDIMMs are still

accessed as block devices [94] in a separate address space, due to the inherent properties of NAND [90].

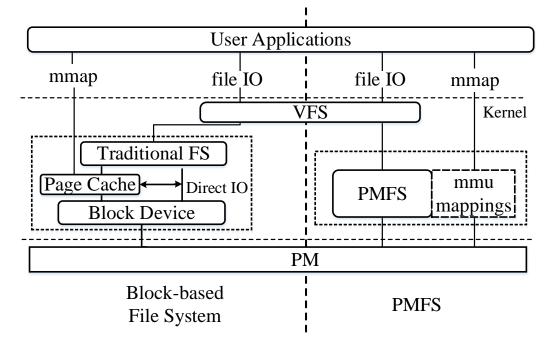

Figure 6: PM System Architecture

However, this appears likely to change in the near future due to emerging non-volatile memory technologies that are suited for use as large capacity, byte-addressable, storage class memory. Table 1 shows per-device characteristics of some of these technologies. We refer to such memory as *Persistent Memory (PM)*.

PM has implications on system architecture, system software, libraries, and applications [90, 52, 101, 51]. In this work, we address the challenge of system software support to enable efficient access of PM by applications.

Traditionally, an OS separates the management of volatile memory (e.g., using a Virtual Memory Manager or VMM) and storage (e.g., using a file system and a block driver). Since PM is both byte-addressable (like volatile memory) and persistent (like storage), system software could manage PM in several ways, such as:

(1) extending VMM to manage PM;

| Parameter        | DRAM             | NAND Flash      | RRAM      | PCM              |

|------------------|------------------|-----------------|-----------|------------------|

| Density          | 1X               | 4X              | 2X-4X     | 2X-4X            |

| Read Latency     | 60ns             | 25µs            | 200-300ns | 200-300ns        |

| Write Speed      | ~1GB/s           | 2.4MB/s         | ~140MB/s  | ~100MB/s         |

| Endurance        | 10 <sup>16</sup> | 10 <sup>4</sup> | $10^{6}$  | $10^6$ to $10^8$ |

| Byte-Addressable | Yes              | No              | Yes       | Yes              |

Table 1: Comparison of Memory Technologies [90, 18]

(2) implementing a block device for PM for use with an existing file system (such as ext4);

(3) implementing a file system optimized for PM without going through a block layer.

*PMFS* adopts the strategy of implementing a POSIX-compliant file system optimized for PM. Figure 6 shows a high-level overview of the proposed PM system architecture, with PMFS as the system software layer managing PM. PMFS has many advantages over the other two approaches:

(1) Support for legacy applications. Many storage-intensive applications rely on a traditional file system interface. PMFS implements a fully POSIX-compliant file system interface.

(2) Support for a light-weight file system. Given the anticipated performance characteristics of PM, the overheads from maintaining a separate storage address space (e.g., operating at block granularity and copying data between storage and DRAM) become dominant [105, 65, 44]. By optimizing for PM and avoiding the block layer, PMFS eliminates copy overheads and provides substantial benefits (up to  $22\times$ ) to legacy applications. Figure 7 shows a high-level comparison of the two approaches. PMFS exploits PM's byteaddressability to optimize consistency using a combination of atomic in-place updates, logging at cacheline granularity (fine-grained journaling), and copy-on-write (CoW).

(3) Optimized memory-mapped I/O. Synchronously accessing fast storage with memory semantics (e.g., using memory-mapped I/O) has documented advantages [105, 44]. However,

with traditional file system implementations, memory-mapped I/O would first copy accessed pages to DRAM, even when storage is load/store accessible and fast. PMFS avoids this overhead by mapping PM pages directly into an application's address space. PMFS also implements other features, such as transparent large page support [23], to further optimize memory-mapped I/O.

PMFS presented us with several interesting challenges. For one, PMFS accesses PM as write-back (WB) cacheable memory for performance reasons [45], but still requires a way to enforce both ordering and durability of stores to PM. To further complicate this situation, memory writes in most modern architectures are posted, with memory controllers scheduling writes asynchronously for performance. This problem is common to all PM software and not just PMFS. To address this issue, we propose a hardware primitive, which we call PM write barrier or  $pm_w barrier$ , that guarantees durability of stores to PM that have been flushed from CPU caches (§3.2).

Figure 7: PMFS vs. Traditional File Systems

For performance and simplicity, PMFS maps the entire PM into kernel virtual address space at the time of mounting. As a result, PM is exposed to permanent corruption from stray writes due to bugs in the OS or drivers. One solution is to map PM pages as readonly in the CPU page tables, and temporarily upgrade specific PM pages as writable in code sections that need to write to them. However, this requires expensive global TLB shootdowns [23]. To avoid these overheads, we utilize processor write protection control to implement uninterruptible, temporal, *write windows* (§3.3.3).

Another challenge in PMFS is validation and correctness testing of consistency. Though a well-known problem for storage software [85], consistency in PMFS is further complicated by the need for careful consideration of processor memory ordering and use of  $pm_wbarrier$ for enforcing durability. For PMFS validation, we use a hypervisor-based validation tool that uses record-replay to simulate and test for ordering and durability failures in PM software (§3.4) [69].

Finally, while memory-mapped I/O (mmap) does provide memory-like access to storage, the interface is too low-level for many applications. Recently researchers have proposed new programming models to simplify direct use of PM by applications [101, 51, 99]. We envision such programming models and libraries, referred to as PMLib in Figure 6, building on PMFS using mmap for direct access to PM. We intend to explore PMLib, including integration with PMFS, in the future.

Contributions of this work are as follows:

- A high-level PM system architecture, including a simple new hardware primitive (*pm\_wbarrier*) that provides software enforceable guarantees of durability and ordering of stores to PM.

- Design and implementation of PMFS, a light-weight POSIX file system with optimizations for PM and the processor architecture, such as fine-grained logging for consistency (§3.3.2), direct mapping of PM to applications with transparent large page support (§3.3.1), and a low-overhead scheme for protecting PM from stray writes by the kernel (§3.3.3).

- Detailed performance evaluation of PMFS with the PM hardware emulator, comparing PMFS with traditional file systems on a RAMDISK-like Persistent Memory Block

Device (*PMBD*).

In next section, we describe the proposed system architecture and  $pm_wbarrier$  primitive in detail (§3.2). We then present the design and implementation of PMFS (§3.3), followed by a detailed performance evaluation of PMFS (§3.5). Finally, we conclude the chapter with a brief survey of related research and thoughts on future work.

#### 3.2 System Architecture

Figure 6 shows the high-level system architecture assumed in the dissertation. For illustration purposes, we assume standard high-volume server platforms and processors based on  $\text{Intel}^{\mathbb{R}}$  64-bit architecture, but the concepts are applicable to other architectures as well.

We assume a processor complex with one or more integrated memory controllers, capable of supporting both volatile DRAM and PM. The OS VMM continues to manage DRAM, while PMFS is responsible for managing PM.

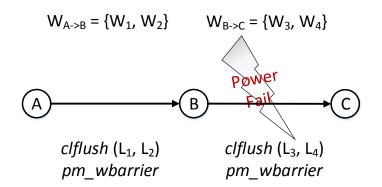

A common flow for consistency in storage software such as PMFS requires a set of writes (A) to be durable before another set of writes (B) [52, 3]. Earlier research explored different approaches to managing ordering and durability of stores to PM, and implications on volatile CPU caches and store buffers. These include mapping PM as write-through (WT) [45], limiting PM writes to use non-temporal store instructions to bypass the CPU caches, or a new caching architecture for epoch based ordering [52].

In our evaluation, we encountered practical limitations with these approaches. While WT mapping offers the simplest solution to avoid caching related complications, it is not suited for use with PM due to both WT overheads [45] and limited PM write bandwidth (Table 1). Meanwhile, restricting PM stores to non-temporal instructions imposes programming challenges; for instance, in switching between cacheable loads and non-temporal stores. Non-temporal instructions also suffer from performance issues for partial cacheline writes, further discouraging general use. Finally, while an epoch-based caching architecture offers an elegant solution, it would require significant hardware modifications, such as tagged cachelines and complex write-back eviction policies. Such hardware mechanisms would involve non-trivial changes to cache and memory controllers, especially for micro-architectures with distributed cache hierarchies.

Based on our analysis, we found that using PM as WB cacheable memory and explicitly flushing modified data from volatile CPU caches (using *clflush* for instance) works well, even for complex usage. However, that alone is not sufficient for desired durability guarantees. Although *clflush* enables software to evict modified PM data and enforce its completion (using *sfence* for instance), it does not guarantee that modified data actually reached the durability point; i.e, to PM or some intermediate power-fail safe buffer.

In most memory controller designs, for performance and scheduling reasons, writes to memory are treated as posted transactions and considered complete once accepted and queued. Also, for all memory write requests accepted, the memory controller enforces processor memory ordering (e.g., read-after-write ordering) [24] by servicing reads of in-flight writes from internal posted buffers. For existing volatile memory usage, such behavior is micro-architectural and transparent to software. But PM usage has additional implications, particularly since the durability point is beyond the memory controller's posted buffers.

To provide PM software with durability guarantees in such an architecture, we propose a simple new hardware primitive  $(pm_wbarrier)$  that guarantees durability of PM stores already flushed from CPU caches. We envision two variants of this primitive: (1) an ondemand variant that allows software to synchronously enforce durability of stores to PM; and (2) a lazy variant that utilizes residual platform capacitance to asynchronously enforce durability of all in-flight accepted writes on detecting power failure. We assume an ondemand (synchronous)  $pm_wbarrier$  in this work.

Consider the above mentioned software flow again. For the desired ordering (A before B) with the proposed primitive, PM software first writes back cachelines dirtied by stores to A (for instance, using *clflush*), issues an *sfence* for completion, and finally issues a single  $pm_wbarrier$ . At this point, A is guaranteed to be durable and software can proceed to the writes in B.

PMFS requires only  $pm_w barrier$  for correct operation. The performance of cache write back is vital to the proposed PM architecture. However, as reported by previous work [45, 101], current implementations of *clflush* are strongly ordered (with implicit fences), and therefore suffer from serious performance problems when used for batch flush operations. For this work, we assume and emulate an optimized *clflush* implementation that provides improved performance through weaker ordering on cache write back operations. Ordering is enforced in software with the use of memory fence operations (e.g., *sfence*). We used special write-combining stores to emulate the optimized *clflush* instruction, and observed up to  $8 \times$  better performance compared to the strongly ordered *clflush* instruction (depending on the cacheline state).

For the remainder of the chapter, we refer to optimized *clflush* simply as *clflush*. Also, unless specified otherwise, by making A durable, we mean the successful completion of the sequence of flushing dirty data in A from CPU caches (using *clflush*), completing the operation with an *sfence* or *mfence*, and enforcing durability with a single *pm\_wbarrier*.

One drawback of the proposed scheme is that software is required to keep track of dirty cachelines in PM. Our evaluation shows that the resulting performance gains justify the additional programming complexity. Moreover, for normal applications, most of the nuances of PM programming can be hidden behind programming models and libraries [101, 51, 99]. PMFS itself uses the proposed hardware primitives and the above mentioned software flow for most usage (for instance, in consistency and logging), and uses non-temporal stores sparingly for specific streaming write operations (e.g., in write system call).

Another important architectural decision is that of wear-leveling. As mentioned before, memory-mapped I/O in PMFS is optimized to grant direct PM access to applications. But, in doing so, one has to consider the issue of wear-leveling. We assume that wear-leveling is done in the hardware (e.g., in the PM modules), which simplifies our decision to map PM directly into the application's address space. We believe that software-based wear-leveling would be overly complicated, particularly when dealing with a large number of PM modules behind multiple memory controllers. We plan to explore this issue further in the future.

### 3.3 PMFS Design and Implementation

Figure 7 shows a high-level software architecture of a system using PMFS, including a comparison with a traditional file system. PMFS design goals are:

(1) Optimize for byte-addressable storage. PMFS exploits PM's byte addressability to avoid the overheads of the block-based design of traditional file systems, such as copies to DRAM during file I/O and read-modify-write at block granularity (as opposed to cacheline granularity) for consistency. PMFS design, including layout (§3.3.1) and consistency (§3.3.2), is optimized for PM and the processor architecture.

(2) Enable efficient access to PM by applications. Because PM performance is comparable to DRAM, it is important to eliminate software overheads in accessing PM [105]. For this reason, PMFS optimizes file read, write, and mmap by avoiding unnecessary copies and software overheads (§3.3.1). File read/write in PMFS, for instance, requires only a single copy between PM and user buffers, while mmap avoids copying altogether.

(3) Protect PM from stray writes. PMFS maps the entire PM into kernel virtual address space for performance, which exposes PM to permanent corruption from stray writes due to bugs in the OS or drivers. To prevent this, PMFS implements a prototype low-overhead write protection scheme using a write protect control feature in the processor (§3.3.3).

#### 3.3.1 Optimizations for memory-mapped I/O

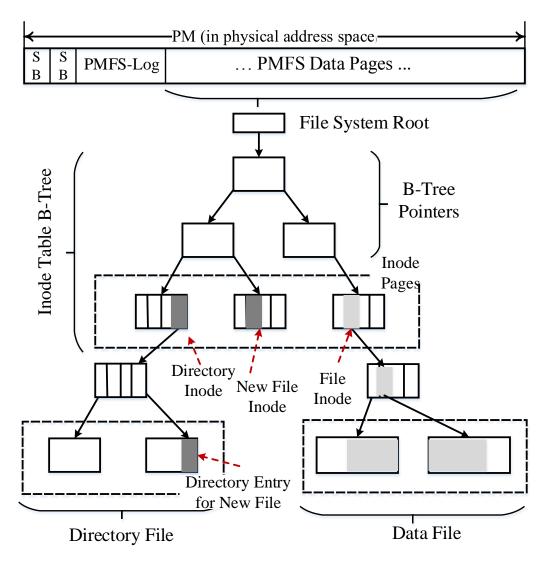

**PMFS Layout:** PMFS data layout is shown in Figure 8. The superblock and its redundant copy are followed by a journal (*PMFS-Log*) and dynamically allocated pages. As in many other file systems, metadata in PMFS is organized using a B-tree, one of the best options for indexing large amounts of possibly sparse data. The B-tree is used to represent both the inode table and the data in inodes.

**Allocator:** Most modern file systems use *extent-based* allocations (e.g., ext4, btrfs), while some older ones are *indirect block-based* (e.g., ext2). Allocations in PMFS are *page-based*, with support for all processor page sizes (4KB, 2MB, 1GB), to enable transparent large page support [23]. By default, the allocator uses 4KB pages for metadata (internal) nodes of a data file's B-tree, but data (leaf) nodes can be 4KB, 2MB, or 1GB.

In many aspects, PMFS allocator is similar to the OS virtual memory allocator, except for consistency and durability guarantees (§3.3.2). Therefore, well-studied memory management issues, such as fragmentation due to support for multiple allocation sizes, apply to

Figure 8: PMFS data layout

PMFS. In the current implementation, the PMFS allocator only coalesces adjacent pages to avoid major fragmentation. We plan to explore more strategies in the future.

Memory-mapped I/O (mmap): *Mmap* in PMFS maps file data directly into the application's virtual address space, so users can access PM directly. PMFS's *mmap* transparently chooses the largest hardware page table mappings, depending on *mmap* and file data node size. Using large page mappings has several benefits, such as efficient use of TLBs, fewer page faults, and shorter page table walks. Another benefit of using large pages is smaller page table structures, which is even more important at large PM capacities since page table pages are allocated from limited DRAM.

Figure 9: PMFS journaling data structures

However, using large pages without application hints could cause internal fragmentation. Therefore, by default, file data nodes in PMFS are 4KB. This default behavior can be overridden using one of the following strategies:

(1) Changing the default page size at mount time. This optimization works well for applications that use large files of fixed or similar sizes [7].

(2) Using existing storage interfaces to provide file size hints. If an application expects a file to grow to 10GB, for example, it can communicate this to PMFS using either *fallocate* (to allocate immediately) or *ftruncate* (to allocate lazily). These hints cause PMFS to use 1GB pages instead of 4KB pages for the file's data nodes. In our experience, modifying the applications to provide such file size hints is usually trivial. For instance, we were able to add basic *fallocate* support to Linux GNU coreutils [6] with just two lines of code, enabling large page allocations for file utilities such as cp and mv.

Finally, PMFS uses large page mappings only if the file data is guaranteed not to be copy-on-write (i.e., for files that are opened read-only or are *mmap*'ed as MAP\_SHARED). Otherwise, we use 4KB mappings. We plan to provide switching between large page and 4KB mappings in the future, so we can use large pages in more cases.

#### 3.3.2 Consistency

A file system must be able to survive arbitrary crashes or power failures and still remain consistent. To provide this guarantee, file systems must implement some form of consistent and recoverable update mechanism for metadata and (optionally) data writes. From the file system's view, an operation is *atomic* if and only if updates made by the operation are committed in all or none fashion. In PMFS, every system call to the file system is an atomic operation. Note that applications directly accessing PM via *mmap* have to manage consistency of the file contents on their own, either within the application or using language, library, and runtime support [101, 51].

Modern file systems and databases use one of the following three techniques to support consistency: copy-on-write (CoW) [2, 52], journaling (or logging) [3], and log-structured updates [91, 65].

CoW file systems and log-structured file systems perform CoW or logging at block or segment granularity, respectively. The block or segment size is typically 4KB or larger. These CoW and log-structured file systems are often accompanied by large write amplification, especially for metadata consistency which typically requires only small metadata updates. Journaling, particularly with PM, can log the metadata updates at much finer granularity.

We performed an analysis of the above mentioned techniques for PM, assessing the cost (number of bytes written, number of  $pm_wbarrier$  operations, etc.) of metadata consistency for various system calls. Based on this study, we found that logging at cacheline or 64-byte granularity (called *fine-grained logging*) incurs the least overhead for metadata updates, compared to both CoW (with or without atomic in-place updates) and log-structured file systems.

Journaling, however, has the drawback that all the updates have to be written twice; once to the journal, and then to the file system. For updates larger than a CoW file system's block size or a log-structured file system's segment size, journaling becomes less desirable due to this double copy overhead and the associated write amplification. Therefore, in PMFS, we use atomic in-place updates and fine-grained logging for the (usually small) metadata updates, and CoW for file data updates. We show (§3.5.2.3) that PMFS incurs much lower overhead for metadata consistency compared to BPFS, a PM-optimized file system that uses CoW and atomic in-place updates for metadata and data consistency [52].

Undo vs. Redo: Journaling comes in two flavors: 1) redo and 2) undo. In redo journaling, the new data to be written is logged and made durable before writing the data to the file system. This new data is written to the file system only when the transaction commits successfully. In undo journaling, the old data (in the file system) is first logged and made durable. The new data is written directly (in-place) to the file system during the transaction. In the event the transaction fails, any modifications to the file system are rolled back using the old data in the undo journal. Both redo and undo have pros and cons. Undo journaling in PMFS requires a  $pm_w barrier$  for every log entry within a transaction while redo journaling requires only two *pm\_wbarrier* operations per transaction, irrespective of the number of log entries. On the other hand, redo journaling is more complex to implement. Since the new data is written only to the redo journal during a transaction, all reads done as part of the transaction have to first search the redo journal for the latest copy. As a result, redo journaling incurs an additional overhead for all the read operations in a transaction, therefore placing practical restrictions on the granularity of logging in redo – the finer the logging granularity, the larger the overhead of searching the redo journal.

Undo journaling is simpler to implement and allows fine-grained logging of shared data structures (e.g., inode table). In PMFS, we use undo journaling for its above mentioned advantages and simplicity. However, we realize that undo is not always better than redo. For instance, redo could be expected to perform better than undo if the transaction creates a large number log entries but modifies only a small number of data structures. We plan to analyze the respective benefits of redo and undo journaling in the future.

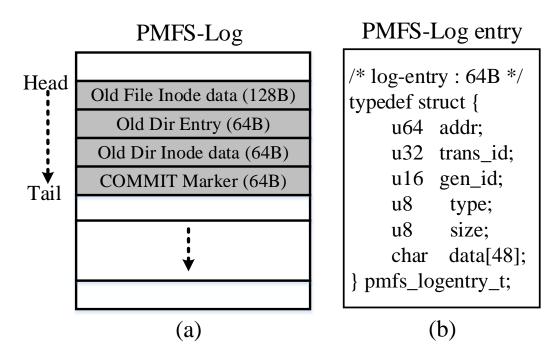

As noted above, in PMFS, the original data is written and committed to the PMFS-Log (Figure 9) before the file system metadata is modified, thereby following undo semantics. If a failure occurs in the middle of a transaction, PMFS recovers on the next mount by reading the PMFS-Log and undoing changes to the file system from uncommitted transactions. To minimize journaling overhead, PMFS leverages processor features to use atomic in-place updates whenever possible, sometimes avoiding logging altogether. For operations where in-place updates to the metadata are not sufficient, PMFS falls back to use fine-grained logging.

To summarize, PMFS uses a hybrid approach for consistency, switching between atomic in-place updates, fine-grained logging, and CoW. We now describe atomic in-place updates and fine-grained logging in more detail.

Atomic in-place updates: As suggested by previous work, PM provides a unique opportunity to use atomic in-place updates to avoid much more expensive journaling or CoW [52]. However, compared to prior work, PMFS leverages additional processor features for 16-byte and 64-byte atomic updates, avoiding logging in more cases. PMFS uses the various atomic update options in the following ways:

- 8-byte atomic updates: The processor natively supports 8-byte atomic writes. PMFS uses 8-byte atomic writes to update an inode's access time on a file read.

- 16-byte atomic updates: The processor also supports 16-byte atomic writes using *cmpxchg16b* instruction (with LOCK prefix) [22]. PMFS uses 16-byte in-place atomic updates in several places, such as for atomic update of an inode's size and modification time when appending to a file.

- 64-byte (cacheline) atomic updates: The processor also supports atomic cacheline (64byte) writes if *Restricted Transactional Memory (RTM)* is available [21]. To atomically write to a single cacheline, PMFS starts a RTM transaction with XBEGIN, modifies the cacheline, and ends the RTM transaction with XEND, at which point the cacheline is atomically visible to rest of the system. On a subsequent *clflush*, the modified cacheline is written back to PM atomically, since the processor caching and memory hardware move data at least at cacheline granularity. PMFS uses cacheline atomicity in system calls that modify a number of inode fields (e.g., in deleting an inode). Note that if RTM is not present, PMFS simply falls back to use fine-grained logging.

Journaling for Metadata Consistency: PMFS uses undo journaling and finegrained logging. The main logging data structure is a fixed-size circular buffer called PMFS-Log (Figure 9(a)). The head and tail pointers mark the beginning and end, respectively, of the sliding window of *active* logged data. For every atomic file system operation that needs logging, PMFS initiates a new transaction with a unique id (*trans\_id*).

PMFS-Log consists of an array of 64-byte *log entries*, where each log entry describes an update to the file system metadata. A log entry consists of a header and data portion, as shown in Figure 9(b). The 2-byte *gen\_id* is a special field. For a log entry in PMFS-Log to be considered valid by recovery code, the gen\_id field in the log entry must match a similar gen\_id field in PMFS-Log metadata. PMFS-Log's gen\_id field is incremented after every log wrap-around and after every PMFS recovery, thereby automatically invalidating all of the stale log entries.

To be able to identify valid entries in PMFS-Log, one of two requirements must hold: either PMFS must atomically append entries to PMFS-Log or the recovery code must be able to detect partially written log entries. One possible solution is to use two  $pm_warrier$ operations: append the log entry to PMFS-Log and make it durable, then atomically set a valid bit in the log entry before making the valid bit durable. Other approaches include using a checksum in the log entry header [86] or tornbit RAWL [101], which converts the logging data in to a stream of 64-bit words, with a reserved torn (valid) bit in each word. However, all these approaches have high overhead from either additional serializing operations (double barrier) or compute (checksum, tornbit RAWL). In PMFS, we fix the size of log entries to a single (aligned) cacheline (64 bytes) and exploit the architectural guarantee in the processor caching hierarchy that writes to the same cacheline are never reordered. For example, if A and B are two separate 8-byte writes to the same cacheline and in that order, then A will always complete no later than B. PMFS uses the gen\_id field in log entry header as a valid field. When writing a log entry to PMFS-Log, gen\_id is written last, before the log entry is made durable. To ensure this scheme works, we instruct the compiler not to reorder writes to a log entry.

At the start of an atomic operation (or transaction), PMFS allocates the maximum

number of required log entries for the operation by atomically incrementing the tail. When a transaction is about to modify any metadata, it first saves the old values by appending one or more log entries to PMFS-Log and making them durable, before writing the new values in-place. This process is repeated for all the metadata updates in the transaction. After all the metadata updates are done, the transaction is committed by first flushing all of the dirty metadata cachelines in PM and then using a single  $pm_wbarrier$  to make them durable. Finally, we append a special *commit* log entry to the transaction and make that durable, to indicate that the transaction has been completed.

As an optimization, we (optionally) skip the  $pm_wbarrier$  after the commit log entry. Some subsequent  $pm_wbarrier$ , either from another transaction or the asynchronous log cleaner thread will ensure that the commit log entry is made durable. This optimization avoids one  $pm_wbarrier$  per transaction, but the last committed transaction may be rolled back if PMFS has to recover from a failure. A log cleaner thread periodically frees up log entries corresponding to the committed transactions by first issuing a single  $pm_wbarrier$ to make the commit log entries durable, and then atomically updating the head pointer in PMFS-Log.

**PMFS recovery:** If PMFS is not cleanly unmounted, due to a power failure or system crash, recovery is performed on the next mount. During recovery, PMFS scans through the PMFS-Log from head to tail and constructs a list of committed and uncommitted transactions, by looking for commit records with a valid gen\_id. Committed transactions are discarded and uncommitted transactions are rolled back.

**Consistency of Allocator:** Using journaling to maintain the consistency of PMFS allocator data structures would incur high logging and ordering overhead, because of the frequency of alloc/free operations in the file system. Therefore, we maintain allocator structures in volatile memory, using freelists. PMFS saves the allocator structures in a reserved (internal) inode on a clean unmount. In case of a failure, PMFS rebuilds the allocator structures by walking the file system B-tree during recovery.

**PMFS Data Consistency:** As mentioned before, the journaling overhead for large file data updates could be prohibitive due to double copy. Hence, PMFS uses a hybrid approach,

switching between fine-grained logging for metadata updates and CoW for data updates. For instance, on a multi-block file data update with the *write* system call, PMFS uses CoW to prepare pages with the new data and then updates the metadata using journaling.

In the current implementation, PMFS only guarantees that the data becomes durable before the associated metadata does. This guarantee is the same as the guarantee provided by ext3/ext4 in *ordered data* mode. We plan to explore stronger consistency guarantees in the future.

One open issue with CoW, however, is its use with large pages; for instance, CoW of a 1GB file data node, even if it is to write a few hundred megabytes, would cause significant write amplification. As this problem also occurs in OS virtual memory management, we plan to explore the best known practices (e.g., breaking down large pages to regular 4KB pages on CoW) in the future.

#### 3.3.3 Write Protection

Since software can access PM as regular memory, we must be concerned about permanent corruption to PM from inadvertent writes due to bugs in unrelated software.

| Table 2. Overview of 1 M write 1 lotection |                   |               |  |

|--------------------------------------------|-------------------|---------------|--|

|                                            | User              | Kernel        |  |

| User                                       | Process Isolation | SMAP          |  |

| Kernel                                     | Privilege Levels  | Write windows |  |

Table 2: Overview of PM Write Protection

Table 2 shows a brief overview of how PM write protection (from stray writes) works in the assumed processor architecture. The row name refers to the address space in which PM is mapped and the column name refers to the privilege level at which stray writes occur. Protection within a process (e.g., between multiple threads) is not covered here, but will be explored in the future. Protecting "kernel from user", and "user from user" follow from existing isolation mechanisms based on privilege levels and paging, respectively. Also, "user from kernel" follows from use of Supervisor Mode Access Prevention (SMAP) feature in the processor [17]. When SMAP is enabled, supervisor-mode (i.e., ring 0 or kernel) accesses to the user address space are not allowed. This feature is important since memory-mapped I/O in PMFS provides the user-level applications with direct access to PM. Due to SMAP, the *mmap*'ed memory is protected from stray writes in kernel. Protecting "kernel from kernel", however, could be challenging, particularly if multiple OS components sharing the same kernel address space are allowed to write to PM. Since PMFS is the only system software that manages PM, the solution space is much simpler in our case.

| P: Read-only PM page in kernel virtual address<br>write(P): Write to page P in ring 0 (kernel)<br>GP: General protection fault |                                                                                                                                       |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| // CR0.WP in x86                                                                                                               | <pre>// Using CR0.WP in PMFS disable_write_protection() {</pre>                                                                       |  |  |