# Analysis and Optimization for Global Interconnects for Gigascale Integration (GSI)

A thesis

Presented to

The Academic Faculty

by

## Azad Naeemi

In Partial Fulfillment

of the Requirements for the degree of

Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology July 2003

Copyright © 2003 by Azad Naeemi

# Analysis and Optimization for Global Interconnects for Gigascale Integration (GSI)

| Approved by:                       |

|------------------------------------|

| Professor James D. Meindl, Advisor |

| Professor D. Scott)Wills           |

| Professer Jeffrey A. Davis         |

| Professor David Citrin             |

| Professor Paul A. Kohl             |

| Date Approved                      |

To my parents, for their wisdom, persistence, and dedication.

### Acknowledgments

I would like to sincerely thank my advisor, Professor James Meindl, for guiding me through this thesis. It has been a great honor and privilege to work under his supervision and benefit from his keen insights. His deep and enlightening questions have always led me to astonishing ideas.

I am also grateful to Dr. Jeff Davis for his thoughtful guidance and interesting discussions, and also for his setting the example as a former student of the gigascale integration (GSI) group. I appreciate the invaluable guidance and attention that I received from Professors Thomas Gaylord and Scot Wills. I am also in great debt to all my ECE professors, especially Professors Glenn Smith and the late John Uyemura, for amazingly teaching me difficult courses in simple language.

My sincere thanks also go to all GSI group members, especially our program manager, Ms. Jennifer Tatham, without whose efforts I could not even start my graduate studies. She has taken care of all GSI students and their families, and because of her efforts, the GSI group has attained a unique pleasant atmosphere.

Most importantly, I would like to thank my wife Nassim whose unconditional love, passion and trust have been the inspiration for this work. Her beautiful smile brought joy and motivation to my life. Thank you for everything.

# Table of Contents

| Chap  | ter 1: Introduction and Background1                       |

|-------|-----------------------------------------------------------|

| 1.2   | Optimal Global Interconnects for GSI4                     |

| 1.3   | Compact Physical Models5                                  |

| 1.3.1 | Distributed RLC Lines above an Ideal Ground Plane5        |

| 1.3.2 | Co-Planar RLC Lines above Orthogonal Lines5               |

| 1.3.3 | Multi-Level Crosstalk Noise6                              |

| 1.4   | Chip-Package Co-Design Methodologies7                     |

| 1.4.4 | Signal Interconnection7                                   |

| 1.4.5 | Power and Ground Interconnection                          |

| 1.5   | Optical Interconnection versus Electrical Interconnection |

|       |                                                           |

| Chap  | ter 2: Optimal Global Interconnects for GSI9              |

| 2.2   | Optimal On-Chip Wire Width                                |

| 2.2.1 | Impact of Wire Width on Latency                           |

| 2.2.2 | Impact of wire width on bandwidth                         |

| 2.2.3 | Optimal Wire Width17                                      |

| 2.3   | Optimal On-Chip Wire Width22                              |

| 2.3.1 | Power Consumption                                         |

| 2.3.2 | Repeater Area                                             |

| 2.3.3 | Via Blockage28                                            |

| 2.4   | Conclusions30                                                  |

|-------|----------------------------------------------------------------|

|       |                                                                |

| Chap  | ter 3: N-Coupled RLC Lines above an Ideal Ground Plane32       |

| 3.2   | Single, Two and Three Coupled RLC Lines                        |

| 3.3   | Five or More Coupled RLC Lines                                 |

| 3.4   | Verification and Results38                                     |

| 3.5   | Conclusions43                                                  |

|       |                                                                |

| Chap  | ter 4: Modeling of Co-Planar RLC Lines45                       |

| 4.1   | Introduction                                                   |

| 4.2   | Periodic Structures                                            |

| 4.3   | Modeling On-Chip Co-Planar Interconnects                       |

| 4.4   | Two Signal Lines between Power and Ground Lines                |

| 4.5   | More Than Two Signal Lines between Power and Ground Lines      |

| 4.6   | Conclusions60                                                  |

|       |                                                                |

| Chap  | ter 5: Optimization of Co-Planar RLC Lines62                   |

| 5.1   | Introduction62                                                 |

| 5.2   | Optimal Signal-Ground Spacing to Signal-Signal Spacing Ratio63 |

| 5.3   | Optimal Wire Width68                                           |

| 5.3.1 | Optimal Wire Width for a Single Signal Line69                  |

| 5.3.2 | Optimal Wire Width for Two Signal Lines                        |

| 5.4     | Optimal Metal thickness and Spacing                                     | 79  |

|---------|-------------------------------------------------------------------------|-----|

| 5.5     | Conclusions                                                             | 85  |

|         |                                                                         |     |

| Chap    | ter 6: Multilevel Interconnect Crosstalk Modeling                       | 87  |

| 6.1     | Introduction                                                            | 87  |

| 6.2     | Methodology                                                             |     |

| 6.3     | Identical Victim and Aggressor Lines                                    |     |

| 6.4     | Non-Identical Victim and Aggressor Lines                                | 95  |

| 6.5     | Noise Voltage-Time Integral                                             | 100 |

| 6.6     | Near and Far Aggressors                                                 | 102 |

| 6.6.1   | Near and Intra-Level Far Aggressors                                     | 102 |

| 6.6.2   | Near and Inter-Level Far Aggressors                                     | 107 |

| 6.7     | Integrated Crosstalk Model                                              | 108 |

| 6.8     | Impact of Wire Width Optimization                                       | 112 |

| 6.9     | Conclusions                                                             | 114 |

|         |                                                                         |     |

| Chap    | ter 7: Chip-Package Co-Design                                           | 115 |

| 7.1     | Introduction                                                            | 115 |

| 7.2     | Signal Interconnection through PWB                                      | 116 |

| 7.2.1   | Maximum On-Chip Interconnect Length to Achieve the Highest Performance. | 117 |

| 7.2.2   | Cost Estimation                                                         | 119 |

| 7.2.2.1 | Extracting the Wiring Distribution                                      | 119 |

| 7.2.2. | 2. Estimating the Required Area and I/O Pads                      | 123    |

|--------|-------------------------------------------------------------------|--------|

| 7.2.2. | 3. Estimating Total PWB Area                                      | 124    |

| 7.3    | Power Distribution                                                | 133    |

| 7.4    | Conclusions                                                       | 135    |

|        |                                                                   |        |

| Chap   | ter 8: Optical Versus Electrical Interconnection                  | 136    |

| 8.1    | Introduction                                                      | 136    |

| 8.2    | Electrical Interconnects                                          | 138    |

| 8.3    | Optical Interconnects                                             | 142    |

| 8.4    | The Partition Length between Electrical and Optical Interconnects | 144    |

| 8.5    | Conclusions                                                       | 147    |

|        |                                                                   |        |

| Chap   | ter 9: Future Work and Conclusion                                 | 149    |

| 9.1    | Advancing Compact Physical Models                                 | 148    |

| 9.2    | Optimizing Other Interconnecting Techniques                       | 149    |

| 9.3    | Developing Stochastic Models for Crosstalk Noise                  | 150    |

| 9.4    | Extending Chip-Package Design Methodologies                       | 151    |

| 9.5    | Analysis and Design of Clock Distribution Networks                | 151    |

| 9.6    | Conclusion of Dissertation                                        | 152    |

|        |                                                                   |        |

| Appe   | endix A: Derivation of Optimal Wire Width                         | 155    |

| Appe   | endix B: Physical Explanation for Crosstalk of Identical Line     | es 157 |

| Appendix C: Peak Crosstalk Voltage in Terms of W/W <sub>opt</sub> | 159 |

|-------------------------------------------------------------------|-----|

| Appendix D: Derivation of Bit-Rate Limit of RLC Lines             | 163 |

| References                                                        | 164 |

| Vita                                                              | 170 |

# List of Tables

| Table 2.1: | Key assumptions and design goals of different methodologies for optimizing interconnecting devices.                                                                                                                                                                                | 11  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2. | Impact of using optimal wire width on a 24 mm-long interconnect in a projected ASIC chip at the 45-nm node of technology. The chip area is 572mm <sup>2</sup> . The global repeater area and number of vias correspond to two global metal levels with a wiring efficiency of 0.5. | 30  |

| Table 7.1: | Key parameters for the projected microprocessor in the year 2011                                                                                                                                                                                                                   | 120 |

| Table 7.2: | Costs and advantages of optimal partition between interconnects and exterconnects.                                                                                                                                                                                                 | 132 |

| Table 7.3: | The key parameters and the required number of power/ground pins for various technology generations. Aspect ratios 1 and 2 are considered for the top global interconnects (A,=1, 2)                                                                                                | 134 |

# List of Figures

| Figure 2.1:  | The cross-section of a wire and its neighbors13                                                                                                                                                                                                                                     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

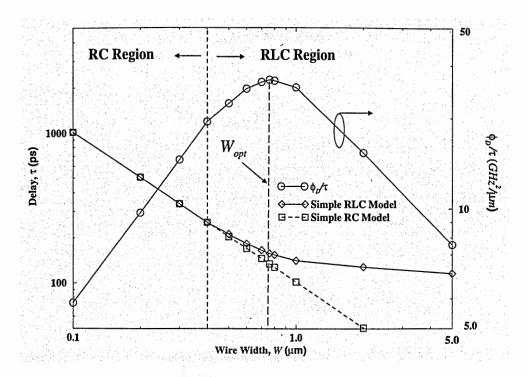

| Figure 2.2:  | Time delay of a 24 mm long interconnect with optimal repeaters versus wire width. The cross-section of the wire is shown in Figure 2.1                                                                                                                                              |

| Figure 2.3:  | A layer of global interconnects. (a) All interconnects have the same length. (b) Length of interconnects are different                                                                                                                                                              |

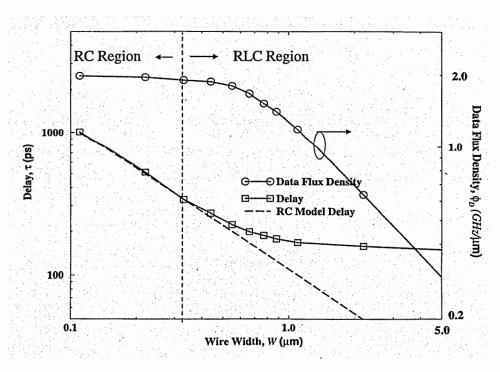

| Figure 2.4:  | Data flux density versus wire width for a 24 mm long interconnect. Interconnect delay is also plotted. Data-flux density is constant in the RC regime and in the RLC regime, it drops as wire width decreases17                                                                     |

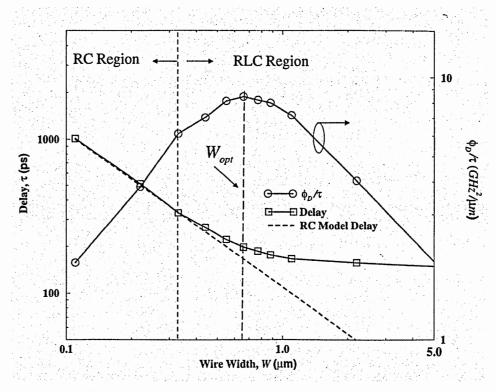

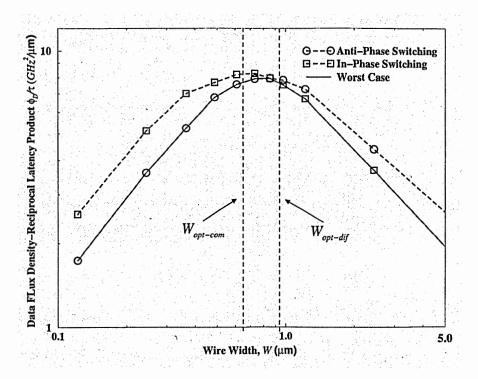

| Figure 2.5:  | Data flux density-reciprocal latency product versus the wire width for a 24 mm long interconnect with optimal repeaters                                                                                                                                                             |

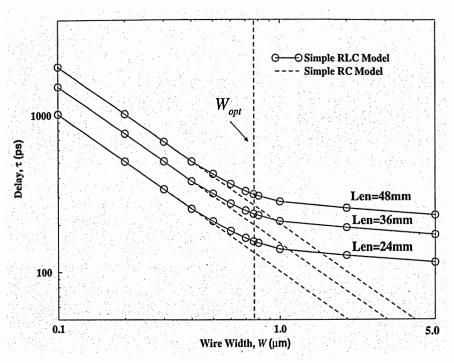

| Figure 2.6:  | Time delay versus the interconnect width for different interconnect lengths. Optimal wire width is independent of length                                                                                                                                                            |

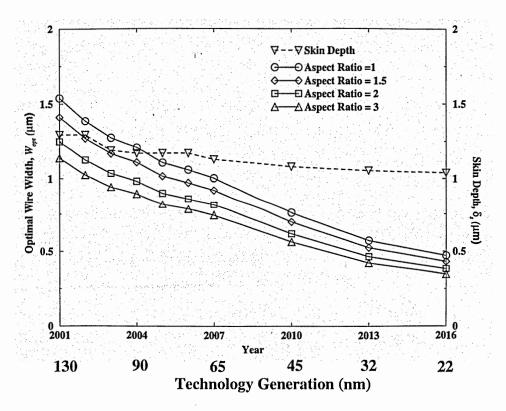

| Figure 2.7:  | Optimal wire width for different generations [1] and aspect ratios. Using optimal wire width makes the skin effect negligible. The skin depth is calculated for the third harmonic of the global clock frequency                                                                    |

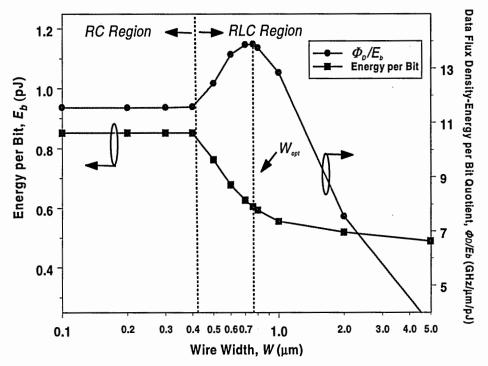

| Figure 2.8:  | The required energy to transfer one bit of data along a 24 mm long interconnect versus the wire width. At the optimal wire width, $\Phi_D/E_b$ is maximized                                                                                                                         |

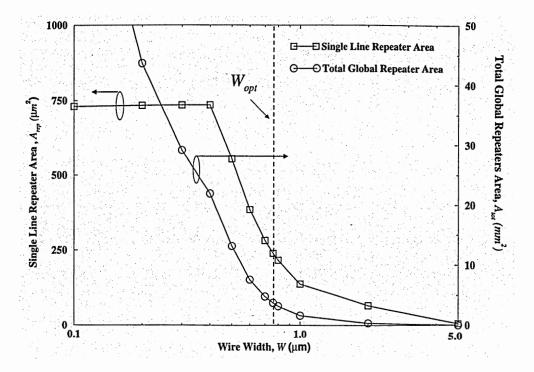

| Figure 2.9:  | The required silicon area for a 24 mm long interconnect and the total silicon area for global repeaters versus the wire width. The Chip area is assumed to be 572 mm <sup>2</sup> , and two levels of metal with a wiring efficiency of 0.5 are considered for global interconnects |

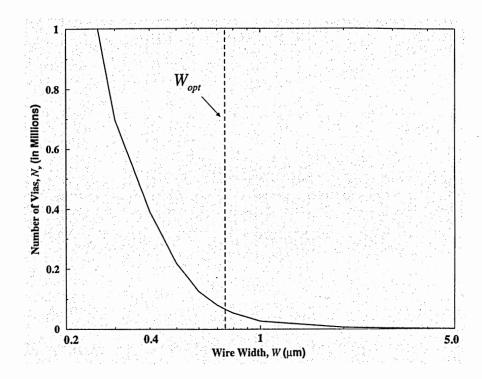

| Figure 2.10: | Number of vias required for the repeaters associated with a pair of global interconnect levels versus the wire width29                                                                                                                                                              |

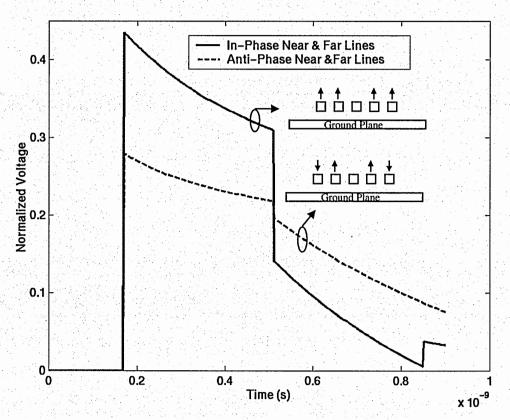

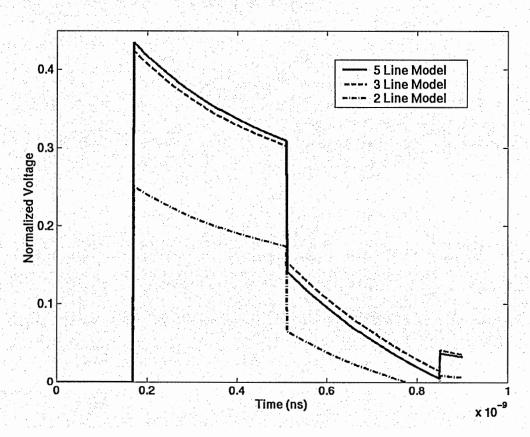

| Figure 3.1:  | Crosstalk Voltage at the end of the middle quiet victim line when far and near aggressors switch in-phase39                                                                                                                                                                         |

| Figure 3.2:  | Crosstalk Voltage at the end of the quiet line when the far and near aggressors switch anti-phase                                                                                                                                                                                   |

| Figure 3.3:  | Effect of increasing Number of Aggressors from one to four when all aggressors switch in-Phase41                                                                                                                                                                                    |

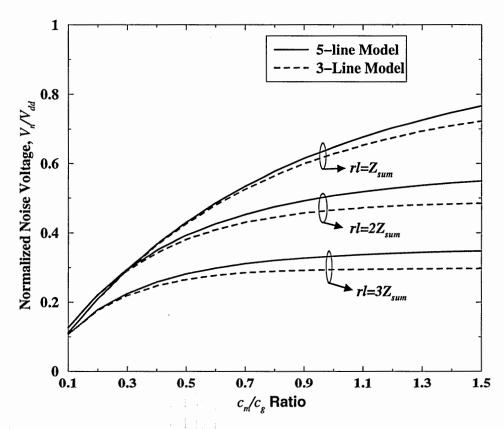

| Figure 3.4: | Normalized noise voltage versus cm/cg ratio. Neglecting far lines causes a negligible error in the worst-case crosstalk especially for the range that crosstalk is less than $0.2V_{dd}$                                                                             |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

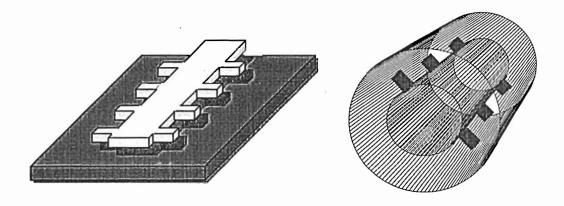

| Figure 4.1: | Two realizations of periodic structures                                                                                                                                                                                                                              |

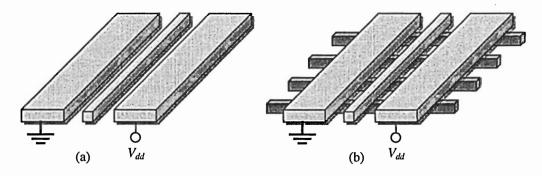

| Figure 4.2: | A double sided shielded signal line. (a) there are no orthogonal lines and therefore the three lines form an ideal transmission line (b) there are orthogonal lines which make the signal and ground lines form a periodic structure.                                |

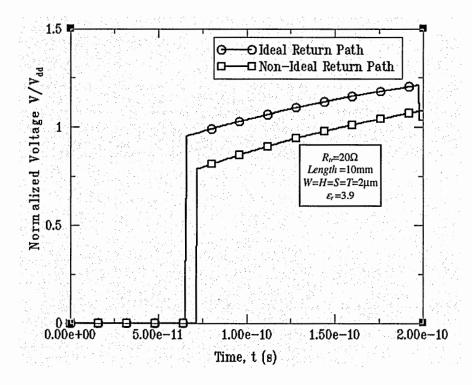

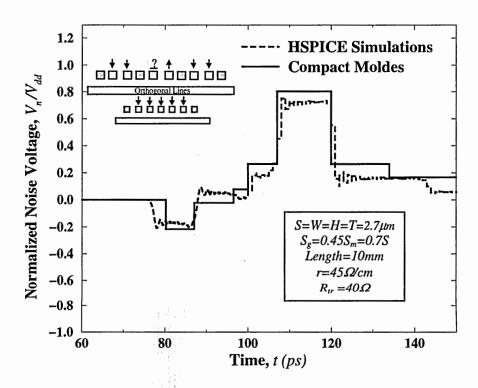

| Figure 4.3: | Voltage at the end of signal line for ideal and non-ideal return path cases. For the ideal case a signal line is above a ground line and in the non-ideal case a signal line is shielded between power/ground lines above orthogonal lines                           |

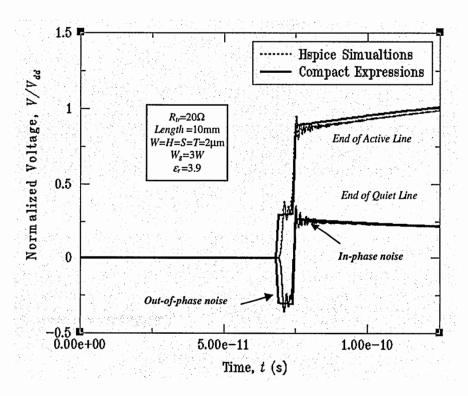

| Figure 4.4: | Normalized voltage at the end of open-ended signal lines when one of them is excited with a step input and the other one is quiet. An out-of-phase noise appears at the end of the victim line due to different propagation speeds for common and differential modes |

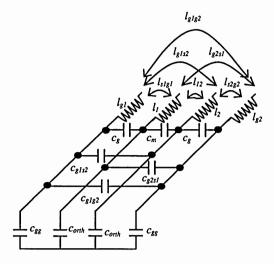

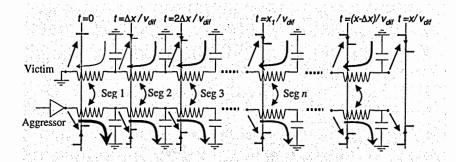

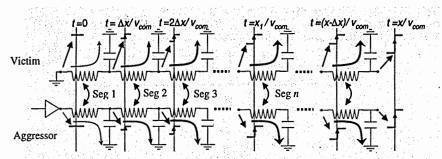

| Figure 4.5: | A segment of the equivalent circuit used for HSPICE simulations.  1000 segments are used in all simulations                                                                                                                                                          |

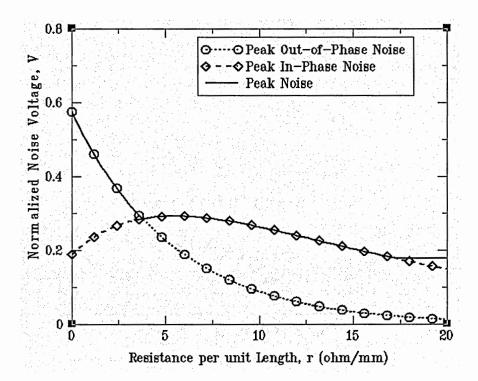

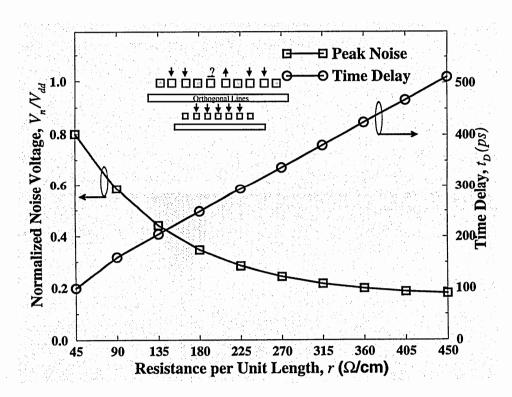

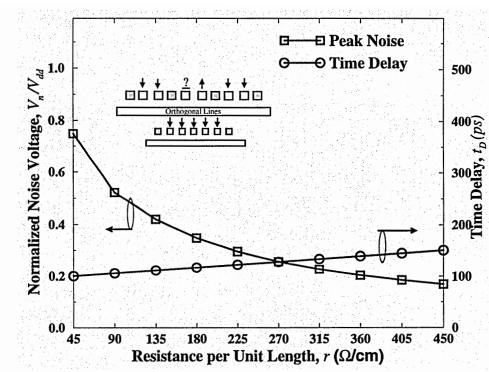

| Figure 4.6: | Peak in and out-of-phase noise voltages versus interconnect resistance per unit length                                                                                                                                                                               |

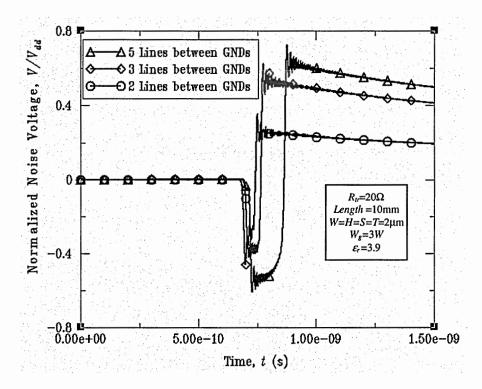

| Figure 4.7: | Noise voltage at the end of a middle victim line when there are 2, 3 or 5 signal lines between power/ground lines. Unlike the ideal return path case, far lines have a large impact on the worst case crosstalk60                                                    |

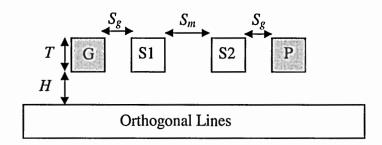

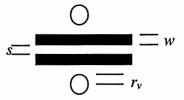

| Figure 5.1: | A cross-sectional view of two signal lines between two power/ground lines                                                                                                                                                                                            |

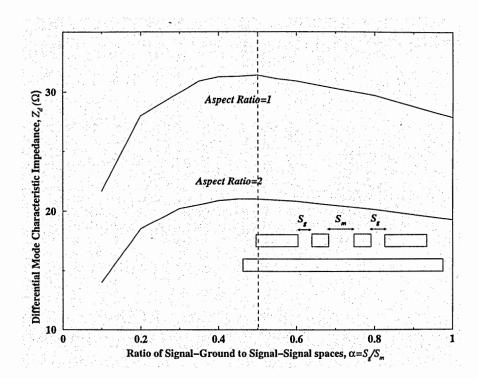

| Figure 5.2: | The differential mode characteristic impedance versus the spacing65                                                                                                                                                                                                  |

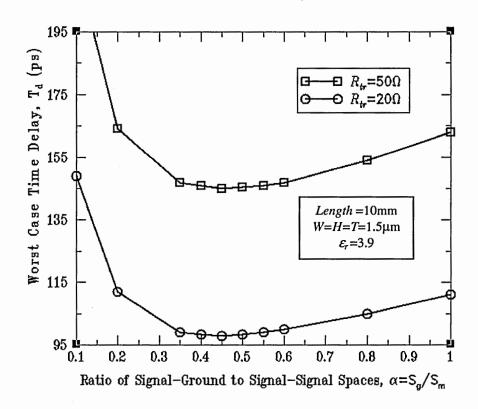

| Figure 5.3: | Worst case time delay versus the ratio of signal-ground to signal-signal spaces                                                                                                                                                                                      |

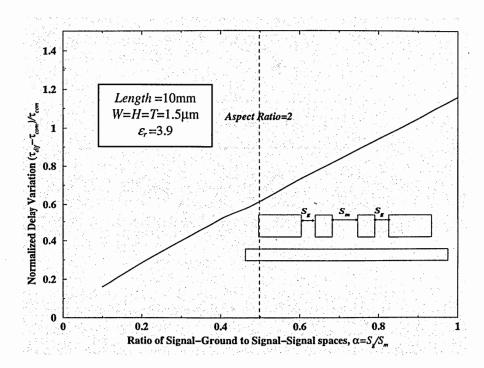

| Figure 5.4: | Normalized delay variation versus the spacing ratio $S_g/S_m$ for the aspect ratio of two                                                                                                                                                                            |

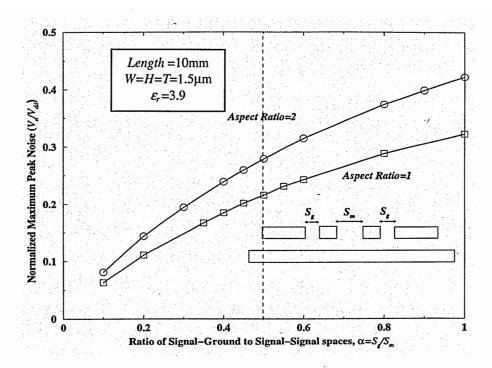

| Figure 5.5: | Maximum peak crosstalk versus the spacing ratio, $S_g/S_m$ for aspect ratios of 1 and 2. The maximum peak crosstalk is pessimistic because it is for a case that $R_{tr}=0$ , $C_L=0$ , and the line resistance is such that crosstalk is maximized                  |

| Figure 5.6:  | RC and RLC model latency and data flux density versus wire width for an interconnect 24mm long implemented at the 45 nm technology node. It has been assumed that optimal repeaters are used, and $W_G=2W$ , $T=S=W$ .                                                                               | 70 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.7:  | Data flux density-reciprocal latency product versus wire width for an interconnect 24 mm long implemented at the 45 nm technology node. In the shallow RLC region, the data flux density-reciprocal product attains its maximum.                                                                     | 72 |

| Figure 5.8:  | Data flux density-reciprocal latency product for in-phase and antiphase switching cases. The optimal wire width for common and differential modes are different. The worst case $\Phi_D/\tau$ is maximized when the difference between in-phase and anti-phase switching latencies is minimum.       | 73 |

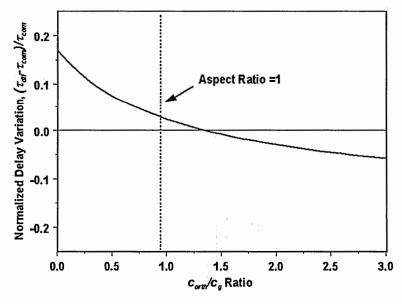

| Figure 5.9:  | Normalized delay variation versus $c_{orth}/c_g$ ratio when the optimal wire width is used. For a wide range of $c_{orth}/c_g$ ratios, common and differential mode delays differ less than 10%                                                                                                      | 75 |

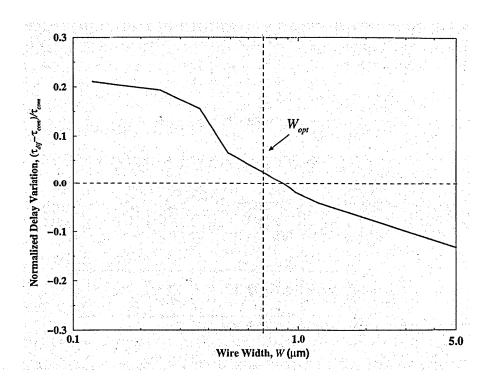

| Figure 5.10: | Normalized delay variation versus wire width for an optimally buffered interconnect implemented at the 45 nm technology node. At the optimal design point, delay variation is less than 3%                                                                                                           | 76 |

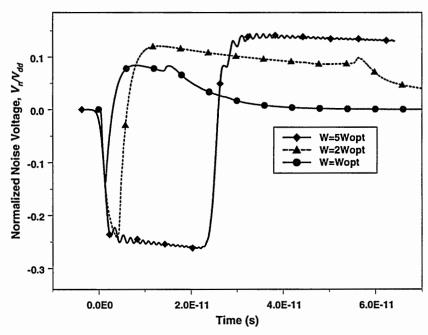

| Figure 5.11: | HSPICE simulations showing normalized crosstalk at the end of a quiet line when its adjacent line switches from low to high. Time zero corresponds to one time-of-flight delay. Peak and duration of out-of-phase noise match very well with what (5.25) and (5.31) predict with less than 3% error. | 77 |

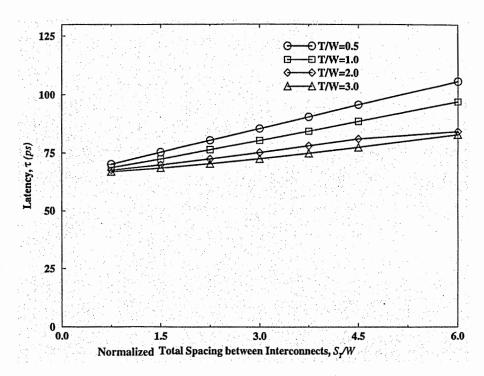

| Figure 5.12: | Interconnect latency versus total spacing for four the aspect ratios of 0.5, 1, 2, and 3. The total spacing $(S_T = S_g + 2S_m)$ is normalized to the wire width, and it is assumed that the optimal spacing ratio $(S_m/S_g = 0.45)$ and the optimal wire width are used.                           | 81 |

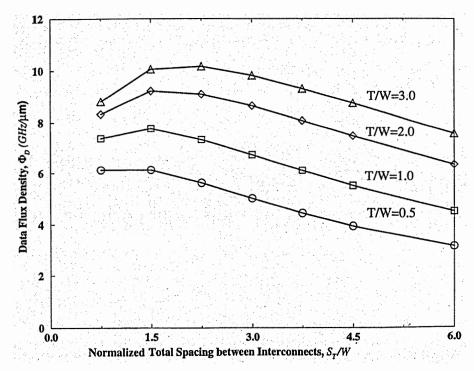

| Figure 5.13: | Data flux density versus total spacing for the aspect ratios of 0.5, 1, 2, and 3. Interconnects are 10mm long and are implemented at the 45 nm technology node.                                                                                                                                      | 82 |

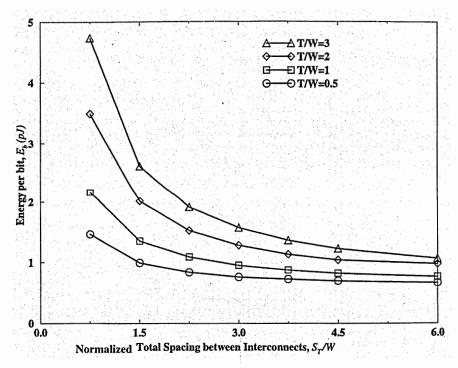

| Figure 5.14: | Energy per bit versus total spacing between interconnects for the aspect ratios of 0.5, 1, 2, and 3. Interconnects are assumed to be 10 mm long.                                                                                                                                                     | 83 |

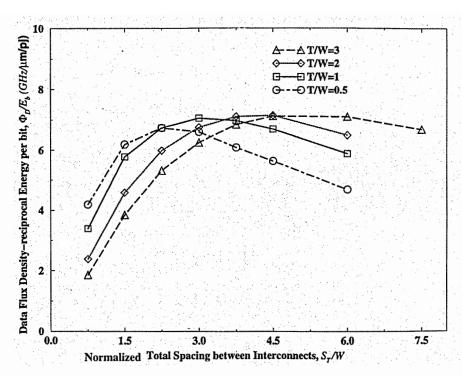

| Figure 5.15: | Data flux density-reciprocal energy per bit product versus total spacing between interconnects for aspect ratios of 0.5, 1, 2, and 3. Interconnects are 10mm long and are implemented at the 45nm technology node.                                                                                   | 84 |

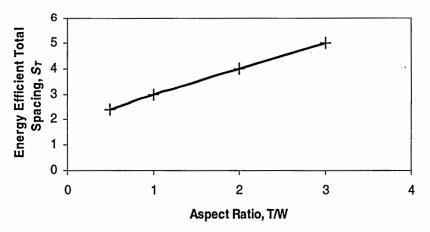

| Figure 5.16: | The energy efficient spacing versus aspect ratio. The energy efficient spacing, which maximizes $\Phi_D/E_b$ , increases as the aspect ratio increases.                                                                                                                                                                         | 84  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

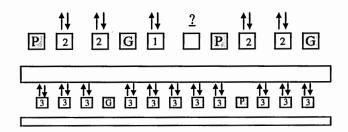

| Figure 6.1:  | A cross-sectional view of 4 top metal levels. Top two levels are relatively fat and due to inductive effects each signal line has a nearby power/ground line as a return path. The spaces between signal and ground lines are 0.45 times smaller than signal to signal spaces to reduce crosstalk and minimize worst-case delay | 88  |

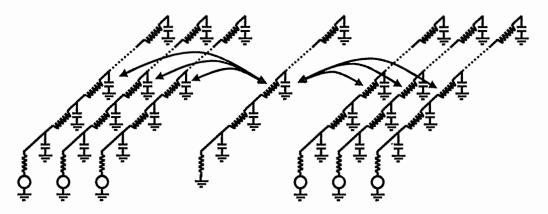

| Figure 6.2:  | A quiet victim line is attacked by some far aggressors. It has been assumed that there is no nearby aggressor and far lines are inductively coupled to the victim line. The resistance and capacitance matrices can be substituted by scalar resistance and capacitance values.                                                 | 90  |

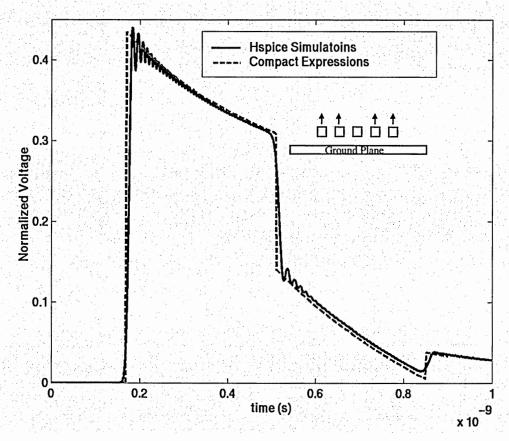

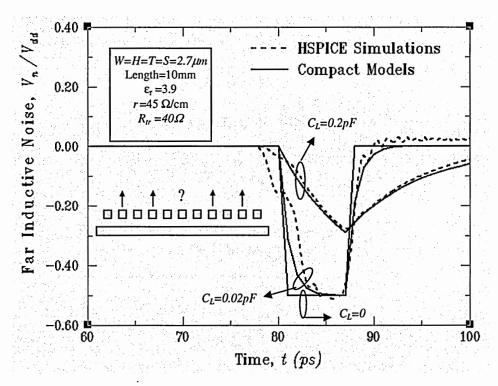

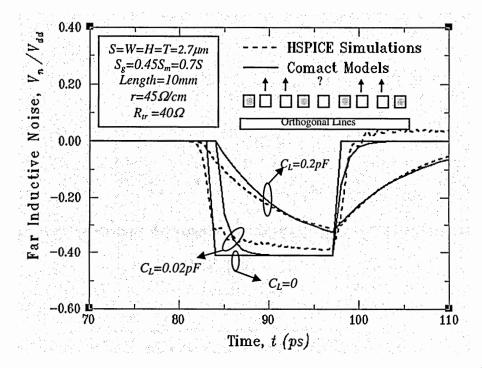

| Figure 6.3:  | The induced noise on the quiet line when all signal lines are shielded by two power/ground lines. HSPICE simulations are compared with compact models for different load capacitances. The input of the aggressors is a positive step voltage, $V_{dd}u_o(t)$ .                                                                 | 94  |

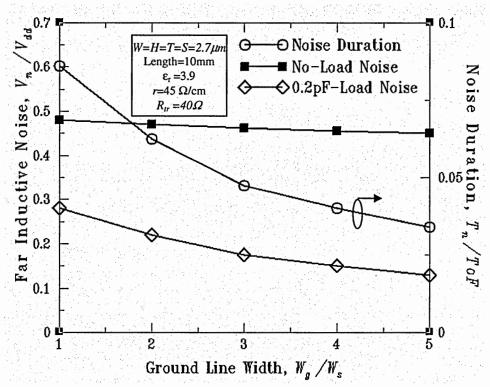

| Figure 6.4:  | The peak and duration of far inductive noise versus the ground line width for the structure shown in Figure 6.2. Increasing ground line width reduces all mutual inductances approximately by the same ratio. The peak noise of an open-ended line is independent of ground line width.                                         | 95  |

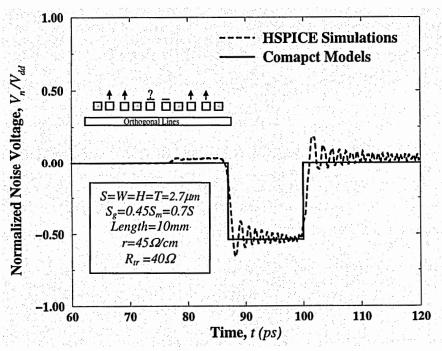

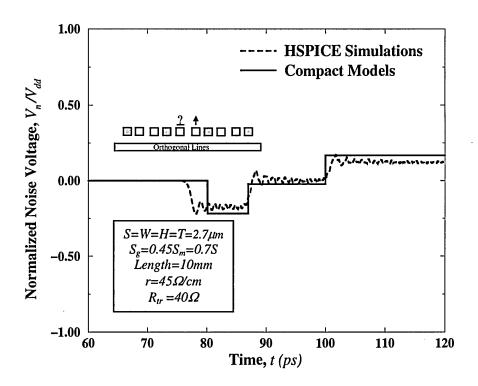

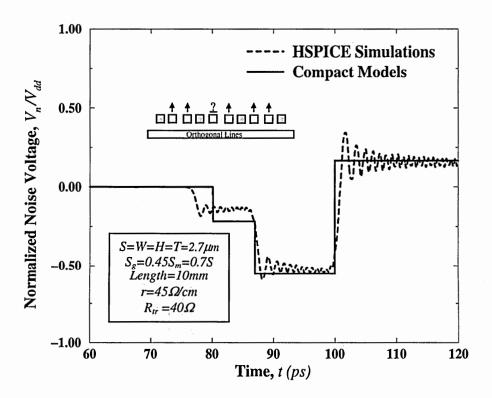

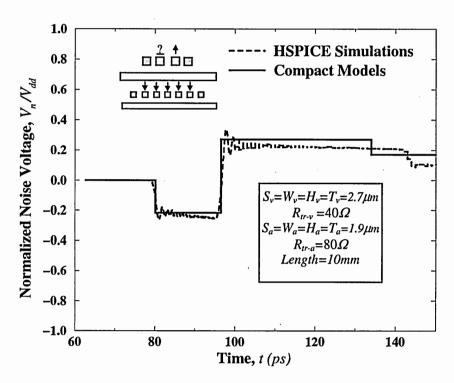

| Figure 6.5:  | The induced noise at the end of a quiet line for three different load capacitances. HSPICE simulations are compared with compact models. $S_g$ and $S_m$ are optimized so that the worst-case delay is minimized [6]                                                                                                            | 97  |

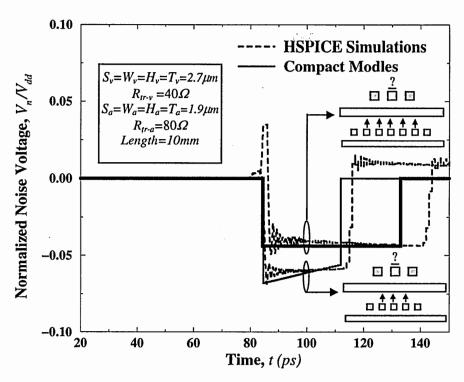

| Figure 6.6:  | Voltage at the end of a quiet victim line when it is affected by either three or five far aggressors that are two metal levels below the victim line. Line resistance for the two top levels is 45 $\Omega$ /cm and for the lower metal levels is 90 $\Omega$ /cm.                                                              | 99  |

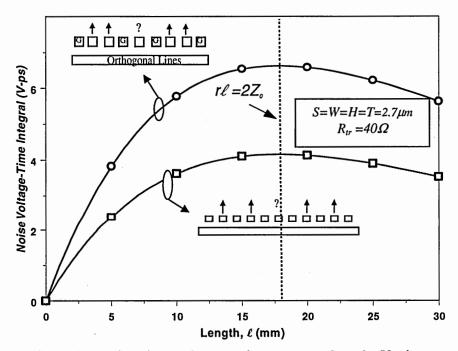

| Figure 6.7:  | Noise voltage-time integral versus interconnect length. $V_{dd}$ is assumed to be 1V. The value of this integral is independent of the load capacitance.                                                                                                                                                                        | 101 |

| Figure 6.8:  | Noise voltage at the end of a quiet victim line when intra-level far lines switch upward and a near aggressor stays quiet                                                                                                                                                                                                       | 103 |

| Figure 6.9:  | Noise voltage at the end of a quiet victim line when intra-level far lines are quiet and a near aggressor switches upward                                                                                                                                                                                                       | 105 |

| Figure 6.10: | Noise voltage at the end of a quiet victim line when all intra-level near and far aggressors switch simultaneously106                                                                                                                                                                                                         |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.11: | Noise voltage at the end of quiet victim line when near and intra-<br>level far aggressors switch simultaneously                                                                                                                                                                                                              |

| Figure 6.12: | Total noise caused by near, far intra- and inter-level aggressors. Far Lines switch in the opposite direction and intra-level far aggressors switch 20 ps after near and inter-level far aggressors. This shows the worst case scenario for crosstalk                                                                         |

| Figure 6.13: | Worst case noise voltage and interconnect latency versus resistance per unit length of interconnects in the top metal level for the structure shown in Fig. 13. It has been assumed that interconnects in the two lower metal levels have a resistance per unit length two times larger than that of the top two metal levels |

| Figure 6.14: | Worst case noise voltage and interconnect latency versus resistance per unit length of interconnects in the top metal level when optimal repeaters are used. All parameters are the same as those in Fig. 1411                                                                                                                |

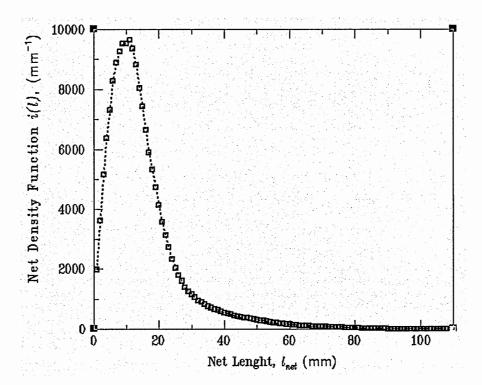

| Figure 7.1:  | Net length distribution for the projected microprocessor in the year 2011120                                                                                                                                                                                                                                                  |

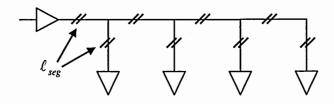

| Figure 7.2:  | A typical net with fan out 4120                                                                                                                                                                                                                                                                                               |

| Figure 7.3:  | The effective length depends on the location of the driver122                                                                                                                                                                                                                                                                 |

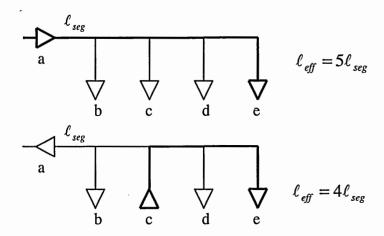

| Figure 7.4:  | Effective global net-length distribution for the projected SoC in the year 2011                                                                                                                                                                                                                                               |

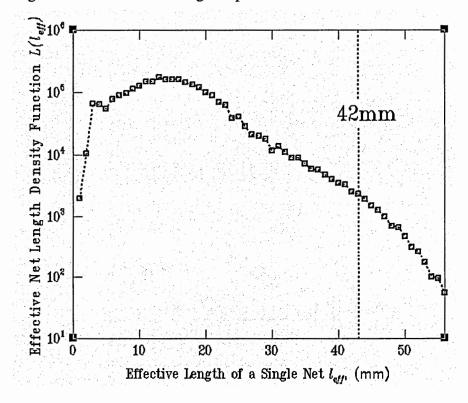

| Figure 7.5:  | The required number of pads versus the maximum on-chip interconnect length                                                                                                                                                                                                                                                    |

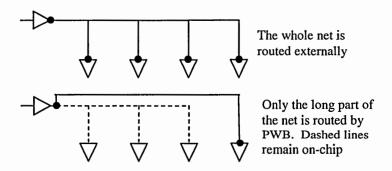

| Figure 7.6:  | By transferring just the longest parts of the nets to PWB the required number of pads can be reduced                                                                                                                                                                                                                          |

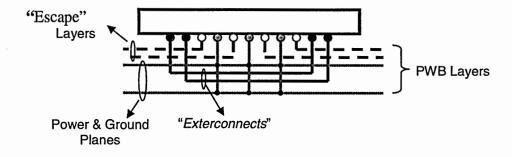

| Figure 7.7:  | PWB layers are used for routing the standard I/Os to other chips, power and ground distribution, and exterconnects125                                                                                                                                                                                                         |

| Figure 7.8:  | A channel with two lanes                                                                                                                                                                                                                                                                                                      |

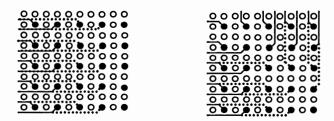

| Figure 7.9:  | A quadrant of the standard I/Os routed to the other chips through PWB. They can be routed either through two edges (left) or four edges (right). The dashed lines show the wires in the next layer12                                                                                                                          |

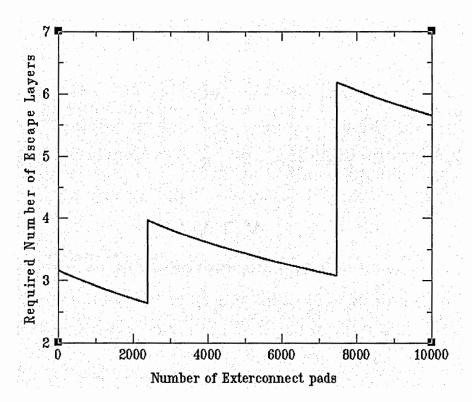

| Figure 7.10: | The required number of PWB layers to route standard I/Os versus the number of exterconnect pads                                                                                                                                                                                                                               |

| Figure 7.11: | The via blockage1                                                                                                                                                                                                                                                                                                                   | 130         |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

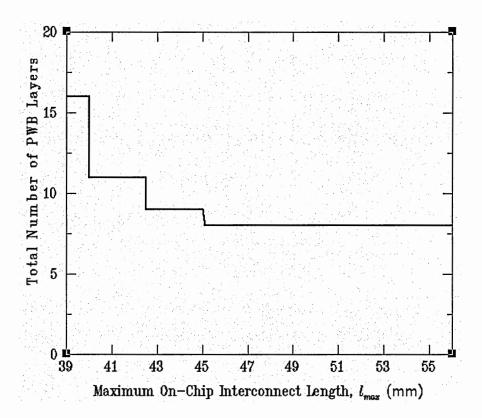

| Figure 7.12: | Total number of PWB layers versus the maximum on-chip interconnect length. Four additional layers are required to achieve the highest global clock frequency.                                                                                                                                                                       | 131         |

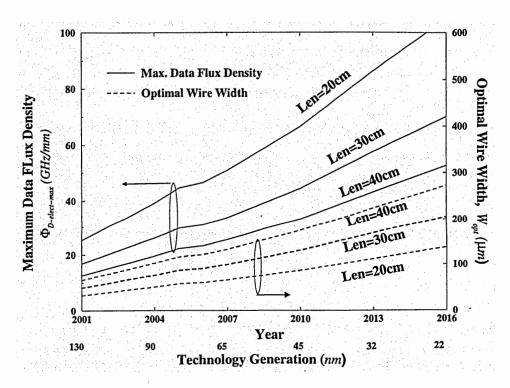

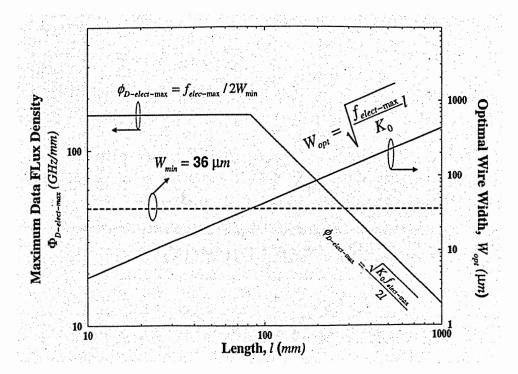

| Figure 8.1:  | Maximum data flux density and optimal wire width for 20, 30 and 40 cm long interconnects implemented in different technology generations. Both maximum data flux density and optimal wire width increase in future generations because of faster transistors                                                                        | 140         |

| Figure 8.2:  | Maximum data flux density and optimal wire width versus interconnect length for the 45 nm technology node. The dashed line shows the minimum line width available on-board as projected by the ITRS                                                                                                                                 | 141         |

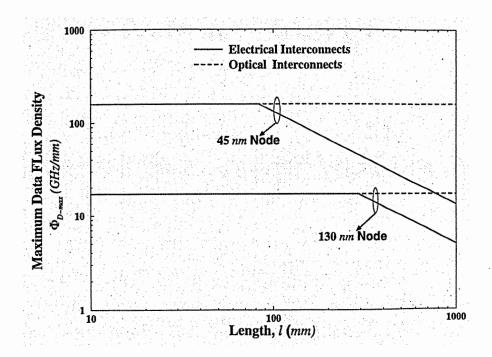

| Figure 8.3:  | Maximum data flux density for electrical and optical interconnects implemented in 130 and 45 nm technology nodes. Performance of optical waveguides is length independent                                                                                                                                                           | 143         |

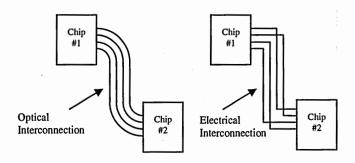

| Figure 8.4:  | Unlike electrical interconnects, optical waveguides can not be routed arbitrarily because sharp bends and inter-level communication should be minimized due to power budget constraints                                                                                                                                             | 144         |

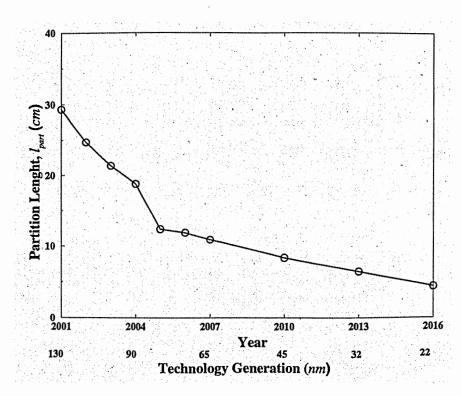

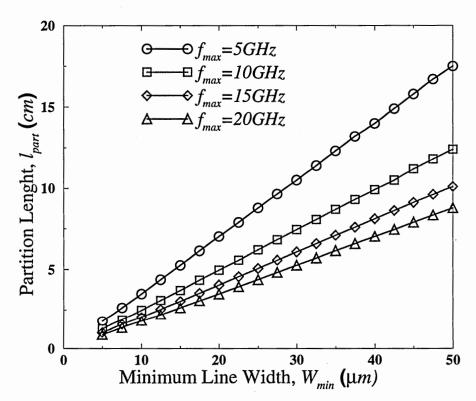

| Figure 8.5:  | Partition length between optical and electrical interconnects for different generations of technology. Partition length decreases in future generations because of faster transistors and finer PWB line width.                                                                                                                     | 145         |

| Figure 8.6:  | The partition length between optical and electrical interconnects versus minimum available board-level line width. Having a $W_{min}$ of about 10 $\mu$ m makes the partition length shorter than almost all board-level interconnects; hence, justifies replacing all board-level electrical interconnects with optical waveguides | l <b>46</b> |

#### Summary

The main objective of this thesis is to develop new interconnect-centric methodologies to optimize global interconnects in a GSI chip. A length-independent optimal wire width is rigorously found that simultaneously maximizes data flux density and minimizes latency. Data flux density is the product of interconnect bandwidth and reciprocal pitch and represents the number of bits per second that interconnects can transfer per unit width. Other cross-sectional dimensions are also optimized to minimize crosstalk, energy-per-bit and the dynamic delay variation caused by different switching patterns. The optimization process is based on novel compact physical models that are derived in this thesis for latency and crosstalk of co-planar distributed RLC lines. Rigorous physical models are derived for multi-level crosstalk noise that take into account virtually all near as well as inter- and intra-level far aggressors. These models prove that crosstalk remains small and constant in all generations of technology if optimal wire dimensions are utilized. Chippackage co-design methodologies are also developed that show the optimal partition between chip-level and package-level signal and power distribution. Finally, the lengths beyond which optical waveguides can outperform electrical wires in terms of data flux densities are identified for various technology generations.

# Chapter 1

## Introduction and Background

#### 1.1 Introduction

Since their invention in 1958, integrated circuits have grown exponentially in terms of number of transistors, speed and functionality. This trend, which is known as Moore's law [1], has survived thanks to the fact that the performance of a transistor improves as its physical dimensions scale down; a smaller transistor runs faster and dissipates less power. On the contrary, interconnect performance degrades as its cross-sectional dimensions scale down; a thinner wire has a larger latency. For instance, as technology advances from 1  $\mu m$  to the 100 nm node, the RC delay of a 1 mm long interconnect devolves from 6 times faster to 20 times slower than the intrinsic delay of a transistor [2]. This turns into a serious problem for inter-macrocell or global interconnects whose lengths do not scale with technology [3, 4]. To avoid prohibitively large interconnect latencies, designers scale down global wire dimensions more slowly than the transistor dimensions [5, 6], and this causes a rapid growth in the gap between transistor density and interconnect density. Thereby, as technology advances, global interconnect resource becomes more and more valuable than the transistor resource. The central hypothesis of this thesis is that the design of GSI chips should shift from transistor-centric to interconnect-centric to facilitate efficient use of valuable on-chip metal levels.

The existing interconnect design methodologies use a pre-defined wiring distribution to determine the required wire dimensions on each metal level which satisfy specified system performance targets [7, 8, 9, 10]. However, as GSI chips become interconnect-limited, such methodologies cannot optimally exploit the available wiring resource. In contrast, the proposed interconnect-centric approach suggests optimizing wire dimensions without making any assumption about wiring distribution, net-list or placement. Wire dimensions are optimized such that minimum latency and maximum data flux density (bandwidth per unit width of interconnects) are simultaneously achieved. The structure of global interconnects, which are mainly data buses between macro-cells, should then be designed based on the optimal wire dimensions.

As the clock frequency of GSI chips reaches several gigahertz, lengths of many onchip global interconnects become comparable with the signal wavelength. Thereby, it

would be quite unrealistic to ignore the impact of inductance on latency and crosstalk of

global interconnects [11]. Because of lack of on-chip ground planes, the classic

transmission line theory cannot be directly applied to the modeling of on-chip distributed

RLC lines. Numerical solutions and circuit simulations can be used to analyze on-chip

RLC lines. However, compact physical models are more insightful, and they can be

easily incorporated in the system-level optimization. A major part of this thesis is,

therefore, devoted to deriving compact physical models for delay and crosstalk of on-chip

distributed RLC lines. These models are then used to optimize the design of global

interconnects.

Today's chips and packages are so inter-related that they can no longer be designed independently. A package can partially distribute signal, clock and power across the chip, and by doing so, it can significantly improve the performance of a chip. In this thesis,

optimal partitions between chip-level and package-level signal and power interconnects are identified.

Optical interconnection has been suggested as an alternative for electrical interconnection for many years. The lengths beyond which optical interconnects outperform electrical interconnects in terms of data flux density are identified for various technology generations. The partition lengths are found assuming that optical emitters and detectors will mature enough to become comparable with their electrical counterparts. The partition lengths show that optical interconnects are more promising for chip-to-chip interconnection, and if high-resolution printed boards are available, optical waveguides can outperform almost all typical chip-to-chip wires.

The outline of this thesis is as follows. In Chapter 2, a new interconnect-centric design methodology is proposed that demonstrates how global wire width can be optimized to minimize latency and maximize data flux density simultaneously. The major emphasis of Chapter 2 is on the concept of wire width optimization, and hence in this chapter, interconnects are modeled as simple RLC interconnects above an ideal ground plane. N-coupled RLC lines above an ideal ground plane are modeled in Chapter 3, and co-planar transmission lines above orthogonal lines that are typically used for on-chip global interconnects are modeled in Chapter 4. In Chapter 5, these physical models are used to identify the optimal cross-sectional dimensions of real on-chip global interconnects. In Chapter 6, novel models are presented for crosstalk in a multi-level interconnect network considering all near as well as intra- and inter-level far aggressors. It is also illustrated that by using optimal wire dimensions, crosstalk remains small and constant in all generations of technology. The impact of on-chip global interconnect

optimization on package design is studied in Chapter 7. Chapter 8 discusses optical and electrical interconnection wherein a partition length is identified that shows the lengths beyond which optical interconnects offer a larger data flux density. Finally, conclusions and future work are portrayed in Chapter 9.

#### 1.2 Optimal Global Interconnects for GSI

Performance of a high-speed chip is largely affected by both latency and bandwidth of global interconnects, which connect different macrocells. Therefore, one of the important goals is to design high-bandwidth and fast buses that connect a processor and its on-chip cache memory, or link different processors within a multiprocessor chip. The width of global interconnects is optimized to achieve a large "data flux density" and a small latency simultaneously. "Data flux density" is the product of interconnect bandwidth and reciprocal wire pitch, which represents the number of bits per second that can be transferred across a unit length bisectional line. The optimal wire width, which maximizes the product of data flux density and reciprocal latency, is independent of interconnect length, and can be used for virtually all global interconnects. It is proved that the optimal wire width is the width that results in a delay 33% larger than the time-offlight. Using the optimal wire width decreases latency, energy dissipation, and repeater area considerably compared to a sub-optimal wire width (e.g. 42% smaller latency, 30% smaller energy-per-bit, and 84% smaller repeater area compared with the  $W_{opt}/2$  case) at the cost of a small decrease in data flux density (e.g. 14% smaller compared with  $W_{opt}/2$ case). A super-optimal wire width, however, causes a slight decrease in latency (e.g. 14% for  $2W_{opt}$ ) at the cost of a large decrease in data flux density (e.g. 35% for  $2W_{opt}$ ).

#### 1.3 Compact Physical Models

#### 1.3.1 Distributed RLC Lines above an Ideal Ground Plane

To study the impact of far aggressors on board-level interconnects, the set of differential equations of n-coupled RLC lines above an ideal ground plane is solved rigorously. The models prove that a nearby ground plane is key in controlling far inductive coupling, and the impact of far lines on the worst-case crosstalk is negligible. In other words, in most practical cases, a three RLC line model can accurately predict the worst-case crosstalk. This result is contrary to what is found for on-chip interconnects, and highlights a major distinction between board-level and chip-level interconnects.

#### 1.3.2 Co-Planar RLC Lines above Orthogonal Lines

Compact physical models are derived for the delay and crosstalk of on-chip co-planar transmission lines, which are employed in state-of-the-art high-speed microprocessors. These lines are mainly used for long global interconnects that are relatively thick and wide, and have prominent inductive effects. Using the existing models for the periodic structures, it is shown that the orthogonal lines increase the capacitance per unit length of interconnects without changing their inductance per unit length because current cannot return through the orthogonal lines. The wave propagation speed is, therefore, smaller than the speed of light in the interconnect dielectric. Simplified compact expressions are also presented that offer insight and accurate estimation for latency and crosstalk of global interconnects.

These models are then used to optimize the design of co-planar global interconnects.

For the case that there are two signal lines between power and ground lines, it is proved

that interconnect latency is minimized if the ratio of signal-ground spacing to signal-signal spacing is equal to 0.45. This optimal spacing ratio is independent of interconnect aspect ratio, and reduces the crosstalk and dynamic delay variation by 38% and 48%, respectively, as compared to the equal spacing case. The optimal wire width that simultaneously maximizes data flux density and minimizes latency is then identified. Using the optimal wire width together with the optimal spacing ratio limits the crosstalk and dynamic delay variation to less than  $0.2V_{dd}$  and 10%, respectively.

#### 1.3.3 Multi-Level Crosstalk Noise

For the first time, compact physical models are derived for crosstalk noise of co-planar RLC lines in a GSI chip that simultaneously consider far and near aggressors in both the same metal level and distant metal levels. Since both the amplitude and duration of noise are important, the noise voltage-time integral can be defined as a figure-of-merit for crosstalk, and it is shown that this integral attains its maximum at the length at which interconnect resistance becomes equal to twice characteristic impedance. It is also established that crosstalk can be prohibitively large if interconnects have small resistances. There is, therefore, a trade-off between interconnect latency and crosstalk. Finally, it is proved that using the optimal wire width results in small and constant crosstalk noise in all generations of technology.

#### 1.4 Chip-Package Co-Design Methodologies

#### 1.4.4 Signal Interconnection

High-quality low-loss transmission lines that are available at the package or board level can be exploited to enhance global signal interconnection. Since on-board interconnects are typically wide and thick, their loss is small, and their latency is ToF limited if they are properly driven. Some of the long global interconnects can be routed through exterconnects (external interconnects), and in this manner, the largest interconnect delay can be reduced that improves the global clock frequency. The main disadvantage of board-level interconnects is their small wiring density that limits the use of exterconnects. An optimal partition is identified between interconnects and exterconnects to achieve the largest possible global clock frequency with minimum number of exterconnects. The partition length is the length of an on-chip interconnect that has a latency equal to the ToF of the longest exterconnect. Knowing that optimal on-chip wire width results in a latency 33% larger than the ToF, the partition length would be equal to 75% of the longest synchronized interconnect.

Using stochastic wire length models, the total length of all nets that should be routed by exterconnects is found. The total additional board layers is then found considering the layers required to route standard signal I/Os and power and ground planes. For a projected chip at the 45 nm technology node, 4 additional board levels and 1800 additional I/Os can improve the global clock to the maximum possible value which is 33% greater than the design with no exterconnects.

#### 1.4.5 Power and Ground Interconnection

For a given IR drop budget, there is a trade-off between the number of power and ground pins of a package and the on-chip metal area that should be dedicated to power and ground distribution. Knowing the optimal on-chip wire dimensions and also considering that every global signal line should have a nearby power/ground line as a return path, the required number of power and ground pins is identified for various generations of technology. The results show that for future technology generations, more I/O pins should be dedicated to power and ground due to larger current densities and smaller power supplies.

#### 1.5 Optical Interconnection versus Electrical Interconnection

The lengths beyond which board-level optical waveguides are capable of transferring a larger number of bits per second than electrical interconnects are found for various technology generations. Based on the ITRS projections, as technology scales from the 130 nm technology node to the 45 nm technology node, the partition length falls from 29 cm to 8.3 cm due to 7 times faster drivers and 25% finer waveguide pitch.

## Chapter 2

## Optimal Global Interconnects for GSI

#### 2.1 Introduction

As CMOS technology advances towards gigascale integration (GSI), the delays of transistors, and local interconnects with negligible resistance scale down. As a result, the local clock frequency is projected to increase significantly [12, 3]. Delay of global interconnects, however, increases with technology scaling because their lengths do not scale down. In fact, since the chip size and the number of transistors are projected to increase, the length and number of global interconnects will increase. Consequently, global interconnects limit the overall performance of a system-on-a-chip [4], and global clock frequency is projected to increase more slowly than local clock frequency. Repeater insertion and reverse scaling are two key solutions to reduce the delay of long interconnects [13]. Using fat wires, however, reduces the wiring density, which may reduce "data flux density", the product of bandwidth and reciprocal pitch of an interconnect. The data flux density represents the number of bits per second that an interconnect can transfer per unit width. It determines the chip bisectional bandwidth and therefore, the total number of bits per second that global interconnect levels can potentially transfer. It should be noted that bandwidth is as important as latency, for highperformance systems. For instance, embedded memory plays a critical role in the performance of a microprocessor. The ITRS has therefore projected that 90% of the transistors in a GSI chip of the 45 nm technology node will be used as embedded memory

[12]. Two key parameters that define the performance of a cache memory are the number of bits per second that can be transferred between the cache and processor, and its access time [14, 15]. Hence, bandwidth and latency of interconnects that connect the cache and processor are equally important. Likewise, in a multiprocessor chip, different processors should be able to transfer large data packets with a small latency. The main goal of this chapter is to determine the wire dimensions which offer the best trade-off between latency and data flux density.

Various approaches to solve the wire sizing and wire layer assignment problems have been described in [7, 8, 9, 10]. All these algorithms assume a pre-defined wiring distribution to determine the required wire dimensions on each metal level which satisfy specified system performance targets. However, as the design of high-performance GSI systems becomes increasingly interconnect-centric [16], new opportunities arise to optimize the global interconnect design without assuming a wiring distribution and before any detailed floor planning or layout is done. A typical GSI chip would have tens of macrocells, with each macrocell consisting of several hundred thousand to a few million gates. This allows greater flexibility in the design of the inter-macrocell global interconnects. For instance, two low bandwidth interconnects can be used instead of one high bandwidth interconnect, or vice versa. Therefore, unlike the local intra-macrocell interconnects, the global interconnect routing need not be restricted to a fixed netlist. This flexibility permits optimization of the global interconnections for achieving a large data flux density and a small latency. The key assumptions and design goals of this new methodology are compared to previous works in Table 2.1.

Table 2.1: Key assumptions and design goals of different methodologies for optimizing interconnecting devices.

| Methodologies                    | Assumptions                                                                                                                                                     | Goals                                                           |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Davis [7]<br>& Venkatesan<br>[8] | <ul> <li>Intra-macrocell interconnect design.</li> <li>A pre-defined homogenous wiring distribution.</li> </ul>                                                 | Minimize area, # of layers, clock frequency, or power.          |

| Kahng [9]                        | <ul> <li>Intra-macrocell interconnect design</li> <li>A pre-defined wiring distribution.</li> </ul>                                                             | Minimize the # of metal levels.                                 |

| Zarkesh-Ha<br>[10]               | <ul> <li>Inter-macrocell interconnect design.</li> <li>A pre-defined heterogeneous global wiring distribution.</li> </ul>                                       | Meet wiring demand, crosstalk, and bandwidth requirements.      |

| New<br>Approach                  | <ul> <li>Inter-macrocell interconnect design.</li> <li>No pre-defined wiring distribution.</li> <li>Flexibility in inter-macrocell interface design.</li> </ul> | Maximize chip bisectional bandwidth-reciprocal latency product. |

The wire width at which the delay of an interconnect is 33% larger than the time-of-flight (ToF) is identified to be the optimal wire width because it maximizes the product of data flux density and reciprocal latency. It is shown that this optimal wire width is determined by the resistivity of the metal and the intrinsic delay of the repeaters, and is independent of the interconnect length, which facilitates its use for all global interconnects. Utilizing the optimal wire width reduces the latency by 42%, the energy dissipation of global interconnects by 30%, and the global repeater area by 84% compared to the case that half the optimal wire width is used. The price is only 14% smaller data flux density. On the other hand, further reduction of latency reduces data flux density, considerably. For instance, increasing the wire width from  $W_{opt}$  to  $2W_{opt}$  decreases latency by only 14%, but data flux density reduces by 35%.

The major emphasis of this chapter is the concept of wire width optimization, and hence interconnects are modeled as simple RLC lines above an ideal ground plane. In Chapter 4, compact physical models are derived for co-planar transmission lines that are

typically utilized for global interconnects. These models are then used in chapter 5 to optimize on-chip global interconnects. Also, in this chapter, all cross-sectional dimensions are considered to be equal, and the aspect ratio and the spacing between interconnects are optimized in Chapter 5.

The impact of wire width on latency and data flux density is shown in Section 2.2, in which the optimal wire width is introduced as the design with the best trade-off between latency and data flux density. The utility of using the optimal wire width in reducing the power consumption, repeater area, and via blockage is demonstrated in Section 2.3. The conclusions are summarized in Section 2.4, and the rigorous derivation of the optimal wire width is provided in the Appendix A.

#### 2.2 Optimal On-Chip Wire Width

#### 2.2.1 Impact of Wire Width on Latency

The delay of an interconnect with optimal number and size of repeaters using the RC model is [13]

$$\tau = 2.5 \frac{\ell}{W} \sqrt{\xi \rho \varepsilon_r \varepsilon_0 R_0 C_0} , \qquad (2.1)$$

where  $\ell$  and W are the wire length and width respectively,  $\rho$  is the metal resistivity,  $R_0$  and  $C_0$  are the output resistance and input capacitance of a minimum size repeater,  $\varepsilon_r \varepsilon_0$  is the dielectric permittivity, and  $\xi$  is a dimensionless constant determined by the wire geometry and it is given by

$$\xi \equiv \frac{rW^2}{\rho} \times \frac{c}{\varepsilon_r \varepsilon_0},\tag{2.2}$$

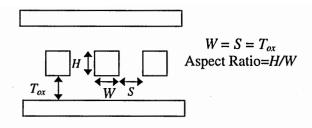

Figure 2.1: The cross-section of a wire and its neighbors.

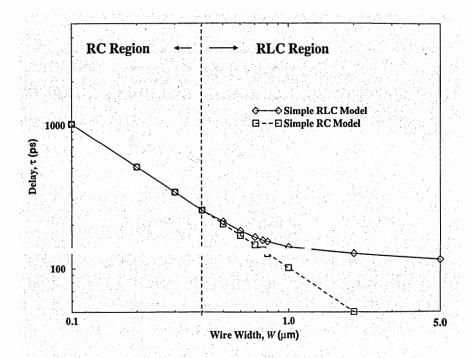

Figure 2.2: Time delay of a 24 mm long interconnect with optimal repeaters versus wire width. The cross-section of the wire is shown in Figure 2.1.

where r and c are the resistance and capacitance per unit length. It should be noted that  $\xi$  is determined by the geometry of the wires and is independent of the resistivity of the metal or the dielectric constant. For instance, if the metal resistivity  $\rho$  changes, the resistance per unit length r changes proportionally, and  $\xi$  remains unchanged. Wire width W, spacing S, and dielectric thickness  $T_{ox}$  are assumed to be equal, as shown in Figure

2.1. For the unity aspect ratio (H/W = 1),  $\xi$  is found to be 6.05 using RAPHAEL [17] for extracting the capacitance per unit length. The dashed line in Figure 2.2 shows the time delay of an interconnect versus the wire width using the RC model described by (2.1). All technology parameters are projections of the International Technology Roadmap for Semiconductors (ITRS) [12] for the year 2010 (45nm node).

Increasing the wire width decreases the RC model delay by the same ratio, as shown in Figure 2.2. Note that this is true only if all dimensions are simultaneously scaled larger  $(W=S=T_{ox}=H)$ ; Otherwise, by only increasing wire width, for example, the delay will not decrease proportionally because a wider line will have a larger capacitance which negates the resistance reduction. Since the metal and the dielectric thicknesses of each interconnect layer have to be constant across the chip, the wire dimensions should be optimized for the whole layer, and it is not feasible to optimize them for each interconnect separately.

Although (2.1) is valid for a small W, the impact of inductance cannot be neglected for large values of W. Optimal number and size of repeaters are determined considering the impact of inductance [18]. Assuming that these optimal values are used, the RLC model delay of an interconnect versus the wire width is shown in Figure 2.2. The skin effect is also considered when the wire dimensions are comparable with the skin depth. The skin depth is calculated for the third harmonic of the global clock frequency.

It can be inferred from Figure 2.2 that as long as the RC model is valid, increasing the wire width decreases the delay by the same ratio. However, when the wire width is large enough so that the RC model deviates from the RLC model, increasing the wire width does not decrease the delay proportionally.

#### 2.2.2 Impact of wire width on bandwidth

Data flux density (per unit width) is defined as the product of bandwidth and reciprocal pitch of an interconnect, and represents the number of bits per second that can be transferred across a unit length bisectional line. The data flux density can be written as

$$\Phi_D(W) \equiv \frac{Bw}{P} = \frac{1/\tau}{2W},\tag{2.3}$$

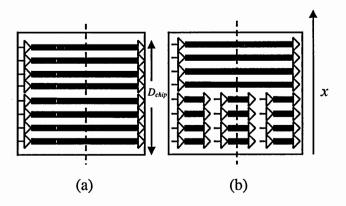

where Bw is the bandwidth of an interconnect and P is the wiring pitch. It has been assumed that Bw is determined by the reciprocal latency and the spacing between wires is equal to the wire width. It will be shown here that maximizing the data flux density, maximizes the "chip bisectional bandwidth," and therefore, the total number of bits per second that can be transferred through the global interconnects. One level of the global interconnects is shown in Figure 2.3.a, where all interconnects are assumed to have a length equal to the chip edge dimension,  $D_{chip}$ . The bisectional bandwidth of the layer (the number of bits per second that pass through the dashed line of length  $D_{chip}$ ) is

$$Bw_{bisec} = D_{chip}\Phi_D; (2.4)$$

therefore, maximizing  $\Phi_D$  maximizes the bisectional bandwidth. This is also true when interconnects have different lengths because in general, the bisectional bandwidth is (Figure 2.3.b)

$$Bw_{bisec} = \int_0^{D_{chip}} \Phi_D(x) dx. \qquad (2.5)$$

Figure 2.3: A layer of global interconnects. (a) All interconnects have the same length. (b) Length of interconnects are different.

For the case that the global communication is synchronized with a global clock, the delay of the longest interconnect determines the clock cycle and the data flux density is the same for interconnects with different lengths. In the asynchronous case, the data flux density can be different. In all cases, however, maximizing the data flux density maximizes the chip bisectional bandwidth or the total bandwidth regardless of the net length distribution. Note that the dashed line in Figure 2.3 is an imaginary line that can be positioned at any location on the die.

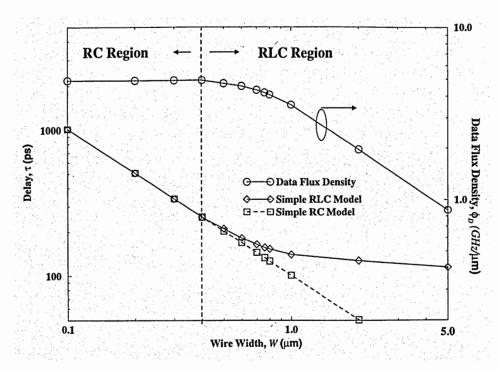

The data flux density,  $\Phi_D$ , is plotted against the wire width in Figure 2.4. It can be seen that as long as the RC model is valid (the difference between the RC and RLC models is small),  $\Phi_D$  is almost constant. This is reasonable since W is canceled out in (2.3) when  $\tau$  is substituted by (2.1). In the deep RLC region, however,  $\Phi_D$  drops rapidly as W increases.

Figure 2.4: Data flux density versus wire width for a 24 mm long interconnect. Interconnect delay is also plotted. Data-flux density is constant in the RC regime and in the RLC regime, it drops as wire width decreases.

#### 2.2.3 Optimal Wire Width

The quintessential purpose of an interconnect is communication between distant points with small latency [2]. It is therefore desirable to transfer as many bits as possible per unit time through the interconnects with small latency. In other words, large data flux density and small latency are simultaneously desired. Assuming that latency and data flux density are equally important, the data flux density-reciprocal latency product,  $\Phi_D/\tau$ , can be defined as the figure of merit, and optimal wire width would be the width at which  $\Phi_D/\tau$  is maximized. Using (2.3), this figure-of-merit can be written as

$$\frac{\Phi_D}{\tau} = \frac{1}{2W\tau^2} \,. \tag{2.6}$$

This new metric is plotted against wire width in Figure 2.5. It is shown that  $\Phi_D/\tau$  attains its maximum in the "shallow" RLC region, where the difference between the RC and RLC model delays is 13%. At this design point, data flux density is only 14% smaller than its maximum value and latency is 33% larger than its minimum value (1.33ToF).

Figure 2.5: Data flux density-reciprocal latency product versus the wire width for a 24 mm long interconnect with optimal repeaters.

Figure 2.6: Time delay versus the interconnect width for different interconnect lengths. Optimal wire width is independent of length.

The optimal wire width is independent of interconnect length as can be seen from Figure 2.6 in which the RC and RLC model delays of three interconnects with different lengths (48, 36, and 24 mm) are plotted. This can be explained qualitatively by observing that in both RC and RLC regimes, interconnect delay is linearly proportional to interconnect length when optimal repeaters are used. Hence,  $1/t^2W$  for interconnects with different lengths differs by a constant factor  $(\ell_1^2/\ell_2^2)$ . Its maximum, however, occurs at the same wire width. This important fact facilitates using the optimal wire width for all global interconnects regardless of their lengths.

It is rigorously proved that the optimal wire width happens when the RC model delay becomes equal to 1.18 times the ToF delay (proof is in the Appendix A). This fact was also verified through HSPICE simulations for varying values of interconnect lengths,

aspect ratios and  $R_0$ ,  $C_0$  values. By substituting the above mentioned condition in (2.1), the optimal wire width is found to be

$$W_{opt} = 2.12c_0\sqrt{\xi\rho\varepsilon_0R_0C_0} , \qquad (2.7)$$

where  $c_0$  is the speed of light in free space. Equation (2.7) shows that the optimal wire width,  $W_{opt}$  depends solely on the resistivity of metal  $\rho$ , the intrinsic delay of a repeater  $R_0C_0$ , and the geometry of the wires ( $\xi$  factor).

The optimal wire widths for different generations of technology and aspect ratios are shown in Figure 2.7 based on the ITRS projections for  $\rho$  and  $R_0C_0$ . The intrinsic delay of a repeater,  $R_0C_0$  is found assuming equal pFET and nFET current drive capabilities.

Figure 2.7: Optimal wire width for different generations [12] and aspect ratios. Using optimal wire width makes the skin effect negligible. The skin depth is calculated for the third harmonic of the global clock frequency.

Skin effect can be neglected if the wire dimensions are smaller than three times the skin depth [19]. Therefore, as shown in Figure 2.7 for all technology generations, using the optimal wire width makes the skin effect negligible and utilizes the interconnect metal efficiently.

Knowing the value of this optimal wire width can help to design an efficient interface between different logic and memory cores in a GSI chip. The optimal wire width can be found at the early stage of the design because its value is determined by two basic parameters—resistivity of metal and intrinsic delay of repeaters. In this way, the structure of global interconnects can be designed such that the global interconnect levels are used as efficiently as possible. For instance, designers can use an n-bit data bus with a wire width of  $W_{opt}$  between the processor and the cache memory rather than a (2n)-bit data bus with  $W_{opt}/2$  wire thickness, or an (n/2)-bit data bus with  $2W_{opt}$  wire width. The wiring area required in all three cases is the same. However, the 2n-bit bus has a large latency (72% larger than the optimal case) and the (n/2)-bit bus has a small bandwidth (35% smaller than the optimal case). The global clock frequency can also be optimized by knowing the delay of the longest synchronized interconnect, which has a width equal to the optimal wire width. Operating at a global clock frequency larger than this value requires a wire width larger than the optimal value, which reduces the bisectional bandwidth; on the other hand, using a smaller global clock frequency increases the latency of all the interconnects, and reduces the system performance.

# 2.3 Optimal On-Chip Wire Width

Repeaters are widely used for global interconnects to increase the wiring density and reduce the delay. There are three important concerns about repeaters: power consumption, the required silicon area, and the via blockage. This section investigates the impact of using the optimal wire width on these three issues.

## 2.3.1 Power Consumption

The average energy consumed in each interconnect switching event can be approximated by

$$E_b = \frac{1}{2} (C_{\text{int}} + C_{rep}) V_{dd}^2.$$

(2.8)

where  $C_{int}$  is the capacitance of the interconnect and  $C_{rep}$  is the total capacitance of the repeaters in that interconnect. The capacitance of each repeater is linearly proportional to its WL ratio, therefore, assuming that WL ratio of repeaters is h times larger than that of a minimum size repeater, the total capacitance of all repeaters inserted along an interconnect is

$$C_{rep} = hkC_0, (2.9)$$

where k is the number of repeaters inserted along the interconnect. In the RC regime, the optimal size of repeaters is [13]

$$h_{opt} = \sqrt{\frac{R_0 C_{\text{int}}}{C_0 R_{\text{int}}}} , \qquad (2.10)$$

and the optimal number of repeaters is

$$k_{opt} = \sqrt{\frac{0.4R_{int}C_{int}}{0.7C_0R_0}}. (2.11)$$

Hence, when optimal repeaters are used the total capacitance of the repeaters can be written as

$$C_{rep} = 0.75C_{int}$$

. (2.12)

The optimum RLC repeater models should be used when [18]

$$1.33\sqrt{\frac{R_0C_0R_{\rm int}}{C_{\rm int}}} < Z_0, (2.13)$$

and the optimal size and number of repeaters in the RLC regime are given by [18]

$$h_{opt} = 1.15 \frac{R_0}{Z_0}, (2.14)$$

and

$$k_{opt} = 0.95 \frac{R_{\text{int}}}{Z_0}. (2.15)$$

$Z_0$ , the characteristic impedance of the line, is defined as

$$Z_0 = \sqrt{\frac{l}{c}} \,, \tag{2.16}$$

where l is the inductance per unit length. Assuming that the propagation speed is equal to the speed of light in the dielectric, the following relation can be derived [20]:

$$\frac{1}{\sqrt{lc}} = \frac{c_0}{\sqrt{\varepsilon_r}},\tag{2.17}$$

where  $c_0$  is the speed of light. Using (2.16) and (2.17),  $Z_0$  can be written as

$$Z_0 = \frac{\sqrt{\varepsilon_r}}{c_0} \times \frac{1}{c}.$$

(2.18)

In this manner, the total capacitance of the repeaters used for an interconnect operating in the RLC regime is

$$C_{rep} = \frac{1.09R_0C_0c_0^2(rc)(\ell c)}{\varepsilon_r}.$$

(2.19)

By using (2.2), the rc product can be written in terms of the geometry coefficient  $\xi$  as

$$rc = \xi \varepsilon_r \varepsilon_0 \frac{\rho}{W^2} \,. \tag{2.20}$$

Substituting (2.20) in (2.19) gives

$$C_{rep} = \frac{1.09R_0C_0c_0^2\xi\rho\varepsilon_0}{W^2}C_{\text{int}}.$$

(2.21)

Using (2.7), (2.21) can be simplified to

$$C_{rep} = 0.234 \frac{W_{opt}^2}{W^2} C_{\text{int}} \,. \tag{2.22}$$

The capacitance of an interconnect is independent of the wire width because it has been assumed that all cross-sectional dimensions are equal or proportional to the width (constant aspect ratio). Hence, as (2.22) shows, in the RLC regime, making wires fatter reduces the capacitance of the interconnect repeaters, thereby, reduces the power dissipation of the repeaters. By comparing (2.12) and (2.22), it can be found that at the optimal wire width, the power consumed by the repeaters is 67% smaller than the RC case, and the energy per bit, which is given by (2.8), is reduced by 30%. This is shown in Figure 2.8, which plots the consumed energy per bit in a 24 mm long interconnect. Figure 2.8 also shows that the optimal wire width offers a good trade-off between bandwidth and power dissipation by plotting data flux density-reciprocal energy per bit product  $\Phi_D/E_b$ .

Compared to the optimal wire width, at  $W_{opt}/2$  and  $2W_{opt}$ ,  $\Phi_D/E_b$  is smaller by 20% and 30%, respectively.

Figure 2.8: The required energy to transfer one bit of data along a 24 mm long interconnect versus the wire width. At the optimal wire width,  $\Phi_D/E_b$  is maximized.

It should be noted that although at the optimal wire width, the RC and RLC model delays are close, the optimal number of repeaters suggested by the RLC model is considerably smaller than that suggested by the RC model. For instance, for a 24 mm long interconnect in the 45 nm generation, the optimal number of repeaters predicted by the RC model is 35 whereas the RLC model predicts 19 repeaters. The power dissipation at the optimal wire width is therefore smaller than that of the RC regime.

#### 2.3.2 Repeater Area

Optimal repeater insertion in the RC regime requires a significant number of large repeaters, which consume a large silicon area and increase the via blockage. Some authors have, therefore, suggested tolerating a larger delay by *adequate* or *sub-optimal* repeater insertion instead of optimal repeater insertion [3, 8, 21, 22]. It will be shown here that the optimal wire width is an alternative solution to reduce the repeater demand with no performance loss.

The area occupied by each repeater with the standard cell model is [23]

$$A_{inv} = K_I \left[ 1 + \frac{(1+\beta)(h-1)}{\sqrt{k_I G_{ar}}} \right] F^2, \qquad (2.23)$$

where  $k_I$  and  $G_{ar}$  are the minimum sized inverter footprint area and aspect ratio, respectively. F is the minimum feature size, and  $\beta$  is the ratio of pFET and nFET sizes. In a custom cell,  $K_I$  is 102 and  $G_{ar}$  is 17/6 and a typical value for  $\beta$  is 2 so that the source and sink currents are approximately equal. Using (2.23) and the equations for optimal number and size of repeaters in the RC and RLC regions the required repeater area for a 24 mm long interconnect is plotted versus the wire width in Figure 2.9. In the RC regime, the repeater area is independent of the wire width and in the RLC regime it decreases with the wire width. At the optimal wire width, the required area is 3 times smaller than that of the RC regime. Further reduction of the repeater area, however, requires a considerable sacrifice in wiring density. The total repeater area that one pair of global wiring layers needs can be found assuming that the wiring efficiency is 50%. For a 570 mm<sup>2</sup> chip, which is projected for the 45 nm node [1], 3.78 mm<sup>2</sup> of silicon area is required for the repeaters if the optimal wire width (0.76  $\mu$ m) is used. In contrast, if a wire width

of  $W_{opt}/2$  (0.38 µm) is used, then a silicon area of 22.9 mm<sup>2</sup> is required for the repeaters of the global interconnect levels. Such a large increase in the repeater area is due to 2x increase in the wiring density and 3x increase in the repeater area per unit length of an interconnect. It is worthwhile to note that, in both cases, the global interconnect levels transfer almost the same number of bits per second.

Figure 2.9: The required silicon area for a 24 mm long interconnect and the total silicon area for global repeaters versus the wire width. The Chip area is assumed to be 572 mm<sup>2</sup>, and two levels of metal with a wiring efficiency of 0.5 are considered for global interconnects.

### 2.3.3 Via Blockage

Each repeater needs two vias to be connected to the wires in the global levels, which cause via blockage for all other metal levels since global wires are on top metal levels. For a given metal level, the via blockage factor is defined as [24]

$$B_{\nu} = A_{\nu} / A_{chip} , \qquad (2.24)$$

where  $A_v$  is the unused wiring area due to vias and  $A_{chip}$  is the chip area. The via blockage factor  $B_v$  can be estimated by [24]

$$B_{\nu} = \sqrt{N_{\nu} (2W + s\lambda)^2 / A_{chip}}$$

, (2.25)

where  $N_{\nu}$  is the number of vias passing through the metal level, s is the via covering factor, and  $\lambda$  is the layout rule unit. As (2.25) shows the wasted area due to via blockage is proportional to the square root of the number of vias. Figure 2.10 shows the number of vias required for a pair of global interconnect levels versus the wire width for the same projected chip implemented in 45 nm technology. It can be seen that the number of vias at the optimal wire width is 86% smaller than that of  $W_{opt}/2$  wire width.

Figure 2.10: Number of vias required for the repeaters associated with a pair of global interconnect levels versus the wire width.

In summary, the optimal wire width not only maximizes the data flux density-reciprocal latency product, but also reduces the power consumption, the repeater area, and the via blockage considerably. The important parameters corresponding to  $W_{opt}/2$ ,  $W_{opt}$ , and  $2W_{opt}$  are summarized in Table 2.2.

Table 2.2. Impact of using optimal wire width on a 24 mm-long interconnect in a projected ASIC chip at the 45-nm node of technology. The chip area is 572mm<sup>2</sup>. The global repeater area and number of vias correspond to two global metal levels with a wiring efficiency of 0.5.

| Parameters                                                                | W <sub>opi</sub> /2<br>(0.38 μm) | <i>W<sub>opt</sub></i> (0.76μm) | 2W <sub>opt</sub><br>(1.52 μm) |

|---------------------------------------------------------------------------|----------------------------------|---------------------------------|--------------------------------|

| Latency, τ (ps)                                                           | 266                              | 156                             | 133                            |

| Data flux density, $\Phi_D$ (GHz/ $\mu$ m)                                | 4.9                              | 4.2                             | 2.45                           |

| Data flux density-<br>reciprocal latency,<br>$\Phi_D/\tau((GHz)^2/\mu m)$ | 18.56                            | 26.8                            | 18.44                          |