# **Hierarchical Optimization of Digital CMOS Circuits for Power, Performance and Reliability**

A Dissertation Presented to The Academic Faculty

By

# Yuvraj Singh Dhillon

In Partial Fulfillment Of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

> Georgia Institute of Technology May, 2005

Copyright © 2005 by Yuvraj Singh Dhillon

# Hierarchical Optimization of Digital CMOS Circuits for Power, Performance and Reliability

Approved by:

Dr. Abhijit Chatterjee, Chair School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Jeffrey A. Davis School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. D. Scott Wills School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Thomas G. Habetler School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Adit D. Singh School of Electrical Engineering Auburn University

Date Approved: April 15, 2005

This dissertation is dedicated to my parents, Jaspal and Rajwant Dhillon, my sister, Monica and my wife, Puneet

## Acknowledgements

I am grateful to my advisor, Dr. Abhijit Chatterjee, for his support and guidance throughout my graduate career. He continuously motivated me to strive for my best and this helped me to improve the quality of my dissertation. I am thankful to Dr. Adit Singh for his keen interest in my research and his insightful comments/suggestions that helped me out of various dead-ends.

I thank Dr. Jeff Davis and Dr. Scott Wills for their suggestions during my proposal examination and afterwards that helped me to improve the work. I would like to thank Dr. Sean Lee for his informative and lively discussions about computer architecture, the "world" outside academia and the politics of conferences.

Thanks to Dr. Smaragdakis, Dr. Linda Wills, Dr. Doug Blough and Dr. Shomu Banerjee for their excellent teaching, which made taking courses so enjoyable.

My colleague, Utku Diril, has been an invaluable friend throughout my studies at Georgia Tech. He cheered me out of innumerable research lows and his cheerful spirits motivated me to keep striving for my goal.

I want to thank all my lab-mates for their friendship. They made my research life so much less tedious by their jokes, laughter and moral support.

I want to thank my parents, my sister and my wife for all the love and support they have provided me. I have reached up to this step only because of their blessings and their belief in me.

Finally, I want to thank God Almighty for always watching over me and guiding me in the right direction in my darkest hours.

# **Table of Contents**

| SummaryxiSummaryxiChapter I - Introduction11.1. Motivation11.2. Organization of Thesis5Chapter II - Survey of Low-Power, Reliable CMOS Circuit Optimization<br>Techniques72.1. Introduction72.2. Low Power Structural/Behavioral Design Techniques82.3. Low Power Logic Design Techniques92.4. Soft-Error Tolerant Design Techniques92.4. Soft-Error Tolerant Design Techniques16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization183.1 Introduction183.2 Topology Matrix Representation of Circuit Netlist183.3 Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1. Introduction274.2. Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3. Procedure for obtaining optimal values of supply and threshold voltages344.4. Clustering heuristic for limited number of supply and threshold voltages364.5. Experimental results394.6. Conclusion48Chapter V - Gate Level Power Optimization49                                                                                                                                                                                                                                                                                                                                                               | Acknow                         | vledgements                                                             | iv |  |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------|----|--|---|

| Glossary       x         Summary       xi         Chapter I - Introduction       1         1.1.       Motivation       1         1.2.       Organization of Thesis       5         Chapter II - Survey of Low-Power, Reliable CMOS Circuit Optimization<br>Techniques       7         2.1.       Introduction       7         2.2.       Low Power Structural/Behavioral Design Techniques       8         2.3.       Low Power Structural/Behavioral Design Techniques       9         2.4.       Soft-Error Tolerant Design Techniques       9         2.4.       Soft-Error Tolerant Design Techniques       14         2.5.       Research Categorization and Comparison       16         Chapter III - Delay-Assignment-Variation (DAV) Based Optimization       18         3.1       Introduction       18         3.2       Topology Matrix Representation of Circuit Netlist       18         3.3       Delay Assignment Variation based Optimization       24         Chapter IV - Module Level Power Optimization       27         4.1.       Introduction       27         4.2.       Mathematical Condition for Minimum Energy Consumption at the Module Level       28         4.3.       Procedure for obtaining optimal values of supply and threshold volta                                                                            | List of                        | List of Tables v                                                        |    |  |   |

| SummaryxiChapter I - Introduction11.1.Motivation11.2.Organization of Thesis5Chapter II - Survey of Low-Power, Reliable CMOS Circuit Optimization<br>Techniques72.1.Introduction72.2.Low Power Structural/Behavioral Design Techniques92.3.Low Power Structural/Behavioral Design Techniques92.4.Soft-Error Tolerant Design Techniques92.4.Soft-Error Tolerant Design Techniques142.5.Research Categorization and Comparison16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization183.1Introduction183.2Topology Matrix Representation of Circuit Netlist183.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages344.4.Clustering heuristic for limited number of supply and threshold voltages394.6.Conclusion48Chapter V - Gate Level Power Optimization495.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling<br>5.3535.3Analysis of Optimization (DAV) based Gate Level Power Optimization585.5Analysis of Optimization of DAV based optimization<                                                                                                                                   | List of                        | List of Figures vii                                                     |    |  |   |

| Chapter I - Introduction11.1. Motivation11.2. Organization of Thesis5Chapter II - Survey of Low-Power, Reliable CMOS Circuit Optimization<br>Techniques72.1. Introduction72.2. Low Power Structural/Behavioral Design Techniques92.4. Soft-Error Tolerant Design Techniques92.4. Soft-Error Tolerant Design Techniques142.5. Research Categorization and Comparison16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization183.1 Introduction183.2 Topology Matrix Representation of Circuit Netlist183.3 Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1. Introduction274.2. Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3. Procedure for obtaining optimal values of supply and threshold voltages364.5. Experimental results394.6. Conclusion48Chapter V - Gate Level Power Optimization495.1 Introduction495.2 Delay, Energy, Output Ramp and Input Capacitance Modeling505.3 Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4 Hierarchical Application of DAV based optimization535.5 Analysis of Optimization Complexity545.6 Implementation and Results68                                                                                                                                                              | Glossa                         | 'y                                                                      | X  |  |   |

| Chapter I - Introduction11.1. Motivation11.2. Organization of Thesis5Chapter II - Survey of Low-Power, Reliable CMOS Circuit Optimization<br>Techniques72.1. Introduction72.2. Low Power Structural/Behavioral Design Techniques92.4. Soft-Error Tolerant Design Techniques92.4. Soft-Error Tolerant Design Techniques142.5. Research Categorization and Comparison16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization183.1 Introduction183.2 Topology Matrix Representation of Circuit Netlist183.3 Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1. Introduction274.2. Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3. Procedure for obtaining optimal values of supply and threshold voltages364.5. Experimental results394.6. Conclusion48Chapter V - Gate Level Power Optimization495.1 Introduction495.2 Delay, Energy, Output Ramp and Input Capacitance Modeling505.3 Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4 Hierarchical Application of DAV based optimization535.5 Analysis of Optimization Complexity545.6 Implementation and Results68                                                                                                                                                              | Summa                          | iry                                                                     | xi |  |   |

| 1.1. Motivation       1         1.2. Organization of Thesis       5         Chapter II - Survey of Low-Power, Reliable CMOS Circuit Optimization Techniques         7       2.1. Introduction       7         2.2. Low Power Structural/Behavioral Design Techniques       8         2.3. Low Power Structural/Behavioral Design Techniques       9         2.4. Soft-Error Tolerant Design Techniques       9         2.4. Soft-Error Tolerant Design Techniques       14         2.5. Research Categorization and Comparison       16         Chapter III - Delay-Assignment-Variation (DAV) Based Optimization         3.1       Introduction       18         3.2       Topology Matrix Representation of Circuit Netlist       18         3.3       Delay Assignment Variation based Optimization       24         Chapter IV - Module Level Power Optimization       27         4.1. Introduction       27         4.2. Mathematical Condition for Minimum Energy Consumption at the Module Level       28         4.3. Procedure for obtaining optimal values of supply and threshold voltages       34         4.4. Clustering heuristic for limited number of supply and threshold voltages       36         4.5. Experimental results       39         4.6. Conclusion       48 <td <="" colspan="2" th=""><th></th><th></th><th>1</th></td> | <th></th> <th></th> <th>1</th> |                                                                         |    |  | 1 |

| 1.2.Organization of Thesis5Chapter II - Survey of Low-Power, Reliable CMOS Circuit Optimization<br>Techniques72.1.Introduction72.2.Low Power Structural/Behavioral Design Techniques82.3.Low Power Logic Design Techniques92.4.Soft-Error Tolerant Design Techniques142.5.Research Categorization and Comparison16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization183.1Introduction183.2Topology Matrix Representation of Circuit Netlist183.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1.Introduction274.3.Procedure for obtaining optimal values of supply and threshold voltages344.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion495.1Introduction495.2Delay Assignment Variation (DAV) based Gate Level Power Optimization505.3Delay Assignment Variation (DAV) based Optimization585.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization (DAV) based optimization58 </th <th>-</th> <th></th> <th></th>                                                                                               | -                              |                                                                         |    |  |   |

| Techniques72.1. Introduction72.2. Low Power Structural/Behavioral Design Techniques82.3. Low Power Logic Design Techniques92.4. Soft-Error Tolerant Design Techniques142.5. Research Categorization and Comparison16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization3.1Introduction183.2Topology Matrix Representation of Circuit Netlist183.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization4.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages364.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion48Chapter V - Gate Level Power Optimization5.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization585.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                     |                                |                                                                         | 5  |  |   |

| 2.1.Introduction72.2.Low Power Structural/Behavioral Design Techniques82.3.Low Power Logic Design Techniques92.4.Soft-Error Tolerant Design Techniques142.5.Research Categorization and Comparison16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization3.1Introduction183.2Topology Matrix Representation of Circuit Netlist183.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization4.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages364.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion48Chapter V - Gate Level Power Optimization5.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization585.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                     | Chapte                         | r II - Survey of Low-Power, Reliable CMOS Circuit Optimization          |    |  |   |

| 2.2.Low Power Structural/Behavioral Design Techniques82.3.Low Power Logic Design Techniques92.4.Soft-Error Tolerant Design Techniques142.5.Research Categorization and Comparison16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization3.1Introduction183.2Topology Matrix Representation of Circuit Netlist183.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization4.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages364.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion495.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                               | -                              | Techniques                                                              | 7  |  |   |

| 2.3.Low Power Logic Design Techniques92.4.Soft-Error Tolerant Design Techniques142.5.Research Categorization and Comparison16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization183.1Introduction183.2Topology Matrix Representation of Circuit Netlist183.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages364.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion495.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity64                                                                                                                                                                                                                                                                                                                                                                                                                | 2.1.                           | Introduction                                                            | 7  |  |   |

| 2.4.Soft-Error Tolerant Design Techniques142.5.Research Categorization and Comparison16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization183.1Introduction183.2Topology Matrix Representation of Circuit Netlist183.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages364.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion495.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity64                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                | 0 1                                                                     |    |  |   |

| 2.5.Research Categorization and Comparison16Chapter III - Delay-Assignment-Variation (DAV) Based Optimization183.1Introduction183.2Topology Matrix Representation of Circuit Netlist183.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages344.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion495.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                |                                                                         |    |  |   |

| Chapter III - Delay-Assignment-Variation (DAV) Based Optimization183.1Introduction183.2Topology Matrix Representation of Circuit Netlist183.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages344.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion495.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                | e i                                                                     |    |  |   |

| 3.1       Introduction       18         3.2       Topology Matrix Representation of Circuit Netlist       18         3.3       Delay Assignment Variation based Optimization       24         Chapter IV - Module Level Power Optimization       27         4.1       Introduction       27         4.2       Mathematical Condition for Minimum Energy Consumption at the Module Level       28         4.3       Procedure for obtaining optimal values of supply and threshold voltages       34         4.4       Clustering heuristic for limited number of supply and threshold voltages       36         4.5       Experimental results       39         4.6       Conclusion       48         Chapter V - Gate Level Power Optimization         5.1       Introduction       49         5.2       Delay, Energy, Output Ramp and Input Capacitance Modeling       50         5.3       Delay Assignment Variation (DAV) based Gate Level Power Optimization       53         5.4       Hierarchical Application of DAV based optimization       58         5.5       Analysis of Optimization Complexity       64         5.6       Implementation and Results       68                                                                                                                                                                        | 2.5.                           | Research Categorization and Comparison                                  | 16 |  |   |

| 3.2Topology Matrix Representation of Circuit Netlist183.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages344.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion495.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Chapte                         | r III - Delay-Assignment-Variation (DAV) Based Optimization             | 18 |  |   |

| 3.3Delay Assignment Variation based Optimization24Chapter IV - Module Level Power Optimization274.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages344.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion48Chapter V - Gate Level Power Optimization495.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.1                            | Introduction                                                            | 18 |  |   |

| Chapter IV - Module Level Power Optimization274.1. Introduction274.2. Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3. Procedure for obtaining optimal values of supply and threshold voltages344.4. Clustering heuristic for limited number of supply and threshold voltages364.5. Experimental results394.6. Conclusion48Chapter V - Gate Level Power Optimization5.1 Introduction495.2 Delay, Energy, Output Ramp and Input Capacitance Modeling505.3 Delay Assignment Variation (DAV) based Gate Level Power Optimization585.5 Analysis of Optimization Complexity645.6 Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                |                                                                         | 18 |  |   |

| 4.1.Introduction274.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages344.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion48Chapter V - Gate Level Power Optimization5.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.3                            | Delay Assignment Variation based Optimization                           | 24 |  |   |

| 4.2.Mathematical Condition for Minimum Energy Consumption at the Module<br>Level284.3.Procedure for obtaining optimal values of supply and threshold voltages344.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion48Chapter V - Gate Level Power Optimization5.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Chapte                         | r IV - Module Level Power Optimization                                  | 27 |  |   |

| Level284.3. Procedure for obtaining optimal values of supply and threshold voltages344.4. Clustering heuristic for limited number of supply and threshold voltages364.5. Experimental results394.6. Conclusion48Chapter V - Gate Level Power Optimization5.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.1.                           | Introduction                                                            | 27 |  |   |

| 4.4.Clustering heuristic for limited number of supply and threshold voltages364.5.Experimental results394.6.Conclusion48Chapter V - Gate Level Power Optimization5.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.                           |                                                                         | 28 |  |   |

| 4.5. Experimental results394.6. Conclusion48Chapter V - Gate Level Power Optimization495.1 Introduction495.2 Delay, Energy, Output Ramp and Input Capacitance Modeling505.3 Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4 Hierarchical Application of DAV based optimization585.5 Analysis of Optimization Complexity645.6 Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.3.                           | Procedure for obtaining optimal values of supply and threshold voltages | 34 |  |   |

| 4.6. Conclusion48Chapter V - Gate Level Power Optimization495.1 Introduction495.2 Delay, Energy, Output Ramp and Input Capacitance Modeling505.3 Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4 Hierarchical Application of DAV based optimization585.5 Analysis of Optimization Complexity645.6 Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |                                                                         | 36 |  |   |

| Chapter V - Gate Level Power Optimization495.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                | 1                                                                       |    |  |   |

| 5.1Introduction495.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.6.                           | Conclusion                                                              | 48 |  |   |

| 5.2Delay, Energy, Output Ramp and Input Capacitance Modeling505.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Chapte                         | r V - Gate Level Power Optimization                                     | 49 |  |   |

| 5.3Delay Assignment Variation (DAV) based Gate Level Power Optimization535.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.1                            | Introduction                                                            | 49 |  |   |

| 5.4Hierarchical Application of DAV based optimization585.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |                                                                         | 50 |  |   |

| 5.5Analysis of Optimization Complexity645.6Implementation and Results68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |                                                                         |    |  |   |

| 5.6 Implementation and Results 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |                                                                         |    |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |                                                                         |    |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |                                                                         |    |  |   |

| Chapter VI - Gate Level Soft-Error Optimization          |     |

|----------------------------------------------------------|-----|

| 6.1 Introduction                                         | 80  |

| 6.2 Glitch tolerance characteristics of individual gates | 82  |

| 6.3 Circuit soft-error tolerance analysis                | 86  |

| 6.3.1 Logical masking                                    | 88  |

| 6.3.2 Electrical masking                                 | 89  |

| 6.3.3 Latching-window masking                            | 91  |

| 6.4 Circuit soft-error tolerance optimization            | 93  |

| 6.5 Experimental results                                 | 95  |

| 6.6 Conclusion                                           | 99  |

| Chapter VII - Conclusions and Future Research            | 100 |

| 7.1. Summary of Research Contributions                   | 100 |

| 7.2. Future Directions                                   | 102 |

| Appendix A - Topological Sort of Directed Acyclic Graphs | 106 |

| Appendix B - Power Aware Zero Slack Algorithm            | 107 |

| References                                               | 109 |

# List of Tables

| 4.1. | Optimization results for Wallace tree multiplier | 42 |

|------|--------------------------------------------------|----|

| 4.2. | Optimization Results                             | 46 |

| 5.1. | Optimization Results (min-cut partitioning)      | 76 |

| 5.2. | Circuit Statistics (min-cut partitioning)        | 77 |

| 5.3. | Circuit Statistics (topological partitioning)    | 77 |

| 5.4. | Optimization Results (topological partitioning)  | 78 |

| 6.1. | Optimization Results                             | 96 |

| 6.2. | Circuit Statistics                               | 97 |

# **List of Figures**

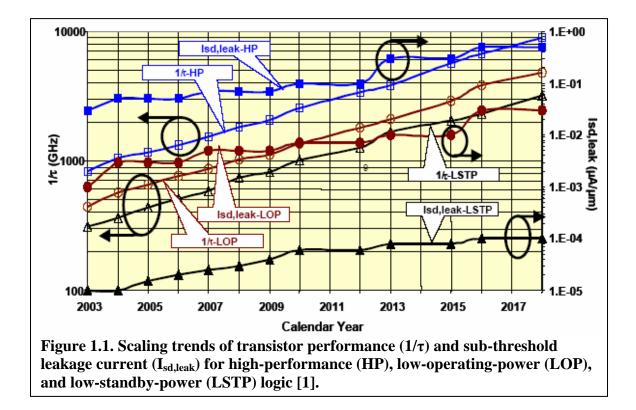

| 1.1. | Scaling trends of transistor performance and sub-threshold leakage current                                                            | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

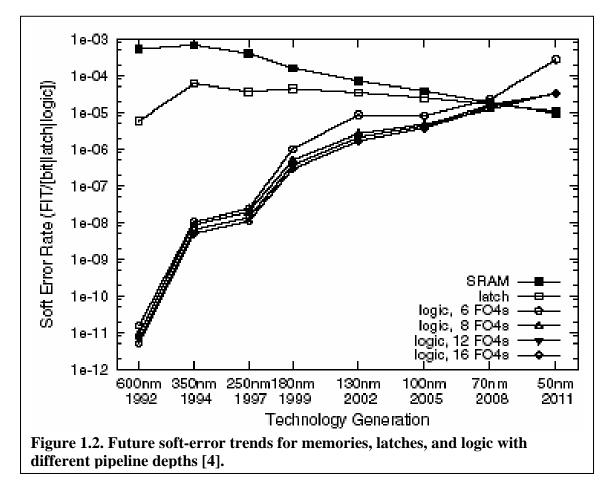

| 1.2. | Future soft-error trends for memories, latches, and logic with different pipeline depths                                              | 3  |

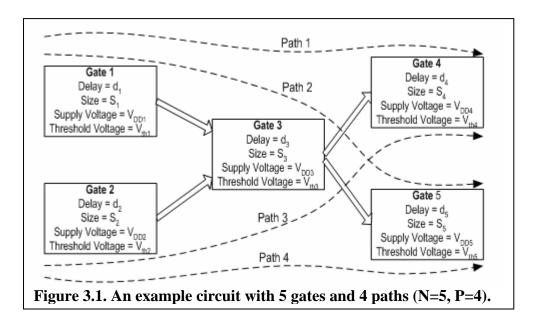

| 3.1. | An example circuit with 5 gates and 4 paths (N=5, P=4)                                                                                | 18 |

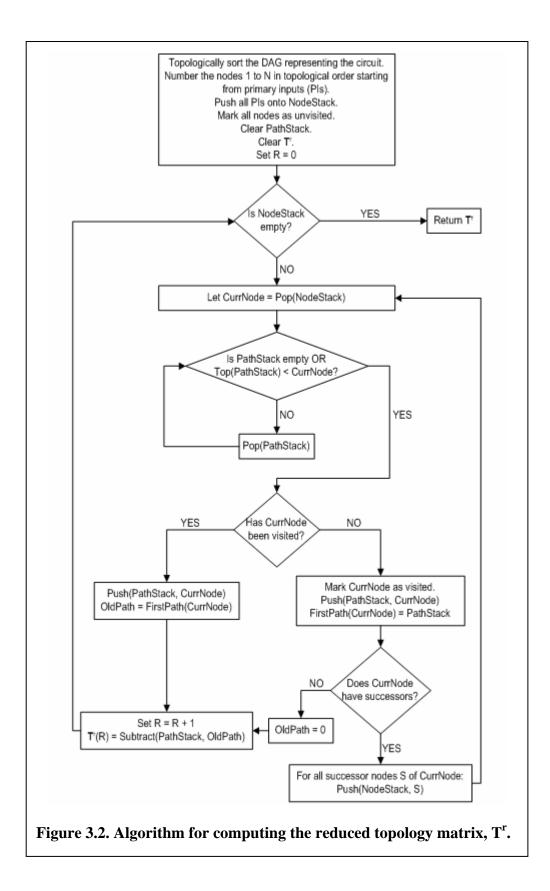

| 3.2. | Algorithm for computing the reduced topology matrix, T <sup>r</sup>                                                                   | 21 |

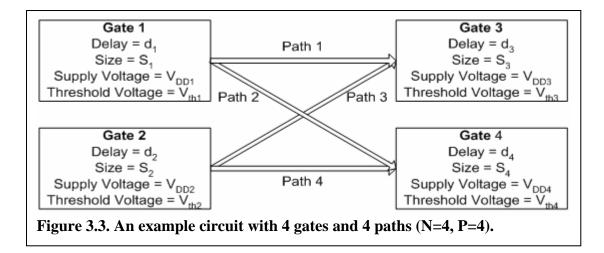

| 3.3. | An example circuit with 4 gates and 4 paths (N=4, P=4)                                                                                | 23 |

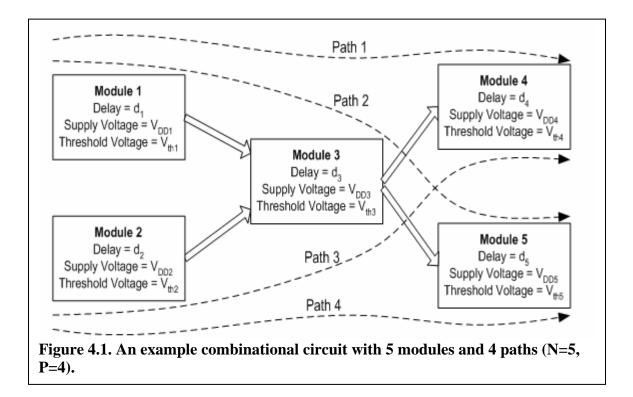

| 4.1. | An example combinational circuit with 5 modules and 4 paths $(N=5, P=4)$                                                              | 29 |

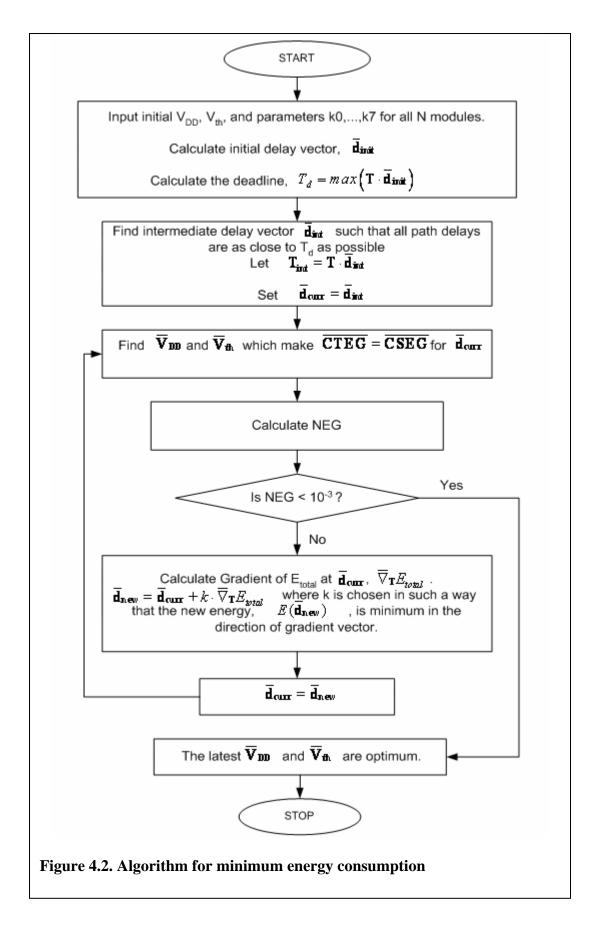

| 4.2. | Algorithm for minimum energy consumption                                                                                              | 37 |

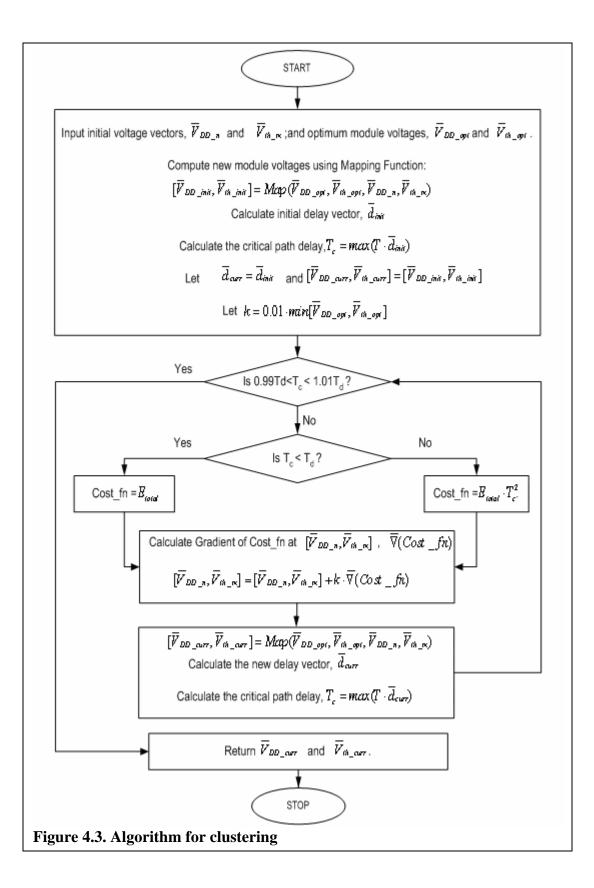

| 4.3. | Algorithm for clustering                                                                                                              | 40 |

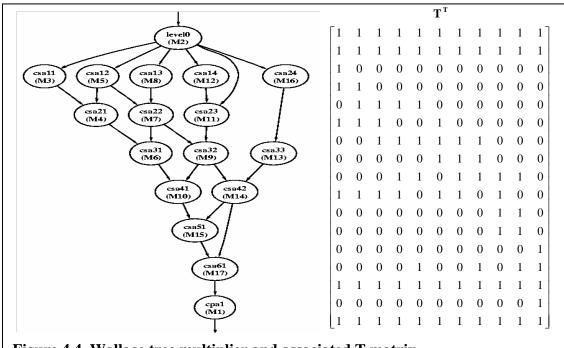

| 4.4. | Wallace tree multiplier and associated T matrix                                                                                       | 42 |

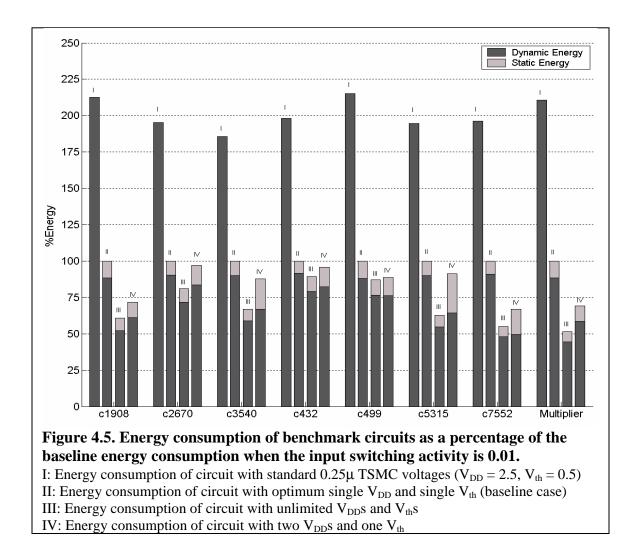

| 4.5. | Energy consumption of benchmark circuits as a percentage of the baseline energy consumption when the input switching activity is 0.01 | 44 |

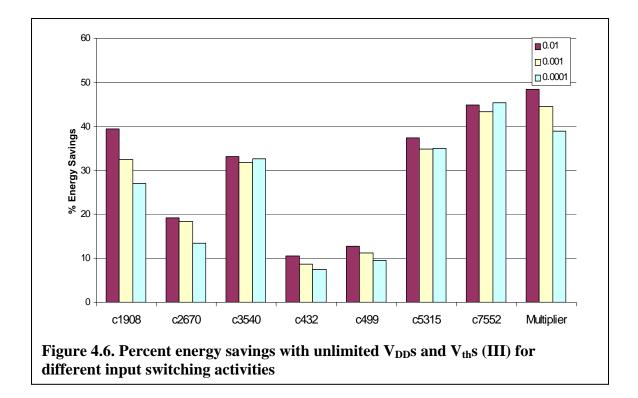

| 4.6. | Percent energy savings with unlimited $V_{DD}s$ and $V_{th}s$ for different input switching activities                                | 45 |

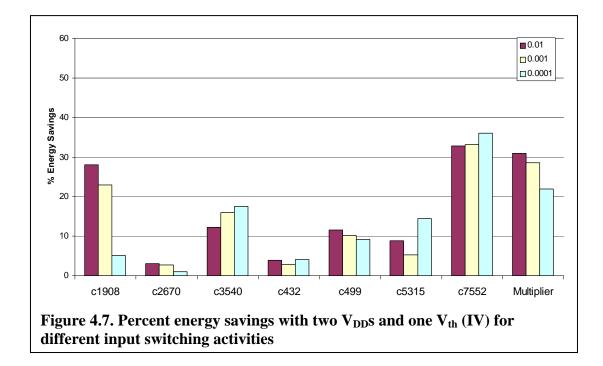

| 4.7. | Percent energy savings with two $V_{DD}s$ and one $V_{th}$ for different input switching activities                                   | 45 |

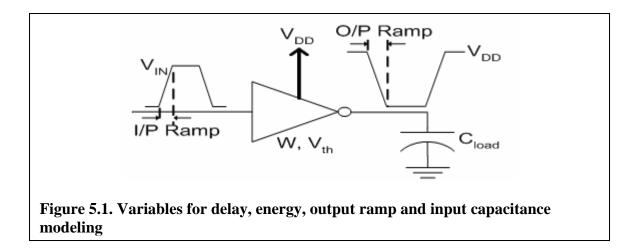

| 5.1. | Variables for delay, energy, output ramp and input capacitance modeling                                                               | 52 |

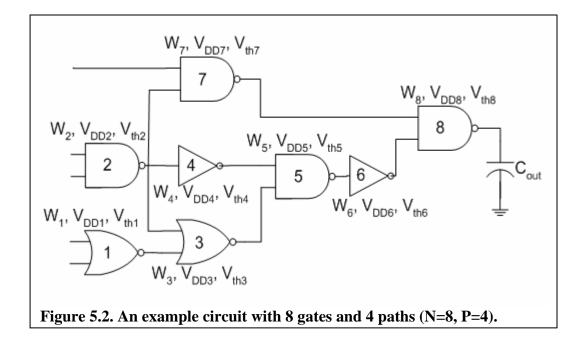

| 5.2. | An example circuit with 8 gates and 4 paths (N=8, P=4).                                                                               | 53 |

| 5.3. | Procedure for matching delays of gates to gate sizes, $V_{\text{DD}}s$ and $V_{\text{th}}s$                                           | 55 |

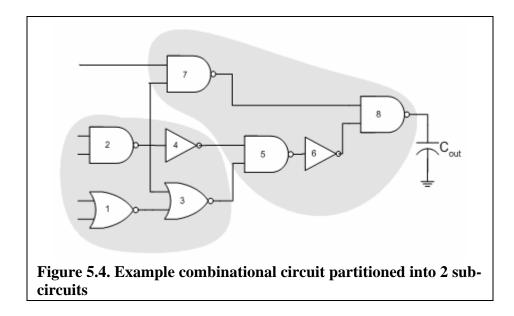

| 5.4. | Example combinational circuit partitioned into 2 sub-circuits                                                                         | 59 |

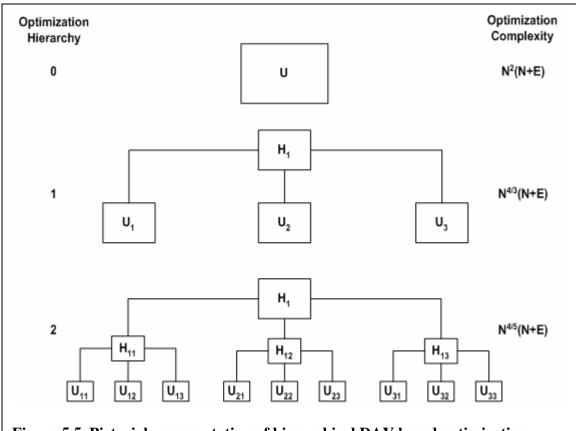

| 5.5. | Pictorial representation of hierarchical DAV based optimization                                                                       | 67 |

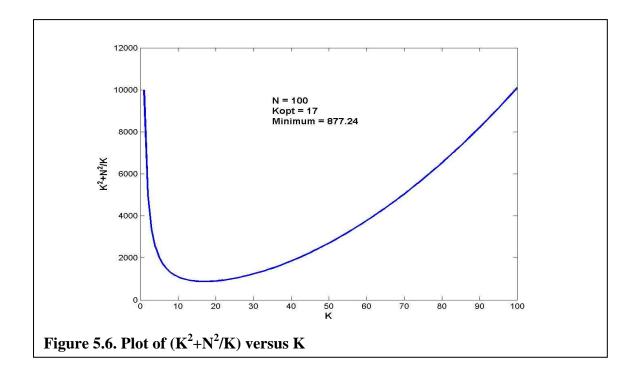

| 5.6. | Plot of $(K^2+N^2/K)$ versus K                                                                                                        | 67 |

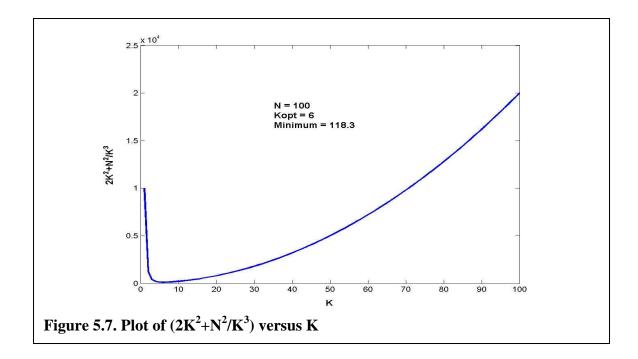

| 5.7.  | Plot of $(2K^2+N^2/K^3)$ versus K                                                              | 68  |

|-------|------------------------------------------------------------------------------------------------|-----|

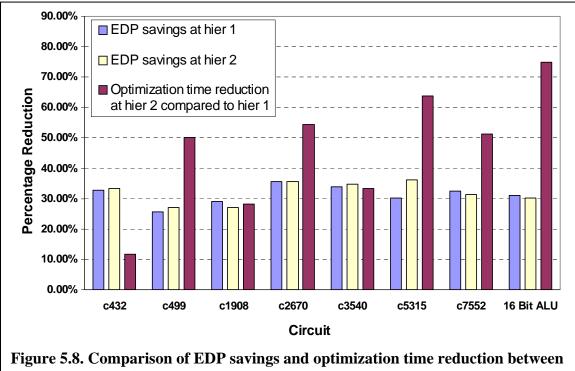

| 5.8.  | Comparison of EDP savings and optimization time reduction between hierarchy 1 and hierarchy 2  | 74  |

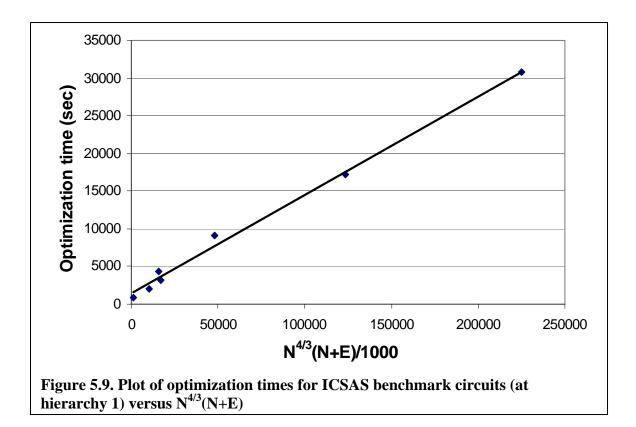

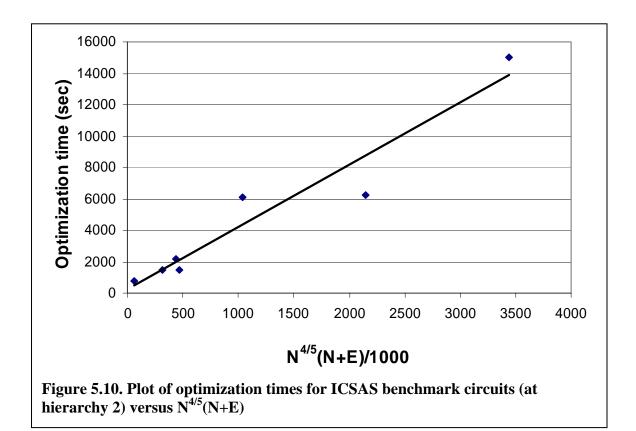

| 5.9.  | Plot of optimization times for ICSAS benchmark circuits (at hierarchy 1) versus $N^{4/3}(N+E)$ | 75  |

| 5.10. | Plot of optimization times for ICSAS benchmark circuits (at hierarchy 2) versus $N^{4/5}(N+E)$ | 75  |

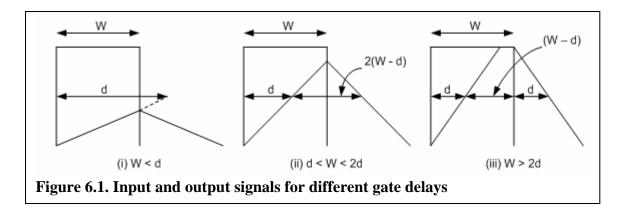

| 6.1.  | Input and output signals for different gate delays                                             | 83  |

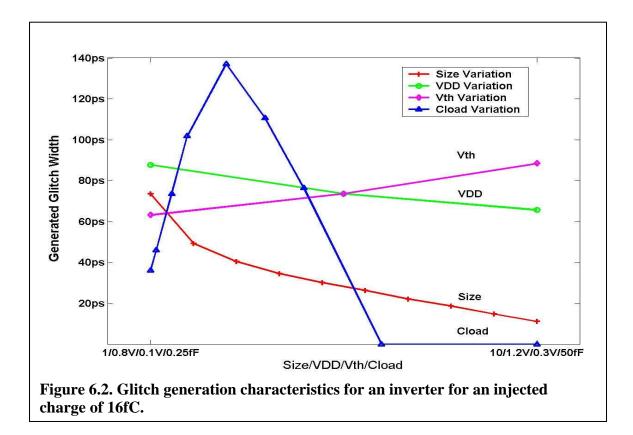

| 6.2.  | Glitch generation characteristics for an inverter for an injected charge of 16fC               | 84  |

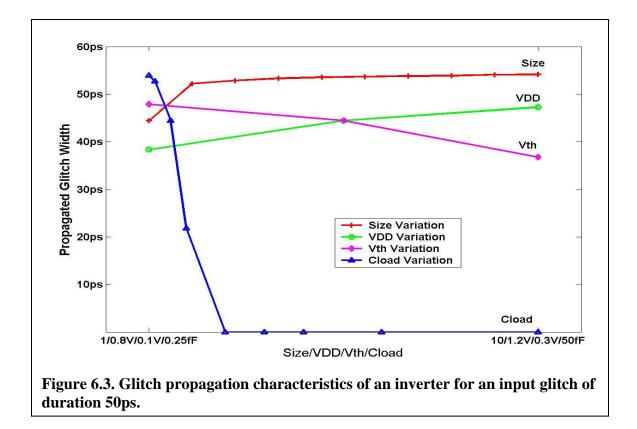

| 6.3.  | Glitch propagation characteristics of an inverter for an input glitch of duration 50ps         | 85  |

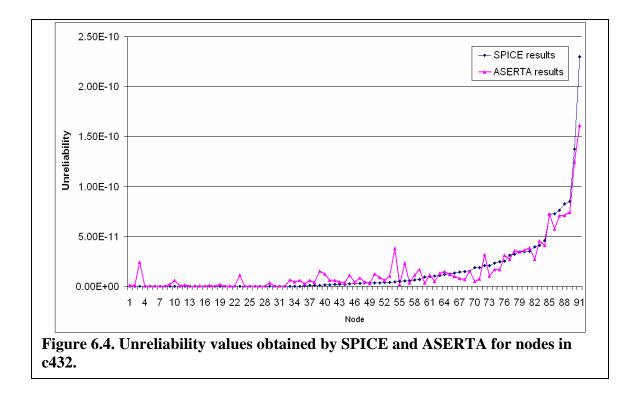

| 6.4.  | Unreliability values obtained by SPICE and ASERTA for nodes in c432                            | 92  |

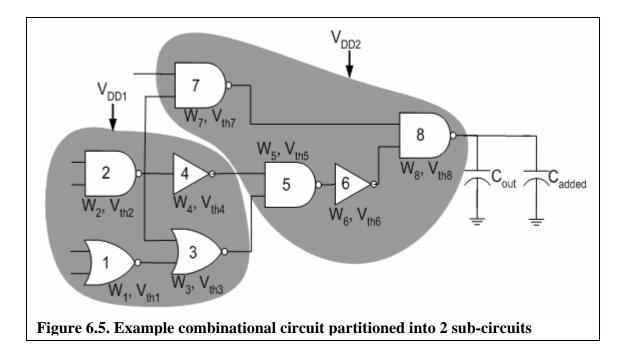

| 6.5.  | Example combinational circuit partitioned into 2 sub-circuits                                  | 94  |

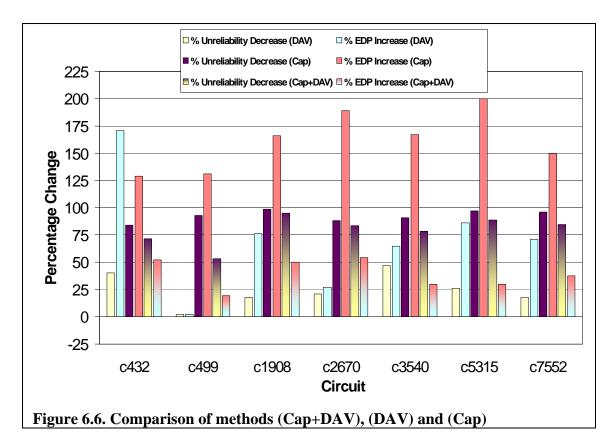

| 6.6.  | Comparison of methods (Cap+DAV), (DAV) and (Cap)                                               | 98  |

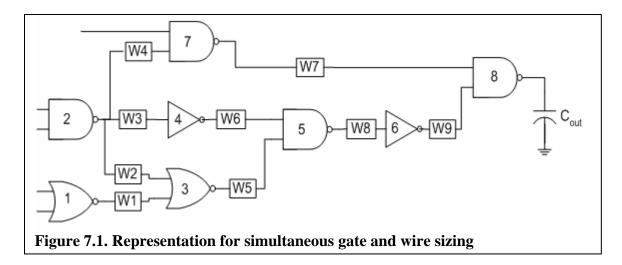

| 7.1.  | Representation for simultaneous gate and wire sizing                                           | 104 |

| A.1.  | Algorithm for obtaining topological numbering of nodes in a DAG                                | 106 |

| B.1.  | Algorithm for computing slacks of nodes in a DAG                                               | 108 |

| B.2.  | Algorithm for removing slacks of nodes in a DAG in a power-<br>aware manner                    | 108 |

# Glossary

| BJT                                | Bi-polar junction transistor                       |

|------------------------------------|----------------------------------------------------|

| CAD                                | Computer-aided design                              |

| CED                                | Concurrent error detection                         |

| CMOS                               | Complementary metal oxide semi-conductor           |

| DAG                                | Directed acyclic graph                             |

| DSM                                | Deep sub-micron                                    |

| ECC                                | Error correcting codes                             |

| EDP                                | Energy-delay product                               |

| IC                                 | Integrated circuit                                 |

| MOSFET                             | Metal oxide semi-conductor field effect transistor |

| PI                                 | Primary input                                      |

| PO                                 | Primary output                                     |

| SER                                | Soft-error rate                                    |

| SPICE                              | General-purpose circuit simulation program         |

| SRAM                               | Static random access memory                        |

|                                    |                                                    |

| V <sub>DD</sub>                    | Supply voltage                                     |

| V <sub>DD</sub><br>V <sub>th</sub> | Supply voltage<br>Threshold voltage                |

## **Summary**

Power consumption and soft-error tolerance have become major constraints in the design of DSM CMOS circuits. With continued technology scaling, the impact of these parameters is expected to gain in significance. Furthermore, the design complexity continues to increase rapidly due to the tremendous increase in number of components (gates/transistors) on an IC every technology generation. This research describes an efficient and general CAD framework for the optimization of critical circuit characteristics such as power consumption and soft-error tolerance under delay constraints with supply/threshold voltages and/or gate sizes as variables.

A general technique called Delay-Assignment-Variation (DAV) based optimization was formulated for the delay-constrained optimization of directed acyclic graphs. Exact mathematical conditions on the supply and threshold voltages of circuit modules were developed that lead to minimum overall dynamic and static power consumption of the circuit under delay constraints. A DAV search based method was used to obtain the optimal supply and threshold voltages that minimized power consumption.

To handle the complexity of design of reliable, low-power circuits at the gate level, a hierarchical application of DAV based optimization was explored. The effectiveness of the hierarchical approach in reducing circuit power and unreliability, while being highly efficient is demonstrated. The usage of the technique for improving upon already optimized designs is described. An accurate and efficient model for analyzing the soft-error tolerance of CMOS circuits is also developed.

xi

# **Chapter I**

# Introduction

#### 1.1. Motivation

Energy consumption is recognized as one of the most important parameters in the design of modern digital systems [1]. With the scaling of transistor feature sizes, more and more transistors can be made to fit in a given area of die. Furthermore, the clock frequencies also have been scaling up with every technology generation. The combination of increased transistor densities and increased clock frequencies has been causing the dynamic power consumption/dissipation density (W/cm<sup>2</sup>) to increase very rapidly even though it has been slightly offset by the scaling down of supply voltages and node capacitances [2]. The high power density causes problems with chip packaging, increase in cooling costs, and reduced chip reliability. Even though the transistor counts per unit area have been going up, designers are putting more and more functionality into ICs. This causes die sizes to go up, for example, by 25% every micro-processor generation. Combined with the increasing power density, the increase in area leads to a roughly 75% increase in total chip dynamic power every technology generation, leading to correspondingly increased energy expenses for consumers. The scaling of technology features has also led to an increase in the leakage energy per transistor. This is because threshold voltages have been reducing to compensate for the decrease in transistor switching speeds due to reduced supply voltages. The reduction in threshold voltage causes an exponential increase in the transistor leakage current [3] which means that the

chip wastes a lot of energy even when in standby mode. This has crucial implications in mobile applications which are battery-powered because the battery gets used up even when the device is not being operated.

Figure 1.1 shows the trends for performance and leakage current of transistors in three different kinds of applications viz. high-performance (HP), low-operating-power (LOP) and low-standby-power (LSTP). The transistor performance is characterized by the metric CV/I, where C is the gate input capacitance, V is the supply voltage and I is the drive current. HP chips use low  $V_{DD}s$  to reduce dynamic power and very low  $V_{th}s$  to maintain high-performance. They, therefore, have the highest leakage power. LOP chips are typically for relatively high-performance mobile applications, such as notebook computers, where the battery is likely to be high capacity and the focus is on reduced operating power. LSTP chips are typically for lower performance consumer type

applications, such as consumer cell-phones, with lower battery capacity and an emphasis on the lowest possible static power dissipation, i.e., the lowest possible leakage current.

Another side-effect of technology scaling that is rapidly coming to the forefront is the increased susceptibility of logic and memory circuits to soft-errors caused due to alpha particles in the chip material and cosmic rays from space [1][4]. Because of the reduced node capacitances, a smaller injected charge is needed to induce a glitch at a circuit node. Thus, low-energy particle strikes that earlier had no effect on a circuit can now cause soft-errors. Because of the reduced supply voltages, noise margins are reduced, which also increases the susceptibility to particle strikes. Increasing clock frequencies increase the probability of a soft-error getting latched. Furthermore, due to super-pipelining, the number of gates in pipeline stages have been reducing, which in

turn reduces the electrical attenuation of glitches as they propagate to the latches. Although the factors described above affect the power consumption and soft-error tolerance of both memory and combinational elements, this work focuses on combinational elements only. Figure 1.2 shows the predicted SER by technology and pipeline depths. The x-axis plots the CMOS technology generation and the y-axis plots the SER (in FIT or failures in time) for each element on a log scale. 1 FIT is equal to 1 error in 10<sup>9</sup> hours. The SER of a single SRAM cell declines gradually with decreasing device size, while the SER of a latch stays relatively constant. The SER for a single logic chain shows the most significant change – increasing over five orders of magnitude from 600nm to 50nm. The effect of super-pipelining is illustrated by the increasing SER for logic circuits at higher pipeline depths (smaller clock period in FO4 delays) within each technology generation.

The power consumption of a circuit is the product of the supply voltage and the current drawn by the circuit from the supply voltage. Thus, the power consumption can be reduced by reducing the supply voltage and/or the current drawn. The supply voltage can only be reduced to a certain extent beyond which the circuit delay becomes unacceptable. One way to reduce the current drawn from the supply voltage is by developing technologies in which transistors need less current for operation. This is seen in the shift of usage from BJT transistors to MOSFETs. Another way is by implementing the circuit using a logic style that draws less current. An example is the usage of CMOS logic style instead of the NMOS logic style to reduce the current drawn. The current drawn can also be reduced by appropriate transistor level design of the circuit. Given the technology, the logic style and the circuit design, there are various other optimization

techniques proposed in literature to reduce the power consumption at the circuit level. Since the major parameters that affect circuit power consumption are the supply voltage(s) ( $V_{DD}$ ), threshold voltage(s) ( $V_{th}$ ), circuit transistor sizes and switching activity; most techniques try to optimize one or more of these parameters. Optimization is necessary since changing the values of these parameters can adversely impact other circuit characteristics such as delay and area. This work focuses on reducing the power consumption of CMOS circuits by optimizing the supply voltages, threshold voltages and gate sizes simultaneously.

The soft-error tolerance of a circuit also depends on the technology, the logic style and the circuit design; and there have been various studies on the effect of these on the soft-error tolerance. However, there has been little investigation into usage of circuit parameter optimization to reduce soft-errors. It is stressed in [1] that such techniques will be urgently needed for mitigation of soft-errors in logic in future technology generations. This work shows that optimization can indeed significantly improve the attenuation of particle-hit induced glitches through CMOS combinational circuits, thereby increasing the soft-error tolerance.

Although circuit reliability refers to a host of issues besides soft-error tolerance such as electro-migration, thermal reliability and noise reliability (cross-talk, ground bounce, substrate coupling, etc); in this thesis, reliability of a circuit will be used to refer solely to its soft-error tolerance.

#### **1.2.** Organization of Thesis

Chapter 2 surveys commonly used techniques for low power and reliable digital design. Since this thesis focuses mainly on optimization at the logic level, technique at

this level will be given more attention. Structural/behavioral level techniques will also be described briefly for the sake of completeness. Chapter 3 first gives a new matrix representation of the topology  $(\mathbf{T})$  of a directed acyclic graph (DAG) and then describes the use of the new representation in the development of Delay-Assignment-Variation (DAV) based optimization, a generic technique for delay-constrained optimization of DAGs. In Chapter 4, the topology matrix representation, T, is used to derive exact conditions on the supply and threshold voltages of circuit modules that yield minimum energy consumption under delay constraints. Search based methods are then used to obtain the values of these voltages and cluster them into small groups that can be used in a practical implementation of the circuit. A metric is developed that can be used by designers to determine the energy efficiency of their designs at the module level. Experimental results of optimizing ISCAS'85 benchmarks are provided. In Chapter 5, the usage of the topology matrix representation for optimization of gate level netlists is explored. A hierarchical method is developed that is able to handle large netlists and provides energy reductions beyond those possible by other methods given in literature. Chapter 6 describes ASERTA (accurate soft-error tolerance analyzer), a tool for fast and accurate estimation of the soft-error tolerance of combinational circuits. The tool yields soft-error estimates close to those generated by SPICE in orders of magnitude less computation time. The energy optimization method developed in Chapter 5 is then extended to also optimize the soft-error tolerance of circuits. Finally, Chapter 7 concludes by summarizing the main contributions of the thesis and providing suggestions for future work. The applicability of the topology matrix representation for optimization at the behavioral and software levels is also discussed.

# **Chapter II**

# Survey of Low-Power, Reliable CMOS Circuit Optimization Techniques

## 2.1. Introduction

This chapter surveys techniques described in literature for the design of lowpower and reliable CMOS circuits. Low power digital design requires optimization at all levels of the design hierarchy viz. system, structural/behavioral, logic, circuit, and device technology level. However, techniques at all levels basically boil down to a fundamental set of concepts: energy dissipation is reduced by lowering the supply voltage, the voltage swing, the physical capacitance, the switching activity or a combination of the above [5]. The application of these techniques may result in an increase in the delay and/or area of the system. Since the focus in this work is on low power CAD techniques at the logic level, design techniques at this level are surveyed in detail in Section 2.3. Design techniques at the behavioral level are also described briefly in Section 2.2, as these can impact the techniques at the logic level.

Soft-error tolerant design has mostly focused on memories and flip-flops since these are highly vulnerable. However, the focus has recently started shifting to combinational logic. In Section 2.4, traditional approaches to soft-error reduction at the combinational level are described as well as emerging approaches. Finally, Section 2.5 categorizes the work in this thesis according to the techniques discussed and compares it to previous approaches.

#### 2.2. Low Power Structural/Behavioral Design Techniques

At the structural/behavioral level, a high-level specification of a problem is mapped into the register-transfer level. The high-level specification is typically in the form of a control-flow graph (CFG) and a data-flow graph (DFG) or a combination of the two (CDFG). The register-transfer level specifies the number of different types of hardware modules needed (allocation), what operations of the CDFG are mapped onto what modules (assignment) and at what time-step what operation is carried out (scheduling).

Power reduction can be achieved with the use of behavioral transformations that reduce the number of time-steps by increasing concurrency and through proper scheduling. The reduced time-steps allow usage of a slower clock, enabling the use of lower supply voltages. The quadratic reduction in power due to reduced supply voltage can often offset the increase in capacitance due to more concurrency. A number of other high-level transformations of the CDFG that reduce the number of operations, reduce the switching activity, increase utilization of modules, etc have been described in [6].

If a number of modules, with a range of power/delay costs, are available for allocation, then an appropriate mapping of modules to operations can lead to lower power consumption for the same performance. In [7], an Integer Linear Programming (ILP) approach is used to generate low-power schedules using an optimal set of supply voltages while accounting for level conversion costs. Approaches that takes up available slack in schedules in a power-aware way are presented in [8][9].

Dynamic Voltage Scaling (DVS) [10][11] is another approach that can yield large power savings while meeting performance constraints. The basic idea is to run modules at a lower supply voltage (and hence lower speed) when the system is idle or has lower computing requirements and to increase the supply voltage (increase speed) when there is an increase in computing demand. The major issues in this technique are (i) whether to have software or hardware control of voltage scaling, (ii) accurate prediction of when the system is going to be idle and when it is going to be busy, (iii) the granularity of voltage changes allowed, and (iv) the frequency of voltage changes allowed. DVS can also be combined with dual/multiple threshold voltage usage to reduce leakage power as well. A low-power RISC processor built using hardware-based DVS and variable-threshold CMOS (VTCMOS) technology has been described in [12].

#### 2.3. Low Power Logic Design Techniques

The power consumption of any CMOS logic circuit is composed of dynamic power, short-circuit power and leakage power. Although dynamic power has been the predominant component of total power in older technologies, the leakage power component is becoming significant due to the reduction of supply and threshold voltages in current deep sub-micron (DSM) technologies. Short-circuit power is a small fraction of the total power and its importance is not expected to grow with device scaling [13].

The dynamic power consumption of any CMOS logic circuit is given by:

$$P_{dyn} = 0.5 \cdot f_{CLK} \cdot V_{DD}^2 \cdot \sum_i \alpha_i \cdot C_i$$

(2.1)

where  $f_{CLK}$  is the clock frequency,  $V_{DD}$  is the supply voltage,  $\alpha_i$  is the switching activity of the i<sup>th</sup> node in the circuit, and  $C_i$  is the load capacitance of the i<sup>th</sup> node in the circuit. Hence, dynamic power of the circuit can be reduced by reducing the supply voltage or by reducing the product of the switching activity and load capacitance (the switched capacitance) at the circuit nodes. The clock frequency generally cannot be lowered as it is determined by the timing constraints.

Lowering the supply voltage is an effective mechanism for reducing dynamic power because of the quadratic dependence in Equation 2.1. However, lowering the supply voltage affects the delay of the logic gates. The delay of a CMOS logic gate is given by:

$$d = \frac{k \cdot C \cdot V_{DD}}{\left(V_{DD} - V_{th}\right)^{\alpha}}$$

(2.2)

where k is a constant depending on the logic function computed by the gate, C is the output capacitance of the gate (includes the load capacitance as well as the parasitic junction capacitance),  $V_{DD}$  is the supply voltage,  $V_{th}$  is the threshold voltage, and  $\alpha$  is the velocity saturation coefficient [14] which is between 1.2 and 1.5 for short-channel devices and 2 for long-channel devices. Thus, lowering  $V_{DD}$  leads to an increase in the delay.

The most common approach uses two or more supply voltages for reducing power. The gates on the critical path use the highest supply voltage to meet the timing constraint. Gates on the non-critical paths that have available slack can use lower supply voltages. There are two major problems facing this approach. The first is the need for generating and routing multiple supply voltages to different parts of the chip and the second is the need for level converters whenever a low supply voltage gate drives a high supply voltage gate. Level converters are needed to prevent the flow of large static current from supply to ground because of the PMOS transistor in a high supply voltage gate not being completely turned off by the lower voltage output by a preceding low supply voltage gate. The first problem is limited by restricting the number of supply voltages used to two [15][16]. The area, delay, and power impact of the level converters is reduced by two ways. In Clustered Voltage Scaling (CVS) [17][18], it is tried to cluster the gates that operate at the reduced supply voltage so that the number of interfacing level-converters is reduced. The other approach [19] is to partition the gate level netlist into modules and use multiple supply voltages at the module level. The area, delay and energy penalties of the level converters are shown to be small compared to the modules. The idea of taking up slack can be straight-forwardly extended to the usage of gate sizing and dual/multiple V<sub>DDS</sub> simultaneously [20].

The delay impact of reduced supply voltage can be decreased by reducing the threshold voltage as can be seen from Equation 2.2. This trend is being increasingly followed in current technologies where the supply and threshold voltages are lowered to reduce dynamic power as well as not impact delay significantly. The reduction in threshold voltage, however, has the adverse effect of increasing the leakage power per transistor exponentially as can be seen from the leakage power equation below:

$$P_{le\,a\,k} = V_{D\,D} \cdot I_{S} \cdot e^{\frac{V_{G\,S} - V_{th}}{n \cdot v_{T}}} \cdot \left(1 - e^{\frac{V_{D\,S}}{v_{T}}}\right)$$

(2.3)

$I_S$  is a circuit and process dependent constant, n is the sub-threshold swing coefficient,  $V_{DD}$  is the supply voltage,  $V_{th}$  is the threshold voltage and  $v_T$  is the thermal voltage.

Leakage energy is expected to equal, if not overtake, dynamic energy as the major component of total energy in future technology generations. To tackle this problem, researchers have proposed using two [21][22] or more [23] threshold voltages. Similar to the dual voltage approach, the idea here is to use the lower threshold voltage for gates on the critical paths so that they can operate at high speed albeit with high leakage energy dissipation and to use the higher threshold voltage for gates on the non-critical paths so that they operate with less leakage.