# MEMS-BASED FABRICATION OF POWER ELECTRONICS COMPONENTS FOR ADVANCED POWER CONVERTERS

A Thesis Presented to The Academic Faculty

by

William Preston Gallé III

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2012

Copyright © 2012 by William Preston Gallé III

# MEMS-BASED FABRICATION OF POWER ELECTRONICS COMPONENTS FOR ADVANCED POWER CONVERTERS

Approved by:

Dr. Mark G. Allen, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Deepak Divan School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Oliver Brand School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Linda Milor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Suresh Sitaraman School of Mechanical Engineering *Georgia Institute of Technology*

Date Approved: August 21st, 2012

Warm hugs straighten my ear muffs and got me through metal detector mornings; and even if never to be seen again, you're in my air.

-from The Poetry of Ajax

## ACKNOWLEDGEMENTS

First and foremost, a superlative debt of gratitude and recognition is owed to my advisor, Dr. Mark G. Allen. His strong support from beginning to end, pragmatic yet open-minded approaches towards everything, and endless patience have shown me that there are very few limits on the ultimate boundaries of achievement.

I would like to than Dr. Deepak Divan for serving as the chairman of my dissertation committee, along with the other committee members, Dr. Oliver Brand, Dr. Linda Milor, and Dr. Suresh Sitaraman. Their attention and willingness to participate in my undertaking is greatly appreciated.

As well, numerous members of the MSMA research group have provided essential education and empowerment to me over the years. These include: Mr. Richad Shafer, an open tome of knowledge and experience of all flavors; Dr. Florian Herrault, Dr. Seong-Hyok Kim, and Dr. Yong-Kyu Yoon, research mentors *par excellence*; and Dr. Jin-Woo Park, Dr. David Arnold, Dr. Chang-Hyeon Ji, Dr. Swaminathan Rajaraman, Dr. Sharon Wu, Mr. Ed Birdsell, and Dr. Seung-Keung Choi, magnanimous collaborators, critics, and teachers.

In a broader scope, many others at Georgia Tech have been continuous sources of assistance, guidance, and perspective. These include Dr. Oliver Brand, Mr. Gary Spinner, Dr. Alan Doolittle, Mrs. Purnima Sharma, Mrs. Laureen Rose, Dr. Muhannad Bakir, and Dr. Amanda Brooks.

As well, I must acknolwedge the extraordinary flexibility and dedication to my success that has been demonstrated by my employer, SiTime Corporation, during the final stages of my graduate studies. In particular, Mr. Pavan Gupta, Mrs. Nivi Arumugam, and Dr. Fari Assaderaghi deserve my sincerest gratitude for their support.

Finally, the people that make everything possible – those closest to me – must be recognized. My dear sister, Julie Baggenstoss, and her lovely family have demonstrated the purest unconditional support throughout this entire experience. My parents, Dr. Bill Gallé and Julia Gallé, have always been my most generous and most essential supporters. And last, but not least, my wife, Houri Johari-Gallé, continues to show me the very meanings of commitment, *joie de vivre*, and kindness.

# TABLE OF CONTENTS

| DE  | DICA  | TION    |                                            |

|-----|-------|---------|--------------------------------------------|

| AC  | KNOV  | WLEDO   | GEMENTS                                    |

| LIS | ST OF | TABL    | ES x                                       |

| LIS | ST OF | FIGUE   | RES                                        |

| SU  | ММА   | RY.     |                                            |

| Ι   | INT   | RODU    | CTION                                      |

|     | 1.1   | Motiva  | ntion                                      |

|     | 1.2   | History | y2                                         |

|     |       | 1.2.1   | The Evolution of Power Converters          |

|     |       | 1.2.2   | Emphasis on Power Converter Packaging    3 |

|     | 1.3   | MEMS    | S Microfabrication for Power Electronics   |

|     |       | 1.3.1   | MEMS Microfabrication Processes            |

|     |       | 1.3.2   | Integrated Power Systems                   |

|     |       | 1.3.3   | Microfabricated Power Components           |

|     | 1.4   | Contril | butions of This Work                       |

|     |       | 1.4.1   | MEMS-based Process for Power Electronics   |

|     |       | 1.4.2   | Microfabricated Power Components           |

|     |       | 1.4.3   | Deployment into Power Converters           |

|     | 1.5   | About   | this Thesis                                |

| Π   | MIC   | CROFAI  | BRICATED POWER INDUCTORS 19                |

|     | 2.1   | Backg   | round                                      |

|     |       | 2.1.1   | Inductor Theory                            |

|     |       | 2.1.2   | Switching Power Supplies 24                |

|     | 2.2   | Design  | and Fabrication                            |

|     |       | 2.2.1   | Full Device Construction    27             |

|     |       | 2.2.2   | Simplified Device Constructions            |

|     |       | 2.2.3   | Fabrication                                |

|     | 2.3   | Charac  | sterization                                |

|     |     | 2.3.1  | Device-level Characterization                                     | 33 |

|-----|-----|--------|-------------------------------------------------------------------|----|

|     |     | 2.3.2  | System-level Characterization                                     | 36 |

|     | 2.4 | Conclu | usions                                                            | 39 |

|     |     | 2.4.1  | Eligibility of Microfabricated Inductors                          | 39 |

|     |     | 2.4.2  | Rewards of Maximizing Flexibility                                 | 40 |

|     |     | 2.4.3  | Critical Importance of Materials                                  | 40 |

| III | SEQ | UENT   | IAL MULTILAYER PLATING                                            | 42 |

|     | 3.1 | Overvi | iew                                                               | 42 |

|     |     | 3.1.1  | Approaches to High Surface Area                                   | 42 |

|     |     | 3.1.2  | Sacrificial Multilayer Plating                                    | 48 |

|     | 3.2 | Multil | ayer electroplating robot                                         | 51 |

|     |     | 3.2.1  | Architecture                                                      | 52 |

|     |     | 3.2.2  | Electronics                                                       | 53 |

|     | 3.3 | Proces | s Extension                                                       | 53 |

|     |     | 3.3.1  | Thicker structures                                                | 53 |

|     |     | 3.3.2  | Thin layers                                                       | 58 |

|     |     | 3.3.3  | Etch optimization                                                 | 60 |

|     | 3.4 | Conclu | usions                                                            | 67 |

|     |     | 3.4.1  | Alignment with electrochemical theory and electroplating practice | 67 |

|     |     | 3.4.2  | Difficulty of imaging                                             | 68 |

|     |     | 3.4.3  | Dependence on mass transport                                      | 69 |

| IV  | MIC | CROFA  | BRICATED CAPACITORS                                               | 70 |

|     | 4.1 | Backg  | round                                                             | 70 |

|     |     | 4.1.1  | Basic Theory                                                      | 71 |

|     |     | 4.1.2  | Key Behavioral Aspects                                            | 72 |

|     | 4.2 | Capaci | itor Implementations                                              | 75 |

|     |     | 4.2.1  | Conventional Constructions                                        | 75 |

|     |     | 4.2.2  | Microfabricated Capacitors                                        | 79 |

|     | 4.3 | Microf | fabricated Capacitor                                              | 79 |

|     |     | 4.3.1  | Overview                                                          | 79 |

|     |     | 4.3.2  | Design                                                            | 80 |

|   |     | 4.3.3  | Fabrication                                                           | 83  |

|---|-----|--------|-----------------------------------------------------------------------|-----|

|   |     | 4.3.4  | Characterization                                                      | 88  |

|   |     | 4.3.5  | Discussion                                                            | 91  |

|   | 4.4 | Conclu | isions                                                                | 92  |

|   |     | 4.4.1  | Utility of Sacrificial Multilayer Plating                             | 92  |

|   |     | 4.4.2  | Inestimable Need for Robust Packaging                                 | 93  |

|   |     | 4.4.3  | Indispensability of ALD                                               | 93  |

|   |     | 4.4.4  | Future Improvements                                                   | 93  |

| V | HIG | HLY L  | AMINATED-CORE INDUCTORS                                               | 95  |

|   | 5.1 | Backg  | round                                                                 | 95  |

|   | 5.2 | Design |                                                                       | 96  |

|   |     | 5.2.1  | Core Design                                                           | 96  |

|   |     | 5.2.2  | Winding Design                                                        | 101 |

|   |     | 5.2.3  | Packaging Design                                                      | 102 |

|   | 5.3 | Core F | abrication                                                            | 105 |

|   | 5.4 | Approa | ach to Inductor Characterization                                      | 106 |

|   |     | 5.4.1  | Emphasis on Power Loss Measurement                                    | 106 |

|   |     | 5.4.2  | Survey of Loss Characterization Approaches                            | 107 |

|   |     | 5.4.3  | Balanced-Reactivity Loss Measurement                                  | 113 |

|   | 5.5 | Charac | eterization Results                                                   | 116 |

|   |     | 5.5.1  | Characterization System Implementation                                | 116 |

|   |     | 5.5.2  | Characterization System Qualification                                 | 122 |

|   |     | 5.5.3  | Selected Samples                                                      | 124 |

|   |     | 5.5.4  | Winding Loss Extraction                                               | 125 |

|   |     | 5.5.5  | Laminated-Core Characterization Results                               | 129 |

|   |     | 5.5.6  | Potential Sources of Discrepancy between Expected and Measured losses | 144 |

|   | 5.6 | Conclu | isions                                                                | 152 |

|   |     | 5.6.1  | Intractability of Electromagnetic Theory                              | 152 |

|   |     | 5.6.2  | Utility of Automated Characterization                                 | 153 |

|   |     | 5.6.3  | Fragility of Microfabricated Cores                                    | 153 |

| VI  | APP | LICAT   | ION IN POWER CONVERTER                             | 55 |

|-----|-----|---------|----------------------------------------------------|----|

|     | 6.1 | Advan   | ced Power Converter Design                         | 55 |

|     |     | 6.1.1   | Design Goals                                       | 55 |

|     |     | 6.1.2   | Circuit Design                                     | 56 |

|     |     | 6.1.3   | Implementation                                     | 56 |

|     |     | 6.1.4   | Inductors Used                                     | 58 |

|     | 6.2 | Experi  | mental Setup                                       | 59 |

|     |     | 6.2.1   | Equipment Used                                     | 59 |

|     |     | 6.2.2   | Efficiency Calculation                             | 60 |

|     | 6.3 | Dynan   | nic Observations                                   | 61 |

|     |     | 6.3.1   | Operation with Ferrite Inductor                    | 61 |

|     |     | 6.3.2   | Operation with Laminated-Core Inductor             | 64 |

|     |     | 6.3.3   | Operation with High-Volume Laminated-Core Inductor | 66 |

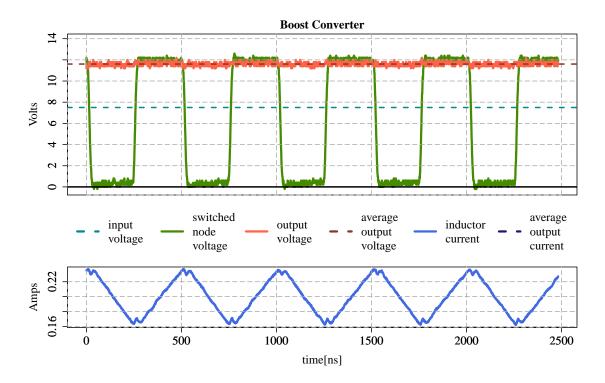

|     | 6.4 | Perform | mance Analysis                                     | 70 |

|     |     | 6.4.1   | Compensation for Inductor Losses                   | 70 |

|     |     | 6.4.2   | Output Loading                                     | 72 |

|     |     | 6.4.3   | Efficiency Results                                 | 73 |

|     | 6.5 | Conclu  | usions                                             | 75 |

|     |     | 6.5.1   | Performance Differences                            | 75 |

|     |     | 6.5.2   | Additional Advances in Power Converter Design      | 76 |

|     |     | 6.5.3   | Higher Efficiency                                  | 77 |

|     |     | 6.5.4   | Importance of Preserving Samples                   | 77 |

|     |     | 6.5.5   | Value of Tight Integration                         | 78 |

| VII | CON | NCLUS   | IONS                                               | 79 |

|     | 7.1 | Review  | v of Major Results                                 | 79 |

|     | 7.2 | Intelle | ctual Contributions                                | 80 |

|     | 7.3 | Potent  | ial Future Applications                            | 82 |

|     |     | 7.3.1   | Additional roles in SMPSs                          | 82 |

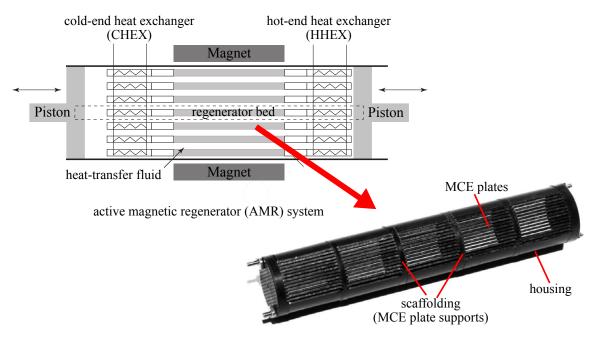

|     |     | 7.3.2   | Magnetic refrigeration                             | 84 |

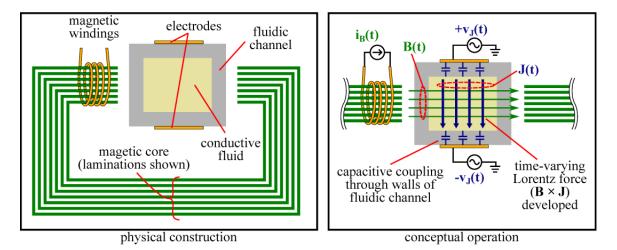

|     |     | 7.3.3   | Magnetohydrodynamic pumps                          | 88 |

|     | 7.4 | Final C | Conclusions                                        | 89 |

| APPENDIX A<br>TRIES     |     |      |       |       |         |          |         | CONAL GEOM |       |

|-------------------------|-----|------|-------|-------|---------|----------|---------|------------|-------|

| APPENDIX B              | -C  | ORE  | LOSS  | MEASU | REMEN   | <b>T</b> |         |            | . 197 |

| APPENDIX C              | — D | ESIG | N ANE | OPER  | ATION ( | OF ELEC  | FROPLAT | TING ROBOT | . 221 |

| APPENDIX D<br>TERIZATIO |     |      |       |       |         |          |         | LOSS CHARA |       |

| REFERENCES              |     |      |       |       |         |          |         |            | . 243 |

| VITA                    |     |      |       |       |         |          |         |            | . 248 |

| INDEX                   |     |      |       |       |         |          |         |            | . 248 |

# LIST OF TABLES

| 1 | Microfabricated Inductor Variants               | 31  |

|---|-------------------------------------------------|-----|

| 2 | Air Bridge Array Geometries                     | 82  |

| 3 | Anode Areas and Expected Capacitances           | 83  |

| 4 | Capacitor Characterization Results              | 91  |

| 5 | Microfabricated Core Plating Mask Geometries    | 101 |

| 6 | Laminated Core Samples                          | 105 |

| 7 | Qualification Sample Properties                 | 122 |

| 8 | Qualification Sample Loss Parameters            | 123 |

| 9 | Samples Selected for Core Loss Characterization | 124 |

# LIST OF FIGURES

| 1  | Power Electronics History                                                        | 3  |

|----|----------------------------------------------------------------------------------|----|

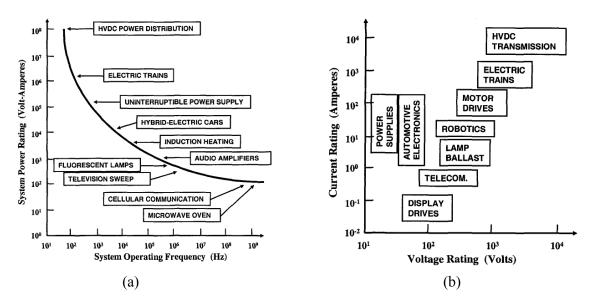

| 2  | Operating Frequency and Power for Electronics Systems                            | 4  |

| 3  | Micromachining Based on Electrodeposition                                        | 6  |

| 4  | Generic Sacrificial Release Process                                              | 6  |

| 5  | Stiction during sacrificial release                                              | 8  |

| 6  | Integrated DC/DC Converter for Wireless Sensor Nodes                             | 10 |

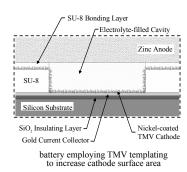

| 7  | Integrated Power Storage and Conversion System                                   | 11 |

| 8  | Isolating, all-MEMS Power Converter                                              | 11 |

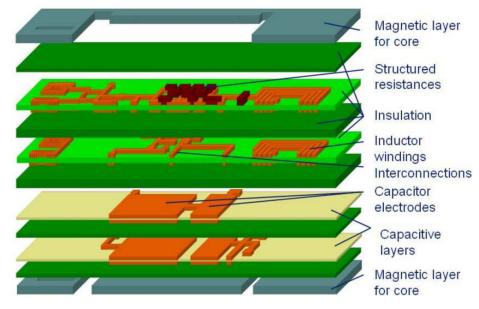

| 9  | Integrated Passive Electronics Modules (IPEM)                                    | 12 |

| 10 | LCT Module Construction                                                          | 13 |

| 11 | PCB-wound Planar Magnetics                                                       | 13 |

| 12 | Matrix-Integrated Magnetics                                                      | 14 |

| 13 | PCB-embedded Capacitors                                                          | 15 |

| 14 | Comprehensive PCB-Integrated Passives Platform                                   | 15 |

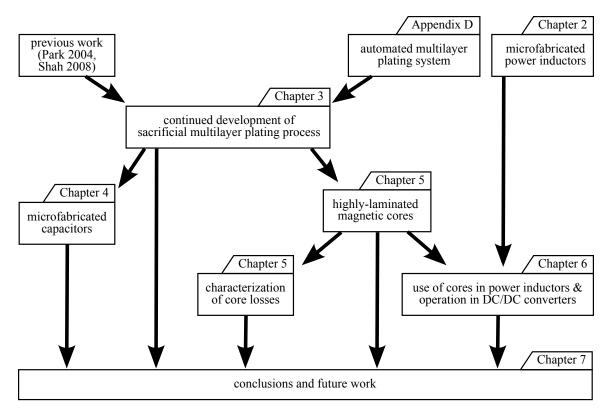

| 15 | Conceptual Map of this Thesis                                                    | 17 |

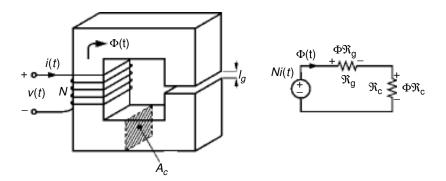

| 16 | Generic Magnetic Circuit                                                         | 23 |

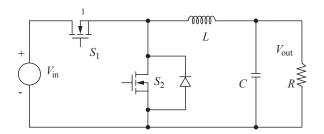

| 17 | Buck Converter Circuit                                                           | 25 |

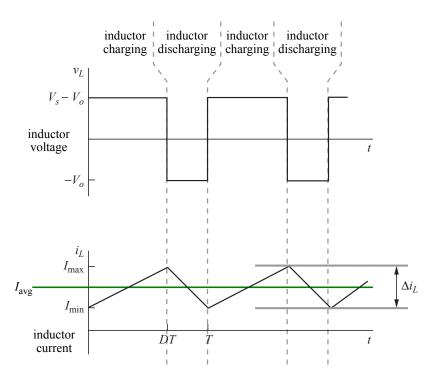

| 18 | Buck Converter Waveforms                                                         | 26 |

| 19 | Single-Chip DC/DC Converter                                                      | 26 |

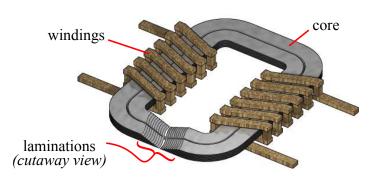

| 20 | Full Inductor Construction                                                       | 27 |

| 21 | Full Inductor Cross-Section                                                      | 27 |

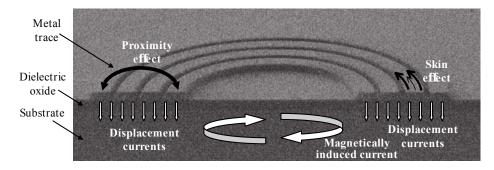

| 22 | Loss Mechanisms in a Conventional Integrated Inductor                            | 28 |

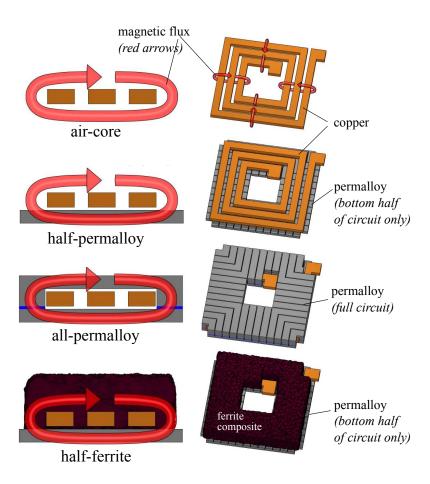

| 23 | Inductor Variants                                                                | 30 |

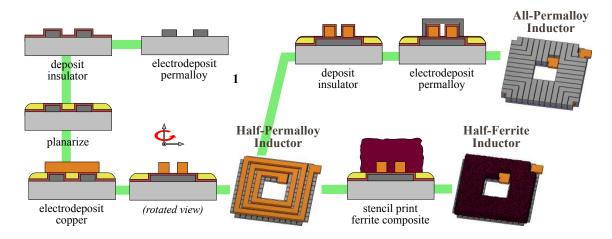

| 24 | Inductor Microfabrication Process                                                | 32 |

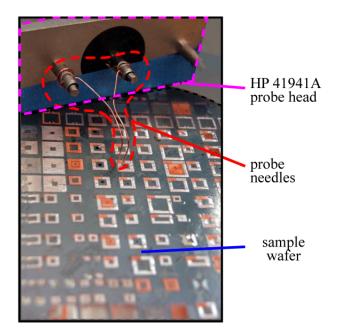

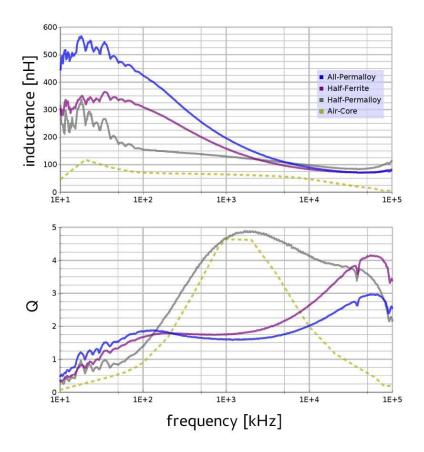

| 25 | Device-level Probing of Microfabricated Inductors                                | 34 |

| 26 | Microfabricated Inductor Device Characterization                                 | 35 |

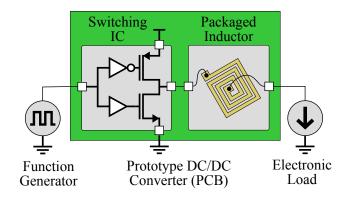

| 27 | Prototype DC/DC Converter Utilizing Microfabricated Inductor                     | 36 |

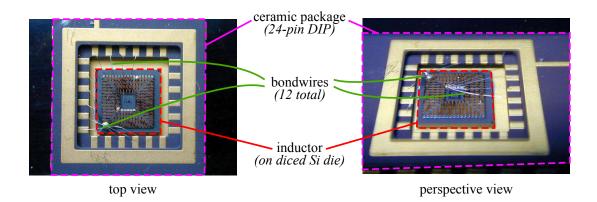

| 28 | Finished and Packaged Microfabricated Inductor                                   | 37 |

| 29 | Experimental Setup for System-Level Characterization of Microfabricated Inductor | 38 |

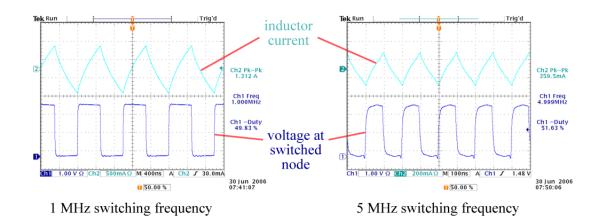

| 30 | DC/DC Converter Waveforms                                           | 38 |

|----|---------------------------------------------------------------------|----|

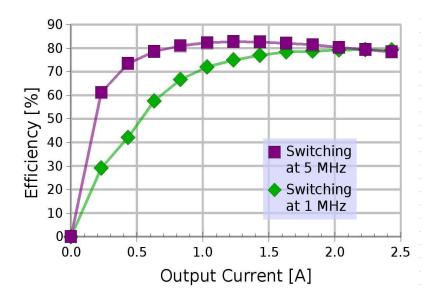

| 31 | DC/DC Converter Efficiency                                          | 39 |

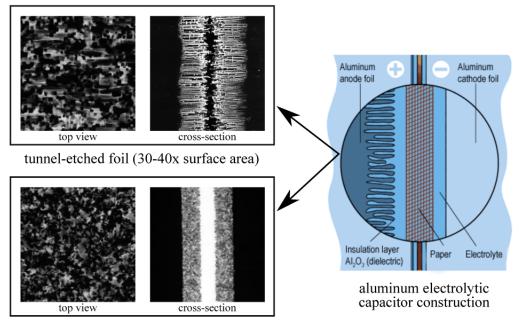

| 32 | Etched foils for electrolytic capacitors                            | 43 |

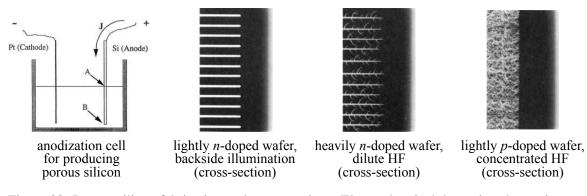

| 33 | Porous silicon fabrication and cross-sections                       | 44 |

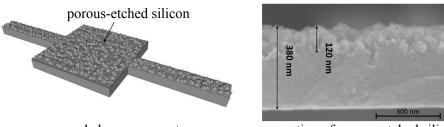

| 34 | Sensor Based on Porous Silicon                                      | 44 |

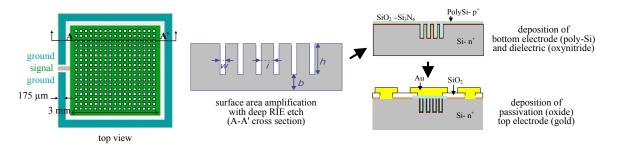

| 35 | Deep RIE-based silicon capacitors                                   | 45 |

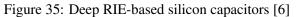

| 36 | Deep RIE-based silicon capacitors                                   | 45 |

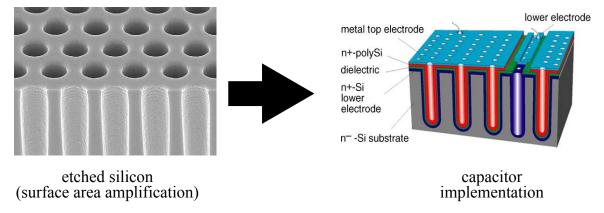

| 37 | High-surface area metal structure formed by plating through silicon | 46 |

| 38 | Photolithography-based high-surface area fabrication                | 46 |

| 39 | Carbon nanotube-based capacitor                                     | 47 |

| 40 | Silicon nanocones                                                   | 47 |

| 41 | Tobacco Mosaic Virus-based Structures                               | 48 |

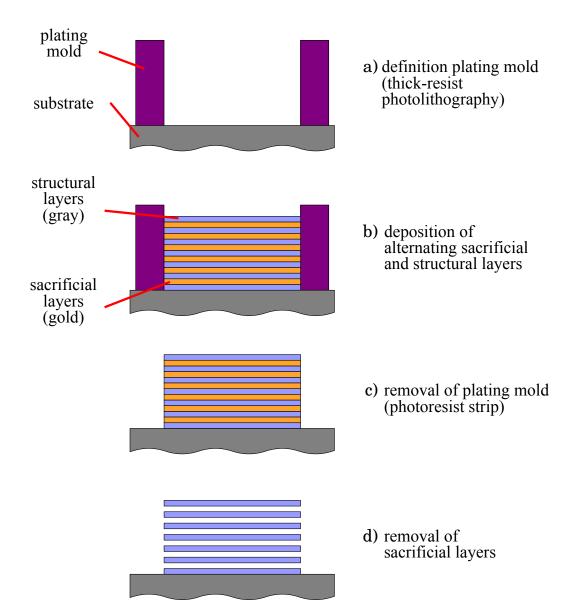

| 42 | Generic sacrificial multilayer plating process.                     | 49 |

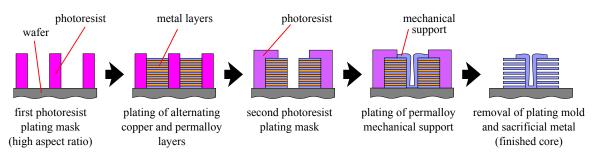

| 43 | Multilayer process for laminated magnetic cores (Park)[46]          | 50 |

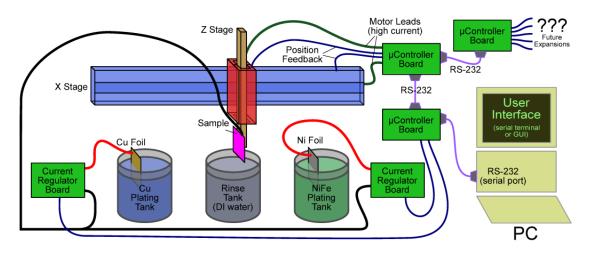

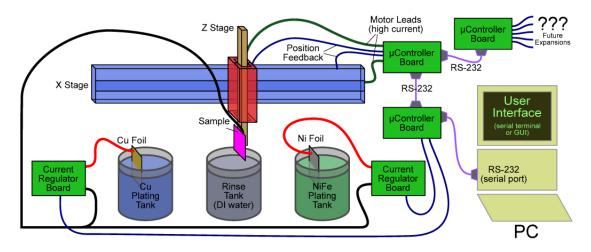

| 44 | Automated Multilayer Electroplating System Architecture             | 52 |

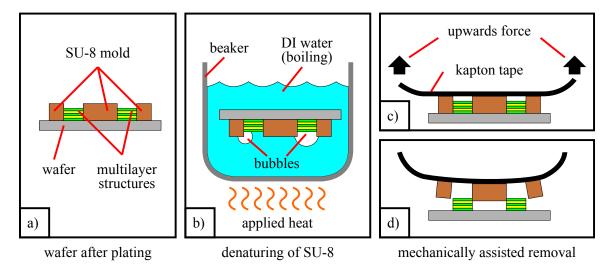

| 45 | Hydrophilic removal of SU-8                                         | 55 |

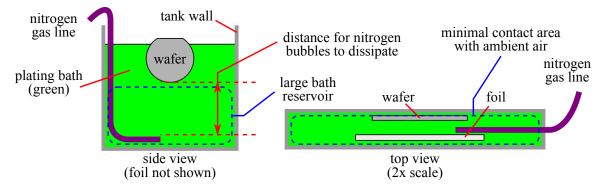

| 46 | Guiding concerns in plating tank design                             | 57 |

| 47 | Etch rate dependence on height                                      | 61 |

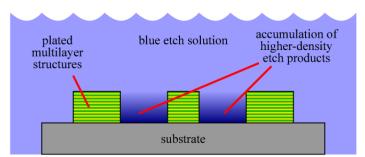

| 48 | Hypothesized pooling of blue etch products                          | 61 |

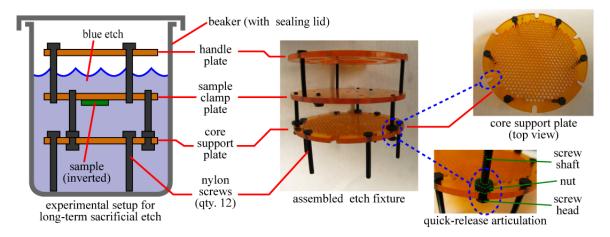

| 49 | Fixture for extended-length sacrificial etching                     | 62 |

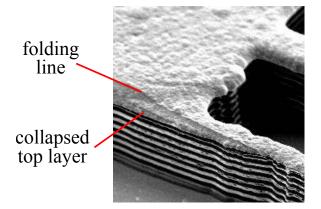

| 50 | Collapse of top layer during drying                                 | 64 |

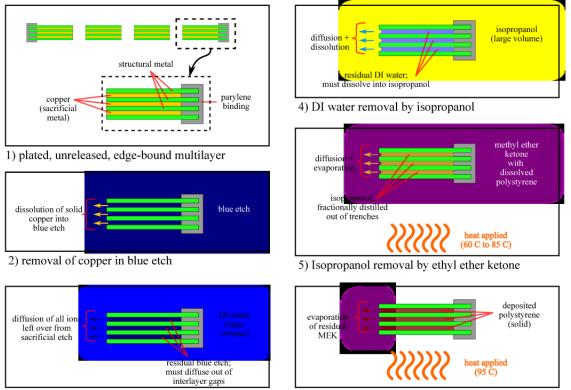

| 51 | All-Liquid Sacrificial Post-Release Process                         | 65 |

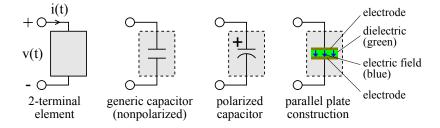

| 52 | Capacitor Representations                                           | 70 |

| 53 | Capacitors for voltage filtering                                    | 71 |

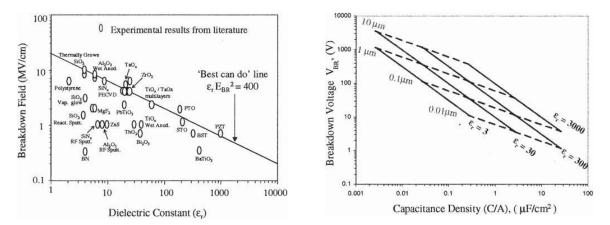

| 54 | Breakdown Characteristics of Common Dielectric Materials            | 73 |

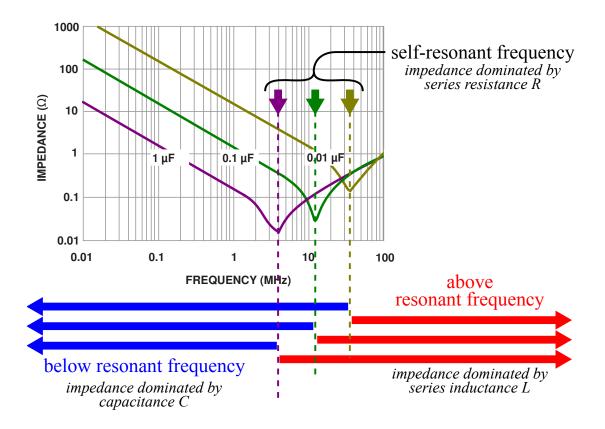

| 55 | Typical Capacitor Impedance vs. Frequency                           | 74 |

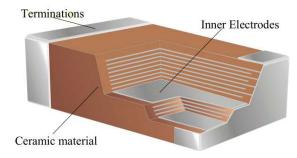

| 56 | Multilayer Ceramic Capacitor Construction                           | 75 |

| 57 | Microfabricated Capacitor Schematic                                 | 79 |

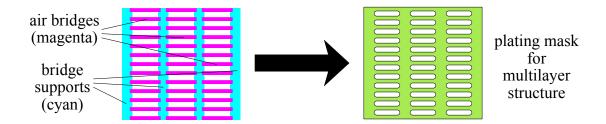

| 58 | Plating Mask Design for Air Bridges and Supports                    | 80 |

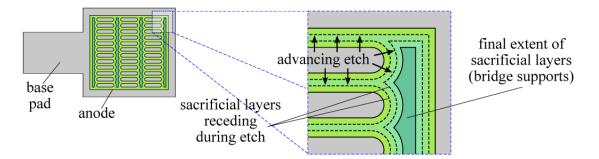

| 59 | Formation of Air Bridges and Supports During Etch                   | 81 |

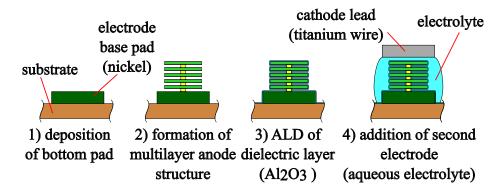

| 60 | Capacitor Fabrication Flow                                          | 83 |

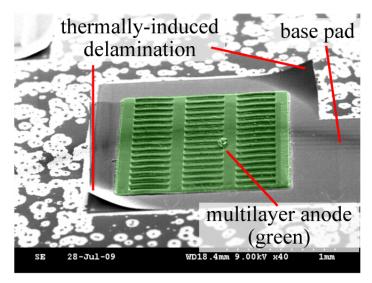

| 61 | Delamination of Capacitor Base Electrode                          | 84  |

|----|-------------------------------------------------------------------|-----|

| 62 | Excessive Dielectric Deposition on Capacitor Electrode            | 86  |

| 63 | Exposed Interior of Capacitor Anode Gap                           | 86  |

| 64 | Parylene for Protecting Layer Edges                               | 87  |

| 65 | Potential Scenarios for Liquid Electrode Infiltration             | 87  |

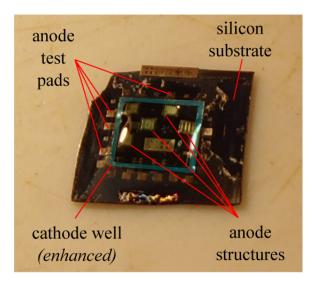

| 66 | Photograph of Microfabricated Capacitor                           | 87  |

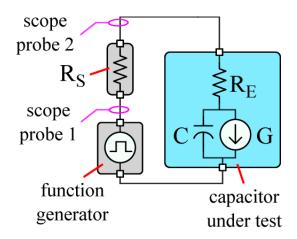

| 67 | Capacitor Characterization Schematic                              | 88  |

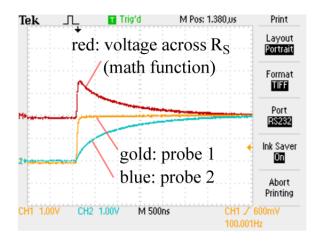

| 68 | Microfabricated Capacitor Test Waveforms                          | 89  |

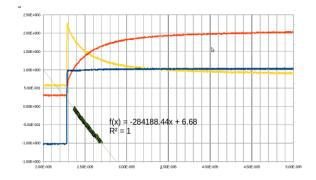

| 69 | Capacitor Characterization Waveform Analysis                      | 90  |

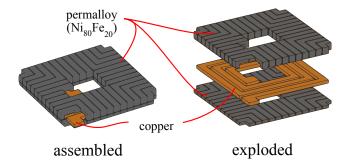

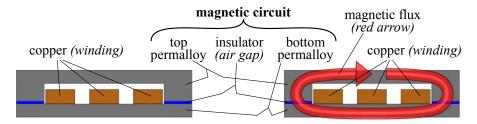

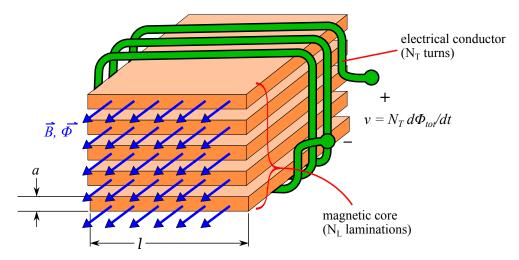

| 70 | Conceptual Representation of Highly Laminated-Core Transformer    | 96  |

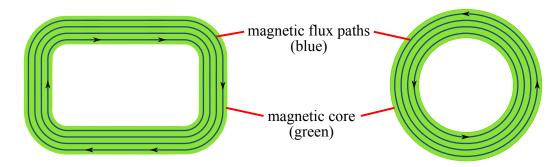

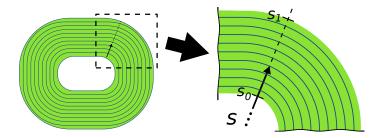

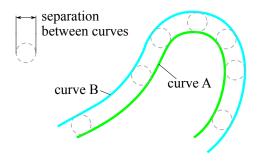

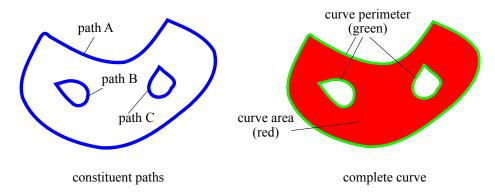

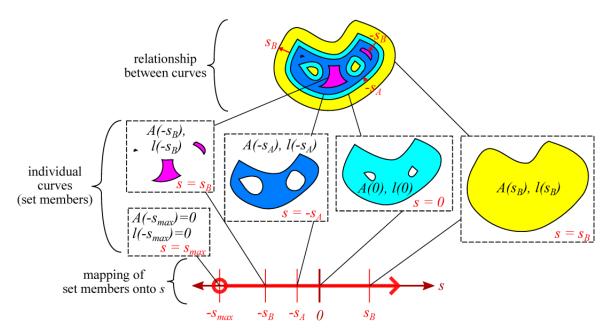

| 71 | Organization of magnetic flux into eikonally-related paths        | 97  |

| 72 | Organization of magnetic flux into eikonally-related paths        | 98  |

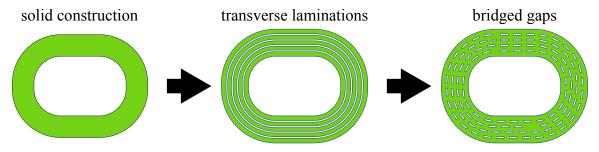

| 73 | Conceptual Evolution of Plating Mask for Laminated Magnetic Cores | 100 |

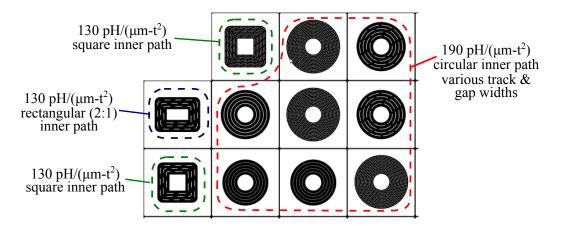

| 74 | Plating Masks for Laminated Magnetic Core                         | 102 |

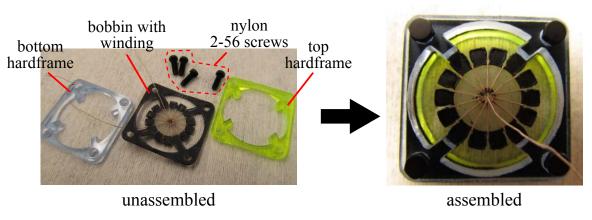

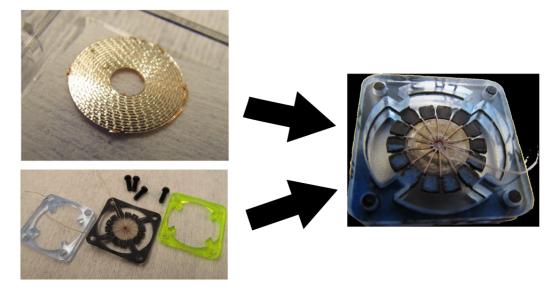

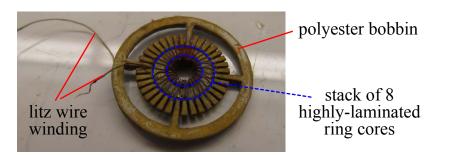

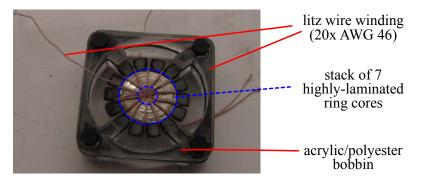

| 75 | Full bobbin assembly                                              | 103 |

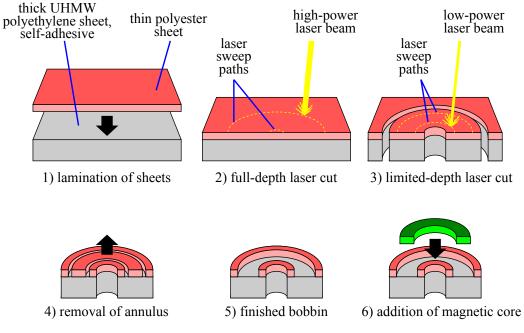

| 76 | Bobbin fabrication by laser machining                             | 104 |

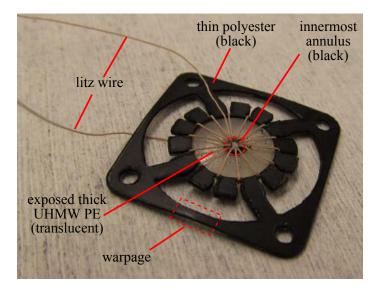

| 77 | Completed bobbin with winding                                     | 104 |

| 78 | Assembly of Laminated-Core Inductor                               | 105 |

| 79 | Laminated Cores on Wafer                                          | 106 |

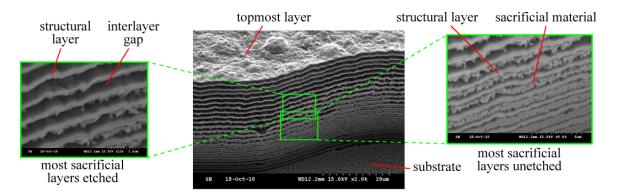

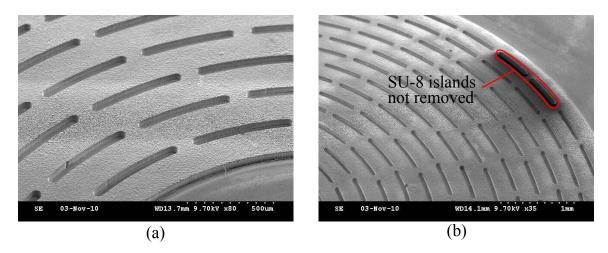

| 80 | SEM micrograph showing multiscale character of laminated cores    | 106 |

| 81 | Laminated cores undergoing final release                          | 107 |

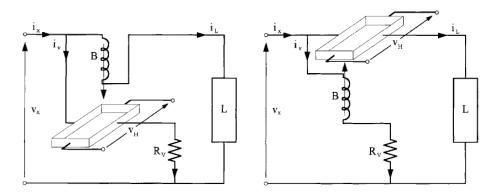

| 82 | Hall Effect Wattmeters                                            | 111 |

| 83 | Thermocouple-based Wattmeter                                      | 111 |

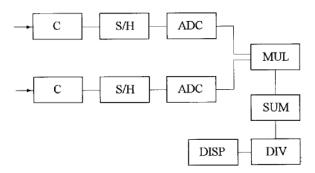

| 84 | Sampling Wattmeter                                                | 113 |

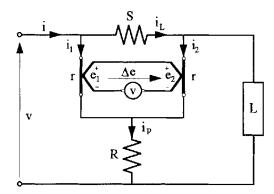

| 85 | Idealized Schematic of Resonant Loss Measurement Circuit          | 116 |

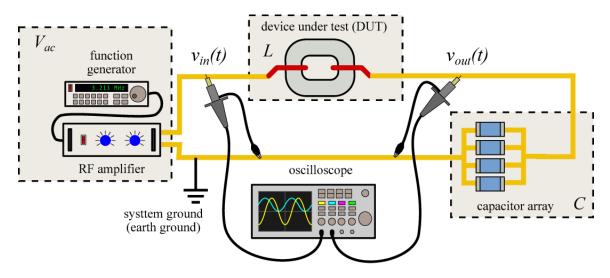

| 86 | Implementation Schematic of Resonant Loss Measurement System      | 117 |

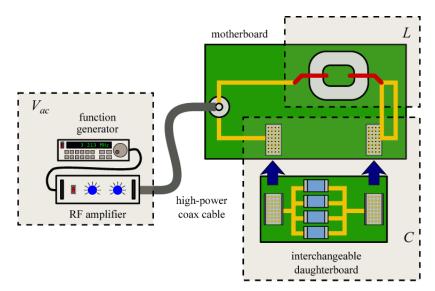

| 87 | Complete loss characterization system schematic                   | 117 |

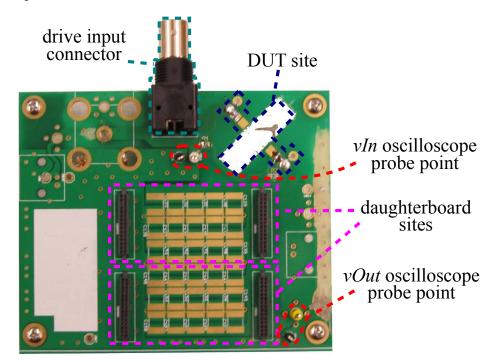

| 88 | Motherboard for loss characterization system                      | 119 |

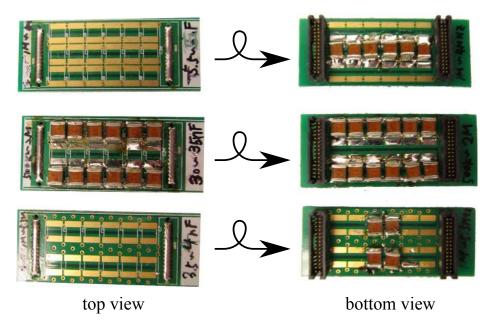

| 89 | Daughterboards for loss characterization system                   | 120 |

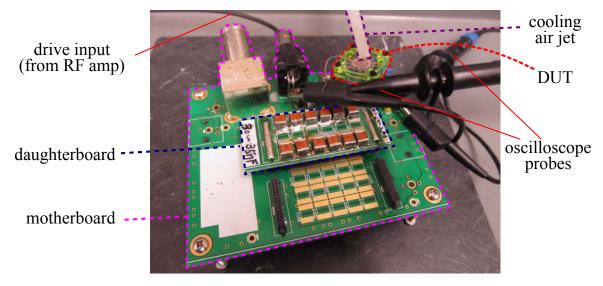

| 90 | Fully connected loss characterization board                       | 120 |

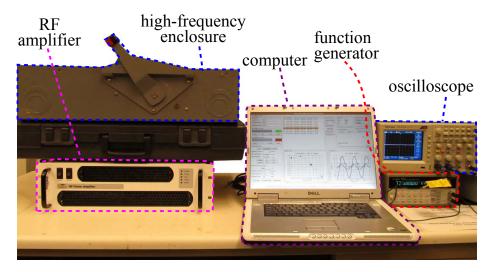

| 91 | Complete loss characterization system                             | 121 |

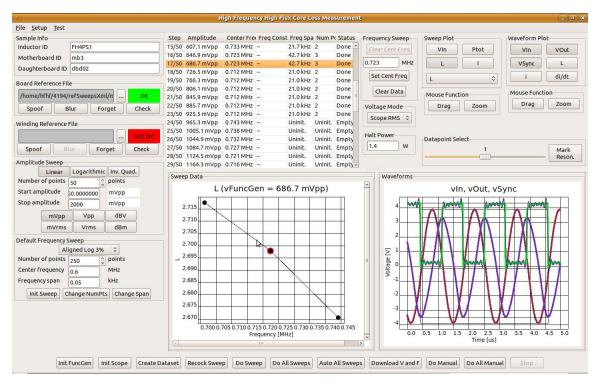

| 92  | Screenshot of characterization system software                                                                                                                                                                                                                                               | 121 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

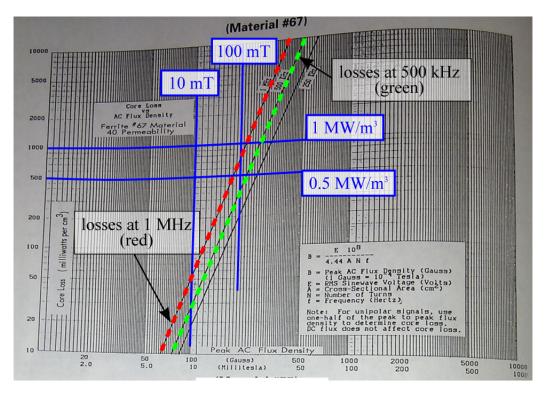

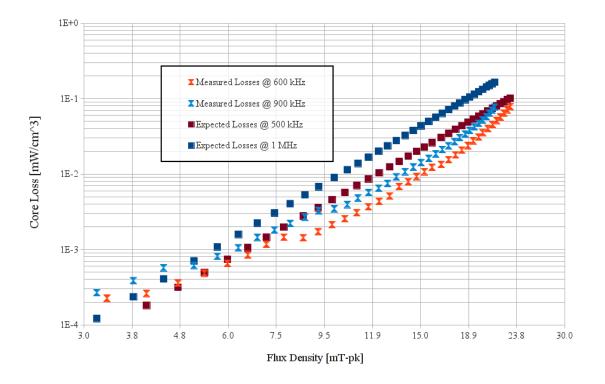

| 93  | Vendor-Provided Loss Data for Qualification Sample                                                                                                                                                                                                                                           | 123 |

| 94  | Qualification Sample Losses, Measured and Expected                                                                                                                                                                                                                                           | 124 |

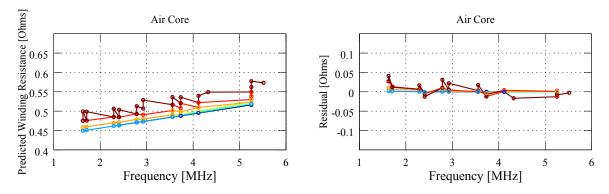

| 95  | Air Core Inductor Losses                                                                                                                                                                                                                                                                     | 125 |

| 96  | Air Core Inductor Losses                                                                                                                                                                                                                                                                     | 126 |

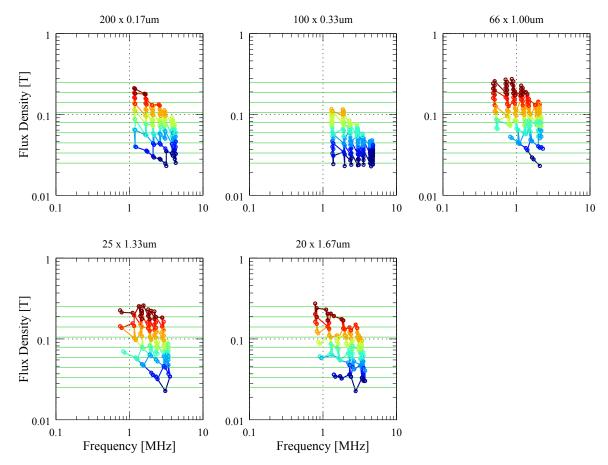

| 97  | Flux Density and Frequency Coverage for Core Loss Measurement                                                                                                                                                                                                                                | 130 |

| 98  | Colorization and Binning of Core Loss Data Based on Core Flux Level                                                                                                                                                                                                                          | 131 |

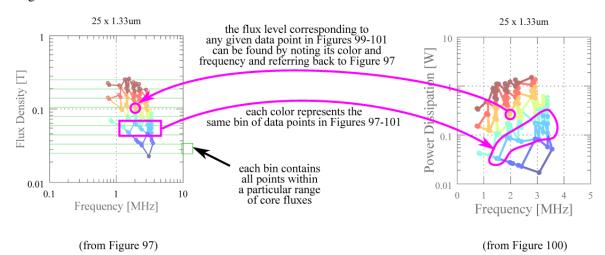

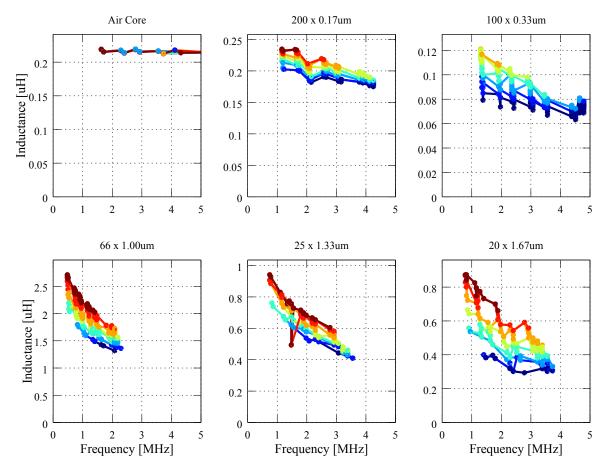

| 99  | Measured Inductance of Laminated-Core Inductors                                                                                                                                                                                                                                              | 132 |

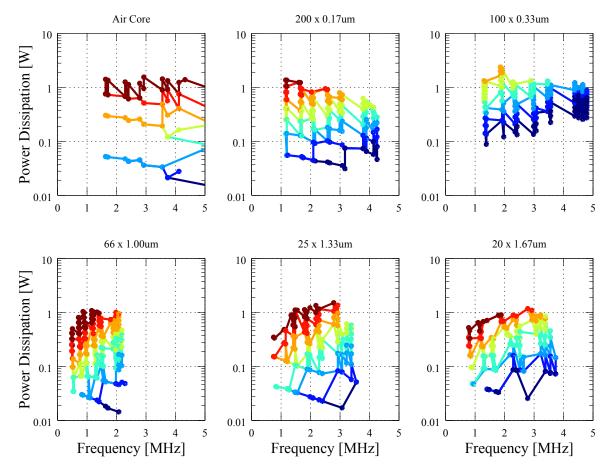

| 100 | Measured Power Loss for Laminated-Core Inductors                                                                                                                                                                                                                                             | 133 |

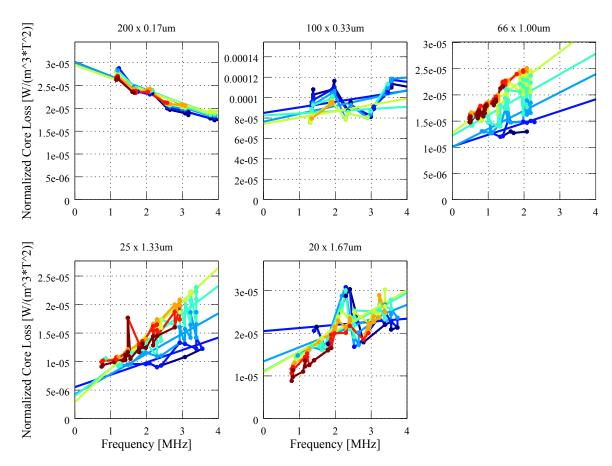

| 101 | Normalized Core Loss per Cycle, with Simple Regression Lines                                                                                                                                                                                                                                 | 134 |

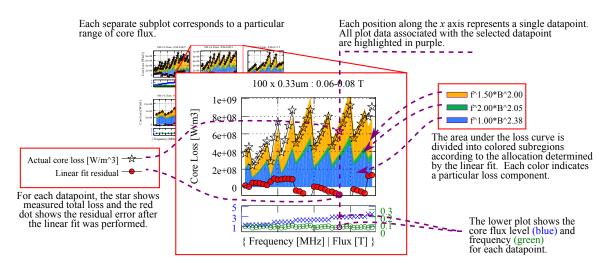

| 102 | Explanation of Fit Plot Format                                                                                                                                                                                                                                                               | 136 |

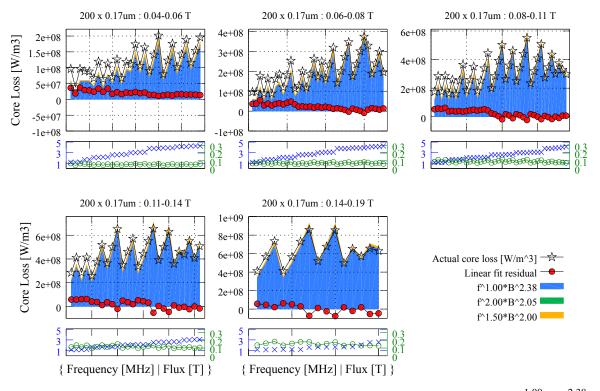

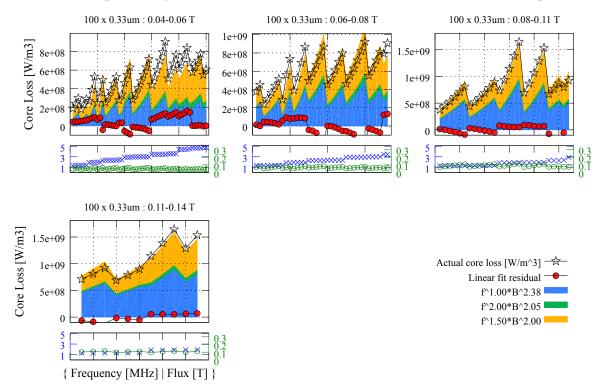

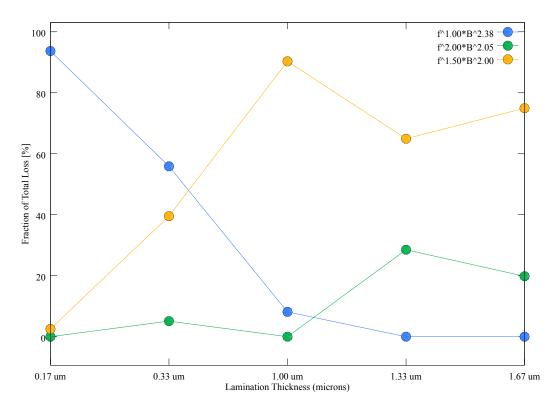

| 103 | Least-squares decomposition of sample SFH6A (166 nm laminations). $f^{1.00} * B^{2.38}$ is the term associated with hysteresis losses, $f^{2.00} * B^{2.05}$ is the term associated with eddy current losses, and $f^{1.50} * B^{2.00}$ is the term associated with anomalous losses .       | 136 |

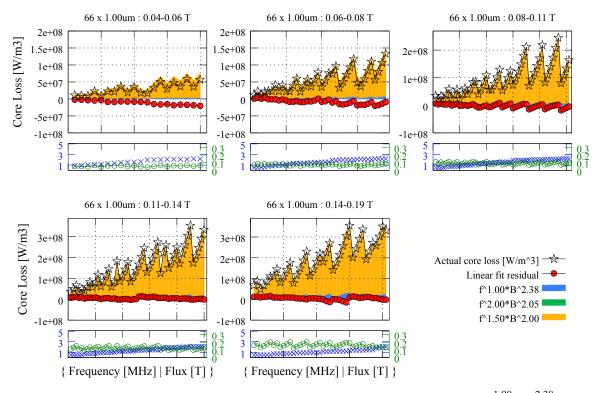

| 104 | Least-squares decomposition of sample SFH5B (333 nm laminations). $f^{1.00} * B^{2.38}$ is the term associated with hysteresis losses, $f^{2.00} * B^{2.05}$ is the term associated with eddy current losses, and $f^{1.50} * B^{2.00}$ is the term associated with anomalous losses .       | 137 |

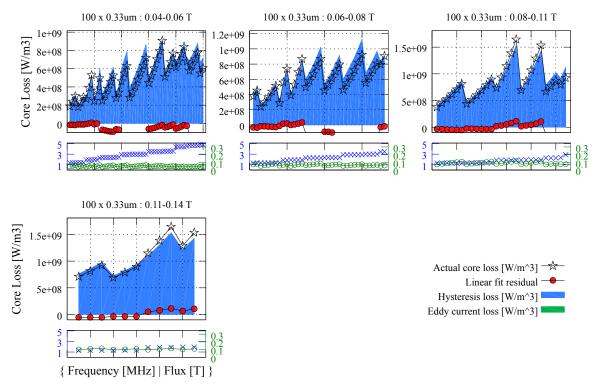

| 105 | Least-squares decomposition of sample SFH4B (1 $\mu$ m laminations). $f^{1.00} * B^{2.38}$ is the term associated with hysteresis losses, $f^{2.00} * B^{2.05}$ is the term associated with eddy current losses, and $f^{1.50} * B^{2.00}$ is the term associated with anomalous losses.     | 139 |

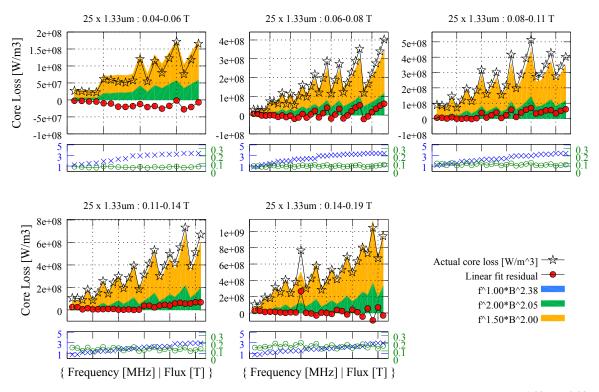

| 106 | Least-squares decomposition of sample SHT3A (1.33 $\mu$ m laminations). $f^{1.00} * B^{2.38}$ is the term associated with hysteresis losses, $f^{2.00} * B^{2.05}$ is the term associated with eddy current losses, and $f^{1.50} * B^{2.00}$ is the term associated with anomalous losses . | 140 |

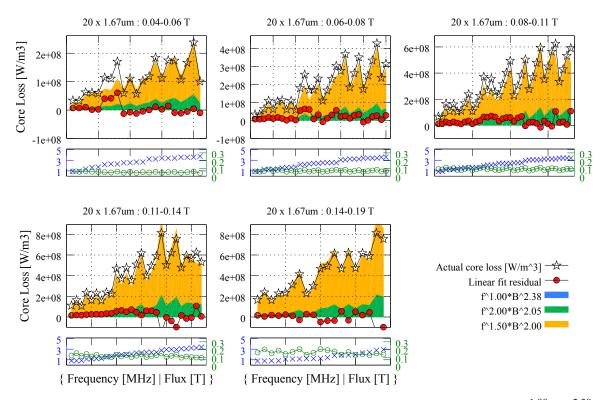

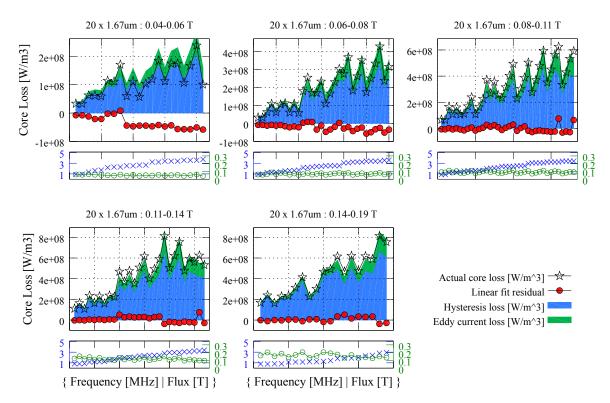

| 107 | Least-squares decomposition of sample SHT2B (1.66 $\mu$ m laminations). $f^{1.00} * B^{2.38}$ is the term associated with hysteresis losses, $f^{2.00} * B^{2.05}$ is the term associated with eddy current losses, and $f^{1.50} * B^{2.00}$ is the term associated with anomalous losses . | 141 |

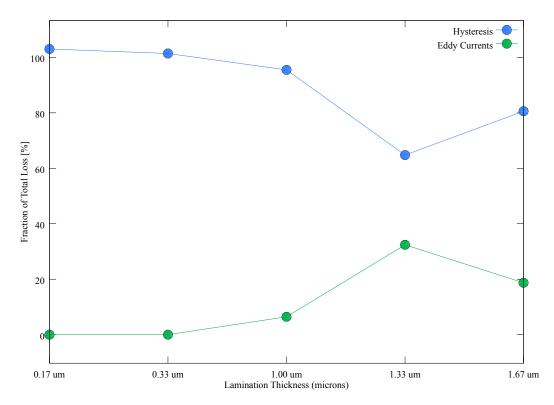

| 108 | Summary of least-squares fit for core losses                                                                                                                                                                                                                                                 | 141 |

| 109 | Least-squares decomposition of sample SHT5B (0.333 $\mu$ m laminations)                                                                                                                                                                                                                      | 142 |

| 110 | Least-squares decomposition of sample SHT2B (1.66 $\mu$ m laminations)                                                                                                                                                                                                                       | 143 |

| 111 | Allocation of measured core losses among core loss components                                                                                                                                                                                                                                | 143 |

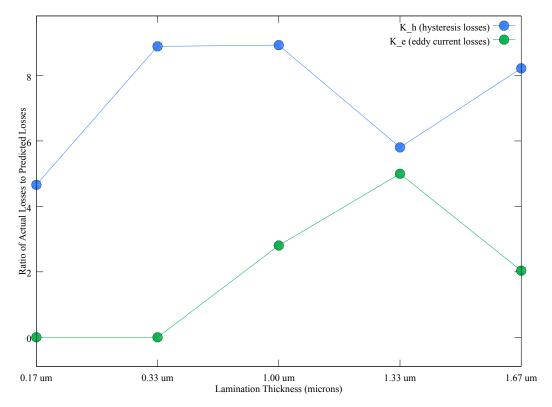

| 112 | Ratio of extracted measured core loss to predicted core loss                                                                                                                                                                                                                                 | 144 |

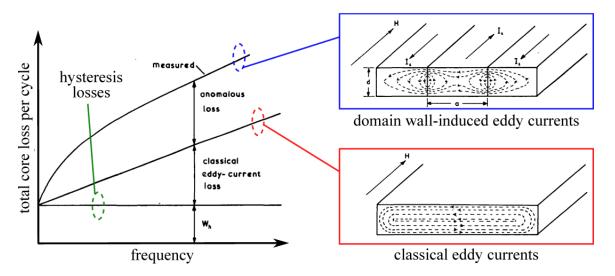

| 113 | Core Loss Constituents, Including Anomalous Losses                                                                                                                                                                                                                                           | 145 |

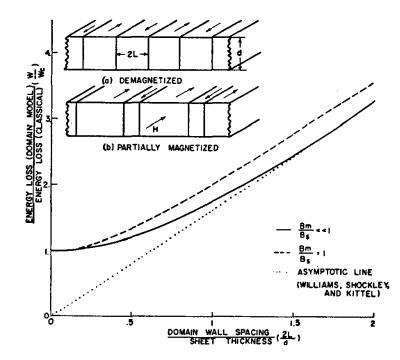

| 114 | Overestimation of Eddy Current Losses in Lamination with Longitudinal Domains                                                                                                                                                                                                                | 147 |

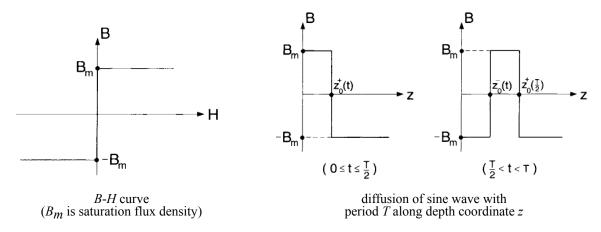

| 115 | Magnetic Diffusion in Nonlinear Material                                                                                                                                                                                                                                                     | 150 |

| 116 | Buck Converter                                                              | 157 |

|-----|-----------------------------------------------------------------------------|-----|

| 117 | Boost Converter                                                             | 157 |

| 118 | Ferrite Inductor                                                            | 158 |

| 119 | Low-Volume Laminated-Core Inductor                                          | 158 |

| 120 | High-Volume Laminated-Core Inductor                                         | 159 |

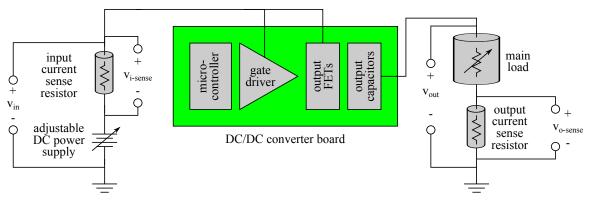

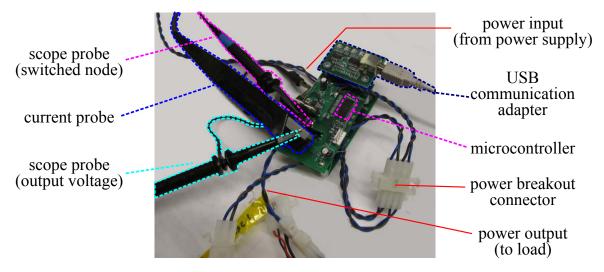

| 121 | Operational Setup for Power Converter Testing (Schematic)                   | 160 |

| 122 | Operational Setup for Power Converter Testing                               | 160 |

| 123 | Buck Converter Waveforms with Ferrite Inductor, 2MHz                        | 162 |

| 124 | Buck Converter Waveforms with Ferrite Inductor, 4MHz                        | 162 |

| 125 | Buck Converter Waveforms with Ferrite Inductor, 6MHz                        | 163 |

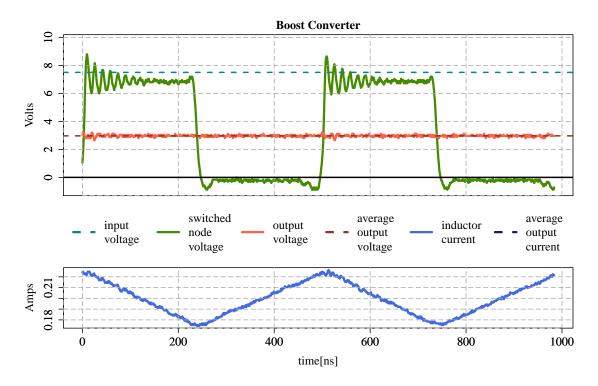

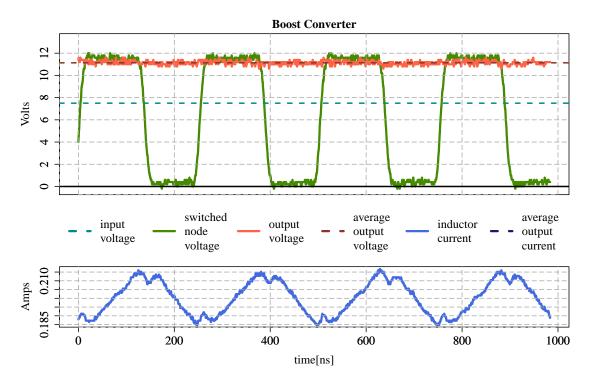

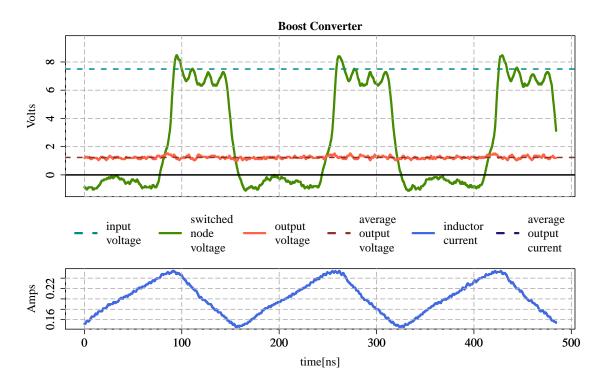

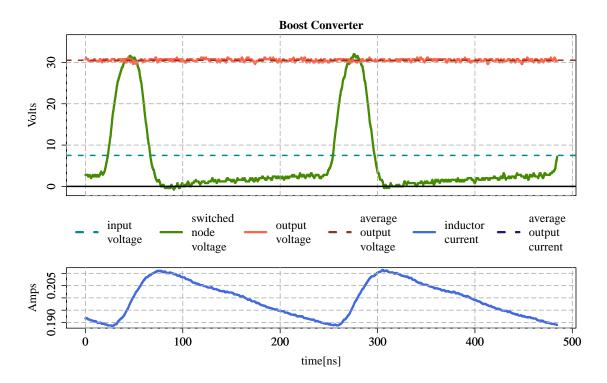

| 126 | Boost Converter Waveforms with Ferrite Inductor, 2MHz                       | 163 |

| 127 | Boost Converter Waveforms with Ferrite Inductor, 4MHz                       | 164 |

| 128 | Boost Converter Waveforms with Ferrite Inductor, 6MHz                       | 165 |

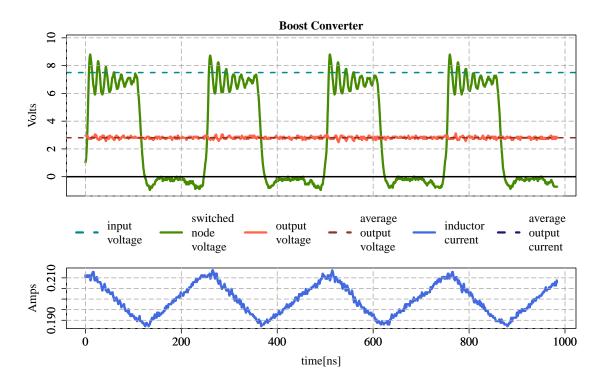

| 129 | Buck Converter Waveforms with Laminated-Core Inductor, 2MHz                 | 165 |

| 130 | Buck Converter Waveforms with Laminated-Core Inductor, 4MHz                 | 166 |

| 131 | Buck Converter Waveforms with Laminated-Core Inductor, 6MHz                 | 167 |

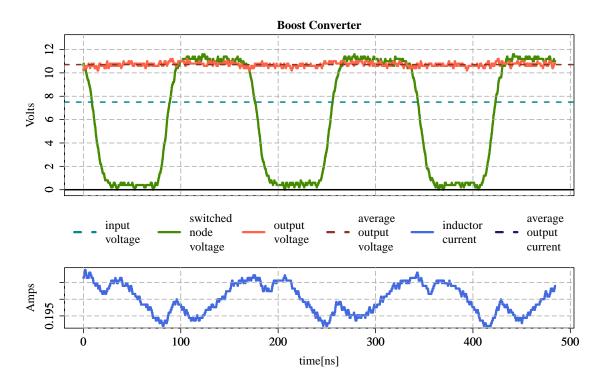

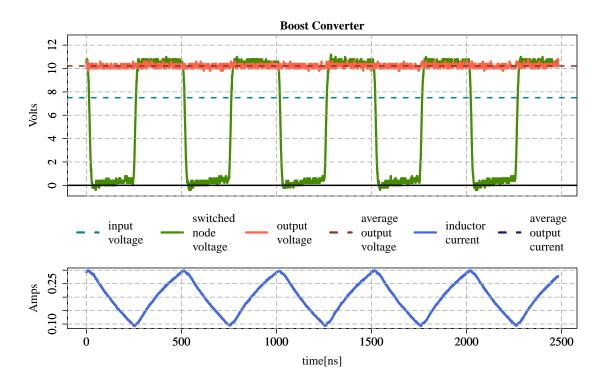

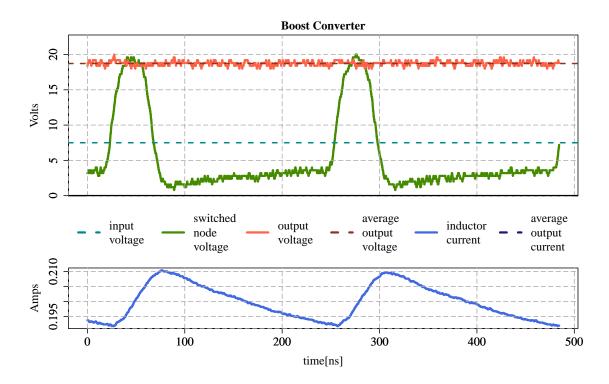

| 132 | Boost Converter Waveforms with Laminated-Core Inductor, 2MHz                | 167 |

| 133 | Boost Converter Waveforms with Laminated-Core Inductor, 4MHz                | 168 |

| 134 | Boost Converter Waveforms with Laminated-Core Inductor, 6MHz                | 168 |

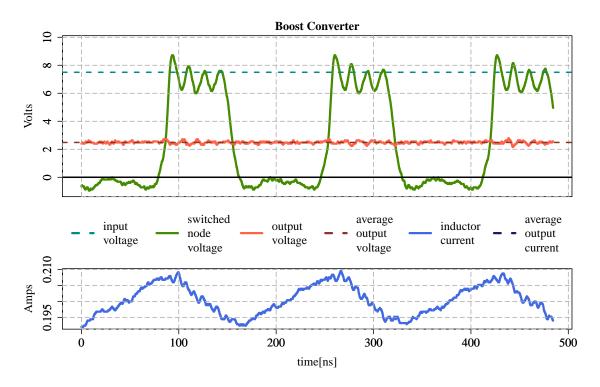

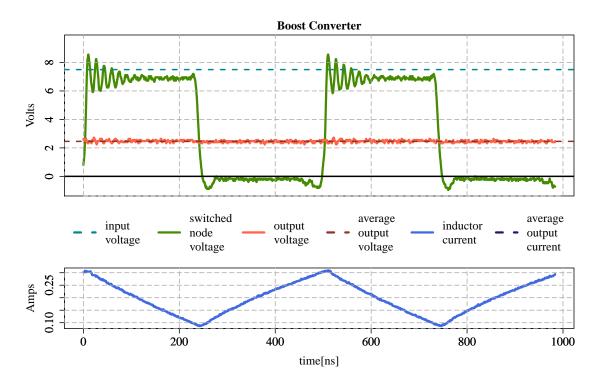

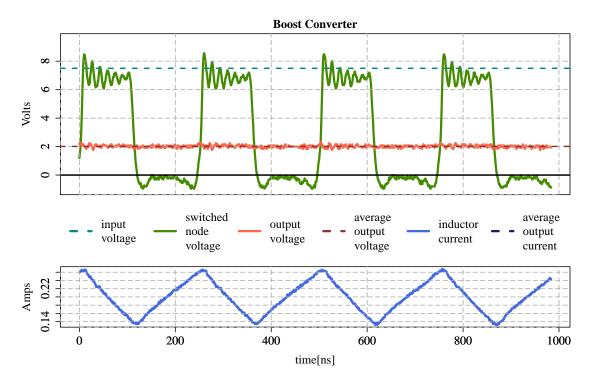

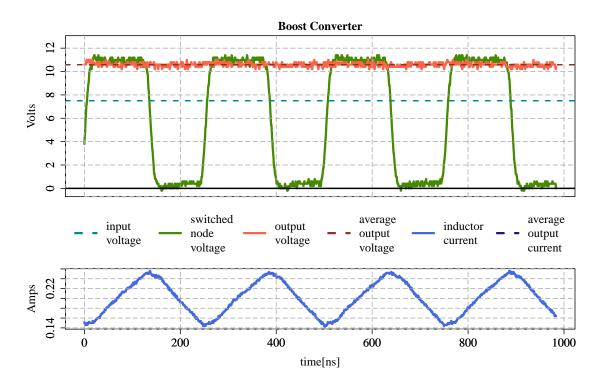

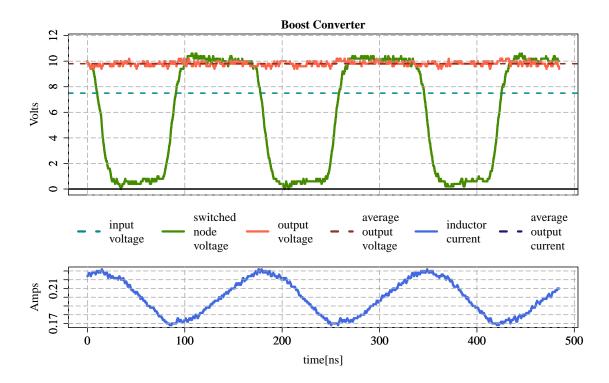

| 135 | Boost Converter Waveforms with High-Volume Laminated-Core Inductor, 4.8 MHz | 169 |

| 136 | Boost Converter Waveforms with High-Volume Laminated-Core Inductor, 4.8 MHz | 169 |

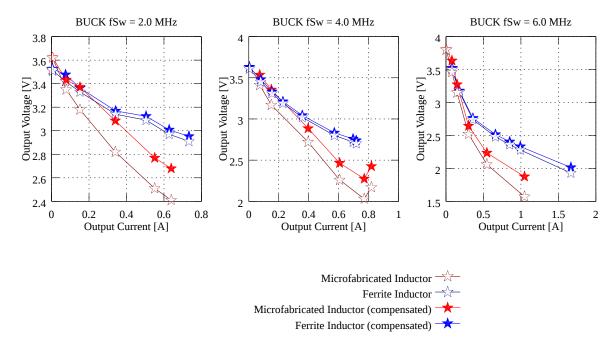

| 137 | Buck Converter Load Characteristic                                          | 172 |

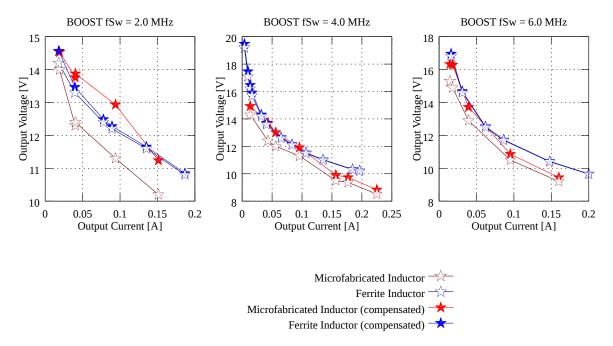

| 138 | Boost Converter Load Characteristic                                         | 173 |

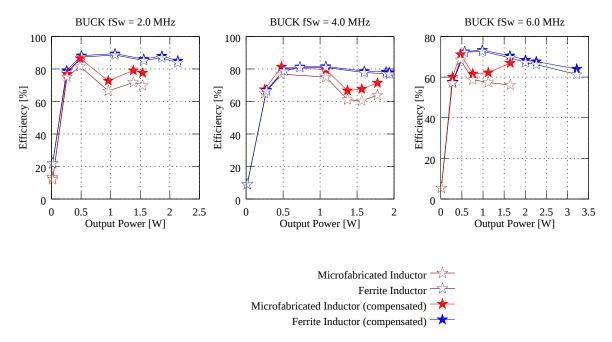

| 139 | Efficiency of Buck Converter                                                | 174 |

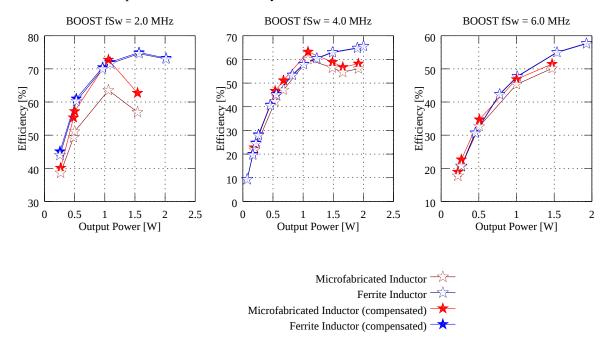

| 140 | Efficiency of Boost Converter                                               | 174 |

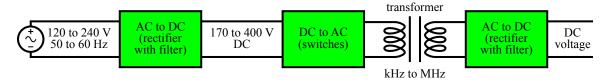

| 141 | Typical Offline AC/DC Converter Architecture                                | 176 |

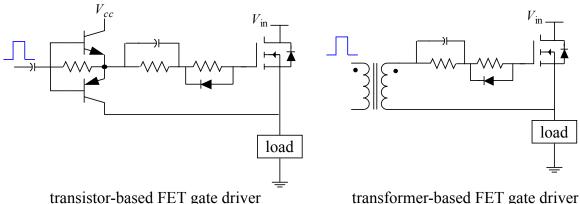

| 142 | High-Side MOSFET Gate Drive Circuits                                        | 182 |

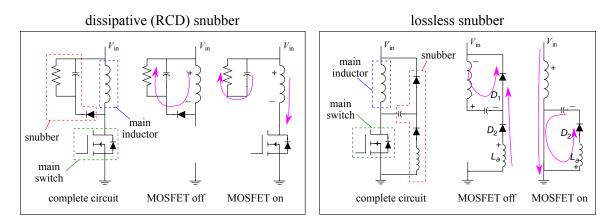

| 143 | Lossless Snubber Circuit                                                    | 184 |

| 144 | Magnetocaloric Refrigerator (AMR) and Regenerator Bed                       | 185 |

| 145 | Schematic of high-speed magnetohydrodynamic pump                            | 188 |

| 146 | Eikonal Curves                                                              | 191 |

| 147 | Curve-related Definitions                                 | 192 |

|-----|-----------------------------------------------------------|-----|

| 148 | Eikonal Curve Set                                         | 193 |

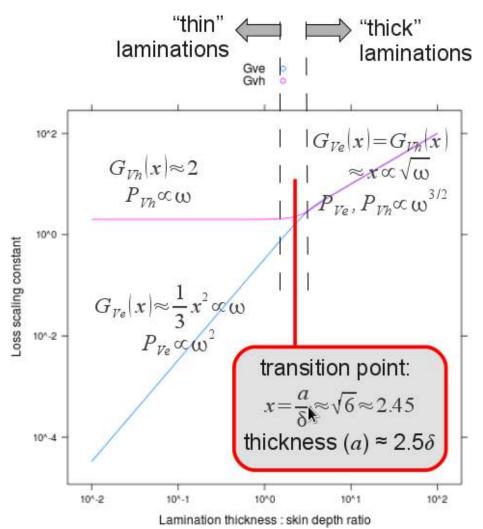

| 149 | Eddy Current Transduction                                 | 198 |

| 150 | Single Lamination Geometry                                | 200 |

| 151 | Geometric Loss Scaling Constants                          | 201 |

| 152 | Geometric Loss Scaling Constants                          | 204 |

| 153 | Interpretation of $P_{magV}$                              | 205 |

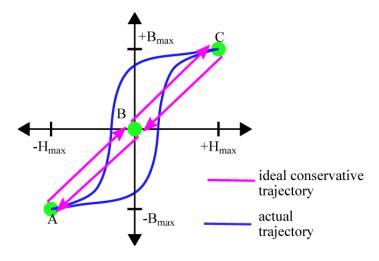

| 154 | Interpretation of $S$                                     | 208 |

| 155 | Observation and Discrimination of <i>S</i> from VSM Trace | 208 |

| 156 | Numerical Determination of $S$                            | 209 |

| 157 | Assumed Power Flow for Inductor Characterization          | 210 |

| 158 | Automated Multilayer Electroplating System Architecture   | 221 |

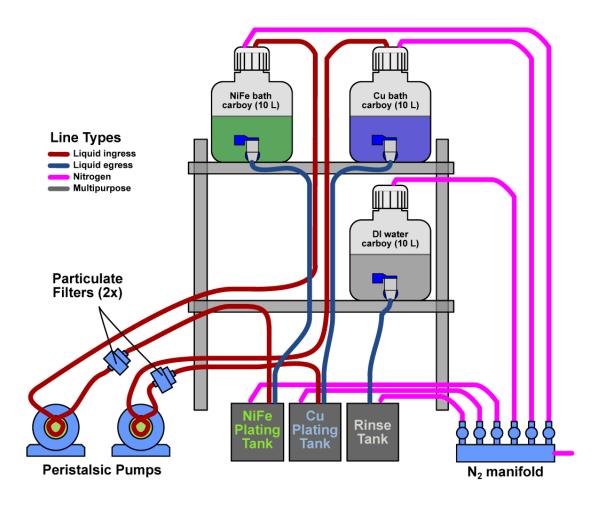

| 159 | Fluidic System Design for Electroplating Robot            | 224 |

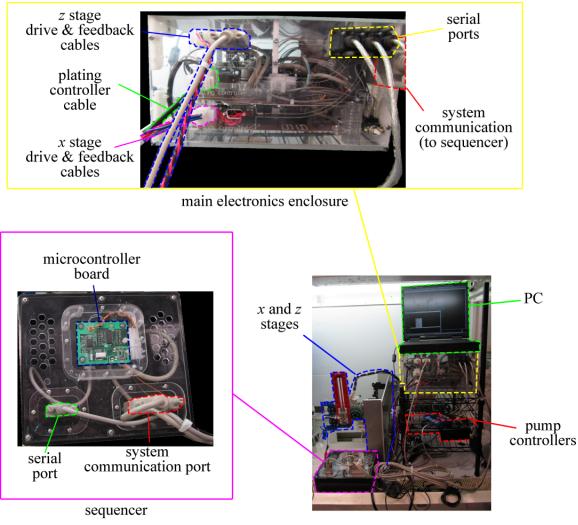

| 160 | Electronics System for Electroplating Robot               | 226 |

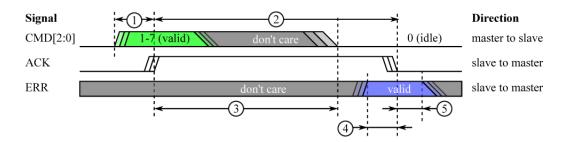

| 161 | Dynamic Communication System (DCS) protocol               | 227 |

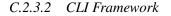

| 162 | CLI Framework Architecture                                | 229 |

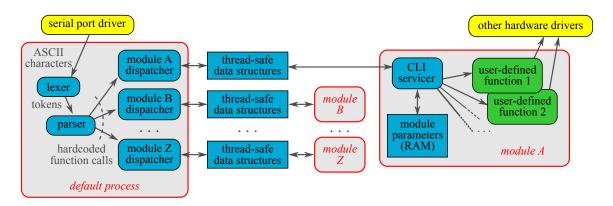

| 163 | z Stage Mechanism                                         | 231 |

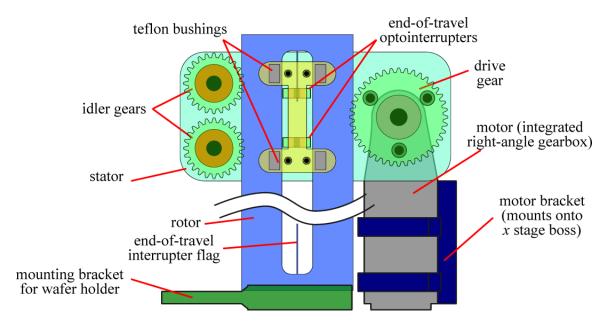

| 164 | Plating Controller Schematic                              | 232 |

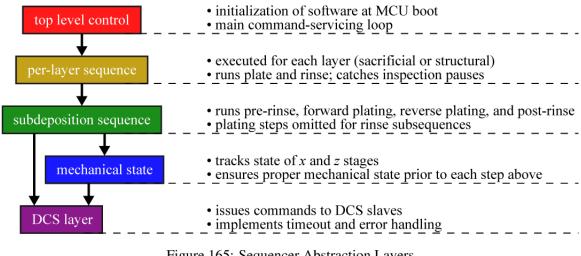

| 165 | Sequencer Abstraction Layers                              | 233 |

## SUMMARY

Fabrication technology, based on MEMS processes, for constructing components for use in switched-mode power supplies are developed and presented. Capacitors, magnetic cores, and inductors based on sacrificial multilayer electroplating are designed, fabricated, and characterized. A coherent set of microfabrication processes based on sacrificial multilayer electroplating followed by a selective, sacrificial etch is utilized and extended.

Construction of capacitors using this technique leverages its intrinsic ability to produce high surface area structures, creating a path to very high-density capacitors. Its capability of producing very thin layers of magnetic alloys is used to create magnetic cores with reduced eddy current losses.

This technique can enable radical performance improvements in power magnetics devices as well. Although magnetic alloys offer high saturation density and low hysteresis losses, eddy current losses remain as a critical obstacle to the employment of these materials in high-speed power converters. By demonstrating that sacrificial multilayer electroplating offers a reliable method for controlling eddy current losses, this work demonstrates a path to bringing the natural benefits of magnetic alloys to bear in power electronics systems.

Accordingly, highly laminated magnetics cores are fabricated and used to build power inductors. In-depth characterization of the produced inductors is presented to confirm this improvement. As well, the demonstration of the produced inductors in DC/DC converters at high frequencies is presented.

Initial work addressing the top-down development of a fully-integrated DC/DC converter is presented. This work focuses on the integration of an advanced power inductor on a silicon substrate, along with provisions for substrate contact as well as performance optimization.

Supporting results detailing the advancement of the core process of sacrificial multilayer electroplating are presented. These results focus primarily on the development of a second-generation automated multilayer electroplating system, as well as on experiential learning and practical packaging of the microfabricated structures. The combination of these advances allowed for the sacrificial multilayer electroplating process to be extended to produce structures not only with thinner layers than previous results, but also larger total thicknesses.

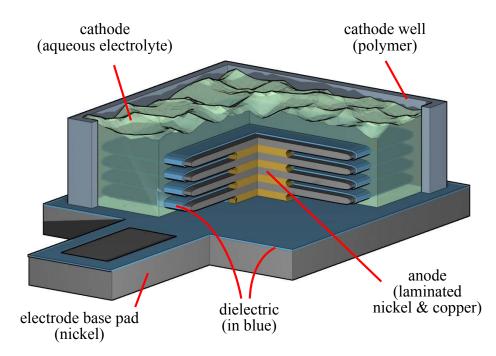

The initial application of the advanced sacrificial multilayer plating process to produce microfabricated capacitors is presented. These capacitors, which achieved in excess of 1.5 nF/mm<sup>2</sup> capacitance density, served both to confirm the ability of the process to produce high surface area structures as well as demonstrate its feasibility for producing high density capacitors.

Next, the fabrication of highly-laminated magnetic cores and power inductors based on sacrificial multilayer electroplating is presented, along with the design and development of a system for characterizing inductor behavior at high-frequency, high-flux conditions. Experimental results for devices of a number of lamination thicknesses are presented and analyzed, and a trend of suppressed eddy current loss is demonstrated.

Finally, the design and operation of DC/DC converters built around these highly-laminated-core inductors are presented. Both buck and boost topologies were implemented and operated from 2 MHz to 6 MHz. For comparison, an off-the-shelf ferrite inductor was also used in place of the laminated-core inductors. While the ferrite inductor dissipated less power than the microfabricated inductors, its magnetic core was also drastically larger than that of the microfabricated inductors.

The principal contributions of this work are: the demonstration of a MEMS-based microfabrication process for the fabrication of both inductors and capacitors; the advancement of this microfabrication process; and the ability of this microfabrication process to produce inductors with minimized eddy current losses and low core volume requirements.

# **CHAPTER I**

# **INTRODUCTION**

#### 1.1 Motivation

The marvels of modern electronics depend every bit as much upon power supplies as they do upon microprocessors, optical displays, and nonvolatile memories. However, the former are not as widely researched the latter, in large part because power converters generally do not play a large role in determining overall system performance. This has resulted in power electronics receiving considerably less design, fabrication, and packaging research attention than the other, more outwardly visible system components have.

This arrangement is economically sound, but it is bound for change nonetheless. Two continuing trends in the electronics industry – mobility and energy efficiency – are now exerting major pressure on power converters. Responses to this pressure have come from circuit design innovations like soft switching and multiphase topologies, or from advances derived from mainstream electronics, chiefly in the form of faster power transistors and more powerful control circuits.

More radical solutions, namely advanced *power* systems packaging and *power* passive components fabrication, bear the mark of this history; they are only weakly accommodated by conventional packaging research, and power electronics-specific approaches are few in number. But, such radical solutions may one day become necessary for supporting continued advances in power electronics circuitry, if not for meeting overall electronics system size, weight, and efficiency demands.

Even if progress in power electronics is not critically slowed by limited innovation in packaging and components, modern electronics can benefit substantially from improved power electronics integration. Certainly, many conventional techniques for achieving smaller size or higher efficiency, such as soft switching or faster switching, could be facilitated by the reduced parasitics and electromagnetic interference (EMI) that fully integrated power passives would provide. As well, microfabrication-based packaging approaches are very apt to favor planar constructions, as opposed to the cubic and cylindrical constructions found in conventional discrete power magnetics and capacitors. This will better match form factor demands not only of other circuit boards within the system but also of the entire system.

This document presents research directed to address the relative lack of power electronics packaging platforms. The essence of the approach is to bring to bear the rapidly growing body of fabrication knowledge found in the field of microelectromechanical systems (MEMS) upon this problem. Previous, proven research results in micromagnetics and high-speed microfabricated magnetic cores are extended and adapted to meet the practical needs of advanced power converters.

## 1.2 History

## **1.2.1** The Evolution of Power Converters

As the "Electric Age" debuted at the turn of the 20th century, power converters – systems to convert electricity from one form to another – were not required. Early power distribution grids were well-tuned to the loads they served, not only as a consequence of electricity's narrow application domain at the time – lights and motors – but also a consequence of electricity providers' vigorous competition. In many ways, the power grid as it now exists was specified by the needs of electricity's first end users. For instance, multi-phase AC distribution saw adoption not because of its large-scale efficiency savings, but because the first robustly self-starting motors required two or more phases.[43]

Inevitably, devices and uses for electricity came about which required power in forms that the contemporary grid could not provide, and the need for power converters thus materialized. An example of this was incandescent light bulbs. When powered by 25 Hz AC electricity, the bulbs produced a visible flicker. The solution to this problem, a motor with a directly coupled DC generator, can be considered as one of the first widely-adopted power converter applications.

Figure 1 shows the main eras of power electronics. With each new generation of devices, and each new era, fundamentally differing power supply needs were presented. Transformers were deployed relatively early within the power grid, and have stood until only recent decades as the primary means for AC/AC power conversion. The shift from magnetic amplifiers, fundamentally AC devices, to vacuum tubes, fundamentally DC devices, drove a pronounced increase in demand demand for AC/DC converters.

Figure 1: Power Electronics History (after [71])

In the 1970s, transistors, again fundamentally DC devices, became commercially feasible, and electronics became increasingly pervasive in consumer markets. Consequently, AC/DC converters became just as pervasive. [45] As battery technology improved and electronics continuously required less power, the field of portable electronics grew at a fast rate, and interest in DC/DC converters grew accordingly. A similar dynamic has driven interest in high-capacity AC/AC converters for use in power distribution grids. [74]

## 1.2.2 Emphasis on Power Converter Packaging

The proliferation of electronics among mass markets fueled a push towards faster and lighter electronics. As mobility and portability are universally on the rise in consumer electronics, this force is also beginning to bear directly on power supplies, since they still contribute a disproportionately large amount of size and weight.

As a result, power converters have been garnering more and more attention from system designers. Market predictions bear the same conclusion; most of the growth areas for power electronics are in sectors where size and weight are at a premium. [57] The generalities of this trend are not new in that its basic drivers are external to the field of power electronics itself.

Tightening regulations governing efficiency, power grid pollution, and electromagnetic compatibility (EMC) provide one broad impetus, while the ever-evolving needs of electron devices provide another. Among the former, [39]

• the need for harmonics-limiting power factor correction,

Figure 2: Operating Frequency and Power for Electronics Systems[3]

- critically slow progress in battery energy densities, requiring ultra-efficient battery-sourced converters,

- growing energy costs, leading to regulations requiring more efficient conversion,

stand out, while the more pronounced aspects of the latter include

- digital integrated circuits (ICs) moving towards low-voltage, high-current supply rails, projected to approach 0.8 V and 200 A by 2012,

- widely diverging supply rails within a single system, often including 1.5 V and lower for processors, 3.3 V and 5 V for interface logic, higher voltages for flash memories, and potentially much higher voltages for displays, and

- continuing shrinkage of electronics systems, to the point that the power supply contributes an "application-killing" quantity of size and weight.

# 1.3 MEMS Microfabrication for Power Electronics

# 1.3.1 MEMS Microfabrication Processes

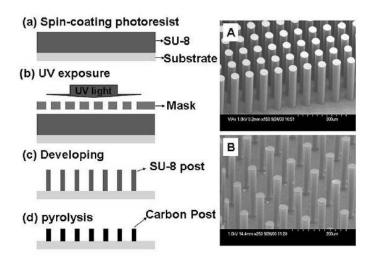

### 1.3.1.1 Thick polymer films

Driven in large part by the electronics packaging industry, photoresists that can be spun into thick layers and patterned with high aspect ratios are under continuous development. Examples include

Shipley SPR20 [41] and Futurrex NR-21 [18] The distinct advantage of photoresists for formation of thick polymer films is the relative ease which with they can be removed. Alternative thick-film materials, such as SU-8 or polyimide, are very difficult to remove.

In addition to photoresists, other polymer materials can be used to create and pattern thick films. Common examples include Microchem's UV-patternable epoxy SU-8 and any of a wide variety of photosensitive polyimides. These materials can enable thicker structures and higher aspect ratios than are generally achievable with photoresist films. [51]

LIGA, a German-language acronym for Lithographie (photolithography), Galvanoformung (electroplating) and Abformung (molding), is a well-known MEMS fabrication process. LIGA relies not only on thick, high-aspect ratio polymer processing – exposure of PMMA photoresist with X-ray radiation – but also on electrodeposition through the resulting PMMA layer. [19]

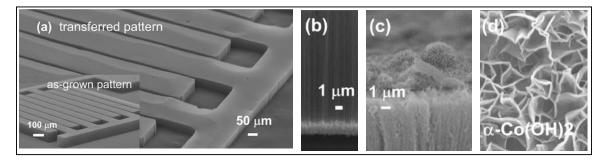

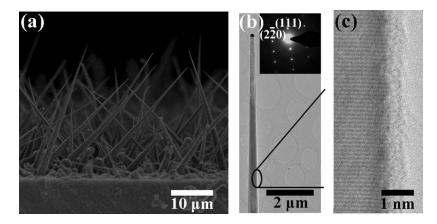

#### 1.3.1.2 Structural electrodeposition

Structures with microscale features can be formed through the electrodeposition of metal, as is done in LIGA. Electrodeposition can be electroless, in which metal deposits spontaneously onto a seed layer from solution, or electrolytic, in which an external source of electricity is connected between the solution and the seed layer to drive the deposition reaction forward. Popular electrodeposited materials include copper, nickel, silver, chromium, and gold, and alloys of these with other metals including iron, cobalt, tin, lead, and zinc.[20]

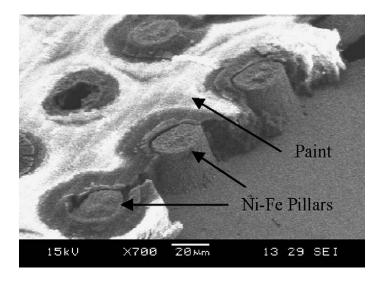

Electrodeposition is typically done with a photoresist plating mold, although other polymers or even silicon can be used as a plating mold. Figure 3 illustrates this process. The partially removed mold was not a photopatterned polymer, but a laser-drilled polymer layer.

#### 1.3.1.3 Sacrificial Release

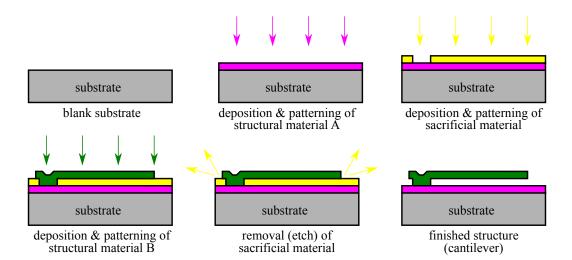

Sacrificial release is a venerable MEMS fabrication processes, used to achieve free-standing structures. The essential process is illustrated in Figure 4. Sacrificial release processes of one form or another are used in virtually all MEMS fabrication processes. From this wide variety of practical applications, a number of generic needs and challenges can be identified. [21]

#### Sacrificial Material Systems

The materials that can be used in a sacrificial release process are subject to certain constraints.

Figure 3: Micromachining Based on Electrodeposition. The pillars are formed by electrodeposition of nickel-iron, and the layer of paint, with laser-drilled holes, serves to dictate the shape of the plated pillars.[55]

Figure 4: Generic sacrificial release process. Layers are sequentially deposited onto a substrate, followed by the removal of selected intervening layers. Typically the selective removal is accomplished by chemically selective etch processes.

Figure 4 suggests the principal ones. First, the structural and sacrificial materials must be compatible in that they can be deposited atop one another. Each deposition process imposes its own thermal budget, handling requirements, and chemical environment that preceding layers may not be compatible with. As well, there can be considerable practical advantage in being able to deposit all materials with the same equipment. For instance, if all three materials in Figure 4 are deposited by the same PECVD system, the entire unreleased structure can be formed from a single run of the PECVD machine. The second major constraint on sacrificial release material systems is that a robust sacrificial etchant, capable of removing the sacrificial material(s) without damaging the structural material(s), must be available. Accordingly, the etchant must be considered as an integral part of the material system.

A large number of material systems have been identified: SiN/Si/KOH, Si/SiOx/HF, and metal/photoresist/acetone

#### Sacrificial Etch Mass Transport

The sacrificial etch step, particularly the removal of the sacrificial material, imposes some fabrication challenges that are not strongly dependent on the material system in use. One of these is the difficulty of transporting chemical reactants to and from the reaction sites. This is alleviated by the inclusion of etch holes throughout the released structure. These essentially enforce a maximum distance that reactants must travel.

Another approach to solving this issue is the use of vapor (gas-phase) etchants. In particular, vapor-phase HF for the sacrificial removal of silicon dioxide is very effective.

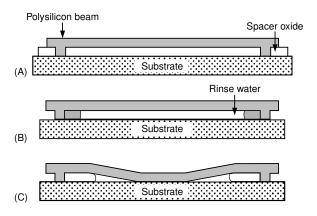

#### Stiction Control

A major difficulty with sacrificial release processes is the phenomenon known as stiction. Stiction, illustrated in Figure 5, is the permanent collapse of the void created by the removal of the sacrificial material. Typically, this collapse is brought on and sustained not by gravity or any bulk forces, but rather by adhesive forces. In the case of wet sacrificial etches, the combination of adhesion between the released structure and whatever liquid remains in the sacrificial void after the etch – generally a rinse solvent – and the surface tension (self-adhesion) of the liquid initiates the collapse. Adhesion between the structure's surfaces perpetuates the collapse.

Several techniques to prevent stiction have been developed. In general, it is possible to alter the

Figure 5: Stiction in sacrificial oxide etch [19]

composition of the liquid through the addition of other, miscible liquids, which then diffuse into the sacrificial void. In this manner, a higher-tension liquid such as water can be largely replaced by a lower-tension solvent such as methanol, to facilitate the subsequent drying step.

The physical behavior of the final rinse liquid can be modified in a number of ways to help avoid stiction. The liquid can be frozen and removed by sublimation; this removes the action of the liquid's surface tension. Alternatively, supercritical drying, where a gas such as CO2 is brought to a supercritical phase and circulated, can be used to remove the remaining solvent without imparting the forces that would be created by evaporation of the liquid.

Another approach to stiction control involves modification of the structural surfaces themselves. So-called "anti-stiction bumps" prevent contact between structural surfaces over a large area. As well, low-adhesion coatings can be applied to the structural surfaces so that any contact that does occur entails less stress. [19]

### 1.3.1.4 CMOS Integration

#### Synergistic Combination

MEMS fabrication techniques generally offer two compelling advantages in terms of commercialization. First, they are often based primarily on batch-oriented processes, not only promising the economies of scale that have defined the dynamics of the CMOS industry, but also allowing a great deal of cost insensitivity across a given device's design space.

Second, MEMS processes are typically highly compatible with silicon wafer substrates practically identical to the ones used in CMOS integrated circuit manufacture. This enables MEMS wafer foundries to take advantage of the well-developed semiconductor capital equipment markets, reducing the scope of the required custom tool development and allowing effective use of the relatively immense body of knowledge and experience that has come from decades of CMOS development and manufacture.

Each of these two advantages stem from the historical development of MEMS as an outgrowth of integrated circuits. They can, in fact, deliver even greater benefits if a MEMS fabrication flow can be merged with CMOS fabrication flow, producing at the end a wafer with fully-integrated CMOS and MEMS structures. In addition to enabling new types of CMOS-MEMS hybrid platforms and allowing interconnect with minimized parasitics, such process integration can also potentially yield enormous cost savings.

Tautologically, the compatibility between CMOS and MEMS fabrication processes depends on both processes. Practically, CMOS foundries do not offer a great array of options to achieve compatibility with MEMS fabrication. This is due not only to the numerous challenges intrinsic in producing modern ICs, but also due to the relatively small size of the market for CMOS-MEMS devices, relative to the market for CMOS-only (*i.e.* normal ICs) devices.

### Post-CMOS MEMS Integration

There are a number of ways in which it is possible to perform the merging of the MEMS and CMOS fabrication flows, but they can be classified according to the chronological ordering of the two flows, engendering the three self-explanatory terms Pre-CMOS, Intra-CMOS, and Post-CMOS integration of MEMS processing. [9]

However, the CMOS fabrication flow makes Post-CMOS integration the most practical. CMOS fabrication imposes very high thermal budgets, with diffusion and oxidation processes that easily approach 1000 C. Many MEMS materials, particularly metal films and polymers, simply cannot tolerate the CMOS thermal budget. As well, planarization requirements for CMOS fabrication, due to lithographic systems that sacrifice depth-of-focus in favor of greater resolution, can also preclude the prior use of substantial micromachining steps.

Correspondingly, in this research, the vision of Post-CMOS integration is pursued. This requires the observation of a thermal budget of approximately 400 C, and the use of processes that would be chemically compatible with typical CMOS passivation materials. Fortunately, this is readily

achievable with the processing presented in this thesis, all of which occurs at less than 250 C, and involves only weak wet etch (*ex.* 1:49 HF:water) treatments.

Most importantly, the targeting of Post-CMOS integration enables the ultimate integration of the presented devices onto finished CMOS wafers, at the wafer level, to produce fully-integrated, single-chip power converters.

#### 1.3.2 Integrated Power Systems

Using the processes presented in the previous section, the implementation of fully-integrated power converters and, more generally, power management systems, has been achieved. The maturity and robustness of these microfabrication processes, as well as proven techniques for fabrication of the components within the power systems, play a central role in their success.

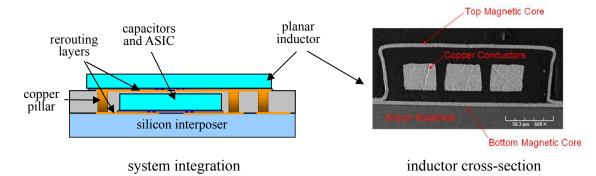

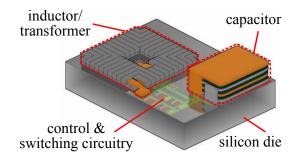

Figure 6: Integrated DC/DC Converter for Wireless Sensor Nodes.[27]

Figure 6 shows one such system, a single-chip DC/DC converter running at 15 MHz, incorporating a 1 to 4  $\mu$ H inductor, 100 nF capacitors, a CMOS circuit fabricated with a 0.35  $\mu$ m process, and achieving an efficiency of over 65 %. Silicon-based polymer and electroplating techniques were used to achieve the full integration of the separately- processed inductor and IC substrates. As well, as suggested by the inductor cross-section in Figure 6, a complex sequence of microfabrication steps was required to fabricate the inductor. [27]

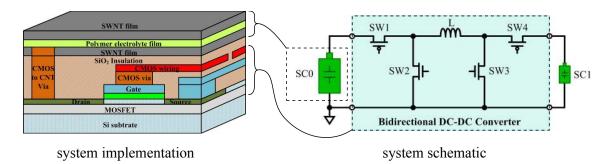

Another example of successful, microfabrication-based power system integration is shown in Figure 7. In [14], a switched-capacitor power converter is integrated with a single-walled carbon nanotube (SWNT)-based supercapacitor to provide comprehensive power support as might

Figure 7: Integrated Power Storage and Conversion System[14]

be needed by a microharvester-powered wireless sensor node. Not only are thick-regime, lowtemperature insulator and electroplating steps used to achieve effective system integration, but a nanofabricated energy storage component – the SWNT supercapacitor – plays a central role in the practical importance of the system.

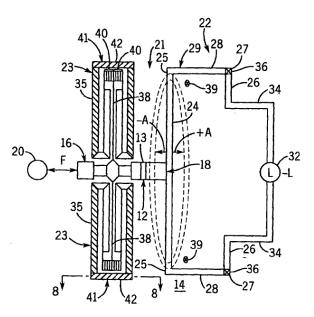

Figure 8: Isolating, all-MEMS Power Converter [25]

Less conventional examples of a fully-integrated power converters are found in [47] and [25]. Each of these patented devices implements DC/DC power conversion in a single microdevice that carries out electrical-to-mechanical and subsequent mechanical-to-electrical conversion. While a pair of co-fabricated, engaged rotary machines are used in [47], a resonant, flexure spring-mounted boss is used in [25]. Both of these applications are based on the extensive use of standard bulk and surface micromachining processes.

#### **1.3.3** Microfabricated Power Components

#### 1.3.3.1 Integrated Passive Electronics Modules

Even in cases where full system integration is not easily reached, microfabrication-based fabrication of individual components and multi-component modules can still deliver great benefit.

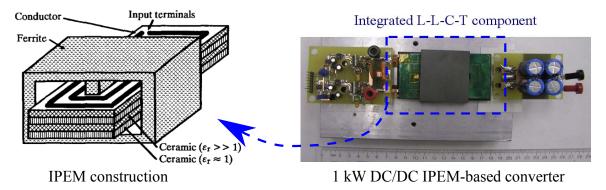

Figure 9: Integrated passive electronics modules (IPEMs) generic construction[73] and application in 1 kW DC/DC converter [36])

The integrated passive electronics module (IPEM) approach to system integration, exemplified in [36], simultaneously creates a number of practical advantages, and is enabled by existing microscale fabrication processes. An IPEM consists of any number of co-fabricated passive components, and is typically fabricated with a low-temperature co-fired ceramic (LTCC) multilayer process. This approach delivers the standard integration benefits of reduced component costs, facilitated system assembly, and improved interconnect parasitics. However, one of its particular advantages is that it implements the grouping of components with similar thermal needs, and the ceramic substrate, with its high thermal conductivity, facilitates the removal of heat.

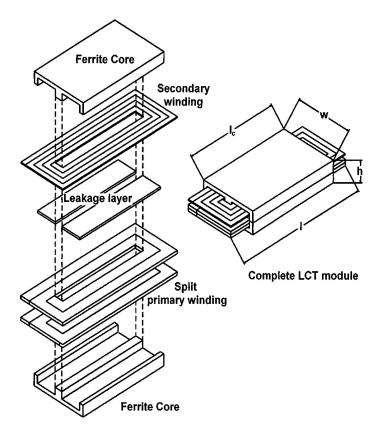

Remarkably as well, the LTCC-based IPEM approach enables the practical deployment of new types of passive networks, which can in turn potentially enable new types of system architectures. One such passive network is the LCT (inductor- capacitor-transformer) module, shown in [32]. This type of module is used in high-efficiency, quasi-resonant power conversion circuits such as LLC and LCC circuits, and can be seen as an enabling technology for these advanced designs.

#### 1.3.3.2 PCB-based Integration

Even well-studied system integration approaches such as printed circuit boards (PCBs) and other printed-circuit interconnect technology can be leveraged in new, power electronics-centric ways.

Figure 10: LCT Module Construction (exploded)[32]

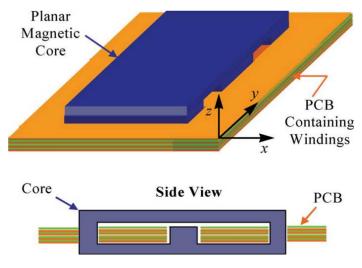

Figure 11: PCB-wound Planar Magnetics[60]

Planar magnetics, illustrated in [60] are now widely used in commercial power converters [61]. In planar magnetics, PCB traces form the coils of magnetic devices such as inductors and transformers, and the magnetic cores are assembled about the PCB coil structures.

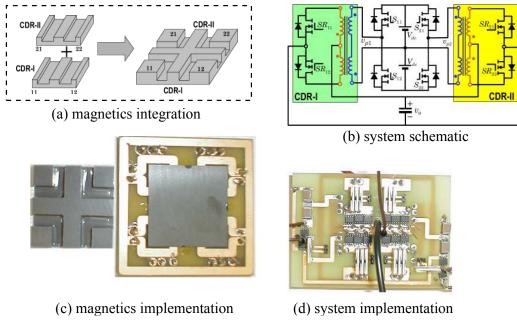

Figure 12: Matrix-Integrated Magnetics [12]

The planar magnetics approach has been extended to create new devices, as well as new circuit topologies, in the matrix-integrated magnetics approach. In this miniaturization-minded research, a regular fabric (matrix) of magnetic structures is envisioned, with PCB coils providing the application-specific configuration of the magnetic circuits.

In the first place, this approach would justify the large-volume production of magnetic cores in the appropriate matrix configurations. This would deliver concomitant economies of scale in the manufacture of the cores, as well as the assembly of the converters. This approach, given a suitable body of knowledge about the corresponding converter circuits, could be scaled, even across fabrication technologies.

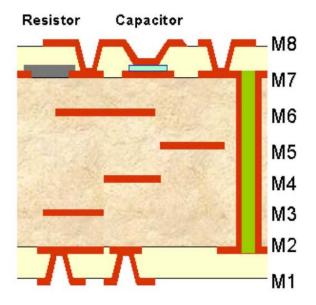

The in-place fabrication of components during PCB manufacture is also a widely followed approach to improved power electronics integration. In [35], shown in Figure 13, an extra sequence of steps is added to the processing of the outer layers of a PCB to add passive components. These passive components are significantly thinner than the PCB's dielectric layers, and this work demonstrated that this can be distinctly advantageous, if a suitable integration process is available.

Figure 13: PCB-embedded Capacitors[35]

The thin capacitors enable the achievement of high capacitance densities, as needed power supply filtering. The thin resistors enable the use of high-conductivity resistive materials, so that lowrange resistors can be produced with laterally compact dimensions. Finally, the large difference in thickness between the passive components and the PCB dielectric facilitates the photopatterning, etching, and plating of the outer copper traces; thicker passives might produce nonplanarities in the outer surfaces, on which patterned copper films must be created.

Figure 14: Comprehensive PCB-Integrated Passives Platform[69]

Figure 14 shows a more comprehensive approach to PCB-embedded passives. In this work, magnetic core materials are provided for, enabling the incorporation of high-density magnetic devices.

## 1.4 Contributions of This Work

The research and development presented in this thesis falls well into line with this process-oriented, bottom-up pursuit of higher-performance, better-integrated power systems.

# 1.4.1 MEMS-based Process for Power Electronics

The microfabrication process of sacrificial multilayer electroplating is further developed in this work, specifically for practical use in power system packaging. This advanced process serves as the basis for the devices produced herein, as well as to establish the great potential of its future applications.

## 1.4.2 Microfabricated Power Components

The primary point of demonstrated impact for the sacrificial multilayer plating process is in the creation of high-performance devices for power electronic applications. A high-density capacitor as well as highly-laminated, high-speed magnetic cores were produces. These two component classes typically furnish not only the majority of the size and weight of power conversion systems, but also the largest integration challenges.

#### 1.4.3 Deployment into Power Converters

The demonstration of these devices in high-efficiency power converters is important not only as an ultimate verification of their functionality, but also as a basis from which more advanced integration methods can be pursued in future work.

# 1.5 About this Thesis

This thesis is organized into six chapters. The relationships between these chapters, as well as significant auxiliary work, is shown in Figure 15. Chapter 1 presents a history of the field, a motivation for the research presented, and related results from other authors.

Figure 15: Conceptual Map of this Thesis. The work detailed in Chapter 3 enabled the concrete developments presented in Chapters 4,5, and 6

Chapter 2 presents the fabrication and characterization of an integrated power inductor. This work is conceptually important, as it shows the viability of a high-efficiency, single-die DC/DC converter based on the same magnetic materials used in later work. As well, it was the vehicle for the development of a substantial body of practical knowledge related to the integration of microfabricated components into power converters.

Chapter 3 presents the chief advances and results in the continued refinement of the sacrificial multilayer plating process. This includes not only an account of the difficulties encountered and the solutions developed accordingly, but also a review of competing approaches and a brief exposition of potential future applications for this promising technology. This topic also encapsulates the development of an advanced robotic multilayer electroplating system, which is discussed more comprehensively in Appendix C.

The initial application of the newly advanced sacrificial multilayer plating process, a highdensity on-silicon capacitor, is presented in Chapter 4. This device proved the effectiveness of the fabrication flow at producing high surface areas. It also establishes the potential for future onchip integration of filter capacitors to complement the integration of inductors, producing a truly self-contained single-chip DC/DC converter. Appendix A provides some supporting mathematical results that are used in the calculations in this chapter, as well as in Chapter 5.

The development, fabrication, and characterization of submicron-laminated magnetic cores, the most substantial application of the sacrificial multilayer plating process, are presented in Chapter 5. The characterization of the cores entailed the development of a complex characterization system, as well as the marshaling of substantial a mathematical framework; this is all covered in Appendix B.

Chapter 6 presents the ultimate step in demonstrating the value of this research: the operation of the submicron-laminated cores in high-frequency SMPSs. The design of the inductors and power supplies, as well as the results constitute this final chapter.

# **CHAPTER II**

# MICROFABRICATED POWER INDUCTORS

This chapter presents the fabrication, characterization, and in-system operation of a microfabricated power inductor. A general background on inductors is presented first, followed by details of the device's design and fabrication. Finally, the device-level characterization and system-level characterization of the device is presented.

# 2.1 Background

# 2.1.1 Inductor Theory

An inductor is one of the fundamental lumped two-terminal electrical components. It generates a voltage v(t) that is proportional to the time derivative of its current i(t) by its inductance *L*:

$$v(t) = L\frac{d}{dt}i(t) \tag{1}$$

This definition covers only behavior at the inductor's terminals, allowing for any conceivable implementation, utilizing any electronic or physical means.

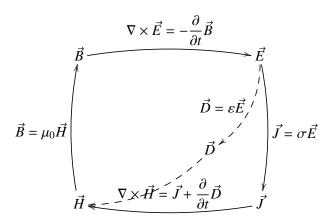

### 2.1.1.1 Electromagnetic Induction

However, in practice, inductors are typically implemented based solely on electromagnetic transduction. The electromagnetic transduction pathway that creates inductive behavior is the same in all such inductors, and is described precisely by Maxwell's equations. An electrical current  $\vec{J}$  gives rise to a magnetic field according to a spatially-distributed magnetic field  $\vec{H}$ :

$$\vec{\nabla} \times \vec{H} = \vec{J} \tag{2}$$

This magnetic field  $\vec{H}$  drives a magnetic flux  $\vec{B}$  according to the constitutive relation

$$\vec{B} = \mu \vec{H} \tag{3}$$

and the magnetic flux  $\vec{B}$ , as it changes over time, creates an electric field  $\vec{E}$  according to Faraday's Law

$$\vec{\nabla} \times \vec{E} = -\frac{\partial B}{\partial t} \tag{4}$$

This electric field, integrated between two points in space

$$\Delta V = \int_{A}^{B} \vec{E} \cdot d\vec{s}$$

<sup>(5)</sup>

creates a potential difference, or voltage, V.

For purposes of modeling inductive behavior, the preceding development implies solving for the magnetic and electric field distributions at each instant in time. While this is the approach used in numerical simulation programs such as HFSS (http://www.ansys.com/hfss), it is unwieldy for manual analysis and design guidance. A useful approximation can be reached by taking into account the fact that, in many cases where inductance is a principal concern, the conductor forms a virtually closed path. In fact, the conductor typically makes many passes around approximately the same closed path; each pass is referred to as a turn, and the collection of turns is referred to as a coil [66].

Revisiting Equation 4 with this closed loop in mind, Stokes' Law can be applied to yield

$$\oint_{P_1} \vec{E} \cdot d\vec{s} = -\frac{\partial}{\partial t} \int_A \vec{B} \cdot d\vec{A}$$

(6)

where the contour integral is evaluated along the path of a single turn  $P_1$ , and the area integral is evaluated over the path's interior area A. Meanwhile, the terminal voltage v, as given in Equation 5, evaluated along the conductor's total path  $P_N$  (*i.e.*  $N_t$  turns), is given by

$$v = \oint_{P_N} \vec{E} \cdot d\vec{s} \tag{7}$$

$$= N_t \oint_{P_1} \vec{E} \cdot d\vec{s} \tag{8}$$

(9)

Capturing the right hand side of Equation 6 in a new quantity  $\Phi$ , known as the total flux,

$$\Phi = \int_{A} \vec{B} \cdot d\vec{A} \tag{10}$$

the structure's inductance is modeled by the relation

$$v = N_t \oint_{P_1} \vec{E} \cdot d\vec{P} \tag{11}$$

$$= -N_t \frac{\partial \Phi}{\partial t} \tag{12}$$

This transduction pathway acts any place where current is flowing, but a variety of analytical constructions are used to model inductance in different cases.

### 2.1.1.2 Self Inductance of a Straight Conductor

An isolated conductor will develop a voltage fluctuation due to changes in the current in carries; thus, it is said to exhibit self inductance. In this case, the magnetic field responsible for the inductance is located in the space immediately surrounding the wire. By Ampere's Law, the intensity of the magnetic field is symmetric about the conductor's axis, and varies inversely with distance from the conductor. In the case of a straight, cylindrical the magnetic field developed has a simple structure. This allows systematic evaluation of the conductor's self-inductance. For a cylindrical conductor of length l and radius r, the self-inductance L is [23]:

$$L = 0.002l \left[ \ln \left( \frac{2l}{r} \right) - 1 + \frac{r}{l} + \frac{\mu_R}{4} \right]$$

(13)

$$\approx 0.002l \left[ \ln \left( \frac{2l}{r} \right) - 0.75 \right], \qquad l >> r \text{ and } \mu_R = 1$$

(14)

, where  $\mu_R$  is the relative magnetic permeability, L is in nanohenries, l and r are in centimeters.

For conductors with rectangular cross section, calculation of self-inductance is more complicated, but closed-form expressions are still available. For a straight conductor with rectangular cross section described by with a and height b, the self-inductance L is [23]:

$$L = 0.002l \left[ \ln \left( \frac{2l}{a+b} \right) + 0.50049 + \frac{a+b}{3l} \right]$$

(15)

$$\approx 0.002l \left[ \ln \left( \frac{2l}{a+b} \right) + 0.50049 + \frac{a+b}{3l} \right], \qquad l >> r \text{ and } \mu_R = 1$$

(16)

where *L* is in nanohenries and *l*, *a*, and *b* are in centimeters.

## 2.1.1.3 Mutual Inductance of Parallel Conductors

Similarly, if two conductors are located relatively close to one another, the magnetic field generated by one conductor's current can affect both conductors. Specifically, a change in the current of either

conductor will generate a voltage fluctuation *in both conductors*. In this case, the mathematical description of the inductive behavior is a generalized version of Equation 1:

$$\begin{bmatrix} v_1(t) \\ v_2(t) \end{bmatrix} = \begin{bmatrix} L_1 & L_m \\ L_m & L_2 \end{bmatrix} \begin{bmatrix} \frac{d}{dt}i_1(t) \\ \frac{d}{dt}i_2(t) \end{bmatrix}$$

(17)

where  $i_1$  and  $v_1$  are the current and voltage in one conductor,  $i_2$  and  $v_2$  are the current and voltage in the other conductor,  $L_1$  and  $L_2$  are the self-inductances of each conductor, and  $L_m$  is said to be the the mutual inductance between the conductors.

For two parallel inductors, when  $\mu_R = 1$ , the mutual inductance M, in nanohenries, is given by

$$M = \pm 2l \left[ \ln \left( \frac{l}{D_G} + \sqrt{1 + \left( \frac{l}{D_G} \right)^2} \right) - \sqrt{1 + \left( \frac{D_G}{l} \right)^2} + \frac{D_G}{l} \right]$$

(18)

where l is the length of the conductors in and  $D_G$  is the geometric mean distance between the conductors, in cm. The sign of the mutual inductance is positive if the two conductors' currents are flowing in the same direction, and negative otherwise.  $D_G$  is approximately equal to the spacing between conductor centers, but also incorporates geometric effects in cases where the conductors' widths occupy a significant portion of the distance between their centers [23].

The mutual inductance expression in Equation 18 and the self-inductance expression in Equation 15 can be combined to accurately estimate the inductance of a planar spiral inductor. This is accomplished by dividing the inductor up into a number of segments and summing, across all segments and all combinations of two segments, the self-inductance and mutual inductance, respectively.

### 2.1.1.4 Magnetic Circuits

The previous discussion applies to cases where conductors are surrounded by free space (*i.e.*  $\mu_R$  = 1), and carefully accounts for geometric effects. However, in cases where the conductors are interlinked with high-permeability magnetic material, there is another approach to modeling of magnetic devices that allows straightforward analysis.

In this approach, illustrated in Figure 16, the magnetic fields are assumed to be confined within the magnetic material, forming a mostly-closed path, known as a magnetic circuit. The geometry of the magnetic material defines the geometry of the magnetic circuit, and the assumptions thus

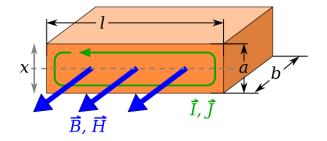

Figure 16: Generic magnetic circuit. A coil with N turns and current *i* creates a flux  $\Phi$  that is distributed across the circuit's cross section  $A_C$ . [66]

enabled create a precise mapping of the magnetic system to an equivalent electrical circuit. Voltage is mapped to magnetmotive force, MMF, which can arise either from a current *i* in a winding with *N* turns (MMF = Ni) or from a magnetic field within the magnetic circuit ( $MMF = -\int H \cdot dl$ ). Ampere's Law,

$$\int H \cdot dl = i \tag{19}$$

then transforms into Kirchoff's Voltage Law ( $\sum V = 0$  for any closed loop within the circuit). Likewise, Gauss's Law ( $\int_V B \cdot dA = 0$ ) is transformed into Kirchoff's Current Law ( $\sum i = 0$  at any node in the circuit). The articulated set of linear relationships between dynamic quantites such as current, flux, field intensity, and voltage are merged into a single quantity, reluctance ( $\Re$  in Figure 16, which acts analagously to resistance:

$$\Re = \frac{l}{A_C \mu_0 \mu_R} \tag{20}$$

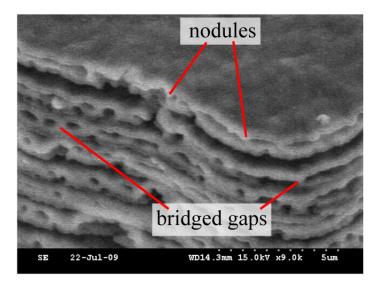

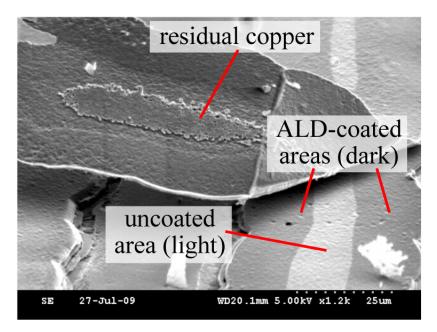

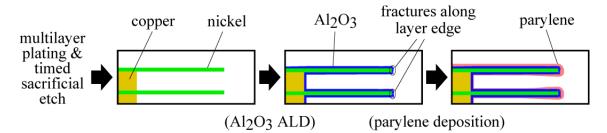

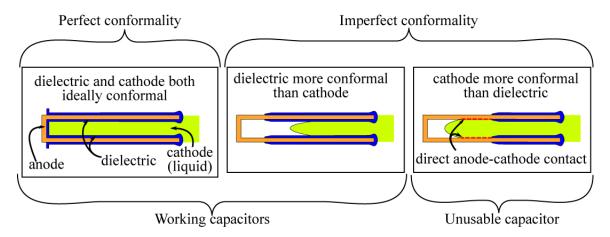

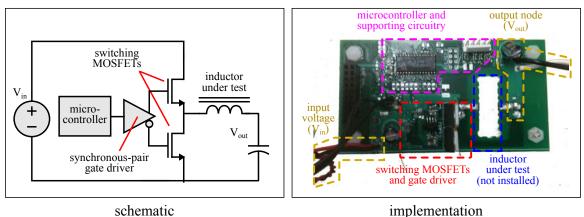

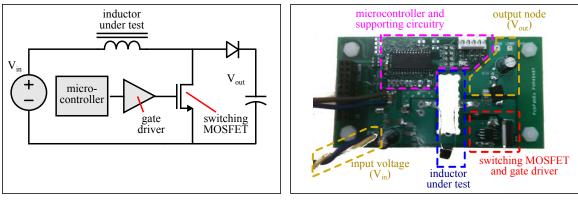

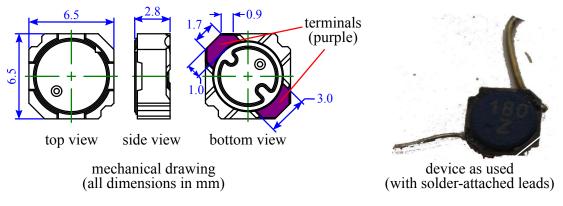

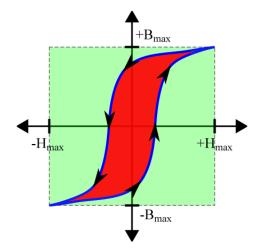

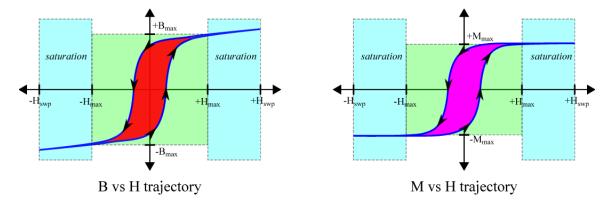

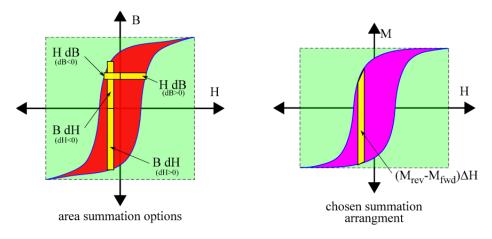

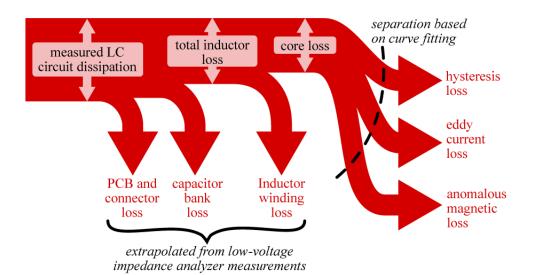

where l is the path length and  $A_C$  is the cross-section area. With these transformations applied, relatively complex magnetic circuit structures may be analyzed using simple, familiar circuit analysis. [66].