### NEAR-MEMORY PRIMITIVE SUPPORT AND INFRASTRUCTURE FOR SPARSE ALGORITHM

A Dissertation Presented to The Academic Faculty

By

Kartikay Garg

In Partial Fulfillment of the Requirements for the Degree Masters of Science in the School of Electrical and Computer Engineering

Georgia Institute of Technology

May 2017

Copyright © Kartikay Garg 2017

### NEAR-MEMORY PRIMITIVE SUPPORT AND INFRASTRUCTURE FOR SPARSE ALGORITHM

Approved by:

Dr. Sudhakar Yalamanchili, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Jeffrey Young, Co-advisor School of Computer Science *Georgia Institute of Technology*

Dr. Tushar Krishna School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Richard Vuduc School of Computational Science and Engineering *Georgia Institute of Technology*

Date Approved: April 28, 2017

#### ACKNOWLEDGEMENTS

I wish to express my gratitude to my advisor Dr. Sudhakar Yalamanchili, for his support and motivation through the course of my thesis. His guidance was invaluable to my research. I would also like to express my utmost respect for my co-advisor, Dr. Jeffrey Young. His unwavering faith in my capabilities and potential helped me make great strides in my work and beyond. I look up to him immensely. He patiently answered all my queries and provided extremely valuable feedback.

I am also very grateful to Piyush Sao, for providing me with his invaluable time and assistance. His efforts to guide me through his base code, greatly assisted me to develop critical components for my work.

I am greatly indebted to Dr. Tushar Krishna, who not only taught me my Computer Architecture course, but also provided me numerous opportunities to expand my knowledge and work on research projects. His support has been an invaluable component of my grad life.

I would also like to thank my fellow lab mates, Burhan Mudassar, Ramyad Hadidi, Blaise Tine, Chad Kersey, and Karthik Rao for helping me out greatly during the course of my program. They were always welcoming and helped me a great deal through different aspects of my graduate studies.

I thank the committee members for their precious time and consent to serve on my committee. I thank them for their insightful comments.

Finally, a special thanks to my family for their moral support and encouragement. They are the pillar of my strength. I thank my parents and my sisters, for their loving support.

## TABLE OF CONTENTS

| Acknow    | vledgments                                         | v  |

|-----------|----------------------------------------------------|----|

| List of Z | <b>Tables</b>                                      | ix |

| List of 1 | Figures                                            | x  |

| Chapte    | r 1: Introduction                                  | 1  |

| 1.1       | Motivation                                         | 1  |

| 1.2       | Introduction to SUPERLU                            | 4  |

| 1.3       | Introduction to 3D-stacked memory architectures    | 6  |

|           | 1.3.1 Hybrid Memory Cube Architecture              | 7  |

| Chapte    | r 2: Background Study 1                            | 0  |

| 2.1       | Related Work                                       | 0  |

|           | 2.1.1 Algorithmic Optimization of SuperLU          | 0  |

|           | 2.1.2 Hardware Approaches for Data Movement        | 3  |

| Chapte    | r 3: Implementing the Target Application for NDP 1 | 5  |

| 3.1       | SUPERLU with HALO 1                                | 5  |

|           | 3.1.1 OpenCL SUPERLU Implementation                | 6  |

| 3.2       | BLAS libraries                                     | 20 |

|        | 3.2.1 clBLAS                                                     | 20 |

|--------|------------------------------------------------------------------|----|

|        | 3.2.2 OpenBLAS                                                   | 21 |

| Chapte | r 4: Evaluating Memory Behavior With Memory Traces               | 22 |

| 4.1    | Hardware platform                                                | 22 |

| 4.2    | PIN tool                                                         | 23 |

|        | 4.2.1 Memory Trace Pintool Filter                                | 25 |

|        | 4.2.2 Custom Pintool Filters                                     | 25 |

| 4.3    | Limitations                                                      | 27 |

|        | 4.3.1 Extrapolations for memory trace for representing GPU trace | 29 |

| Chapte | r 5: Evaluation Model and Hardware Infrastructure                | 31 |

| 5.1    | Evaluation Platform                                              | 32 |

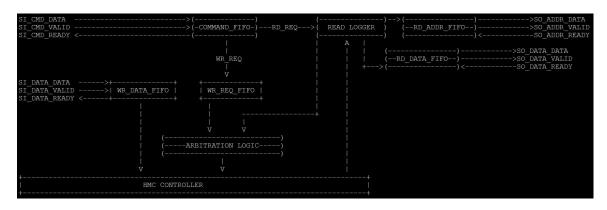

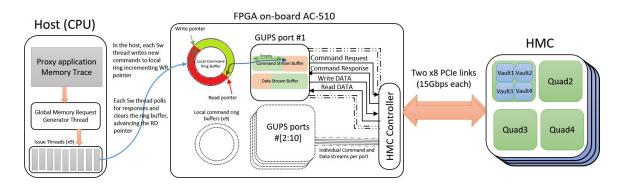

|        | 5.1.1 PICO stream framework                                      | 33 |

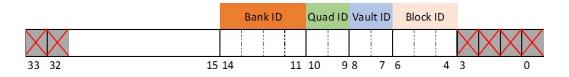

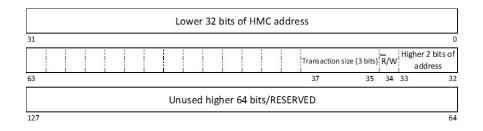

| 5.2    | HMC addressing                                                   | 34 |

| 5.3    | GUPS framework                                                   | 35 |

| 5.4    | Measurements and metric instrumentation                          | 38 |

| 5.5    | Operations supported                                             | 39 |

| Chapte | r 6: Experiments and Results                                     | 41 |

| 6.1    | Dense SuperLU proxy measurements                                 | 41 |

| 6.2    | Memory trace experiments                                         | 45 |

|        | 6.2.1 Serial issue of commands                                   | 46 |

|        | 6.2.2 Parallel issue of commands                                 | 57 |

| Chapter 7: Conclusions | 62 |

|------------------------|----|

| Chapter 8: Future Work | 64 |

| References             | 67 |

## LIST OF TABLES

| 6.1 | Profiling code phase timing contributions on GPU                     | 42 |

|-----|----------------------------------------------------------------------|----|

| 6.2 | Profiling code phase timing contributions on CPU (OpenCL accelerator |    |

|     | kernel)                                                              | 42 |

## LIST OF FIGURES

| 1.1 | Scope of Work                                       |

|-----|-----------------------------------------------------|

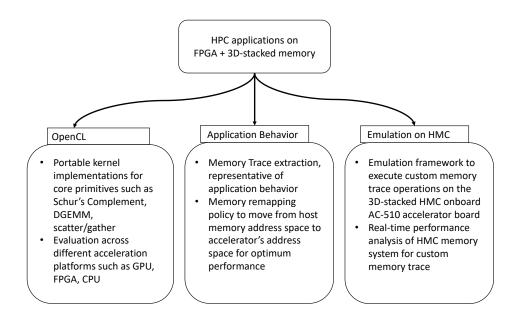

| 1.2 | Thesis Contributions                                |

| 1.3 | 3D-stacked structure                                |

| 1.4 | Memory organization in Hybrid Memory Cube (HMC)     |

| 1.5 | CPU HMC link                                        |

| 2.1 | Asynchronous data transfer and compute time sharing |

| 2.2 | HALO elimination tree                               |

| 2.3 | DGEMM phase in HALO                                 |

| 3.1 | Schur Complement Update Overview                    |

| 4.1 | PIN tool                                            |

| 4.2 | Proxy target disassembly                            |

| 4.3 | Custom PIN tool                                     |

| 4.4 | Sample Memory Trace                                 |

| 5.1 | Pico framework software stack                       |

| 5.2 | Internal architecture of Ac-510 board               |

| 5.3 | Pico stream framework                               |

| 5.4  | HMC addressing scheme                                                                                                     | 34 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

| 5.5  | Algorithm to measure HMC performance                                                                                      | 37 |

| 5.6  | GUPS statistics                                                                                                           | 39 |

| 5.7  | 128 bit command packet                                                                                                    | 40 |

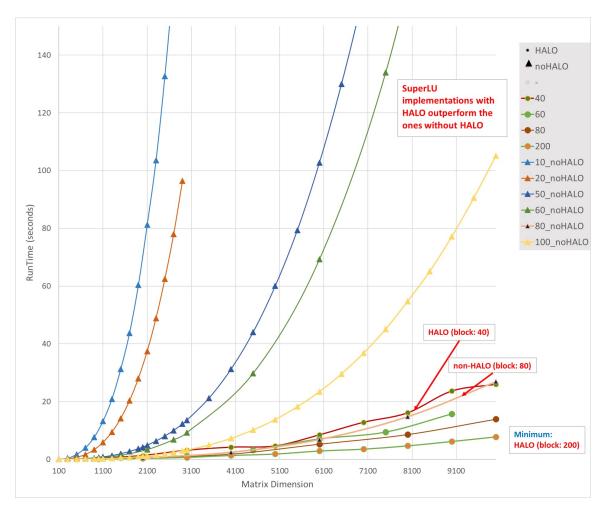

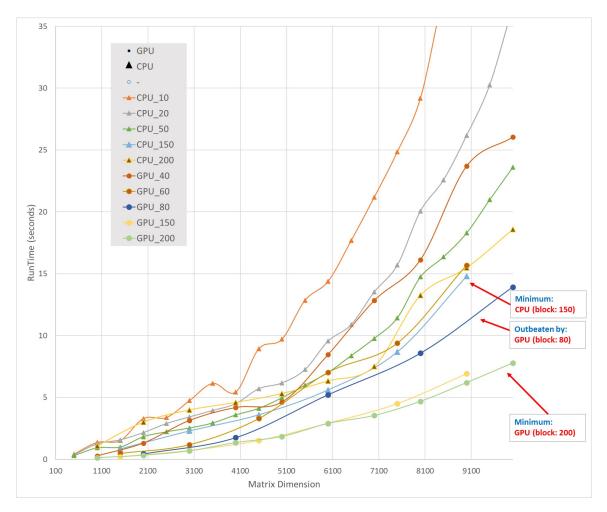

| 6.1  | Performance comparison of HALO optimization for SuperLU on GPU                                                            | 44 |

| 6.2  | Performance comparison of HALO on different platforms                                                                     | 45 |

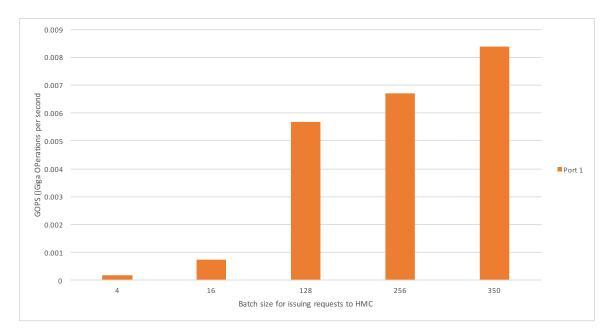

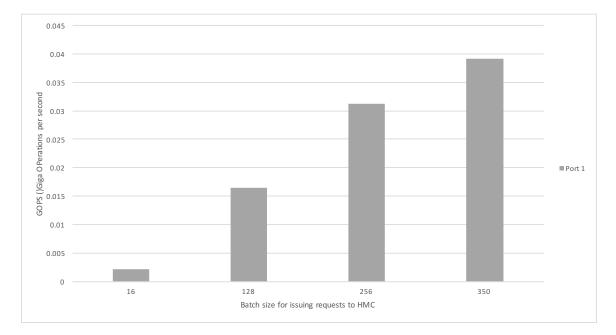

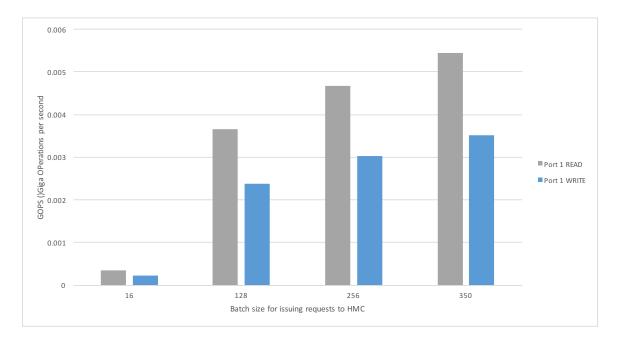

| 6.3  | Per port GOPS as a function of Batch Size (READ-only)                                                                     | 47 |

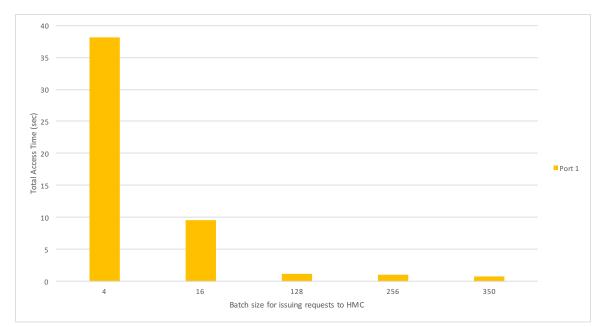

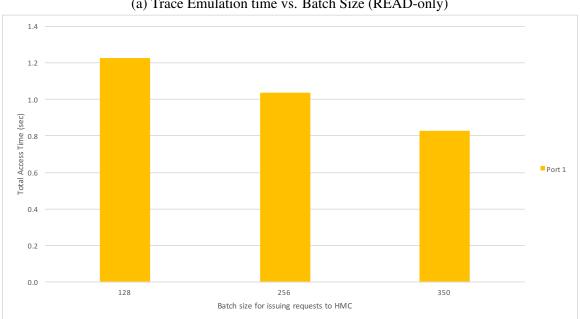

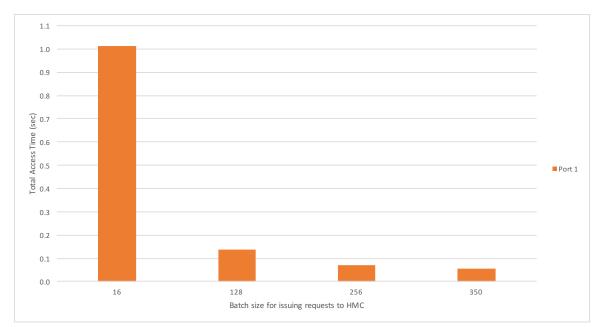

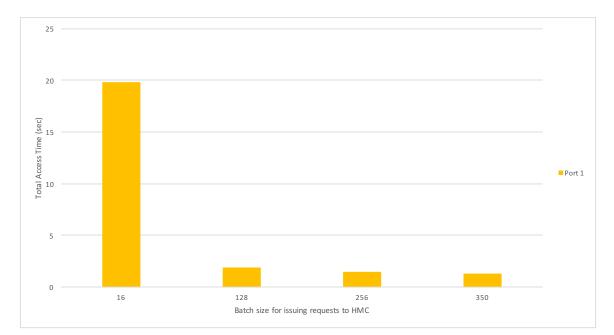

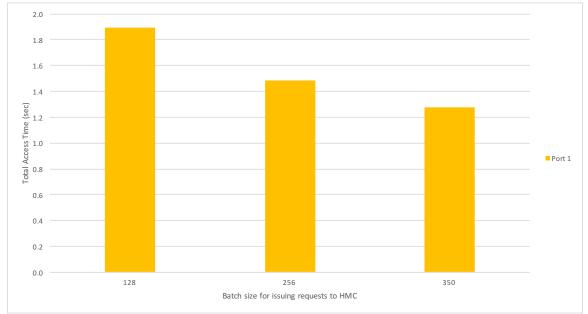

| 6.4  | Cumulative time to emulate memory trace on the HMC as a function of Batch Size (READ-only)                                | 48 |

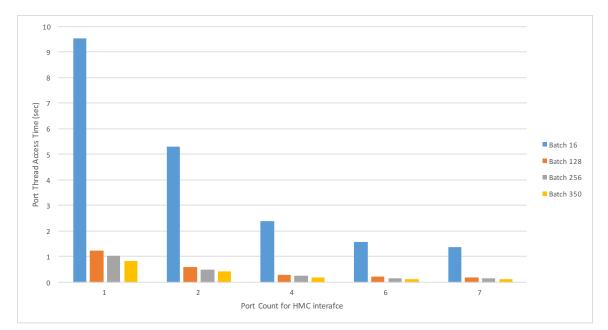

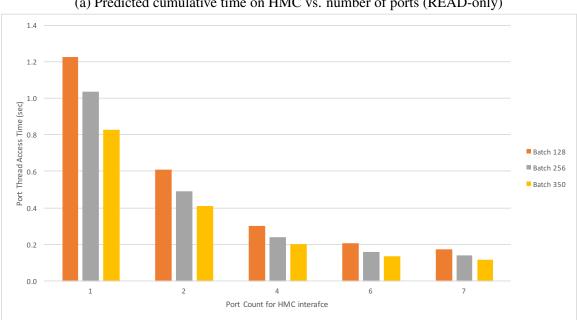

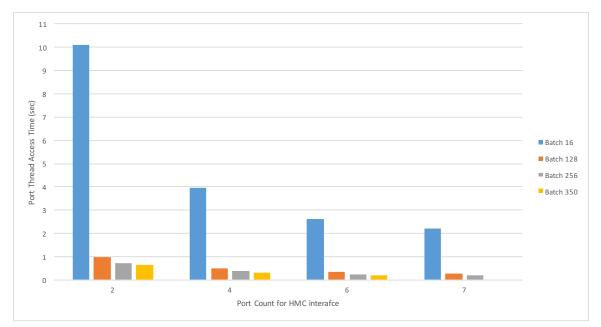

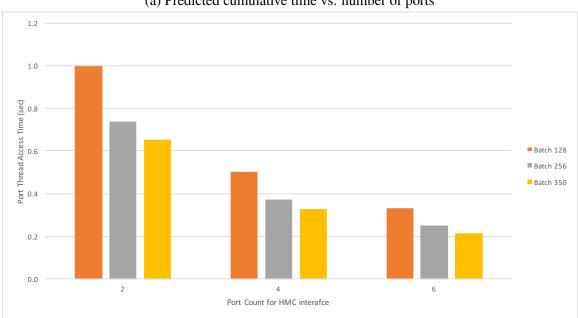

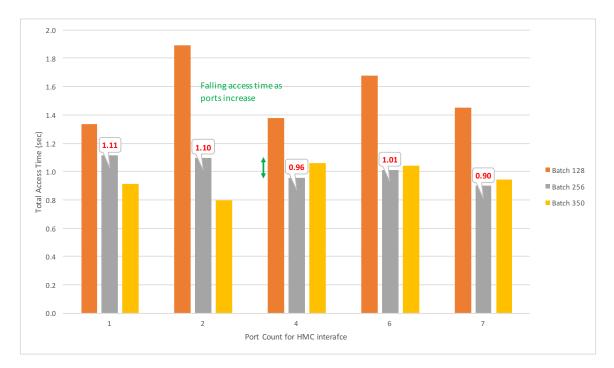

| 6.5  | Predicted cumulative time to service memory requests on the HMC as a function of number of ports (READ-only)              | 49 |

| 6.6  | Per port GOPS as a function of Batch Size (WRITE-only)                                                                    | 51 |

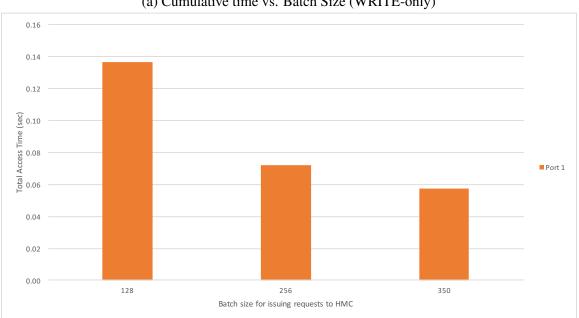

| 6.7  | Cumulative time to service memory requests on the HMC as a function of Batch Size (WRITE-only)                            | 52 |

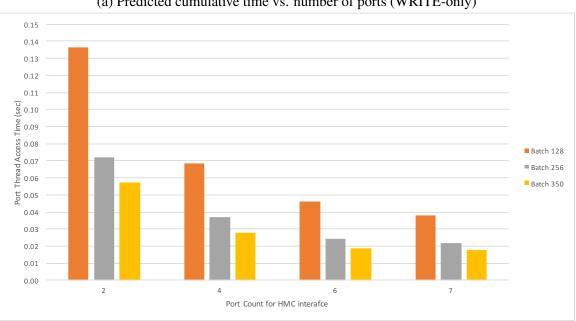

| 6.8  | Predicted cumulative time to service memory requests on the HMC as a function of number of ports (WRITE-only)             | 53 |

| 6.9  | Per port GOPS as a function of Batch Size                                                                                 | 54 |

| 6.10 | Cumulative time to service all memory requests on the HMC as a function of Batch Size                                     | 55 |

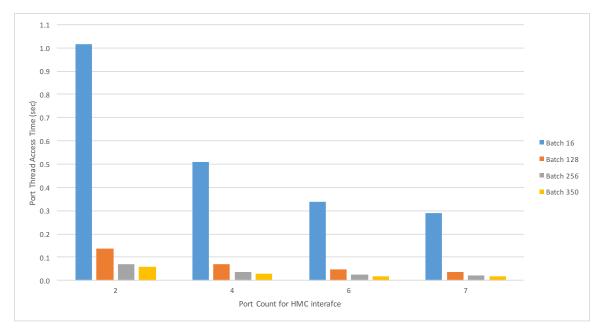

| 6.11 | Predicted cumulative time to service all memory requests on the HMC as a function of number of ports                      | 56 |

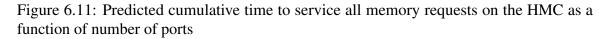

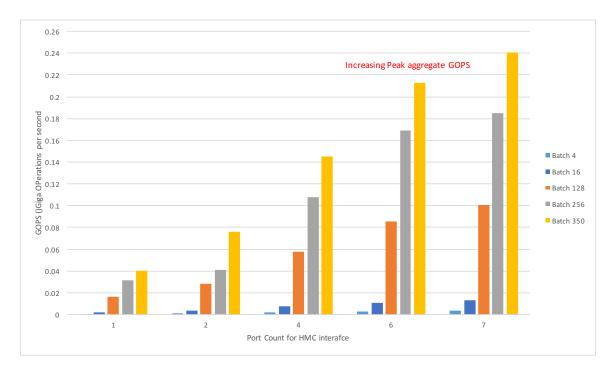

| 6.12 | Aggregate GOPS as a function of port count and batch size (READ-only) .                                                   | 57 |

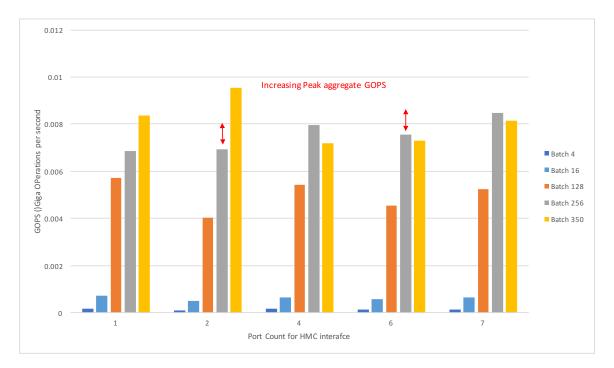

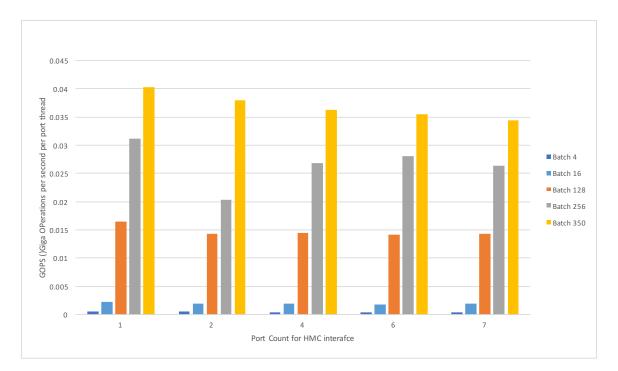

| 6.13 | Per port GOPS as a function of batch size and port count (READ-only)                                                      | 58 |

| 6.14 | Cumulative time to service requests from the trace file on the HMC as a function of port count and batch size (READ-only) | 59 |

| 6.15 | Aggregate GOPS as a function of port count and batch size (WRITE-only) .                                                  | 60 |

6.16 Per port GOPS as a function of batch size and port count (WRITE-only) . . 61

#### SUMMARY

Current trends in multi-core processors and heterogeneous architectures have aimed at improving and performance in terms of raw GFLOPS/sec . This has had fundamental implications on interaction between compute cores and the memory system. Particularly for the HPC (High Performance Computing) community, the conventional DRAM memory subsystem poses a major bottleneck in achieving peak acceleration speedups due to bandwidth and fetch latency limitations. Developers invest time and resources to select and design the optimal offload accelerators to avoid paying these latencies directly, and they couple this hardware design with algorithms to maximize compute utilization while hiding the maximum memory latencies [1].

This thesis introduces an approach to solving the problem of memory latency performance penalties with traditional accelerators. By introducing simple near-data-processing (NDP) accelerators for primitives such as SpMV (Sparse Matrix Multiplication of Vectors) and DGEMM (Double Precision Dense Matrix Multiplication) kernels, applications can achieve a considerable performance boost. NDP can be combined with new 3D-stacked architectures to provide high internal bandwidth and data parallelism. Additionally, the vertical TSV (Through Silicon Via) links in 3D-stacked memories can help reduce average access times for memory requests and accelerate atomic-type operations like Read-Modify-Write.

We evaluate these technologies using a common HPC algorithm, "*LU* decomposition for large order, sparse matrices". This algorithm is included in one of the most commonly used solvers for the HPC community, SUPERLU [2], and has been accelerated on GPU and Xeon Phi. We take the existing state of the art solver implementations of the SUPERLU suite as a baseline implementation to study and analyze memory access patterns with DRAM and stacked DRAM and to make meaningful inferences about the opportunities for acceleration. The work includes a preliminary analysis of extensions to the SUPERLU algorithm like HALO (Highly Asynchronous Lazy Offload) [1] on the CPU and GPU with a near-term path to Field Programmable Gate Array (FPGA) accelerator platforms as well. We study the effect of block and grid size decisions and other optimization parameters on the performance of the application. Finally choosing a baseline implementation, we discuss the techniques to extract a memory trace, representative of an accelerated, bulk synchronous parallel (BSP) application behavior. This includes exploration of binary instrumentation techniques and simulation infrastructures as potential candidates.

Using the Pico Computing FPGA board with an on-board interfaced HMC (Hybrid Memory Cube) chip, we build upon the primitive framework provided by the vendor for application performance estimation and studying memory subsystem metrics. This enables us to study the behavior of the HMC for any given memory access pattern/trace. We study the effect of varying the command issue queue size and the number of contending ports (hardware queues) on the access latency and available peak bandwidth. Experiments include the effect of queuing parallel memory requests in a similar fashion to GPUs across multiple requesting ports contending for a single access link to the HMC. This is compared to an in-order issue strategy across multiple requesting ports. These experiments help us decide an optimum batch size for the target application on the hypothetical custom offload HMC accelerator.

From our experiments, the optimum batch size is also dependent upon the number of active ports contending for access to the HMC. We demonstrate that the performance of the HALO *LU* decomposition kernel is platform dependent and that block size should match the throughput of the CPU, GPU, or FPGA accelerator. We conclude by saying that a strong correlation exits between the command FIFO depth in the HMC hardware and request batch size in the kernel on host and that future algorithm design should take these factors in to account.

# CHAPTER 1 INTRODUCTION

#### 1.1 Motivation

Large scientific codes, such as simulations of experimental fusion systems like NIMROD [3], rely in part on solving large systems of linear equations and solver libraries like Lawrence Berkeley's SUPERLU library [2]. When these real world applications are modeled as HPC problems, they tend to be represented as large sparse matrix based calculations, and a major chunk of HPC applications use sparse kernels like Sparse Matrix-Vector multiplication (SpMV) as part of their core simulation kernels. These simulation kernels can thus be accelerated by linear algebra operations, such as *LU* decomposition, a computational technique that is widely incorporated in the aforementioned SUPERLU library. Accelerating HPC compute primitives such as SpMV or *LU* decomposition can directly lead to a performance boost for the applications employing them, including more than 15 well-known DoE scientific codes. Previous approaches to accelerate these types of primitives, such as those in [4, 1], map these computations onto distributed and accelerated systems like large CPU or GPU-based clusters. However, these systems are ultimately limited by the slowest component, which has recently been the memory subsystem.

Secondly, with the end of Dennard Scaling, HPC compute clusters face a tremendous fundamental problem of thermal budgeting. For data-intensive applications with limited cache locality, the data transfer cost between the memory and the compute core constitutes a major chunk of the energy expenses. Thus, energy constraint considerations from the perspective of data movement need to be given utmost priority. One of the best ways to optimize energy usage for data intensive applications is to place processing as close as possible to the data in main memory [5]. Advances in 3D integration, specifically with

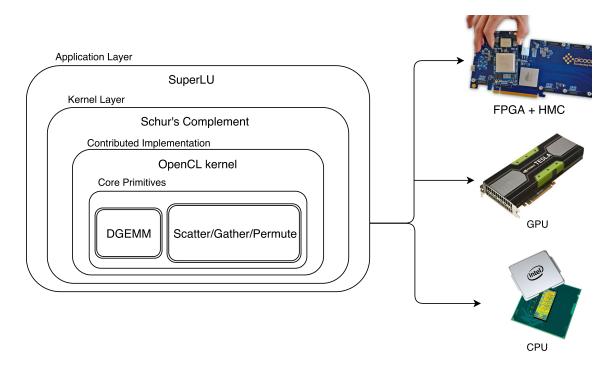

Figure 1.1: Scope of Work

High-Bandwidth Memory (High Bandwidth Memory (HBM)) and Hybrid Memory Cube (HMC), provide an opportunity to implement near-data processing (NDP) and processing in memory (PIM) without the technology problems that similar efforts had in the past.

These NDP and PIM architectures can reduce latency penalties of deep caches but can also offer extensive data level parallelism opportunities. This directly translates to reduced memory access latency and higher internal bandwidth for applications. This reduced latency helps support faster context switches and in the case of PIMs, open up opportunities for high-bandwidth Single Instruction Multiple Thread (SIMT) and Single Instruction Multiple Data (SIMD) architecture accelerator designs that can sit on the logic layer beneath the DRAM stacks.

At the same time, Field Programmable Gate Arrays (FPGAs) combined with 3D memories provide a power efficient platform for NDP designs due to their customization capabilities for specific applications. Additionally, new high-level synthesis techniques for programming FPGAs using OpenCL have introduced new avenues for accelerating HPC applications on re-configurable fabric. Together, 3D stacked memories and FPGA fabrics can potentially enable developers to program a customized yet high-performance algorithm that uses less power than an equivalent GPU implementation.

Following the compelling reasons stated above, this work will look at such HPC primitives that can better support sparse algorithms (specifically those included in the SUPERLU package) with a new class of high-performance, 3D-stacked memories and also help to design and implement infrastructure to use algorithm components on new FPGA-based systems with 3D-stacked memories.

**Thesis Statement:** Reevaluating core primitives such as DGEMM, SCATTER, and GATHER for 3D-stacked PIM architectures that incorporate re-configurable fabrics can deliver multi-fold performance improvements for SUPERLU and other sparse algorithms.

Figure 1.1 visualizes the scope of our work and Figure 1.2 details the thesis contributions. This work analyzes the existing *LU* decomposition methods in SUPERLU and the recently proposed state of the art extensions for reducing data movement [4]. We complement our proposal with an analysis of dense matrices of large dimensionality to estimate the potential benefits of accelerating computation on the typical sparse matrices that are computed with SUPERLU. The results are bench-marked against the performance of the same SUPERLU primitives on GPU, which is the currently most widely adopted platforms for hardware acceleration of similar HPC workloads

Figure 1.2: Thesis Contributions

#### **1.2 Introduction to SUPERLU**

SUPERLU is a general purpose library which has implementations of solvers for efficiently handling large sets of linear equations of the form AX = B [6]. Non-linear systems tend to be expressed in form of a sparse matrix of high dimension value ranges. This calls for highly specialized direct solver algorithmic implementations to avoid redundant or unnecessary computation. The SUPERLU library is employed in a variety of computational science and engineering applications.

The library implementations offers single and double precision implementations. The properties of the matrices which act as raw input data structures for such libraries, have a major influence on the system call implementation. The rank, symmetric nature, fractal representations, etc. have a direct effect on the technique adopted. These different input requirements have led to optimized implementations of the functionality in various flavors such as sequential, parallel and distributed.

SUPERLU helps to solve a given sparse matrix A with LU decomposition, which factors

it to a product format represented as A = L.U, where L is a unit lower triangular matrix and U is an upper triangular matrix. This problem (sometimes referred to as sparse LU) is usually the most expensive step computationally, in a sparse direct solver like SUPERLU. It typically has a large memory footprint, thereby benefiting from the use of a distributed memory system. Given the increased utilization of some form of GPU-like acceleration for such systems, we need an efficient way to exploit all forms of available parallelism, whether in distributed memory or shared memory. This is the prime motivation for selecting "sparse LU decomposition" as the target application.

With this in mind, we aim at matching the available high degree of parallelism in the HMC with the respective flavor of the SUPERLU library to leverage maximum benefit. For this reason, we pick the SUPERLU\_DIST package which has a high degree of parallel calls to map fractals of the matrix for partial solving to independent distributed clusters, many of which have accelerators like GPUs.

This implementation provides good motivation for an optimized offload accelerator in the HMC logic layer for data parallel independent HPC primitives similar to those scheduled on GPU SIMD lanes. An improvement in the primitive's memory request access latency and internal bandwidth owing to the HMC's 3D-stacked architecture could translate to direct boost in performance metrics for application run time. Since we cannot currently test acceleration in the HMC stack we instead pursue NDP implementations with FPGA for this work.

Stacked memory bandwidth and latency benefits can be complemented by the reduction in the number of multiple local copies needed to be created in accelerator global memories such as those of GPU clusters. For GPUs to achieve peak memory access performance, each independent workgroup/thread-block needs to be assigned local memory copies for asynchronized accesses by threads within the group/block. Later, different copies need to be merged in a synchronizing code section to create a contiguous copy (as in the case of array representations) or one big block of merged data elements stored in a sparse matrix format. This can be handled much more elegantly in an NDP or PIM HMC implementation. Independent data fractals of the same sparse block representation can potentially be mapped to independent compute entities on the logic layer by carefully mapping the data store format in the HMC. This can be controlled by adjusting the granularity of assignment of banks, vaults or quads to independent data fractals. This can help bypass the need for multiple copies of the data blocks. This is because before finally shipping off the result in a sparsely formatted data to the host, a simple address stream for accesses to independent banks/vaults/quads can be created in a reorder buffer which delivers the desired data blocks in the respective order to the host. This may potentially help to overcome data copying overheads.

#### **1.3 Introduction to 3D-stacked memory architectures**

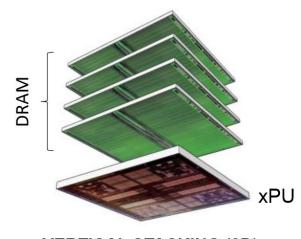

With advancements in packaging technology, we are now able to integrate multiple DRAM dies in a three dimensional structure. This architecture offers a high internal link bandwidth between stacks, and offer low energy consumption benefits. The energy savings stem mainly from the opportunity to be able to move computation much closer to the memory, on the logic layer integrated in the 3D stack, as shown in figure 1.3. This helps save energy otherwise wasted in shipping data from the memory store to the compute core, and to transfer the updated data back to the memory for permanent storage. Such was the paradigm in previous processor-centric architectures, where compute cores would request data from the shared DRAM memory store, over a communication channel.

**VERTICAL STACKING (3D)**

Figure 1.3: 3D stacking for Near Data Processing (NDP) [7]

Thus now basic tasks such as Read-Update-Write can be associated with memory and may be performed very close to the memory die.

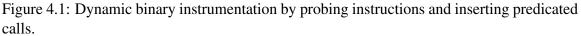

#### 1.3.1 Hybrid Memory Cube Architecture

Hybrid Memory Cube (HMC) is a 3D-stacked memory architecture proposed by one of the industry leaders, Micron. This architecture proposes the integration of a network and logic layer under multiple DRAM dies in a 3D-stacked structure. The dies are vertically connected by means of Through Silicon Vias (TSV), or vertical communication channels. The TSVs provide high internal communication bandwidth between memory and the controller when compared to 2D structures for similar memory densities.

HMC introduces significant improvements in access bandwidth, lower chip area footprint and lower power consumption when compared to DRAM. Although in order to achieve these benefits, memory requests cannot be naively sent to the device. For example, access patterns and read-write request ratios and communication overhead between the HMC and host play a crucial role in determining the performance benefits that may be achieved for a target application.

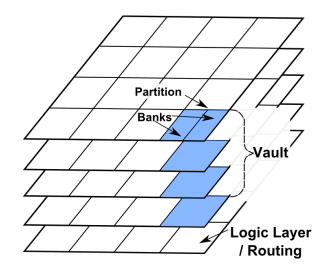

Figure 1.4: Memory organization in Hybrid Memory Cube (HMC).

#### (a) Memory organization

A HMC memory may be understood by breaking it down into constituent building blocks. The chip on board our evaluation platform (See Section 5) accelerator board is HMC Consortium 1.1 compliant. As shown in figure 1.4, it consists of 8 DRAM dies with one logic layer. The 3D structure is divided into 16 vertical sections, known as vaults. Each vault has a dedicated memory controller in the logic layer to handle vertical requests to any of the DRAM stacks. Four such vaults in the same physical vicinity are logically grouped together, and are known as a quadrant. The four vaults of a quadrant usually share a common external link. Each layer within a vault consists of 2 banks. This means that our HMC device has 256 banks of DRAM.

$$Banks_{(spec1.1)} = 8Memorystacks \times 16vault/stack \times 2banks/partition$$

$$= 256banks$$

In each subsequent iteration of the HMC specification, the memory partitions are made more dense.

#### (b) Interface protocol

HMC works over a serial link, employing a packet based communication protocol. Thus in contrast to conventional parallel DRAM interfaces, HMC utilizes serialization and deserialization (SerDes) modules. Thus it enables us to achieve higher bandwidth over HMC links at the cost of higher power usage for SerDes. A packet in this communication protocol is usually of a 16B or higher granularity. These packets are called "Flits". Special header and tail flits carry header information to ensure packet integrity and flow control for communication.

A HMC is usually connected to a host via two or four external links, as shown in figure 1.5. Each link is an independent link to a quadrant in the HMC. The quadrants within a HMC are internally connected via a crossbar, which serves as a router between the external links and the distributed vaults. Routing latency is lower for packets with vault destinations in the same quadrant, and higher for packets with vault destinations in other quadrants.

Figure 1.5: Serial links between CPU and HMC [8]

# CHAPTER 2 BACKGROUND STUDY

An extensive study into the existing widely accepted state of the art implementation for our target application, *LU* decomposition for large order sparse matrices with SUPERLU, is necessary to understand possible optimization. This chapter discusses a deeper analysis of the *LU* decomposition algorithm in the SUPERLU\_DIST package to better understand the opportunities for parallelism on an offload accelerator or GPU platform. This is also followed by a literature survey of prior recent work with similar approaches to mitigate the memory bottleneck by hardware improvements.

#### 2.1 Related Work

For the target application, *LU* decomposition, numerous efforts in the past have been made in order to increase the performance of relevant HPC primitives such as matrix-multiply and related SpMV kernels. Some focus on improvement in the algorithmic implementations to increase the occupancy of the compute units, reduce memory transfer invocations, and/or hide memory access latency to the maximum possible extent. Other approaches emphasize hardware improvements to reduce the absolute memory access costs and the peak achievable bandwidth.

#### 2.1.1 Algorithmic Optimization of SuperLU

Most implementations usually invoke a phase to perform matrix row and column manipulations to create favorable fractal formations without changing the properties of the matrix. This is followed by multiple DGEMM (Double-precision Matrix Multiply) API calls mapped to a GPU or other accelerator for operations on dense data fractals of the otherwise sparse matrix. This phase, sometimes referred to as the Schur Complement, is the most common choice for optimization algorithms to improve the efficiency of the algorithm from a compute efficiency point of view. We tackle this phase from the memory system's perspective by employing a combined FPGA and HMC architecture to exploit potential benefits.

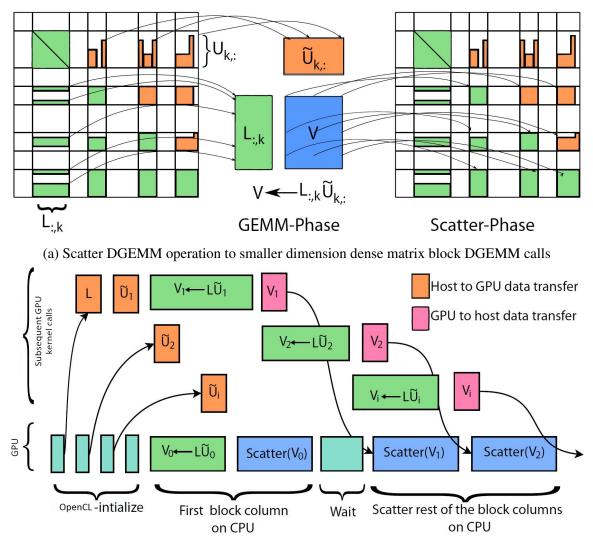

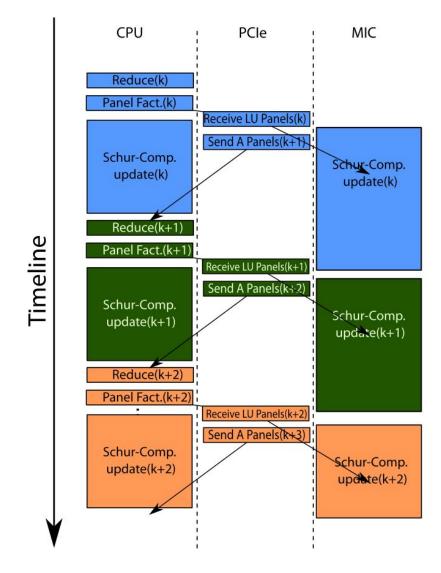

(b) Using Data Transfer idle time on host for DGEMM compute

Figure 2.1: Asynchronous data transfer and compute time sharing. Adopted from P.Sao, R. Vuduc, X. S. Li, Euro-Prar, 2014 [4]

Efforts like those of Sao, et. al [4] aim to optimize this phase in order to speed up the overall computation. One of the approaches to do so is by distributing the workload across multiple compute nodes or GPU lanes or threads to overlap the embarrassingly parallel computations, like those of Schur Complement updates of matrix blocks. The authors of

this work do so by presenting the first hybrid MPI+OpenMP+CUDA implementation of a distributed memory, right-looking, asymmetric sparse direct solver for sparse LU using static pivoting.

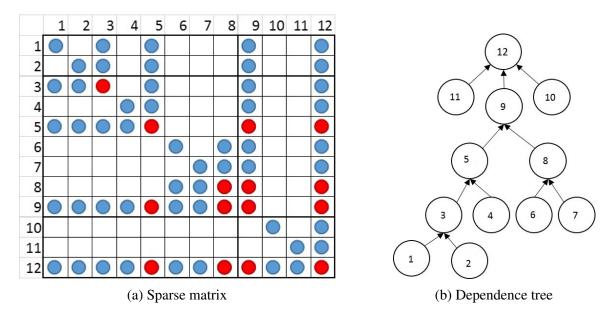

Another state of the art approach is one which reduces the wall clock time of the previous approach considerably by overlapping the data transfer overheads with SC (Schur Complement) update computations. This is the approach taken in the Highly Asynchronous Lazy Offload (HALO) optimization that was added an implementation of SUPERLU\_DIST [4]. The HALO approach is described in figure 2.1. The updates to matrix blocks in memory are scheduled in parallel to manipulation of other independent blocks prepared in a prior step in the form of a tree data structure. The nodes of the tree, as shown in figure 2.2, represent an independent sub-block ready for a SC update. The parent of a node represents a dependency relationship on the result of its child's SC update before the SC update can occur for a parent sub-block. Thus the partial results of the computation are stored on the respective offload accelerator/GPU unless deemed absolutely necessary as a dependency for the SC update of the parent sub-block node.

Figure 2.2: Dependent sub-blocks are coded in red, and independent sub-blocks that may be scheduled for Schur Complement update in the same iteration stage are coded in blue. The dependence tree shows independent blocks that may be processed for Schur Complement in the same iteration stage.

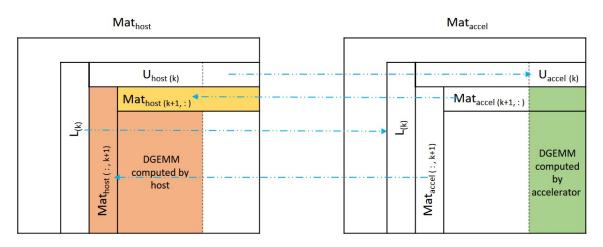

Another crucial contribution of the work in [1] is in minimizing size of such data transfers between the CPU and the GPU local memories. This is made possible by sharing the computation overhead between the CPU (host) and the GPU (accelerator) in a proportion (chosen dynamically) such that the overall time taken by the two to process their chunks is the same. Thus only the required sub-group of the U-panels and the L-panel, as shown in figure 2.3 is shipped off to the GPU, instead of the entire matrix or the entire U-panel as in case of naive sparse LU direct solver implementations. Naive accelerator implementations offload all the BLAS calls for operations such as DGEMM to the GPU (accelerator) leaving the CPU (host) idle while it waits to receive the final results. This is further aggravated by the need to ship entire U and L block panels to the accelerator, increasing data copy overheads.

Figure 2.3: Schur Complement update in k-iteration. The L(k) and U(k) panels, calculated in k-th panel-factorization on the CPU, are sent to the GPU. The GPU sends (k + 1) matrixpanels to the CPU. The CPU and GPU update parts of the k-th Schur-complement. The DGEMM result for areas marked in orange is computed by CPU and the one in green is computed by GPU. The CPU merges the received GPUs (k + 1) matrix-panels with its own (k + 1) matrix-panels, before the (k + 1) iteration starts. Adopted from P.Sao, R. Vuduc, X. S. Li, Euro-Prar, 2014 [4]

#### 2.1.2 Hardware Approaches for Data Movement

Another approach taken by [9] suggests augmenting the hardware to reap benefits. They propose using the logic layer of the 3D-stacked memory architecture to implement a data

restructuring engine for irregular access patterns, that would ultimately reduce the volume of data to be transferred to the compute core on the memory bus. The proposal discusses a hardware engine that acts as a hardware offload unit for a CPU requesting data reorganization for a data structure with large strides or a statically determinable irregular access pattern, to a cache friendly layout buffer. This hardware engine takes over the responsibility for address translation and coherence housekeeping, while moving data between DRAM banks local view buffer which is ultimately streamed to the CPU. The high package internal bandwidth of the stacked memory helps achieve lower latency for data reorganization compared to other prior similar approaches on the host.

Although the approach seems to offer many benefits for sparse access streams with fixed access patterns, the limiting factor of the proposal is its dependence on scatter/gather and DMA (Direct Memory Access) kernels to deliver a static irregular access stream to the hardware engine. This may limit opportunities to optimize for dynamic access streams that are dependent on previously accessed data values. It does however reinforce the need for data movement and access primitives like scatter and gather on these types of architectures.

# CHAPTER 3 IMPLEMENTING THE TARGET APPLICATION FOR NDP

This chapter talks about the design of the OpenCL implementation of the target proxy application that is suitable to run on CPU, GPU, and FPGA. OpenCL is selected as the target language due to its versatility across platforms and new compilers that support FPGA hardware compilation via High-Level Synthesis (HLS). We discuss the assumptions that are used to implement the matrix data structure representation in memory while implementing the proxy SUPERLU or LU decomposition kernel. We go into more detail about the different computation phases of the algorithm and the parallelism opportunities within. Finally we highlight the libraries used for efficient BLAS (Basic Linear Algebra Subroutines) calls on the CPU and the GPU platforms.

#### 3.1 SUPERLU with HALO

For the purpose of studying the maximum achievable benefit from the HMC near-memory SUPERLU implementation, we use a dense matrix as our initial input kernel. This is an assumption made in order to maximize the number of memory accesses requests made to access the data elements, as compared to the house keeping overhead information such as data indexes that are used with sparse matrix representations. This worst case scenario model for the HMC memory model provides a counterpoint to the competing baseline model of a GPU accelerator. Normally a GPU would have a large data parallelism potential and the opportunity to hide memory access latency with an abundance of compute scheduling. Thus an improvement for the worst case scenario of dense matrix input would make the best argument further exploring memory models supporting NDP architectures for HPC, particularly for sparse LU implementations.

This proxy HALO implementation in OpenCL, is then used to obtain memory traces

representative of the application behavior which are then used for simulation using the GUPS HMC framework to make application performance estimates (Ch. 6).

The final SUPERLU implementation for sparse matrices and HALO data movement implemented in OpenCL is kept as a final piece of the work for testing on the real FPGA hardware interfaced with HMC memory chip. While this thesis does not examine this in detail, this implementation will be used to study real achievable numbers of performance improvements for sparse matrices. A respective vendor toolchain to convert the OpenCL solver implementation for sparseLU to an optimum verilog design for prototyping on the FPGA is later discussed in Ch. 5.

#### 3.1.1 OpenCL SUPERLU Implementation

SUPERLU with HALO can be summarized as multiple progressive iterations of 3 phases, namely panel-factorization, DGEMM (Double Precision Matrix Multiplication) and SC (Schur Complement) update. A detailed explanation of these phases can be found in the following paper [1].

Since our argument is for a PIM or NDP architecture acheived by moving the accelerator to the logic layer of a 3D-stacked memory chip, we are only concerned with the memory access stream of the BLAS calls offloaded to the accelerator. Thus for our discussion of the SUPERLU\_DIST package [4], the distributed memory model of a cluster of hosts interacting with MPI calls is not of our utmost concern. Thus, for simplicity, in our proxy application, we consider interaction between a single CPU (host) and a GPU (offload accelerator). For this reason, the phase that interest us is the DGEMM phase, which is offloaded to the GPU.

To discuss the DGEMM phase, we must understand how the data is prepared for the GPU and the asynchronous lazy offload calls, which help reduce the data transfer overhead costs in HALO. During the initialization phase, the GPU kernel is allocated a section of the memory  $(A^{\phi})$  initialized to all zeros. This memory serves as an analogous representation of the input matrix (A), where the computed partial DGEMM products are superimposed.

To understand this, consider a matrix  $A_{host}(i, j)$  and its analogous copy on the accelerator (GPU),  $A_{GPU}(i, j)$ .  $A_{host}^0(i, j)$  denotes the initial value of  $A_{host}(i, j)$ . As described above, we initialize  $A_{GPU}(i, j)$  with zero values. In an iteration k < min(i, j), HALO updates either  $A_{GPU}(i, j) \leftarrow A_{GPU}(i, j) - L(i, k) \cdot U(k, j)$  on the GPU or  $A_{CPU} \leftarrow A_{CPU} - L(i, k) \cdot U(k, j)$ on the CPU. Let  $\alpha_1$  denote the set of iterations in which  $A_{GPU}(i, j)$  is updated on the GPU, and  $\alpha_2$  denote the iterations when  $A_{CPU}(i, j)$  is updated on the CPU. Then, the images of  $A_{CPU}(i, j)$  and  $A_{GPU}(i, j)$  can be represented by:

$$A_{GPU}(i,j) \leftarrow -\sum_{k \in \alpha_1} L(i,k)U(k,j)$$

(3.1)

$$A_{CPU}(i,j) \leftarrow A^0_{host}(i,j) - \sum_{k \in \alpha_2} L(i,k)U(k,j)$$

(3.2)

If we added  $A_{GPU}(i, j)$  to  $A_{CPU}(i, j)$ , it would lead to the same result as updating  $A_{CPU}(i, j)$  each  $\alpha_1$  iterations. i.e.,

$$A_{CPU}(i,j) \leftarrow A_{CPU}(i,j) + A_{GPU}(i,j)$$

$$= A_{host}^{0}(i,j) - \sum_{k \in (\alpha_1 \cup \alpha_2)} L(i,k)U(k,j)$$

Thus before the  $k = min(i, j)^{th}$  iteration begins, we can query for the  $A_{GPU}(i, j)$  block and add it to  $A_{CPU}(i, j)$ . The resultant  $A_{CPU}(i, j)$  block contains updates from all  $\alpha_1 \cup \alpha_2$ iterations. Thus, when in the  $k = min(i, j)^{th}$  panel-factorization stage, the images of the  $A_{CPU}(i, j)$  block in the GPU offload case and the non-offloaded case are the same. This analysis holds true for all the blocks in the  $k^{th}$  panel-factorization stage. Hence, the factored L(k) and U(k) panels in the GPU offloaded case are the same as they would have been in the vanilla non-offloaded case.

Post panel-factorization phase, the burden of the SC update call is shared by the host

and the GPU. The HALO algorithm schedules the matrix multiply operation of the lower triangular matrix panel (L-panel) and the upper triangular matrix panel (U-panel), required for the SC update step, over the host and the GPU in an efficient way. Thus one portion of the result matrix is obtained as the result of a BLAS library call on the CPU while the remaining is scheduled on the GPU. The GPU computes the result of the DGEMM operation and superimposes it over the local GPU memory representing the analogous section of the input matrix. This is critical to the data transfer savings promised by HALO. This avoids the need for transferring the entire computed result to the host for each GPU call. Thus the GPU keeps accumulating the results of the partial L, U panel multiplications for the subsequently scheduled DGEMM operations. This results in the GPU local memory  $(A^{\phi})$ serving as a temporary storage for the compounded summation of the partial L, U panel products. A data transfer request call to the GPU is thus triggered by the host only when it is absolutely necessary to apply the sum of the computed partial products of the L, U panels to the respective block in the host memory store. This is done in order to complete the SC update of a block on the host before scheduling it for panel factorization on the host. Thus the data transfer overhead costs are reduced significantly.

In order to achieve the maximum GPU occupancy, HALO uses the elimination tree as described in the paper to identify the blocks which can be processed in the Schur Complement (SC) update stage in parallel in  $k^{th}$  iteration. Thus at any point of time, multiple blocks panels could be issued for computing DGEMM products if they are independent nodes on non-overlapping branches of the elimination tree. This helps overlap DGEMM computation of  $k^{th}$  iteration with data transfer calls invoked for completing SC update to a block, to be issued for panel factorization in  $k + 1^{th}$  iteration. Thus hiding memory access latency for fetching the computed result from GPU. It should be noted that this in no way helps the GPU to hide the local GPU memory access latency. That is strictly dependent on the number of blocks scheduled at the moment on the GPU, for DGEMM. Thus our argument for a HMC memory model contends for a quicker result computation on the GPU.

Figure 3.1: Concurrent execution of the remainder of Schur complement update for blocks A(k) on the GPU after transfer of required panels A(k + 1) to CPU. Allows for concurrent factorization of subsequent independent block A(k + 1) on CPU. In general, the Schur complement update is much longer than both other steps and data transfer. Adopted from P.Sao, R. Vuduc, X. S. Li, Euro-Par, 2014 [4]

Another important aspect is that this implementation is for a strict comparison of a portable application. This means that it is compatible with both the hardware platforms, one with a GPU using a DDR3 memory subsystem, and another with a GPU/accelerator using a HMC chip. Thus the benefits of dynamic HMC address mapping (as discussed in the section 1.1) by rewriting the accelerator (GPU) kernel cannot be exploited. We cannot

avoid the need for multiple local partial copies of the product on different local memories of SMXs (Symmetric Multi-streaming processors).

#### 3.2 BLAS libraries

Our implementation includes standard BLAS libraries in order to perform linear algebraic manipulations on matrices in an efficient manner. We invoke CBLAS library calls on the host using the OpenBLAS runtime package bound dynamically to the executable. Similarly we include the clBLAS runtime library package to support efficient BLAS implementations in OpenCL kernels running on an accelerator (CPU, GPU, etc.).

#### 3.2.1 clBLAS

This library [10] houses efficient OpenCL kernel implementations of BLAS level 1, 2 and 3 routines. The library supports running on CPU devices to facilitate debugging and multicore programming. Thus dedicated implementation for efficient OpenCL BLAS execution on CPU is assured. Importing this library helps us implement an efficient proxy application for the accelerator capable of representing a tuned accelerator kernel. This is irrespective of the actual hardware platform chosen for the accelerator. Thus assumptions may be taken in the thus obtained memory trace to expect maximum data parallelism.

The PICO vendor toolchain discussed for FPGA compilation in Ch. 5 has only limited support for BLAS call translations to efficient Verilog design implementations. Thus for final execution of the sparseLU application on FPGA interfaced with a HMC memory, we may need to implement a custom OpenCL implementation for DGEMM.

### 3.2.2 OpenBLAS

This library houses efficient multi-thread, multi-core implementations of BLAS level 1, 2 and 3 routines. This ensures efficient manipulation of the matrix data structures during BLAS calls on host. Its significance is that while generating the memory trace (Ch. 4, we must be careful of these contending threads executing BLAS calls because they may make requests to the same blocks of memory simultaneously.

#### **CHAPTER 4**

#### EVALUATING MEMORY BEHAVIOR WITH MEMORY TRACES

Since our FPGA and HMC Near Data Processing platform currently has limited support for running BLAS operations that are key to the proxy application, we use this chapter to discuss how memory traces are generated and used with our FPGA framework to test the memory access characteristics of our kernel. A memory trace refers to a record of attributes of all the memory access requests made by the hardware, including the size of transaction, access type (read/write), address, etc. The possible approaches to get the trace include binary instrumentation or executing the binary through a simulation framework with a custom memory model. The span of memory requests which are of interest to us, is too wide over the lifetime of the executable in our case. This is so because the DGEMM call invocations are distributed across multiple iterations of the LU factorization algorithm. Thus a simulation framework modeling the host and the accelerator pipelines through memory stages would simply take too long to simulate the entire program to generate the memory trace. Thus the alternate approach for binary instrumentation is adopted.

#### 4.1 Hardware platform

At the time of this work, there was a lack of a stable compatible binary instrumentation tool to record memory trace for a binary running on a GPU hardware. Most tool chains exist for recording memory trace for an instruction trace running on a simulator frameworks for a GPU platform. Only a few dynamic instrumentation tools, like "lynx" [11] exist for GPU platforms. But these tools support instrumentation for only a small subset of NVIDIA GPU architectures of the ages past. Recent tools such as GT-Pin [12] and GPUPROF lack the necessary documentation and support for experimentation and reliable usage on more recent GPU architectures. They are also often vendor restricted i.e. they work for only select

vendor platforms; GT-pin is restricted for only Intel GPU platforms and currently exists only in beta format.

For this reason, we choose a stable CPU platform capable of executing OpenCL kernels coupled with the PIN instrumentation tool [13]. The supported runtime packages on Intel CPUs provide efficient multi-threaded implementations for multi-core processor platforms.

We use the Intel(R) Core(TM) i7-4790K CPU processor clocked at 4.00GHz for our experiments to generate the memory traces. The generation of a memory trace for the proxy application with a square matrix of dimension 1000 takes ~25 GB of storage space and 4 hours instrumentation runtime.

#### 4.2 PIN tool

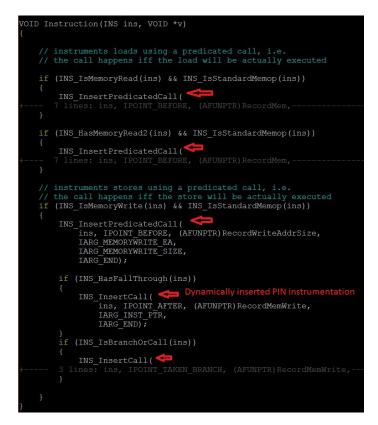

Pin [13, 14] is a dynamic binary instrumentation framework by Intel for their IA-32, x86-64 and MIC instruction-set architectures. The tool enables creation of dynamic program analysis tools or "pintools" for user space applications. Instrumentation is performed at run time on the compiled binary files. Thus, it does not require recompiling of source code and can support instrumenting programs that dynamically generate code. It allows context information such as register contents to be passed to the injected code as parameters.

The tool provides a rich API library which allows for specialized filtering of information to be monitored for the executing binary. It enables us to dynamically modify the target binary application on the fly through the static definition of procedure calls that are inserted dynamically into the instruction stream based on instruction type. This is depicted in figure 4.1.

The tool fidelity encompasses:

- 1. The granularity of instrumentation: instruction, basic blocks, trace

- 2. Information to extract: memory references, instruction pointer information, routine name, instruction image name

- 3. Multi-thread primitives, etc...

Our focus is to obtain the memory trace for the offloaded DGEMM routine invoked from the clBLAS library. Thus we need to focus on the OpenCL kernel execution on the Intel CPU. Hence, we concentrate our efforts to isolate the memory accesses initiated from the instruction stream that belong to the dynamically linked Intel OpenCL runtime package images. Similarly, we trigger the instruction level instrumentation only after invocation of the proxy application routine. And we end the instrumentation, as soon as we return with the factored LU result. This is shown in figure 4.3. The entry and exit point of the proxy are identified using the dis-assembly dump of the binary as shown in figure 4.2.

#### 4.2.1 Memory Trace Pintool Filter

Pintool refers to the filter applications developed using Pin to focus the scope of instrumentation on the instruction stream which is of deep interest. In order to isolate memory access requests to generate a trace, the technique involves two logical steps. These include identifying the instruction type to pinpoint memory operations that interest us, and then isolating the required information attributes from the instruction header.

For standard memory manipulation instructions which perform simple "loads" and "stores" on memory operands, predicated calls for instrumentation are inserted. These trigger a routine which records the the details if the memory operation is indeed performed. The attributed recorded include the instruction pointer, memory address, request size, type of operation (read/write), and the actual probed data.

For other standard memory access instructions initiating write requests on its operands or for conditional codes making control decisions, a respective instrumentation call for tracking the write update to the AFUNPTR pointer is inserted. This helps the profiler track the path taken by the branches for subsequent calls.

#### 4.2.2 Custom Pintool Filters

In order to maintain a good degree of performance for the instrumentation phase, and to restrict the amount of pre-processing required for the memory trace to extract the OpenCL kernel memory references, we limit the scope of the instrumentation with a filter.

We generate a dis-assembly of the compiled binary to identify the memory address of the instruction invoking the proxy application routine. Similarly the memory address for the return instruction for the target is noted. These instruction addresses are hard coded in a custom pintool which triggers instruction level instrumentation only when the routine for the target application is executed. The instrumentation is disabled once a return from the routine is acknowledged by the instruction pointer. This also triggers other house keeping actions such as closing the trace file pointer and exiting the application. This is shown in figure 4.3.

|                    |            | 26 - | <_Z      | 8dei     | ıse_     | _LU | PdRP7 |       | iRP11_cl_contextRP17_cl_command_queue>: |

|--------------------|------------|------|----------|----------|----------|-----|-------|-------|-----------------------------------------|

| 403926:            | 55         |      |          |          |          |     |       | push  | %rbp                                    |

| 403927:            |            |      | e5       |          |          |     |       | mov   | %rsp,%rbp                               |

| 40392a:            |            | 57   |          |          |          |     |       | push  | %r15                                    |

| 40392c:            |            | 56   |          |          |          |     |       | push  | %r14                                    |

| 40392e:            |            | 55   |          |          |          |     |       | push  | %r13                                    |

| 403930:            | 41         | 54   |          |          |          |     |       | push  | %r12                                    |

| 403932:            | 53         |      |          |          |          |     |       | push  | %rbx                                    |

| 403933:            | 48         | 81   |          | a8       | 80       |     |       | sub   | \$0x8a8,%rsp                            |

| 40393a:            | 48         | 89   | bd       | 58       | f7       | ff  | ff    | mov   | %rdi,-0x8a8(%rbp)                       |

| 403941:            |            |      | b5       |          | f7       | ff  | ff    | mov   | %rsi,-0x8b0(%rbp)                       |

|                    |            |      |          |          |          |     |       |       | -                                       |

|                    | :          |      |          |          |          |     |       |       |                                         |

| 406070:            | 48         | 89   |          |          |          |     |       | mov   | %rbx,%rax                               |

| 406073:            | 48         |      | c7       |          |          |     |       | mov   | %rax,%rdi                               |

| 406076:            | 40<br>e8   |      | c3       | <u> </u> | <u> </u> |     |       |       |                                         |

|                    |            |      |          |          |          |     |       | callq |                                         |

| 40607b:<br>406080: |            |      | c2<br>65 |          | II       |     |       | callq |                                         |

|                    |            | 8a   | 65       | α8       |          |     |       | lea   | -0x28(%rbp),%rsp                        |

| 406084:            | 5b         |      |          |          |          |     |       | pop   | %rbx                                    |

| 406085:            | 41         |      |          |          |          |     |       | pop   | %r12                                    |

| 406087:            | 41         |      |          |          |          |     |       | pop   | %r13                                    |

| 406089:            | 41         |      |          |          |          |     |       | pop   | %r14                                    |

| 40608b:            | 41         | 5f   |          |          |          |     |       | pop   | %r15                                    |

| 40608d:            | 5d         |      |          |          |          |     |       | pop   | %rbp                                    |

| 40608e:            | <b>c</b> 3 |      |          |          |          |     |       | retq  |                                         |

Figure 4.2: Disassembly of the proxy target application. Helps identify the memory address for entry and return instructions for the OpenCL kernel subroutine.

| VOID Trace(TRACE trace, VOID * val)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>if (!filter.SelectTrace(trace))     return;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <pre>for (BBL bbl = TRACE_BblHead(trace); BBL_Valid(bbl); bbl = BBL_Next(bbl))</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| for (INS ins = BBL_InsHead(bbl); INS_Valid(ins); ins = INS_Next(ins))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <pre>t if((INS_Address(ins) == 0x403926)) {     FIN_MutexLock(&amp;thread_Lock);     flag_inst = true;     FIN_MutexUnlock(&amp;thread_lock);     FIN_MutexUnlock(&amp;thread_lock);     FIN_MutexUnlock(#thread_lock);     FIN_MUtexUnlock(#thread_lock(#thread_lock);     FIN_MUtexUnlock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#thread_lock(#t</pre> |

| )<br>PIN_MutexLock(&thread_lock);<br>out << hex << setw(8) << INS_Address(ins) << " ";<br>PIN_MutexUnlock(&thread_lock);<br>RTN_rtn = TRACE_Rtn(trace);<br>if (RTN_Valid(rtn))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <pre>{ IMG img = SEC_Img(RTN_Sec(rtn)); probing for OpenCL kernel calls if (IMG_Valid(img)) [ if((strstr[UMG Name(img).c_str(), "intel")]!= NULL) &amp;&amp; (flag_inst == out &lt;&lt; IMG_Name(img) &lt;&lt; ";" &lt;&lt; RTN_Name(rtn) &lt;&lt; " "; Instruction(ins, NULL); </pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| }<br>PIN MutexLock(&thread lock);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| out << INS_Disassemble(ins) << endl;<br>PIN MutexUnlock(&thread lock);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |