## PREDICTIVE MODELING OF DEVICE AND CIRCUIT RELIABILITY IN HIGHLY SCALED CMOS AND SIGE BICMOS TECHNOLOGY

A Dissertation Presented to The Academic Faculty

by

Kurt A. Moen

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology May 2012

## PREDICTIVE MODELING OF DEVICE AND CIRCUIT RELIABILITY IN HIGHLY SCALED CMOS AND SIGE BICMOS TECHNOLOGY

Approved by:

Professor John D. Cressler, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Shyh-Chiang Shen School of Electrical and Computer Engineering Georgia Institute of Technology

Professor David S. Citrin School of Electrical and Computer Engineering Georgia Institute of Technology Professor Faramarz Fekri School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Samuel Graham School of Mechanical Engineering Georgia Institute of Technology

Date Approved: April 10, 2012

To my dear wife,

Jennifer

## ACKNOWLEDGEMENTS

I would first like to express my deepest gratitude to Dr. John D. Cressler for his guidance and support as my advisor. Both in the lab and in the classroom, his enthusiasm for research and teaching, combined with his sincere care for others, has shown me how to excel as an engineer while being a blessing to those around you.

I would like to thank the other members of my dissertation committee. I would also like to sincerely thank all of the members of the SiGe research team at Georgia Tech for their support and collaboration: Stan Phillips, Partha Chakraborty, Jiahui Yuan, Ted Wilcox, Tushar Thrivikraman, Tom Cheng, Laleh Najafizadeh, Steven Horst, Ryan Diestelhorst, Marco Bellini, Aravind Appaswamy, Uppili Ragunathan, Duane Howard, Sachin Seth, Akil Sutton, Prabir Saha, Anuj Madan, and others. I am grateful to Dr. Guofu Niu from Auburn University for helpful discussions regarding my research.

I am very grateful for the support provided by the Graduate Fellowship Program of the Semiconductor Research Corporation, as well as that given by DTRA, NASA ETDP, and the SiGe BiCMOS team at IBM Microelectronics. I am particularly thankful for the close collaborations I have enjoyed with Marek Turowski and Ashok Raman of CFD Research Corporation in Huntsville, AL, and with Hiroshi Yasuda of Texas Instruments in Dallas, TX.

I am deeply indebted to my parents, Dale and Marghy Moen, for their love and care throughout my life. I am very grateful to my brother and his wife, Brent and Amy, for the sincere care and support that they have shown me. And most of all, I am beyond grateful to my wife Jennifer, who has made me a better person in so many ways, and who I have grown to love so dearly. Her constant care has sustained me.

# TABLE OF CONTENTS

| DE  | DIC | ATIOI  | N                                                                       | iii      |

|-----|-----|--------|-------------------------------------------------------------------------|----------|

| AC  | KN  | OWLE   | DGEMENTS                                                                | iv       |

| LIS | т о | F TAE  | BLES                                                                    | vi       |

| LIS | т о | F FIG  | URES                                                                    | vii      |

| SU  | MM  | ARY .  |                                                                         | viii     |

| I   | INT | rodu   | UCTION                                                                  | 1        |

|     | 1.1 | Broad  | band IC Technologies                                                    | 2        |

|     | 1.2 | The S  | iGe HBT                                                                 | 4        |

|     | 1.3 | Extre  | me Environment Electronics                                              | 7        |

|     |     | 1.3.1  | Radiation Effects in CMOS                                               | 8        |

|     |     | 1.3.2  | Radiation Effects in SiGe HBTs                                          | 9        |

|     | 1.4 | Long-' | Term Device and Circuit Reliability                                     | 10       |

|     | 1.5 | Resear | rch Objectives                                                          | 12       |

| II  |     |        | ED TRANSIT-TIME ANALYSIS FOR SIGE HBT PER                               |          |

|     |     |        | NCE OPTIMIZATION                                                        | 16       |

|     | 2.1 | 2-D T  | ransit Time Analysis                                                    | 17       |

|     | 2.2 | Region | nal Transit Times                                                       | 18       |

|     | 2.3 | Simula | ation Results                                                           | 19       |

|     |     | 2.3.1  | Scaled npn SiGe HBTs                                                    | 20       |

|     |     | 2.3.2  | Application Towards a C-SiGe Scaling Roadmap                            | 25       |

|     | 2.4 | High-l | Injection Effects                                                       | 29       |

| III |     |        | EMENT AND MODELING OF CARRIER TRANSPOR<br>TERS FOR EXTREME ENVIRONMENTS | RТ<br>31 |

|     | 3.1 | Minor  | ity Carrier Recombination                                               | 32       |

|     |     | 3.1.1  | Experimental Details                                                    | 32       |

|     |     | 3.1.2  | Measurement Results                                                     | 34       |

|               |     | 3.1.3  | Calibrated Trap Modeling                                                      | 38         |

|---------------|-----|--------|-------------------------------------------------------------------------------|------------|

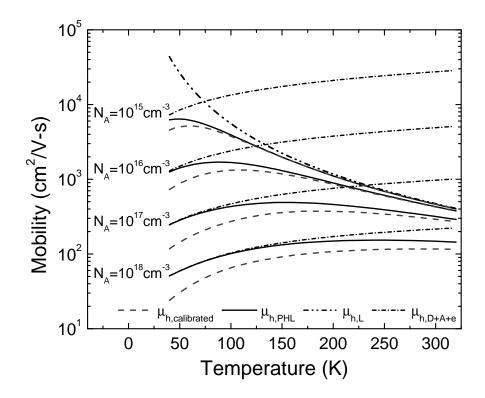

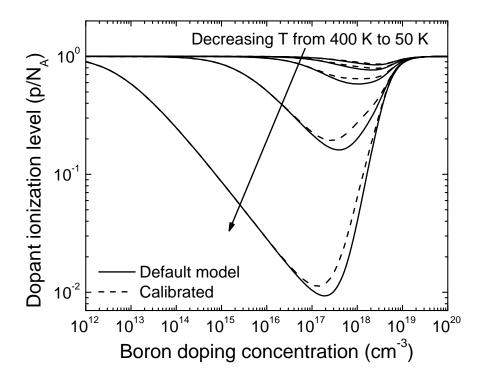

|               | 3.2 | Mobil  | ity and Incomplete Ionization                                                 | 43         |

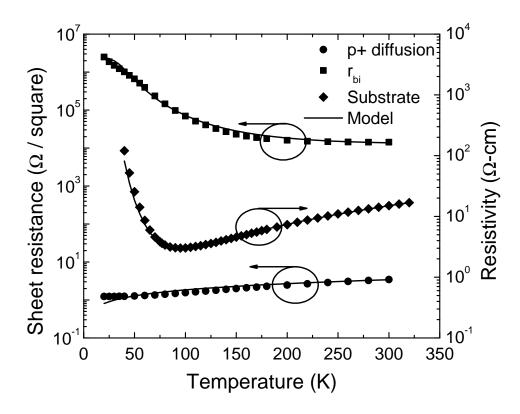

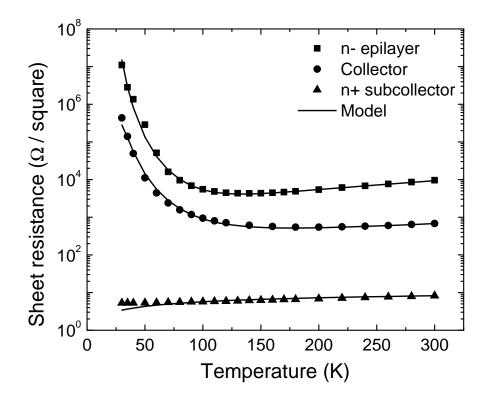

|               |     | 3.2.1  | Resistance Measurements                                                       | 45         |

|               |     | 3.2.2  | Calibrated Modeling                                                           | 50         |

|               | 3.3 | Applie | cations                                                                       | 52         |

| $\mathbf{IV}$ | SIN | [GLE-] | EVENT TRANSIENTS IN 45-NM RF-CMOS ON SOI                                      | 53         |

|               | 4.1 | Exper  | imental Details                                                               | 54         |

|               | 4.2 | Exper  | imental Testing of Different Body-Tie Geometries                              | 55         |

|               |     | 4.2.1  | Preliminary Results                                                           | 55         |

|               |     | 4.2.2  | Additional Testing at Lower Laser Pulse Energies                              | 64         |

|               |     | 4.2.3  | Trade-offs of Body-Tie Variants                                               | 69         |

| V             |     |        | SHING BEST PRACTICES FOR MODELING CIRCUIT                                     | -<br>70    |

|               | 5.1 | Motiv  | ation for Using Mixed-Mode TCAD to Model Single-Event Effects                 | 71         |

|               | 5.2 |        | ate Modeling of Single-Event Transients in a SiGe BiCMOS ge Reference         | 74         |

|               |     | 5.2.1  | Background                                                                    | 75         |

|               |     | 5.2.2  | Single-Event Transient Simulation Approaches                                  | 77         |

|               |     | 5.2.3  | SiGe Voltage Reference Simulations                                            | 81         |

|               |     | 5.2.4  | Conclusions                                                                   | 93         |

|               | 5.3 | Under  | standing Single-Event Transients in Gb/s SiGe Digital Logic $% \mathcal{S}$ . | 95         |

|               |     | 5.3.1  | Circuit and Simulation Details                                                | 95         |

|               |     | 5.3.2  | Static Bias Simulation Results                                                | 98         |

|               |     | 5.3.3  | Clocked Simulation Results                                                    | 107        |

|               |     | 5.3.4  | Conclusions                                                                   | 112        |

|               | 5.4 | Best I | Practices in Circuit-Level SEE Simulation                                     | 113        |

| VI            |     |        | -BASED TCAD FRAMEWORK FOR PREDICTIVE MO<br>F BIPOLAR CIRCUIT RELIABILITY      | DD-<br>117 |

|               | 6.1 | Physic | cs-Based Trap Degradation Model                                               | 118        |

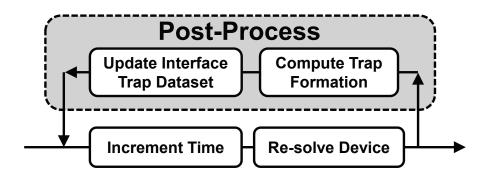

|                 | 6.2 | Transie | ent Degradation Simulation Methodology | 122 |

|-----------------|-----|---------|----------------------------------------|-----|

|                 | 6.3 | Bias D  | ependence and Calibration to Data      | 134 |

|                 | 6.4 | Applica | ation to Mixed-Mode TCAD               | 138 |

| VII CONCLUSIONS |     |         | SIONS 1                                | 140 |

|                 | 7.1 | Future  | Work                                   | 143 |

|                 |     | 7.1.1   | Single-Event Transient Modeling        | 143 |

|                 |     | 7.1.2   | Conventional Reliability Modeling      | 144 |

| REFERENCES      |     |         |                                        | 146 |

| VI              | ГА. |         |                                        | 157 |

## LIST OF TABLES

| 1 | Trap parameters for calibrated carrier lifetime models                                                       | 40 |

|---|--------------------------------------------------------------------------------------------------------------|----|

| 2 | Calibrated parameters used in mobility model for arsenic-, phosphorus-, and boron-doped silicon              | 51 |

| 3 | Calibrated parameters used in incomplete ionization model for arsenic-, phosphorus-, and boron-doped silicon | 51 |

# LIST OF FIGURES

| 1  | Cross-section of a representative first-generation SiGe HBT                                                                                                                | 4  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Measured doping profile of a representative first-generation SiGe HBT                                                                                                      | 5  |

| 3  | Energy-band diagrams for a Si BJT and a graded-base SiGe HBT $$                                                                                                            | 6  |

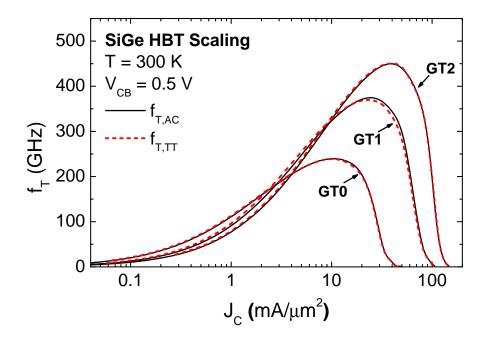

| 4  | Comparison of $f_T$ vs. $J_C$ curves simulated for a calibrated model of a 50 GHz npn SiGe HBT, using both the 2-D transit time analysis and frequency-domain simulations. | 20 |

| 5  | Comparison of $f_{\rm T}$ vs. $J_{\rm C}$ curves for scaled npn SiGe HBTs as computed by the 2-D transit time analysis and frequency-domain simulations                    | 21 |

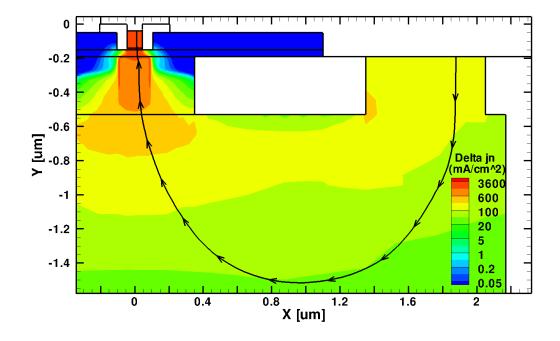

| 6  | Example streamline computed for GT1 at $V_{\rm BE}=0.8V$ and $V_{\rm CB}=0.5V$                                                                                             | 21 |

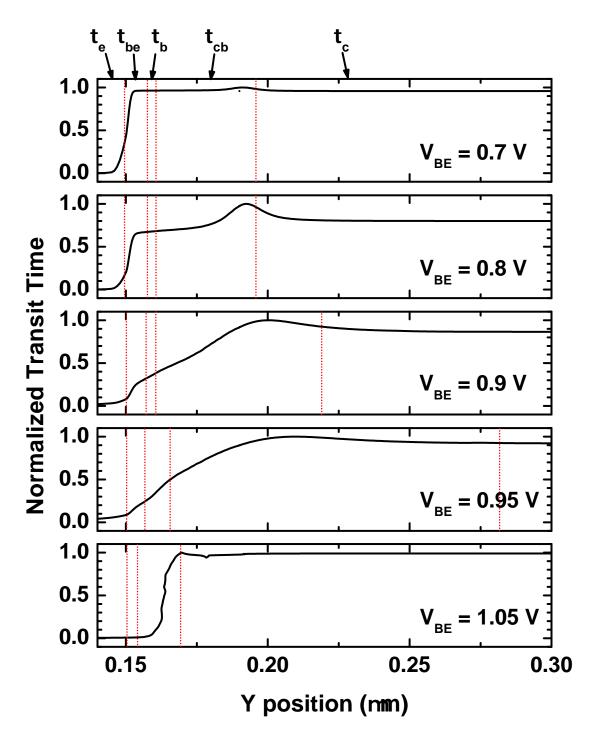

| 7  | Normalized cumulative transit time for GT1                                                                                                                                 | 23 |

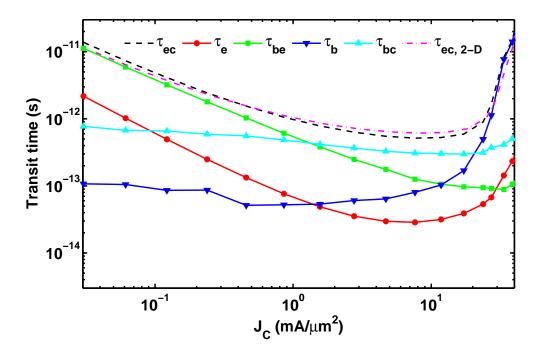

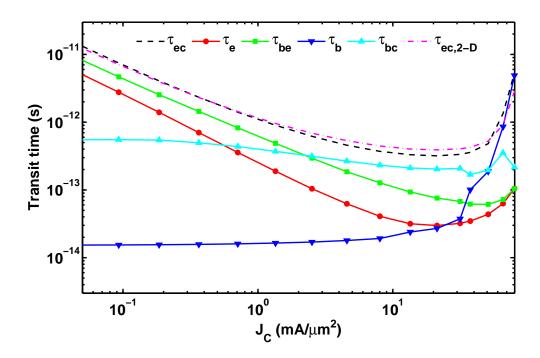

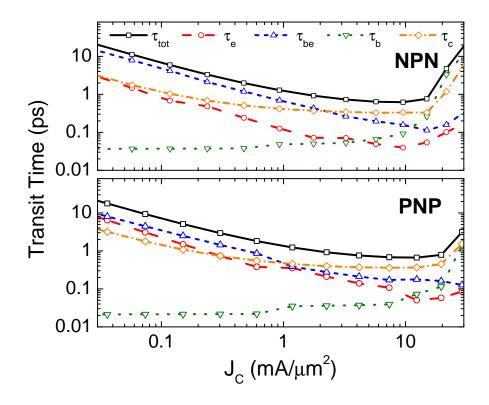

| 8  | Regional transit times vs. bias for GT0 with $V_{CB}=0.5V$                                                                                                                 | 24 |

| 9  | Regional transit times vs. bias for GT1 with $V_{CB}=0.5V$                                                                                                                 | 24 |

| 10 | Regional transit times vs. bias for GT2 with $V_{CB}=0.5V$                                                                                                                 | 25 |

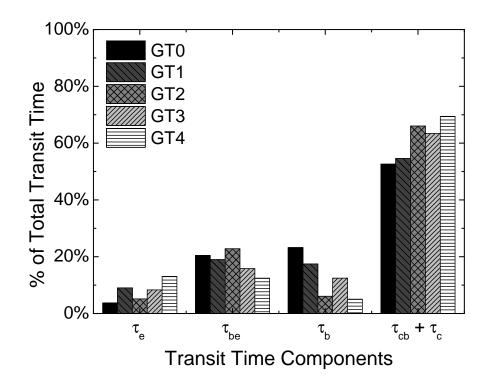

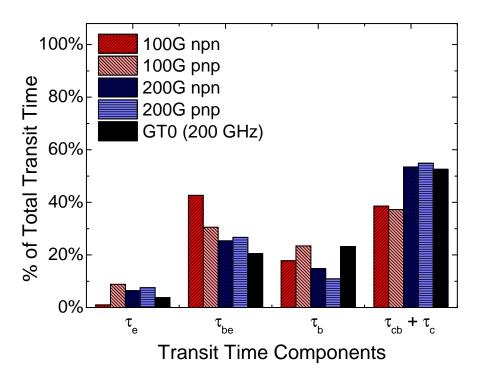

| 11 | Regional transit time components for scaled npn SiGe HBTs biased at peak- $f_T$ , normalized to total transit time                                                         | 26 |

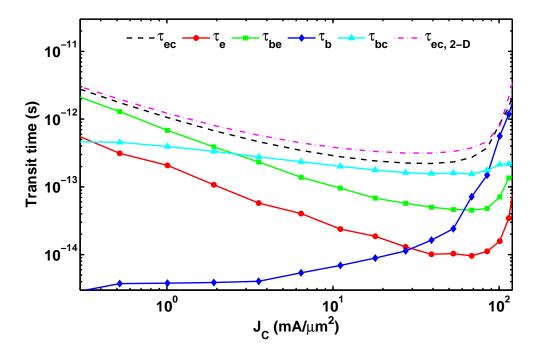

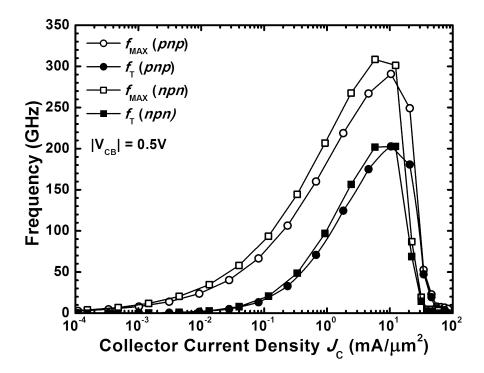

| 12 | Comparison of the ac performance $(f_T, f_{max})$ for the calibrated 200 GHz C-SiGe HBT models.                                                                            | 27 |

| 13 | Regional transit time components for the 200 GHz C-SiGe HBTs vs. collector current density.                                                                                | 28 |

| 14 | Regional transit time components for 100 GHz and 200 GHz C-SiGe HBTs biased at peak- $f_T$ , normalized to total transit time                                              | 28 |

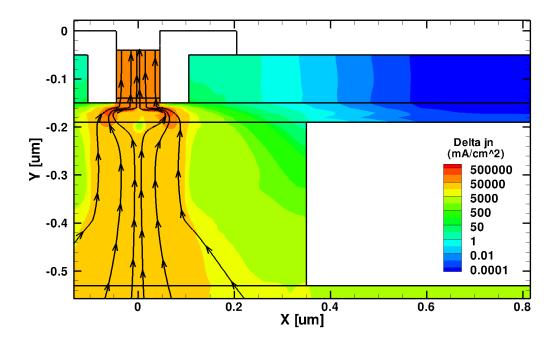

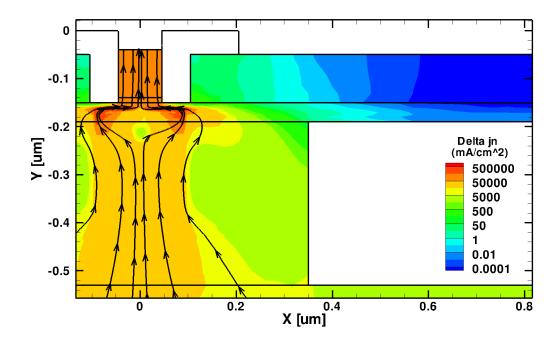

| 15 | Streamlines computed for GT1 at early onset of HBE, with $V_{BE} = 1.01 V$ and $V_{CB} = 0.5 V$ .                                                                          | 30 |

| 16 | Streamlines computed for GT1 with $V_{\rm BE}=1.03V$ and $V_{\rm CB}=0.5V.$                                                                                                | 30 |

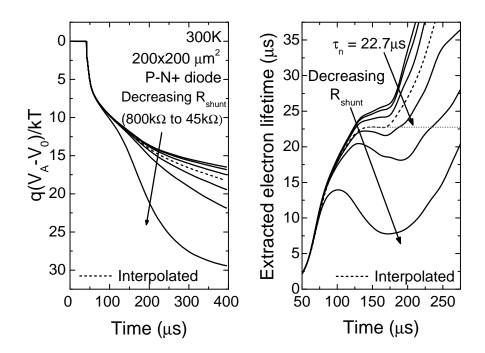

| 17 | Example set of OCVD and corresponding lifetime extraction curves                                                                                                           | 34 |

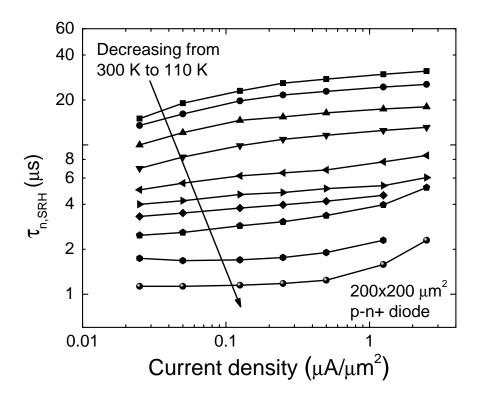

| 18 | Minority electron and hole lifetimes as a function of diode current density.                                                                                               | 35 |

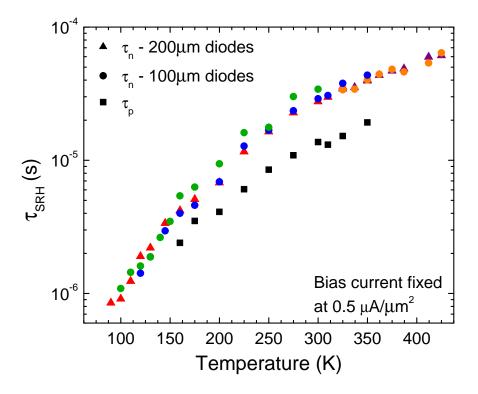

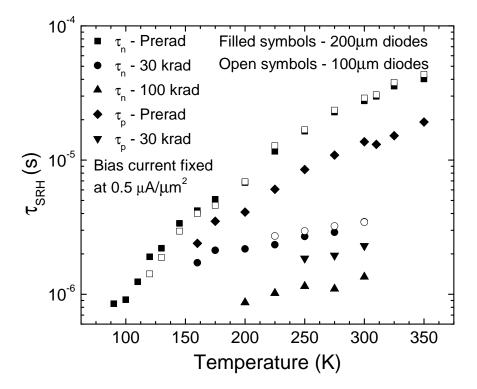

| 19 | Minority electron and hole lifetimes across temperature for fixed current density of $0.5 \mu A/\mu m^2$ .                                                                 | 35 |

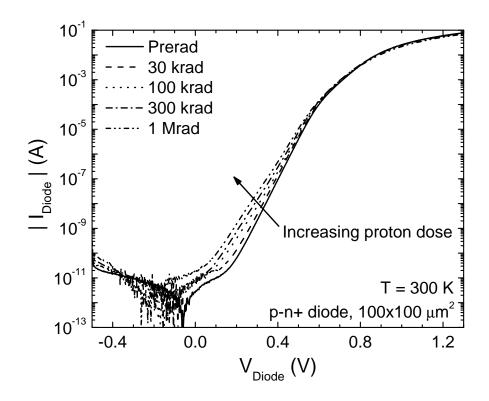

| 20 | Radiation response of p-n+ diode I-V characteristic                                                                                                                        | 37 |

| 21 | Radiation response of minority electron and hole lifetimes across temperature                                                                                                                                                            | 37 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

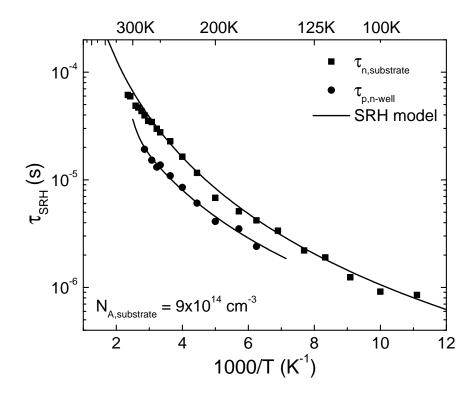

| 22 | Comparison of simulated and experimental temperature dependence of minority electron and hole lifetimes.                                                                                                                                 | 41 |

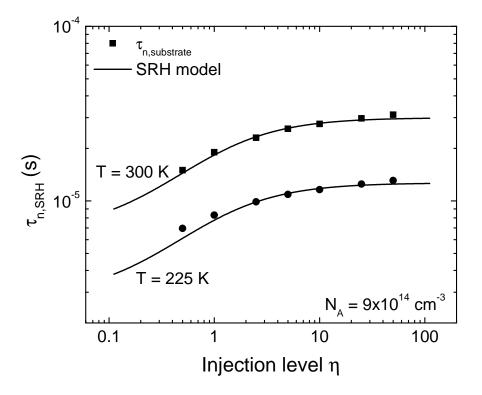

| 23 | Comparison of simulated and experimental injection dependence of minority electron lifetimes.                                                                                                                                            | 41 |

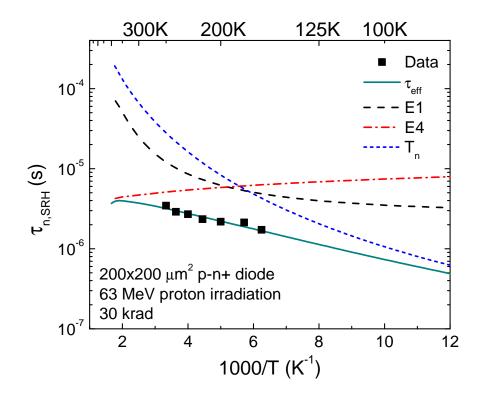

| 24 | SRH model fit of minority electron lifetime vs. temperature after 30 krad proton irradiation                                                                                                                                             | 42 |

| 25 | Comparison of the temperature dependence of scattering mechanisms<br>used in Philips unified mobility model for various doping concentrations.<br>The effective hole mobility from the calibrated model is shown by the<br>dashed lines. | 44 |

| 26 | Ionization level as a function of boron doping concentration across a wide temperature range                                                                                                                                             | 45 |

| 27 | P-type resistivity and sheet resistance measurements in IBM's 5HP/5AM<br>SiGe BiCMOS technology                                                                                                                                          | 47 |

| 28 | N-type resistivity and sheet resistance measurements in IBM's 5HP/5AM SiGe BiCMOS technology                                                                                                                                             | 48 |

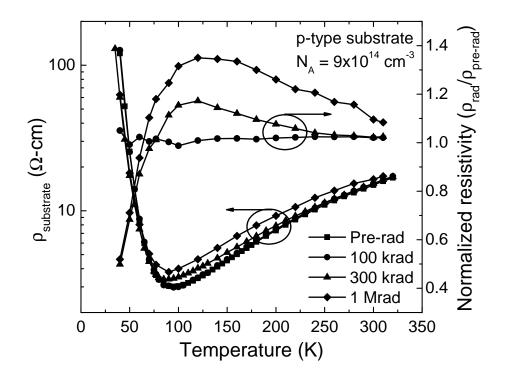

| 29 | Proton radiation response of the substrate resistivity across temperature.                                                                                                                                                               | 50 |

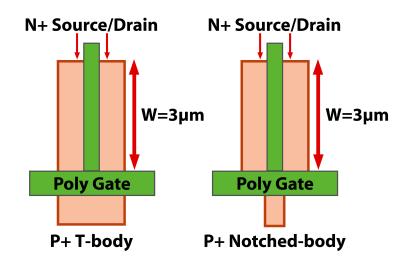

| 30 | Layout geometries for T-body and notched-body contacting schemes (not to scale)                                                                                                                                                          | 55 |

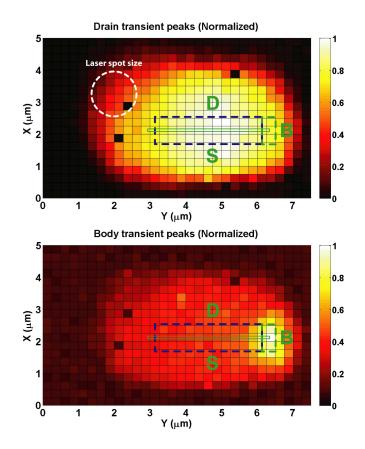

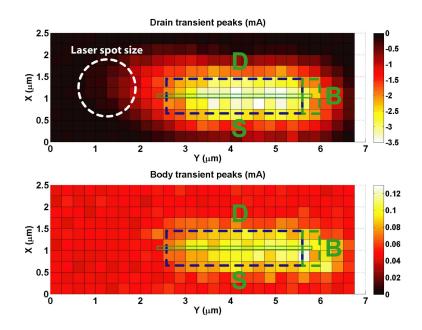

| 31 | Normalized peak drain and body currents for laser-induced transients as a function of laser position for a $3.0\mu\text{m} \ge 0.056\mu\text{m}$ SOI T-body nFET with an incident-laser pulse energy of $10.7\text{nJ}$                  | 56 |

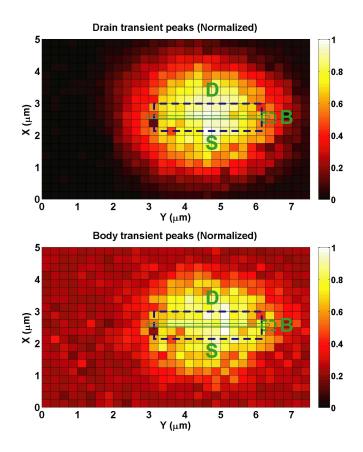

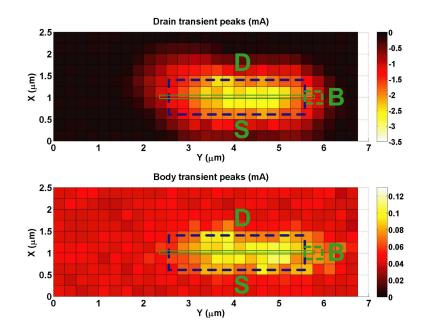

| 32 | Normalized peak drain and body currents for laser-induced transients as a function of laser position for a $3.0 \mu\text{m} \ge 0.056 \mu\text{m}$ SOI notched-body nFET with an incident-laser pulse energy of $10.7 \text{nJ}$         | 57 |

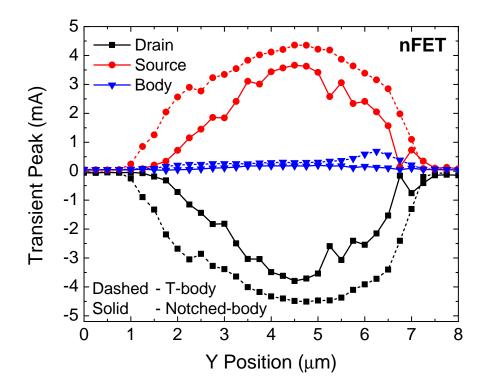

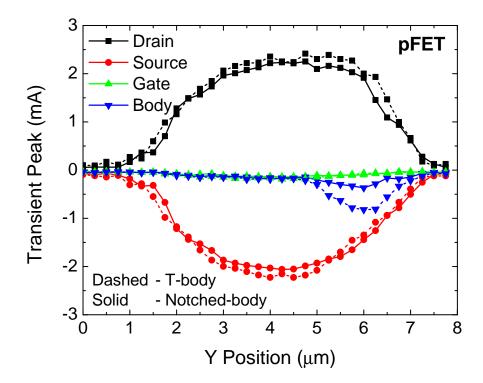

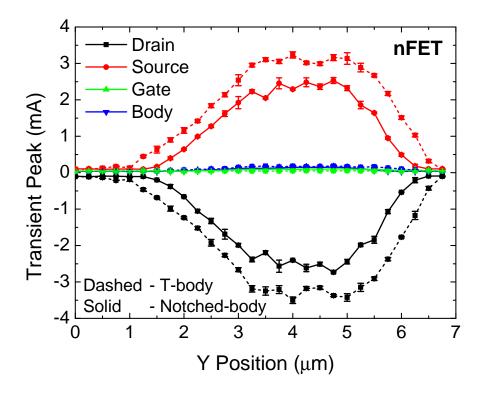

| 33 | Peak laser-induced transient currents as a function of laser position along the width of $3.0\mu\text{m} \ge 0.056\mu\text{m}$ T-body and notched-body SOI nFETs with an incident-laser pulse energy of $10.7\text{nJ}$                  | 59 |

| 34 | Peak laser-induced transient currents as a function of laser position along the width of $3.0\mu\text{m} \ge 0.056\mu\text{m}$ T-body and notched-body SOI pFETs with an incident-laser pulse energy of $10.7\text{nJ}$                  | 60 |

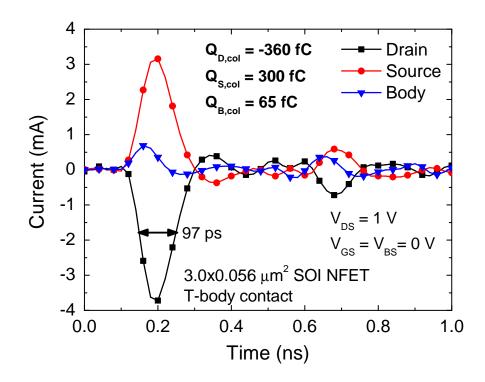

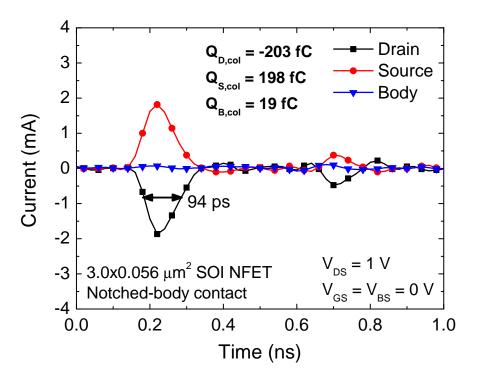

| 35 | Transient currents for incident laser near body contact of a $3.0\mu{\rm m}$ x $0.056\mu{\rm m}$ T-body nFET with an incident-laser pulse energy of $10.7{\rm nJ}$                                                                       | 61 |

| 36 | Transient currents for incident laser near body contact of a $3.0 \mu\text{m}$ x $0.056 \mu\text{m}$ notched-body nFET with an incident-laser pulse energy of $10.7 \text{nJ}$                                                           | 61 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

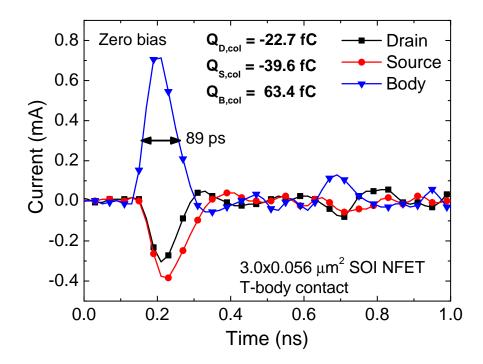

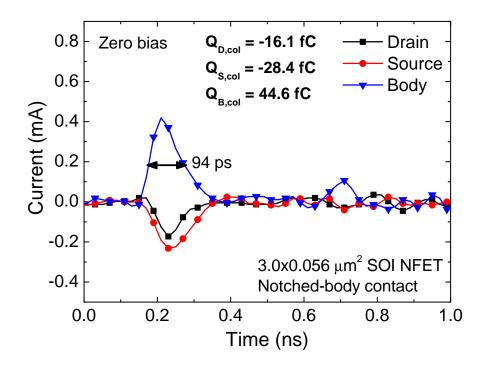

| 37 | Transient currents at zero bias for incident laser pulse near body contact of a $3.0\mu{\rm m}$ x $0.056\mu{\rm m}$ T-body nFET with a laser pulse energy of $10.7{\rm nJ}$                                                              | 63 |

| 38 | Transient currents at zero bias for incident laser pulse near body contact of a $3.0 \mu\text{m} \ge 0.056 \mu\text{m}$ notched-body nFET with a laser pulse energy of $10.7 \text{nJ}$                                                  | 63 |

| 39 | Peak drain and body currents for laser-induced transients as a function of laser position for a $3.0 \mu\text{m} \ge 0.056 \mu\text{m}$ T-body nFET with an incident laser pulse energy of $1.0 \text{nJ}$                               | 64 |

| 40 | Peak drain and body currents for laser-induced transients as a function of laser position for a $3.0 \mu\text{m} \ge 0.056 \mu\text{m}$ notched-body nFET with an incident laser pulse energy of $1.0 \text{nJ}$                         | 65 |

| 41 | Peak transient currents for laser-induced transients as a function of laser position along the width of $3.0 \mu\text{m} \ge 0.056 \mu\text{m}$ T-body and notched-body SOI nFETs with an incident-laser pulse energy of $1.0 \text{nJ}$ | 66 |

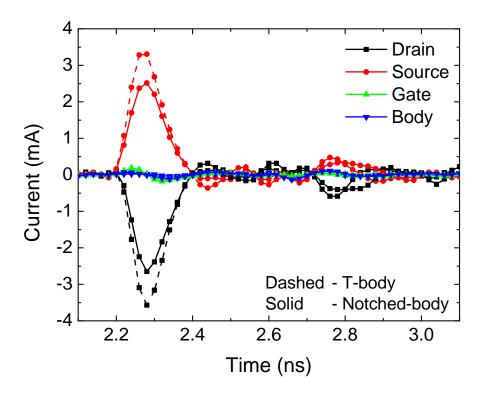

| 42 | Transient currents for a laser position at the center of the device width of $3.0 \mu\text{m} \ge 0.056 \mu\text{m}$ T-body and notched-body SOI nFETs with a laser pulse energy of $1.0 \text{nJ}$                                      | 67 |

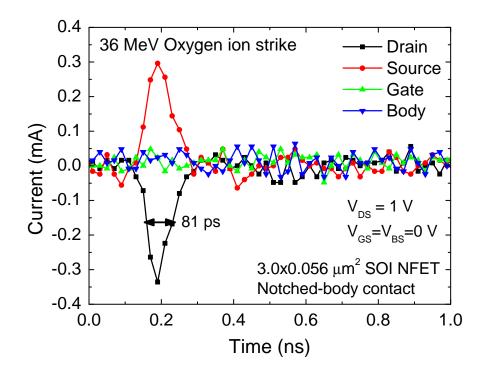

| 43 | Single event transients in a $3.0\mu m \ge 0.056\mu m$ notched-body nFET biased at $V_{DS} = 1.0V$ for a 36 MeV oxygen ion strike                                                                                                        | 68 |

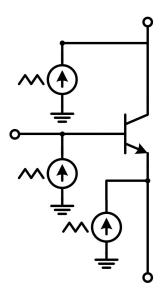

| 44 | Basic configuration of device-level current transient modeling for de-<br>coupled current-injection approaches.                                                                                                                          | 72 |

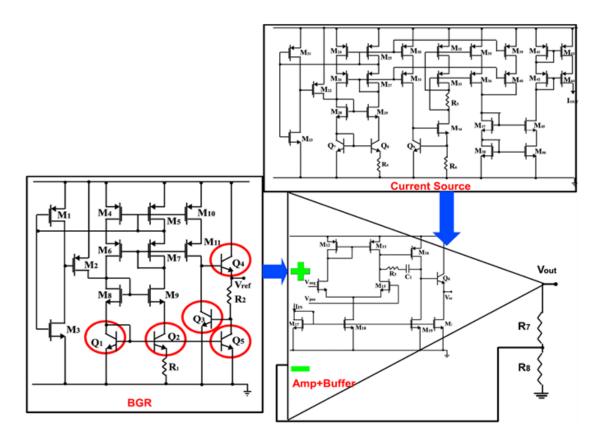

| 45 | SiGe voltage reference circuit schematic                                                                                                                                                                                                 | 76 |

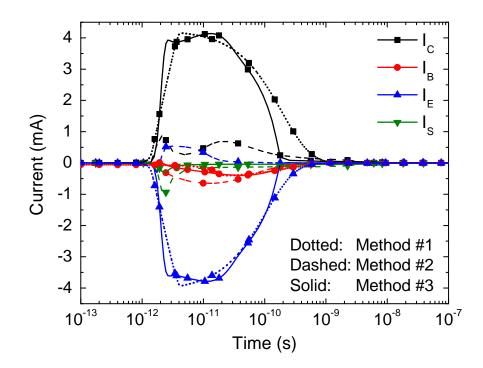

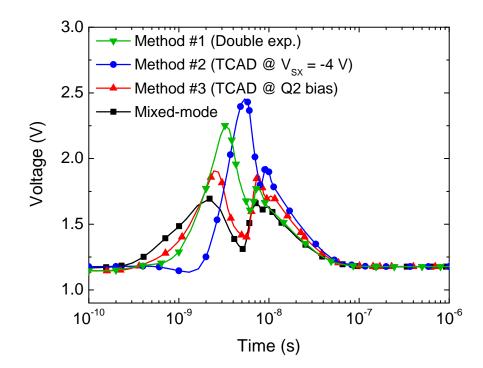

| 46 | Comparison of injected device transients from each simulation approach:<br>(1) double exponential, (2) 3-D TCAD SiGe HBT transients at $V_{SX} = -4 V$ , and (3) 3-D TCAD transients at Q2 biases $\ldots \ldots \ldots \ldots$          | 78 |

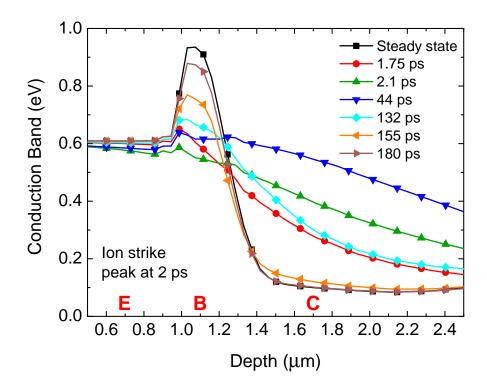

| 47 | Time evolution of the conduction band energy within a SiGe HBT during a simulated ion strike, taken from a line probe through the center of the emitter                                                                                  | 79 |

| 48 | Comparison of device terminal transients computed from a 3D TCAD simulation and from within the full 3-D mixed-mode circuit simulation                                                                                                   | 80 |

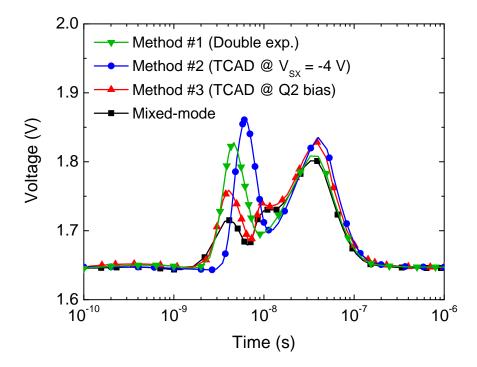

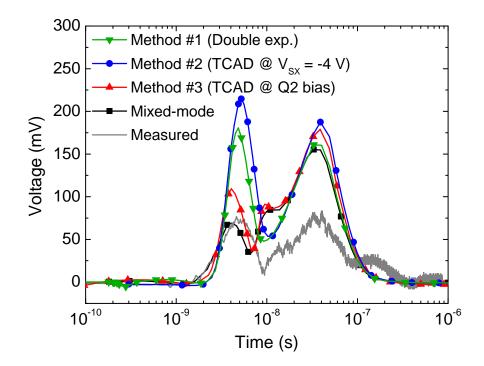

| 49 | Comparison of circuit transients at the BGR output as simulated according to the different approaches                                                                                                                                    | 82 |

| 50 | Comparison of circuit transients at the regulator output as simulated according to the different approaches.                                                                                                                             | 82 |

| 51 | Comparison of simulated and measured transients at the oscilloscope input                                                                                                                                                                                       | 83   |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

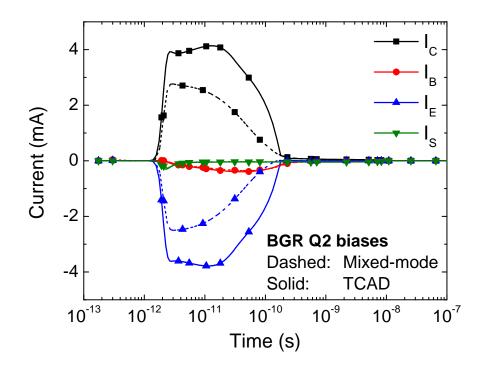

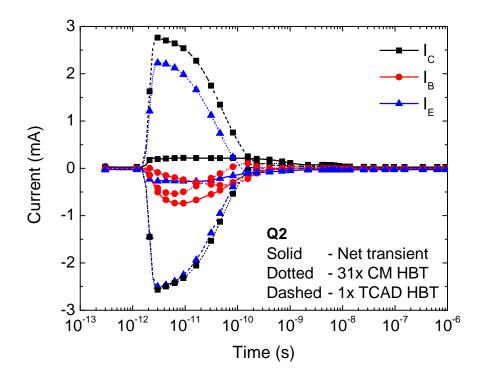

| 52 | Mixed-mode transient currents at Q2                                                                                                                                                                                                                             | 85   |

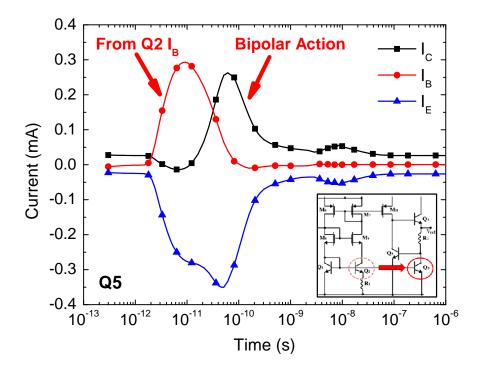

| 53 | Mixed-mode current transients at terminals of Q5                                                                                                                                                                                                                | 85   |

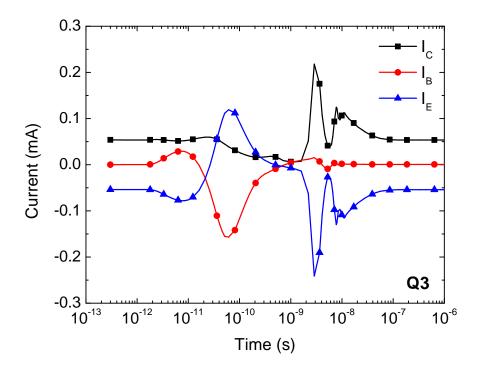

| 54 | Mixed-mode current transients at terminals of Q3                                                                                                                                                                                                                | 86   |

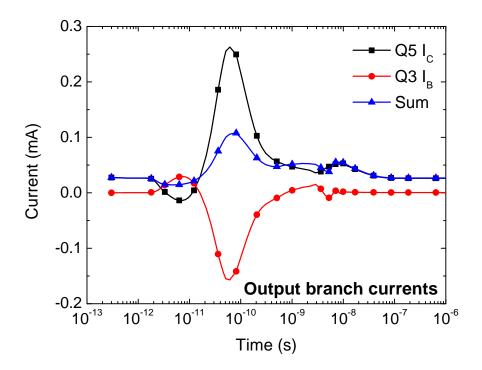

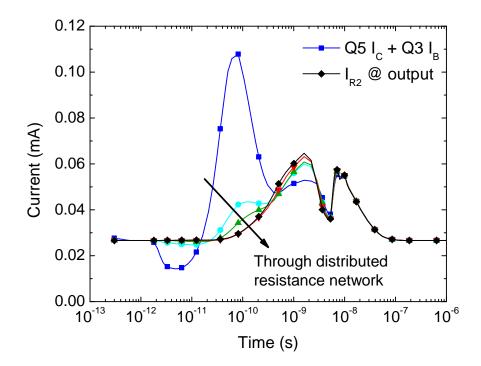

| 55 | Mixed-mode current transients that contribute to the BGR output voltage through the resistive drop across R2                                                                                                                                                    | 87   |

| 56 | Transformation of current transient as it flows through resistor R2, a polysilicon resistor modeled as a distributed network of resistors and parasitic capacitors.                                                                                             | 88   |

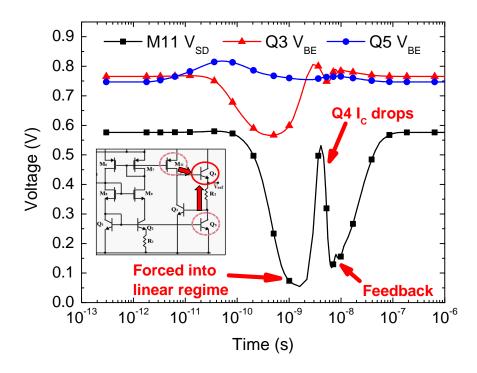

| 57 | Mixed-mode voltage bias transients for transistors M11, Q3, and Q5 .                                                                                                                                                                                            | 88   |

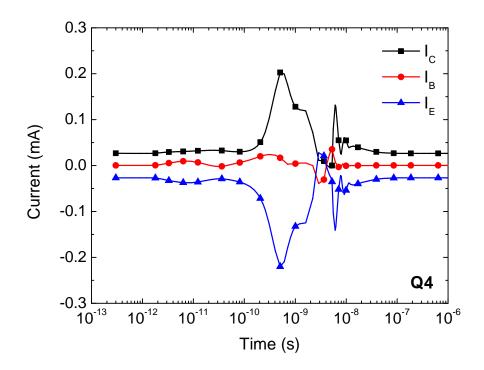

| 58 | Mixed-mode current transients at the terminals of transistor Q4                                                                                                                                                                                                 | 89   |

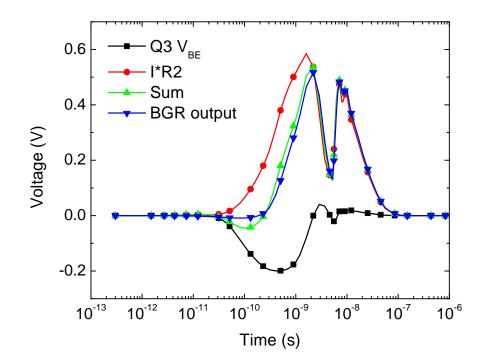

| 59 | Mixed-mode BGR output transient along with its key components: the resistive drop across R2 and the $V_{BE}$ across Q3. The DC offset of each curve has been removed to highlight the contributions of each component to the overall SET.                       | 90   |

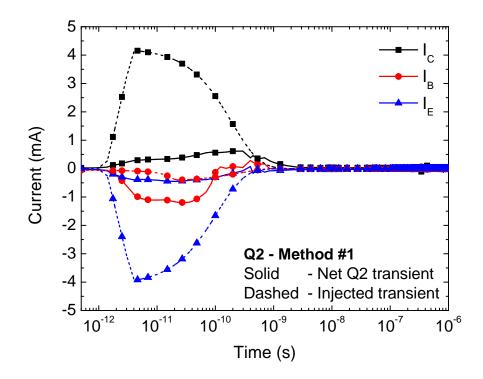

| 60 | Transient currents at Q2: injected current transients (dashed) and net transient currents seen by the remainder of the circuit (solid), computed according to Method $\#1$ .                                                                                    | 92   |

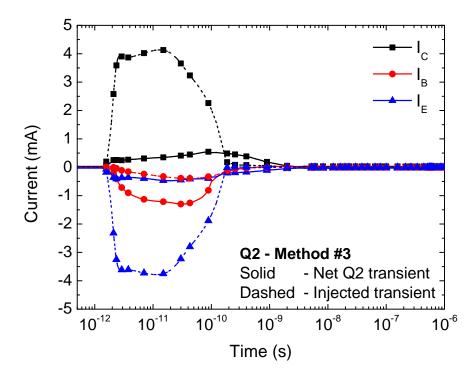

| 61 | Transient currents at Q2: injected current transients (dashed) and net transient currents seen by the remainder of the circuit (solid), computed according to Method $\#3. \ldots \ldots$ | 92   |

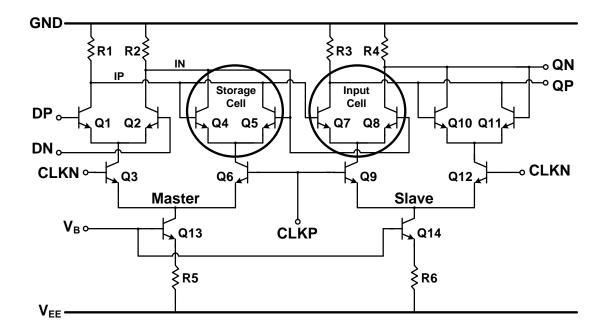

| 62 | Standard SiGe master/slave D flip-flop schematic                                                                                                                                                                                                                | 96   |

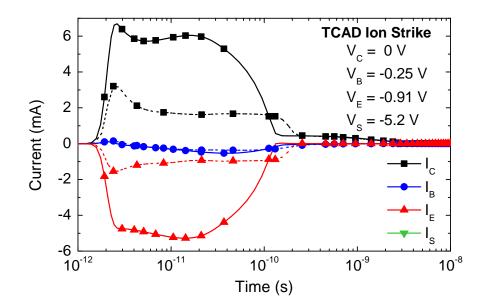

| 63 | 3-D TCAD current transients for a 36 MeV oxygen ion strike to a standalone SiGe HBT with fixed voltage biases corresponding to an off-state HBT.                                                                                                                | 97   |

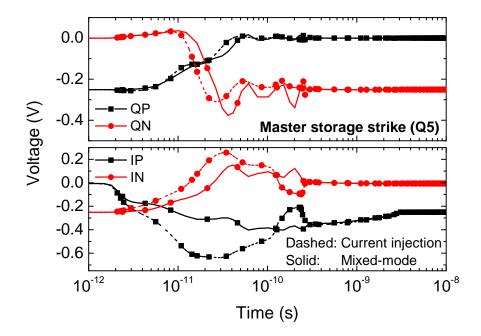

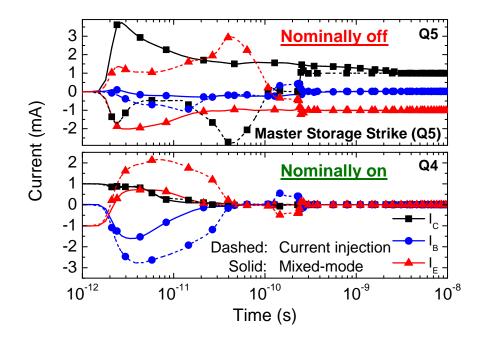

| 64 | Mixed-mode and current-injection voltage transients for an ion strike to transistor Q5                                                                                                                                                                          | 99   |

| 65 | Mixed-mode and current-injection current transients for an ion strike to transistor Q5.                                                                                                                                                                         | 99   |

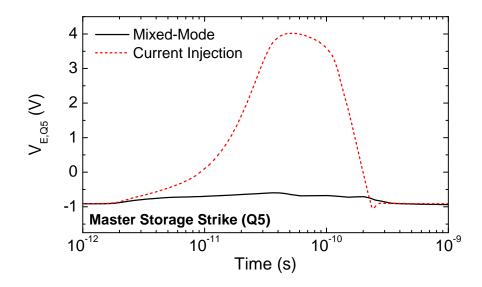

| 66 | Mixed-mode and current-injection emitter voltage transients for an ion strike to transistor Q5.                                                                                                                                                                 | 100  |

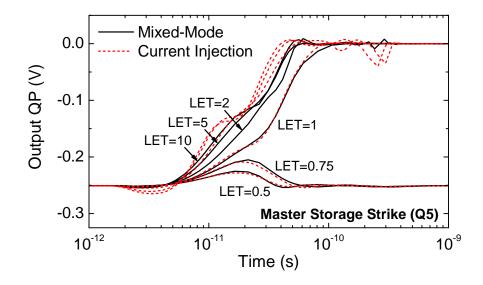

| 67 | Mixed-mode and current-injection output voltage transients for ion strikes to transistor Q5, with the LET varied from 0.5 to $10 \mathrm{MeV} \cdot \mathrm{cm}^2/\mathrm{mg}$ .                                                                                | .101 |

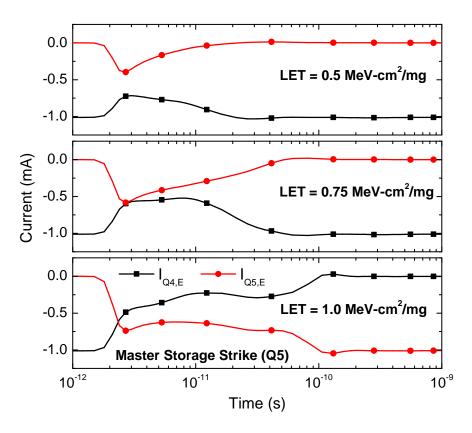

| 68 | Mixed-mode emitter current transients for ion strikes to transistor Q5, for LET values of 0.5, 0.75, and $1.0 \mathrm{MeV} \cdot \mathrm{cm}^2 \cdot \mathrm{mg}^{-1}$ .               | 102   |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

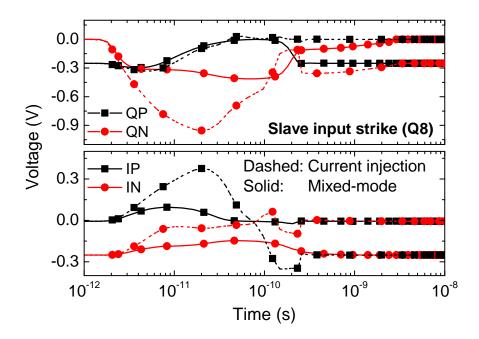

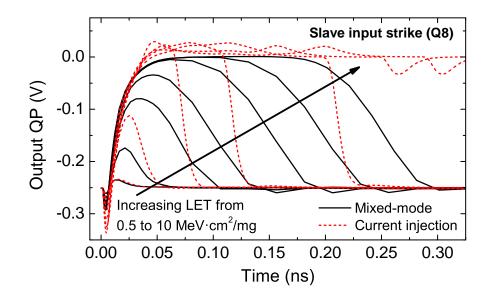

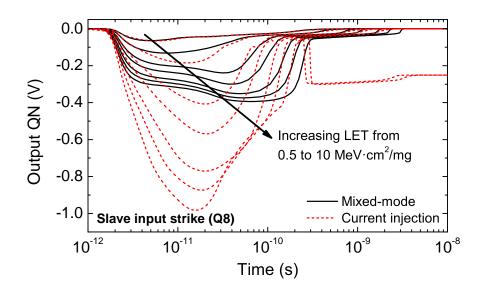

| 69 | Mixed-mode and current-injection voltage transients for ion strike to transistor Q8                                                                                                    | 102   |

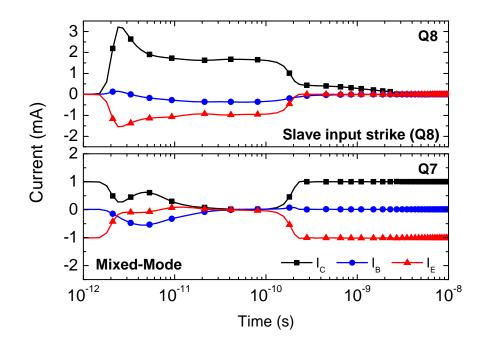

| 70 | Mixed-mode current transients for Q7/Q8 following an ion strike to transistor Q8                                                                                                       | 103   |

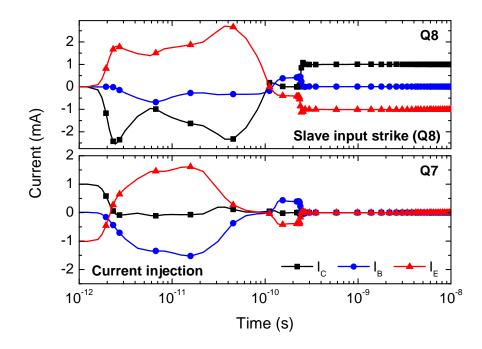

| 71 | Current-injection current transients for Q7/Q8 following an ion strike to transistor Q8.                                                                                               | 104   |

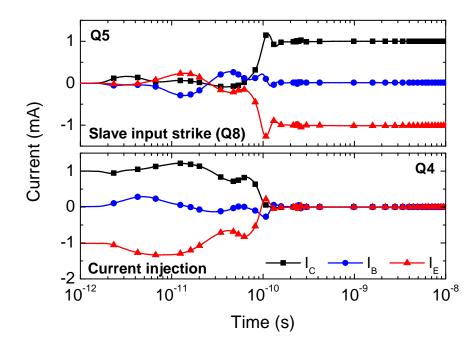

| 72 | Current-injection current transients for Q4/Q5 following an ion strike to transistor Q8.                                                                                               | 105   |

| 73 | Mixed-mode and current-injection output voltage (QP) transients for ion strikes to transistor Q8, with the LET varied from 0.5 to $10 \mathrm{MeV} \cdot \mathrm{cm}^2/\mathrm{mg}$    | g.106 |

| 74 | Mixed-mode and current-injection output voltage (QN) transients for ion strikes to transistor Q8, with the LET varied from 0.5 to $10 \mathrm{MeV} \cdot \mathrm{cm}^2/\mathrm{mg}$ .  | 106   |

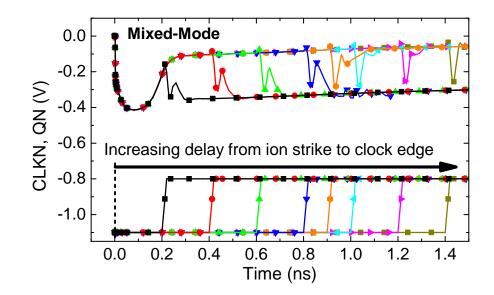

| 75 | Mixed-mode voltage transients for ion strikes to transistor Q8, with increasing delay to the clock edge. The strike time is held constant at $2 \text{ ps.}$                           | 108   |

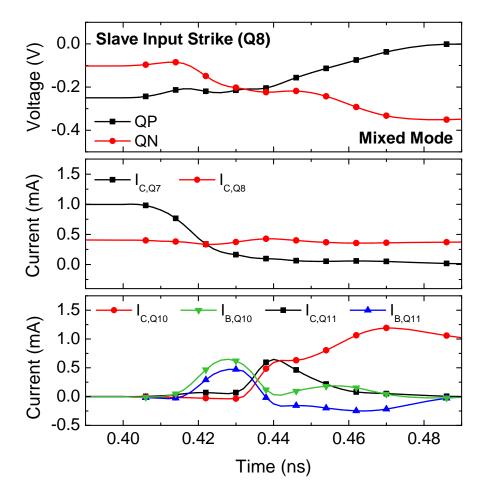

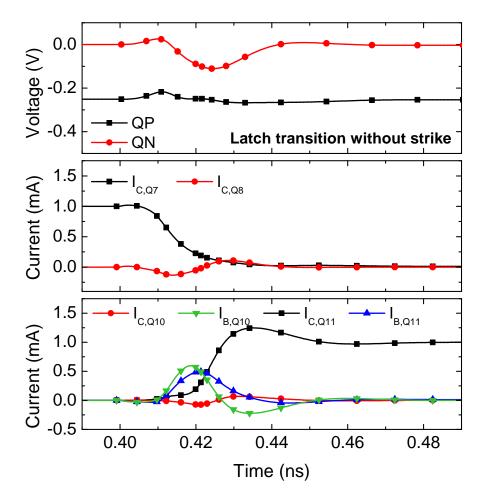

| 76 | Mixed-mode voltage and current transients for an ion strike to transistor Q8 at 2 ps, with the clock transition occurring at $0.4 \text{ ns.} \ldots \ldots \ldots$                    | 109   |

| 77 | Spectre-computed voltage and current transients for a clock transition occurring at 0.4 ns, with no ion strike                                                                         | 110   |

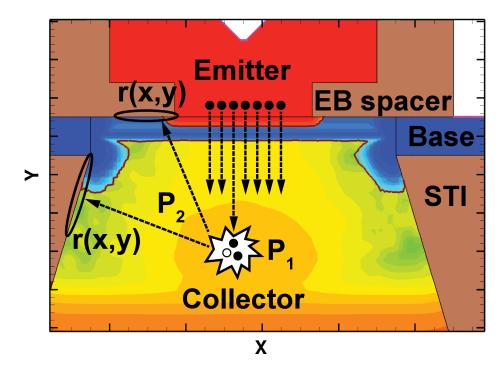

| 78 | Cross-section of 2-D device model used for transient degradation simulations, annotated with the basic process behind the mixed-mode degradation mechanism.                            | 119   |

| 79 | Simulation flow during transient simulation with PMI degradation model enabled.                                                                                                        | 123   |

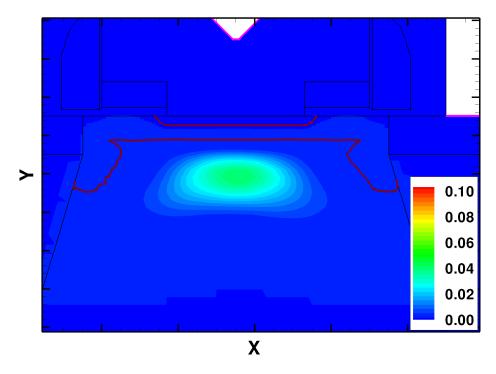

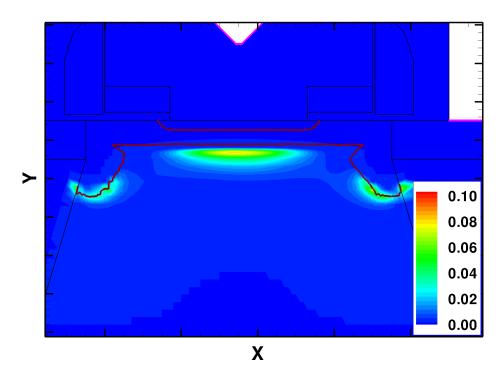

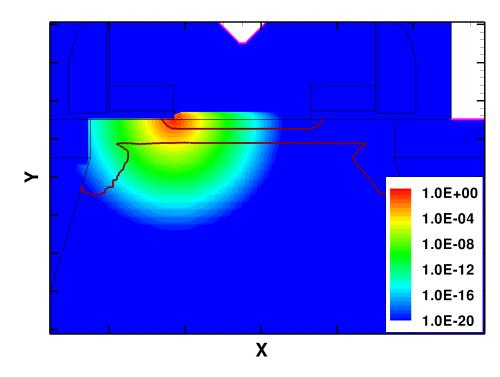

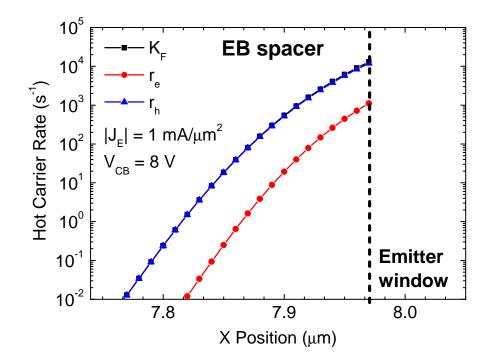

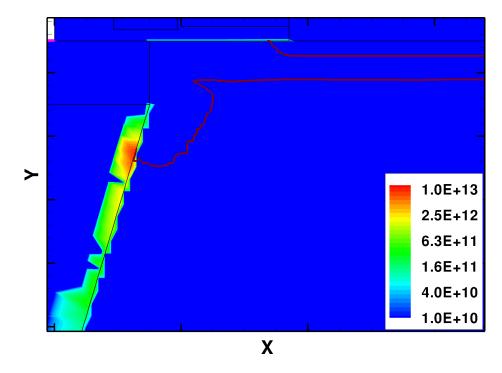

| 80 | Hot electron redirection probability at $t = 1000s$ , for a constant stress condition of $J_E = -1 \text{ mA}/\mu\text{m}^2$ and $V_{CB} = 8 \text{ V.} \dots \dots \dots \dots \dots$ | 124   |

| 81 | Hot hole redirection probability at $t = 1000s$ , for a constant stress condition of $J_E = -1 \text{ mA}/\mu\text{m}^2$ and $V_{CB} = 8 \text{ V}$                                    | 125   |

| 82 | $P_2$ as a function of position through the semiconductor volume, computed for the EB spacer oxide interface vertex nearest the emitter window.                                        | 125   |

| 83 | Rate of hot electrons reaching the left EB spacer oxide interface vertex nearest the emitter window at $t = 1000s$ , as a function of the hot electron origin, for a constant stress condition of $J_E = -1 \text{ mA}/\mu\text{m}^2$ and $V_{CB} = 8 \text{ V.}$ | 126 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 84 | Rate of hot holes reaching the left EB spacer oxide interface vertex nearest the emitter window at $t = 1000s$ , as a function of the hot hole origin, for a constant stress condition of $J_E = -1 \text{ mA}/\mu\text{m}^2$ and $V_{CB} = 8 \text{ V}$          | 126 |

| 85 | Rate of hot carriers reaching the left EB spacer oxide interface at $t = 1000s$ as a function of the x coordinate along the interface, for a constant stress condition of $J_E = -1 \text{ mA}/\mu\text{m}^2$ and $V_{CB} = 8 \text{ V.}$                         | 127 |

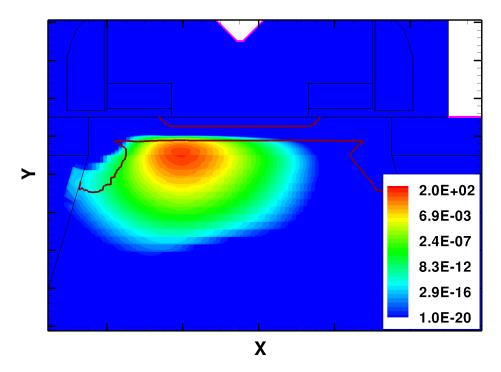

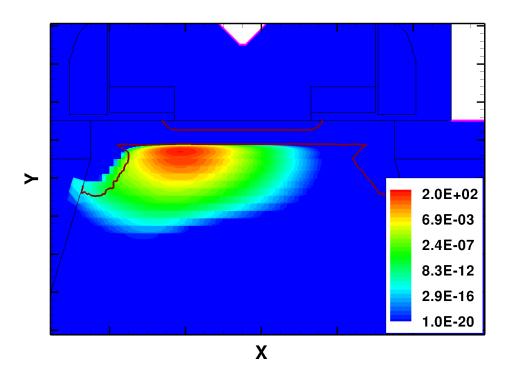

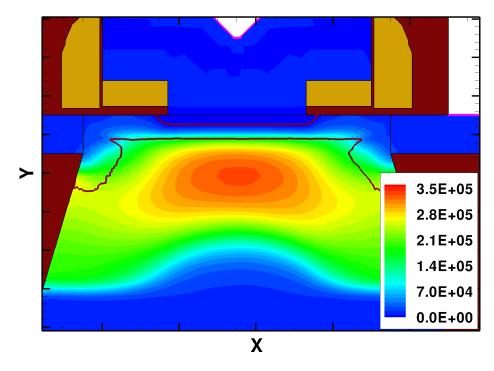

| 86 | Electron effective electric field computed from the electron temperature distribution, for a constant stress condition of $J_E = -1  mA/\mu m^2$ and $V_{CB} = 8  V.$                                                                                             | 128 |

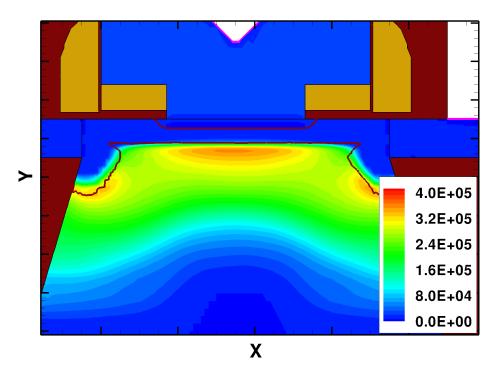

| 87 | Hole effective electric field computed from the electron temperature distribution, for a constant stress condition of $J_E = -1  mA/\mu m^2$ and $V_{CB} = 8  V.$                                                                                                 | 129 |

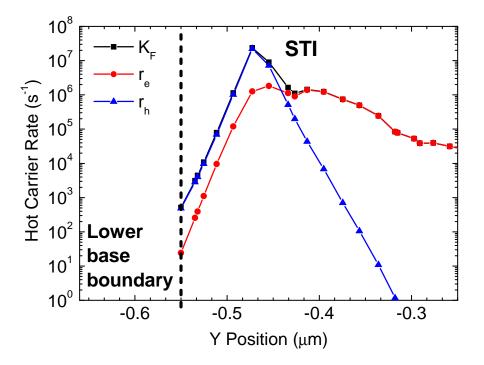

| 88 | Rate of hot carriers reaching the left STI interface at $t = 1000s$ as a function of the y coordinate along the interface, for a constant stress condition of $J_E = -1 \text{ mA}/\mu\text{m}^2$ and $V_{CB} = 8 \text{ V}$                                      | 129 |

| 89 | Interface trap density at $t = 1000s$ , for a constant stress condition of $J_E = -1 \text{ mA}/\mu\text{m}^2$ and $V_{CB} = 8 \text{ V}$                                                                                                                         | 131 |

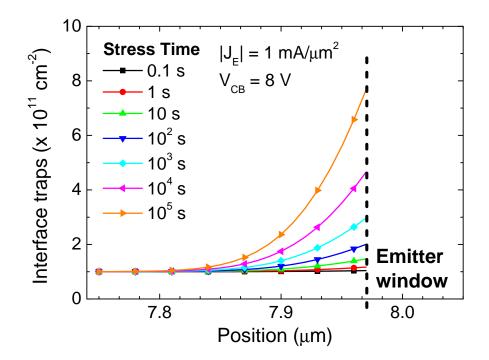

| 90 | Interface trap density along the EB spacer oxide for increasing stress time. The npn SiGe HBT is stressed at $J_E = -1 \text{ mA}/\mu\text{m}^2$ , $V_{CB} = 8 \text{ V}$ .                                                                                       | 132 |

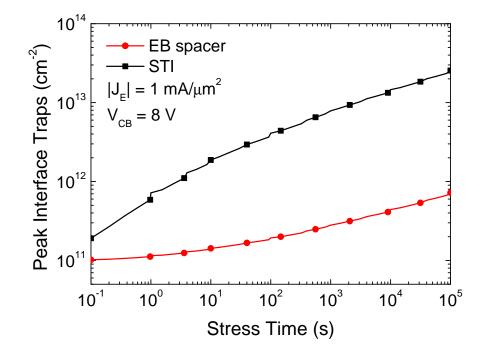

| 91 | Peak interface trap density at the EB spacer and STI oxides as a function of stress time. The npn SiGe HBT is stressed at $J_E = -1 \text{ mA}/\mu\text{m}^2$ , $V_{CB} = 8 \text{ V.}$                                                                           | 132 |

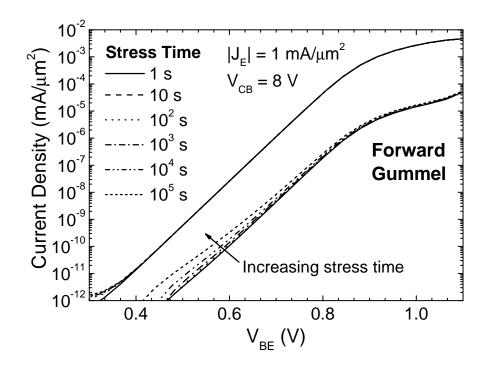

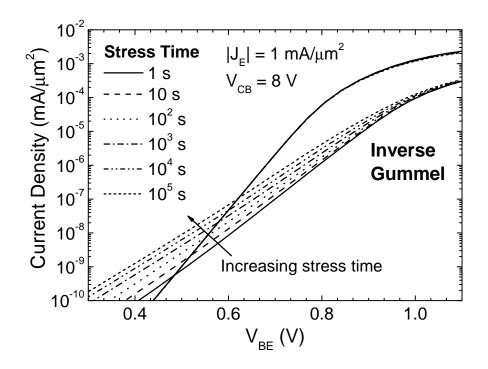

| 92 | Post-stress forward gummel characteristics for stress times ranging from $1{\rm s}$ to $10^5{\rm s},$ with a stress condition of $J_{\rm E}=-1{\rm mA}/{\mu m^2},V_{\rm CB}=8V_{\cdot}$ .                                                                         | 133 |

| 93 | Post-stress inverse gummel characteristics for stress times ranging from $1{\rm s}$ to $10^5{\rm s},$ with a stress condition of $J_{\rm E}=-1{\rm mA}/{\mu m^2},V_{\rm CB}=8V_{\cdot}$ .                                                                         | 134 |

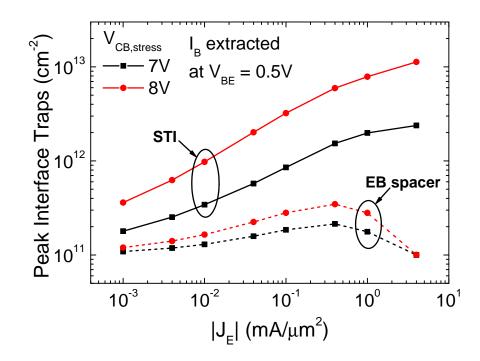

| 94 | Peak interface trap density at the EB spacer and STI oxides for increasing magnitude of emitter current stress. The trap density is extracted after $10^3$ s stress at $V_{CB} = 8 \text{ V}$ .                                                                   | 135 |

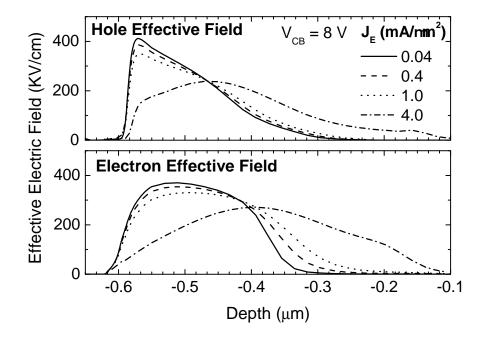

| 95 | Hole and electron effective electric fields, taken from a vertical cut through the center of the npn SiGe HBT, for a range of emitter current stress conditions with $V_{CB} = 8 V. \dots \dots \dots \dots \dots \dots \dots \dots$                              | 135 |

|    |                                                                                                                                                                                                                                                                   |     |

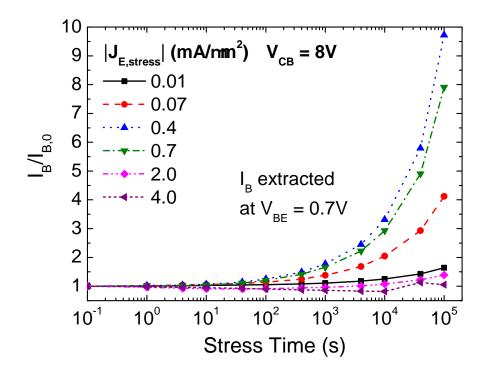

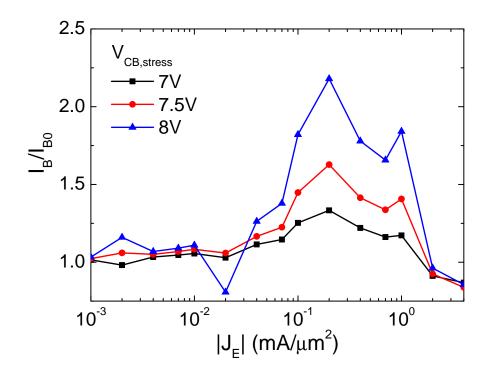

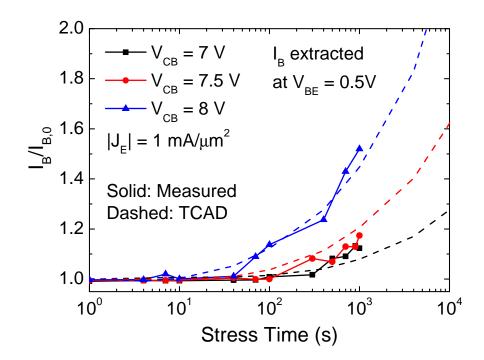

| 96 | Normalized increase in base current as a function of increasing stress time, for a range of emitter current stress conditions with $V_{CB} = 8 V$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 136 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 97 | Normalized increase in base current after $10^3$ s stress as a function of stress condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 137 |

| 98 | $ \begin{array}{l} \mbox{Comparison between simulation and measurement of normalized base} \\ \mbox{current vs. stress time for a range of } V_{CB} \mbox{ stress conditions with } J_E = \\ -1 \mbox{ mA} / \mu m^2 \hdots $ | 138 |

## SUMMARY

The advent of high-frequency silicon-based technologies has enabled the design of mixed-signal circuits that incorporate analog, RF, and digital circuit components to build cost-effective system-on-a-chip solutions. Emerging applications provide great incentive for continued scaling of transistor performance, requiring careful attention to mismatch, noise, and reliability concerns. If these mixed-signal technologies are to be employed within space-based electronic systems, they must also demonstrate reliability in radiation-rich environments. SiGe BiCMOS technology in particular is positioned as an excellent candidate to satisfy all of these requirements. The objective of this research is to develop predictive modeling tools that can be used to design new mixed-signal technologies and assess their reliability on Earth and in extreme environments. Ultimately, the goal is to illuminate the interaction of device- and circuit-level reliability mechanisms and establish best practices for modeling these effects in modern circuits. To support this objective, several specific areas have been targeted first, including a TCAD-based approach to identify performance-limiting regions in SiGe HBTs and support device optimization, measurement and modeling of carrier transport parameters that are essential for predictive TCAD simulations, and measurement of device-level single-event transients to better understand the physical origins and implications for device design. These tasks provide the foundation for the bulk of this research, which addresses circuit-level reliability challenges through the application of novel mixed-mode TCAD techniques. All of the individual tasks are tied together by a guiding theme: to develop a holistic understanding of the challenges faced by emerging broadband technologies by coordinating results from material, device, and circuit studies.

## CHAPTER I

## INTRODUCTION

In the past decade, there has been extraordinary growth in the global telecommunications market, driven largely by emerging broadband-communications applications, such as mobile communications (GSM/CDMA), WLAN, GPS, DSL, and satellite communications. At the core of this growth is the development of monolithic integrated circuit (IC) technologies that have made it possible to build complex integrated systems at reasonable cost. In part, this growth been enabled by the relentless scaling of core device-performance metrics; more importantly, however, technologies have been developed to support increasingly high levels of integration, which allow a wide variety of functionality to be defined together on the same chip, simplifying packaging and reducing total die count.

One increasingly important segment of the broadband-communications market is high-speed communications with satellites in orbit around the earth. Extra-terrestrial electronics systems are required to operate in extremely harsh environments and are subjected to both particle radiation and cryogenic temperatures. Cryogenic temperatures induce significant changes in all aspects of device operation. The fundamental physical properties that drive these changes must be accurately characterized to provide a solid foundation for the development of robust devices and circuits. Furthermore, radiation effects introduce serious reliability concerns that must be addressed before a particular technology can become viable for extreme-environment applications.

Among the building blocks for broadband technologies are low-noise amplifiers, power amplifiers, and voltage-controlled oscillators. The key performance metrics for these blocks include low power consumption, high gain, high-frequency operation, high dynamic range, good linearity, and low noise. However, these circuit-level metrics are necessarily coupled to corresponding device-level metrics; thus, an understanding of device-level performance is critical to achieving circuit and system-level performance gains. Any useful analysis of device performance depends on a solid understanding of the fundamental physical processes that operate within the device.

## 1.1 Broadband IC Technologies

The advent of high-frequency silicon-based technologies has enabled the design of mixed-signal ICs that incorporate analog and radio-frequency (RF) circuit components, including the requisite passive elements and interconnects, with highly-integrated digital circuit components. Leveraging the economy of scale provided by silicon IC manufacturing, these technologies allow designers to build cost-effective system-on-a-chip (SoC) or system-in-a-package (SiP) solutions for a variety of communications applications [26]. At present, there exist two families of high-frequency silicon-based mixed-signal technologies: highly-scaled RF complementary-metal-oxide-semiconductor (RF-CMOS) and silicon-germanium bipolar-CMOS (SiGe BiCMOS), with each possessing its own unique advantages.

Aggressive lithographic scaling, new materials, and process innovations such as strain engineering have enabled the integration of RF-optimized metal-oxidesemiconductor field-effect-transistors (MOSFETs) into traditional digital CMOS technology. Strain-engineered RF-CMOS on silicon-on-insulator (SOI) represents the leading edge of CMOS technology, possessing advantages over bulk RF-CMOS by minimizing parasitics, improving isolation, decreasing leakage, improving short-channel effects, and improving single-event upset (SEU) tolerance [58]. The combination of enhanced RF performance with state-of-the-art digital CMOS makes RF-CMOS on SOI an attractive technology for system-on-a-chip applications such as integrating RF front ends and baseband analog/digital circuitry on a single chip. Similarly, SiGe BiCMOS technology is well suited for a wide variety of analog, RF, and high-speed digital circuits, because of its high-frequency operation, low broadband and 1/f noise, high transconductance per unit area, and compatibility with conventional CMOS fabrication. Modern SiGe technology is almost universally implemented with the high-frequency SiGe heterojunction bipolar transistor (HBT) as an add-on to a core digital CMOS technology (SiGe HBT + Si CMOS). Consequently, within a mixed-signal IC, this allows the SiGe HBT to be used where it is best suited, that is, within RF, microwave, analog, and high-speed digital circuit components, whereas Si CMOS can be used to its greatest advantage within lower-performance memory and digital circuit components [23]. Although InP HBTs have demonstrated greater current-gain and power-gain cutoff frequencies ( $f_T$  and  $f_{max}$ ) at higher breakdown voltage (BV<sub>CEO</sub>) than their SiGe HBT counterparts, scaling trends suggest that THz levels of performance could be achieved by SiGe HBTs at useful levels of breakdown, combining the enormous integration and cost advantages of silicon manufacturing with device performance comparable to III-V technologies [115].

Comparing SiGe BiCMOS to RF-CMOS, one key difference is that the frequency performance of the SiGe HBT is primarily determined by its vertical profile, whereas RF-optimized MOSFETs depend on the minimum feature size allowed at a particular lithography node. Consequently, SiGe HBTs enjoy roughly a two-generation lithographic scaling advantage over CMOS for fixed performance. Since lithography has increasingly become the largest fixed cost for IC manufacturing, this gives the SiGe HBT a significant cost advantage over RF-CMOS, outweighing the cost of the additional masks needed to define the SiGe HBT in the BiCMOS process [24]. Furthermore, CMOS transistors face increasingly difficult challenges with device-to-device matching as they are scaled because of larger relative variations in the lateral dimensions, further compounded by increased short-channel effects and the high-k dielectrics and metal gate used in the most advanced technology nodes. In contrast, matching in bipolar

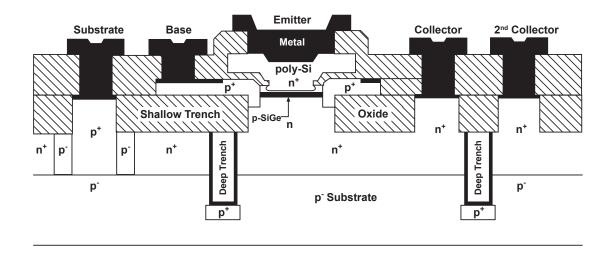

Figure 1: Cross-section of a representative first-generation SiGe HBT.

devices tends to improve with scaling as a result of the increase in doping levels. Highly-scaled RF-CMOS also presents serious challenges for circuit designers because of poor output conductance, high leakage currents, degraded low-frequency noise, and low breakdown voltages. For the SiGe HBT, breakdown voltage is becoming one of the major scaling bottlenecks, although breakdown voltages remain higher than CMOS for fixed frequency performance [115].

## 1.2 The SiGe HBT

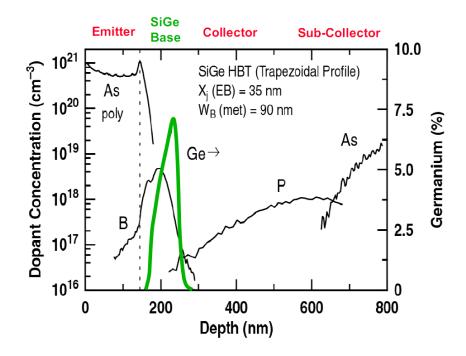

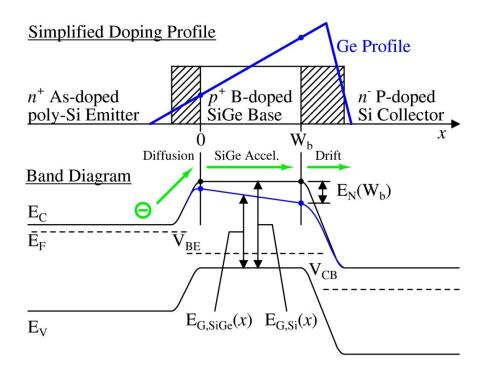

Fundamentally, the SiGe HBT is very much the same as its Si bipolar-junction transistor (BJT) counterpart, except that in the HBT a graded Ge profile is introduced in the base layer, which allows device designers to exercise bandgap-engineering for the first time in silicon-based technology. The cross-section of a representative firstgeneration SiGe HBT is shown in Figure 1. Its corresponding doping and Ge profiles are given in Figure 2. In the resulting energy-band diagram (Figure 3), the Ge profile produces a graded offset that is primarily manifested in the conduction band. Although the inherent band offset caused by the Ge profile occurs in the valence band, it is effectively translated to the conduction band. With a constant p-type doping in the base, both the Fermi level and the energy difference between the Fermi level

Figure 2: Measured doping profile of a representative first-generation SiGe HBT.

and valence band are fixed; the Ge grading induces a valence band offset, but because the Fermi level must remain constant in equilibrium, it must decrease in energy along with the conduction-band edge.

For DC operation, one fundamental impact of the graded conduction-band offset is to enhance minority-electron transport across the base by inducing a drift field. In addition, the Ge content at the emitter-base (EB) junction will reduce the potential barrier for electron injection from the emitter to the base, yielding exponentially greater electron injection for the same applied  $V_{BE}$  (i.e. higher current gain). Finally, a finite Ge content at the collector-base (CB) junction will positively influence the output conductance of the transistor (i.e. higher Early voltage), since the smaller base band gap near the CB junction effectively weights the base profile so that back side depletion of the neutral base with increasing  $V_{CB}$  is suppressed [24].

For AC operation, the Ge grading-induced drift field will intuitively lead to a reduced base transit time, which typically is the limiting transit time that determines

**Figure 3:** Energy-band diagrams for a Si BJT and a graded-base SiGe HBT, biased in forward active mode at low-injection.

performance metrics such as the maximum operating frequency. In addition, the Ge-enhanced injection of electrons from the emitter into the base dynamically produces a back-injection of holes from the base into the emitter. This reduces the emitter charge-storage delay time, which is reciprocally related to the AC current gain of the transistor [24].

These DC and AC effects are dependent on the profile of the Ge content, especially the mole fraction at the EB junction and the degree of grading across the neutral base. However, trade-offs in profile design exist because of the fact that SiGe film stability limits the total Ge content that can be present. Consequently, different Ge profiles can be designed to achieve specific performance goals. For example, a triangular profile beginning at the EB junction and peaking just inside the CB space-charge region would maximize the frequency performance and Early voltage while providing little improvement to the current gain. A box-shaped profile that is flat across the base would maximize the DC current gain, but would not enhance electron transport across the base. Alternately, a trapezoidal profile or a profile as illustrated in Figure 3 would simultaneously improve all performance metrics, albeit to a lesser extent.

At present, state-of-the-art npn SiGe HBTs have been demonstrated with peak  $f_T$  and  $f_{max}$  above 400 GHz at room temperature [20, 117]. Great motivation for continued performance scaling exists as a result of increasing performance requirements for existing RF through mm-wave applications, as well as emerging applications such as mm-wave to sub-mm-wave radars and sensors for security, automotive, and medical applications. With the SiGe HBT breakdown voltage becoming a key challenge to performance scaling as a result of the inherent tradeoff between peak  $f_T$  and breakdown voltage, the collector doping profile and Ge retrograde in the CB junction must be carefully designed. Moreover, the development of next-generation SiGe HBTs will require implementation of new structures to minimize base resistance ( $R_B$ ) and collector-base capacitance ( $C_{BC}$ ) [116]. Developing and enhancing effective technology-computer-aided-design (TCAD) techniques will remain a key tool in addressing these scaling challenges by identifying the limiting factors during iterative optimization of new device designs.

## 1.3 Extreme Environment Electronics

Radiation fields result from the magnetosphere and proton and electron belts surrounding the earth. Solar wind particles trapped in the earth's magnetic field result in the "Van Allen" radiation belts, which are particularly concerning for the orbital paths of satellites [60, 61]. As a result of operating in this extreme environment, electronic systems often suffer from degraded performance or altogether fail after a length of time. Radiation-induced damage is of particular concern as technologies scale, since changes to the device structure and fabrication process can potentially lead to increased radiation sensitivity. Device and circuit performance degradation can be attributed to three primary mechanisms: displacement damage, ionization damage, and single-event effects (SEE). The first two mechanisms are typically addressed together as total-ionizing-dose (TID) damage. SEE can be divided by the various types of errors that can be caused within a circuit. For example, temporary errors include single-event transients (SET), single-event upset (SEU), and multiple-bit upset (MBU), whereas permanent errors include single-event latchup (SEL), single-event burnout (SEB), and single-event gate rupture (SEGR).

#### 1.3.1 Radiation Effects in CMOS

CMOS technologies suffer from increased off-state leakage as a result of TID radiation. The primary cause of leakage in modern CMOS platform is traps that are created along the shallow trench isolation (STI) sidewalls at each end of the transistor, creating leakage paths between the source and drain terminals [29]. TID radiation hardness appears to improve with device scaling, but studies show considerable variability between different manufacturers and even different fabrication lots of the same IC [51]. In SOI CMOS, considerable complexity is introduced with the addition of the SOI buried oxide, in which positive trapped charge can result in TID-induced back-channel leakage. The most effective mitigation technique to achieve multi-Mrad( $SiO_2$ ) TID hardness is to employ an annular MOSFET geometry; however, the penalties of this approach include increased layout area and parasitics, limitations in width to length ratio, a lack of existing compact models, and the inherent device asymmetry [29].

Continued scaling of CMOS has led to an increased SEE sensitivity both in SOI and bulk platforms. Although SOI CMOS is inherently immune to latchup and more resistant to SEE because of the elimination of charge collection from the substrate [28], its SEE sensitivity increases nonetheless as circuit switching speeds increase and the amount of charge that represents stored information is reduced [29]. As a result, SEE have become a significant reliability challenge not only for space-based CMOS technologies, but even for advanced Earth-based CMOS technologies. SET may set fundamental limits on the operating speed of radiation-hardened ICs, and studies have shown that many newer ICs suffer complex failure modes such as single-event functional interrupt (SEFI) that may require a device reconfiguration or power cycle for recovery [29]. Thus, SEE mitigation will be critical to the design of any reliable circuit operating in terrestrial, high-altitude, or space environments. To date, a variety of mitigation techniques have successfully been implemented, including device-level hardening through cross-coupled feedback resistors [88], circuit-level hardening through internally-redundant storage elements [9], and system-level hardening through error detection and correction circuitry.

#### 1.3.2 Radiation Effects in SiGe HBTs

Due to its inherent tolerance to multi-Mrad(SiO<sub>2</sub>) TID radiation and improved DC and AC performance at cryogenic temperatures [23], SiGe BiCMOS technology has emerged as a strong contender for extreme-environment applications such as spacebased electronics, which must operate in radiation-rich conditions and at cryogenic temperatures (e.g., 43 K in the shadowed polar craters of the Moon). In bipolar transistors, unlike MOSFETs, the primary transistor action occurs away from any Si-SiO<sub>2</sub> interfaces; thus, the SiGe HBT is inherently hardened to TID damage without any process or layout modifications. Some TID-induced base leakage current does appear as a result of traps created along the EB spacer oxide, but this current is negligible up to multi-Mrad(SiO<sub>2</sub>) and TID hardness has been demonstrated across all existing SiGe technology nodes [25, 54, 104]. SEE, however remain an area of concern for space-based SiGe circuits, and the inherent susceptibility of SiGe digital logic circuits to SEU [62, 84] is further compounded by the apparent increase in SEU (proton) sensitivity at cryogenic temperatures [102].

To mitigate SEE in SiGe ICs, a variety of circuit- [50, 62, 76] and device-level hardening techniques [82, 103] have been implemented with minimal impact on system complexity. These radiation-hardening-by-design (RHBD) techniques can be supported considerably by modeling and simulation—at the device level through 3-D physical TCAD simulations of ionizing radiation effects, and at the circuit level either through traditional compact modeling [71, 78] or true mixed-mode simulations (compact models + 3-D TCAD) [106, 108]. Nevertheless, effective optimization of RHBD techniques can only be performed when there is sufficient fidelity between simulated and measured SET. The SEE response at the circuit level depends heavily on the circuit topology as a result of feedback effects, varying device biases, and for certain circuits, dynamic biases that evolve on the same time scale as that of measured device SET. Moreover, the importance of addressing this issue when modeling SET grows as circuit response times scale and become comparable to the duration of the individual transistor transients [106]. Clear guidelines must be established as to which approaches to modeling SET are valid for various conditions (circuit topology, technology node, device geometry, environment, etc.).

## 1.4 Long-Term Device and Circuit Reliability

In addition to radiation-related reliability concerns, device technologies must be ensured to be sufficiently immune to all types of degradation mechanisms associated with any extreme operating conditions. Circuits and systems impose a wide range of voltage and current conditions that can cause degradation of the device building blocks, passive elements such as inductors and capacitors, and back-end-of-line (BEOL) metal interconnects. Reliability of a given technology means that under typical circuit operating conditions, the circuits—and the systems ultimately constructed from those circuits—must not wear out or degrade to a level at which they fail over the entire functional life of the system. Reliability is ensured by extensive testing of each individual component of a given technology, each of which possesses unique degradation mechanisms.

Considering bipolar transistors, reliability has historically been ensured by first subjecting the devices to extreme operating conditions for extended periods of time, then quantifying the change in device figures-of-merit (FoM), and finally inferring the maximum stress conditions that ensure a tolerable change in those FoM over the lifetime of the device. Traditionally, the two extreme operating conditions imposed upon bipolar transistors have been: (1) a larger reverse bias stress applied to the emitter-base junction, causing hot-carrier damage (hot electrons, hot holes, or both), and (2) a high forward collector current density stress. Accelerated stress conditions are typically applied to minimize the stress time required to produce sufficient damage, and testing is performed at either elevated (for high  $J_{\rm C}$  stress) or reduced (for reverse EB stress) temperatures to impose worst-case stress conditions. During a technology's qualification process, various process parameters will be tuned until all of the desired reliability metrics have been met. This methodology has been the standard practice for bipolar technologies for the past several decades, but more recent studies of the high-speed SiGe HBT prove that this methodology does not capture all possible degradation mechanisms [22]

The modern SiGe HBT has evolved significantly from the older Si bipolar technologies that were originally designed primarily for digital logic applications. The device speeds are much higher (with much higher peak doping concentrations), and in addition to the Ge grading of the SiGe base, many advancements have been made in the physical device structure that make it radically different from its Si BJT predecessor. Consequently, the full scope of possible degradation mechanisms must be reconsidered, including reverse EB and forward- $J_C$  stress, but also addressing the impact of Ge film stability on process yield, radiation-induced degradation, breakdown voltage, bias instabilities, and impact-ionization-induced mixed-mode stress. The mixed-mode stress degradation mechanism, first reported in [118], poses a unique challenge for RF and mixed-signal applications because it arises when a high collector current density and high collector-base voltage are applied simultaneously to a SiGe HBT; these of course are common bias conditions for many RF and mixed-signal circuits. It can be distinguished from conventional reverse EB and forward- $J_C$  stress by the inverse-mode  $I_B$  degradation as well as its unique geometrical dependence. Fundamentally, the mixed-mode degradation mechanism results from hot carriers that originate in the collector-base junction, traverse to the shallow-trench isolation (STI) oxide and emitter-base (EB) spacer oxide interfaces, and depassivate silicon dangling bonds to cause a net increase in interface traps.

A variety of experimental [11, 16, 18, 118, 119, 120] and theoretical studies [15, 16, 110] of the mixed-mode degradation mechanism have been published. In the theoretical work, ideas have often been appropriated from studies of CMOS reliability and hot-carrier injection, such as the lucky-electron model [38, 41] and the reactiondiffusion model [42, 77, 83] to explain the dynamic nature of trap passivation and depassivation at the Si-SiO<sub>2</sub> interfaces. What has been made clear through all of this work is that the degradation mechanisms of the SiGe HBT are by nature highly dependent on the specific device technology, circuit type, and time-dependent circuit operating conditions. The reliability response of single device at fixed bias conditions does not provide sufficient information to assess overall circuit and system reliability, since the mixed-mode degradation mechanism exhibits a complex spectrum of damage and annealing regions [18, 19]. Thus, much more research is needed to establish methods by which the overall degradation response of modern mixed-signal circuits can be accurately predicted.

## 1.5 Research Objectives

Throughout the history of the semiconductor industry, the principal driving force behind IC technology innovation has been device scaling. The reduction of device dimensions has led to increasing levels of integration, a trend recognized by the rise of labels such as small-scale integration (SSI), medium-scale integration (MSI), large-scale integration (LSI), and very-large-scale integration (VLSI), which refer to the total number of transistors on a given IC. At present, ICs with greater than one billion transistors are commonly available. However, simply scaling transistor dimensions to improve speed and transistor count is not sufficient to maintain the technological growth necessary to meet the challenges of emerging mixed-signal and RF applications. Replacements are needed for costly III-V IC components to drive down costs and facilitate design of complete SoC solutions. This requires continued scaling of silicon-based transistor performance, improving peak cutoff frequencies, gain, and other relevant performance metrics while minimizing mismatch, noise, and reliability concerns. Furthermore, as mixed-signal technologies become more widely accepted, they must overcome the additional hurdle of validation for reliable operation in extreme environments if they are to be employed within satellite or other spacebased electronic systems. SiGe BiCMOS technology in particular is positioned as an excellent candidate to satisfy all of these requirements. The present research addresses performance-scaling and reliability of the SiGe HBT as well as operation of state-of-the-art CMOS and HBT devices in extreme environments. The purpose of this research is to develop enhanced predictive modeling tools that can be used to design new devices and subsequently predict their reliability on Earth and in extreme environments. Experimental measurements have been used to benchmark and validate these tools.

A significant amount of research has been completed to enhance predictive-modeling capabilities for advanced broadband technologies that have great promise for extremeenvironment applications. This research has leveraged access to the IBM 45-nm RF-CMOS platform as well as multiple generations of commercially-available SiGe BiCMOS technology to conduct experimental measurements for support and validation of new modeling approaches. Contributions of this research include improved modeling tools to facilitate continued performance scaling of the SiGe HBT, calibration of TCAD-compatible physical models for extreme environments, new measurements of device-level single-event transients, and improved modeling of circuit-level single-event transients. First, an improved 2-D transit time analysis is introduced in Chapter 2. This tool greatly enhances device optimization by enabling device designers to very quickly extract the  $f_T$  from a TCAD device model and identify the spatial distribution of the contributions to the total device delay. Subsequently, experimental measurements of recombination lifetime and resistance in a SiGe BiCMOS technology are reported in Chapter 3 and used to calibrate models of fundamental carrier-transport parameters that are key to accurate modeling of single-event effects. Chapter 4 presents and analyzes experimental measurements of SETs captured for the first time from a commercial 45-nm RF-CMOS technology. Chapter 5 builds upon the foundation of the material and device research from Chapters 2-4 to achieve a new understanding of underlying SET mechanisms and establish best practices for modeling circuit-level SET. In Section 5.2, existing SET data from a SiGe voltage reference is used to investigate the accuracy of various circuit-level SET modeling approaches, identifying the limitations of each approach and providing new insight into best practices for modeling circuit SET in different circuit topologies and device technologies. A similar approach is then applied in Section 5.3 to a building-block of digital circuits, the D flip flop, to reveal pitfalls in conventional circuit SET modeling approaches and highlight coupled mixed-mode TCAD simulations as an essential tool for understanding SEE in modern IC technologies. Chapter 6 extends this mixed-mode TCAD approach to address long-term device and circuit reliability due to hot carrier-induced degradation. In addressing circuit reliability associated with transient radiation effects, physicsbased TCAD models of ion-strike charge collection are embedded in a compact model circuit environment to assess the impact on circuit operation. In the same way, physicsbased TCAD models can be used to model device operation at or beyond classical "safe

operating area" (SOA) limits, where complexities arise such as pinch-in instabilities, thermal effects, current-dependent breakdown phenomena, complex 3-D effects, and stress-induced leakage. Finally, Chapter 7 will summarize the key contributions of this research and highlight the critical topics for which further research is needed to support the development of high-performance, reliable broadband IC technologies.

## CHAPTER II

# IMPROVED TRANSIT-TIME ANALYSIS FOR SIGE HBT PERFORMANCE OPTIMIZATION

Developing and enhancing effective TCAD optimization techniques will enable the design of more highly scaled device profiles. One such technique is the quasi-static transit-time analysis [26, 99, 109], which enables a detailed look at the regional contributions to the total transit time through the physical device. A key advantage of this technique is that it allows one to rapidly quantify and visualize the dynamic performance of a given device profile in greater detail than traditional frequency-domain simulations, and in only a fraction of the computational time. Moreover, since this technique is based on a DC bias-sweep simulation, the current gain  $\beta$  can be extracted simultaneously with the cutoff frequency, f<sub>T</sub>. Variations of this technique have been successfully applied to npn SiGe HBTs at several different scaling nodes [2, 6, 21, 53, 96, 97] as well as complementary-SiGe (C-SiGe) HBTs [13].

In addition to estimating the cutoff frequency of a device, transit-time analysis can also provide insight into the regional contributions to its total delay time. For a 1-D transit-time analysis, the extraction of regional transit-time components is relatively straightforward [2, 53, 96, 109]. However, proper optimization of modern SiGe HBTs requires 2-D or even 3-D simulations to capture the intricacies of effects such as the high-injection Kirk effect and heterojunction-barrier effect (HBE). The result is an increase in the complexity of defining region boundaries and integrating over these to obtain the regional transit times. Previous 2-D transit-time studies have estimated the regional transit-time components, but these were limited to integrations over fixed regions chosen based on the doping profiles and the intrinsic and extrinsic areas of the device [21, 97]. Although these provide rough approximations of the transit-time components, the region boundaries are more correctly delineated by the carrier dynamics throughout the active device. Moreover, these boundaries will change dynamically according to the device operating conditions, particularly at high-injection.

With this in mind, the traditional transit time analysis is enhanced here by introducing a 2-D streamline analysis that enables direct extraction of the regional transit times using bias-dependent region boundaries. This analysis tool is fully automated and integrated within commercially-available TCAD software [105] and is thus well-suited for TCAD-based optimized scaling of SiGe HBTs.

## 2.1 2-D Transit Time Analysis

The basis for the 2-D transit-time analysis is described in [99, 109]. In the quasi-static approximation, the transit time for a 2-D npn bipolar transistor from the emitter contact to the collector contact is given by

$$\tau_{ec} = \frac{1}{2\pi f_T} = \frac{\Delta Q_{tot}}{\Delta I_C}\Big|_{V_{CE}} = \frac{q}{\Delta I_C} \iint \Delta n(x, y)\Big|_{V_{CE}} dy dx.$$

(1)

The small-signal quantities  $\Delta J_C$  and  $\Delta n$  are calculated from a pair of static device simulations modeling a small voltage perturbation,  $V_{BE}$ , around a DC bias point. For the results presented here, hydrodynamic simulations were performed in which the DC bias across the emitter-base junction was swept from low-injection to high-injection regimes, with a small-signal perturbation of  $V_{BE} = 1 \text{ mV}$ , and fixed collector-base bias of  $V_{CB} = 0.5 \text{ V}$ . Negligible change was observed in the estimated  $f_T$  for  $V_{BE}$  values from 1 mV to 10 mV. The simulation mesh was optimized and refined throughout the active device regions to ensure a precise representation of the 2-D charge distributions used in the transit-time calculations.

The transit-time streamline analysis resembles that of previous 1-D transit time analyses [2, 26, 96, 109] in that the cumulative transit time,  $\tau_n$ , is defined along the path of electron transport (or hole transport for pnp HBTs), which can then be divided into regional transit times by various methods. The fundamental difference, however, is that for a 1-D simulation there is a single carrier transport path, whereas for a 2-D simulation domain this path must be chosen carefully. Furthermore, in calculating  $\tau_n$ , the local current density varies along the streamline path and must be used in place of J<sub>C</sub>. Consequently, the cumulative transit time along the length of a streamline is given by

$$\tau_n(s) = q \int_0^s \frac{\Delta(x(s), y(s))}{|\Delta \vec{j}_n(x(s), y(s))|} \Big|_{V_{CE}} ds.$$

(2)

A desired streamline path can be generated for any point of interest from the smallsignal electron current-density vector field, which is calculated as the difference in large-signal current-density vector fields of the two static solutions:

$$\Delta \vec{j}_n(x,y) = \vec{J}_{n2}(x,y) - \vec{J}_{n1}(x,y).$$

(3)

This is in contrast to the 3-D streamline analysis of [6], in which streamlines were computed from the large-signal current-density vector field. The small-signal current must be used since this is a small-signal analysis. This becomes critical when 2-D high-injection effects are present. It is important to note that this analysis can also be directly extended to 3-D TCAD models without any fundamental changes, and also applied to pnp SiGe HBT optimization.

#### 2.2 Regional Transit Times

For highly-scaled bipolar transistors, the depletion approximation becomes invalid in the base and thus abrupt space-charge-region boundaries cannot be clearly identified [26]. Furthermore, the region in the base where  $\Delta n \approx \Delta p$  disappears for sufficiently scaled devices [2, 96]. Although this indicates that diffusive delay in the base of such devices is negligible at low injection, there remains utility in subdividing spacecharge and quasi-neutral-base transit times to capture the sharp increase in the quasi-neutral-base transit time at high injection. For the analysis presented here, boundary definitions were chosen based on carrier and dopant densities to maximize the robustness of the boundary algorithm. The space-charge boundary in the emitter is defined to be the position at which the majority carrier concentration comes within 10% of the background doping concentration. At low injection, the same definition is used for the space-charge boundaries in the base. At high injection, this definition cannot be used, as the carrier densities increase well beyond the base doping concentration; instead, the base boundaries are chosen simply to be the position where n = p. The collector space-charge boundary is defined in the same way as the emitter boundary, with the exception that the majority carrier density is adjusted by subtracting the density of mobile carriers that comprise the collector current,  $J_C/qv_{sat}$ . Although velocity overshoot occurs within the collector-base space-charge region, the carriers are assumed to exit the space-charge region at approximately  $v_{sat}$ . The definition of these four boundaries gives rise to five regional transit-time components: the quasi-neutral transit times,  $\tau_e$ ,  $\tau_b$ , and  $\tau_c$ , and the space-charge transit times,  $\tau_{be}$  and  $\tau_{cb}$ .

A key advantage of this regional analysis over previous 2-D studies [21, 97] is that the region boundaries are bias dependent. To accurately reflect the regional transit times at high injection, it is critical that the base boundary follow the base push-out into the collector with the onset of the Kirk effect. Moreover, this analysis allows the space charge and quasi-neutral regions to be separately defined. Since the streamline computes the delay along a single path, multiple streamlines can be computed through various areas of the device to ascertain the regional transit times throughout the simulation domain.

#### 2.3 Simulation Results

To verify that the quasistatic transit time analysis can be substituted for conventional frequency-domain simulations, the cutoff frequency of a calibrated model of a 50 GHz

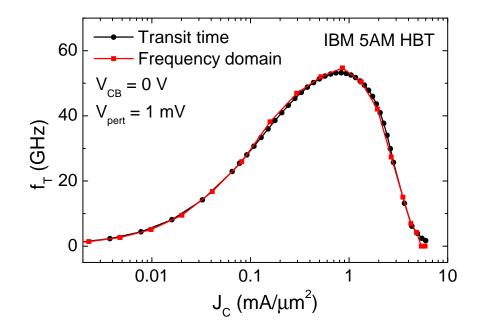

**Figure 4:** Comparison of  $f_T$  vs.  $J_C$  curves simulated for a calibrated model of a 50 GHz npn SiGe HBT, using both the 2-D transit time analysis and frequency-domain simulations.

SiGe HBT (IBM 5AM SiGe BiCMOS) was computed using both types of simulations. As shown in Figure 4, the two simulations produce remarkably similar results across the entire range of bias conditions.

#### 2.3.1 Scaled npn SiGe HBTs