# **ACTIVE MANAGEMENT OF CACHE RESOURCES**

A Dissertation Presented to The Academic Faculty

By

## Subramanian Ramaswamy

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology Aug 2008

# **ACTIVE MANAGEMENT OF CACHE RESOURCES**

Approved by:

Prof. Sudhakar Yalamanchili, Advisor School of ECE Georgia Institute of Technology

Prof. Jeffrey Davis School of ECE Georgia Institute of Technology

Prof. David Schimmel School of ECE Georgia Institute of Technology Prof. Yorai Wardi School of ECE Georgia Institute of Technology

Prof. Umakishore Ramachandran College of Computing Georgia Institute of Technology

Date Approved: June 30 2008

Dedicated to Appa, Amma and Divya

## ACKNOWLEDGMENT

As a doctoral student, the one decision that matters most is choosing an advisor. I chose the best. Prof. Sudhakar Yalamanchili is not only a great researcher and teacher, but also a wonderful friend. The motivation, support and guidance he provided were the core elements in my graduate student career. His encouragement kept me going in stressful times. I owe a debt of gratitude to him that will never be fulfilled.

My proposal and defense committee members including Professors Jeffrey Davis, Yorai Wardi, David Schimmel, Sean Lee and Umakishore Ramachandran provided me with valuable suggestions and feedback which helped make my contributions stronger.

If I completed my thesis, I owe it to my loving wife Divya. She was always there for me. She put up with my insane working hours and my inability to spend any measurable time with her over the last couple of years as I entered the business end of my doctoral studies. She was an unending source of happiness and joy for me. The few hours I spent in her company were always priceless.

Anything I ever accomplished or will accomplish owes a lot to my dearest parents. They instilled the value of education in me and taught me many life lessons that I value in my personal and professional endeavours. My late father always provided me with the support and encouragement to pursue whatever interests me and my mother taught me never to be satisfied with second prize.

My sister Geetha was another person who was there for me with her support and love during my graduate studies. Visiting her in Chicago during December always filled me with warmth in spite of the winter temperatures.

Last, but definitely not the least, I owe a lot to all my friends and colleagues who helped me at various stages of my career by acting as a sounding board, providing me with unlimited support and helping me with the logistics and paperwork—Jeff Young, Tushar Kumar, Jaswanth Sreeram and Nawaf Al-moosa deserve special mention.

## TABLE OF CONTENTS

| ACKNO                                         | WLEDGMENT                                                                                                                               | iv                                     |  |  |  |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|--|

| LIST OF TABLES                                |                                                                                                                                         |                                        |  |  |  |  |

| LIST OF                                       | LIST OF FIGURES                                                                                                                         |                                        |  |  |  |  |

| SUMMA                                         | RY                                                                                                                                      | xi                                     |  |  |  |  |

| СНАРТИ                                        | ER 1 INTRODUCTION                                                                                                                       | 1                                      |  |  |  |  |

| <b>CHAPTI</b><br>2.1<br>2.2<br>2.3            | ER 2 RELATED WORK                                                                                                                       |                                        |  |  |  |  |

| СНАРТИ                                        | ER 3 AN EFFICIENCY MODEL FOR CACHES                                                                                                     | 13                                     |  |  |  |  |

| 3.1<br>3.2<br>3.3<br>3.4                      | Analytical Model                                                                                                                        | 13<br>15<br>20<br>23                   |  |  |  |  |

| СНАРТИ                                        | ER 4 SYSTEM MODEL                                                                                                                       | 26                                     |  |  |  |  |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | Programmable Placement                                                                                                                  | 26<br>28<br>29<br>30                   |  |  |  |  |

| СНАРТИ                                        | ER 5 OFF-LINE STRATEGIES                                                                                                                | 34                                     |  |  |  |  |

| 5.1<br>5.2                                    | Data Trace Cache                                                                                                                        | 34<br>35<br>36<br>38<br>46<br>52<br>52 |  |  |  |  |

| 5.3                                           | 5.2.2       Greedy Algorithm Based Placement         5.2.3       Performance Evaluation         Fault Tolerant Cache (FTC) Architecture | 53<br>56<br>62<br>62                   |  |  |  |  |

|                                               | 5.3.2 Capturing Reference Locality                                                                                                      | 63                                     |  |  |  |  |

|       | 5.3.3                                                                          | Fault Tolerant Placement Policies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                       |

|-------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

|       | 5.3.4                                                                          | Results and Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                       |

| 5.4   | Conclu                                                                         | uding Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                                       |

| CHAPT |                                                                                | STATIC STRATEGIES FOR IMPROVING EFFICIENCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                       |

| 6.1   |                                                                                | d Placement Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                                                       |

|       | 6.1.1                                                                          | Strided Placement for One-dimensional Arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                       |

|       | 6.1.2                                                                          | Miss Folding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                       |

|       | 6.1.3                                                                          | Performance Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                       |

| 6.2   | Extens                                                                         | sions to Multi-threaded Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                                       |

|       | 6.2.1                                                                          | Hardware Extensions for Multi-threading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9                                                       |

|       | 6.2.2                                                                          | Impact of the Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                       |

|       | 6.2.3                                                                          | Performance Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                       |

| 6.3   | Conclu                                                                         | uding Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9                                                       |

| CHAPT | ER 7                                                                           | RUNTIME STRATEGIES FOR IMPROVING EFFICIENCY .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ç                                                       |

| 7.1   | Impro                                                                          | ving Efficiency via Resizing+Remapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                       |

|       | 7.1.1                                                                          | Cache Downsizing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9                                                       |

|       |                                                                                | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |

|       | 7.1.2                                                                          | Runtime Heuristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9                                                       |

|       | 7.1.2<br>7.1.3                                                                 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                       |

| 7.2   | 7.1.3                                                                          | Runtime Heuristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9                                                       |

| 7.2   | 7.1.3                                                                          | Runtime Heuristics       Performance Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9<br>10                                                 |

| 7.2   | 7.1.3<br>An Ut                                                                 | Runtime Heuristics       Performance Evaluation         Pilization Driven Framework for Improving Efficiency       Performance         Empirical Analysis       Performance         Operational Model       Performance                                                                                                                                                                                                                                                                                                                                                                 | 9<br>10<br>10<br>10                                     |

| 7.2   | 7.1.3<br>An Ut<br>7.2.1                                                        | Runtime Heuristics       Performance Evaluation       ilization Driven Framework for Improving Efficiency       Empirical Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9<br>10<br>10<br>10                                     |

| 7.2   | 7.1.3<br>An Ut<br>7.2.1<br>7.2.2                                               | Runtime Heuristics       Performance Evaluation         Pilization Driven Framework for Improving Efficiency       Performance         Empirical Analysis       Performance         Operational Model       Performance                                                                                                                                                                                                                                                                                                                                                                 | 9<br>10<br>10<br>10<br>10                               |

| 7.2   | 7.1.3<br>An Ut<br>7.2.1<br>7.2.2<br>7.2.3                                      | Runtime Heuristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10<br>10<br>10<br>10                                    |

| 7.2   | 7.1.3<br>An Ut<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4                             | Runtime Heuristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9<br>10<br>10<br>10<br>10<br>10<br>10                   |

| 7.2   | 7.1.3<br>An Ut<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6           | Runtime Heuristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9<br>10<br>10<br>10<br>10<br>10<br>10<br>11             |

|       | 7.1.3<br>An Ut<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>Conch  | Runtime Heuristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9<br>10<br>10<br>10<br>10<br>10<br>10<br>11<br>11       |

| 7.3   | 7.1.3<br>An Ut<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>Conclu | Runtime Heuristics       Performance Evaluation         Performance Evaluation       Improving Efficiency         ilization Driven Framework for Improving Efficiency       Improving Efficiency         Empirical Analysis       Improving Efficiency         Operational Model       Improving Efficiency         On-Line Cache Management       Improving Efficiency         Cache Sizing       Improving Efficiency         Shaping the Cache       Improving Efficiency         Performance Evaluation       Improving Efficiency         uding Remarks       Improving Efficiency | 9<br>10<br>10<br>10<br>10<br>10<br>10<br>11<br>11<br>11 |

# LIST OF TABLES

| Table 1 | Description of Benchmarks                                            | 46 |

|---------|----------------------------------------------------------------------|----|

| Table 2 | Performance comparison of Data Trace Cache Vs. a Traditional Cache . | 48 |

| Table 3 | Performance Yield Comparison                                         | 72 |

## LIST OF FIGURES

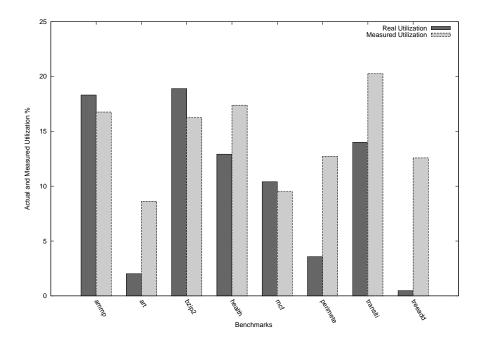

| Figure 1  | Cache utilizations for traditional cache designs     | 16 |

|-----------|------------------------------------------------------|----|

| Figure 2  | Cache efficiencies for traditional cache designs     | 17 |

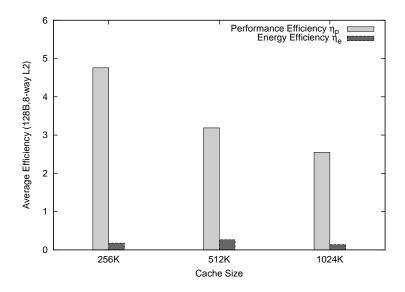

| Figure 3  | Sensitivity of efficiencies to cache size.           | 18 |

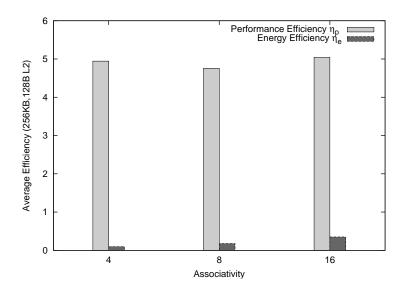

| Figure 4  | Sensitivity of efficiencies to cache associativity   | 19 |

| Figure 5  | Utilization with modern caches                       | 21 |

| Figure 6  | Performance efficiency with modern caches            | 21 |

| Figure 7  | Energy efficiency with modern caches                 | 22 |

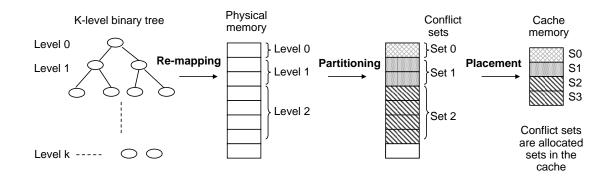

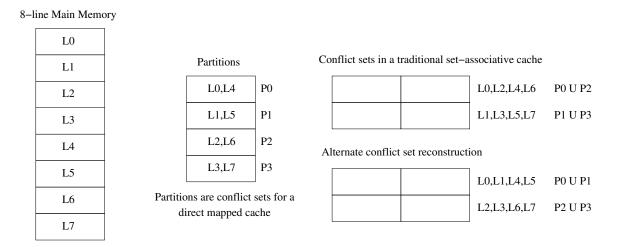

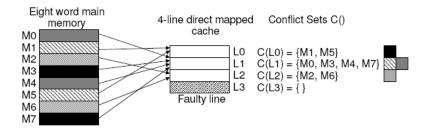

| Figure 8  | Conflict set construction                            | 24 |

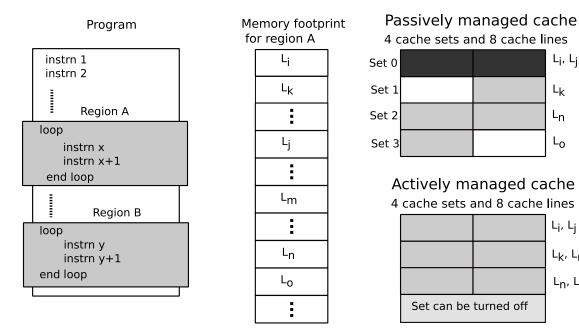

| Figure 9  | Cache sizing and shaping.                            | 27 |

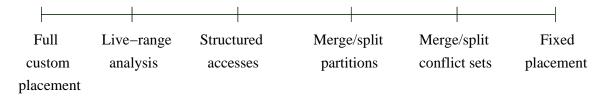

| Figure 10 | Range of optimization possibilities.                 | 28 |

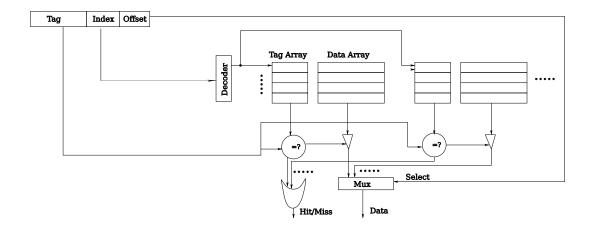

| Figure 11 | Base Cache                                           | 29 |

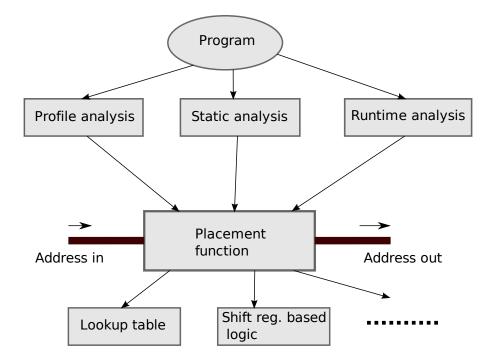

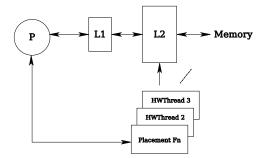

| Figure 12 | Operational Model                                    | 30 |

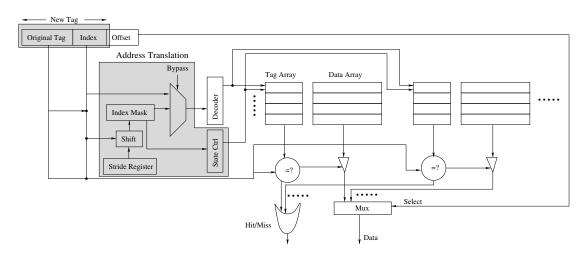

| Figure 13 | Architecture Model                                   | 31 |

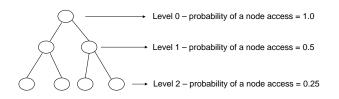

| Figure 14 | A Binary Search Tree                                 | 37 |

| Figure 15 | A n-ary Tree Data Structure                          | 38 |

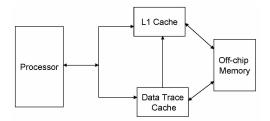

| Figure 16 | Data Trace Cache Principle                           | 39 |

| Figure 17 | Data Trace Cache: System Architecture                | 40 |

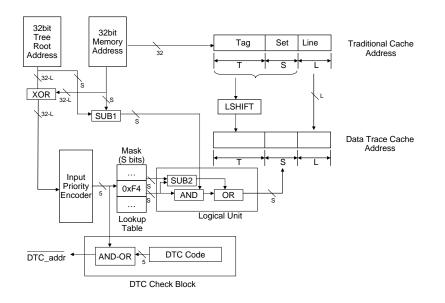

| Figure 18 | Methodology                                          | 41 |

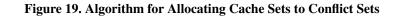

| Figure 19 | Algorithm for Allocating Cache Sets to Conflict Sets | 43 |

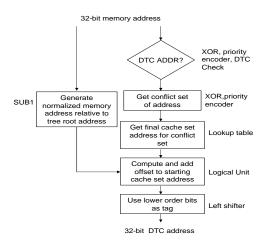

| Figure 20 | Flowchart for Indexing the DTC                       | 44 |

| Figure 21 | Implementation of Runtime decoding for the DTC       | 45 |

| Figure 22 | Evaluation Infrastructure                            | 47 |

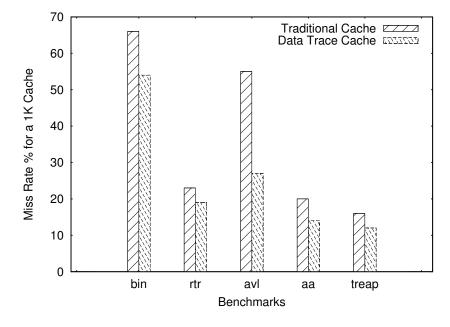

| Figure 23 | Single threaded DTC Results                          | 48 |

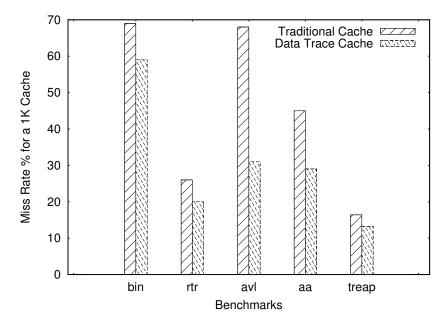

| Figure 24 | Multi-threaded DTC Results                           | 49 |

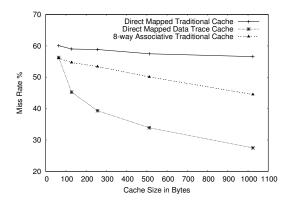

| Figure 25 | DTC performance for <i>avl</i>                       | 50 |

| Figure 26 | Partitions and conflict sets in a traditional cache.                              | 53 |

|-----------|-----------------------------------------------------------------------------------|----|

| Figure 27 | Algorithm for determining set-associative cache placement                         | 55 |

| Figure 28 | Direct-mapped cache placement                                                     | 56 |

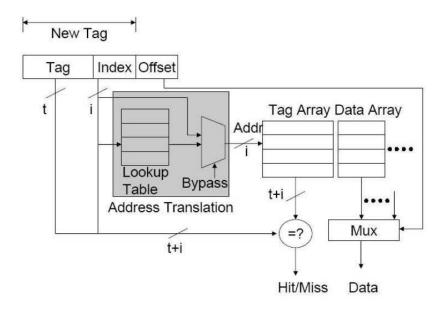

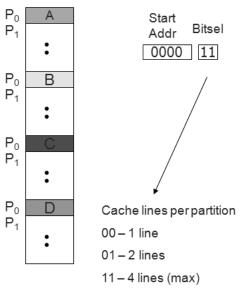

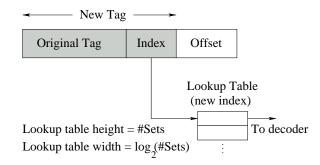

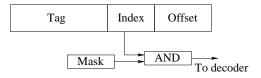

| Figure 29 | Address decoding for set-associative caches                                       | 57 |

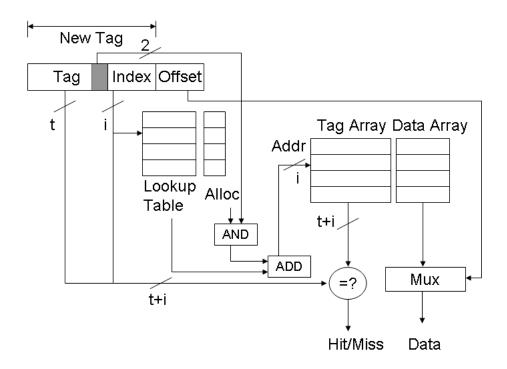

| Figure 30 | Address translation of direct-mapped caches - concept                             | 58 |

| Figure 31 | Address decoding for direct-mapped caches (bypass path not shown)                 | 58 |

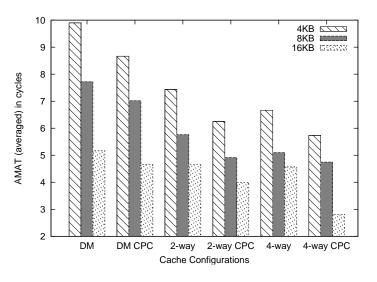

| Figure 32 | AMAT comparison for various cache configurations.                                 | 59 |

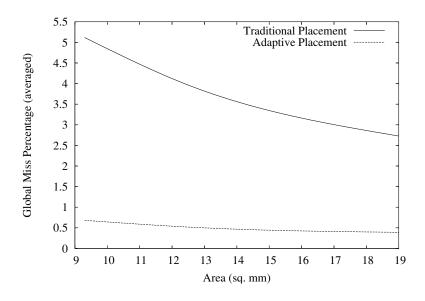

| Figure 33 | Area costs of various cache configurations                                        | 60 |

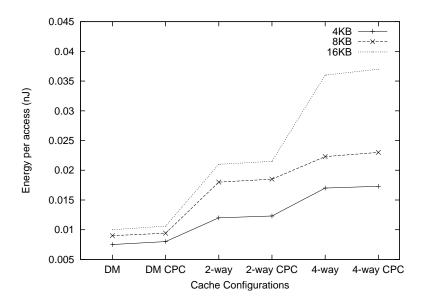

| Figure 34 | Energy costs of various cache configurations                                      | 60 |

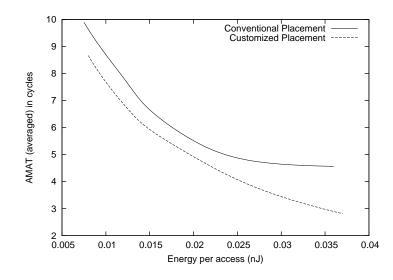

| Figure 35 | Energy-AMAT curves compared for traditional and customized place-<br>ment caches. | 61 |

| Figure 36 | Cache with Customized Placement                                                   | 63 |

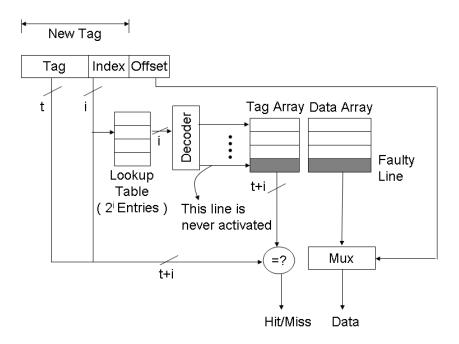

| Figure 37 | FTC Placement Implementation                                                      | 66 |

| Figure 38 | Placement Algorithm for FTC                                                       | 67 |

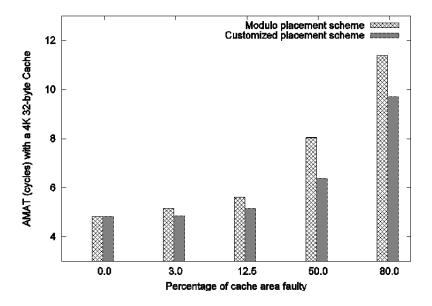

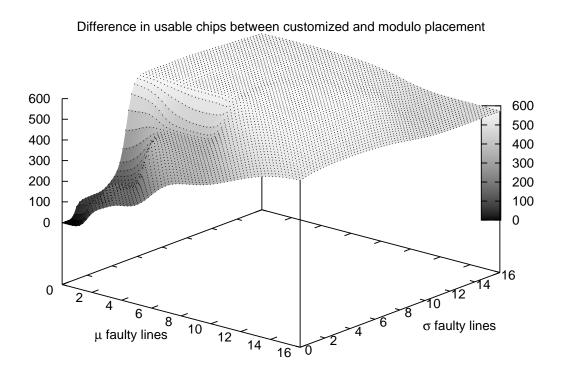

| Figure 39 | Modulo Vs Custom Placement                                                        | 69 |

| Figure 40 | AMAT Variation with Faults                                                        | 69 |

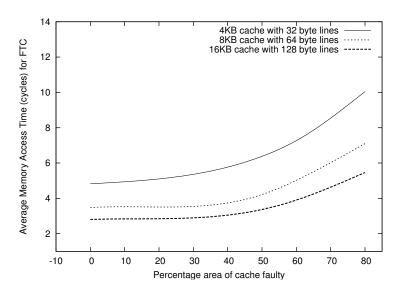

| Figure 41 | AMAT Variation with Faults for Various Cache Configurations                       | 70 |

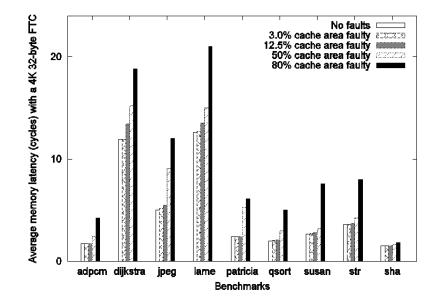

| Figure 42 | Performance Yield                                                                 | 72 |

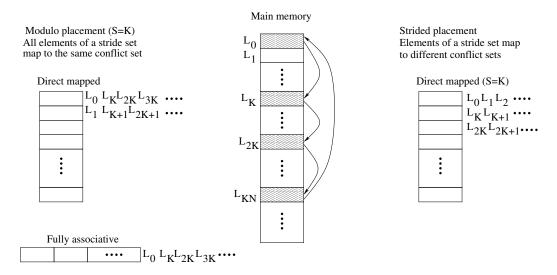

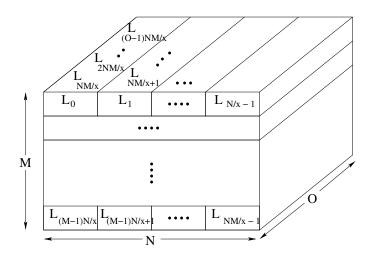

| Figure 43 | Strided placement: Basic concepts.                                                | 77 |

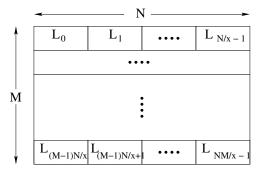

| Figure 44 | Strided placement for matrices.                                                   | 78 |

| Figure 45 | Strided placement for 3D arrays                                                   | 78 |

| Figure 46 | Algorithm computing the cache placement function                                  | 81 |

| Figure 47 | Algorithm computing the number of active cache sets                               | 81 |

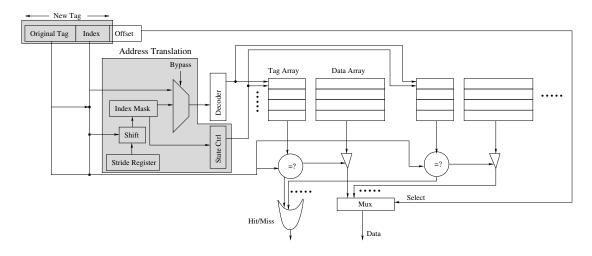

| Figure 48 | Run-time address translation for strided placement                                | 82 |

| Figure 49 | Cache utilization comparison for scientific computation.                          | 85 |

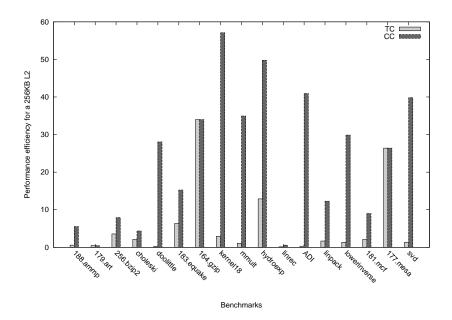

| Figure 50 | Performance efficiency comparison for scientific computation                      | 86 |

| Figure 51 | Energy efficiency comparison for scientific computation                           | 86 |

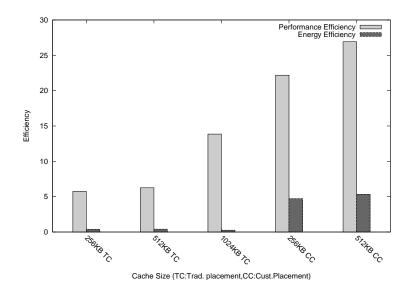

| Figure 52 | Efficiency variation with cache size                                          |

|-----------|-------------------------------------------------------------------------------|

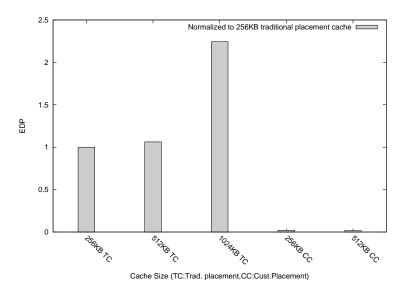

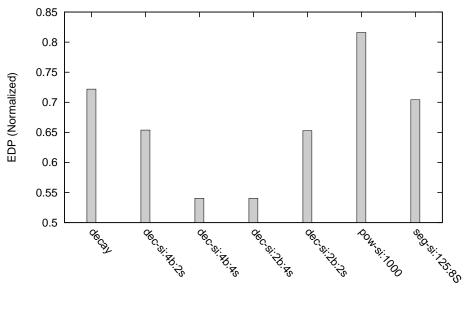

| Figure 53 | EDP variation with cache size                                                 |

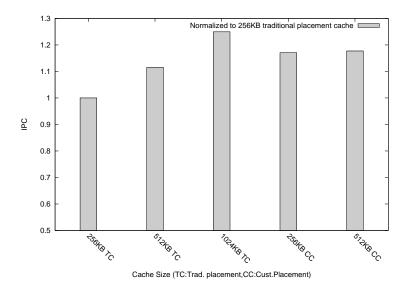

| Figure 54 | IPC variation with cache size                                                 |

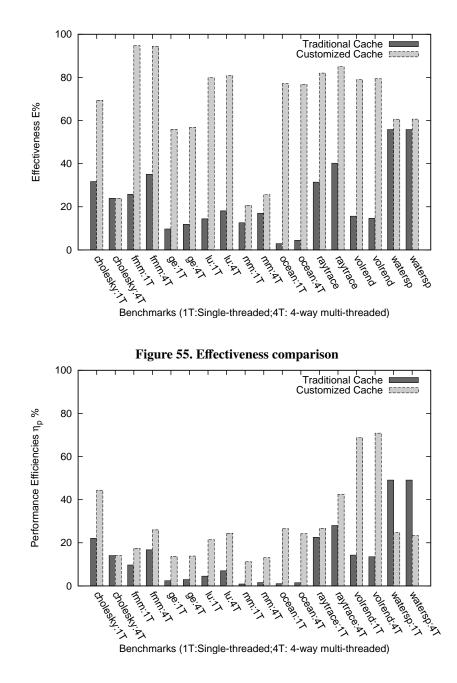

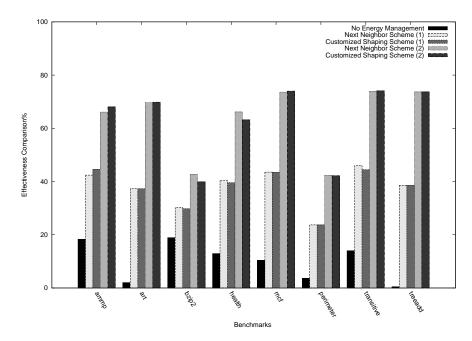

| Figure 55 | Effectiveness comparison                                                      |

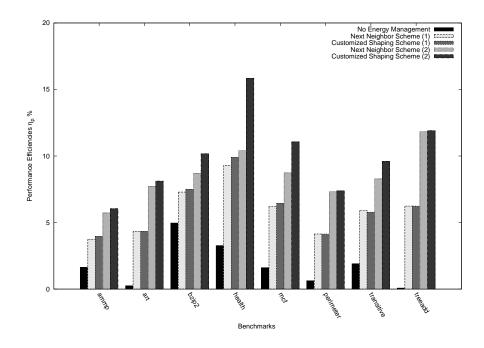

| Figure 56 | Performance efficiency comparison                                             |

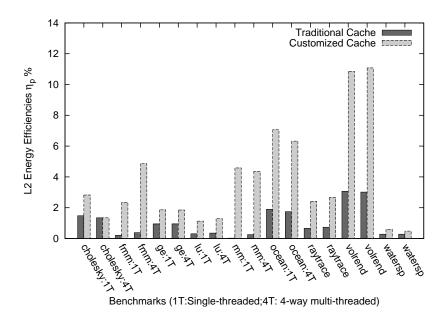

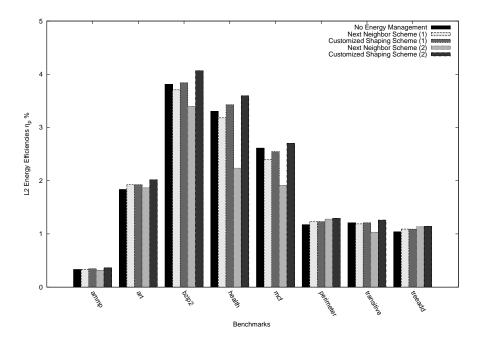

| Figure 57 | Energy efficiency comparison                                                  |

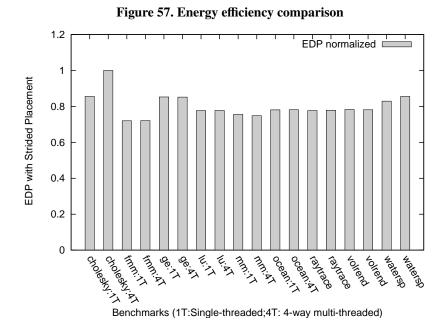

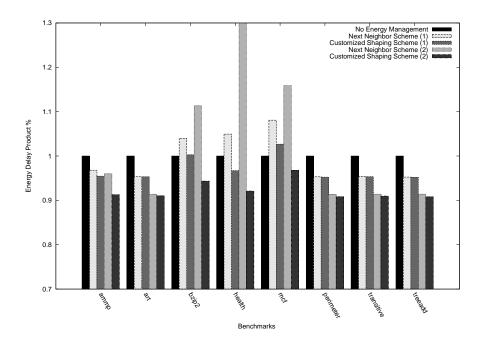

| Figure 58 | EDP comparison                                                                |

| Figure 59 | Cache decay resizing                                                          |

| Figure 60 | Power of two resizing                                                         |

| Figure 61 | Cache segment resizing                                                        |

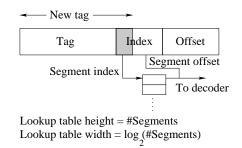

| Figure 62 | Energy efficiency comparison of folding heuristics                            |

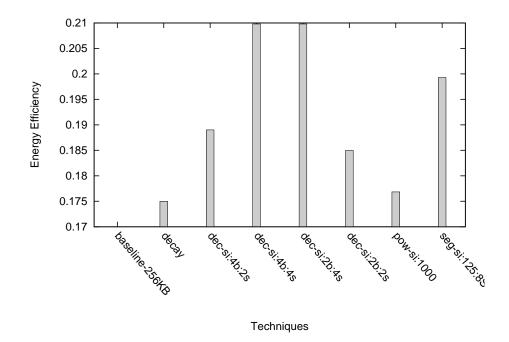

| Figure 63 | Performance efficiency of folding heuristics                                  |

| Figure 64 | EDP of folding heuristics                                                     |

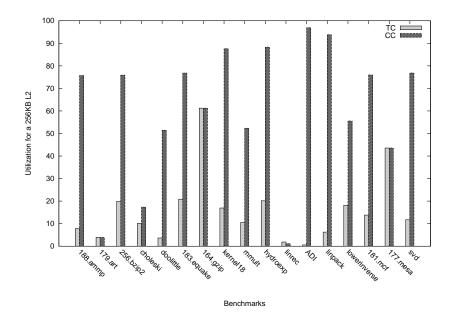

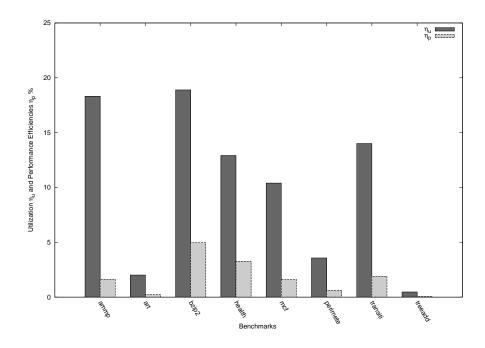

| Figure 65 | Utilization and Performance Efficiencies for a traditional 256KB L2 Cache 105 |

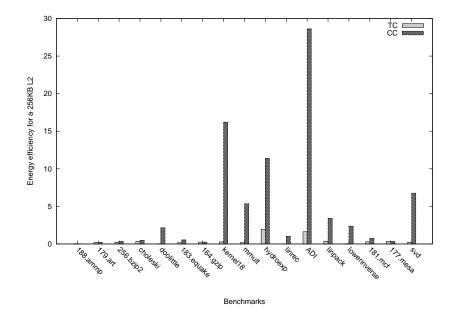

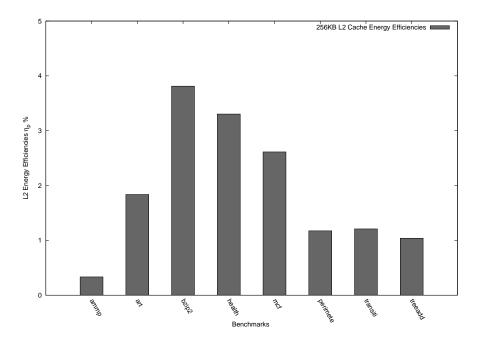

| Figure 66 | Energy efficiencies for a 256KB L2 cache                                      |

| Figure 67 | Conflict set construction                                                     |

| Figure 68 | Utilization Measured vs. Actual                                               |

| Figure 69 | Hardware Implementation                                                       |

| Figure 70 | Shaping Algorithm using Utilization                                           |

| Figure 71 | Effectiveness comparison                                                      |

| Figure 72 | Performance Efficiency comparison                                             |

| Figure 73 | Energy Efficiency comparison                                                  |

| Figure 74 | Energy Delay Product comparison                                               |

## SUMMARY

**Thesis Statement**: Active cache management customized to application memory behavior improves cache efficiency.

The shift from scaling frequency to scaling the number of cores, continues the trend of stressing off-chip memory bandwidth and reliance on larger on-chip caches. Caches typically occupy 40–60% of the chip area and account for 15–30% of energy consumption on chip. For a fixed die size, execution performance will drive the need for more cores while the increased memory bandwidth required to sustain these cores will drive the need for larger caches while keeping energy costs at a minimum. This dissertation is focused on the development of techniques to reconcile these conflicting area and energy demands. The solutions provided in this dissertation are driven in part by the observation of very low performance efficiencies and energy efficiencies for modern data caches. For a range of application domains, data cache utilizations are below 20%, performance efficiencies below 15% and energy efficiencies *below* 1%! These low efficiencies are not sustainable for a critical architectural resource that is also a dominant resource consumer on-chip. Consequently, the ability to scale the number of cores while concurrently pushing back the memory and power walls will require significant improvements in cache efficiency. Concepts and implementations to achieve such improvements are addressed in this dissertation.

Two significant causes of low cache efficiencies are: (i) transistor leakage, and, (ii) the fixed manner in which main memory lines share the cache. At technologies below 70 nm, a L2 cache with size greater than 256 KB has 95% of its energy consumption attributed to leakage. Further, typical L2 cache line is accessed only once every hundreds of thousands of cycles, whereas, the transistors comprising the cache line leak *every cycle* leading to poor energy efficiencies. The low utilization and performance efficiencies can be attributed to the fixed mapping of main memory lines to the cache. This fixed mapping typically

results in the majority of the cache storing data that will not be accessed in future. Indeed, a utilization number of 25% indicates that, on average only 25% of the cache stores data that will be accessed in the future!

The approaches proposed for efficiency improvement is predicated on addressing the preceding two sources of inefficiency. The approach to improving energy efficiency primarily relies on *sizing* the cache to match application memory footprint or working set during a program phase and powering down all remaining cache lines. The approach to improving cache utilization and performance efficiency primarily relies on changing the placement function—the manner in which main memory lines share cache resources motivated in part by compiler-driven approaches where application-data shares registers via compiler based register allocation techniques. This is referred to as *shaping* the cache. The approach to sizing differs from past approaches in that these techniques produce fully functional smaller caches. There can be no references to inactive cache lines. This is feasible since sizing is used in conjunction with shaping. These techniques are predicated on partitioning main memory into conflict sets-each set of memory lines is mapped to the same cache set. The optimization problem is the application-driven construction of conflict sets to maximize energy and performance efficiencies. The engineering challenge is the development of hardware-software techniques for static and dynamic sizing and shaping. Collectively, the application of these techniques is referred to as *active management*. This dissertation makes the following specific contributions.

First, a model is developed for quantifying cache utilization, energy efficiency and performance efficiency. Efficiency metrics are introduced followed by an analysis of common single-threaded and multi-threaded benchmarks. The resulting efficiencies are found to be very low (< 25% for utilization, 15% for performance efficiency, < 1% for energy efficiency). The analysis exposes some of the key sources of cache inefficiency (e.g.,leakage and how memory lines share the cache) and provides the insights for the development of energy improvement through active management techniques. Second, profile-driven algorithms for computing placement functions for caches are provided. This was first applied to the design of application specific caches for network processors. In such architectures memory accesses are dominated by accesses to a few major data structures: in the case of network processors, it is the route lookup data structures. This dissertation demonstrates the design of an application specific cache, named the data trace cache for application in networking applications. The customized cache exploited the predictability of accesses to the routing table data structure. The proposed solution has the flavor of stream buffers in general-purpose caches.

This notion of profile driven placement is developed further by adapting it to a more general solution for embedded processors. Greedy algorithms are used on profile data to develop application specific customized cache placement to manage the cache for embedded processors. This resulted in a sharp decrease in conflict misses in embedded processor caches. Another application of these profile-driven solutions was aimed at masking out faulty cache lines with minimal performance degradation which was found to be very effective. The low performance degradation seen using customized placement strategies exposed the existing redundancy in traditional cache storage, which could be intelligently adapted for energy and performance benefits.

Third, the preceding two techniques are consolidated in a solution for application specific cache configurations. The key insight is to recognize the relationship between voltage level and fault free memory cells in the cache. A configuration profile is generated for the cache where each voltage level is mapped to a size and shape (placement function). This shape in turn can be profile driven particularly useful for embedded processors. During program execution voltage levels and consequently cache size and shape can be selected for each program region to concurrently improve both energy and performance efficiencies.

Fourth, active management techniques are developed for static sizing and shaping caches for scientific computing applications which have predictable memory reference behavior with well defined memory footprints. This domain knowledge was used to derive customized cache placement solutions, which in conjunction with sizing improved performance and energy efficiencies significantly over traditional caches (Section 6.1). The solutions exploited the property of strided accesses to multi-dimensional array data structures being a common feature in scientific applications. The improved sharing achieved using active management, i.e., cache shaping, led to significant drops in miss rates and execution time in addition to improved energy efficiency by sizing the cache to the program phase memory footprint. This work on static sizing and shaping strategies is further extended to include the current environment of multi-threaded applications. In Section 6.2. The application of static sizing and shaping strategies is extended to multi-threaded domains to optimize the efficiencies of caches shared among multiple application threads.

Fifth, active management techniques are developed for runtime sizing and shaping for applications lacking statically characterizable profiles. The concept of miss folding is introduced as a technique for dynamically sizing and shaping the cache. Simple folding schemes relying on various heuristics were found to be effective in decreasing the energydelay product (EDP) significantly and increasing energy and performance efficiency.

To summarize, state of the practice is focused on applying power down events such as gated-Vdd or drowsy state to selected components of the cache. Consequently references can be made to inactive cache components with accompanying performance penalties, for example the need to power and reload a line or way. In contrast this dissertation sizes a cache in conjunction with customized placement to produce fully functional caches of varying sizes with references accessing only active (i.e., powered) cache components.

Sizing and shaping can be applied at different phase of the design cycle. For example, after burn in test, sizing and shaping can be used to mask faulty cache elements and perform a per application configuration of the on-chip cache hierarchy (Techniques 2 and 3). During compile time, cache configurations (a size and shape) can be computed for various program phases and effected via a software interface (Technique 4). Such an approach is particularly

effective for applications where memory access patterns can be determined via program analysis such as in the scientific computing domain. A more flexible variant is the runtime inference of memory access patterns (Technique 5) and the dynamic determination of a new cache size and shape configuration. This dissertation contributes techniques at all of the preceding points in the life cycle of a program.

Finally, this dissertation opens up a new degree of freedom for compiler optimizations. Compilers have been restricted to a cache with fixed mapping from main memory. Opening up the cache placement function provides another avenue for optimization. The relaxation of the placement coupled with the conflict set construction and notion of liveness provides the means for formulating a range of tractable memory system optimizations.

# CHAPTER 1 INTRODUCTION

This dissertation addresses two major sets of challenges facing processor design as the industry enters the deep sub-micron region of semiconductor design. The first set of challenges relates to the well understood memory bottleneck [1] that shows no signs of easing even as the focus shifts from scaling processor frequency to scaling the number of cores. This trend has led to the increasing reliance on larger on-chip caches which occupies 40–60% of area on chip and consuming 15–30% of energy expended on chip. The second set of challenges is posed by transistor leakage and process variation (both inter-die and intra-die) at future technology nodes with leakage power anticipated to increase exponentially and sharply lower defect-free yield with successive technology generations. This dissertation focuses on resolving these two challenges by abstracting them as one problem—developing efficient caches.

The first set of challenges results in efforts to decrease the average memory access latency through the addition of larger and deeper cache hierarchies. However, this has led to an over reliance of caches, with caches typically occupying 40–60% [2] of the chip area and are estimated to account for 15–30% [3, 4] of the overall chip energy consumption. For example, the Intel Itanium 2 processor 9010 has a 6 MB L3 cache [5], with the cache hierarchy occupying almost 60% of the die area. Apart from the increasing cache costs, adding more cache resources results in lower resources for the processing cores limiting Moore's law expansion in raw processing power.

Transistor leakage at sub-micron technologies is at the forefront of the second set of challenges facing the semiconductor industry. Borkar estimates leakage energy to be 60% of the overall processor energy consumption at 65 nm and anticipates the leakage current to increase by a factor of 7.5 with successive technology generations [6]. This increase in leakage current is expected to scale total leakage power on the chip by a factor of 5.

Leakage is a function of area on the chip, and caches, because of their significant area budgets are major contributors to leakage [3, 4]. Additionally, since the majority of the cache is idle most of the time (especially L2 and L3 caches), the SRAM cells in caches contribute significantly more to leakage energy than to switching energy.

The efficiencies of the cache hierarchy is quantified and it was determined that across a range of application domains, data cache utilizations have been found to be below 25%, performance efficiencies below 15% and energy efficiencies *below* 1%! These low efficiencies are not sustainable. Consequently, the ability to scale the number of cores concurrently while pushing back the memory and power walls will require significant improvements in cache efficiency, which is the focus of this dissertation.

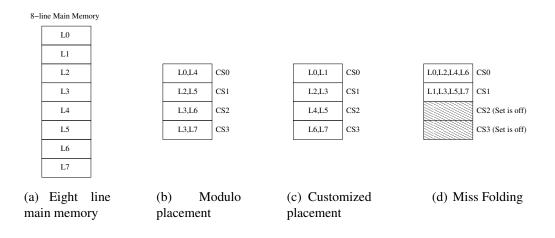

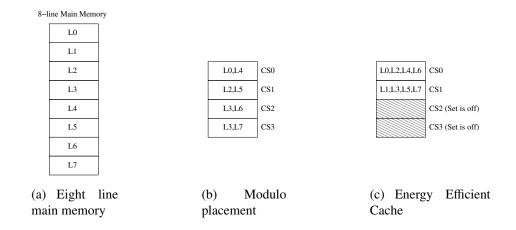

Two significant causes of low cache efficiencies are identified: (i) transistor leakage, and, (ii) the fixed manner in which main memory lines share the cache. At technologies below 70 nm, a L2 cache with size greater than 256 KB has 95% of its energy consumption attributed to leakage. A typical L2 cache line is accessed only once every hundreds of thousands of cycles, whereas, the transistors comprising the cache line leak *every cycle* leading to poor energy efficiencies. The low utilization and performance efficiencies can be attributed to the fixed mapping of main memory lines to the cache. In traditional caches the set of memory lines mapping to a cache set (a *conflict set*, Section 3.4), is fixed at design time and this structure is one of the major sources of cache inefficiency. This fixed mapping typically results in the majority of the cache storing data that will not be accessed in future. Indeed, a utilization number of 25% indicates that, on average only 25% of the cache stores data that will be accessed in the future! Thus, the dominance of leakage energy coupled with the static cache architecture leads to inefficiency.

This thesis focuses on actively managing the cache structure, leading to increased utilization and performance efficiency while at the same time limiting any adverse impact on energy consumption. Managing the cache resources in an active manner improves the sharing of cache resources among main memory lines by making this mapping malleable. This increases cache efficiency—this is the focal point of this dissertation. As technology scales and designs incorporate larger caches for greater performance, cache efficiency is of paramount importance, and this dissertation takes a first step towards that direction.

The key to improving cache energy and performance efficiencies is to construct *conflict sets* customized to the application memory access pattern (i.e., *shaping*) and minimizing the footprint of the application in the cache (i.e., *sizing*). Collectively, *sizing* and *shaping* are referred to as *active management*, as they match the cache size and placement structure to the application memory access behavior. The vehicle that is adopted to achieve active management in this thesis is customizing the cache placement. The result is lower conflict misses (better performance efficiency) and smaller footprints with the ability to turn off unused lines (better energy efficiency). This dissertation focuses on hardware-software approaches embodying this philosophy to improve cache efficiencies.

Sizing and shaping can be applied at different phase of the design cycle. For example, after burn in test, sizing and shaping can be used to mask faulty cache elements and perform a per-application configuration of the on-chip cache hierarchy. During compile time, cache configurations (a size and shape) can be computed for various program phases and effected via a software interface. Such an approach is particularly effective for applications where memory access patterns can be determined via program analysis such as in the scientific computing domain. A more flexible variant is the runtime inference of memory access patterns and the dynamic invocation of a new cache configuration. This dissertation contributes techniques at all three of the preceding points in the life cycle of a program.

The optimization problem is one of forming conflict sets customized to the memory reference pattern of a program phase. The engineering problem is to architect low cost software and hardware solutions to effect sizing and shaping. The design problem is to decide where such techniques should be applied: one-time (per-application) configuration, statically at compile time, or dynamically at run time.

The state of the practice in making caches more energy efficient has been to power

down cache components such as cache lines, sets or ways—turn them off or maintain them in a low voltage state. Strategies focus on *when* to turn off *which* components. Studies improving cache performance include pseudo-associative designs and compiler optimizations along with fixed hardware modifications. Strategies to improve performance efficiency rely on hardware strategies that implement new fixed management structures or through compiler optimizations, noticeable for scheduling and data layout. Existing strategies to improve efficiencies are constrained by one of the primary causes of inefficiency—the fixed manner in which main memory shares the cache. Additionally, improving cache efficiency leads to solutions that might seem counter-intuitive; for example, accesses concentrated on a few cache sets can lead to better efficiency than distributing those accesses across the entire cache but may degrade performance substantially if applied in an agnostic manner. By making the cache *size* and *shape* fluid, efficiencies can be improved by exploiting memory access behavior. Thus, active management can be viewed as an evolution of present day energy saving and performance improvement strategies.

This thesis is organized as follows. The following chapter describes several related techniques used in the literature for improving cache performance and contrasts the strategies proposed in this thesis with them. Chapter 3 describes a model for quantifying cache utilization and efficiency and applies this model to empirically analyse the performance of single threaded and multi-threaded applications in traditional caches. This analysis provides the necessary insights for developing customized active management techniques. Chapter 4 describes the programmable placement system model including the programming model, the operational model and the architecture model employed along with the range of options customization. Chapters 5, 6 and 7 describe various techniques for improving cache performance and efficiencies subdivided into offline profile driven strategies, compile-time strategies driven by program analysis, and dynamic strategies driven by runtime measurements. The dissertation concludes with a brief discussion of the potential extensions to this body of work and a brief summary of this dissertation.

# CHAPTER 2 RELATED WORK

A vast body of work applies hardware and software strategies to enhance cache performance and power profiles. However, techniques in the literature are constrained by the passive cache management structure which limits optimization opportunities. Additionally, the optimizations outlined tend to either improve performance or save energy; whereas active management focuses on performance and energy; i.e., cache management to minimize energy and delay simultaneously. The proposed work couples programmable cache placement functions to a domain of applications that can be programmed using analysis (either statically via compilers or at run-time via dynamic optimizers). Active cache management subsumes many of the optimizations outlined in this chapter and, additionally, is complementary to many techniques that can lead to further optimizations. The existing work in literature can be broadly classified into three categories—those which seek to improve execution time, those which seek to improve energy savings and those which provide defect tolerance to caches. A brief discussion of the literature in the three categories follows.

## 2.1 Execution Time Optimizations

This class of optimizations focus on decreasing cache miss rates and program execution time by means of hardware adaptations or through compiler optimizations. While overall energy consumption may be reduced using these optimizations because of the decrease in execution time, none of these optimizations focus on efficiency, i.e., the maximum performance that can be obtained per transistor. Finally, when performance is being chased, energy becomes second priority. In this dissertation, the focus is on improving cache efficiency—both energy efficiency and performance efficiency. Additionally, many of these performance optimizations are complementary to the approach described in this dissertation and can be applied together. Finally, some of these optimizations may be realized as instances of the active management approach prescribed in this thesis.

#### Pseudo Associativity Mechanisms

Multiple optimizations focus on providing the performance of higher associativity caches with access latencies similar to those of lower associativity caches to decrease conflict misses and miss rates. For example, Jouppi [7], proposed small fully-associative buffers called victim caches for reducing misses to heavily accessed entries in a traditional cache, Qureshi et al.[8] designed a V-way associativity cache by doubling the number of ways of associativity and using global replacement strategies, Peir et al.[9] proposed the adaptive group-associative cache (AGAC), which improves the performance of first level directmapped caches by using multiple banks for swapping data with variable access latency. Various other forms of pseudo-associative caches, which trade variable hit latency for increasing associativity, include the hash-rehash cache proposed by Agarwal et al.[10], the column associative cache proposed by Agarwal and Pudar [11], and the predictive sequential-associative cache proposed by Calder *et al.*[12]. Hallnor and Reinhardt [13] proposed the Indirect Index Cache (IIC) to achieve full-associativity through software management relying on chain traversal. In the NuRAPID cache proposed by Chishti et al.[14], the access latency of different cache lines varies depending on the physical placement of data within the data-store and lowers the cache access latency for increased associativity caches. The proposed active management techniques are complementary to many of these schemes since the mapping of a memory line to a cache set is adapted (as opposed to being mapped to a fixed cache set).

#### **Indexing Schemes**

Innovative approaches in cache indexing seek to find better *fixed* design time placement functions than modulo placement functions, and active cache management subsumes many of these schemes. For example, the two-way skewed associative cache proposed by Seznec [15]

attempts to distribute memory accesses uniformly to minimize conflicts by having two indexing functions per cache set. Other techniques aimed at distributing memory accesses across cache sets uniformly by modifying the indexing function include the prime modulo scheme proposed by Kharbutli *et al.*[16], the randomized cache placement scheme proposed by Topham and Gonzalez [17], and the balanced cache proposed by Zhang [18] that uniformly distributes accesses to a direct-mapped cache for reducing misses using programmable content addressable memory decoders for embedded systems. Uniform distribution does not necessarily result in better efficiency, as all cache sets have to be maintained as active or powered on, thereby expending leakage energy.

#### Cache Replacement Optimizations

An orthogonal body of work for improving cache performance focuses on the replacement policies, i.e., the placement of a memory line within a set. This includes many innovations, including frequency-based replacement proposed by Robinson and Devarakonda [19], recency-based replacement proposed by Jiang and Zhang [20], and adaptive replacement schemes proposed by Subramanian *et al.*[21] and Smaragdakis *et al.*[22]. Puzak [23] proposed the inclusion of extra tags in a shadow directory to provide feedback to a local replacement engine in a set-associative cache.

#### **Compression Optimizations**

Cache compression can store larger chunks of data in the cache as shown by Lee *et al.*[24], Zhang *et al.*[25], Alameldeen and Wood [26], Wilson *et al.*[27]. Cache compression is complementary and can be applied concurrently to active management strategies. However, compressing and decompressing data upon entry and exit from the cache involve a substantial overhead.

#### **Partitioned Caches**

Many techniques such as sub-banking achieve power reduction by partitioning the data cache into smaller, low-power components. This includes work done by Ghose and Kamble [28] and Su and Despain [29]. Other approaches to partitioned caches categorize locality and reference behavior and cache the different categories separately for energy and performance benefits. Several strategies partition the cache to exploit reference locality across scalar and vector data. Examples include split caches proposed by Dahlgren and Stenstrom [30] and techniques proposed by Petrov and Orailoglu [31]. Lee and Tyson[32] partitioned the cache for memory regions such as heap and stack for lowering energy dissipation.

Stone *et al.*[33] studied optimal static partitioning of the cache ways between two or more applications. Suh *et al.*[34] described a scheme using hit recency of the lines in the cache to estimate the utility of the cache for each application and share the cache ways accordingly. Partitioning mechanisms for shared caches were described by Iyer [35]. Hsu *et al.*[36] studied different policies for partitioning a shared cache among competing applications. Qureshi and Patt [37] proposed a utility-based cache partitioning for sharing the cache across two applications while lowering miss rates. Chang and Sohi [38] proposed dynamic mechanisms for providing latency comparable to that of a private cache while obtaining the benefits of a shared cache. Liu *et al.*[39] proposed a split L2 cache for chip multiprocessors with non-uniform access latencies. Many of these strategies seek to partition ways in a shared cache, whereas the strategy proposed in the research herein partitions a uniform latency shared cache by sets. Additionally, the cache can be made private or shared by customizing the cache placement using active management strategies.

#### NUCA caches

Non-uniform cache architectures (NUCA) are offered as an alternative to monolithic fixed latency set-associative caches and were proposed by Kim *et al.*[40], Chishti *et al.*[41], Huh *et al.*[42]. NUCA caches are specifically targeted to multiprocessor memory hierarchies.

Dynamic NUCA caches migrate sets of memory lines closer to the processor that might use the data to optimize latency. On the other hand, active management schemes determine the construction of the sets of memory lines and are, therefore, complementary to such optimizations.

#### Stride Prediction and Pre-fetching

Memory latency can be decreased by employing data pre-fetching. These techniques involve capturing memory access patterns (MAP) and using them to pre-fetch data into the cache. Examples include Luk and Mowry [43], Mowry *et al.*[44], Kim *et al.*[45, 46].

Stride predictors, as proposed by Sazeides and Smith [47], Fu *et al.*[48], Sair *et al.*[49], etc., can be used to predict access strides, which can lead to better pre-fetching decisions. The proposed active management cache design can decrease conflicts among pre-fetched data, leading to better cache efficiencies and bandwidth preservation. Furthermore, memory behavior can be analyzed for better pre-fetching and caching strategies, as shown by Ghosh *et al.*[50], and these techniques can be used to optimize cache management decisions.

#### Data Layout and Scheduling Optimizations

Data re-layout techniques optimize cache performance for specific access patterns. This includes works proposed by Chilimbi *et al.*[51], Panda *et al.*[52], and, Rabbah and Palem[53]. Carter *et al.*[54] propose using a memory controller to modify the virtual layout to make better use of pre-fetching. Other works proposing active memory controllers include Kim *et al.*[55], and, Heinrich *et al.*[56]. Another theme is reordering memory reference streams via loop transformations such as those proposed by Panda *et al.*[57], and, McKinley *et al.*[57].

The research proposed herein does not alter the memory layout (virtual or physical), or, the instruction schedule in any manner, and is therefore complementary to all such compiler optimizations. However, in certain scenarios, active management can provide similar performance benefits obtained using these compiler optimizations at lower costs. For example, re-mapping data is expensive, and at run-time, data re-mapping becomes infeasible for large data structures. In such cases, the active management schemes proposed herein provide similar benefits without any of the added disadvantages. The compiler optimizations found in the literature are targeted to fixed cache designs with modulo placement. These optimizations can benefit from actively managed caches since they provide greater opportunity for optimizations. For example, a specific layout may no longer preclude certain instruction schedules for good performance.

#### Scratch-pad Memories

Several efforts propose compiler controlled on-chip scratch-pad memories as an alternative to hardware caches. Examples include Banakar *et al.*[58], Steinke *et al.*[59], Miller and Agarwal [60], Udayakumaran *et al.* [61], and Panda *et al.* [62]. Scratch-pad memories require explicit control of all data movement between the scratch-pad and the off-chip memory, which leads to an increase in code size and software complexity. In this context, Chiou *et al.*[63] proposed column caching to map specific application data within a specified region in the cache, thereby approximating scratch-pad memory behavior.

## 2.2 Energy Optimizations

The optimizations in this category are focused on energy savings and simultaneously minimizing performance degradation. While this approach can increase energy efficiency, the degradation in performance can compensate for energy savings thereby causing the adopted strategies to be very conservative. This thesis approaches energy savings by increasing efficiency, i.e., energy savings with performance improvements or adaptations that limit performance degradation even with significant energy savings through aggressive cache line turn off strategies.

#### Scheduling Cache Turn-offs and Drowsy States

The state of the practice in reducing leakage energy has been to power down cache components such as cache lines, sets or ways. Examples include Albonesi [64], Abella *et al.*[65], Kaxiras *et al.*[66], Powell *et al.*[67], C. Zhang *et al.*[68], M. Zhang and Asanovic [4], and Zhou *et al.*[69]. Another approach is to keep the cache in a low voltage *drowsy* state as proposed by Flautner *et al.* [70]. W. Zhang *et al.*[71, 72] use special instructions to schedule instruction cache turn offs using loop and branch information or maintain the cache in a drowsy state, activating cache lines prior to access, while Geiger *et al.* [73] combine region-based caching with drowsy caching to reduce cache power dissipation. These strategies focus on *when* to turn off *which* components. Poor decisions lead to expensive misses and power-up events and therefore strategies tend to be conservative. These approaches tune the cache on system level metrics, such as the number of accesses and misses, and do not exploit the concept of conflict set live ranges in data caches to increase leakage savings with minimal performance degradation. Furthermore, many of these approaches can be combined with customized placement to increase energy savings.

#### Filter Caches

In a two-level inclusive cache, an access to the L2 cache esults in the data being brought into the L1 cache. Therefore, the L1 cache acts as a filter to the L2 cache. For example, there will not be any stride zero access to the L2 cache. Kin *et al.*[74] propose using a small-sized L1 cache to save energy while having an L2 cache sized similar to a typical L1 cache to improve performance. Memik *et al.*[75] use the notion of filtering and prediction to prevent accesses to L2 caches if the access potentially results in a miss, thus saving energy. Bloom filters were used to reduce the energy of virtual cache synonym look-ups by Wyoo *et al.*[76].

## 2.3 Defect Tolerance

Defect tolerance optimizations have traditionally focussed on next neighbor re-mapping or redirecting faulty cache cell accesses to memory; these approaches are not scalable and result in rapid performance degradatation with increases in the number of faulty cells, as expected with DSM technologies. This dissertation, by focussing on efficiency provides approaches that can result in caches with a high degree of defect tolerance, as performance loss due to faulty cells can be compensated by applying active management schemes.

#### **Redundancy and ECC Schemes**

Adding redundant blocks, as proposed by Turgeon *et al.*[77], Lucente *et al.* [78], Nokolos *et al.* [79], etc., is one approach to designing fault tolerant caches. Using error correcting codes (ECC) as proposed by Kalter *et al.* [80] also provides fault tolerance for on-chip caches. However, these techniques are limited in the number and distribution of faulty cells that can be tolerated, and are improved upon by active cache management approaches that use re-mapping.

#### **Re-mapping or Eliminating Faulty Cache Blocks**

The re-mapping approach modifies the cache placement policy to map main memory lines to non-faulty cache lines and is proposed by Shirvani *et al.* [81] and Agarwal *et al.*[82]. Other approaches for fault tolerant caches include avoiding faulty ways in a set-associative cache as proposed by Ooi *et al.* [83], or placing code intelligently in faulty set-associative caches to minimize misses, as proposed by Zarandi *et al.*[84]. The goal of those efforts was fault tolerance, while performance optimization was not addressed. These techniques are additionally limited by their selection of block size (not the same as cache line size). The proposed active management techniques optimize for performance when faults are present and achieve a greater degree of fault tolerance as measured by lower performance degradation for the same distribution of faults.

### **CHAPTER 3**

## AN EFFICIENCY MODEL FOR CACHES

This chapter describes a model for quantifying and analysing the efficiency of caches. Several metrics are introduced for the purpose, followed by an analysis of common singlethreaded and multi-threaded benchmarks from the efficiency viewpoint. The analysis exposes several sources of inefficiency that can be ameliorated through active management techniques for improving both the cache performance and energy efficiencies.

## 3.1 Analytical Model

At a clock cycle, a cache line may be *active* (powered) or *inactive* (turned off). Thus, without any energy management, all cache lines are active. A cache line is *live* at a clock cycle if it contains data that will be used prior to eviction, and it is *dead* otherwise [85, 66]. Thus, on any clock cycle, a cache line is live, dead, or inactive. For a cache with L lines over T cycles, the total cache cycles expended is the sum of the *live cycles*, the *dead cycles*, and the *inactive cycles*.

*Cache utilization*,  $\eta_u$ , is the average percentage of cache lines containing live data at a clock cycle [85, 66]. Utilization is computed as shown in Equation 1.

$$\eta_u = \frac{\sum_{i=0}^{i=L-1} live\_cycles_{line_i}}{\sum_{i=0}^{i=L-1} active\_cycles_{line_i}}$$

(1)

The *effectiveness* of the cache, E, is the percentage of cache cycles devoted to live lines and is shown in Equation 2. Effectiveness serves as a metric for comparing programmed cache line shutdown strategies; the higher the effectiveness, the higher the percentage of the active cache that retains live data.

$$E = \frac{\sum_{i=0}^{i=L-1} (live\_cycles_{line_i} + inactive\_cycles_{line_i})}{\sum_{i=0}^{i=L-1} (active\_cycles_{line_i} + inactive\_cycles_{line_i})}$$

(2)

Effectiveness can also be represented as shown in Equation 3, where *total\_cycles* refers

to the program execution time. Here, the number of active cycles for a cache line, i.e., the number of cycles the cache line is powered on, is equal to the sum of the number of dead and live cycles for that cache line. The most effective scheme is one where all cache cycles are either live or inactive. Effectiveness is equivalent to utilization without any energy management.

$$E = 1.0 - \frac{\sum_{i=0}^{i=L-1} dead\_cycles_{line_i}}{total\_cycles * L}$$

(3)

Effectiveness can be increased at the expense of a high miss rate. For example, shutting down all but one line in a direct-mapped cache can produce high effectiveness for structured accesses. An efficient cache must be *effective* with high performance. Cache *performance efficiency*,  $\eta_p$ , is defined in Equation 4 as the product of effectiveness and a scaling factor, where  $t_c$  is the cache access time,  $t_p$  is the miss penalty, and *m* is the miss rate. A cache has 100% performance efficiency if it does not contribute any dead cycles and has a 100% hit rate.

$$\eta_p = E * \frac{t_c}{t_c + m * t_p} \tag{4}$$

*Energy efficiency*,  $\eta_e$ , is the ratio of *useful work* to total work. Useful work is the switching energy (i.e., energy consumed during access to the cache) expended in a cache hit. The total work is the sum of the switching energy consumed during all cache accesses (hits and misses) and the leakage energy. A cache has an energy efficiency of unity if all the energy consumed by the cache is equal to the switching energy consumed during cache hits. Energy efficiency is defined in Equation 5, where  $sw_{energy}$  represents the switching energy and  $leak_{energy}$  represents the leakage energy. The switching energy consumed during a cache miss; this approximation affects the results marginally as explained in the next section.

$$\eta_e = \frac{SW_{energy} * num_{hits}}{SW_{energy} * (num_{hits} + num_{misses}) + leak_{energy}}$$

(5)

Although cache sets or lines may be turned off to reduce leakage energy, additional misses that may result from the powering down of parts of the cache can increase program execution times. These increases in execution cycles can lead to higher energy consumption by all active lines, and therefore, the choice of lines or sets to turn off is critical. These additional cache misses and the resultant increase in execution times will in turn drop effectiveness and utilization since the number of dead cycles will also increase. Understanding this relationship between energy efficiency and cache line shutdowns helps identify good strategies for increasing cache efficiency.

### **3.2 Empirical Analysis of Single-threaded Applications**

This section analyses the efficiency of several single-threaded applications. The execution of benchmarks from the SPEC2000 [86], Olden [87] and DIS [88] suites was simulated using the *Simplescalar* [89] simulator, which was modified to obtain cache efficiency.

The initialization phases for the SPEC2000 programs were fast-forwarded during simulation. Energy estimates were derived using *Cacti 4.2* [90] for 70 *nm* technology. The L2 cache access latency was assumed to be fixed at 15 cycles independent of the size and associativity of the cache. Varying the L2 cache latency affected execution times by less than 2%. The definition of energy efficiency assumed that the switching energy for a read was equal to the switching energy for a write. This assumption artificially increased energy efficiency because the real switching energy for a write is lower than that for a read (only one bank is accessed for a write compared to all banks for a read).

Leakage power constituted 95% of the total cache power at 70 *nm* for cache sizes of 256 KB or greater [90], and cache writes constituted a small fraction of the total number of accesses. Therefore, these assumptions affected efficiencies by less than 1%. Finally, the energy was calculated assuming that the cache operated at the highest frequency as given

by Cacti.

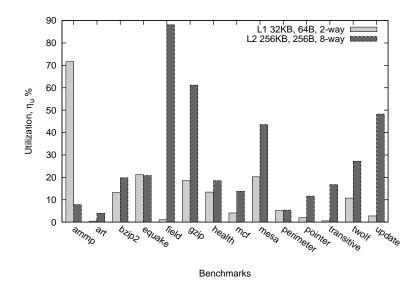

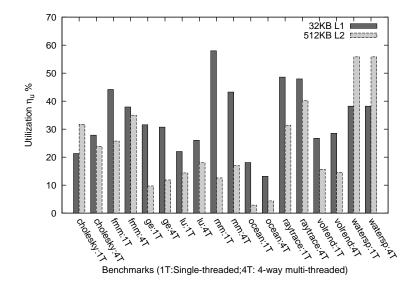

Cache utilization for a 256 KB 8-way L2 cache with 128-byte lines averaged 24% and utilization for the L1 cache averaged 12%. Cache utilizations for the various benchmarks are shown in Figure 1. Since the L2 cache accommodated some data structures entirely for certain applications (*164.gzip, field*), conflict misses were restricted, which resulted in higher utilization values for the L2 cache compared to the L1 cache. The low utilization numbers suggest that both levels of the cache maintain more *dead* lines than *live* lines. Thus, the majority of cache costs are spent in maintaining data that will not be re-used.

Figure 1. Cache utilizations for traditional cache designs.

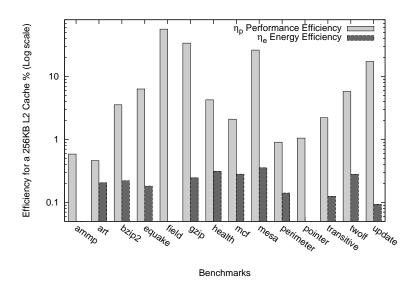

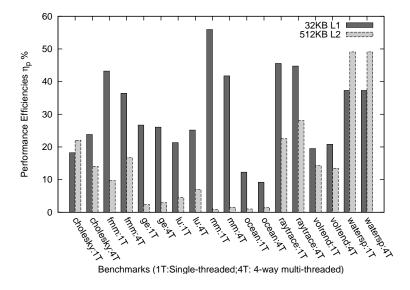

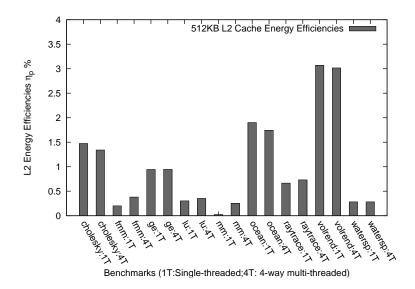

Performance efficiency is shown in Figure 2 and averaged 4.7% for the L2 cache. Cache energy efficiency for current designs averaged 0.17% as observed from Figure 2. The major contributor to this low efficiency value was transistor leakage.

Utilization captures the temporal residency of live data in the cache. Performance efficiency captures how well this residency of live data in the cache is exploited. Thus, a live line that is accessed 10 times during its period of residence is more efficient than if it was only accessed twice during its period of residence. Energy efficiency captures the percentage of overall energy that is *useful* (energy expended servicing cache hits).

Figure 2. Cache efficiencies for traditional cache designs.

Some benchmarks had good utilization; for example, 164.gzip had 60% L2 cache utilization. For this benchmark, two supporting data structures had a 64 KB footprint each. While miss rates for both caches were low for 164.gzip, conflicts arose in the L1 cache because of its smaller size. Since the L1 cache size was only 32 KB, it was unable to fit the supporting data structures; this resulted in low utilization. However, the two data structures fit in the larger 256 KB L2 cache, which resolved most conflicts. Therefore, the larger L2 cache had better utilization than the smaller L1 cache for some benchmarks. The high utilization for 164.gzip was attributable to the linear manner in which the compression object was accessed. L2 cache misses were primarily accesses to this data structure; misses only occurred once per cache line, which resulted in high utilization.