Low-voltage C60 organic field-effect transistors with high mobility and low contact resistance

X.-H. Zhang and B. Kippelen

Citation: Appl. Phys. Lett. **93**, 133305 (2008); doi: 10.1063/1.2993349 View online: http://dx.doi.org/10.1063/1.2993349 View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v93/i13 Published by the American Institute of Physics.

**Applied Physics**

Letters

## **Related Articles**

Designing the rectification behavior of molecular diodes J. Appl. Phys. 112, 113720 (2012) Light emission and current rectification in a molecular device: Experiment and theory J. Appl. Phys. 112, 113108 (2012) Rectifying and perfect spin filtering behavior realized by tailoring graphene nanoribbons J. Appl. Phys. 112, 114319 (2012) Spin filter and molecular switch based on bowtie-shaped graphene nanoflake J. Appl. Phys. 112, 104328 (2012) Universal scaling of resistivity in bilayer graphene Appl. Phys. Lett. 101, 223111 (2012)

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/ Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded Information for Authors: http://apl.aip.org/authors

## ADVERTISEMENT

## Low-voltage C<sub>60</sub> organic field-effect transistors with high mobility and low contact resistance

X.-H. Zhang and B. Kippelen<sup>a)</sup>

Center for Organic Photonics and Electronics (COPE), School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, Georgia 30332, USA

(Received 20 August 2008; accepted 14 September 2008; published online 2 October 2008)

State-of-the-art C<sub>60</sub> organic transistors are reported here by engineering the essential electrode/ semiconductor and dielectric/semiconductor interfaces. By using calcium (Ca) as the source and drain electrodes, the width-normalized contact resistance ( $R_CW$ ) at the electrode/semiconductor interface could be reduced to a constant value of 2 k $\Omega$  cm at a gate-source voltage ( $V_{GS}$ ) of 2.6 V, for devices with channel lengths ranging from 25 to 200  $\mu$ m. Channel transconductance is observed to follow channel length scaling, and charge mobility average value of 2.5 cm<sup>2</sup>/Vs at  $V_{GS} < 5$  V is found independent of channel length within the studied range. © 2008 American Institute of *Physics*. [DOI: 10.1063/1.2993349]

Driven by the demands for low-cost, large-area flexible electronics with low processing temperatures, low-power organic field-effect transistors (OFETs) are of great interest. To date, a major challenge has been to improve the discrete device performance of n-channel OFETs. Electron mobilities as high as 4.9 and 6 cm<sup>2</sup>/Vs have been reported by Itaka<sup>1</sup> and Anthopoulos<sup>2</sup> in C<sub>60</sub> devices when operated at high voltage (>60 V). However, in the former report the on/off current ratio was inevitably reduced by the use of a pentacene (a well-known p-type semiconductor) layer at the dielectric/ semiconductor interface. In the latter report, C<sub>60</sub> was deposited by hot wall epitaxy requiring deposition temperatures as high as 250 °C. Recently, low-voltage C<sub>60</sub> OFETs were demonstrated with a triple layer gate insulator of SiO<sub>2</sub>/ZSO/SiO<sub>2</sub> (ZSO: zirconium-silicon oxide) with low level of hysteresis.<sup>3</sup> However, the threshold voltage of 1.9 V was high compared with the applied voltage of 5 V.

The electrical characteristics of OFETs are governed not only by the properties of the semiconductor material but also by the boundary conditions imposed by the device architecture. The most important factors related to above mentioned conditions to look at are the contacts and the interfaces. For example, the low electron mobility measured from *n*-channel OFETs is often due to the contact resistance imposed by the injection barrier between the organic semiconductor and the source/drain electrodes, sometimes s-shaped output curves are also reported due to the high injection barrier in *n*-type OFETs.<sup>4</sup> The issue of contact resistance in n-channel OFETs, which is far more serious than that of *p*-channel OFETs, has not yet been widely studied. On the other hand, electron trapping at the interface from carbonyl, hydroxyl, and silanol groups has been confirmed as a primary limiting factor for *n*-channel conduction and a major contribution to large threshold voltage.4,5

In this letter, state-of-the-art *n*-channel transistors with commercially available  $C_{60}$  are reported by engineering the essential electrode/semiconductor and dielectric/semiconductor interfaces. The width-normalized contact resistance ( $R_cW$ ) has been reduced to a constant value of

2 k $\Omega$  cm at a gate-source voltage ( $V_{GS}$ ) of 2.6 V for the channel lengths ranging from 200 down to 25  $\mu$ m by using a low work function metal (Ca) as the source/drain electrode, leading to excellent electrical characteristics. Besides high electron mobility with an average value of 2.5  $\text{cm}^2/\text{V}$  s, overall high electrical performance and stability at low operating voltages are demonstrated by using a combination of Al<sub>2</sub>O<sub>3</sub>:BCB (gate dielectric)/C<sub>60</sub> (semiconductor)/Ca (source/drain electrodes) in the device architecture. It not only enables higher performance parameter in a wide range of channel lengths at a low operating voltage, but also significantly improves the electrical stability and reproducibility.<sup>6</sup> The active C<sub>60</sub> layers were formed using physical vapor deposition (PVD) with the substrates kept at room temperature, which would enable the fabrication of  $C_{60}$ devices and circuits on plastic substrates. The combined operating properties of these OFETs are comparable to the best reported p-channel OFETs (Ref. 7) and outperform amorphous silicon thin-film transistors (TFTs).

OFETs were fabricated on heavily n-doped silicon substrates (also serve as gate electrodes) with a top-contact geometry. A 100 nm thick layer of Al<sub>2</sub>O<sub>3</sub> as a gate insulator was formed by atomic layer deposition: a deposition technique that allows for the deposition of highly conformal, defect-free dielectric layers at lower temperature.<sup>8,9</sup> To better control the interfacial properties at the dielectric and C<sub>60</sub>, the Al<sub>2</sub>O<sub>3</sub> dielectric surface was passivated with a thin buffer layer of BCB (Cyclotene<sup>TM</sup>, Dow Chemicals). Crosslinkable BCB can provide a high-quality hydroxyl-free interface to the organic semiconductor with a high dielectric breakdown strength exceeding 3 MV/cm.<sup>6,10</sup> The total capacitance density  $(C_{OX})$  measured from parallel-plate capacitors with 12 varying contact areas was 50 nF/cm<sup>2</sup>. The leakage current density through the gate dielectrics was negligible (below  $10^{-8}$  A/cm<sup>2</sup>) under an applied field of 2 MV cm<sup>-1</sup>. Sublimed grade C<sub>60</sub> (Alfa Aesar) was purified using gradient zone sublimation prior to deposition. A 50 nm thick film of  $C_{60}$  was deposited at a rate of 0.6 Å/s using PVD at a constant pressure of  $5 \times 10^{-8}$  Torr while the substrates were held at room temperature. Subsequently, without breaking vacuum, the deposition of 150 nm thick top source/drain electrodes was done through a shadow mask containing the

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: kippelen@ece.gatech.edu.

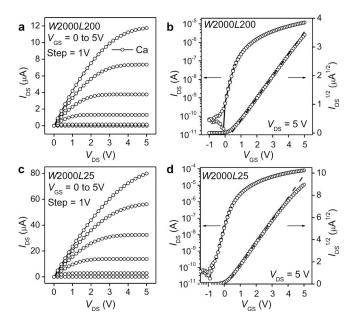

FIG. 1. Comparison of output and hysteretic transfer characteristics of [(a) and (b)] long-channel (L=200  $\mu$ m/W=2000  $\mu$ m) and [(c) and (d)] short-channel (L=25  $\mu$ m/W=2000  $\mu$ m) C<sub>60</sub> OFETs.

desired patterns. Devices had a wide range of width versus length ratios, between 2.5 and 80, with channel lengths ranging from L=25 to 200  $\mu$ m and channel widths ranging from W=500 to 2000  $\mu$ m. With a low work function of 2.9 eV, Ca was chosen for the source/drain electrodes to facilitate electron injection into the lowest unoccupied molecular orbital (LUMO) (3.6 eV) level of C<sub>60</sub> (Refs. 11 and 12) since there is no barrier ( $\Phi_B$ ) between the C<sub>60</sub> LUMO level and the Ca Fermi level ( $E_F$ ) according to the conventional Mott– Schottky model. The electrical measurements were performed in a N<sub>2</sub>-filled glovebox (O<sub>2</sub>, H<sub>2</sub>O < 0.1 ppm) at normal pressure (1 atm) in the dark using an Agilent E5272A source/monitor unit.

Representative output and hysteretic transfer characteristics are compared in Fig. 1 for both long-channel devices  $(L=200 \ \mu\text{m})$  [Figs. 1(a) and 1(b)] and short-channel devices  $(L=25 \ \mu\text{m})$  [Figs. 1(c) and 1(d)] with the same channel width  $W=2000 \ \mu\text{m}$ . The electrical parameters: fieldeffective mobility ( $\mu$ ), threshold voltage ( $V_{\rm T}$ ), subthreshold slope (S), and on/off current ratio ( $I_{\rm on/off}$ ), are summarized and compared in Table I. In this work, the maximum mobility values from the dependence of gate bias in the saturation regime were used to characterize C<sub>60</sub> OFETs. The threshold voltage  $V_{\rm T}$  was determined at the maximum of the second derivative of  $I_{\rm DS}$  with respect to  $V_{\rm GS}$  in the linear regime

TABLE I. Summary of the electrical parameters for C<sub>60</sub> transistors with L=200 or 25  $\mu$ m and  $W=2000 \ \mu$ m. Each data point represents the mean value and the error bars represent the s.d. calculated from two identical devices.  $\mu$  is the field-effect mobility,  $V_{\rm T}$  is the threshold voltage, *S* is the subthreshold slope, and  $I_{\rm on/off}$  is the on/off current ratio.

|                               | $\mu$ (cm <sup>2</sup> /V s) | V <sub>T</sub><br>(V) | S<br>(V/decade) | $I_{ m on/off}$<br>(×10 <sup>6</sup> ) |

|-------------------------------|------------------------------|-----------------------|-----------------|----------------------------------------|

| W=2000, L=200<br>( $W/L=10$ ) | $2.3 \pm 0.2$                | $0.2 \pm 0.1$         | $0.1 \pm 0.04$  | $1.0 \pm 0.3$                          |

| W=2000, L=25                  | $2.3 \pm 0.2$                | $0.2 \pm 0.1$         | 0.1 ± 0.04      | $1.0 \pm 0.3$                          |

| (W/L=80)                      | $2.3\pm0.1$                  | $0.1\pm0.1$           | $0.3\pm0.03$    | $4.0 \pm 0.3$                          |

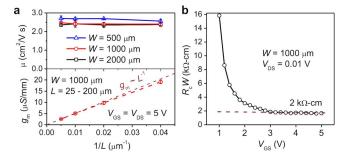

FIG. 2. (Color online) (a) Effect of channel scaling on mobility  $\mu$ , transconductance  $g_{\rm m}$  in *n*-channel C<sub>60</sub> OFETs. Each data point represents the mean value and the error bars represent the s.d. calculated from two to four identical devices (two for W=2000  $\mu$ m and four for W=500 and 1000  $\mu$ m). (b) Contact resistance analysis for *n*-channel C<sub>60</sub> OFETs with a channel width W=1000  $\mu$ m and a channel length *L* ranging from 25 to 200  $\mu$ m. Width-normalized contact resistance  $R_{\rm C}W$  is shown as a function of gate-source voltage  $V_{\rm CS}$  for a drain-source voltage  $V_{\rm DS}$ =0.01 V.

where  $V_{GS}$  (5 V) is much larger than  $V_{DS}$  (0.05 V).<sup>13</sup> Subthreshold slopes (S) and on/off current ratios  $(I_{on/off})$  are also extracted from the transfer characteristics. For each type of transistors, two to four devices with identical geometry were measured to obtain a mean value and standard deviation (s.d.). As shown Figs. 1(b) and 1(d), the devices show no hysteresis in the transfer characteristics. As detailed in the previous report,<sup>6</sup> with BCB at the interface, C<sub>60</sub> OFETs also show excellent electrical stability under both repeated and continuous dc stress. For long-channel devices (W =2000  $\mu$ m/L=200  $\mu$ m) as shown in Figs. 1(a) and 1(b), devices show excellent performance with a high mobility of  $2.3 \pm 0.2 \text{ cm}^2/\text{V}$  s,  $V_{\text{T}}$  close to zero, subthreshold slope S around 0.1 V/decade. When the channel length is scaled down to 25  $\mu$ m, devices start to show short-channel effects, such as a less pronounced saturation of  $I_{DS}$ , earlier turn-on and higher subthreshold voltage,<sup>14</sup> as shown in Fig. 1(d). However, unlike in most n-channel OFETs, the mobility of the devices with Ca contacts remains unaffected with maximum  $I_{\rm DS}$  increased by almost eight times.

To investigate the dependence of mobility on channel length, field-effect mobilities of devices with channel width W=500, 1000, and 2000  $\mu$ m are statistically plotted over the inverse of channel length ( $L^{-1}$ ) in Fig. 2(a). The transconductance  $g_m$ , calculated in the saturation regime as a function of the inverse of channel length ( $L^{-1}$ ) is also plotted in Fig. 2(a), where a  $g_m$  larger than 15  $\mu$ S/mm was achieved for the short-channel devices with L=25  $\mu$ m. With no Schottky barrier between Ca source/drain electrodes and C<sub>60</sub>, the mobility for devices with Ca becomes independent of channel length in the range of L=200  $\mu$ m down to 25  $\mu$ m, as seen in Fig. 2(a). Hence, devices with Ca as source/drain contacts show channel scaling as in metaloxide-semiconductor FET (MOSFET)–like characteristics where  $g_m$  becomes proportional to  $L^{-1}$ .

To gain a better understanding of the contact effect on the mobility, the width-normalized contact resistance ( $R_CW$ ) of C<sub>60</sub> transistors with Ca contacts was extracted using a transmission line method, as shown in Fig. 2(b). The contact resistance was calculated at a low drain-source voltage ( $V_{DS}$ ) of 0.01 V for  $V_{GS}$  values ranging from 1 to 5 V. In general, there are two contributions to contact resistance in topcontact OFETs: the resistance of the metal contact/organic interface and the resistance of organic film itself from the

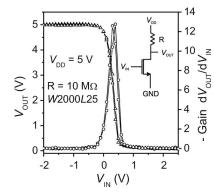

FIG. 3. Voltage transfer characteristics and dc gain of a resistance-load inverter operated under a supply voltage  $V_{\text{DD}}$  of 5 V with a C<sub>60</sub> OFET (W=2000  $\mu$ m/L=25  $\mu$ m) and a resistor (R=10 M $\Omega$ ).

metal to the channel. The former can be reduced by tuning the Fermi level ( $E_{\rm F}$ ) of the metal with  $V_{\rm GS}$  to lower the injection barrier and the latter can be reduced by induced charge density in the accumulation regime with  $V_{\rm GS}$ . In the case of Ca, the contact resistance drops drastically and rapidly reaches a constant value of 2 k $\Omega$  cm by applying only 2.6 V, which is in contrast to the tens of volts needed for most OFETs. The residual contact resistance (which is no longer modulated by the gate bias) could be governed by the intrinsic conductivity of C<sub>60</sub> films. The low residual contact resistance achieved at extremely low  $V_{\rm GS}$  is attributed to the combination of a low injection barrier between C<sub>60</sub> and Ca and a high intrinsic mobility of C<sub>60</sub> (therefore high conductivity).

Figure 3 exhibits the static behavior of resistive-load inverters along with a scheme of the device (inset), which is composed of C<sub>60</sub> OFET and a load resistor (load resistance R=10 M $\Omega$ ). With a low threshold voltage, the inverter operates at a low supply voltage  $V_{DD}$  of 5 V and the inverter shows an almost ideal transfer curve with a sharp output voltage switching between 5 ("high") and 0 V ("low"). No hysteresis was observed during the inverter action, reflecting excellent threshold voltage stability in our OFETs. The measured voltage gain  $-dV_{out}/dV_{in}$ , an important parameter for subsequent stage switching, was as large as 13. This gain obtained at low supply voltage directly benefits from low threshold voltage and high bias current resultant from high mobility and low contact resistance in our  $C_{60}$  OFETs. The parameter exhibits real potential of our OFETs for logic circuits operating at low voltage.

In summary, we have fabricated high-performance *n*-channel C<sub>60</sub>-based OFETs with MOSFET-like electrical characteristics, high electron mobilities of 2.3 cm<sup>2</sup>/V s, threshold voltages near zero ( $V_T < 1$  V), low subthreshold slopes (S < 0.3 V/decade), on/off current ratios larger than 10<sup>6</sup>, and maximum transconductance  $g_m$  larger than 15  $\mu$ S/mm. This overall excellent performance was obtained by engineering the dielectric/organic semiconductor interface and by reducing the contact resistance at the metal contact/organic semiconductor interface. Finally, a simple resistive load organic inverter operating at low voltages (~5 V) was also demonstrated with a high dc gain and without hysteresis in its transfer curve.

This material is based upon work supported in part by the STC Program of the National Science Foundation under Agreement No. DMR-0120967 and by the Office of Naval Research. This work was performed in part at the Microelectronics Research Center at the Georgia Institute of Technology, a member of the National Nanotechnology Infrastructure Network, which is supported by NSF (Grant No. ECS-03-35765).

- <sup>1</sup>K. Itaka, M. Yamashiro, J. Yamaguchi, M. Haemori, S. Yaginuma, Y. Matsumoto, M. Kondo, and H. Koinuma, Adv. Mater. (Weinheim, Ger.) **18**, 1713 (2006).

- <sup>2</sup>T. D. Anthopoulos, B. Singh, N. Marjanovic, N. S. Sariciftei, A. Montaigne Ramil, H. Sitter, M. Colle, and D. M. de Leeuw, Appl. Phys. Lett. **89**, 213504 (2006).

- <sup>3</sup>M. Kitamura, Y. Kuzumoto, M. Kamura, S. Aomori, and Y. Arakawa, Appl. Phys. Lett. **91**, 183514 (2007).

- <sup>4</sup>L.-L. Chua, J. Zaumseil, J.-F. Chang, E. C. W. Ou, P. K. H. Ho, H. Sirringhaus, and R. H. Friend, Nature (London) **434**, 194 (2005).

- <sup>5</sup>M.-H. Yoon, C. Kim, A. Facchetti, and T. J. Marks, J. Am. Chem. Soc. **128**, 12851 (2006).

- <sup>6</sup>X.-H. Zhang, B. Domercq, and B. Kippelen, Appl. Phys. Lett. **91**, 092114 (2007).

- <sup>7</sup>T. W. Kelley, L. D. Boardman, T. D. Dunbar, D. V. Muyres, M. J. Pellerite, and T. P. Smith, J. Phys. Chem. B **107**, 5877 (2003).

- <sup>8</sup>M. D. Groner, F. H. Fabreguette, J. W. Elam, and S. M. George, Chem. Mater. **16**, 639 (2004).

- <sup>9</sup>X.-H. Zhang, B. Domercq, X. Wang, S. Yoo, T. Kondo, Z. L. Wang, and B. Kippelen, Org. Electron. **8**, 718 (2007).

- <sup>10</sup>L.-L. Chua, P. K. H. Ho, H. Sirringhaus, and R. H. Friend, Appl. Phys. Lett. 84, 3400 (2004).

- <sup>11</sup>N. Sato, Y. Saito, and H. Shinohara, Chem. Phys. **162**, 433 (1992).

- <sup>12</sup>P. J. Benning, D. M. Poirier, T. R. Ohno, Y. Chen, M. B. Jost, F. Stepniak, G. H. Kroll, J. H. Weaver, J. Fure, and R. E. Smalley, Phys. Rev. B 45, 6899 (1992).

- <sup>13</sup>H. S. Wong, M. H. White, T. J. Krutsick, and R. V. Booth, Solid-State Electron. **30**, 953 (1987).

- <sup>14</sup>S. M. Sze, *Physics of Semiconductor Devices* (Wiley, New York, 1981).