# EXPLOITING ON-CHIP MEMORY CONCURRENCY IN 3D MANYCORE ARCHITECTURES

A Dissertation Presented to The Academic Faculty

By

Syed Minhaj Hassan

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology December 2016

Copyright © 2016 by Syed Minhaj Hassan

# EXPLOITING ON-CHIP MEMORY CONCURRENCY IN 3D MANYCORE ARCHITECTURES

Approved by:

Dr. Sudhakar Yalamanchili, Advisor Joseph M. Pettit Professor, School of ECE Georgia Institute of Technology

Dr. Tushar Krishna Assistant Professor, School of ECE Georgia Institute of Technology

Dr. Santosh Pande Associate Professor, College of Computing Georgia Institute of Technology Dr. Saibal Mukhopadhyay Associate Professor, School of ECE Georgia Institute of Technology

Dr. Hyesoon Kim Associate Professor, College of Computing Georgia Institute of Technology

Dr. Richard Vuduc Associate Professor, College of Computing Georgia Institute of Technology

Date Approved: August 22, 2016

Dedicated to,

my parents and my siblings - my life is nothing without you all.

## ACKNOWLEDGMENT

During the course of my PhD, which spanned the last seven years of my life, many people inspired me, contributed technically towards my work, and helped me stay focused in pursuit of my goals. I would like to thank all of them for their contributions that allowed me to achieve my dream.

The most important contribution comes from my PhD advisior, Dr. Sudhakar Yalamanchili, to whom I will remain indebted forever. He has encouraged me to be bold and creative and present new far fetched ideas, listened patiently to every small and crazy thought that I came up with and provided guidance and constructive feedback to each one of them, kept me up-to-date for any new development in my subject allowing my work to remain relevant and state-of-the-art, pushed me to not give up when things are not working as I expected them to, helped me improve my writing, presentation, and communication skills, and even took care of me during my financial and visa problems. He is one of the nicest person that I have ever met and I feel extremely lucky to find such a great mentor in early days of my studies at Georgia Tech. Thank you very much Professor Sudha for enduring me through all these years and helping me shape and reshape my thesis, career, and life goals.

I would also like to thank my dissertation committee members: Dr. Saibal Mukhopadhyay, Dr. Moin Qureshi, Dr. Tushar Krishna, Dr. Hyesoon Kim, Dr. Richard Vuduc, and Dr. Santosh Pande. A few of them have been providing me extremely valuable feedback during the course of my PhD. All of them have given me necessary advices and suggestions after my proposal and dissertation that helped me focus my attention to critical tasks and polish my results. It is the classes taken by these very professors that helped me improve my understanding of the thesis topic allowing me to consider it from different angles. I would also like to thank all my teachers in Georgia Tech and also my teachers during my previous masters and undergraduate studies for teaching me the necessary skills to overcome the challenges of a PhD.

Next, I would like to thank all my labmates / colleagues of Georgia Tech for the support they have provided me in my work. Six seven years is a long time to work, collaborate, discuss ideas with a large number of people. I would like to thank all of them for their constructive comments and thoughts that have shaped up my research and career goals. Special mention needs to be given to Mitchelle and Dhruv from the early days and Si, Eric, and William in the later half of my thesis. Thank you very much for helping and supporting me during crazy never ending deadlines. Special thanks to the developers of the tools, specially manifold and kitfox, that I have used extensively during my research. I would also like to thank my managers, mentors, and colleagues of my internships / parttime jobs that I did during this period specially Luv and his team, Vinod and his team, and Dr. Shoab and his team. In a brief period, you guys have transfered part of your knowledge that not only improved my understanding of the subject matter but helped me a great deal in shaping up my thesis. Thank you very much for listening to my crazy ideas and keep encouraging me to broaden my knowledge base even further. Thanks also to the research collaborators from other universities and departments as well specially Maciej Besta of ETH Zurich for the SlimFly work.

Next, I would also like to thank all the friends that I made during my time in Atlanta. I met some of the most amazing people during my stay and had some unforgettable memories with them. These are the people that keep me positive through difficult times, made me laugh, and allowed me to keep going. The list is very long but special thanks to Hussain, Sajid, and Ali; Muneeb and Abdul Qadir; Saad and Asif; Mohsin and Umer; and Adil, Naveed, and Ahmad. You guys became my mini-family and made my time in Atlanta one of the most memorable days of my life. My utmost gratitude to Hussain, who endured all my frustrations, supported me in every thick and thin from day one, and never allowed me to loose focus.

I am left with thanking my family members. I will start with my siblings: Meiraj, Maryam, Murtaza, Mujtaba, and Maliha. You are the lights in my heart, the people who have always stood by my side, encouraging me, supporting me, picking me up, and never allowing me to loose faith on myself. Talking and chatting with you guys always brings smile to my face. Sorry for not being available in your happiness and sorrows during the last few years because of the crazy amount of work required to finish the dissertation.

And finally my parents, Mumtaz and Sarwat, for all the prayers, love, and sacrifices they have made to make me a doctoral candidate and then patiently waiting for my dissertation to finish. Thanks to my mother, who deep down never wanted me to leave, but still always encouraged me to pursue my goals. My utmost thanks to my father, who sacrificed his own ambitions to allow his kids to pursue long successful careers. I owe everything to you both.

## TABLE OF CONTENTS

| ACKNO   | WLEDGMENT                                                           | iv  |

|---------|---------------------------------------------------------------------|-----|

| LIST OF | TABLES                                                              | xi  |

| LIST OF | FIGURES                                                             | xii |

| SUMMA   | <b>RY</b>                                                           | xvi |

| CHAPTI  | ER 1 INTRODUCTION                                                   | 2   |

| 1.1     | Analysis and Optimization of an Exemplar 3D System                  | 4   |

| 1.2     | The 2D Network                                                      | 5   |

| 1.3     | Thermal Analysis and Optimizations of 3D Memories                   | 8   |

| CHAPTI  | ER 2 BACKGROUND AND RELATED WORK                                    | 10  |

| 2.1     | Conventional Memory Systems                                         | 10  |

| 2.2     | 2D vs. 2.5D vs. 3D Stacked Memory                                   | 12  |

|         | 2.2.1 Challenges and Trends                                         | 14  |

| 2.3     | Thermal Concerns in 3D Memory                                       | 15  |

|         | 2.3.1 Various Cooling solutions                                     | 16  |

|         | 2.3.2 Pin-fin Enhanced Microgap Cooling (Microfluidics)             | 17  |

|         | 2.3.3 Various Refresh Management Schemes                            | 18  |

| 2.4     | On-Chip Network                                                     | 20  |

|         | 2.4.1 Topologies                                                    | 21  |

|         | 2.4.2 Buffer Area and Power                                         | 22  |

|         | 2.4.3 Bubble Flow Control and its Variant                           | 24  |

| CHAPTI  | ER 3 ANALYSIS AND OPTIMIZATION OF AN EXEMPLAR 3D SYS-               |     |

|         | ΤΕΜ                                                                 | 25  |

| 3.1     | Summarizing the Experiments and Motivation Behind Them              | 25  |

| 3.2     | The Exemplar 3D System - An Overview                                | 26  |

| 3.3     | Simulation Environment                                              | 27  |

| 3.4     | Impact of the Number of Memory Channels                             | 29  |

|         | 3.4.1 Larger BL and Smaller Transaction Wastes Memory Bandwidth -   | •   |

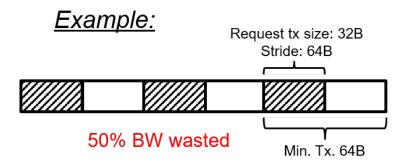

|         | All Hits Case                                                       | 30  |

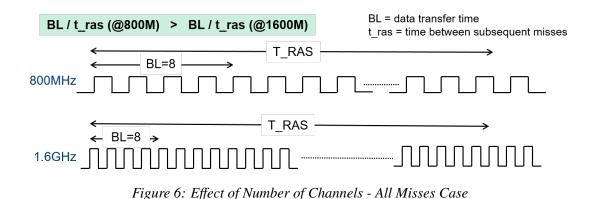

|         | 3.4.2 Increased Frequency Reduces DRAM Efficiency - All Misses Case | 31  |

|         | 3.4.3 Cost of a Channel                                             | 33  |

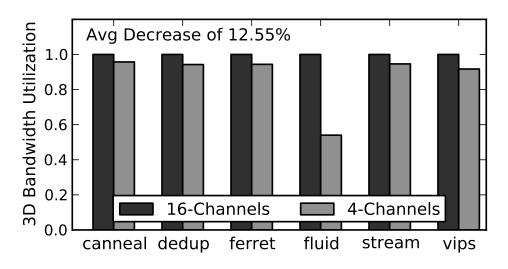

| 2.5     | 3.4.4 Current Standards                                             | 33  |

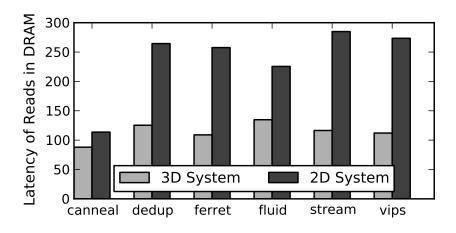

| 3.5     | Impact of High Bandwidth                                            | 34  |

|         | 3.5.1 Smaller Cache Sizes and Fewer Levels                          | 34  |

|         | 3.5.2 Reduced MC Queuing Delay                                      | 34  |

| 2.6     | 3.5.3 Comparable Network Latency                                    | 35  |

| 3.6     | Impact of Address Translations                                      | 37  |

|       | 3.6.1        | CAM and GAM under Multi-level Cache Hierarchy    | 40 |

|-------|--------------|--------------------------------------------------|----|

| 3.7   | An Im        | proved 3D Memory System                          | 41 |

|       | 3.7.1        | Same Address Mapping and Memory Side Cache       | 41 |

|       | 3.7.2        | DRAM Traffic Distribution - Neighbor Mapping     | 43 |

|       | 3.7.3        | Keeping Data Local                               | 44 |

| 3.8   | Perfor       | mance with the Improved Organization             | 45 |

|       | 3.8.1        | Address Mapping - Results                        | 45 |

|       | 3.8.2        | Effect of Mem-Side Caching                       | 47 |

|       | 3.8.3        | Neighbor Mapping - Results                       | 48 |

|       | 3.8.4        | First Touch Policy - Results                     | 49 |

| 3.9   | Concl        | uding Remarks                                    | 50 |

| CHAPT | ER 4         | CENTRALIZED BUFFER ROUTERS                       | 51 |

| 4.1   |              |                                                  | 51 |

|       | 4.1.1        |                                                  | 51 |

|       | 4.1.2        |                                                  | 52 |

|       | 4.1.3        | Pipeline Stages                                  | 53 |

| 4.2   | Looka        | · ·                                              | 54 |

|       | 4.2.1        |                                                  | 55 |

| 4.3   | Deadl        | ock Avoidance                                    | 56 |

|       | 4.3.1        | Avoiding Routing Deadlock                        | 57 |

|       | 4.3.2        | Avoiding Message Dependent Deadlock              | 61 |

| 4.4   | Power        | Reduction Techniques                             | 62 |

|       | 4.4.1        | Reducing the number of CB ports                  | 63 |

|       | 4.4.2        | Power Gating of CB                               | 63 |

| 4.5   | Result       | S                                                | 64 |

|       | 4.5.1        | Simulation Setup                                 | 64 |

|       | 4.5.2        |                                                  | 66 |

|       | 4.5.3        | Buffer Space Reduction Analysis                  | 71 |

|       | 4.5.4        | Power Analysis                                   | 72 |

|       | 4.5.5        | Results with Real Benchmarks                     |    |

| 4.6   | Concl        | uding Remarks                                    | 74 |

| CHAPT | E <b>R 5</b> | IMPROVING DETERMINISTIC CBR - BUBBLE-SHARING FLO | W  |

|       |              | CONTROL                                          | 76 |

| 5.1   | Bubbl        | e Sharing with the Central Buffers               | 76 |

|       | 5.1.1        | Black & White Bubbles:                           | 77 |

|       | 5.1.2        | Gray Bubble:                                     | 78 |

|       | 5.1.3        |                                                  | 80 |

|       | 5.1.4        |                                                  | 81 |

| 5.2   | -            | 8                                                | 82 |

|       | 5.2.1        | e                                                | 82 |

|       | 5.2.2        |                                                  | 83 |

|       | 5.2.3        |                                                  | 84 |

|       | 5.2.4        | Satisfying Condition 3                           | 85 |

| 5.3    | Modif | fications to Centralized Buffer Router                   |    |     | . 87  |

|--------|-------|----------------------------------------------------------|----|-----|-------|

|        | 5.3.1 | Worm Bubble Coloring (WBCS)                              |    |     | . 88  |

| 5.4    | Resul | ts                                                       |    |     | . 88  |

|        | 5.4.1 | Simulation Setup                                         |    |     | . 88  |

|        | 5.4.2 | Performance with Synthetic Traffic                       |    |     | . 89  |

|        | 5.4.3 | Buffer Space Analysis                                    |    |     | . 91  |

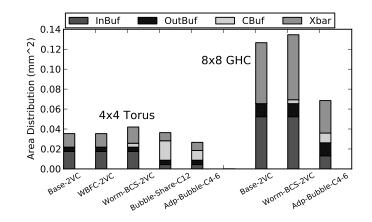

|        | 5.4.4 | Impact on Area                                           |    |     | . 93  |

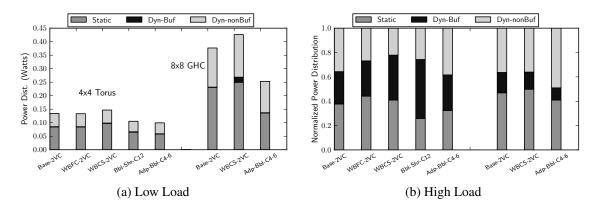

|        | 5.4.5 | Impact on Power                                          |    |     |       |

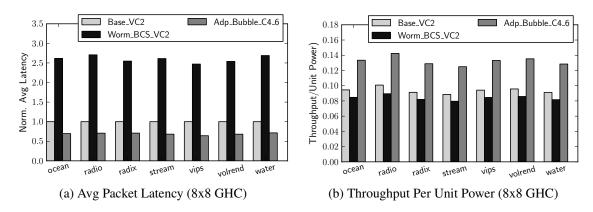

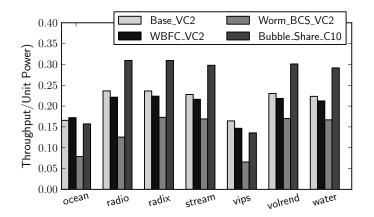

|        | 5.4.6 | Results with Real Benchmarks                             |    |     | . 94  |

| 5.5    | Concl | uding Remarks                                            |    | • • | . 95  |

| СНАРТЕ | ER 6  | DETERMINISTIC CBR WITH VCS FOR IRREGULAR                 | TO | PO  | LO-   |

|        |       | GIES                                                     |    |     | . 97  |

| 6.1    | Multi | -VC Centralized Buffer Router                            |    |     | . 97  |

| 6.2    |       | lim Fly Topology (SF)                                    |    |     |       |

| 6.3    |       | CHIP SLIM FLY                                            |    |     |       |

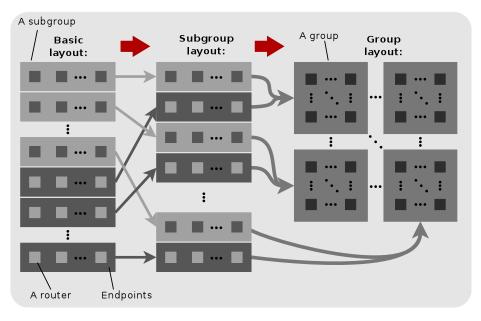

|        | 6.3.1 | Slim Fly Layouts                                         |    |     | . 102 |

|        | 6.3.2 | Ensuring Deadlock Freedom                                |    |     |       |

| 6.4    |       | UATION OF ON-CHIP SLIM FLY                               |    |     |       |

|        | 6.4.1 | Simulation Setup                                         |    |     | . 104 |

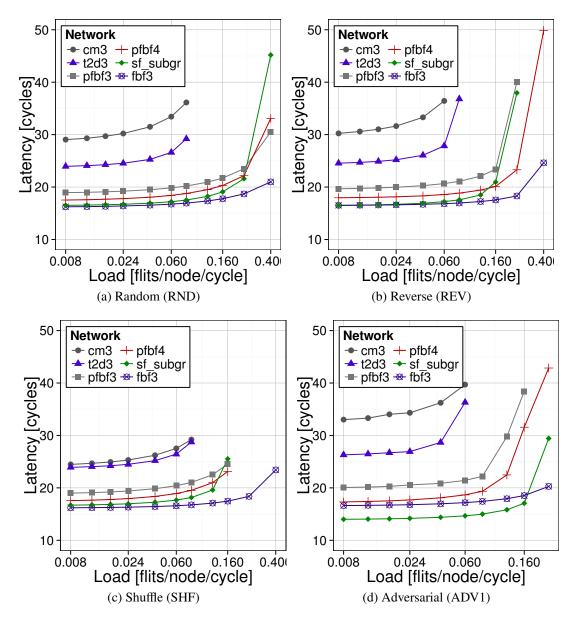

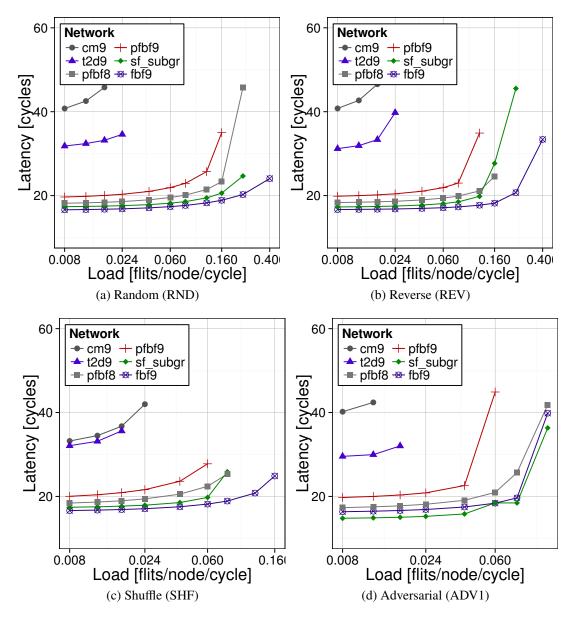

|        | 6.4.2 | Performance: Synthetic Traffic                           |    |     |       |

|        | 6.4.3 | Buffer Sizes                                             |    |     | . 107 |

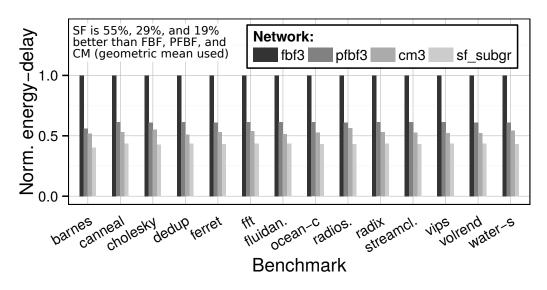

|        | 6.4.4 | Performance & Power: Traces                              |    |     | . 108 |

| 6.5    | Concl | uding Remarks                                            |    | • • | 109   |

| СНАРТЕ | ER 7  | THERMAL ANALYSIS OF 3D MEMORIES                          |    |     | . 110 |

| 7.1    | Evalu | ation Methodology                                        |    |     |       |

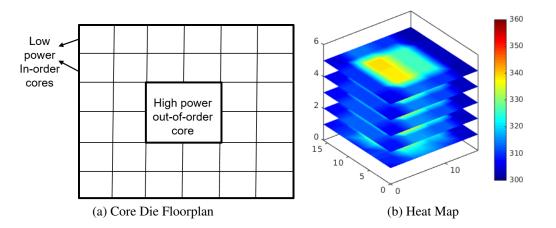

| 7.2    |       | nal Characteristics of a 3D System                       |    |     |       |

|        | 7.2.1 |                                                          |    |     |       |

|        | 7.2.2 | High Variance within and across the Dies                 |    |     |       |

|        | 7.2.3 | Higher DRAM leakage                                      |    |     |       |

|        | 7.2.4 | 3D Thermal Wall                                          |    |     |       |

| 7.3    | 3D Re | eliability and Thermal Dependency                        |    |     | . 116 |

|        | 7.3.1 | Reliability-Performance Tradeoff                         |    |     | . 117 |

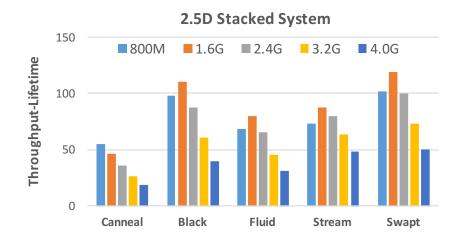

|        | 7.3.2 | Throughput-Lifetime Product                              |    |     | . 118 |

| 7.4    | Impac | et of Microfluidics Cooling                              |    |     |       |

|        | 7.4.1 | Thermal Maps with and w/o Microfluidics Cooling          |    |     |       |

|        | 7.4.2 | Performance Scaling with and w/o Microfluidics           |    |     |       |

|        | 7.4.3 | Impact of Microfluidics using the Roofline Model         |    |     |       |

|        | 7.4.4 | Challenges and Future Potential of Microfluidics Cooling |    | • • | . 126 |

| 7.5    | Concl | uding Remarks                                            |    | • • | . 127 |

| CHAPTI |                                                         |     |

|--------|---------------------------------------------------------|-----|

|        | MENT FOR 3D STACKED SYSTEMS                             | 128 |

| 8.1    | DRAM Refresh Problem                                    |     |

|        | 8.1.1 DRAM Refresh Dependency on Temperature            |     |

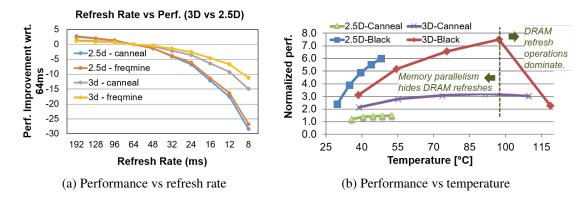

| 8.2    | Impact of 3D Characteristics on Refresh                 |     |

|        | 8.2.1 Reduced Refresh Performance Penalty               |     |

|        | 8.2.2 Thermal Limit Affecting Performance               |     |

|        | 8.2.3 Correlation Between Performance and Refresh Power | 133 |

|        | 8.2.4 Summarizing the Idea                              | 133 |

| 8.3    | A Motivating Example                                    | 134 |

| 8.4    | Various Refresh Management Aspects                      | 136 |

|        | 8.4.1 Demand vs. Opportunistic vs. Postponed Refresh    | 136 |

|        | 8.4.2 Fine- vs. Coarse-Grained Refresh                  | 137 |

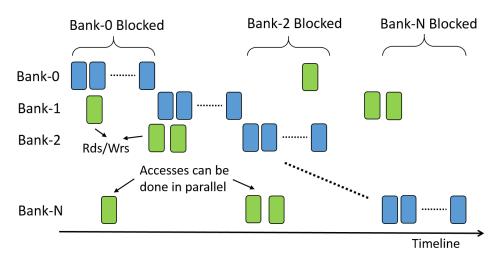

| 8.5    | Per-Bank Refresh                                        | 138 |

|        | 8.5.1 Advantages                                        | 138 |

|        | 8.5.2 Challenges                                        | 139 |

| 8.6    | Variable-Rate Per-Bank Refresh Management (VPReM)       | 144 |

|        | 8.6.1 Fixed- vs Variable-Rate Refresh                   | 144 |

|        | 8.6.2 Temporal vs Spatial Variations                    | 145 |

|        | 8.6.3 Exploiting Variations Per Channel                 | 146 |

|        | 8.6.4 Exploiting Variations Per Bank                    | 146 |

| 8.7    | Results                                                 | 147 |

|        | 8.7.1 Evaluation Methodology                            | 147 |

|        | 8.7.2 Per-Bank Refresh Management Results               |     |

|        | 8.7.3 VPReM Results                                     |     |

| 8.8    | Concluding Remarks                                      | 153 |

| HAPTI  |                                                         |     |

| EFERI  | ENCES                                                   | 156 |

## LIST OF TABLES

| Table 1  | System configuration                                             |

|----------|------------------------------------------------------------------|

| Table 2  | DRAM timing parameters [97]                                      |

| Table 3  | Latency Distribution with different Address Mappings for vips 47 |

| Table 4  | System configurations of various routers                         |

| Table 5  | Various traffic patterns                                         |

| Table 6  | Buffer space (KB) with different configurations                  |

| Table 7  | Buffering configurations of various routers                      |

| Table 8  | Buffer space per router (bytes) with different configurations 92 |

| Table 9  | Considered network configurations                                |

| Table 10 | Buffering requirements [KB] for different configurations         |

| Table 11 | DRAM parameters [60] [95]                                        |

| Table 12 | Cooling parameters                                               |

| Table 13 | Refresh rate with various device sizes                           |

| Table 14 | Refresh related differences in conventional and 3D memories      |

# LIST OF FIGURES

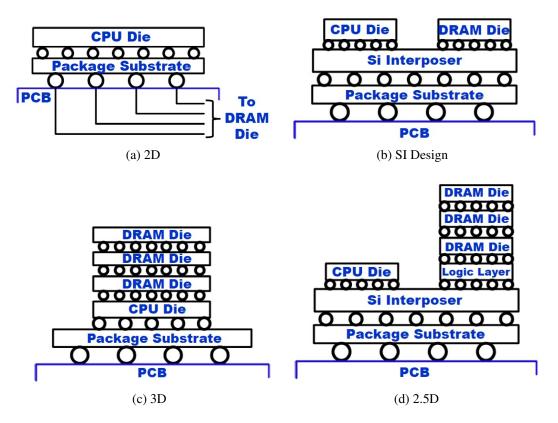

| Figure 1  | Various packaging options for CPUs and memories                                                                                                                           | 12 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

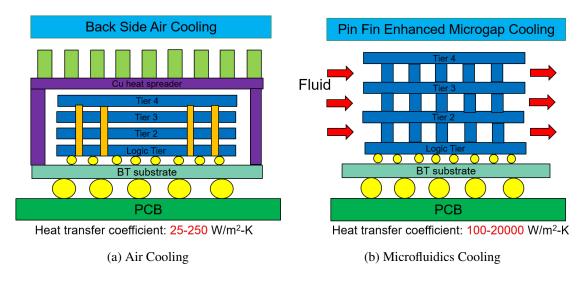

| Figure 2  | Various cooling solutions for 3D-stacked memories                                                                                                                         | 16 |

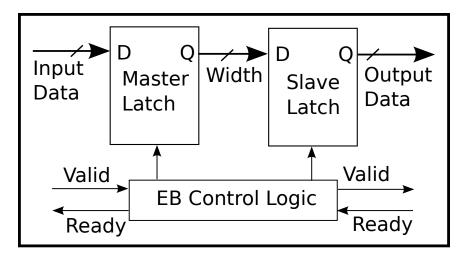

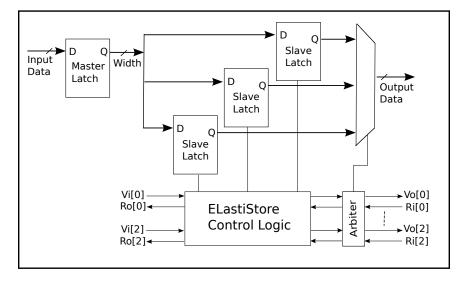

| Figure 3  | An Elastic Buffer (From [59]). Master slave latches of a flip flop are split<br>along with an associated control logic to make them two independent<br>storage locations. | 23 |

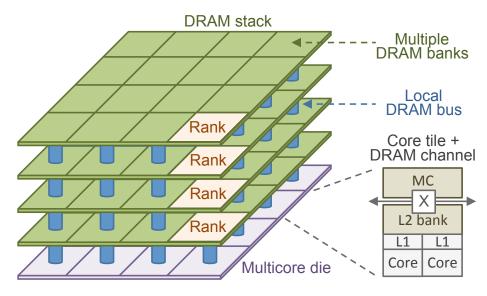

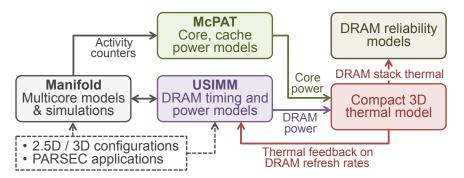

| Figure 4  | Full system model                                                                                                                                                         | 27 |

| Figure 5  | Effect of Number of Channels - All Hits Case                                                                                                                              | 31 |

| Figure 6  | Effect of Number of Channels - All Misses Case                                                                                                                            | 32 |

| Figure 7  | 3D bandwidth utilization with various number of channels                                                                                                                  | 32 |

| Figure 8  | 2D vs. 3D system DRAM latency (cycles)                                                                                                                                    | 35 |

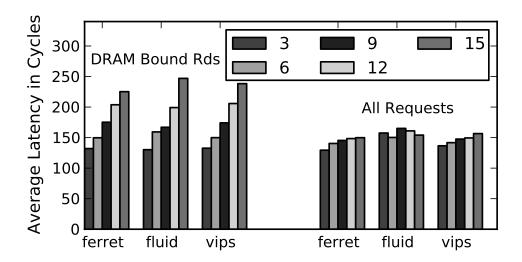

| Figure 9  | Latency of requests from DRAM (cycles)                                                                                                                                    | 36 |

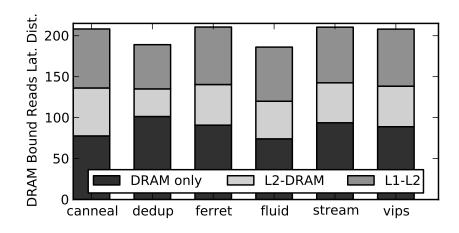

| Figure 10 | DRAM-bound read latency vs. CAS latency. CAS in DRAM cycles,<br>Request in CPU cycles                                                                                     | 36 |

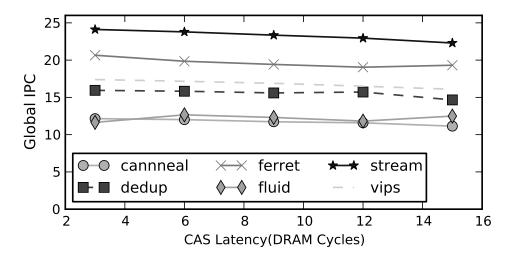

| Figure 11 | CAS latency vs. IPC                                                                                                                                                       | 37 |

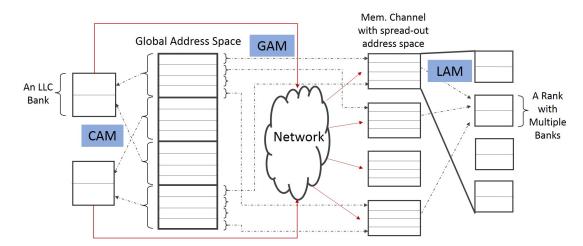

| Figure 12 | Global address space distribution in cache banks and DRAM channels/banks                                                                                                  | 37 |

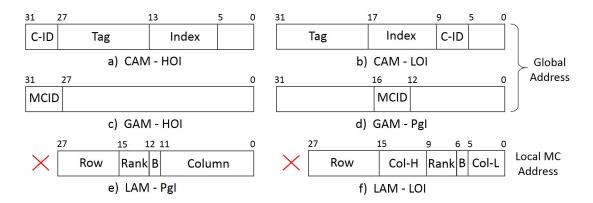

| Figure 13 | Various address space mappings with CAM, GAM, and LAM                                                                                                                     | 38 |

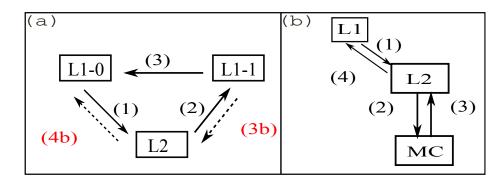

| Figure 14 | Messages generated to fetch from a) a remote cache and b) the DRAM .                                                                                                      | 40 |

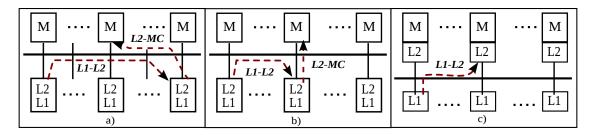

| Figure 15 | a) The basic exemplar system, b) same CAM and GAM organization, and c) mem-side cache organization                                                                        | 42 |

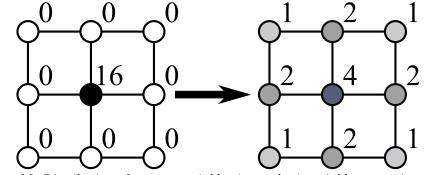

| Figure 16 | Distribution of pages to neighboring nodes in neighbor mapping scheme                                                                                                     | 43 |

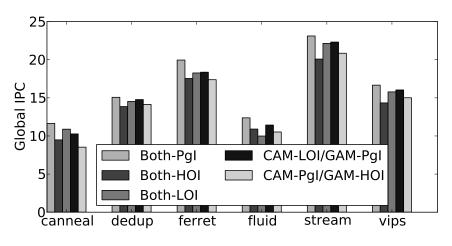

| Figure 17 | IPC with valous address mapping functions                                                                                                                                 | 46 |

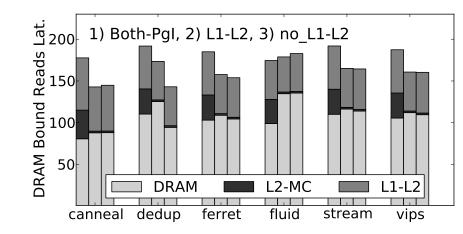

| Figure 18 | Latency distribution of mem-side cache organization                                                                                                                       | 47 |

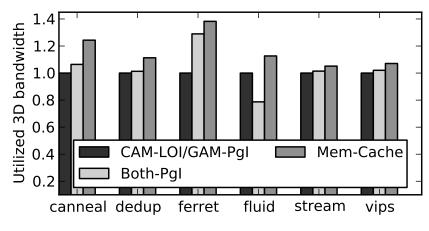

| Figure 19 | 3D bandwidth utilization normalized to baseline                                                                                                                           | 48 |

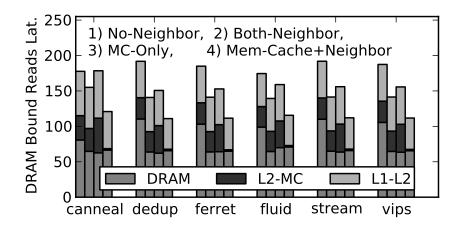

| Figure 20 | DRAM bound reads latency distribution with neighbor mapping                                                                                                               | 49 |

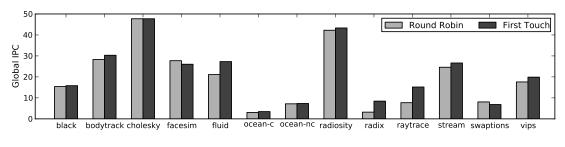

| Figure 21 | Global IPC with and w/o first touch policy                                                                                                                                | 50 |

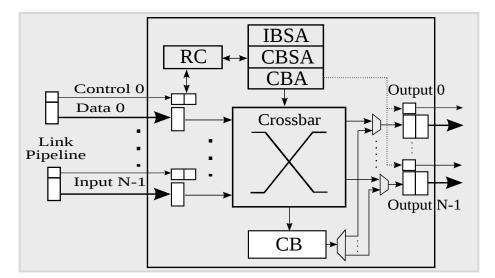

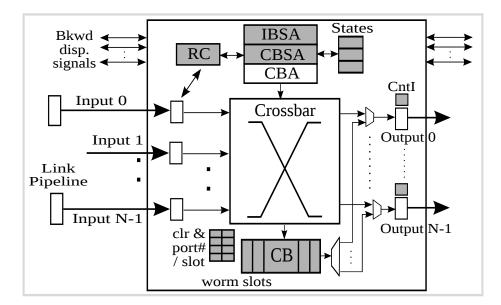

| Figure 22 | Centralized buffer router (CBR) - Micro-architecture                                                                                                                      | 52 |

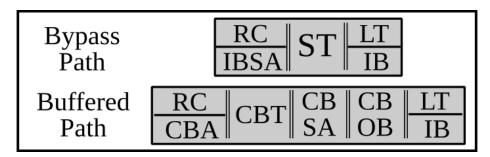

| Figure 23 | Centralized buffer router - Pipeline stages                                                                                   | 53 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|----|

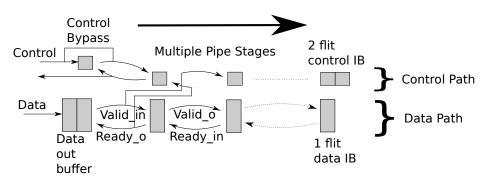

| Figure 24 | Guaranteeing one cycle ahead - Ready Valid handshake signals of data and control path                                         | 55 |

| Figure 25 | Message Dependent Deadlock                                                                                                    | 61 |

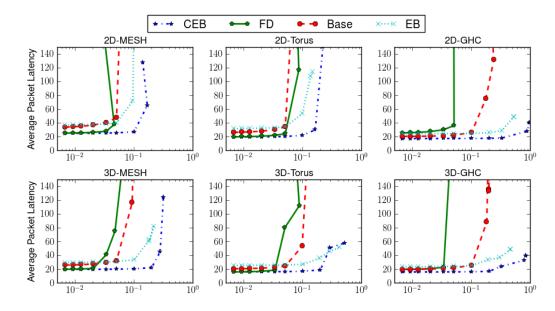

| Figure 26 | Throughput (retired flits / node /cycle) vs average latency (cycles) for different network configurations                     | 67 |

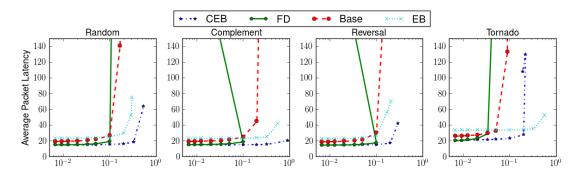

| Figure 27 | Throughput (retired flits / node / cycle) vs average latency (cycles) with different traffic patterns                         | 68 |

| Figure 28 | Performance Impact (throughput vs latency) of individual optimizations .                                                      | 69 |

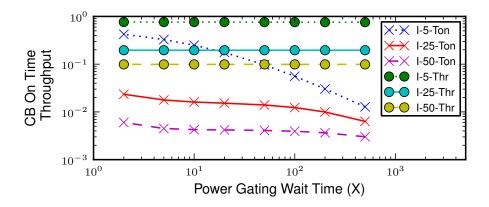

| Figure 29 | Sensitivity to power gating wait time (cycles)                                                                                | 70 |

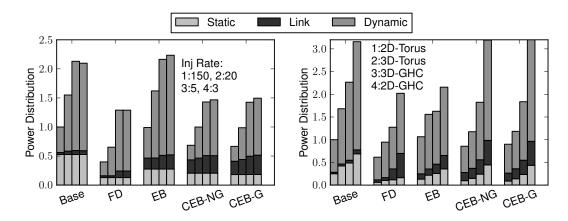

| Figure 30 | Static and dynamic power distribution (a) varying injection rate, (b) vary-<br>ing topology                                   | 72 |

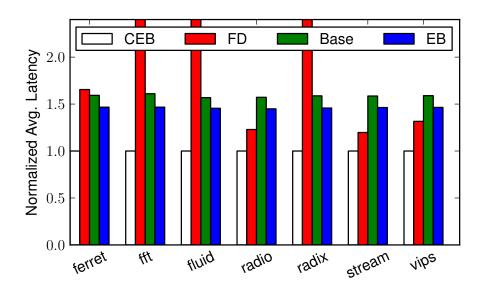

| Figure 31 | Normalized average packet latency for real application traces                                                                 | 73 |

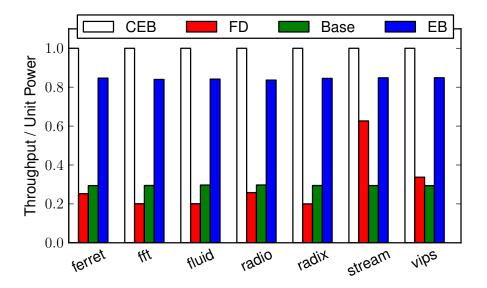

| Figure 32 | Normalized throughput per unit power for real application traces                                                              | 74 |

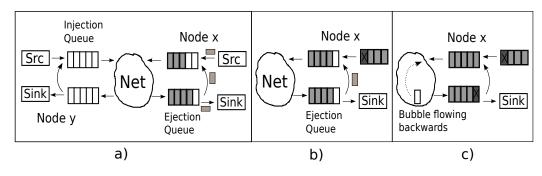

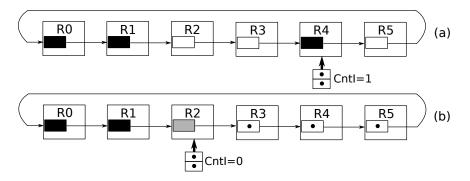

| Figure 33 | Worm-bubble flow control (WBFC)                                                                                               | 78 |

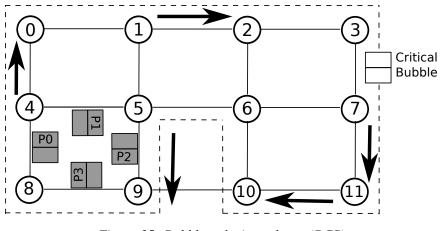

| Figure 34 | Avoiding one ring to take all bubbles                                                                                         | 81 |

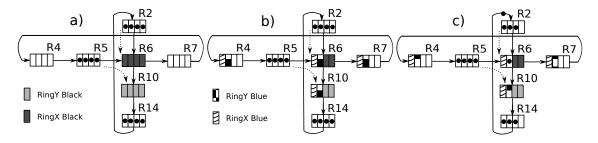

| Figure 35 | Bubble-coloring scheme (BCS)                                                                                                  | 83 |

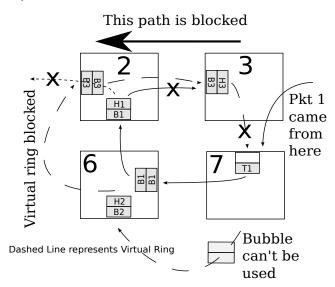

| Figure 36 | An example showing deadlock with BCS in wormhole networks                                                                     | 84 |

| Figure 37 | Modified centralized buffer router [32] to support bubble and adaptive bubble sharing                                         | 87 |

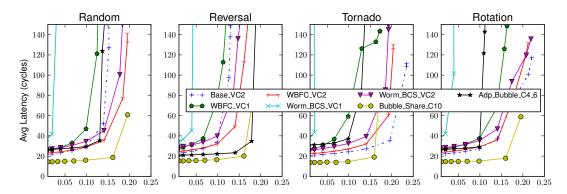

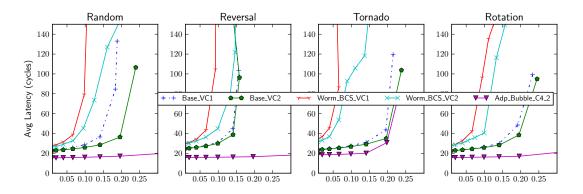

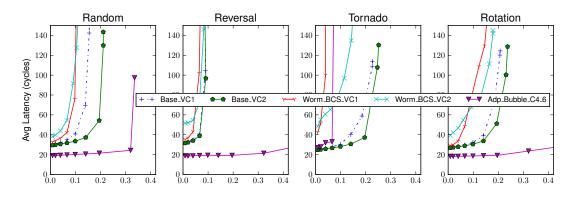

| Figure 38 | Delivered throughput (retired flits / node / cycle) vs average latency (cycles) for 4x4 torus with different traffic patterns | 89 |

| Figure 39 | Delivered throughput (retired flits / node / cycle) vs average latency (cycles) for 4x4 GHC                                   | 90 |

| Figure 40 | Delivered throughput (retired flits / node / cycle) vs average latency (cycles) for 8x8 GHC                                   | 91 |

| Figure 41 | Router area distribution with different configurations                                                                        | 93 |

| Figure 42 | Router power distribution with different configurations: a) Low-load power distribution, b) high-load power distribution      | 94 |

| Figure 43 | Results with benchmark traces - Normalized average packet latency and throughput per unit power for 8x8 GHC                   | 95 |

| Figure 44 | Benchmark Traces Results - Throughput per unit power for 8x8 torus 95                                                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 45 | A basic ElastiStore link                                                                                                                                                                                         |

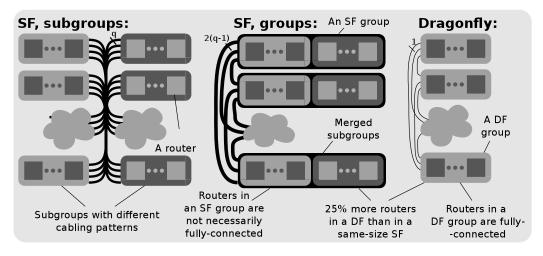

| Figure 46 | High-level overview of Slim Fly topology                                                                                                                                                                         |

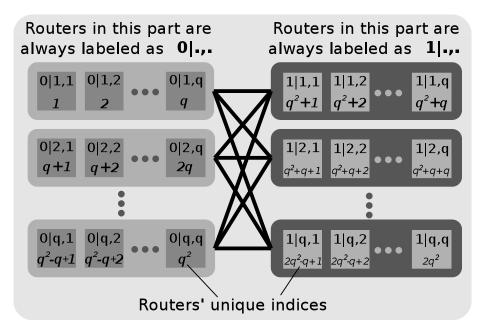

| Figure 47 | Labeling and respective indexes of SF routers                                                                                                                                                                    |

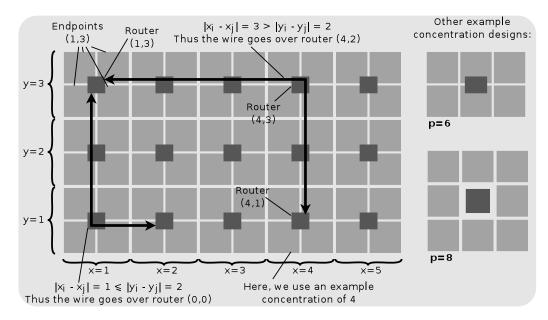

| Figure 48 | The layout model with two example wires                                                                                                                                                                          |

| Figure 49 | Different physical SF layouts                                                                                                                                                                                    |

| Figure 50 | An example partitioned FBF (1D). Cores are not shown                                                                                                                                                             |

| Figure 51 | Performance analysis (synthetic traffic) of networks with $N \approx 200$ endpoints and with SMART links                                                                                                         |

| Figure 52 | Performance analysis (synthetic traffic) of networks with $N = 1,296$<br>endpoints and with SMART links                                                                                                          |

| Figure 53 | (section 6.4.4) PARSEC/SPLASH benchmarks (with SMART) 108                                                                                                                                                        |

| Figure 54 | Evaluation methodology for thermal analysis of 3D stacked memories 111                                                                                                                                           |

| Figure 55 | 2.5D Stacked Memory System for Comparison Purposes                                                                                                                                                               |

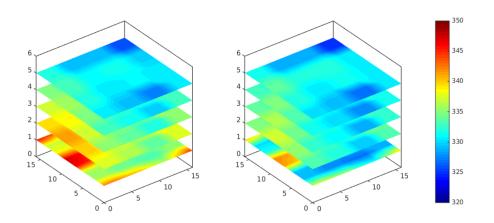

| Figure 56 | 3D Thermal map @2.4GHz with die separation of a) 300e-6m and b)<br>100e-6m                                                                                                                                       |

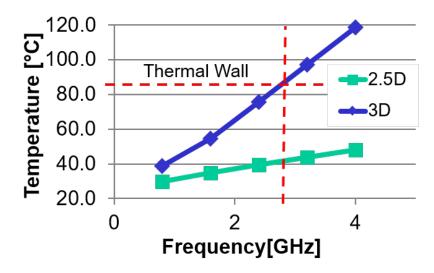

| Figure 57 | 3D thermal wall. Temperature of 3D stacks rise sharply with activity of cores                                                                                                                                    |

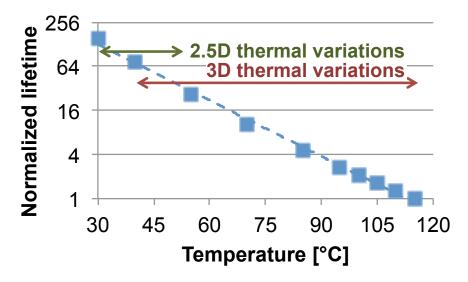

| Figure 58 | Impact of temperatures on DRAM lifetime reliability, and the extent of thermal variations in 2.5D and 3D processors. Lifetime reduces exponentially with temperature                                             |

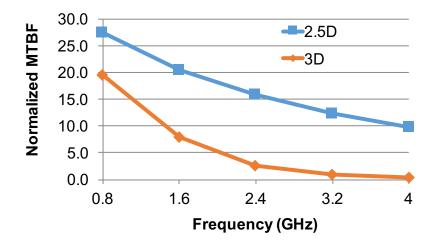

| Figure 59 | 2.5D and 3D lifetime at different operating frequencies. 3D lifetime de-<br>grades rapidly with frequency                                                                                                        |

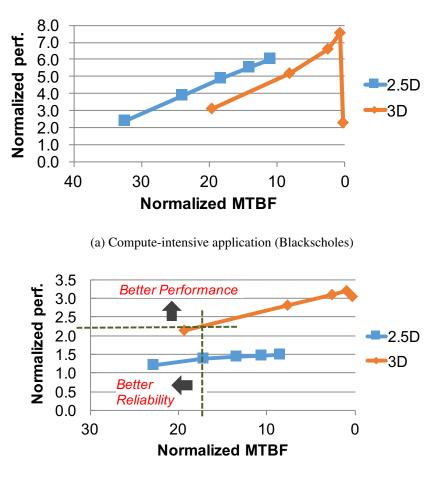

| Figure 60 | Performance and reliability tradeoff between 2.5D and 3D-stacked DRAM processors. Compute-intensive applications has better tradeoff with 2.5D while memory-intensive applications prefers 3D memory systems 118 |

| Figure 61 | Throughput-lifetime product of various applications with various fre-<br>quencies. 2.5D stacked systems exhibit much lower variation in TLP<br>with changing frequency                                           |

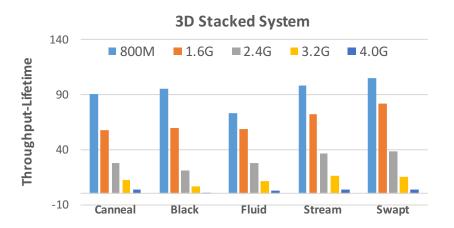

| Figure 62 | Throughput-lifetime product of various applications with various fre-<br>quencies. 3D stacks show higher variation in TLP                                                                                        |

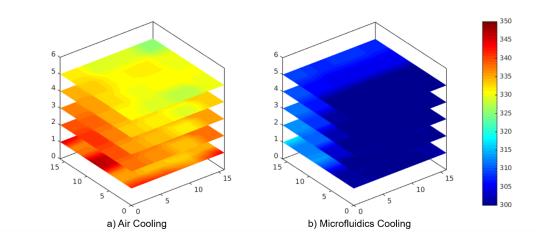

| Figure 63 | Heat-map of blackscholes @2.4GHz with and w/o microfluidics. Mi-<br>crofluidics cooling keeps the temperature very nominal                                                             |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

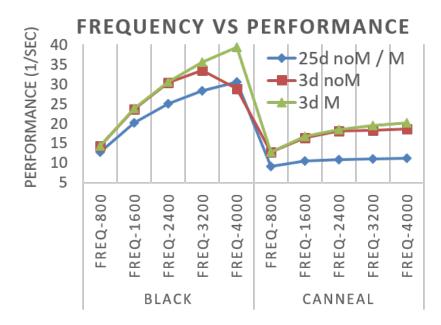

| Figure 64 | Frequency vs Performance. Microfluidics cooling allow continued per-<br>formance scaling specially for compute intensive applications                                                  |

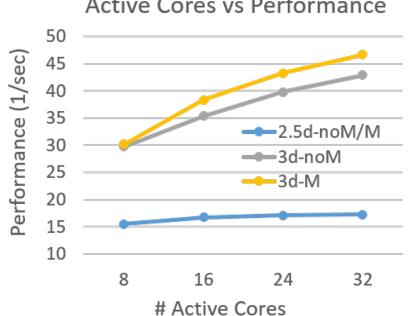

| Figure 65 | Active Cores vs Performance. Microfluidics cooling supports core scaling in the logic die                                                                                              |

| Figure 66 | The roofline model with thermal constraints and microfluidics cooling.<br>Microfluidics cooling allow both compute and memory intensive appli-<br>cations to run at higher frequencies |

| Figure 67 | Utilized 3D bandwidth with and without microfluidics cooling 125                                                                                                                       |

| Figure 68 | DRAM power breakdown with various device sizes [12]                                                                                                                                    |

| Figure 69 | Refresh cycle time for DRAM under different operating temperatures [82].<br>The graph is made by looking at current values of temperature-compensated<br>self-refresh                  |

| Figure 70 | Correlation between performance, power, and temperature of 3D vs.<br>2.5D stacks                                                                                                       |

| Figure 71 | An example floorplan and thermal profile of a heterogeneous 3D stacked system                                                                                                          |

| Figure 72 | Advantages / disadvantages of postponed refresh                                                                                                                                        |

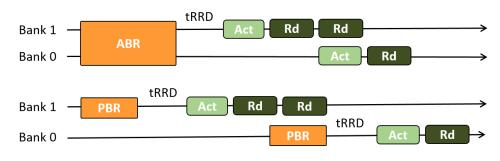

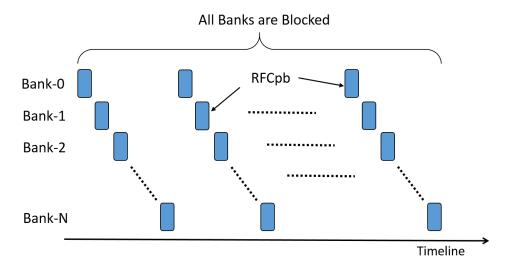

| Figure 73 | Comparison of all-bank and per-bank refresh management                                                                                                                                 |

| Figure 74 | Increased $t\_RRD$ penalty                                                                                                                                                             |

| Figure 75 | Per-bank postponed refresh                                                                                                                                                             |

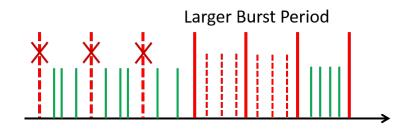

| Figure 76 | Two competing postponed refresh options with per-bank refresh 142                                                                                                                      |

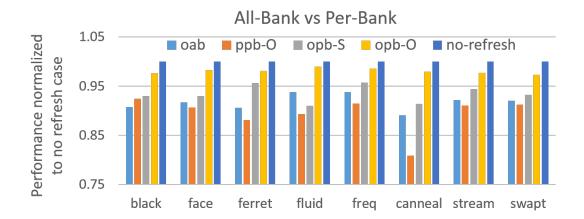

| Figure 77 | Performance of various per-bank refresh management schemes normal-<br>ized to the no-refresh case                                                                                      |

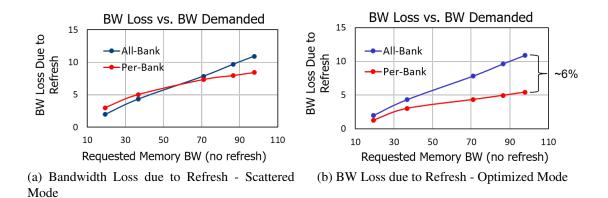

| Figure 78 | Bandwidth loss due to refresh with various refresh management schemes 150                                                                                                              |

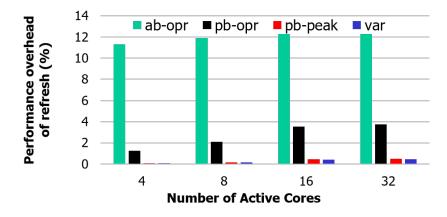

| Figure 79 | Performance overhead with different variable-rate refresh schemes 151                                                                                                                  |

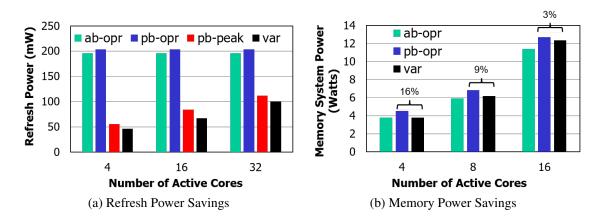

| Figure 80 | Power savings with various variable-rate refresh management schemes . 152                                                                                                              |

### SUMMARY

3D packaging has emerged as a vehicle for scaling system densities and performance due to i) increased inter-tier bandwidth, ii) reduced inter-tier latencies, and iii) ability to integrate dies from different process technologies as a means of customization and hence performance improvement. Moving forward, continued scaling of fine-grained Through Silicon Vias (TSVs) across a 2D cross section can support a large number of memory channels, hence concurrency in the memory system. High concurrency in 3D memory alters the basic relationships between bandwidth, latency, and energy of the memory hierarchy [53, 105]. We re-evaluate these relationships and identify a few key characteristics, optimizing which can significantly improve power and performance of the overall system. These include i) a re-factored memory latency path, in which the difference between the cache and the DRAM latency is reduced, and the network latency becomes a critical part of the overall memory-access latency, ii) an increase in the importance of concurrency management using address space translations to effectively balance various power and performance trade-offs, and iii) a wider thermal operating range of DRAM that significantly impacts its refresh rate and hence, performance. We exploit these observations by proposing architectural modifications and optimizations at various levels of the memory hierarchy with a goal of improving performance and energy efficiency of the overall system.

We first identify the need for fine-granularity and highly-parallelism in 3D memories and characterize its impact on latency in various components of the cache and memory subsystem. We further establish the role of hardware address translations at various levels of the memory hierarchy in regulating locality vs parallelism trade-off in concurrent memory channels and maximize performance [29]. We propose to re-organize the 3D memory hierarchy in order to reduce network traffic and latency. This re-organization is achieved by coupling the addressing scheme of a distributed last-level cache (LLC) with that of a distributed high-channel-count main memory. To reduce the network latency further, we design a single-cycle *centralized-buffer router* (CBR) [33] that supports high-radix networks with small dependence of buffer area on radix. We extend it to support adaptivity [31] and multiple virtual channels [4]. Furthermore, we evaluate its power and performance advantages for both regular and irregular topologies. Lastly, we analyze the temperature problem of 3D memories and characterize its impact on system performance and reliability. We take two distinct approaches. First, we explore how new technologies, such as microfluidics cooling, can help alleviate temperature and reliability concerns. Second, we study how adaptations to the current micro-architecture can expand the operating range of 3D memories that exploits the variability in 3D DRAM temperature to reduce refresh power and allow the DRAM to operate at much higher temperatures tolerating hotspots in the memory subsystem.

# CHAPTER 1 INTRODUCTION

A fundamental limitation of performance scaling in chip multi-processors (CMPs) is the decreasing memory bandwidth per core, generally referred to as the *memory-wall problem* [79]. The problem has worsened over the years as the number of cores per chip doubled every two years while the external pin bandwidth has not increased at the same rate. It is further exacerbated by the increasing demand of power delivery pins reducing the availability of data pins. Three-dimensional (3D) packaging [119] and silicon interposer technology [89] have emerged as promising new solutions to overcome the problem; mainly because of their i) increased inter-tier bandwidth, ii) reduced inter-tier distance, and iii) the ability to integrate dies from different process technologies as a means of customization. Higher bandwidth is achieved by a large number of fine-grained Through Silicon Vias (TSVs), or thin metallic wires of the interposer, which, coupled with DRAM RAS / CAS trends and the need to distribute TSVs evenly across the dies, points towards an increase in the number of channels, thus concurrency in the memory systems [30]. Smaller inter-tier distance has brought large amounts of data close to compute, which potentially can reduce the ever-increasing cost of data movement and has renewed the interest in concepts like near-data processing (NDP) [71], processing-in-memory (PIM) [121], and memory-centric computing [41]. A common theme with all these developments is the rise of fine-grained memory-level parallelism on-chip opening up interesting new challenges and opportunities. In this thesis, we analyze an exemplar 3D system, identify its major bottlenecks, and propose architectural modifications to remove these limitations with the goal of improving performance and energy efficiency of 3D memories.

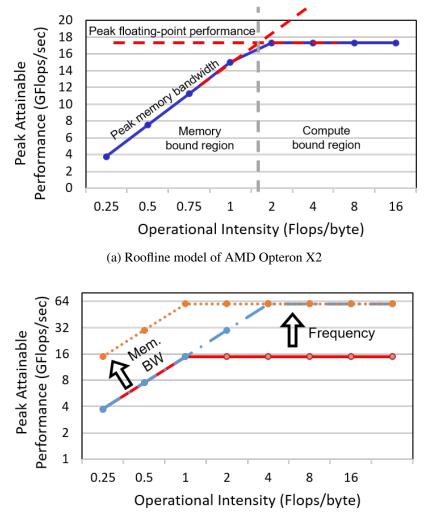

A 3D system alters the basic relationships (i.e. design points) between bandwidth, latency, and power of the memory hierarchy [53, 105]. We re-evaluate these relationships and propose architectural modifications and optimizations that adapts to the new challenges. Specifically, we identify three key characteristics which will be exploited in this thesis.

- A 3D system consists of highly parallel memories with large number of banks and channels, effective utilization of which trades off locality, parallelism, and energy. These trade-offs can be managed by various types of address translations which can be used to reshape the memory traffic and optimize power and performance of the overall system.

- Reduced 3D DRAM delay leads to refactoring of the memory latency path which increases pressure on the interconnection network between the memory and the cache hierarchy. Specifically, network latency becomes comparable to DRAM latency.

- 3. Lower heat removal capability and higher DRAM density of 3D stacks increases their temperature and requires larger number of rows to be refreshed at significantly higher rates. Increased refresh time decreases memory bandwidth availability and higher temperature puts a limit on core operating frequency; both limiting continued performance scaling.

Exploiting these observations requires architectural modifications and optimizations at various levels of the memory hierarchy which is the topic of this thesis; and stated as follows, "High concurrency in 3D stacked memory systems have severely impacted locality, bandwidth, and energy trade-offs, management of which is critical to fully exploit the potential of 3D memory systems".

Following is a brief summary of the major work accomplished in this thesis and is categorized into three distinct parts.

#### **1.1** Analysis and Optimization of an Exemplar 3D System

The first major contribution of this thesis involves analyzing an exemplar 3D system (described in chapter 3), identifying its major bottlenecks, and proposing architectural modifications to address these bottlenecks. The goal is to understand how to carefully manage the parallelism in 3D memories and remove performance inefficiencies by proposing address translations and memory hierarchy re-organization without adding or modifying the internal hardware structures of the core and the memory subsystem. The key insights gained by the analysis of the exemplar 3D system are as follows.

- Assuming a fixed wiring density between the processor and the memory, a 3D system with large number of narrow memory channels has superior performance over a 3D system with a small number of wide memory channels. We use a channel count of 16 for our baseline configuration.

- A large number of channels and banks results in high parallelism, which can be

effectively managed by simple address translation schemes at various levels of the

memory hierarchy to regulate the power and performance trade-offs of the overall

system. A fine-grained interleaving between channels and banks exploits parallelism

increasing performance, but destroys any locality in the memory access stream. It

also increases the load on the network and increases power of the overall memory

subsystem. A coarse-grained interleaving scheme on the other hand does not fully

utilize the high bandwidth of 3D memories and creates hotspots in the network.

- High parallelism in 3D memories reduces the load on individual DRAM banks and channels, which results in decreased queuing delay and smaller latency in the DRAM itself; thus putting more pressure on the interconnection network connecting these channels.

- Reduced DRAM latency and high network traffic increases the criticality of network latency making it comparable to that of DRAM latency, an observation that does not

hold true in conventional 2D systems. This makes 2D network bandwidth a limiting factor for full exploitation of 3D DRAM bandwidth.

• Address management schemes at various levels of the memory hierarchy can nullify each others benefits. Their careful co-ordination is critical to optimize the power and performance of the overall system.

Taking these observations into consideration we reorganize the memory hierarchy into a banked memory-side cache organization that reduces the network traffic. The re-organization is made possible by the co-ordination of address mapping at the LLC and the MC level. To reduce the network traffic further we implemented locality based OS page allocation strategies that tries to keep the data close to the requesting cores as much as possible and analyze their impact on the overall system performance. We also show the importance of traffic distribution to all the channels in order to utilize maximum bandwidth without violating the conventional principles of spatial locality and DRAM hit rate; and use customized address translation schemes to provide this distribution.

#### **1.2 The 2D Network**

The first part of the thesis served to identify i) the importance of the 2D network bandwidth in exploiting 3D bandwidth, and ii) its increasingly dominant role in the overall memory access latency. The thesis focuses on addressing this challenge via the design of a family of interconnection networks that enable effective tradeoffs between area (buffer space), power and bandwidth. The second contribution of this thesis proposes a router micro-architecture suitable for high-radix on-chip networks that reduces network latency and power while maximizing throughput. The goal is to minimize network latency and maximize 2D bandwidth utilization in order to achieve full potentials of high 3D bandwidth. Network latency can be reduced by increasing the router radix and reducing the average hop count of the memory accesses. Higher radix requires large number of links which are also available in abundance on-chip. However, the problem in using large number of links is that each link is associated with multiple buffers, with each one of them taking significant amount of area and power. Furthermore, the minimum depth of each of these buffers has to be equal to the credit round-trip latency (to avoid bubbles between successive flits and maximize link utilization), which also grows with radix and link length. Thus, increasing router radix to reduce latency amplifies buffer needs and exacerbates energy inefficiency.

In this thesis, we propose the use of centralized buffers (CB) in the routers to decouple the required buffer space from its radix and link length. We further present modifications to the baseline centralized buffer router improving its performance and energy and making it suitable for different network configurations. The key contributions in this domain are the following.

- We propose centralized buffer router (CBR) a router micro-architecture based on the use of centralized buffers (CB) with elastic buffered (EB) links [59] that supports high-radix networks. At low loads, the CB is power gated, bypassed, and optimized to produce single cycle operation. At high loads, flits are streamed through the buffered path taking three cycles. A novel extension to bubble flow control enables routing deadlock and message-dependent deadlock to be avoided with the same mechanism having constant buffer size per router independent of the number of message types.

- Flow control of the centralized buffer routers works at a granularity of individual packets in the central buffers. This increases the minimum buffering space required by the CBs. We reduce the buffering requirement of the central buffers by introducing *Bubble Sharing*, a flow control technique that extends the worm-bubble flow-control [16] scheme to centralized buffer routers, reducing its buffer space.

- We also propose *Adaptive Bubble Sharing* that enables adaptive routing with bubblesharing flow control for wormhole switched networks. This reduces latency of the centralized buffer routers further, specially in the case of high-radix networks with

large number of adaptive paths.

- Centralized buffer routers uses elastic buffer (EB) links with variations of bubbleflow control for deadlock avoidance [32]. However, bubble-flow control works only for regular topologies, such as rings and torus. For complex irregular topologies, we extend the centralized buffer design to support multiple VCs. We used recently proposed ElastiStore [84] technique to allow virtual channel with CBRs.

- To explore VC-based CBRs with high-radix irregular topologies, we used the VCenabled CBR design with Slim Fly, a recently proposed high-radix topology by Besta and Hoefler [5], for an optimum diameter-2 on-chip network with the least number of ports in the router. The topology is fairly irregular and requires two VCs for deadlock freedom. Hence CBRs with multi-VC support are used.

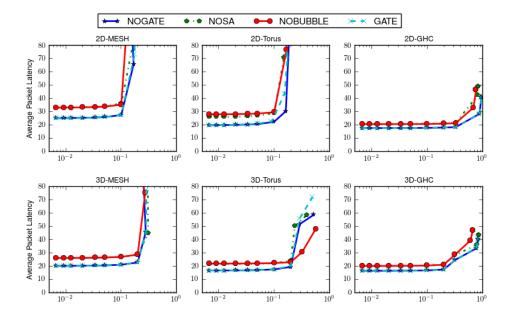

We evaluated the centralized buffer router design and its modifications with various regular and irregular, and low- and high-radix networks and compared its results with various state-of-the-art routers. The major conclusions of these evaluations are as follows. i) A small central buffer in an EB-like design (CBR) can avoid deadlock and improves throughput without the need of having separate virtual channels and physical networks. The size of this buffer is small which can be further reduced by using bubble-sharing flow control, thus the area and power requirement reaches that of EB with a single physical network. The low-load latency is equal to buffer-less routers and the high-load latency is higher than state-of-the-art buffered routers. ii) CBRs, in general, are superior with high-radix topologies because of the slow rate of increase of their buffer space with that of their radix. They perform equally well with low-radix topologies. However, adaptive bubble-sharing CBRs do not perform well with low-radix topologies because of fewer adaptive paths in them. In such a case, deterministic bubble sharing routers performs the best with very small buffering requirements. iii) CBRs that uses bubble-flow control for deadlock freedom are applicable only for regular topologies, such as rings and torus. For irregular topologies, multi-VC CBRs that does not use bubble-flow control are required which provides the best energy-delay product and throughput per unit power for large networks.

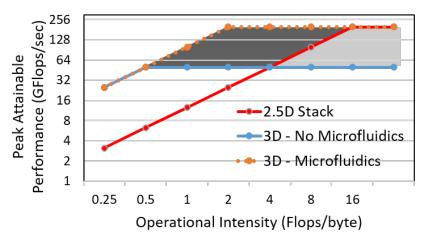

## **1.3** Thermal Analysis and Optimizations of 3D Memories

The last major contribution of this thesis involves dealing with the temperature problem of 3D memories. 3D stacked DRAMs with their lower heat removal capability, higher DRAM density, and higher heat flux operate at much higher temperature as compared to conventional 2D memories. Thus, their usage has been limited to memory-intensive applications running at low frequencies which inherently have lower performance. Further improvement in performance scaling by increasing core complexity or frequency cannot be achieved as it is limited by thermal constraints of the stack. Increased temperature also has a negative impact on lifetime reliability of the memory system.

To this end, we analyze the thermal profile of an exemplar 3D system and identify that thermal constraints are a limiting factor for full utilization of 3D bandwidth. We also analyze and compare the reliability-performance tradeoffs between multicore systems with 3D and 2.5D stacked memory identifying correlations between frequency, performance, temperature, and reliability; and uses it to quantify the reliability-performance tradeoff. Our analysis indicates that 3D-stacked DRAM provides better performance for most applications, but exhibits poorer lifetime due to higher operating temperature. Furthermore, it also indicates that compute-intensive applications have better performance-reliability trade-offs with 2.5D designs, even at higher frequencies, whereas memory-intensive applications favor 3D stacked systems operating at lower frequencies.

We broadly looked at two different solutions to address the thermal challenges of 3D memories, i) how new cooling technologies, such as microfluidics cooling, can help alleviate temperature and reliability concerns and pushes its envelope to both compute- and memory-intensive applications operating at much higher frequencies, thus utilizing the full

potential of high 3D bandwidth, ii) how adaptations to the current memory architecture and algorithms can expand the operating range of 3D memories improving performance and power of the overall system. Specifically, we make a case for variable-rate per-bank refresh management for 3D stacked memories; motivated as follows. Higher temperature of 3D stacks requires large number of rows to be refreshed at higher rates increasing power. Further, different DRAM channels and dies operate at different temperatures due to a high variance in the heat generated by the processor die and a high variance in the heat removal capability of the conventional heat sinks. Exploiting this variation in temperature by allowing different channels and banks to be refreshed at different rates based on their operating temperature not only reduces refresh power and performance penalty but also tolerates thermal hotspots in memory, thus allowing the overall system to operate at much higher frequencies improving performance.

The rest of the dissertation is organized as follows. Chapter 2 gives a brief background of various problems along with the related work in that domain. Chapter 3 analyzes an exemplar 3D system, identifies its performance bottlenecks, and proposes an optimized memory system organization that uses address co-ordination between various levels of the memory hierarchy to reduce the traffic in the network. The next three chapters describes our centralized buffer router (CBR) architecture. Chapter 4 describes the baseline router micro-architecture along with latency and area reduction optimizations. Chapter 5 reduces the buffering space of CBR by proposing bubble-sharing scheme that extends worm-bubble-flow-control to flit level in the CBs. It also proposes adaptive bubble-sharing with CBRs. Chapter 6 extends CBR for multiple VCs and uses it with a recently proposed high-radix irregular topology to reduce the buffering and power requirements of the system. Chapter 7 analyzes the thermal problems of 3D memory and quantifies its reliability concerns along with describing various advantages of microfluidics cooling. Chapter 8 motivates our variable-rate per-bank refresh management scheme and presents its power and performance advantages with chapter 9 concluding the dissertation.

#### **CHAPTER 2**

### **BACKGROUND AND RELATED WORK**

#### 2.1 Conventional Memory Systems

DRAMs conventionally have evolved to consist of multiple ranks (collection of devices operating in unison) that combine to form a DRAM channel [36]. Each rank has many banks which allow multiple outstanding requests to be serviced in parallel by the memory controller (MC). An MC takes incoming requests from the last level cache and issues DRAM specific commands to access the data present in the arrays. The corresponding response is then sent back on completion. However, the number of channels and thus banks are limited in a conventional 2D system resulting in application level interference in the MC. Conventional 2D systems have limited number of memory channels resulting in low DRAM bandwidth and thus application/thread-level interference in the MC queues. Under high load caused by the increasing number of cores and slow DRAM service rates, MCs [65] suffer high queuing delays. To minimize the queuing delays, as well as improve DRAM service rates, several memory scheduling algorithms have been proposed. Their main optimization criteria is to improve either hit-rate or bank-level parallelism (BLP) of the memory requests [78, 65]. Some works have also looked upon optimizing both in tandem in a single-MC case [65], as well as in multiple-MC cases [46]. Yuan et al. [120] uses switch arbitration in the network to increase DRAM hit rate. Das et al. [20] further uses the notion of criticality over hit rate to improve overall system performance. These algorithms improve performance by reordering memory requests going to a bank or across different banks. However, the scope of scheduling is limited, since it is the arrival pattern of requests that govern the delays, and scheduling alone cannot change them.

The arrival pattern of requests can be modified by the use of various address translation mechanisms, which have been explored extensively to spread the data across multiple channels and banks of a DRAM. Zhang et al. [124] uses XOR of bank bits to spread accesses from an application across different banks in a single DRAM. Hassan et al. [29] presents a class of address mapping that distributes traffic to different MCs while preserving the DRAM hit rate. Impulse [122] performs another level of address translation to align consecutive requests and improve hit rate. Micro-pages [99] allocate separate physical DRAM pages to frequently accessed cache lines in order to increase hit rate. Awasthi et al. [3] proposes dynamic page migration from highly congested DRAM channels to less congested DRAM channels that distributes the traffic across different DRAMs. Some other solutions [40] [64] have combined address mapping with memory scheduling to not only distribute the traffic but also reduce the interference caused by various threads on each other. Some groups [35] have also explored using address translations and MC scheduling to reduce DRAM power. All these works improve power and performance of a system by manipulation of memory request in various manners without changing the inherently-inefficient internal structures of the DRAM.

Some researchers have explored changing the internal structure of the DRAM to improve bandwidth or power efficiency. These include approaches like early fully-buffered DIMM [25] and decoupled DIMM [126], which separates the dependence of DRAM bus with its internal storage sub-arrays to improve bandwidth; rank subsetting [1] and mini-rank [125], which reduces the DRAM row size to improve its power efficiency; and SSA [106] and sub-array-level parallelism [47] architectures that propose modifications to the peripherals of DRAM sub-arrays to improve parallelism and reduce energy for each DRAM operation. All these schemes try to improve DRAM efficiency, however, they cannot remove the fundamental challenge of DRAM, that is, the small number of connections between the CPU die and the DRAM chips. In the next section, we provide two promising solutions that address this problem.

## 2.2 2D vs. 2.5D vs. 3D Stacked Memory

A typical integrated circuit (IC) with a ball grid array (BGA) package consists of a single die placed on top of a package substrate as shown in Fig 1 a). The connections between the die and the substrate, called bumps or more recently micro-bumps, has a pitch around 30-50um while the connections between the package substrate and the printed circuit board (PCB), ball interconnect, is around 400-600um. Although the pitch of micro-bumps can be reduced further, PCB designers are facing numerous challenges lowering the ball pitch down resulting in a very slow increase in the pin count of modern chips. Furthermore, these ball interconnects are connected to long wires in the pcb with non-linear coupling and impedance mismatch effects that keep the speed of these wires low. The combined problem has hindered the rapid increase of pin bandwidth mainly affecting off-chip memory bandwidth and power delivery mechanisms in modern chip multi-processors (CMPs).

Figure 1: Various packaging options for CPUs and memories

A promising solution to this problem is to introduce another silicon layer, a silicon interposer, between the package substrate and the die and have multiple dies placed together on a single substrate as shown in Fig 1 b). The interconnections between the two dies will have a very small pitch and much lesser distance increasing both the number of connections and their speed. The speed and thus bandwidth is further increased by the fact that the connection between the two dies passes through a much faster silicon layer than through the slow metallic wires of a PCB. Lesser distance also means smaller wires with lower electrical loads and thus smaller drivers to drive these wires, all of which decreases the overall power dissipation. Another advantage of wires in the faster silicon layer is their higher signal integrity leading to removal of sophisticated signal preserving techniques like delay locked loops, on-die termination etc., again improving power efficiency. However, the area and thus cost of the silicon interposer and the package substrate is high.

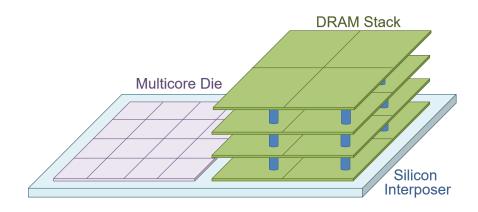

Another, even better solution to the problem is to stack multiple dies together and make a true 3D package as shown in Fig 1 c). Stacking is enabled by etching holes called throughsilicon vias (TSVs) in the bulk silicon portion of the die [7] [24]. TSVs have the advantage that two dies of completely different technologies can be stacked and later bonded using various bonding processes [62]. 3D configuration has several important advantages, such as, reduced distance between the dies, low electrical load on the TSVs, an increase in the number of interfaces between the dies, and a reduction in overall chip area and thus cost. A hybrid of the three technologies can also be used as shown in Figure 1 d). The hybrid configuration has only similar structures like multiple DRAM dies stacked in a 3D configuration with a lower probability of defects due to technology mismatch thus achieving significantly higher yield.

Any organization of various components of a system can be stacked. The most straight forward choice is to stack multiple DRAM dies and place them next to a processor die as a 2.5D structure [118] or put it directly on top of the processor die as a 'true 3D structure' [54]. In this thesis, we will analyze the later case [50] of true 3D stacking, which will simply be referred to as a 3D system. An example of such a design is 3D-Maps [24], which has already been successfully taped out and fabricated. Other common 3D configurations include placing large DRAM- or SRAM-based caches on top of the processor die [105], splitting individual components like processors or caches into multiple layers[116], or even splitting small units like ALU to multiple layers [23]. All these approaches are orthogonal to processor-memory 3D integration and less likely to be adapted in the near future.

#### 2.2.1 Challenges and Trends

3D processor-memory systems have been gaining significant attention since a decade. Earlier approaches tend to exploit higher bandwidth of 3D, for example, Dong et al [115] have evaluated the use of larger cache lines (equivalent to an OS page) to improve performance. Others [85, 100] have looked towards either restructuring the DRAM array or modifying the interconnect between various DRAM sub-banks in a manner that reduces DRAM access time or energy. However, the adoption of these schemes have been slow mainly because of technology challenges in 1) TSV packaging, 2) thermal management, 3) combined multi-die yield, and 4) DRAM capacity. Recent advancements in packaging [119], microfluidics [110], and silicon-on-interposer [89] technologies indicate rapid progress towards solving these issues leading to the proposal of a few new memory standards [97, 95]. Increasing the capacity of DRAM, however, is still a problem specially with a small number of dies being allowed to stack due to thermal constraints. Increasing the chip size is also not desirable because of lower yield with bigger chips. Consequently, stacked DRAM is mainly been explored as a 2.5D structure [67] with an optional logic die below the DRAM stack. This prompted the architects to come up with interesting new designs, such as, NDC [71] and PIM [121], in which it is used as either a large last-level cache (LLC) [73] or part of a multi-level main memory [88]. Consequently, the focus has been on the management of the DRAM caches or the OS- or hardware-based page swapping between the fast and the slow memory. However, with 4GB of stacked DRAM coming soon [108], the assumption that stacked DRAM will be used only as a cache or page swapping mechanisms are the main performance determinants is less likely to be true. Another problem that arises from large capacity memories is the higher number of refresh operations to be performed, which affects memory bandwidth availability, its power, and the wait time during refresh operations [52]. In this thesis, we revisit the 3D stacked processor-memory system and analyzed it in more detail, identifying its bottlenecks and proposing optimizations to remove them. We focus on the impact of such a system on on-chip network latency, 3D parallelism management and thermal regulation.

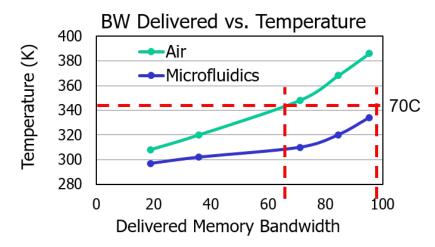

### 2.3 Thermal Concerns in 3D Memory

A major problem with 3D stacks, specially in the case of 'true 3D systems', is their lower heat removal capability, and higher DRAM density and heat flux which increases their operating temperature. Higher temperature limits the operating frequency and requires more frequent DRAM refresh operations (or shorter duty cycles until all DRAM rows are refreshed), both having a negative impact on overall system performance. Furthermore, complex, high power cores are not deemed feasible with 3D stacks as are applications with high compute intensity. Thus, the usage of 3D stacks has been limited to memory-intensive applications running at low frequencies which inherently have low performance. Further improvement in performance scaling by increasing core complexity or frequency cannot be achieved as it is limited by thermal constraints of the stack. We broadly looked at two different solutions to address the thermal challenges of 3D memories, i) how new cooling technologies, such as microfluidics cooling, can help alleviate temperature and reliability concerns and pushes its envelope to both compute- and memory-intensive applications operating at much higher frequencies. ii) how adaptations to the current memory architecture and algorithms can expand the operating range of 3D memories improving performance and power of the overall system. Specifically, we make a case for variable-rate per-bank refresh management for 3D stacked memories.

#### 2.3.1 Various Cooling solutions

Several solutions have been proposed to address 3D stack's heat removal problem. Conventional air cooled heat sinks, as shown in Figure 2a, are placed on top of the stack and has significantly larger form factor than the chip size. Besides the size, the cooling effectiveness or heat transfer coefficient of such systems is low in the range of  $25 - 200W/m^2K$  [110]. Other solutions that try to reduce air cooling limitations include thermal-aware floorplanning [18] and thermal TSVs [18] with no electrical characteristics to increase thermal conductivity between the dies and the heat sink. These solutions, although, distribute the heat within or across the dies but does not remove the fundamental problem of high heat flux within the stack. Furthermore, they are not scalable with the increasing number of dies per stack. Another orthogonal solution is to place the high power dissipating logic die closer to the heat sink away from the package substrate but this requires large number of power and ground connections passing through all the memory layers; a solution which is less likely to be practical.

Figure 2: Various cooling solutions for 3D-stacked memories

Liquid cooling using parallel-plate fins called micro-channels [37] has been identified as an alternative to air-cooled heat sinks. Micro-channels are embedded in the inter-layers of a 3D IC. Liquid coolant is pumped through these channels absorbing heat while flowing to the outlet. Micro-channels has been reported to have cooling capability as high as  $790W/cm^2$  [37]. A problem in using micro-channels with 3D stacks is that they compete with the TSV area of the dies in the stack. Besides, they require large coolant pumping power. A hybrid of micro-channel and thermal TSVs is proposed to reduce cooling power and still enjoy effective cooling capability [86].

#### 2.3.2 Pin-fin Enhanced Microgap Cooling (Microfluidics)

Although microchannels provide effective cooling solution, recent advancements in fabrication technology has allowed researchers to explore more complex geometries to improve the heat transfer capability of liquid-cooled heat sinks. One promising approach is to have staggered array of micro-sized pin fins distributed across the dies [110] providing localized cooling as shown in Figure 2b. Zhang et al. [128] recently fabricated inter-tier pin-fin enhanced microgap cooling solution, and demonstrated that a staggered pin-fin heat sink with two-die stack can cool at a rate of  $100W/cm^2$  with a maximum junction temperature of 47°C. The electrical TSVs are embedded in the pin fins allowing them to not compete with the thermal fins as was the case in micro-channel based heat sink. A compact thermal model to calculate the thermal grids for each of the die was also developed [109]. We have used an extended version of that model in our infrastructure to generate heat maps for different dies in the DRAM stack.

Liquid cooling can be classified as a single-phase or a two-phase solution based on whether the fluid boils and changes its phase while flowing inside the chip or not. We stick to single-phase microfluidics cooling in this dissertation. The flow rate of the coolant determines the cooling capability or thermal resistance of the system which is generally determined by the inlet pressure or pumping power of the system. Zheng et al. [127] shows how thermal resistance decreases with flow rate. The direction of the liquid flow also impacts the effectiveness of cooling. The heat transfer coefficient at the inlet is higher removing more heat than the outlet due to variation in the fluid temperature at the inlet and the outlet. Another important determinant of cooling capability is the pin-fin geometry and height. Ideally, we would like to scatter the pin-fins across the die in a manner that has a uniform heat transfer capability. However, since the TSVs are embedded in the pinfins, their placement is regulated by the electrical requirements of the TSVs. Zhiyuan et al. [117] explored co-placement of pin-fin arrays based on thermal as well as electrical requirements. Furthermore, higher pin-fin height and larger microgap increases the liquid flow and thus improves cooling. However, electrical TSVs performance are regulated by their aspect ratio, which means thicker pin fins and thus reduced cooling if the pin-fin height is increased further.

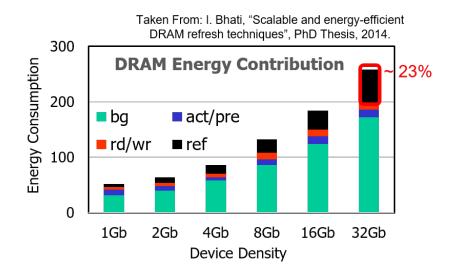

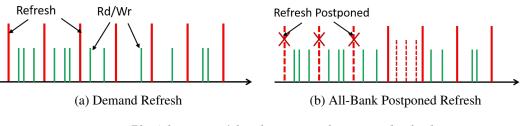

#### **2.3.3** Various Refresh Management Schemes

The dynamic nature of DRAM cells means that they lose their charge after a certain amount of time and require periodic restoration through a process known as refresh. A common way to perform refresh of all the cells in the DRAM is to stagger the refresh operations into 8K intervals, generally referred to as distributed refresh [8]. Thus, each refresh operation refreshes multiple number of rows (equivalent to the total number of rows divided by 8K) taking significant amount of time, which is on the rise with larger capacity DRAMs. In conventional DDRx, a refresh operation is performed on all the banks simultaneously making them unavailable during the refresh operations leading to DRAM bandwidth unavailability and reduced performance. Reducing performance penalty of refresh has been a target of numerous publications. Earlier works, such as RAIDR [51], exploits the variation in retention time characteristics of DRAM cells to propose different refresh rates for different rows of the DRAM. The authors in this work assert that only a few weak cells or rows require refresh at a faster rate with most rows allowing a slower rate, thus incurring less performance loss. RAPID [107] uses this idea to partition OS pages into two categories and allocate long-retention-time pages first before allocating the short-retentiontime pages, hence minimizing faster-rate refresh operations. Flikker [52] allocates critical data into long-retention-time pages and allows non-critical data to have a few errors.

A problem with all these schemes, however, is that they assume fixed retention time of various DRAM cells determinable statically at the beginning. However, a few cells also show variance in their own retention time, a phenomenon called variable retention time (VRT) [77]. Avatar [72] proposes variable-rate refresh in the presence of VRT cells by periodically redetermining the retention time of cells using memory scrubbing and prevents the intermediate errors using error correction codes. Elastic refresh [98] postpones refresh operations allowing more critical read and write operations to be performed first (more details of this in section 8.4). A similar idea is presented in refresh pausing [66], which pauses the refresh operations allowing critical reads to be serviced immediately before the actual refresh operation can be restored. All these schemes requires refresh mechanism to be controlled from the memory controller which is external to the DRAM. However, JEDEC does not allow fine row-level control of refresh mechanism. Flexible auto-refresh [9] modifies the DRAM control register access protocol to overcome this challenge, thus making other refresh schemes feasible.

More recently, JEDEC has allowed performing refresh at a finer granularity. For example, LPPDDR2 and LPDDR3 standards support per-bank refresh. Kevin et. al [13] shows the advantages of per-bank refresh which allows refreshes to be accessed in parallel with read/write accesses to other banks. Similarly, DDR4 introduces fine-granularity refresh [63]. The idea is to decrease the number of rows to be refreshed with each refresh operation reducing refresh latency but increase the frequency of refresh operations, for example, perform 16K or 32K refresh operations in a 64ms cycle; termed as 2x and 4x modes, respectively. More details of per-bank and fine-grained refresh are given in chapter 8. Partial-array self-refresh (PASR) [21] allows refreshes to be performed for a few banks only ignoring the rest in the self-refresh mode [8], thus saving refresh power.

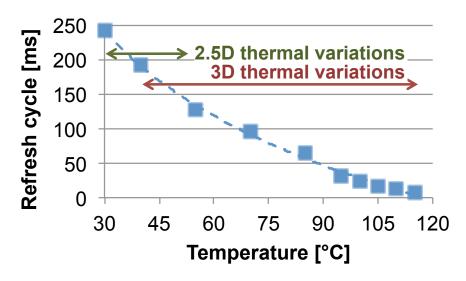

Another important characteristic of DRAM cells is that its retention time is severely impacted by the operating temperature. Typically, for temperatures below 85°C, DRAMs

are refreshed at a period of 64ms and at double the rate for every  $10^{\circ}C$  rise [60]. However, the rate of 64ms is a conservative value designed for the weak cells to operate at high temperatures. Some recent works have pointed towards decreasing the refresh rate for lower temperatures [82]. A feature called thermal-compensated self-refresh [103] (TCSR) is already provided in modern DDRs which reduces the refresh rate based on the device temperature in self-refresh mode. However, this mechanism is based on internal DRAM refresh counter in self-refresh mode and temperature cannot be regulated from the outside. Our variable-rate per-bank refresh management policy combines per-bank refresh with temperature-aware refresh [28] for 3D memories. It reduces DRAM power and performance penalty and tolerates thermal hotspots in memory, thus allowing the overall system to operate at much higher frequencies improving performance, as will be explained in chapter 8.

#### 2.4 **On-Chip Network**