## NEURO-GENERAL COMPUTING AN ACCELERATION-APPROXIMATION APPROACH

A Dissertation Presented to The Academic Faculty By

Amir Yazdanbakhsh

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology

August 2018

Copyright © 2018 by Amir Yazdanbakhsh

## NEURO-GENERAL COMPUTING AN ACCELERATION-APPROXIMATION APPROACH

Approved by:

Dr. Hadi Esmaeilzadeh, Advisor School of Computer Science *Georgia Institute of Technology*

Dr. Nam Sung Kim Department of Electrical and Computer Engineering University of Illinois at Urbana-Champaign

Dr. Milos Prvulovic School of Computer Science *Georgia Institute of Technology*  Dr. Hyesoon Kim School of Computer Science *Georgia Institute of Technology*

Dr. Sudhakar Yalamanchili School of Computer Science *Georgia Institute of Technology*

Date Approved: May 3, 2018

Be humble or else you tumble.

Anonymous

This dissertation is dedicated to all members of my family, especially to my: father, Mohammad Esmaeil Yazdanbakhsh; mother, Shahla Roosta; and sister, Niloofar Yazdanbakhsh—my first teacher of my life—who have always loved and supported me unconditionally and whose good examples have taught me to work hard for the things that I aspire to achieve.

### ACKNOWLEDGEMENTS

This long venture of my PhD journey is a combined effort of many characters, including the scholars whom I had the privilege to meet and work with, family members who constantly supported me and evinced me to finish my PhD, and friends who were always accessible and guided me through this journey. All of them played a crucial role in one or another step of this journey and helped me to achieve my goals. None of my achievements, if any, would have been possible without the unconditional support and help from them. This thesis would therefore be incomplete without expressing my gratitude to all of them.

First and foremost, I want to thank my marvelous advisors, Hadi Esmaeilzadeh and Nam Sung Kim, for always trusting me, giving me enough resources and opportunities to improve my work and excel in my path of learning, as well as my presentation and writing skills. An special thank to Hadi Esmaeilzadeh (my direct advisor) whom I was honored to work with for almost four years. He undoubtedly had played a pivotal role in my life. He was always available and supportive through my PhD journey. He provided me unparalleled opportunities, supported me in both my academic life and personal life, and inspired me to work hard and maintain my determination. His commitment to guide me for carrying out high-impact and high-quality research and instilling his unique creative vision in research have helped me to form a visionary research personality and be always ambitious about my goals, something that I will be indebted to him for the rest of my life. I am proud to say my experience of working with him was intellectually exciting and fun, and has energized me to continue research. I am also grateful to the members of my PhD committee: Hyesoon Kim, Sudhakar Yalamanchili, and Milos Prvulovic for their valuable feedback and for making the final steps towards my PhD very smooth.

I am also grateful to all the current and previous members of Alternative Computing Technologies (ACT) Lab who taught me new things every day. I will not forget the allnighters that we pulled together and the crazy nights that we spent in the lab crunching numbers. Thanks for the fun and support which made my PhD extremely enjoyable and memorable. Thanks for being patient with me during our heated research discussions and openly listening to all of my ideas and providing me the most invaluable feedback and comments. I greatly look forward to having all of you as colleagues in the years ahead.

During my education journey, I was fortunate to be surrounded by some of the most wonderful people I know. Hooman Tahayori and Farzin Sobhanmanesh, my advisors in Shiraz University, who motivated me to pursue my studies at graduate level. My late advisor in University of Tehran, Sied Mehdi Fakhraie, a scholar and a true human being, who was the one that introduced me to the research world. His death, undoubtedly, is a loss in my life. Azadeh Davoodi, my advisor in University of Wisconsin-Madison, who gave me the opportunity to continue my studies in the USA and supported me unconditionally to become a successful researcher. Pejman Lotfi-Kamran who passionately taught me the underpinnings of research in Computer Architecture and assisted me to grow in my chosen career path. I am extremely grateful to work under Gennady Pekhimenko's close mentorship. He helped me to better form my ideas and clearly and coherently present them to others. Gennady was always available for offering his unsolicited advice which helped me to transcend in my career and become a more mature researcher. He also helped me to be a better citizen of the Computer Architecture community.

I would like to thank Doug Burger, Luis Ceze, Onur Mutlu, and Todd C. Mowry with whom I had the opportunity to collaborate. Working with these renowned scholars helped me to better understand the research in our field and taught me to always set the bar high in my career and follow my dreams. I am grateful for having the opportunity to work under the supervision of Karu Sankaralingam for a short period of time. He supported me and took me under his wing when I needed it the most in my career path. His unwavering support put me back on the track to pursue my dream in the academic world. Although, working with Karu was short, his impact on me and my career was tremendous. During working in his lab, I had the opportunity to work with many great scholars, such as Raghuraman Balasubramanian and Anthony Nowatzki, from whom I learned much about research in Computer Architecture. I am grateful for having Mehdi Kamal as my mentor and now a reliable friend. He helped me to grow when I first joined University of Tehran for my Master degree and taught me the first steps to become a researcher. I also want to thank my first grade teacher, Mrs. Farzaneh, who I always remember for the rest of my life. She patiently taught me how to read and write despite me being a high-maintenance student. I wish I could see her one more time and thank her for all she has done for me.

During my PhD, I had the opportunity to work in many acclaimed companies as a research intern. I am grateful to my internship mentors for making my work in their companies mutually successful for both sides. At Information Sciences Institute, I had the chance to work with Michel Sika, Jonatan Ahlbin, and Bradley Kiddie. An special thank to Michel who has faithfully mentored me and taught me how to carry out high impact research. At Rambus, I had the fortunate to work with David Stork and Craig Hampel. At Microsoft Research, I had the privilege to closely work with leading researchers in the field, Madan Musuvathi, Todd Mytkowicz, Saeed Maleki. At NVIDIA Research, I had the privilege to closely work with Joel Emer, Michael Pellauer, Christopher Fletcher, Angshuman Parashar, Steve Keckler. I am also thankful to all the companies that financially supported my research and helped me to continue living my dream life. Specially, Microsoft for Microsoft Research PhD Fellowship and Qualcomm for the Qualcomm Innovation Fellowship.

During my PhD, I had the privilege to mentor and supervise many undergraduate and graduate students from multiple illustrious universities, including Michael Brzozowski, Fatemehsadat Mireshghallah, Hajar Falahati, Vahideh Akhlaghi, Manali Kumar, Oleg Filatov, Anandhavel Nagendrakumar, and Sindhuja Sethuraman. Thank you for letting me to be your mentor, helping me grow as a person and become a better leader, and contributing significantly to my research. Each day of working with you was a treasured lesson for me. I can not wait to see what you all do next.

I am also deeply grateful to my friends, colleagues, and mentors for their vital contri-

butions to my personal and academic life (in no particular order), Farshad Firouzi, Hamid Shojaee, Min Li, Mohammad Fattah, Iman Entezari, Amin Farmahini, Bashir Ebrahimi, Hamid Noori, Saeed Safari, Solmaz Asanfi, Mostafa E. Salehi, Ali Azarpeyvand, Kia Bazarga, Hamed Dorosti, Zeinalabedin Navabi, David Palframan, Mikko Lipasti, Ali Afzali-Kusha, Masoud Pedram, Renée St. Amant, Arjang Hassibi, Saba Amanollahi, Amir Rostami, Abbas Rahimi, Atieh Lotfi, Rajesh K. Gupta, Kambiz Samadi, Manu Rastogi, Behnam Khaleghi, Girish Varatkar, Sunjae Park, Ching-Kai Liang, Girish Mururu, Sarah Cannon, Mohmmadali Rahimian, Bita Darvish Rohani, Mehdi Ahmadi, Tushar Krishna, Santosh Pande, Sriseshan Srikanth, Amin Momeni, Amirhossein Davoodi, Abolghasem Beheshti, Mohammad Reza Karami Mehr, Vijay Thiruvengadem, Emmanuel Amaro, Jared Urban, Emily Faszold, Hadi Mirisaee, Ramtin Raji, Mehdi Askari.

I also thank the wonderful staff in the School of Computer Science as well as in other departments of Georgia Institute of Technology for always being so helpful and friendly. People here are genuinely nice and want to help you out and Im glad to have interacted with many.

Last but not the least, I especially thank my mom, dad, and sister. My hard-working parents have sacrificed their lives for my sister and myself and provided unconditional love and care. I love them so much, and I would not have made it this far without them. My sister has been my best friend all my life and I love her dearly and thank her for all her advice and support. I know I always have my family to count on when times are rough.

# TABLE OF CONTENTS

| Acknov    | vledgments                                     | v   |

|-----------|------------------------------------------------|-----|

| List of ' | Tables                                         | XV  |

| List of ] | Figures                                        | vii |

| Propos    | al Summary                                     | iii |

| Chapte    | r 1: Limited Precision Neuro-General Computing | 1   |

| 1.1       | Summary                                        | 1   |

| 1.2       | Introduction                                   | 2   |

| 1.3       | Overview and Background                        | 5   |

| 1.4       | Analog Circuits for Neural Computation         | 7   |

| 1.5       | Mixed-Signal Neural Accelerator (A-NPU)        | 11  |

|           | 1.5.1 ANU Circuit Design                       | 12  |

|           | 1.5.2 Reconfigurable Mixed-Signal A-NPU        | 15  |

|           | 1.5.3 Architectural interface for A-NPU        | 16  |

| 1.6       | Compilation for Analog Acceleration            | 16  |

| 1.7       | Evaluations                                    | 20  |

| 1.8       | Limitations and Considerations                 | 26  |

| 1.9    | Conclusions                                                 | 27 |

|--------|-------------------------------------------------------------|----|

| Chapte | er 2: Neuro-General Computing for GPU Throughput Processors | 29 |

| 2.1    | Summary                                                     | 29 |

| 2.2    | Introduction                                                | 30 |

| 2.3    | Neural Transformation for GPUs                              | 33 |

|        | 2.3.1 Safe Programming Interface                            | 34 |

|        | 2.3.2 Compilation Workflow                                  | 34 |

| 2.4    | Instruction Set Architecture Design                         | 37 |

| 2.5    | Accelerator Design and Integration                          | 38 |

|        | 2.5.1 Integrating the Neural Accelerator                    | 39 |

|        | 2.5.2 Executing Neurally Transformed Threads                | 41 |

|        | 2.5.3 Orchestrating Neurally Enhanced Lanes                 | 41 |

| 2.6    | Controlling Quality Tradeoffs                               | 43 |

| 2.7    | Evaluation                                                  | 44 |

|        | 2.7.1 Applications and Neural Transformation                | 44 |

|        | 2.7.2 Experimental Setup                                    | 47 |

|        | 2.7.3 Experimental Results                                  | 48 |

| 2.8    | Conclusion                                                  | 54 |

| Chapte | er 3: In-DRAM Near-Data Neuro-General Computing             | 56 |

| 3.1    | Summary                                                     | 56 |

| 3.2    | Introduction                                                | 57 |

| 3.3    | Overview                                                    | 59 |

|         | 3.3.1   | Challenges and Opportunities                                  | 59 |

|---------|---------|---------------------------------------------------------------|----|

|         | 3.3.2   | Approximation for Near-Data Processing                        | 61 |

| 3.4     | AxRA    | M Execution Flow and ISA                                      | 62 |

|         | 3.4.1   | Neural Acceleration of GPU Warps                              | 63 |

|         | 3.4.2   | Execution Flow with AxRAM                                     | 64 |

|         | 3.4.3   | ISA Extensions for AxRAM                                      | 65 |

| 3.5     | AxRA    | M Microarchitecture                                           | 67 |

|         | 3.5.1   | Background: GDDR5 Architecture                                | 67 |

|         | 3.5.2   | In-DRAM Accelerator Integration                               | 69 |

|         | 3.5.3   | Interfacing the GPU with AxRAM                                | 73 |

| 3.6     | Data O  | Prganization for AXRAM                                        | 74 |

| 3.7     | Arithm  | netic Units Simplification                                    | 77 |

| 3.8     | Memor   | ry Model                                                      | 78 |

| 3.9     | Evalua  | tion and Methodology                                          | 79 |

|         | 3.9.1   | Methodology                                                   | 79 |

|         | 3.9.2   | Experimental Results                                          | 82 |

| 3.10    | Conclu  | sion                                                          | 88 |

| Chapter | •4: Lar | nguage Support for Acceleration-Appriximation Hardware Design | 89 |

| -       |         |                                                               |    |

| 4.1     | Summa   | ary                                                           | 89 |

| 4.2     | Introdu | action                                                        | 90 |

| 4.3     | Approx  | ximate Hardware Design with Axilog                            | 91 |

|         | 4.3.1   | Design Annotations                                            | 93 |

|        | 4.3.2 Reuse Annotations                                     |

|--------|-------------------------------------------------------------|

| 4.4    | Relaxability Inference Analysis                             |

| 4.5    | Approximate Synthesis                                       |

| 4.6    | Evaluation                                                  |

| 4.7    | Conclusion                                                  |

| Chapte | r 5: Acceleration-Approximation in Deep Neural Networks 108 |

| 5.1    | Summary                                                     |

| 5.2    | Introduction                                                |

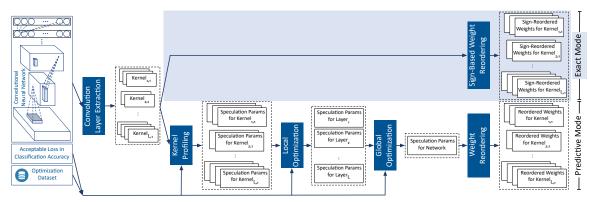

| 5.3    | SnaPEA Hardware-Software Solution                           |

|        | 5.3.1 SnaPEA Software Workflow                              |

| 5.4    | Computation Reduction in SnaPEA                             |

|        | 5.4.1 Problem Formulation                                   |

|        | 5.4.2 Finding the Speculation Parameters                    |

| 5.5    | Architecture Design for SnaPEA                              |

| 5.6    | Evaluation                                                  |

|        | 5.6.1 Methodology                                           |

|        | 5.6.2 Experimental Results                                  |

| 5.7    | Conclusion                                                  |

| Chapte | r 6: Unsupervised Learning Acceleration                     |

| 6.1    | Summary                                                     |

| 6.2    | Introduction                                                |

| 6.3    | Flow of Data in Generative Models                           |

| 6.4    | Architecture Design for GANAX                                                                           | 5          |

|--------|---------------------------------------------------------------------------------------------------------|------------|

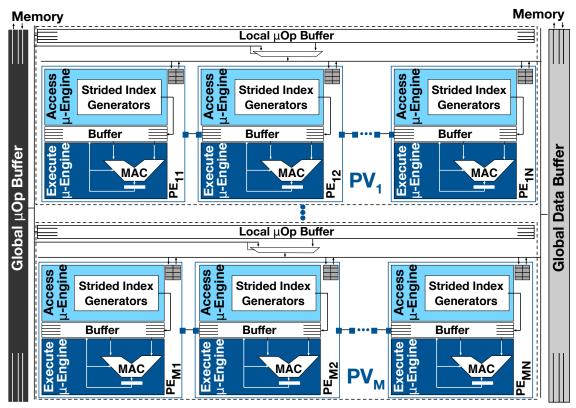

|        | 5.4.1 Unified MIMD-SIMD Architecture                                                                    | 7          |

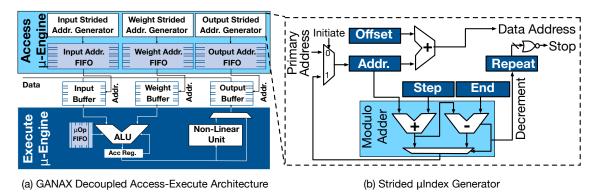

|        | 5.4.2 Decoupled Access-Execute $\mu$ Engines                                                            | 51         |

| 6.5    | Instruction Set Architecture Design ( $\mu$ Ops)                                                        | <i>i</i> 4 |

|        | 6.5.1 Algorithmic Observations                                                                          | ;5         |

|        | $6.5.2  \text{Access } \mu \text{Ops}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 6          |

|        | 6.5.3 Execute $\mu$ Ops                                                                                 | 7          |

| 6.6    | Methodology                                                                                             | 8          |

| 6.7    | Evaluation                                                                                              | 60         |

| 6.8    | Conclusion                                                                                              | 53         |

| Chapte | <b>7: Related Work</b>                                                                                  | 54         |

| 7.1    | Limited Precision Neuro-General Computing                                                               | 54         |

| 7.2    | Neuro-General Computing for GPU Throughput Processors                                                   | 6          |

| 7.3    | Acceleration-Approximation in Deep Neural Networks                                                      | 57         |

| 7.4    | Unsupervised Learning Acceleration                                                                      | <u>i</u> 9 |

| 7.5    | In-DRAM Near-Data Neuro-General Computing                                                               | '1         |

| Chapte | 8: Future Work                                                                                          | '3         |

| Chapte | 9: Other Work From This Author                                                                          | '5         |

| 9.1    | Approximate Computing                                                                                   | '5         |

| 9.2    | FPGA Acceleration                                                                                       | '9         |

| 9.3    | Heterogeneous Computing                                                                                 | 30         |

| References | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | . 2 | 203 | 3 |

|------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|-----|---|

|            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |     |   |

| Vita       | • | • | • |   |   | • |   | • |   |   | • |   |   |   |   |   |   |   |   |   |   | • |   |   | • |   |   |   | • |   |   |   |   |   |   |   | • | • | . 2 | 204 | 1 |

# LIST OF TABLES

| 1.1 | The evaluated benchmarks, characterization of each offloaded function, training data, and the trained neural network                                                                                   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | Area estimates for the analog neuron (ANU)                                                                                                                                                             |

| 1.3 | Error with a floating point D-NPU, A-NPU with ideal sigmoid, and A-NPU with non-ideal sigmoid                                                                                                          |

| 2.1 | Applications, accelerated regions, training and evaluation datasets, quality metrics, and approximating neural networks.                                                                               |

| 2.2 | GPU microarchitectural parameters                                                                                                                                                                      |

| 3.1 | Applications (from AXBENCH [126]), quality metrics, train and evaluation datasets, and neural network configurations                                                                                   |

| 3.2 | Major GPU, GDDR5, and in-DRAM neural accelerator microarchitectural parameters                                                                                                                         |

| 3.3 | Area overhead of the added major hardware components                                                                                                                                                   |

| 4.1 | Summary of Axilog's language syntax                                                                                                                                                                    |

| 4.2 | Benchmarks, input datasets, and error metrics                                                                                                                                                          |

| 4.3 | The energy reduction when the quality degradation limit is set to 10% for two different PVT corners. Here, we consider temperature variations 106                                                      |

| 5.1 | Workloads, their released year, model size, number of convolution (Conv.) and fully-connected (FC) layers, and baseline classification accuracy. The model size shows the size of weights in Megabytes |

| 5.2 | SNAPEA and EYERISS [111] design parameters and area breakdown 125                                                                                                                                                                                    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3 | Absolute and relative energy comparison for different components of SNA-<br>PEA architecture along with off-chip memory access energy cost. PE<br>energy includes the cost of Predictive Activation Unit (PAU)                                       |

| 5.4 | The percentage of convolution layers that operates in the predictive mode, when classification accuracy drop is set to $\leq 3\%$ . The second and third column illustrates the average speedup and energy reduction across these convolution layers |

| 5.5 | True negative and false negative rate in predictive mode when classification accuracy drop is set to $\leq 3\%$                                                                                                                                      |

| 6.1 | The evaluated GAN models, their released year, and the number of convolution (Conv) and transposed convolution (TCONV) layers per generative and discriminative models                                                                               |

| 6.2 | Energy comparison between GANAX microarchitectural units and mem-<br>ory. PE energy includes the energy consumption of an arithmetic operation<br>and the strided $\mu$ index generators                                                             |

| 6.3 | Area measurement of the major hardware units with TSMC 45nm                                                                                                                                                                                          |

# LIST OF FIGURES

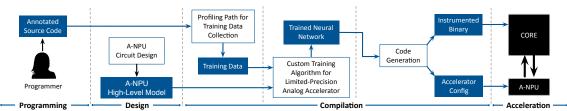

| 1.1 | Framework for using limited-precision analog computation to accelerate code written in conventional languages.                                               | 4  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

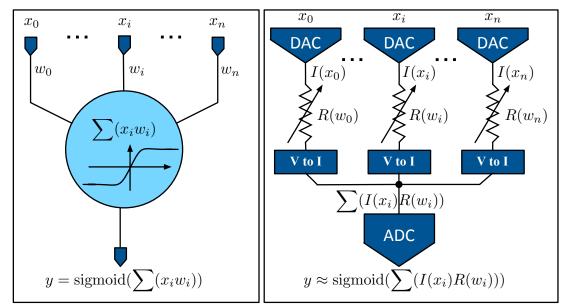

| 1.2 | One neuron and its conceptual analog circuit.                                                                                                                | 8  |

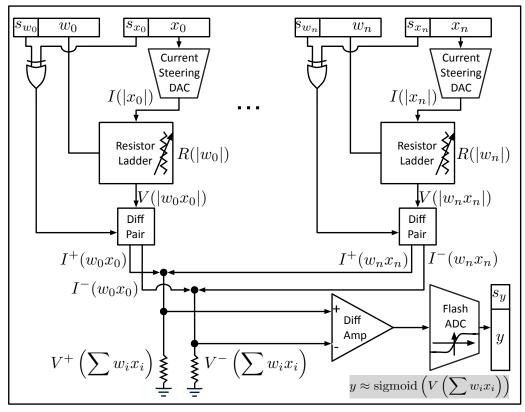

| 1.3 | A single analog neuron (ANU)                                                                                                                                 | 12 |

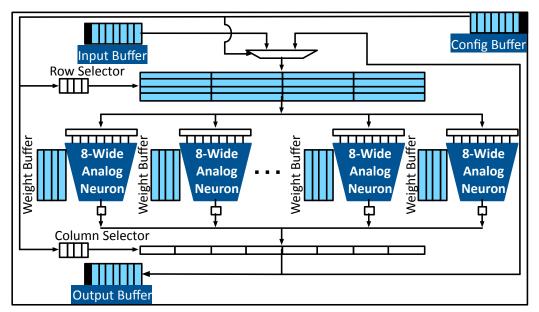

| 1.4 | Mixed-signal neural accelerator, A-NPU. Only four of the ANUs are shown. Each ANU processes eight 8-bit inputs.                                              | 14 |

| 1.5 | A-NPU with 8 ANUs vs. D-NPU with 8 PEs                                                                                                                       | 22 |

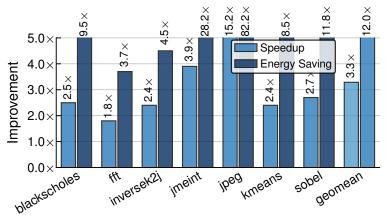

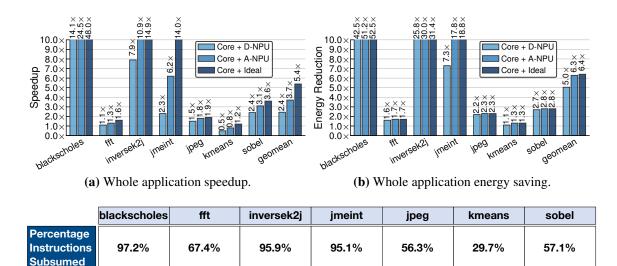

| 1.6 | Whole application speedup and energy saving with D-NPU, A-NPU, and<br>an Ideal NPU that consumes zero energy and takes zero cycles for neural<br>computation | 23 |

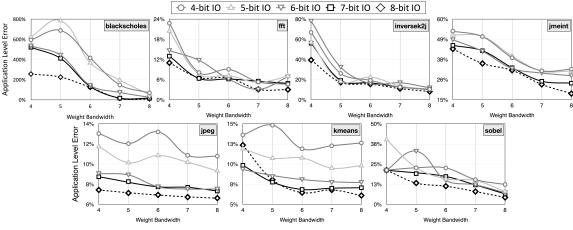

| 1.7 | Application error with limited bit-width analog neural computation                                                                                           | 24 |

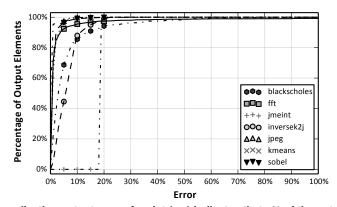

| 1.8 | CDF plot of application output error. A point $(x,y)$ indicates that y% of the output elements see error $\leq x\%$ .                                        | 25 |

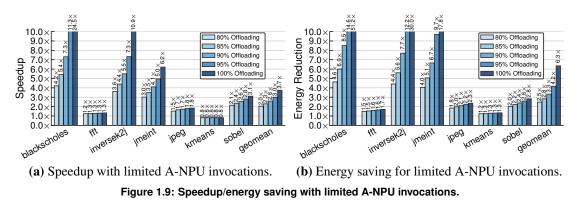

| 1.9 | Speedup/energy saving with limited A-NPU invocations                                                                                                         | 26 |

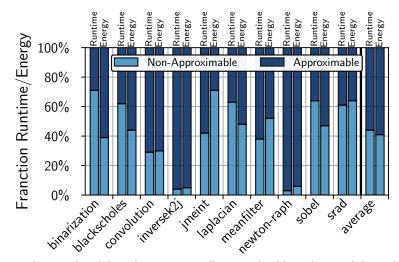

| 2.1 | Runtime and energy breakdown between neurally approximable regions and the regions that cannot be approximated.                                              | 31 |

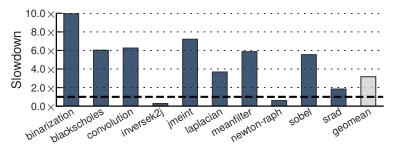

| 2.2 | Slowdown with software-only neural transformation due to the lack of hardware support for neural acceleration.                                               | 32 |

| 2.3 | Overview of the compilation workflow for neural acceleration in GPU throughput processors.                                                                   | 35 |

| 2.4 | SM pipeline after integrating the neural accelerator within SIMD lanes. The added hardware is highlighted in gray.                                           | 40 |

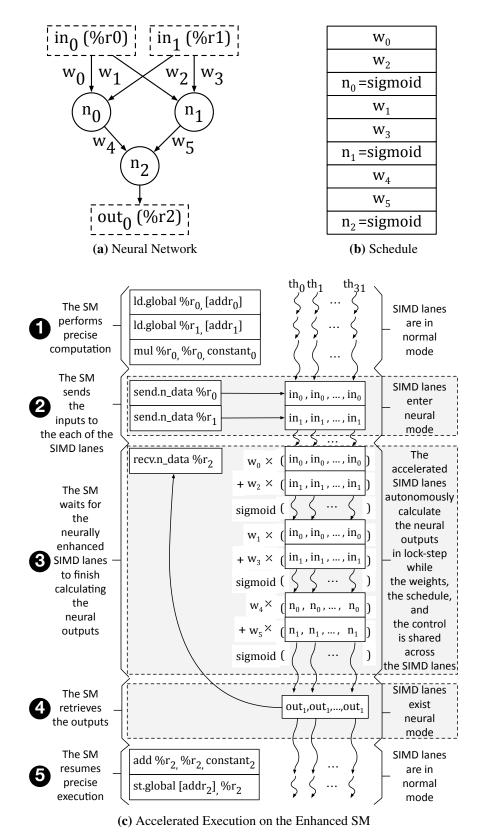

| 2.5  | (a) Neural network replacing a segment of a GPU code. (b) Schedule for the accelerated execution of the neural network. (c) Accelerated execution of the GPU code on the enhanced SM                                                                                                                                                                                                                                                                                           | 42 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

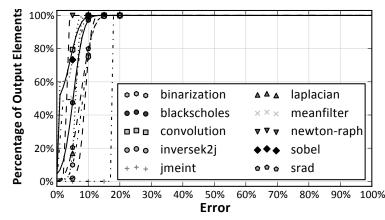

| 2.6  | Cumulative distribution function (CDF) plot of the applications output quality loss. A point $(x, y)$ indicates that y fraction of the output elements see quality loss less than or equal to x.                                                                                                                                                                                                                                                                               | 47 |

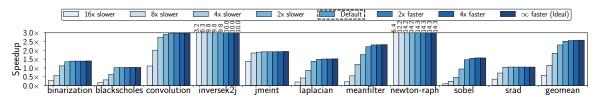

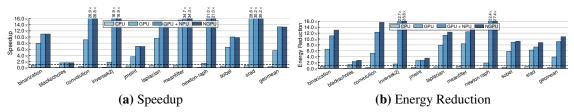

| 2.7  | NGPU whole application speedup and energy reduction                                                                                                                                                                                                                                                                                                                                                                                                                            | 48 |

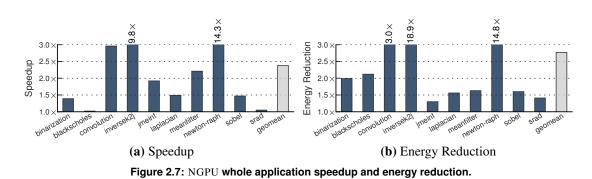

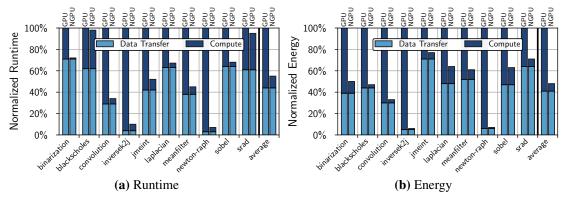

| 2.8  | Breakdown of (a) runtime and (b) energy consumption between non-<br>approximable and approximable regions normalized to the runtime and<br>energy consumption of the GPU, respectively. For each application, the first<br>(second) bar shows the normalized value when the application is executed<br>on the GPU (NGPU).                                                                                                                                                      | 50 |

| 2.9  | Sensitivity of the total application's speedup to the neural accelerator delay. Each bar indicates the total application's speedup when the neural accelerator delay is altered by different factors. The default delay for neural accelerator varies from one application to the other and depends on the neural network topology trained for that application. The ideal case ( $\infty$ faster) shows the total application speedup when neural accelerator has zero delay. | 50 |

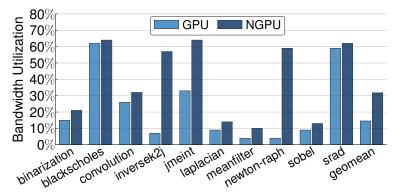

| 2.10 | Memory bandwidth consumption when the applications are executed on GPU (first bar) and NGPU (second bar)                                                                                                                                                                                                                                                                                                                                                                       | 51 |

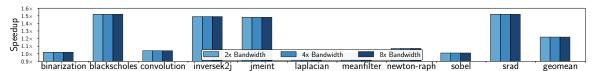

| 2.11 | The total application speedup with NGPU for different off-chip memory communication bandwidth normalized to the execution with NGPU with default bandwidth. The default bandwidth is 177.4 GB/s                                                                                                                                                                                                                                                                                | 52 |

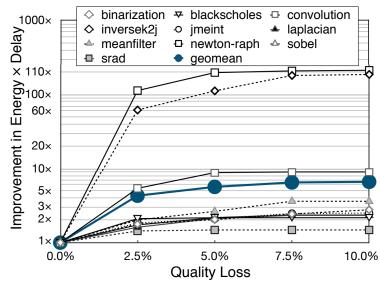

| 2.12 | Energy $\times$ delay benefits vs output quality (log scale)                                                                                                                                                                                                                                                                                                                                                                                                                   | 53 |

| 2.13 | Speedup and energy reduction with CPU, GPU, GPU+NPU, and NGPU.(The baseline is CPU+NPU, which is a CPU augmented with a NPU accelerator [12]).                                                                                                                                                                                                                                                                                                                                 | 55 |

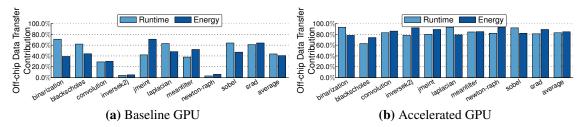

| 3.1  | The fraction of total application runtime and energy spent in off-chip data transfer for (a) a baseline GPU and (b) an accelerated GPU [38]                                                                                                                                                                                                                                                                                                                                    | 60 |

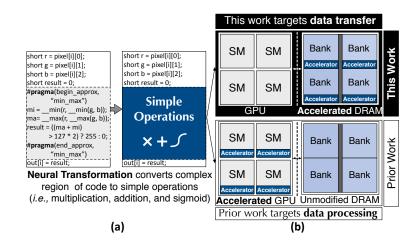

| 3.2  | (a) Neural transformation of a code segment from the binarization benchmark. (b) Comparison of prior work (bottom diagram) [38] and this work (top diagram).                                                                                                                                                                                                                                                                                                                   | 62 |

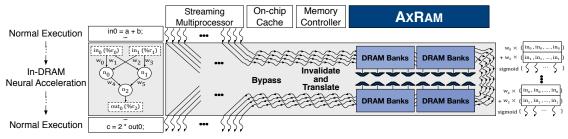

| 3.3  | Execution flow of the accelerated GPU code on the in-DRAM accelerator.                                                                                                                                                       | 63  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.4  | (a) High-Level GDDR5 DRAM organization. (b) Layout of two half bank-<br>groups (Left Half Bank-Group #0 and Left Half Bank-Group #1) and the<br>accelerators. The black-shaded boxes show the placement of the accelerators. | 68  |

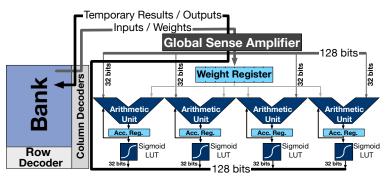

| 3.5  | Integration of weight register, arithmetic units, accumulation registers, and sigmoid LUTs.                                                                                                                                  | 70  |

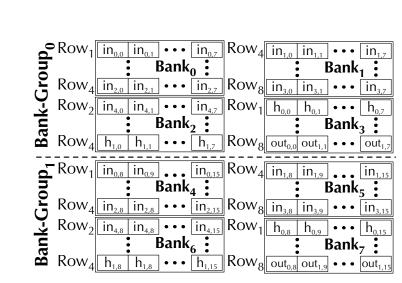

| 3.6  | The data layout for a neural network with $5\rightarrow 2\rightarrow 1$ configuration in bank-<br>group <sub>0</sub> and bank-group <sub>1</sub> after data shuffling. For simplicity, we assume a<br>row buffer (256 bits). | 75  |

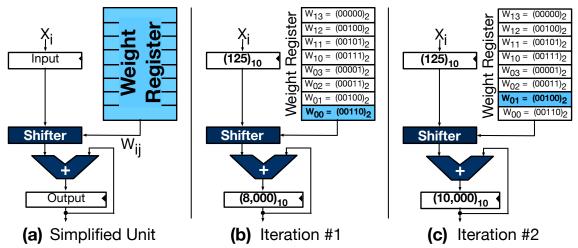

| 3.7  | <ul><li>(a) Example of the simplified shift-add unit with pre-loaded shift amounts.</li><li>(b-c) Two iterations of the shift-add unit.</li></ul>                                                                            | 76  |

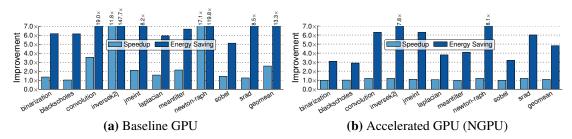

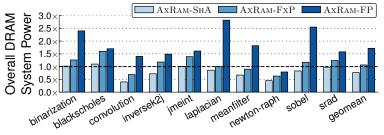

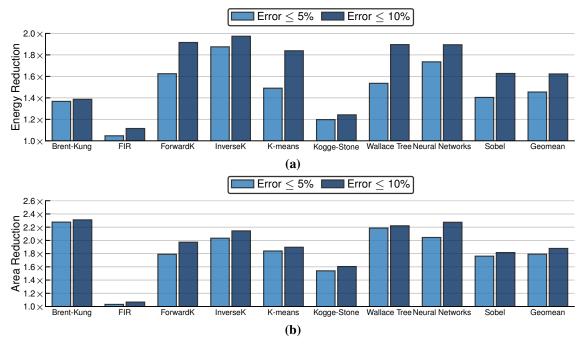

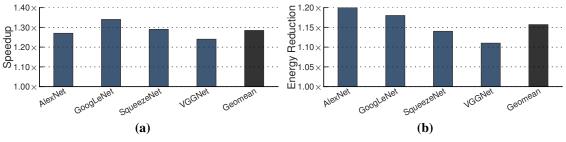

| 3.8  | AXRAM-SHA whole application speedup and energy reduction compared to (a) baseline GPU and (b) an accelerated GPU (NGPU) [38].                                                                                                | 83  |

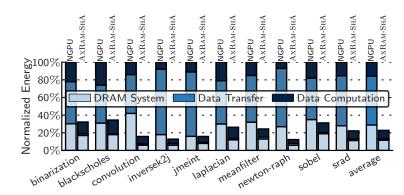

| 3.9  | Breakdown of AXRAM-SHA's energy consumption between DRAM system, data transfer, and data computation normalized to NGPU [38]                                                                                                 | 84  |

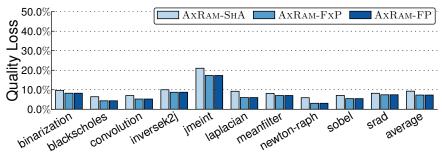

| 3.10 | Application quality loss with AXRAM-SHA, AXRAM-FXP, and AXRAM-FP compared to a baseline GPU                                                                                                                                  | 84  |

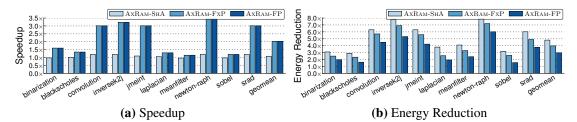

| 3.11 | AXRAM whole application (a) speedup and (b) energy reduction with the dif-<br>ferent microarchitectural options compared to a neurally accelerated GPU<br>(NGPU [38])                                                        | 86  |

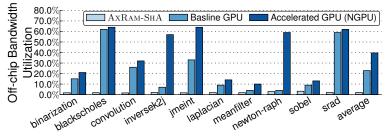

| 3.12 | Off-chip memory bandwidth consumption for AXRAM-SHA, a baseline GPU, and an accelerated GPU (NGPU) [38]                                                                                                                      | 86  |

| 3.13 | AXRAM average DRAM system power with the different microarchitectural options normalized to a baseline GPU.                                                                                                                  | 86  |

| 3.14 | The AXRAM-SHA application energy reduction <i>vs</i> . different target output quality loss (2.5%, 5%, 7.5%, and 10%), normalized to a baseline GPU with no acceleration.                                                    | 87  |

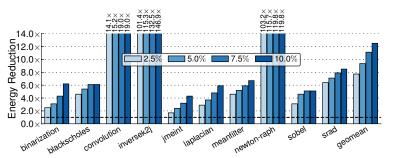

| 4.1  | Synthesis flow for (a) baseline and (b) approximate circuits                                                                                                                                                                 | 103 |

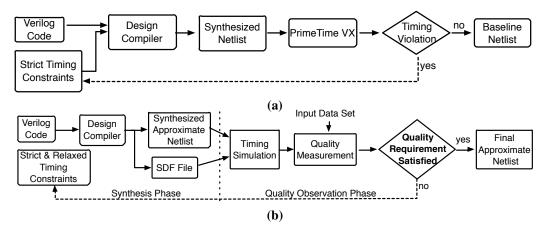

| 4.2  | Reductions in (a) energy and (b) area when the quality degradation limit is set to 5% and 10% in the synthesis flow.                                                                                                         | 105 |

| 4.3  | Visual depiction of the output quality degradation with approximate syn-<br>thesis for the Sobel application                                                                                                                                                               | 107 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

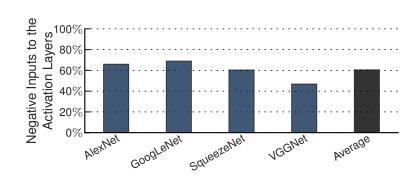

| 5.1  | Fraction of activation input values that are negative                                                                                                                                                                                                                      | 109 |

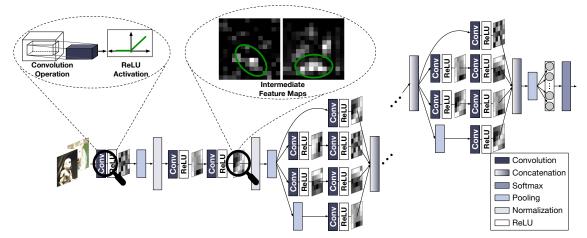

| 5.2  | GoogLeNet [154], in which the intermediate feature maps for two input im-<br>ages are magnified. The ellipses on the intermediate feature maps highlight<br>the varying spatial distribution of non-zero values for distinct input images.                                 | 110 |

| 5.3  | Software workflow for SnaPEA.                                                                                                                                                                                                                                              | 112 |

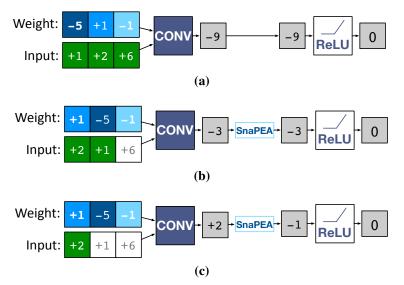

| 5.4  | Example of a $1 \times 3$ convolution in (a) unaltered (b) exact, and (c) predictive modes. In the latter two, the weights and their corresponding inputs are reordered. The white boxes highlight the operations that are cut. $\dots$                                    | 115 |

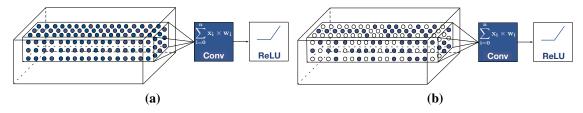

| 5.5  | (a) The unaltered 3D convolution where all the MAC operations (bubbles) are carried out. (b) The same convolution with SNAPEA, where a significant number of operations are eliminated, delineated by the white bubbles.                                                   | 115 |

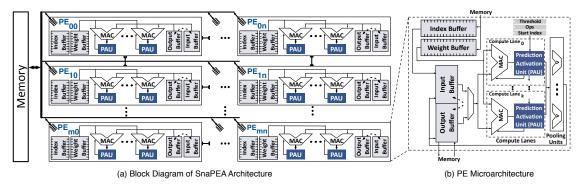

| 5.6  | (a) The overall structure of the SNAPEA architecture and its multilevel memory hierarchy, containing an off-chip memory and a distributed on-<br>chip buffer for input and outputs. (b) The microarchitecture of each PE. The weights are shared across the compute lanes. | 118 |

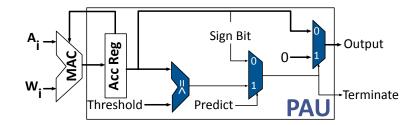

| 5.7  | Prediction Activation Unit (PAU). The <b>Predict</b> signal determines the PAU operation mode (exact or predictive). The Terminate signal, once asserted, terminates the computation early.                                                                                | 123 |

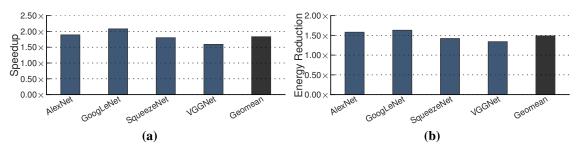

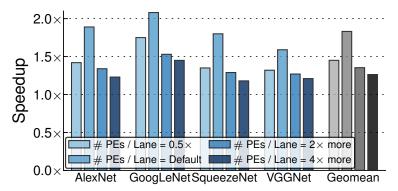

| 5.8  | Overall (a) speedup and (b) energy reduction with exact mode                                                                                                                                                                                                               | 127 |

| 5.9  | Overall (a) speedup and (b) energy reduction with SNAPEA over EYERISS [111] in the predictive mode. The acceptable classification accuracy drop is maintained within $\leq$ 3% range of its baseline value                                                                 | 129 |

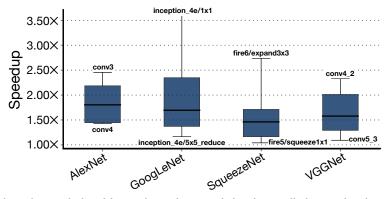

| 5.10 | Speedup of convolutional layers in each network for the predictive mode when the degradation in classification accuracy is set to $\leq 3\%$ .                                                                                                                             | 129 |

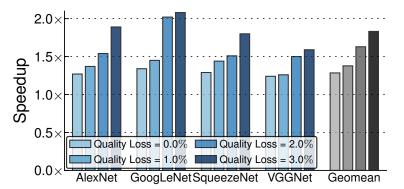

| 5.11 | Speedup vs. loss in the CNN classification accuracy. Each bar indicates the speedup when the acceptable degradation in the classification accuracy is 0% (pure exact mode), 1% (predictive mode), 2.0% (predictive mode), and 3.0% (predictive mode), respectively.        | 131 |

| 5.12 | Sensitivity of speedup with SNAPEA over EYERISS to the number of compute lanes per each PEs. Each bar indicates the speedup when the number of compute lanes per each PEs is altered by different factors. The acceptable classification accuracy drop is maintained within $\leq 3\%$ range of its baseline value.                                                       | 132 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

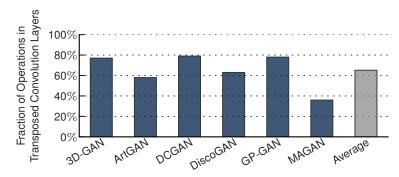

| 6.1  | The fraction of multiply-add operations in transposed convolution layers that are inconsequential due to the inserted zeros in the inputs.                                                                                                                                                                                                                                | 138 |

| 6.2  | High-level visualization of a Generative Adversarial Network (GAN)                                                                                                                                                                                                                                                                                                        | 140 |

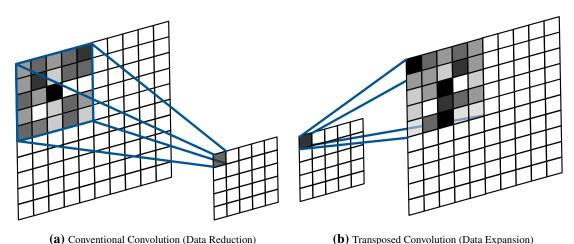

| 6.3  | (a) Convolution operations decreases the size of data (data reduction). (b) Transposed convolution increases the size of data (data expansion)                                                                                                                                                                                                                            | 140 |

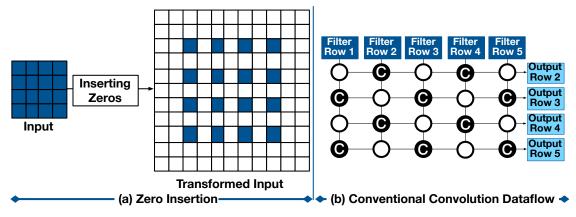

| 6.4  | (a) Zero-insertion step in a transposed convolution operation for a $4 \times 4$ input and the transformed input. The light-colored squares display zero values in the transformed input. (b) Using conventional dataflow for performing a transposed convolution operation.                                                                                              | 142 |

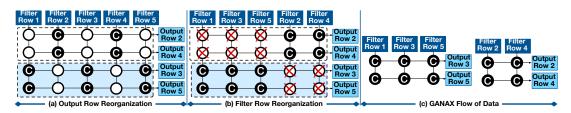

| 6.5  | The GANAX flow of data after applying (a) output row reorganization<br>and (b) filter row reorganization. (c) The GANAX flow of data after ap-<br>plying both output and filter row reorganization and eliminating the idle<br>compute nodes. The combination of these flow optimizations reduces the<br>idle (white) compute nodes and improves the resource utilization | 142 |

| 6.6  | Top-level block diagram of GANAX architecture                                                                                                                                                                                                                                                                                                                             | 146 |

| 6.7  | Organization of decoupled Access-Execute architecture                                                                                                                                                                                                                                                                                                                     | 148 |

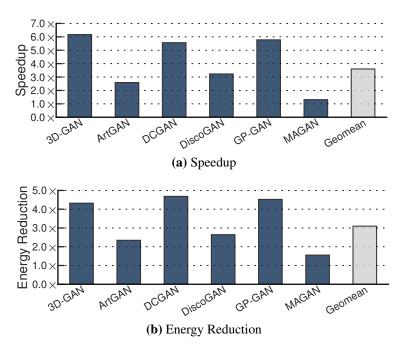

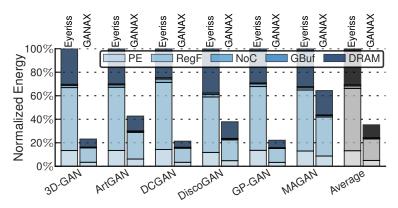

| 6.8  | Speedup and energy reduction of generative models compared to EYERISS [111].                                                                                                                                                                                                                                                                                              | 161 |

| 6.9  | Breakdown of energy consumption of the generative models between dif-<br>ferent microarchitectural units. The first bar shows the normalized energy<br>breakdown for EYERISS. The second bar show the energy breakdown for<br>GANAX normalized to EYERISS.                                                                                                                | 162 |

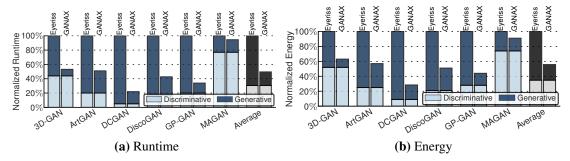

| 6.10 | Breakdown of (a) runtime and (b) energy consumption between discrim-<br>inative and generative models normalized to the runtime and energy con-<br>sumption of EYERISS. For each network, the first (second) bar show the<br>normalized value when the application is executed on EYERISS (GANAX).                                                                        | 162 |

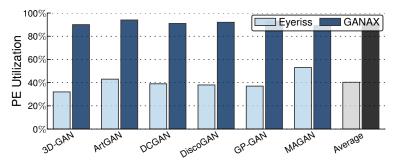

| 6.11 | Average PE utilization for the generative models in EYERISS and GANAX.                                                                                                                                                                                                                                                                                                    | 163 |

**Keywords:** Approximate Computing; Machine Learning; Generative Adversarial Networks; Convolutional Neural Networks; CNN; Transposed Convolution; Access-Execute Architecture; GAN; DNN; MIMD; SIMD; Accelerator

#### SUMMARY

## Neuro-General Computing An Acceleration-Approximation Approach

A growing number of commercial and enterprise systems rely on compute and power intensive tasks. While the demand of these tasks is growing, the performance benefits from general-purpose platforms are diminishing. As the result of the Dark Silicon studies shows [1, 2, 3, 4, 5] the improvements in per-transistor speed and energy efficiency diminishing. Moreover, the current paradigm of microprocessor design falls significantly short of the historical cadence of performance improvements [1, 4, 5]. Performance has hit the power wall. These challenges have coincided with the big data era where the data is being generated in such an overwhelming rate that is beyond the capabilities of current computing systems to match. While data generation is quadrupling each year, modern processors have seen a performance improvement 15% every two years. Without continuous performance improvements, grand-challenge applications, such as enhanced cognition and immersive virtual reality, computer vision, machine learning, sensory data processing, stochastic optimization and big data analytics may stay out of reach due to their need for significantly higher compute capacity. To address these convoluted challenges, there is a need to move beyond traditional techniques and explore unconventional paradigms in computing. This thesis is set to introduce a new paradigm in computing, called neurogeneral computing that leverages the approximibility in many emerging applications (e.g., machine learning, physical simulation, data visualization, big data analytics, sensory data processing, augmented reality, stochastic optimization, and computer vision) for delivering significant gains in performance and energy efficiency. Furthermore, in this thesis, I study the symbiosis between accelerator design and approximation in deep neural networks. Finally, I explore the challenges of accelerating generative adversarial networks, the frontier of deep networks, and introduce and develop an architecture which accelerate this new

class of deep networks. As such, this thesis consists of three main parts:

- 1. Neuro-general computing. We explore three different design points for this new paradigm of computing. First, we leverage the simplicity of the operations in neuro-general paradigm, add and multiplication, to design a mixed-signal accelerator. We introduce a novel architecture that carefully implement the microarchitectural components in analog or digital domain. Furthermore, we introduce a compiler-circuit co-design to mitigate the inherent imprecision in analog circuits. Then, we study the potential benefits of neuro-general computing in GPU throughput processors. Integrating neural accelerator units within GPUs is fundamentally different from doing so in a CPU, because of the hardware constraints and the many-thread SIMT execution model in GPUs. Finally, we observe that neurally accelerating GPU cores increase the pressure on the already-limited GPU memory bandwidth. As such, we study the integration of neural accelerators within DRAM. We introduce a novel DRAM architecture that integrates several low-overhead neural accelerators within DRAM while preserving the SIMT execution model of GPUs.

- 2. Accelerator-approximation in deep neural networks. Deep Convolutional Neural Networks (CNNs) are among the most widely used family of machine learning methods that have had a transformative effect on a wide range of applications. CNNs require ample amounts of computation even for a single input query. For instance, assigning a label to a relatively small RGB image requires billions of multiply-and-accumulate operations. In this part of thesis, we aim to reduce these copious amount of computation by exploiting both their runtime information and algorithmic structure. In convolutional layers of many modern CNNs, each convolution operation is commonly followed by an activation function called a Rectifying Linear Unit (ReLU) that returns zero for negative inputs and yields the input itself for the positive ones. Leveraging this insight, we introduce a holistic software-hardware solution, that cuts a large fraction of the computations short by identifying the zero intermediate values earlier during the runtime.

3. Unsupervised learning acceleration. Generative Adversarial Networks (GANs) are one of the most recent deep learning models that generate synthetic data from limited genuine datasets. GANs are on the frontier as further extension of deep learning into many domains (e.g., medicine, robotics, content synthesis) requires massive sets of labeled data that is generally either unavailable or prohibitively costly to collect. GANs leverage a new operator, called transposed convolution, that exposes unique challenges for hardware acceleration. This operator first inserts zeros within the multidimensional input, then convolves a kernel over this expanded array to augment information to the embedded zeros. Even though there is a convolution stage in this operator, the inserted zeros lead to underutilization of the compute resources when a conventional convolution accelerator is employed. We propose an architecture to alleviate the sources of inefficiencies associated with the acceleration of GANs using conventional convolution accelerators, making the first GAN accelerator design possible. We propose a reorganization of the output computations to allocate compute rows with similar patterns of zeros to adjacent processing engines, which also avoids inconsequential multiply-adds on the zeros. This compulsory adjacency reclaims data reuse across these neighboring processing engines, which had otherwise diminished due to the inserted zeros. The reordering breaks the full SIMD execution model, which is prominent in convolution accelerators. Therefore, we propose a unified MIMD-SIMD design that leverages repeated patterns in the computation to create distinct microprograms that execute concurrently in SIMD mode.

## **CHAPTER 1**

## LIMITED PRECISION NEURO-GENERAL COMPUTING

## 1.1 Summary

As improvements in per-transistor speed and energy efficiency diminish, radical departures from conventional approaches are becoming critical to improving the performance and energy efficiency of general-purpose processors. We propose a solution-from circuit to compiler—that enables general-purpose use of limited-precision, analog hardware to accelerate "approximable" code—code that can tolerate imprecise execution. We utilize an algorithmic transformation that automatically converts approximable regions of code from a von Neumann model to an "analog" neural model. We outline the challenges of taking an analog approach, including restricted-range value encoding, limited precision in computation, circuit inaccuracies, noise, and constraints on supported topologies. We address these limitations with a combination of circuit techniques, a hardware/software interface, neuralnetwork training techniques, and compiler support. The results of this work show that using limited-precision analog circuits for code acceleration, through a neural approach, is both feasible and beneficial over a range of approximation-tolerant, emerging applications including financial analysis, signal processing, robotics, 3D gaming, compression, and image processing. This chapter is based on work presented in ISCA 2014 [6] and IEEE Micro Top Picks [7]. This work is a result of collaboration with Renée St Amant<sup>1</sup>, Bradley Thwaites<sup>2</sup>, Arjang Hassibi<sup>1</sup>, Luis Ceze<sup>3</sup>, Doug Burger, and Hadi Esmaeilzadeh<sup>4</sup>.

<sup>&</sup>lt;sup>1</sup>University of Texas at Austin

<sup>&</sup>lt;sup>2</sup>Georgia Institute of Technoloy

<sup>&</sup>lt;sup>3</sup>University of Washington

<sup>&</sup>lt;sup>4</sup>University of California, San Diego

### **1.2 Introduction**

Energy efficiency now fundamentally limits microprocessor performance gains. CMOS scaling no longer provides gains in efficiency commensurate with transistor density increases [1, 8]. As a result, both the semiconductor industry and the research community are increasingly focused on specialized accelerators, which provide large gains in efficiency and performance by restricting the workloads that benefit. The community is facing an "iron triangle"; we can choose any two of performance, efficiency, and generality at the expense of the third. Before the effective end of Dennard scaling, we improved all three consistently for decades. Solutions that improve performance and efficiency, while retaining as much generality as possible, are highly desirable, hence the growing interest in GPGPUs and FPGAs. A growing body of recent work [9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19] has focused on *approximation* as a strategy for the iron triangle. Many classes of applications can tolerate small errors in their outputs with no discernible loss in *QoR* (Quality of Result). Many conventional techniques in energy-efficient computing navigate a design space defined by the two dimensions of performance and energy, and traditionally trade one for the other. General-purpose approximate computing explores a third dimension—that of error.

Many design alternatives become possible once precision is relaxed. An obvious candidate is the use of analog circuits for computation. However, computation in the analog domain has several major challenges, even when small errors are permissible. First, analog circuits tend to be special purpose, good for only specific operations. Second, the bit widths they can accommodate are smaller than current floating-point standards (i.e. 32/64 bits), since the ranges must be represented by physical voltage or current levels. Another consideration is determining where the boundaries between digital and analog computation lie. Using individual analog operations will not be effective due to the overhead of A/D and D/A conversions. Finally, effective storage of temporary analog results is challenging in current CMOS technologies. These limitations has made it ineffective to design analog von Neumann processors that can be programmed with conventional languages.

Despite these challenges, the potential performance and energy gains from analog execution are highly attractive. An important challenge is thus to architect designs where a significant portion of the computation can be run in the analog domain, while also addressing the issues of value range, domain conversions, and relative error. Recent work on Neural Processing Units (NPUs) may provide a possible approach [12]. NPU-enabled systems rely on an algorithmic transformation that converts regions of approximable general-purpose code into a neural representation (specifically, multi-layer perceptrons) at compile time. At run-time, the processor invokes the NPU instead of running the original code. NPUs have shown large performance and efficiency gains, since they subsume an entire code region (including all of the instruction fetch, decode, etc., overheads). They have an added advantage in that they convert many distinct code patterns into a common representation that can be run on a single physical accelerator, improving generality.

NPUs may be a good match for mixed-signal implementations for a number of reasons. First, prior research has shown that neural networks can be implemented in analog domain to solve classes of domain-specific problems, such as pattern recognition [20, 21, 22, 23]. Second, the process of invoking a neural network and returning a result defines a clean, coarse-grained interface for D/A and A/D conversion. Third, the compile-time training of the network permits any analog-specific restrictions to be hidden from the programmer. The programmer simply specifies which region of the code can be approximated, without adding any neural-network-specific information. Thus, no additional changes to the programming model are necessary.

In this work we evaluate an NPU design with mixed-signal components and develop a compilation workflow for utilizing the mixed-signal NPU for code acceleration. The goal of this study is to investigate challenges and define potential solutions to enable effective mixed-signal NPU execution. The objective is to both bound application error to

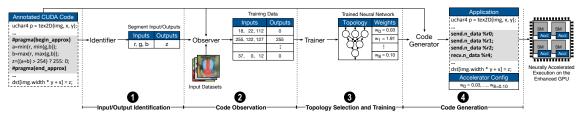

Figure 1.1: Framework for using limited-precision analog computation to accelerate code written in conventional languages. sufficiently low levels and achieve worthwhile performance or efficiency gains for general-purpose approximable code. This study makes the following four findings:

- 1. Due to range limitations, it is necessary to limit the scope of the analog execution to a single neuron; inter-neuron communication should be in the digital domain.

- 2. Again due to range issues, there is an interplay between the bit widths (inputs and weights) that neurons can use and the number of inputs that they can process. We found that the best design limited weights and inputs to eight bits, while also restricting the number of inputs to each neuron to eight. The input count limitation restricts the topological space of feasible neural networks.

- 3. We found that using a customized continuous-discrete learning method (CDLM) [24], which accounts for limited-precision computation at training time, is necessary to reduce error due to analog range limitations.

- 4. Given the analog-imposed topology restrictions, we found that using a Resilient Back Propagation (RPROP) [25] training algorithm can further reduce error over a conventional backpropagation algorithm.

We found that exposing the analog limitations to the compiler allowed for the compensation of these shortcomings and produced sufficiently accurate results. The latter three findings were all used at training time; we trained networks at compile time using 8-bit values, topologies restricted to eight inputs per neuron, plus RPROP and CDLM for training. Using these techniques together, we were able to bound error on all applications but one to a 10% limit, which is commensurate with entirely digital approximation techniques. The average time required to compute a neural result was  $3.3 \times$  better than a previous digital implementation with an additional energy savings of  $12.1 \times$ . The performance gains result in an average full-application-level improvement of  $3.7 \times$  and  $23.3 \times$  in performance and energy-delay product, respectively. This study shows that using limited-precision analog circuits for code acceleration, by converting regions of imperative code to neural networks and exposing the circuit limitations to the compiler, is both feasible and advantageous. While it may be possible to move more of the accelerator architecture design into the analog domain, the current mixed-signal design performs well enough that only 3% and 46% additional improvements in application-level energy consumption and performance are possible with improved accelerator designs. However, improving the performance of the analog NPU may lead to higher overall performance gains.

#### **1.3** Overview and Background

**Programming.** We use a similar programming model as described in [12] to enable programmers to mark error-tolerant regions of code as candidates for transformation using a simple keyword, approximable. Explicit annotation of code for approximation is a common practice in approximate programming languages [26, 27]. A candidate region is an errortolerant function of any size, containing function calls, loops, and complex control flow. Frequently executed functions provide a greater opportunity for gains. In addition to error tolerance, the candidate function must have well-defined inputs and outputs. That is, the number of inputs and outputs must be known at compile time. Additionally, the code region must not read any data other than its inputs, nor affect any data other than its outputs. No major changes are necessary to the programming language beyond adding the approximable keyword.

**Exposing analog circuits to the compiler.** Although an analog accelerator presents the opportunity for gains in efficiency over a digital NPU, it suffers from reduced accuracy and flexibility, which results in limitations on possible network topologies and limited-

precision computation, potentially resulting in a decreased range of applications that can utilize the acceleration. These shortcomings at the hardware level, however, can be exposed as a high-level model and considered in the training phase.

Four characteristics need to be exposed: (1) limited precision for input and output encoding, (2) limited precision for encoding weights, (3) the behavior of the activation function (sigmoid), (4) limited feasible neural topologies. Other low-level circuit behavior such as response to noise can also be exposed to the compiler. Section 1.6 describes this necessary hardware/software interface in more detail.

Analog neural accelerator circuit design. To extract the high-level model for the compiler and to be able to accelerate execution, we design a mixed-signal neural hardware for multilayer perceptrons. The accelerator must support a large enough variety of neural network topologies to be useful over a wide range of applications. As we will show, each applications requires a different topology for the neural network that is replacing its approximable regions of code. Section 1.5 describes a candidate A-NPU circuit design, and outlines the challenges and tradeoffs present with an analog implementation.

**Compiling for analog neural hardware.** The compiler aims to mimic approximable regions of code with neural networks that can be executable on the mixed-signal accelerator. While considering the limitation of the analog hardware, the compiler searches the topology space of the neural networks and selects and trains a neural network to produce outputs comparable to those produced by the original code segment.

1) **Profile-driven training data collection.** During a profiling stage, the compiler runs the application with representative profiling inputs and collects the inputs and outputs to the approximable code region. This step provides the training data for the rest of the compilation workflow.

2) Training for a limited-precision A-NPU. This stage is where our compilation workflow significantly deviates from the framework presented in [12] that targets digital NPUs. The compiler uses the collected training data to train a multilayer perceptron neural network, choosing a network topology, i.e. the number of neurons and their connectivity, and taking a gradient descent approach to find the synaptic weights of the network while minimizing the error with respect to the training data. This compilation stage does a neural topology search to find the smallest neural network that (a) adheres to the organization of the analog circuit and (b) delivers acceptable accuracy at the application level. The network training algorithm, which finds optimal synaptic weights, uses a combination of a resilient back propagation algorithm, RPROP [25], that we found to outperform traditional back propagation for restricted network topologies, and a continuous-discrete learning method, CDLM [24], that attempts to correct for error due to limited-precision computation. Section 1.6 describes these techniques that address analog limitations.

**3**) Code generation for hybrid analog-digital execution. Similar to prior work [12], in the code generation phase, the compiler replaces each instance of the original program code with code that initiates a computation on the analog neural accelerator. Similar ISA extensions are used to specify the neural network topology, send input and weight values to the A-NPU, and retrieve computed outputs from the A-NPU.

#### **1.4 Analog Circuits for Neural Computation**

This section describes how analog circuits can perform the computation of neurons in multi-layer perceptrons, which are widely used neural networks. We also discuss, at a high-level, how limitations of the analog circuits manifest in the computation. We explain how these restrictions are exposed to the compilation framework. The next section presents a concrete design for the analog neural accelerator.

As Figure 1.2a illustrates, each neuron in a multi-layer perceptron takes in a set of inputs

Figure 1.2: One neuron and its conceptual analog circuit.

$(x_i)$  and performs a weighted sum of those input values  $(\sum_i x_i w_i)$ . The weights  $(w_i)$  are the result of training the neural network on training data (compile time) and are constant during the recall phase (execution time). After the summation stage, which produces a linear combination of the weighted inputs, the neuron applies a nonlinearity function, *sigmoid*, to the result of summation.

Figure 1.2b depicts a conceptual analog circuit that performs the three necessary operations of a neuron: (1) scaling inputs by weight  $(x_iw_i)$ , (2) summing the scaled inputs  $(\sum_i x_iw_i)$ , and (3) applying the nonlinearity function (*sigmoid*). This conceptual design first encodes the digital inputs  $(x_i)$  as analog current levels  $(I(x_i))$ . Then, these current levels pass through a set of variable resistances whose values  $(R(w_i))$  are set proportional to the corresponding weights  $(w_i)$ . The voltage level at the output of each resistance  $(I(x_i)R(w_i))$ , is proportional to  $x_iw_i$ . These voltages are then converted to currents that can be summed quickly according to Kirchhoff's current law (KCL). Analog circuits only operate linearly within a small range of voltage and current levels, outside of which the transistors enter saturation mode with IV characteristics similar in shape to a non-linear sigmoid function. Thus, at the high level, the non-linearity is naturally applied to the result of summation when the final voltage reaches the analog-to-digital converter (ADC). Compared to a digital implementation of a neuron, which requires multipliers, adder trees and sigmoid lookup tables, the analog implementation leverages the physical properties of the circuit elements and is orders of magnitude more efficient. However, it operates in limited ranges and therefore offers limited precision.

**Analog-digital boundaries.** The conceptual design in Figure 1.2b draws the analogdigital boundary at the level of an algorithmic neuron. As we will discuss, the analog neural accelerator will be a composition of these analog neural units (ANUs). However, an alternative design, primarily optimizing for efficiency, may lay out the entirety of a neural network with only analog components, limiting the D-to-A and A-to-D conversions to the inputs and outputs of the neural network and not the individual neurons. The overhead of conversions in the ANUs significantly limits the potential efficiency gains of an analog approach toward neural computation. However, there is a tradeoff between efficiency, reconfigurability (generality), and accuracy in analog neural hardware design. Pushing more of the implementation into the analog domain gains efficiency at the expense of flexibility, limiting the scope of supported network topologies and, consequently, limiting potential network accuracy. The NPU approach targets code approximation, rather than typical, simpler neural tasks, such as recognition and prediction, and imposes higher accuracy requirements. The main challenge is to manage this tradeoff to achieve acceptable accuracy for code acceleration, while delivering higher performance and efficiency when analog neural circuits are used for *general-purpose code acceleration*.

As prior work [12] has shown and we corroborate, regions of code from different applications require different topologies of neural networks. While a holistically analog neural hardware design with fixed-wire connections between neurons may be efficient, it effectively provides a fixed topology network, limiting the scope of applications that can benefit from the neural accelerator, as the optimal network topology varies with application. Additionally, routing analog signals among neurons and the limited capability of analog circuits for buffering signals negatively impacts accuracy and makes the circuit susceptible to noise. In order to provide additional flexibility, we set the digital-analog boundary in conjunction with an algorithmic, sigmoid-activated neuron. where a set of digital inputs and weights are converted to the analog domain for efficient computation, producing a digital output that can be accurately routed to multiple consumers. We refer to this basic computation unit as an analog neural unit, or ANU. ANUs can be composed, in various physical configurations, along with digital control and storage, to form a reconfigurable mixed-signal NPU, or A-NPU.

One of the most prevalent limitations in analog design is the *bounded range* of currents and voltages within which the circuits can operate effectively. These range limitations restrict the bit-width of input and weight values and the network topologies that can be computed accurately and efficiently. We expose these limitations to the compiler and our custom training algorithm and compilation workflow considers these restrictions when searching for optimal network topologies and training neural networks. As we will show, one of the insights from this work is that even with limited bit-width ( $\leq 8$ ), and a restricted neural topology, many general-purpose approximate applications achieve acceptable accuracy and significantly benefit from mixed-signal neural acceleration.

Value representation and bit-width limitations. One of the fundamental design choices for an ANU is the bit-width of inputs and weights. Increasing the number of bits results in an exponential increase in the ADC and DAC energy dissipation and can significantly limit the benefits from analog acceleration. Furthermore, due to the fixed range of voltage and current levels, increasing the number of bits translates to quantizing this fixed value range to fine granularities that practical ADCs can not handle. In addition, the fine granularity encoding makes the analog circuit significantly more susceptible to noise, thermal, voltage, current, and process variations. In practice, these non-ideal effects can adversely affect the final accuracy when more bit-width is used for weights and inputs. We design our ANUs such that the granularity of the voltage and current levels used for information encoding is to a large degree robust to variations and noise.

**Topology restrictions.** Another important design choice is the *number of inputs* in the ANU. Similar to bit-width, increasing the number of ANU inputs translates to encoding a larger value range in a bounded voltage and current range, which, as discussed, becomes impractical. There is a tradeoff between accuracy and efficiency in choosing the number ANU inputs. The larger the number of inputs, the larger the number of multiply and add operations that can be done in parallel in the analog domain, increasing efficiency. However, due to the bounded range of voltage and currents, increasing the number of inputs requires decreasing the number of bits for inputs and weights. Through circuitlevel simulations, we empirically found that limiting the number of inputs to eight with 8-bit inputs and weights strikes a balance between accuracy and efficiency. A digital implementation does not impose such restrictions on the number of inputs to the hardware neuron and it can potentially compute arbitrary topologies of neural networks. However, this unique ANU limitation restricts the topology of the neural network that can run on the analog accelerator. Our customized training algorithm and compilation workflow takes into account this topology limitation and produces neural networks that can be computed on our mixed-signal accelerator.

**Non-ideal sigmoid.** The saturation behavior of the analog circuit that leads to sigmoidlike behavior after the summation stage represents an approximation of the ideal sigmoid. We measure this behavior at the circuit level and expose it to the compiler and the training algorithm.

### **1.5** Mixed-Signal Neural Accelerator (A-NPU)

This section describes a concrete ANU design and the mixed-signal, neural accelerator, A-NPU.

Figure 1.3: A single analog neuron (ANU).

# 1.5.1 ANU Circuit Design

Figure 1.3 illustrates the design of a single analog neuron (ANU). The ANU performs the computation of one neuron, or  $y \approx sigmoid(\sum_i w_i x_i)$ . We place the analog-digital boundary at the ANU level, with computation in the analog domain and storage in the digital domain. Digital input and weight values are represented in sign-magnitude form. In the figure,  $s_{w_i}$  and  $s_{x_i}$  represent the sign bits and  $w_i$  and  $x_i$  represent the magnitude. Digital input values are converted to the analog domain through current-steering DACs that translate digital values to analog currents. Current-steering DACs are used for their speed and simplicity. In Figure 1.3,  $I(|x_i|)$  is the analog current that represents the magnitude of the input value,  $x_i$ . Digital weight values control resistor-string ladders that create a variable resistance depending on the magnitude of each weight ( $R(|w_i|)$ ). We use a standard resistor ladder thats consists of a set of resistors connected to a tree-structured set of switches. The digital weight bits control the switches, adjusting the effective resistance,  $R(|w_i|)$ , seen by the

input current  $(I(|x_i|))$ . These variable resistances scale the input currents by the digital weight values, effectively multiplying each input magnitude by its corresponding weight magnitude. The output of the resistor ladder is a voltage:  $V(|w_ix_i|) = I(|x_i|) \times R(|w_i|)$ . The resistor network requires  $2^m$  resistors and approximately  $2^{m+1}$  switches, where *m* is the number of digital weight bits. This resistor ladder design has been shown to work well for  $m \leq 10$ . Our circuit simulations show that only minimally sized switches are necessary.

$V(|w_ix_i|)$ , as well as the XOR of the weight and input sign bits, feed to a differential pair that converts voltage values to two differential currents  $(I^+(w_ix_i), I^-(w_ix_i))$  that capture the sign of the weighted input. These differential currents are proportional to the voltage applied to the differential pair,  $V(|w_ix_i|)$ . If the voltage difference between the two gates is kept small, the current-voltage relationship is linear, producing  $I^+(w_ix_i) = \frac{I_{bias}}{2} + \Delta I$ and  $I^-(w_ix_i) = \frac{I_{bias}}{2} - \Delta I$ . Resistor ladder values are chosen such that the gate voltage remains in the range that produces linear outputs, and consequently a more accurate final result. Based on the sign of the computation, a switch steers either the current associated with a positive value or the current associated with a negative value to a single wire to be efficiently summed according to Kirchhoff's current law. The alternate current is steered to a second wire, retaining differential operation at later design stages. Differential operation combats environmental noise and increases gain, the later being particularly important for mitigating the impact of analog range challenges at later stages.

Resistors convert the resulting pair of differential currents to voltages,  $V^+(\sum_i w_i x_i)$  and  $V^-(\sum_i w_i x_i)$ , that represent the weighted sum of the inputs to the ANU. These voltages are used as input to an additional amplification stage (implemented as a current-mode differential amplifier with diode-connected load). The goal of this amplification stage is to significantly magnify the input voltage *range of interest* that maps to the linear output region of the desired sigmoid function. Our experiments show that neural networks are sensitive to the steepness of this non-linear function, losing accuracy with shallower, non-linear activation functions. This fact is relevant for an analog implementation because

Figure 1.4: Mixed-signal neural accelerator, A-NPU. Only four of the ANUs are shown. Each ANU processes eight 8-bit inputs.

steeper functions increase range pressure in the analog domain, as a small range of interest must be mapped to a much larger output range in accordance with ADC input range requirements for accurate conversion. We magnify this range of interest, choosing circuit parameters that give the required gain, but also allowing for saturation with inputs outside of this range.