## LARGE-SIGNAL RELIABILITY OF SILICON-GERMANIUM HETEROJUNCTION BIPOLAR TRANSISTOR AMPLIFIERS

A Dissertation Presented to The Academic Faculty

by

Michael A. Oakley

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology August 2016

Copyright  $\bigodot$  2016 by Michael A. Oakley

## LARGE-SIGNAL RELIABILITY OF SILICON-GERMANIUM HETEROJUNCTION BIPOLAR TRANSISTOR AMPLIFIERS

Approved by:

Professor John D. Cressler, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor John Papapolymerou School of Electrical and Computer Engineering Georgia Institute of Technology

Assistant Professor Hua Wang School of Electrical and Computer Engineering Georgia Institute of Technology Professor Gregory D. Durgin School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Samuel Graham School of Mechanical Engineering Georgia Institute of Technology

Date Approved: 25 July 2016

for my family

## ACKNOWLEDGEMENTS

Were it not for the invitation of Dr. Cressler to join his group at a critical moment in my graduate education, I would never have earned a Ph.D. at Georgia Tech. I thank him for committing to me and helping me to develop as a professional. I was truly fortunate to have landed in his group, and will always be grateful.

I thank the current and former members of the SiGe Devices and Circuits Group for their support over the years. Special thanks must be extended to Seungwoo, Ickhyun, Saeed, Adilson, Peter and Zach for their collaborations on various publications. I am deeply indebted to Brian, Uppili and Partha for helping me enter the realm of device engineering by answering my incessant questions.

I am very thankful for the resources my sponsors have given me. I thank RFMD, Qorvo and Raytheon SAS for supporting my Ph.D., and Samsung, the GEDC and the Institute for supporting my initial efforts at Georgia Tech. Special thanks to Glenn, Cynthia, Julio, Mike, Phil, Kyu Hwan, Dong-Ho, and Chang-Ho. I also thank my dissertation reading committee for accepting my invitation to serve and for providing feedback on this work.

Having taught my first classes at Georgia Tech, I now realize how truly great my teachers have been over the years. At the top of the list, directly above my advisor, are my parents, Ted and Wanda. My father is the greatest teacher I have ever had, without question, and I deeply appreciate the example he has set for me. My mother's kindness and love are undeniable influences on my character, and I am thankful to be her son. Finally, thanks to my extremely talented sister Amanda for convincing everyone that I am smart. Hopefully, from time to time, I will be.

# TABLE OF CONTENTS

| AC            | KN(  | OWLEDGEMENTS                                                          | iv   |

|---------------|------|-----------------------------------------------------------------------|------|

| LIS           | от о | F TABLES                                                              | vii  |

| LIS           | о тъ | F FIGURES                                                             | viii |

| $\mathbf{SU}$ | MM   | ARY                                                                   | xiii |

| 1             | INT  | <b>TRODUCTION</b>                                                     | 1    |

|               | 1.1  | Origin and History of the Problem                                     | 1    |

|               | 1.2  | Hot-Carrier Effects                                                   | 3    |

|               | 1.3  | Avalanche-Induced Hard Breakdown                                      | 4    |

|               | 1.4  | Electromigration and Mutual Heating                                   | 5    |

|               | 1.5  | SiGe BiCMOS on High-Resistivity Substrates                            | 6    |

|               | 1.6  | RF Voltage Stress in MOSFETs                                          | 6    |

|               | 1.7  | Summary                                                               | 7    |

| <b>2</b>      | SIG  | E HBT DRIVER AMPLIFIER RELIABILITY                                    | 8    |

|               | 2.1  | Introduction                                                          | 8    |

|               | 2.2  | Cascode Gummel Characteristics                                        | 8    |

|               | 2.3  | Cascode Base Leakage                                                  | 11   |

|               | 2.4  | The Junction Waveform                                                 | 11   |

|               | 2.5  | Differences in RF and <i>dc</i> Damage                                | 15   |

|               | 2.6  | Avalanche Breakdown Under RF                                          | 18   |

|               | 2.7  | Summary                                                               | 21   |

| 3             |      | LIABILITY ANALYSIS OF SIGE HBT AMPLIFIERS UNDER<br>RGE VOLTAGE SWINGS | 22   |

|               | 3.1  | Introduction                                                          | 22   |

|               |      | 3.1.1 PA Breakdown                                                    | 26   |

|               |      | 3.1.2 LNA Breakdown                                                   | 27   |

|               | 3.2  | TCAD Simulations                                                      | 28   |

|          | 3.3 | Comparing LNA Breakdown Points                                                       | 32        |

|----------|-----|--------------------------------------------------------------------------------------|-----------|

|          | 3.4 | Conclusions                                                                          | 35        |

| 4        | TC. | AD WAVEFORM ANALYSIS FOR SIGE HBTS                                                   | 38        |

|          | 4.1 | TCAD Setup                                                                           | 39        |

|          | 4.2 | Cascode RF Simulations                                                               | 42        |

|          | 4.3 | Differences in RF and $dc$ Damage $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 46        |

|          | 4.4 | Implications and Summary                                                             | 47        |

| <b>5</b> | ASS | SESSING SIGE HBT MUTUAL HEATING                                                      | 48        |

|          | 5.1 | Introduction                                                                         | 48        |

|          | 5.2 | Measurement Methodology                                                              | 50        |

|          | 5.3 | Measurement Results                                                                  | 52        |

|          | 5.4 | Implications                                                                         | 60        |

|          | 5.5 | Thermal Performance of Copper Pillar Flip-Chip PAs                                   | 61        |

| 6        |     | VERAGING IMPROVED PERFORMANCE OF FET SWITCH<br>HIGH-RESISTIVITY SUBSTRATES           | IES<br>64 |

|          | 6.1 | Introduction                                                                         | 64        |

|          | 6.2 | Stacked FETs                                                                         | 67        |

|          | 6.3 | Switched-Base SiGe HBT Power Cores                                                   | 73        |

|          |     | 6.3.1 Introduction                                                                   | 74        |

|          |     | 6.3.2 Topology Implementation                                                        | 76        |

|          |     | 6.3.3 Measurements                                                                   | 77        |

|          | 6.4 | Programmable Arrays of Capacitors (PACs)                                             | 79        |

| 7        | CO  | NCLUSIONS AND FUTURE WORK                                                            | 84        |

|          | 7.1 | Reliability Guidelines for RF Circuit Designers                                      | 84        |

|          | 7.2 | Contributions                                                                        | 86        |

|          | 7.3 | Suggested Future Work                                                                | 87        |

| RE       | FER | LENCES                                                                               | 88        |

| VI       | ГА. |                                                                                      | 97        |

## LIST OF TABLES

| 3.1 | Hard failure input power levels for three third-generation SiGe HBT<br>Cascode LNAs.                                                | 33 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | NF for three third-generation SiGe HBT Cascode LNAs                                                                                 | 33 |

| 3.3 | The 2.4 GHz narrowband LNA's NF response to stress from a 2.4 GHz continuous-wave input power sweep, extending to hard failure      | 34 |

| 3.4 | The 0.3-15 GHz Resistive LNA's NF response to stress from a 10 GHz continuous-wave input power sweep, extending to 20 dBm           | 34 |

| 3.5 | The 15 GHz wideband LNA's NF response to stress from a short-term and long-term 26 dBm 14.9 GHz continuous-wave input power stress. | 35 |

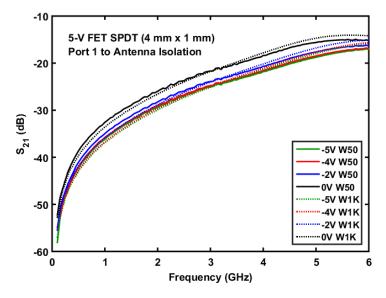

| 6.1 | Cellular band performance for a 5 V 4-stack SPDT with 4 mm series FETs and 1 mm shunt FETs                                          | 68 |

| 6.2 | Cellular band performance for a 3.3 V 4-stack SPDT with 4 mm series FETs and 1 mm shunt FETs                                        | 68 |

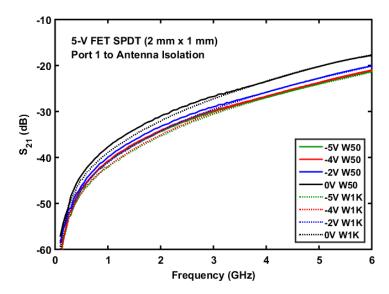

| 6.3 | Cellular band performance for a 5 V 4-stack SPDT with 2 mm series FETs and 1 mm shunt FETs                                          | 69 |

## LIST OF FIGURES

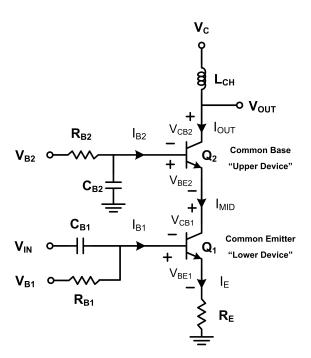

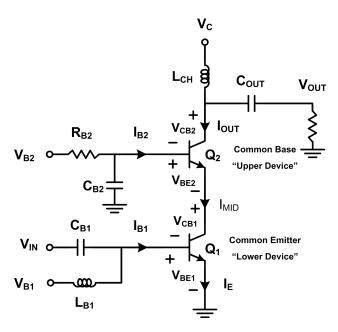

| 1.1  | Schematic of an emitter-ballasted cascode HBT amplifier. © 2015<br>IEEE [2]                                                              | 3  |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Schematic of an emitter-ballasted cascode HBT amplifier. © 2015<br>IEEE [2]                                                              | 9  |

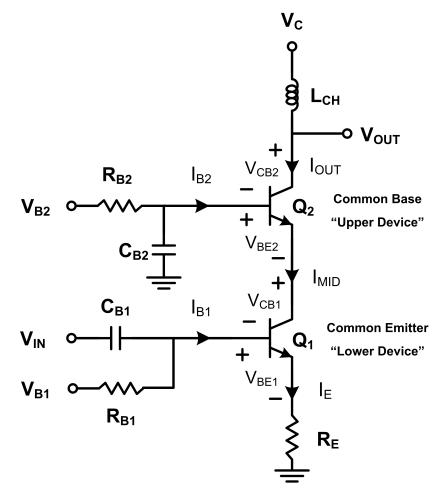

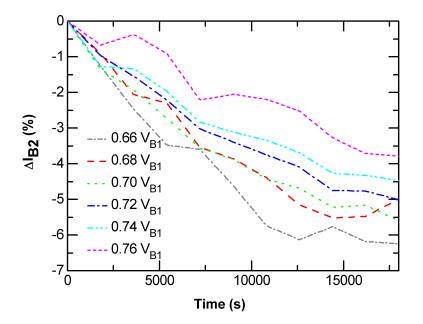

| 2.2  | The upper device's base leakage as a function of RF stress duration.<br>© 2015 IEEE [2]                                                  | 10 |

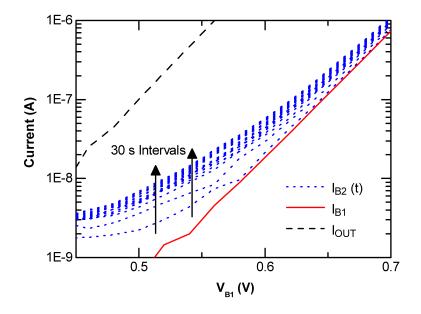

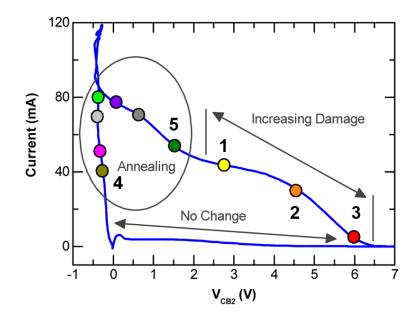

| 2.3  | Example of accruing damage under nominal RF operation. © 2015<br>IEEE [2]                                                                | 12 |

| 2.4  | Example of annealing when RF is <i>off</i> and quiescent bias continues.<br>© 2015 IEEE [2]                                              | 12 |

| 2.5  | Collector, emitter and forward transit currents as a function of voltage over one period of RF operation. © 2015 IEEE [2]                | 13 |

| 2.6  | CB capacitance calculated by two methods to assess simulation preci-<br>sion. © 2015 IEEE [2]                                            | 14 |

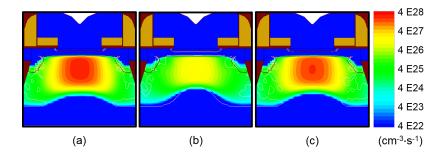

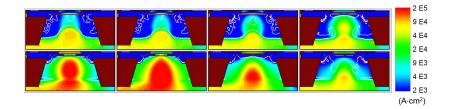

| 2.7  | TCAD cross-sections showing RF and $dc$ comparisons of total current<br>in a SiGe HBT. © 2015 IEEE [2]                                   | 15 |

| 2.8  | TCAD cross-sections showing RF and $dc$ comparisons of impact ion-<br>ization in a SiGe HBT. © 2015 IEEE [2]                             | 15 |

| 2.9  | RF and $dc$ output characteristics for SiGe HBTs in common emitter<br>and cascode configurations. © 2015 IEEE [2]                        | 16 |

| 2.10 | Comparison of RF and $dc$ hot-carrier damage for a given point in the output plane. © 2015 IEEE [2]                                      | 17 |

| 2.11 | Shift in base leakage during $dc$ cycled stress. © 2015 IEEE [2]                                                                         | 19 |

| 2.12 | Points chosen for $dc$ cycled stress. © 2015 IEEE [2]                                                                                    | 19 |

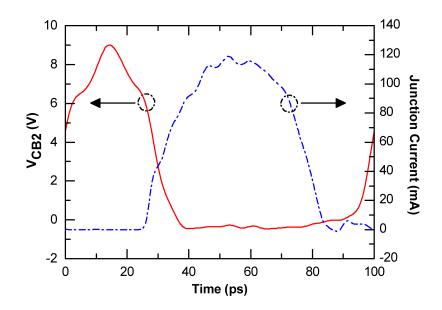

| 2.13 | Junction current and voltage waveforms as a function of time. © 2015<br>IEEE [2]                                                         | 20 |

| 3.1  | Current vs. collector-base voltage with an open emitter, with $BV_{CBO}$ indicated. Above breakdown the device current sharply increases | 23 |

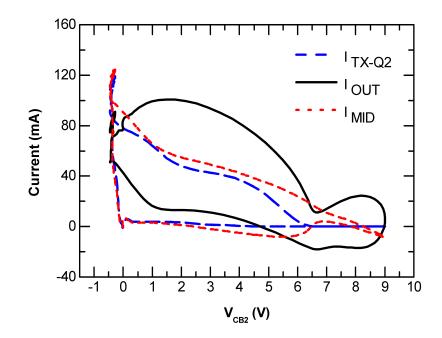

| 3.2  | Oscillations seen in a cascode SiGe HBT test structure when biased above $BV_{CBO}$ .                                                    | 24 |

| 3.3  | Cascode schematic used to describe circuit voltages and currents                                                                         | 27 |

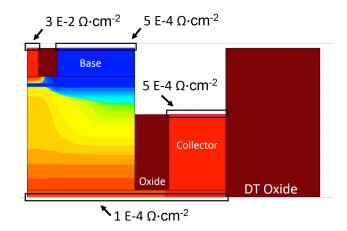

| 3.4  | A one-half TCAD cross-section with approximate thermal surface re-<br>sistance for the four-terminal device. The location of the surface used<br>for the substrate connection (at bottom) begins below the deep trench<br>and not in the location shown. | 29 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

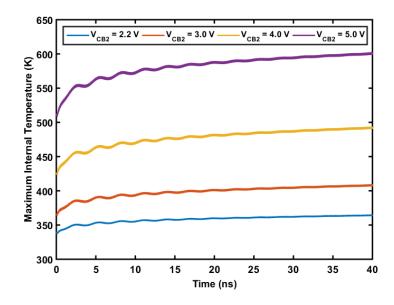

| 3.5  | Maximum device temperature vs. time for the first 400 periods of a 10 GHz, 0.4 V amplitude input signal, across various collector-base voltages, indicating the danger of aggressive bias.                                                               | 31 |

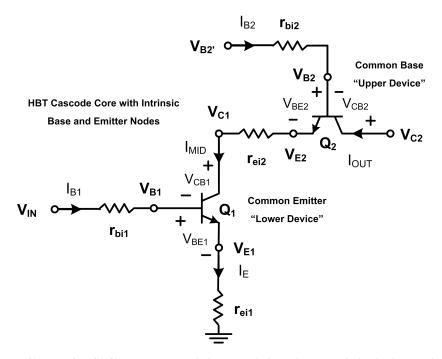

| 3.6  | Cascode SiGe HBTs with crucial voltages labeled, and including in-<br>trinsic resistances                                                                                                                                                                | 32 |

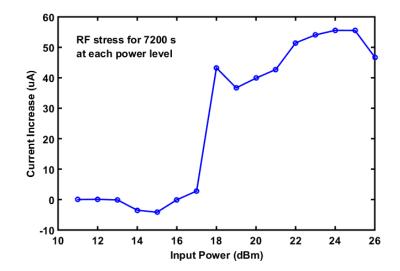

| 3.7  | Leakage current in the 15 GHz wideband LNA as a function of 7200 s RF input stress                                                                                                                                                                       | 35 |

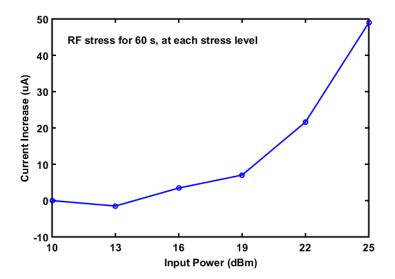

| 3.8  | Leakage current in the 15 GHz wideband LNA as a function of 60 s RF input stress                                                                                                                                                                         | 36 |

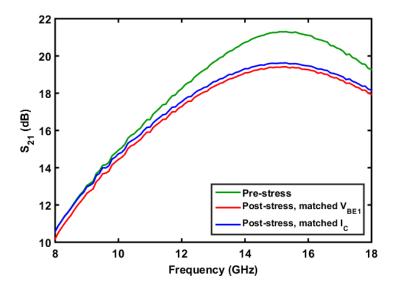

| 3.9  | Measured gain degradation in the 15 GHz wideband LNA after high RF input stress                                                                                                                                                                          | 36 |

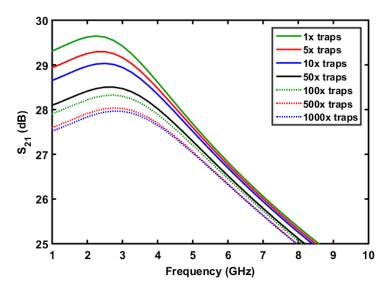

| 3.10 | Gain degradation correlation in TCAD with increasing trap density                                                                                                                                                                                        | 37 |

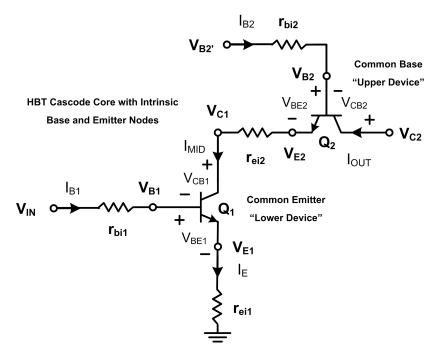

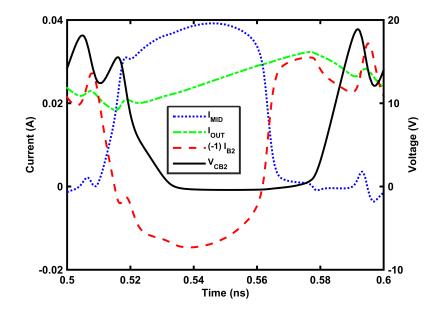

| 4.1  | Voltage nodes and current designations for cascode waveform analysis, showing intrinsic emitter and base resistances.                                                                                                                                    | 40 |

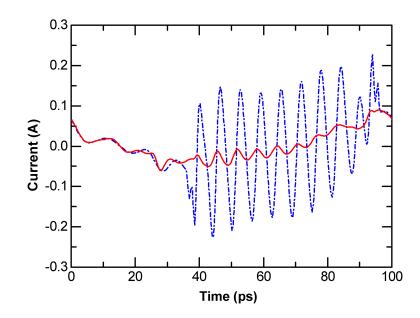

| 4.2  | Input voltage distortion due to intrinsic base and emitter resistances.<br>This distortion affects the upper device, which produces additional<br>distortion.                                                                                            | 40 |

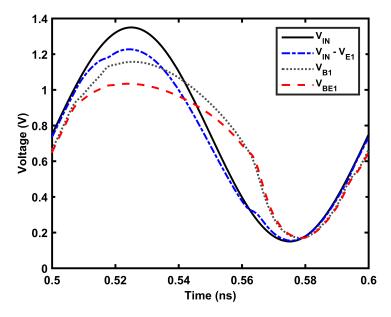

| 4.3  | TCAD (transient simulation) node currents and intrinsic base-emitter voltage for the upper device for one period of aggressive voltage swing.                                                                                                            | 41 |

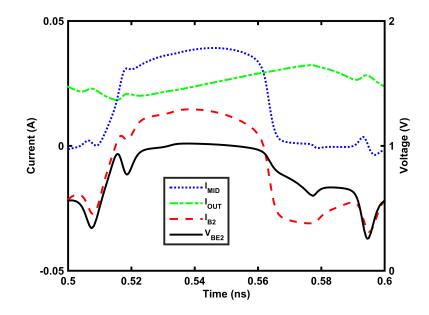

| 4.4  | TCAD (transient simulation) node currents and intrinsic collector-base voltage for the upper device for one period of aggressive voltage swing. The upper device's base current is reversed to better indicate the onset of BCR.                         | 41 |

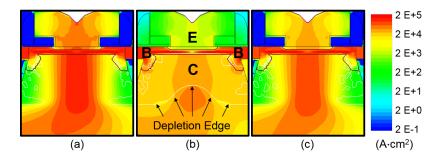

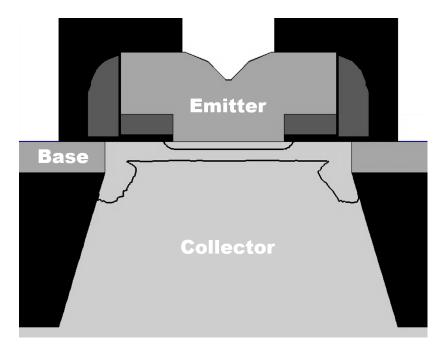

| 4.5  | A labeled TCAD cross-section.                                                                                                                                                                                                                            | 43 |

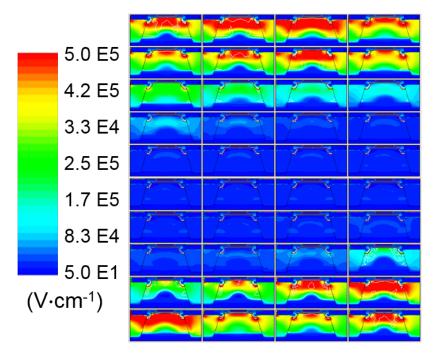

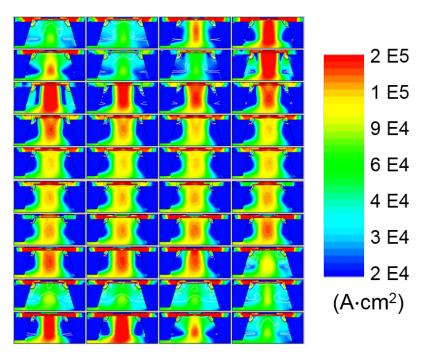

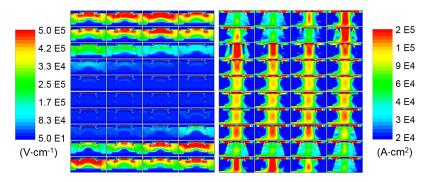

| 4.6  | Electric field cross-sections taken at 40 of 41 equally spaced intervals across one period                                                                                                                                                               | 44 |

| 4.7  | Total current cross-sections taken at 40 of 41 equally spaced intervals across one period                                                                                                                                                                | 44 |

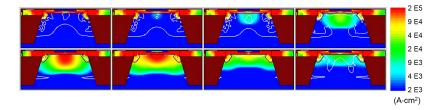

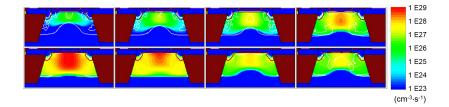

| 4.8  | A side-by-side comparison of Figure 4.6 and Figure 4.7, electric field<br>on the left and total current on the right                                                                                                                                     | 45 |

| 4.9  | Electron current only, matching last two rows in Figure 4.8                                                                                                                                                                                              | 45 |

| 4.10 | Hole current only, matching last two rows in Figure 4.8                                                                                                                                                                                       | 45 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.11 | Impact ionization only, matching last two rows in Figure 4.8                                                                                                                                                                                  | 45 |

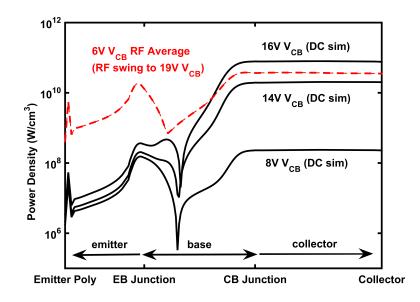

| 4.12 | Average power dissipation for RF operation (as shown in previous figures) compared to $dc$ simulation with a varying CB voltage. RF operation is comparable to 15 V across $V_{CB2}$ , although swinging up to 18.8 V.                        | 46 |

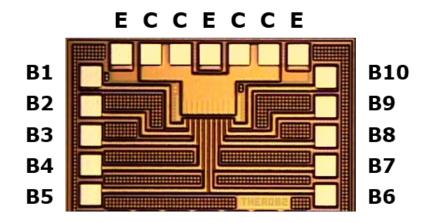

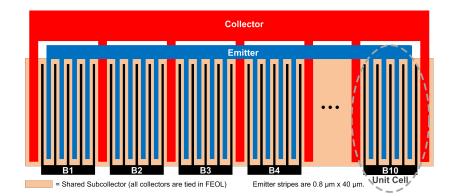

| 5.1  | A labeled die micrograph of the mutual heating test structure, a 10-<br>cell, shared-subcollector SiGe HBT array. The emitter terminals are<br>connected by through-silicon vias to a grounded backplane, minimizing<br>emitter degeneration. | 49 |

| 5.2  | Layout of the 10-cell array indicating 4-stripe emitter unit cells (not to scale)                                                                                                                                                             | 50 |

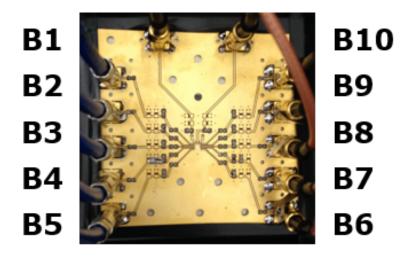

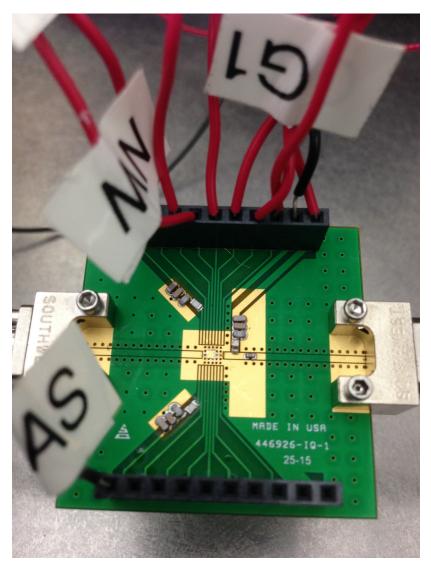

| 5.3  | A photo of the PCB used in the mutual heating experiments                                                                                                                                                                                     | 52 |

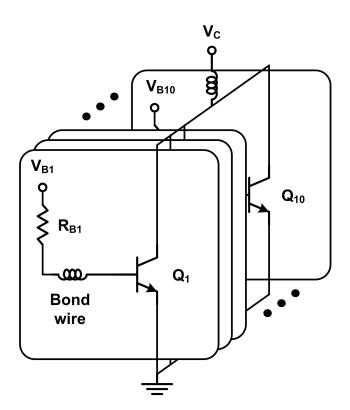

| 5.4  | Schematic of the mutual heating test circuit. The ground connection is<br>a combination of bond wires and through-silicon vias, and the collector<br>connection is also wire bonded. The base resistance is surface mounted<br>on the PCB.    | 53 |

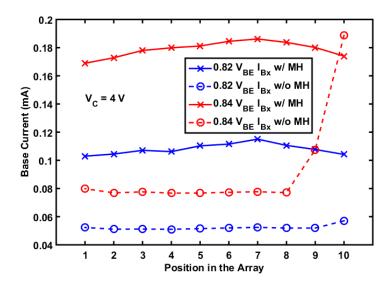

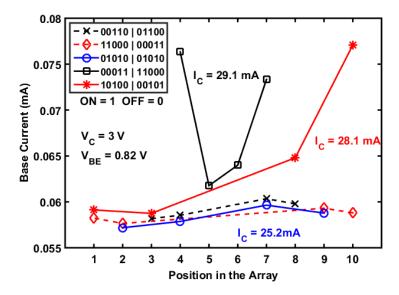

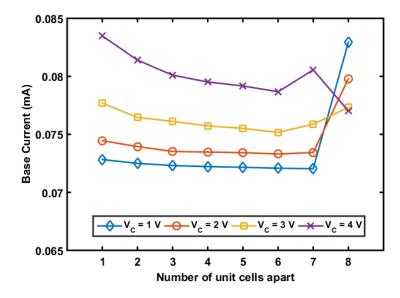

| 5.5  | Base current for each HBT in the 10-cell array, with and without mutual heating at 4 V on the collector. The base currents without mutual heating are collected with all other HBT base voltages set to zero volts.                           | 53 |

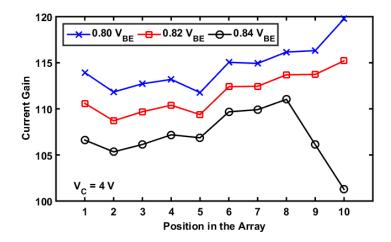

| 5.6  | Collector current divided by base current for each HBT in the 10-cell array, without mutual heating, at 4 V on the collector.                                                                                                                 | 55 |

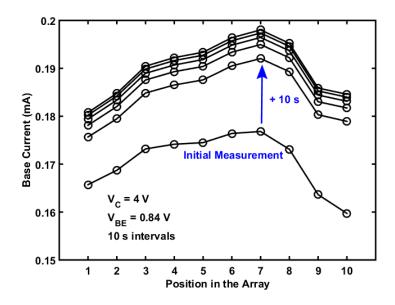

| 5.7  | Time progression of base currents in the array in 10 s intervals, indi-<br>cating how the array heats up over time.                                                                                                                           | 55 |

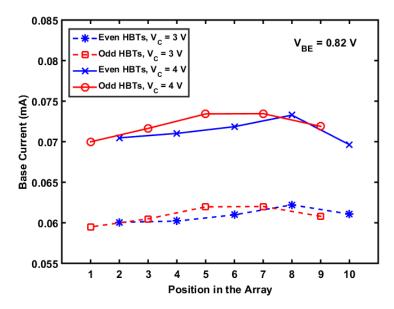

| 5.8  | Base currents when half of the array is <i>off</i> . Even and odd positions in the array are turned <i>off</i> and compared                                                                                                                   | 56 |

| 5.9  | The impact of resizing the array to $4/10$ size with 4 of 10 HBTs <i>on</i> . Various configurations are shown, with binary representations in the legend                                                                                     | 56 |

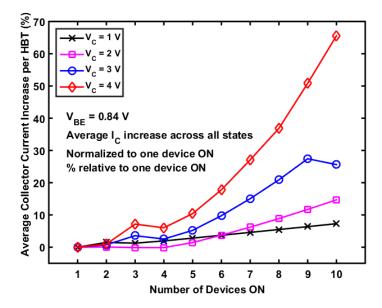

| 5.10 | The average contribution to collector current by a single HBT plotted against the number of devices <i>on</i> . The currents are all relative to the average current of a single device being <i>on</i>                                       | 57 |

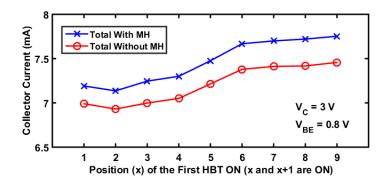

| 5.11 | Collector current when two adjacent devices are $on$ in the array. The collector current without MH is taken as the sum of the collector currents measured when each of the devices is $on$ individually                                      | 57 |

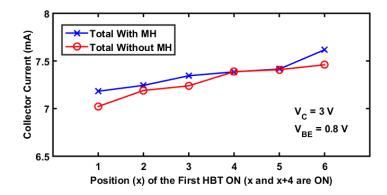

| 5.12 | Collector current when two devices, four cells apart, are $on$ in the array.<br>The collector current without MH is taken as the sum of the collector<br>currents measured when each of the devices is $on$ individually                                                                   | 58 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.13 | Base current for an interior device when two devices are <i>on</i> in the array, indicating the increasing effect of mutual thermal coupling as the devices are closer. Increased influence can also be seen when devices are the furthest apart, partly due to measurement memory effects | 58 |

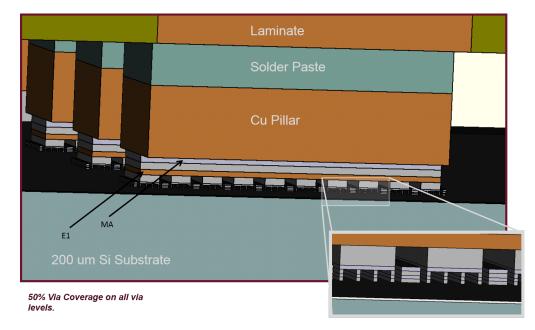

| 5.14 | Copper pillar flip-chip BEOL layers                                                                                                                                                                                                                                                        | 61 |

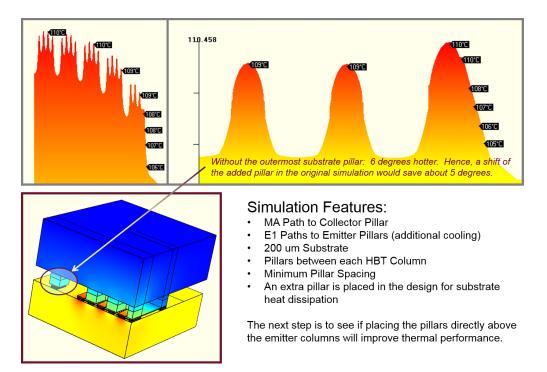

| 5.15 | Results of thermal simulations with copper pillars between emitters                                                                                                                                                                                                                        | 63 |

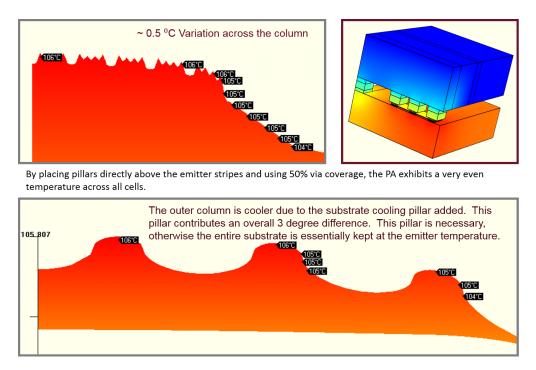

| 5.16 | Results of thermal simulations with copper pillars above emitters                                                                                                                                                                                                                          | 63 |

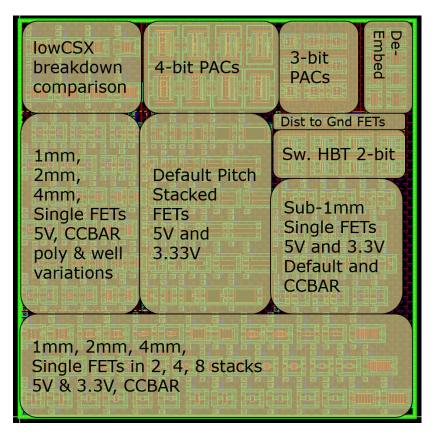

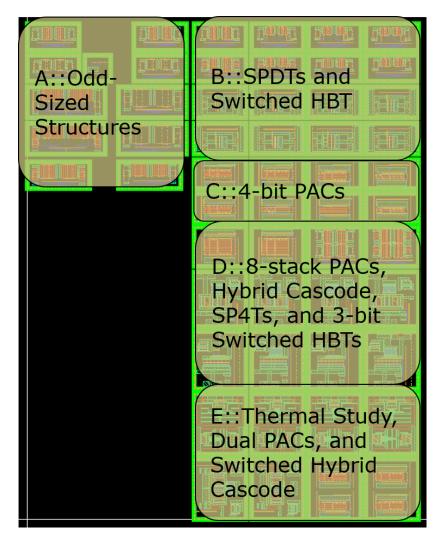

| 6.1  | Probe structures in 5PAe for switch evaluation.                                                                                                                                                                                                                                            | 65 |

| 6.2  | Structures for dicing from the 5PAe tapeout                                                                                                                                                                                                                                                | 66 |

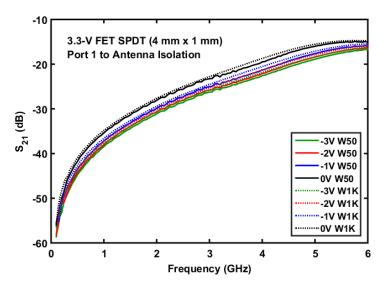

| 6.3  | Isolation for a 4-stack, 4 mm 5 V FET across p-well bias conditions for 50 $\Omega$ and 1 k $\Omega$ substrate resistivity.                                                                                                                                                                | 69 |

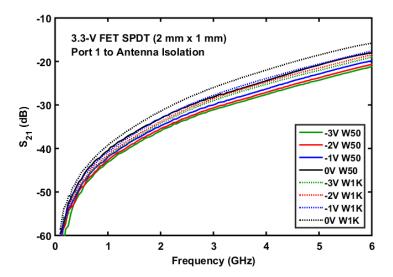

| 6.4  | Isolation for a 4-stack, 2 mm 5 V FET across p-well bias conditions for 50 $\Omega$ and 1 k $\Omega$ substrate resistivity.                                                                                                                                                                | 70 |

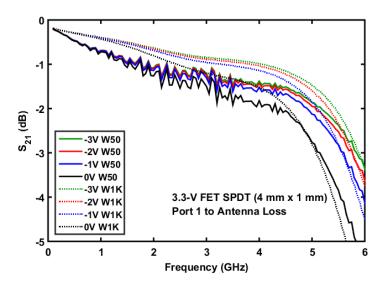

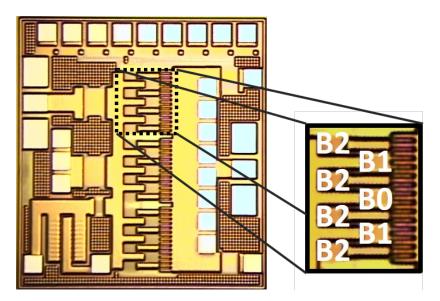

| 6.5  | Isolation for a 4-stack, 4 mm 3.3 V FET across p-well bias conditions for 50 $\Omega$ and 1 k $\Omega$ substrate resistivity.                                                                                                                                                              | 70 |

| 6.6  | Isolation for a 4-stack, 2 mm 3.3 V FET across p-well bias conditions for 50 $\Omega$ and 1 k $\Omega$ substrate resistivity.                                                                                                                                                              | 71 |

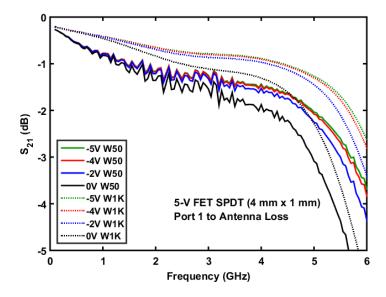

| 6.7  | Insertion loss for a 4-stack, 4 mm 5 V FET across p-well bias conditions for 50 $\Omega$ and 1 k $\Omega$ substrate resistivity.                                                                                                                                                           | 71 |

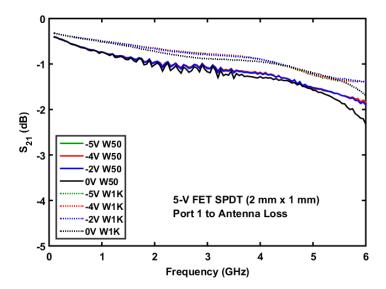

| 6.8  | Insertion loss for a 4-stack, 2 mm 5 V FET across p-well bias conditions for 50 $\Omega$ and 1 k $\Omega$ substrate resistivity.                                                                                                                                                           | 72 |

| 6.9  | Insertion loss for a 4-stack, 4 mm 3.3 V FET across p-well bias condi-<br>tions for 50 $\Omega$ and 1 k $\Omega$ substrate resistivity.                                                                                                                                                    | 72 |

| 6.10 | Insertion loss for a 4-stack, 2 mm 3.3 V FET across p-well bias condi-<br>tions for 50 $\Omega$ and 1 k $\Omega$ substrate resistivity.                                                                                                                                                    | 73 |

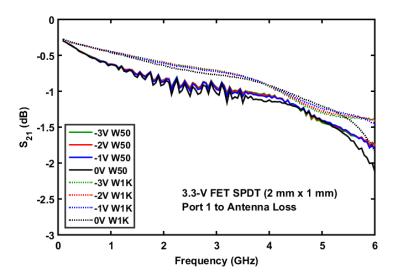

| 6.11 | Schematic of base-switched HBT unit cell with shunt FET for break-<br>down protection.                                                                                                                                                                                                     | 73 |

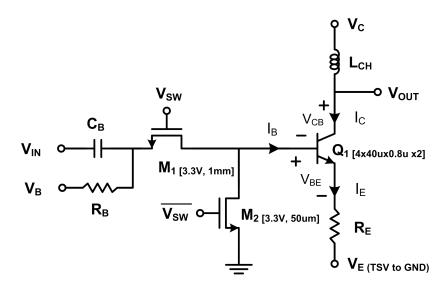

| 6.12 | Die photo of an eight-state base-switched SiGe HBT power cell in IBM 5PAe BiCMOS. The three-bit control incorporates 3, 6 and 12 equally spaced unit cells, without the shunt breakdown protection FET                                                                                     | 75 |

| 6.13 | Photograph of the PCB for the switched-base amplifier load pull experiments.                                                                                                                                                                                                               | 77 |

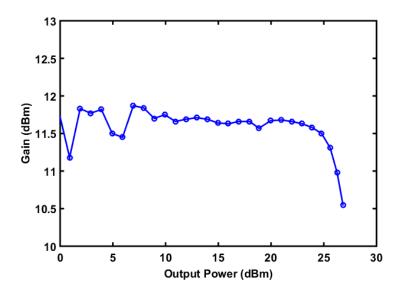

| 6.14 | Gain vs. output power for the matched switched-base amplifier, with all devices <i>on</i> .                                                     | 78 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

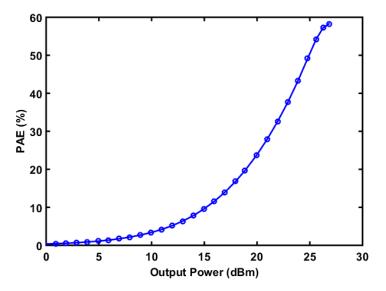

| 6.15 | PAE vs. output power for the matched switched-base amplifier, with all devices <i>on</i>                                                        | 78 |

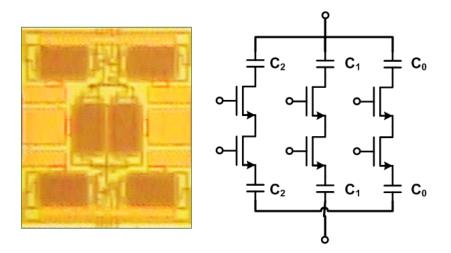

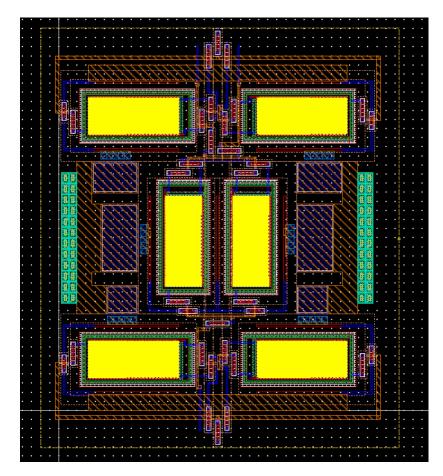

| 6.16 | Die photo and schematic from a 3-bit minimal resolution switched capacitor network.                                                             | 79 |

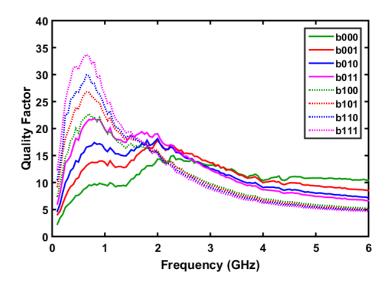

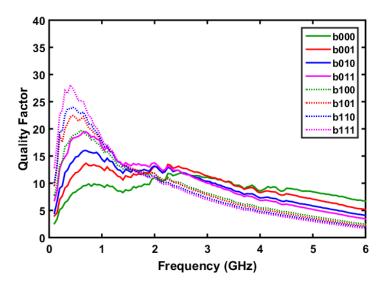

| 6.17 | 3-bit capacitor Q as a function of frequency on 50 $\Omega$ substrate                                                                           | 80 |

| 6.18 | 3-bit capacitor Q as a function of frequency on 1 k<br>$\Omega$ substrate                                                                       | 80 |

| 6.19 | A 3-bit compact PAC layout showing the hi-res keep-out layer surrounding all of the structure, which degrades Q for the 1 k $\Omega$ structure. | 81 |

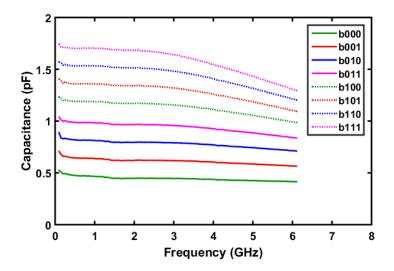

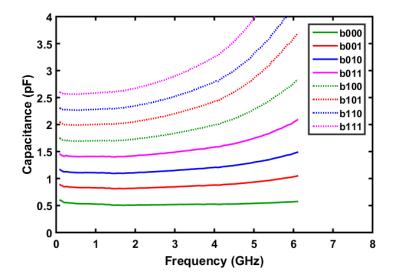

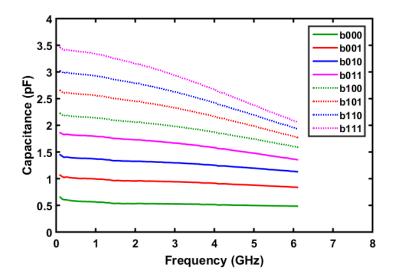

| 6.20 | 3-bit capacitance as a function of frequency for PAC version A on 50 $\Omega$ substrate.                                                        | 82 |

| 6.21 | 3-bit capacitance as a function of frequency for PAC version B on 50 $\Omega$ substrate.                                                        | 82 |

| 6.22 | 3-bit capacitance as a function of frequency for PAC version C on 50 $\Omega$ substrate.                                                        | 83 |

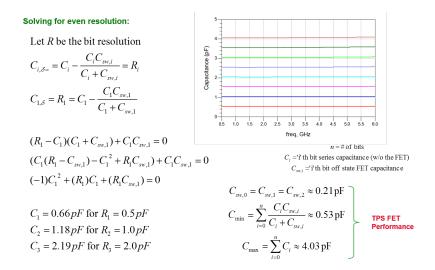

| 6.23 | Derivation and simulation of an even capacitance distribution for a 3-bit PAC in 5PAx                                                           | 83 |

### SUMMARY

This objective of this work is to answer open questions related to the largesignal reliability of SiGe HBT amplifiers. These questions are primarily focused on the impact of large RF voltage swings on both the base of LNAs and the collector of PAs. The limitations set by time-varying ac voltage swing had been cursorily investigated, but not to the depths explored in this dissertation. At the basic level, the evaluation of internal device temperatures is a crucial aspect of the knowledge set forth in this document. The primary benefit of this work is to set forth techniques that maximize the performance of SiGe HBT PAs without sacrificing long-term reliability. Additionally, the input power ruggedness of LNAs can be maximized with these techniques. The understanding communicated in this dissertation can be applied to failure analysis of SiGe HBT amplifiers in any circuit, such that the impact of dcvoltage bias and ac voltage swing can be quantitatively reasoned as the root cause.

It is the intention of the author that circuit designers will be able to glean essential device knowledge to maximize performance, and device engineers will obtain a perspective on amplifier design necessary to advance technology toward the needs of a required specification. Bridging the gap between the two disciplines is the overarching principle of this work, which is organized as enumerated below.

- 1. An introduction to the SiGe HBT device concepts necessary to understand the work is established.

- 2. An analysis of SiGe HBT driver amplifier reliability under large ac swings is presented. The capacitive portion of the collector current is separated from the simulated current to understand voltage swing beyond dc breakdown conditions. This work was first presented at IEEE RFIC 2014 in Tampa Bay [1] and later

extended to *IEEE Transactions on Electron Devices* [2].

- 3. An in-depth analysis of the thermal effects of a third-generation SiGe HBT as part of a LNA is conducted. Measurement on various LNAs and cascode structures are presented, showing noise degradation caused by large negative swings on the base of the amplifier. This has been submitted for publication to *IEEE Transactions on Electron Devices* [3].

- 4. Waveform analysis of SiGe HBT devices as well as TCAD visualizations of the thermal impact inside the device under *ac* operation are explored. This work is a first step beyond the concepts in [2] and supplements the work described in [3] in a separate technology.

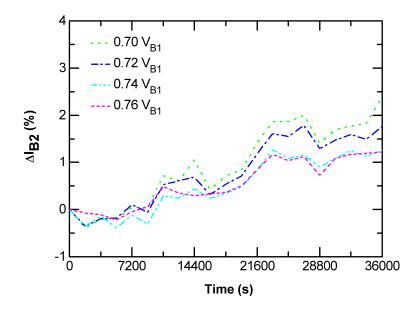

- 5. Assessment of mutual thermal coupling between devices in a SiGe HBT power array is presented. The impact of process variations on array temperature is visualized electrically for the first time. This work has been submitted for publication to *IEEE Transactions on Electron Devices* [4].

- 6. Switches on high-resistivity (1 k $\Omega$ ) substrate are briefly evaluated for three applications: SPDT antenna switches, resizable power cores and programmable arrays of capacitors. Comparisons to 50  $\Omega$  substrate are also provided.

#### Copyright Statement

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of Georgia Institute of Technology's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html to learn how to obtain a License from RightsLink.

Portions of the enclosed text and many of the figures will become IEEE copyrighted material in the future.

#### Acknowledgment of Support

This material is based upon work supported by Raytheon Space and Airborne Systems, RF Micro Devices and Qorvo.

## CHAPTER 1

## INTRODUCTION

### 1.1 Origin and History of the Problem

The two most important failure mechanisms to consider when designing integrated silicon-germanium (SiGe) heterojunction bipolar transistor (HBT) circuits are electromigration and impact ionization [5,6]. Electromigration is a well-understood topic concerning void formation in metal, and from this understanding the average lifetime of integrated circuit interconnects can be established [7]. If SiGe HBT interconnects are designed to withstand electromigration issues, operational lifetime of the device will be dominated by this mechanism, assuming guidelines set for the voltage across transistor junctions are also followed. Properly quantifying voltage maximums under large-signal operation, particularly at the output of power amplifier (PA) transistors, remains an unsolved problem that must be addressed in the field of SiGe HBT reliability.

Limitations on junction voltage are necessary to reduce impact ionization, which causes hot-carrier damage and eventual breakdown of the collector-base (CB) junction once a critical electric field is reached. Although the effects of impact ionization can be simply correlated to constant current conditions for a given SiGe HBT circuit, the onset and extent of the resultant damage created under radio frequency (RF) operation is not completely understood, therefore safe operating conditions are derived solely from direct current (dc) measurements in practice. This leads to unnecessarily conservative biasing of large-signal amplifiers, wasting the efficiency and output power benefits attributable to maximized voltage swing. Therefore, the careful study of differences between dc and RF operation with respect to impact ionization will result in optimized, and reliable, large-signal PA performance using SiGe HBTs.

Understanding RF reliability is an important step for SiGe HBTs, which are consistently integrated with silicon complementary metal-oxide-semiconductor (CMOS) processes to leverage the advantages of bipolar and CMOS transistors in a single platform (BiCMOS) [8]. SiGe HBTs also exhibit a robustness to radiation, allowing implementations in extreme environment electronics [9]. In extreme environment radar applications, voltage swing maximums are particularly important as output power is the primary design objective, and cascode amplifier cores are typically employed to increase voltage handling. Since the impact of hot-carrier damage can be mitigated with a cascode configuration, through the isolation provided by the additional device, the true limitation impact ionization introduces in a cascode amplifier is catastrophic failure due to avalanche breakdown [1]. Hence, quantifying this limit in terms of RF voltage and current for various SiGe HBT technologies will provide device and circuit designers an essential tool for optimizing performance.

Reliability analysis of large-signal bipolar circuits is an under-investigated topic in electronics design literature, perhaps due to the complexity presented by timedependent thermal considerations necessary to correlate RF to dc damage. Most explorations in the literature concerning SiGe HBTs are limited to either dc safe operating area (SOA) or qualitative RF comparisons [10–15].

To get at RF reliability, a well-founded understanding of SiGe HBT hot-carrier effects and avalanche-induced breakdown is necessary. The next two sub-sections review these topics in the context of a cascode amplifier (Figure 1.1), a widely used topology for SiGe HBT amplifiers, in large part due to its increased voltage handling.

Subsequently, electromigration in extrinsic back-end-of-line (BEOL) metals will be discussed briefly to further present the complexity of design for reliability. In the final two sub-sections, an overview of benefits arising from high-resistivity substrates and the limitations of CMOS RF stress will be simply stated.

Figure 1.1: Schematic of an emitter-ballasted cascode HBT amplifier. © 2015 IEEE [2]

#### **1.2** Hot-Carrier Effects

High electric fields in the collector-base (CB) region of a SiGe HBT caused by high CB voltage ( $V_{CB}$ ) produce high-energy carriers. The changes to the overall transistor performance caused by these carriers are referred to as hot-carrier effects. For example, hot carriers are more capable of propagating to the emitter-base (EB) spacer as  $V_{CB}$  increases. The energy of the carrier upon reaching the oxide interface can break hydrogen bonds, forming interface traps. These traps contribute to a voltage-dependent parasitic base-leakage current, which increases with stress duration. Trap annealing simultaneously occurs at a rate dependent on temperature, and the operating conditions of the SiGe HBT determine the dominant mechanism.

For a single SiGe HBT in a common-emitter configuration, device lifetime can be calculated as the point where current gain is degraded by 10%. For the cascode configuration, device lifetime is unaffected by base leakage as it accrues only in the common-base (or upper) device for which the current is set by the common-emitter (or lower) device. The lower device is shielded from hot-carrier-inducing high- $V_{CB}$  swings by the shunt decoupling capacitance placed on the base of the upper device; although extremely high input voltage swings will in fact cause damage to the lower device [1, 14].

#### 1.3 Avalanche-Induced Hard Breakdown

While the shunt capacitance placed at the base of the upper cascode device protects the lower transistor, series resistance at the upper device's base terminal limits the safe operating voltage for the CB junction of that device. Breakdown voltage decreases with increasing resistance at that terminal, ranging from the larger open-emitter breakdown voltage ( $BV_{CBO}$ ) to the smaller open-base breakdown voltage ( $BV_{CEO}$ ) as the series resistance is increased [16–19]. This upper limit deteriorates with increasing emitter current and temperature due to positive thermal feedback during avalanche [20–23]. This limit is often mitigated in designs through the incorporation of base and emitter ballast in the lower device [24]. The quantification of this limit as a function of base resistance has been termed  $BV_{CER}$  [25, 26].

The range of breakdown in relation to base resistance is a consequence of base current reversal (BCR) which occurs at voltages above  $BV_{CEO}$  [27–34]. As the name suggests, base current reverses direction in response to increased voltage due to avalanche-generated carriers, flowing toward the biasing voltage source. With increased impedance at the base node, majority carriers are directed to the emitter where gain of the device contributes further to the avalanche mechanism, causing breakdown to occur at a reduced voltage. In concert with non-zero intrinsic base resistance, this reversed current also creates a differential in electric field within the SiGe HBT, with voltage reaching a peak at the center of the emitter stripe. This differential causes current to pinch-in to the center of the transistor, and eventually avalanche multiplication leads to thermal runaway and the likelihood of catastrophic junction damage. The point at which the derivative of current with respect to voltage tends to infinity is considered the flyback locus for a given base bias. Due to the thermal instability of these points in the I-V plane, the flyback loci delineate the worst-case dc SOA for SiGe HBTs. These points are quantifiable for a SiGe HBT cascode amplifier, as a function of thermal and resistive quantities [24]. For example, failure of the junction can be shifted to higher voltages by resistively ballasting the emitter-to-ground connection of a cascode amplifier. From the opposing viewpoint, failure is shifted to lower voltages by increasing positive feedback at the upper device emitter, from a maximum boundary of  $BV_{CBO}$  when no current is present.

## 1.4 Electromigration and Mutual Heating

The redistribution of metallic mass caused by high current density is referred to as electromigration. In integrated circuit interconnects, this redistribution aggregates in voids and hillocks, which eventually form unintended opens and shorts in a circuit design [35]. This eventuality can be quantified as a mean time-to-failure (MTTF), which is proportional to temperature and the square of current density, yet inversely proportional to cross-sectional area of the interconnect [7]. Aluminum interconnects have worse electromigration failure rates than copper, but are still employed in some first-generation technologies due to the reduced cost of aluminum [36]. As higherfrequency applications continue to drive the decrease in HBT emitter width and spacing, the available cross-sectional area for connecting to the transistor terminals decreases, and copper is used to add robustness [37].

In large arrays of transistors, mutual heating between transistors will lead to increased temperature and current density at the center of the array [38]. Although there are techniques for flattening the temperature differential, they are oftentimes impractical due to increased periphery and design complexity [39,40]. Therefore, the central cells of the array will tend to fail sooner than the outer cells. Similarly, central fingers of an HBT unit cell (a pair of collector connections on either side of multiple emitter stripes, each separated by base connections) will conduct more current than the outer fingers.

It should be noted that the central cells do not always dominate the current of the overall power core, due to process variation and the ongoing development of electromigration voids and hillocks. Current bifurcation has been shown to occur in multi-cell arrays, whereby one cell can dominate the overall current regardless of position [41]. Hence, the common mitigation technique for preventing current from becoming increasingly disproportionate due to electrothermal feedback is resistive ballasting [42]. For increased lifetime, cross-sectional area of interconnects should be maximized and current should be shared across an increased emitter area to reduce current density within the transistors.

#### 1.5 SiGe BiCMOS on High-Resistivity Substrates

The addition of through-silicon via (TSV) and high-resistivity substrate are helping first-generation SiGe HBT technologies to find increased application from 1 to 10 GHz [36, 43, 44]. The high breakdown of these devices (approximately 7 V  $BV_{CEO}$ and 20 V  $BV_{CBO}$ ) makes them useful in watt-level cellular handset applications. The inclusion of TSV improves gain by reducing emitter degeneration. High-resistivity substrates reduce losses in passives and CMOS switches, since increased frequency leads to additional substrate eddy currents [45, 46]. This reduction in loss contributes improved efficiency to PA designs, which might be traded for additional functionality, such as tunable matching or core resizing [47, 48].

#### **1.6 RF Voltage Stress in MOSFETs**

With the availability of reduced-loss metal-oxide-semiconductor field-effect transistors (MOSFETs), the incorporation of FET switches in the RF path becomes a more

attractive idea to explore. Indeed, RF CMOS using silicon-on-insulator (SOI) technology is a major player in the RF switch market [49,50]. Similar to HBTs, FETs accrue gate-oxide traps, from hot-carrier injection, that increase threshold voltage over time. The on-state drain-source resistance also shifts over device lifetime. Damage to the oxide eventually leads to shorts between the gate and channel in the device, effectively breaking down the dielectric insulation and resulting in a catastrophic failure of the transistor [51–54]. This is in contrast to dieletric damage in HBTs, which only introduces parasitic leakage as opposed to an electrical short. To reduce the impact of breakdown phenomena, the electric field between the drain and gate must be minimized in FETs. In CMOS PAs and switches, MOSFETs are carefully stacked together to share the voltage burden for this reason [55–60].

#### 1.7 Summary

For watt-level handset and radar applications, SiGe BiCMOS is an emerging solution due to an attractive cost-performance ratio. Since oxide damage in HBTs is noncatastrophic in nature, SiGe HBTs inherently hold an advantage over CMOS. Hence, understanding RF breakdown conditions for SiGe HBTs is crucial to evaluating the full potential of any BiCMOS technology. The challenge is identifying the onset of thermal runaway under a variety of RF operating conditions. Neither soft breakdown (performance shifts from hot-carrier damage) nor hard breakdown (catastrophic failure from thermal runaway) have been fully evaluated with respect to RF operation in the SiGe HBT literature. An improved understanding of large-signal SiGe HBT reliability holds promise, perhaps leading to techniques that can be applied during the circuit design process to improve performance without sacrificing operational lifetime.

## CHAPTER 2

## SIGE HBT DRIVER AMPLIFIER RELIABILITY

#### 2.1 Introduction

This chapter reviews original research into the effects of large-signal voltage swings on SiGe HBT cascode amplifiers. This analysis resulted in two published works [1,2]. This work provides a perspective for relating RF to dc damage through the lens of the intrinsic transistor's forward transit current (referred to as the junction waveform) as opposed to the extrinsic transistor waveform, which includes capacitive currents. Capacitive currents are shown to have minimal effect on hot-carrier damage. The limitations of junction waveform analysis are also set forth.

## 2.2 Cascode Gummel Characteristics

To assess hot-carrier damage, code was developed to control three separate voltage supplies connected to  $V_{B1}$ ,  $V_{B2}$ , and  $V_C$  (refer to Figure 2.1). Following a period of stress (either *dc* bias alone or under RF drive), the cascode Gummel (terminal currents measured across an increasing base-emitter bias voltage) was measured, and thereafter the stress conditions were reapplied. During Gummel measurements,  $V_C$  was set such that  $V_{CB2}$  remained constant at 1.0 V, while  $V_{B2}$  was set such that  $V_{CB1}$  would remain as close as possible to 1.0 V. A low  $V_{CB}$  is necessary to prevent additional hot-carrier damage during the Gummel measurement. (Low  $V_{CB}$  is particularly necessary in the case of fourth-generation 1.5 V  $BV_{CEO}$  SiGe HBTs where the order of bias application becomes of prime importance.)  $V_{B1}$  was increased in equal steps up to a maximum 1.0 V (or lower in cases where high-current annealing was considered a factor) to control the current through both devices, while  $V_{B2}$  and  $V_C$  were increased at twice the rate

Figure 2.1: Schematic of an emitter-ballasted cascode HBT amplifier. © 2015 IEEE [2].

of  $V_{B1}$  to maintain equivalent voltage drops across like terminals in both devices.

This method of comparing currents is effective when the upper and lower devices have equivalent emitter area (as was the case for Figure 2.2). Although the precision of this measurement is complicated by emitter ballast and base currents, this measurement method nonetheless results in an adequate depiction of the upper device base currents, since ballasting effects are minimal at the low-current-density settings where damage-induced leakage is most evident.

The currents  $I_{B1}$  and  $I_{B2}$  will be equivalent across  $V_{BE}$  prior to stress (using the above method), which serves as indication that the device has not been stressed previously. Because of this equivalency, changes in  $I_{B2}$  can be set relative to initial  $I_{B1}$ values to account for percent damage caused by prior operation. This is particularly important when analyzing aggressively biased amplifiers, as the bias point and input drive contribute quickly to hot-carrier damage. For example, the leakage evident in Figure 2.2 is plotted in 30-second intervals of nominal RF continuous-wave operation.

Figure 2.2: The upper device's base leakage as a function of RF stress duration. © 2015 IEEE [2].

#### 2.3 Cascode Base Leakage

Hot-carrier reliability of two emitter-ballasted IBM 7HP SiGe HBT cascode driver amplifiers (X-band and C-band) was studied under normal operation. Due to the high voltage swing across  $V_{CB2}$ , hot-carrier damage, seen in the base current of the upper device, approaches a slope of twice the inverse thermal voltage on the order of minutes, as opposed to the hours necessary for more modestly biased amplifiers (refer to Figure 2.2). This observed damage is consistent with impact ionization induced trap generation at the EB spacer region. Figure 2.3 shows the voltage dependence of base leakage over RF stress time. Nominal operation of the driver amplifiers in this study increases damage, whereas the quiescent bias stress alone is shown to anneal traps once a certain density of traps is reached (in Figure 2.4).

As evident in data, two concurrent effects must be included to properly model base leakage in stressed SiGe HBTs: (1) thermally dependent annealing and (2) electrically dependent hot-carrier rates. The TCAD models used in this work do not include annealing effects as this is an ongoing area of research, so analyzing impact ionization is the focus of the following sections.

#### 2.4 The Junction Waveform

In [1], the concept of revising the dynamic load line across a device to exclude capacitive currents internal to the transistor was first presented. What remains is the junction waveform, namely the voltage across and current through the depletion region existing at a particular junction (e.g.,  $V_{CB2}$ ). A visualization of the junction waveform being compared to the traditional transistor waveform (referenced henceforth as the extrinsic-transistor current) is presented in Figure 2.5. For the cascode driver amplifiers studied here, the CB junction current collapses to zero in the upper device, effectively protecting the amplifier from damage. Self-protection during saturated operation is discussed in [15], to which junction waveform analysis

Figure 2.3: Example of accruing damage under nominal RF operation. © 2015 IEEE [2].

Figure 2.4: Example of annealing when RF is off and quiescent bias continues. © 2015 IEEE [2].

Figure 2.5: Collector, emitter and forward transit currents as a function of voltage over one period of RF operation. © 2015 IEEE [2].

adds support and perspective. It should be noted that the junction current calculation in this study ignores a portion of the current passing to the base under BCR, assuming it to be capacitive in nature. In practice this may not be the case if  $V_{CB2}$  is biased well above the reversal point, where swings are aggressively large.

A junction's time-dependent current can be directly calculated from simulated harmonic balance data using equations specific to the transistor model. This is achieved by saving intrinsic voltage nodes during simulation and then calculating current from appropriate equations available from the model, as intrinsic currents are not typically saved by a harmonic balance simulator. The simulated current  $I_{MID}$  closely approximates the upper CB junction waveform and can be used as a first-order design tool (shown in Figure 2.5). This current includes capacitive currents related to the upper EB junction (as does  $I_{B2}$ , which also includes CBrelated depletion capacitance current) and therefore exaggerates the current. For a better approximation, these capacitive currents can be calculated and filtered out of the emitter current.

Figure 2.6: CB capacitance calculated by two methods to assess simulation precision. © 2015 IEEE [2].

To verify the precision of the simulations, the junction current should equal the value calculated by subtracting capacitive currents (primarily voltage-dependent CB depletion charge over time) from the extrinsic-transistor currents. For a designer working to simulate the junction waveform for the first time, this equivalence will bring to light large errors in the multitude of manually entered variables and equations used to derive the intrinsic-transistor currents.

An equivalent method of verifying simulation setup would be to graph the capacitive currents in two ways: (1) by calculating the derivative of intrinsic CB charge in  $Q_2$ , and (2) by comparing it to the current calculated by Kirchhoff's circuit law (KCL) at the intrinsic collector node. Figure 2.6 gives the results of such a comparison. The magnitude of this current is considerable, yet has negligible impact on hot-carrier damage, since it never crosses into the region where the overwhelming majority of hot carriers are created. Once setup is validated, differences in current in such a comparison will also show the designer if further harmonics are necessary in the simulation.

## 2.5 Differences in RF and *dc* Damage

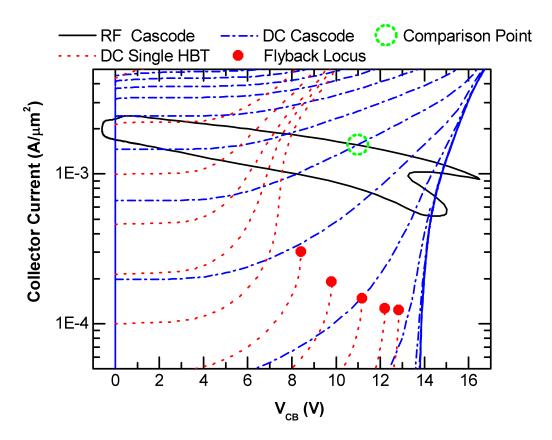

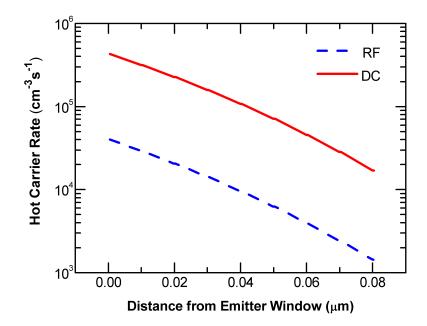

This section describes the complications associated with correlating RF to dc hotcarrier damage. Visualized through TCAD cross-sections (Figure 2.7 and Figure 2.8) based on the I-V conditions set forth in Figure 2.9, differences in current density and impact ionization are clearly evident. Flyback loci for the single device output characteristics in Figure 2.9 are located at the ends of the curves, coincident with TCAD simulation conditions that produce non-convergence issues. Convergence at higher  $V_{BE}$  values is attributable to secondary flyback caused by  $R_E$ . For the cascode, flyback extends to breakdown, although mutual heating between the upper and lower device will shrink this dc SOA for the cascode [24]. Self-heating and mutual-heating effects are ignored in TCAD simulations shown here.

Inspecting the TCAD cross-sections under RF and dc for identical I-V conditions, dc simulations have significantly increased current and impact ionization over the RF

Figure 2.7: TCAD cross-sections showing RF and dc comparisons of total current in a SiGe HBT. © 2015 IEEE [2].

Figure 2.8: TCAD cross-sections showing RF and dc comparisons of impact ionization in a SiGe HBT. © 2015 IEEE [2].

Figure 2.9: RF and dc output characteristics for SiGe HBTs in common emitter and cascode configurations. © 2015 IEEE [2].

Figure 2.10: Comparison of RF and dc hot-carrier damage for a given point in the output plane. © 2015 IEEE [2].

simulation snapshots. This can be attributed to differences in  $V_{BE2}$  which is effectively cut in half under RF. Under dc, a specific  $V_{BE2}$  (set by  $V_{BE1}$ ) is necessary for a given current (0.9 V and 0.875 V for the TCAD cross-sections shown). Under RF, the current follows the voltage waveform, thus by the time the current matches dc,  $V_{BE2}$ has dropped into cut-off at 0.4 V, choking off the positive feedback mechanism at the upper device emitter. With the time dependence of avalanche also playing part, this explains the reduced pinch-in seen under RF.

Hence, attempting to correlate RF damage from dc data along the extrinsic RF load line points would prove highly inaccurate. Indeed, since the waveform can travel beyond dc breakdown conditions, gathering such data would result in catastrophic failure of the SiGe HBT due to thermal runaway exacerbated by the pinch-in effect.

In Figure 2.7(a), the pinch-in under dc conditions is pronounced, while an RF snapshot in time at the same I-V point, in Figure 2.7(b), shows this centralization of current only reaching the collector-side edge of the space-charge region. This halting of current under RF is consistent with the intrinsic capacitive currents.

In [1], correlating dc damage to RF damage was performed, and found to be significantly complicated by annealing effects. In subsequent attempts to integrate dc data along the junction waveform, the data repeatedly overestimated the damage measured under the corresponding RF conditions. Of course, the temperature and interface-trap dependence of annealing behavior complicates this correlation, but TCAD simulations still show increased impact ionization and hot-carrier rates under dc conditions, even if the junction waveform is considered as the reference. Numerically, dc hot-carrier damage at the EB spacer outpaces the RF damage by an order of magnitude at the same bias point (Figure 2.10).

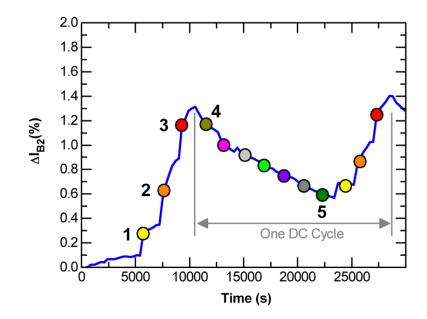

In Figure 2.12, trends in leakage current created by cycled dc stress along the junction waveform (at the points indicated in Fig 2.11) are shown to be a balance of annealing and damaging behavior. The mutually positive points in Figure 2.11 (current and voltage both greater than zero), account for a small portion of the waveform period, as can be gleaned from Figure 2.13, which plots both as a function of time.

In summation of these findings, acquiring RF hot-carrier damage rates from dc data will overestimate damage, and hence RF damage should be investigated through direct experiment. This data can then be used to calibrate TCAD simulations.

#### 2.6 Avalanche Breakdown Under RF

Driver amplifiers are driven deeply into saturation, resulting in significant harmonic content, as well as periods where the transistor junctions are non-conductive. The natural question that follows concerning the time dependence of avalanche in SiGe is somewhat hidden in this study, as any increasing effect of avalanche over RF stress is quelled by the fact that the CB junction of  $Q_2$  is effectively off for a majority of the time (Figure 2.13), acting primarily as a voltage-dependent capacitor. In saturated operation, breakdown is primarily dependent on reverse current induced by the high

Figure 2.11: Shift in base leakage during dc cycled stress. © 2015 IEEE [2].

Figure 2.12: Points chosen for dc cycled stress. © 2015 IEEE [2].

Figure 2.13: Junction current and voltage waveforms as a function of time. © 2015 IEEE [2].

field, hence RF stressing the CB junction leads to a good understanding of SiGe HBT cascode driver reliability.

As an example of how to experimentally determine the RF safe operating area (SOA) of a real driver amplifier design, fourth-generation IBM SiGe HBTs were CBjunction stressed with 1.0 V amplitude signals at 10 GHz. The base was well-grounded with respect to RF, and the waveform was applied to the collector. This was done to isolate the effects of emitter current on the CB voltage swing maximum. Fixed-bias *dc* breakdown for these devices occurred nominally at 5.4 V, while the full RF signal could swing to 6.1 V (centered at 5.1 V) before catastrophic failure resulted from 0.1 V steps. Base leakage under high-voltage capacitive swings might also be correlated from this methodology. By increasing the voltage amplitude and shifting the bias point, the time dependence of this phenomenon can be explored experimentally for a given frequency.

### 2.7 Summary

In this work, the complications of correlating RF and dc hot-carrier damage are investigated. TCAD simulations show that RF damage cannot be calculated from dc points along the RF load line, as this will overestimate damage. Furthermore, the temperature dependence of trap annealing also complicates this correlation, as the currents within the transistor are distributed differently, which also influences pinch-in phenomena. Therefore, to accurately model hot-carrier effects in SiGe HBT cascode amplifiers, fully calibrated TCAD models are necessary.

Nonetheless, a worst-case ceiling for base leakage can be taken from *dc* cycled stress along a revised load line consisting of the intrinsic-transistor CB-junction current. More importantly, this junction waveform can be used to analyze SOA with respect to catastrophic breakdown. Since hot-carrier damage does not lead to failure of a SiGe HBT cascode, as shown herein and throughout the literature, preventing catastrophic failure is the major design consideration for these structures.

A SiGe HBT can be swung above  $BV_{CBO}$ . If the junction is off (zero emitter current), as in the case of highly compressed driver amplifiers, the extent of this swing can be derived from capacitive swing measurements on single devices or from convergence issues seen in TCAD simulations. As a guideline, purely capacitive swing above breakdown may extend anywhere from 10% to 20%, dependent on upper-base resistance and ballast.

# CHAPTER 3

# RELIABILITY ANALYSIS OF SIGE HBT AMPLIFIERS UNDER LARGE VOLTAGE SWINGS

This work analyzes the effects of large voltage swings on a third-generation silicongermanium heterojunction bipolar transistor (SiGe HBT) as part of a cascode amplifier. Output swing beyond dc hard breakdown and input swing well beyond the inputreferred 1 dB compression point are evaluated in device simulation and measurement. To better understand power amplifier maximum output swing (as limited by hard breakdown), transistor lattice temperature is evaluated using calibrated device models with particular focus on the electrothermal impact of an aggressively biased collectorbase junction. In an examination of soft breakdown in low-noise amplifiers, the impact of interface trap creation caused by large input signals is shown to effect noise figure and gain. With this work, practitioners in SiGe HBT amplifier design will gain insight into the onset of damage under various bias conditions and input power levels, resulting in improved trade-off between performance and reliability.

# 3.1 Introduction

Performance of silicon-germanium (SiGe) heterojunction bipolar transistor (HBT) circuits is limited by junction breakdown mechanisms. To provide reliability guidelines, output voltage limits are based upon two dc measurements, the open-base and openemitter breakdown voltages,  $BV_{CEO}$  and  $BV_{CBO}$ .  $BV_{CEO}$  marks the onset of base current reversal (BCR) during forward active operation, after which higher collectorbase (CB) potentials avalanche-multiply majority carriers in the base [18]. These

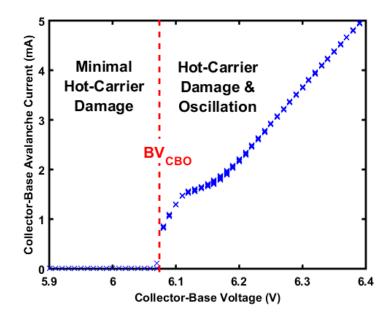

Figure 3.1: Current vs. collector-base voltage with an open emitter, with  $BV_{CBO}$  indicated. Above breakdown the device current sharply increases.

carriers either find a low impedance path out of the extrinsic base terminal (producing the reversed current), or proceed to the emitter if base impedance is restrictively high. If directed to the emitter-base (EB) junction, carriers are multiplied by the current gain of the SiGe HBT such that a large number of minority carriers are injected back into the base, to be swept across the CB junction, thus exacerbating avalanche. This positive feedback mechanism contributes toward thermal runaway which can result in irreparable device damage from the influence of excessive heat on the silicon lattice. Because of the dependency on base impedance, a breakdown voltage relative to base resistance ( $BV_{CER}$ ) is sometimes quantified, ranging between  $BV_{CEO}$  and  $BV_{CBO}$  [26].

Unfortunately, any dc limit provided to the circuit designer will be overly constricting in an application preferring maximized voltage swing, as in a wireless power amplifier (PA), as lattice temperatures will differ from large-signal ac operation. Furthermore, dc values for breakdown are sometimes quantified at the point of inflection in the current, rather than the voltage at which catastrophic failure occurs. For example, breakdown voltage values for the GlobalFoundries 8HP SiGe HBTs used

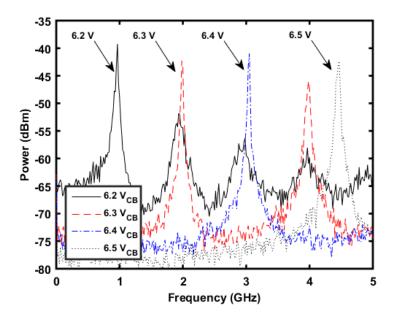

Figure 3.2: Oscillations seen in a cascode SiGe HBT test structure when biased above  $BV_{CBO}$ .

in this work are quantified by the foundry at a given current, above which current rapidly increases with CB voltage, as in Figure 3.1.

Hence, the term 'breakdown voltage' can be misleading from an *ac* perspective, especially since performance drift, or soft breakdown, is related to hot-carrier effects, while catastrophic failure, or hard breakdown, is dependent on the onset of thermal runaway [2]. Indeed, large-signal swings 10-20% beyond breakdown have been shown to be possible on the output side of a cascode pair [1, 2, 12]. Although the device can survive *dc* bias well beyond  $BV_{CBO}$ , the stability of the device is quite volatile. Spikes in current during bias adjustment, caused by increasing the voltage in too large of a step, led to immediate destruction of the SiGe HBTs in this work. In some cases, oscillations are evident, as shown in Figure 3.2, during a  $BV_{CBO}$  extrapolation using the common-base device in a cascode structure ( $V_{CB2}$  in Figure 3.3, with both base-emitter junctions off via reverse biasing).

For input-side power handling, the EB junction is of greater concern. Excessive negative voltage swing, as might be applied to the base of a low noise amplifier (LNA) by a nearby PA, accelerates hot-carrier damage in the EB spacer oxide resulting in a parasitic leakage current evident in the base [61–65]. This current can affect biasing, and therefore scattering (S-) parameters are known to shift [66]. Furthermore, large input swings on the LNAs in this study will be shown to degrade noise figure (NF). The EB junction enters breakdown at a lower voltage than the CB junction due to higher donor doping concentration [67], although failure requires greater over-voltage in comparison with the CB junction. In a high-gain PA with an aggressive collector bias, the CB junction will likely fail first [12]. In an LNA, the CB junction voltage is limited by high current effects acting on a small device periphery, which saturate the output current and limit output voltage swing, as described in [15] as RF stress quenching. Hence, device damage and performance drift in cascode SiGe LNAs as observed in [14, 68] are primarily attributable to EB stress as outlined in [15], since output swings have minimal effect on cascode amplifier performance [1, 2].

The advantages of quantifying *ac* limitations of SiGe HBTs are related to both performance and reliability. Higher voltage swings allow for reduced current in achieving the same target output power, and thus have the added benefits of increased efficiency and output impedance [69]. Increased output impedance contributes to more efficient output matching networks due to reduced impedance transformation ratios [70]. Hence, understanding the impact of swinging above breakdown is important to the SiGe HBT circuit design process, especially for PA applications. For LNA design, increased voltage headroom equates to improved dynamic range as collector voltage increases to extend P1dB [70].

Thus far in the literature, the negative impact of pursuing more aggressive bias schemes has not been fully addressed. The long term reliability of SiGe BiCMOS processes is primarily restricted by electromigration in the back-end-of-line (BEOL) metal layers closest to the device [7, 35], since short-term stress has minimal effect on performance [1, 2]. This is oftentimes outside the scope of scholarly investigations which observe short-term breakdown effects. Additionally, BEOL temperature and device self-heating may be difficult to incorporate into the design process due to the added complexity of mutual heating between devices in the amplifier core [4, 24]. To fill this void, the present work presents thermally calibrated device simulations. The objective of this work is to provide the designer with a full introduction to the complexities of SiGe design-for-reliability such that the performance-reliability tradeoff can be optimized. The next paragraphs continue this introduction in a broad sense.

#### 3.1.1 PA Breakdown

When designing wireless PAs that venture above  $BV_{CEO}$  there are two major issues to understand: junction breakdown and hot-carrier effects. Whenever possible, the design should provide a low resistance path at the base to stave off the onset of junction breakdown [26]. In a single-transistor common-emitter design, this low resistance path may, in practice, oppose resistive biasing and ballast requirements [71,72], hence, many designs will closely adhere to the  $BV_{CEO}$  guideline to compensate. Above  $BV_{CEO}$ , BCR also has some influence on non-linearity for swings that cross  $BV_{CEO}$ . Additionally, larger voltages increase impact ionization in the CB junction, which can damage the oxide used to shape the emitter window in a vertically integrated SiGe HBT. This damage leads to a parasitic base-leakage current, effectively lowering the current gain of the device over time. In some applications, this might be thwarted over the design lifetime with bias adjustments, without which the design performance may eventually drift beyond acceptable limits [14,68]. This soft breakdown effect, in concert with electromigration in the metal interconnects which is also exacerbated by increased CB voltage, sets the lifetime of a SiGe HBT circuit design [7,35].

As higher frequency applications continue to emerge for SiGe HBTs, cascode amplifiers are increasingly necessary to improve voltage handling. Fortunately, an

Figure 3.3: Cascode schematic used to describe circuit voltages and currents.

additional benefit of the cascode is protection from soft breakdown, as hot-carrier damage has limited impact in the common-emitter, or lower, device, since high fields are handled solely by the common-base, or upper, device [2]. This protection assumes modest input voltage and sufficient shunt capacitance on a low-resistance upper-base terminal. Under these circumstances, concern shifts to the onset of hard breakdown (the conditions under which catastrophic failure of the device occurs) with a focus on  $V_{CB2}$  as the limiting quantity, with increasing  $R_{B2}$  shrinking this limit further (see Figure 3.3). Under large-signal *ac* operation, it has been shown experimentally that  $V_{CB2}$  can safely swing above  $BV_{CBO}$  (by about 10% if swinging down to the knee voltage) when  $R_{B2}$  is kept low (on the order of 10  $\Omega$ ) [1,2,11,12].

#### 3.1.2 LNA Breakdown

As input voltage swing increases on a SiGe HBT LNA, the cascode output swing is limited by high injection effects. Hence, the one-decibel compression point (P1dB) of the design limits the voltage swing on the CB junction, rendering it very difficult to create hard failures in SiGe HBT LNAs on the output side. Experimentally, the present work will show that driving an X-band and a  $K_u$ -band LNA with 29 dBm is possible without causing hard breakdown. However, soft breakdown is accelerated for large input swings on the lower base due to stress caused by the negative BE potentials applied by the input drive.

Soft breakdown in SiGe HBTs implies the onset of a parasitic base-leakage current. For large output swings in cascode power amplifiers, this leakage can be limited to the upper device by limiting the input drive. In contrast, if input drive increases, the lower device will exhibit leakage. Since the emitter-base breakdown  $BV_{EBO}$  is smaller than  $BV_{CBO}$  due to doping differences [67], this occurs at a lower voltage than on the collector. Furthermore, hot carriers are created closer to the regions that can become damaged, therefore effects occur more rapidly. This increased current leads to increased noise figure (NF) and can result in deflated gain (which correlates to the NF shift) if the leakage current affects the input match, as will be shown in this work. As transistors get faster, breakdown voltage inherently decreases via the Johnson limit. Hence, understanding how the devices in cascode designs react to aggressive voltage swings beyond breakdown is an important step toward realizing the full potential of SiGe HBTs as the technology scales.

### 3.2 TCAD Simulations

Two-dimensional TCAD models of BiCMOS 8HP were calibrated from HBT measurement data to enable comparison with actual hardware. Models were updated with thermal boundary conditions consistent with parameter values accessible in the design kit (Figure 3.4). The detailed intricacies of the thermal boundary conditions are not precisely shown, for proprietary reasons, but parabolic spread is assumed at the substrate connection to help account for thermal discrepancies between the simplified two-dimensional simulations used and known three-dimensional effects. Device temperature will aggregate further to the center of the device when the third

Figure 3.4: A one-half TCAD cross-section with approximate thermal surface resistance for the four-terminal device. The location of the surface used for the substrate connection (at bottom) begins below the deep trench and not in the location shown.

dimension is added to the model, hence the data shown underestimates the impact of electrothermal interaction, particularly pinch-in. Avalanche multiplication (M-1) was calibrated from measured data to capture the impact of large CB potentials. Doping-dependent thermal properties were also included in the model.

Previous work on cascode amplifiers in the same technology recommended limiting collector-base maximum voltage to 10% above  $BV_{CBO}$  [5]. This is consistent with a 20% maximum voltage above  $BV_{CBO}$  if typical values for breakdown are assumed, as opposed to minimum values resulting from process variation. Hence, for a TCAD model set up for typical GlobalFoundries BiCMOS 8HP SiGe high-performance HBT process values, it can be hypothesized that 20% above breakdown is the predictive RF breakdown level for Class A operation utilizing the full linear range of the device (i.e, the low end of the swing hits the knee voltage) [69]. Non-optimal load lines could result in a decrease in the 20% approximation due to increased average CB voltage and therefore increased temperature.

A 10 GHz continuous-wave transient simulation was performed in Synopsys TCAD

under 11 mA quiescent bias conditions, with a  $V_{CB2}$  of 2.2 V. The upper-base resistance was kept at 10  $\Omega$ . The device size was scaled from one 0.12  $\mu$ m by 10  $\mu$ m single-stripe CBEBC-layout unit cell. Half-device structures of 1  $\mu$ m were modeled in two-dimensional TCAD to reduce simulation time, and the currents were scaled by 20 to match overall current to the measured device data.

The first TCAD experiment looked at internal device temperature of the upper device in the cascode structure. A large 0.4 V amplitude signal was applied to an unmatched cascode structure, as in Figure 3.3, to force the output swing to approach  $BV_{CBO}$ . Inductors were 10 nH and all capacitances were 20 pF. A decoupled load resistance was attached and set to 100  $\Omega$  to maximize the output swing. The maximum internal temperature for various collector-base voltage settings is given in Figure 3.5. As the maximum internal temperature is rising, there is some concern that thermal boundary conditions are too harsh in the setup. Furthermore, the simulations showed no thermal coupling to the lower device. Hence, a second setup was pursued including both devices in the same model, instead of each device being simulated separately in the cascode. With this revision, which took significantly longer to simulate, thermal coupling was determined to be minimal above 30  $\mu$ m separation, which is a reasonable design metric, so the original simulations were deemed sufficient.

Nonetheless, the 10-year lifetime temperature for the metals in this process limits the maximum collector-base voltage that can be reliably employed. With the results of Figure 3.5, a 3 V maximum is suggested. Although a short-term measurement for soft and hard breakdown would lend itself to a conclusion that it would be safe to increase  $V_{CB2}$  further, this would not capture the full impact of aggressive bias. In the hundreds of 8HP devices and circuits stressed in this work, catastrophic failure points varied, as electrothermal instability during RF operation might occur at any point above 50% of  $BV_{CB0}$  for a given circuit. This is primarily evident in PAs or cascode cores where a shift in bias left the device conducting for the majority of the

Figure 3.5: Maximum device temperature vs. time for the first 400 periods of a 10 GHz, 0.4 V amplitude input signal, across various collector-base voltages, indicating the danger of aggressive bias.

period, and therefore is not of immediate concern. However, to observe the electrical conditions that produce this effect, an LNA design with a high base resistance was evaluated.

As example, a 2.4 GHz cascode LNA was dc stressed to 3 V  $V_{CB2}$  with a 2.5 V  $V_{B2}$ . Over time, even small amounts of dc stress led to thermal runaway and amplifier failure. This phenomenon would first appear to conflict with previous data, but is attributable to two elements: the upper-base bias, 2.5 V  $V_{CB2}$ , and the high impedance bias network driving the lower base voltage  $V_{BE1}$  (refer to Figure 3.6). Because the upper-base voltage is high, the lower device is biased very close to  $BV_{CEO}$ . Avalanching current in the upper device is forced out of the upper device's base terminal, and the reversed current further increases the collector bias of the lower device, since the upper-base bias point adjusts with resistive effects and the direction of the current. With a base resistance above 1 k $\Omega$  for the lower device in the cascode, going beyond 1.5 V (worst-case  $BV_{CEO}$ ) on  $V_{CB1}$  leads to thermal runaway in the lower device. Hence, it would be expected that this circuit would fail from an RF

stress level that is lower than that of a similar amplifier that had a reduced bias point and low-impedance bias network. A comparison with such an amplifier is documented in the next section.

#### 3.3 Comparing LNA Breakdown Points