# SYSTEMATIC ANALYSIS OF THE SMALL-SIGNAL AND BROADBAND NOISE PERFORMANCE OF HIGHLY SCALED SILICON-BASED FIELD-EFFECT TRANSISTORS

A Thesis Presented to The Academic Faculty

by

Sunitha Venkataraman

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology August 2007

Copyright © 2007 by Sunitha Venkataraman

## SYSTEMATIC ANALYSIS OF THE SMALL-SIGNAL AND BROADBAND NOISE PERFORMANCE OF HIGHLY SCALED SILICON-BASED FIELD-EFFECT TRANSISTORS

#### Approved by:

Dr. Joy Laskar, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. John D. Cressler School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Emmanouil M. Tentzeris School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Kevin T. Kornegay School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Chang-Ho Lee Samsung RFIC Design Center Atlanta, Georgia

Date Approved: 11 May 2007

To my beloved parents and  $my\ grandfather\ \dots$

#### ACKNOWLEDGEMENTS

My research work at Georgia Tech commenced in Fall 2001 and has come to fruition through the help and constant support I received from many people. I wish to express my deepest gratitude to my advisor, Professor Joy Laskar, for his support, encouragement, and invaluable guidance throughout the course of my doctoral studies. He has been a great source of motivation and inspiration for me. I would like to thank Professor John D. Cressler, Professor Manos Tentzeris, Professor Kevin T. Kornegay, and Dr. Chang-Ho Lee for serving as members of my dissertation committee.

My sincere thanks to all the members of the Microwave Applications Group for their support, assistance and mentorship that has helped me carry out my research work. I am thankful to Dr. Sebastien Nuttinck, Dr. Arvind Raghavan, Dr. Chang-Ho Lee, and Dr. Deukhyoun Heo for introducing me to RF measurements and modeling techniques, to Dr. Bhaskar Banerjee for the fruitful discussions, constant support and help in the measurements and modeling activities. I would like to thank Dr. Kyutae Lim, Dr. Sudipto Chakraborty, Dr. Stephane Pinel, Anand Raghavan, Rahul Bhatia, Umesh Jalan, Dr. Sangwoon Yoon, Dr. Kiseok Yang, Dr. Chris Scholz, Saikat Sarkar, Padmanava Sen, Bevin G. Perumana, and Soumya Chandramouli for their help in numerous occasions. I would also like to thank my colleagues in the SiGe Research Group, Dr. Qingqing Liang, Dr. Enhai Zhao, Dr. Zhenrong Jin, Dr. Yuan Lu, Dr. Ramkumar Krithivasan, Dr. Tianbing Chen, Dr. Jonathan Comeau, Dr. Joel Andrews, Dr. Wei-Min Kuo, Jiahui Yuan, Becca Haugerud, Akil Sutton, Dr. Gnana Prakash, Dr. Bongim Jun for their significant contributions. I am very thankful to the support staff at the Georgia Electronic Design Center - Christopher Evans, DeeDee Bennett, Angelika Braig, Korinne Lassiter, Joi Adams, and Tammy Scott for their invaluable help.

I am deeply indebted to Dr. Chandra Shekhar, my Masters thesis advisor at Birla Institute of Technology and Science, India, for his invaluable guidance. His simplicity, dedication, and passion for teaching and research has always been a source of inspiration. I am grateful to my friends Anita Balasubramaniam, Veena Pureswaran, Nandini Hengen, Anurup Mitra, Indrani Devi, Anupama Seshadri, Abhijit Pethe, Tony Thomas, Prerna Goel, Cleitus Antony, Urvashi Rau, Samaksh Sinha, Himani Apte, Amit Nayyar, Ajit Sharma, Aruna Srinivasan, Sonali Tare, Karan Singhal, Rishi Ranjan, Bhaskar Saha, Sankalita Saha, Ajay Kumar, Vindhya Narayanan, and Vivek Venkatraman for their encouragement.

The unwavering support, love, and constant encouragement from my beloved parents has made this day possible for me. The sacrifices that they have made to provide me the best education and opportunities cannot be described in words. I am forever indebted to them. I would like to thank my late grandfather for his love and encouragement. I am thankful to all my family members for their love and support.

#### TABLE OF CONTENTS

| DED  | ICAT                                                           | ΓΙΟΝ . |                                                            | iii |  |

|------|----------------------------------------------------------------|--------|------------------------------------------------------------|-----|--|

| ACK  | NOW                                                            | VLEDG  | EMENTS                                                     | iv  |  |

| LIST | OF                                                             | TABLE  | S                                                          | ix  |  |

| LIST | OF                                                             | FIGUR  | ES                                                         | X   |  |

| SUM  | MAF                                                            | RY     |                                                            | XV  |  |

| Ι    | INT                                                            | RODU   | CTION                                                      | 1   |  |

|      | 1.1                                                            | A Brie | f History of Radio                                         | 1   |  |

|      | 1.2                                                            | Evolut | ion of Silicon CMOS Technology and its Application Space . | 3   |  |

|      | 1.3                                                            | Scope  | of the Dissertation                                        | 7   |  |

|      | 1.4                                                            | Thesis | Organization                                               | 9   |  |

| II   | FUNDAMENTALS OF NOISE AND HIGH-FREQUENCY NOISE MEASUREMENTS    |        |                                                            |     |  |

|      | 2.1                                                            | High-F | Frequency Noise in Scaled MOSFETs                          | 11  |  |

|      | 2.2                                                            | Noise  | Figure and Noise Parameters                                | 14  |  |

|      | 2.3                                                            | RF No  | pise Measurements                                          | 15  |  |

| III  | BROADBAND NOISE ANALYSIS AND MODELING OF HIGHLY SCALED MOSFETS |        |                                                            |     |  |

|      | 3.1                                                            | Two-P  | ort Noise Theory                                           | 18  |  |

|      | 3.2                                                            | Direct | Extraction of the Noise Sources of a MOSFET                | 20  |  |

|      | 3.3                                                            | Broad  | band Noise Modeling of 130 nm nFETs                        | 24  |  |

|      |                                                                | 3.3.1  | Device Technology and Experiments                          | 24  |  |

|      |                                                                | 3.3.2  | Results and Discussion                                     | 25  |  |

| IV   | CRYOGENIC PERFORMANCE OF DEEP SUB-MICRON CMOS DE-VICES         |        |                                                            |     |  |

|      | 4.1                                                            | On-wa  | fer Cryogenic Measurement System                           | 36  |  |

|      |                                                                | 4.1.1  | Closed-cycle Helium Refrigeration System                   | 37  |  |

|    |      | 4.1.2  | Open-cycle Cryogenic Probing System                                        | 38 |

|----|------|--------|----------------------------------------------------------------------------|----|

|    |      | 4.1.3  | Calibration Considerations                                                 | 40 |

|    | 4.2  | Opera  | tion of MOSFETs at Cryogenic Temperatures                                  | 42 |

|    | 4.3  | Broad  | band Noise Modeling of MOSFETs at Cryogenic Temperatures                   | 45 |

|    | 4.4  |        | Signal Operation of 0.18 $\mu m$ MOSFETs at Liquid Nitrogen erature (77 K) | 46 |

|    |      | 4.4.1  | Device Technology and Experiment                                           | 46 |

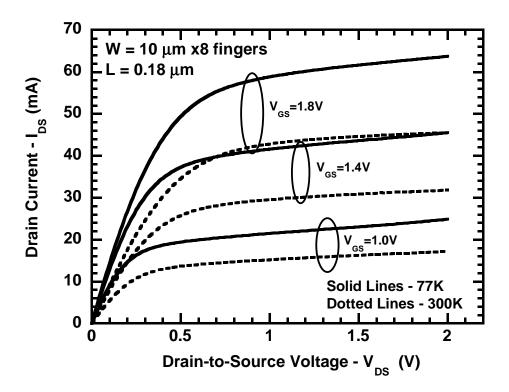

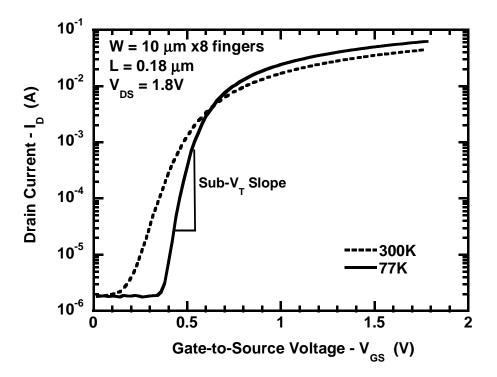

|    |      | 4.4.2  | DC Performance                                                             | 47 |

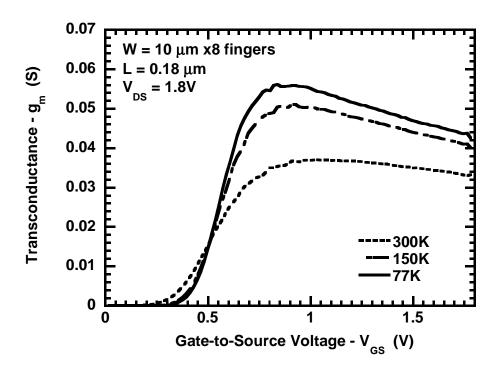

|    |      | 4.4.3  | Small-Signal AC Performance                                                | 49 |

|    | 4.5  | Cryog  | enic Performance of 130 nm MOSFETs                                         | 52 |

|    | 4.6  | Device | e Technology and Measurement                                               | 52 |

|    | 4.7  | DC Pe  | erformance                                                                 | 53 |

|    | 4.8  | Small- | Signal AC and Broadband Noise Performance                                  | 57 |

|    | 4.9  | Hot-ca | arrier Degradation of n-MOSFETs at 77 K                                    | 66 |

|    | 4.10 | Hot-C  | arrier Stress Experiment                                                   | 68 |

|    | 4.11 | Result | s and Discussion                                                           | 69 |

| V  | PRO  | TON I  | RADIATION TOLERANCE OF SCALED RF CMOS DEVICES                              | 76 |

|    | 5.1  | Total  | Dose Effects in MOSFETs                                                    | 77 |

|    | 5.2  | Proton | n Radiation Tolerance of a 130 $nm$ CMOS Technology                        | 79 |

|    |      | 5.2.1  | Device Technology and Experimental Details                                 | 79 |

|    |      | 5.2.2  | DC Performance                                                             | 81 |

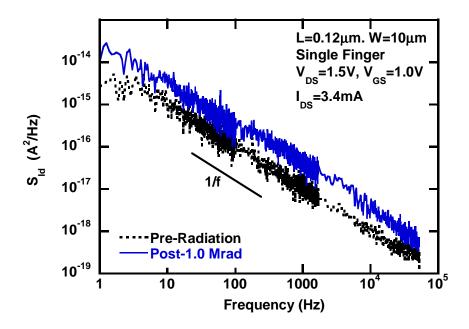

|    |      | 5.2.3  | Low-frequency $(1/f)$ Noise Performance                                    | 82 |

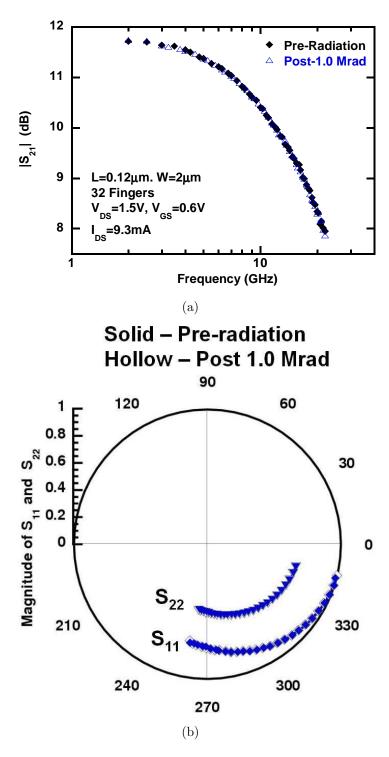

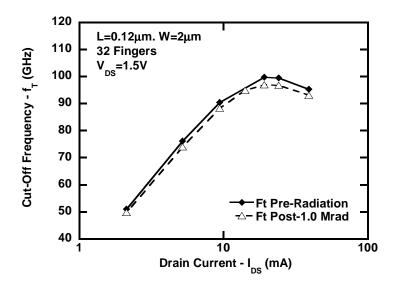

|    |      | 5.2.4  | Small-Signal Performance                                                   | 85 |

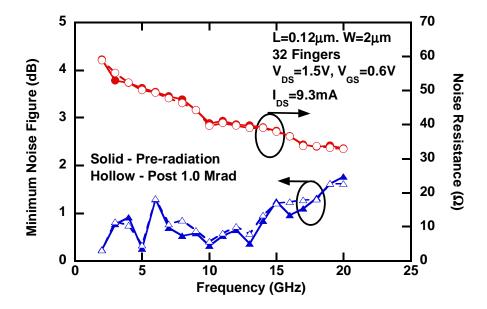

|    |      | 5.2.5  | Broadband Noise Performance                                                | 87 |

|    | 5.3  | Summ   | ary                                                                        | 88 |

| VΙ |      |        | DRMANCE OF HIGHLY SCALED SILICON GERMANIUM                                 | 90 |

|    | 6.1  | Device | e Technology                                                               | 90 |

|    | 6.2  | Result | s and Discussion                                                           | 92 |

|     |     | 6.2.1  | DC Performance                               | 92  |

|-----|-----|--------|----------------------------------------------|-----|

|     |     | 6.2.2  | Small-Signal AC and Broadband Noise Analysis | 94  |

| VII | COI | NCLUS  | IONS AND FUTURE WORK                         | 99  |

|     | 7.1 | Contri | ibutions and Impact of the Dissertation      | 99  |

|     | 7.2 | Scope  | for Future Work                              | 100 |

| APP | END | IX A   | PUBLICATIONS                                 | 102 |

| VIT | Α.  |        |                                              | 118 |

#### LIST OF TABLES

| 1 | Small-signal Parameters of a nFET with $W/L = 8.0/0.12$ (with 32 fingers) biased at $V_{GS}$ =0.6V and $V_{DS}$ =1.2V | 26 |

|---|-----------------------------------------------------------------------------------------------------------------------|----|

| 2 | Small Signal Parameters of the nFET biased at $V_{GS}$ =1.0V and $V_{DS}$ =1.8V, at 300 K and 77 K                    | 50 |

| 3 | Small Signal Parameters of the nFET biased at $V_{GS}$ =0.9 V and $V_{DS}$ =1.2 V, at 300 K and 77 K                  | 57 |

| 4 | Small Signal Parameters of the nFET biased at $V_{GS} - VTH = 0.76$ V and $V_{DS} = 1.2$ V, at 300 K and 77 K         | 73 |

#### LIST OF FIGURES

| 1  | Photograph of the first Si-MOSFET fabricated by Kahng and Atalla in 1960                                                                                                                                                                                                                                                                                                                 | 4  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

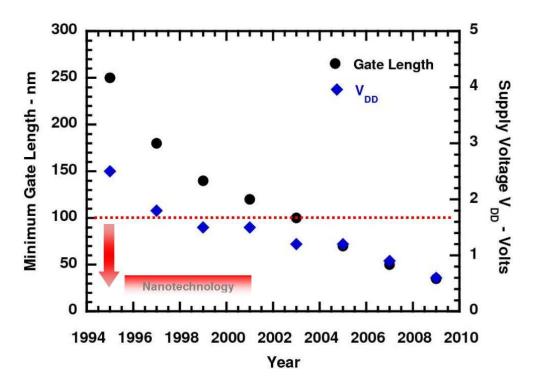

| 2  | Scaling of minimum gate-length and supply voltage $(V_{DD})$ of CMOS technologies over the years                                                                                                                                                                                                                                                                                         | 5  |

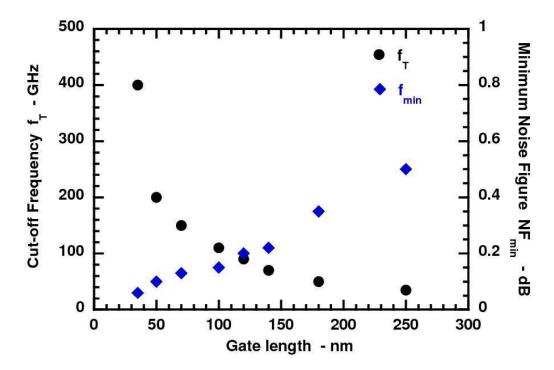

| 3  | Cut-off frequency $(f_T)$ and minimum noise figure $(NF_{min})$ versus gatelength                                                                                                                                                                                                                                                                                                        | 5  |

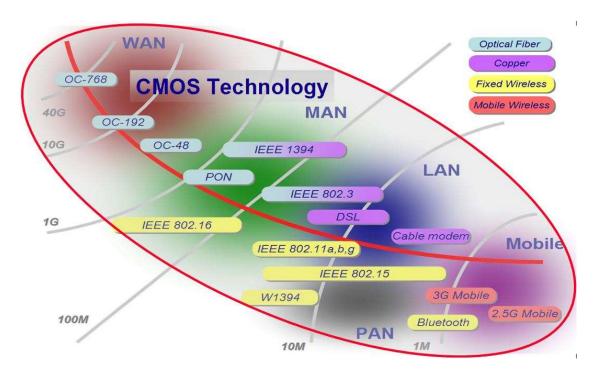

| 4  | The application space of modern CMOS technologies (Courtesy Dr. Kyutae Lim)                                                                                                                                                                                                                                                                                                              | 7  |

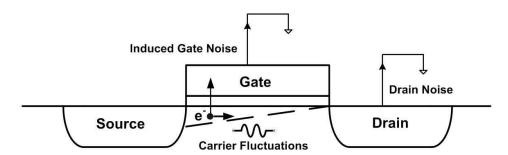

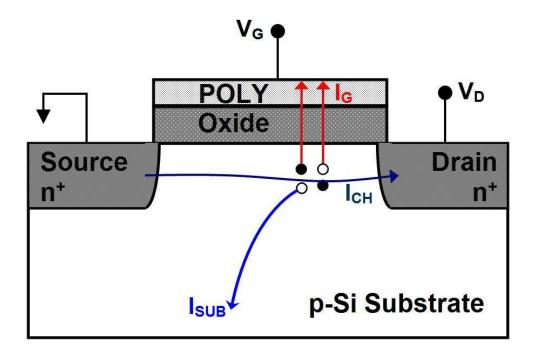

| 5  | Cross-section of a typical MOSFET illustrating the channel noise mechanism                                                                                                                                                                                                                                                                                                               | 11 |

| 6  | RF noise sources in a MOSFET                                                                                                                                                                                                                                                                                                                                                             | 13 |

| 7  | Dependence of noise figure on the source admittance                                                                                                                                                                                                                                                                                                                                      | 15 |

| 8  | Block diagram of the ATN-NP5B RF noise measurement system                                                                                                                                                                                                                                                                                                                                | 16 |

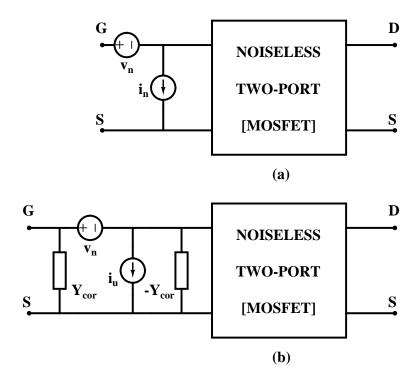

| 9  | (a) Noise equivalent circuit with correlated noise sources $(v_n \text{ and } i_n)$ at the input of the two-port. (b) Noise equivalent circuit with uncorrelated noise current source $i_u$ and noise voltage source $v_n$ , with a correlation admittance $Y_{cor}$                                                                                                                     | 19 |

| 10 | RF sub-circuit for small-signal and high-frequency noise modeling of a MOSFET                                                                                                                                                                                                                                                                                                            | 21 |

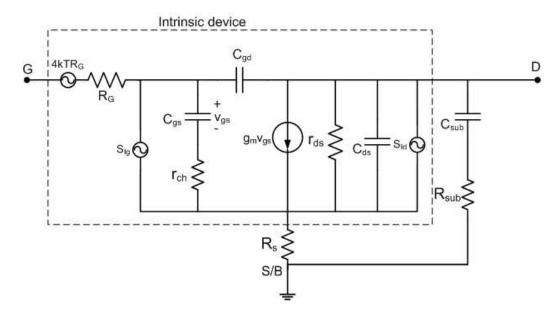

| 11 | Cut-off frequency $(f_T)$ and maximum oscillation frequency $(f_{max})$ versus drain current for an nFET with $W/L=8.0/0.12$ (32 fingers)                                                                                                                                                                                                                                                | 25 |

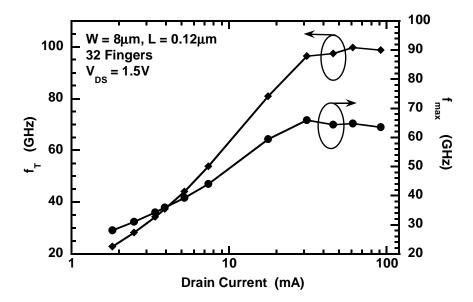

| 12 | (a) Measured and modeled real parts of $y_{11}$ and $y_{22}$ versus frequency, (b) Measured and modeled imaginary parts of $y_{11}$ and $y_{22}$ versus frequency, (c) Measured and modeled real parts of $y_{12}$ and $y_{21}$ versus frequency, (d) Measured and modeled imaginary parts of $y_{12}$ and $y_{21}$ versus frequency – for a nFET with $W/L=8.0/0.12$ (with 32 fingers). | 26 |

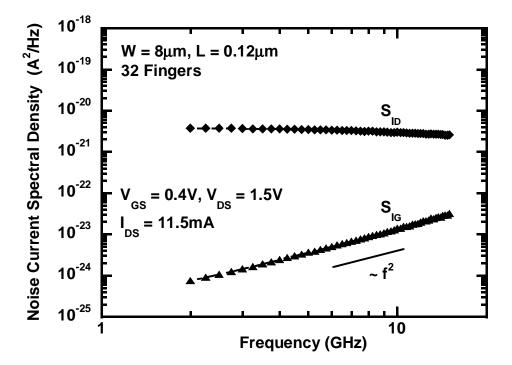

| 13 | Frequency dependence of channel thermal noise $(\overline{i_d^2})$ and gate current noise $(\overline{i_g^2})$ for an nFET with $W/L=8.0/0.12$ (32 fingers)                                                                                                                                                                                                                              | 27 |

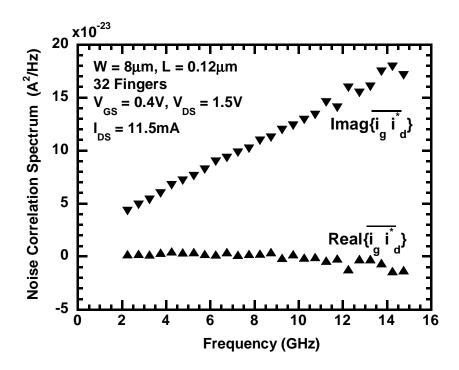

| 14 | Frequency dependence of real and imaginary part of the cross-correlation between channel thermal noise and induced gate noise – for a nFET with $W/L=8.0/0.12$ (with 32 fingers)                                                                                                                                                                                                         | 28 |

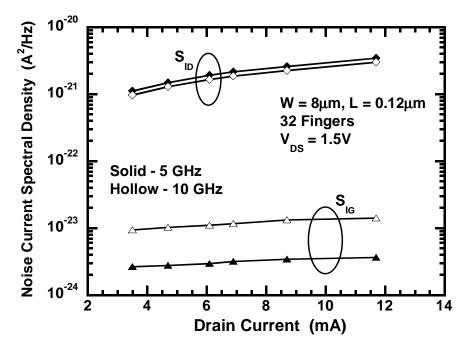

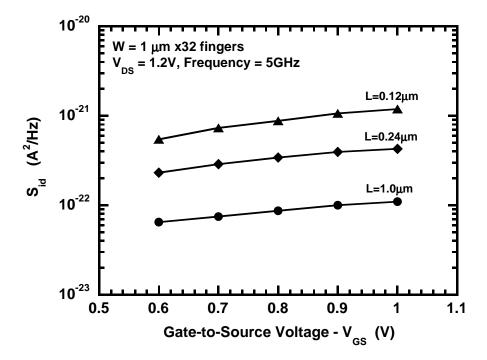

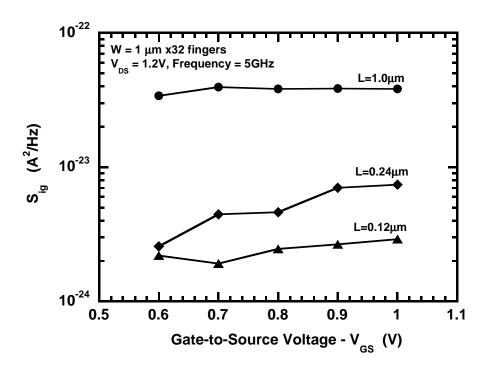

| 15 | Bias dependence of channel thermal noise $(\overline{i_d^2})$ and gate current noise $(\overline{i_d^2})$ for an nFET with $W/L = 8.0/0.12$ (32 fingers)                                                                                                                                                                                                                                 | 28 |

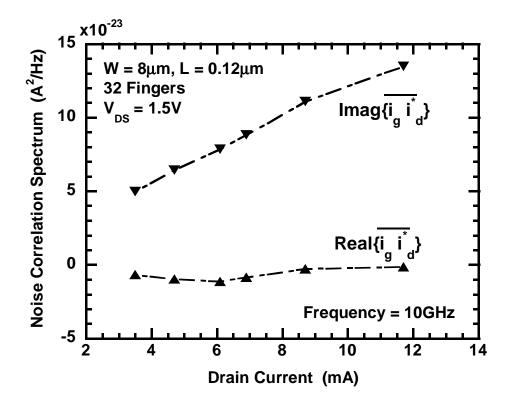

| 16 | Bias dependence of real and imaginary part of the cross-correlation between channel thermal noise and induced gate noise – for a nFET with $W/L = 8.0/0.12$ (with 32 fingers) | 29 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

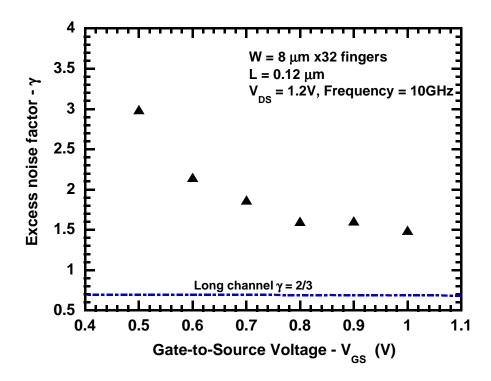

| 17 | Bias dependence of $\gamma$ for a nFET with $W/L=8.0/0.12$ (32 fingers)                                                                                                       | 30 |

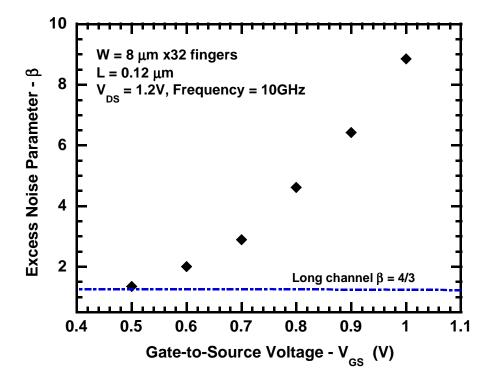

| 18 | Bias dependence of $\beta$ for a nFET with $W/L=8.0/0.12$ (32 fingers)                                                                                                        | 30 |

| 19 | Bias dependence of channel thermal noise $(\overline{i_d^2})$ for various gate lengths.                                                                                       | 31 |

| 20 | Bias dependence of induced gate noise $(\overline{i_g^2})$ for various gate lengths                                                                                           | 32 |

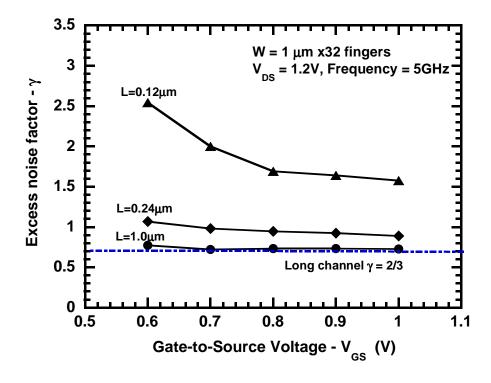

| 21 | Bias dependence of excess noise factor $\gamma$ for various gate lengths                                                                                                      | 32 |

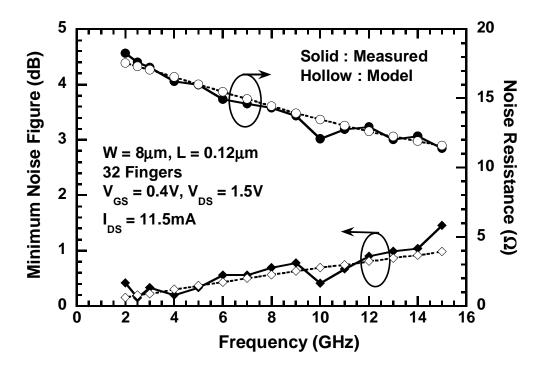

| 22 | Measured and modeled $NF_{min}$ and $R_n$ versus frequency – for an nFET with $W/L = 8.0/0.12$ (with 32 fingers)                                                              | 33 |

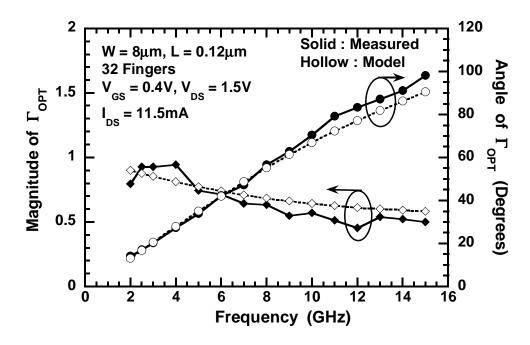

| 23 | Measured and modeled optimum source reflection coefficient ( $\Gamma_{opt}$ ) versus frequency – for an nFET with $W/L=8.0/0.12$ (with 32 fingers).                           | 34 |

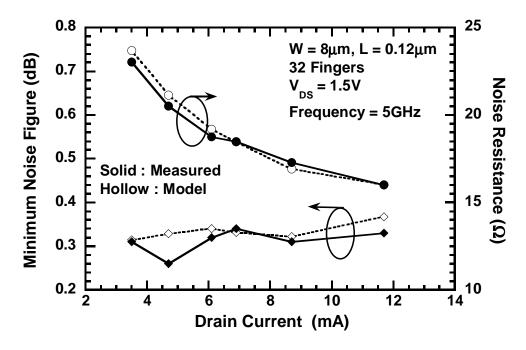

| 24 | Measured and modeled $NF_{min}$ and $R_n$ across bias - for an nFET with $W/L = 8.0/0.12$ (with 32 fingers)                                                                   | 34 |

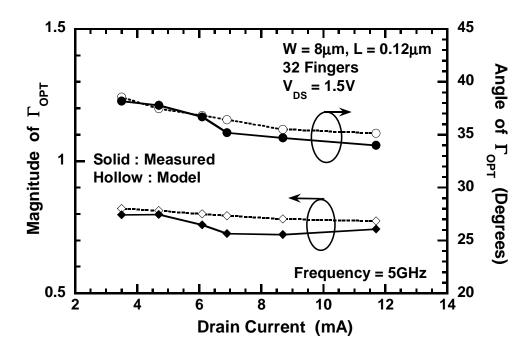

| 25 | Measured and modeled $\Gamma_{opt}$ across bias – for an nFET with $W/L = 8.0/0.12$ (with 32 fingers)                                                                         | 35 |

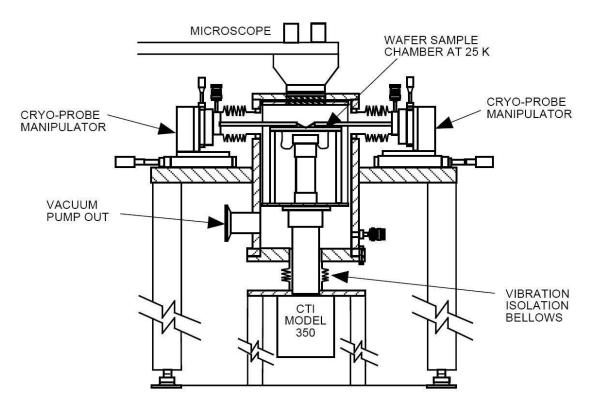

| 26 | Schematic view of the closed-cycle cryogenic probing system                                                                                                                   | 37 |

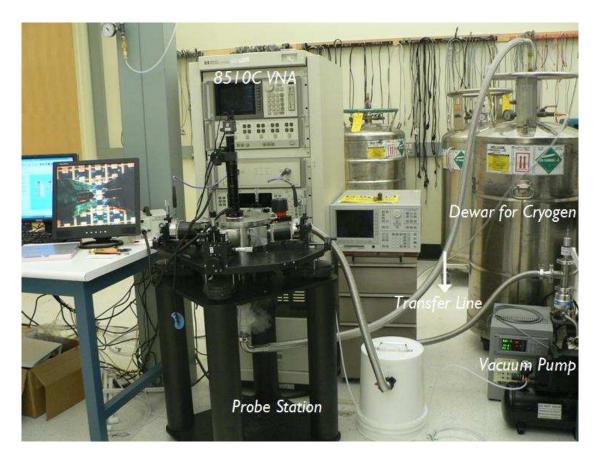

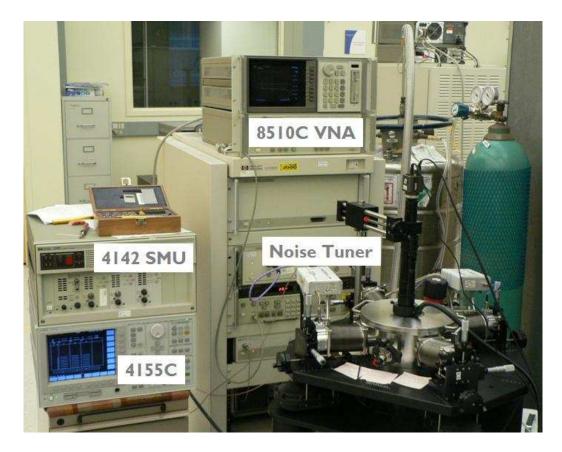

| 27 | Photograph of the open-cycle cryogenic probing system                                                                                                                         | 39 |

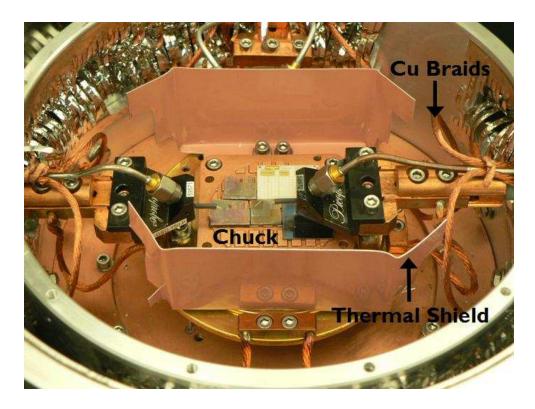

| 28 | View of the sample holder                                                                                                                                                     | 40 |

| 29 | Photograph of the cryogenic chamber connected to the VNA and noise tuners for on-wafer S-parameter and RF noise parameter measurements.                                       | 41 |

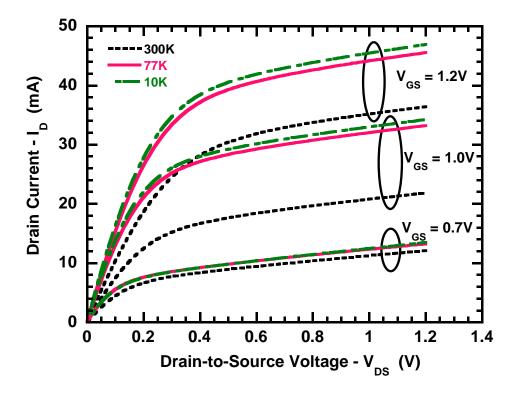

| 30 | Drain current as a function of drain-to-source voltage, at $300\mathrm{K}$ and $77\mathrm{K}$                                                                                 | 47 |

| 31 | Drain current as a function of gate-to-source voltage, at 300<br>K and $77\mathrm{K}$                                                                                         | 48 |

| 32 | Transconductance as a function of gate-to-source voltage at various temperatures                                                                                              | 49 |

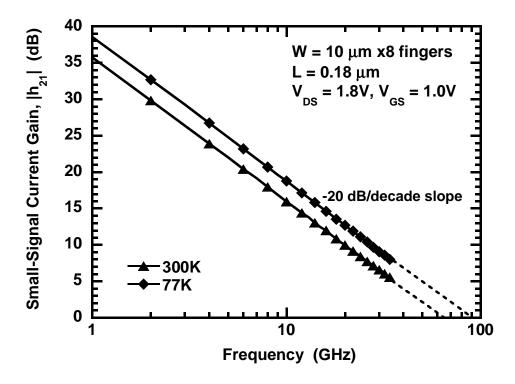

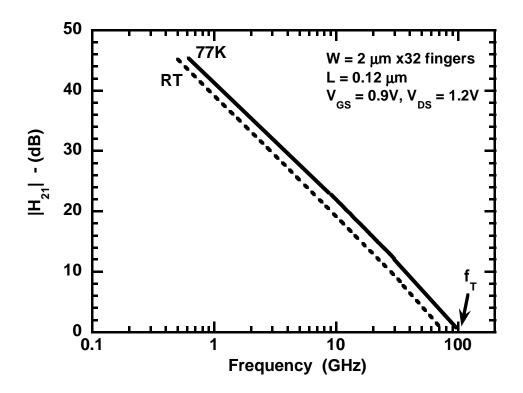

| 33 | Small-signal current gain as a function of frequency at 300K and 77K                                                                                                          | 50 |

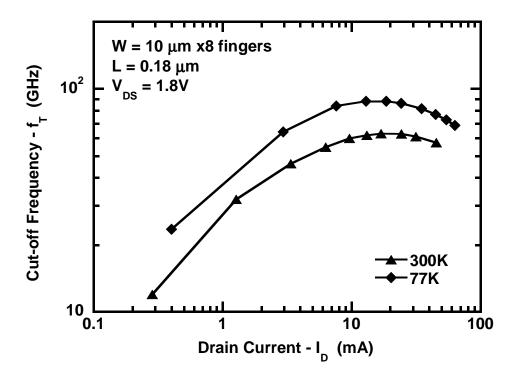

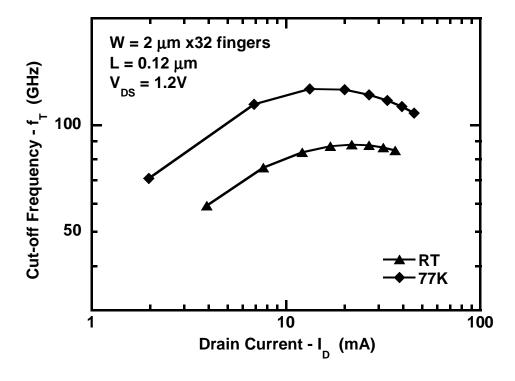

| 34 | Cut-off Frequency as a function of drain current at 300K and $77\mathrm{K}$                                                                                                   | 51 |

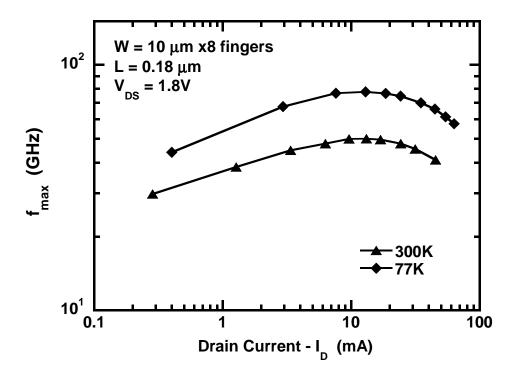

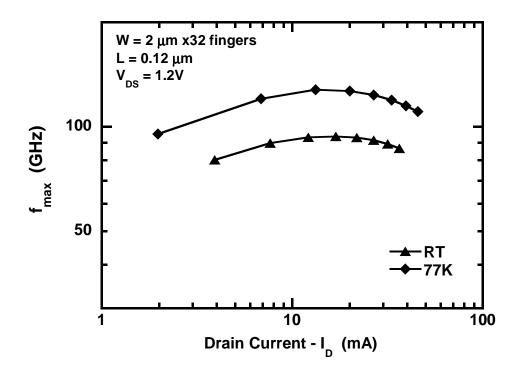

| 35 | Maximum Frequency of Oscillation as a function of drain current at 300K and 77K                                                                                               | 52 |

| 36 | Drain current as a function of drain-to-source voltage, at 300 K, 77 K, and 10 K                                                                                              | 53 |

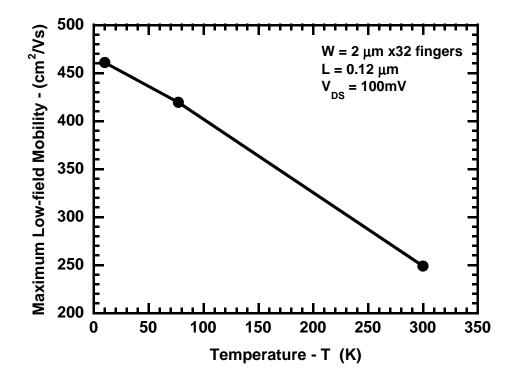

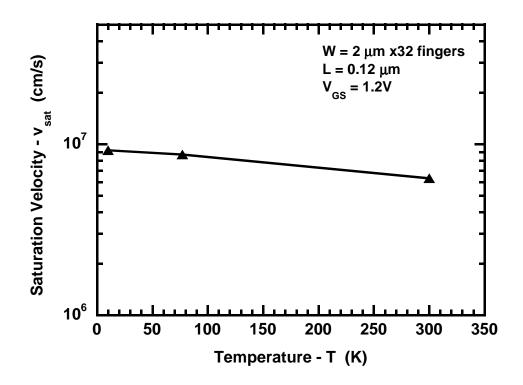

| 37 | Peak low-field mobility for the nFET as a function of temperature                                                                                                             | 54 |

| 38 | Saturation Velocity for the nFET as a function of temperature                                                                                                                 | 55 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

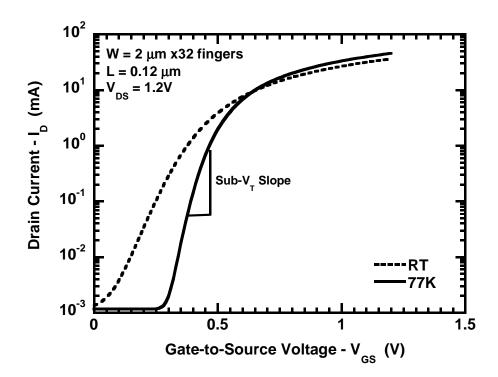

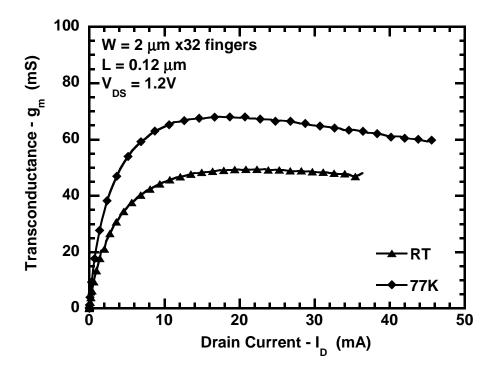

| 39 | Drain current as a function of gate-to-source voltage, at 300 K and 77 K                                                                                                      | 56 |

| 40 | Transconductance as a function of drain current at 300 K and 77 K                                                                                                             | 56 |

| 41 | Small-signal current gain as a function of frequency at 300 K and 77 K $$                                                                                                     | 58 |

| 42 | Cut-off Frequency as a function of drain current at 300 K and 77 K $$ .                                                                                                       | 58 |

| 43 | Maximum Frequency of Oscillation as a function of drain current at 300 K and 77 K                                                                                             | 59 |

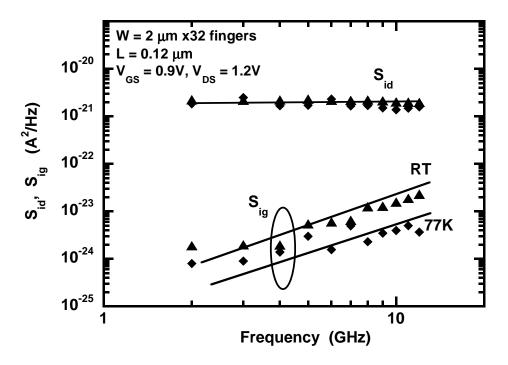

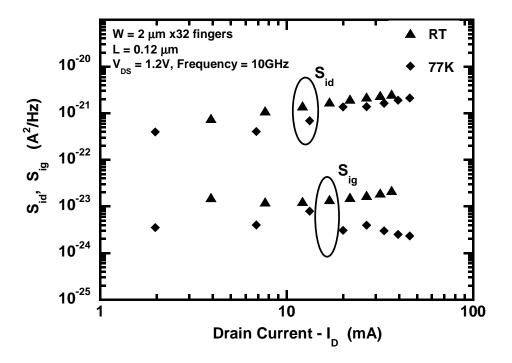

| 44 | Frequency dependence of channel thermal noise $(\overline{i_d^2})$ and gate current noise $(\overline{i_g^2})$ for an nFET with $W/L=2.0/0.12$ (32 fingers) at 300 K and 77 K | 60 |

| 45 | Bias dependence of channel thermal noise $(\overline{i_d^2})$ and induced gate noise $(\overline{i_g^2})$ for an nFET with $W/L=2.0/0.12$ (32 fingers) at 300 K and 77 K.     | 60 |

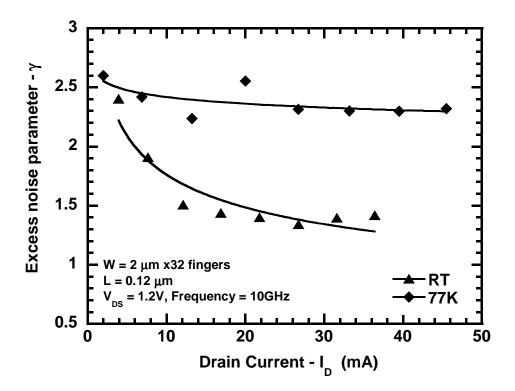

| 46 | Bias dependence of $\gamma$ for an nFET with $W/L=2.0/0.12$ (32 fingers) at 300 K and 77 K                                                                                    | 61 |

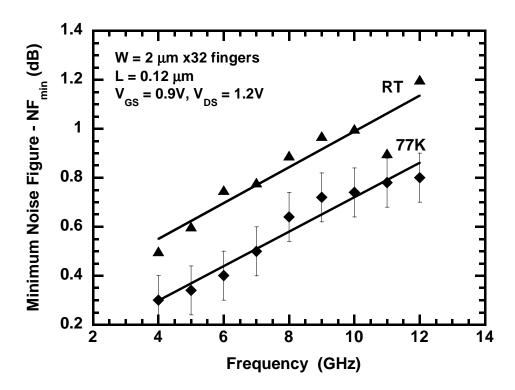

| 47 | Measured and modeled $NF_{min}$ versus frequency – for an nFET with $W/L=2.0/0.12$ (with 32 fingers) at 300 K and 77 K                                                        | 62 |

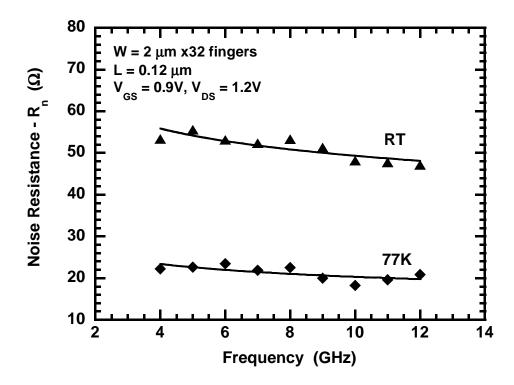

| 48 | Measured and modeled $R_n$ versus frequency – for an nFET with $W/L = 2.0/0.12$ (with 32 fingers) at 300 K and 77 K                                                           | 63 |

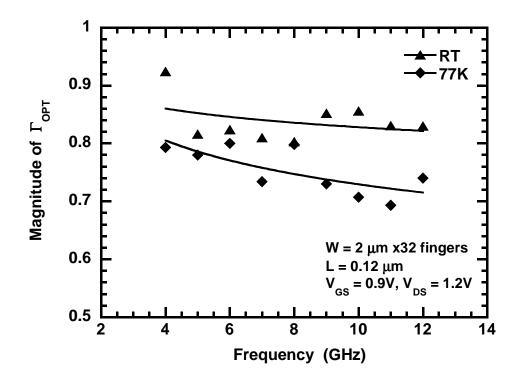

| 49 | Measured and modeled magnitude of $\Gamma_{opt}$ versus frequency – for an nFET with $W/L=2.0/0.12$ (with 32 fingers) at 300 K and 77 K                                       | 64 |

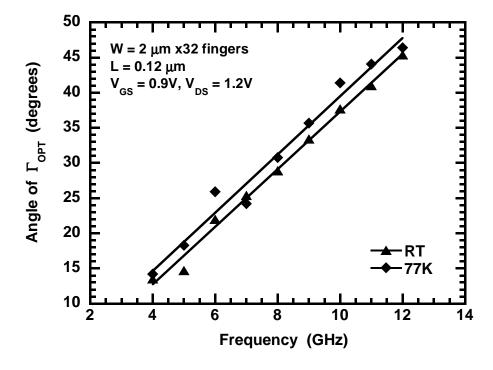

| 50 | Measured and modeled angle of $\Gamma_{opt}$ versus frequency – for an nFET with $W/L=2.0/0.12$ (with 32 fingers) at 300 K and 77 K                                           | 64 |

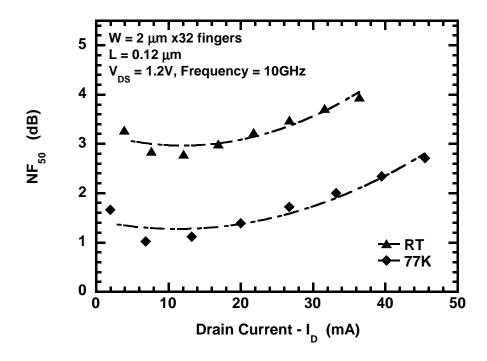

| 51 | Measured and modeled $NF_{50}$ versus drain current – for an nFET with $W/L=2.0/0.12$ (with 32 fingers) at 300 K and 77 K                                                     | 65 |

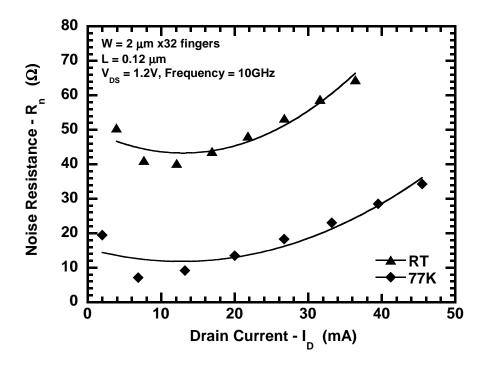

| 52 | Measured and modeled $R_n$ versus drain current – for an nFET with $W/L=2.0/0.12$ (with 32 fingers) at 300 K and 77 K                                                         | 65 |

| 53 | Hot-carrier injection mechanisms in MOSFETs                                                                                                                                   | 67 |

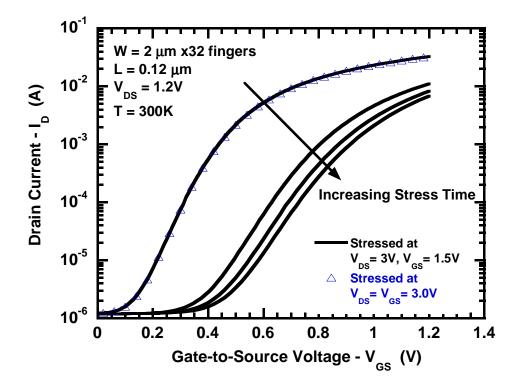

| 54 | Drain current versus gate-to-source voltage for increasing stress time at 300 K                                                                                               | 69 |

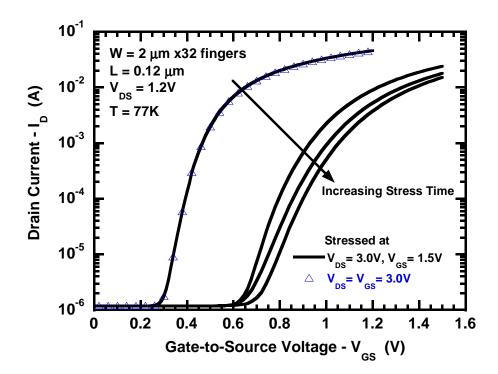

| 55 | Drain current versus gate-to-source voltage for increasing stress time at 77 K                                                                                                | 70 |

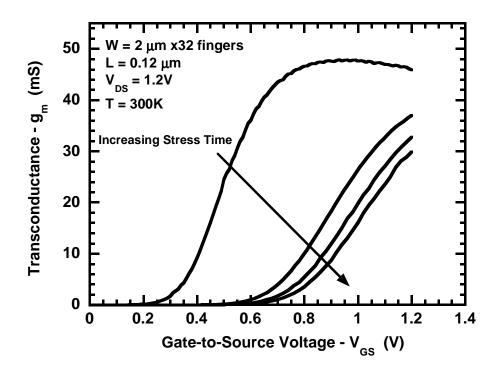

| 56 | Transconductance versus gate-to-source voltage for increasing stress time at 300 K                                                                                            | 71 |

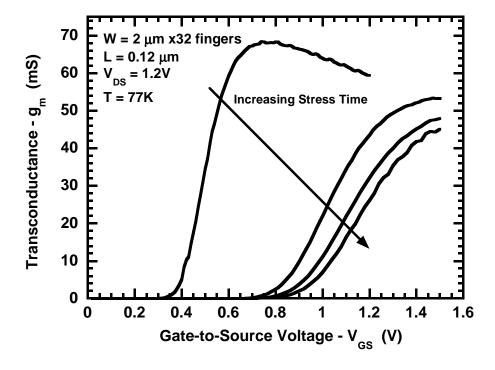

| 57 | Transconductance versus gate-to-source voltage for increasing stress time at 77 K                                                                                                                      | 71 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

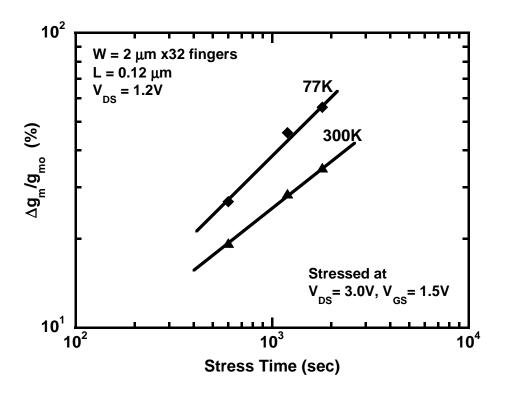

| 58 | Time-dependent transconductance degradation at 300 K and 77 K. $$ .                                                                                                                                    | 72 |

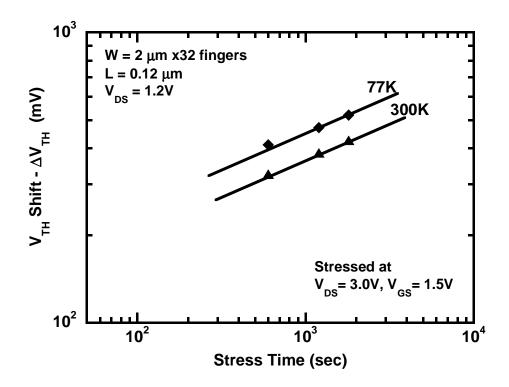

| 59 | Time-dependent threshold voltage shift at 300 K and 77 K                                                                                                                                               | 73 |

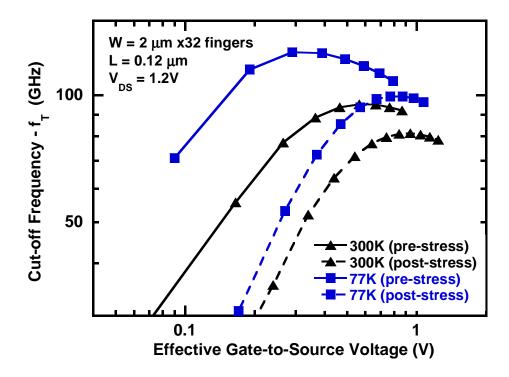

| 60 | $f_T$ versus gate-overdrive voltage $(V_{GS}-V_{TH})$ at 300 K and 77 K                                                                                                                                | 74 |

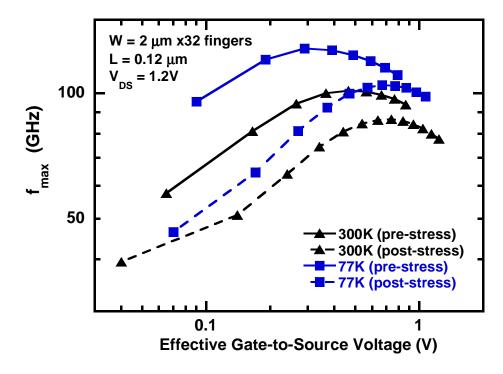

| 61 | $f_{max}$ versus gate-overdrive voltage $(V_{GS}-V_{TH})$ at 300 K and 77 K                                                                                                                            | 74 |

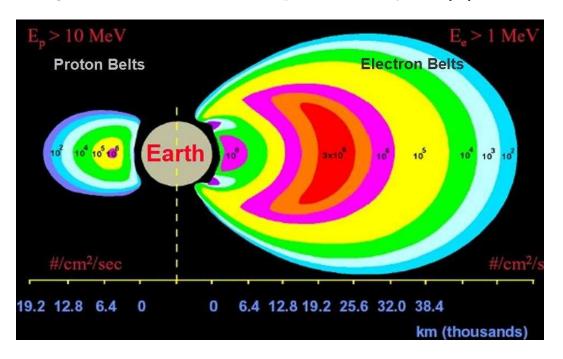

| 62 | Proton and electron belts surrounding the Earth                                                                                                                                                        | 76 |

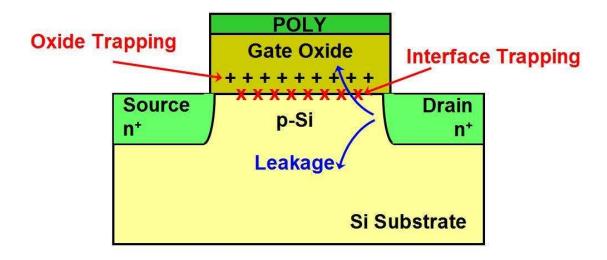

| 63 | Illustration of total dose effects in a MOSFET                                                                                                                                                         | 78 |

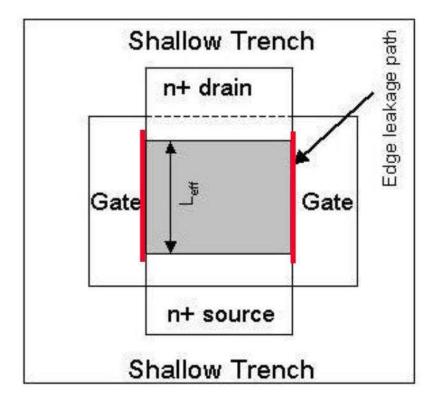

| 64 | Schematic top view of the STI edge leakage path in a MOSFET $$                                                                                                                                         | 78 |

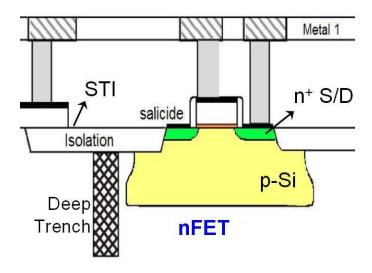

| 65 | Schematic cross-section of the nFET                                                                                                                                                                    | 80 |

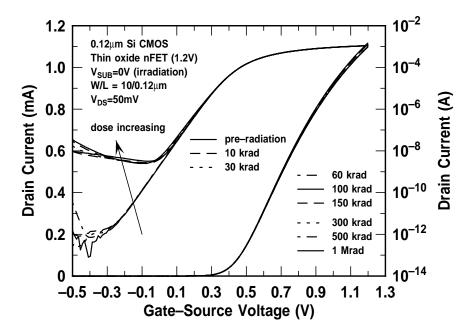

| 66 | Drain current as a function of gate-to-source voltage, before and after radiation for an nFET with $W/L=10.0~\mu m/0.12~\mu m.$                                                                        | 81 |

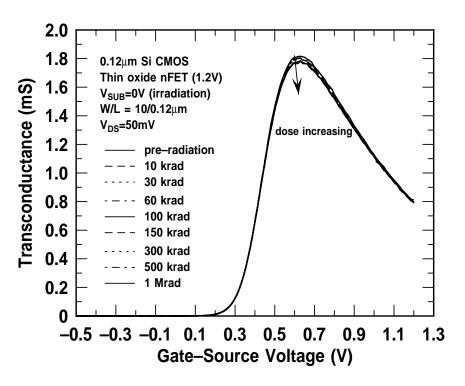

| 67 | Transconductance $(g_m)$ as a function of drain current, before and after radiation for an nFET with $W/L=10.0~\mu m/0.12~\mu m.$                                                                      | 83 |

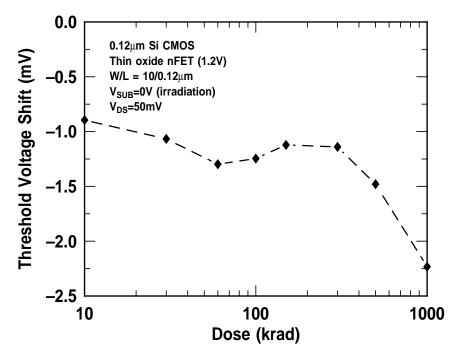

| 68 | The threshold voltage shift as a function of equivalent total dose for both the 10.0 $\mu m/0.12~\mu m$ nFETs                                                                                          | 83 |

| 69 | Drain noise current spectrum, before and after irradiation, for an nFET with $W/L=10.0~\mu m/0.12~\mu m$                                                                                               | 84 |

| 70 | (a) Magnitude of $S_{21}$ as a function of frequency, (b) Magnitude of $S_{11}$ and $S_{22}$ as a function of frequency - pre- and post- 1.0 Mrad, for an nFET with $W/L=2.0/0.12$ and 32 gate fingers | 86 |

| 71 | Cut-off frequency $f_T$ as a function of drain current, before and after irradiation, for an nFET with $W/L=2.0~\mu m/0.12~\mu m$ and 32 gate fingers                                                  | 87 |

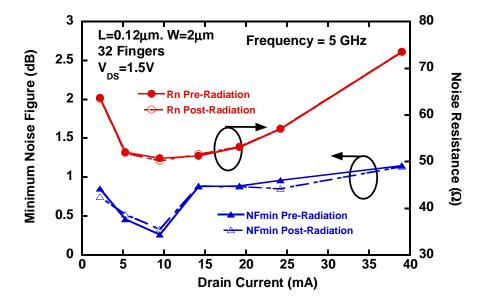

| 72 | Minimum Noise Figure and Noise Resistance as a function of frequency, before and after radiation, for a NMOS device with $W/L=2.0~\mu m/0.12~\mu m$ and 32 fingers                                     | 88 |

| 73 | Minimum Noise Figure and Noise Resistance at 5 GHz as a function of drain current, before and after irradiation, for an nFET with $W/L = 2.0 \ \mu m/0.12 \ \mu m$ and 32 gate fingers                 | 88 |

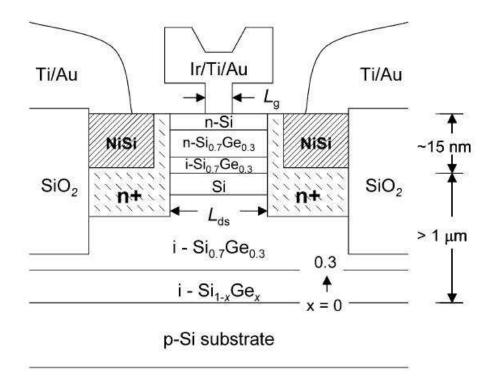

| 74 | Schematic cross-section of a Si-SiGe n-MODFET device structure                                                                                                                                         | 91 |

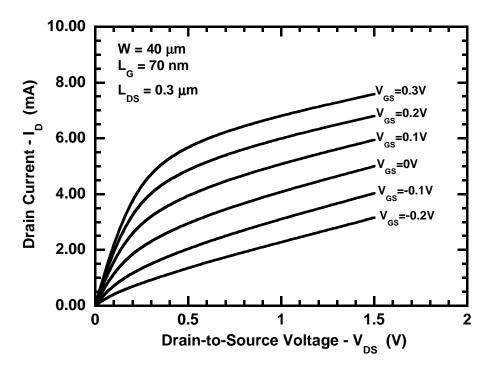

| 75 | Drain current versus drain-to-source voltage for an n-type SiGe MOD-FET with $L_g$ =70 $nm$ , $W_g$ = 40 $\mu m$                                                                                       | 92 |

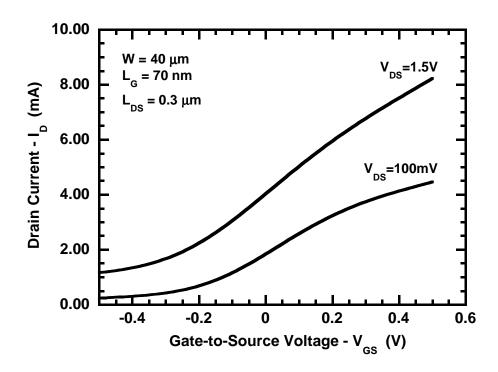

| 76 | Drain current versus gate-to-source voltage for an n-type SiGe MOD-<br>FET with $L_g$ =70 nm, $W_g = 40 \mu m$                                                                  | 93 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

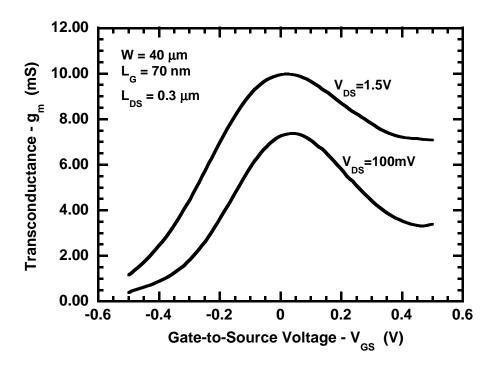

| 77 | Transconductance versus gate-to-source voltage for an n-type SiGe MODFET with $L_g$ =70 nm, $W_g$ = 40 $\mu m$                                                                  | 93 |

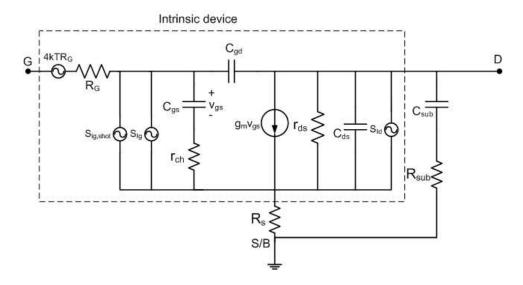

| 78 | Sub-circuit model for the small-signal AC and RF noise analysis of an n-MODFET                                                                                                  | 94 |

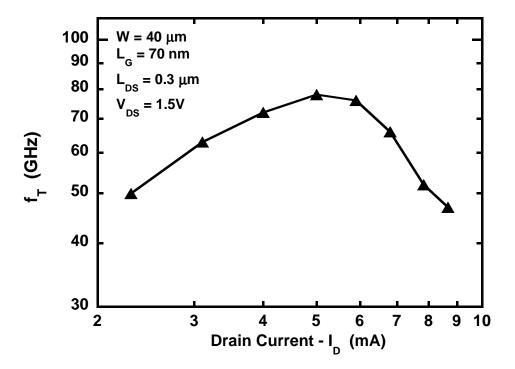

| 79 | Cut-off frequency versus drain current for an n-type SiGe MODFET with $L_g$ =70 $nm$ , $W_g$ = 40 $\mu m$                                                                       | 95 |

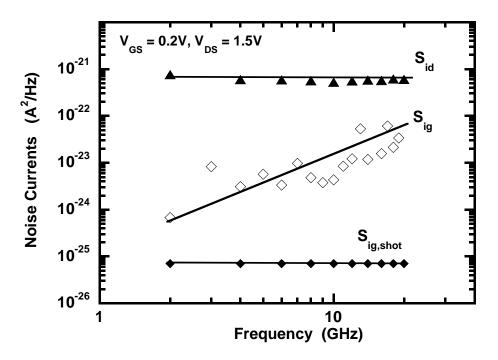

| 80 | Power spectral densities of the channel thermal noise, induced gate noise, and gate shot noise versus frequency for an n-type SiGe MOD-FET with $L_g$ =70 $nm$ , $W_g=40~\mu m$ | 96 |

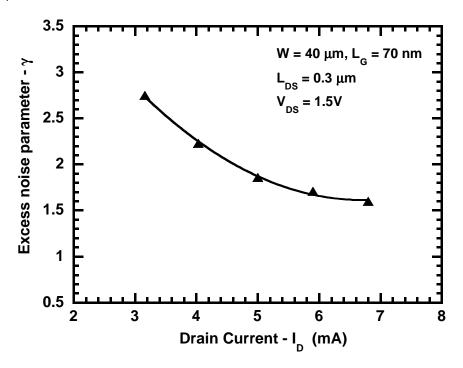

| 81 | Excess noise factor $\gamma$ versus drain current for an n-type SiGe MODFET with $L_g$ =70 $nm$ , $W_g$ = 40 $\mu m$                                                            | 96 |

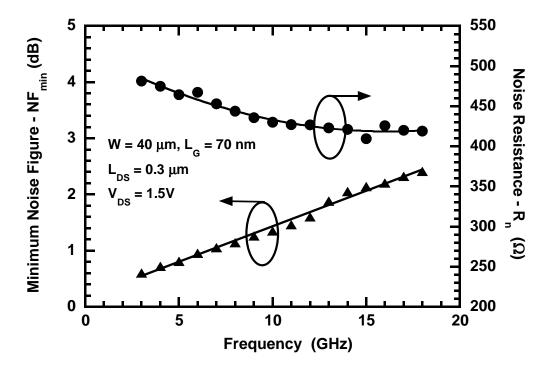

| 82 | $NF_{min}$ and $R_n$ versus frequency for an n-type SiGe MODFET with $L_g$ =70 $nm$ , $W_g=40~\mu m$                                                                            | 97 |

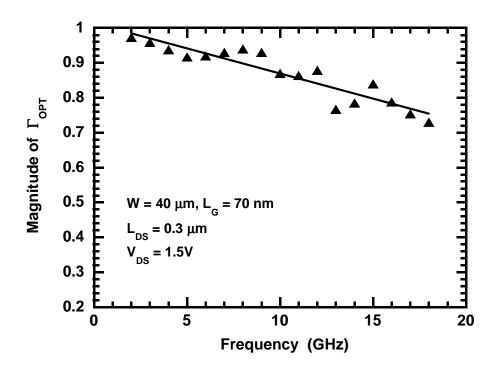

| 83 | Magnitude of $\Gamma_{opt}$ versus frequency for an n-type SiGe MODFET with $L_g$ =70 nm, $W_g=40~\mu m.$                                                                       | 98 |

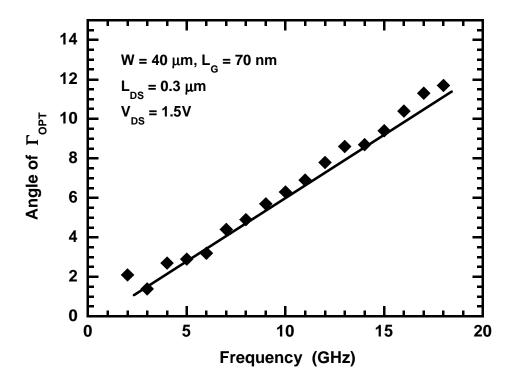

| 84 | Angle of $\Gamma_{opt}$ versus frequency for an n-type SiGe MODFET with $L_a=70~nm,~W_a=40~\mu m.$                                                                              | 98 |

#### **SUMMARY**

The objective of this work is to provide a comprehensive analysis of the small-signal and broadband noise performance of highly scaled silicon-based FETs, and develop high-frequency noise models for robust radio frequency circuit design. An analytical RF noise model is developed and implemented for scaled Si-CMOS devices, using a direct extraction procedure based on the linear two-port noise theory.

This research also focuses on investigating the applicability of modern CMOS technologies for extreme environment electronics. A thorough analysis of the DC, small-signal AC, and broadband noise performance of 0.18  $\mu m$  and 130 nm Si-CMOS devices operating at cryogenic temperatures is presented. The room temperature RF noise model is extended to model the high-frequency noise performance of scaled MOSFETs at temperatures down to 77 K and 10 K. Significant performance enhancement at cryogenic temperatures is demonstrated, indicating the suitability of scaled CMOS technologies for low temperature electronics. The hot-carrier reliability of MOSFETs at cryogenic temperatures is investigated and the worst-case gate voltage stress condition is determined. The degradation due to hot-carrier-induced interface-state creation is identified as the dominant degradation mechanism at room temperature down to 77 K. The effect of high-energy proton radiation on the DC, AC, and RF noise performance of 130 nm CMOS devices is studied. The performance degradation is studied up to an equivalent total dose of 1 Mrad, which represents the worst case condition for many earth-orbiting and planetary missions.

The geometric scaling of MOSFETs has been augmented by the introduction of novel FET designs, such as the Si/SiGe MODFETs. A comprehensive characterization and modeling of the small-signal and high-frequency noise performance of highly

scaled Si/SiGe n-MODFETs is presented. The effect of gate shot noise is incorporated in the broadband noise model. SiGe MODFETs offer the potential for high-speed and low-voltage operation at high frequencies and hence are attractive devices for future RF and mixed-signal applications.

This work advances the state-of-the-art in the understanding and analysis of the RF performance of highly scaled Si-CMOS devices as well as emerging technologies, such as Si/SiGe MODFETs. The key contribution of this dissertation is to provide a robust framework for the systematic characterization, analysis and modeling of the small-signal and RF noise performance of scaled Si-MOSFETs and Si/SiGe MODFETs both for mainstream and extreme-environment applications.

#### CHAPTER I

#### INTRODUCTION

#### 1.1 A Brief History of Radio

"Stay connected" is the motto of today's information age. Information interchange plays a pivotal role in our everyday life. Several technologies such as telephony, wireless and optical networks, internet, and satellite communication have revolutionized the way we communicate. The modern day world is built on a robust communication infrastructure that is inextricably linked to these technologies to facilitate the seamless exchange of information in the form of speech, text, data, images, audio, and video.

In 1844, Samuel F.B. Morse successfully demonstrated the first electrical communication over a long distance by transmitting a "dot-dash" message over a single wire that connected the entities involved in the information exchange. The development of the Morse code led to the establishment of telegraph systems. This was soon followed by the invention of telephone by Alexander Graham Bell, which made distant audio communication possible. Heinrich Hertz's experimental demonstration of the existence of electro-magnetic (EM) waves established the basis for wireless communication. However, it took several years for wireless technology to be deployed for long-distance communication. In 1901, Guglielmo Marconi successfully demonstrated the transatlantic transmission of wireless signals with the help of J.C. Bose's "mercury coherer with a telephone" detector. This revolutionary experiment ushered in the age of radio. These early systems employed spark-gap transmitters and detectors for low-frequency long-distance communication. The invention of vacuum tubes and

their application as receivers and sources of EM energy in transmitters was instrumental in the development of high-frequency and microwave radios [1]-[4]. Since their inception, microwave radio systems have undergone several significant improvements over the years. The invention of the point-contact transistor by John Bardeen, Walter Brattain, and William Shockley in 1947, followed by the development of commercial silicon (Si) transistors by Texas Instruments in 1954, coupled with the advances in information theory, have facilitated the realization of affordable mobile communication systems. Today, the wireless technology market spans some important existing and emerging applications, such as mobile telephony, wireless local area networks (WLAN), radio frequency identification systems (RFIDs), radar and remote sensing, medical electronics, and intelligent transportation systems. The Federal Communications Commission (FCC) was established to ensure the efficient and effective use of the radio spectrum for various applications. The need for ubiquitous access to information is constantly driving the next-generation wireless communication technologies and has created the need for using higher-frequency carrier waves with proportionally increased modulation bandwidths. The restricted band allocation by the FCC for various applications has made it necessary to transmit more information in a limited spectrum. The need for achieving higher data rates has necessitated the use of highly complex signal modulation and multiplexing schemes in modern communication systems, thereby placing a stringent requirement on the performance of devices and circuits used for building the next-generation wireless systems.

Performance, cost, size, power consumption, and time to market are the main factors that influence the choice of device technology for radio frequency (RF) circuits. In addition to these parameters, high-density integration capability is very desirable to build smaller and faster systems that are cost effective and efficient. Modern complementary metal-oxide-semiconductor (CMOS) technologies have emerged as a strong contender for building RF integrated circuits (ICs) for myriad of commercial

and niche applications.

### 1.2 Evolution of Silicon CMOS Technology and its Application Space

In 1930, Lilienfeld patented the idea of surface conductance modulation of a semiconductor by the application of an electric field. The fundamental concept of surface states and conductance modulation of a surface inversion layer was suggested by Bardeen and Brattain. The n-type surface inversion layer on p-type Si and the ptype surface inversion layer on an n-type germanium (Ge) were the principal reasons for the successful operation of the field-effect point-contact transistors invented by Bardeen and Brattain in 1947. However, early attempts to fabricate a field-effect transistor were not successful because of the presence of large densities of surface states, which shielded the surface potential from the influence of an external field. In 1960, Kahng and Attala successfully fabricated the first metal-oxide-semiconductor field-effect transistor (MOSFET) on a Si substrate with silicon dioxide  $(SiO_2)$  as the gate dielectric. Figure 1 shows the photograph of the first Si-MOSFET [5], [6]. A major breakthrough in the level of integration came in 1963 with the invention of CMOS technology by Wanlass and Sah [7]. Since then CMOS technology has played a pivotal role in the development of high-density ICs, such as memory modules, logic chips, and microprocessors.

In 1974, Robert Dennard, and his team from IBM proposed the concept of constant field scaling of MOSFETs and pointed out that scaling of supply voltages along with the lithographic dimensions could achieve improvements in speed, power, and component density [8]. Remarkable improvements in optical lithography and manufacturing technology, coupled with the ever increasing need for aggressive performance, have fueled the rapid scaling of CMOS technology. Over the past few decades, the minimum feature size (gate length) of MOSFETs has decreased exponentially from micrometers well into the nanometer regime. Figure 2 illustrates the

**Figure 1:** Photograph of the first Si-MOSFET fabricated by Kahng and Atalla in 1960.

scaling of gate lengths and operating voltages of CMOS technologies over the years [9]. The scaling of gate length and gate-oxide thickness  $(t_{ox})$  has led to an increase in the drive current and transconductance  $(g_m)$  of MOSFETs.

Traditionally, CMOS devices were considered suitable for digital and low-frequency analog applications. However, the rapid scaling of MOSFET gate lengths has resulted in a strong improvement in the RF performance of CMOS devices. The peak cut-off frequency  $(f_T)$  of state-of-the-art CMOS technologies is well over 100 GHz, thus enhancing the useful operating frequency range of scaled CMOS devices. Scaling also has a favorable impact on the broadband noise performance of MOSFETs. As shown in Fig. 3, the modern CMOS devices exhibit a peak- $f_T$  greater than 100 GHz and a sub-1.0 dB minimum noise figure  $(NF_{min})$ . The significant improvement in the RF performance coupled with the high levels of integration and cost effectiveness have made Si-CMOS the technology of choice for the development of RF ICs and system-on-chip (SOC) solutions for various wireless applications. Several foundries provide

Figure 2: Scaling of minimum gate-length and supply voltage  $(V_{DD})$  of CMOS technologies over the years.

**Figure 3:** Cut-off frequency  $(f_T)$  and minimum noise figure  $(NF_{min})$  versus gatelength.

high-performance RF CMOS technologies that include high gain RF CMOS devices along with passive components like inductors, varactors, and capacitors [10]–[16].

In addition to device scaling, technological innovations and novel integration approaches are being employed to enhance the performance of mainstream CMOS devices. Silicon germanium (SiGe) heterostructure technology using strained-Si and SiGe epi-layers has recently attracted substantial attention as it improves the performance of Si-based FETs by achieving higher carrier mobility and thereby opens up the possibility of employing SiGe modulation-doped FETs (MODFETs) for low-power RF applications. The need for superior performance has thus fostered active research in the field of Si-based FET device design and process optimization, high-frequency characterization and modeling of these devices, and circuit design for RF and microwave applications.

Today, Si-CMOS ICs and SOCs are widely used for several commercial applications that span both wireless and wired communication applications such as Bluetooth, IEEE 802.11 a/b/g WLANs, ultra-wideband (UWB) radios, synchronous optical networks (SONET), etc. Figure 4 shows the application space of modern CMOS technologies, that spans an entire gamut of wireless and wired communication applications and standards. In addition to the various commercial applications, there is an increasing interest in investigating the applicability of Si-CMOS devices for extreme-environment applications. Some of the important extreme-environment scenarios include operation at extreme temperatures and operation in a radiation-intense environment such as outer space. Extreme-environment electronics represents a class of important niche applications that spans deep-space electronics, radio astronomy, smart electronic systems for automobiles, semiconductor-superconductor hybrid systems, and high-sensitivity cooled sensors and detectors.

**Figure 4:** The application space of modern CMOS technologies (Courtesy Dr. Kyutae Lim).

#### 1.3 Scope of the Dissertation

The aggressive scaling of CMOS technologies has resulted in a significant improvement in the RF performance of MOS devices. Consequently, CMOS radio transceivers and SOCs have been deployed in various commercial wireless communication applications that used to be traditionally dominated by the III-V technologies such as gallium arsenide (GaAs) and indium phosphide (InP).

The development of robust RF CMOS SOCs presents a host of challenges in the high-frequency characterization, modeling, and circuit design using scaled MOSFETs. Broadband noise is one of the main concerns in the design of low-noise RF front-ends, as it has a direct impact on the sensitivity of the receiver chain. A thorough characterization and modeling of high-frequency noise in MOSFETs is a prerequisite for the development of low-noise CMOS RF ICs. This work contributes to the ongoing research efforts aimed at developing accurate broadband noise models for scaled CMOS devices. The dominant sources of high-frequency noise in a MOSFET are the

channel thermal noise, the induced gate noise, and the thermal noise generated by the gate resistance. Scaled CMOS devices exhibit a higher channel thermal noise compared to the long-channel MOSFETs, and this increase is captured by introducing a parameter called the excess noise coefficient. The bias and channel-length dependence of the excess noise coefficient is still actively debated in the current literature. Widely used MOS compact models, such as the Berkeley short-channel insulated-gate FET (IGFET) model (BSIM), ignore the bias dependence of the excess noise factor, thereby causing inaccuracies in modeling the channel thermal noise. In this work, a direct extraction technique is used to determine the device noise sources from the measured noise parameters using the "noisy two port" analysis. The extracted noise sources are incorporated in a sub-circuit-based RF noise model. The evolution of the noise sources is studied as a function of bias and frequency, thereby providing a comprehensive analysis of the broadband noise performance of scaled Si-MOSFETs. The measurement and modeling results are presented for an nFET from a commercially available 130 nm CMOS technology. The impressive RF performance of the state-ofthe-art Si-CMOS technologies also motivates the study of their performance in extreme environments in order to expand the application space of CMOS technologies to include these niche applications. This work encompasses a systematic investigation of the RF performance of scaled CMOS devices in two important extreme-environment scenarios, namely, 1) operation in a radiation-intense environment and 2) operation at cryogenic temperatures, down to liquid nitrogen (77K) and liquid helium (4K) temperatures. These conditions of operation are very relevant for electronic systems used in deep-space, radio astronomy, and high-precision instrumentation applications. This work is envisioned to provide a framework for the robust on-wafer RF characterization and modeling of scaled CMOS devices operating in the above-mentioned extreme-environment conditions. The room temperature noise model is extended to analyze the device noise performance at 77 K and 10 K. The hot-carrier reliability of these scaled CMOS devices is investigated at cryogenic temperatures using DC stress techniques.

The geometric scaling of MOSFETs has been augmented by the introduction of novel FET designs, such as the Si/SiGe MODFETs. SiGe MODFETs offer the potential for high-speed and low-power operation at high frequencies and hence are attractive devices for future RF and mixed-signal applications. This work presents a systematic analysis of the small-signal and broadband noise performance of SiGe MODFETs.

#### 1.4 Thesis Organization

The rest of the thesis is organized as follows:

Chapter 2 describes the fundamental high-frequency noise sources in MOSFETs and the basic concepts of noise figure and high-frequency noise parameters of a two-port device. The RF noise measurement system and methodology is described in detail.

Chapter 3 presents a technique for the direct extraction of the channel thermal noise, the induced gate noise, and the gate resistance thermal noise from measured RF noise parameters and scattering parameters (S-parameters). This technique is based on the linear two-port noise theory and can be applied to any two-port device. A sub-circuit-based RF noise model for MOSFETs is described, that is used to obtain the simulated noise parameters. The measurement and modeling results are presented for a 130 nm CMOS technology.

Chapter 4 discusses the operation of scaled CMOS devices at cryogenic temperatures, down to liquid nitrogen (77K) and liquid helium (4K) temperatures. The on-wafer cryogenic system is described in detail and the challenges of performing robust cryogenic measurements are outlined. A thorough DC, small-signal, and RF

noise characterization of 0.18  $\mu m$  and 130 nm MOSFETs is presented. The room temperature noise model is extended to investigate the behavior of device noise sources in the cryogenic regime. The hot-carrier reliability of scaled MOSFETs is studied at cryogenic temperatures using DC stress measurements. This is necessary for understanding the dominant failure mechanisms at low temperatures and also to determine the worst-case bias conditions for hot-carrier degradation.

Chapter 5 discusses the effect of proton radiation on the RF performance of scaled CMOS devices. The total dose effects in MOSFETs are studied and the experimental results are presented for a 130 nm nFET irradiated by 63.3 MeV protons.

Chapter 6 presents the small-signal and broadband noise performance of SiGe MODFETs to explore the applicability of these novel band-engineered FETs for the development of RF and microwave ICs.

Chapter 7 summarizes the contributions of this dissertation and discusses the future work that this thesis could motivate.

#### CHAPTER II

## FUNDAMENTALS OF NOISE AND HIGH-FREQUENCY NOISE MEASUREMENTS

In electronic systems, noise can be defined as any random interference unrelated to the signal of interest. The sensitivity of a communication system is limited by noise. The fundamental noise sources are inherent to the device or the system itself. This chapter describes the fundamental high-frequency noise sources in a MOSFET, and the measurement system and methodology used to characterize RF noise.

#### 2.1 High-Frequency Noise in Scaled MOSFETs

The fundamental noise mechanism in MOSFETs is the thermal noise of the conducting channel [17]. Figure 5 illustrates the channel noise mechanisms in a MOSFET. The channel thermal noise is the dominant noise source and is generated by the ran-

**Figure 5:** Cross-section of a typical MOSFET illustrating the channel noise mechanism.

dom thermal motion of charged carriers in the channel region at high frequencies. This channel thermal noise is detected at the drain terminal through the drain current fluctuation, and hence is also known as the drain current noise  $(\overline{i_d^2})$ . At high

frequencies, the channel thermal noise also manifests itself in the gate current spectrum owing to a significant capacitive coupling through the gate-oxide capacitance. This noise current is termed as the induced gate noise  $(\overline{i_g^2})$ . This induced gate noise is partially correlated with the drain channel noise, as they are generated by the same physical noise mechanism. Using Van der Ziel's theory [17], these noise sources can be expressed as

$$\overline{i_d^2} = 4kT\Delta f \ \gamma \ g_{do} \tag{1}$$

$$\overline{i_g^2} = 4kT\Delta f \ \beta \ \frac{\omega^2 C_{gs}^2}{5 \ g_{do}} \tag{2}$$

$$c = \frac{\overline{i_g} \, i_d^*}{\sqrt{\overline{i_d^2}} \sqrt{\overline{i_g^2}}} \tag{3}$$

where c is the correlation coefficient, and  $\gamma$  and  $\beta$  are the excess noise factor and excess gate noise factor. These factors are in general bias dependent.

For long-channel MOSFETs  $\gamma$  varies from 2/3 in the saturation region to 1 for the zero drain bias condition. The long-channel values for  $\beta$  and c are 4/3 and j0.395, respectively. The channel thermal noise is observed to increase in short-channel devices, hence causing an increase in the excess noise factor  $\gamma$  compared to the long-channel value of 2/3 [18]-[30]. Some earlier reports have indicated a significant increase (up to a factor of 4 or 5) in  $\gamma$  [18] -[21], and this excess channel noise was attributed to hot-electron effects and carrier heating. However, some recent reports show a moderate increase in  $\gamma$  [25] - [28] for short-channel MOSFETs. The  $\beta$  factor is also known to increase in shorter channel MOSFETs. The results reported in [22] suggest a significant enhancement (up to a factor of 30) in  $\beta$ , whereas a much smaller increase in  $\beta$  is reported in [25] and [26]. The precise amount of increase in  $\gamma$  and  $\beta$  and the mechanisms responsible for this excess noise is still actively debated in current literature. Evidently, large enhancements in  $\gamma$  and  $\beta$  would seriously limit the

use of MOS devices for low-noise RF IC design, and hence an extensive experimental study is required.

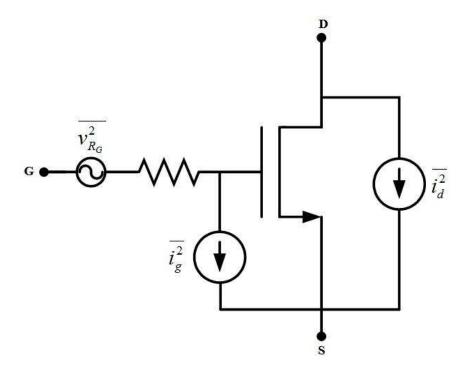

The other dominant noise source in short-channel MOSFETs is the thermal noise generated by the distributed gate resistance  $(R_G)$ . The important RF noise sources in a MOSFET are shown in Fig. 6. To determine  $R_G$ , the polysilicon sheet resistance

Figure 6: RF noise sources in a MOSFET

and the appropriate poly to silicide contact resistances have to be estimated [28]. The mean square thermal noise voltage generated by the gate resistance is given by,

$$\overline{v_{R_G}^2} = 4kTR_G\Delta f \tag{4}$$

The gate resistance thermal noise increases with scaling the gate-length and hence requires highly optimized device layouts. A good RF test structure employs multi-finger gate layout with narrow gate fingers and double-sided gate contacts. The distributed substrate resistance also contributes to the thermal noise of MOSFETs and can be minimized by placing a guard-ring around the device. It is also necessary

to place abundant contacts and vias at the source, drain, and gate terminals to minimize contact resistances.

In highly scaled MOSFETs with ultra-thin gate oxides, gate leakage current becomes very important owing to the direct tunneling of charge carriers through the gate dielectric. This gate leakage current gives rise to a shot noise component in the gate current, which is given by

$$\overline{i_{g,shot}^2} = 2qI_G \Delta f \tag{5}$$

where q is the electronic charge, and  $I_G$  is the DC gate current. The extraction of these noise sources from DC, high-frequency S-parameter, and noise parameter measurements is described in Chapter 3.

#### 2.2 Noise Figure and Noise Parameters

Noise figure (NF) or the noise factor (F) is widely used as a measure of the noise performance of a system. The noise figure of a network is defined as the ratio of the signal-to-noise power ratio (SNR) at the input to the signal-to-noise power ratio at the output. The noise factor is expressed as

$$F = \frac{(SNR)_{in}}{(SNR)_{out}} \tag{6}$$

and the noise figure is expressed in dB.

$$NF = 10 \log_{10} F \ dB \tag{7}$$

Thus the NF represents the degradation in the SNR as the signal passes through a system.

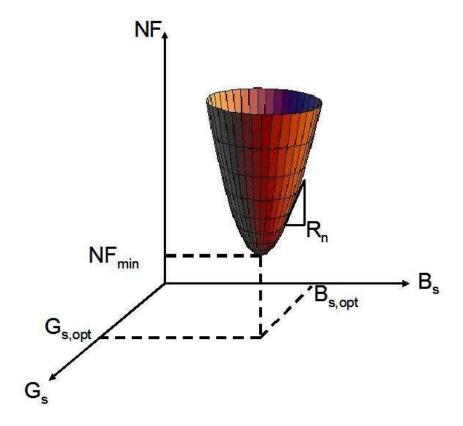

The noise figure is generally affected by two factors, the intrinsic noise sources of the system and the source (input) admittance driving the system. As shown in Fig. 7, the noisefactor of a linear system exhibits a parabolic dependence on the source admittance  $(Y_s = G_s + jB_s)$  at a single frequency point, and can be expressed as:

Figure 7: Dependence of noise figure on the source admittance

$$F = F_{min} + \frac{R_n}{G_s} |Y_s - Y_{opt}|^2 \tag{8}$$

Thus, the noise performance of any two-port network can be completely characterized by four noise parameters, namely minimum noise figure (or noise factor)  $F_{min}$ , noise resistance  $R_n$ , and the optimum source admittance  $Y_{opt}$  (=  $G_{opt} + jB_{opt}$ ).  $Y_{opt}$  is the optimum source admittance at which the minimum noise figure  $F_{min}$  of the system is achieved.  $R_n$  determines the sensitivity of the noise figure of the system to the variations in the source admittance from the optimum condition. These four noise parameters are very widely used in RF circuit design and are closely related to the intrinsic device noise sources.

#### 2.3 RF Noise Measurements

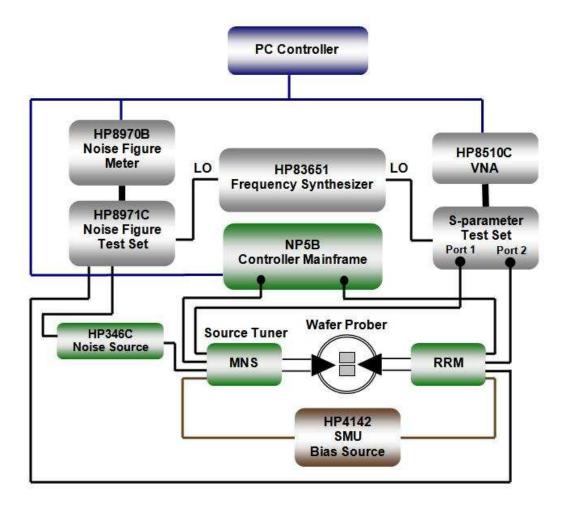

A block diagram of the RF noise measurement system is shown in Fig. 8. For the broadband noise measurements, the ATN-NP5B system is used in conjunction with

an HP8510C vector network analyzer (VNA), an HP8970B noise figure meter and a microwave probe station. The system uses a "multiple source impedance" technique

Figure 8: Block diagram of the ATN-NP5B RF noise measurement system

proposed by Adamian and Uhlir to extract the four noise parameters of the device under test (DUT) [31], [32]. The noise figure of the DUT is measured for various source admittances, and the four noise parameters are extracted using a least-square fit algorithm. The ATN-NP5B noise measurement system consists of a mismatched noise source (MNS), a remote receiver module (RRM), and a mainframe controller unit. The MNS contains a solid-state tuner that presents the DUT with multiple source admittances. The RRM contains a low-noise amplifier that is intended to lower the system noise figure, thereby reducing the measurement uncertainty. The

MNS and RRM have built-in bias tees and can be connected to an external bias source. This system allows the measurement of the four noise parameters from 2 GHz to 26.5 GHz. The system must be calibrated before performing the DUT noise characterization in order to account for the losses due to the cables, connectors, and probes, and thereby define a device reference plane. After calibration, the total noise figure of the system  $(F_{SYS})$  is measured for various source admittances and the noise figure of the DUT can be extracted using the Friis chain equation:

$$F_{DUT} = F_{SYS} - \frac{F_{REC} - 1}{G_{DUT}} \tag{9}$$

where,  $G_{DUT}$  is the available gain of the DUT calculated from the DUT S-parameters and the source reflection coefficient, and  $F_{REC}$  is the noise factor of the receiver chain that is known from the calibration data. The four noise parameters of the DUT can be determined by measuring the  $F_{DUT}$  for various source admittances.

#### CHAPTER III

### BROADBAND NOISE ANALYSIS AND MODELING OF HIGHLY SCALED MOSFETS

The dominant high-frequency noise sources in scaled MOSFETs have been enumerated in section 2.1. The development of accurate small-signal and noise equivalent circuits for MOSFETs necessitates a clear understanding of the device noise mechanisms along with a complete characterization of the device in terms of S-parameters and high-frequency noise parameters. A comprehensive analysis of the intrinsic broadband noise sources in state-of-the-art 130 nm nMOSFETs is presented in this chapter. A direct extraction procedure based on the two-port noise theory is used for obtaining the channel thermal noise, induced gate noise, and their cross-correlation from the measured S-parameters and RF noise parameters. A sub-circuit based RF noise model has been used that incorporates the channel thermal noise, the induced gate noise, and the thermal noise contribution from the gate resistance. This sub-circuit based RF noise model is used to obtain the simulated noise parameters: minimum noise figure  $NF_{min}$ , noise resistance  $R_n$ , and optimum source reflection coefficient  $\Gamma_{opt}$ .

#### 3.1 Two-Port Noise Theory

From the theory of of linear noisy two-port networks [33]–[35], all the noise generated by a two-port device can be represented by its noise-less counterpart and two inputreferred noise sources. Figure 9 (a) shows the noise equivalent circuit of a MOSFET with an input-referred voltage noise generator  $v_n$  and an input-referred current noise generator  $i_n$ . These intrinsic noise generators  $v_n$  and  $i_n$  can be derived from the chain or ABCD small-signal representation of the two-port network. These noise sources are, in general, correlated. By introducing a correlation admittance  $Y_{cor}$ , we have two independent noise sources  $v_n$  and  $i_u$  at the input of the two-port device, as shown in Fig. 9 (b). In this representation of the noisy two-port,

**Figure 9:** (a) Noise equivalent circuit with correlated noise sources  $(v_n \text{ and } i_n)$  at the input of the two-port. (b) Noise equivalent circuit with uncorrelated noise current source  $i_u$  and noise voltage source  $v_n$ , with a correlation admittance  $Y_{cor}$ .

$$i_n = i_u + Y_{cor} \ v_n \tag{10}$$

$$\overline{v_n^2} = 4kT\Delta f R_n \tag{11}$$

$$\overline{i_u^2} = 4kT\Delta f G_n \tag{12}$$

The four independent noise generators  $R_n$ ,  $G_n$ , and  $Y_{cor}$  (real and imaginary part) completely characterize the noise performance of a two-port device. These noise generators represent the input-referred noise sources of the device, and hence can be

directly expressed in terms of the intrinsic device noise sources. For establishing a valid noise model, these fundamental noise generators have to be determined from the measured RF noise parameters, namely,  $F_{min}$ ,  $R_n$ , and  $Y_{opt}$ .

The intrinsic noise generators  $(R_n, G_n \text{ and } Y_{cor})$  can be obtained from the measured noise parameters  $(F_{min}, R_n \text{ and } Y_{opt})$  using the noise correlation matrix representation of a two-port device [36]. The noise correlation matrix of a two-port device can be written as

$$\mathbf{C_{A}} = 2kT \begin{bmatrix} R_{n} & \frac{F_{min} - 1}{2} - R_{n}Y_{opt}^{*} \\ \frac{F_{min} - 1}{2} - R_{n}Y_{opt} & R_{n}|Y_{opt}|^{2} \end{bmatrix}$$

$$= \frac{1}{\Delta f} \begin{cases} \langle v_{n} \ v_{n}^{*} \rangle & \langle v_{n} \ i_{n}^{*} \rangle \\ \langle i_{n} \ v_{n}^{*} \rangle & \langle i_{n} \ i_{n}^{*} \rangle \end{cases}$$

(13)

From 13, we can write the intrinsic noise generators in terms of the measured noise parameters as follows:

$$R_n = \frac{\overline{v_n^2}}{4kT\Delta f} = R_n \ (measured) \tag{14}$$

$$G_n = \frac{\overline{i_u^2}}{4kT\Delta f} = G_{opt}(F_{min} - 1) - \frac{(F_{min} - 1)^2}{4R_n}$$

(15)

$$Y_{cor} = \frac{\overline{v_n \ i_n^*}}{\overline{v_n^2}} = \frac{F_{min} - 1}{2R_n} - Y_{opt}$$

$$\tag{16}$$

The intrinsic noise sources of a MOSFET can be extracted from these fundamental noise generators using the procedure outlined in the next section.

#### 3.2 Direct Extraction of the Noise Sources of a MOSFET

Figure 10 shows the RF sub-circuit of an nFET with the intrinsic device noise sources. This sub-circuit model is used for the small-signal and RF noise modeling of

the nFET. Here,  $r_{ch}$  is the channel charging resistance,  $R_G$  is the gate resistance,  $g_m$

**Figure 10:** RF sub-circuit for small-signal and high-frequency noise modeling of a MOSFET.

is the transconductance,  $1/r_{ds}$  is the channel conductance, and  $C_{gs}$ ,  $C_{gd}$ , and  $C_{ds}$  are the gate-to-source, gate-to-drain, and drain-to-source capacitance, respectively. The  $r_{ch}$  is a non-quasistatic parameter and is usually inversely proportional to the channel conductance  $(g_{do})$ . The gate resistance  $R_G$  consists of two components, namely the polysilicon sheet resistance and the contact resistance between silicide and polysilicon. The  $R_G$ , for a single side gate contact, can thus be given by

$$R_G = \frac{\rho_{poly}}{3} \frac{W}{L} \frac{1}{N_f} + R_{con} \tag{17}$$

where,  $\rho_{poly}$  is the sheet resistance of polysilicon, L is the gate-length, W is the width of each gate finger, and  $N_f$  is the number of gate fingers. The elements of the small-signal equivalent circuit in Fig. (10) were extracted from the measured and de-embedded Y-parameters of the device [11], [37] – [39].

The Van der Ziel's long-channel model for channel thermal noise  $(\overline{i_d^2})$ , induced gate noise  $(\overline{i_g^2})$ , and their correlation (c) are given by equations (1)-(3). As described in section 2.1, the excess drain noise coefficient  $\gamma$  increases from its long-channel

value (of 2/3) for deep sub-micron MOSFETs. The gate-resistance thermal noise  $(v_{R_G}^2)$ , given by (4), also plays a very important role in the noise behavior of shortchannel MOSFETs. Hence, modeling the  $\gamma$  parameter and the gate-resistance thermal noise are very essential for scaled MOSFETs. The thermal noise models in BSIM3 and BSIM4 compact models are based on Van der Ziel's MOSFET noise model. However, in the BSIM3v3 model, there are no independent parameters that can be used to fit the simulated noise parameters to the measured data. Also, BSIM3v3 does not model the induced gate noise and the gate resistance thermal noise, and hence under-predicts the  $F_{min}$  and  $R_n$  of the device. BSIM4 model has introduced more parameters to model the channel thermal noise in short-channel MOSFETs. However, the parameter NTNOI, that models the excess noise is a fixed parameter and hence does not capture the bias dependence of the  $\gamma$  parameter. To build a broadband noise model, it is necessary to accurately extract the intrinsic noise sources directly from the measured data and build a RF sub-circuit model that would be usable for RF circuit design. The direct extraction procedure described below is a generic approach and can be applied to any two-port device.

The channel thermal noise, the induced gate noise, and the gate-resistance thermal noise are the dominant intrinsic noise sources of a MOSFET, as shown in fig. 10. As described in section 3.1, these noise sources can be represented by an equivalent voltage  $(v_n)$  and current  $(i_n)$  noise generator at the input of the MOSFET. Using the representation shown in fig. 9,  $i_n$  can be split into two components, one that is correlated with  $v_n$   $(i_c)$ , and one that is uncorrelated  $(i_u)$ . Thus,  $i_n$  can be expressed as

$$i_n = i_u + i_c = i_u + v_n Y_{cor}$$

(18)

The Y-parameters of the MOSFET are used for the transformation of the intrinsic noise sources of the MOSFET to the  $v_n$ - $i_n$  representation. From the sub-circuit model

(in fig. 10), we can write

$$v_n = v_{R_G} + \frac{i_d}{Y_{21}} \tag{19}$$

$$i_n = i_g - \frac{Y_{11}}{Y_{21}} i_d \tag{20}$$

The induced gate noise  $i_g$  is partially correlated with the channel thermal noise  $i_d$ , and hence can be written as

$$i_q = i_{qu} + i_{qc} \tag{21}$$

where  $i_{gc}$  is correlated with  $i_d$ . Therefore, from equations (18), (20), and (21),  $i_n$  can be written as

$$i_n = i_{gu} + i_{gc} - \frac{Y_{11}}{Y_{21}} i_d$$

(22)

The intrinsic noise generators  $R_n$ ,  $G_n$ , and  $Y_{cor}$  can be evaluated from the measured RF noise parameters  $F_{min}$ ,  $R_n$ , and  $Y_{opt}$  as described in equations (14)-(16). These intrinsic noise generators essentially describe the noise power spectral densities  $\overline{v_n^2}$  and  $\overline{i_n^2}$ , which are directly related to the device noise sources. The  $\overline{v_n^2}$  and  $\overline{i_n^2}$  are given as

$$\overline{v_n^2} = \overline{v_{R_G}^2} + \frac{\overline{i_d^2}}{|Y_{21}|^2} = 4kT_o \, \Delta f R_n$$

(23)

$$\overline{i_n^2} = \overline{i_{gu}^2} + |Y_{cor}|^2 \overline{v_n^2} = 4kT_o \Delta f \left[ G_n + |Y_{cor}|^2 R_n \right]$$

(24)

Using this formulation, the power spectral densities of the channel thermal noise, induced gate noise, and their cross-correlation can be extracted as follows:

$$\frac{\overline{i_d^2}}{\Delta f} = 4kT_o (R_n - R_G) |Y_{21}|^2$$

(25)

$$\frac{\overline{i_g^2}}{\Delta f} = 4kT_o R_n \left\{ |Y_{opt}|^2 - |Y_{11}|^2 + 2\Re \left[ \left( \left( 1 - \frac{R_G}{R_n} \right) Y_{11} - Y_{cor} \right) Y_{11}^* \right] + \frac{R_G}{R_n} |Y_{11}|^2 \right\} (26)$$

$$\frac{\overline{i_g \ i_d^*}}{\Delta f} = 4kT_o \ R_n \ \left\{ \left[ \left( 1 - \frac{R_G}{R_n} \right) Y_{11} - Y_{cor} \right] Y_{21}^* \right\}$$

(27)

Using Van der Ziel's formulation (1) and equation (25), the excess noise coefficient  $\gamma$  can be expressed as

$$\gamma = \frac{(R_n - R_G)|Y_{21}|^2}{g_{do}} \tag{28}$$

The  $\beta$  factor can be extracted from equations (2) and (26).

Hence, the intrinsic device noise sources are extracted directly from the measured S-parameters and broadband noise parameters. The calculated noise sources are applied to the sub-circuit shown in Fig. 10 to obtain the simulated RF noise parameters  $-NF_{min}$ ,  $R_n$ , and  $\Gamma_{opt}$ .

## 3.3 Broadband Noise Modeling of 130 nm nFETs

The direct extraction method was applied to an nFET from a 130 nm CMOS technology. The measurement and modeling results are presented in this section [40].

#### 3.3.1 Device Technology and Experiments

The MOSFETs used in this study are contained in a fully integrated, commercially available 0.13  $\mu m$  CMOS technology [41], [42]. The DUTs used for our analysis are nFETs with a W/L of  $8.0\mu m/0.12\mu m$  (with 32 gate fingers). Figure 11 shows the the high-frequency figures-of-merit, the cut-off frequency  $(f_T)$ , and maximum frequency of oscillation  $(f_{max})$  of this device, as a function of the drain current. This nFET exhibits a peak  $f_T$  of about 100 GHz and  $f_{max}$  over 50 GHz. The S-parameters were measured

Figure 11: Cut-off frequency  $(f_T)$  and maximum oscillation frequency  $(f_{max})$  versus drain current for an nFET with W/L = 8.0/0.12 (32 fingers).

using an Agilent 8510C VNA. The conventional "Open-Short" de-embedding technique was performed on the raw S-parameters of the devices to eliminate the effects of pad parasitics. The high-frequency noise parameters were measured from 2 GHz to 26 GHz using the ATN NP5B noise measurement system, as described in section 2.3. The noise parameters were de-embedded using the generalized two-port noise de-embedding procedure [43].

#### 3.3.2 Results and Discussion

The de-embedded Y-parameters of the DUT were used to compute the elements of the small-signal sub-circuit model shown in fig. 10. The modeled Y-parameters show a very good agreement with the measured data, as shown in fig. 12. The small-signal parameters of the DUT at a representative bias point are enumerated in Table 1.

**Figure 12:** (a) Measured and modeled real parts of  $y_{11}$  and  $y_{22}$  versus frequency, (b) Measured and modeled imaginary parts of  $y_{11}$  and  $y_{22}$  versus frequency, (c) Measured and modeled real parts of  $y_{12}$  and  $y_{21}$  versus frequency, (d) Measured and modeled imaginary parts of  $y_{12}$  and  $y_{21}$  versus frequency – for a nFET with W/L = 8.0/0.12 (with 32 fingers).

**Table 1:** Small-signal Parameters of a nFET with W/L = 8.0/0.12 (with 32 fingers) biased at  $V_{GS}$ =0.6V and  $V_{DS}$ =1.2V

| Parameters | $R_G$ | $r_{ch}$ | $g_m$                 | $g_{ds}$ | $C_{gs}$ | $C_{gd}$ |

|------------|-------|----------|-----------------------|----------|----------|----------|

| Values     | 6.0 Ω | 7.1 Ω    | $152.4 \mathrm{\ mS}$ | 18.8 mS  | 235.5 fF | 101.0 fF |

The intrinsic device noise sources were extracted from the measured high-frequency noise parameters and the elements of the RF sub-circuit model using the procedure described in the previous section. Figure 13 shows the frequency dependence of the channel thermal noise and the induced gate noise. The channel thermal noise is, in general, independent of frequency. The induced gate noise, however, is proportional to the square of the frequency, as expected theoretically. The gate shot noise estimated using equation (5) is about 1.3 x  $10^{-25}$   $A^2/Hz$  at the frequency and bias condition of interest ( $I_G$  is about 0.4  $\mu A$ ). As we can see, the gate shot noise is not very significant at high frequencies. The cross-correlation between channel thermal

Figure 13: Frequency dependence of channel thermal noise  $(\overline{i_d^2})$  and gate current noise  $(\overline{i_g^2})$  for an nFET with W/L = 8.0/0.12 (32 fingers).

noise and induced gate noise as a function of frequency is shown in Fig. 14. The imaginary part of the correlation term is proportional to the frequency, whereas, the real part of the correlation term is almost zero up to about 10 GHz. This is mainly due to the capacitive coupling of the gate-induced noise through  $C_{gs}$ .

The dependence of channel thermal noise and induced gate noise on the drain current (at a fixed  $V_{DS}$  and varying  $V_{GS}$ ) is shown in Fig. 15. The channel thermal noise shows a strong bias dependence and increases as  $V_{GS}$  increases. The induced

**Figure 14:** Frequency dependence of real and imaginary part of the cross-correlation between channel thermal noise and induced gate noise – for a nFET with W/L = 8.0/0.12 (with 32 fingers).

**Figure 15:** Bias dependence of channel thermal noise  $(\overline{i_d^2})$  and gate current noise  $(\overline{i_d^2})$  for an nFET with W/L = 8.0/0.12 (32 fingers).

gate noise shows a weaker bias dependence and increases slightly with increase in  $V_{GS}$ . This is due to the increase in the effective channel resistance due to velocity saturation at high gate bias conditions. The bias dependence of noise correlation between the channel thermal noise and induced gate noise is plotted in Fig. 16. The

**Figure 16:** Bias dependence of real and imaginary part of the cross-correlation between channel thermal noise and induced gate noise – for a nFET with W/L = 8.0/0.12 (with 32 fingers).

imaginary part of the correlation term increases with increasing gate bias, whereas the real term exhibits a weak dependence on the gate bias. The excess noise factors  $\gamma$  and  $\beta$  are evaluated from  $\overline{i_d^2}$  and  $\overline{i_g^2}$  respectively. Figures 17 and 18 show the bias dependence of  $\gamma$  and  $\beta$ , respectively. It is observed that both  $\gamma$  and  $\beta$  increase with increasing  $V_{GS}$ . There is a moderate enhancement of  $\gamma$  compared to the theoretical long channel value of 2/3. This enhancement of  $\gamma$  in short-channel MOSFETs is attributed to channel length modulation and carrier heating. The maximum value of  $\gamma$  in saturation region is around 2, which is in agreement with the values reported for

Figure 17: Bias dependence of  $\gamma$  for a nFET with W/L = 8.0/0.12 (32 fingers).

Figure 18: Bias dependence of  $\beta$  for a nFET with W/L = 8.0/0.12 (32 fingers).

a 0.18  $\mu m$  technology node [25]–[27]. We see that  $\beta$  is close to the long-channel value of 4/3 for small gate bias and becomes as large as 8 at higher  $V_{GS}$ . The increase in  $\beta$  at high gate bias is due to the increase in effective channel resistance because of velocity saturation. However, it is observed that the contribution of the induced gate noise to the total device noise is relatively small for these highly scaled MOSFETs.

The impact of channel length on the intrinsic noise currents is shown in figs. 19 and 20. From fig. 19, we see that the channel thermal noise increases rapidly as the channel length decreases. This is mainly due to the more pronounced channel length modulation effect and carrier heating in short-channel MOSFETs. The increase in

**Figure 19:** Bias dependence of channel thermal noise  $(\overline{i_d^2})$  for various gate lengths.

current drive and channel conductance of short-channel MOSFETs leads to a decrease in the induced gate noise with decreasing gate lengths, as shown in fig. 20. As shown in fig. 21, the increase in channel thermal noise results in higher excess noise factor  $\gamma$  for the short-channel devices.

**Figure 20:** Bias dependence of induced gate noise  $(\overline{i_g^2})$  for various gate lengths.

Figure 21: Bias dependence of excess noise factor  $\gamma$  for various gate lengths.

The extracted noise currents are fed to the equivalent circuit model to obtain the simulated RF noise parameters -  $NF_{min}$ ,  $R_n$ , and  $\Gamma_{opt}$ . Figure 22 shows the measured and simulated  $NF_{min}$  and  $R_n$  across frequency. This 130 nm nFET device exhibits a sub-1.0dB  $NF_{min}$  up to about 10 GHz, which is very useful for C-band applications. The optimum source reflection coefficient versus frequency is shown in Fig. 23.

Figure 22: Measured and modeled  $NF_{min}$  and  $R_n$  versus frequency – for an nFET with W/L = 8.0/0.12 (with 32 fingers).

Figure 23: Measured and modeled optimum source reflection coefficient ( $\Gamma_{opt}$ ) versus frequency – for an nFET with W/L = 8.0/0.12 (with 32 fingers).

The bias dependence of  $NF_{min}$  and  $R_n$  is shown in Fig. 24. Figure 25 shows the bias dependence of the  $(\Gamma_{opt})$ . The measured and modeled noise parameters agree

**Figure 24:** Measured and modeled  $NF_{min}$  and  $R_n$  across bias - for an nFET with W/L = 8.0/0.12 (with 32 fingers).

**Figure 25:** Measured and modeled  $\Gamma_{opt}$  across bias – for an nFET with W/L = 8.0/0.12 (with 32 fingers).

well with each other, confirming the validity of the sub-circuit model.

## CHAPTER IV

# CRYOGENIC PERFORMANCE OF DEEP SUB-MICRON CMOS DEVICES