## OPTIMIZING HIGH LOCALITY MEMORY REFERENCES IN CACHE COHERENT SHARED MEMORY MULTI-CORE PROCESSORS

A Dissertation Presented to The Academic Faculty

By

Suk Chan Kang

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology

May 2019

Copyright © Suk Chan Kang 2019

## OPTIMIZING HIGH LOCALITY MEMORY REFERENCES IN CACHE COHERENT SHARED MEMORY MULTI-CORE PROCESSORS

Approved by:

Dr. Sudhakar Yalamanchili, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Linda M Wills School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Ada Gavrilovska School of Computer Scienece *Georgia Institute of Technology*  Dr. Tushar Krishna School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Santosh Pande School of Computer Scienece *Georgia Institute of Technology*

Date Approved: January 10, 2019

To my God and family

#### ACKNOWLEDGEMENTS

This thesis could be completed with the help of many individuals. Above all, I would like to express my deepest appreciation to my parents, Joo Shin Kang and Kwang Yeon Kim, for their love, trust, and sacrifice for me. I would like to thank my brother, Dr. Sang Yop Kang, for his warm brotherhood and encouragement. My special thanks should also go to my maternal grandmother, Gab Nieu Kim, my late maternal grandfather, Hyung Chul Kim, and my late paternal grandmother, Kyung Jieom Kim, for being my heart-warm grand parents who are full of love. I must also thank my aunt Kwang Woo Kim and my uncle Dr. Sung Mou Cho, for their generous support in my life.

I would also like to extend my deepest gratitude to Dr. Sudhakar Yalamanchili who is my advisor. As my role model, he demonstrates that an outstanding scholar can also be a nice and generous person with quiet charisma. Every one-on-one meeting with him was simply the precious opportunity to get myself cheered up significantly and to clearly learn the meaning of a advisor. He always respected me as his PhD student, listened to and encouraged me, gave exceptional technical solutions and ingenious suggestions, and patiently waited for my research progress with profound belief in my work. Hence, "who is your PhD thesis advisor?" has been and also will be one of my favorite question, ever since I first met with him.

I would also like to extend my gratitude to late Dr. George Riley who is the former ECE's associate chair for graduate affairs, for enabling me to have Dr. Sudhakar Yalamanchili as my new advisor. I am so sorry that I was too busy even to know that Dr. George Riley passed away recently. Occasionally, I remind myself of the touching words he gave me when I was in the midst of hard time looking for a new advisor.

I would like to extend my sincere thanks to Dr. Linda M Wills, Dr. Ada Gavrilovska, Dr. Tushar Krishna, and Dr. Santosh Pande, for serving as my kind committee members, which is my honor. I must especially thank Dr. Linda M Wills, for generously giving me the insightful guidance, thorough and frequent proof-reads of my thesis, and emotional support, even though she herself was extremely busy. I cannot appreciate her enough because her help encouraged me extensively and enabled me to remain calm while I was preparing my thesis and final defense. I learned valuable and useful knowledge used for my thesis from the courses which Dr. Ada Gavrilovska and Dr. Santosh Pande taught. I also learned many valuable and critical knowledge from Dr. Tushar Krishna when he kindly answered my abrupt unscheduled questions related to my research, in the hall ways and lab space.

Thanks should also go to Dr. Jongman Kim who is my former advisor at Gerogia Tech and his colleague Dr. Chrysostomos Nicopoulos at University of Cyprus, as my former coworkers with whom I had precious time in my life.

I very much thank Dr. Daniela Staiculescu and Ms. Tasha M Torrence at ECE Graduate Affairs Office, for their ever consistent kind help and advice.

Additionally, I must very much appreciate Korean Government, for having granted me the scholarship while I studied at Carnegie Mellon University as a master student. I am so proud of the support.

Finally, I am extremely grateful to my God. My PhD program was the time when I realize that you always stay with me. It is you who let me get over all the hardships and eventually complete my PhD degree.

## TABLE OF CONTENTS

| Acknow    | ledgements                             |

|-----------|----------------------------------------|

| List of T | ables                                  |

| List of F | <b>'igures</b>                         |

| List of C | Zodes                                  |

| Acronyr   | <b>ns</b>                              |

| Summar    | <b>y</b>                               |

| Chapter   | <b>1: Introduction</b>                 |

| 1.1       | False Shared Memory Object    2        |

| 1.2       | Two Target Memory Reference Types    3 |

|           | 1.2.1 Pure Local Memory Data           |

|           | 1.2.2 Centralized Spin-Lock Variables  |

| 1.3       | Thesis Statement                       |

| 1.4       | Thesis Contributions                   |

| Chapter   | <b>2: Literature Review</b>            |

| 2.1       | Memory Reference Stream Decoupling     |

| 2.2    | Virtua | Cache Memory Architecture                                                                                    | 9  |

|--------|--------|--------------------------------------------------------------------------------------------------------------|----|

| 2.3    | Spinlo | cks And Linux Kernel                                                                                         | 10 |

|        | 2.3.1  | Ticket Spinlock                                                                                              | 11 |

|        | 2.3.2  | MCS Lock                                                                                                     | 11 |

|        | 2.3.3  | Linux qspinlock                                                                                              | 12 |

| Chapte |        | <i>LMD 1)</i> Pure Local Memory Data Cache: Effective Architected gister File Extension for Multi-Processors | 14 |

| 3.1    | Insigh | ts and Contributions                                                                                         | 15 |

|        | 3.1.1  | Pilot Design to Effectively Extend Architected Registers of CCSM<br>Multi-Processors                         | 15 |

|        | 3.1.2  | Cost-Effective and Flexible VIVT Cache Implementation                                                        | 17 |

| 3.2    | Backg  | round                                                                                                        | 17 |

| 3.3    | Impler | mentation                                                                                                    | 19 |

|        | 3.3.1  | Manual Virtual Address Space Filtering                                                                       | 19 |

|        | 3.3.2  | The Implementation of The Proposed VIVT PLMD Cache for Multi-Processors                                      | 20 |

| 3.4    | Evalua | ation                                                                                                        | 22 |

|        | 3.4.1  | Simulation Limitation                                                                                        | 22 |

|        | 3.4.2  | Simulation Framework                                                                                         | 23 |

|        | 3.4.3  | Designs Under Evaluation                                                                                     | 24 |

|        | 3.4.4  | Overall Performance Evaluation                                                                               | 24 |

|        | 3.4.5  | TLB Access Behavior                                                                                          | 25 |

|        | 3.4.6  | L1/L2 Statistics Analysis (Multi-Level Benefits of PLMD Caches) .                                            | 25 |

| 3.5    | Summ   | ary                                                                                                          | 29 |

| Chapter | r 4: ( <i>PL</i> | MD 2) Subtleties of Run-Time Virtual Address Stacks         | 31 |

|---------|------------------|-------------------------------------------------------------|----|

| 4.1     | Contri           | butions                                                     | 32 |

|         | 4.1.1            | Breaking Chain of a Widespread Erroneous Assumption         | 32 |

|         | 4.1.2            | Safeguards for Related Prior Work                           | 33 |

| 4.2     | Backg            | round                                                       | 33 |

| 4.3     | Insight          | s: Myths and Realities of Run-Time Stacks                   | 34 |

|         | 4.3.1            | Myth1: Dichotomy of Stack/Non-Stack Area                    | 35 |

|         | 4.3.2            | Myth2: Privacy of the VA Stack Data                         | 38 |

| 4.4     | Insight          | s: Potential Hazards                                        | 44 |

|         | 4.4.1            | Dichotomy Affects Data Consistency and Dependencies         | 44 |

|         | 4.4.2            | Privacy Affects Cache Coherence and Memory Consistency      | 45 |

| 4.5     | Safegu           | ards for Stack/Non-Stack Decoupled-Data Architecture        | 48 |

|         | 4.5.1            | Suggested Safeguards to Achieve Real Dichotomy              | 48 |

|         | 4.5.2            | Suggested Safeguards to Achieve Real Privacy                | 49 |

| 4.6     | Summ             | ary                                                         | 49 |

| Chapter | r 5: ( <i>CS</i> | SLVs) QT Spinlock: Queuing Ticket Spinlock for Linux Kernel | 51 |

| 5.1     | Insight          | s and Contributions                                         | 52 |

|         | 5.1.1            | Ultimate Minimalism in Cache Line Bouncing                  | 52 |

|         | 5.1.2            | Small Lock Variable Size                                    | 53 |

|         | 5.1.3            | Proper Approximate Simulation Model                         | 53 |

| 5.2     | Backg            | round                                                       | 54 |

|         | 5.2.1            | Test-and-Set (TS) Spinlock: Centralized Spin-Lock           | 54 |

|     | 5.2.2  | Test-and-Test-and-Set (TTS) Spinlock: Centralized Spin-Lock                | 55 |

|-----|--------|----------------------------------------------------------------------------|----|

|     | 5.2.3  | Ticket Spinlock: Centralized Spin-Lock                                     | 56 |

|     | 5.2.4  | General Queuing Spinlock Scheme                                            | 57 |

|     | 5.2.5  | MCS Lock: Queuing Lock                                                     | 58 |

|     | 5.2.6  | Important Properties of Spinlock Operation inside Linux Kernel             | 60 |

|     | 5.2.7  | Linux qspinlock: Centralized Spin-Lock Enhanced with Internal Queuing Lock | 62 |

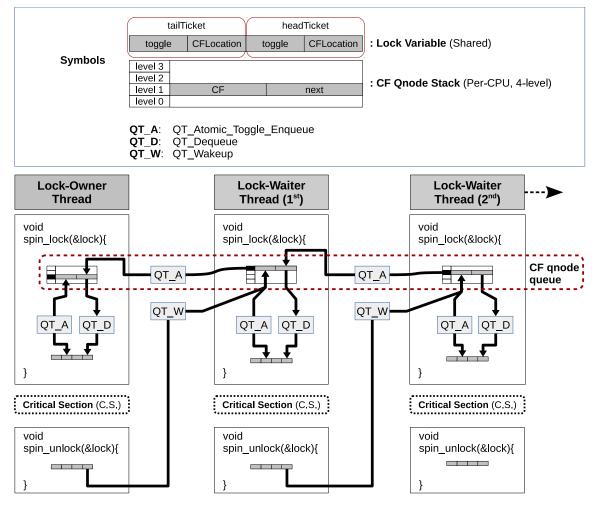

| 5.3 | Impler | nentation of QT Spinlock                                                   | 67 |

|     | 5.3.1  | Caching-Flag (CF)                                                          | 67 |

|     | 5.3.2  | QT Instructions and QT Messages                                            | 69 |

|     | 5.3.3  | Transformed Ticket Spinlock Code                                           | 70 |

|     | 5.3.4  | Intuitive View on Procedures in Lock Contention                            | 75 |

|     | 5.3.5  | Impact on Underlying Memory Consistency Model                              | 77 |

| 5.4 | Essent | ials Required for Proper Simulators                                        | 77 |

|     | 5.4.1  | Essential 1: The Perfect-Synchronization-Based Processor Multi-<br>plexing | 78 |

|     | 5.4.2  | Essential 2: The Proper Coherence Message Implementation                   | 80 |

| 5.5 | Simula | ator Setup                                                                 | 82 |

|     | 5.5.1  | Baseline Simulator (Marssx86)                                              | 82 |

|     | 5.5.2  | Approximate Simulation Model: Critical-Path of Cache Line<br>Bouncing      | 84 |

| 5.6 | Evalua | tion                                                                       | 87 |

|     | 5.6.1  | Simulation Configuration                                                   | 87 |

|     | 5.6.2  | Simulation Workload: Steady State Extreme Lock Contention                  | 88 |

|         | 5.6.3    | Unfair Simulation Model  | 89 |

|---------|----------|--------------------------|----|

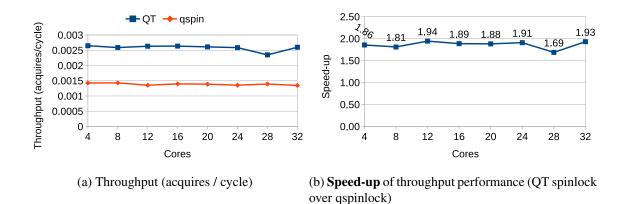

|         | 5.6.4    | Throughput Performance   | 89 |

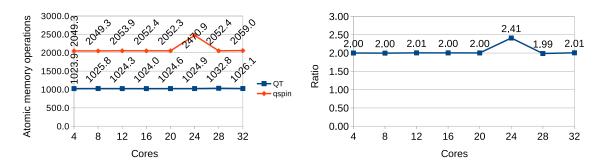

|         | 5.6.5    | Atomic Memory Operations | 90 |

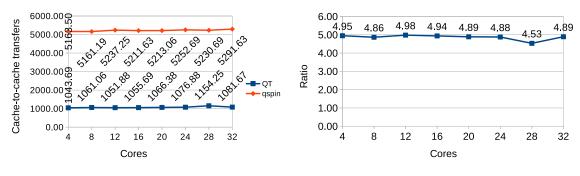

|         | 5.6.6    | Cache-to-Cache Transfers | 91 |

| 5.7     | Summ     | nary                     | 92 |

| Chapte  | r 6: Dis | ssertation Conclusion    | 94 |

| Referen | nces .   |                          | 99 |

# LIST OF TABLES

| 3.1 | The OoO opportunities of the architected register operations, PLMD helper cache memory operations, and regular memory operations on the single- |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | processor and CCSM multi-processor systems                                                                                                      | 16 |

| 3.2 | The simulation configuration of the two designs under evaluation                                                                                | 23 |

| 5.1 | Summary of the representative spinlock designs                                                                                                  | 66 |

| 5.2 | Simulation configuration                                                                                                                        | 87 |

## LIST OF FIGURES

| 3.1 | The two prevalent virtual address space-sharing types                                                                                                                   | 17 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Implementation of the proposed VIVT PLMD cache for multi-core systems                                                                                                   | 21 |

| 3.3 | Overall performance improvement over the baseline design                                                                                                                | 24 |

| 3.4 | Memory access pattern analysis                                                                                                                                          | 26 |

| 3.5 | L1 data cache read/write statistics of the two evaluated architectures                                                                                                  | 27 |

| 3.6 | L2 cache read/write statistics of the two evaluated architectures                                                                                                       | 28 |

| 4.1 | Diagram of an example pipeline of (a) a conventional superscalar processor<br>and (b) a data-decoupled architecture. This is obtained from [10] and is<br>redrawn here. | 34 |

| 4.2 | Kernel-space synonyms are observed in contemporary OSes                                                                                                                 | 36 |

| 4.3 | Page reallocation (a) and remapping (b)                                                                                                                                 | 39 |

| 5.1 | Illustration of the per-thread qnodes establishing a spin-wait queue of a lock.                                                                                         | 58 |

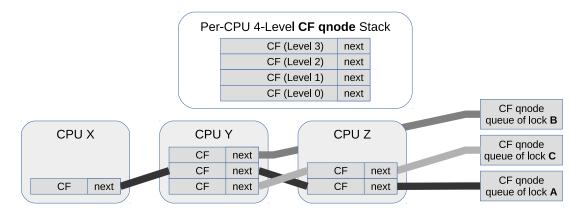

| 5.2 | Illustration of the abstraction of the per-CPU 4-level spin-wait stack and per-lock spin-wait queue.                                                                    | 62 |

| 5.3 | Illustration of the per-CPU 4-level qnode stack and per-lock qnode queue of the Linux qspinlock.                                                                        | 64 |

| 5.4 | Illustration of the per-CPU 4-level CF qnode stack and per-lock CF qnode queue.                                                                                         | 68 |

| 5.5 | Sketch of the QT instructions which update the CF qnodes and lock variable CFLocation fields, in the lock contention case. | 76 |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

| 5.6 | Lock acquisitions/releases throughput performance of the Linux qspinlock and QT spinlock designs.                          | 89 |

| 5.7 | Run-time atomic memory operations used by the Linux qspinlock and QT spinlock.                                             | 90 |

| 5.8 | Run-time cache-to-cache transfers incurred by the Linux qspinlock and QT spinlock.                                         | 91 |

## LIST OF CODES

| 1.1 | The first target memory object type addressed in this thesis: <b>Pure local memory data</b> (bufA[10][20][30], r)                                           | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | The second target memory object type addressed in this thesis: <b>Centralized spin-lock variables</b> (lock).                                               | 4  |

| 4.1 | Direct I/O working example code                                                                                                                             | 36 |

| 4.2 | The "cow_user_page()" function in the "mm/memory.c" file of Linux kernel 3.14                                                                               | 37 |

| 4.3 | An <i>OpenMP</i> pseudo-code snippet evaluating the variable dotp in a fork-<br>join task model.                                                            | 39 |

| 4.4 | A code example (pnlPearlInferenceEngine.cpp) from the BioParallel benchmark suite [42]                                                                      | 40 |

| 4.5 | Working code with the mmap() function mapping a file inside the VA stack                                                                                    | 42 |

| 4.6 | A code snippet of the run-time binding parallel callback function parallel_produce_cb() to be called by the producer of a "producer-consumer" style program | 46 |

| 5.1 | A pseudo-C code of the test-and-set (TS) spinlock.                                                                                                          | 54 |

| 5.2 | A pseudo-C code of the test-and-test-and-set (TTS) spinlock                                                                                                 | 55 |

| 5.3 | A pseudo-C code of the ticket spinlock.                                                                                                                     | 56 |

| 5.4 | A pseudo-C code of the MCS spinlock                                                                                                                         | 58 |

| 5.5 | A simplified pseudo-C code of the Linux kernel qspinlock. This code as-<br>sumes the 1-level per-CPU qnode stack for simplification                         | 62 |

| 5.6 | The pseudo-Verilog code describing the per-CPU CF stack                                                                                                     | 68 |

| 5.7 | The pseudo-C description of the transformed ticket spinlock code for the QT spinlock. The code employs the QT instructions which have the "QT_" prefix in their names. This example is for systems having up to 64 CPUs 7 | 1 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 5.8 | The OpenMP code generating the false sharing cache line update inflation on the array False_Shared_Array[]                                                                                                                | 1 |

| 5.9 | The main simulation loop of Marssx86 simulator. The loop has all the vCPUs run on every single simulation cycle. It is located in the BaseMachine::run() function of the ptlsim/sim/machine.cpp file                      | 3 |

### ACRONYMS

- **2D** 2-dimensional.

- CAS compare-and-swap.

- **CCSM** cache coherence shared memory.

- CF caching flag.

- CoW copy-on-write.

- CSL centralized spin-lock.

- CSLV centralized spin-lock variable.

- **DDA** data-decoupled architecture.

- FIFO first-in-first-out.

- FSMO false shared memory object.

- **ILP** instruction level parallelism.

- **IPC** inter-process communication.

- **ISA** instruction set architecture.

- LKM loadable kernel module.

- LRSW least recently spin-waiting.

LSQ load/store queue.

MRSW most recently spin-waiting.

NUMA non-uniform memory access.

**OoO** out-of-order.

OS operating system.

**PIPT** physically indexed physically tagged.

PLMD pure local memory data.

**RMW** read-modify-write.

ROI region of interest.

SM shared memory.

TLB translate look-aside buffer.

ToS top of stack.

TS test-and-set.

**TSO** total store ordering.

TTS test-and-test-and-set.

VA virtual address.

vCPU virtual CPU.

**VIVT** virtually indexed virtually tagged.

#### SUMMARY

Optimizing memory references has been a primary research area of computer systems ever since the advent of the stored program computers. The objective of this thesis research is to identify and optimize two classes of high locality data memory reference streams in cache coherent shared memory multi-processors. More specifically, this thesis classifies such memory objects into spatial and temporal false shared memory objects. The underlying hypothesis is that the policy of treating all the memory objects as being permanently shared significantly hinders the optimization of high-locality memory objects in modern cache coherent shared memory multi-processor systems: the policy forces the systems to unconditionally prepare to incur shared-memory-related overheads for every memory reference. To verify the hypothesis, this thesis explores two different schemes to minimize the shared memory abstraction overheads associated with memory reference streams of spatial and temporal false shared memory objects, respectively. The schemes implement the exception rules which enable isolating false memory objects from the shared memory domain, in a spatial and temporal manner. However, the exception rules definitely require special consideration in cache coherent shared memory multi-processors, regarding the data consistency, cache coherence, and memory consistency model. Thus, this thesis not only implements the schemes based on such consideration, but also breaks the chain of the widespread faulty assumption of prior academic work. This high-level approach ultimately aims at upgrading scalability of large scale systems, such as multi-socket cache coherent shared memory multi-processors, throughout improving performance and reducing energy/power consumption. This thesis demonstrates the efficacy and efficiency of the schemes in terms of performance improvement and energy/power reduction.

# CHAPTER 1 INTRODUCTION

The modern cache coherence shared memory (CCSM) multi-processor architecture presents a shared memory (SM) abstraction to enable software designers to leverage the intuitive, convenient, and flexible SM programming model. However, the SM abstraction not only requires support by operating system (OS)s and compilers, but also incurs overhead in utilizing the underlying micro-architectures. For example, the versatile technique of creating virtual address (VA) synonyms in SM requires the OS provided inter-process communication (IPC) interfaces (e.g. shared memory segments in Linux), corresponding compiler support, virtual-to-physical address translation support, and cache coherence and memory consistency enforcement while performing synchronization operations on accesses to the shared synonymed memory. The resultant cache coherence and memory ordering (for memory consistency) traffic can eventually strain the interconnection networks. These overheads can grow with increasing core count and eventually overwhelm any intended performance speed-up and power/energy efficiency advantages, reducing scalability in the end. A socket based CCSM non-uniform memory access (NUMA) system will be more sensitive to the scalability challenges, due to its large average memory latency resulting from crossing of socket borders.

We observe that shared memory accesses can be distinguished based on their locality properties. In particular, we find that a significant number of accesses that are not shared, are treated as shared accesses and therefore incur all of the overheads associated with the SM abstraction. On the other hand, we also take notice that the extremely concurrent accesses to shared memory data naively make such data the hot spots of the overheads associated with the SM abstraction. Therefore, this thesis explores opportunities to optimize such high-locality memory accesses, by bypassing the aforementioned SM overheads in multi-processors. This high-level approach ultimately aims at upgrading system scalability by improving performance and energy/power efficiency.

#### 1.1 False Shared Memory Object

This thesis hypothesizes that the policy of treating all the memory objects as being permanently shared significantly prevents modern CCSM multi-processors from further optimizing the access of high-locality memory objects. Accordingly, we observe that there are two classes of memory objects whose accesses exhibit high locality and can be subject to optimization to improve scalability. To better identify such objects, we develop the concept of the spatial/temporal false shared memory object (FSMO):

- *Spatial FSMO*: memory object which can be spatially isolated from the SM domain, due to its private scope

- *Temporal FSMO*: memory object which can be temporally isolated from the SM domain, until the critical moment

The FSMO concept is motivated by the clear discrepancy between the design principle of the parallel SM programs and the actual SM domain operation of the CCSM multiprocessors. The parallel SM programs are optimized to maximally perform the computation locally, while minimally generating the global SM transactions (e.g. loop parallelization usually targets the outer loops, rather than the inner ones). Meanwhile, the contemporary CCSM multi-processors too conservatively treat every memory object as a permanently shared one, getting ready to incur the SM overhead mechanisms. This high false positive rate in identifying actual shared memory objects becomes the origin of the redundant SM overheads. For instance, the CCSM multi-processors prohibit even the qualified private memory operations from being executed in the full out-of-order (OoO) manner, constraining them to memory ordering rules regulated by the SM consistency model.

### **1.2 Two Target Memory Reference Types**

This thesis focuses on the following two high-locality FSMOs:

- 1. **Pure Local Memory Data:** source of *NO* shared memory references (neither interthread/process nor intra-thread/process), spatial FSMOs

- 2. Centralized Spin-Lock Variables: source of *SEVERE* shared memory references (inter-thread/process), temporal FSMOs

Listing 1.1 and 1.2 depict examples of the two memory objects.

```

1 int foo() {

2

/*

* Pure local memory data "bufA[10][20][30]" and "r"

3

* Scope: function foo() alone

4

*/

5

char bufA[10][20][30];

6

int r;

7

8

9

/*

* NOT pure local memory data "bufB[16]"

10

11

* Scope: function foo() and its sub-function bar()

12

*/

13

char bufB[16];

14

15

. . .

16

r = bar(bufB);

17

return r;

18 }

```

Listing 1.1: The first target memory object type addressed in this thesis: **Pure local memory data** (bufA[10][20][30], r).

```

1 /*

2 * Centralized spin-lock variable "lock" inside the spin-waiting loop.

3 * Other threads/processes can share it, to concurrently read/update it.

4 */

5 do {} while(lock == LOCKED_CONDITION);

6 ....

```

Listing 1.2: The second target memory object type addressed in this thesis: Centralized spin-lock variables (lock).

#### 1.2.1 Pure Local Memory Data

The pure local memory data (PLMD) are the memory objects accessed **exclusively within** the functions where they are declared and, consequently, are not referenced from outside the function scope. We classify PLMD as spatial FSMOs because their spatial function frame scope is private to their threads.

In handling the PLMD, the contemporary CCSM multi-processors have been wasting a significant portion of performance and energy. Specifically, the accesses to the PLMD can perfectly avoid SM overheads such as dealing with VA synonyms and regulating memory consistency. Additionally, if keeping CPU-affinity scheduling, virtually no coherence checks are required,

To address this inefficiency of losing performance and energy improvement opportunities, this thesis proposes to treat the PLMD as spatial FSMOs which extend the architected registers in CCSM multi-processors. Even though there could be other spatial FSMOs than the PLMD in one running program, the PLMD are relatively easy to filter from the run-time VA function frame stacks.

Note that the raw function frame stacks can contain minor NON-PLMD memory objects, as well. For example, "char bufB[16]" in Listing 1.1 is *not* PLMD, because the bar() function references it with the pointer bufB. The portion of the PLMD references can be *roughly* estimated, through counting the references to the VA stack data.

Prior work [1] shows that stack references account for an average of 56% of all memory accesses in SPEC CPU 2000 integer benchmarks (single-threaded workloads). The thesis research in Chapter 3 also shows that on average around 50% of all memory accesses in PARSEC benchmarks (multi-threaded workloads) belong to stack references. However, it is not straight-forward to detect/decouple the references to the stack data (i.e. the superset of the PLMD), let alone to the PLMD. For this reason, prior work optimizing the stack data references including [2, 3, 4, 1, 5] all rely on function-critical faulty assumptions. Chapter 4 explains where the assumptions come from, the subtleties of the run-time VA stacks, and the proper safeguards for the issues.

#### 1.2.2 Centralized Spin-Lock Variables

The centralized spin-lock variable (CSLV) is a hot spot memory object on which all the lock-waiter threads concurrently spin-wait. The example of the centralized spin-lock (CSL) design is the ticket spinlock. We classify CSLVs as temporal FSMOs because they can temporally delay appearing on the CPU node until the thread acquires the lock (this will be explained further in Chapter 5).

The spinlock is generally the best synchronization option to protect short sized shared data in memory. However, the spin-waiting synchronization easily becomes the most massive source of concurrent fine-grain cache coherence operations of the typhoon-like cache line bounces, and should consider the memory consistency issues. Ironically, it is only after going through this heavy SM synchronization overhead that the concurrently competing threads can safely access the very short sized shared data. In socket based CCSM NUMA systems, the overhead becomes more complicated: it not only comes from the interconnection network bandwidth limit (throughput) to handle cache coherence contention, but also from the latency penalty of moving cache lines across the socket boundaries. For this reason, the existing sophisticated scalable software spinlocks are still not good enough for the large scale socket based CCSM NUMA multi-processors [6]. Unfortunately, the spinlocks

using CSLVs are notorious as the worst design in terms of the overhead.

To address this synchronization overhead issue (in terms of both bandwidth and latency), this thesis proposes to handle CSLVs as temporal FSMOs which only the lockowner thread can see (while other threads cannot) in the local cache memory. This is designed to work without destroying the underlying memory consistency rule.

#### **1.3** Thesis Statement

The key ideas, insights, and challenges lead to the following **thesis statement**: *Significant performance improvement is possible by identifying and optimizing high locality reference streams in cache coherent shared memory multi-core processors*.

#### **1.4 Thesis Contributions**

The principle contribution of this thesis is identification and optimization of two classes of high locality reference streams (PLMD and CSLVs) that significantly affect performance in CCSM multi-processors. The specific contributions are as follows.

- It develops the concept of false shared memory objects (FSMOs). Contemporary CCSM multi-processors unconditionally assume all memory references to be permanently shared accesses and have them restricted by the SM related overheads. The concept of FSMOs is the main insight of this thesis enabling optimization of memory accesses to PLMD (spatial FSMOs) and CSLVs (temporal FSMOs).

- It describes how CCSM multi-processors can effectively extend the architected registers cost-efficiently, by taking advantage of spatial FSMO attributes of the PLMD, if they can be properly detected and decoupled from the rest of the memory objects [5].

- 3. It presents fundamental insights on how future OSes and compilers can effectively and correctly exploit the benefits of the run-time VA stack data as a superset of PLMD

[7].

4. It proposes the contrarian idea of enabling the centralized spinlock to accomplish the ultimate minimalism in cache line bouncing, by handling CSLVs as temporal FSMOs. The idea aims to unleash the power of the centralized spinlock design.

This thesis is organized as follows. Chapter 2 goes through the important prior work related to this research. Chapter 3 (the first PLMD optimization) presents a novel architecture for L1 data helper caches in CCSM multi-processors, to realize contribution 2. Chapter 4 (the second PLMD optimization) details the subtleties of the run-time VA stacks, to realize contribution 3. Chapter 5 (the CSLV optimization) illustrates the new hardware-supported Linux kernel default spinlock design, to realize contribution 4. Finally, Chapter 6 concludes the thesis.

# CHAPTER 2 LITERATURE REVIEW

#### 2.1 Memory Reference Stream Decoupling

This research topic has been important and popular, ever since the advent of the storedprogram computers. Harvard mark-1 [8] is the first stored-program computer which employs two separate memory reference pathways to instruction and data streams. As such, it became the root of the prevalent Harvard architecture systems. The separate instruction and data pathways help increase the memory referencing throughput, by enabling simultaneous accesses to the two streams. However, it is generally not straight-forward to perfectly decouple memory reference streams.

Quite a few works attempt to further decouple **data** memory reference streams. The Compiler Controlled Memory (CCM) scheme [9] decouples memory references into the two separate memories of the main memory and the compiler controlled memory (CCM). The register spilled memories generated by compilers are fed into the CCM, to prevent them from causing the cache pollution problem. However, the CCM scheme is not proper for the contemporary general purpose systems, because on every context switch, the data stored in the CCM should be flushed into the main memory. Therefore, the research is better suited for specialized hardware using dedicated memories, such as DSP devices.

Additionally, the Stack Cache [10], Access Region Locality (ARL) [2], Stack Value File (SVF) [1], Reverse (Register) Integration [3], Selective Snoop Probe (SSP) [4], Specialized Stack Cache and Pseudo Set-Associative Cache (SSC and PSAC) [11], and Separate Stack-Based Memory Organization [12] techniques all demonstrated the potential benefit of decoupling the data memory references into stack/non-stack streams, in terms of performance improvement and energy/power reduction. However, these approaches

have function-critical hazards because they are all based on faulty assumptions: (1) the stack/non-stack memory data regions can be perfectly dichotomized and (2) the raw VA stack memory regions are only composed of PLMD which have the register-file-like properties. This is described further in Chapter 4 and [7]. Interestingly, the Safe Stack scheme [13, 14] (which enhances the security of the run-time function call stacks) can help provide the safeguards for these previous approaches [10, 2, 1, 3, 4, 11, 12]: for each function call stack, the compiler transform technique creates a new separate "safe" stack and moves all the PLMD of the original stack there.

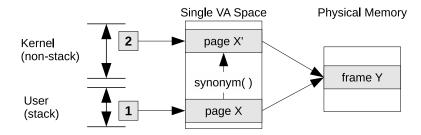

#### 2.2 Virtual Cache Memory Architecture

Virtual caches [15] work using virtual address tags and/or indexes, avoiding the virtual to physical address translation overhead. The idea is to achieve fast cache access time and energy/power reduction by avoiding accesses to the translate look-aside buffer (TLB). However, these advantages cannot be obtained for free because homonym and synonym (aliasing) issues must be resolved [15, 16] for data consistency. Homonym memory objects are the objects in different VA spaces (processes) having the same virtual addresses but which are mapped (translated) into different physical addresses. Conversely, synonym memory objects are the objects mapped (translated) into the same physical addresses but which have different virtual addresses. Normally, virtual caches can resolve homonym issues relatively simply, for instance, by tagging cache lines with the address space identifiers (ASIDs) or flushing the cache memory when context switches take place. However, synonym objects are mostly impossible to classify without proper help from the OS. To make matters worse, synonym objects can exist within the same virtual address space (i.e. intraprocess synonyms) as well as across different VA spaces (i.e. inter-process synonyms) [15, 16]. Therefore, simple solutions such as flushing the cache memory on context switches can not resolve all synonym issues.

The hardware-only solutions to resolve synonym issues have to rely on looking up or

tracking down the synonymed cache lines, with significant energy and area overheads. A simple preferred design to resolve the synonym issue is to prohibit any duplicate synonym cache lines from residing in the cache memory [17, 18]. That is, on a cache miss, the cache controller invalidates all the other synonymed cache lines after looking up the candidate lines. Meanwhile, Woo, et al. [19] propose a scheme to use bloom filters [20] to minimize the overhead of this looking-up approach: the bloom filter early notifies if the virtual cache memory contains the synonym line of the requested cache line access, to indicate whether or not the energy-consuming synonym look-up process is still necessary.

The software-supported solutions to resolve synonym issues can have the OS restrict page allocation, albeit at the cost of increased page fault rates [15]. Other more advanced ways involve utilizing the OS-provided synonym page mapping information. An example is the Opportunistic Virtual Caching (OVC) technique [21]. To that end, the work enhances the Linux kernel's virtual address range allocator, to inform the supporting hardware whether the user-space pages are currently free from the read-write synonym page mappings. More specifically, when a user-space page has the read-write synonym page mappings, the enhanced virtual address range allocator sets the highest order bit (i.e. 48th bit, VA<sub>47</sub>) of the virtual address of the page. Note that the VA<sub>47</sub> bit is always kept unset for user-space pages, in the current 48 bit canonical form X86-64 virtual address space [22]. The proposed OVC cache memory has physical tags as well as virtual tags, to handle the default physical caching mode operation and cache coherence mechanism. Each line of the OVC cache also has ASIDs to resolve the homonym issue. The scheme requires only modifying 240 lines of the Linux kernel code.

#### 2.3 Spinlocks And Linux Kernel

This section focuses on the three first-in-first-out (FIFO) spinlocks (MCS lock [23, 24, 25], ticket spinlock [23, 24], and qspinlock [25]) to explain the evolution of the contemporary default Linux kernel spinlocks. A spinlock design should satisfy the "4-byte lock variable"

and "4-level stacked context spin-wait" requirements, to be employed as the default Linux kernel spinlock. The 4-byte lock variable requirement prohibits most of the sophisticated queuing spinlock schemes (e.g. the MCS lock design [23, 24, 25], CLH lock [26], hierarchical CLH lock [27], and K42 lock [28]) from being employed as the Linux kernel default spinlock. In addition, the 4-level stacked context spin-wait requirement hinders any novel lock accelerator techniques supporting only 1-level lock context (e.g. the Misar technique [29]) from being employed for the Linux kernel.

#### 2.3.1 Ticket Spinlock

The ticket spinlock [23, 24] does not build an explicit linked list to conduct the FIFO lock operation. Instead, the lock and unlock operations update the tail/head ticket number, respectively. The lock-competing threads have to spin-wait, unless their uniquely assigned ticket numbers become equal to the current head ticket number. Therefore, the ticket spinlock is a centralized spinlock (CSL) design: all the lock-waiter threads spin on the shared lock variable. Like other centralized spinlocks, the ticket spinlock has the advantage of using simple code. Hence, the ticket spinlock performs the best, out of all the software spinlocks, in case of experiencing no lock contention [24]. On the other hand, due to the heavy cache coherence contention surrounding the lock variable, ticket lock definitely does not scale with increased CPU counts, especially in the socket based CCSM NUMA systems [24]. The Linux kernel employed the ticket spinlock as the default spinlock, until the qspinlock replaced it.

#### 2.3.2 MCS Lock

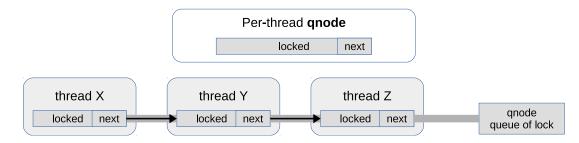

The MCS lock [23, 24, 25] is the representative scalable queuing spinlock design, which conducts the FIFO lock operation. Each lock-waiter thread spin-waits on its own per-thread local "qnode," instead of on the centralized shared lock variable. The per-thread qnodes are manually declared inside the function stacks of the lock-competing threads, and passed as

an argument to the lock()/unlock() API functions, so the design can build a linked listed queue structure of them.

However, the MCS lock has some native critical problems and/or potential vulnerabilities. First, the lock variable unavoidably becomes much larger than 4 bytes, because it should contain VA pointer values pointing to the current tail thread qnode. This is the reason why the MCS lock has not yet been employed in the Linux kernel as the default spinlock, even though it scales nicely. The other queuing locks such as CLH lock [26], hierarchical CLH lock [27], and K42 lock [28] have a similar problem. Second, the unlocking operation (in addition to the locking operation) imperatively uses the atomic memory operation, when it detects no successor lock-waiter thread at the moment. This has everything to do with the multiple lock-competing threads concurrently managing the linked-listed qnode queue structure. The centralized spinlock designs such as ticket spinlock basically do not use any atomic memory operation, when releasing the lock. Third, the adjacent predecessor and successor lock-waiter threads should move their qnode cache lines between them, in a ping-pong way. This can be a heavy overhead taking long latency, if the threads are running on the large scale socket based CCSM NUMA systems [6].

#### 2.3.3 Linux qspinlock

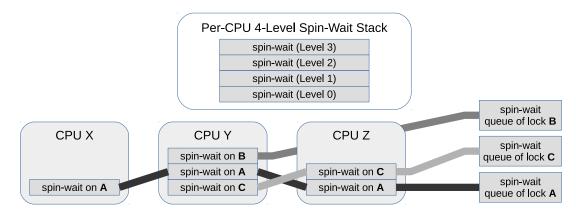

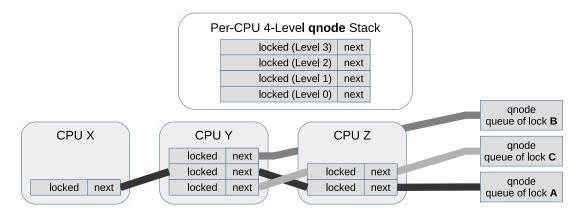

Even though the MCS lock scales excellently, it cannot be employed as the default Linux kernel spinlock, just because the design cannot meet the "4-byte lock variable" requirement. Alternatively, as of the kernel version 4.2, Linux kernel substitutes the qspinlock [25] for the previous default ticket spinlock.

As a matter of fact, the qspinlock is not the pure queuing spinlock, but is the workaround design to make the MCS lock fit into the 4 byte small lock variable. To this end, the qspinlock is designed to work in the form of a baseline centralized spinlock (CSL) which is enhanced with an internal MCS lock. The baseline centralized spinlock variable (CSLV) is referenced for the locking, unlocking, and spin-wait operations. The internal MCS lock

removes the cache coherence contention surrounding the baseline CSLV, by letting only one lock-waiter thread spin-wait on the CSLV. The 4 byte small lock variable size is facilitated by the fact that the internal MCS lock establishes the queue structure with the per-CPU qnodes, instead of with the per-thread qnodes. Note that unlike the per-thread qnodes, the per-CPU qnodes are viable only while CPU-migrations are disabled (e.g. during the spin-wait iterations). Consequently, this design ends up having a "two-step" spin-wait operation: the first step spin-waits on the per-CPU qnode of the internal MCS lock, while the second step spin-waits on the baseline CSLV. Due to this complex design, the qspinlock naturally can incur much more cache line bounces than the original MCS lock, especially accompanying a number of atomic memory operations.

#### **CHAPTER 3**

# (*PLMD 1*) PURE LOCAL MEMORY DATA CACHE: EFFECTIVE ARCHITECTED REGISTER FILE EXTENSION FOR MULTI-PROCESSORS

The original research document of this thesis work was published in [5].

In general, memory accesses to the VA stack area data (which are a superset of the PLMD) play an instrumental role in overall system performance. Research in this domain has shown that real workloads tend to access the VA stack area at a high frequency, albeit within a small memory footprint [10, 1], because a process/thread is always running within a function during its execution, and, usually, function frames tend not to be very deep. It is precisely this observation that has led to various designs for the single-processor systems that handle memory accesses to the stack area at a higher level in the memory hierarchy, in order to improve performance and reduce energy consumption.

This thesis research demonstrates that special L1 PLMD helper caches can significantly boost the performance of one primary and dominant multi-threaded workload running on a CCSM multi-processor, while actually reducing its energy consumption. This helper cache introduces the "address space filtering" technique which filters the VA spaces (i.e. processes) and subsequently handles only the PLMD of the selected virtual address space.

The idea exploits the spatial FSMO attribute of the PLMD, and the ultimate goal is to present the exclusively selected multi-threaded process the L1 helper cache structure. This cache is extremely fast and perfectly isolated from the SM domain, just like the architected register file. The scheme targets the modern workstation and server environments that run a single, dedicated multi-threaded application workload per machine.

The PLMD helper cache is implemented as a virtually indexed virtually tagged (VIVT) cache structure, and minimizes the overhead incurred in resolving virtual-cache-related

artifacts (e.g. the synonym and homonym issues), in a cost effective way. This is mainly due to the fact that the scheme grants exclusive access to the PLMD stream of only one multi-threaded process at a time, as previously introduced.

This chapter first shows a conceptual description of the PLMD cache-based approach in Section 3.1. It then provides background in Section 3.2 on its context. Section 3.3 details its implementation and Section 3.4 evaluates the performance and energy efficiency of the PLMD helper cache technique, demonstrating the usability of this design in future CCSM multi-processors. The PLMD cache mechanism is especially available to systems that run one primary and dominant multi-threaded application per machine.

*Note* that this thesis work makes the assumption which all major related prior work including [10, 2, 1, 3, 4, 11, 12] rely on: the stack area data are all PLMD, and their memory references can be perfectly decoupled from the other memory reference streams. Chapter 4 explains the myths and realities of this assumption, and also explains how to correctly filter and decouple the PLMD references from the stack area data stream.

#### **3.1 Insights and Contributions**

#### 3.1.1 Pilot Design to Effectively Extend Architected Registers of CCSM Multi-Processors

The architected registers are the fastest storage areas in a system. Moreover, on CCSM multi-processors, storing data in architected registers creates a more significant impact on performance than storing them in memory: the architected register operations participate in the full OoO execution, while memory operation reordering is restricted by the shared memory consistency model of the systems. This overhead has the potential to create the anomaly that single-threaded programs which require *no* shared memory operations run much faster on the OoO single-processors than on the OoO CCSM multi-processors.

Meanwhile, it is nearly impossible to extend the architected registers of existing machines, because they already have the maximum number of architected registers which their fixed instruction set architecture (ISA) allows. This thesis proposes a cache-based design Table 3.1: The OoO opportunities of the architected register operations, PLMD helper cache memory operations, and regular memory operations on the single-processor and CCSM multi-processor systems

| Regular Memory Opera            | Regular Memory Operations                                      |  |  |

|---------------------------------|----------------------------------------------------------------|--|--|

| Single-Processors               | Full OoO                                                       |  |  |

| CCSM Multi-Processors           | Limited re-ordering allowed by shared memory consistency model |  |  |

| Architected Register Operations |                                                                |  |  |

| Single-Processors               | Full OoO                                                       |  |  |

| CCSM Multi-Processors           | Full OoO                                                       |  |  |

| PLMD Helper Cache Me            | PLMD Helper Cache Memory Operations                            |  |  |

| Single-Processors               | Full OoO                                                       |  |  |

| CCSM Multi-Processors           | Full OoO                                                       |  |  |

which has a similar effect as extending the architected register file. This effect would remarkably increase the opportunities of the full OoO executions of the selected one primary and dominant multi-threaded process, especially on an ISA with relatively small number of architected registers (e.g. X86 or X86-64 [30]).

The L1 PLMD helper cache architecture proposes a **pilot** design of the "architectedregister-like" cache memory for the CCSM multi-processors, which is (1) extremely fast and (2) perfectly isolated from the SM domain. The idea does not require changing the ISA to deliver the architected register file extension effect. To achieve the fast speed, the design profits from the VIVT cache memory structure. To achieve perfect isolation from the SM domain, the design utilizes the spatial FSMO attribute of the PLMD. The "isolation from the SM domain" property frees the PLMD helper cache from both the memory ordering regulation and the cache coherence interference (by enforcing "CPU-Affinity" scheduling). Additionally, the architected register "extension" includes the effect of storing even the bulky data (e.g. data structures and arrays) in the virtually extended architected registers (i.e. PLMD helper caches), which is generally not possible with the actual architected registers.

Table 3.1 recaps the OoO execution opportunities of the architected register operations, PLMD helper cache memory operations, and regular memory operations.

#### 3.1.2 Cost-Effective and Flexible VIVT Cache Implementation

The L1 PLMD helper cache architecture manually filters out all VA spaces except the main VA space (process). Thus, the run-time PLMD of this lone process become the exclusive occupants of the PLMD helper cache. This address space filtering technique automatically removes the synonym and homonym problems of the employed VIVT cache structure, without incurring additional expensive overhead.

The address space filtering technique also presents the PLMD helper cache with the unlimited freedom for the VIVT cache configuration. Note that virtually indexed cache designs usually prefer limiting the cache set size to be equal to or smaller than the virtual address page size of the OS [21, 31, 32]. This design policy intends to take advantage of enabling the virtual indices to actually work as physical indices, skipping the address translation overhead. However, the resulting virtually indexed cache memories have the only restrictive and bizarre option of adding more associativities, to increase their size, which ironically increases the access latency and tag-matching power/energy consumption.

#### 3.2 Background

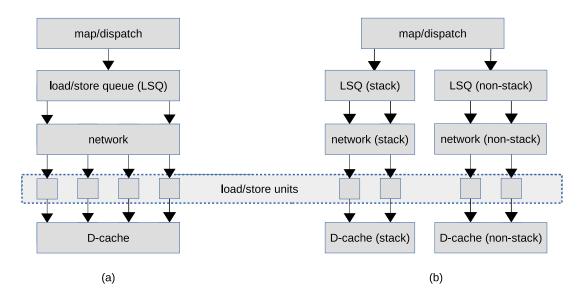

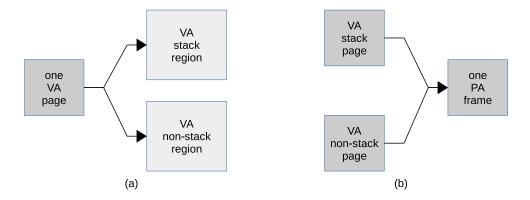

Figure 3.1: The two prevalent virtual address space-sharing types

There are two prevalent methodologies that are typically utilized in shared-memory

architectures: the multi-threaded methodology and the shared memory inter-process communication.

#### Multi-threaded methodology

Multi-threaded methodology operates on the principle of one main thread and its N subthreads residing in a single VA space and comprising one process (abstractly visualized in Figure 3.1a). The main thread creates its sub-threads using a "clone()" system call. Consequently, the main thread and its sub-threads share the page table, global variable area, and file descriptor. The principle of confinement within a single VA space aims to alleviate the heavy overhead of context switching during parallel execution. However, the main thread and all sub-threads must have their own separate resources, such as stack area (user-level/kernel-level) and registers. User-level thread libraries such as POSIX Threads [33] and OpenMP [34] are based on this concept. In the x86 architecture, the main thread and its sub threads use the same "cr3" register to refer to the page table for the single shared VA space. Note that this "cr3" register-sharing activity by a multi-threaded process can easily be monitored by a full-system simulator such as Simics [35]. This is employed in the evaluation framework of this thesis described in Section 3.4.

#### Shared memory inter-process communication (IPC)

Shared memory IPC follows a different philosophy, which does not allow as much resource sharing as possible. Instead, this type imposes strict VA space protection among processes, while permitting one shared area, aptly called the "shared memory segment" (illustrated in Figure 3.1b). The only shared resource is this shared memory segment. A programmer may utilize this methodology by creating N processes with each one having a different VA space. The processes interact through the OS-granted shared memory segment. The N processes are not aware of each other's existence, because they are conventionally created by a "fork()" system call from the "shell." However, processes can communicate with each

other through the shared memory segment. The "POSIX shared memory segment" is an example of this methodology. One downside is that this programming type usually causes synonym problems when using VIVT caches. (One can easily verify this phenomenon by simply observing that each process uses a different VA pointer value to point to the shared memory segment.) While the VA pointers of the different processes will have different values, they still physically point to the same "shared memory segment" location.

The VIVT PLMD cache architecture proposed in this thesis work is targeted at the multi-threaded style (Figure 3.1a) of address space-sharing.

### **3.3 Implementation**

## 3.3.1 Manual Virtual Address Space Filtering

The PLMD cache is the quintessential embodiment of a "small-but-fast" cache that can satisfy the stack area requirement of high frequency accesses within a confined memory footprint. Moreover, owing to its small size, the PLMD cache can elevate system performance with minimal power overhead. Its VIVT cache structure can offer significant advantages over a PIPT equivalent. Most of the additional benefits emanate predominantly from the elimination of address translation:

- Larger allowed size for the "small-but-fast" cache: PIPT caches require address translation on every memory access. Therefore, the address translation path latency from the TLB to the cache would inevitably lower the maximum size that would still allow for a single-cycle hit. On the contrary, by removing the TLB access, a VIVT design enables larger cache sizes that are still able to achieve a single-cycle delay.

- Lower energy consumption: typically, the TLB has large (or full) associativity. This high associativity comes at the cost of energy expensive tag-matching operations. Instead, a VIVT cache can skip this process, as well as further overhead associated

with a TLB miss.

However, it is imperative to address the pathological scenarios of synonyms and homonyms, which incur undue overhead in typical VIVT caches. In an effort to extract all the inherent benefits of VIVT caches, while minimizing the adverse side effects, the PLMD helper cache manually filters out all VA spaces except one main VA space (process). Thus, the run-time stack areas of this lone process become the exclusive occupants of the PLMD cache. This design naturally favors modern workstation or server environments that run one primary and dominant multi-threaded workload. The proposed VA space filtering approach within the PLMD helper caches results in the following important attributes:

- No synonyms: the inter-process synonyms are created (shared) through the SM domain, while by definition, the PLMD are the spatial FSMOs which are isolated from the SM domain, due to the scope. Note that, even within one VA space, the intraprocess synonyms can still be deliberately created by the programmer, as described in [15, 16]. However, the PLMD are also free from this kind of synonym, due to their function frame stack scope.

- No homonyms: since other VA spaces (processes) are filtered out of the PLMD cache, they do not interfere with the selected, active VA space.

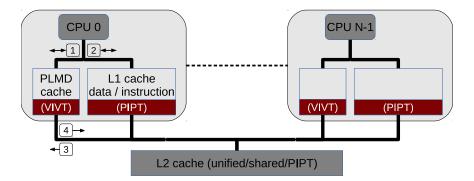

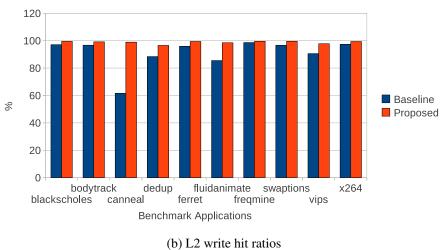

# 3.3.2 The Implementation of The Proposed VIVT PLMD Cache for Multi-Processors

Figure 3.2 illustrates the proposed mechanism. It depicts the location of the PLMD cache. The non-PLMD L1 data caches are implemented as physically indexed physically tagged (PIPT), whereas the accompanying PLMD caches are VIVT. It is important to note that the PLMD cache is small enough to guarantee a hit access latency of a single CPU cycle, while the regular L1 caches (Data/Instruction – for non-stack region) require two to three CPU cycles for a cache hit (in line with most L1 caches found in commercially available CPUs today). For example, the 32 KB L1 data cache of the Intel micro-architecture (codename

Figure 3.2: Implementation of the proposed VIVT PLMD cache for multi-core systems Sandy Bridge) has a 4-cycle access time [36].

# VA Space Filtering in Detail

The proposed VIVT PLMD cache revolves around the notion of VA space filtering. This technique allows one of the running applications to receive preferential treatment through an exclusive access to the PLMD cache. Any application can be chosen by the system administrator to receive this special status. Naturally, the selected application is one that tends to dominate all other running applications at a particular point in time. Once a program is granted this status, its VA space will be granted exclusive access of each core's PLMD cache in order to boost its overall performance.

This VA space filtering is achieved through the "cr3" register. The "cr3" register in the x86 architecture is the register pointing to a VA space's page table, and can be used as a unique VA space identifier. Hence, a system administrator can deliver a specific "cr3" register value to all the CPUs, in order to boost the performance of (potentially) one primary and dominant multi-threaded workload. This can be achieved through the invocation of a special command. Note, that this command is not a new ISA instruction, since the "cr3" register is already accessible to the programmer. Instead, operating system designers may create a new command that manages the newly proposed PLMD cache resources through the use of "cr3" register value manipulations. This command would, essentially, work in a fashion similar to the Unix "nice" command, which modifies the CPU scheduler priorities of all running processes in order to assign more CPU time to specific processes. Upon a change in the value of the "cr3" register, all VIVT PLMD caches flush their dirty cache lines into the Level 2 cache. This process prepares the PLMD caches to commence the handling of the newly selected VA space. The "cr3" VA space filtering mechanism was modeled in our evaluations using the Simics "Magic" instruction.

# L1 Data Memory Reference Stream Decoupling

During VA space filtering, data cache accesses are directed in two separate pathways (designated by the labels "1" and "2" in Figure 3.2). Pathway "3" in Figure 3.2 denotes line fetching from the L2 cache, caused by L1 PLMD cache misses that require TLB lookup. Pathway "4" in Figure 3.2 denotes dirty write-backs from the L1 PLMD caches to the L2 cache, which also require TLB lookup. The stack area memory references of the active VA space are directed to path "1" (i.e., to the PLMD cache), while all other memory references are directed to path "2" (i.e., the regular L1 data cache).

# 3.4 Evaluation

# 3.4.1 Simulation Limitation

This section evaluates the performance improvement and energy reduction coming from these architected-register-like features of the L1 PLMD helper caches: <sup>1</sup>

- The cache intends to handle only the decoupled spatial FSMO data which are isolated from the SM domain.

- The cache functions fast with single cycle latency.

- The caches are implemented in the VIVT architecture to significantly reduce TLB accesses

<sup>&</sup>lt;sup>1</sup>Due to the simulator limitation, the effect of full OoO execution opportunities (Section 3.1) of the PLMD helper caches is *not* evaluated.

| Simulation Configuration    |                     |                      |                                              |  |

|-----------------------------|---------------------|----------------------|----------------------------------------------|--|

| L1D Design (Regular + PLMD) | Component           | Size/Number          | Information                                  |  |

| Baseline (32 KB + 0 KB)     | L1 (data)           | 32 KB; 64 B; 2 way   | 3-cycle hit; write back/allocate             |  |

|                             | L1 (instruction)    | 32 KB; 64 B; 2 way   | 3-cycle hit                                  |  |

|                             | L2 (unified/shared) | 512 KB; 128 B; 8 way | 12-cycle hit; write back/allocate            |  |

|                             | Main Memory         | 2 GB                 | 218-cycle stall                              |  |

|                             | CPU Cores           | 8                    | Multi-threaded workloads each 16 sub-threads |  |

|                             | Coherence Protocol  | -                    | MESI                                         |  |

| Proposed (16 KB + 2 KB)     | L1 (data)           | 16 KB; 64 B; 2 way   | 3-cycle hit; write back/allocate             |  |

|                             | L1 (stack)          | 2 KB; 64 B; 2 way    | 1-cycle hit; write back/allocate             |  |

|                             | L1 (instruction)    | 32 KB; 64 B; 2 way   | 3-cycle hit                                  |  |

|                             | L2 (unified/shared) | 512 KB; 128 B; 8 way | 12-cycle hit; write back/allocate            |  |

|                             | Main Memory         | 2 GB                 | 218-cycle stall                              |  |

|                             | CPU Cores           | 8                    | Multi-threaded workloads each 16 sub-threads |  |

|                             | Coherence Protocol  | -                    | MESI                                         |  |

Table 3.2: The simulation configuration of the two designs under evaluation

# 3.4.2 Simulation Framework

In order to comprehensively evaluate the operational efficacy and efficiency of the proposed L1 PLMD cache, we employ Simics, a full-system simulator developed by Wind River [35]. Simics provides a "Magic" instruction that enables the simulated software on the target platform to deliver events to the simulator itself. The "Magic" instruction is incorporated as a special No Operation (NOP) instruction within the Simics's target ISA, and, hence, can be directly implemented in real computer systems. We use the "Magic" instruction to correctly acquire each multi-threaded benchmark's "cr3" register value, which is essential to the VA space filtering mechanism. The benchmark applications used in the simulations come from the PARSEC benchmark suite [37]. PARSEC is a popular benchmark suite containing parallel workloads from various emerging applications that are considered representative of next-generation shared-memory programs for multi-processors. Furthermore, all individual benchmarks can be executed in a multi-threaded mode and are, therefore, suitable for the proposed PLMD helper cache architecture for multi-processors.

The simulated target is the Simics "Tango machine" in a multi-core setting. This machine models an Intel Pentium 4 processor (x86-440bx machines). We simulate a system with 8 *processing cores* running the Fedora Core 5 Operating System (with Linux kernel 2.6.15, including SMP support).

## 3.4.3 Designs Under Evaluation

Two designs are compared, by using the full-system simulation framework; namely, a "Baseline" design and the "Proposed" architecture. The "Baseline" system serves as the reference point and employs a 32-Kbyte L1 data cache per core, which is *twice as large* as the one in the "Proposed" setup (i.e., 16 Kbytes per core). Of course, the "Proposed" design has an additional 2-Kbyte L1 VIVT PLMD cache, for a total of 18 (16 + 2) Kbytes of L1 data cache per core. Despite this unfair comparison that tilts strongly in favor of the baseline design, it will be demonstrated in the following sub-sections that the proposed design comfortably outperforms the generic architecture, despite the significantly smaller L1 data cache. Both the 32- and 16-Kbyte L1 data caches (of the baseline and proposed architectures, respectively) have a 3-cycle hit latency. The 2-Kbyte PLMD cache has a single-cycle hit latency, similar to the one proposed in [11]. Table 3.2 summarizes the two design configurations.

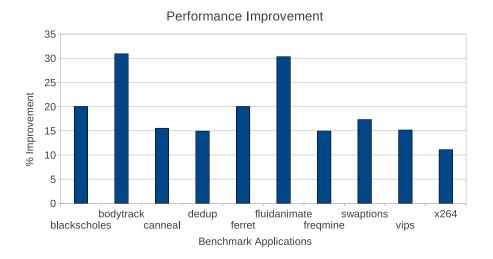

#### 3.4.4 Overall Performance Evaluation

Figure 3.3: Overall performance improvement over the baseline design

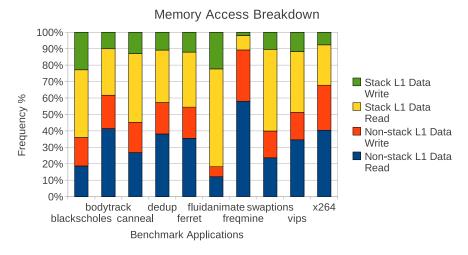

Figure 3.3 corroborates the prior assertions that the proposed VIVT PLMD cache instills dramatic performance improvements over the much larger L1 data cache of the baseline design. The (simple arithmetic) average overall performance improvement was found to be 19% for the 10 benchmark applications tested. Of course, the performance boost is attributed to the presence of the decoupled "small-but-fast" VIVT PLMD cache. Figure 3.4a depicts the breakdown statistics of the memory access patterns. One can notice the large percentage of accesses served by the PLMD cache. In fact, around 50% (on average) of all memory accesses can be directed to the small PLMD cache. Such a high percentage of accesses would easily justify the incorporation of the proposed VIVT PLMD cache in future multi-core systems.

# 3.4.5 TLB Access Behavior

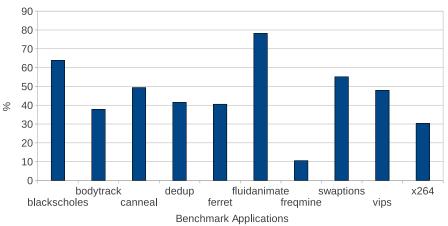

Figure 3.4a can also help us comprehend the TLB access behavior of the two designs, which is presented in Figure 3.4b. Since the PLMD cache read/write hit ratios are very high, the TLB access reduction percentages shown in Figure 3.4b are almost identical to the sum of the "Stack L1 Data Write" and "Stack L1 Data Read" portions in Figure 3.4a. It is important to note that the TLB access reductions in Figure 3.4b are a direct consequence of the VIVT PLMD cache hits, which obviate the need for TLB accesses. In fact, a TLB access is only needed in the infrequent cases of a PLMD cache read/write miss and a PLMD cache dirty write-back, (as illustrated by pathways "3" and "4", respectively, in Figure 3.2). On average, the proposed design reduces the amount of TLB accesses by 45.5%. This substantial reduction in TLB references will, in turn, translate into a reduction in energy consumption. As previously described in Section 3.3.1, TLB accesses are energy expensive, due to the high associativities that typically characterize TLB implementations.

# 3.4.6 L1/L2 Statistics Analysis (Multi-Level Benefits of PLMD Caches)

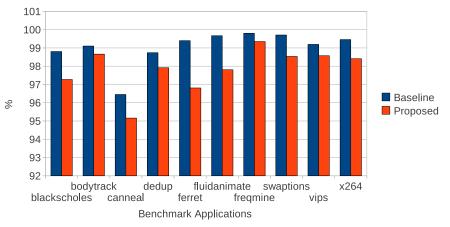

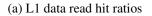

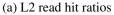

As expected from the smaller L1 data cache (18 KB vs. 32 KB) of the proposed architecture, the L1 data cache hit ratio is noticeably lower, as compared to the baseline design. Figure 3.5 illustrates the L1 data read/write hit ratios of the two evaluated configurations.

(a) Frequency breakdown of the memory area accesses

Reduced TLB accesses

(b) Reduction in TLB accesses in the proposed (16KB + 2KB PLMD cache) design over the baseline (32K and no PLMD cache) design

Figure 3.4: Memory access pattern analysis

In the case of the proposed design, the L1 ratios refer to the *combined* hit ratios of the regular L1 data cache *and* the PLMD cache. Naturally, the lower L1 data hit ratios in the proposed architecture result in increased L2 cache accesses.

L1 Data Read Hit Ratio

L1 Data Write Hit Ratio

(b) L1 data write hit ratios

Figure 3.5: L1 data cache read/write statistics of the two evaluated architectures

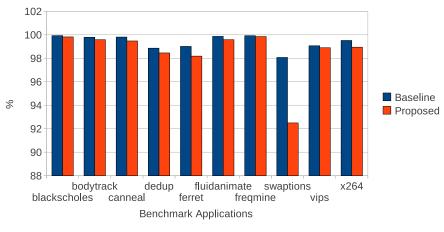

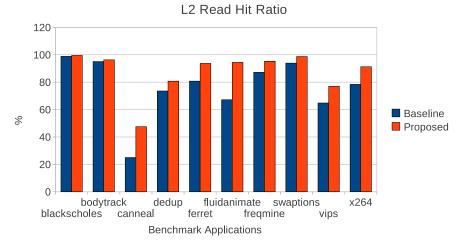

L2 Write Hit Ratio

Figure 3.6: L2 cache read/write statistics of the two evaluated architectures

Figure 3.6 shows the effect of the presence of the PLMD cache on the L2 cache behavior. Despite the elevated number of L2 cache accesses in the proposed design (caused by the lower L1 hit ratios), the existence of the PLMD cache beneficially alters the operational behavior of the L2 cache. As illustrated in Figure 3.6, all benchmark applications running on the proposed design experience increased read and write hit ratios in the L2 cache. This is because the PLMD cache's operation leads to the precipitation of a strong partitioning effect against data access thrashing between the L1 and L2 caches. This partitioning effect enables, for example, the "canneal" benchmark to exhibit an overall performance improvement of over 15%, even though it suffers from a relatively low L1 read hit ratio, as shown in Figure 3.5. This result is very important, since it showcases the *multi-level benefits* of the proposed PLMD cache. Its presence not only lowers the average L1 data cache hit latency, it also improves the performance of the L2 cache. Hence, the combined effect on overall performance far outweighs the reduction in L1 hit ratios (resulting from the smaller overall L1 regular data cache size).

### 3.5 Summary

The PLMD accesses have a profound effect on overall system performance, since application workloads tend to access the stack area data (i.e. the superset of the PLMD) at a very high frequency. It is apparent that contemporary ubiquitous CCSM multi-processor machines will continue to be front-runners in exploiting thread-level parallelism, in the future. Thus, it becomes imperative to devise a methodology that efficiently extends the architected registers in multi-processors, by making use of the spatial FSMO attribute of the PLMD. Toward this end, this thesis proposes the first PLMD cache architecture geared toward CCSM multi-core processors.

The presented PLMD cache employs a manual filtering technique that selects the run-time PLMD references of only one VA space (process) for caching into the per-CPU L1 VIVT helper caches. The filtering process very simply helps remove the synonym/homonym issue overheads and set-size limitations of VIVT caches, while, at the same time, it enables the extraction of all associated performance and energy advantages. The proposed PLMD cache mechanism is especially amenable to contemporary work-station and server systems that aim at running one primary and dominant multi-threaded application per machine.

The evaluation using a full-system simulation environment conclusively proves the efficacy and efficiency of the proposed VIVT PLMD cache for multi-core settings. Overall, this research certifies the viability of such helper PLMD caches in future CCSM multiprocessors and demonstrates their powerful capabilities.

## **CHAPTER 4**

# (PLMD 2) SUBTLETIES OF RUN-TIME VIRTUAL ADDRESS STACKS

The original research document of this thesis work was published in [7].

The run-time virtual address (VA) stack has some unique properties, which have garnered the attention of researchers. The stack one-dimensionally grows and shrinks at its top, and contains data that is seemingly local/private to one thread, or process. Accordingly, the optimization of accesses to local variables on run-time VA stacks has been widely investigated, focusing on these properties. Prior research indicates that real workloads tend to access the VA stack area with high temporal/spatial locality and within a small memory footprint [10, 2, 38, 11, 1]. This attribute directly stems from the fact that a process/thread always runs within a particular function (e.g., main()) whose frame is usually not very deep, and a stack simply grows and shrinks in one dimension at its top. Moreover, the VA stack data is assumed to be private to one thread/process.

These well defined attributes of the VA stack can be utilized to help improve the performance and energy/power consumption of the highest level of the memory hierarchy. The common practice of past work in this area is to first decouple the raw VA stack data from the entire data memory stream. However, the sophisticated behavior of contemporary operating systems (OS) and compilers not only prohibits this straight-forward data decoupling by VA, but it also invalidates the assumption that stacks are private to only one thread/process. This problematic phenomenon gives rise to potential function-critical hazards, which have (so far) been ignored in the literature. Hence, the behavior of run-time VA stacks should be fully investigated under the new light of contemporary OSes and compilers, so that its nuances do not lead to unexpected (at best), or incorrect (at worst) behavior.

This thesis work aims to demonstrate how conventional wisdom pertaining to the run-

time VA stack fails to capture some critical subtleties and complexities. It first explores two widely established assumptions surrounding the VA stack area. Then, it demonstrates why these assumptions are invalid, and highlights the potential hazards regarding data consistency, shared memory consistency, and cache coherence. Finally, it suggests safeguards against these hazards, which helps correctly filter and decouple the PLMD objects from the stack address space. Overall, the work explores the function-critical issues that future operating systems and compilers should address to effectively help reap all the benefits of using run-time VA stacks.

# 4.1 Contributions

## 4.1.1 Breaking Chain of a Widespread Erroneous Assumption

There is a widespread assumption underlying the run-time VA stack area memory references, which all major prior work depends upon, including [10, 2, 1, 3, 4, 11, 12]. Moreover, much of this work is interconnected, building on concepts developed by the others, so it was difficult to isolate the sources of the hazards. For instance, the Stack Cache [10] and Access Region Locality (ARL) [2] inspired the SVF technique [1], while the SVF technique (and possibly Reverse Integration [3]) inspired the SSP mechanism [4].