# Implementing and Programming Weakly Consistent Memories GIT-CC-95-12

A Thesis Presented to The Academic Faculty

by

Ranjit John

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Computer Science

**Georgia Institute of Technology** March 1995

# Implementing and Programming Weakly Consistent Memories GIT-CC-95-12

| Mustagua     | Ahamad, Chairman |

|--------------|------------------|

| rustaque 1   | Mamau, Chairman  |

| Gil Neiger   |                  |

| Umakishor    | e Ramachandran   |

| Karsten Sci  | hwan             |

| Divyakant .  | Agrawal          |

| Div y amario |                  |

## Acknowledgments

I would like to begin by expressing my gratitude to my advisor, Mustaque Ahamad. It was his guidance and encouragement which has made this thesis possible. I would also like to thank the members of my dissertation committee, Gil Neiger, Umakishore Ramachandran, Karsten Schwan and Divyakant Agrawal, for their time and helpful suggestions which have vastly improved this thesis.

Several people associated with the Clouds project have contributed with their assistance, ideas and coding: In particular, Sathis Menon who helped me find my bearings in the Clouds project and was always around when I needed help; R. Ananthanarayanan and Ajay Mohindra for the discussions on DSM related issues which to a great extent simplified my implementations.

I would like to thank my cubicle-mates Vibby Gottemukkala, M. Chelliah and Srinivas Doddapaneni for their companionship during the last five years. Also, Rida Bazzi for the late night tea sessions, while we were both writing our theses, where we argued about everything from the format of the thesis to life after school.

The work leading to this thesis was done in part with funding from the National Science Foundation and financial support from the College of Computing. Their assistance is gratefully acknowledged.

Finally, I would like to thank my parents who deserve the credit for encouraging me to continue studying through all these years. This thesis is dedicated to them.

## **Contents**

| A  | Acknowledgments |                                     |    |  |  |

|----|-----------------|-------------------------------------|----|--|--|

| Sı | ımm             | ary                                 | хi |  |  |

| 1  | Introduction    |                                     |    |  |  |

|    | 1.1             | Programming Distributed Systems     | 1  |  |  |

|    | 1.2             | Problem Statement                   | 3  |  |  |

|    | 1.3             | Organization of the Thesis          | 5  |  |  |

| 2  | Rel             | Related Work                        |    |  |  |

|    | 2.1             | Traditional Implementations         | 7  |  |  |

|    | 2.2             | Newer Approaches to building DSM    | 10 |  |  |

|    |                 | 2.2.1 Data-Annotation-Based Systems | 11 |  |  |

|    |                 | 2.2.2 Weakly Consistent Systems     | 12 |  |  |

|    |                 | 2.2.3 Weakly Ordered Systems        | 14 |  |  |

|    |                 | 2.2.4 Non-Page-Based Systems        | 16 |  |  |

|    | 2.3             | Why Causal Memory?                  | 17 |  |  |

| 3  | Cau             | ısal Memory                         | 20 |  |  |

|    | 3.1             | The Model                           | 20 |  |  |

|    | 3.2             | Synchronization Operations          | 23 |  |  |

|    | 3.3             | Defining Causal Memory              | 25 |  |  |

|    | 3.4             | Concluding Remarks                  | 27 |  |  |

| 4 | Pro | gramn  | ning on ( | Causal Memory                          | <b>28</b> |

|---|-----|--------|-----------|----------------------------------------|-----------|

|   | 4.1 | Data-  | Race-Free | e Programs                             | 28        |

|   |     | 4.1.1  | Linear I  | Equation Solver                        | 29        |

|   | 4.2 | Non I  | ata-Race  | -Free Programs                         | 33        |

|   |     | 4.2.1  | Asynchr   | onous Linear Equation Solver           | 33        |

|   |     | 4.2.2  | Distribu  | ted Calendar                           | 34        |

|   | 4.3 | Progra | ams with  | Incorrect Executions                   | 37        |

|   | 4.4 | Concl  | uding Rei | marks                                  | 38        |

| 5 | Imp | olemen | iting Cai | asal Memory                            | 40        |

|   | 5.1 | A Sim  | ple Owne  | er Based Protocol                      | 40        |

|   |     | 5.1.1  | Vector T  | 'imestamps                             | 42        |

|   |     | 5.1.2  | The Bas   | ic Algorithm                           | 42        |

|   |     | 5.1.3  | Correctr  | ness                                   | 46        |

|   |     | 5.1.4  | Limitati  | ons of the Owner Protocol              | <b>47</b> |

|   | 5.2 | A Pag  | e Based I | Protocol                               | 48        |

|   |     | 5.2.1  | Issues in | Scaling the Unit of Sharing            | 48        |

|   |     | 5.2.2  | Impleme   | entation Approach                      | 49        |

|   |     |        | 5.2.2.1   | Data Structures                        | 50        |

|   |     |        | 5.2.2.2   | Handling Page Faults                   | 51        |

|   |     |        | 5.2.2.3   | Vector Clocks and Timestamps           | 53        |

|   |     |        | 5.2.2.4   | Maintaining Data Consistency           | 54        |

|   |     |        | 5.2.2.5   | Synchronization Operations             | 55        |

|   |     |        | 5.2.2.6   | Reducing the Unnecessary Invalidations | 57        |

|   |     | 5.2.3  | Perform   | ance Analysis                          | 59        |

|   | 5.3 | Concl  | uding Rei | marks                                  | 61        |

| 6                        | Opt            | imizin | ng for Data-Race-Free Programs                        | <b>63</b> |

|--------------------------|----------------|--------|-------------------------------------------------------|-----------|

|                          | 6.1            | Causa  | al Memory and DRF Programs                            | 63        |

| 6.2 Causal Memory Implem |                | Causa  | al Memory Implementation Based on Vector Timestamps . | 64        |

|                          |                | 6.2.1  | Unnecessary Invalidations                             | 71        |

|                          | 6.3            | Causa  | al Memory Implementation Based on Versioned Pages     | 72        |

|                          |                | 6.3.1  | Page Fault Handling and Version Management            | 72        |

|                          |                | 6.3.2  | Maintaining Data Consistency                          | 75        |

|                          | 6.4            | Comp   | aring the Two Implementations                         | 76        |

|                          | 6.5            | Addit  | ional Optimizations                                   | 77        |

|                          |                | 6.5.1  | Avoiding Page Copying                                 | 77        |

|                          |                | 6.5.2  | Avoiding Page Transfers on Double Faults              | 78        |

|                          | 6.6            | Concl  | uding Remarks                                         | 78        |

| 7                        | Per            | forma  | nce Evaluation of Causal Memory                       | 80        |

|                          | 7.1            | System | m Descriptions                                        | 80        |

| 7.2 Applications         |                | Applie | cations                                               | 81        |

|                          | 7.3            | Perfor | rmance Metrics                                        | 85        |

|                          | 7.4            | Resul  | ts                                                    | 87        |

|                          |                | 7.4.1  | CGM                                                   | 89        |

|                          |                | 7.4.2  | TSP                                                   | 92        |

|                          |                | 7.4.3  | SOR                                                   | 97        |

|                          | 7.5 Discussion |        | ssion                                                 | 101       |

|                          |                | 7.5.1  | False Sharing                                         | 101       |

|                          |                | 7.5.2  | Causal Memory Implementations                         | 103       |

|                          |                | 7.5.3  | Scalability                                           | 104       |

|                          |                | 7.5.4  | Impact of Faster Processors and Network               | 105       |

|                          | 7.6            | Comp   | arison with Related Work                              | 106       |

|    |     | 7.6.1 Experimental Evaluation |

|----|-----|-------------------------------|

|    | 7.7 | Concluding Remarks            |

| 8  | Cor | nclusions and Future Work 112 |

|    | 8.1 | Conclusions                   |

|    | 8.2 | Future Work                   |

|    |     | 8.2.1 Synchronization         |

|    |     | 8.2.2 Fine Granular Sharing   |

|    |     | 8.2.3 Hardware Support        |

|    |     | 8.2.4 Size of Timestamps      |

| Vi | ta  | 124                           |

# **List of Figures**

| 1  | A PRAM execution                                                  | 18 |

|----|-------------------------------------------------------------------|----|

| 2  | An execution which is causal but not sequentially consistent      | 26 |

| 3  | Causal but not processor consistent execution                     | 27 |

| 4  | Synchronous iterative linear equation solver                      | 31 |

| 5  | Asynchronous iterative linear solver on causal memory             | 34 |

| 6  | Shared memory distributed calendar                                | 35 |

| 7  | Peterson's 2-process mutual exclusion                             | 37 |

| 8  | An execution history and processor views for Peterson's algorithm | 38 |

| 9  | Example to show causal over-writing of data                       | 41 |

| 10 | A simple owner protocol                                           | 44 |

| 11 | A weakly consistent execution                                     | 45 |

| 12 | An example to illustrate unnecessary invalidation                 | 47 |

| 13 | Causal memory implementation using vector timestamps              | 52 |

| 14 | The invalidate operator                                           | 55 |

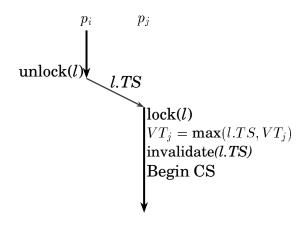

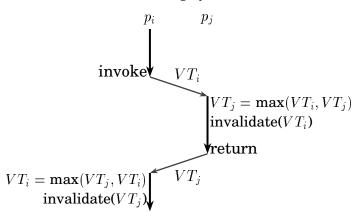

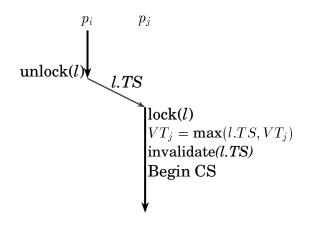

| 15 | Synchronization and Invocations                                   | 58 |

| 16 | Applications with annotations                                     | 59 |

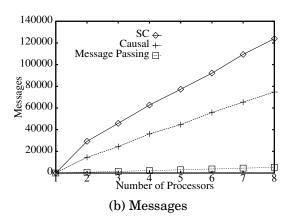

| 17 | Message counts for different memory models                        | 61 |

| 18 | Example to show why clock update is necessary on write faults .   | 66 |

| 19 | Causal memory implementation for data race free programs          | 67 |

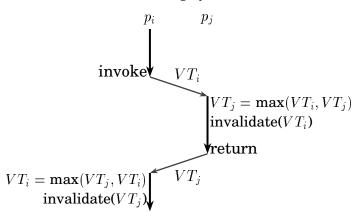

| 20 | Synchronization and Invocations                                   | 68 |

| 21 | Unnecessary invalidation of page containing data item $x$         | 71 |

| 22 | Causal memory implementation using versioned pages                | 73 |

| 23 | The invalidate operator for versioned pages   | 75  |

|----|-----------------------------------------------|-----|

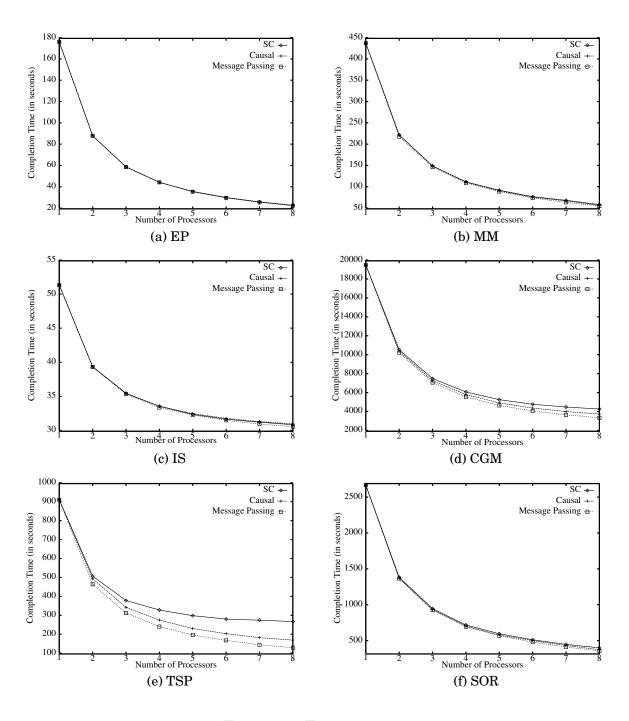

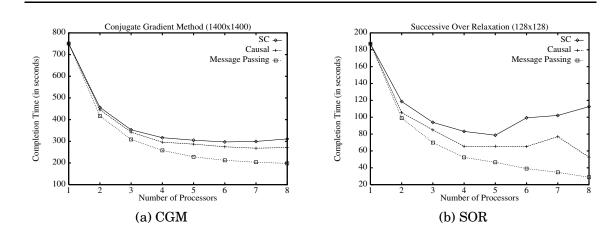

| 24 | Execution times                               | 88  |

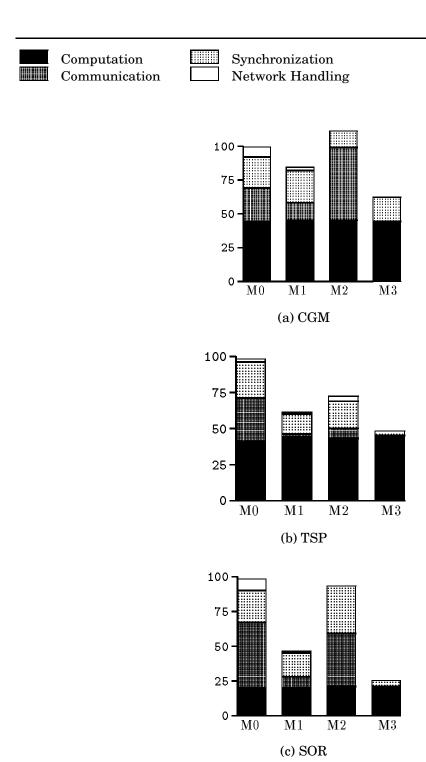

| 25 | CGM analysis                                  | 90  |

| 26 | Nodes visited in TSP                          | 94  |

| 27 | TSP analysis                                  | 95  |

| 28 | SOR analysis                                  | 98  |

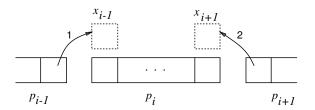

| 29 | Data sharing for SOR                          | 100 |

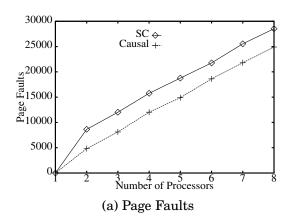

| 30 | Effect of false sharing                       | 103 |

| 31 | Comparing the two implementations             | 104 |

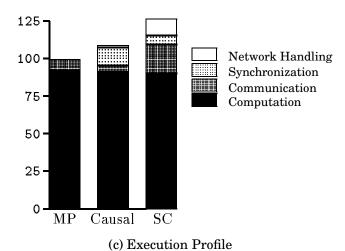

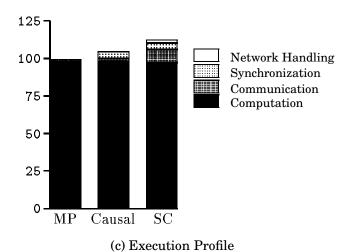

| 32 | Execution profiles (scaled to 100 for $M_0$ ) | 108 |

## **Summary**

A distributed operating system should provide abstractions that make it easy to program applications, provide good performance and allow applications to scale. Operating systems structured around message passing kernels typically ensure good performance and are scalable. On the other hand, Distributed Shared Memory (DSM) systems are much easier to program since the programmer need not be directly concerned with the data placement and data movement between processors.

The ease of programming applications using DSM comes at a cost. DSM systems usually replicate data for efficient implementations. Replication allows shared data to be accessed faster but introduces the problem of maintaining consistency among these copies. Early DSM implementations used variants of multiprocessor cache consistency algorithms that provided sequential consistency. These, however, do not perform very well in distributed systems where the message latencies are much higher.

Maintaining sequential consistency, which requires that all replicas are kept consistent, has been shown to limit performance. Weakly consistent memory models do not require that caches be kept consistent but control the inconsistencies so that most applications still run correctly.

This thesis explores a memory consistency model called causal consistency which provides weaker consistency guarantees than sequential consistency. Causal memory is a weakly consistent memory which requires that a read of a location return a value which is consistent with all causally preceding reads

and writes to that location. Many applications which execute correctly on a sequentially consistent DSM can run correctly without any change in code on a causal DSM.

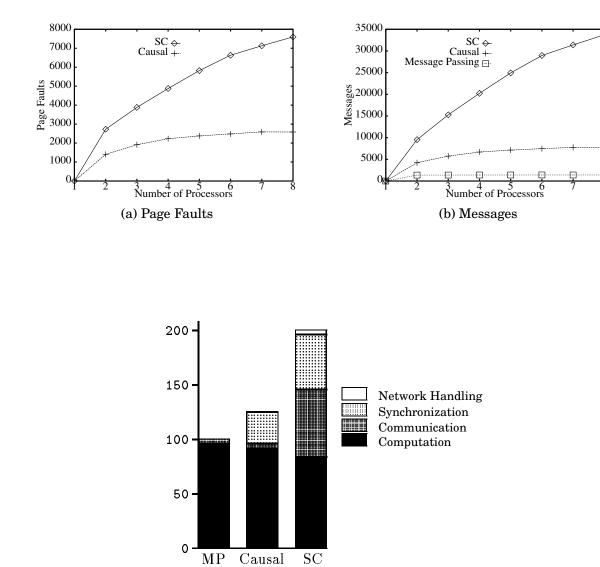

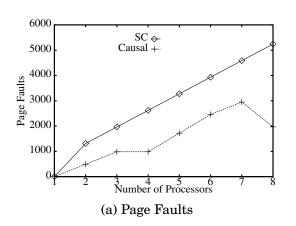

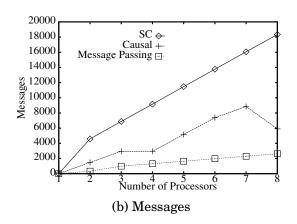

By programming applications that have a variety of data sharing patterns, it is shown that performance comparable to the message passing implementations of the applications can be achieved on the causal DSM system. The improved performance is due to a significant reduction (70-90%) in communication costs compared to the implementation of a sequentially consistent DSM system. These results show that causal memory can meet the consistency and performance requirements of many distributed and parallel applications.

## Chapter 1

#### Introduction

Computers are becoming faster, cheaper and commonplace. It is not unusual today to find workstations on every desk in an organization. When networked together, their cumulative computing power can provide performance at a cost much less than any equivalent centralized system. It is not surprising that much research is being targeted towards utilizing the computing power on the network to solve problems which were previously the exclusive domain of main-frames and super-computers.

A distributed operating system attempts to facilitate the sharing of computing and storage resources provided by these multiple autonomous computing elements. Such systems not only allow *resource sharing* but can also be used to provide *fault tolerance* and *parallelism*. To take advantage of these added benefits, distributed systems should allow programmers to write distributed applications without increasing the complexity of programming.

#### 1.1 Programming Distributed Systems

A distributed system consists of a set of processors connected by a communication network. A process is the computational entity at a processor. There could be multiple processes at a processor. A distributed application, in general, consists of a number of co-operating processes which execute on different

processors. Processors in a distributed system do not share memory and the interactions between them is through messages.

Programming a distributed application requires the specification of the computation at different processors and the interactions between them. Distributed operating systems provide the necessary abstractions to specify the computation and the interactions. Message passing, Remote Procedure Call (RPC) and Distributed Shared Memory (DSM) are a few of the programming abstractions commonly supported by distributed operating systems.

The early distributed systems were built with message passing as the underlying model for distributed computation. Amoeba [47] and the V system [18] are examples of message-based distributed systems. Message-based operating systems support processes that communicate via explicit message send and receive calls. Message-based systems require the programmer to pack data into a buffer which is given to the send call. The receive call receives this buffer and it is the programmer's responsibility to unpack and interpret the data. Such systems typically give good performance since the programmer controls the data placement and data movement between processors. However, programming is more complex since the programmer has to do the packing and unpacking of data and control explicitly the communication between the processors.

Remote Procedure Calls were proposed for remote communication, as it was felt that message passing as an abstraction was too primitive to provide to programmers of distributed applications. Cedar [48], Sun RPC [1] and Argus [42] are among several notable RPC-based systems which have been built. RPC-based systems support a procedural interface for executing remote operations where the actual packing of parameters and communication is hidden

away in library procedures. Similar to RPC's, object oriented systems use Remote Object Invocations (ROI) where communication between processors takes place by invoking a method on a remote object. In addition, ROI's allow the benefits of object orientation, namely encapsulation and inheritance to be exploited by application programmers. Spring [28] and Chorus [51] are examples of systems which provide ROI.

The procedural paradigm supported by RPC-based systems, however, is inadequate for programs which pass complex data structures, use global variables or have dynamic communication patterns. Another way of supporting distributed applications is based on providing a "virtual" shared memory across processors. Systems which support Distributed Shared Memory (DSM) provide a programmer with the illusion of a global shared memory across multiple processors. Kai Li's Ivy [39] system was the first instance of an implementation of DSM. Such systems simplify the programming of distributed applications since the programmer can make use of a uniform mechanism to access both local and remote data. They also allow programs written for shared memory multiprocessors to be ported fairly easily onto a network of workstations.

#### 1.2 Problem Statement

The abstractions provided by a distributed operating system should be efficient to implement, allow the system to scale and make it easy to program applications. Distributed operating systems structured around message passing kernels typically ensure good performance and are scalable since programmers can control the data placement and data movement. On the other hand, DSM systems are much easier to program since the programmer need not be directly concerned with data placement and data movement between processors.

The ease of programming applications using DSM comes at a cost. DSM systems usually cache or replicate data for efficient access. Replication allows shared data to be accessed faster but introduces the problem of maintaining consistency among these copies. Memory has to be kept consistent across processors since multiple processors could simultaneously read or write the same data item. Early DSM implementations used variants of multiprocessor cache consistency algorithms which provided *sequential consistency* [38].

Maintaining sequential consistency has been shown to limit performance. Several researchers have proposed memory consistency conditions which offer weaker guarantees than sequential consistency. Weakening the consistency guarantees provided by a memory system allows simpler and more efficient implementations of the memory system but on the other hand may also increase the complexity of programming applications. This thesis explores one such weakly consistent memory model called causal memory [5] and shows that it can be efficiently implemented and easily programmed. The goal of this thesis is to demonstrate that:

- Causal memory can be efficiently implemented and is a viable architecture for programming distributed applications.

- The execution of the applications on causal memory provides performance comparable to message passing systems for most applications.

- Scalable shared memory systems can be built using the causal memory model, since no form of global synchronization (e.g., messages which need to be sent atomically to all processors in a system) is required.

## 1.3 Organization of the Thesis

The rest of the thesis is divided into eight chapters. Chapter 2 discusses the related work. It starts by describing the Ivy system and then goes on to describe the newer approaches which have been proposed for building a high performance DSM system.

Chapter 3 motivates the need for weakening the memory consistency requirement and introduces causal memory. Causal memory is formally defined using a history based method by putting constraints on the allowable memory executions. Several examples are shown to illustrate how causal memory differs from other related memory models. Chapter 4 shows how to write programs for causal memory. It introduces a class of programs which would run on causal memory without any change in code. To illustrate, a linear equation solver and a distributed calendar service are programmed on causal memory. Also, examples are shown of programs which fail to execute correctly on causal memory.

Chapter 5 describes a simple protocol for implementing causal memory, which defines the consistency actions that need to be executed on access to each memory location, and argues its correctness. This protocol is used to develop a page based DSM system. Several optimizations are possible when programs are free of data races. For such programs, the consistency operations can be limited to certain synchronization points in a program. We show how the general implementation can be optimized if programs are known to be data-race-free in Chapter 6. We then give an alternative implementation which has the same structure as the previous protocols but optimizes on the earlier implementations.

Chapter 7 is a detailed experimental evaluation of the causal DSM. The

chapter describes the benchmark applications that were used and the performance metrics that were collected. The performance of the applications on three systems is reported; the first supports message passing, the second is a DSM protocol which is sequentially consistent and the third is the causal DSM protocol. Further, a performance comparison with other related work is reported. Chapter 8 concludes the thesis and also suggests possible directions for future work.

## Chapter 2

#### **Related Work**

Over the last decade, several researchers have described implementations of Distributed Shared Memories across a network of workstations. This chapter surveys the work which has been done in the area of DSM. The first instance of such an implementation was Kai Li's Ivy system [39]. Since then there have been several other implementations which extend the work done by Kai Li. The Ivy implementation is discussed first and then more recent work, which address some of the problems the early systems had, is described.

#### 2.1 Traditional Implementations

The Ivy system supported DSM across a local area network of Apollo workstations. DSM was supported by integrating the virtual memory mechanisms (page-faults and access rights to pages) with the consistency maintenance algorithms. The consistency maintenance algorithms manifested as page-fault handlers and server processes which handled the requests for a page.

Ivy supported sequential consistency, where the value returned by a read operation was the value written by the most recent write operation to the same address. Sequential consistency was maintained by restricting a page to a single writer or multiple readers at any time. This was done using a writer-invalidate-readers protocol where all the copies of a page are invalidated before

letting a processor write to a page.

To implement the protocol, the Ivy system introduced the notion of an owner and a manager. The owner of a page was the most recent processor which had write access to the page. The owner also maintained information about the processors that had a copy of the page. A manager processor knew the identity of the owner. The manager could be centralized or distributed. A centralized manager maintained a table which tracked the owners of all the shared pages. In the fixed distributed manager scheme, every processor is given a pre-determined subset of shared pages to manage. In the dynamic distributed manager scheme, each processor tries to keep track of the ownership of the page. This is achieved by using a field prob\_owner with every page. If a processor faults on a page, a request is sent to the prob\_owner. If that processor is the true owner, it sends the page, otherwise it forwards the request to the processor indicated by its prob\_owner field. By following the forwarding chain of pointers, the message would eventually get to the current owner.

On a read-fault, the fault handler sends a message to the owner of the page. The owner would respond by sending a copy of the page. If the owner had write access to the page, it would downgrade its access to the page to a read. On a write-fault, a similar message was sent to the owner which would then supply the page and the list of processors with read access to that page. The faulting processor would now invalidate all other copies of the page. This ensured that while a processor was writing to a page, no other processor could read from the page simultaneously.

The Mirage system [23] is an extension of the Ivy system where a processor could retain access to a page for a certain amount of time irrespective of pending requests for the page. This controlled page thrashing, where a page is moved between processors continuously preventing the processors from doing any

useful work.

The approach these early systems took was to adapt a cache consistency protocol developed for shared memory multiprocessors and implement it in software on a network of workstations. However distributed systems differ from multiprocessor systems in several respects and using a multiprocessor cache consistency protocol is inappropriate because of the following differences:

- **Message Latency** Accessing a page of memory which is not locally cached at a processor requires communication with some other processor. Message latencies on a multiprocessor are of the order of microseconds. In contrast, the message latencies in a distributed system are typically in the range of milliseconds. This leads to much lower processor utilization, since the process has to block while its page request is being serviced.

- Page as the unit of sharing The virtual memory page does not correspond to any logical entity in a program. This lead to the problem of *false sharing* where unrelated data may reside on the same page. Processors accessing data residing on different parts of a page would still cause contention for the page. Also, sending data in units of pages sometimes results in excessive communication when the size of the actual shared data is small compared to the page size.

- Use of multicasts/broadcasts These systems rely on multicasts or broadcasts to invalidate copies of pages. In multiprocessors, broadcasts are done in hardware. In distributed systems, multicasts and broadcasts are costly operations and do not scale well when there are a large number of processors.

• **Network Processor** — Multiprocessors have a separate network processor which handles requests from other processors without interrupting the CPU. In a workstation environment, the CPU has to be interrupted to service the network messages. In such an environment, messages do not just have the latency cost but in addition have the cost of traversing several software layers and context switching overheads.

The key to building a high performance DSM is to reduce the number of messages which need to be sent to maintain consistency of data. The next section discusses more recent work which addresses this problem.

#### 2.2 Newer Approaches to building DSM

More recently, many researchers have looked at the problem of providing a high performance and scalable DSM. Their work can be categorized into the following approaches which are discussed in detail:

- **Data-annotation-based systems** This approach is based on the fact that data movement protocols can be optimized if the data access patterns of the programs are known. These systems require the application programmer to annotate the data in the program based on their data sharing patterns.

- **Weakly consistent systems** This approach is motivated by the reasoning that sequential consistency is the bottleneck and weakening it would allow improved performance.

- **Weakly ordered systems** This approach unifies data transfer with synchronization. These systems require that the synchronization operations are made explicit to the memory system and consistency is only guaranteed at synchronization points.

- Non-Page-Based systems These systems provide consistency at the level of language level objects and require applications to be structured into objects or shared data structures which are made explicit to the underlying system.

#### 2.2.1 Data-Annotation-Based Systems

Accesses to shared data in parallel programs follow some common patterns. Bennett et. al. [13] analyzed the data sharing behavior of common parallel programs and found that the data accesses can be divided into the following categories: write once, private, write many, result, migratory, producer/consumer, read mostly and general read write.

The cost of maintaining consistency can be reduced if the knowledge of the data sharing behavior in an application is made available to the system. Instead of supporting one protocol, the data-annotation-based systems support multiple protocols each optimized for a particular kind of data sharing behavior. The Munin system [14] is a data-annotation-based system where the application programmer annotates the data in the program based on its access pattern. Accessing a particular data item causes the appropriate protocol for that data to be employed. The Munin system also handled the false sharing problem by allowing multiple writers to access a page and merging the changes at a later time. Allowing multiple writers on a page prevented contention for the page but required some mechanism for merging the changes

made by the multiple writers. Systems that require annotations provide good performance, but the application writer has the onus of providing the protocol specification for the data in the program.

#### 2.2.2 Weakly Consistent Systems

Several researchers [9, 41] have shown that a sequentially consistent memory cannot scale. This is because any implementation of sequentially consistent memory cannot avoid either a read or write operation from incurring the network latency cost of communicating with some other processor. Weakly consistent systems improve the performance of shared memory systems by weakening the consistency guarantees provided by the system. The weaker consistency does not guarantee that the execution of memory operations of all processes is equivalent to some sequential execution of these operations as in a sequentially consistent system. Examples of weakly consistent memory systems include *Pipelined RAM* (PRAM) [41], *processor consistency* [4, 24, 26], and *causal* memory [5].

PRAM - Lipton and Sandberg proposed a memory system, Pipelined RAM [41], which offered weaker consistency guarantees than sequential consistency. In a PRAM memory system, a read operation on a processor would just return the value in the local memory of the processor. A write operation on a processor would write the value to its local memory and then send a message about the write to all other processors. When another processor receives the write message, the write is applied to its local copy of memory. A PRAM memory guarantees that write operations by a processor are seen in the order they were executed by all processors. Writes from different processors can be seen in a different order by different processors.

**Processor Consistency** - Processor Consistency was proposed by Goodman [26] and a slightly different version was implemented by the DASH multiprocessor [4, 24]. Processor Consistency as defined by Goodman requires that the memory be PRAM consistent and coherent. Memory coherence is the property that all read and write operations to a single location in memory are observed in the same order by all processors.

Causal Memory - Causal memory was proposed by Hutto and Ahamad [30] and requires that all read operations return values which are consistent with all causally related reads and writes of that same location. The causal relation is similar to Lamport's *happens-before* relation [37] used to order events in a distributed system but applied to a shared memory environment. Two operations are causally related if they occur in program order or if one of the operations is a read and the other is a write and the read operation returns the value written by the write operation. The causal relation applies transitively. Write operations which are causally related are seen in the same order by all processors. Concurrent write operations can be seen in different orders by different processors.

To execute applications in such weakly consistent memory systems, either the applications must have data sharing patterns that are not effected by the weaker consistency or the program must explicitly deal with the lack of strong consistency. Programming on these memory systems is different from programming on a system supporting sequential consistency. All represent weakenings where it is no longer required that all processors agree on a global view in which all the memory operations occur in some serial order. Many programs written assuming sequential consistency, however, do run correctly on the weaker memory systems.

Several systems have been proposed which support multiple consistency

models. This is useful where applications or the data within the applications demand different levels of consistency. The Maya [3] and GARF [27] systems provide a DSM abstraction but do not enforce any particular consistency criterion. The Maya system offers a programming model called mixed consistency which supports both causal memory and pipelined RAM and provides explicit synchronization operations. The memory and synchronization operations can be tailored for efficient implementations of applications. The GARF system provides a library of consistency criteria and applications can bind to the appropriate library.

#### 2.2.3 Weakly Ordered Systems

One way to reduce communication between processors in shared memory system is to guarantee consistency only at certain points in the execution of a process. This approach was first outlined by Dubois et al. [21]. They observed that parallel programs define their own consistency requirements through the means of synchronization operations. They define a *weakly ordered* system, where synchronization operations are made explicit to the memory system, and consistency maintenance is done only at synchronization points. One of the earliest implementations where the data transfer is linked with the synchronization operations is reported in [50]. The DASH multiprocessor [24] is a weakly ordered system which implements a memory model called *release consistency*. Release consistency refined the weakly ordered approach by dividing synchronization operations into two types: acquire and release. Release consistency allows remote memory accesses to be propagated asynchronously, as long as they complete before a release operation (e.g., an *unlock* operation on a synchronization variable).

Weakly ordered systems require a certain behavior from application programs to ensure their correct execution. Such systems guarantee correct execution only for programs which are data-race-free [2] or properly labeled [24]. In other words, when these programs are executed on a sequentially consistent memory system, conflicting accesses to the same shared location (two writes or a read and write to the same location conflict) will always be separated by accesses to synchronization variables in the equivalent serial order. Since consistency is guaranteed at synchronization points, data-race-free programs can be written on weakly ordered memory systems assuming a sequentially consistent system.

Hardware implementations of weakly ordered systems use optimizations such as instruction reordering, pipelining and write buffering but still maintain a coherent cache. In contrast, software implementations sacrifice coherence by delaying consistency related operations to certain specific points in the program execution. The Munin system [14] implements release consistency in software, by delaying the propagation of the changes made inside a critical section till the lock is released. More recently *lazy release consistency* [33] and *entry consistency* [15] memory models have been proposed which use synchronization information to further reduce communication.

Lazy Release Consistency (LRC) - Release consistency requires that all processors are made consistent at the release of a synchronization variable. This is done in Munin by propagating all modified data to all the processors with a cached copy of the data. LRC is an optimization where the propagation of modifications is postponed until the time of the acquire. At this time, the acquiring processor determines which modifications it needs to see according to the definition of release consistency. LRC is implemented in the Tread-Marks [34] system at Rice University. No consistency actions are done at a

release. At an acquire, the processor doing the acquire has to make sure that its cache is updated correctly. LRC based systems send far fewer messages as compared to release consistent systems since modified data is propagated only to the next processor that acquires the synchronization variable.

Entry Consistency (EC) - Entry consistent systems require the explicit association of data with synchronization variables. This allows further optimizations since only the data associated with a synchronization variable needs to be made consistent. The Midway system [15] supports entry consistency. A special compiler keeps track of the data which has been modified inside of a critical section. The time of modification is kept track by attaching a Lamport's clock [37] with each shared data item. On an acquire, the acquiring processor sends the Lamport time of the data associated with the synchronization variable to the last releaser. The releaser sends all the modifications to data associated with the variable that were made since the acquirer's Lamport time. Entry consistent systems typically give performance very close to message passing implementations. However, programming applications is more involved as programmers have to explicitly associate data with synchronization variables and in some cases may have to include more synchronization operations into their programs.

#### 2.2.4 Non-Page-Based Systems

The Midway implementation is a non-page-based approach where the programmer is responsible for providing the information about the units of sharing. Applications on Midway are C or ML programs, extended with the data associations. Many programming languages allow related data to be encapsulated into objects, modules or other similar structures. In non-page-based systems

data is communicated in units of language objects instead of pages. If a processor accesses some part of an object, the whole object is moved to that processor as it is likely that the rest of the object would be accessed too. Orca [11] is another example of a shared memory system that maintains consistency at the level of language level objects.

#### 2.3 Why Causal Memory?

A large number of parallel applications exist which have been developed for shared-memory multiprocessors. Shared-memory multiprocessor vendors have typically relied on proprietary hardware which has not kept pace with the commodity processor technologies. The recent demise of multiprocessor manufacturers like Thinking Machines and Kendall Square Research further endorse this argument. With current processor speeds and increasing network bandwidths, networks of workstations provide a competitive price/performance alternative to shared-memory multiprocessors. DSM systems allow the parallel programs developed for shared-memory multiprocessors to be ported to a network of workstations without too much effort.

Using data-annotation-based systems, however, requires determining the data sharing behavior of these applications which would require a detailed understanding of the programs. Weakly ordered systems require a certain contract by the applications. Running applications which do not confirm to the contract can result in unexplained results. Non-page-based systems would require that the applications be rewritten as language level objects which would be a non-trivial task. Causal memory is interesting since, as we show later, it allows most applications to port without change in the code. This is not true for consistency conditions which are weaker than causal consistency.

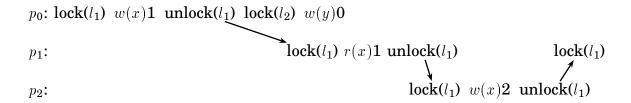

$$p_0$$

: lock $(l_1)$   $w(x)$ 1 unlock $(l_1)$   $p_1$ : lock $(l_1)$   $w(y)$ 1 unlock $(l_1)$   $p_2$ : lock $(l_1)$   $v(y)$ 1  $v(y)$ 1  $v(y)$ 1  $v(y)$ 1  $v(y)$ 2 unlock $(l_1)$

Figure 1: A PRAM execution

For example, consider a PRAM execution shown in Figure 1. When processor  $p_2$  reads the location y, it would read the value written by  $p_1$  as the write happened before  $p_1$  did the unlock. However, when  $p_2$  reads the location x, it is not guaranteed that it would see the write by  $p_0$ , leading to possible incorrect executions. This implies that either programs have to be rewritten to avoid such anomalies, or the synchronization operations have to be extended to enforce stronger semantics.

Another area where the causal semantics seem appropriate are cooperative distributed applications where users asynchronously interact to share data. Such applications include conferencing systems, distributed calendars etc. The sharing requirements of these applications usually do not require that modifications to shared data are seen at once or in the same order by all users. Causal consistency also seems appropriate for applications like mail agents and news readers. Consider the scenario where a user A sends a mail message to users B and C. B now responds to this message to A with a copy to C. We would ideally like C to receive A's mail before she gets the response from B. The response by B would not make any sense to C unless she has received the original mail. Current systems rarely support this level of consistency because of the overhead involved in guaranteeing this message delivery order for large systems. The ISIS [16] system provides a group communication

primitive called CBCAST which guarantees such causal delivery of messages within the group. The GARF system uses the CBCAST protocol to ensure causal consistency for shared objects. However, for page-based DSM systems, update-based protocols which rely on multicasts or broadcasts, do not scale well.

The next chapter defines causal memory more precisely. Later chapters show that programming is not complicated by the weaker consistency of causal memory and that it can be efficiently implemented.

## Chapter 3

## **Causal Memory**

There is at present no consensus on the best way of defining formally memory consistency models. Different researchers have used different approaches and notations which makes it difficult to compare the various memory models which have been defined in literature. Goodman [26] and Gharachorloo et. al. [24] used an operational characterization which lead to many misinterpretations [4]. Gibbons et. al. [25] used an automata based characterization for describing release consistency. Cekelov et. al. [55] used an axiomatic approach to formally describe Total Store Order (TSO) and the Partial Store Order (PSO). Both the automata based and axiomatic approaches have the formal rigidity but fail to provide an easy way of comparing different memory models. Initially, causal memory was defined [6] by characterizing the possible values that could be returned when a read operation is executed by a processor. A more general framework described by Ahamad et. al. [5] is used here, as it allows us to define and easily relate causal memory to a range of memory models that have been proposed.

#### 3.1 The Model

The model is motivated by the ones used by Misra [45] and by Herlihy and Wing [29]. A system is defined to be a finite set of *processors* that interact via a

shared memory consisting of a finite set of *locations*. Processors execute *read* and *write* operations. Each such operation acts on a named location and has an associated value. For example, a write operation executed by processor p, denoted by  $w_p(x)v$ , stores the value v in location x; a similarly denoted read operation,  $r_p(x)v$ , reports that v is stored in location x. The execution of a processor is defined by a *processor execution history*, which is a sequence of read and write operations. The execution history of processor p, denoted by  $H_p$ , is the sequence  $o_{p,1}$ ,  $o_{p,2}$ , ...,  $o_{p,i}$ , ... where  $o_{p,i}$  is the  $i^{th}$  operation issued by processor p. A *system execution history* is a collection of processor execution histories, one for each processor in the system. Thus, a system execution history  $H = \{H_p \mid p \in \mathcal{P}\}$  where  $\mathcal{P}$  is the set of processors in the system.

It is possible to establish orderings on the operations that appear in a system execution history H. The following orders are used in defining causal memory.

- **Program order:** For operations  $o_{p,i}$  and  $o_{p,j}$ , we say  $o_{p,i} \stackrel{po}{\to} o_{p,j}$  when  $o_{p,i}$  precedes  $o_{p,j}$  in the program, i.e., i < j. In this case, we say  $o_{p,i}$  is ordered before  $o_{p,j}$  by the program order. This defines program order to be total; it orders all operations of a given processor<sup>1</sup>.

- **Writes-before order:** If  $o_i$  (we drop the first subscript where it is unimportant) is a write to some location, and  $o_j$  is a read by a processor (which may be different from the writer), and  $o_j$  returns the value written by  $o_i$ , then  $o_i \stackrel{wb}{\rightarrow} o_j$ . We call this the writes-before order and it captures the natural requirement that if a read operation returns the value written by a certain write operation, then the write operation must be ordered

<sup>&</sup>lt;sup>1</sup>As defined here, program order totally orders the operations of each processor. In other memory models, the ordering between the local operations of a processor could be partial [24].

before the read.

- Causal order: The *happens-before* relation defined by Lamport [37] can be adapted to a shared memory system; this captures the causal relationship between the read and write operations. For any two operations  $o_1$  and  $o_2$  in H,  $o_1 \stackrel{c_0}{\rightarrow} o_2$  if

- $o_1 \stackrel{p_0}{\rightarrow} o_2$  or

- $o_1 \stackrel{wb}{\rightarrow} o_2$  or

- for some operation o',  $o_1 \stackrel{co}{\rightarrow} o'$  and  $o' \stackrel{co}{\rightarrow} o_2$ .

Ideally, a processor should be able to assume that a shared memory system executes a set of read and write operations one at a time, in a sequential order, and that the value returned by a read of location x was stored by the most recent write to x preceding the read in the sequential order. We call such an ordered sequence of memory operations the *view* of the processor. A memory model can be characterized by the types of views that result when processors execute with that type of memory system. For example, if the memory is sequentially consistent, all processors have a single view. Furthermore, the order in which the operations appear in the view is consistent with program order. Weakly consistent memories can be defined by allowing each processor to develop a different view. Views can be different because they may differ in the set of operations included in them, or in the order in which common operations appear in the views. By choosing the set of operations to be included in a processor view and the orders that must be maintained between them, implementation independent definitions of several memory systems can be developed [4, 36].

#### 3.2 Synchronization Operations

In parallel applications, communication between processors is not restricted to the messages generated by sharing of data. Processors also communicate to achieve synchronization and also when one process forks another process on some other processor. Synchronization is used to ensure that a sequence of memory operations (e.g., a critical section) are executed atomically. When a processor p acquires a lock released by another processor q, memory operations of q that precede the unlock operation on the lock, are ordered before memory operations of p that follow the operation in which the lock is acquired. In addition, parallel and distributed programs achieve parallelism by forking computation onto different processors. Domain decomposition is a commonly used method for developing parallel programs, where a "parent" process initializes the domains and then creates "child" processes on different processors, each working on a different partition. The semantics of fork assumes that the initializations done by the parent will be visible to the children. Similarly, at fork-joins, the programmer assumes that the changes made by the children will be visible to the parent. The synchronization and fork operations are typically implemented outside the memory system on distributed systems. However, these operations would create additional orderings between the memory operations.

The model can be extended to include the orderings induced by the synchronization and forking operations. Causal orderings would now arise between memory operations due to synchronization acquires and releases and also between the forking parent process and the forked child processes. We can now define the following orders induced between memory operations  $o_i$  and  $o_j$  by lock, barrier and fork-join operations (similar orders can be defined for

other synchronization constructs which are implemented outside the memory system).

- **Lock order:** We say  $o_i \stackrel{lo}{\to} o_j$ , when  $o_i$  and  $o_j$  are two memory operations such that  $o_i$  immediately precedes an unlock operation and  $o_j$  immediately follows the corresponding lock acquire. This order captures the orderings induced by read-write locks and semaphores.

- Barrier order: We say  $o_i \stackrel{bo}{\rightarrow} o_{k,j}$ , k = 1..n, when  $o_i$  immediately precedes a n-process barrier operation and  $o_{k,j}$  immediately follows the matching barrier operation in process  $p_k$ .

- **Fork order:** We say  $o_i \stackrel{f_o}{\rightarrow} o_j$ , when  $o_i$  immediately precedes a fork (or join) operation and  $o_j$  is the first memory operation executed by the forked child process (or after the join).

Let  $o_1 \stackrel{s_Q}{\to} o_2$  be the order induced by the synchronization operations. Two memory operations  $o_1$  and  $o_2$  are related by  $\stackrel{s_Q}{\to}$  if

- $o_1 \stackrel{p_0}{\rightarrow} o_2$  or

- $o_1 \stackrel{lo}{\rightarrow} o_2$  or

- $o_1 \stackrel{bo}{\rightarrow} o_2$  or

- $o_1 \stackrel{f_0}{\rightarrow} o_2$  or

- there exists an o' such that  $o_1 \stackrel{s_0}{\to} o'$  and  $o' \stackrel{s_0}{\to} o_2$ .

The causal order definition can now be extended to include these orderings. Two operations  $o_1$  and  $o_2$  in H are ordered by the *extended causal order*,  $o_1 \stackrel{eco}{\rightarrow} o_2$ ,

if  $o_1 \stackrel{co}{\to} o_2$  or  $o_1 \stackrel{so}{\to} o_2$  or for some operation o',  $o_1 \stackrel{eco}{\to} o'$  and  $o' \stackrel{eco}{\to} o_2$ . Causal memory can now be defined using this extended causal ordering  $^2$ .

## 3.3 Defining Causal Memory

Causal memory requires that values returned by read operations respect the extended causal order between memory operations. Since the effects of concurrent operations (operations not related by the causal order) can be observed in different order at different processors, causal memory allows each processor to develop a different view of shared memory.

Causal orderings between the operations of processor p and the operations of other processors are established when p reads values written by other processors. Since write operations update the state of shared memory and p's reads can return values written by other processors, a processor's view in causal memory needs to include all write operations. The causal ordering established by a read operation of processor p can propagate to another processor q but that happens only as a result of p writing a value that q reads (or through the synchronization and fork operations). Thus, the values that can be read by q are affected by only the write operations of other processors. As a result, p does not become aware of the read operations of other processors directly. This observation, coupled with the fact that orderings of operations in views must respect causality, leads to the following definition of causal memory. For system execution history H,  $H_{p+w}$  refers to the history resulting after read operations of all processors other than p are deleted from their processor execution histories.

<sup>&</sup>lt;sup>2</sup>Recently, the Maya system has also proposed a causal memory system that includes orderings induced by synchronization operations [3].

**Causal Memory** A history H is causal if, for each processor p, there is a  $view S_p$ , such that, for all operations  $o_1$  and  $o_2$  in  $H_{p+w}$ , if  $o_1 \stackrel{eco}{\rightarrow} o_2$  then  $o_1$  precedes  $o_2$  in  $S_p$ .

A memory system implements causal memory if all histories allowed by it are causal. The example execution in Figure 2(a) is possible with causal memory because the corresponding views (shown in Figure 2(b)) exist for each processor, as required by the definition of causal memory. We assume that all variables have an initial value of zero. This history is not sequentially consistent since both processors would not "agree" on a common sequence of operations (there is no single view that includes all operations and respects the program order established by each processor).

```

\begin{array}{lll} p_0: & w(x)\mathbf{1}\ w(y)\mathbf{2}\ r(z)\mathbf{0} & S_{p_0}: & w_0(x)\mathbf{1}\ w_0(y)\mathbf{2}\ r_0(z)\mathbf{0}\ w_1(z)\mathbf{1} \\ p_1: & w(z)\mathbf{1}\ r(x)\mathbf{0}\ r(y)\mathbf{2}\ r(x)\mathbf{1} & S_{p_1}: & w_1(z)\mathbf{1}\ r_1(x)\mathbf{0}\ w_0(x)\mathbf{1}\ w_0(y)\mathbf{2}\ r_1(y)\mathbf{2}\ r_1(x)\mathbf{1} \\ & \text{(a) Two Processor Execution} & \text{(b) Causal Views} \end{array}

```

Figure 2: An execution which is causal but not sequentially consistent

Causal memory differs from other weakly consistent memories. Figure 3 shows an execution that is permitted by causal memory which is not allowed by processor consistent memory as implemented by the DASH multiprocessor [24]. Causal memory allows concurrent writes to a memory location to be read in any order by different processors. The DASH implementation of processor consistency requires memory to be coherent, that is, writes to a single memory location are serialized and observed in the same order by all processors. For this reason, the execution would not be permitted by processor consistent memory. Pipelined RAM [41] is strictly weaker than causal memory

because it only requires that processors order two write operations in the same order in their views only if the writes are executed by the same processor.

$p_0: w(x)1$   $p_1: w(x)2$   $p_2: r(x)1 r(x)2$  $p_3: r(x)2 r(x)1$

Figure 3: Causal but not processor consistent execution

### 3.4 Concluding Remarks

This chapter developed a history based approach for formally defining causal memory. Causal ordering was defined as the transitive closure of the program order and the writes-before order. Synchronization and fork operations, which are normally implemented outside the memory system, cause additional orderings on the memory operations. The causal order was extended to include the effects of these non-memory operations. A memory was defined to be causally consistent if the values returned by read operations were consistent with the extended causal order. Causal memory is weaker than sequential consistency as it allows multiple processors to have different views of the memory operations. The following chapters show that causal memory can be easily programmed and that efficient implementations of causal memory are possible.

# Chapter 4

# **Programming on Causal Memory**

The weaker consistency of causal memory can provide more efficient implementations but it should not have an adverse impact on the ease of programming with DSM's. This chapter shows that programming with causal memory is not more complex than programming with sequentially consistent memory for a wide range of applications. These include data-race-free programs that employ synchronization operations to ensure atomicity of critical section code as well as applications which have data races but where causality introduces enough orderings between memory operations such that there are no concurrent writes. Towards the end, programs with data access patterns which do not execute correctly on causal memory are discussed.

## 4.1 Data-Race-Free Programs

In parallel and distributed programs where processes share data, access to data is controlled by synchronization operations. When programs use "sufficient" synchronization to control access to shared data, consistency maintenance can be limited to the synchronization points [52]. Adve and Hill [2] formalized this and introduced the notion of data-race-free programs. In these programs, conflicting accesses to a shared location by different processors (two accesses to a memory location conflict when they are not both reads) are always separated

by one or more synchronization operations. More precisely, all conflicting memory operations must be ordered by a happens-before relation,  $\stackrel{hb}{\rightarrow}$ , that is derived from program order and the order in which synchronization operations are executed. Data-race-free programs can be developed on causal memory the same way as on sequentially consistent memory. Thus, programming of this class of applications is not made more complex when we use causal instead of sequentially consistent memory. This is formally proved in [7]. Intuitively, it follows from the fact that writes to a location must all be ordered by the happens before relation,  $\stackrel{hb}{\rightarrow}$ , as there can be no conflicting writes. The extended causal order,  $\stackrel{eco}{\rightarrow}$ , includes all orderings induced by  $\stackrel{hb}{\rightarrow}$ , and hence it follows that writes to a single location must appear in the same order in all processor views. Since this holds for each location and causality is respected across memory operations, it can be shown that an execution of a program on causal memory is also possible on sequentially consistent memory. Thus, if a data-race-free program executes correctly on sequentially consistent memory, its execution on causal memory is also correct. We illustrate this next by showing that a linear equation solver, programmed assuming sequentially consistent memory, executes correctly even on causally consistent memory.

### 4.1.1 Linear Equation Solver

Very large systems of linear equations often arise in many scientific and engineering applications. Iterative methods such as the Gauss-Seidel algorithm are particularly amenable to parallelization. Iterative methods work in a sequence of phases. Each phase uses the results of the previous phase to generate a new, more accurate solution. Computation terminates when the result of the last phase passes a convergence test or has been computed to sufficient

accuracy.

Consider a parallel iterative algorithm that solves Ax = b, where A is a  $n \times n$  matrix and x and b are vectors of size n.  $a_{i,j}$  refers to the element of A in row i and column j and  $b_i$  (similarly  $x_i$ ) refers to the ith element of vector b (x).  $x_i^{k+1}$  represents the value of the ith component of x in phase k+1.  $x_i^{k+1}$  is computed using the following equation:  $x_i^{k+1} = \left(b_i - \sum_{j=1}^{i-1} a_{i,j} x_j^k - \sum_{j=i+1}^n a_{i,j} x_j^k\right) / a_{i,i}$ . A and b are inputs and remain constant but computing  $x_i^{k+1}$  requires access to all  $x_i^k$  ( $i \neq j$ ) from the previous iteration.

A parallel implementation of the iterative method partitions the tasks of computing the new  $x_i$ 's among available processes. At the beginning of each iteration, a process reads the results of the previous iteration from the shared global vector x and computes and stores the new  $x_i$  in a private local variable  $t_i$ . Since processes may proceed at different rates, a synchronous implementation requires processes to synchronize twice per iteration. Before beginning phase k+1, each process waits until all results from the previous phase have been copied to the global vector x. Then, before copying the newly computed value  $t_i$  to global  $x_i$ , each process waits until all other processes have completed computation of their new  $t_i$  (allowing the old  $x_i$  to be overwritten). Barriers are used to achieve this synchronization. Figure 4 shows the code for the linear equation solver.

There are N worker processes. The vector x is partitioned among the processes, such that, each process computes approximately an equal number of elements. As described previously, each worker process begins by assuming access to the previous (or initial) values in the global vector x and proceeds to compute and store the new value in the local variable  $t_i$ . The processes

<sup>&</sup>lt;sup>1</sup>It is possible to synchronize just once per iteration by having the processes read alternately from  $x_i$  and  $t_i$ , but we do not consider that here.

```

{f object} linear_solver \{

float A[n][n];

float b[n];

float x[n];

main()

initialize A & b;

create\ N\ worker\ processes;

worker(int from, int to, int n)

{

int i;

while (¬ converged())

\boldsymbol{for} \ (i = from; i < to; i++)

t_{i} := \left(b_{i} - \sum_{j=1}^{i-1} a_{i,j} x_{j} - \sum_{j=i+1}^{n} a_{i,j} x_{j}\right) / a_{i,i};

barrier();

\textbf{for} (i = from; i < to; i++)

x_i := t_i;

barrier();

}

```

Figure 4: Synchronous iterative linear equation solver

then synchronize at a barrier to ensure that all the processes would have computed the  $t_i$ 's. After synchronizing, the processes copy the new value  $t_i$  to the global  $x_i$  and goes through a similar barrier before resuming the next phase of computation or terminating.

The code in Figure 4 correctly solves the system Ax = b on both sequentially consistent memory and causal memory. Consider a read of some  $x_j$  by  $p_i$  in phase k, where  $x_j$  is in the partition of  $p_j$ . We need to show that the only value that may be correctly returned is the write to  $x_j$  by  $p_j$  in phase k-1. In other words, values from all earlier iterations are overwritten and causal memory behaves like sequentially consistent memory in this instance. Following our notation for  $x_i^k$ , we use superscripts on read and write operations to denote the phase in which the operation was performed. For example,  $w_i^k(x_i)v$  denotes a write of  $x_i$  by  $p_i$  in phase k. Consider the causal relations established between  $p_j$ 's write of  $x_j$  in phase k-2 and  $p_i$ 's read of  $x_j$  in phase k by the interactions between the two processes (i and j).

$$(1) \quad w_i^{k-2}(x_j)v \stackrel{po^*}{\to} w_i^{k-1}(x_j)v'$$

(2)

$$w_i^{k-1}(x_i)v \stackrel{bq}{\to} o_i$$

(3)

$$o_i \stackrel{po^*}{\to} r_i^k(x_j)v''$$

Above, (1) holds because the two writes happen in consecutive iterations on  $p_j$ . (2) relates the write to  $x_j$  in the (k-1)'th iteration to the first memory operation after the barrier on  $p_i$ . (3) holds because after  $p_i$  has checked for convergence, it reads the value of  $x_j$  in the next iteration (assuming that the convergence test fails). Taken together (1)–(3) imply that  $w_j^{k-2}(x_j)v \stackrel{co}{\to} w_j^{k-1}(x_j)v' \stackrel{co}{\to} r_i^k(x_j)v''$ . This ordering must be respected by the individual views of the processors and therefore the read operation on  $x_j$  in the k'th iteration must return the value written in the (k-1)'th iteration (i.e, v'=v''). Since we assumed an arbitrary

i and j, this argument shows that all reads of x in the computation return the value computed in the previous iteration, the same value returned when the computation is executed on sequentially consistent memory.

### 4.2 Non Data-Race-Free Programs

Several programs execute correctly on causal memory even when they have data races. These programs include applications where causality introduces enough orderings between memory operations such that there are no concurrent writes to a single location. The effect of such a data race is that a process could continue reading an old value of a data item residing in its cache. Some applications converge to a solution even with older values and some interactive applications can tolerate old values.

#### 4.2.1 Asynchronous Linear Equation Solver

It is possible to eliminate the synchronization entirely by using an asynchronous algorithm. The asynchronous algorithm is based on the observation that the iterative procedure may be used to improve close but inexact results. If we eliminate synchronization, processes may read, in a single phase,  $x_i$ 's computed in several previous phases. Fortunately, due to the error-correcting properties of the iterative method, the algorithm will still converge on the correct solution even when the  $x_i$  used to compute  $t_i^k$  are not all from the same iteration. All that is necessary is that processes never observe an  $x_i$  older than the values already read. This is precisely the property preserved by causal memory. Reads respect the order of causally related writes. An asynchronous iterative algorithm given in [12] is shown in Figure 5. The code works cor-

**while**

$$(\neg converged())$$

$x_i := \left(b_i - \sum_{j=1}^{i-1} a_{i,j} x_j - \sum_{j=i+1}^{n} a_{i,j} x_j\right) / a_{i,i}$

Figure 5: Asynchronous iterative linear solver on causal memory

rectly on both sequentially consistent and causal memory. However, unlike in sequentially consistent memory, each worker may execute different number of iterations as the new values propagate at different times and as a result the convergence test would not return true at the same time for all the processes.

#### 4.2.2 Distributed Calendar

Consider the problem of implementing a distributed calendar service. Every user in the system maintains an appointment calendar. The calendar is used to record appointments and daily schedules. In addition, we allow a user to browse through other people's calendars. We will not consider privacy of information issues; if it is a problem then data could be marked as private or public. Looking into someone else's calendar would only show the public information. Occasionally there could be a need to schedule a common meeting time for some group of people. We would also like a feature where a user is alerted if his/her calendar has been updated when someone schedules a meeting. The code for such a service is shown in Figure 6.

Access to a user's calendar is protected by a read-write lock. This is required since we allow users to update and browse any other person's calendar. <code>browse\_calendar</code> allows a user to look at anyone's appointment calendar by specifying the appropriate user-id. To bring up one's own calendar the user has to specify his/her user-id. The function <code>update\_calendar</code> permits one to add

```

object calendar {

calendar_type calendar[MAX_USERS];

lock mutex[MAX_USERS];

boolean changed[MAX_USERS];

browse_calendar(user_id i)

acquire_read_lock(mutex[i]);

display calendar;

release_lock(mutex[i]);

update_calendar()

acquire_write_lock(mutex[my_id]);

update entry in calendar;

release_lock(mutex[my_id]);

set_up_meeting(group_id group)

∀ members i in group

acquire_write_lock(mutex[i]);

insert entry into calendar of each member of group;

\forall i \text{ changed[i]} = \text{TRUE};

\forall i \ \mathbf{release lock}(\mathbf{mutex}[i]);

listener_daemon()

while(1) {

if (changed[my_id] == TRUE) {

beep();

changed[my_id] = FALSE;

sleep(NUM_SECS);

}

} // end of calendar object.

```

Figure 6: Shared memory distributed calendar

and delete appointments from one's own calendar. The function set up meeting is invoked when a user needs to schedule a group meeting. The locks are acquired in some pre-defined order to prevent deadlocks. The listener daemon is responsible for notifying a user that his calendar has been modified. It periodically reads a flag to determine if any change has been done to the calendar.

The data race happens since we allow the flag *changed* to be read without locking it first. While a process is reading the flag, another process could be concurrently updating the value of the flag, leading to the data race.

A user will see his/her updates to the calendar immediately. If someone else schedules a meeting, we need to show that the daemon would alert us of a change and if we bring up our calendar, it would have a record of the scheduled meeting. Since the daemon, keeps reading the flag *changed*, it would eventually see the value *true* and alert the user. The user would then use *browse\_calendar* to read the calendar. Before displaying the calendar, a read lock has to be obtained. Since all accesses to the calendar are guarded by a read-write lock, there can be no concurrent updates to the calendar and hence all processes must see the order of updates in the same order. The lock order would guarantee that the user sees the last update of his/her calendar.

Programming on causal memory is remarkably similar to programming on sequentially consistent memory, identical in fact, for the synchronous and asynchronous linear equation solver and the distributed calendar service.

```

var flag: array [0..1] of boolean;

turn: 0..1;

repeat

flag[i] = true;

turn = j;

while (flag[j] and turn == j);

critical section

flag[i] = false;

remainder section

until false;

```

Figure 7: Peterson's 2-process mutual exclusion

## 4.3 Programs with Incorrect Executions

There exist several programs which rely on a memory system being sequentially consistent for correct execution. Such programs include software solutions to the mutual exclusion problem. For example, the Peterson's two-process mutual exclusion algorithm [54] and Lamport's bakery algorithm [54] will not execute correctly on causal memory. We show here how Peterson's algorithm fails to provide mutual exclusion on causal memory.

Figure 7 shows the algorithm for achieving two-process mutual exclusion. To show that the above solution is incorrect on causal memory, consider the following execution history shown in Figure 8(a). This history is possible on a causally consistent memory as the two processes could have observed views as shown in the Figure 8(b). Since each process could see the value

```

p_0: w(flag[0])true\ w(turn)\mathbf{1}\ r(flag[1])false

p_1: w(flag[1])true\ w(turn)\mathbf{0}\ r(flag[0])false

(a) Execution History

```

```

S_{p_0}: w_0(flag[\mathbf{0}])true\ w_0(turn)\mathbf{1}\ r_0(flag[\mathbf{1}])false\ w_1(flag[\mathbf{1}])true\ w_1(turn)\mathbf{0}

S_{p_1}: w_1(flag[\mathbf{1}])true\ w_1(turn)\mathbf{0}\ r_1(flag[\mathbf{0}])false\ w_0(flag[\mathbf{0}])true\ w_0(turn)\mathbf{1}

(b) Processor Views

```

Figure 8: An execution history and processor views for Peterson's algorithm

of the *flag* variable as *false*, both would enter the critical section and mutual exclusion would not be preserved. A similar argument can be made for the Bakery algorithm that implements a solution to the n-process mutual exclusion problem.

### 4.4 Concluding Remarks

In this chapter, we investigated how to program applications on a memory system supporting causal consistency. Programming on a causally consistent memory system seems remarkably similar to programming assuming a sequentially consistent memory system. In fact, if a program is free of data races, it would run without any change in code on causal memory.

The synchronous linear equation solver is a data-race-free program. The asynchronous linear equation and the distributed calendar are both examples of programs with data races. They execute correctly as the former converges to a solution even with older values and the latter due to the interactive nature of the application can tolerate old values of the boolean variable *changed*.

There are, however, programs which do not execute correctly. The Peterson's algorithm and the Bakery algorithm require sequentially consistent memory for correct execution.

The next chapter discusses how to actually build a system supporting causal consistency. We will also analyze and compare the performance of the applications discussed here, in terms of the number of messages required for maintaining consistency of data, on a system supporting sequentially consistent memory and a causally consistent memory system.

# Chapter 5

# **Implementing Causal Memory**

This chapter investigates the problem of implementing a causal DSM. We first present a simple protocol to support a causally consistent shared memory. We initially restrict the implementation to programs in which processes only communicate via read and write operations to shared locations in memory. This allows us to study the issues involved in building a weakly consistent DSM. We extend this implementation to a page based DSM and introduce the actions which need to be performed at non-memory operations, namely the synchronization and forking operations. We then analyze the performance advantage, in terms of number of messages, of causal memory over sequentially consistent memory for some of the applications described in the last chapter.

### 5.1 A Simple Owner Based Protocol

We assume a system where the shared causal memory is partitioned among the processors. The locations assigned to a processor are *owned* by that processor. Each processor  $p_i$  has a local memory  $M_i$  indexed by location names (addresses). The locations owned by a processor are always stored in the local memory of that processor so that, if i = owner(x) then  $M_i[x]$  always contains a value of x. The remaining locations in a processor's local memory are used to *cache* copies of locations owned by other processors. The distinguished value  $\bot$  is

$p_0$ : w(x)1 w(y)1

$p_1$ : r(y)1 w(x)2 w(y)2

$p_2$ : r(x)1 r(y)2

Figure 9: Example to show causal over-writing of data

used to indicate that a processor does *not* possess a cached copy of a location. If  $M_i[x] = \bot$  then x is invalid (not cached) at  $p_i$ . Also, assigning  $\bot$  to a location  $(M_i[x] := \bot)$  invalidates that location at  $p_i$ . The locations owned by a processor can never be invalidated by that processor.  $C_i$  is the set of locations currently cached by processor  $p_i$ , that is, locations that are not owned by  $p_i$  and that are not invalid in  $M_i$ .

Causal orderings between memory operations at different processors are established when a processor reads a value written by another. Thus, each time a processor caches a data value written at another processor, it must ensure that the newly cached value is causally consistent with the data values already existing in its memory. In particular, any new causal orderings that get established by the reading of the newly cached data value must not cause the existing data to be over-written in the causal sense. In the example shown in Figure 9, when  $p_2$  caches the value of y written by  $p_1$  and reads it, the cached value of x at  $p_2$  has become over-written (the write to x by  $p_0$  causally precedes the write to x by  $p_1$ ), and the value 1 must not be returned by a future read to x by  $p_2$ . The implementation maintains correctness by invalidating cached copies that might violate causal memory correctness if read. This is done by detecting cached data which could be causally over-written each time a new value is introduced into the cache. Causally over-written data is detected using a mechanism called vector timestamps which is explained below.