### INVESTIGATION OF LIGHT INDUCED DEGRADATION IN PROMISING PHOTOVOLTAIC GRADE SILICON AND DEVELOPMENT OF POROUS SILICON ANTI-REFLECTION COATINGS FOR SILICON SOLAR CELLS

A Thesis Presented to the Academic Faculty

by

Ben M. Damiani

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical Engineering

> Georgia Institute of Technology April 2004

### INVESTIGATION OF LIGHT INDUCED DEGRADATION IN PROMISING PHOTOVOLTAIC GRADE SILICON AND DEVELOPMENT OF POROUS SILICON ANTI-REFLECTION COATINGS FOR SILICON SOLAR CELLS

Approved by:

Dr. Ajeet Rohatgi, Advisor

Dr. Russ Callen

Dr. Miroslav Begovic

Dr. Tom Gaylord

Dr. James Gole

Date Approved

## **DEDICATION**

This work is dedicated to

my mom Judith Damiani for supporting freedom of expression my brothers and sisters for inspiring me to learn, explore, and do good (Danny, Gabe, Donna, Tim, Debbie, Chrissie, Marie, and Tom) my wife, Jennie Damiani for her faith, encouragement, and love and my kids for the happiness they give me (Lucas, Ethan, and Bailey)

### ACKNOWLEDGEMENTS

I would like to express my gratitude to all the past and present members of the university center of excellence in photovoltaic research and education, UCEP, at Georgia Institute of Technology. I would like to express my sincere thanks to my advisor Dr. Ajeet Rohatgi for the incredible time commitment given to develop this thesis and for providing a truly exceptional research environment to learn in. I would like to thank Wayne Devezin, Dean C. Sutter, Ajay Upadhyaya, and Brian Rounsaville for their assistance in developing and maintaining the equipment used to fabricate and analyze the work in this thesis. I also want to extend my sincere appreciation to Denise Taylor for all her efforts to keep my research, travel, and other administrative tasks running smoothly. I would like thank to Dr. Thomas Krygowski and Dr. Abasifreke Ebong for guidance and advice. I would also like to thank Dr. Ralf Lüdemann for friendship and wisdom concerning this research. I would like to extend my sincere gratitude to all my fellow students for their friendship and dedication to photovoltaics, especially Ji-Weon Jeong, Alan Ristow, Vijay Yelunder, Mohamed Hilali, Jed Brody, Aleksander Pregelj, Kenta Nakayashiki, and Vichai Meemongkolkiat who assisted me in various aspects of this research. Finally I would like to thank my wife for her patience, inspiration, confidence, and support of this research through many challenges and accomplishments.

# **TABLE OF CONTENTS**

| DEDICATION                                                                       | . iii |

|----------------------------------------------------------------------------------|-------|

| ACKNOWLEDGEMENTS                                                                 | . iv  |

| LIST OF TABLES                                                                   | viii  |

| LIST OF FIGURES                                                                  | . ix  |

| SUMMARYx                                                                         | vii   |

| CHAPTER 1 Introduction and research objectives                                   | 1     |

| 1.1 Statement of Problem                                                         | 1     |

| 1.2 Specific Research Objectives                                                 | 5     |

| 1.2.1 Task 1. Investigation of trap formation conditions for the metastable      |       |

| defect that causes light induced degradation in Czochralski silicon              | 5     |

| 1.2.2 Task 2. Determination of the impact of the metastable defect on the        |       |

| efficiency screen-printed industrial solar cells.                                | 6     |

| 1.2.3 Task 3. Investigate light induced degradation trap formation conditions    | in    |

| low-cost multi-crystalline silicon solar cells                                   |       |

| 1.2.4 Task 4. Develop solar cell designs that reduce or eliminate the effects of | f     |

| light induced degradation in crystalline silicon solar cells.                    |       |

| 1.2.5 Task 5. Investigate low-cost texturing methods for multi-crystalline       |       |

| silicon solar cells.                                                             |       |

| 1.2.6 Task 6. Develop process sequence and fabricate high efficiency porous      |       |

| silicon etched solar cells.                                                      | 9     |

| CHAPTER 2 Solar Cell Fundamentals and Efficiency Limiting Mechanisms             | 10    |

| 2.1 Current and Voltage                                                          | 10    |

| 2.2 Fill Factor and Cell Efficiency                                              |       |

| 2.3 Carrier Lifetime and Recombination in Silicon                                | 14    |

| 2.3.1 Bulk                                                                       | 15    |

| 2.3.1.1 Shockley-Read-Hall Recombination                                         | 16    |

| 2.3.1.2 Radiative Band-to-Band Recombination                                     | 17    |

| 2.3.1.3 Auger Recombination                                                      | 18    |

| 2.4 Surface Recombination                                                        | 18    |

| CHAPTER 3 A review of texturing multi-crystalline silicon solar cells            | 21    |

| 3.1 Challenges in Texturing Multi-Crystalline Silicon                            | 21    |

| 3.2 Reactive Ion Etching                                                         | 23    |

| 3.3 Mechanical Grooving for Surface Texturing of mc-Si Solar Cells               | 28    |

| 3.4 Chemical Etching for Surface Texturing of Multi-Crystalline Wafers           | 30    |

| 3.4.1 Conventional Methods                                                       |       |

| 3.4.2 Discovery of Porous Si Formation                                           | 31    |

| 3.4.3 Porous Silicon Anti-Reflection Coatings                                    | 32    |

| 3.4.4 Porous Silicon Texturing and Anti-Reflection Coating for Multi-            |       |

| Crystalline Silicon Solar Cells                                                  |       |

| 3.4.5 Applications and Limitations of Porous Silicon for Solar Cells             |       |

| CHAPTER 4 Review of light induced degradation in Czochrlaski Silicon solar cells |       |

| 4.1 Industrial Solar Cells                                                       |       |

| 4.2 Light Induced Degradation in Czochralski Silicon Solar Cells                 | 48    |

| 4.2.1 Understanding of Light Induced Degradation and its Behavior                 | . 48 |

|-----------------------------------------------------------------------------------|------|

| 4.2.2 Structural Configuration of the Metastable Defect Responsible for LID.      | . 50 |

| 4.3 Lifetime Analysis of the Metastable Defect                                    | . 60 |

| 4.3.1 Illumination Intensity and Temperature Dependence of Efficiency             |      |

| Degradation                                                                       |      |

| CHAPTER 5 Improved Understanding of the Metastable Defect in Czochralski Silicor  | n70  |

| 5.1 Study of LID Under Simultaneous Generation and Annihilation                   | . 70 |

| 5.2 Light Induced Degradation Via Charged Carrier Transport                       | . 77 |

| 5.3 Effects of Light Induced Degradation on Low-Cost Crystalline Silicon Solar    | •    |

| Cell Performance                                                                  |      |

| 5.3.1 Electrical and Material Characteristics of Light Induced Degradation        | . 80 |

| 5.3.2 Understanding and Mitigation of Light Induced Degradation in Single         |      |

| Crystalline Silicon Solar Cells                                                   | . 84 |

| 5.3.3 Solar Cell Design Parameters to Reduce or Eliminate Light Induced           |      |

| Degradation Effect on Efficiency                                                  |      |

| 5.4 Conclusions                                                                   | . 99 |

| CHAPTER 6 Light Induced Degradation in Cast Multi-Crystalline and Ribbon          |      |

| Silicon                                                                           |      |

| 6.1 Efficiency Degradation in Industrially Screen-Printed Multi-Crystalline Silic |      |

| Solar Cells                                                                       |      |

| 6.2 Efficiency Degradation in Laboratory Photolithography Multi-Crystalline Sc    |      |

| Cells                                                                             | 107  |

| 6.3 Understanding and Investigation of Spatial Dependence of the Metastable       |      |

| Defect (Light Induced Degradation) in Cast Multi-Crystalline Silicon              |      |

| 6.4 Spatial Distribution of Light Induced Degradation in String Ribbon and Edg    |      |

| Defined Film-Fed Growth Ribbon Silicon                                            |      |

| 6.5 Impact of Ambient Conditions on LID in Ribbon Silicon Solar Cells             |      |

| 6.6 Conclusions                                                                   | 129  |

| CHAPTER 7 Understanding and Development of Porous Silicon Anti-Reflection         |      |

| Coatings by Stain Etching                                                         |      |

| 7.1 Development of Low-Cost Porous Silicon ARC by Stain Etching                   |      |

| 7.2 Novel Processing of Silicon Solar Cells with Porous Silicon Etching and DC    |      |

|                                                                                   | 137  |

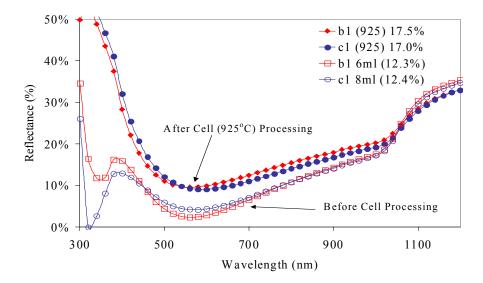

| 7.2.1 Formation of Porous Silicon and the Change of the Optical Properties        |      |

| Before and After Cell Processing                                                  |      |

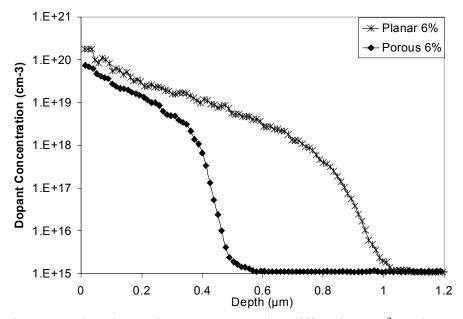

| 7.2.2 Surface Recombination Properties of Porous Silicon Emitter                  |      |

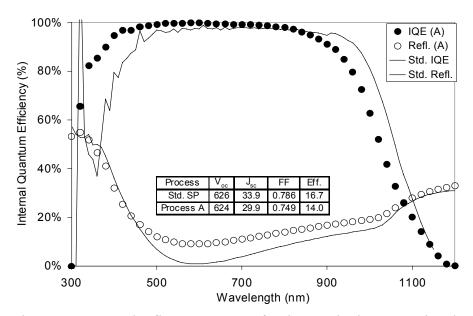

| 7.2.3 Porous Silicon Etched DOSS Solar Cells                                      |      |

| 7.3 Investigation and Optimization of Post-Processed Reflectance of Porous Sili   |      |

| Etched Solar Cells                                                                | 147  |

| 7.3.1 Implementation of Rapid Thermal Processing for Higher Efficiency            |      |

| Porous Silicon Textured Solar Cells                                               |      |

| 7.4 Conclusions                                                                   | 159  |

| CHAPTER 8 Improved Reflectance by a Combination of Acid Texturing and Porous      |      |

| Silicon Anti-Reflection Coating for Low-cost Crystalline Silicon Solar Cells      |      |

| 8.1 Characterization of Acidic Texture for Silicon Wafers Formed by Wire Saw      |      |

| 8.1.1 Formation of Porous Silicon Layer on Top of Acidic Texture                  | 165  |

| 8.2 Rapi      | d Thermal Processing of Low-Cost Czochralski and Cast Multi | -Crystalline |

|---------------|-------------------------------------------------------------|--------------|

| Silicon Solar | r Cells Using a Porous Silicon Anti-Reflection Coating      |              |

| 8.3 Effic     | iency Improvement of Low-Cost Czochralski and Cast Multi-C  | rystalline   |

| Silicon Solar | r Cells with Porous Silicon Anti-Reflection Coatings        |              |

| 8.4 Conc      | lusions                                                     | 178          |

| CHAPTER 9 C   | Suidelines for Future Research                              | 179          |

| 9.1 Futur     | re Research for Light Induced Degradation                   | 179          |

| 9.2 Futur     | re Research for Porous Silicon Anti-Reflection Coatings     |              |

| APPENDIX A    |                                                             |              |

| Measuremen    | It Theory                                                   |              |

| Lifetime      |                                                             |              |

| IQE           |                                                             | 191          |

| APPENDIX B    |                                                             | 192          |

| Clean         |                                                             | 192          |

| RTP anneal.   |                                                             | 192          |

| Diffusion     |                                                             | 192          |

| Front Contac  | ets                                                         | 193          |

| RTP Fire      |                                                             | 193          |

| Measure       |                                                             | 193          |

| REFERENCES    | 5                                                           | 194          |

| LIST OF PUB   | LICATIONS                                                   | 198          |

| VITA          |                                                             | 199          |

# LIST OF TABLES

| Table 1.  | I-V data for RIE multi-crystalline solar cells                                                                                                     | 26  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.  | I-V data for SiN coated solar cells                                                                                                                | 26  |

| Table 3.  | Impact of efficiency and direct manufacturing cost for crystalline silicon technology cost [\$/Wp]                                                 | 37  |

| Table 4.  | LID characteristics of various single crystal Si materials                                                                                         | 81  |

| Table 5.  | PC1D simulation settings                                                                                                                           | 84  |

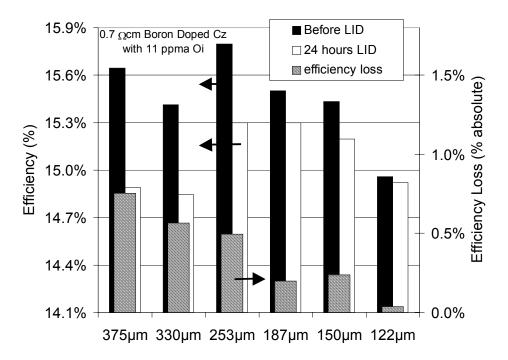

| Table 6.  | Light Induced Degradation in $V_{oc}$ , $J_{sc}$ , and Efficiency of B doped Cz cells with varying thickness.                                      | 96  |

| Table 7.  | Interstial oxygen O <sub>i</sub> concentration in promising crystalline Si materials [49,50].                                                      | 105 |

| Table 8.  | Efficiency degradation after 3 days illumination of ~0.5 suns for various efficiency mc-Si wafers                                                  | 109 |

| Table 9.  | Best porous silicon solar cell results for photolithography (PL) and screen-printed porous silicon solar cells. *Confirmed at Sandia National Labs | 145 |

| Table 10. | Cell efficiency performance for various surface treatments on cast mc-Si wafers                                                                    | 173 |

| Table 11. | List of positive and negative attributes for Cz Si solar cells fabricated with each process sequence developed at Georgia Tech                     | 175 |

| Table 12. | Lighted I-V parameters for screen-printed solar cells fabricated using<br>Process A and Process D for cast mc-Si and Cz Si solar cells             | 176 |

# **LIST OF FIGURES**

| Figure 1.  | Cost associated with solar cell fabrication for screen-printed technologies for single and multi-crystalline silicon                                                             | 2  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.  | Model of depletion region, space charge density, and Electric field.                                                                                                             | 10 |

| Figure 3.  | a.) Current-Voltage curve under light bias, FF is shaded region b.)<br>Equivalent circuit                                                                                        | 12 |

| Figure 4.  | a.) Shockley Read Hall recombination b.) Radiative recombination c.) Auger recombination                                                                                         | 15 |

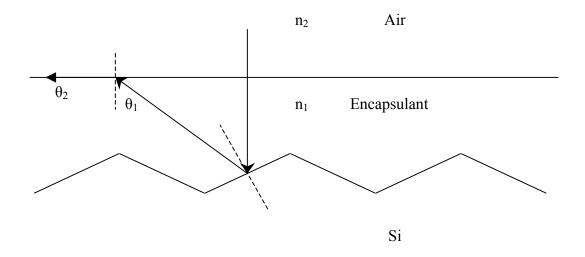

| Figure 5.  | Total internal reflection schematic for a textured solar cell                                                                                                                    | 22 |

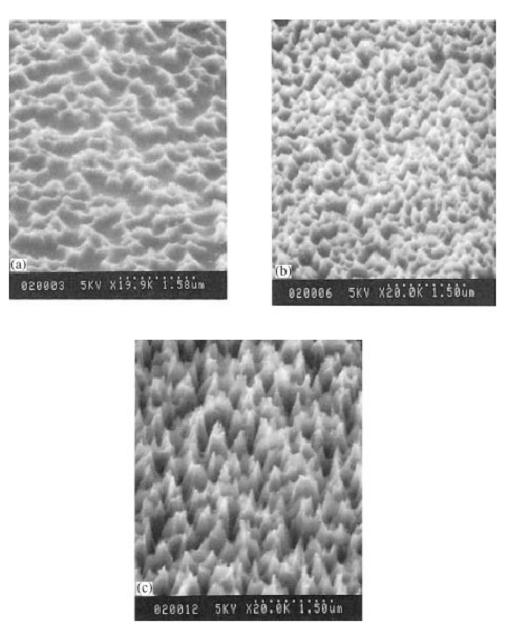

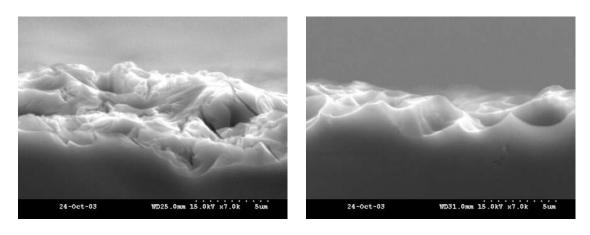

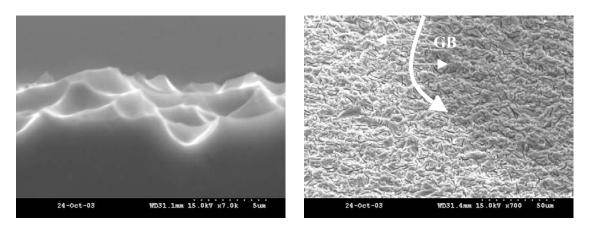

| Figure 6.  | SEM pictures of RIE-textured material with different $Cl_2$ flow ratios                                                                                                          | 24 |

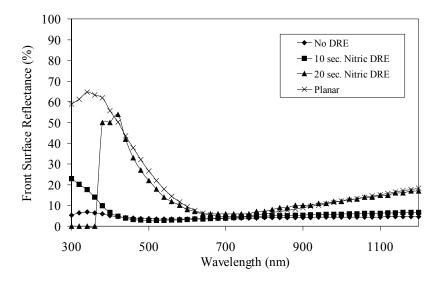

| Figure 7.  | Front surface reflectance curves for RIE textured + SiN ARC on multi-crystalline solar cells with varying damage removal etching schemes applied.                                | 27 |

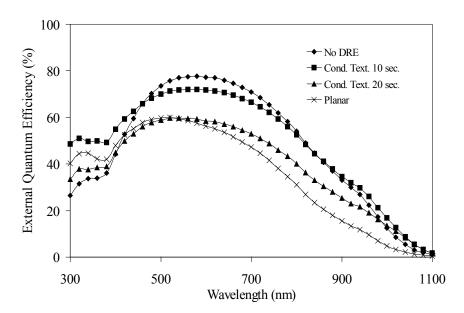

| Figure 8.  | External Quantum Efficiency of RIE textured samples with different Damage Removal Etches applied                                                                                 | 27 |

| Figure 9.  | Multi-blade V-grooving technique and resulting surface structure with feature size from trench to peak of 3-4 $\mu$ m                                                            | 29 |

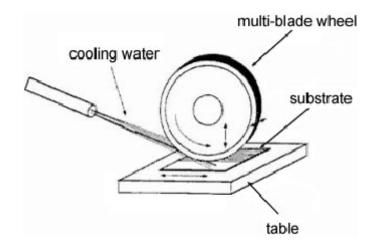

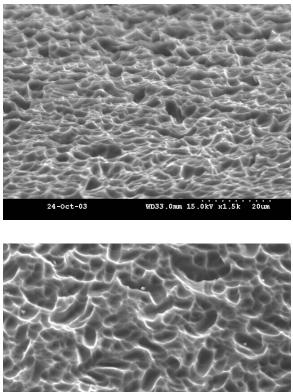

| Figure 10. | SEM image of isotropic acid texture on a mc-Si surface. Bottom picture is normal to the surface. The top picture is a view of the surface at slight angle.                       | 31 |

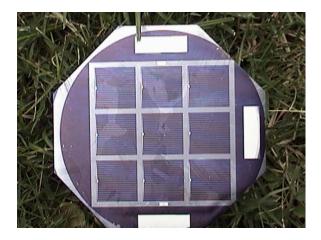

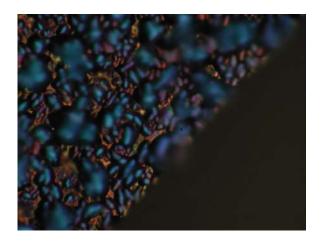

| Figure 11. | A porous silicon etched mc-Si solar cell fabricated using<br>photolithography contacts. No dependence on grain orientation and<br>the color uniformity was good to the naked eye | 34 |

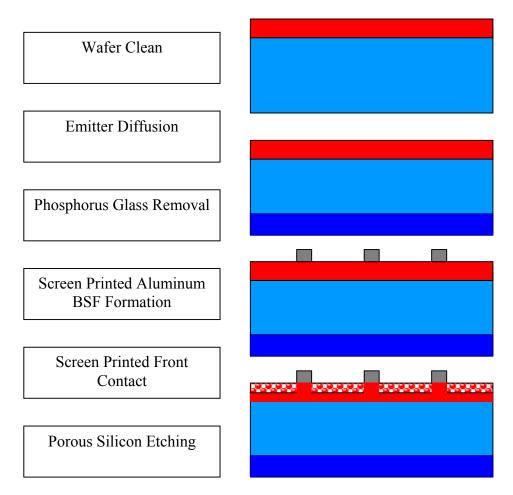

| Figure 12. | Typical process steps for a porous silicon ARC solar cell                                                                                                                        | 39 |

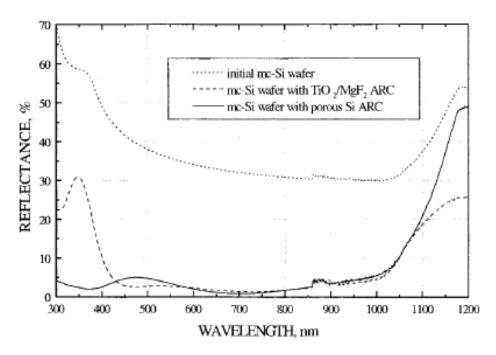

| Figure 13. | Reflectance characteristics of non-textured mc-Si wafer after PS formation by stain etching and pre-textured mc-Si wafer with DLARC.                                             | 41 |

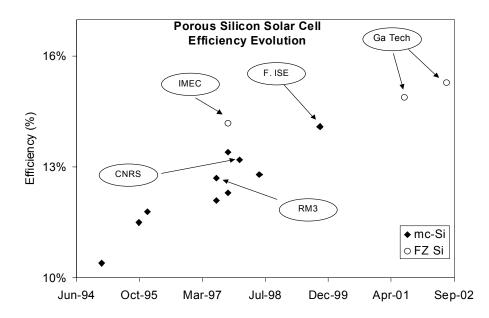

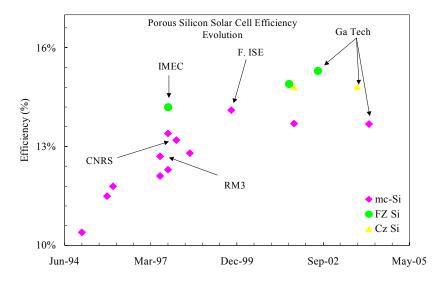

| Figure 14. | Efficiency evolution for all solar cells using porous silicon as part of the solar cell design [33,39]                                                                                                                                                                                                                                                                                                                                                            | 42 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

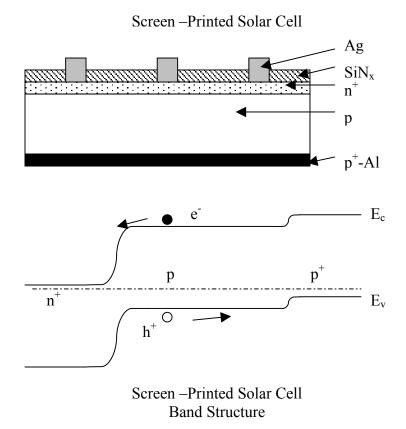

| Figure 15. | Schematic of industrial solar cell structure and associated energy band diagram                                                                                                                                                                                                                                                                                                                                                                                   | 47 |

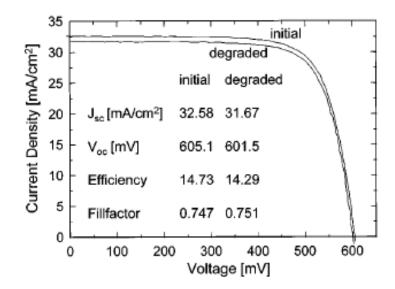

| Figure 16. | Change in I-V characteristics after 30 minutes illumination at 0.1 $mW/cm^2$ and 25°C.                                                                                                                                                                                                                                                                                                                                                                            | 49 |

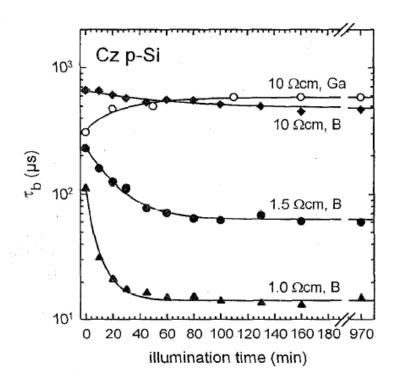

| Figure 17. | Bulk lifetime degradation in B doped Cz Si increasing with time but not in Ga doped Cz Si                                                                                                                                                                                                                                                                                                                                                                         | 51 |

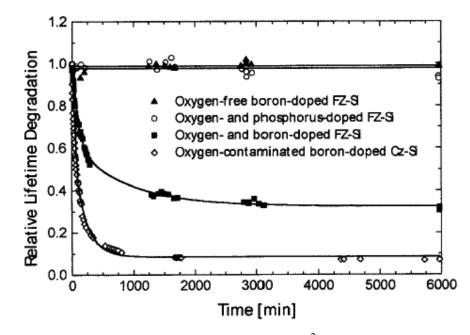

| Figure 18. | Lifetime degradation by $0.5 \text{ m}\Omega/\text{cm}^2$ white light verse time. Boron, Phosphorus and Oxygen doped FZ as well as B doped Cz Si samples exposed to carrier injection.                                                                                                                                                                                                                                                                            | 52 |

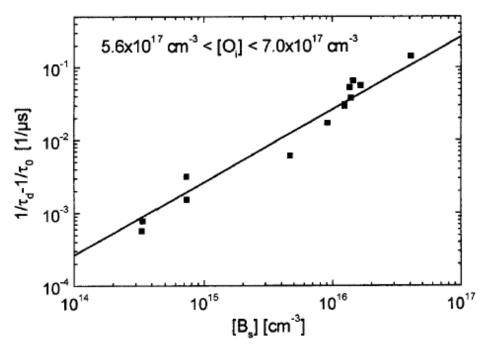

| Figure 19. | $1/\tau_d$ - $1/\tau_o$ (proportional defect concentration) vs boron concentration for Cz Si wafers with O <sub>i</sub> between $5.6 \times 10^{17}$ and $7.0 \times 10^{17}$                                                                                                                                                                                                                                                                                     | 54 |

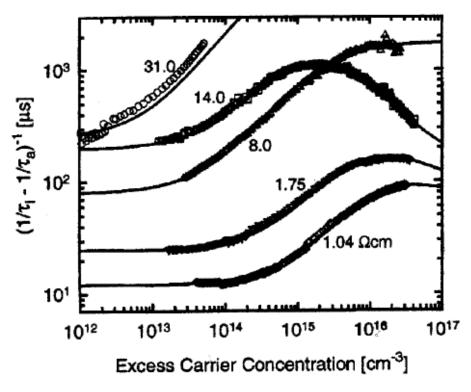

| Figure 20. | Measured injection level dependence of $\tau_d$ on excess carrier concentration for various resistivity Cz Si samples (using SRH theory).                                                                                                                                                                                                                                                                                                                         | 56 |

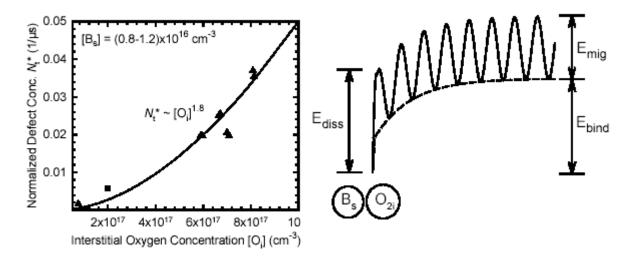

| Figure 21. | Normalized defect concentration $N_t^*$ as a function of $O_i$ concentration which supports the defect model proposed for the $B_sO_{2i}$ interaction.                                                                                                                                                                                                                                                                                                            | 58 |

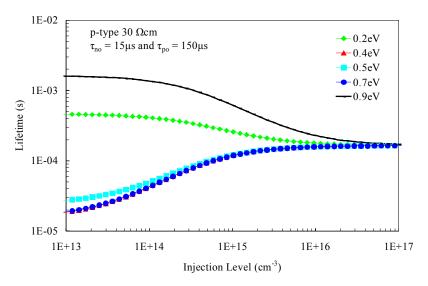

| Figure 22. | Shockley-Read-Hall lifetime versus injection level for various trap energy levels.                                                                                                                                                                                                                                                                                                                                                                                | 62 |

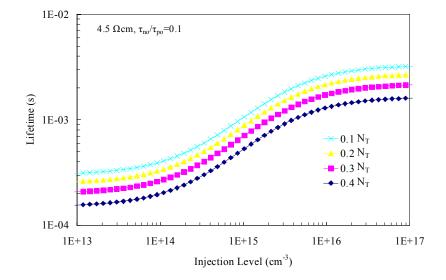

| Figure 23. | Shockley-Read-Hall lifetime verse injection level for various trap concentration $N_T$ values                                                                                                                                                                                                                                                                                                                                                                     | 62 |

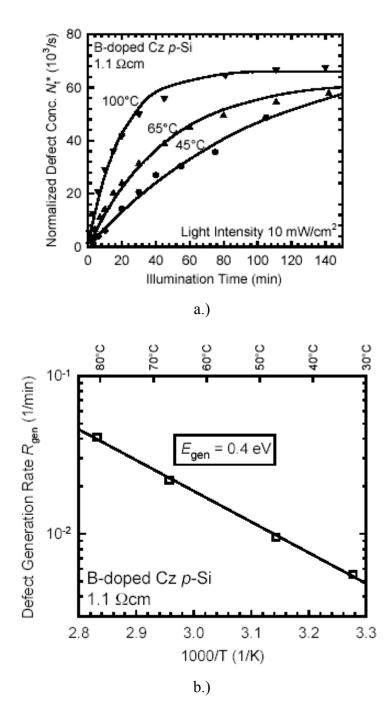

| Figure 24. | a.) Isothermal measurements of the time-dependent normalized defect concentration $N_t^*(t)$ . Between each measurement, the sample was illuminated with a halogen lamp at 0.1 suns at temperatures ranging from 45 to100°C [64] b.) Isothermal measurements of the time-dependent normalized defect concentration $N_t^*(t)$ . Between each measurement, the sample was illuminated with a halogen lamp at 0.1 suns at temperatures ranging from 45 to100°C [64] | 65 |

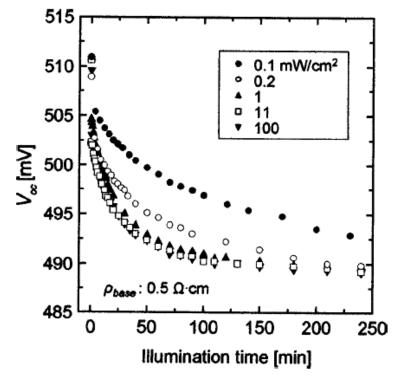

| Figure 25. | $V_{oc}$ decay curves of solar cell with base resistivity of 0.5 $\Omega$ cm under illumination of various intensities [20]                                                                                                                                                                                                                                                                                                                                       | 67 |

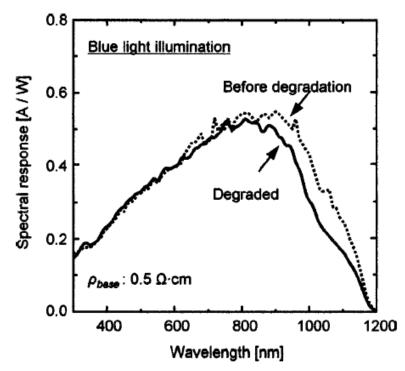

| Figure 26. | Spectral response degradation of a solar cell with a base resistivity $0.5 \Omega$ cm under a blue light illumination for 6 hours [20]                                                                                                                                                                 | 68 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

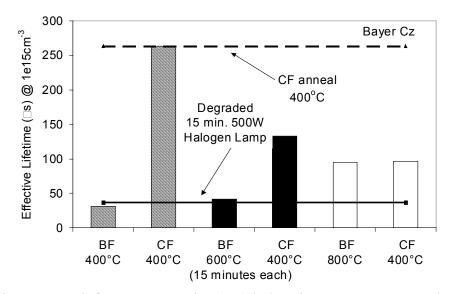

| Figure 27. | Belt furnace processing (BF) induced LID at 400,600, and 800°C in Cz sample followed by conventional furnace (CF) recovery at 400°C.                                                                                                                                                                   | 73 |

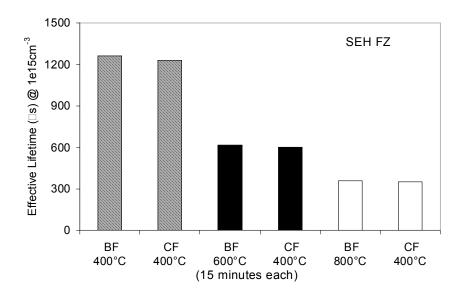

| Figure 28. | Surface passivation performance on FZ samples at 400, 600, and 800°C in a belt furnace (BF) followed by a conventional furnace (CF) anneal or recovery at 400°C.                                                                                                                                       | 73 |

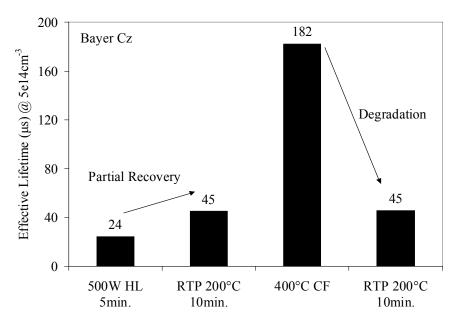

| Figure 29  | RTP LID cycling revealing partial recovery after halogen lamp (HL) heating at 200°C as well as partial degradation following a CF anneal.                                                                                                                                                              | 75 |

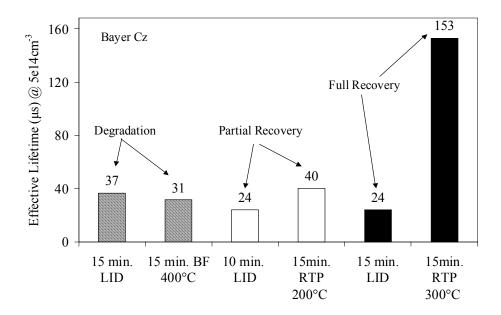

| Figure 30. | RTP LID partial recovery at 200°C and 300°C preceded by LID and BF partial degradation at 400°C                                                                                                                                                                                                        | 76 |

| Figure 31. | Photoluminescent map of a half wafer of B doped Cz Si subjected to shading by a aluminum block on the bottom ~42-43 mm of the wafer. LID confined predominantly to the illuminated region                                                                                                              | 78 |

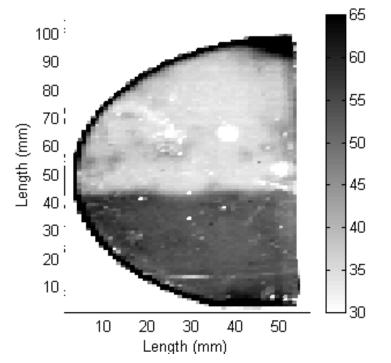

| Figure 32. | Change in effective lifetime (arbitrary units) along the vertical line<br>at 35 mm showing the transition from the illuminated side of a B<br>doped Cz wafer that suffered localized degradation to the shaded<br>region. The transition region was from ~42 mm to ~46 mm on the y<br>axis in Fig. 31. | 79 |

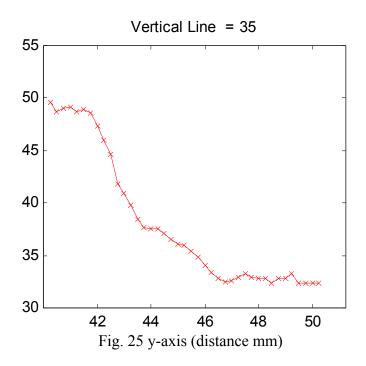

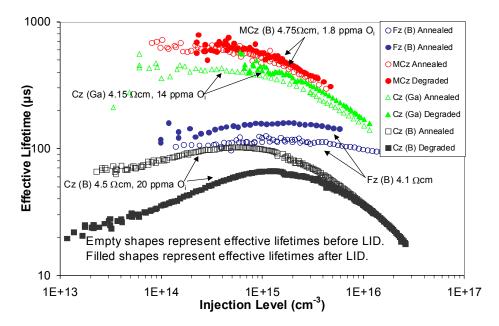

| Figure 33. | Effective lifetime measurements before and after illumination on similar resistivity Si crystal types. Investigation of LID effects in B doped FZ, Ga doped Cz, B doped MCz, and B doped Cz                                                                                                            | 82 |

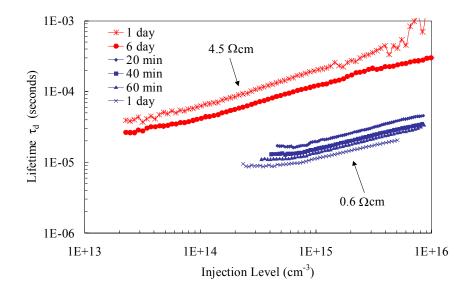

| Figure 34. | Injection level dependence of the trap responsible for LID. Rising slope reflects near midgap trap behavior                                                                                                                                                                                            | 83 |

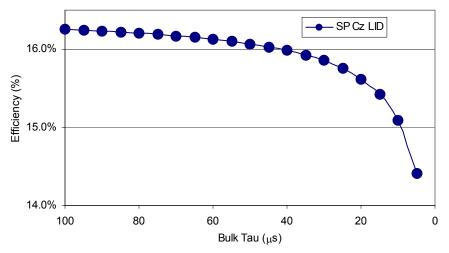

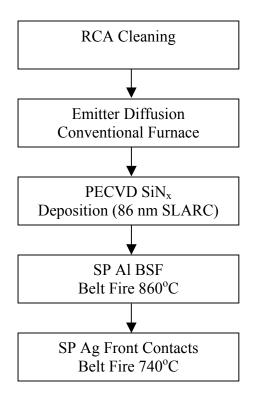

| Figure 35. | PC1D simulation of LID effect on solar cell efficiency                                                                                                                                                                                                                                                 | 85 |

| Figure 36. | Process sequence diagram for single crystal SP solar cells used to<br>analyze LID in finished devices                                                                                                                                                                                                  | 86 |

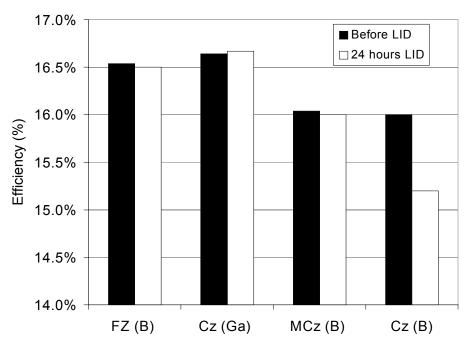

| Figure 37. | AM1.5 efficiencies for various single crystal silicon solar cells (400µm) before and after 24 hours of one sun illumination                                                                                                                                                                            | 87 |

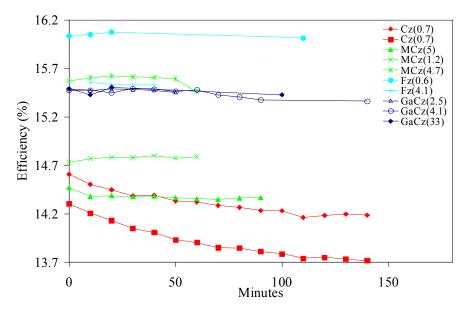

| Figure 38. | Efficiency Degradation or stability for Single crystal Si samples listed in Table 4                                                                                                                                                                                                                    | 88 |

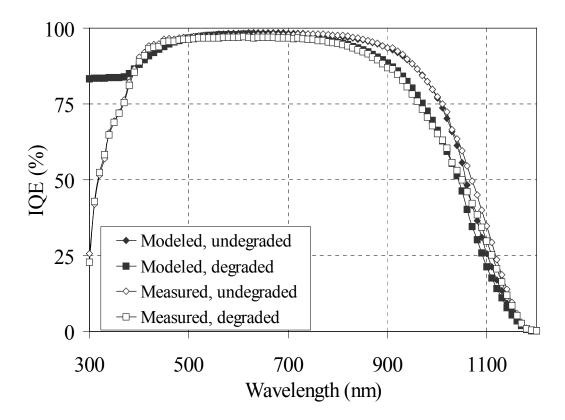

| Figure 39. | Measured and modeled IQE of the 254 $\mu$ m B doped Cz solar cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 90  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

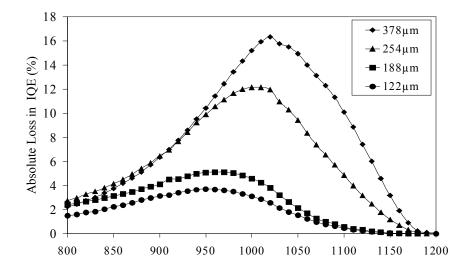

| Figure 40. | Measured LID in IQE in the long wavelength range for cells with varying thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93  |

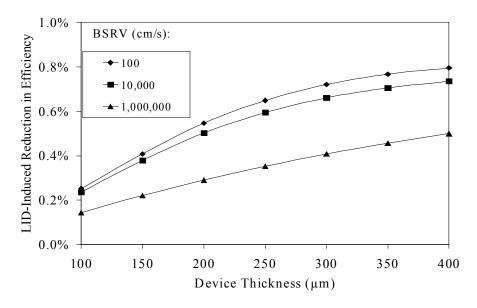

| Figure 41. | PC1D modeling of the effect of LID on efficiency in Cz Si solar cells that suffer bulk lifetime degradation from 75 to 20µs                                                                                                                                                                                                                                                                                                                                                                                                               | 95  |

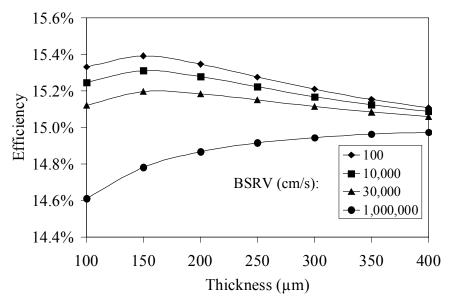

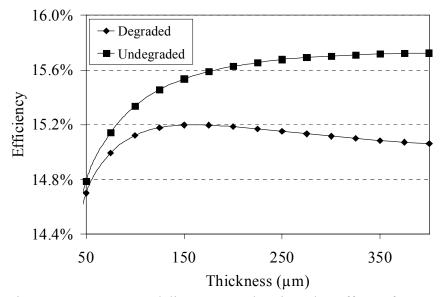

| Figure 42. | PC1D modeling of the effect of BSRV on the optimum thickness<br>and efficiency of light degraded Cz Si solar cells with 20µs bulk<br>lifetime.                                                                                                                                                                                                                                                                                                                                                                                            | 95  |

| Figure 43. | Degraded and Un-degraded efficiencies for B doped Cz Si solar cells for varying wafer thickness                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97  |

| Figure 44. | PC1D modeling curve showing the effect of LID as a function of thickness (BSRV = $30,000$ <sup>cm</sup> /s)                                                                                                                                                                                                                                                                                                                                                                                                                               | 98  |

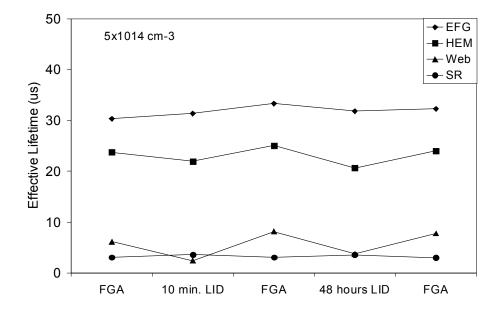

| Figure 45. | QSSPCD effective lifetime data for ribbon and cast mc-Si                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 103 |

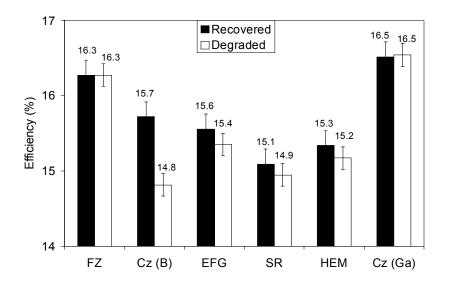

| Figure 46. | Average efficiency change after 4 degradation / recovery cycles for mc-Si solar cells                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 104 |

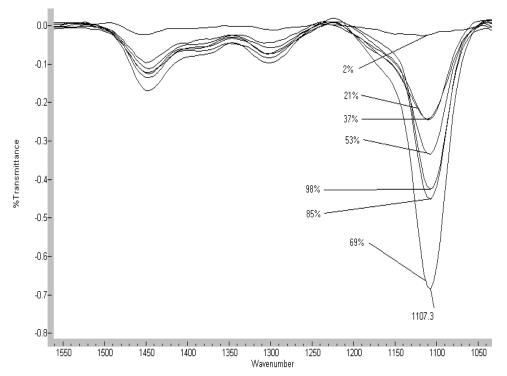

| Figure 47. | Room-temperature FTIR spectra that shows the relative $O_i$ concentration (wavenumber = 1107 cm <sup>-1</sup> ) in HEM mc-Si as a function of wafer position from the top of the ingot (2%) to the bottom of the ingot (98%). Detection limit ~ $5x10^{16}$ cm <sup>-3</sup>                                                                                                                                                                                                                                                              | 106 |

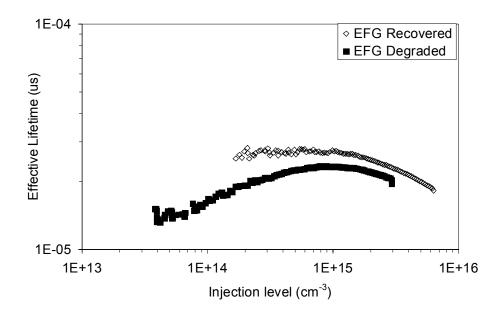

| Figure 48. | $\tau_{eff}$ versus injection level for processed and hydrogenated EFG Si.<br>"Recovered" is before LID and "Degraded" is after                                                                                                                                                                                                                                                                                                                                                                                                           | 107 |

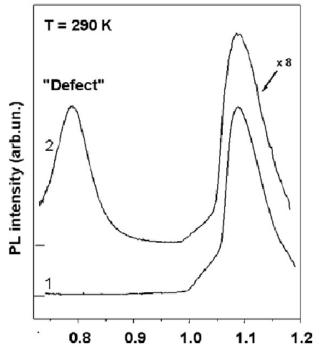

| Figure 49. | Room temperature PL spectra in the area with a high (1) and low (2) minority carrier bulk lifetime. The defect band at about 0.8 eV is observed only in low lifetime regions of EFG and cast mc-Si wafers [51].                                                                                                                                                                                                                                                                                                                           | 110 |

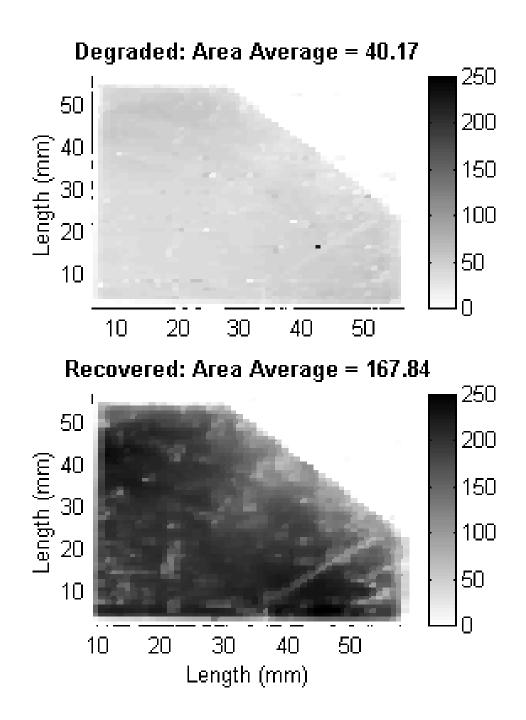

| Figure 50. | PL map of a quarter B doped Cz Si wafer before and after LID                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 113 |

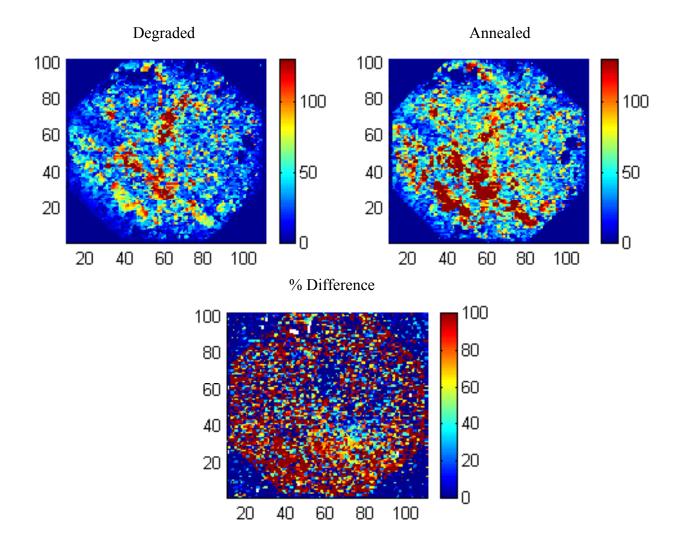

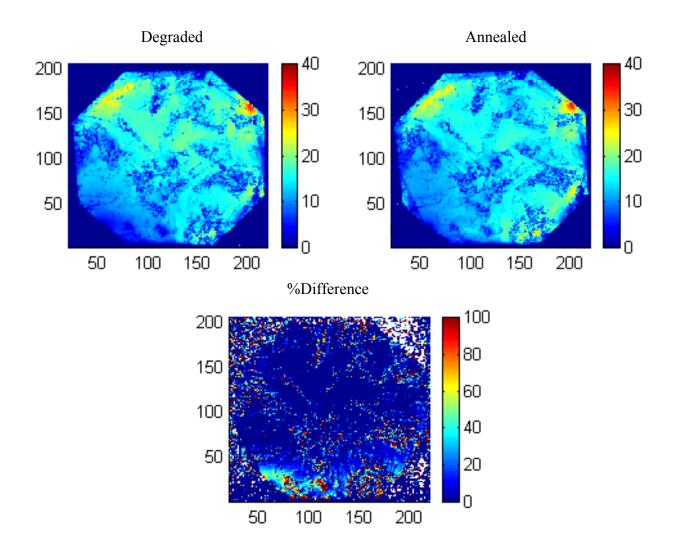

| Figure 51. | HEM cast mc-Si wafer passivated with SiN and measured using a photoluminescence mapping technique analogous to effective lifetime mapping. The change in the annealed and degraded state is mapped in the bottom figure labeled %Difference. This cast mc-Si had the highest measured effective lifetime before and after LID (18-25µs) using the QSSPCD technique. A relatively uniform trap recovery is observed with up to a 100% improvement in effective lifetime. The colorbar has arbitrary units of intensity for I <sub>bb</sub> | 116 |

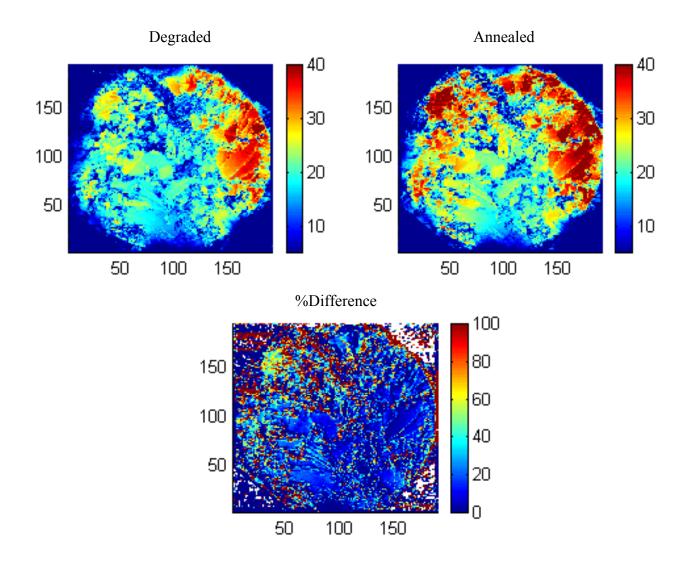

| Figure 52. | HEM cast mc-Si passivated with SiN and measured using a photoluminescence mapping technique analogous to effective lifetime mapping. The change in the annealed and degraded state is mapped in the bottom figure labeled %Difference. This sample had a relatively low oxygen concentration because it was taken from an ingot depth of ~37% from the top. Only the upper left corner showed LID. QSSPCD effective lifetime measurements revealed a low initial (or as-grown) bulk lifetime (< 8µs). The low lifetime could obscure LID The colorbar has arbitrary units of intensity for $I_{bb}$ | 117 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 53. | PL (effective lifetime) mapping of HEM cast mc-Si with relatively<br>high O <sub>i</sub> content (taken from ~69% ingot depth from the top). The<br>change in the annealed and degraded state is mapped in the bottom<br>figure labeled %Difference. Essentially no lifetime is recovered or<br>degraded suggesting no LID. However, QSSPCD effective lifetime<br>measurements revealed low initial (or as-grown) bulk lifetime<br>values that could obscure the LID cycle.                                                                                                                         | 118 |

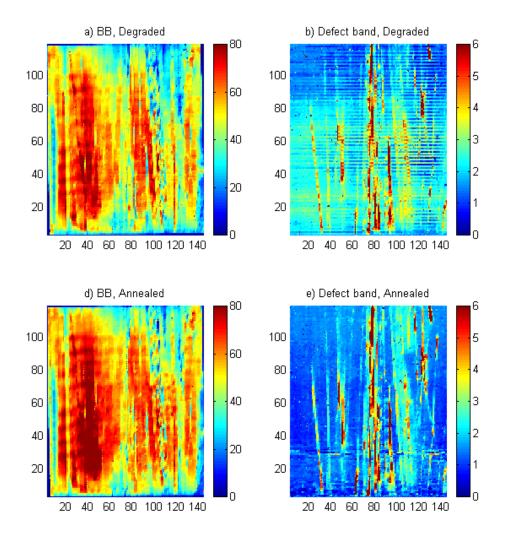

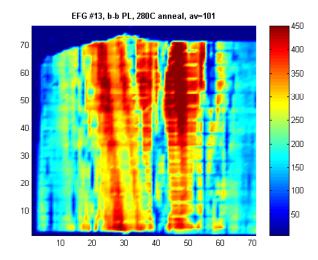

| Figure 54. | String Ribbon (SR) photoluminescence map using the band-to-band<br>radiative recombination intensity before and after treatment for light<br>induced degradation (LID) for the two pictures on the right. The<br>two pictures on the left are the defect band intensity before and after<br>LID. The colorbar has arbitrary units of photoluminescent intensity<br>for either the defect band or the band-to-band recombination                                                                                                                                                                     | 121 |

| Figure 55. | Edge Defined Film-fed Growth (EFG) ribbon photoluminescence<br>map using the band-to-band radiative recombination intensity<br>before and after treatment for light induced degradation                                                                                                                                                                                                                                                                                                                                                                                                             | 122 |

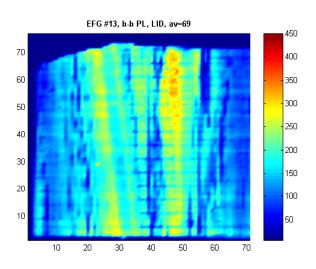

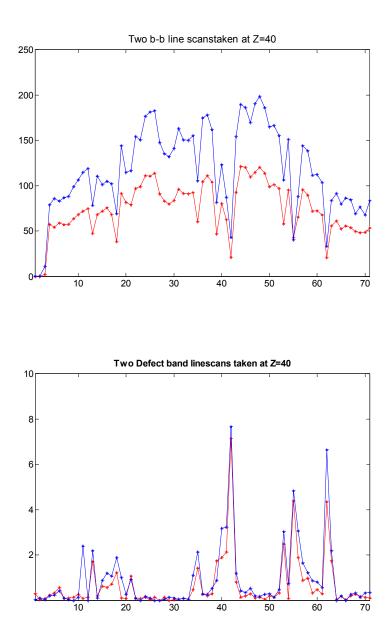

| Figure 56. | Line scans through the photoluminescence map for the EFG sample<br>at the 40 mm height. Top graph is the band-to-band intensity<br>comparison for the degraded and annealed state. Bottom graph is<br>the defect band intensity (sub bandgap recombination event) for the<br>annealed and degraded state. Blue is annealed and red is<br>degraded                                                                                                                                                                                                                                                   | 123 |

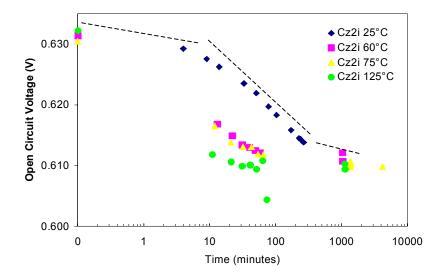

| Figure 57. | Open circuit voltage degradation for increasing temperatures from 25°C to 125°C. The degradation rate increases with temperature. The initial fast degradation, the slower middle region, and slowest end regions are denoted by the dashed lines for the 25°C curve                                                                                                                                                                                                                                                                                                                                | 126 |

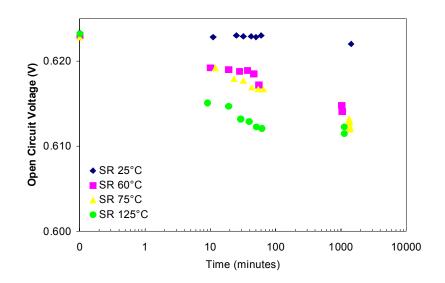

| Figure 58. | Open circuit voltage degradation for increasing temperatures from 25°C to 125°C. The degradation rate increases with temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 127 |

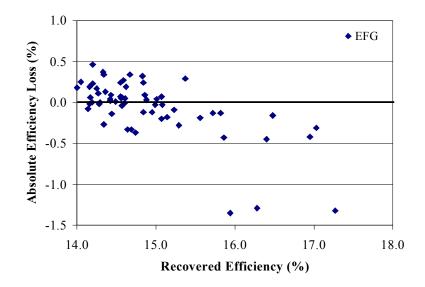

| Figure 59. | Scatter plot of the absolute efficiency degradation for samples with initial efficiencies recorded on the x-axis                                         | 129 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

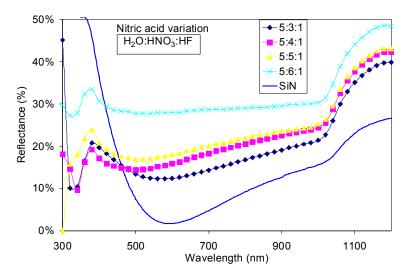

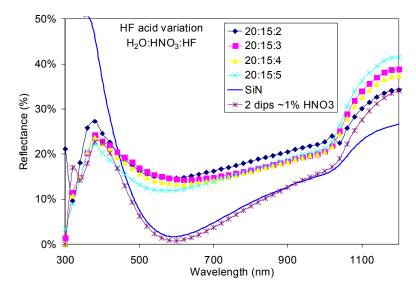

| Figure 60. | Total reflectance for porous silicon layers etched in a solution with varying concentrations of Nitric Acid                                              | 134 |

| Figure 61. | Total reflectance for porous silicon layers etched in a solution with varying concentrations of hydrofluoric acid                                        | 134 |

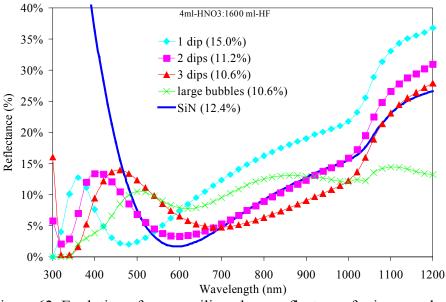

| Figure 62. | Evolution of porous silicon layer reflectance for increased soak time in etching solution.                                                               | 135 |

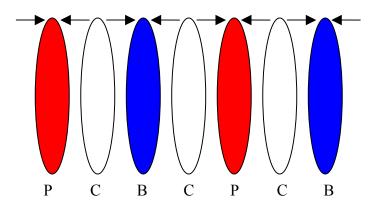

| Figure 63. | DOSS diffusion source diagram. Boron Sources (B), Phosphorus Sources (P), and Solar Cells (C)                                                            | 136 |

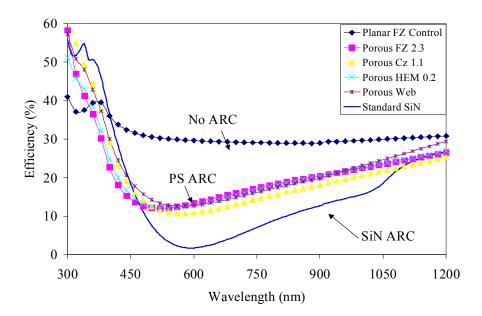

| Figure 64. | Porous silicon solar cell reflectance for FZ, Cz, and mc-Si (web and HEM) samples after cell processing                                                  | 138 |

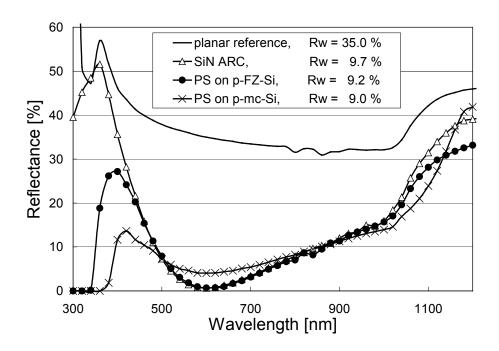

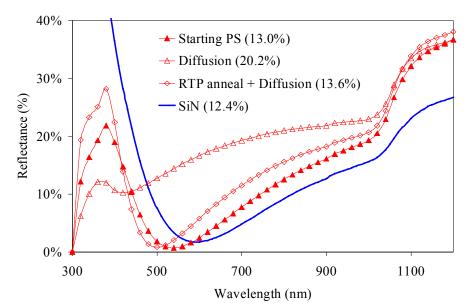

| Figure 65. | Reflectance of planar silicon, silicon with SiN ARC, and with porous silicon texturing, respectively                                                     | 139 |

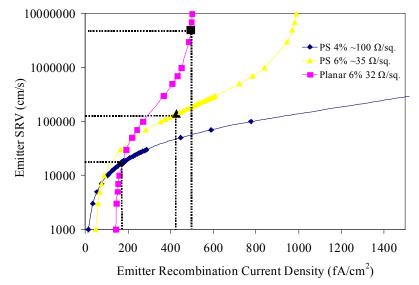

| Figure 66. | Calculated Front Surface Recombination Velocity (FSRV) versus J <sub>oe</sub> for porous silicon and planar control wafers of various sheet resistivity. | 143 |

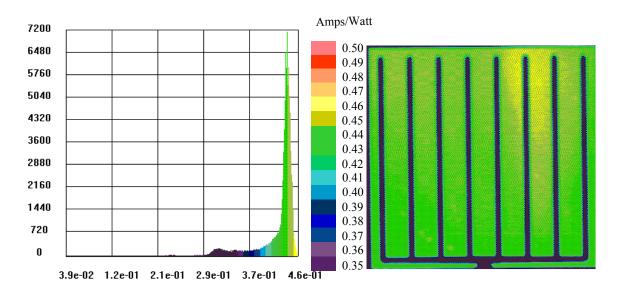

| Figure 67. | LBIC map of 0.6 $\Omega$ cm (4 cm <sup>2</sup> FZ) sample with a Porous Silicon ARC along with the histogram of data points                              | 146 |

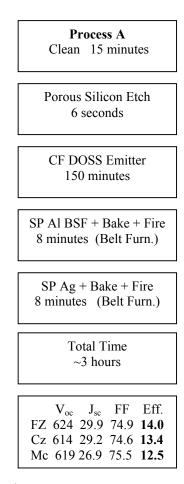

| Figure 68. | Process sequence diagram for porous silicon ARC solar cells using DOSS processing.                                                                       | 147 |

| Figure 69. | Change in porous silicon reflectance subjected to high temperature processing in a conventional tube furnace                                             | 148 |

| Figure 70. | Phosphorus dopant concentration diffused at 925°C using 6% $P_2O_5$                                                                                      | 150 |

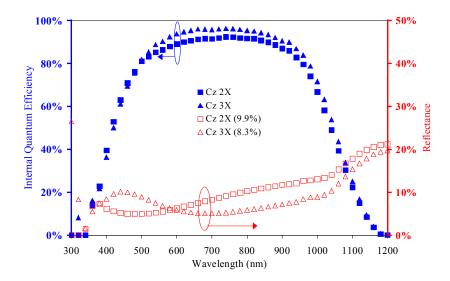

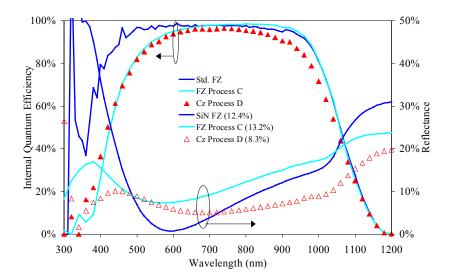

| Figure 71. | IQE and Reflectance curves for the standard screen printed solar cell and a porous silicon ARC solar cell (Process A)                                    | 151 |

| Figure 72. | Reflectance curves for SiN <sub>x</sub> and porous silicon AR coatings subjected to different RTP processing                                             | 152 |

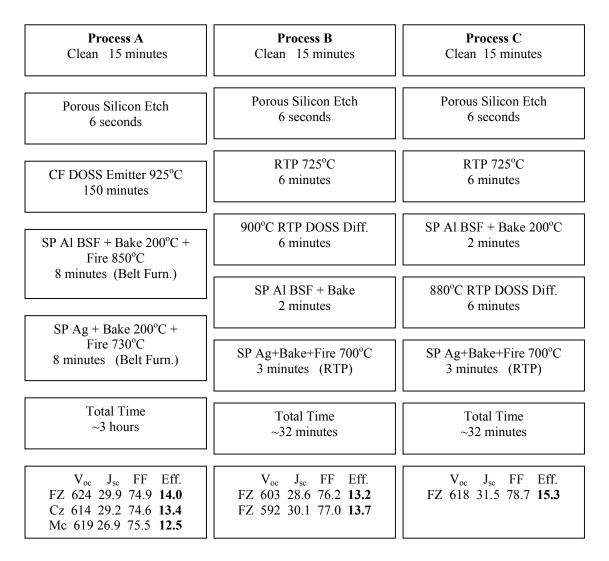

| Figure 73. | Process sequence diagram for porous silicon ARC solar cells using DOSS processing with and without RTP                                                   | 154 |

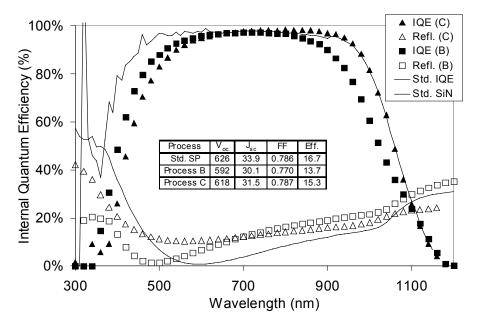

| Figure 74. | IQE and Reflectance curves for the standard screen-printed solar cell and porous silicon ARC solar cells (Process B and Process C)                                                                                                                                                                                                                                                                                                                                                                                | 156 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 75. | Porous Silicon etched wafers after DOSS diffusion. Top left – FZ,<br>Top Right – cast mc-Si, bottom left – EFG ribbon, bottom right –<br>Cz.                                                                                                                                                                                                                                                                                                                                                                      | 158 |

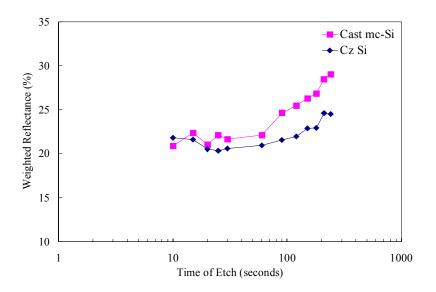

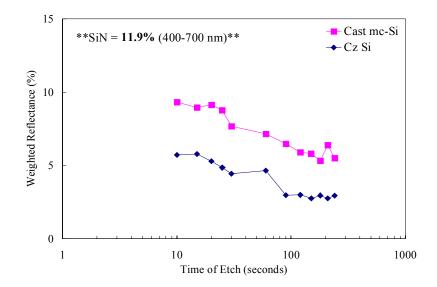

| Figure 76. | Weighted reflectance (400-700 nm) of acidic texture developed at Georgia Tech on cast mc-Si and Cz Si samples as a function of increasing etch time.                                                                                                                                                                                                                                                                                                                                                              | 162 |

| Figure 77. | (a, b, c, d). SEM pictures of crystalline silicon wafer surfaces after<br>acidic texturing developed at Georgia Tech. Picture "a" shows the<br>surface morphology of a Cz sample etched for 10 seconds. Picture<br>"b" shows the surface morphology of a Cz sample etched for 60<br>seconds. Picture "c" shows the surface morphology of a cast mc-Si<br>sample etched for 60 seconds. Picture "d" shows the surface<br>morphology of a planar view for a cast mc-Si wafer across a grain<br>boundary labeled GB. | 164 |

| Figure 78. | Weighted reflectance behavior of Cz Si samples that were<br>submerged in an acidic texture for various amounts of time and then<br>subsequently coated with a SiN layer that would deposit 78 nm on a<br>planar surface.                                                                                                                                                                                                                                                                                          | 165 |

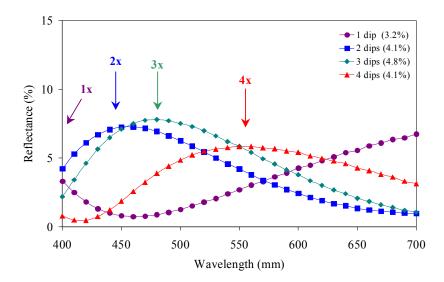

| Figure 79. | Porous Si etched acid textured Cz wafers for multiple dips into the optimized porous silicon etching solution. Notice the shift of the initial peak to longer wavelengths with increasing time. The weighted reflectance for the 400-700 nm wavelength range is denoted in parenthesis.                                                                                                                                                                                                                           | 166 |

| Figure 80. | Optical microscope view of the edge of an acid textured Cz Si sample etched in a porous silicon solution at 50X magnification                                                                                                                                                                                                                                                                                                                                                                                     | 168 |

| Figure 81. | Process D sequence diagram for porous silicon ARC solar cells<br>using DOSS processing                                                                                                                                                                                                                                                                                                                                                                                                                            | 169 |

| Figure 82. | Internal Quantum Efficiency (primary y-axis) and total reflectance<br>(secondary y-axis) for acid textured porous silicon etched RTP<br>processed Cz silicon solar cells using Process D                                                                                                                                                                                                                                                                                                                          | 170 |

| Figure 83. | Internal Quantum Efficiency (primary y-axis) and total reflectance<br>(secondary y-axis) for the standard FZ screen-printed solar cell<br>process compared to a porous silicon etched FZ (Process C) and Cz<br>silicon solar cell (Process D)                                                                                                                                                                                                                                                                     | 172 |

| Figure 84. | Efficiency evolution for all types porous silicon etched solar cell<br>structures including photolithography. All reported efficiencies<br>from Georgia Tech are manufacturable screen-printed devices [33,<br>36, 38, 39]                                                                                   | 178 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

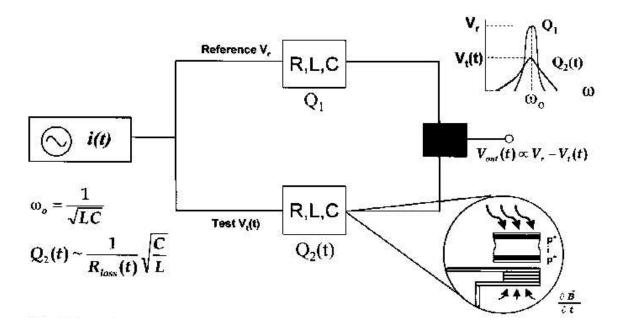

| Figure 85. | Using Maxwell's laws and a basic circuit structure the Q factors are<br>nulled initially to get maximum signal. The change in voltage<br>response is then analyzed to yield the carrier lifetime. Many<br>considerations need to be accounted for in the circuit design and<br>measurement reliability range | 185 |

### SUMMARY

The current cost of photovoltaics is two to four times the cost of conventional energy sources in the United States. Crystalline Si accounts for more than 90% of the photovoltaic modules produced today. Nearly 55% of the cost of a Si photovoltaic module is associated with the crystallization and wafering of the silicon substrate. In an effort to reduce production costs, a great deal of research has been devoted to the development of low-cost photovoltaic grade silicon substrates. These low-cost silicon crystals often suffer from lower bulk lifetimes as a result of less stringent growth constraints that lead to higher incorporation of impurities, dislocations, and other defects. Cast multi-crystalline silicon substrates are used in more than 50% of the photovoltaic modules produced today. The random grain orientations of multi-crystalline silicon wafers inhibit the formation of uniform and effective surface texturing using conventional alkaline etching techniques. An effective surface texture can result in a 6 to 8% relative improvement in the conversion efficiency for multi-crystalline silicon solar cells. In addition, a textured surface acts to reduce the dependence on the bulk lifetime by obliquely coupling the light into the silicon substrate, keeping the photo-generated electron-hole pairs closer to the collecting junction. This provided the motivation for investigating porous silicon texturing in the second part of this thesis (Chapters 7 and 8).

The other main substrate used by industrial manufacturers of silicon solar cells is single crystalline Czochralski wafers (~30% of the market share). Czochralski silicon material

is known to suffer from the formation of a metastable defect under carrier injection, which acts to reduce the bulk lifetime and cause industrial screen-printed solar cells to lose 1 to 1.5% in absolute efficiency (or 7 to 10% relative efficiency) and is sometimes referred to as light induced degradation (LID). The electrical and structural properties of this defect are still not precisely known, thus providing the motivation for the first part of this thesis (Chapters 5 and 6), where the investigation of light induced degradation in low-cost photovoltaic grade silicon is studied. A typical Czochralski Si solar cell with an initial efficiency of  $\sim 16.5\%$  could suffer a reduction in efficiency to  $\sim 15\%$  after the formation of the metastable defect responsible for LID. It is known that the degradation in Czochralski Si occurs under illumination at room temperature and is annealed at temperatures greater than 200°C in the dark. In Chapter 5 it is shown that trap formation can occur at temperatures above 200°C, provided sufficient carrier injection via illumination is present. Methods to eliminate or mitigate the effects of light induced degradation on finished solar cells are also discussed in Chapter 5. It is shown that by removing boron or oxygen from the silicon crystal, degradation is eliminated. Using a combination of device modeling and cell fabrication, it is also shown that by thinning the wafer substrate, the effect of light induced degradation on solar cell efficiency can be reduced. Appropriate cell design accounting for the back surface recombination velocity as well as the stable bulk lifetime in Czochralski Si solar cells can be used to optimize the efficiency performance. For the Cz material used in this study, which degraded from a 75  $\mu$ s bulk lifetime to a 20 $\mu$ s bulk lifetime after degradation, the optimum cell thickness for planar devices was found to be in the range of 150 to 250 µm. Efficiency degradation reduced from 0.75% to 0.24% when the cell thickness was reduced from 378 to 157 $\mu$ m.

This represents a reduction in cell thickness by more than a factor of two. Combined with a higher stabilized cell efficiency, a reduction in cost (in \$/W) of Cz solar cells can be realized. In addition, the careful analysis of defect formation conditions provides a better understanding of the trap responsible for light induced degradation.

The presence of light induced degradation in ribbon silicon solar cells is documented and analyzed for the first time in this thesis (Chapter 6). In addition, the role of light induced degradation in cast multi-crystalline silicon substrates is investigated. It is found that LID is often much smaller in cast multi-crystalline silicon compared to Cz silicon samples. In addition, the LID in multi-crystalline silicon is shown to be spatially nonuniform.

Using a photoluminescence mapping technique, the spatial dependence of light induced degradation in ribbon and cast multi-crystalline silicon (mc-Si) samples is analyzed. Trap generation and annihilation are observed in high lifetime regions of multi-crystalline silicon samples, while low lifetime regions tend to obscure light induced degradation. The impact of ambient conditions on the degradation of ribbon silicon samples was shown to be an important factor for the observation of LID. No degradation was observed over a 24-hour period at 25°C, but at an elevated temperature of ~75°C, appreciable efficiency degradation was observed in high efficiency ribbon solar cells (>16%). Czochralski silicon solar cells showed full degradation within 24 hours at 25°C. Thus, a more thorough description of LID in mc-Si materials needs to include some

temperature profiling to decrease the observation time required to quantify the efficiency degradation.

Part two of this thesis involves the development of a rapid surface texturing technique suitable for all crystalline silicon substrates. It is demonstrated in Chapter 7 that chemically formed porous silicon is a simple and rapid technique for texturing single as well as multi-crystalline silicon. Only 6 to 10 seconds in a 200:1 HF to HNO<sub>3</sub> solution at room temperature allows for the formation of an effective porous silicon anti-reflection coating. Low reflectance and good surface passivation were achieved by using the DOSS solar cell process. The DOSS diffusion from a limited source wafer was tailored to obtain the desired sheet resistivity underneath the porous silicon layer. This resulted in a porous silicon anti-reflection coated solar cell efficiency of 15.3% on a float zone Si sample with an excellent fill factor (78.7%). This represents the highest efficiency porous silicon etched solar cell reported to date. The typical process used in the literature involves porous silicon etching as the final step in the solar cell fabrication sequence. The major problem associated with this process sequence is fill factor degradation resulting from exposure of the metal contacts to the porous silicon etching solution. This problem was overcome in this research by porous silicon etching prior to cell processing, which resulted in a 0.807 and 0.787 fill factor for photolithography cells and screenprinted solar cells, respectively.

In Chapter 8, it is shown that incorporating an acid texture prior to porous silicon etching can improve the surface reflectance for cast multi-crystalline and Czochralski (Cz) silicon

samples that have significant surface damage when they arrive from manufacturers. The addition of an acidic texture to Cz and cast mc-Si solar cells gave the highest efficiency screen-printed porous silicon solar cells fabricated to date. Solar cell efficiencies of 14.8% for Cz Si and 13.6% for cast mc-Si (without the conventional SiN anti-reflection coating) were achieved using Process D developed in this work. Although these efficiencies are lower than what can be achieved with traditional SiN coated solar cells, they provide the opportunity to use an alternative, less expensive anti-reflection coating that is rapidly formed and still achieves enhanced performance. The weighted reflectance of Cz silicon solar cells fabricated with Process D obtained a lower weighted reflectance (8.3%) than the traditional SiN single layer anti-reflection coating (12.4%). Thus, the development of a rapid, inexpensive texture and anti-reflection coating was achieved through the use of porous silicon etching and the DOSS diffusion technique.

# **CHAPTER 1**

### **1 INTRODUCTION AND RESEARCH OBJECTIVES**

#### 1.1 Statement of Problem

Worldwide demand for electrical energy is growing rapidly in conjunction with the depletion of traditional energy sources and increasing world population. In addition, the burning of fossil fuels is resulting in significant increases in CO<sub>2</sub> and other greenhouse gases in our environment, leading to increased pollution and potential global warming. There is a real need to develop alternate energy sources that can solve energy and environmental problems simultaneously. Viable energy sources for the future must be available on demand and should be renewable and environmentally friendly. In addition, the cost of energy production and delivery must be comparable to current energy sources. This is particularly important for countries like the United States where cost competitiveness is more critical because other forms of energy are readily available through the electrical grid. Photovoltaics, or solar electricity, is a promising renewable energy technology that is rapidly approaching mainstream feasibility. Solar energy is free, unlimited, and not localized in any part of the world. The sun is expected to continue shining for the next five billion years, providing an abundant source of energy. Solar cells are simple semiconductor devices that convert sunlight directly into electricity without any undesirable impact on the environment. More than 95% of solar cells are currently produced from silicon semiconductors in the form of single crystal, multicrystalline, or amorphous Si, with greater than 90% from crystalline silicon alone [1].

Silicon is the second most abundant element (27.7%) in the earth's crust [2]. Thus, the raw material used for energy production is also seemingly inexhaustible. Once a silicon solar module is finished, no harmful gases are emitted. Solar power generation is clean, quiet, and environmentally friendly. However, the cost of generating electricity from solar cells is currently two to four times greater than that of fossil fuels [1].

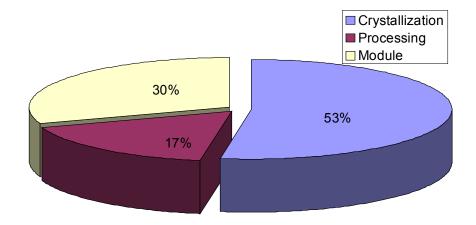

A typical cost breakdown of crystalline silicon solar modules is depicted in Figure 1 for screen-printed cast multi-crystalline silicon cells [1]. Only  $\sim$ 17% of the total module cost is associated with solar cell processing. Approximately 30% of the cost is associated with the module assembly. The bulk of the cost is associated with the silicon substrate,

Figure 1. Cost associated with solar cell fabrication for screen-printed technologies for single and multi-crystalline silicon.

which includes feedstock production, crystallization, and wafer slicing, accounting for  $\sim$ 53% of the total cost. Therefore, different strategies and technologies aimed at reducing

the cost of wafer production are currently being developed and investigated. High module cost today can be partially offset by using building integrated photovoltaics (BIPV) [3]. Solar modules can be used to substitute for roofs, walls, or windows of a building, thereby reducing the marginal or effective cost of photovoltaics (PV). In addition, the power can be produced at the point of use, avoiding power transmission and distribution losses. Silicon ribbon growth techniques, such as string ribbon (SR) and edge-defined film-fed growth (EFG) can reduce the cost of Si substrates by eliminating kerf losses attributed to the loss of Si material resulting from wafer sawing and ingot shaving for the useable core section [2].

The theoretical efficiency limit of a single junction, one-sun crystalline Si solar cell is ~29% [4]. Solar cell efficiencies in laboratories have reached 24.7% for one-sun illumination [4] using high-quality float zone (FZ) silicon substrates and several advanced design features such as selective emitter, inverted pyramid texturing, and front and back surface oxide passivation incorporated into the Passivated Emitter and Rear Locally diffused back surface field cell (PERL cell). Unfortunately, the process sequence used to fabricate these cells involves many high-temperature and photo-mask steps along with low through-put technologies such as vacuum deposition and photolithography. On the other hand, current industrial cell efficiencies are only in the range of 10 to 15% because of the use of low-cost silicon and simplified processing, and the absence of high efficiency features [1]. However, industrial cells can be produced in a few hours as opposed to 1 to 2 weeks. As a result, laboratory cells are too expensive and industrial cells are not efficient enough to meet the cost and efficiency targets (\$/watt)

simultaneously. There is a need for a low-cost solution that incorporates high efficiency design features in commercial cells that currently suffer from low minority carrier bulk lifetimes caused by impurities, traps, or defects. Crucible-grown Czochralski (Cz) silicon has been a dominant source material for photovoltaic (PV) substrates, accounting for ~30% of the PV modules produced today. Recently, however, light induced degradation (LID) in boron doped Cz Si solar cells has been recognized as a significant cause of minority carrier lifetime degradation during cell operation because of a metastable defect formation under carrier injection. The drop in minority carrier lifetime results in a significant decrease in Cz silicon solar cell efficiency (approximately 8 to 10%, relatively). In addition, there are recent reports on LID in multi-crystalline silicon (mc-Si).

Multi-crystalline Si, including cast and ribbon materials, accounts for ~55% of PV modules today. Model calculations have shown that light trapping via surface texturing can enhance the efficiency of Si cells by 1.2% absolute. However, because of the random grain orientation, conventional isotropic texturing methods do not effectively texture the surface of multi-crystalline materials. This introduces another efficiency-limiting mechanism for industrial solar cells fabricated on cast or ribbon multi-crystalline Si. The lack of texturing for multi-crystalline Si is estimated to account for a 6 to 8% loss in efficiency for industrial type solar cells. This thesis attempts to address both of these important issues: investigating light induced degradation in low-cost PV grade materials and improving the anti-reflection coating in mc-Si via porous silicon etching and acidic isotropic texturing using low-cost technologies.

### 1.2 Specific Research Objectives

The objective in this thesis is to improve the performance and stability of promising solar grade silicon materials, in particular, Czochralski and cast multi-crystalline silicon. This is accomplished by addressing major efficiency-limiting mechanisms in each substrate. The specific goals addressed in this thesis are to develop low-cost rapid technologies aimed at preserving or improving bulk lifetime in solar grade silicon wafers; in particular, understanding, quantifying, and mitigating light induced degradation in promising boron doped p-type Si substrates, including single crystal Si, cast mc-Si, and Si ribbons. Part two involves the development of a cost-effective porous silicon anti-reflection coating (ARC) suitable for single and mc-Si cells.

# 1.2.1 Task 1. Investigation of trap formation conditions for the metastable defect that causes light induced degradation in Czochralski silicon.

LID is known to reduce the minority carrier lifetime in single crystal Cz silicon substrates. Electrical and structural characteristics of the LID trap are not currently fully understood. Therefore, trap formation and annihilation mechanisms need to be further investigated. In this task, effective lifetime measurements are performed on as-grown and processed Si materials. First, lifetime degradation is demonstrated in traditional B doped Cz silicon with high O<sub>i</sub> concentration before and after laboratory and industrial cell processing. Next, key parameters affecting the magnitude of LID are investigated, including B and Ga doping, O<sub>i</sub> concentration, annealing temperature, and illumination time.

# 1.2.2 Task 2. Determination of the impact of the metastable defect on the efficiency screen-printed industrial solar cells.

Task 2 quantifies the extent of bulk lifetime and efficiency degradation in industrial-type screen-printed silicon solar cells. Industrial solar cells focus on achieving an appropriate \$/Wp and therefore are typically lower in efficiency (12 to 15%) than laboratory solar cells (20%). Laboratory cells are typically fabricated on Si with high lifetimes and thus suffer more from lifetime degradation. Industrial solar cells do not typically achieve such high lifetime values and therefore would seemingly suffer less. In this task complete solar cells are fabricated using screen-printing followed by light soaking to study LID. Quantum efficiency and light and dark I-V analysis are performed on various single crystal silicon samples before and after LID to assess the impact of LID on industrial-type screen-printed solar cells. Since LID can be avoided if either B or O is eliminated from the silicon crystal, high efficiency screen-printed devices are fabricated and characterized on single crystal materials such as B doped Cz with high O<sub>i</sub>, Ga doped Cz with high O<sub>i</sub>, B doped FZ with undetectable O<sub>i</sub>, and B doped MCz with low O<sub>i</sub> content.

# 1.2.3 Task 3. Investigate light induced degradation trap formation conditions in low-cost multi-crystalline silicon solar cells.

In addition to Cz Si, cast mc-Si and Si ribbons are also being extensively used for silicon PV. Currently, all Si materials used for industrial photovoltaic production contain boron and some level of oxygen. However, the extent of LID in these materials is largely unknown. Limited information exists on cast multi-crystalline silicon LID [5], while there are no reports on cell efficiency degradation as a result of LID in ribbon multi-crystalline silicon cells. As-grown material lifetime is generally too low in mc-Si materials to detect any LID. Therefore, appropriate preprocessing is performed to enhance lifetime to detect the metastable defect formation. Lifetime versus injection level measurements and analysis are performed on several promising multi-crystalline silicon materials after various processing steps used to improve bulk lifetime during cell fabrication. In addition, photoluminescence lifetime mapping is used to detecting LID in very high efficiency mc-Si cells.

# 1.2.4 Task 4. Develop solar cell designs that reduce or eliminate the effects of light induced degradation in crystalline silicon solar cells.

In this task, special attention is given to B doped Cz Si because it is the material of choice for most PV manufacturers using single crystal wafers and it suffers the most from LID.

Appropriate cell design can limit or eliminate the affects of LID on solar cell efficiency for both single and multi-crystalline Si. For example, reducing cell thickness increases the minority carrier diffusion length to cell width ratio (L/W) and may make cell efficiency less sensitive to lifetime degradation provided other device parameters are properly selected or designed. In this task, a combination of device modeling, cell fabrication, and characterization are used to minimize LID through careful cell design.

# 1.2.5 Task 5. Investigate low-cost texturing methods for multi-crystalline silicon solar cells.

In addition to LID in mc-Si solar cells acting to reduce the final cell efficiency, the random grain orientation on the surface of mc-Si solar cells restricts effective light trapping. This is because of difficulties achieving uniform texturing, resulting in the loss of photo-current. Conventional isotropic texturing methods are not effective for enhanced light trapping. This results in the loss of 8 to 10% in relative cell efficiency. Mechanical texturing, Reactive Ion Etching, isotropic acidic texturing, and porous silicon etching are four methods currently being investigated as possible solutions to this problem. Therefore, in Task 5, a rapidly formed uniform porous silicon coating is developed that is suitable for solar cell fabrication and does not depend on surface morphology or grain orientation.

# 1.2.6 Task 6. Develop process sequence and fabricate high efficiency porous silicon etched solar cells.

The Dopant Oxide Solid Source (DOSS) process, developed at Georgia Tech, is particularly suitable for porous silicon etched emitters because it can produce uniform diffusions on textured surfaces. This allows the formation of porous silicon prior to the emitter diffusion. Most investigators do the porous silicon etching as the final step in the solar cell process sequence. It is sometimes undesirable to do porous silicon etching at the end of cell fabrication because it could attack the metal contacts. DOSS processing can produce emitter, BSF, and oxide passivation in a single high-temperature step and does not require any glass etching after diffusion. Task 6 focuses on fabricating DOSS solar cells with a porous silicon anti-reflection coating (ARC) applied at the end of the standard wafer cleaning, *before* the start of solar cell processing. Various porous silicon solutions are examined to minimize reflectance in conjunction with good uniformity and reproducibility. Changes in porous silicon properties during subsequent cell processing are examined, along with establishing constraints or limitations pertaining to porous silicon ARC implementation at the start of cell processing. Finally, high-efficiency solar cells are fabricated with high fill factors using porous silicon anti-reflection coatings, without the need for deposition of a conventional SiN anti-reflection coating.

# **CHAPTER 2**

## 2 SOLAR CELL FUNDAMENTALS AND EFFICIENCY LIMITING MECHANISMS

#### 2.1 Current and Voltage

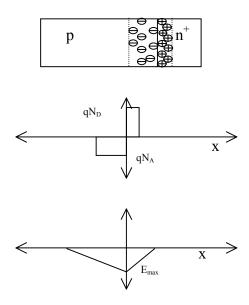

The presence of a p-n junction in a semiconductor makes solar power possible. The space charge region is formed as a result of the diffusion of majority carriers across the

metallurgical junction, and its width is fixed when the diffusion is counter balanced by the drift of carriers in the opposite direction (Figure 2), thus setting up a compact but strong electric field as the "collecting junction" in the depletion In thermal equilibrium, drift and region. diffusion currents through the depletion region oppose each other, resulting in zero net current Figure 2 shows a schematic junction flow. formation along with the space charge region and electric field that has a maximum at the metallurgical junction. Using light as an external stimulus allows the p-n junction to

Figure 2. Model of depletion region, space charge density, and electric field.

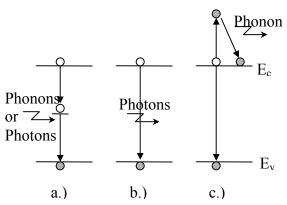

behave as follows. Part of the solar spectrum is absorbed in a semiconductor through the transfer of optical energy to electrons that are excited into the conduction band,  $E_{c}$ ,

creating holes in the valence band,  $E_v$ . The electric field in the depletion region helps in separating these electron-hole pairs, resulting in a voltage or the photovoltaic effect.

In discussing a solar cell, it is constructive to start with the simple diode equations used to describe the operation of a p-n junction. The dark saturation current,  $I_{o1}$ , is the "leakage" current that flows out a diode in the dark under reverse bias and is represented analytically by the following equation:

$$I_{o1} = q n_i^2 A \left( \frac{D_n}{L_n N_A} + \frac{D_p}{L_p N_D} \right)$$

(1)

where  $n_i$  is the intrinsic carrier concentration,  $N_A$  and  $N_D$  are the ionized concentration of acceptors and donors,  $L_n$  and  $L_p$  are the diffusion lengths of electrons and holes, q is the electron charge, and  $D_n$  and  $D_p$  are the diffusivity constants for the minority carriers.  $I_{o1}$ is primarily a drift current because reverse bias increases the barrier for diffusion current. On the other hand, forward bias lowers the barrier for diffusion and the current is largely dominated by diffusion, where

$$I \cong I_{o1} e^{qV_{kT}}$$

<sup>(2)</sup>

The total current of an ideal diode can be written as

$$I = I_{o1}(e^{\frac{qV}{kT}} - 1)$$

(3)

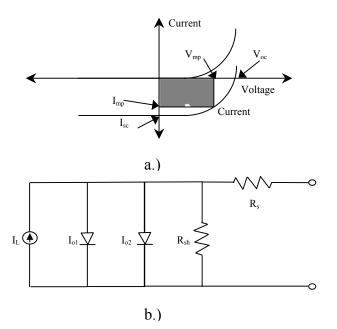

Figure 3 shows the light and dark current-voltage curves for a solar cell, along with the equivalent circuit used to analyze a solar cell. Non-ideal diode behavior in solar cells is typically a result of recombination in the depletion region, series resistance ( $R_s$ ), and shunts resistance ( $R_{sh}$ ) and can be described using the following equation:

$$I = I_{o1} \left( e^{q(V - IR_s)/kT} - 1 \right) + I_{o2} \left( e^{q(V - IR_s)/nkT} - 1 \right) + \frac{V - IR_s}{R_{sh}}$$

(4)

where  $I_{o2}$  and n are used to describe the recombination in the depletion region. When a light bias is applied to a solar cell, according to superposition, light and dark currents oppose each other, and the terminal current is given by

$$I = I_{dark} - I_{light} \tag{5}$$

Figure 3. a) Current-voltage curve under light bias, FF is shaded region, b) Equivalent circuit.

$$I = -I_{light} + \left[ I_{o1} \left( e^{q(V - IR_s)/kT} - 1 \right) + I_{o2} \left( e^{q(V - IR_s)/nkT} - 1 \right) + \frac{V - IR_s}{R_{sh}} \right]$$

(6)

where V is the terminal voltage, k is Boltzmann's constant, n is the non-ideality factor,  $R_s$  is the series resistance, and  $R_{sh}$  is the shunt resistance. If short circuit conditions are applied, the current out of the solar cell, I, is equal to the short circuit current,  $I_{sc}$ . The above equation is sometimes approximated by a single exponential

$$I = -I_{sc} + I_o (e^{qV/_{nkT}} - 1)$$

(7)

which, under  $V_{oc}$  or open circuit conditions, I=0 and V= $V_{oc}$ , (7) results in

$$V_{oc} = \frac{nkT}{q} \ln \left( \frac{I_{sc}}{I_o} + 1 \right)$$

(8)

where  $I_{light}$  is assumed equal to  $I_{sc}$ . To maximize  $V_{oc}$ , the dark current  $I_o$  must be minimized. To maximize  $J_{sc}$ , recombination in the cell must be minimized and light trapping must be maximized. The reverse saturation current,  $I_{o1}$ , is composed of an emitter saturation current,  $I_{oe}$ , and a base saturation current,  $I_{ob}$ , or correspondingly, the emitter and base saturation current densities  $J_{oe}$  and  $J_{ob}$  make up the reverse saturation current density  $J_{o1}$ . These parameters are discussed more in Appendix A and are used throughout this thesis to help analyze and quantify surface passivation.

#### 2.2 Fill Factor and Cell Efficiency

Terrestrial solar cell efficiency is reported at the standard AM1.5 global conditions. The measuring temperature is 298 K, and light intensity is 100 mW/cm<sup>2</sup> given by the zenith cycle of 48°. Cell efficiency is given mathematically by

$$\eta = \frac{V_{oc}J_{sc}FF}{P_{in}} \tag{9}$$

P<sub>in</sub> is the incident light intensity, and the fill factor, FF, is the measure of the squareness of the illuminated curve in Figure 3, given by

$$FF = \frac{V_{mp}I_{mp}}{V_{oc}I_{sc}}$$

(10)