## DESIGN AND INTEGRATION OF HYBRID AND MONOLITHIC MICROWAVE POWER AMPLIFIERS FOR WIDEBAND APPLICATIONS USING GALLIUM NITRIDE TECHNOLOGY

A Dissertation Presented to The Academic Faculty

by

George Christopher Barisich

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical Engineering

Georgia Institute of Technology December 2017

## **COPYRIGHT © 2017 BY GEORGE CHRISTOPHER BARISICH**

## DESIGN AND INTEGRATION OF HYBRID AND MONOLITHIC MICROWAVE POWER AMPLIFIERS FOR WIDEBAND APPLICATIONS USING GALLIUM NITRIDE TECHNOLOGY

Approved by:

Dr. John Papapolymerou, Advisor School of Electrical & Computer Engineering *Georgia Institute of Technology*

Dr. Edward Gebara School of Electrical & Computer Engineering *Georgia Institute of Technology*

Dr. John Cressler School of Electrical & Computer Engineering *Georgia Institute of Technology*  Dr. Hua Wang School of Electrical & Computer Engineering *Georgia Institute of Technology*

Dr. Z. John Zhang School of Chemistry & Biochemistry *Georgia Institute of Technology*

Date Approved: August 23, 2017

"Why?"

"Why not?"

#### ACKNOWLEDGEMENTS

Whenever I look backwards in time from a new vantage point, I gain more appreciation for the interconnectedness of life. For me to even have approached this point means that an untold number of people and decisions had to align and converge. Reaching it has required not only dedication from me (along with some luck), but also the help of many others who I would like to recognize for their support.

I wish to express my sincere thanks to my research advisor, Dr. John Papapolymerou, for his guidance, understanding, and patience as I found my way through this often difficult process. I am grateful to Dr. Edward Gebara for our conversations, his advice, and our friendship. I would also like to acknowledge Dr. John Cressler, Dr. Hua Wang, and Dr. John Zhang for their time and effort in serving on my defense committee with John and Edward.

I appreciate Dr. Cagri Ulusoy and Dr. Moon-Kyu Cho for their insights and assistance at various times throughout my years as a graduate student. I am thankful to the cleanroom staff for their help in navigating the maze of equipment, and to the administrative staff for their help in navigating the maze of paperwork. I am also thankful to Nanowave Technologies for funding this research and for providing their expertise in sample assembly.

My thanks go out to all of my MiRCTECH groupmates, who provided a genuine laugh, heated political discussion, or an expert opinion nearly every day. My thanks also go out to the 'prelim' group, who helped to make life as a graduate student much more enjoyable. Thank you to Fernando and to Sarah for your encouragement when I needed it most. To Louann, for sharing her hard-earned wisdom and delicious gin. To Mark, whose friendship I will cherish for a lifetime. To Brooke, for her unwavering support. To Justin, whom I have relied on for so much and can depend on for anything. To Aida, without whom I may never have found the resolve to finish.

I would like to thank every one of my colleagues, friends, and family who has helped me to learn and to grow. Above all, I wish to express my deepest gratitude for the risks my grandparents took and the sacrifices my parents made to give me the opportunity to succeed.

# TABLE OF CONTENTS

| ACKNOWL                                          | EDGEN.   | MENTS                                                | iv  |

|--------------------------------------------------|----------|------------------------------------------------------|-----|

| LIST OF TA                                       | ABLES.   |                                                      | ix  |

| LIST OF FI                                       | GURES    |                                                      | X   |

| LIST OF SY                                       | MBOL     | S AND ABBREVIATIONS                                  | xiv |

| SUMMARY                                          |          |                                                      | xvi |

| CHAPTER                                          | 1: Intro | duction                                              | 1   |

| 1.1                                              | Backg    | ground                                               | 4   |

| 1.2                                              | Recen    | t Developments in Wideband PA Design                 | 7   |

| CHAPTER                                          | 2: Large | e Signal Device Characterization                     | 12  |

| 2.1                                              | Load-    | pull Technique                                       | 13  |

|                                                  | 2.1.1    | Theory of Operation                                  |     |

|                                                  | 2.1.2    | Passive Load-pull Configuration with Power Sensor    |     |

|                                                  | 2.1.3    | Passive Load-pull Configuration with Vector-receiver |     |

|                                                  | 2.1.4    | Active Load-pull Configuration                       |     |

| 2.2                                              | Devic    | e Measurements                                       | 23  |

|                                                  | 2.2.1    | Verification of Foundry PDK Models                   |     |

|                                                  | 2.2.2    | Device Characterization Measurements                 |     |

| 2.3                                              | Mode     | ling                                                 | 27  |

|                                                  | 2.3.1    | Nonlinear Device Model Creation                      |     |

| CHAPTER 3: Hybrid Microwave GaN Power Amplifiers |          |                                                      |     |

| 3.1                                              | •        | d Power Combining of Commercial Power<br>istors      | 32  |

|      | 5.1  | Futur          | e Work                                                                        | 91 |

|------|------|----------------|-------------------------------------------------------------------------------|----|

|      |      |                |                                                                               |    |

| СНА  | PTER | 5: Conc        | lusions                                                                       |    |

|      |      | 4.3.3          | Assembly and Measurements                                                     |    |

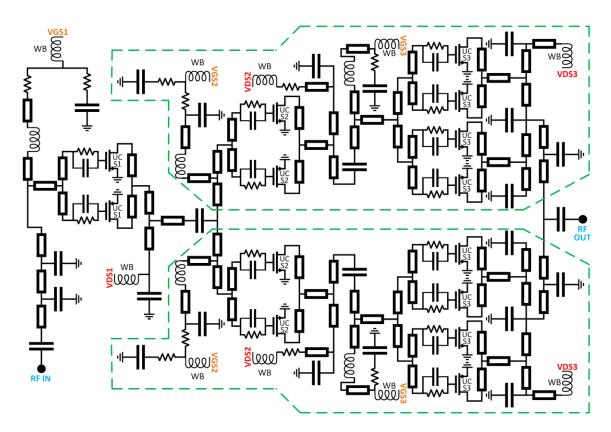

|      |      | 4.3.2          | Ultra-wideband 10-cell Traveling-Wave PA Design                               |    |

|      |      | 4.3.1          | Cree G28V5 Process Description                                                | 75 |

|      | 4.3  | Non-ı          | uniform Distributed 2-40 GHz MMIC PA                                          | 75 |

|      |      | 4.2.3          | Assembly and Measurements                                                     | 69 |

|      |      | 4.2.2          | 2-Stage Corporate-Combined PA Design                                          | 67 |

|      |      | 4.2.1          | Cree G28V5 Process Description                                                | 66 |

|      | 4.2  | React          | ively Matched Ka Band MMIC PA                                                 | 66 |

|      |      | 4.1.3          | Assembly and Measurements                                                     | 60 |

|      |      | 4.1.2          | 3-Stage Corporate-Combined Broadband Design                                   | 58 |

|      |      | 4.1.1          | NRC GaN150 Process Description and Sample<br>Characterization                 | 55 |

|      | 4.1  |                | ively Matched C-Ku Band MMIC PA                                               |    |

| CIIA |      |                | -                                                                             |    |

| СНА  | PTER | 4. Mon         | olithic Microwave GaN Power Amplifiers                                        | 55 |

|      |      | 3.3.3          | Measured Results                                                              |    |

|      |      | 3.3.2          | Fabrication and Assembly                                                      |    |

|      |      | 3.3.1          | Amplifier Topology and Design                                                 |    |

|      | 3.3  |                | -wideband Hybrid PA with Reactive / Resistive<br>hing on Disparate Substrates | 46 |

|      | 2.2  | - · ·          |                                                                               |    |

|      |      | 3.2.1<br>3.2.2 | Amplifier Topology and Design<br>Assembly and Measurements                    |    |

|      |      |                | eling Wave Technique                                                          |    |

|      | 3.2  | •              | id Broadband PA Implementation Using the                                      | 41 |

|      |      | 3.1.3          | Assembly and Measurements                                                     |    |

|      |      | 3.1.2          | Matching Network Design                                                       |    |

|      |      | 3.1.1          | Low-loss Wilkinson Power Dividers                                             |    |

| A.1     | Passive load-pull Configuration with Power-sensor:<br>System Setup   | 95 |

|---------|----------------------------------------------------------------------|----|

| A.2     | Passive load-pull Configuration with Power-sensor:<br>Calibration    | 95 |

| A.3     | Passive Load-pull Configuration with Vector-receiver:<br>Calibration | 96 |

| A.4     | Active Load-pull Configuration: Calibration                          | 97 |

| REFEREN | CES                                                                  |    |

# LIST OF TABLES

| Table 1 - Simulated and measured optimal large-signal impedances and         device performance of the TGF2023-01 die at 10 GHz | 35 |

|---------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2 - Final hybrid UWBPA design parameters                                                                                  | 48 |

| Table 3 - Facilities and tools used for microwave circuit fabrication and assembly                                              | 50 |

| Table 4 - Comparison of C-Ku Band GaN MMIC Reactively Matched PAs                                                               | 65 |

| Table 5 - Artificial Transmission Line Termination Components                                                                   | 80 |

| Table 6 - Comparison of Ultra-wideband GaN MMIC PAs                                                                             | 88 |

# LIST OF FIGURES

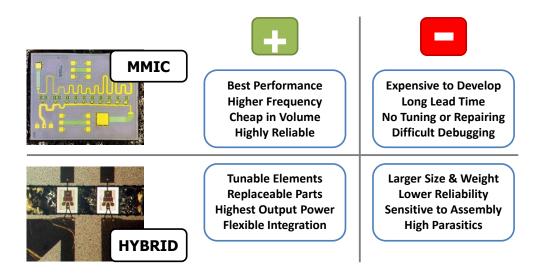

| Figure 1 - MMIC and HMIC comparison                                                                                                                                            | 5  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

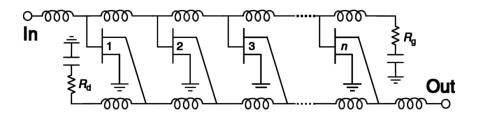

| Figure 2 - Simplified diagram of a traveling-wave amplifier [17]                                                                                                               | 7  |

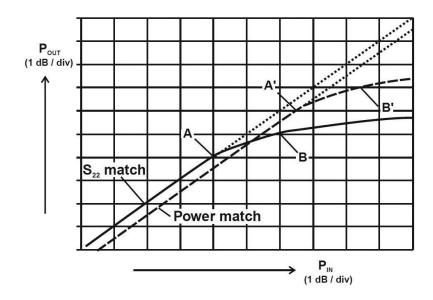

| Figure 3 - Power and compression characteristics for different output matching conditions [5].                                                                                 | 14 |

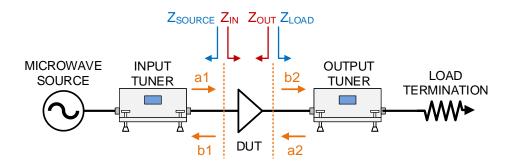

| Figure 4 - Annotated power wave block diagram                                                                                                                                  | 14 |

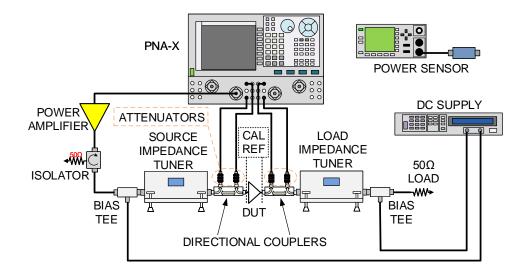

| Figure 5 - Diagram of the power-sensor based passive load-pull system                                                                                                          | 19 |

| Figure 6 - Photograph of the laboratory equipment setup for the power-<br>sensor based passive load-pull system                                                                | 19 |

| Figure 7 - Diagram of the vector-receiver based passive load-pull system                                                                                                       |    |

| Figure 8 - Photograph of the laboratory equipment setup for the vector-<br>receiver based passive load-pull system                                                             |    |

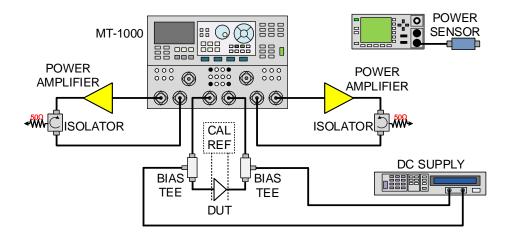

| Figure 9 - Diagram of the MT-1000 active load-pull system                                                                                                                      |    |

| Figure 10 - Photograph of the laboratory equipment setup for MT-1000 active load-pull system                                                                                   | 22 |

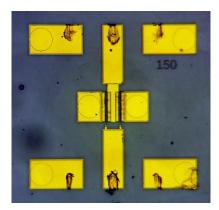

| Figure 11 - Photograph of the NRC GaN150 2x100µm device used for characterization and modeling                                                                                 |    |

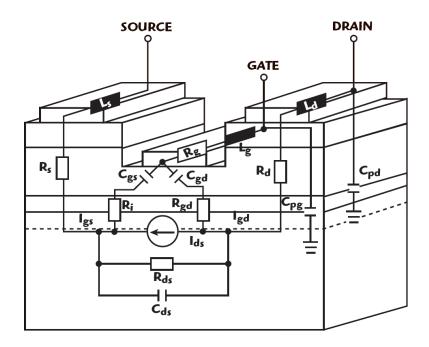

| Figure 12 - Schematic of the compact transistor model used for the NRC<br>GaN150 2x100 µm device                                                                               |    |

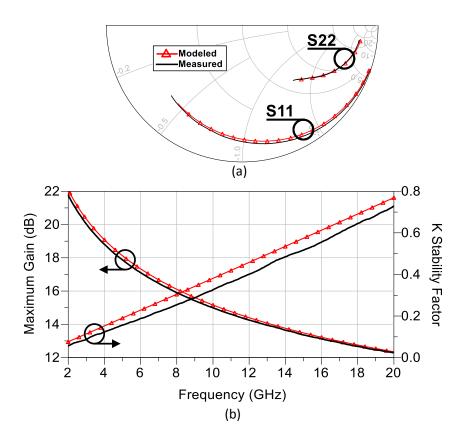

| Figure 13 - Measured and modeled S-parameters comparing (a) S11 and S22,<br>and (b) max gain and stability factor for a NRC GaN150 $2x100$ µm device at V <sub>DS</sub> = 28 V |    |

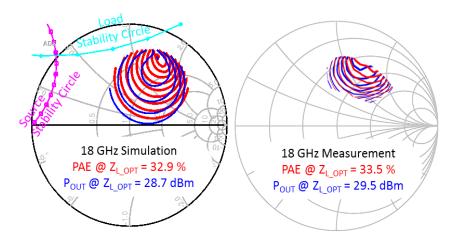

| Figure 14 - Nonlinear model simulation and large signal measurement comparison for a $2x100 \ \mu m$ device at $V_{DS} = 28 \ V$ , $P_{IN} = 22 \ dBm$ , and $f = 18 \ GHz$    |    |

| Figure 15 - Block diagram of hybrid multi-die PA architecture                                                                                                                  |    |

| Figure 16 - Material stack-up for EM simulation of the power divider networks                                                                                                  |    |

| Figure 17 - EM-simulated (a) insertion loss and (b) isolation and return loss for the equal-split Wilkinson power divider design                                               |    |

| Figure 18 - | (a) Simulated and (b) measured load-pull and source-pull contours for P <sub>OUT</sub> and PAE   | 36 |

|-------------|--------------------------------------------------------------------------------------------------|----|

| Figure 19 - | Diagram of hybrid PA module assembly using metal carrier with integrated die pedestal            | 37 |

| Figure 20 - | Photograph of the fabricated and assembled PA with inset showing gold wirebonds                  | 38 |

| Figure 21 - | Simulated and measured small-signal results                                                      | 39 |

| Figure 22 - | Simulated and measured P <sub>OUT</sub> , gain, and PAE vs. frequency results                    | 40 |

| Figure 23 - | Simulated and measured POUT, gain, and PAE vs. PIN at 9.5 GHz                                    | 40 |

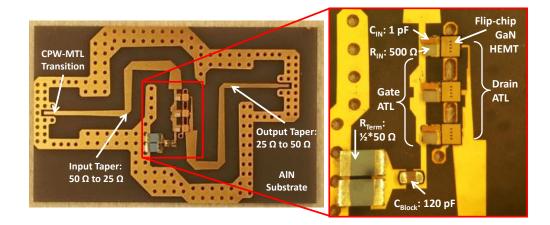

| Figure 24 - | Wideband distributed power amplifier schematic                                                   | 42 |

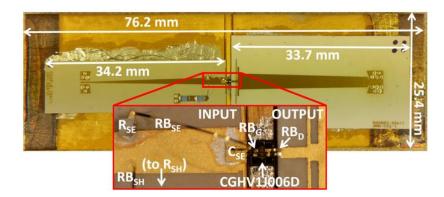

| Figure 25 - | Fabricated hybrid distributed power amplifier with assembly detail                               | 43 |

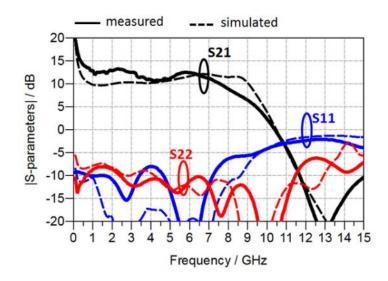

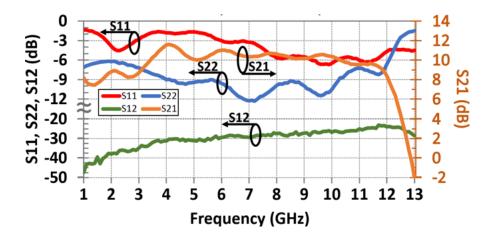

| Figure 26 - | Measured S-parameters under 10% duty cycle pulsed operation                                      | 44 |

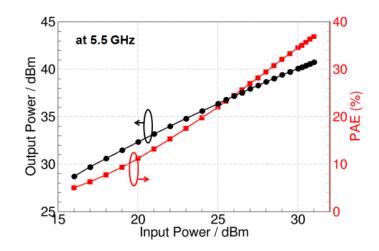

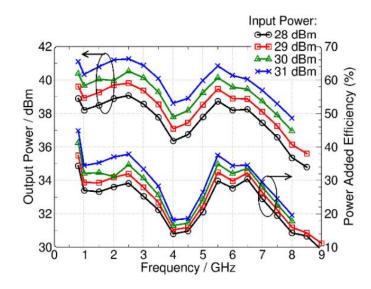

| Figure 27 - | • Measured P <sub>OUT</sub> and PAE at 5.5 GHz (10% duty cycle pulsed operation)                 | 45 |

| Figure 28 - | Measured P <sub>OUT</sub> and PAE from 1 to 9 GHz (pulsed with 10% duty cycle)                   | 45 |

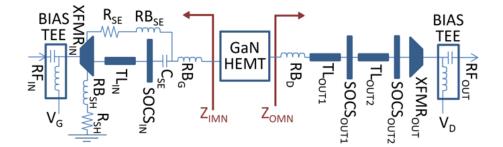

| Figure 29 - | Hybrid UWBPA schematic                                                                           | 47 |

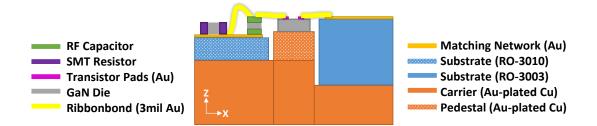

| Figure 30 - | Assembly diagram showing multi-level carrier with integrated pedestal                            | 51 |

| Figure 31 - | Fully assembled hybrid amplifier with dimensions                                                 | 51 |

| Figure 32 - | • Measured S-parameters of 1-11.5 GHz hybrid PA                                                  | 52 |

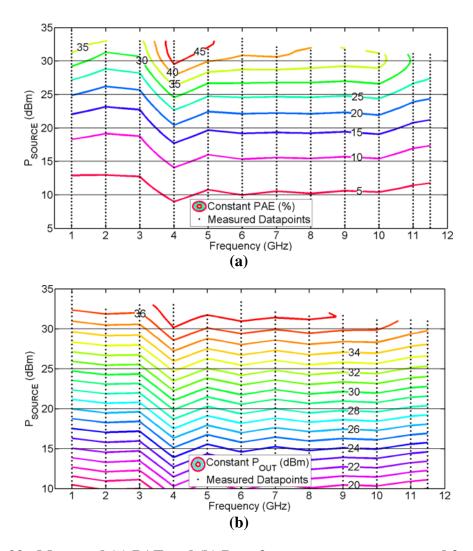

| Figure 33 - | Measured (a) PAE and (b) P <sub>OUT</sub> for swept source power and frequency                   | 53 |

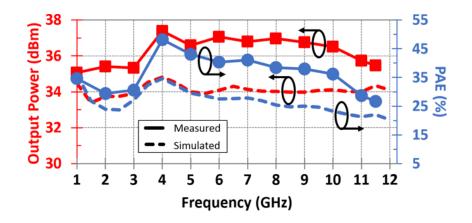

| Figure 34 - | P <sub>OUT</sub> and PAE from 1 to 11.5 GHz at fixed source power of 31 dBm                      | 54 |

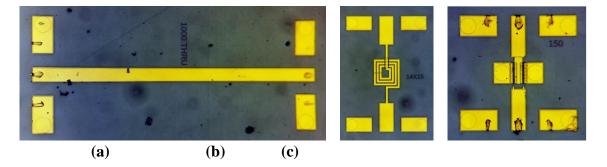

| Figure 35 - | Photos of measured NRC GaN150 (a) MTL, (b) inductor, and<br>(c) 2x100 μm HEMT samples            | 56 |

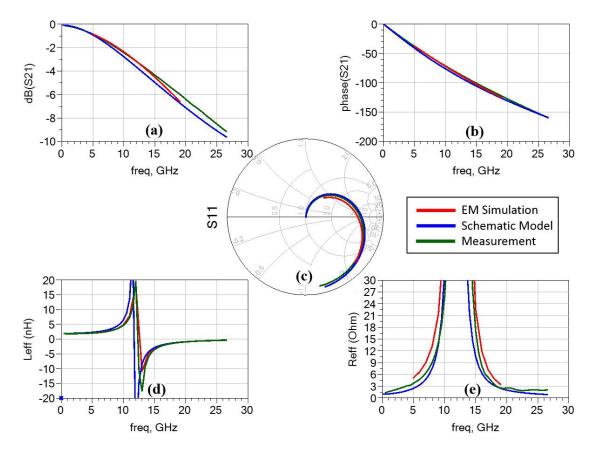

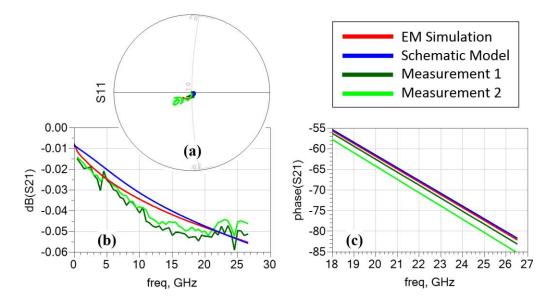

| Figure 36 - | Comparison of schematic model, EM simulation, and measured data for a NRC GaN150 spiral inductor | 57 |

| Figure 37 - | Comparison of schematic model, EM simulation, and measured data for a NRC GaN150 1000 µm TL                                                         | 58 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 38 - | Simplified schematic of the 3-stage PA design                                                                                                       | 59 |

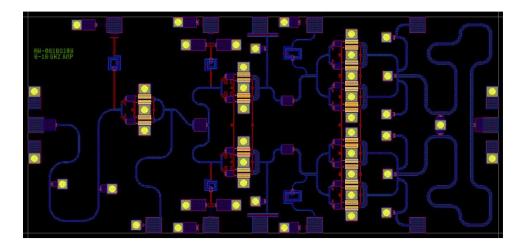

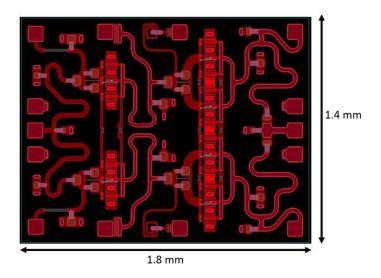

| Figure 39 - | C-Ku Band MMIC PA layout                                                                                                                            | 60 |

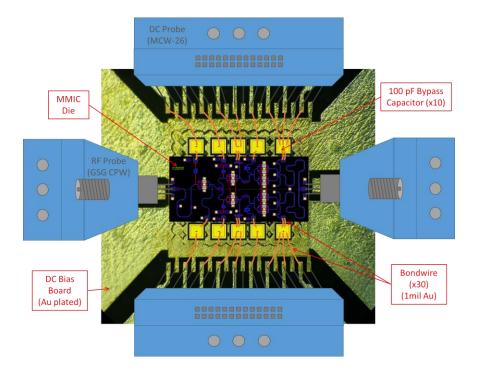

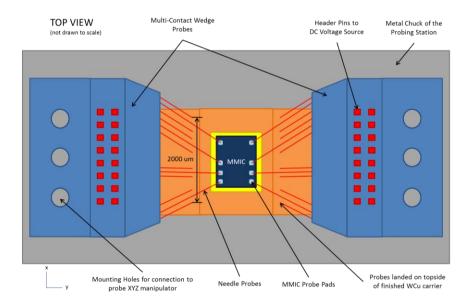

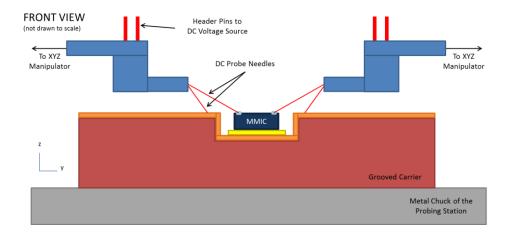

| Figure 40 - | Diagram of PA assembly and die probing for MMIC measurements                                                                                        | 61 |

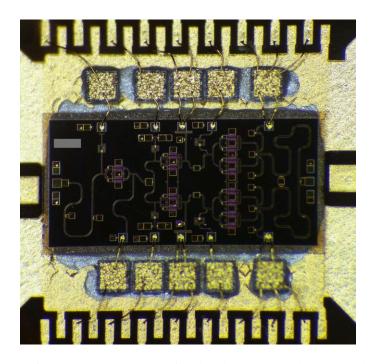

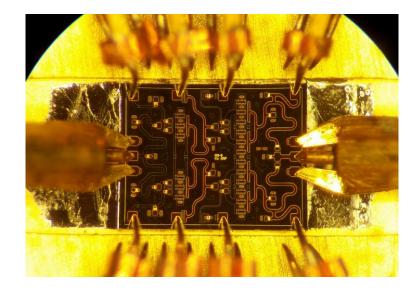

| Figure 41 - | Photo of the mounted MMIC PA with decoupling capacitors, gold WBs, and the DC multi-contact probe landing pads for biasing                          | 62 |

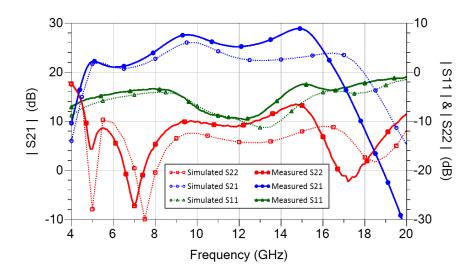

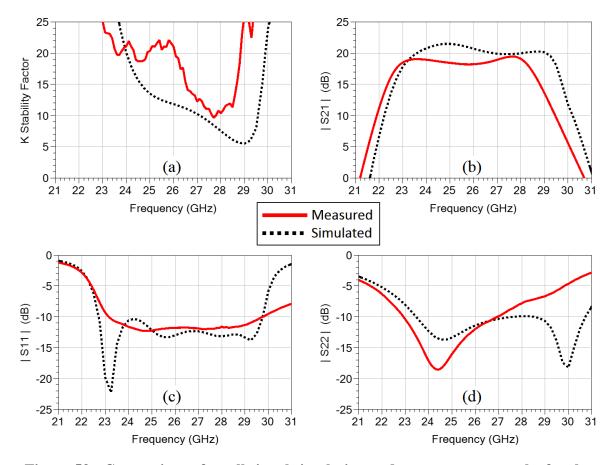

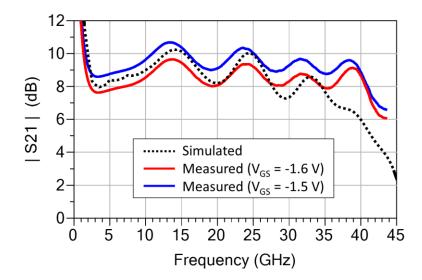

| Figure 42 - | S-parameter simulation and measurement results                                                                                                      | 63 |

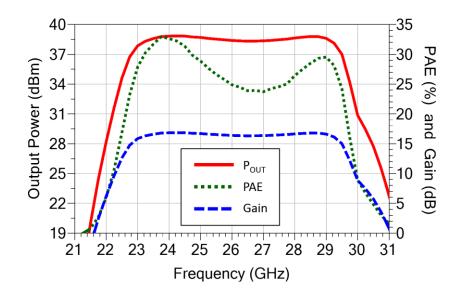

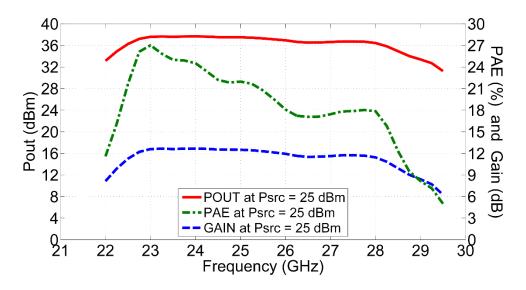

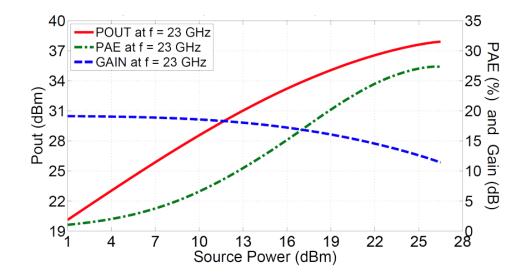

| Figure 43 - | Comparison of large signal swept frequency simulations and measurements at 20 dBm source power                                                      | 64 |

| Figure 44 - | 50 $\Omega$ power sweep measurement results at 16 GHz                                                                                               | 64 |

| Figure 45 - | Final schematic showing fully EM-simulated matching networks for the input, interstage, and output                                                  | 67 |

| Figure 46 - | Harmonic balance simulation results with EM-simulated<br>networks for the 2-stage Ka band MMIC PA showing output<br>power, PAE, and transducer gain | 68 |

| Figure 47 - | Final layout of the 2-stage Ka band reactively-matched MMIC PA                                                                                      | 68 |

| Figure 48 - | Probing setup (top view) for DC biasing of the Ka band MMIC PA                                                                                      | 70 |

| Figure 49 - | Probing setup (front view) for DC biasing of the Ka band MMIC PA                                                                                    | 70 |

| Figure 50 - | Gold-plated CuW carrier with milled grooves for eutectic die attach                                                                                 | 70 |

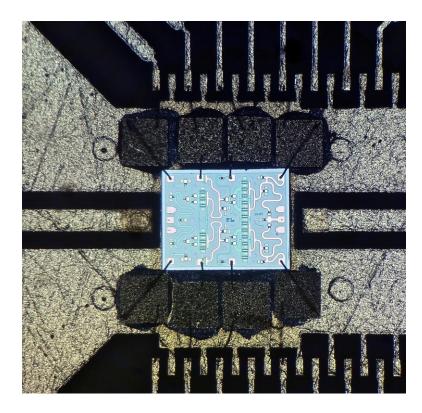

| Figure 51 - | Photo of a fabricated, probed, and measured Ka band MMIC PA                                                                                         | 71 |

| Figure 52 - | Ka band MMIC PA sample assembled with wirebonds and single layer capacitors for DC bias connections                                                 | 72 |

| Figure 53 - | Comparison of small signal simulation and measurement results for the Ka band MMIC PA                                                               | 73 |

| Figure 54 - | Large signal measurements of the Ka band MMIC PA versus frequency at 25 dBm source power                                                            | 74 |

| Figure 55 – | Power sweep measurements of the Ka band MMIC PA at 23 GHz                                                                  | 74 |

|-------------|----------------------------------------------------------------------------------------------------------------------------|----|

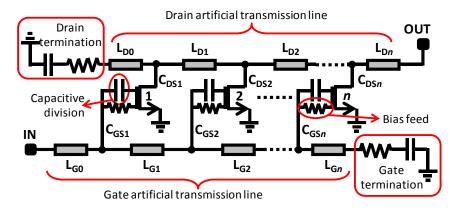

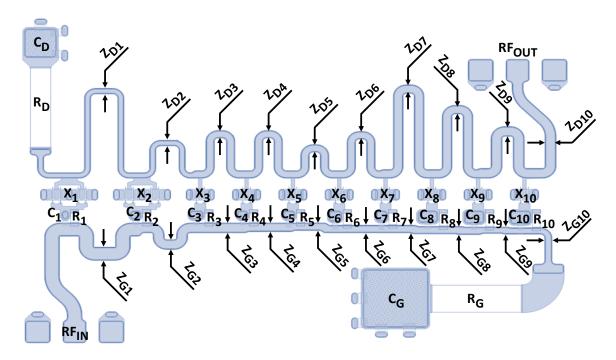

| Figure 56 - | Non-uniform distributed PA topology                                                                                        | 76 |

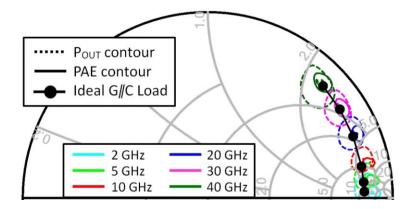

| Figure 57 - | Comparison of optimal power load impedance contours and a constant G  C load condition at select frequencies from 2-40 GHz | 78 |

| Figure 58 - | Layout of 10-cell NDPA with annotated component references                                                                 | 79 |

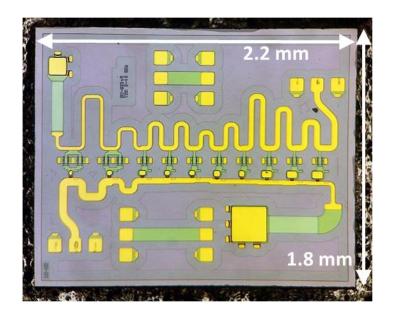

| Figure 59 - | Annotated photo of the fabricated and measured NDPA die                                                                    | 81 |

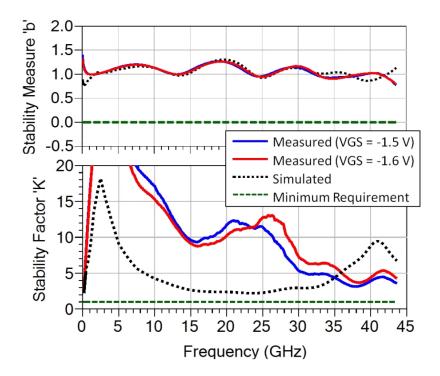

| Figure 60 - | Stability measure and stability factor, simulated vs. measured                                                             | 82 |

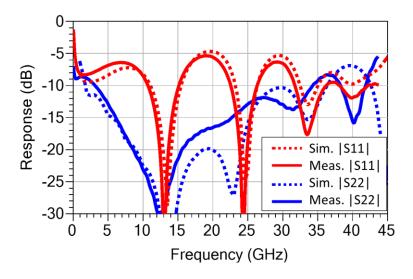

| Figure 61 - | Input and output return loss, simulated vs. measured                                                                       | 83 |

| Figure 62 - | Small-signal gain, simulated vs. measured                                                                                  | 83 |

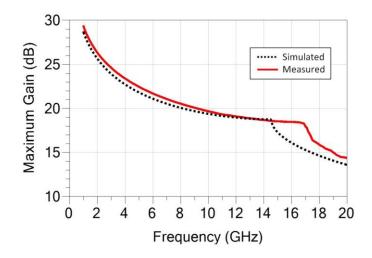

| Figure 63 - | Simulated vs. measured maximum gain for a 4x100 µm G28V5 device fabricated on the same wafer and reticle as the NDPA       | 84 |

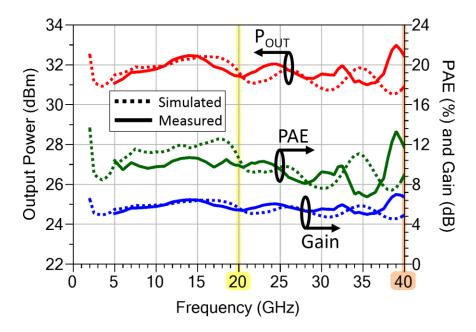

| Figure 64 - | NDPA large signal measurement results vs. frequency with 26 dBm source power                                               | 85 |

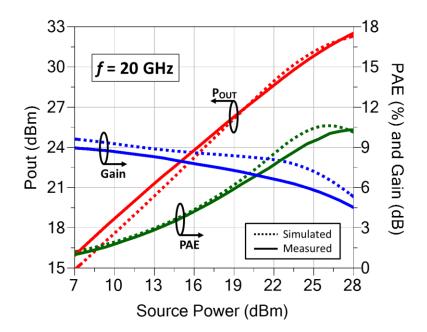

| Figure 65 - | Swept source power measurement results of the NDPA at 20 GHz                                                               | 86 |

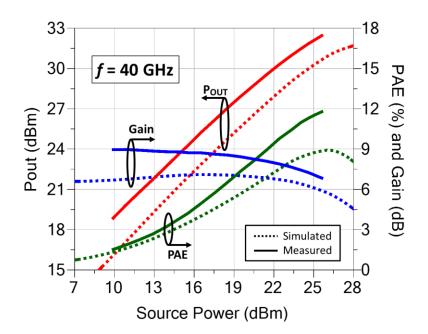

| Figure 66 - | Swept source power measurement results of the NDPA at 40 GHz                                                               | 87 |

# LIST OF SYMBOLS AND ABBREVIATIONS

| ADS              | Keysight's Advanced Design System             |

|------------------|-----------------------------------------------|

| AlN              | Aluminum Nitride                              |

| AuSn             | Gold Tin                                      |

| CuW              | Copper Tungsten                               |

| DC-IV            | Direct-Current Current-Voltage                |

| DC-MCW           | Direct-Current – Multi Contact Wafer          |

| DPA              | Distributed Power Amplifier                   |

| DUT              | Device Under Test                             |

| EM               | Electromagnetic                               |

| GaAs             |                                               |

| GaN              |                                               |

| HEMT             | High Electron Mobility Transistor             |

| HMIC             | Hybrid Microwave Integrated Circuit           |

| LDMOS            | Laterally Diffused Metal Oxide Semiconductor  |

| MMIC             | Monolithic Microwave Integrated Circuit       |

| NASA             | National Aeronautics and Space Administration |

| NDPA             | Non-Uniform Distributed Power Amplifier       |

| NRC              | National Research Council of Canada           |

| PA               | Power Amplifier                               |

| PAE              | Power Added Efficiency                        |

| PDK              | Process Development Kit                       |

| P <sub>IN</sub>  | Input Power                                   |

| P <sub>OUT</sub> | Output Power                                  |

| P <sub>SRC</sub> |                                           |

|------------------|-------------------------------------------|

| SiC              | Silicon Carbide                           |

| SMD              | Surface Mount Device                      |

| SOLT             | Short Open Load Thru (calibration method) |

| TaN              |                                           |

| TRL              |                                           |

| TWA              | Traveling-Wave Amplifier                  |

| TWTA             | Traveling-Wave Tube Amplifier             |

| UC               | Unit Cell                                 |

| UWBPA            | Ultra-Wideband Power Amplifier            |

#### SUMMARY

The objective of this research is to compare and advance the predominant methods of realizing broadband microwave power amplifiers (PAs) up to 40 GHz with high efficiency using gallium nitride (GaN) technology. The studied architectures are based on the reactive/resistive matching approach and the traveling wave technique in both hybrid and monolithic microwave integrated circuits (MMICs). Important details of design development and integration are discussed, featuring discrete component descriptions, substrate material selections, additional matching techniques, and comparisons of both wirebonds and flip-chip bonds that are used for PA interconnections.

With a focus on improving the bandwidth and efficiency of the architectures mentioned above, the presented hybrid PA designs achieve state-of-the-art performance with commercially-available GaN power transistors. This work demonstrates the highest power added efficiency (27–48%) and widest bandwidth (1.0-11.5 GHz) for a multi-watt hybrid PA implementation.

To complement these novel hybrid PA designs and integration developments, broadband MMIC PAs were designed at higher frequencies. The results of device characterization and wideband modeling are presented for a new 0.15  $\mu$ m GaN process in support of a 3-stage broadband MMIC PA design with reactive/resistive matching. Lastly, an ultra-wideband non-uniform distributed PA design is fabricated on a pre-release version of a new 0.14  $\mu$ m GaN process. For the first time, a GaN MMIC PA with output power greater than 1 W and nearly 10% power added efficiency was successfully achieved from 2 to 40 GHz, surpassing previously-reported results.

### **CHAPTER 1:**

### **INTRODUCTION**

*"Our astonishment at what has been accomplished would be uncontrollable were it not held in check by the expectation of greater miracles to come."* – Nikola Tesla, 1905

Ever since the days of the spark gap experiments, humans have been discovering and inventing new techniques to harness electromagnetic phenomena for the benefit of mankind [1]. Developments in the generation, amplification, transmission, and reception of high-frequency electromagnetic waves have unlocked an expansive set of applications for microwave technology. From the revolutionary emergence of terrestrial radio telegraphy [2] to the remarkable normalcy of a satellite video feed from across the globe, advancements in the wireless arts have been transforming the ways in which people communicate with one another for over a century.

Moreover, the utility of microwave radiation extends far beyond communication. This type of energy can interact with our environment in predictable patterns, thereby forming the basis for spectroscopy and remote sensing. The study of these interactions can both deepen our understanding of the universe around us [3] and enhance our quality of life here on Earth. Since their initial development in the 1930s for defense purposes [4], modern radar systems have found enduring success in aerospace, marine, and weather applications. Because these systems usually require high levels of microwave power to function, there is naturally a strong interest in both novelty and improvement of devices that can offer high output power at high frequencies. It is the role of the power amplifier (PA) circuitry to realize these high-powered signals in a microwave system.

The primary objective of a PA design is to deliver the highest output power possible from a selected active device [5]. Similar emphasis is often placed on maximizing the power added efficiency (PAE) of a power amplifier design, as PAE represents how well the amplifier accomplishes the conversion from direct current (DC) and microwave input power to microwave output power. Another important PA metric is its power gain, which indicates the amount of signal amplification at a given level of output power. Some additional figures of merit describe the noise figure, matching quality, and degree of non-linearity. Depending on the intended application, these parameters can be included in PA design optimizations as well. Whatever the specific design goals may be, a PA must deliver power to a load across a range of operating frequencies.

The PA is at the heart of any communication system, and modern communication systems demand wideband performance. Increases in wideband power amplifier (PA) output power and large signal gain are critical for advancements in electronic warfare, next-generation wireless communication, and multi-band radar applications. Amplifier designs for these applications – and others, such as phased arrays and satellites – could benefit from increased bandwidth, reduced size, and improved efficiency. Two different technologies can enable us to meet the requirements of these high-performance applications: traveling-wave tubes and semiconductor devices.

Radar systems have historically employed traveling wave tubes for the required power amplification, but the tubes are large and heavy, require kV range supply voltages, have poor reliability, and often fail catastrophically [6]. Semiconductor technologies such as silicon-based laterally diffused metal oxide semiconductors (Si-LDMOS), gallium arsenide (GaAs), and gallium nitride on silicon carbide (GaN-on-SiC) have also been developed to address the challenges of high-power microwave amplification. Si-LDMOS is a mature semiconductor process that can deliver kW levels of output power, but it is currently limited to a maximum usable frequency of about 6 GHz [7]. While GaAs has excellent linearity characteristics and frequency response, it suffers from low power density and low breakdown voltage [8].

In contrast to Si-LDMOS and GaAs, GaN-on-SiC has an unprecedented combination of power density, thermal conductivity, and breakdown voltage. This technology alone has demonstrated high power and high-frequency operation over wide bandwidths in a solidstate amplifier [9]. Beginning in the late 1990s, significant investments in GaN technology – from both government [10] and industry [11] sponsors – have spurred massive research efforts, streamlined manufacturing processes, and sparked enormous commercial market growth. With Wolfspeed's announcement in April 2016 that its GaN-on-SiC process has demonstrated compliance with NASA reliability standards for satellite and space systems [12], GaN technology is poised to aggressively expand into this perfectly-suited market.

Because of their higher operating voltage and current density, GaN devices exhibit a relatively higher load impedance for a given power level [9] as compared to other semiconductor technologies. This lower transformation ratio to match a standard 50  $\Omega$  load

is a major asset in wideband microwave circuit design. The higher output power density (over 4.5 W/mm) provided by GaN process technology is supported by its SiC substrate, which can significantly improve the thermal performance of the device. By harnessing these characteristics of GaN technology, future innovations in broadband PA design can offer improvements in size and weight to existing applications, increase data transmission rates, and facilitate development of novel transmission encoding schemes. In addition to supporting wider bandwidths in high-power circuits, GaN high electron mobility transistors (HEMTs) can withstand severe impedance mismatches without failure [13]. Therefore, the use of GaN devices can provide a microwave system with a higher degree of interoperability, reliability, and simplicity. Considering these compelling benefits, this dissertation is concentrated on the design and integration of broadband microwave power amplifiers using GaN technology.

#### 1.1 Background

To capitalize on the benefits of GaN technology, a microwave circuit designer must select an implementation method for bringing a design into reality. After the nascent years of microwave system development using waveguides, mechanical processing improvements enabled the fabrication of passive microwave circuits on planar dielectric substrates. When an active microwave component – such as a transistor – is bonded onto this passive structure, the resulting device is termed a hybrid microwave integrated circuit (HMIC). This hybrid circuit is contrasted by a monolithic microwave integrated circuit (MMIC), which has all of its passive and active elements integrated into a single chip by a

semiconductor technology process [14]. These two integration methods are complementary in many ways [15], as shown in Figure 1.

Figure 1 - MMIC and HMIC comparison

However, regardless of their individual characteristics, all MMICs will eventually become hybrids. An MMIC is of no use alone, as it must connect to other chips for bias, logic, thermal sinking, and other such functions. The distinction can be recognized by the degree of integration, and the lower parasitics can provide the MMIC with a larger bandwidth and higher frequency response. Yet, both HMICs and MMICs in GaN technology must contend with the effects of high thermal dissipation. This issue directly influences many design decisions, such as substrate material selection and die attach method. Given the substantial power density of GaN technology, the careful management of heat with prudent integration and packaging techniques can help to improve the performance of any GaN PA design [9]. Achieving multi-octave bandwidths in power amplifiers is particularly challenging due to several inherent properties of microwave transistors. The frequency-dependent gain roll-off, usually 4-6 dB/octave, must be compensated with additional circuitry to obtain a flat gain profile [16]. The input and output impedances of the transistor also vary with frequency, and they must be matched across the entire design bandwidth. Furthermore, to achieve higher output power levels with a given technology, the device's size must be increased. This increase in active periphery drives the transistor's impedances even lower. With such a high transformation ratio for operation in a 50  $\Omega$  environment, the quality of the match will suffer for a wideband design, reducing PAE and increasing the likelihood of thermal degradation.

Several circuit topologies have been developed to achieve broadband amplifier performance at microwave frequencies [16]. Each topology has its own methods and trade-offs to address these and other broadband design challenges. The main two topologies used in microwave PA design are reactive/resistive matching and the traveling-wave technique [17]. The reactive/resistive matching approach involves the use of reactive elements (capacitors, inductors, transmission lines) and resistors in the design of transistor matching networks [18]. A broadband PA using this approach will require a higher number of elements to achieve both the impedance transformation necessary for 50  $\Omega$  system operation and the gain compensation for a flat gain profile [16]. Reactive/resistive matching can yield better large-signal performance (i.e., higher output power, gain, and/or PAE) if the matching network design can tune the source and load to their optimal values

over the desired band. However, it is typically more limited in bandwidth than a travelingwave design.

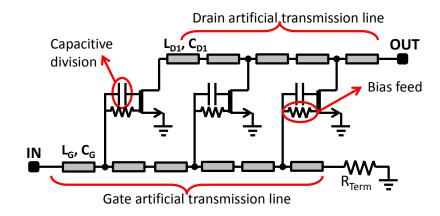

A traveling-wave amplifier (also known as a distributed PA) involves cascading several transistors together, as shown in Figure 2, and designing their interconnections as artificial transmission lines (ATLs). The gate and drain interconnection lines are optimized to enable in-phase addition of transistor currents at each cell and absorb the transistor capacitances for broadband operation [19]. While a traveling wave amplifier can realize an extremely wide bandwidth, it comes at the cost of reduced power gain and reduced output power density. When the transistor cells of a traveling-wave amplifier have different active peripheries, the design is said to be non-uniform. This adjustment in methodology can help to improve the output power and efficiency of a distributed amplifier design. With that in mind, this research is focused on enhancing the performance of two selected topologies – the reactive/resistive matching approach and the traveling wave technique – in both HMIC and MMIC implementations.

Figure 2 - Simplified diagram of a traveling-wave amplifier [17]

#### **1.2 Recent Developments in Wideband PA Design**

Microwave applications in the 1-40 GHz range – such as radar, wireless communication, and remote sensing – have an immense impact on our way of life.

Considering this impact, sustained research efforts have concentrated on improving the performance of the underlying technologies that enable these applications. Since the PA is an essential component of many microwave systems, many published works have focused on innovative PA designs in both HMIC and MMIC implementations.

#### Hybrid Microwave Integrated Circuit Power Amplifiers

With an aim of improving radar efficiency and range, several hybrid PA designs near X band have employed the reactive/resistive matching technique with GaN dies. Results have been reported from 1.6-14.1 W output power at 15-32% PAE and bandwidths in the 3-10 GHz range [20], [21]. This output power range is studied most often because a multi-watt PA module is typically selected as the "unit cell," or fundamental building block, of a high-power PA that uses many modules to achieve kilowatt levels of output power. It also represents the region of output power where thermal effects can begin to seriously degrade a device's performance. To mitigate this thermal degradation by physically spreading out the heat sources, a four-way Wilkinson division PA on AlN with four 1 mm-class GaN dies was designed in [22]. That publication reported measurements of 20% PAE and 8.5 W output power, giving a power density of 2.2 W/mm.

While increased output power and reduced thermal degradation are essential objectives in a GaN PA design, improvements in PAE and bandwidth are vital for driving the mobile broadband applications of tomorrow. A flip-chip hybrid design in [23] produced 1.8 W output power from 6.5-16 GHz at 17-39% PAE, featuring a wide bandwidth and high efficiency. However, the GaN dies required special processing, and device heating

becomes problematic because the flip-chip method of die attach creates a very poor thermal sink. Further improvements were reported in [24], where the design achieved a decade bandwidth and high PAE, but had an upper frequency limit of 4.1 GHz.

The best hybrid performance was published in [25], where 5 W output power and 20-33% PAE were measured over a 0.35-8 GHz bandwidth. Analysis of these previously-published results suggested that a multi-watt, ultra-wideband PA design using the reactive/resistive approach with commercial GaN dies above 10 GHz was unexplored for a hybrid implementation. Therefore, part of this work is devoted to the design of a reactively-matched multi-watt hybrid GaN PA covering the L-X bands.

Previously-published examples of an HMIC PA using the distributed approach at microwave frequencies are limited. When compared with an MMIC, the transistor interconnection parasitics can be large in a hybrid implementation, and device parasitics can be large for even the smallest singulated GaN HEMT die. Therefore, prior designs have concentrated on a lower frequency range, with [26] reporting 5-10 W output power and 20-50% PAE from 0.02-3 GHz. Since the published literature has not generally addressed the challenges of ultra-wideband distributed PA design near X band in a hybrid implementation, that area represents another focal point of this dissertation.

### Monolithic Microwave Integrated Circuit Power Amplifiers

Significant research into the GaN MMIC implementation of reactive/resistive PAs in the X-Ku bands has been conducted, and the published results are summarized in the

comparison table of [27]. Five of these results cover a 100% relative bandwidth, from 6-18 GHz, which is a valuable range of operation for multi-band radar and electronic warfare applications. Further analysis of the results provides insight into the performance trade-off of output power, PAE, and bandwidth in a wideband GaN MMIC PA. As the output power of the reported MMICs increases from 2 W to 16 W, the average PAEs tend to decrease from 28% to 17%. In two other publications shown in [27], an increase of bandwidth to 6-20 GHz led to 2.5 W output power and 10% average PAE. Conversely, a decrease of bandwidth to 8-14 GHz led to 3.2 W output power and 41% average PAE. Another important facet to the performance trade-off described above is output power density, as it impacts the size and weight of the fabricated PA. A reduced physical footprint is beneficial in both commercial and military applications, so a piece of this work is allocated to improving the output power per die area in a multi-stage wideband GaN MMIC PA design.

Compared to HMICs, the use of a distributed approach in MMICs is demonstrated more frequently in publications. Most of these publications have targeted the 2-20 GHz band. The best reported PAs have achieved 10-20 W output power with 12-39% PAE over this band using GaN technology [28], [29]. However, few publications have addressed the additional challenges as frequency and bandwidth are increased. One such publication presented a 2-stage distributed MMIC using 100 nm GaN technology with output power of 0.5 W from 8-42 GHz [30]. The same author also reported 1 W output power from 6-37 GHz with 10% PAE in a dual-stage distributed MMIC design [31], representing the first time this level of output power had been achieved over such a wide band. Given these

previously published works, a portion of this research is dedicated to achieving multi-watt output power up to 40 GHz in a distributed GaN MMIC PA design.

Before any amplifier designs can be studied, we first need to have a device model that accurately represents the power transistor's performance. To better understand the fundamental relationships of PA design for large signal operation, Chapter 2 explores the different measurement techniques and challenges related to non-linear device characterization and modeling. In preparation for an MMIC PA design, the chapter concludes with the creation of a compact model for a new GaN transistor. Chapter 3 begins with the verification of a manufacturer's model for a commercially-available GaN device, and then presents the design, fabrication, assembly, and measurement of three different *hybrid* microwave PAs. Finally, Chapter 4 presents the design, fabrication, assembly, and measurement of three different *monolithic* microwave PAs. Large-signal PA characteristics will now be discussed to provide context for the upcoming measurement techniques and modeling results.

#### **CHAPTER 2:**

### LARGE SIGNAL DEVICE CHARACTERIZATION

To attain broadband amplifier performance at microwave frequencies, it is imperative to understand and predict how an active device will behave under the expected range of operating conditions. Due to their parasitic reactances, active devices generally have low gain at microwave frequencies. Compensation of these parasitics is critical to obtain useable gain in a microwave amplifier [5]. Furthermore, any conductor used for interconnections has appreciable electrical length with respect to wavelength at microwave frequencies. Since quasi-static circuit theory is not valid under these conditions, transmission line theory is applied to include these interconnections as part of the circuit.

In a linear amplifier design, an active device is provided a simultaneous conjugate match at its input and output ports for optimal gain. Although preliminary power amplifier designs can often be obtained through modification of linear amplifier designs, PAs are typically operated under nonlinear conditions [5]. When a PA is driven with a large signal, or a signal of sufficient magnitude to cause bias variations or gain compression, the active device begins to behave in a nonlinear manner. Unfortunately, accurate predictions of device performance in a nonlinear region cannot generally be obtained from linear methods alone. This dilemma is what imposes the requirement of nonlinear device characterization and modeling in PA design. To help determine the optimal termination conditions for nonlinear operation, we use the load-pull technique.

#### 2.1 Load-pull Technique

A power amplifier design is typically focused on achieving maximum output power (or PAE, or both) from an active device. The impedances required for optimal power or optimal efficiency can be significantly different from the impedances required for optimal gain [5]. The most prevalent method of determining the optimal large signal impedances for an active device is to perform a sequence of device measurements under large signal drive conditions for a range of swept impedance values. This process, known as *load-pull*, is widely employed for characterizing the nonlinear behavior of microwave transistors [33].

Figure 3 illustrates the value of the load-pull technique by comparing the output power of an amplifier under two different output impedance conditions: conjugate match and power match. Although gain is slightly lower, almost 2 dB of additional output power is realized from the active device when it is provided with an optimal power match. Consequently, to obtain the best large signal performance in a PA design, the transistor's output port is not presented with a linear conjugate match [5]. Instead, load-pull is used to determine the optimal matching conditions for the device.

Figure 3 - Power and compression characteristics for different output matching conditions [5].

#### 2.1.1 Theory of Operation

Load-pull measurement systems have evolved over time to improve accuracy, speed, and flexibility; but their underlying principle has remained the same: vary the impedance presented to a device under test (DUT), and measure the device performance over a range of excitation conditions [32]. The generic power wave block diagram in Figure 4 is annotated to help clarify the relationships and performance metrics defined below.

Figure 4 - Annotated power wave block diagram

The input reflection coefficient  $\Gamma_{IN}$  of the DUT, which is related to its input impedance  $Z_{IN}$ , is defined below in Equation 1. The input power  $P_{IN}$  (Equation 2) describes the power that is actually delivered to the DUT and amplified by the active device. Equation 3 defines the source power  $P_{SOURCE}$ , which is the power available from a microwave source with an internal impedance of  $Z_{SOURCE}$ . Lastly, Equation 4 describes the output power  $P_{OUT}$ , or the power delivered by the DUT to the load impedance  $Z_{LOAD}$ .

$$\Gamma_{IN} = \frac{b1}{a1} \tag{1}$$

$$P_{IN} = \frac{1}{2} (|a1|^2 - |b1|^2) = \frac{1}{2} |a1|^2 * (1 - |\Gamma_{IN}|^2)$$

(2)

$$P_{SOURCE} = \frac{P_{IN}}{1 - \left|\frac{Z_{IN} - Z_{SOURCE}}{Z_{IN} + Z_{SOURCE}}\right|^2}$$

(3)

$$P_{OUT} = \frac{1}{2} (|b2|^2 - |a2|^2) = \frac{1}{2} |b2|^2 * (1 - |\Gamma_{LOAD}|^2)$$

(4)

Note that  $P_{SOURCE}$  (power available from the source) is always greater than  $P_{IN}$  (input power delivered to the DUT), except under perfect input matching conditions where  $Z_{SOURCE} = Z_{IN}^*$ . With these definitions of power, we can now create several different ratios of power which describe specific gain relationships. The power gain  $G_P$  is the output power to input power ratio (Equation 5). In other words, power gain is the ratio of power delivered

into the load to power delivered into the DUT. This is contrasted by transducer power gain G<sub>T</sub>, found in Equation 6, which is the ratio of output power to source power.

$$G_P = \frac{P_{OUT}}{P_{IN}} = \frac{|b2|^2 * (1 - |\Gamma_{LOAD}|^2)}{|a1|^2 * (1 - |\Gamma_{IN}|^2)}$$

(5)

$$G_T = \frac{P_{OUT}}{P_{SOURCE}} = \frac{|b2|^2 * (1 - |\Gamma_{LOAD}|^2)}{|a1|^2 * (1 - |\Gamma_{IN}|^2)} * \left(1 - \left|\frac{Z_{IN} - Z_{SOURCE}}{Z_{IN} + Z_{SOURCE}}\right|^2\right)$$

(6)

Lastly, we define power added efficiency (PAE) of the DUT as the ratio of power added to power consumed. As Equation 7 shows, the  $P_{IN}$  (not the  $P_{SOURCE}$ ) must be known in order to accurately calculate PAE.  $P_{DC}$  is the total DC power consumed by the DUT, and linear quantities should be used for all values in Equation 7.

$$PAE = \frac{P_{OUT} - P_{IN}}{P_{DC}}\%$$

(7)

The primary goal of a load-pull system is to measure the quantities defined in Equations 1-7 [32] at every selected impedance condition. Impedance tuning is achieved using either passive mechanical tuners, active amplifier tuners, or a combination of both. A passive mechanical tuner uses the relative positioning of its internal passive elements to determine which part of the signal is transmitted through the tuner and which part of the signal is reflected back toward the signal source [33]. In this way, the magnitude and phase of the impedance at the DUT can be controlled. If fixture losses are minimized, a wide range of impedances on the Smith Chart can be presented to the DUT. In contrast to the partial signal reflection of a mechanical tuner in a passive load-pull system, an active load-pull system injects a signal at a particular magnitude and phase to tune the impedance at the DUT [34]. Since an external amplifier is used for this active signal injection, the entire range of the Smith Chart can be presented to the device.

For characterization of power devices, a load-pull system will typically be configured to associate the impedance presented to the DUT with the measured large-signal parameters (e.g., output power, power added efficiency, power gain). Measurements are collected over a swept range of impedances, and the data are shown on the Smith Chart in the form of *load-pull contours*. These data are plotted for a specified large-signal performance metric, so each parameter (such as output power or PAE) has its own set of contours. The contours show how the behavior of the DUT changes with respect to impedance, and indicate the value of impedance required for optimal performance.

Load-pull data are most valuable when the measurements are collected at the desired operating conditions of the device. Biasing of the DUT is required, and the bias point for the device can be swept to measure the impact of reduced conduction angles on large-signal performance. The bias can be applied at any duty cycle, but the DC supply for the drain of a power device is often configured for pulsed operation with ~10% duty cycle. This technique mitigates the performance reduction and reliability issues that occur due to thermal degradation at high dissipated power levels. For depletion-mode devices (such as the GaN HEMTs discussed in this work), the bias voltage must first be applied at the gate,

and then at the drain, for safe operation. Therefore, pulse order and synchronization are critical for protecting the DUT from catastrophic damage during measurement.

In addition to configuring the bias, the drive conditions of the microwave signal must be defined. Load-pull contours are only valid for a particular frequency, so selection of the fundamental operating frequencies involves a tradeoff of measurement granularity and time. For each selected measurement frequency, the power level of the signal must also be chosen. Power amplifiers are almost always operated with some amount of gain compression to obtain higher output power and efficiency, so the source power of the microwave signal must be calibrated and controlled to enable load-pull measurements at the desired level of compression. The source power can also be swept during measurement to provide insight on how the amount of gain compression impacts the device performance.

Different configurations of laboratory equipment can be used to execute load-pull measurements, each with its own benefits and drawbacks. With this general understanding of the excitation conditions and impedance tuning requirements for load-pull measurements, the specific load-pull systems that were used for all large-signal measurements throughout this work can now be discussed.

#### 2.1.2 Passive Load-pull Configuration with Power Sensor

This traditional load-pull method uses passive mechanical tuners to control the impedances at the DUT and a scalar power meter to determine the output power of the device. The diagram in Figure 5 identifies the main functional blocks of the measurement system [32], and the photo in Figure 6 depicts the laboratory equipment setup. A more

detailed description of the required hardware interconnections is provided in Appendix A.1.

Figure 5 - Diagram of the power-sensor based passive load-pull system

Figure 6 - Photograph of the laboratory equipment setup for the power-sensor based passive load-pull system

Biasing of the DUT is accomplished with external bias tees fed by DC supplies that are capable of sourcing the required currents at the required voltages. When the DUT is equipped with DC blocking capacitors, the external bias tees can be removed and bias can be applied directly to the DUT with wires or probes. After the laboratory equipment setup is finalized, the system is calibrated using the procedure described in Appendix A.2. Once the calibration is complete, the vector network analyser (VNA) is no longer required for load-pull measurement.

#### 2.1.3 Passive Load-pull Configuration with Vector-receiver

This upgraded passive load-pull method uses the same passive mechanical tuners and biasing setup as discussed in Section 2.1.2, but it also introduces directional couplers between the tuners and the DUT. The diagram in Figure 7 identifies the main functional blocks of the measurement system [32], and Figure 8 depicts the laboratory equipment setup. Directional couplers are connected to two receivers on the VNA, which enables direct measurement of the a and b waves at the input and output planes of the DUT. After the laboratory equipment setup is finalized, the system is calibrated using the procedure described in Appendix A.3.

Figure 7 - Diagram of the vector-receiver based passive load-pull system

Figure 8 - Photograph of the laboratory equipment setup for the vector-receiver based passive load-pull system

While this load-pull configuration requires a network analyser during all measurements, it can accurately record both source power and input power at the DUT plane. Furthermore, the network analyser is frequency-selective, so the output power of the DUT can be accurately measured at a single frequency. These features represent significant improvements to the power-sensor based passive load-pull configuration, in which only the available source power is known, and the output power is measured simultaneously at all frequencies covered by the power sensor. Because of its input power measurement capability and frequency selectivity, the vector-receiver based passive load-pull configuration can provide a true measurement of PAE, which is a critical metric in nearly every microwave PA design.

# 2.1.4 Active Load-pull Configuration

Although passive mechanical tuners can handle high power and are less costly, there is no realistic way to overcome the losses introduced by the passive tuner itself and the fixturing required to interface it with the DUT. In contrast to the passive load-pull configurations, no mechanical tuners are required in an active load-pull system. Instead, the active system uses high powered loop amplifiers to inject specific signals at the source and load. The diagram in Figure 9 identifies the main functional blocks of the measurement system [34], and Figure 10 depicts the laboratory equipment setup.

Figure 9 - Diagram of the MT-1000 active load-pull system

Figure 10 - Photograph of the laboratory equipment setup for MT-1000 active load-pull system

The active load-pull configuration achieves impedance tuning by using signal injection to manipulate the ratio between reflected signals and forward-traveling signals, thereby providing the desired impedance conditions at the DUT. After the laboratory equipment setup is finalized, the system is calibrated using the procedure described in Appendix A.4. While this type of load-pull configuration is very expensive, it provides the widest tuning range possible, flexible reconfiguration, and 100-fold reduction in measurement time.

The three load-pull system configurations discussed above – power-sensor, vectorreceiver, and active – were available at various times for large-signal device characterization and PA performance verification measurements. All the large-signal measurement results presented throughout this dissertation were collected on one of these three measurement configurations. We will now examine how a load-pull system is used to verify the accuracy of a nonlinear device model for use in a PA circuit design.

#### 2.2 Device Measurements

Many manufacturers of microwave power devices provide circuit designers with models to help predict the electrical performance of their transistors. These models are typically based on measurements of a unit cell, or a transistor with small active periphery. Microwave design software, such as Keysight ADS, can be used to access the models and determine optimal bias, impedance, and drive conditions to achieve the goals of the circuit. For any PA design, it is crucial to ensure that model simulations are consistent with measured data. Therefore, characterization of device samples and verification of device models are essential to build confidence in the simulation results and increase the likelihood of a successful design. All of the work discussed in Chapter 3 and Chapter 4 used transistor models that were validated with both S-parameter and load-pull measurements. A  $2x100 \mu m$  device fabricated on the NRC GaN150 process will now be used to provide details on device characterization measurements and present the creation of a non-linear device model.

#### 2.2.1 Verification of Foundry PDK Models

Foundries often provide their device models in the context of a process development kit (PDK), which are developed for their specific semiconductor device fabrication process. An early version of a PDK for the NRC GaN150 process had been created for use in circuit design on that technology, and the kit included electrical models and layouts for standard passive and active components [35]. Prior to collecting any measurements, preliminary simulations were executed in ADS to provide insights on the operating conditions and expected behavior of the 2x100  $\mu$ m device pictured in Figure 11. The NRC GaN150 HEMT nonlinear model was derived at V<sub>DS</sub> = 20 V and V<sub>GS</sub> = -3 V, which was considered the nominal starting point for investigation.

Figure 11 - Photograph of the NRC GaN150 2x100µm device used for characterization and modeling

The first measurement configuration consisted of a VNA with 150  $\mu$ m pitch ground-signal-ground (GSG) probes, external bias tees, and 50  $\Omega$  coaxial cables. A short-open-load-thru (SOLT) calibration was completed to move the measurement plane to the probe tips. After the die was probed, a negative voltage of sufficient magnitude to put the device into a non-conductive region of operation was applied to the gate. Next, a small positive voltage was applied to the drain, and the current was monitored to ensure that a short circuit was not present. The drain voltage was then increased to the nominal starting point of 20 V, and the gate voltage was gradually increased until the channel began to conduct (as indicated by an increase in drain current). S-parameter measurements were then collected from 0.5-26.5 GHz for a swept range of gate voltages. The measurement setup was then recalibrated with on-wafer thru-line-reflect (TRL) standards, which moved the measurement plane to the gate and drain terminals of the device. This TRL calibration removed the effects of the probe pads and feed lines from the results, producing the most accurate measurement of device performance. The biasing procedure described above was

then repeated, and another set of S-parameter measurements were collected from 0.5-26.5 GHz for a swept range of gate voltages.

As expected, the measured data showed good agreement with the simulation results at a bias of  $V_{DS} = 20$  V,  $V_{GS} = -3$  V. Accurate results had been anticipated because the  $V_{DS} = 20$  V,  $V_{GS} = -3$  V bias condition had been specified as the nominal operating point for the NRC model. However, the model accuracy was impacted at other bias points, and the effects of interconnection parasitics were not fully captured in the model. As will be discussed in Section 4.1, the design goal with this GaN technology was to achieve wideband PA performance up to 18 GHz at a higher drain voltage. Therefore, this 2x100 µm transistor was chosen to undergo a more complete set of characterization measurements with the intention of using the collected data to generate a new electrical model for the device.

# 2.2.2 Device Characterization Measurements

A complete on-wafer characterization of a microwave transistor involves DC-IV, small-signal, large-signal, and noise parameter measurements over a range of operating temperatures [36]. Because this device will be used in a PA design at a specific bias point and tested at room temperature, a selected subset of the complete characterization measurements produced sufficient data to construct an accurate electrical model for use under these operating conditions. Specifically, noise figure was not measured, and the remaining measurements were collected at room temperature only.

Using the TRL calibration method and biasing sequence described above, the S-parameters of the 2x100  $\mu$ m device were measured at CW from 0.5-26.5 GHz, over a swept DC bias of V<sub>GS</sub> = -5 V : 0.1 V : -2 V and V<sub>DS</sub> = 0 V : 1 V : 40 V. The DC-IV and small-signal measurement sequence was then repeated for pulsed bias duty cycles of 50% and 5% (100  $\mu$ s period), from multiple quiescent bias conditions, with V<sub>GS</sub> = -5 V : 0.1 V : -1 V and V<sub>DS</sub> = 0 V : 1 V : 50 V. Finally, large-signal data were collected using the vector-receiver load-pull configuration described in Section 2.1.3. The measurement results were used to extract optimal P<sub>OUT</sub> and PAE contours at 6, 12, and 18 GHz for a range of Class-AB bias points to complete the device characterization.

### 2.3 Modeling

Since the existing transistor model was optimized for a different bias point, the data collected during characterization measurements were used to extract a new transistor model for operation with a 28 V drain supply [37]. While there are many different modeling techniques, the three most common types in use today are physical, behavioral, and compact. Physical models are based on the underlying physics of the specific device technology. While they are valid over the largest operating range, physical models use complex equations which require longer simulation time, so this type of model is more suited for the transistor itself and not the full microwave circuit. Behavioral models are based on the measured responses of a component to a controlled input signal. Although development is easier for any component type (on-wafer, packaged, etc.), behavioral models are only applicable for the measured operating conditions, so this type of model

has reduced flexibility. Compact models are based on measurements of DC-IV and S-parameters which are then used to converge a formula-based transistor model with a reduced set of circuit parameters. The valid operating range of a compact model is somewhat reduced when compared with a physical model, and the modeling process is more involved when compared with a behavioral model (particularly for a packaged device). However, a compact model requires relatively straightforward measurements, needs less simulation time, and captures complex phenomena over a useful range of operating conditions. The compact model is an excellent choice when developing a model of a microwave transistor die for use in circuit design, so this technique was selected to create the electrical model for the NRC GaN150 2x100 µm device.

# 2.3.1 Nonlinear Device Model Creation

To extract the compact model, pulsed S-parameter and quasi-isothermal pulsed DC-IV data were collected for an on-wafer sample of the NRC GaN150  $2x100 \,\mu m$  transistor. Load-pull measurements at 6, 12, and 18 GHz were also performed on the same device for model validation. Measurement system control and compact model extraction were accomplished with IVCAD software from Maury Microwave.

After the device measurements in Section 2.2.2 were completed, the modeling process began with the extraction of a linear model. The extrinsic parasitic elements  $R_g$ ,  $L_g$ ,  $C_{pg}$ ,  $R_d$ ,  $L_d$ ,  $C_{pd}$ ,  $R_s$ , and  $L_s$ , as defined in the compact model schematic in Figure 12, were determined by parameter optimization using the collected S-parameter data [38]. These extrinsic parameter values were selected such that the values of the intrinsic parameters  $C_{gs}$ ,  $C_{gd}$ ,  $G_m$ ,  $G_d$ ,  $C_{ds}$ ,  $R_i$ ,  $T_{au}$ , and  $R_{gd}$  were constant with respect to frequency.

During this procedure, the measured and modeled S-parameters were constantly compared to ensure agreement over the bandwidth of interest.

Figure 12 - Schematic of the compact transistor model used for the NRC GaN150 2x100 µm device

The modeling process was continued by using both continuous and pulsed DC-IV data to extract a nonlinear model. These measurements were required to determine the thermal impedance of the device, which enabled the compact model to predict the response of the device as a function of self-heating and baseplate temperature. The duty cycle of the pulsed measurements was configured to minimize the mean variation of device temperature, and the pulse width was configured to avoid temperature variations for the duration of the pulse.

To complete the modeling process, one-dimensional nonlinear capacitance models for  $C_{gd}$  and  $C_{gs}$  were extracted from the pulsed DC-IV and pulsed S-parameter

measurements. The value of  $C_{gd}$  heavily depends on the drain voltage, while the value of  $C_{gs}$  heavily depends on the gate voltage along the same RF load line [38]. Since  $C_{ds}$  exhibits only a weak voltage dependence in amplifier designs, it is treated as a linear element. Finally, the extracted compact model was simulated in ADS and compared with the measured data. The small-signal plots in Figure 13 and large signal load-pull contours in Figure 14 were used to validate the new model for design use.

Figure 13 - Measured and modeled S-parameters comparing (a) S11 and S22, and (b) max gain and stability factor for a NRC GaN150  $2x100 \mu m$  device at  $V_{DS} = 28 V$

Figure 14 - Nonlinear model simulation and large signal measurement comparison for a 2x100  $\mu$ m device at V<sub>DS</sub> = 28 V, P<sub>IN</sub> = 22 dBm, and *f* = 18 GHz

Load-pull results are provided at 18 GHz, the highest frequency at which the impedance tuners could function. The comparison plots show highly-correlated measurement and simulation results, indicating the efficacy of the newly extracted model. With the concepts and methods of large signal device characterization and modeling introduced, it is now possible to begin a power amplifier design. In the upcoming chapter, the manufacturer's device models will be applied in the development of several hybrid PA circuits. Then, in Chapter 4, the new model extracted above for the NRC GaN150 2x100 µm device will be used in the design of an MMIC PA.

# **CHAPTER 3:**

# HYBRID MICROWAVE GAN POWER AMPLIFIERS

By using large signal models from discrete device manufacturers, we can now focus on achieving cutting-edge performance from commercial power transistors in hybrid PAs. For a typical hybrid PA implementation, passive microwave circuits are fabricated on planar dielectric substrates, and active microwave components – in this case, GaN HEMTs – are bonded onto this passive structure. Hybrid PAs can enable faster design cycles, shorter production cycles, lower costs (for small quantities), and more flexible integration.

The first design presented in this chapter used multiple discrete GaN transistors with power-combining networks implemented on a low-loss substrate to achieve maximum efficiency and high output power at X band. The findings of this design were published in IEEE's International Conference on Microwaves, Communications, Antennas and Electronic Systems [39].

#### 3.1 Hybrid Power Combining of Commercial Power Transistors

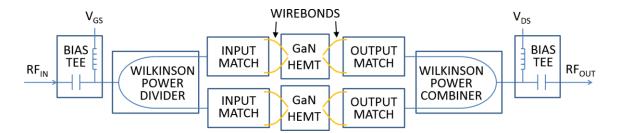

This hybrid configuration contained two commercially available TGF2023-01 GaN HEMT dies in parallel. The multi-die topology helped manage thermal constraints while increasing the total output power [22] by expanding the total circuit area and doubling the effective HEMT periphery, respectively. An overview of the PA architecture in Figure 15 shows the interconnections of the Wilkinson combiners, input matching networks, output matching networks, GaN devices, and wirebonds.

Figure 15 - Block diagram of hybrid multi-die PA architecture

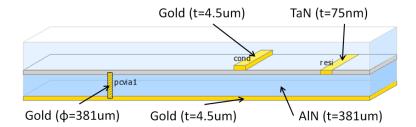

Several characteristics of ideal microwave circuit substrates [40] – such as low dielectric loss and high dielectric strength – are particularly desirable for PAs, and a high thermal conductivity is essential to achieving good system efficiency in a high-power design [41]. With its thermal conductivity of 170 W/m·K, AlN can more quickly sink the excess heat generated by PA circuitry than many other substrate materials [42]. Given its excellent physical properties [42], 15 mil AlN was chosen as the substrate with 4.5  $\mu$ m Au as the conductor for the power divider network designs, as shown in Figure 16.

Figure 16 - Material stack-up for EM simulation of the power divider networks

#### 3.1.1 Low-loss Wilkinson Power Dividers

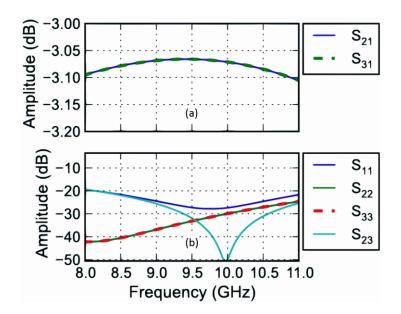

To divide and recombine the power for the two dies, an equal-split Wilkinson divider [43] was designed and optimized in ADS. Thin-film TaN was used for the isolation resistors, and the final EM-simulated design had less than 0.1 dB insertion loss, over 20 dB isolation, and over 20 dB return loss as shown in Figure 17.

Figure 17 - EM-simulated (a) insertion loss and (b) isolation and return loss for the equal-split Wilkinson power divider design

# 3.1.2 Matching Network Design

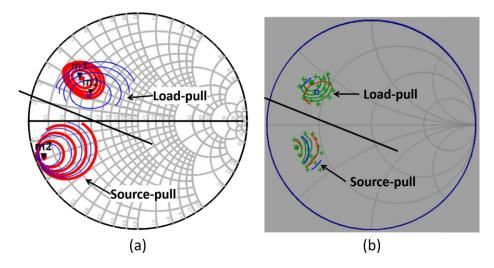

To maximize output power and PAE, the 50  $\Omega$  impedance of the Wilkinson dividers must be transformed to present optimal large-signal impedances to the TGF2023-01 power transistor. Iterative load-pull and source-pull simulations were performed in ADS to determine the optimal impedances, and the passive power-sensor based load-pull configuration described in Section 2.1.2 was used to measure the TGF2023-01. The simulated optimal impedance values were then compared with measured data in Table 1. All simulations and measurements presented in Table 1 were performed at I<sub>DS</sub> = 70 mA and V<sub>DS</sub> = 28 V, with optimal impedance extractions at 10 GHz for a source power of 24 dBm at the GaN die.

Good agreement was observed for the optimal load impedances, as indicated by the load values in Table 1 and the load-pull contours in Figure 18. Because the impedance

tuning range of the measurement system was limited, the measured optimal source resistance seemed somewhat different than the simulated result. Since the tuner and fixture losses prevented the realization of any impedance with a  $|\Gamma| > 0.8$  at 10 GHz, source-pull measurements could not be collected for source impedances near the edge of the Smith Chart. Although measurements taken at the edge of the Smith Chart are desirable, they are not required to verify the model in this case. The simulated contours in Figure 18(a) are very similar in shape and size to the measured contours in Figure 18(b), and the maximum  $P_{OUT}$  and PAE of the device are also in good agreement after correcting for the limited source impedance tuning range. Taken together, these data confirm the model's validity for use in circuit design.

| Parameter              | Simulated               | Measured         |  |

|------------------------|-------------------------|------------------|--|

| ZSOURCE, OPTIMAL       | 2.3 - j9.5 Ω            | 7.48 - j7.37 Ω   |  |

| ZLOAD, OPTIMAL (POUT)  | $15.6 + j11.0 \ \Omega$ | 13.47 + j12.79 Ω |  |

| ZLOAD, OPTIMAL (PAE)   | 11.64 + j15.8 Ω         | 10.04 + j15.41 Ω |  |

| POUT, MAXIMUM          | 36.5 dBm                | 34.75 dBm        |  |

| PAE <sub>MAXIMUM</sub> | 62%                     | 52%              |  |

Table 1 - Simulated and measured optimal large-signal impedances and device performance of the TGF2023-01 die at 10 GHz

Figure 18 - (a) Simulated and (b) measured load-pull and source-pull contours for Pout and PAE

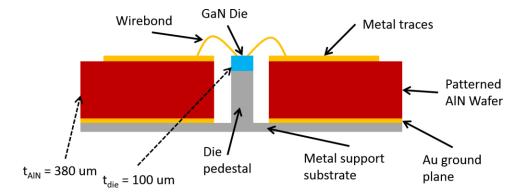

With these optimal impedances determined, the input and output matching networks were designed on the AlN substrate using double radial stubs and microstrip transmission lines. In HMICs, parasitics from interconnections (e.g., wirebonds, via holes) often limit the achievable performance. Circuit optimizations showed that a specific wirebond length at the gate would enable a better large-signal impedance match. However, the minimum realizable wirebond length was constrained by the height difference between the AlN substrate and GaN dies. Therefore, the metal carrier in Figure 19 was designed to include an integrated pedestal upon which the GaN dies would be mounted. The pedestal's dimensions were cut so that the bondpads of the mounted die would align in the z-direction with the patterned metal layer of the mounted matching networks. This carrier helped to reduce the minimum realizable wirebond length and provided an excellent heat sink for the dissipated power from the dies.

Figure 19 - Diagram of hybrid PA module assembly using metal carrier with integrated die pedestal

After optimization of the schematic level design, EM simulations were executed in Momentum on the full network layouts. These layouts were tuned until the EM simulation results were close to the schematic simulation results, at which time the mask was finalized and submitted for thin-film fabrication. After the completed wafers were diced, the microwave structures were ready for assembly into a hybrid X band PA.

## 3.1.3 Assembly and Measurements

The first step in PA assembly was affixing the GaN dies to the carrier. An 80% Au 20% Sn eutectic preform was used to attach the dies to the Au-plated pedestal on the metal carrier. Although this method of die attach required high heat, it provided the transistor with the lowest possible thermal resistance. Next, the input and output matching networks were affixed to the carrier with silver epoxy, providing a good thermal pathway to ground. Because silver epoxy is viscous until cured, choosing this material enabled precise alignment of the matching networks with the die bondpads in both x- and y-dimensions.

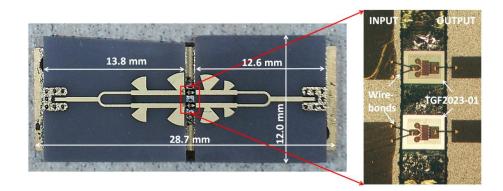

Lastly, 1-mil gold wires were wedge-bonded from the dies to the networks as shown in Figure 20 to complete assembly.

Figure 20 - Photograph of the fabricated and assembled PA with inset showing gold wirebonds

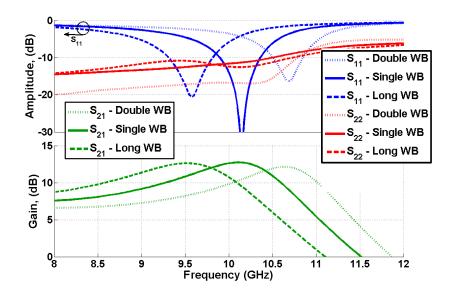

The fabricated and assembled circuit seen in Figure 20 was probed, biased, and tested for small-signal and large-signal performance. Plots of the small-signal reflection coefficients and linear gain for a -10 dBm input signal are found in Figure 21, which also shows traces for three different wirebond configurations for the input matching network to gate interconnection – double, single, and long. Initial PA measurements indicated an upwards frequency shift which was due to mechanical positioning limitations. The assembled circuit had the matching networks physically closer to the dies, which decreased the length (and, therefore, inductance) of the wirebonds. Since the desired large-signal performance can be partially targeted by tracking the small-signal input match, the frequency response was tuned with different configurations of IMN-to-gate wirebonds to achieve a peak output power of 38.1 dBm at 9.5 GHz.

Figure 21 - Simulated and measured small-signal results

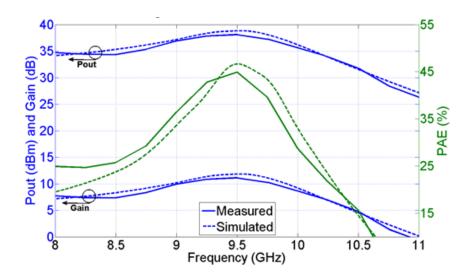

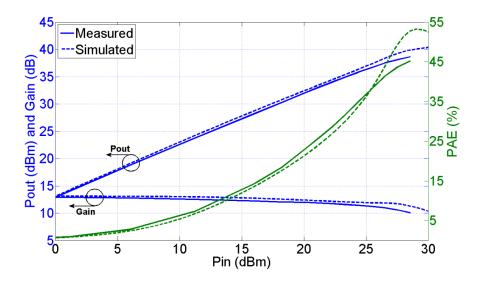

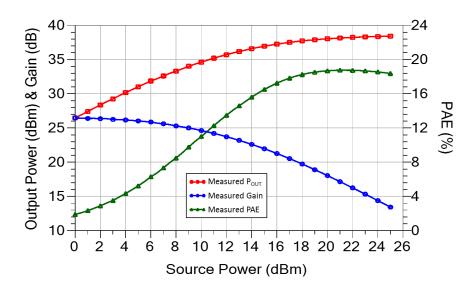

The large-signal measurements at 27 dBm source power are compared with simulations in Figure 22. The source power was then swept (up to the available maximum) at the peak power frequency, and Figure 23 shows both the simulated and measured performance. This design effectively mitigated thermal effects with its parallel-die configuration, AlN substrate, and use of WPDs. Although thermal degradation can be difficult to capture in simulation, pulsed modes of operation (unavailable at the time of measurement) would help to identify and address any thermal limitations.

Figure 22 - Simulated and measured Pout, gain, and PAE vs. frequency results

Figure 23 - Simulated and measured Pout, gain, and PAE vs. PIN at 9.5 GHz