# DIGITAL COMMUNICATION AND CONTROL CIRCUITS FOR 60GHz FULLY INTEGRATED CMOS DIGITAL RADIO

A Thesis Presented to The Academic Faculty

by

Gopal B. Iyer

In Partial Fulfillment

of Requirements for the Degree

Master of Science in

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2010

COPYRIGHT © 2010 BY GOPAL B. IYER

# DIGITAL COMMUNICATION AND CONTROL CIRCUITS FOR 60GHz FULLY INTEGRATED CMOS DIGITAL RADIO

## Approved by:

Dr. Joy Laskar, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Saibal Mukhopadhyay

School of Electrical and Computer Engineering

Georgia Institute of Technology

Dr. Manos Tentzeris

School of Electrical and Computer Engineering

Georgia Institute of Technology

Date Approved: 2<sup>nd</sup> April 2010

I dedicate all my research work and the culmination, this thesis:

to my Mom, Dad,

my sisters, Sheela and Sheetal

my brother-in-law, Vinayak,

and to the apple of my eye, my nephew, Vivek ©

# **ACKNOWLEDGEMENTS**

I would like to thank my advisor Dr. Joy Laskar for his inspiring leadership and guidance throughout the course of my research project. I would also like to express my gratitude to Dr. Saibal Mukhopadhyay and Dr. Manos Tentzeris for taking the time and serving on my reading committee.

I wish to acknowledge Dr Stephane Pinel and Dr. Bevin Perumana for providing excellent technical guidance in helping me complete my research work. In particular I would like to thank Dr. Bevin Perumana, for mentoring me in the art of Mixed Signal Design. I wish to thank Dr. Padmanava Sen and Dr. Saikat Sarkar for their constant support and valuable friendship.

I take this opportunity to thank all the team members of the Millimeter-Wave Applications Group, who have been a part of this Digital Radio Transceiver project. I thank Chan-Kim and Jin-Keyong Kim from ETRI, Korea, for their help during the design of PHY and MAC modules. I would like to thank Ashwin Muppalla, Jacob Leemaster, Matthew Leung and David Yeh for their support during the SPI testing. I thank my colleagues and seniors from Tata Honeywell and LSI Logic, who have mentored me during my stay there. I thank all my friends for sharing my special moments and making this journey exciting. I specially thank Saumya Venkatram for sharing this journey with me and being a constant support.

None of this would have ever been possible without the unwavering support and blessing of my parents, sister and brother-in-law, the grace of my Maharaj, Shri Brahmachaitanya Maharaj Gondavlekar and Lord Sri Rama and Shri Hanuman.

# **Table of Contents**

| A | CKN          | OWLEDGEMENTS                                               | 4  |

|---|--------------|------------------------------------------------------------|----|

| L | IST (        | OF TABLES                                                  | 7  |

| L | IST (        | OF FIGURES                                                 | 8  |

| L | IST (        | OF SYMBOLS AND ABBREVIATIONS                               | 13 |

| S | U <b>M</b> M | IARY                                                       | 15 |

| 1 | IN           | TRODUCTION                                                 | 17 |

|   | 1.1          | Motivation                                                 | 17 |

|   | 1.2          | Choice of 60GHz for the Digital Radio                      | 20 |

|   | 1.3          | Digital Control and backend                                | 22 |

|   | 1.4          | Organization of Thesis                                     | 23 |

| 2 | PF           | HYSICAL DESIGN FLOW FOR ASIC IMPLEMENTATION                | 24 |

|   | 2.1          | Design Entry                                               | 26 |

|   | 2.2          | Logic Synthesis                                            | 26 |

|   | 2.3          | Logical Verification:                                      | 27 |

|   | 2.4          | Static Timing Analysis                                     | 29 |

|   | 2.5          | Physical Design                                            | 32 |

| 3 | SE           | ERIAL COMMUNICATION INTERFACES                             | 50 |

|   | 3.1          | JTAG                                                       | 50 |

|   | 3.2          | SPI                                                        | 53 |

|   | 3.3          | $I^2C$                                                     | 56 |

|   | 3.4          | Choice of SPI as the chosen serial communication interface | 60 |

| 4 | TI           | HE SPI SUB-SYSTEM FOR CMOS DIGITAL RADIO CUM MODEM         | 61 |

|   | 4.1          | Block Description                                          | 61 |

|   | 4.2          | Version 1 of the SPI sub-system                            | 64 |

|   | 4.2          | 2.1 Overview                                               | 64 |

|   | 4.2          | 2.2 Modes of Operation                                     | 64 |

|   | 4.2          | 2.3 Cell Naming Convention                                 | 65 |

|   | 4.2          | 2.4 Typical SPI sub-system address space                   | 66 |

|   | 4.2          | 2.5 Top Level SPI System                                   | 67 |

|   | 4.2          | 2.6 SPI Core Design (for spic6w16s0r8)                     | 68 |

|   | 4.2          | 2.7 SPI Junction Circuitry                                 | 69 |

|   | 4.2          | 2.8 SPI Layout                                             | 70 |

|   | 4.2          | 2.9 Read Operation                                         | 70 |

|          | 4.2.10                                                             | Typical RF Radio Initialization sequence                                                                                                                                                                                                                             | 71          |

|----------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|          | 4.3 Ne                                                             | w Upgraded V2 SPI Sub-System                                                                                                                                                                                                                                         | 73          |

|          | 4.3.1                                                              | Motivation for the upgrade                                                                                                                                                                                                                                           | 73          |

|          | 4.3.2                                                              | Block description                                                                                                                                                                                                                                                    | 75          |

|          | 4.3.3                                                              | Simplistic Timing Diagram                                                                                                                                                                                                                                            | 76          |

|          | 4.3.4                                                              | Control Word Format                                                                                                                                                                                                                                                  | 77          |

|          | 4.3.5                                                              | Common Mode                                                                                                                                                                                                                                                          | 78          |

|          | 4.3.6                                                              | Software Reset                                                                                                                                                                                                                                                       | 82          |

|          | 4.3.7                                                              | Detailed Timing Diagrams                                                                                                                                                                                                                                             | 84          |

|          | 4.3.8                                                              | Physical Layout                                                                                                                                                                                                                                                      | 89          |

|          | 4.3.9                                                              | MAC-RF Adapter and SPI Bypass                                                                                                                                                                                                                                        | 92          |

|          | 4.3.10                                                             | An in-depth look at the Common Mode                                                                                                                                                                                                                                  | 95          |

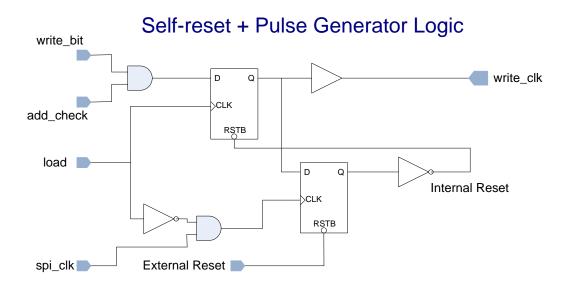

|          | 4.3.11                                                             | Sub-circuits                                                                                                                                                                                                                                                         | 96          |

|          |                                                                    |                                                                                                                                                                                                                                                                      |             |

| 5        | SPI TE                                                             | EST AND MEASUREMENT SETUP                                                                                                                                                                                                                                            | 98          |

| <b>5</b> |                                                                    | EST AND MEASUREMENT SETUPA HIGH SPEED DIGITAL I/O DESIGN                                                                                                                                                                                                             |             |

|          | ULTR                                                               |                                                                                                                                                                                                                                                                      | 104         |

|          | ULTR.                                                              | A HIGH SPEED DIGITAL I/O DESIGN                                                                                                                                                                                                                                      | <b> 104</b> |

|          | ULTR. 6.1 ST 6.2 Cla                                               | A HIGH SPEED DIGITAL I/O DESIGN                                                                                                                                                                                                                                      |             |

|          | ULTR. 6.1 ST 6.2 Cla 6.3 I/O                                       | A HIGH SPEED DIGITAL I/O DESIGN                                                                                                                                                                                                                                      |             |

|          | ULTR. 6.1 ST 6.2 Cla 6.3 I/O                                       | A HIGH SPEED DIGITAL I/O DESIGN                                                                                                                                                                                                                                      |             |

|          | ULTR. 6.1 ST 6.2 Cla 6.3 I/O 6.4 Ele                               | A HIGH SPEED DIGITAL I/O DESIGN                                                                                                                                                                                                                                      |             |

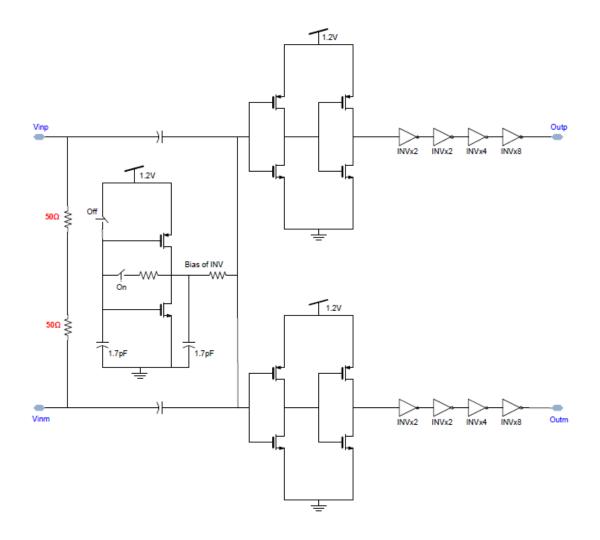

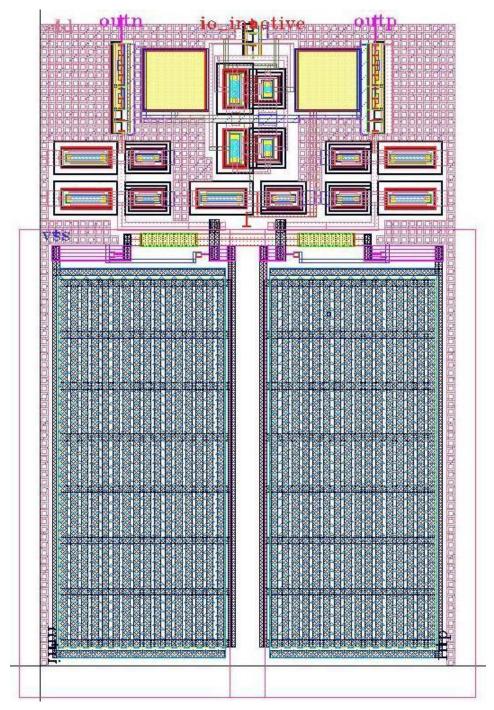

|          | ULTR. 6.1 ST 6.2 Cla 6.3 I/O 6.4 Ele 6.4.2                         | A HIGH SPEED DIGITAL I/O DESIGN  90nm Standard Digital IO Evaluation  assification of I/O cells  Performance Evaluation  ectro-Static Discharge  SLVS Output Buffer                                                                                                  |             |

|          | ULTR. 6.1 ST 6.2 Cla 6.3 I/O 6.4 Ele 6.4.2 6.4.3                   | A HIGH SPEED DIGITAL I/O DESIGN  90nm Standard Digital IO Evaluation  assification of I/O cells  Performance Evaluation  ectro-Static Discharge  SLVS Output Buffer  SLVS Input Buffer                                                                               |             |

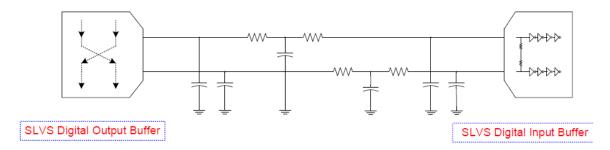

|          | ULTR. 6.1 ST 6.2 Cla 6.3 I/O 6.4 Ele 6.4.2 6.4.3 6.4.4             | A HIGH SPEED DIGITAL I/O DESIGN  90nm Standard Digital IO Evaluation  selfication of I/O cells  Performance Evaluation  ectro-Static Discharge  SLVS Output Buffer  SLVS Input Buffer  SLVS Input-Output Buffers back-to-back Simulation Results                     |             |

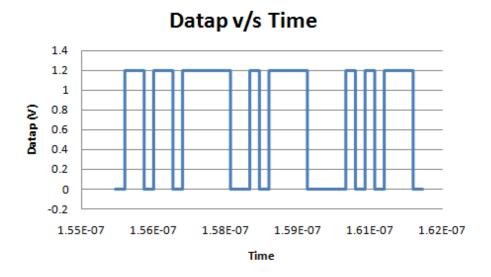

|          | ULTR. 6.1 ST 6.2 Cla 6.3 I/O 6.4 Ele 6.4.2 6.4.3 6.4.4 6.4.5 6.4.6 | A HIGH SPEED DIGITAL I/O DESIGN  90nm Standard Digital IO Evaluation  sessification of I/O cells  Performance Evaluation  ectro-Static Discharge  SLVS Output Buffer  SLVS Input Buffer  SLVS Input-Output Buffers back-to-back Simulation Results  Measured Results |             |

# **LIST OF TABLES**

| Table 1: Clock Tree Specification File                                | 39  |

|-----------------------------------------------------------------------|-----|

| Table 2: Overview of SPI, I2C and JTAG Serial Communication Protocols | 60  |

| Table 3: Pin Description for SPI Slave                                | 62  |

| Table 4: SPI Subsystem Address Space                                  | 66  |

| Table 5: Common Mode Control Word                                     | 79  |

| Table 6: Mode Selection Table                                         | 80  |

| Table 7: Channel Change Table [3]                                     | 81  |

| Table 8: Output buffer voltage swings (into 50ohms)                   | 122 |

| Table 9: SLVS Output Buffer Performance Summary                       | 125 |

| Table 10: SLVS Output Buffer Component List                           | 126 |

| Table 11: SLVS Input Buffer Performance Summary                       | 131 |

| Table 12: SLVS Input Buffer Component List                            | 131 |

# **LIST OF FIGURES**

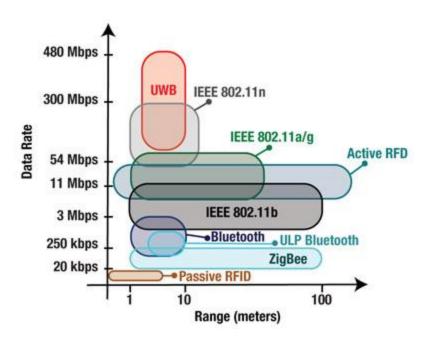

| Figure 1: Comparison of various communication standards                             | 18        |

|-------------------------------------------------------------------------------------|-----------|

| Figure 2: Wireless standards spectrum                                               | 18        |

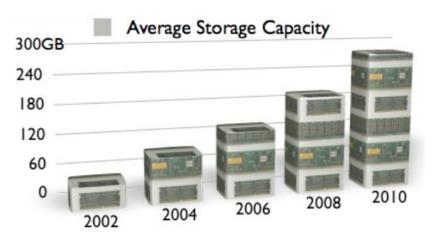

| Figure 3: Average storage capacity of hard disks                                    | 19        |

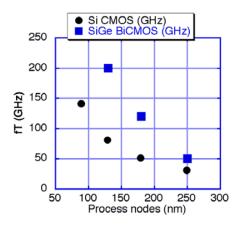

| Figure 4: Transit frequencies for SiGe and CMOS at various technology nodes         | 20        |

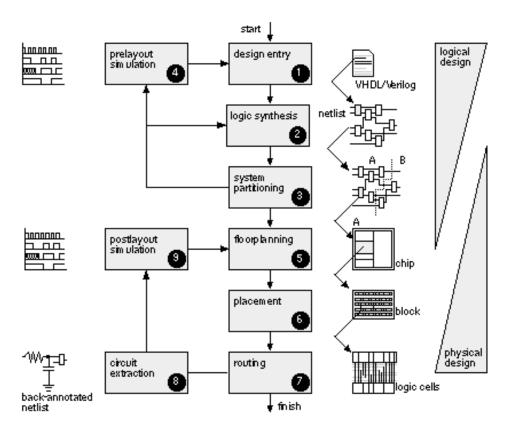

| Figure 5: Designing SoC - From Logic design to Physical design                      | 24        |

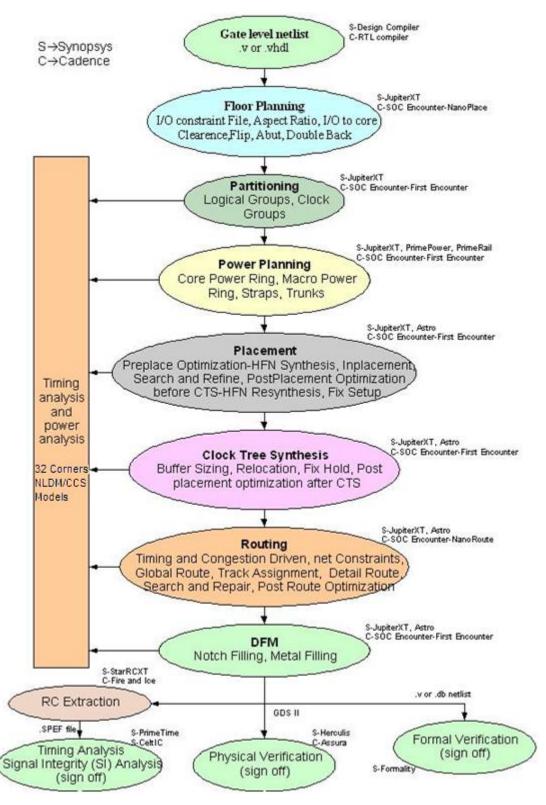

| Figure 6: System-On-Chip Design Flow                                                | 25        |

| Figure 7: ModelSim Workspace                                                        | 27        |

| Figure 8: ModelSim Schematic                                                        | 28        |

| Figure 9: ModelSim Waveform                                                         | 28        |

| Figure 10: DC Shell Execution                                                       | 31        |

| Figure 11: Design netlist read into SoC Encounter                                   | 33        |

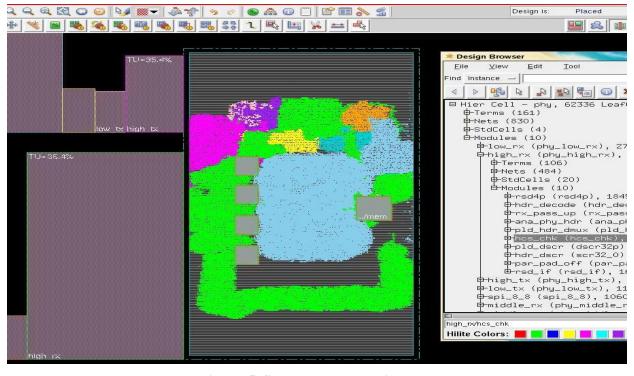

| Figure 12: SoC Encounter Views for Floorplan (Macro Placement)                      | 35        |

| Figure 13: Placing memories with power termination rings                            | 36        |

| Figure 14: Power ring and stripe                                                    | 37        |

| Figure 15: Standard cell groups in colors                                           | 37        |

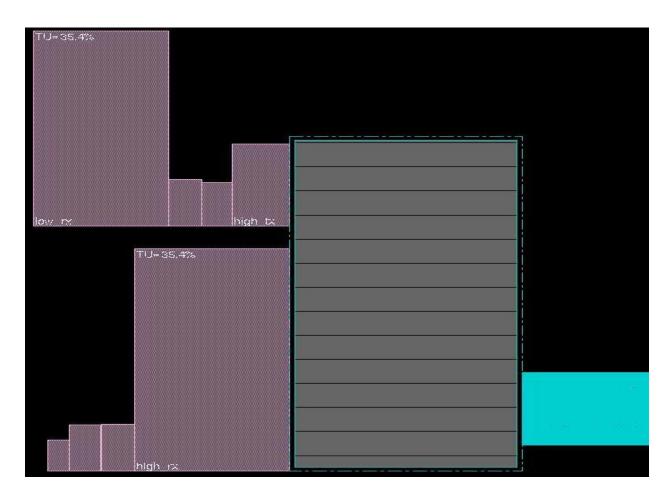

| Figure 16: Congestion map and tracks used                                           | 42        |

| Figure 17: Showing congestion                                                       | 42        |

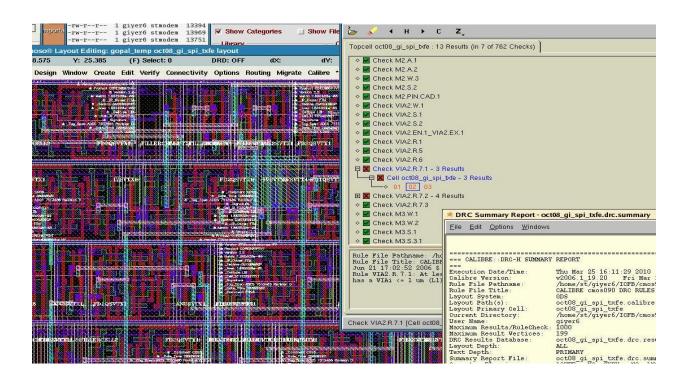

| Figure 18: SoC Encounter – DRC                                                      | 44        |

| Figure 19: Calibre DRC                                                              | 45        |

| Figure 20: Calibre LVS                                                              | 46        |

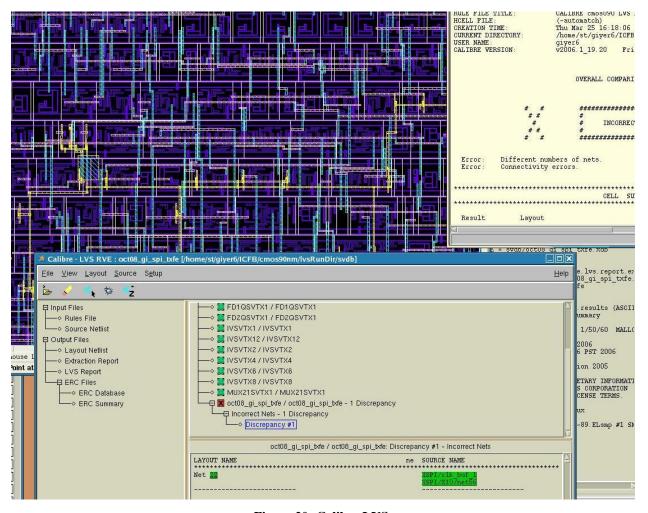

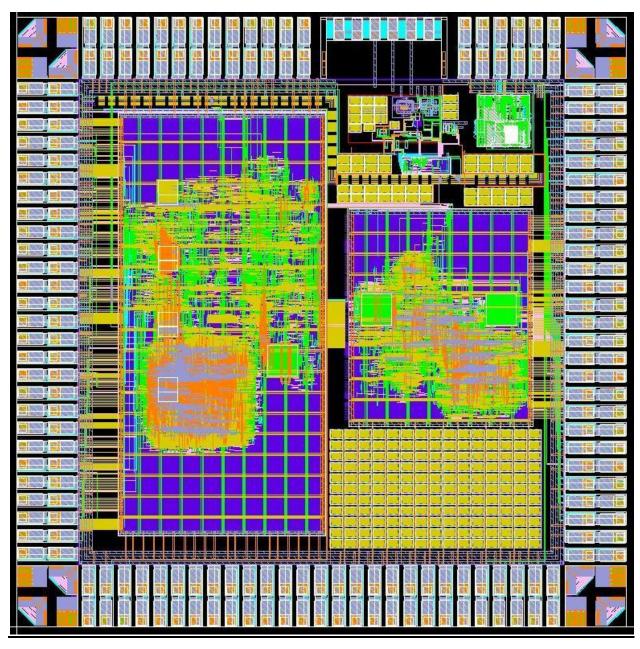

| Figure 21: Design Completion                                                        | 49        |

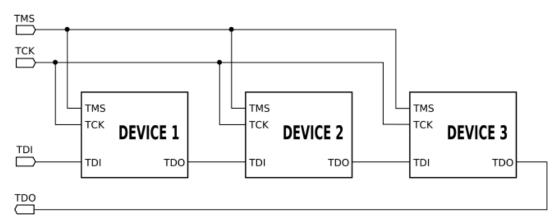

| Figure 22: JTAG Interface                                                           | 51        |

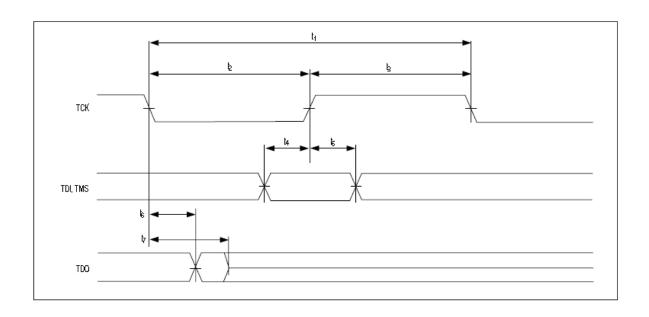

| Figure 23: JTAG Timing Diagram                                                      | 52        |

| Figure 24: Timing numbers for DS4550 [37]                                           | 52        |

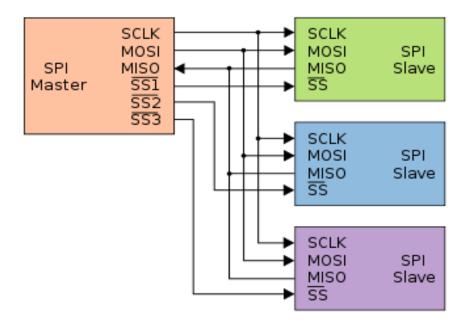

| Figure 25: SPI Subsystem depicting Master-Slave Configuration with individual slave | select 54 |

| Figure 26: SPI Subsystem in Daisy-Chain Format                                      | 54        |

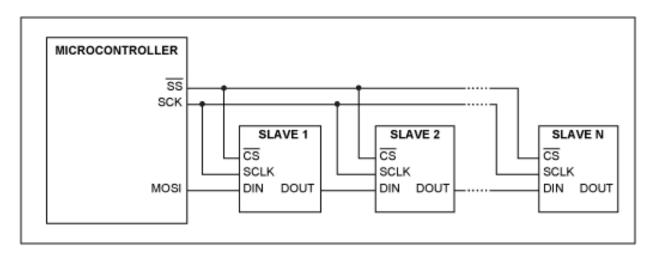

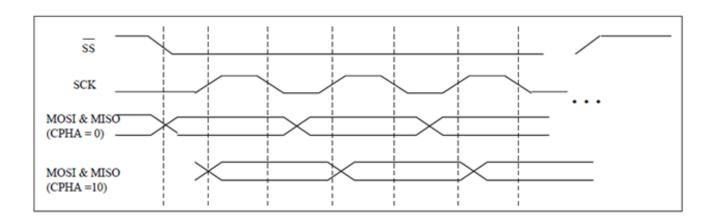

| Figure 27: SPI sample timing diagram                                                | 55        |

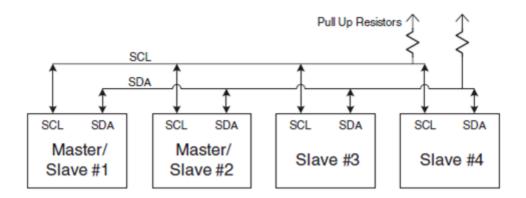

| Figure 28: Typical I2C Bus System                                                   | 57        |

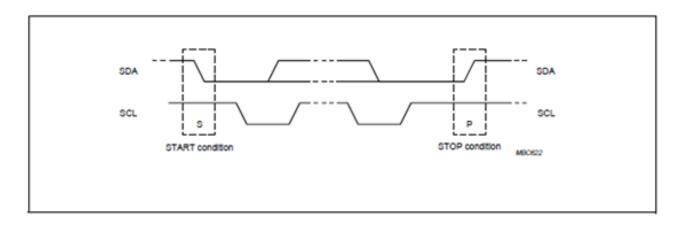

| Figure 29: START and STOP Conditions                                                | 58        |

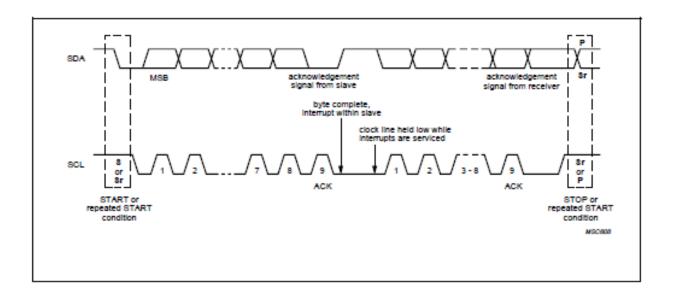

| Figure 30: Data Transfer on I2C Bus                                              | 58 |

|----------------------------------------------------------------------------------|----|

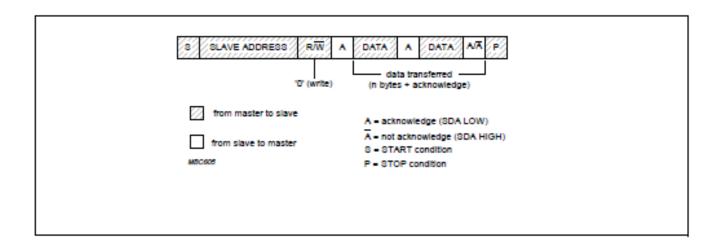

| Figure 31: A master-transmitter addressing a slave receiver with a 7-bit address | 59 |

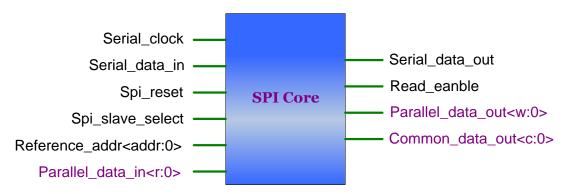

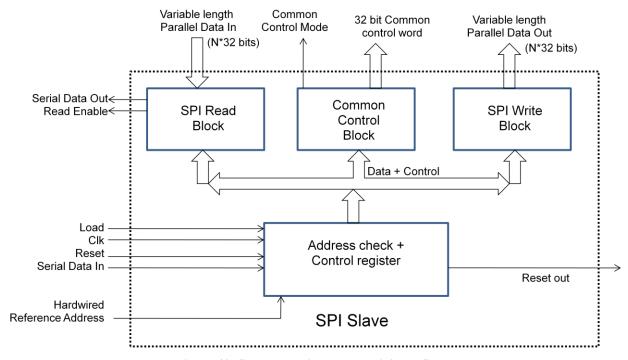

| Figure 33: Typical SPI Slave                                                     | 61 |

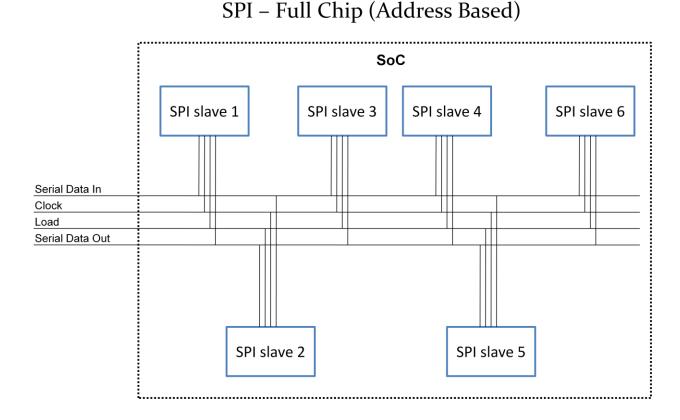

| Figure 34: Typical SPI Subsystem with Multiple slaves                            | 63 |

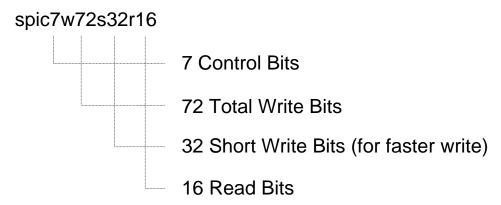

| Figure 35: SPI slave naming convention                                           | 65 |

| Figure 36: Top Level SPI System                                                  | 67 |

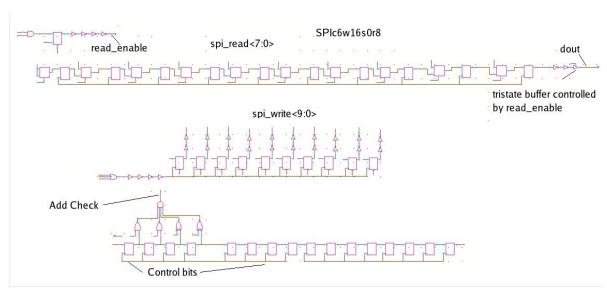

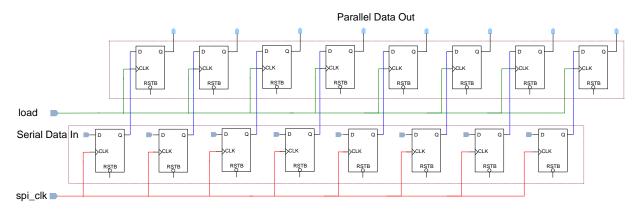

| Figure 38: Two level of registers clocked by spi_clk and load                    | 68 |

| Figure 37: SPI Core Design                                                       | 68 |

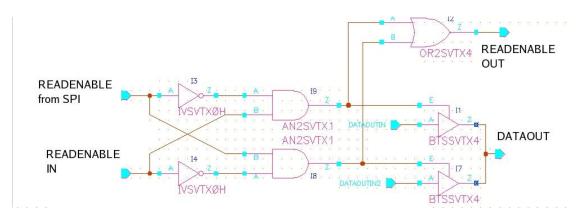

| Figure 39: SPI Junction Circuitry                                                | 69 |

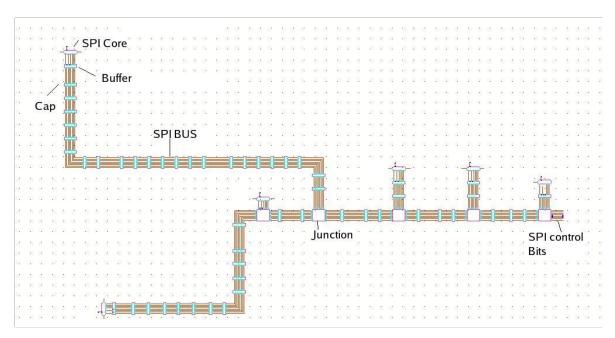

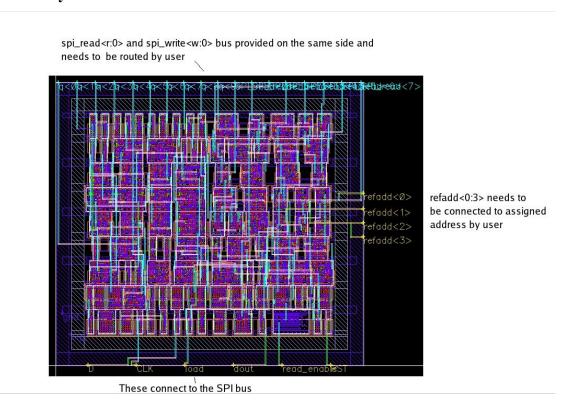

| Figure 40: SPI Layout                                                            | 70 |

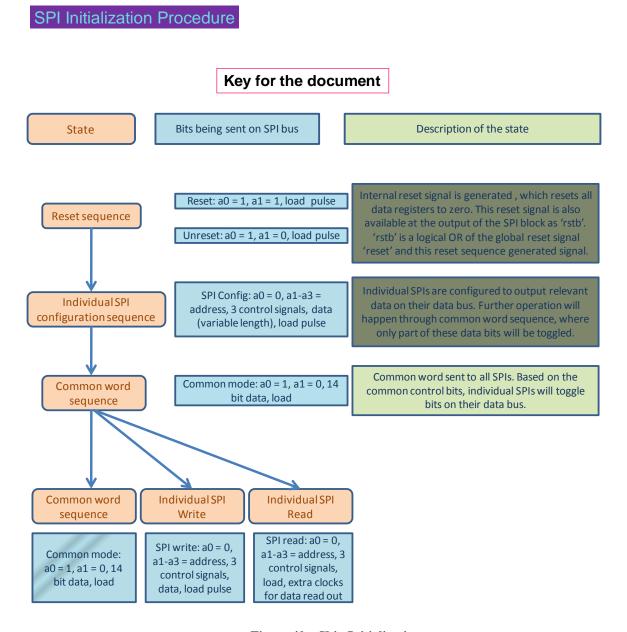

| Figure 41: Chip Initialization                                                   | 71 |

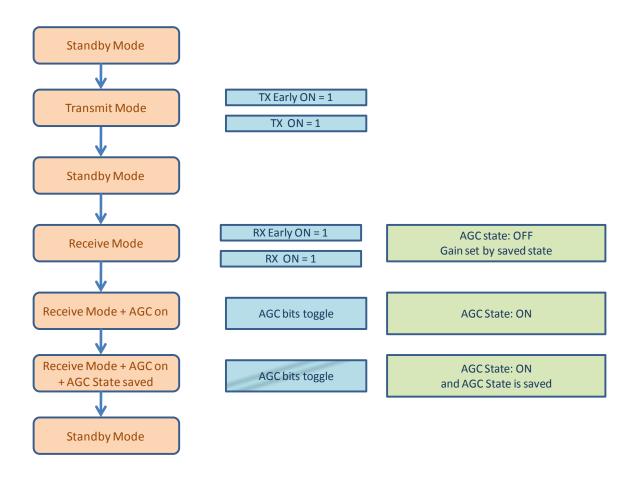

| Figure 42: Time Domain Duplexing Operation                                       | 72 |

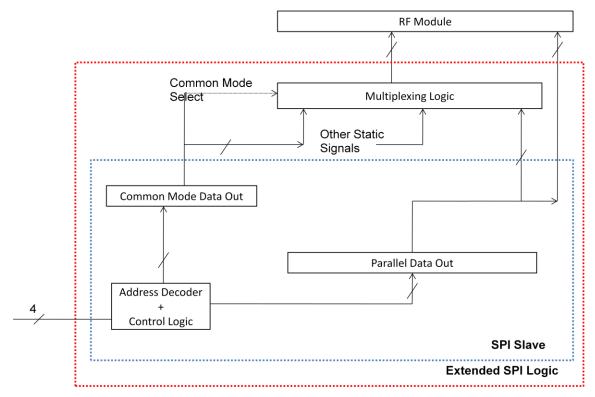

| Figure 43: SPI Block Diagram - Individual Slave                                  | 75 |

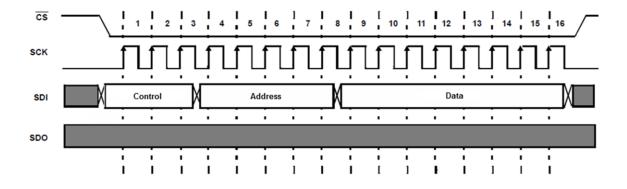

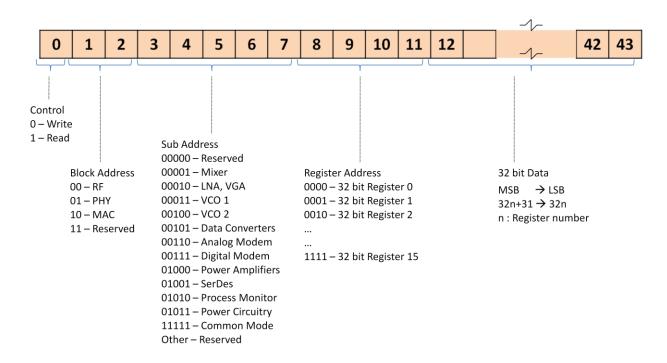

| Figure 44: SPI Timing Diagram (Version 2 implementation)                         | 77 |

| Figure 45: SPI Timing Diagram - Control Word                                     | 78 |

| Figure 46: SPI Slave - Common Mode Operation                                     | 82 |

| Figure 47: SPI Slave - Common Mode Reset                                         | 83 |

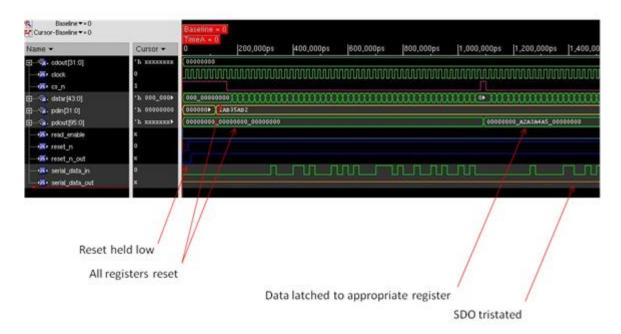

| Figure 48: SPI Parallel Write                                                    | 84 |

| Figure 49: SPI Write Operation - Excess Clocks (Redundant Data)                  | 85 |

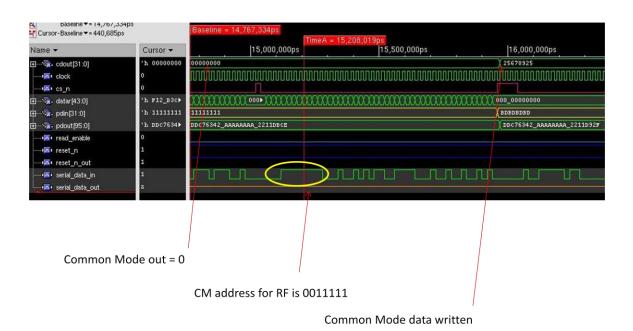

| Figure 50: SPI Common Write Sequence                                             | 86 |

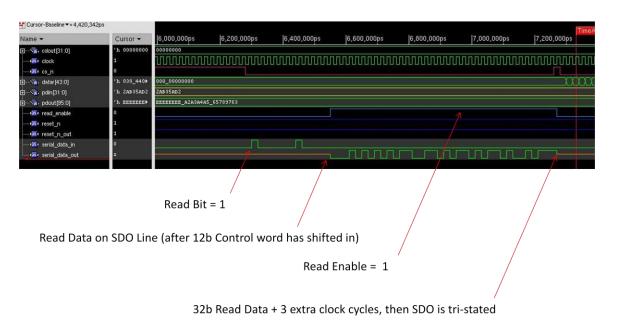

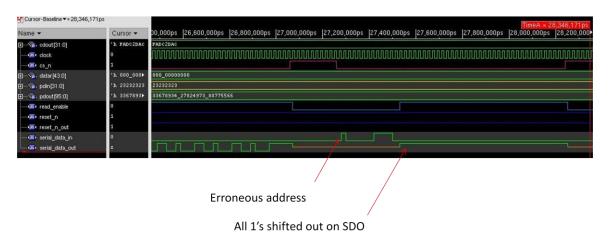

| Figure 51: SPI Slave - Read Sequence                                             | 87 |

| Figure 52: SPI Slave - Read Sequence with Wrong Register Address                 | 88 |

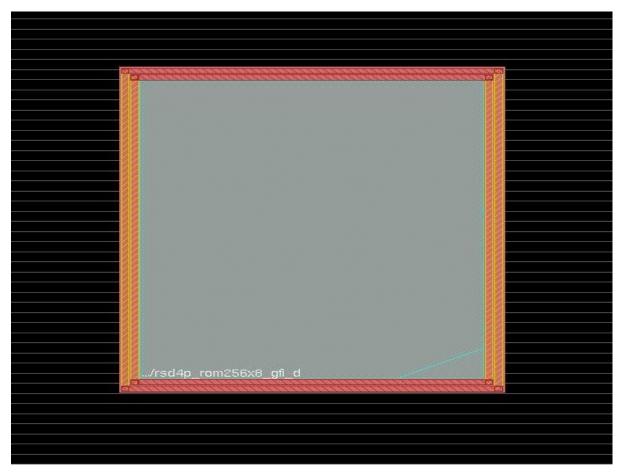

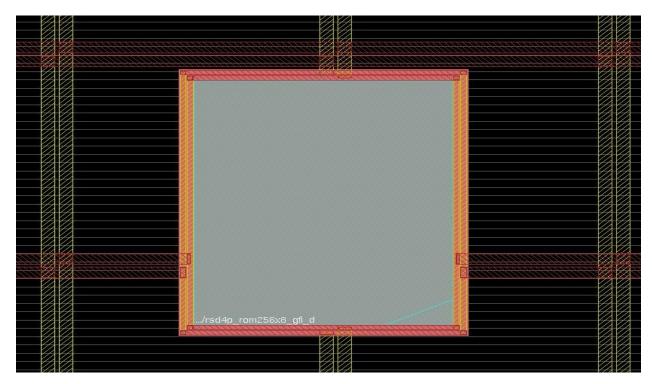

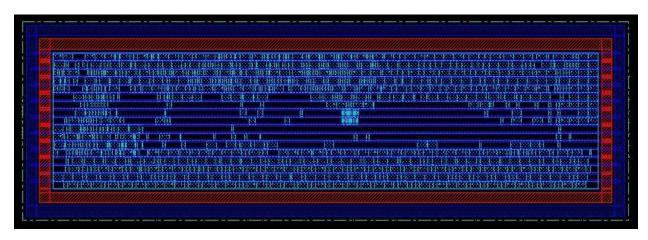

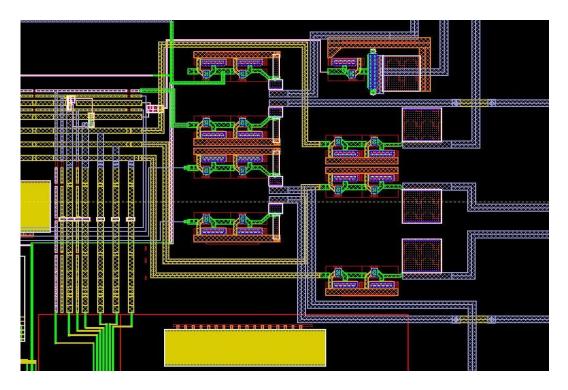

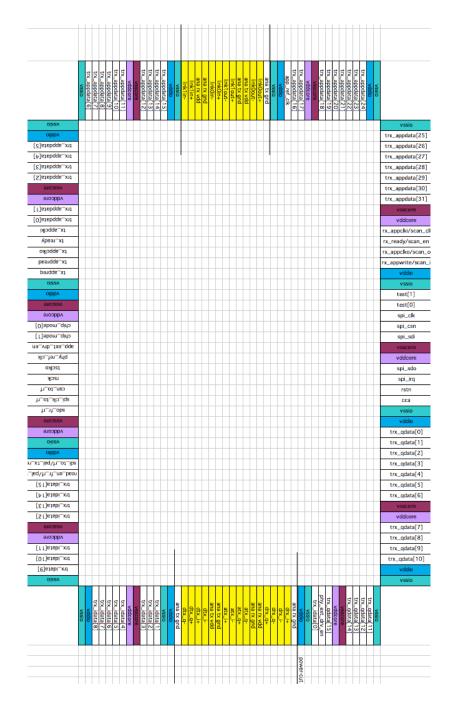

| Figure 53: Physical Design of SPI Slave - Placement Stage                        | 89 |

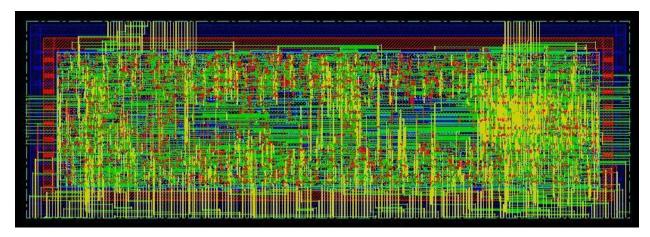

| Figure 54: Completed Physical Design of SPI Slave                                | 89 |

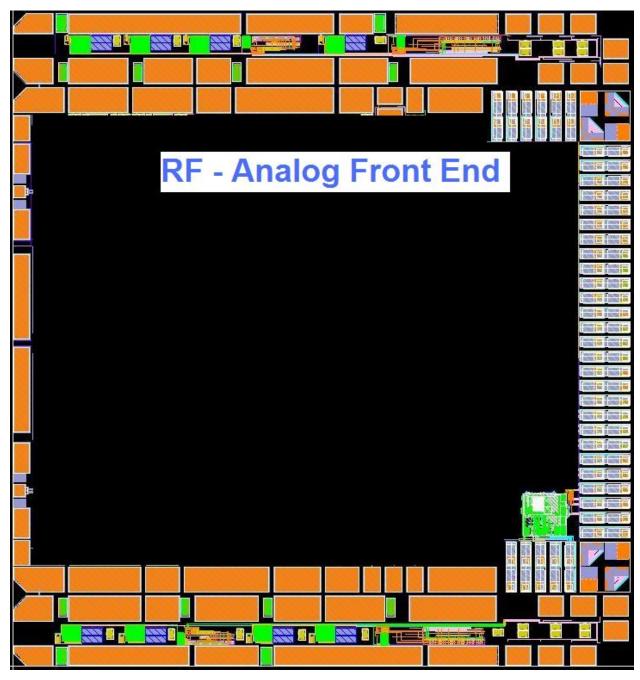

| Figure 55: SPI Integrated with an RF Module (VCO)                                | 90 |

| Figure 56: SPI Bus arbiter Junction                                              | 90 |

| Figure 57: SPI Bus                                                               | 91 |

| Figure 58: SPI I/O circuit and pad interface                                     | 91 |

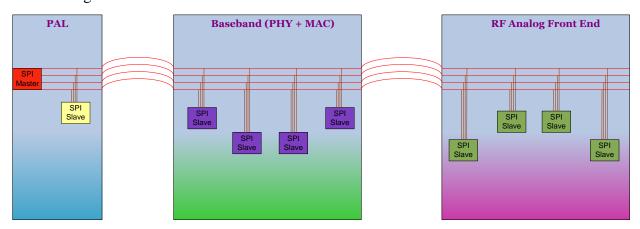

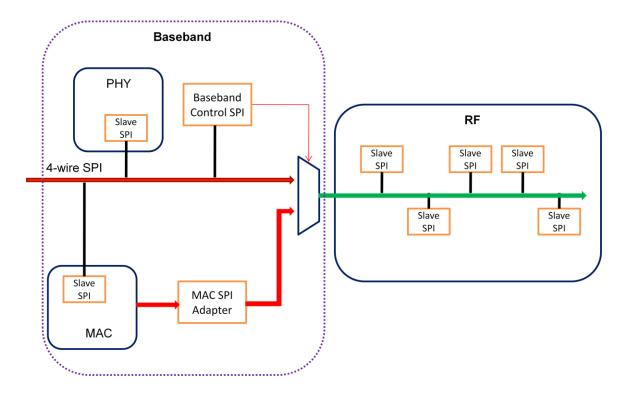

| Figure 59: Common SPI Bus on PAL -> Baseband (PHY/MAC) -> RF AFE interface       | 92 |

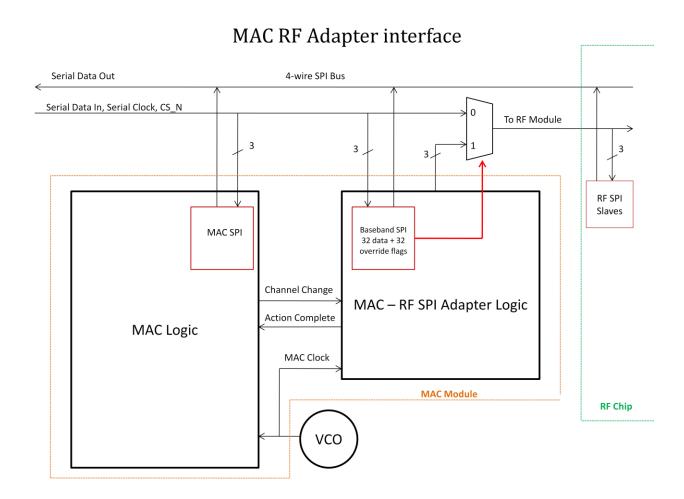

| Figure 60: SPI sub-system inside MAC                                             | 93 |

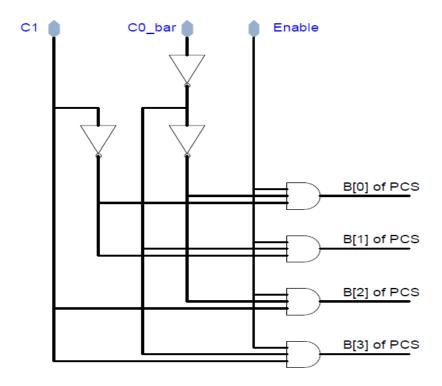

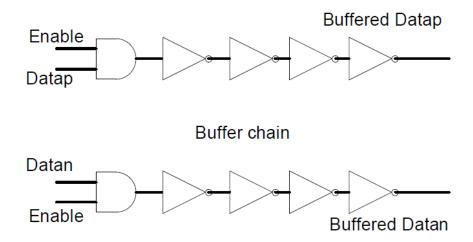

| Figure 61: SPI Bypass Logic                                                      | 94 |

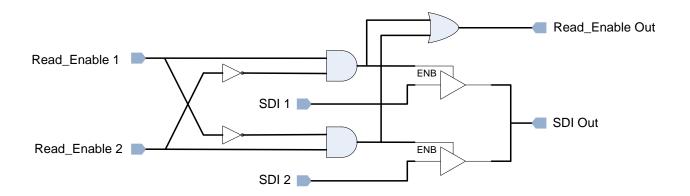

| Figure 62: Bus Arbitration Logic on SPI Read Path                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Figure 63: Self-Reset and Pulse Generator Logic developed for the first version of SPI                                                                                                                                                                                                                                                                                                                                                                                                                          | slave 97          |

| Figure 64: GP-22050 from Byte Paradigm used as the Embedded Protocol Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                   | 98                |

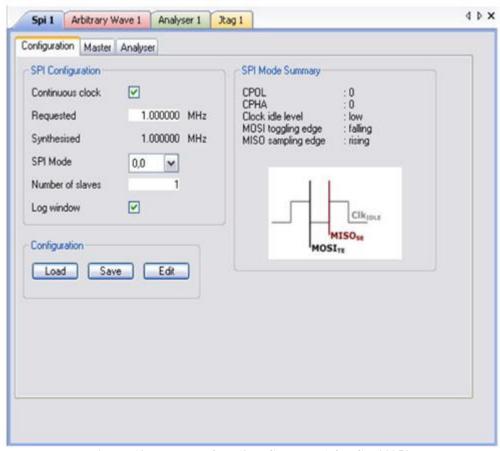

| Figure 65: User Interface (8PI-Controller) for GP-22050                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99                |

| Figure 66: CY3684 Development Board from Cypress Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100               |

| Figure 67: Graphical User Interface in Matlab for Cypress ADB                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 101               |

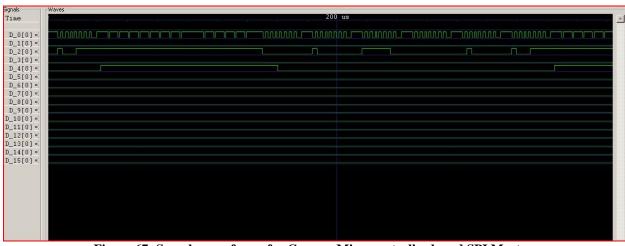

| Figure 68: Sample waveforms for Cypress Microcontroller based SPI Master                                                                                                                                                                                                                                                                                                                                                                                                                                        | 101               |

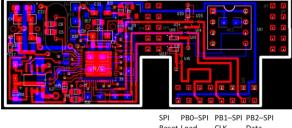

| Figure 69: Mini-board for self contained RF CMOS Digital Radio evaluation kit                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102               |

| Figure 70: Working demo for mini-USB based solution                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 103               |

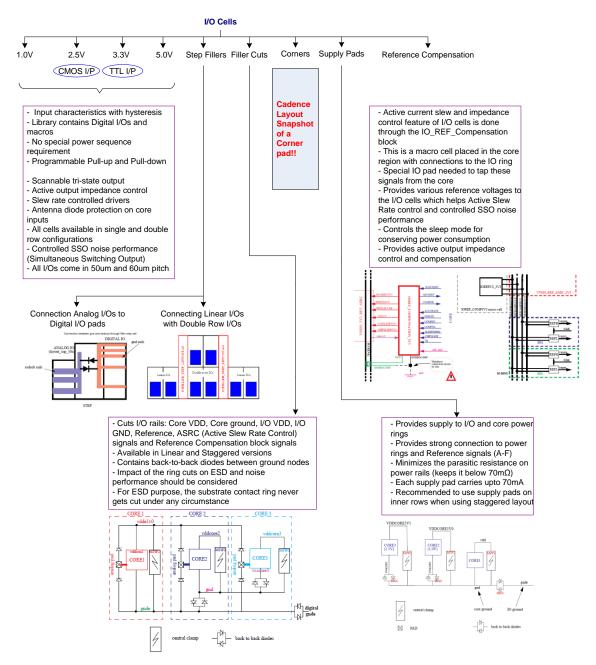

| Figure 71: Classification of IO Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 105               |

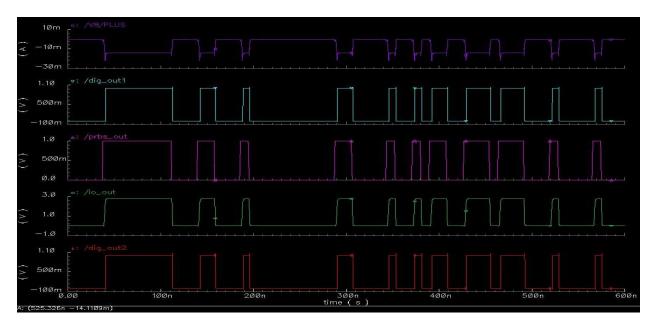

| Figure 74: Simulation results for Max loading (200ohms//1pF). The first waveform sho                                                                                                                                                                                                                                                                                                                                                                                                                            | ws the            |

| current consumption in two IOs = +/- 14.5mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 106               |

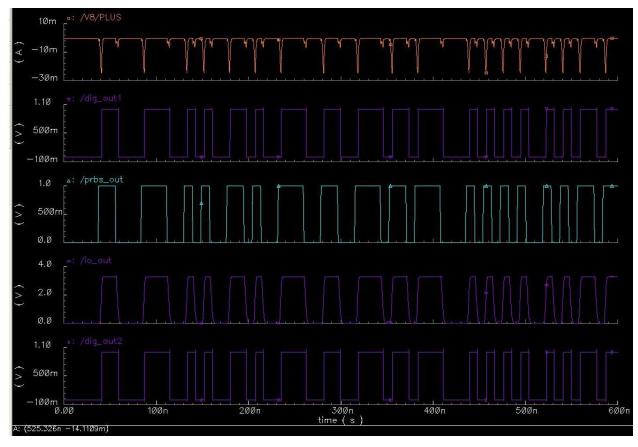

| Figure 75: Simulation results when one Bidi cell is driving another Bidi cell (10pf wire                                                                                                                                                                                                                                                                                                                                                                                                                        | load). 107        |

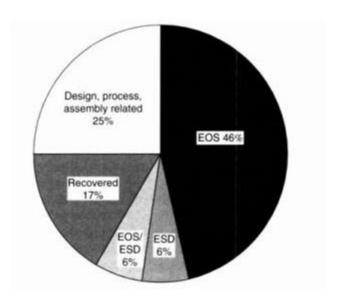

| Figure 76: Distribution of failure models in Silicon ICs. ESD accounts for approximate                                                                                                                                                                                                                                                                                                                                                                                                                          | ly 10%            |

| with EOS responsible for close to 5% of the failures. [47]                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 108               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

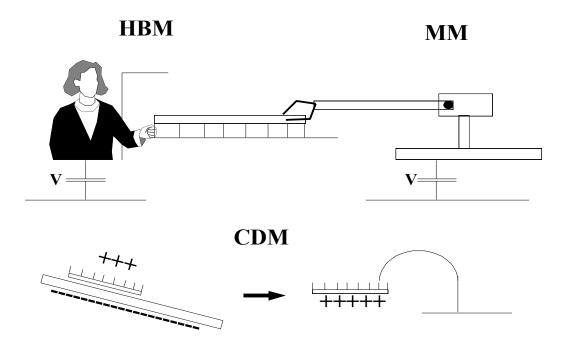

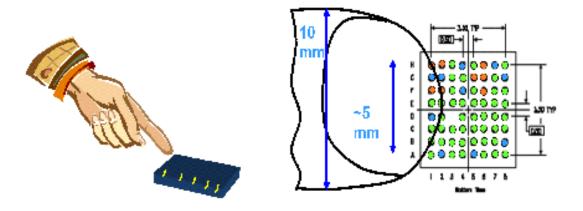

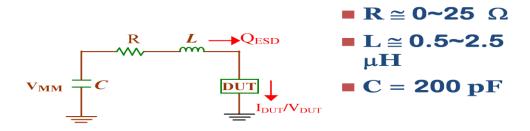

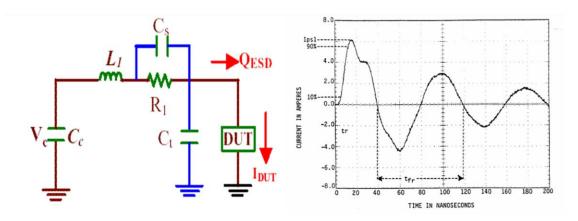

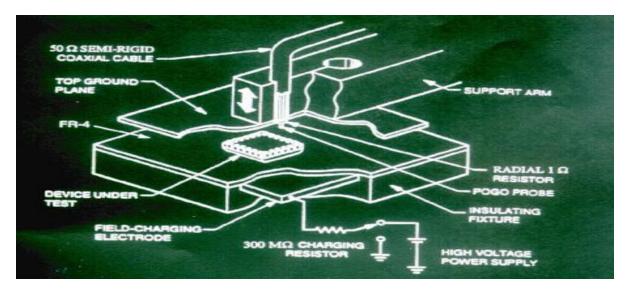

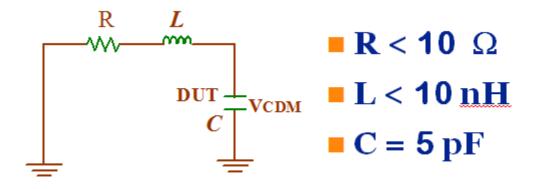

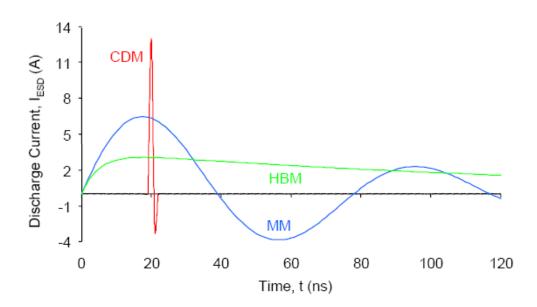

| Figure 77: Three dominant ESD mechanisms, namely the Human Body Model, Machin                                                                                                                                                                                                                                                                                                                                                                                                                                   | ne Model          |

| and Charge Device Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 109               |

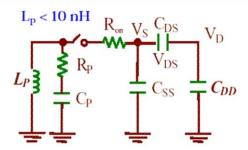

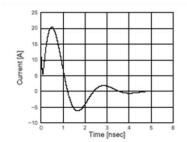

| and Charge Device Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 109<br>110        |

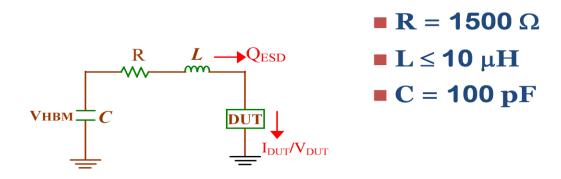

| and Charge Device Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 109<br>110<br>110 |

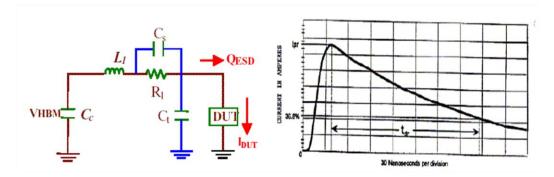

| and Charge Device Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| and Charge Device Model  Figure 78: ESD Failure - Human handling the chip [56]  Figure 79: Simplified HMB Equivalent Circuit [56]  Figure 80: HBM Test circuit [56]  Figure 81: Machine Model Equivalent Circuit [56]  Figure 82: Machine Mode Test Circuit [56]  Figure 83: Field induced CDM Simulator [56]  Figure 84: CDM Simplified Circuit Model [56]  Figure 85: CDM Test Circuit [56]  Figure 86: ESD Stress Waveform Comparison [56]                                                                   |                   |

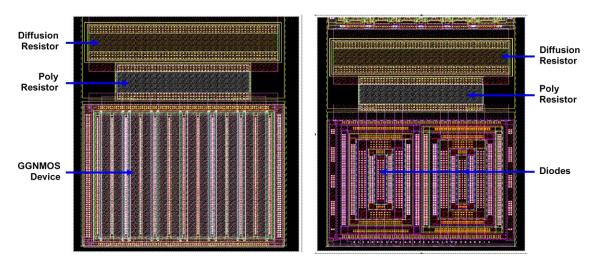

| and Charge Device Model  Figure 78: ESD Failure - Human handling the chip [56]  Figure 79: Simplified HMB Equivalent Circuit [56]  Figure 80: HBM Test circuit [56]  Figure 81: Machine Model Equivalent Circuit [56]  Figure 82: Machine Mode Test Circuit [56]  Figure 83: Field induced CDM Simulator [56]  Figure 84: CDM Simplified Circuit Model [56]  Figure 85: CDM Test Circuit [56]  Figure 86: ESD Stress Waveform Comparison [56]  Figure 87: Some standard structures for ESD protection [54] [55] |                   |

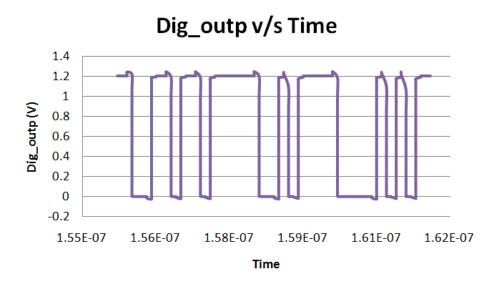

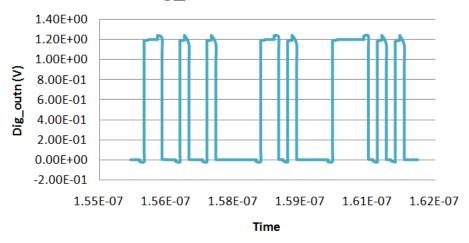

| Figure 114: Digital output of SLVS Digital Input buffer                                       | . 136    |

|-----------------------------------------------------------------------------------------------|----------|

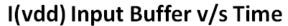

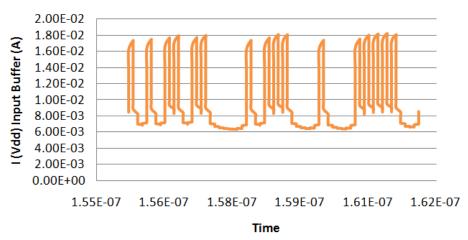

| Figure 115: Power supply current drawn into SLVS Digital Input buffer                         | . 136    |

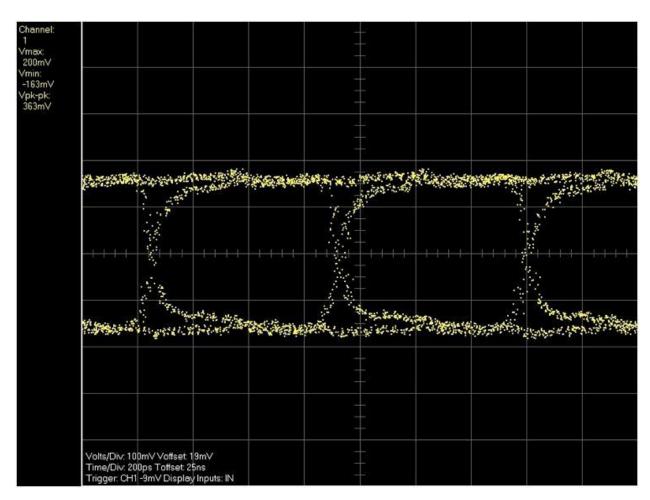

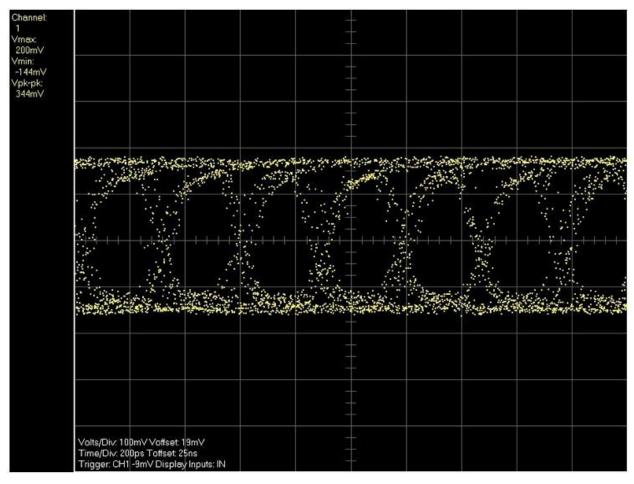

| Figure 116: 1.728 Gbps eye Diagram                                                            | . 137    |

| Figure 117: 3.456 Gbps eye Diagram                                                            | . 138    |

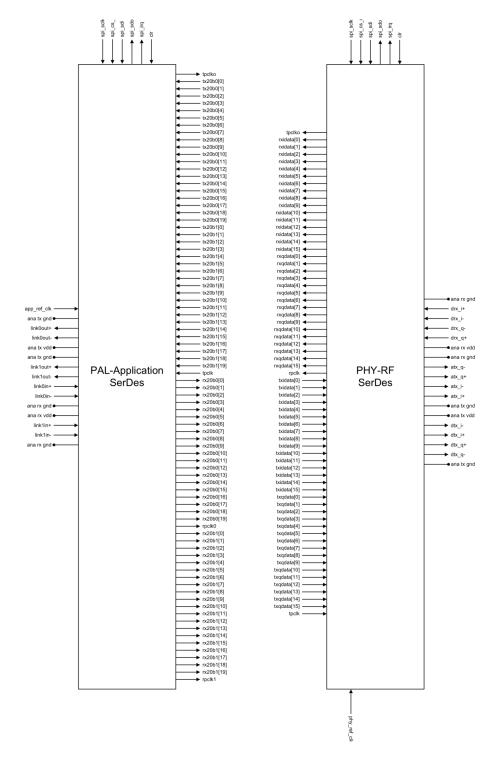

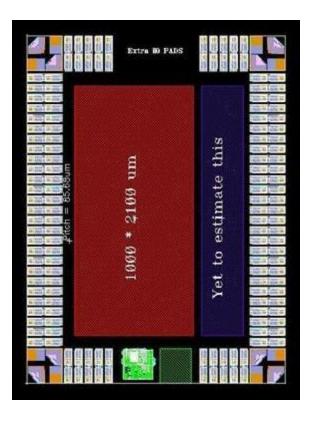

| Figure 118: Multi-chip solution developed for the RF CMOS Radio (version-1)                   | . 139    |

| Figure 119: Pin locations for the Application-PAL interface block and the PHY-RF interface    | <u>,</u> |

| block                                                                                         | . 140    |

| Figure 120: Full chip IO plan (Application on top & RF at bottom)                             | . 141    |

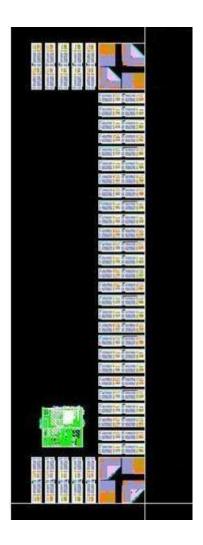

| Figure 121: Preliminary bonding diagram for the Parallel I/O section                          | . 142    |

| Figure 122: Preliminary bonding diagram for the Baseband Chip                                 | . 143    |

| Figure 123: I/O ring of the Parallel Interface Section seen to the right of the CMOS RF Radio | О        |

| Chip                                                                                          | . 144    |

| Figure 124: I/O Ring on the Baseband chip                                                     | . 145    |

| Figure 125: Die photograph of the Parallel I/O                                                | . 146    |

|                                                                                               |          |

# **LIST OF SYMBOLS AND ABBREVIATIONS**

| ABBREVIATION / | MEANING                                              |

|----------------|------------------------------------------------------|

| SYMBOL         | MEANING                                              |

| CMOS           | Complementary Metal Oxide Semiconductor              |

| RF             | Radio Frequency                                      |

| WLAN           | Wireless Local Area Network                          |

| WPAN           | Wireless Personal Area Network                       |

| MIMO           | Multiple Input Multiple Output                       |

| PHY            | Physical Layer of the Open System Interconnect Model |

| MAC            | Media Access Control                                 |

| ASIC           | Application Specific Integrated Circuit              |

| SoC            | System on Chip                                       |

| I/O            | Input – Output                                       |

| LVDS           | Low Voltage Differential Signaling                   |

| SLVS           | Scalable Low Voltage Signaling                       |

| ESD            | Electro-Static Discharge                             |

| HBM            | Human Body Model                                     |

| MM             | Machine Model                                        |

| CDM            | Charge Device Model                                  |

| RTL            | Register Transfer Logic                              |

| VHDL           | Very High Speed Integrated Circuit Hardware          |

| VIIDL          | Description Language                                 |

| TLU            | Table Look Up                                        |

| STA            | Static Timing Analysis                               |

| HFNS           | High Fanout Net Synthesis                            |

| CTS            | Clock Tree Synthesis                                 |

| SDC            | Synopsys Design Constraints                          |

| SDF            | Standard Delay Format                                |

| SI             | Signal Integrity                                     |

| ABBREVIATION / | MEANING                                               |

|----------------|-------------------------------------------------------|

| SYMBOL         | MEANING                                               |

| SPEF           | Standard Parasitic Exchange Format                    |

| DRC            | Design Rule Check                                     |

| LVS            | Layout versus Schematic                               |

| OCV            | On-Chip variation                                     |

| ECO            | Engineering Change Order                              |

| CMP            | Chemical Mechanical Planarization                     |

| SAR ADC        | Successive Approximation Register Analogue to Digital |

| STICTION       | Converter                                             |

| DAC            | Digital to Analogue Converter                         |

| AGC            | Automatic Gain Control                                |

| VGA            | Variable Gain Amplifier                               |

| VCO            | Voltage Controlled Oscillator                         |

| RFID           | Radio Frequency Identification                        |

| UWB            | Ultra Wide Band                                       |

| HDMI           | High Definition Multimedia Interface                  |

| PCI            | Peripheral Component Interconnect                     |

| MIPI           | Mobile Industry Processor Interface                   |

| GbE            | Gigabit Ethernet                                      |

| HBT            | Heterojunction Bipolar Transistor                     |

| PHMET          | Pseudomorphic High Electron Mobility Transistor       |

| CMOS           | Complementary Metal Oxide Semiconductor               |

| RF             | Radio Frequency                                       |

# **SUMMARY**

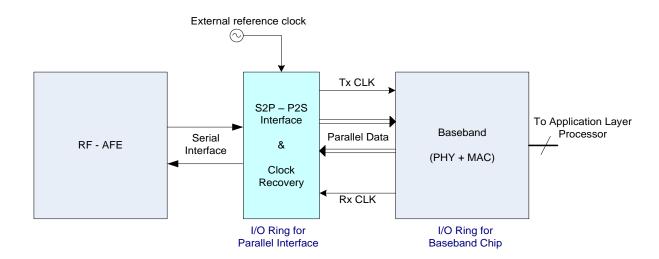

Emerging "bandwidth hungry" applications such as high definition video distribution and ultra fast multimedia side-loading have extended the need for multi-gigabit wireless solutions beyond the reach of conventional WLAN technology or even more recently emerging UWB and MIMO systems. The availability of 7GHz of unlicensed bandwidth in the 60GHz spectrum [1] represents a unique opportunity to address such data-throughput requirements. The 60GHz Integrated CMOS digital radio chipset comprises of PHY and MAC layers, RF transceiver, High-Speed Digital Interface and an underlying Serial Communication Fabric.

To have a complete communication solution compliant with the latest ECMA-369 [3], ISO/DIS 13156 and IEEE 802.15.3c standards [4], we build a digital implementation of MAC and PHY with over a million gates. The Serial Peripheral Interface (SPI) serves as the bridge between the higher layers in the communication stack (PAL-MAC) [5] [6] and the lower layers like PHY-RF Front End. The MAC module can setup the communication link on the fly by tuning parameters such as operating channel, channel bonding and bandwidth, data rates, error correction mechanisms, handshaking mechanisms, etc, by using the SPI to communicate with internal components. The SPI interface plays a crucial rule in not only this, but also during the testing and debug phase. Operation of each of the RF modules is monitored through the serial interface using local SPI slaves which are hooked up to the 4-wire serial bus running all through the chip. The SPI host controller emulates an embedded protocol analyzer. For calibration and fine tuning purposes, digital settings can also be loaded onto these modules through the SPI interface. R-2R DACs are used to convert these commands into analog voltages which then provide a tunable bias to the RF and mixed-signal modules. Other key functions of this serial communication and control interface are: Initialization of all of the RF and mixed signal modules, DC calibration of data converter [7], PLL and other mixed-signal modules [8], data acquisition, parametric tuning for digital modules such as linear equalizer, Gain Control loops (AGC, VGA) [9], etc.

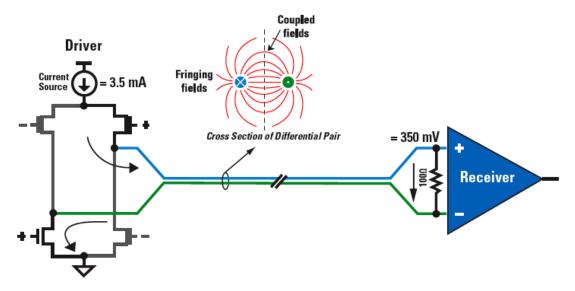

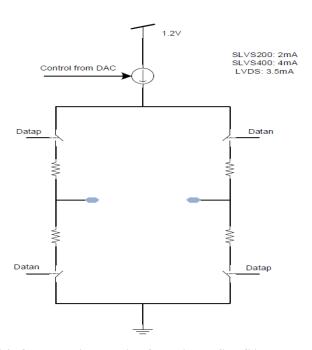

Ultra high speed digital Input-Output buffers are used to provide an external data interface to the radio chipset. These high speed I/Os are also used in the Gbps (gigabit-persecond) link for data transfer between the RF transceiver chip and the PHY-MAC baseband chip. The IOs are expected to comply with different signaling standards such as LVDS [10],

SLVS200, SLVS400 [11], etc. A robust system involves a meticulous pad ring design with proper power domains and power cuts. Full-chip integration of the digital PHY, MAC, peripheral logic and IO ring is done in a semi-custom fashion.

# 1 <u>INTRODUCTION</u>

#### 1.1 Motivation

Over the past decade, advances in wireless communication have significantly altered the networking and connectivity space. This transformation has been two-pronged. On one hand, advances in semiconductor manufacturing coupled with innovative design techniques have pushed forward the bandwidth envelope. On the other hand, the overcrowded electromagnetic spectrum compels us to develop newer data transmission and modulation techniques.

Recent advances in semiconductor technology have shrunk the CMOS devices from 180nm down to 32nm and 22nm. These developments have brought in a lot of positive changes like higher operating frequencies and much smaller silicon real estate (die areas). However, these advantages come with a flip side, namely, the static power consumption has increased manifold. Most recent trends indicate that there is growing emphasis to develop newer devices and innovative design techniques to minimize the power consumption. With active device  $f_T$ 's (unity current gain transit frequency) of over 100GHz, it is now possible to have Radio Frequency Front End circuitry (signal conditioning, filtering and amplification) along with digital baseband on the same silicon die. This technology improvement has created newer market segments with a variety of high bandwidth applications. This is the "technology driven" perspective.

Another perspective is the "user need" based. Figure 1 depicts a comparative study of various communication standards that were prevalent at the turn of the century. As seen, traditional mobile communication standards such as Global System for Mobile (GSM), Code Division Multiple Access (CDMA) and Wideband Code Division Multiple Access (WCDMA), have throughputs of a few megabits per second. The Ultra Wide Band (UWB) standard supports data rates of 1Gbps. All these are limited to transfer of voice, data and images. Streaming of video needs much higher bandwidths and only wired communication standards were capable of supporting it.

| Standard  | Frequency                                          | Data rate                            | Distance                                        |

|-----------|----------------------------------------------------|--------------------------------------|-------------------------------------------------|

| CDMA      | 824-849 MHz<br>869-894 MHz                         | Less than 1 Mbps                     | Greater than 1 mile                             |

| GSM       | 880-915 MHz<br>925-960 MHz                         | Less than 1 Mbps                     | Greater than 1 mile                             |

| GPS       | 1.575 GHz                                          | Very slow                            | Greater than 1 mile                             |

| WCDMA     | Around 2 GHz                                       | 2 Mbps                               | Greater than 1 mile                             |

| Bluetooth | 2.402-2.408<br>GHz                                 | 3 Mbps                               | 10 meters                                       |

| 802.11b/g | 2.4-2.483 GHz                                      | 11 Mbps @802.11b<br>54 Mbps@ 802.11g | 35 meters (indoor)                              |

| 802.11a   | 5.15-5.35 GHz<br>5.47-5.725 GHz<br>5.725-5.875 GHz | 54 Mbps                              | 30 meters (indoor)                              |

| UWB       | 3-10 GHz                                           | Up to1 Gbps                          | 3-10 meters depending on the transmission speed |

Figure 1: Comparison of various communication standards

Figure 2: Wireless standards spectrum

Transfer of huge amounts of data would also need high bandwidth communication. Figure 3 shows the growing size of the average computer hard disk, which will soon move into the terabyte regime. As this trend grows, we would soon need systems for faster data transfer between these devices [12]. A variety of multi-gigabit application interfaces and entertainment connectivity solutions such as HDMI, USB2/3, MIPI, GbE, PCI, etc... can be address with the single chip 60GHz solution. This is the "user need" driven motive to explore 60GHz Communication system.

Figure 3: Average storage capacity of hard disks

# 1.2 Choice of 60GHz for the Digital Radio

A wide variety of reasons influenced the choice of developing a 60GHz digital radio, some of which are highlighted below. Typical transit frequency ( $f_T$ ) curves for Silicon Germanium (SiGe) and Complementary Metal Oxide Semiconductor (CMOS) devices at various technology nodes are presented in Figure 4. At the 90nm node, the CMOS  $f_T$  is over 140GHz, making it an ideal choice for the development of 60GHz radio transceiver.

Figure 4: Transit frequencies for SiGe and CMOS at various technology nodes

From the mid 90's, the defense sector has applications in the higher frequency band (77GHz) using III-V compound semiconductors (GaAs, HBT, PHMET) [13] [14]. The digital post processing for these applications was realized on vanilla CMOS processes, mainly for cost benefits. Using the III-V semiconductors for high volume production design was not feasible and this was one of the major thrusts for CMOS RF front-ends. The interest in utilizing the unlicensed band at 60GHz for high-speed short-range communication was exploited. A unique feature of this frequency band is the high oxygen absorption level (~15dB/km). High absorption levels prohibited long range communication. However they were advantageous from the frequency reuse perspective. This meant that two communication links, located in close proximity of each other could operate simultaneously. This wireless network was standardized by the IEEE 802.15 Working Group for Wireless Personal Area Networks (WPAN).

The Federal Communications Commission (FCC) in the United States, allocate the 59-64GHz frequency band for general unlicensed use. Japan standardized the 59-66GHz band for high-speed data communication. In Europe, the 59-62GHz band has been allocated for Wireless Local Area Network (WLAN) and mobile broadband systems use the 62-63GHz and 65-66GHz bands. Since propagation losses increase with the operating frequency, we need high gain antennas for longer reach. Higher the gain of the antenna, narrower the beam width and this helps minimize the beam spread. Overall, the combined effect of oxygen absorption, narrower beam widths, and higher frequency reuse positions the 60GHz band [15] most appropriate for short range high data rate communications.

This 60GHz unlicensed band has a sufficiently large bandwidth of about 7GHz and is capable of providing multi-gigabit throughput using simple modulation schemes like ASK (Amplitude Shift Keying) and BPSK (Binary Phase Shift Keying). More complex schemes such as QPSK (Quadrature Phase Shift Keying), QAM (Quadrature Amplitude Modulation) and OFDM (Orthogonal Frequency Division Multiplexing) support data-rates as high as 10Gbps. Thus we can ensure a seamless integration with multimedia standards.

## 1.3 Digital Control and backend

The design of 60GHz CMOS Digital Radio Transceiver is extremely complex with many RF, Analog and digital modules juxtaposed on the chip. Each of these RF and Analog mixed-signal modules need to be tuned for optimal performance. Doing so would ensure lower power consumption, higher spectral efficiency and higher data rates with lower BERs (Bit Error Rates). Hence it is crucial for us to ensure that all these modules get tuned and calibrated appropriately. This gives rise to the need for a reliable debug and tuning mechanism over a robust communication channel. Amongst the available serial interfaces, the SPI [16] communication protocol suits our needs best. This duplex serial communication link has been customized for high speed operation.

The digital backend on this transceiver forms the backbone of the wireless communication channel. The digital modem, PHY (physical communication layer of the OSI 7 layer software stack) [17] and the MAC (Media Access Control sub-part of the Link Layer), form the digital content on this chip. The Radio link is serial and hence the digital modem also operates on the serial data stream. Thus it is designed to be fairly simple with only the necessary functionality built into it. For ease of test, the transceiver was designed in a two-chip solution. Later revisions were fully integrated single silicon die CMOS transceiver solutions. The serial data stream is sent off-chip using high-speed digital I/Os. The separate test-chip for PHY and MAC modules interfaces with this high speed serial link. The PHY and MAC make up a million gate design which was implemented using the ASIC physical design flow. Special attention was given while building the I/O ring with extra attention to the pad ring, power cuts and pad assignments.

## 1.4 Organization of Thesis

The thesis is divided into seven chapters. After introducing the research objective of the 60GHz digital radio and its design challenges in chapter 1, chapter 2 talks about the physical design flow in ASIC design. It starts with register transfer level (RTL) design and briefly touches upon the entire flow: RTL coding, synthesis, simulation, layout, verifications. The PHY and MAC designs were developed using this flow. For version-1 they were part of a separate chip (ease of testing). In the later versions, they were integrated with the RF front-end on a single chip. Screenshots used to illustrate the digital flow are some of the intermediate steps during the MAC-PHY Physical layout development. Chapter 3 discusses the various serial communication interfaces used for on-chip and off-chip data acquisition. The chapter concludes with the choice of Serial Peripheral Interface (SPI) as the chosen serial communication protocol for the 60GHz digital radio system.

Details of the serial interface sub-system are explained in chapter 4. Two designs for the SPI were realized in 90nm CMOS process. The differences in the two designs and the motivation to switch from one to the other, is provided. Detailed timing diagrams for the different modes of operation are presented. Chapter 5 talks about the measurement setup developed for using this serial communication interface. The testing phase began with standard off-the-shelf protocol analyzers and bit-stream signaling sources, and went on to custom-designed modules.

Digital I/Os (with standard 50Ω termination) were designed to bring out the SPI ports. For bringing out the baseband signal we developed a multi-gigabit digital I/O interface. Chapter 6 discusses these designs. This chapter briefly touches upon the importance of ESD protection in the ASIC development flow. It discusses the major ESD failure mechanisms and outlines a few design techniques to mitigate that risk. A special I/O ring had to be developed for the MAC-PHY standalone chip (version-1) which forms the last part of this chapter. The chapter concludes with some measurement results. Chapter 7 concludes this thesis by summarizing the work performed and suggesting future improvements.

# 2 PHYSICAL DESIGN FLOW FOR ASIC IMPLEMENTATION

The *Physical Design* of any full-custom ASIC [18] can follow either the top-down design or the bottom-up approach. Figure 5 shows an overview of the physical design flow for ASIC (Application Specific Integrated Circuit) implementation from RTL to GDSII, in the top-down approach. The following subsections detail the individual steps mentioned. The step-wise physical design flow [19], highlighting the corresponding tool used at each step, is shown in Figure 6.

Figure 5: Designing SoC - From Logic design to Physical design

Figure 6: System-On-Chip Design Flow

#### 2.1 Design Entry

The physical design flow for ASIC implementation begins with design entry in logical format as shown in Figure 5. The system is described in a symbolic or descriptive language and a simulation is run to test the functionality. This description resembles a flowchart and hence is technology independent. The system operation is tested at an abstract level. High-level architectural changes need to be incorporated at this stage.

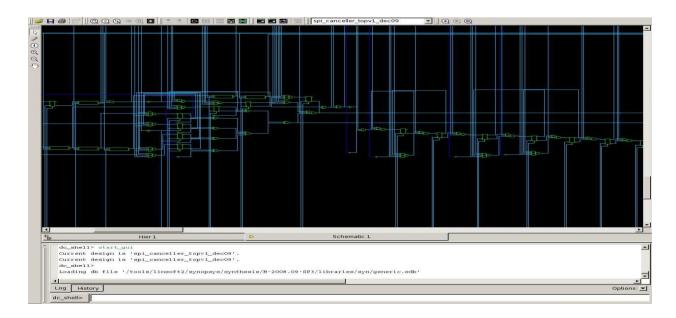

# 2.2 Logic Synthesis

Generally, all the digital cells are developed in each of the fabrication houses (foundries) and licensed out as "Digital Standard Cell Libraries." The standard cells come in different descriptions with each one called a "view". During the synthesis stage we make use of the Verilog [20] (behavioral) view and the timing-power view. The logical description of the design is mapped on to standard cells (digital gates) through this process of synthesis. Synopsys Design Compiler [21] and Cadence BuildGates [22] are some of the tools that we used for synthesis. These tools support schematic viewers for viewing the gate level design and the connectivity. At this stage, we are ready to perform a Static Timing Analysis (STA) [23] on the design.

# 2.3 Logical Verification:

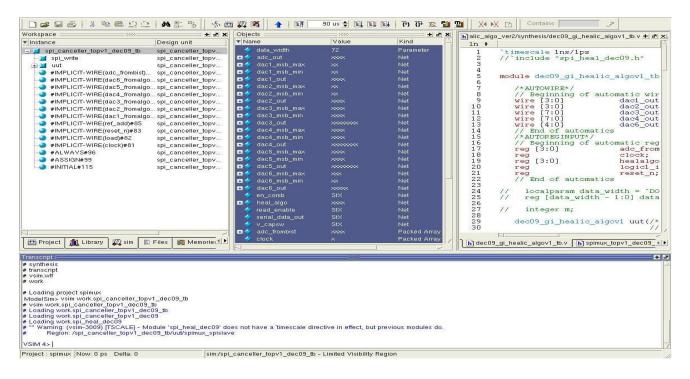

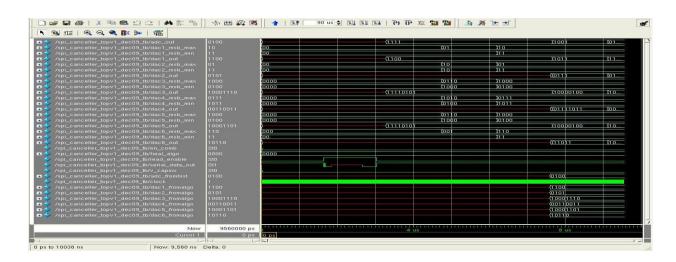

The synthesized gate level Netlist is read into a simulation tool like "ModelSim" from Mentor Graphics [24]. A detailed testbench is created in the same descriptive language (Verilog or VHDL [25]). This testbench has a sequence of test vectors that are applied to the unit under test (our design). A waveform viewer is used to view the test results. The following set of images highlight the procedure.

Figure 7: ModelSim Workspace

Figure 8: ModelSim Schematic

Figure 9: ModelSim Waveform

## 2.4 Static Timing Analysis

All the standard cells are characterized and Look-Up Tables (LUT) for timing and power data has been generated. The timing views for the standard cells are read into a static timing analysis tool like PrimeTime from Synopsys [23] and the design is linked. We then define the boundary conditions and the timing constraints for the design through the Synopsys Design Constraint (SDC) file [26]. A detailed outline of the timing analysis flow is shown below:

#### i. Preparing the Analysis Environment

The standard cell libraries are read in first. Then the Netlist (design) is read in. The link paths are setup and the design is linked. The appropriate wire load models are read in and the operating conditions are set.

#### ii. Preparatory timing and clocking checks

The most important step here is to define the system clock. Min-max values for the clock uncertainties and latencies are set. We can also define the clock duty cycle and transition times. Setup, hold and other clock gating checks are verified as part of this step. This timing verification is done at multiple stages in the flow, starting with post-synthesis, then post-layout and finally during the timing sign-off phase. During the post-synthesis phase, the wire delay is only an estimate. However we have real extracted data during the other two phases. The wire delay is extracted in a format called the Standard Delay Format (SDF) [27] and is back-annotated on the design.

#### iii. Checking design integrity

When the design has been setup correctly, the design integrity can be checked by commands such as *report\_design*, *report\_reference* and so on.

#### iv. Running timing analysis

Executing the command 'check\_timing' will use all the timing constraints and run the timing engine on the design. A thorough check on setup times, hold times and transitions time will be performed. Warnings and errors will be thrown up for each and every check. Some of these could be exceptions such as false paths, multi-cycle paths, clock domain crossings, etc. These errors need to be resolved at this stage. Timing slacks [28] can be reported for further detailed analysis. Some of the advanced timing issues like reset recovery and removal, clock synchronization, etc are explained in the references [29].

#### v. Boundary timing characterization

Timing characterization can be hierarchical with sub-designs and parent design. The partitioning could be in design compiler (synthesis) or within PrimeTime (for ease of timing analysis). Some of the key aspects related to timing hierarchy are: input and output arrival delays, input and output port loads, constant logic values on inputs, logic propagation, annotated delays and parasitic, timing exceptions and so on.

#### vi. Fixing timing violations

Timing violations need to be fixed on a case-by-case basis. Some violations could be false, such as false paths. Like the reset paths on flip-flops. Some paths may span multiple clock periods and need to be constrained as multicycle paths. Then there are IO paths that need to be properly constrained with commands such as 'set\_input\_delay'.

| in routine s<br>'/ho                                               | pi_l             |                  | c09                                        | li                 |                         |         |                      |                                    |               | рi     | mux    | x/1 | temp   | 0_: | syn           | th                                        | esi                | s/                    | sp            | i_ł | neal_dec09                                |

|--------------------------------------------------------------------|------------------|------------------|--------------------------------------------|--------------------|-------------------------|---------|----------------------|------------------------------------|---------------|--------|--------|-----|--------|-----|---------------|-------------------------------------------|--------------------|-----------------------|---------------|-----|-------------------------------------------|

| l Register Name                                                    | 1                | Туре             |                                            | 1                  | Width                   | I       | Bus                  | 1                                  | МВ            | I      | AR     | ı   | AS     | 1   | SR            | 1                                         | SS                 | 1                     | S             | ΤI  |                                           |

| load_sync_1_reg<br>  load_sync_2_reg                               |                  | Flip-f<br>Flip-f |                                            |                    | 1<br>1                  | 1       | N<br>N               |                                    | N<br>N        | 1      | Y<br>Y | 1   | N<br>N | 1   | N<br>N        | 1                                         | N<br>N             | <br> <br> <br>        | N<br>N        | 1   |                                           |

| Inferred memory devi<br>in routine s<br>'/ho                       | pi_l             | heal_de          | c09                                        | li                 |                         |         |                      |                                    |               | pi     | mus    | x/1 | temp   | o_: | syn           | th                                        | esi                | s/                    | sp            | i_ŀ | neal_dec09                                |

| l Register Name                                                    | 1                | Туре             |                                            | 1                  | Width                   | 1       | Bus                  | 1                                  | МВ            | 1      | AR     | 1   | AS     | 1   | SR            | Ī                                         | SS                 | 1                     | S             | ТΙ  |                                           |

| I idr2_reg                                                         | 1                | Flip-f           | ====<br>lop                                | <br>I              | 72                      | 1       | Υ                    | 1                                  | N             | ı      | Υ      | 1   | N      | 1   | N             |                                           | N                  | ==<br>                | N             | ī   |                                           |

| in routine s<br>'/ho<br>                                           | me/s             |                  | r6/B<br>====                               | G/<br>==           | healid                  | 2/0     | dec09                | 9_9                                | i_s           | ==     | ==:    | ==: |        | ==  | ===           | ==                                        | ===                | ==                    | ==:           | === | neal_dec09<br>:                           |

|                                                                    | ===:             |                  |                                            |                    |                         |         | bus                  | 1                                  | LIR.          | 1      | LIIZ   | 1   | пэ     | 1   | DK            | 1                                         | 22                 | . 1                   | S             | ΤI  |                                           |

| pdout_reg<br>  pdout_reg                                           |                  | Flip-f<br>Flip-f |                                            |                    | =====                   | 1       | Y<br>Y               | 1                                  | ===           | ==     | Y<br>Y | ==: | N<br>N | ==: | N<br>N        | ==                                        | N<br>N             | <br> ==<br> <br> <br> | N<br>N        | T   |                                           |

| pdout_reg<br>=============<br>Inferred memory devi<br>in routine s | l<br>ces<br>pi_h | Flip-f           | lop<br>====<br>cess<br>c09<br>r6/B<br>==== | <br>==<br>li<br>G/ | 64<br>64<br>64<br>===== | 1 1 2 : | Y<br>Y<br>Y<br>in f: | <br> <br> <br> <br> <br> <br> <br> | N<br>N<br>=== | l<br>l | Y<br>Y |     | N<br>N | 1   | N<br>N<br>=== | ==<br> <br> <br> <br> <br> <br> <br> <br> | N<br>N<br>N<br>esi | ==<br> <br> <br> <br> | N<br>N<br>==: |     | :<br>:::::::::::::::::::::::::::::::::::: |

**Figure 10: DC Shell Execution**

# 2.5 Physical Design

Once the design passes timing checks, it is ready to be taken into layout. We use the SOC Encounter tool form Cadence Design Systems [30] for physical design. An outline of the physical design flow is presented here:

#### i. Data Preparation

Before the design is taken into the physical layout tool, the reference libraries and constraints are setup. These steps include: setting up the path of the technology file, reading in the physical (.lef) and timing (.db) libraries, reading in the timing constraints file (.sdc), I/O assignments (.tdf or .io) and setting up the TLU+ model files for parasitic RC extraction.

#### ii. Design Check

The 'checkDesign' command checks the design integrity with respect to the following:

- Physical library

- Timing library

- Netlist

- I/O constraint

- Power and Ground nets and pins

- Tie-highs and tie-lows

#### iii. Read Design

The Netlist must be read into the design. While doing so, the *SoC Encounter* can be instructed to preserve logical hierarchies in the design. This will show up as soft-macros during the placement stage and helps group relevant cells (logic).

Figure 11: Design netlist read into SoC Encounter

The Netlist is made unique as part of the reading process. A unique Netlist is a pre-requisite for performing Clock Tree Synthesis (CTS), scan chain reordering and Timing optimization and closure related functions (command: uniquifyNetlist).

Another important check at this stage is the check for "assign" statements. The assign statement emulates a wire in RTL/Verilog. This is not the case with a physical design tool. In Verilog, the two ends of the logical wire can be connected to two different net names. However in physical layout as well as in reality, there exists only one unique name for that net. Hence the assign statements need to be cleanup by modifying the Netlist (*setDoAssign on*) or inserting buffers

(setDoAssign on -buffer buffer\_name). A little care needs to be taken by manually ensuring that the timing constraints through that net are retained.

#### iv. Design Partitioning

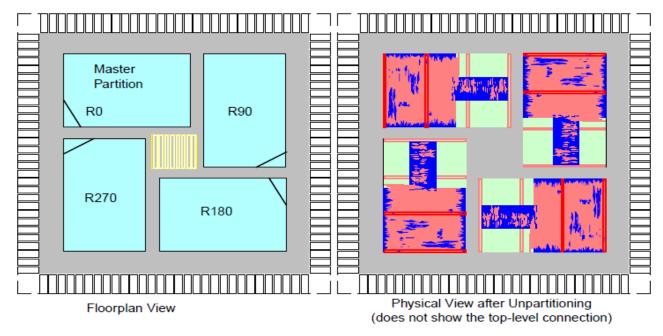

To minimize the run-time and memory requirements, large designs are partitioned either in a top-down method or a bottom-up method. Both approaches involve the use blackboxes. When working with blackboxes, they need to be defined early in the flow. The logical boundary needs to be specified with intermediate ports/pins. Timing sync (synchronization) points need to be specified. Separate power domains need to be defined. When the blackbox is taken into the placement stage, the top level power mesh needs to be pushed down into the macro. The I/O and timing information needs to be pushed down into the macro. After that, the blackbox macro would be laid out as a separate design. To integrate the blackbox back into the top level design, special commands need to be used; 'loadBlackBoxNetlist', 'convertBlackBoxToFence', 'assignPtnPin', 'alignPtnClone' and so on. At this stage, the partitioning on the macro can be undone and the subsequent macro can be merged with the top design if needed. The designer needs to make this engineering judgment which is primarily influenced by the timing criticality of the design. For a detailed timing closure, a flat design is preferred and hence the purpose of Unpartitioning.

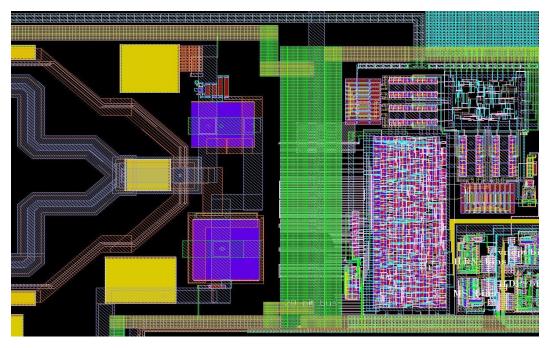

Figure 12: SoC Encounter Views for Floorplan (Macro Placement)

Figure 12 shows the blackboxes in different orientations. The fig on right shows the macros after unpartitioning. The top level wirings are not shown here. In the *Floorplan view*, we can see placement blockage at the center of the chip. [31].

#### v. Floorplanning and Placement

After reading in the Netlist, the design moves into the floorplan stage. Various options exist for defining the floorplan; rectilinear floorplan, core-to-io spacing, aspect ratio, cell placement utilization, number of rows and columns and so on. All this information can be saved and re-read during the design iteration. The design connectivity needs to be studied and memories, macros and blockages need to be properly placed. This is very crucial to avoid routing congestion at a later time which might trickle down to timing closure problems. Common layout practice is to place placement halos around memories. The halo is generally concentric with the inner-halo being a hard placement blockage and the outer-halo allowing decap (decoupling capacitor cells) and buffer placement.

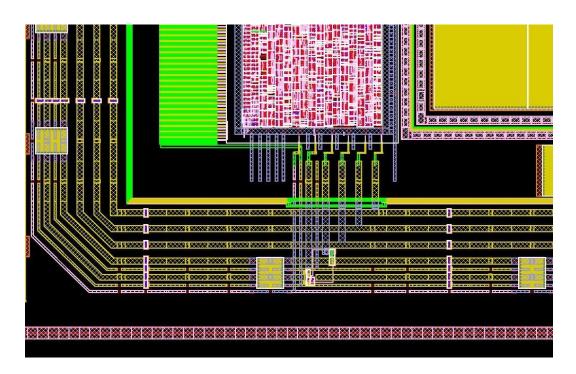

Figure 13: Placing memories with power termination rings

The design is now ready for timing driven placement of standard cells. To save up on the layout area, the standard cell rows should be flipped and abutted. The cells can be grouped by logical partitions and optimized for timing. It is a general practice to "glue" related cells together in a group and to color them. Thus the layout can be optimized in a partitioned design scenario. Pre-routes are created in the next step. Power ring and stripe widths are decided by the power and delay requirements.

Figure 14: Power ring and stripe

Figure 15: Standard cell groups in colors

The pins are placed during this stage. Care needs to be taken when placing the Clock and reset pins. Clock pin placement decides the H-tree structure during clock tree synthesis stage. Reset pin is also important due to the large fan-out on that net.

Certain process nodes mandate the use of tap cells to supply power to the Nwell and to ground the p-substrate. The taps need to be placed in a repetitive fashion and must lie within some specific distance from each other. Tie-off cells are used on inputs which are tied off to VDD or GND, as an additional ESD (Electro-Static Discharge) protection.

### vi. Synthesizing the clock tree

The goal of Clock Tree Synthesis (CTS) [32] is to minimize clock skew and insertion delay. The process of CTS involves the usage of the following list of files:

- The timing constraints file (.sdc)

- The clock specification file (.ctstch)

- o The capacitance table and

- o The LEF (physical library) for clock buffers and delay cells.

Table 1 enumerates the structure of the clock tree specification file.

**Table 1: Clock Tree Specification File**

| AutoCTSRootPin | <clock name="" pin=""></clock>       |

|----------------|--------------------------------------|

| NoGating       | Rising                               |

| SetDPinAsSync  | YES                                  |

| SetIoPinAsSync | YES                                  |

| PostOpt        | YES                                  |

| OptAddBuffer   | YES                                  |

| Buffer         | <buffers in="" library=""></buffers> |

| MaxDelay       | 200 ps                               |

| MinDelay       | 0 ps                                 |

| MaxSkew        | 50 ps                                |

| End            | ·                                    |

Most of the attributes specified above are self explanatory. The attribute "NoGating" sets clock gating as a sink. Hence the CTS engine stops tracing through the gates and considers those inputs as rising edge triggered flip-flop clock pins. Assign a "NO" value to have a gated clock tree synthesis. We also specify to run a post CTS optimization to confirm that the timings are within bounds. Some details about the timing related terminology (skew, slew, etc) is presented later.

The timing constraints for the design need to be setup. Common practice suggests addition of some design margin into these constraints to account for routing bottle necks later in the flow. Encounter timing engine will trace the clock net throughout the design and propagate it through combinational logic. The tool is smart enough to figure out the correct phase of the clock at every flip-flop.

For gated clock tree synthesis, the clock tracing stops at:

- 1. A clock pin

- 2. An asynchronous set/reset pin

- 3. A user specified leaf pin (clock sink) or an exclude pin

- 4. An input pin without a timing arc to an output pin.

The designer can check whether the clock specifications were properly applied on the design by executing the 'ckSynthesis –check' command and fixing any errors. The next step after this is to synthesize the clock tree on the design. The setup and hold times are reported in the command console. CTS added cells and affected nets are dumped into reports that can be read from a web browser or text editor. Special (detailed) analysis for delay variation and OCV (On Chip variation) [33] can be performed using 'setAnalysisMode' and 'setTimingDerate' commands. Clock reconvergence issues are discussed in a later section.

#### vii. Routing

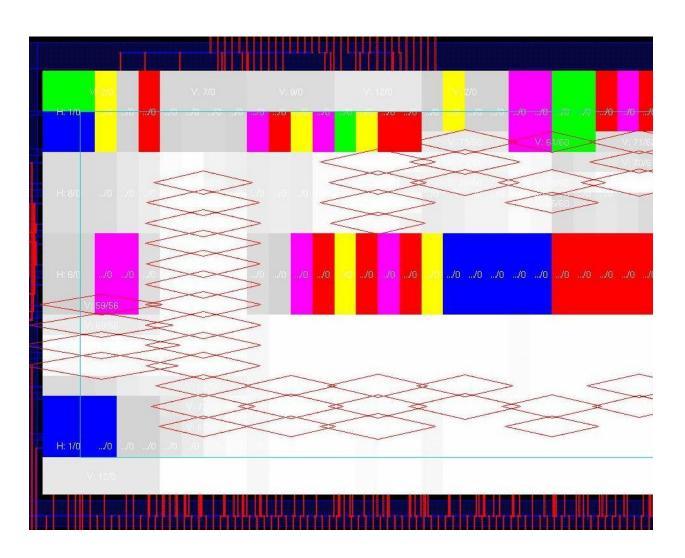

SoC Encounter tool divides the core area in smaller regions called g-cells (global routing cells). This is similar to the small delta areas we consider when performing surface integrals. The entire core region is divided into routing channels which are alternating and orthogonal. Each g-cell will have about 10-20 routing resources which get assigned to the nets in the design. This helps in analyzing the congestion in the design. If some areas seem to have very high congestion numbers then we need to go back to the placement stage to reorient or to move cells around. There exist other tricks such as creating density screens, strategically placing routing blocks and so on.

Before we are ready to route the design, we need to set the correct layer stack information. Extra spacing, double via, extended via and other options need to be set. Special routes are generally done before the entire design gets routed. Clock nets would be an example of special routes.

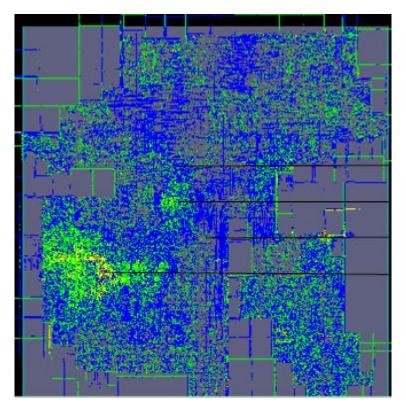

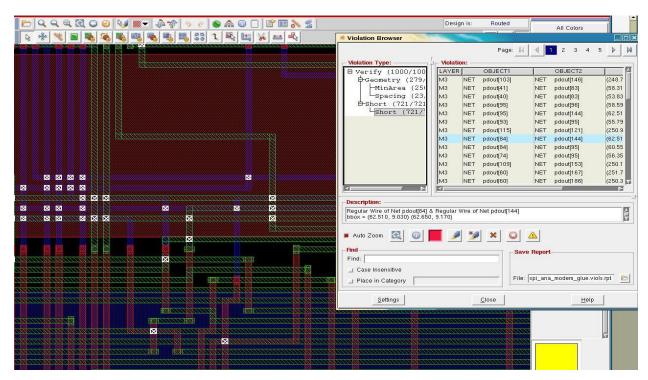

Routing is divided into three stages: global route, detailed route and eco route. The designer needs to ensure that the design is placed and power routing is complete. Once the Nano Router has run, various reports are generated. Depending on the complexity and size of the design, there could be opens and shorts as well as DRC (Design Rule Check) violations such as *vias* under wide power nets, etc, which need to be fixed. These can be fixed with ECO routing. It is customary to run a timing check and timing optimization loop before fixing these errors. Since the routing is complete, the timing optimization engine can perform setup as well as hold fixes. This step is also called as the Post Route Optimization step. Though the timing engines used while routing and timing optimization are identical, their accuracy settings are different, with the most accurate one being sign-off timing checks.

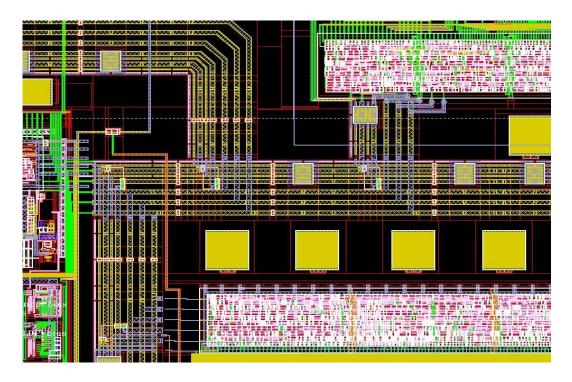

Figure 16: Congestion map and tracks used

Figure 17: Showing congestion

The designer should ensure that the special routes are not messed up during detailed route. Special routes are clock routes (generally on higher metal layers to minimize parasitic caps) and analog routes (differential routing with shielding). This would be a good time to verify the geometry (DRCs) and connectivity (LVS).

### viii. Design finishing

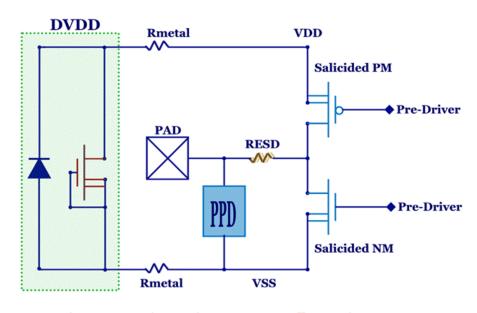

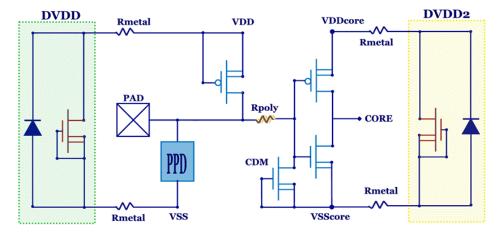

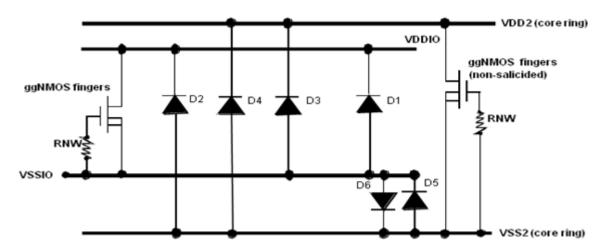

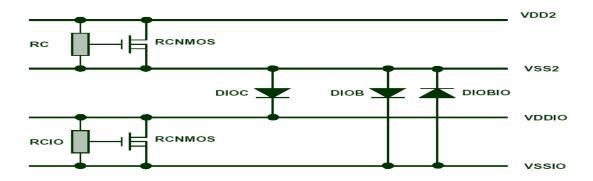

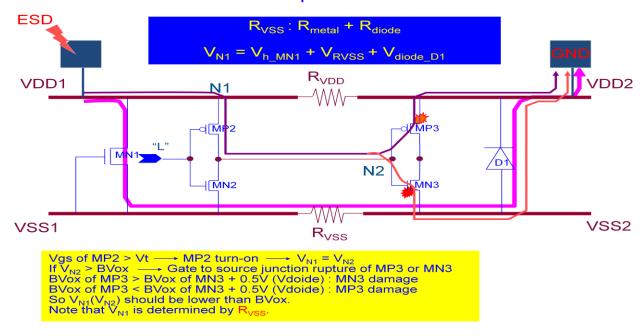

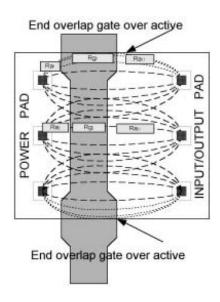

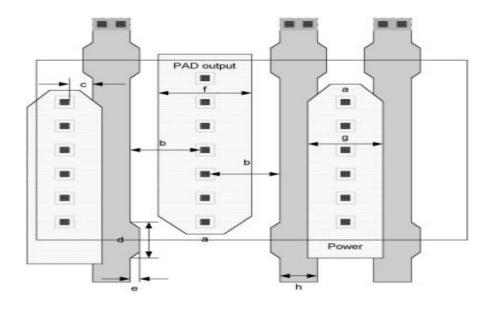

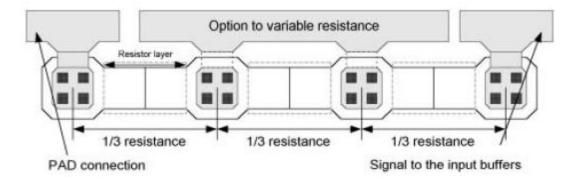

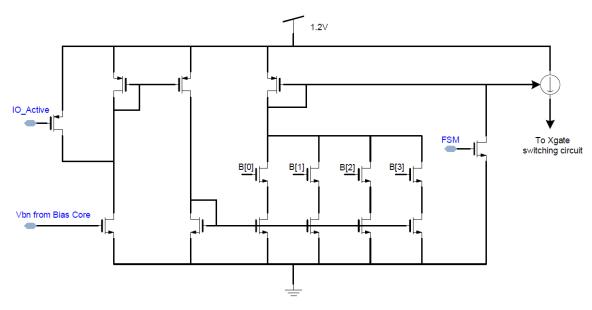

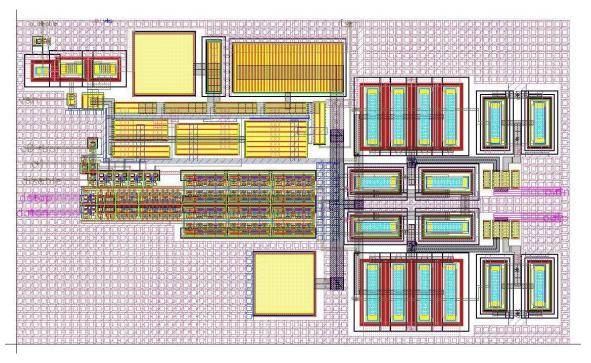

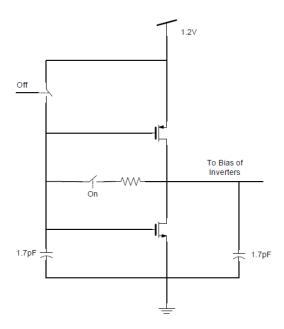

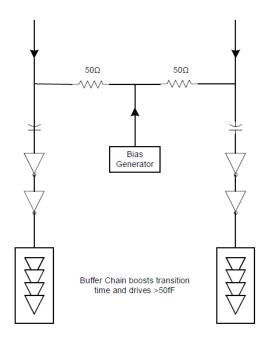

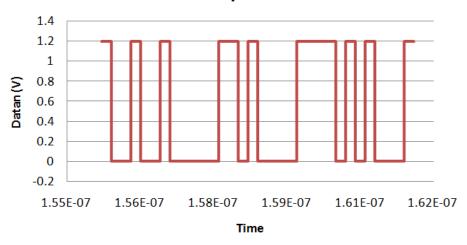

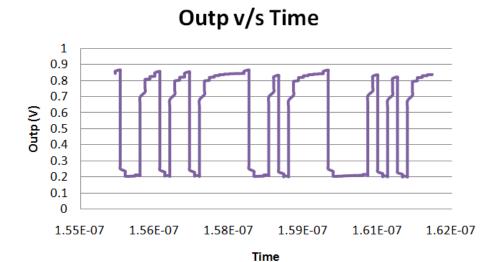

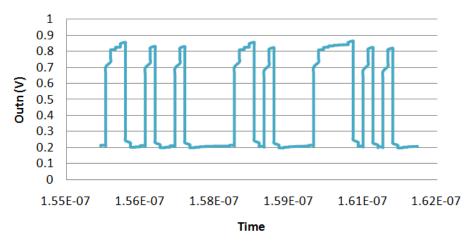

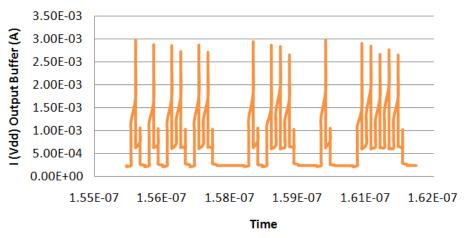

Post route optimization stage will fix all setup violations and most hold violations. Any setup violations left might need an RTL level fix, in which case, an ECO flow would be necessary. Hold violations can generally be fixed by insertion of buffers and rerouting. Sometimes hold is not fixed by the tool due to lack of space. Freeing up the placement a little helps. At the 90nm and finer technology nodes there is a minimum metal density needed for proper CMP (Chemical Mechanical Planarization). To have uniform metal thickness all over the chip, with varying thicknesses of dielectric layers, we need passive (floating chunks of metal) or active (connected to a particular net) metal fill. Making the topology of the metal layers more uniform, we can minimize the variations in metal density.