# COLLECTING AND REPRESENTING PARALLEL PROGRAMS WITH HIGH PERFORMANCE INSTRUMENTATION

A Thesis Presented to The Academic Faculty

by

Brian Paul Railing

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology December 2015

Copyright  $\bigodot$  2015 by Brian Paul Railing

# COLLECTING AND REPRESENTING PARALLEL PROGRAMS WITH HIGH PERFORMANCE INSTRUMENTATION

Approved by:

Professor Thomas M. Conte, Advisor School of Computer Science Georgia Institute of Technology

Professor Sudhakar Yalamanchili School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor Santosh Pande School of Computer Science Georgia Institute of Technology Professor Richard Vuduc School of Computational Science and Engineering Georgia Institute of Technology

Dr Bruce Worthington Windows Platform Health Microsoft Corporation

Date Approved: 30 October 2015

Man's chief end is to glorify God.

## ACKNOWLEDGEMENTS

A dissertation is not a sprint, but a marathon. I have trained for years with many people, practiced my work, and then find so many there at the race cheering me on until I reach the finish. Many have contributed to this research, from the anonymous reviewers and readers who have given feedback and suggestions, to the family, friends, and church members encouraging and praying for me. I am thankful for their efforts and contributions that have helped carry me to the finish.

The research group is vital to completing the dissertation work, with their encouragement and collaboration, and the serious discussions over the core of so many topics. I would like to thank Eric Hein, whose efforts were vital to get Contech off of the ground and whose patience for my speculation, questions, and venting lasted throughout this work. Sriseshan Srikanth, thank you for providing the late push to complete this research. And thank you to Dr. Jesse Beu with whom I discussed much in those early years, for whom we started preparing Contech to help us understand parallel programs, and to quote your dissertation, "we will publish together!"

To my advisor, Dr. Tom Conte, who took me in when I was an advisor-less graduate student, thank you. Also thank you for telling us over and over again that we needed to think bigger when first planning Contech; we just wanted to solve a problem, but you pushed the topic from a paper to a dissertation. And a further thank you for supporting my passion and desire to teach, letting me take those opportunities to develop and grow in my chosen profession.

To Dr. Bruce Worthington, who helped form my knowledge of computing in the real world as my manager for four years and now served on my dissertation committee, thank you. Thank you to the rest of my committee for their time and effort in serving the future generation of scientists, guiding and reviewing us.

A deep thank you to my parents, the teacher and the computer scientist, who inspired me in my chosen career, read so many drafts over the years, and helped support this work in so many ways.

I would be remiss if I did not thank my son, Titus, who would tell me, "Daddy, type!" For being only two years old, you understand so much of what is going on around you and what I needed to be doing.

Finally, Vickie Railing, who agreed to marry me and travel across the country to enter graduate school. You are my helper each and every day. For how much you have read of Computer Science, listened to me discuss my work, my reviews, and everything else, this is your degree too.

# TABLE OF CONTENTS

| DE                  | DIC          | ATION                                                                            | iii  |  |

|---------------------|--------------|----------------------------------------------------------------------------------|------|--|

| ACKNOWLEDGEMENTS iv |              |                                                                                  |      |  |

| LIST OF TABLES      |              |                                                                                  |      |  |

| LIS                 | ат о         | F FIGURES                                                                        | xi   |  |

| SU                  | MM           | ARY                                                                              | xiii |  |

| 1                   | INTRODUCTION |                                                                                  |      |  |

|                     | 1.1          | Definitions                                                                      | 2    |  |

|                     | 1.2          | Future Challenges                                                                | 3    |  |

|                     |              | 1.2.1 Architectural Challenges                                                   | 3    |  |

|                     |              | 1.2.2 Programmer Challenges                                                      | 4    |  |

|                     | 1.3          | Designing a New Tool                                                             | 6    |  |

|                     | 1.4          | Contributions                                                                    | 7    |  |

|                     | 1.5          | Organization                                                                     | 8    |  |

| <b>2</b>            | TAS          | SK GRAPH REPRESENTATION                                                          | 9    |  |

|                     | 2.1          | Extending from Prior Task Graphs                                                 | 9    |  |

|                     | 2.2          | Parallel Program Representation                                                  | 10   |  |

|                     | 2.3          | Contech Task Graph                                                               | 12   |  |

|                     | 2.4          | Visualizing a Contech Task Graph                                                 | 16   |  |

|                     | 2.5          | Incorporating a Parallel Programming Model into the Task Graph<br>Representation | 17   |  |

|                     | 2.6          | Example Task Graphs                                                              | 18   |  |

|                     |              | 2.6.1 Why are syncs (i.e. non-work) a unique type of task $\ldots$ .             | 20   |  |

|                     | 2.7          | Other Parallel Program Representations                                           | 23   |  |

|                     |              | 2.7.1 Communicating Sequential Processes                                         | 23   |  |

|                     |              | 2.7.2 Concurrent Collections                                                     | 24   |  |

|                     |              | 2.7.3 LogP                                                                       | 25   |  |

|   |     | 2.7.4  | Legion                       | 25        |

|---|-----|--------|------------------------------|-----------|

|   |     | 2.7.5  | Galois                       | 25        |

|   |     | 2.7.6  | X10                          | 26        |

| 3 | PR  | OGRA   | M INSTRUMENTATION            | <b>27</b> |

|   | 3.1 | Reduc  | ing Instrumentation Overhead | 28        |

|   |     | 3.1.1  | Inlined Instrumentation      | 29        |

|   |     | 3.1.2  | Sampling                     | 29        |

|   |     | 3.1.3  | Mirroring Program            | 30        |

|   | 3.2 | Source | e Instrumentation            | 31        |

|   |     | 3.2.1  | GProf                        | 31        |

|   |     | 3.2.2  | ICECAP                       | 32        |

|   |     | 3.2.3  | LLVM-Based Approaches        | 33        |

|   | 3.3 | Instru | mentation Frameworks         | 34        |

|   |     | 3.3.1  | Pin                          | 35        |

|   |     | 3.3.2  | Valgrind                     | 37        |

|   |     | 3.3.3  | DynamoRIO and PiPA           | 38        |

|   |     | 3.3.4  | PEBIL                        | 39        |

|   |     | 3.3.5  | QEMU                         | 39        |

| 4 | СО  | NTEC   | H INSTRUMENTATION            | 41        |

|   | 4.1 | Overa  | ll Design Goals              | 41        |

|   | 4.2 |        | end                          | 43        |

|   |     | 4.2.1  | Front End Instrumentation    | 44        |

|   |     | 4.2.2  | Event Ordering               | 49        |

|   |     | 4.2.3  | Runtime Buffer Management    | 52        |

|   |     | 4.2.4  | Trace Formats                | 58        |

|   | 4.3 | Middle | e Layer                      | 58        |

|   | 4.4 | Instru | mentation Performance        | 61        |

|   |     | 4.4.1  | Data Write Performance       | 63        |

|      | 4.4.2   | Background Writing Performance | 66  |

|------|---------|--------------------------------|-----|

| 4.5  | Runni   | ng on ARM ISA                  | 70  |

| 4.6  | Compa   | arison with Pin                | 71  |

|      | 4.6.1   | Instruction Execution Rate     | 73  |

|      | 4.6.2   | Data Cache Miss Rates          | 75  |

| 4.7  | Variat  | ion on Workload Parameters     | 76  |

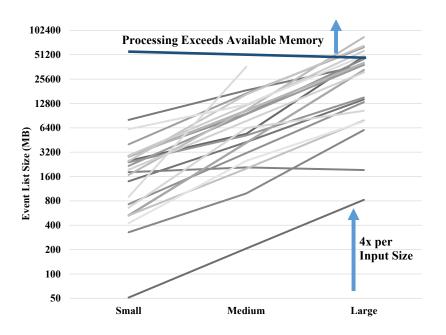

|      | 4.7.1   | Increasing Input Size          | 77  |

|      | 4.7.2   | Thread Counts                  | 78  |

| 4.8  | OpenM   | ΛP Support                     | 79  |

|      | 4.8.1   | Rodinia Benchmarks             | 81  |

|      | 4.8.2   | LULESH                         | 82  |

| 4.9  | MPI S   | upport                         | 82  |

| 4.10 | Cilk S  | upport                         | 83  |

| 4.11 | Other   | Implementation Issues          | 84  |

| 4.12 | Contec  | ch Compiler Wrapper            | 85  |

|      | 4.12.1  | Undefined Behavior             | 86  |

| 4.13 | Predic  | tor of Contech Performance     | 87  |

| PRA  | ACTIC   | CAL TASK GRAPH ANALYSIS        | 90  |

| 5.1  | Back e  | end tools                      | 90  |

|      | 5.1.1   | Types                          | 92  |

|      | 5.1.2   | Determinism in Analysis        | 94  |

|      | 5.1.3   | Basic Blocks                   | 95  |

| 5.2  | Paralle | el Programming Paradigms       | 96  |

| 5.3  | Sample  | e Analyses                     | 97  |

|      | 5.3.1   | Control Flow Graphs            | 98  |

|      | 5.3.2   | Cache Simulation               | 98  |

|      | 5.3.3   | Memory Usage                   | 99  |

| 5.4  | Summ    | ary                            | 100 |

$\mathbf{5}$

| 6  | PA  | RALLI  | EL PROGRAM MODELING                        | 101 |

|----|-----|--------|--------------------------------------------|-----|

|    | 6.1 | Relate | ed Work                                    | 102 |

|    |     | 6.1.1  | Modeling Parallel Programs                 | 102 |

|    |     | 6.1.2  | Simulating Parallel Programs               | 102 |

|    |     | 6.1.3  | Software-based Reconfiguration             | 103 |

|    |     | 6.1.4  | Hardware-based Reconfiguration             | 105 |

|    | 6.2 | Recon  | figurable Parallel Architecture            | 105 |

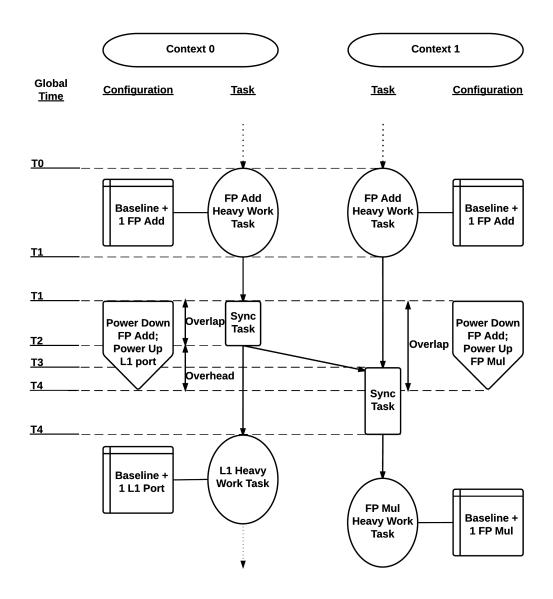

|    |     | 6.2.1  | Reconfiguration Time                       | 107 |

|    | 6.3 | Archit | tectural Model                             | 109 |

|    |     | 6.3.1  | Integration with Program Model             | 110 |

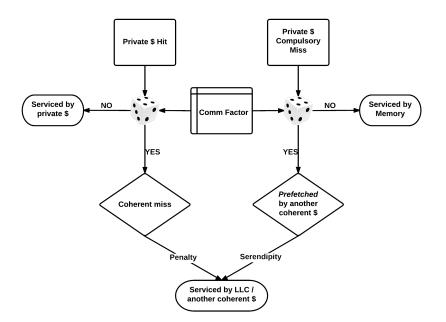

|    |     | 6.3.2  | Modeling Communication and Coherence       | 110 |

|    | 6.4 | Parall | el Program Modeling                        | 114 |

|    | 6.5 | Exper  | imental Results                            | 116 |

|    |     | 6.5.1  | Performance Improvement                    | 119 |

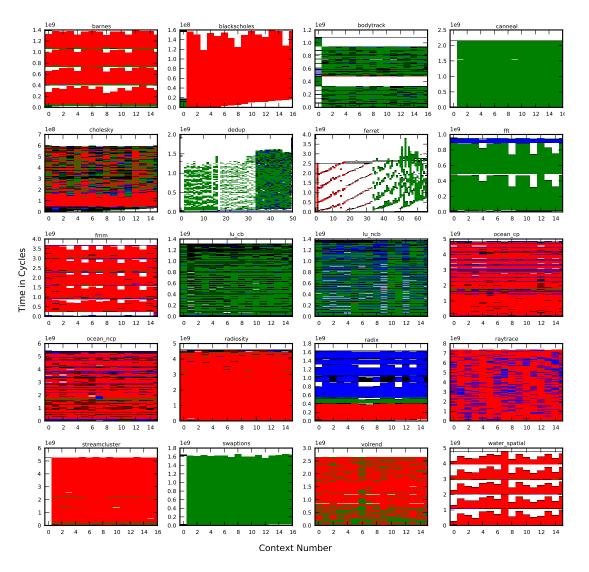

|    |     | 6.5.2  | Context Phase Variation                    | 121 |

|    |     | 6.5.3  | Comm Factor Granularity                    | 122 |

|    |     | 6.5.4  | Staticness of Configurations               | 123 |

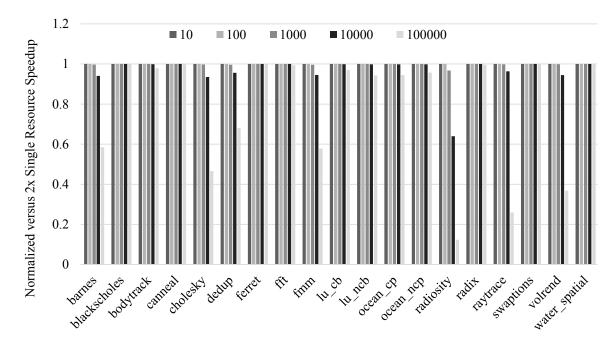

|    |     | 6.5.5  | Overlapping Reconfiguration and Wait Times | 125 |

|    | 6.6 | Summ   | nary                                       | 126 |

| 7  | CO  | NCLU   | SION                                       | 128 |

| RE | FER | ENCE   | $\mathbf{ES}$                              | 130 |

# LIST OF TABLES

| 1  | Instrumentation Tools with Similar Functionality to Contech (x - Support Present, b - Basic Block count without Full Path Information) . | 28  |

|----|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | System Configuration for Contech Measurements                                                                                            | 43  |

| 3  | Static Global Accesses per Benchmark                                                                                                     | 65  |

| 4  | System Configuration for Contech Measurements on ARM $\ldots$                                                                            | 70  |

| 5  | Runtime Overhead for PARSEC (simsmall) with Clang and Optimized Contech (without lto) on ARM                                             | 70  |

| 6  | Decision Forest Regression Model Parameters                                                                                              | 87  |

| 7  | Baseline Function Unit Configuration                                                                                                     | 106 |

| 8  | Baseline Resource Configuration                                                                                                          | 106 |

| 9  | Data Race Analysis Results (in Bytes)                                                                                                    | 112 |

| 10 | Benchmark Characteristics                                                                                                                | 117 |

| 11 | Number of Operations Concurrently Issued in Blackscholes Critical<br>Task (1:0)                                                          | 119 |

| 12 | Staticness of Ideal Per-Task Configurations                                                                                              | 124 |

# LIST OF FIGURES

| 1  | Different Simulation Types in Computer Architecture, (Figure 1 from Rico, et al. [102])                              | 7  |

|----|----------------------------------------------------------------------------------------------------------------------|----|

| 2  | Aggregating a Computation Graph into Tasks (Work: 1, 3, and 4; Create: 2)                                            | 11 |

| 3  | Classic Task Graph, circa 1993 [22]                                                                                  | 12 |

| 4  | Parallel Program Graph [107]                                                                                         | 13 |

| 5  | Legend for Visualized Contech Task Graphs                                                                            | 15 |

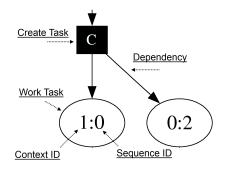

| 6  | Contech Task Graph Features by Type                                                                                  | 16 |

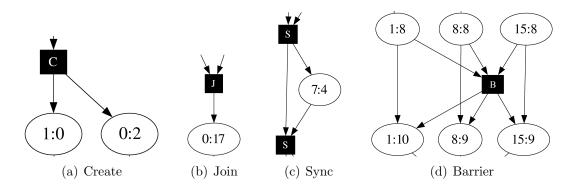

| 7  | Simple OpenMP Program as a Contech Task Graph                                                                        | 19 |

| 8  | Simple OpenMP Program Using OMP Tasks                                                                                | 20 |

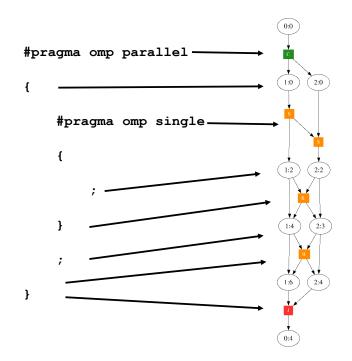

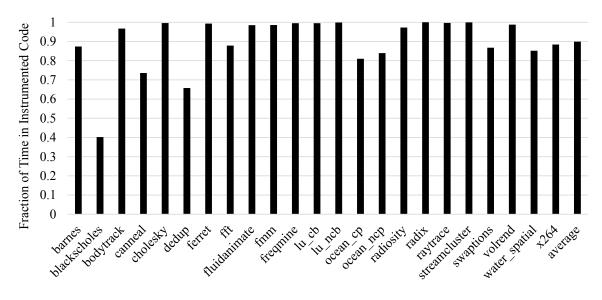

| 9  | Code Coverage by Contech Instrumentation                                                                             | 45 |

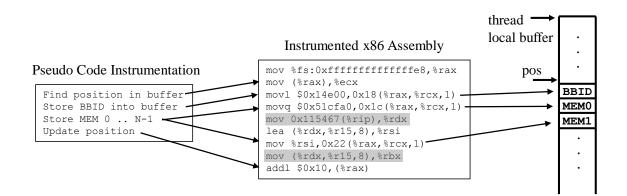

| 10 | Runtime Instrumentation Design (grey instructions are original code)                                                 | 48 |

| 11 | Instrumentation Slowdown due to Varying the Threshold for Using<br>Small Buffer Copy Path                            | 53 |

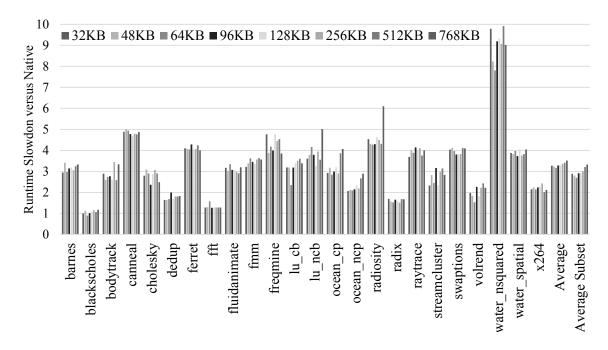

| 12 | Impact of Changing Buffer Size on Contech Runtime Slowdown                                                           | 54 |

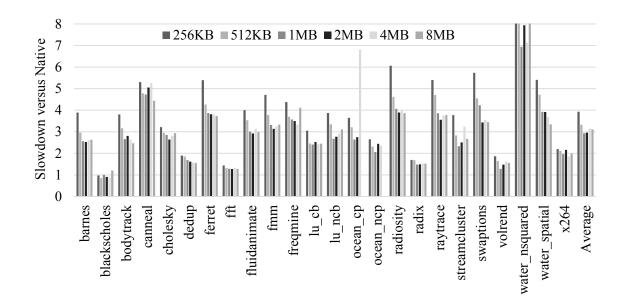

| 13 | Cost to Allocate Buffers based on the Size of Buffer                                                                 | 55 |

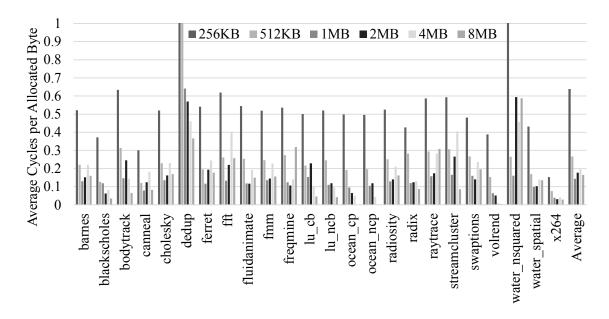

| 14 | Varying Buffer Allocation and Reuse                                                                                  | 57 |

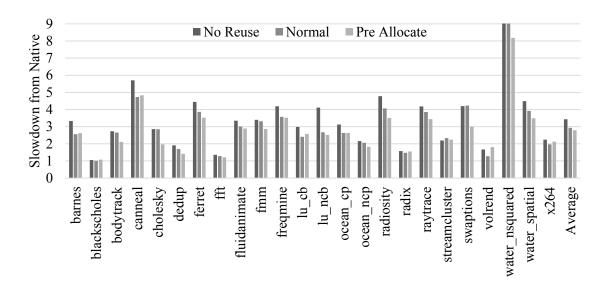

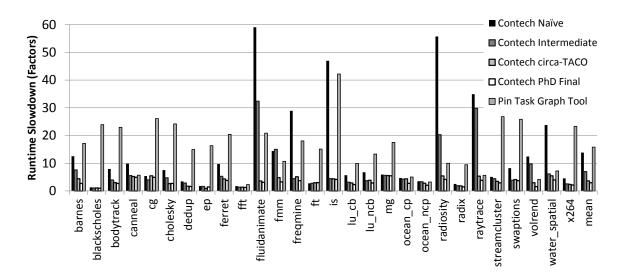

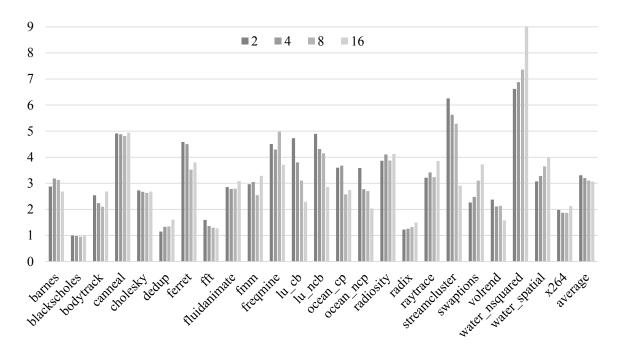

| 15 | Comparison of Contech and Pin Runtime Slowdown for PARSEC and SPLASH (simmedium, 16 threads) and NAS (A, 16 threads) | 61 |

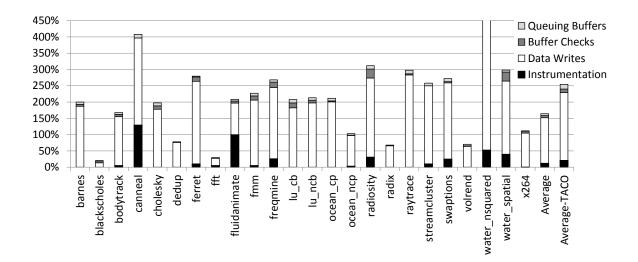

| 16 | Overhead Increase from Runtime Instrumentation over Uninstrumented<br>Programs                                       | 62 |

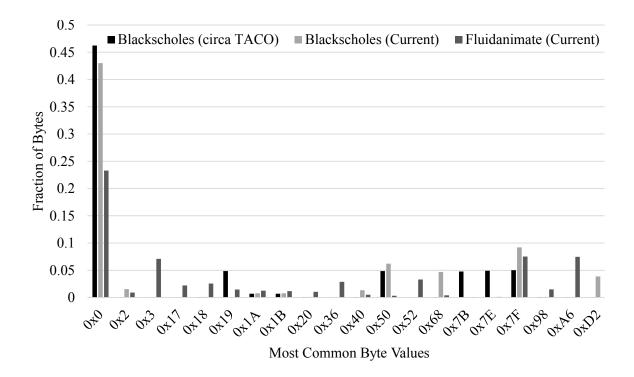

| 17 | Frequency of Byte Values in Contech Trace                                                                            | 68 |

| 18 | Simple Compression Algorithm                                                                                         | 69 |

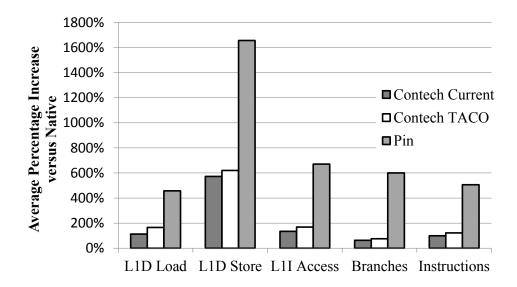

| 19 | Average Increase of Architectural Events over Uninstrumented Execution                                               | 73 |

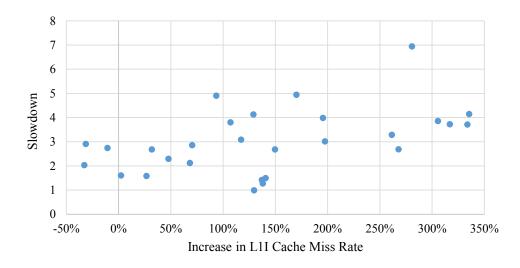

| 20 | Correlation between Runtime Slowdown and the Change in the L1I Cache Miss Rate                                       | 74 |

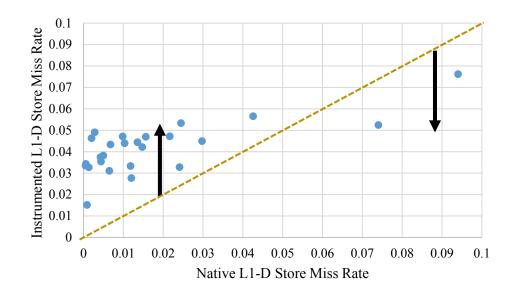

| 21 | Relationship between Native and Instrumented L1 D Cache Store Miss<br>Rates                                          | 76 |

| 22 | Size of Event List Generated from PARSEC and SPLASH with Different Inputs                                            | 77 |

| 23 | Runtime Slowdown of Contech Instrumented PARSEC and Splash 2 workloads by Varying the Number of Threads                                              | 78  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

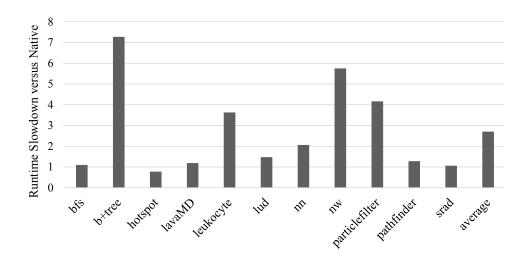

| 24 | Contech Instrumentation Performance on the Rodinia Benchmark Suite                                                                                   | 81  |

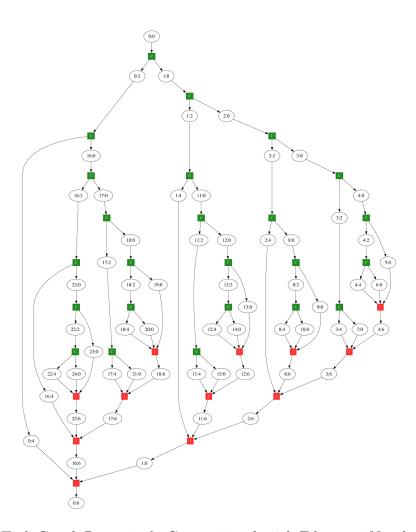

| 25 | Task Graph Recursively Computing the 6th Fibonacci Number usingCilk                                                                                  | 83  |

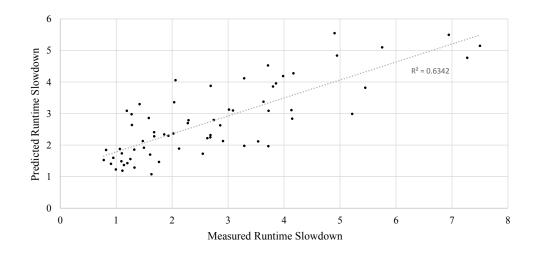

| 26 | Approximate Fitting of Runtime Slowdown based on Other Metrics .                                                                                     | 88  |

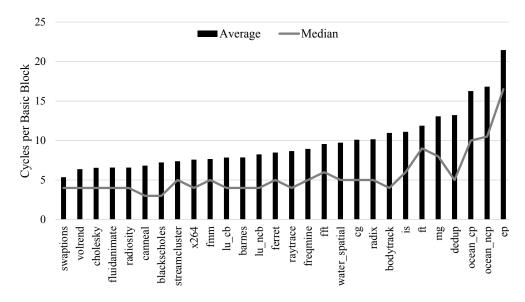

| 27 | Average and Median Basic Block Cycle Times                                                                                                           | 95  |

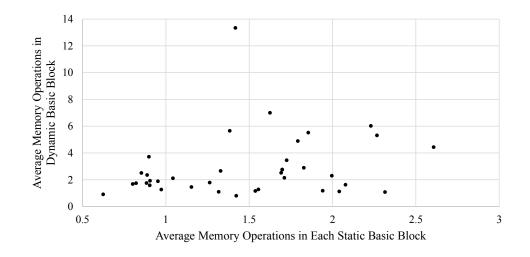

| 28 | Average Static versus Dynamic Memory Operations per Basic Block .                                                                                    | 96  |

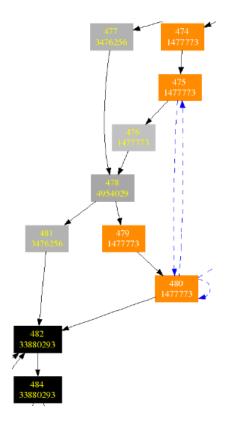

| 29 | Subset of Dynamic CFG from Fluidanimate (BBID and Execution Count)                                                                                   | 97  |

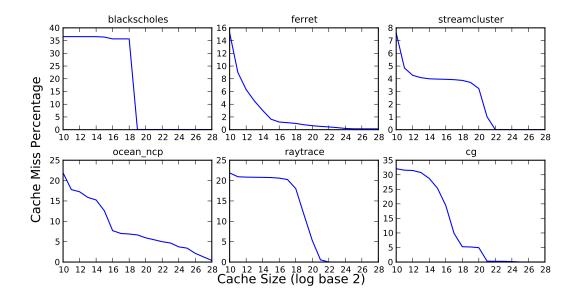

| 30 | Miss Rate for Selected PARSEC, SPLASH-2, and NAS benchmarks with 16 threads, across shared caches sized 1KB to 256MB $(2^{10} \text{ to } 2^{28})$   | 98  |

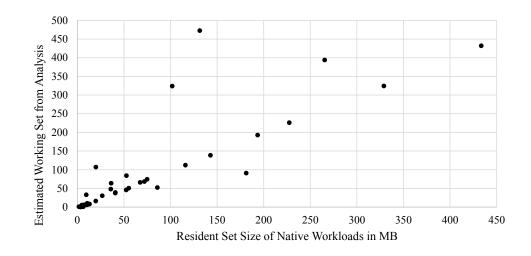

| 31 | Estimated Working Set versus Actual Resident Set Sizes for Uninstru-<br>mented Benchmarks in MB                                                      | 99  |

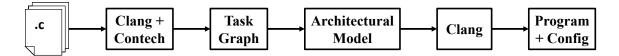

| 32 | Proposed Reconfigurable System Workflow                                                                                                              | 101 |

| 33 | Overlapping Reconfiguration and Synchronization                                                                                                      | 108 |

| 34 | Simulating Communication with Randomness                                                                                                             | 113 |

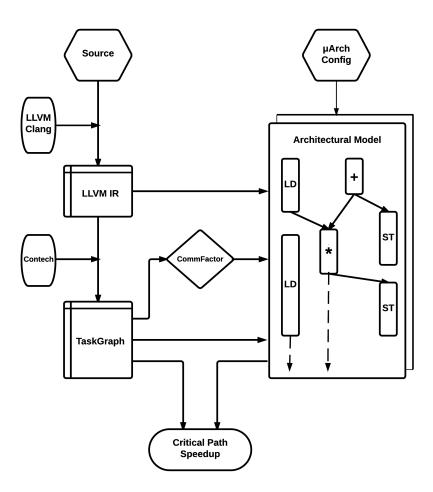

| 35 | Using task graphs to drive parallel program modeling and analysis                                                                                    | 115 |

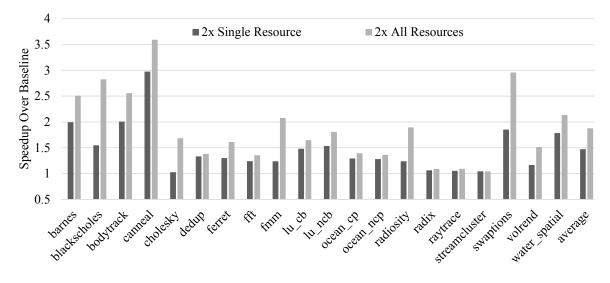

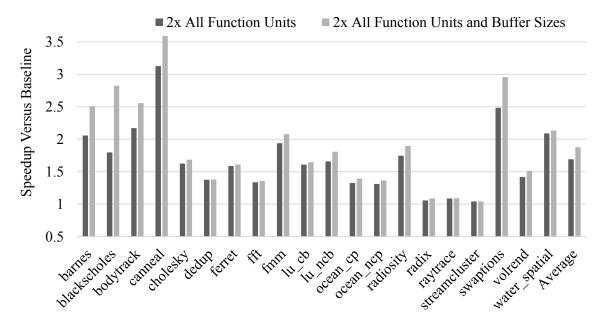

| 36 | Speedups of ROI in PARSEC Benchmarks                                                                                                                 | 118 |

| 37 | Speedups of ROI in PARSEC Benchmarks Accounting for Buffer Increases                                                                                 | 120 |

| 38 | Configuration Type Used in Accelerating the ROI in PARSEC Benchmarks (Green - Integer, Red - Floating Point, Blue - Memory, Black - Minimal Speedup) | 121 |

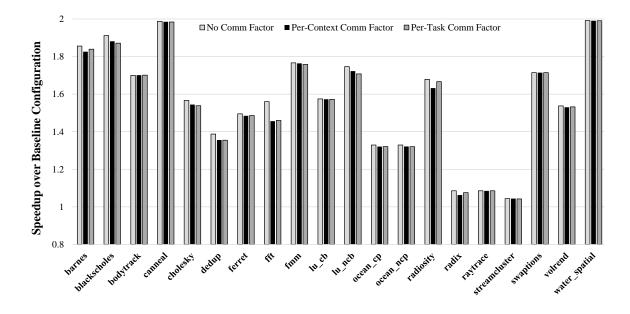

| 39 | Speedups from Varying Comm Factor Granularity in PARSEC Benchmarks (2X All Configuration) Using Earlier Architectural Model                          | 122 |

| 40 | Impact of Reconfiguration Latency (in cycles) on Speedup                                                                                             | 125 |

## SUMMARY

Computer architecture has looming challenges with finding program parallelism, process technology limits, and limited power budget. To navigate these challenges, a deeper understanding of parallel programs is required. I will discuss the task graph representation and how it enables programmers and compiler optimizations to understand and exploit dynamic aspects of the program.

I will present Contech, which is a high performance framework for generating dynamic task graphs from arbitrary parallel programs. The Contech framework supports a variety of languages and parallelization libraries, and has been tested on both x86 and ARM. I will demonstrate how this framework encompasses a diversity of program analyses, particularly by modeling a dynamically reconfigurable, heterogeneous multi-core processor.

# CHAPTER 1

# INTRODUCTION

Modern hardware is going through a paradigm shift. The solutions and techniques of the past decades are reaching physical limits. Already architectures are embracing parallelism to continue to provide improved performance. Many opportunities are looming ahead, such as 3D stacking, heterogeneous components, and dark silicon. Designing for these opportunities requires greater understanding of the software.

Software is ever increasing in size and complexity. To continue its development and improvement, programmers must understand their software. How does the software work with the compiler, hardware, operating system, and other programming libraries. To understand the software and how it is executing, tools and analyses are required. Without quality tools and analyses, software will not be able to fully utilize the resources provided, especially as the computing ecosystem continues to evolve and change.

Therefore, there is a continuing need of programmers, compilers and computer architects to understand modern parallel programs, and each in different ways [7]. The common approach has been to develop a targeted instrumentation and corresponding analysis for each particular need. In many circumstances, existing instrumentation frameworks have been available to assist in collecting the specific data about the program, mitigating some of the work to develop the instrumentation. While some

This work will demonstrate that a common representation, in the form of a task graph, can provide a unified platform for a diversity of parallel program analysis, while matching the performance overheads of more targeted approaches.

instrumentation is designed to have negligible overhead (e.g., using sampling), allowing these tools to be used with production systems, there is still a need for more detailed insight into parallel programs.

Some problems of analysis can be solved with simple tools and techniques, yet to encompass the great diversity of common analyses, more comprehensive approaches are required. The task graph representation is one such approach. By gathering the threading interactions of the software along with the trace of execution, a task graph can serve as a common representation upon which analysis tools can be developed.

Task graphs of various kinds are well established in the study of efficient scheduling of parallel tasks [76] [109] [120] [132], as well as evaluating future architectures [4] [42] and parallelizing applications [52]. Yet task graphs have been limited by the nature of their generation. In software, research has relied on programs being appropriately annotated or written in a task-oriented language. Even hardware-based approaches have assumed the programs have been extended to expose the "tasks". Task graph representations have generally been designed for targeted problems of scheduling, which necessitates extending the representation if the task graph is to be used to solve other complex problems.

## 1.1 Definitions

Task graphs will be described in detail in Chapter 2. The concept is that parallel programs are composed of sequential execution regions, called tasks. Tasks are delimited by operations that may affect the concurrency, such as exposing additional concurrency or coordinating between tasks.

Concurrent operations are those that may potentially operate simultaneously with other operations in a program or system. The architecture of the system, scheduling decisions, and other constraints then determine whether any two operations actually execute in parallel with each other. A task graph is expressing the actual concurrency exposed and thus potential parallelism of a program.

Parallel paradigms are different approaches to expressing the concurrency of a program. The approaches may be implemented through runtime or library APIs, compiler pragmas or extensions, or integral to the programming language.

Heterogeneous architectures are those whereby the processing elements of a single system differ in some aspect, such as the frequency or cache configuration. Heterogeneity can have both static and dynamic traits, for example, the ARM big.LITTLE [50] combines different processor cores (static) and dynamically enabling and frequency scaling the cores. Scheduling and modeling such a system will be analyzed in Chapter 6.

### 1.2 Future Challenges

Software development is being guided by the changes in computer architecture, whereby processor designs are constrained by their power and energy requirements. This constraint brings increasing focus on core counts and heterogeneity as ways for the hardware to continue to provide more performance. Software and programs are also burdened by their own success, whereby the designs and software architecture continue to grow, while layers of abstraction are introduced to aid the programmer. These burdens further distance the developer from the tools to leverage the changes in the hardware.

#### **1.2.1** Architectural Challenges

What are the architectural challenges of the near future? Even now, the presence of multicore chip designs has created difficulties for compilers and programmers to achieve the performance and stability expected of modern software. In focusing on increasing core counts, modern software does not yet have sufficient scaling to always use the cores available [41]. Simply increasing the core count will leave greater portions of the processor unused.

For the past several decades, the decreasing feature size of silicon has had similar decreases in power consumption; however, as the features increasing depart from classical mechanics and are subject to quantum effects, the savings in power are diminishing [41] [133]. Should the power consumed by the transistors exceed the thermal dissipation capability of the design, some of the transistors must be disabled at all times except in short bursts. This design would now have different on chip components that are enabled depending on the requirements of the executing code. Even switching to other cooling techniques cannot prevent the fundamental scaling problems of power dissipation.

Improvements in process technology have been shrinking the features in silicon; however, there is a looming limit in the size of features. Eventually, each feature would be the size of a single atom, at which point the transistor counts can only be increased by macro scaling, either larger dies or vertical stacking. There is always the possibility of changing materials, yet unless the fundamental architecture is changed the trends remain.

The above trends lead to increasing opportunity for die space to be devoted to different purposes, whether it be cores with a variety of computation power or specialized accelerators. In this heterogeneous space, how a program is designed to use the resources is of importance and requires more focused analyses.

#### **1.2.2** Programmer Challenges

Programmers must ensure the correctness of their code, while meeting the architectural challenges that are proliferating the number of cores. One increasingly common approach is the use of alternative programming languages that better address the costs and difficulties of modern programming. For example, Facebook recently adopted Haskell for better scalability in detecting spam messages [87]. Other groups have developed new languages, such as X10, Go, and Rust, or adopt different parallel paradigms, such as OpenMP or Cilk, in an effort to ease the burden on the programmer to meet these challenges. However, rewriting millions of lines of legacy code is rarely an option and therefore programmers also require improved support from tools.

Program correctness requires locks, barriers, and other forms of synchronization. Significant research has explored more efficient and scalable implementations both from software as well as hardware changes. Vallejo, et al. [118] provides a good summary of the various lock-based implementations available. It can be difficult for a programmer to make an informed decision as to the appropriate lock implementation based on the usage of the lock and the underlying architecture. Program scalability is further impacted due to coarse-grained locking, whereby a critical section protects more than is required for correctness. In many cases, it is possible to statically identify operations that do not require the critical section [11], and thereby reduce the size of the critical section. Furthermore, synchronization may also be split into finer-grained units to protect smaller sets of locations, thereby reducing contention when the different sets can be accessed independently.

By incorrectly reducing the critical sections and otherwise changing the synchronization, accesses to shared data may no longer be safely ordered and serialized, thereby introducing data races. Data races can be difficult to identify due to the diversity of synchronization in programs [116], as well as the impact of the memory model [73]. Changes to synchronization may also introduce deadlocks and other failing execution scenarios.

Programmers utilize the available abstractions in selecting algorithms and data structures during development to improve their productivity. These conventions may not be efficient from an architectural or compiler standpoint. One example is the use of data structures in a program. *Brainy* [69] showed that not only do programmers often chose a suboptimal data structure, but the optimality of the choice can depend on the architecture itself. This work was extended to also consider the parallel usage of the data structures [90].

### 1.3 Designing a New Tool

The general approach by programmers to understand and analyze a program follows repeated iterations across increasingly complex tools toward the specific problem of interest. The complexity of the tools requires greater time to collect as well as analyze the information from the program. This has lead to a significant diversity of analysis tools.

The original challenge presented three years ago was identifying the thread and communication relations to best exploit Manager Client Pairing (MCP) [17] [18], which is a hierarchical coherence compositional design. Without any immediate tool available to solve the problem, a new instrumentation tool or plug-in would be required. The minimum data necessary for this problem would be the memory accessed by the parallel program, as well as the thread ID or context of each access. This diversity of data required to support MCP leads the design of what would become Contech to collect additional data in order that the tool would be able to support many of the existing tools and analyses. Given the desire to support this diversity, Contech's design generates traces of the program's execution, so that multiple tools can analyze precisely the same events from that execution.

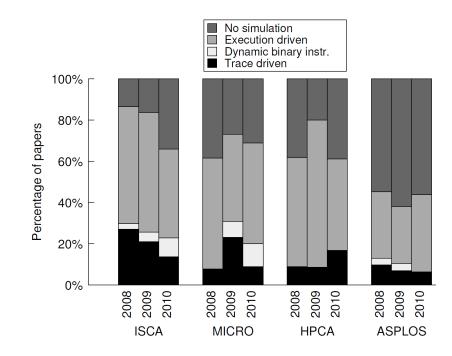

Figure 1, from Rico, et al. [102], illustrates the decreasing use of trace-driven models for computer architecture. Program traces have difficulties modeling parallel programs, due to the need to capture timing related aspects of execution such as lock ordering. Fitting with this trend, only 16% of papers in ISCA 2015 used traces. The

**Figure 1:** Different Simulation Types in Computer Architecture, (Figure 1 from Rico, et al. [102])

development of a new tracing tool would need to properly encapsulate the different timing aspects of parallel programs.

From interviews with parallel programmers [7], a regular concern with tools and debugging approaches is whether the techniques used to find the performance issue will introduce other phenomena (i.e., probe effects) that will mask the original issue. Therefore, any tool used to understand programs, especially parallel ones, must be designed with an awareness of the performance costs of its associated instrumentation.

# 1.4 Contributions

The contributions of this dissertation are three-fold:

• A novel, "Contech", task graph representation of parallel programs that supports independence of architecture, language, and threading paradigm. This representation splits synchronization tasks from work tasks, and includes the memory and execution trace.

- The design and implementation of a framework in the popular LLVM compiler infrastructure to efficiently generate the dynamic Contech task graph representation for arbitrary parallel programs.

- Demonstration of the comprehensive nature of the task graph representation by modeling the parallel programs on a parallel, reconfigurable architecture.

# 1.5 Organization

The remainder of the dissertation is organized as follows: Chapter 2 describes the task graph representation, Chapter 3 explores the different approaches taken to instrument and analyze programs, Chapter 4 demonstrates the Contech framework that collects and supports the analysis of task graphs. Chapter 5 will cover the analysis of task graphs, along with several sample tools. Chapter 6 presents a parallel reconfigurable architecture and shows how Contech task graphs can be used to model the architecture. Chapter 7 concludes the dissertation.

## CHAPTER 2

# TASK GRAPH REPRESENTATION

This chapter will present the theoretical underpinnings of the task graph representation that the Contech parallel program instrumentation and analysis framework uses. It will also discuss the basis and history of the task graph representation and how Contech's model differs from the prior work. These differences are what enables Contech task graph analysis to address a greater diversity of problems, as well as to encompass many parallel programs.

Parts of this chapter have been extended from the prior publication of Contech [100].

# 2.1 Extending from Prior Task Graphs

Contech is not the first work to propose task graphs for representing the parallel program and generate them from instrumented programs. However, prior approaches have been limited to specific languages and program structures, or required that programmers add annotations to their code so that a tool could construct a task graph. Nabbit [3] and Vandierendonck, et al. [120] both extend Cilk with annotations to identify tasks for scheduling, while Heumann, et al. [56] proposed similar annotations for Java to provide tasks with safety guarantees. Even hardware-based approaches to task scheduling have relied on programmer annotations made to C or C++ programs [42] [52] [76].

Adve, et al.[1] demonstrated a framework that can collect task graphs without any programmer annotations, when the program is written in High Performance Fortran (HPF). When they extended their work to more general programs, they relied on hand-generated task graphs, as they noted, "[we] manually wrote scripts to generate each of the task graphs" [2]. Thus they decided to focus their work on an interesting analysis of parallel programs rather than extending their prior framework.

Tareador [8] used Valgrind-based instrumentation to generate a (artificial) task graph for the program. This task graph is primarily a recording of the sequential execution of the program, with additional user-supplied annotations to identify the potential parallelism of the program. It is primarily designed to explore parallelism strategies before implementation.

While not generating a task graph, Varuna [109] identifies virtual tasks out of parallel programs, using existing parallelism APIs to identify when parallel work is created, and dynamically finds efficient schedules of the running programs. ParaOps [102] [103] has been used to encapsulate parallel operations in execution traces, to better support parallel simulation. Varuna and ParaOps, along with Contech, represent parallel operations via abstraction to either better schedule, simulate, or analyze parallel programs.

The following section describes the task graph representation, as based out of prior publications. These papers developed the representation for theoretic analysis of scheduling algorithms, where the programs had been abstracted as task graphs.

# 2.2 Parallel Program Representation

A parallel program can be represented as a set of tasks that may execute in parallel and interact via both actions and data dependencies. A task graph models the behavior and execution of a parallel program as a directed acyclic graph, where nodes are tasks and edges are the explicit dependencies between tasks, which gives the following expressions for a task graph:

$$G = (V, \vec{E}), \forall v \in V :< task >$$

$$\forall \vec{e} \in \vec{E} :< scheduling dependencies >$$

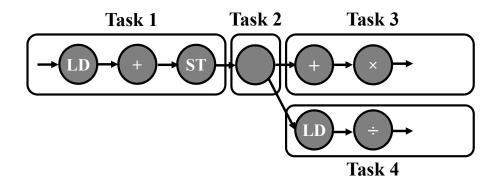

**Figure 2:** Aggregating a Computation Graph into Tasks (Work: 1, 3, and 4; Create: 2)

The focus of Contech has generally been on shared-memory programs; however, a distributed-memory program could be similarly represented where all memory accesses are mapped to disjoint sets of addresses and there exist send and receive actions that allow accesses between these sets [46], see also Section 4.9.

To derive a task graph, first begin with a program's execution, which is considered as a computation graph. In the computation graph, every node is an action, be it an instruction, basic block, function, or some other unit of execution. Some actions have additional explicit non-data dependencies on prior actions, and are termed *synchronization actions*. Programs may use these dependencies to enforce an order on its data dependencies. The actions are then aggregated together into tasks, thereby transforming a computation graph into a dynamic task graph. Figure 2 shows an aggregation of compute nodes into tasks.

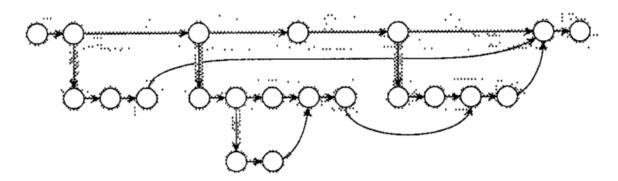

The task graphs representation was first used to analyze program scheduling by decomposing the program into tasks [21] [22] [46]. Figure 3 shows an example task graph from that work. In it, tasks are circles and there are three types of edges: horizontal - continue, vertical - spawn, and curved - data-dependency. Additional research extended task graphs with their potential interactions [84] and found subsets of the graph with no interaction and representing the subset as a single node [15].

Figure 3: Classic Task Graph, circa 1993 [22]

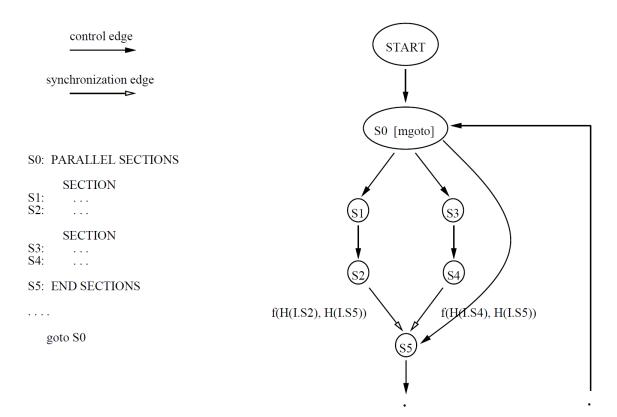

Parallel Program Graphs [107] is an extension of control flow graphs (CFGs), which adds a parallelism node and synchronization edges; however, it does not cleanly partition out other edge types controlling parallelism. Figure 4 provides one example of a Parallel Program Graph. Note how the synchronization edges (S2 to S5, and S4 to S5) are only conveying the ordering information. This graph also demonstrates its CFG origin with the backward edge and representing each statement as a separate node. Finally, node S5 is a generic node and does not have a special type, even though it represents the end of the parallel section.

A task is defined as containing either a sequence of actions taken without an intervening synchronization action, or the synchronization action itself, which is similar to Cilk's definition of a strand [83]. Tasks consisting of the former are identified as work tasks (task partition W), which may contain individual instructions, basic blocks, or entire functions. In practice, most tasks are sequences of basic blocks; however, a standard system function such as malloc is stored intact in a task, although other work have used different sequences [21] [22]. Tasks may also contain a set of data locations accessed.

# 2.3 Contech Task Graph

One extension of Contech task graphs from prior work is that tasks containing synchronizing actions are assigned into one of four partitions on the task graph: creates

#### **EXAMPLE OF PARALLEL SECTIONS (COBEGIN-COEND)**

Figure 4: Parallel Program Graph [107]

(C), joins (J), syncs (S) and barriers (B), which along with the fifth partition, work(W), cover all tasks in the graph. Each *synchronization action* can only map to a single partition type in the task graph. Thus the task graph formalism is extended:

C, J, S, B, W are partitions on V:<  $task\_type >$

These synchronization tasks define the topology of the task graph, and cleanly separate the synchronization from the useful work within the graph. Using these partitions, the task graph has one type of edge, and the cause of dependency edges is clear from the partitions of the tasks, whereas prior task graph representations either stored the cause as an action in the tasks or as different edge types. Thus the dependencies in the task graph are only those actions explicitly invoked by the program to order otherwise concurrently executing contexts. Unlike prior work, the dependencies between tasks are not associated with data being produced or consumed by the tasks. In practice, the particular mapping of parallelism functions to the partitions is left to tools that generate task graphs. For example, the end of an OpenMP parallel region has an implicit barrier followed by a joining of the parallel execution, which could be mapped to both a barrier and join or just a join task.

The following properties are expected of each partition regardless of the architectural details of the generating tool: Create tasks increase the possible parallelism in the task graph, commonly having an *out* degree greater than their *in* degree. Join tasks are the complement of creates, in that they reduce the possible parallelism in the task graph. Sync tasks capture actions that impose an order between tasks, but without changing the parallelism in the task graph. The sync task may encapsulate a semaphore or condition variable, where one task is waiting on another task's notification. Tasks in the sync partition can also represent lock acquires and releases. The particular mapping is again left to tools implementing the task graph definition and could capture other functionality. Barrier tasks are similar to sync tasks, except that the ordering requirement is all to all rather than one to one (e.g., lock) or one to many (e.g., condition variable). Together, the dependencies in a task graph establish a partial order between the tasks. While it may be possible to create a total order using additional annotations such as the start and end times of tasks, such an order would be an artifact of a particular execution.

The set of work tasks can also be partitioned into disjoint subsets, where each subset represents a *context*. This partitioning of work tasks can be constructed using information known for each execution action. The practical definition of a context depends on threading models, but in general such a subset in the task graph represents the implicit data dependencies that many architectures carry between work tasks via registers, stack locations, return values, et cetera. As such, tasks in a context are

Figure 5: Legend for Visualized Contech Task Graphs

expected to depend on prior tasks in the context and may not be able to execute in parallel with each other, even if there are no explicitly represented data dependencies.

The task graph only contains the program order of the actions in each task, which may differ from the order dictated by the architecture executing the program. This property of the task graph also holds for any data locations accessed by the task. Dependencies between these actions may restrict the set of possible reorderings that the compiler or hardware can exploit. As the task graph is independent of the architecture, it does not preserve the actual execution order, only the program order. These orderings, along with the dependencies from synchronizing actions, define possible orderings of the actions in a parallel program. A correct parallel program uses synchronizing actions to restrict the set of possible orderings to those that preserve the intended dependencies between memory writes and reads in different threads. In other words, the synchronization actions prevent data races.

Contech work tasks contain sequences of execution and memory actions. The Contech task graph also contains properties and annotations such as, a set of predecessor and successor tasks for each node, as well as start and end times. Being annotations, the start and end times are not used in constructing the task graph, and are only provided for certain analyses.

Figure 6: Contech Task Graph Features by Type

#### 2.4 Visualizing a Contech Task Graph

It is useful to visualize the elements of Contech task graphs. Figure 5 provides the legend for the subsequent figure. Tasks are uniquely labeled with a Task ID, which is the pair of <Context ID>:<Sequence ID>. The Context ID is a unique identifier for a context, akin to a thread ID. The Sequence ID is a monotonically increasing identifier in each context. Work tasks are represented by ovals, with their Task ID visible. Other task types have a Task ID, but are represented instead by their type. The edges in the graph are represented as arrows, with the direction of the arrow pointing towards the dependent task. Synchronization actions are black squares labeled with a single letter indicating the type. Note that while the implementation also assigns identifiers to these actions, they are not shown in the visualization. While these images are taken from actual task graphs, in our experience most parallel programs use thousands to millions of tasks during execution, which exceeds the capabilities of even a simple graphical visualization.

Figure 6 shows each of the task types from a task graph. The Create task (Figure 6.a) shows one task entering the create task and two tasks dependent on the create. The 1:0 shows that Context 1 has been created, and therefore Context 0 invoked the create. Join (Figure 6.b) has two tasks entering the join task, and one task (Context 0) continuing. Syncs (Figure 6.c) involve two tasks entering and leaving the sync, which represent the two chains of dependencies. One chain of dependencies follows the sync tasks, as each sync must occur after its predecessor, for example, a lock is acquired after being released. The second chain of dependencies reaching a sync task follows the context that executes that sync, whether it be an atomic, lock, or other construct. The final task graph feature, the barrier (Figure 6.d), involves many tasks entering and leaving. Tasks after the barrier are dependent on both their context's last task as well as the barrier task itself, although the former is known transitively via the latter.

# 2.5 Incorporating a Parallel Programming Model into the Task Graph Representation

The process of integrating a new parallel programming model is straightforward. Each construct within a parallel programming model must be mapped to the appropriate representation in a task graph. The construct is considered for how it affects the (potential) parallelism of the program: is it increased (create), decreased (join), or has the parallelism remained the same (sync / barrier). The intent of the programmer also influences classification; for instance, atomic instructions can be used for fine-grained concurrent access to shared locations and should therefore be represented explicitly as sync tasks rather than be contained within work tasks.

When a representation for a construct is established, the construct must be appropriately instrumented to record the necessary information to represent the task. For create and join tasks, this often requires identifying the contexts involved in the operation. Sync and barrier tasks are identified by the address of the dynamic instance of the construct. This instrumentation is at the core of the Contech framework.

Condition variables, part of the POSIX threads standard, provide a way for threads to signal both 1:1 and 1:many. The core design is centered on representing condition wait, which performs three operations: it unlocks the mutex, after some time the condition variable is signaled, and the mutex is reacquired. Each of the three operations is represented as a separate sync task performed on either the mutex or condition variable, with the mutex's or the condition variable's identifier (e.g., address) stored in their respective tasks.

OpenMP 3.0 introduced the *task* keyword, which was extended in 4.0 to add a *depend* keyword. As the OpenMP task increases the potential parallelism, it is first bracketed by Contech create and join tasks. Then each OpenMP task dependency provides an ordering constraint between separate tasks without changing the program's exposed parallelism, and each is therefore represented by a Contech sync task for the associated item. The constraint's identifier (e.g., address) are then used to link the dependencies together in the final task graph.

#### 2.6 Example Task Graphs

In its simplest, a task graph is a single task. This program can be as short as "Hello World" or a multi-day serial architectural simulation. Across this range of serial programs, the programs are without any parallelism actions, and so the aggregation from the computation graph will never encounter an action that should be in a separate task, which contrasts with the example in Figure 2.

The program's computation graph can be initially viewed as being aggregated as a single task. Parallel actions are then selected that are part of larger tasks. Each parallel action (P), in general, will split the task (T) containing it into three pieces: computational actions in T prior to P, P itself, and the computational actions in T following P. Specific parallel actions may introduce additional tasks. A create action is part of the three split tasks plus one additional task per created context. And a barrier action splits each waiting context and introduces the single barrier task as a common dependency.

In practice, parallel programs will either be dominated by syncs and barriers or creates and joins, based on the underlying programming paradigm. In pthreads and

Figure 7: Simple OpenMP Program as a Contech Task Graph

MPI, threads are explicitly managed, therefore the high cost of thread creation results in few creates. Concurrent access by the parallel program to its data is protected through syncs (mutexes, condition variables, et cetera) and barriers. With OpenMP and Cilk, the programs will instead decompose the problem into parallel components that are created through **#pragma omp parallel** or **cilk\_spawn**, which the parallelism runtime may map to different threads. Decomposing into finer granularity can then mitigate the need to use fine-grained synchronization. This analysis will be revisited in Section 5.2.

Figure 7 shows how a simple OpenMP program maps to a Contech Task Graph. From top to bottom, the parallel region creates two parallel contexts, which then execute up to the *single* directive. The contexts synchronize and one enters the region, while the other skips to the end of the region. The end of the *single* construct implies a barrier within this parallel region. The contexts continue executing, until they reach the end of the parallel region, where they wait at the implicit barrier and then join back into the serial execution. Note again that the implementation of the

Figure 8: Simple OpenMP Program Using OMP Tasks

instrumentation used to generate this Contech task graph represented the implicit barrier and join separately.

Figure 8 demonstrates how the OpenMP task construct is represented in Contech, along with conveying the dependency information between tasks. Context 3 creates two tasks (context 4 and 5) each with an input and an output dependency on the same variable. The dependencies are each represented with a sync task, as each (potentially) orders the execution of different contexts. In the example figure, the syncs surrounding work task 4:2 are the input and output dependencies to that task. The OpenMP task in context 5 syncs on context 4's output after work task 5:0.

#### 2.6.1 Why are syncs (i.e. non-work) a unique type of task

Prior work has generally treated non-sequential dependencies as separate edge types. For example, Blumofe, et al. [22] had three edge types: continuation, spawn, and data dependency. Parallel Program Graphs [107] used two edge types: control and sync. Yet the Contech task graph only uses one edge type. More importantly, Contech promotes syncs and barriers to be distinct types of nodes, rather than using types of edges. In principle, this decision begins with the underlying computation graph representation whereby a synchronization would be one or more actions in the graph. Beyond this underlying representation, this section will work through several cases where prior designs would have difficulties adequately supporting desired functionality.

In general, synchronizations form a continuous chain throughout the program, as each synchronization is ordered with respect to the one before and the one after it, such as atomic operations on a single memory location. From this primitive synchronization, programmers (and architects, parallelism libraries, et cetera) can build more complex forms of synchronization, such as locks, condition variables, or semaphores. Some complex types may have implicit orderings that overlap with the underlying ordering. For instance, consider a lock that alternates between *acquire* and *release*. *Release* will follow *acquire* in the same context, and therefore will have the context's ordering constraint. In contrast, the *acquire* after a *release* may cross between contexts and require the constraint explicitly. If only the latter were required, then an edge from the releasing task to the acquiring task would convey this same ordering. In such a case, the synchronization action itself could be placed before (for *acquire*) or after (for *release*) the work of the task itself. Initially, Contech's design attempted to do that and place the synchronization with the work.

Three problems limit the suitability of including synchronization with work: identifying syncs in the graph, representing non-lock types, and measuring the costs of syncs. Tasks with syncs could be identified by extra flags, special edge types or even the number of incoming / outgoing edges. Differentiating the diversity of syncs can be (and is) accomplished by including an enum with the task. However, non-lock types do not have the clear *acquire* and *release* that enables inclusion with work. Until now, the discussion of syncs has focused on locks; however, as initially noted, there are a variety of types built on atomic primitives. If the sync is not a lock, then there may be no implicit ordering and therefore the complete order should exist in the task graph. Thus, the synchronization event (*current*) has two edges: (*previous*  $\rightarrow$  *current*) and then (*current*  $\rightarrow$  *next*). If this generic synchronization was part of a work task with actions before and/or after it, then either the edge from *previous* must enter the middle of the task to correspond to the synchronization or the edge to *next* must exit from the middle of the task. Yet tasks should be treated like basic blocks, such that edges should only enter at the start of a task and exit at the end of a task. That being the case, then synchronizations become degenerate work tasks only containing the synchronization itself. Furthermore with synchronizations being discrete tasks representing a variety of potential coordination between tasks, the special case of locks is not treated separately by restricting its edges to the releaseacquire pair, and instead retaining the general representation of each node having a partial order (1 or more predecessors and 1 or more successors).

A key feature of modeling synchronization is being able to measure the various costs associated with any atomic operation, for example: how expensive is the operation? Is there contention? What effect does contention have? Therefore, each sync action needs, at minimum, the start and end time annotations. If the sync is part of work, then both the task and any syncs each have start and end time annotations. And each sync in the work would have the appearance of a task: having incoming / outgoing edges and start / end times. Alternatively, some prior work treated syncs as edges. A sync edge would still have time annotations, where the edge would be defined from not two but four times: a start time and end time for the first action and a start and end time for the second action. If the actions temporally overlap, then the edge exists at a time in between each start and end. If instead, the actions do not overlap, then the edge is after the first and before the second sync actions. A barrier is a common instance of all to all ordering between tasks. By representing the action as a single barrier task, rather than barriers per context, the edges in the graph pass through the single ordering point. This avoids creating a clique between the associated contexts.

# 2.7 Other Parallel Program Representations

Other parallel program representations had been developed. Some representations are formal in nature and support proving the properties of the parallel programs. Other representations are designed as a comprehensive programming interface to represent and then efficiently execute a parallel program. Contech's task graph is comparable to the former and is designed to encompass the latter. I will summarize several representations and frameworks not (currently) supported by Contech in this section.

#### 2.7.1 Communicating Sequential Processes

Communicating Sequential Processes (CSP) provides a description of the program's potential actions. This formalism describes the actions that every process in a program will or may take in each step of its execution. The representation is therefore closer to the computation graph that is the theoretic basis for the task graph, rather than the task graph itself. However, CSP includes language to hide parts of a process's actions, so this technique could be used to restrict the actions exposed by a process to just the actions required to describe the interactions between processes.

A Contech task graph could be described using CSP; however, given that these task graphs are traces of specific executions, individually they do not contain the nondeterminism that CSP captures. CSP could be used to unify a set of traces from a program's execution, although such an effort is far beyond this dissertation. In so far as it might be done, contexts are treated as processes that interact with each other through locks and other synchronization. These interacting elements are distinct processes in CSP, whereby a lock is a state machine alternating between the acquire and release events. After mapping more than one Contech task graph to a CSP description, further work would be required to show how the different descriptions could be merged through finding commonalities. Only by unifying a diversity of task graphs for a given parallel program would a CSP-based representation be then able to correspond to the static task graph (implicitly) within a parallel program.

#### 2.7.2 Concurrent Collections

Concurrent Collections (CnC) [74] consist of three types to govern the execution of a parallel program: computational steps, control, and data. Similar to other runtime parallelism libraries, it is expected that programs will identify the parallel constructs dynamically. Computational steps define possible high-level functions that can be applied to data. Control tags determine whether a computation should execute when its data is available. This design choice enables programs to define the data used by computation in simpler terms, and thereby enable the runtime to better partition the program's execution based on greater prior knowledge of its possible execution. For example, an image is partitioned into windows and passed through a series of classifiers, where each classifier will either decide reject or emit the control tag for the next classifier to process the corresponding window. Data elements are defined in a write-once manner, such that a computational step will input data elements and output other elements. This permits multiple computations to consume the same data element; however, it introduces the need to identify when an element will no longer be required by a computational and can be garbage collected.

A parallelism expert separately defines the architecture- / platform- specific runtime that will appropriately map the parallel constructs onto the hardware. One example mapping would be deciding between assigning executing computation steps to different hardware contexts, based on the number of units as well as the communication costs between them. A CnC-based program forms a directed acyclic graph that is generated dynamically from its execution, and the program (as well as its task graph) is generally constructed independent of the specific architecture. These traits are shared with Contech's task graph representation, and given these commonalities it would be a reasonable future step to extend Contech's instrumentation to support programs targeting CnC.

# 2.7.3 LogP

Part of analyzing parallel programs and parallel algorithms has been developing analytical models to estimate the runtime costs on different possible hardware. One classic model is LogP [35], which emphasized that data movement via the interconnection network can be a bottleneck at higher processor scalings. The model is based on four parameters: L - the latency of communication, o - the overhead or cost to send or receive a message, g - the minimum gap between consecutive messages, and P - the number of processors. The problem of modeling parallel programs analytically will be revisited in Section 6.1.1.

## 2.7.4 Legion

Legion is organized around logical regions [14], in which a set of objects are grouped and accessed through a set of permissions. Legion also utilizes *tasks*, which are a set of functionality that accesses regions. The runtime then manages these entities and schedules the *tasks* to preserve their ordering as well as the region permissions. In effect, a program using Legion is executing a task graph, where the dependencies are logical regions.

# 2.7.5 Galois

Efficient graph processing is becoming increasingly relevant as big data pervades computing. Graphs have notoriously bad locality and are often difficult to process efficiently, as their accesses do not fit the traditional dependence graph model [98]. Graph algorithms often rely on fine-grained computations applied to all nodes or edges in the graph. In order to support these efforts, Nguyen, et al. [95] proposed a general infrastructure for writing graph domain specific languages (DSLs).

## 2.7.6 X10

X10 [29] is a second generation language in the space of those intrinsically supporting partitioned global address spaces (PGAS), and is built on top of the Java language and runtime. This support is centered around a *place*, which is a virtual pairing of computational and memory resources, such that the actual mapping of *places* to physical resources may change during execution. Parallel execution is supported particularly through asynchronous statements, quoting:

[Asynchronous statements are expressed by the following:] async (P) S where P is a place expression and S is a statement. The statement async S is treated as shorthand for async(here) S, where here is a constant that stands for the place at which the activity is executing.

Other parallel programming support includes atomic blocks, which utilize **atomic** and rely on the runtime to select the best synchronization mechanism. X10 also provides guarantees that programs written using certain language features will not deadlock.

Altogether, I would expect that programs written in X10 could generate valid Contech task graphs to represent their execution. However, the instrumentation of virtual machine-based languages (such as, Java, C#, et cetera) as well as interpreted languages (such as Python, JavaScript, et cetera) is a problem beyond the scope of this dissertation. Given the current instrumentation tools available, it is possible to leverage them to collect the appropriate aspects of the parallel program's execution to generate the appropriate task graph.

# CHAPTER 3

# PROGRAM INSTRUMENTATION

There is a significant spectrum of program instrumentation. Each instance of instrumentation has costs from two components: the cost of the instrumentation and the frequency of the instrumentation's execution. Simple program instrumentation can answer questions such as how often was a routine executed or what was the largest value observed at a location.

Table 1 compares a variety of program analysis tools similar to Contech, which will separately be described in detail in Chapter 4. For each tool, I have provided the slowdown for the instrumentation as reported by its publication. Each tool potentially records three components: the dynamic control flow of the program, the memory accesses, and explicitly recording the parallel actions (creates, syncs, et cetera). Many tools only record partial information about the control flow such as the execution count of each basic block rather than the complete path, and are so denoted separately. These tools will be discussed in this chapter grouped by the framework each uses, rather than ordered by instrumentation features.

A major decision for any instrumentation approach is whether it should be sourceor binary-level. Source-level instrumentation can provide greater details about the program, information that is lost during the compilation process. Additionally, the instrumentation can be better integrated into the program itself. Binary instrumentation, in contrast, does not require the program to be recompiled. However, it may not be able to accurately identify every detail about the program. Thus, one is faced with the choice between ease of use and richness of analysis.

|                    |           | Control | Memory   | Parallel |               |

|--------------------|-----------|---------|----------|----------|---------------|

|                    | Slowdown  | Flow    | Accesses | Actions  | Reference     |

| Pin BBCount        | 2x-4x     | b       |          |          | [9] [108]     |

| Harmony            | 1.2x      | b       |          |          | [70]          |

| CAB Path Profiling | 1.4x-2.2x | Х       |          |          | [53]          |

| Pin Memory Trace   | 2x-8x     |         | х        |          | [9] [108]     |

| PEBIL              | 7.7x      |         | Х        |          | [80]          |

| MACPO              | 1.5x-6x   |         | х        |          | [101]         |

| ShadowReplica      | 2.7x      | Х       | Х        |          | [65]          |

| PiPA               | 5x        | х       | х        |          | [135] $[136]$ |

| Cilkview           | 2x-10x    | b       |          | Х        | [55]          |

| ParaMeter          | 3x-200x   | b       |          | Х        | [75]          |

| Peregrine          | 2x-35x    |         | Х        | Х        | [34] $[129]$  |

| Pin Task Graph     | 16x       | х       | х        | х        | [100]         |

| ParaOPs            | n/a       | х       | Х        | х        | [102] $[103]$ |

| Contech            | 1x-5x     | Х       | Х        | Х        | Chapter 4     |

**Table 1:** Instrumentation Tools with Similar Functionality to Contech (x - Support Present, b - Basic Block count without Full Path Information)

# 3.1 Reducing Instrumentation Overhead

In its simplest, program instrumentation is answering questions about the program's behavior. As the instrumentation is invoked more frequently or increases in complexity, the program's execution will be impacted by this overhead. Analysis tools effectively have three approaches to managing the overhead: optimizing the cost of each instrumentation event, reducing the quality or accuracy by removing specific instrumentation events, and reducing the frequency of all instrumentation events. For example, PiPA [135] is an instrumentation system focused on reducing the cost of the instrumentation events. In contrast, reducing the number of captured events is part of the approach of ShadowReplica [65], whereby it statically elides the instrumentation components that are identified as not required for the requested analysis. And PEBIL [80] is designed to switch in and out of executing instrumented code to reduce the cost of the instrumentation. Each of these instrumentation systems has taken a different approach to minimizing its overhead.

#### 3.1.1 Inlined Instrumentation

Inlining function calls is a longstanding technique to place the called code directly inline in the calling context. This removes the overhead of the function call, as well as providing opportunities to optimize the combined code. The technique is often used as part of the initial compilation of the code and many heuristics exist to balance the benefits of inlining with the cost of increased code size. With instrumentation, the routines are often simple, yet invoked from countless locations in the program. For example, Contech's instrumentation of memory accesses can be inlined at the cost of a single instruction.

#### 3.1.2 Sampling

One approach to mitigate instrumentation overhead is to only enable the instrumentation periodically. This approach can always improve (i.e. reduce) the overhead of existing instrumentation designs; however, this ease can result in some tool designs relying on sampling rather than a better instrumentation implementation. This design weakness can still be apparent if the instrumentation imposes some overhead when it is disabled, such as checks for enablement. Along with any periodicity of the instrumentation, the overall approach must incorporate appropriate statistical modeling to ensure that the actual program behavior is still being captured.

By minimizing the overhead, sampled tools can be used with production code, where the analysis can be running continuously to monitor for potential problems.

Arnold, et al. [6] studied periodic instrumentation and published two observations. If the instrumentation is enabled on a regular period, it may coincide with other periodic behavior in the program. Furthermore, if sampling only applies to a subset of the instrumentation, then care must also be taken to ensure that the non-instrumented regions do not count against the sampling period.

# 3.1.2.1 Perf / Oprofile

Rather than sampling complex instrumentation, a tool can also take samples of the current executing code in a program or running system (thus in the extreme, the sampled instrumentation is a record of every PC value of the program). By taking many profiles of a steady state, the tool can reconstruct the total amount of time spent in each region of code. This is a valuable approach to quickly observing a minimally impacted behavior of a program.

#### 3.1.2.2 SHIM

SHIM [131] provides a very low overhead sampling of various performance counters. This tool relies on two pieces of functionality: first, it is placed within a Java VM so that targeted software instrumentation can be added to the software, and second, the performance counters on an SMT system are unified so that any hardware context can access the counters for the core. SHIM introduces a second thread to each executing application thread that consistently polls the hardware counters for that core, as well as injected software counters. This allows the system to provide sampling rates in the 10s of cycles at around 60% overhead and down to 2% overhead at 1500 cycle rate. This approach is reliant on the free resources of another core and the ability to schedule the observer thread on this context.

#### 3.1.3 Mirroring Program

In many cases, the instrumentation required can result in the application executing orders of magnitude slower. Given the additional resources of multi-processor computers, it is possible to execute the instrumented and uninstrumented program in parallel. The design put forward by two simultaneous publications [91] [124] was to fork the program into two or more copies. The original program continues executing without instrumentation, while the copies are instrumented and run slower. Shadow Profiling [91] opts to fork periodically in order to provide samples of the original program without excessive impact. In contrast, SuperPin [124] repeatedly forks such that multiple slices of the program are executing the instrumentation, which provides results similar to executing the entire program under the instrumentation. In both cases, the authors note that there is limited support for forking multithreaded programs and the forked copies only retain a single thread from the original execution.

# 3.2 Source Instrumentation

To inject instrumentation into a program, one approach is to start with the source code and extend it with the appropriate routines. Generally, the compiler is required to be modified or extended to support the instrumentation. By instrumenting at the source code level, there is greater static knowledge available about the code, such as the actual types of variables and the program's control flow graph.

As the Contech front end relies on source-level instrumentation, I will describe several tools that do the same and establish how they influenced the design for Contech.

## 3.2.1 GProf

GProf [49] is an instrumentation tool integrated into the *gcc* compiler framework. It works by instrumenting function calls to record execution counts and path information. Path information is collected by recording the incoming arc when the instrumentation for a routine is triggered. It determines this arc by finding the return address, thereby identifying the caller routine. Primarily, GProf is used to identify the hot code in the program, and by incorporating path information it can also provide the context of the code and frequency of its invocation. A separate study found that this simple instrumentation incurs an average of 115% overhead on SPEC 2000 Int [45].

#### 3.2.2 ICECAP

Within the Microsoft Windows kernel, there is a function call instrumentation known as ICECAP [123]. This instrumentation records function calls and returns, along with spin locks, into per-processor buffers. Each record has an associated time stamp. As the buffers are per-processor, each record also has information to attribute which process / thread was executing given that interrupts and context switches may occur at any time. And as this is kernel instrumentation, the interrupts and context switch code will also be logged in the buffers. Furthermore, being source level instrumentation, it can be enabled and disabled on a per-source file basis. This allows the user (a kernel developer) to budget how the costs are spent: space required to record the events and slowdowns of the instrumented code.

When kernel components are recompiled with the instrumentation, they have inlined calls to the instrumentation routine. The first step of the routine is to check whether logging is enabled, thus most of the overhead is avoided until required. When in use, the kernel sets aside a region of memory that is split by processor. As it runs, each record advances the corresponding per-processor buffer pointer until the buffer is full (and consequently each processor in the trace may end at different times). Therefore, the instrumentation routine also checks whether there is space and then atomically (remember interrupts and context switches) reserves that space for the record.

After the instrumentation run finishes, a separate tool processes the buffers and reconstructs the functions involved using the debugging symbols. This output can be analyzed by other tools to determine lock usage, particularly the high contention / long critical sections; as well as understanding the common paths through the kernel. ICECAP complemented other approaches by being able to distinguish between whether expensive routines are being frequently invoked or doing significant work per call. ICECAP could also support logging other performance counters to relate architectural phenomena, such as cache misses or branch mispredicts, with the specific locations in the code. However, most of the analysis has been superseded by ETWbased tools [88].

#### 3.2.3 LLVM-Based Approaches

LLVM [79] is a compiler framework that provides a well-documented API for writing additional compiler passes. This lends the framework toward supporting compilerbased instrumentation.

#### 3.2.3.1 Harmony