## ENERGY-EFFICIENT AND SCA-RESISTANT CRYPTOGRAPHIC HARDWARE FOR IOT APPLICATIONS

A Dissertation Presented to The Academic Faculty

By

Arvind Singh

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Georgia Institute of Technology

Georgia Institute of Technology

August 2019

Copyright © Arvind Singh 2019

## ENERGY-EFFICIENT AND SCA-RESISTANT CRYPTOGRAPHIC HARDWARE FOR IOT APPLICATIONS

Approved by:

Dr. Saibal Mukhopadhyay, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Tushar Krishna School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Raheem Beyah School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Hyesoon Kim School of Computer Science *Georgia Institute of Technology*

Dr. Vivek De Circuits Research Lab Intel Labs

Date Approved: July 8, 2019

Look up at the stars and not down at your feet. Try to make sense of what you see, and wonder about what makes the universe exist. Be curious.

-Stephen Hawking

To my family.

#### ACKNOWLEDGEMENTS

I would like to express my most sincere gratitude towards my advisor, Professor Saibal Mukhopadhyay, for the support and encouragement he provided throughout my PhD. I'd like to thank him for believing in my abilities, even at times when my own confidence wavered. His persistent motivation and encouragement gave me strength to overcome difficulties, take up new challenges and to come up with innovative ideas, I will forever remain indebted to him. I could not have imagined having a better advisor and mentor for my Ph.D study, his advice on my research as well as on my career has been invaluable.

I'd also like to extend my thanks to dissertation committee members - Prof. Tushar Krishna, Prof. Raheem Beyah, Prof. Hyesoon Kim and Dr. Vivek De for their time, support, for their insightful comments and constructive feedback before and during the dissertation defence process which helped me a lot to improve the quality of my dissertation.

I am thankful to past members of the GREEN Lab, Dr. Amit Ranjan Trivedi, Dr. Boris Alexandrov, Dr. Sergio Carlo, Dr. Denny Lie, Dr. Wen Yueh, Dr. Khondker Z. Ahmed, Dr. Monodeep Kar, Dr. Jaeha Kung, Dr. Duckhwan Kim, Dr. Jong-HWan Ko, Dr. Md. Faisal Amir and Dr. Taesik Na, who mentored me and provided tremendous support to make PhD research less stressful and more fun. I'd especially like to thank Dr. Monodeep Kar for 3-long years of collaborative research and numerous discussions on multitude of research problems. I'd like to extend my sincere thanks to current members of GREEN Lab, Yun Long, Burhan, Chaitanya, Edward, Nikhil, Minah, Nihar, Priyabrata, Xueyuan, Nael, Arslan, Mandovi, Daehyun, who have been of immense help throughout the thesis work in countless ways, GREEN Lab wouldn't have been the same without them!

I'd like to acknowledge the support of my family, especially my parents who have raised me to be the person I am today. I would also like to thank my brothers Vinay and Amit and sister Kalpana for their love and support throughout the years and to my highschool teacher Mr. Manoj Dwivedi for his continued guidance, teachings and belief in me. Most importantly, I'd like to thank my wife, Pratima, who partners with me to tackle every challenge life throws my way, she is equally responsible for all of my achievements. I want to thank her for all the unconditional love, for helping me to see the bright side of things and being always by my side which gave me the confidence that no matter how challenging my goals become, I am capable of achieving them with my persistence and her unwavering faith in me.

## TABLE OF CONTENTS

| Acknow         | ledgme   | ents                                                 | v  |  |  |

|----------------|----------|------------------------------------------------------|----|--|--|

| List of Tables |          |                                                      |    |  |  |

| List of l      | Figures  | x                                                    | ٢V |  |  |

| Chapte         | r 1: Int | roduction                                            | 1  |  |  |

| 1.1            | Proble   | m Statement                                          | 3  |  |  |

| 1.2            | Organi   | zation of this Thesis                                | 4  |  |  |

| Chapte         | r 2: Bao | ckground                                             | 6  |  |  |

| 2.1            | Lightw   | veight Cryptography                                  | 6  |  |  |

| 2.2            | On-Ch    | ip Power Management                                  | 8  |  |  |

|                | 2.2.1    | Fully Integrated Inductive Voltage Regulators (FIVR) | 9  |  |  |

|                | 2.2.2    | All-Digital Low Dropout Regulators (DLDO             | 10 |  |  |

| 2.3            | Adapti   | ve Clocking                                          | 1  |  |  |

| 2.4            | Side C   | hannel Attack and Countermeasures                    | 12 |  |  |

|                | 2.4.1    | Power & EM based Side Channels and Countermeasures 1 | 12 |  |  |

|                | 2.4.2    | Fault based Side Channels and Countermeasures        | 17 |  |  |

| Chapte         | r 3: Sid | e Channel Leakage Characterization                   | 20 |  |  |

| 3.1                  | Measu                                                         | rement Methodology                                        | 20                                                                                             |

|----------------------|---------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------|

|                      | 3.1.1                                                         | Measurement of Power Signatures                           | 20                                                                                             |

|                      | 3.1.2                                                         | Measurement of EM Signatures                              | 20                                                                                             |

| 3.2                  | Statisti                                                      | cal Methods                                               | 22                                                                                             |

|                      | 3.2.1                                                         | Signal to Noise Ratio (SNR)                               | 22                                                                                             |

|                      | 3.2.2                                                         | Correlation Power/EM Analysis (CPA/CEMA)                  | 22                                                                                             |

|                      | 3.2.3                                                         | Test Vector Leakage Assessment (TVLA)                     | 24                                                                                             |

| 3.3                  | Archit                                                        | ecture of Encryption Engines                              | 25                                                                                             |

|                      | 3.3.1                                                         | Architecture of 128-bit AES Engines                       | 25                                                                                             |

|                      | 3.3.2                                                         | Architecture of 128-bit SIMON Engine                      | 26                                                                                             |

|                      | 3.3.3                                                         | Threat Model                                              | 28                                                                                             |

|                      |                                                               |                                                           |                                                                                                |

| Chapte               | r 4: En                                                       | ergy-Efficient and SCA-Resistant Lightweight Cryptography | 30                                                                                             |

| <b>Chapte</b><br>4.1 |                                                               | ergy-Efficient and SCA-Resistant Lightweight Cryptography |                                                                                                |

| -                    |                                                               |                                                           | 34                                                                                             |

| -                    | Energy                                                        | ASIC Implementations of SIMON128 Block Cipher             | 34<br>34                                                                                       |

| -                    | Energy<br>4.1.1<br>4.1.2                                      | ASIC Implementations of SIMON128 Block Cipher             | 34<br>34<br>42                                                                                 |

| 4.1                  | Energy<br>4.1.1<br>4.1.2                                      | ASIC Implementations of SIMON128 Block Cipher             | <ul> <li>34</li> <li>34</li> <li>42</li> <li>43</li> </ul>                                     |

| 4.1                  | Energy<br>4.1.1<br>4.1.2<br>Side C                            | ASIC Implementations of SIMON128 Block Cipher             | <ul> <li>34</li> <li>34</li> <li>42</li> <li>43</li> <li>43</li> </ul>                         |

| 4.1                  | Energy<br>4.1.1<br>4.1.2<br>Side C<br>4.2.1                   | ASIC Implementations of SIMON128 Block Cipher             | <ul> <li>34</li> <li>34</li> <li>42</li> <li>43</li> <li>43</li> <li>44</li> </ul>             |

| 4.1                  | Energy<br>4.1.1<br>4.1.2<br>Side C<br>4.2.1<br>4.2.2          | ASIC Implementations of SIMON128 Block Cipher             | <ul> <li>34</li> <li>34</li> <li>42</li> <li>43</li> <li>43</li> <li>44</li> <li>44</li> </ul> |

| 4.1                  | Energy<br>4.1.1<br>4.1.2<br>Side C<br>4.2.1<br>4.2.2<br>4.2.3 | ASIC Implementations of SIMON128 Block Cipher             | <ul> <li>34</li> <li>34</li> <li>42</li> <li>43</li> <li>43</li> <li>44</li> <li>44</li> </ul> |

| 4.4    | Applic  | ation of SIMON-128 to an Image Sensor Node                              | 53 |

|--------|---------|-------------------------------------------------------------------------|----|

|        | 4.4.1   | Baseline Image Sensor Node                                              | 54 |

|        | 4.4.2   | Overhead Comparison                                                     | 54 |

| 4.5    | Summ    | ary                                                                     | 58 |

| Chapte | r 5: Im | proved SCA Resistance with Random Fast Voltage Dithering                | 59 |

| 5.1    | Systen  | n Overview                                                              | 62 |

|        | 5.1.1   | Advanced Encryption Standard (AES) Designs                              | 63 |

|        | 5.1.2   | Integrated Inductive Voltage Regulator (IVR)                            | 63 |

|        | 5.1.3   | All-Digital Clock Modulation (ADCM)                                     | 63 |

| 5.2    | Basic ] | Random Fast Voltage Dithering (B-RFVD)                                  | 64 |

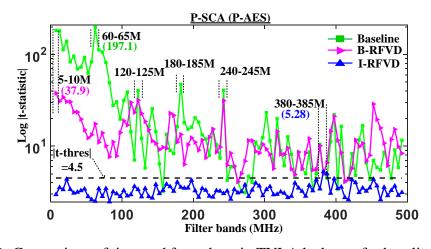

|        | 5.2.1   | Impact of B-RFVD on SCA                                                 | 66 |

| 5.3    | Improv  | ved Random Fast Voltage Dithering (I-RFVD)                              | 67 |

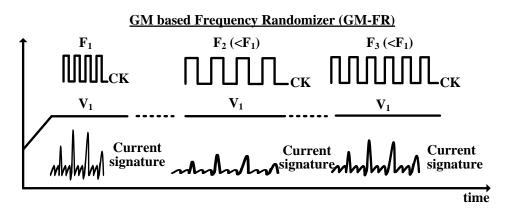

|        | 5.3.1   | Impact of Global-Modulator based Frequency Randomization (GM-FR) on SCA | 68 |

|        | 5.3.2   | Impact of IVR Loop Randomizer (IVR-LR) on SCA                           | 69 |

| 5.4    | Measu   | rement Setup and SCA Methods                                            | 69 |

|        | 5.4.1   | Acquisition of Power Signatures                                         | 70 |

|        | 5.4.2   | Acquisition of EM Signatures                                            | 70 |

|        | 5.4.3   | Measurement Conditions                                                  | 70 |

|        | 5.4.4   | Side Channel Analysis (SCA) Methods                                     | 71 |

|        | 5.4.5   | Postprocessing and Alignment Techniques                                 | 72 |

| 5.5    | Measu   | red Results: Power Side Channel Analysis (P-SCA)                        | 75 |

|        | 5.5.1   | Parallel AES (P-AES)                                                    | 75 |

|        | 5.5.2    | Serial AES (S-AES)                                                | 80  |

|--------|----------|-------------------------------------------------------------------|-----|

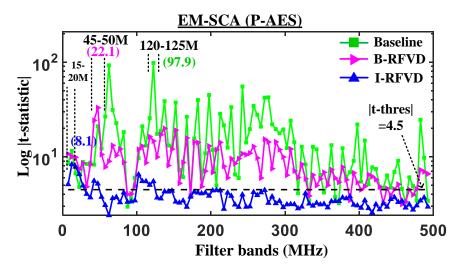

| 5.6    | Measu    | red Results: EM Side Channel Analysis (EM-SCA)                    | 83  |

|        | 5.6.1    | Test Vector Leakage Assessment (TVLA)                             | 83  |

|        | 5.6.2    | Correlation EM Analysis (CEMA)                                    | 84  |

|        | 5.6.3    | Comparison of P-SCA and EM-SCA                                    | 86  |

|        | 5.6.4    | Overheads of the Proposed Scheme                                  | 87  |

|        | 5.6.5    | Discussion                                                        | 88  |

| 5.7    | Summ     | ary                                                               | 90  |

| Chapte | r 6: Fai | ult Attack Mitigation with All-digital Clock Modulation Circuit . | 91  |

| 6.1    | Systen   | n Overview and Implementation                                     | 91  |

| 6.2    | Experi   | mental Setup                                                      | 93  |

| 6.3    | Measu    | red Results                                                       | 95  |

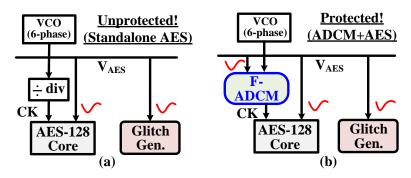

|        | 6.3.1    | Fault Injection and Analysis for Standalone AES                   | 95  |

|        | 6.3.2    | Fault Mitigation with ADCM (Protected AES Mode)                   | 98  |

|        | 6.3.3    | Discussion                                                        | 101 |

| 6.4    | Summ     | ary                                                               | 102 |

| Chapte | r 7: Lig | htweight SCA Countermeasures Utilizing Integrated Digital LDO     | 103 |

| 7.1    | System   | n Architecture                                                    | 105 |

|        | 7.1.1    | Design of Encryption Engines                                      | 105 |

|        | 7.1.2    | Design of Digital LDO                                             | 105 |

|        | 7.1.3    | Transformations via Digital LDO                                   | 106 |

| 7.2    | Propos   | sed Circuit Techniques                                            | 109 |

|        | 7.2.1   | Switching Noise Injection (SNI)                                                     |

|--------|---------|-------------------------------------------------------------------------------------|

|        | 7.2.2   | All-digital Clock Modulation (ADCM) Circuit                                         |

|        | 7.2.3   | Random VREF Generator (R-VREF)                                                      |

| 7.3    |         | ation Study for Impact of Digital LDO on Side Channel Leakage<br>Encryption Engines |

|        | 7.3.1   | Simulation Framework                                                                |

|        | 7.3.2   | SCA for Standalone P-AES                                                            |

|        | 7.3.3   | Impact of Digital LDO                                                               |

| 7.4    | Experi  | imental Setup and SCA Methodology                                                   |

|        | 7.4.1   | Measurement Scenarios                                                               |

|        | 7.4.2   | SCA Methodology                                                                     |

|        | 7.4.3   | Postprocessing of Measured Traces                                                   |

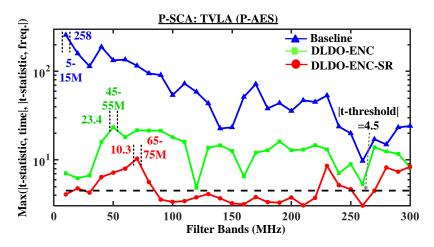

| 7.5    | Measu   | ared SCA Results: Power and EM SCA                                                  |

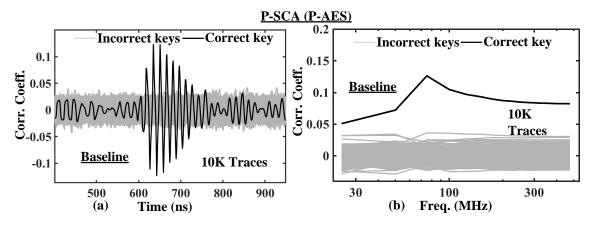

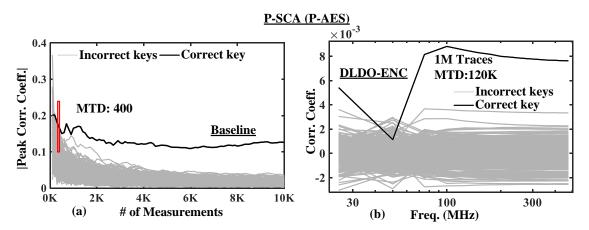

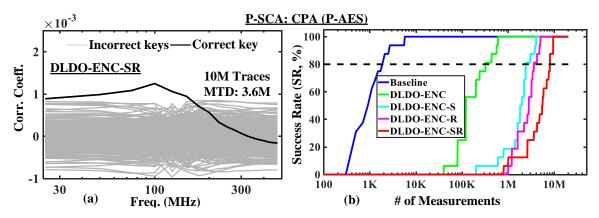

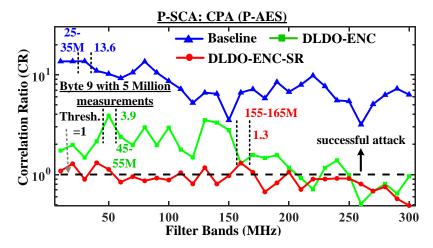

|        | 7.5.1   | Power Side Channel Analysis (P-SCA) on P-AES                                        |

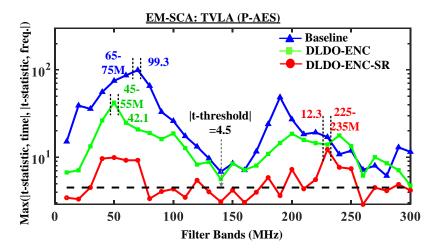

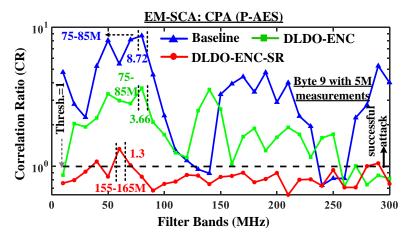

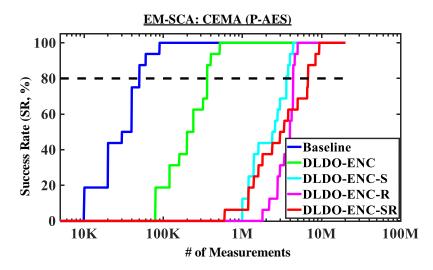

|        | 7.5.2   | EM Side Channel Analysis (EM-SCA) for P-AES                                         |

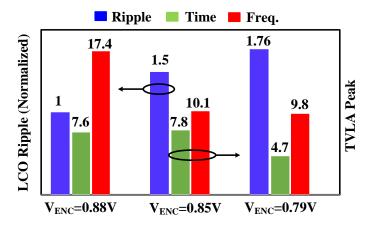

|        | 7.5.3   | Role of Limit Cycle Oscillations (LCO)                                              |

|        | 7.5.4   | Power Injection Attack (PIA)                                                        |

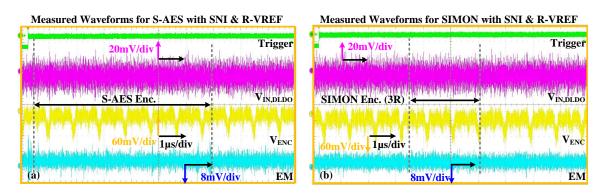

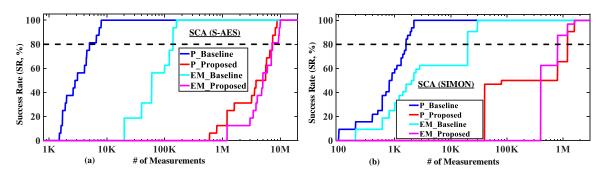

|        | 7.5.5   | Power and EM SCA on S-AES and SIMON                                                 |

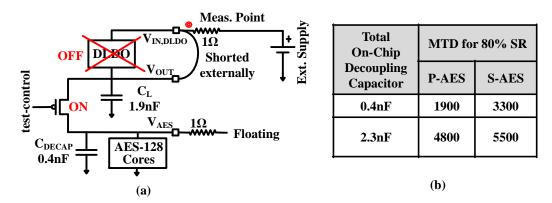

|        | 7.5.6   | Overhead Analysis for the Proposed Countermeasure                                   |

|        | 7.5.7   | Discussion                                                                          |

| 7.6    | Summ    | ary                                                                                 |

| Chapte | r 8: Co | nclusion and Future Work                                                            |

| 8.1    | Disser  | tation Summary                                                                      |

| 8.2     | Future   | Directions                                                      |

|---------|----------|-----------------------------------------------------------------|

|         | 8.2.1    | Energy, Security and Performance Tradeoffs                      |

|         | 8.2.2    | Compute Complexity and Ideas to Improve Proposed Techniques 147 |

|         | 8.2.3    | Advanced Power Models and Attack Methods                        |

|         | 8.2.4    | Application to Other Cryptographic Algorithms                   |

| Append  | lix A: A | Abbreviations                                                   |

| Referer | nces .   |                                                                 |

## LIST OF TABLES

| 2.1 | Area and Performance overhead comparison for some of the popular coun-<br>termeasures at different levels of hardware design                                                                                                                                         | 14 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Comparison of side channel analysis attack resistance offered by power management and low power techniques.                                                                                                                                                          | 16 |

| 4.1 | Comparing area, performance, power and energy consumption for bitserial, parallel and round unrolled datapath architectures for SIMON128 from designs synthesized in NanGate FreePDK15 technology.                                                                   | 40 |

| 4.2 | Comparison of SIMON128 architectures from this work with state-of-the-<br>art lightweight ciphers and traditional AES128 architectures implemented<br>on ASIC                                                                                                        | 41 |

| 4.3 | Comparing area, performance, power and energy consumption for bitserial, parallel and round unrolled datapath architectures for SIMON128 from designs programmed on Sakura-G FPGA (Spartan 6, 45nm process).                                                         | 42 |

| 4.4 | Comparison of different datapath architectures for lightweight cipher SI-<br>MON128 and state-of-the-art AES128 encryption scheme                                                                                                                                    | 52 |

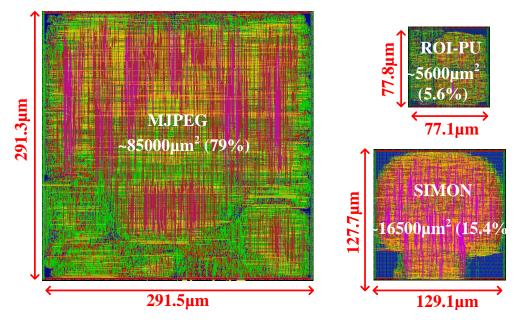

| 4.5 | Physical implementation details for high-performance image sensor node<br>with side-channel secure communication with NCSU FreePDK 15nm tech-<br>nology libraries - summary of area and power consumption for individual<br>blocks after synthesis and place & route | 56 |

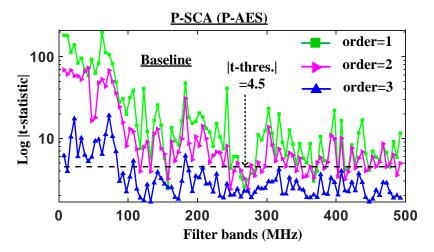

| 5.1 | Summary of higher order TVLA analysis for P-AES with baseline, B-RFVD and I-RFVD systems.                                                                                                                                                                            | 78 |

| 5.2 | Comparison of high order TVLA leakages for order=1, 2, 3 for baseline, B-RFVD, and I-RFVD systems for S-AES.                                                                                                                                                         | 81 |

| 5.3 | Summary of all measured results for P-AES and S-AES with respect to power/EM analysis                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------|

| 5.4 | Comparison of proposed I-RFVD scheme with existing countermeasures 88                                                      |

| 6.1 | Summary of testchip with respect to S-AES, ADCM, VCO circuits 95                                                           |

| 6.2 | Summary of testchip with respect to S-AES, ADCM, VCO circuits 96                                                           |

| 7.1 | Configurations of Digital LDO analyzed with respect to their impact on SCA leakage for P-AES                               |

| 7.2 | Comparison of DLDO bandwidth and stability margins with SCA leakage for different values of controller parameter(s)        |

| 7.3 | Comparison of different configurations with respect to TVLA leakage 127                                                    |

| 7.4 | TVLA leakage analysis under power injection attacks at $V_{IN,DLDO}$ and $V_{CTRL}$ .134                                   |

| 7.5 | Summary of CPA/CEMA attacks for AES cores for different systems with respect to MTD for 80% SR                             |

| 7.6 | Summary of improvement in SCA resistance (with respect to MTD for 80% SR) for AES & SIMON with the proposed countermeasure |

| 7.7 | Comparison with prior works on circuit based SCA countermeasures 139                                                       |

# LIST OF FIGURES

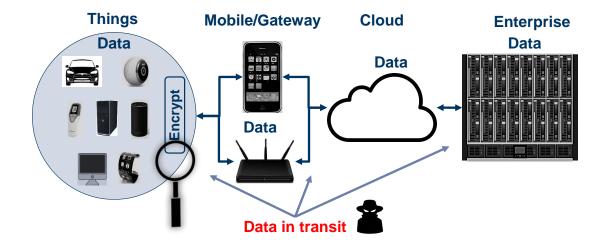

| 2.1 | Security threats of the interconnected world where security (in terms of security protocols and defenses against physical attacks) must be the first priority and not optional.                                                                                                      | 6  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

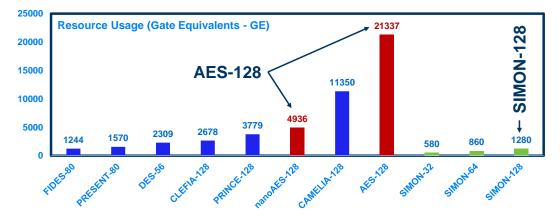

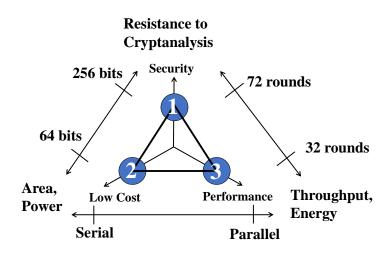

| 2.2 | SIMON provides much higher flexibility when choosing an encryption al-<br>gorithm for a target IoT application with respect to security parameters and<br>with its resource-efficiency compared to other lightweight ciphers as well<br>as compact implementations of AES algorithm. | 7  |

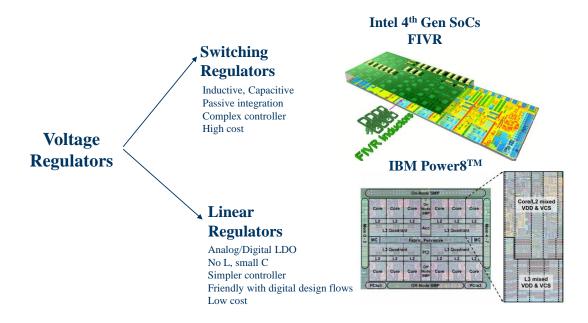

| 2.3 | Categorization of different types of integrated voltage regulators used in modern power management systems.                                                                                                                                                                          | 9  |

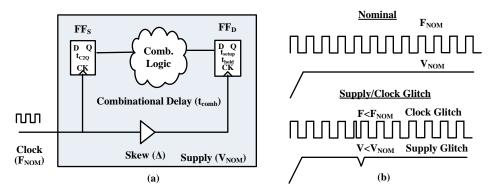

| 2.4 | <ul><li>(a) Timing properties of a digital circuit depend on supply and clock and</li><li>(b) may fail when supply/clock based glitch is injected</li></ul>                                                                                                                          | 18 |

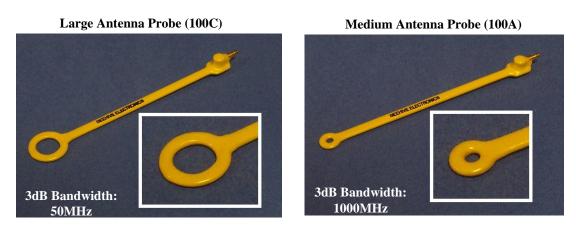

| 3.1 | Two different EMC probes from Beehive Electronics [98] with different loop area are used in our experiments.                                                                                                                                                                         | 21 |

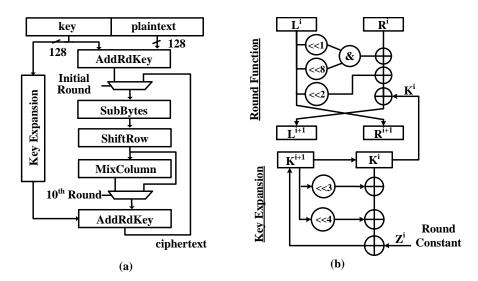

| 3.2 | Cryptographic algorithms employed in this paper to evaluate improvement<br>in SCA resistance: (a) 128-bit AES algorithm and (b) 128-bit SIMON al-<br>gorithm.                                                                                                                        | 25 |

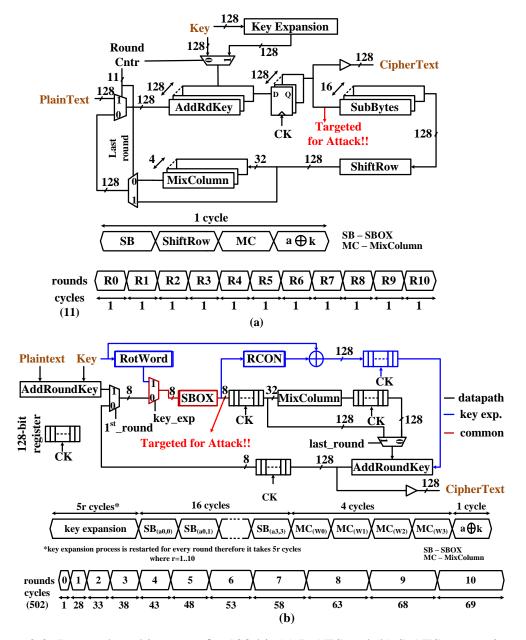

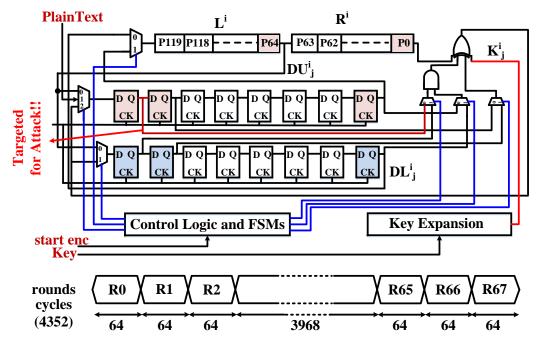

| 3.3 | Datapath architectures for 128-bit (a) P-AES and (b) S-AES encryption cores.                                                                                                                                                                                                         | 27 |

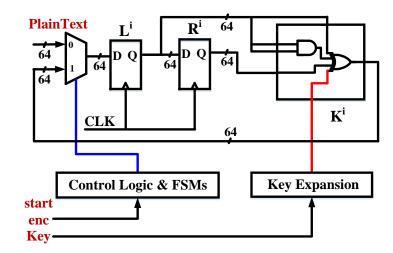

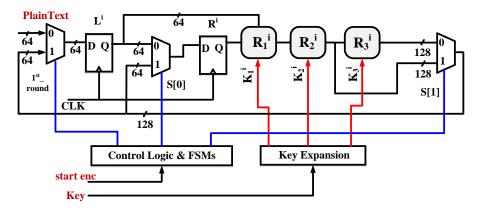

| 3.4 | Datapath architecture for 128-bit SIMON encryption core                                                                                                                                                                                                                              | 28 |

| 4.1 | Available algorithmic/architectural design space for SIMON enabling flex-<br>ible tunable security for based on application requirements                                                                                                                                             | 31 |

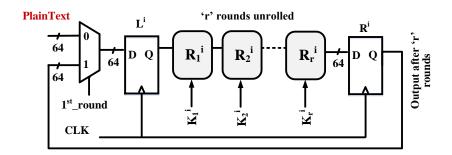

| 4.2 | Unrolled architectures for lightweight cryptographic algorithms provide<br>optimal energy at very high performance while simultaneously improving<br>resistance against power side channel analysis attacks                                                                          | 33 |

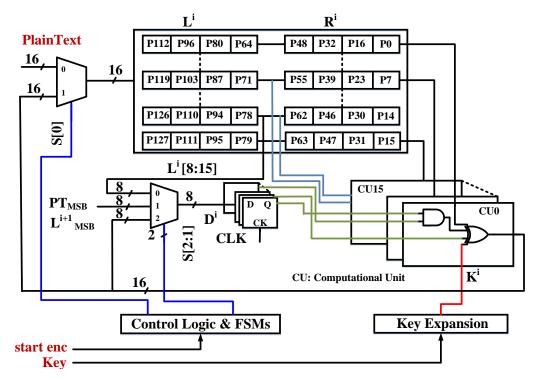

| 4.3  | 16-bit parallel datapath architecture for SIMON128                                                                                                                                                                                                                                       | 36 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.4  | 64-bit parallel datapath for SIMON                                                                                                                                                                                                                                                       | 38 |

| 4.5  | 3-round unrolled datapath architecture for SIMON128. It is the most energy optimal implementation with respect to ASIC implementations of all dapapaths for SIMON128.                                                                                                                    | 39 |

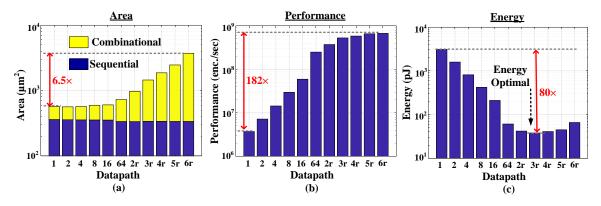

| 4.6  | Design tradeoffs for different hardware architectures for SIMON128 with respect to ASIC implementations, (a) area, (b) performance and (c) energy. 3-round unrolled datapath gives the optimal energy while offering very good performance.                                              | 40 |

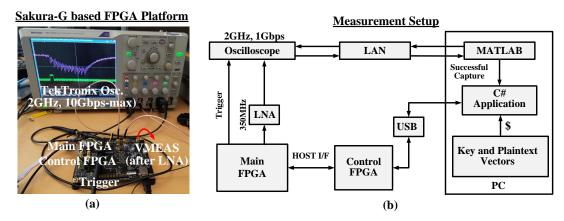

| 4.7  | (a) Sakura-G based side channel leakage characterization platform and (b) measurement setup details.                                                                                                                                                                                     | 43 |

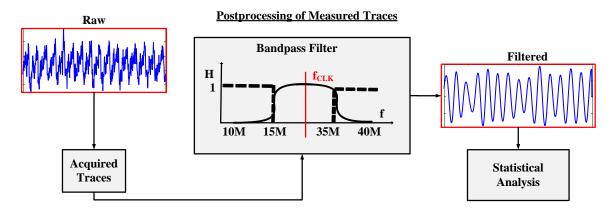

| 4.8  | Postprocessing of measured power traces with band pass filter to remove out-of-band noise                                                                                                                                                                                                | 44 |

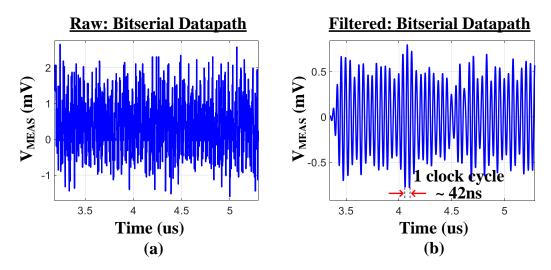

| 4.9  | Measured power traces for bitserial datapath, (a) raw power trace, (b) fil-<br>tered power trace                                                                                                                                                                                         | 45 |

| 4.10 | Measured power traces for 64-bit datapath architecture (a) raw power trace<br>and (b) filtered power trace. Raw signatures show significant voltage varia-<br>tions during round operation for 64-bit datapath as all bits are computed in<br>parallel.                                  | 45 |

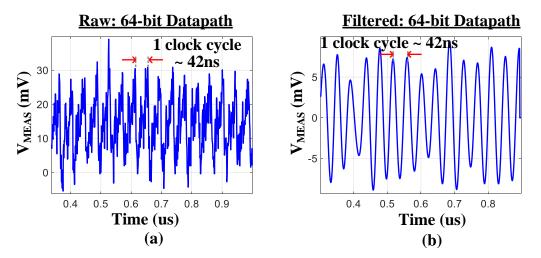

| 4.11 | (a) Intermediate state after completion of 2 rounds, $L^3$ , is targeted for attack and (b) key dependency paths for $L^3$ .                                                                                                                                                             | 46 |

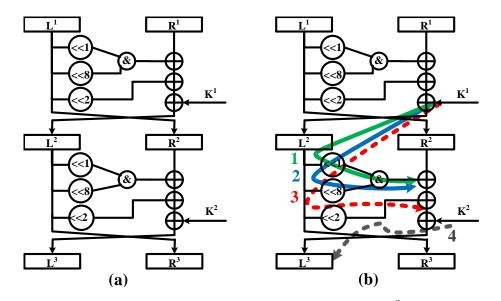

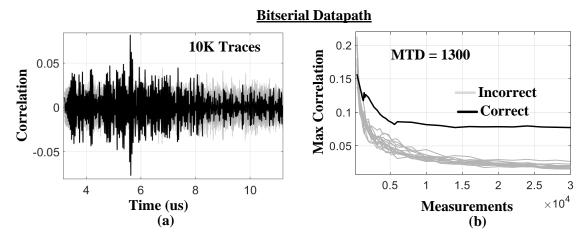

| 4.12 | Successful attacks for bitserial datapath architecture: (a) correlation vs time plot shows successful attack with 10,000 measurements and (b) MTD vs number of measurements plot shows MTD of 1300                                                                                       | 47 |

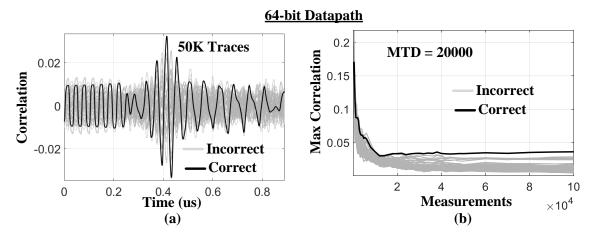

| 4.13 | Successful attacks for 64-bit parallel datapath architecture: (a) correlation vs time plot shows successful attack with 10,000 measurements and (b) MTD vs number of measurements plot shows MTD of 20,000 indicating an improvement of $15 \times$ over bitserial datapath architecture | 48 |

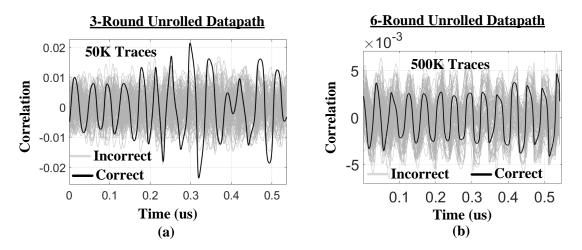

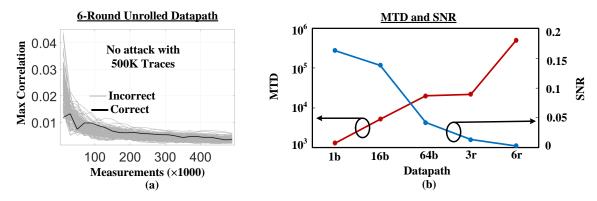

| 4.14 | Correlation power analysis attack for round unrolled datapath with increas-<br>ing degree of unrolling: (a) successful CPA for 3-round unrolled datapath,<br>(b) no CPA attack observed for 6-round unrolled datapath even with 500K<br>measurements                                     | 51 |

| 4.15 | Correlation power analysis attack for round unrolled datapath with increas-<br>ing degree of unrolling, (a) max correlation vs number of measurements<br>for 6-round unrolled datapath and (b) MTD and SNR plotted for different<br>datapath architectures. SNR decreases as the datapath width and degree of<br>unrolling is increased. Similar trend is seen for MTD with no CPA attack<br>for 6-round unrolled datapath indicating an increase of at least $384 \times$ with |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | respect to bitserial datapath                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52 |

| 4.16 | The IoT environment with IoT cloud and edge devices. An edge device with encryption engine transmits secure data to the IoT cloud                                                                                                                                                                                                                                                                                                                                               | 53 |

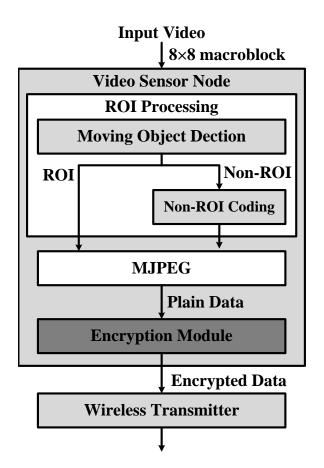

| 4.17 | Block diagram of the image sensor node                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55 |

| 4.18 | Physical implementation details for high-performance image sensor node with side-channel secure communication with NCSU FreePDK 15nm technology libraries- placed and routed layout of individual blocks (MJPEG, ROI processing unit and 64b, 6 round unrolled SIMON)                                                                                                                                                                                                           | 56 |

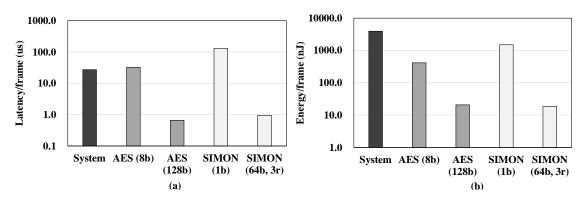

| 4.19 | (a) Latency and (b) energy consumption of the unsecured sensor system and AES/SIMON encryption engines.                                                                                                                                                                                                                                                                                                                                                                         | 57 |

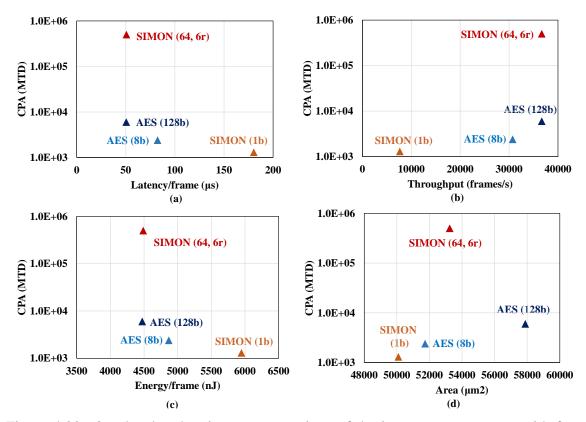

| 4.20 | Overhead and resistance comparison of the image sensor system with four different encryption engines. (a) End-to-end latency, (b) system throughput, (c) energy, and (d) area overhead.                                                                                                                                                                                                                                                                                         | 57 |

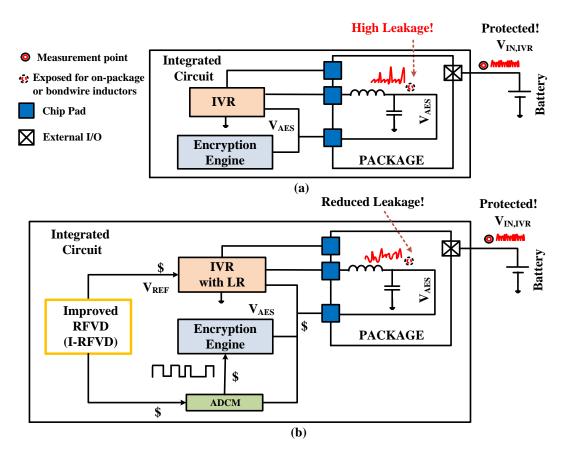

| 5.1  | Exploiting integrated voltage regulators (IVR) and all-digital clock modu-<br>lation (ADCM) for improved resistance to side channel analysis (SCA) at-<br>tacks: (a) on-chip IVR with bondwire/on-package inductors and (b) on-chip<br>integrated IVR+ADCM architecture for SCA-resistant encryption engines                                                                                                                                                                    | 60 |

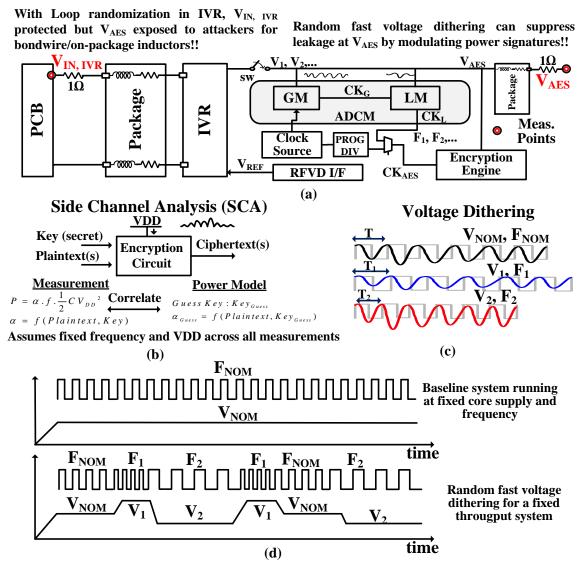

| 5.2  | (a) Overall system architecture for RFVD, (b) supply and frequency depen-<br>dence of correlation power analysis (CPA), (c) SCA leakage suppression of<br>an AES core with RFVD, and (d) RFVD for fixed throughput encryption<br>core                                                                                                                                                                                                                                           | 62 |

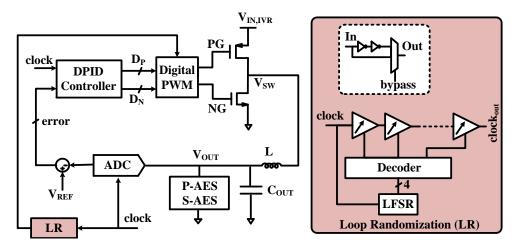

| 5.3  | (a) Block diagram for IVR and (b) Loop randomization (LR) circuit [20]. $\ .$                                                                                                                                                                                                                                                                                                                                                                                                   | 63 |

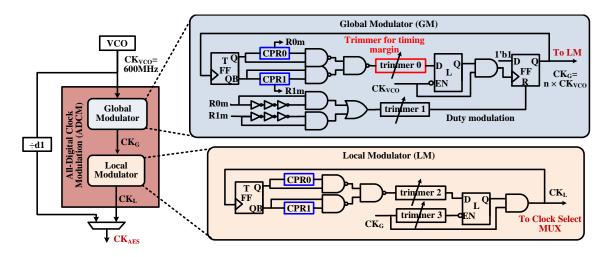

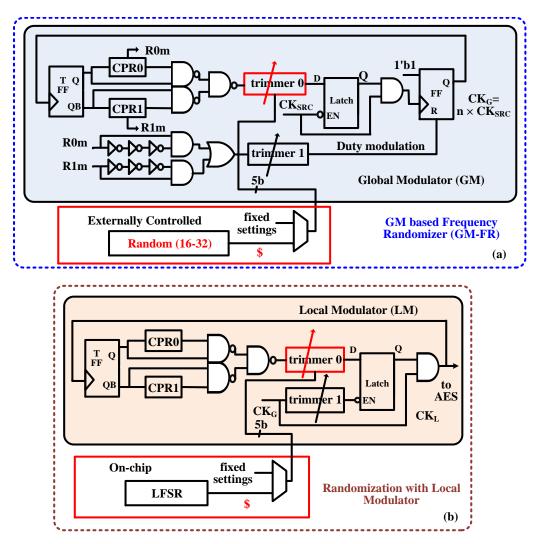

| 5.4  | Block diagram for ADCM circuit with GM and LM utilizing critical path replicas for P-AES. ADCM when enabled supplies clock to encryption cores.                                                                                                                                                                                                                                                                                                                                 | 64 |

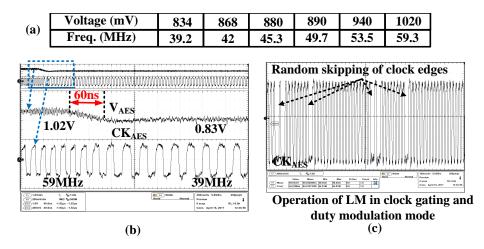

| 5.5  | (a) Table listing all 6-quantized voltage and frequency levels, (b) worst case voltage transition from 1.02V to 0.834V occurs in 60ns with ADCM modulating clock, even during the transition, ensuring correct operation, and (c) Additional random shifts added to clock edges from LFSR controlled LM trimmer. | 65 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.6  | Block diagram for ADCM circuit: (a) trimmer 0 inside GM can be exter-<br>nally programmed to randomize the frequency corresponding to a voltage<br>level and (b) randomly triggered duty modulation and clock gating modes<br>with LFSR controlled trimmer 0 in LM                                               | 66 |

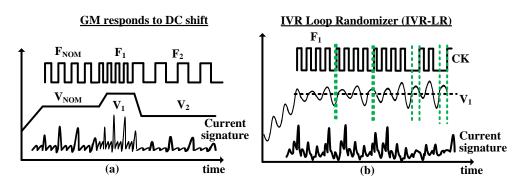

| 5.7  | Sources of randomization from B-RFVD scheme: (a) GM dithers clock freq. in response to voltage dithering and responds to any global noise/DC shift, (b) IVR-LR not only adds noise in $V_{AES}$ but also interacts with GM and LM in ADCM.                                                                       | 67 |

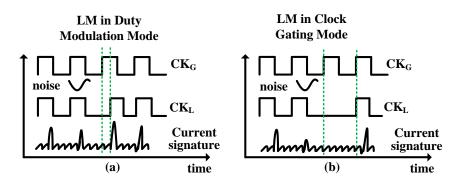

| 5.8  | Sources of randomization from B-RFVD scheme: (a) LM modulates duty cycle of output clock, and (b) LM skips some of the clock edges in presence of random noise.                                                                                                                                                  | 68 |

| 5.9  | Additional sources of randomization from I-RFVD scheme - externally controlled trimmer 0 producing different clock freq. levels breaking 1-to-1 V-F correspondence.                                                                                                                                              | 68 |

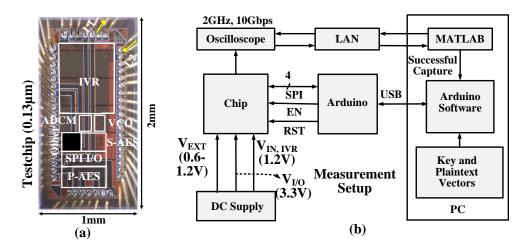

| 5.10 | (a) Die photo of IVR+ADCM+AES system, and (b) measurement setup                                                                                                                                                                                                                                                  | 70 |

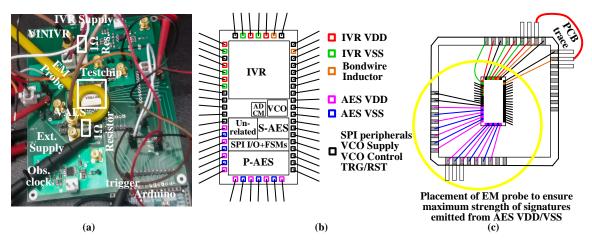

| 5.11 | (a) Test-board for measuring side channel activity, (b) pad diagram for the test-chip, and (c) placement of EM probe for capturing EM signatures generated by local VDD and VSS nodes of AES.                                                                                                                    | 71 |

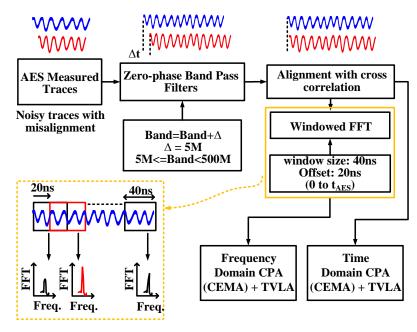

| 5.12 | Post-processing, alignment techniques and side channel analysis in time and freq. domain with sliding window based FFT.                                                                                                                                                                                          | 73 |

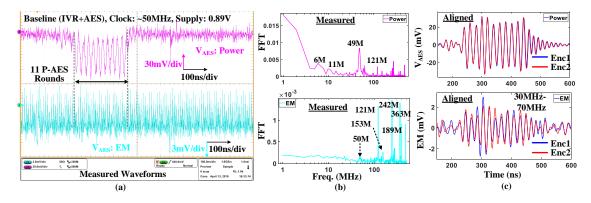

| 5.13 | Filtering and alignment of measured waveforms for baseline IVR+P-AES:<br>(a) measured raw waveforms for power/EM signatures, (b) FFT of mea-<br>sured waveforms, and (c) filtered with 30-70MHz band and aligned wave-<br>forms.                                                                                 | 73 |

| 5.14 | Filtering and alignment of measured waveforms for P-AES with I-RFVD:<br>(a) measured raw waveforms for power/EM signatures, (b) FFT of mea-<br>sured waveforms, and (c) filtered with 65-70MHz band and aligned wave-<br>forms.                                                                                  | 74 |

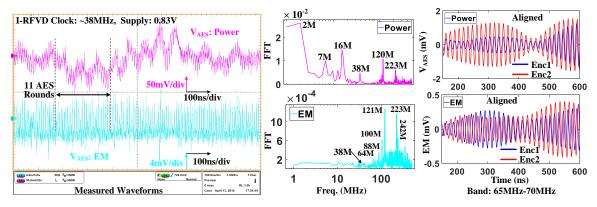

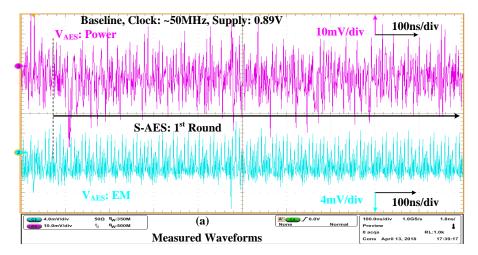

| 5.15 | Effect of different randomizations on spectral content of measured power signatures: (a) B-RFVD system, (b) B-RFVD+GM-FR system, and (c) I-RFVD system. | 74 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

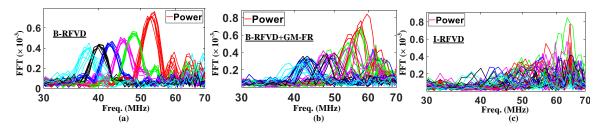

| 5.16 | Measured raw waveforms for power/EM signatures for baseline IVR+S-AES system                                                                            | 74 |

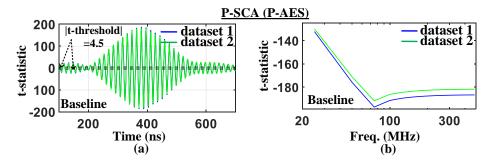

| 5.17 | TVLA analysis results for baseline (IVR+AES) system. t-statistic plotted across: (a) time, and (b) freq                                                 | 76 |

| 5.18 | Comparison of time and freq. domain TVLA leakages for baseline IVR+AES system                                                                           | 76 |

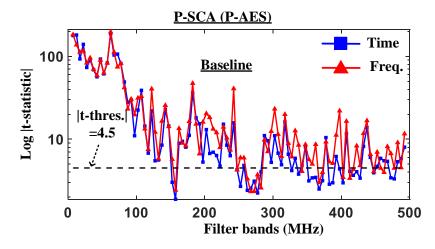

| 5.19 | Comparison of time and freq. domain TVLA leakages for baseline IVR+AES system                                                                           | 77 |

| 5.20 | Comparison of time and freq. domain TVLA leakages for baseline IVR+AES system                                                                           | 78 |

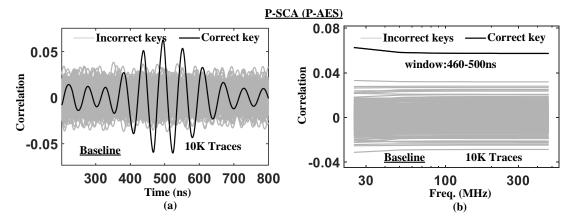

| 5.21 | CPA analysis results for baseline (IVR+AES) system in time and freq. do-<br>mains. Correlation plotted against (a) time, and (b) freq                   | 79 |

| 5.22 | Comparison of time and freq. domain TVLA leakages for baseline IVR+AES system.                                                                          | 79 |

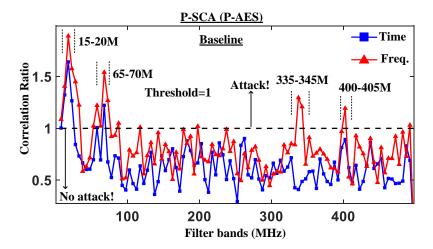

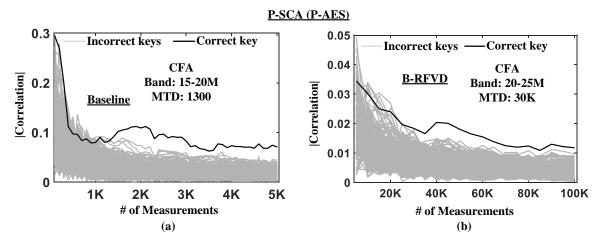

| 5.23 | MTD plot for correlation frequency analysis (CFA) for P-AES (a) baseline, and (b) B-RFVD system.                                                        | 80 |

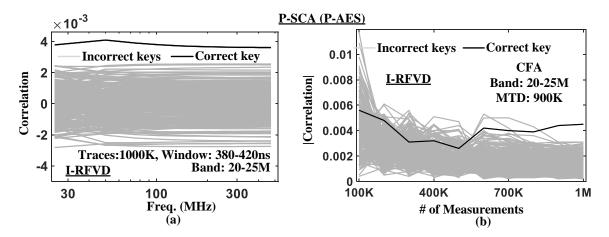

| 5.24 | CFA results for I-RFVD system: (a) correlation against freq., and (b) MTD plot.                                                                         | 80 |

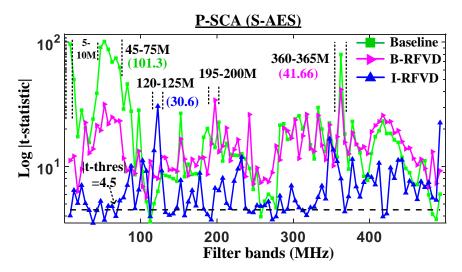

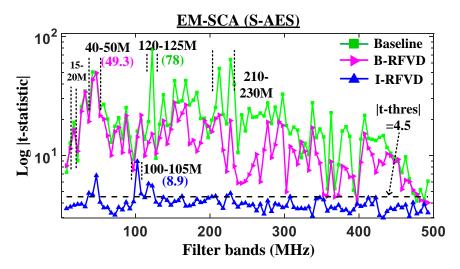

| 5.25 | Log of —t-statistic— plotted against filter bands. S-AES shows significant leakage even for I-RFVD system                                               | 81 |

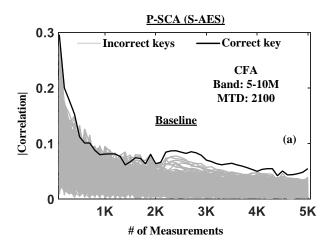

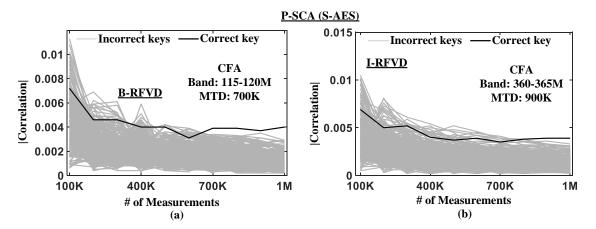

| 5.26 | CFA results for S-AES. MTD plots for: (a) baseline, (b) B-RFVD, and (c) I-RFVD systems.                                                                 | 82 |

| 5.27 | CFA results for S-AES. MTD plots for: (a) B-RFVD, and (b) I-RFVD systems.                                                                               | 83 |

| 5.28 |                                                                                                                                                         | 84 |

| 5.29 |                                                                                                                                                         | 85 |

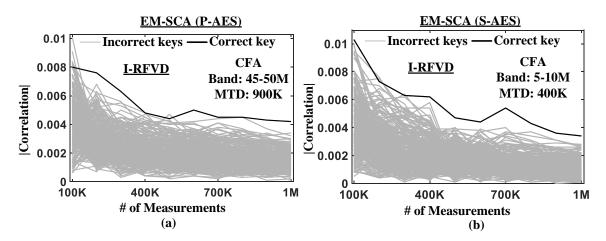

| 5.30 | CEMA for I-RFVD system for: (a) P-AES, (b) S-AES                                                                                                                                                                                           | 85  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

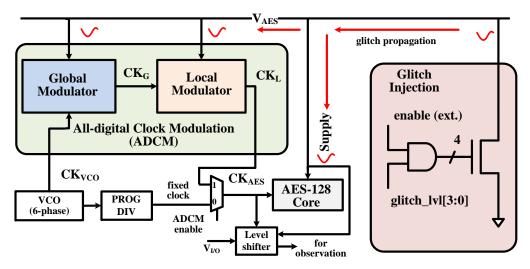

| 6.1  | System architecture of ADCM circuit to prevent supply glitch and temper-<br>ature variations-based fault attacks for a 128-bit AES encryption core                                                                                         | 92  |

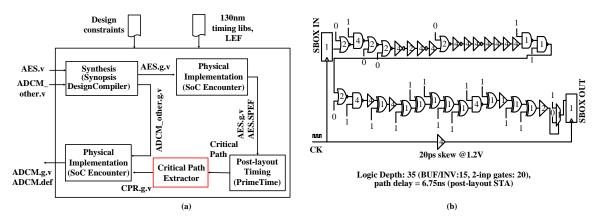

| 6.2  | (a) Fully synthesizable design flow to implement ADCM circuit and (b) worst case timing critical path for S-AES extracted from post-layout STA.                                                                                            | 92  |

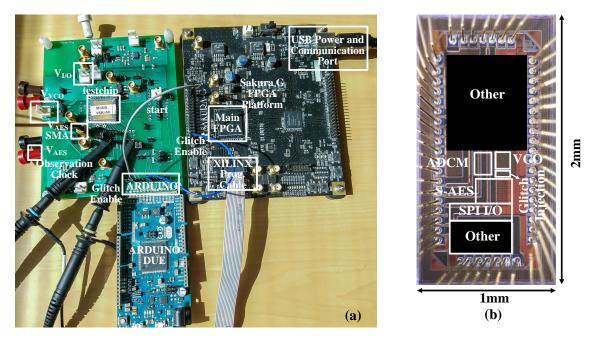

| 6.3  | (a) Measurement setup with testchip and PCB integrated with Sakura-G FPGA platform and Arduino Due (b) testchip with relevant blocks marked for FIA experiments.                                                                           | 93  |

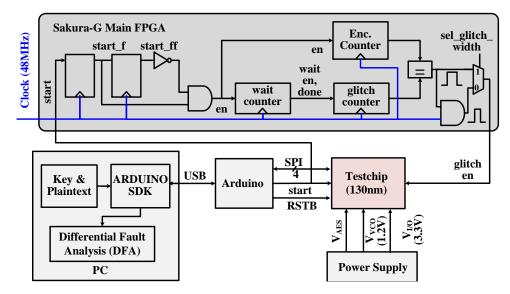

| 6.4  | Measurement setup for fault injection- Sakura-G platform integrated with testchip to generate programmable glitch enable signal once every encryption.                                                                                     | 94  |

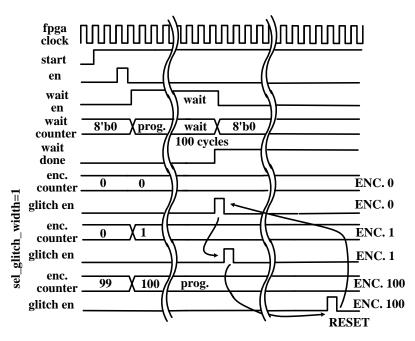

| 6.5  | timing diagram for glitch enable generation with respect to AES encryption.                                                                                                                                                                | 94  |

| 6.6  | (a) Unprotected standalone AES and (b) AES protected with on-chip ADCM circuit are analyzed with respect to FIA.                                                                                                                           | 95  |

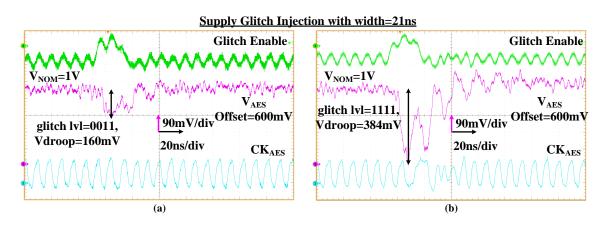

| 6.7  | Glitch injection under nominal conditions ( $V_{AES}=1V$ , $F_{AES}=110MHz$ ) with programmable glitch height and width: (a) glitch level=0011, width=21ns, (b) glitch level=1111, width=21ns.                                             | 97  |

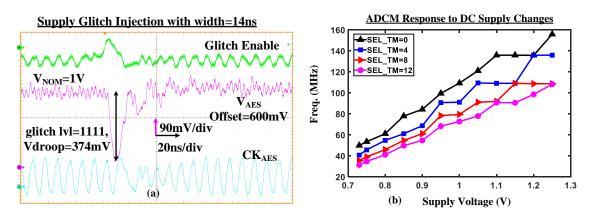

| 6.8  | (a) Glitch injection under nominal conditions ( $V_{AES}=1V$ , $F_{AES}=110MHz$ ) with programmable glitch height and width: glitch level=0011, width=21ns and (b) Characterization of ADCM for DC supply voltage ranging from 0.72-1.25V. | 98  |

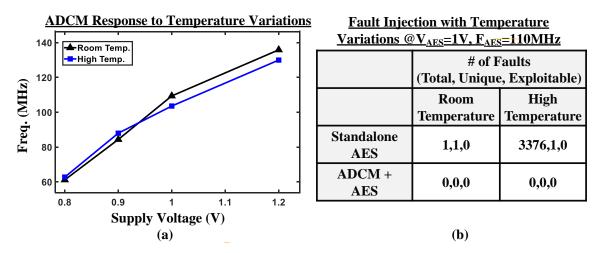

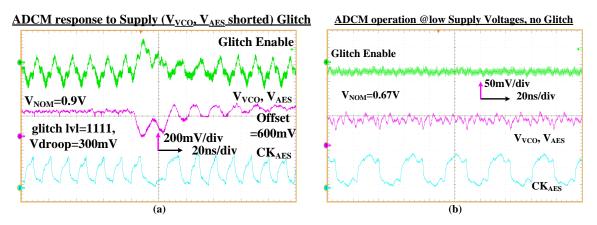

| 6.9  | ADCM responds to supply glitches: (a) at nominal conditions ( $V_{AES}=1V$ , $F_{AES}=110MHz$ ) with the highest glitch level and (b) at $V_{AES}=0.72V$ with the highest glitch level.                                                    | 99  |

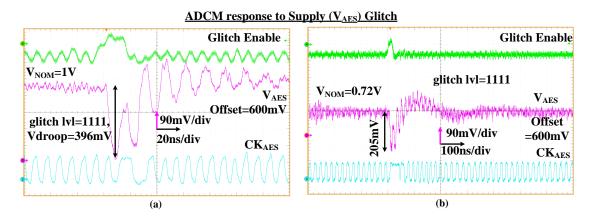

| 6.10 | (a) effect of increased temperature on ADCM output clock freq., and (b) more faults are injected at high temperature at nominal conditions ( $V_{AES}=1V$ , $F_{AES}=110MHz$ ) however with ADCM turned ON, all faults are prevented.      | 100 |

| 6.11 | (a) effect of glitch on VCO supply voltage when $V_{AES}$ and VVCO are shorted, ADCM still operates reliably under glitches and (b) Impact of reducing $V_{AES}$ , VVCO (shorted) to very low levels.                                      | 101 |

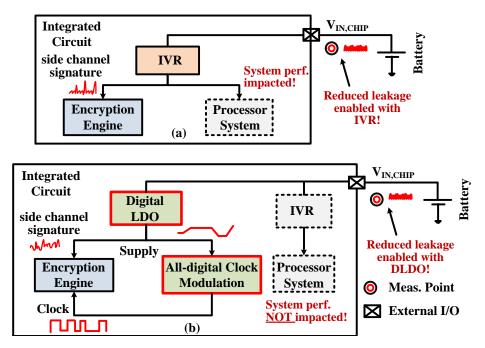

| 7.1  | Utilizing integrated voltage regulators as SCA countermeasures, (a) limi-<br>tations of switching DC-DC converter based SCA protection schemes and<br>(b) proposed on-die digital LDO integrated with ADCM circuit for simul-<br>taneous supply and clock modulation to improve SCA resistance 104                                                                                                                                                                                 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

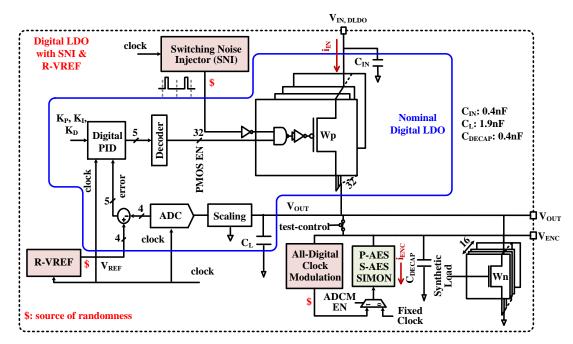

| 7.2  | System architecture consisting of nominal DLDO, AES and SIMON cores, proposed SNI, R-VREF R-VREF & ADCM circuits                                                                                                                                                                                                                                                                                                                                                                   |

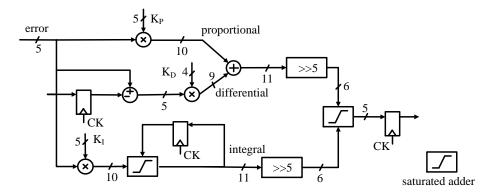

| 7.3  | Digital implementation of proportional-integral-derivative (PID) compen-<br>sator in parallel form                                                                                                                                                                                                                                                                                                                                                                                 |

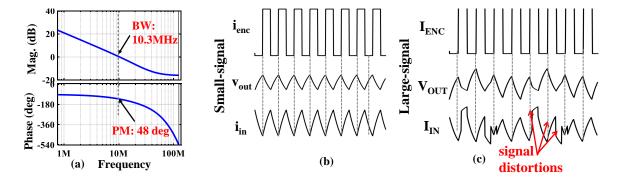

| 7.4  | DLDO model analysis and transformations. (a) Bode plot for the open loop DLDO under nominal operating conditions and at 31mA base current, (b) small signal attenuation and (c) large signal amplitude distortions 108                                                                                                                                                                                                                                                             |

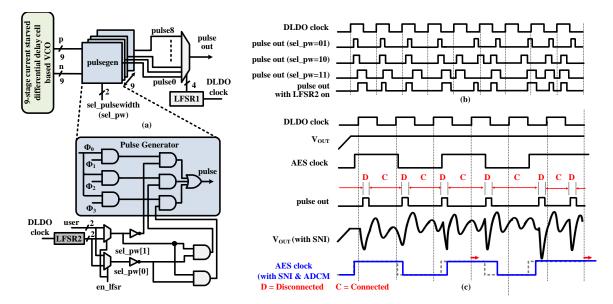

| 7.5  | Block diagram for (a) proposed SNI circuit, (b) circuit operation, and (c) supply and clock randomization achieved with SNI and ADCM                                                                                                                                                                                                                                                                                                                                               |

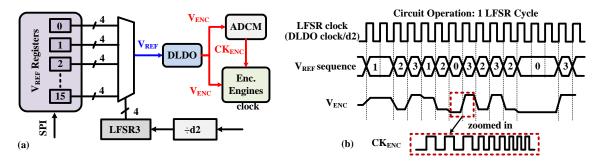

| 7.6  | Block diagram for (a) proposed R-VREF circuit and (b) circuit operation. 111                                                                                                                                                                                                                                                                                                                                                                                                       |

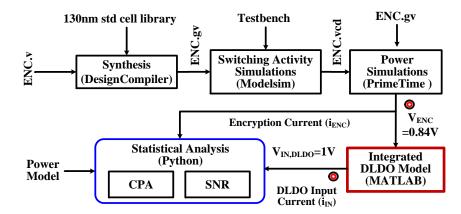

| 7.7  | Simulation framework for integrated digital LDO and encryption core 112                                                                                                                                                                                                                                                                                                                                                                                                            |

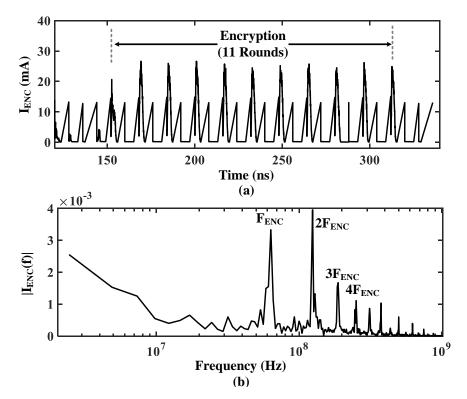

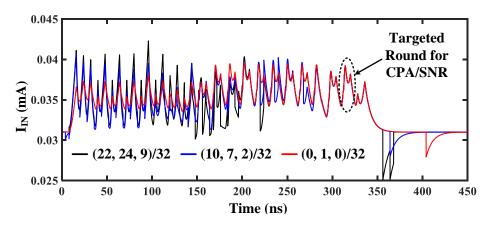

| 7.8  | (a) Simulated current waveform for one P-AES encryption and (b) spectral content shows major peak corresponding to encryption clock frequency $(F_{ENC})$ and its harmonics                                                                                                                                                                                                                                                                                                        |

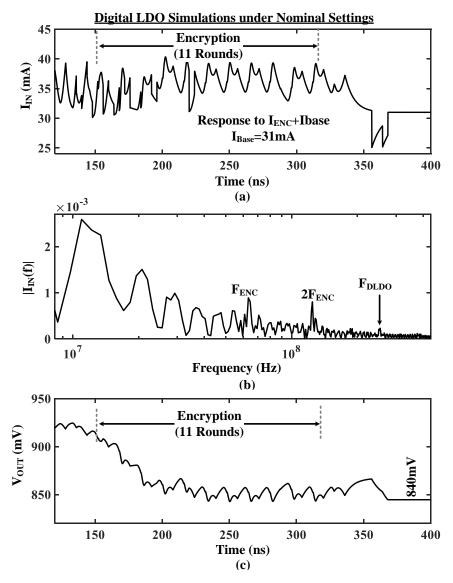

| 7.9  | (a) Current profile at the input of DLDO (I <sub>IN</sub> ) in response to changes in the encryption current for one P-AES encryption, (b) spectral content shows major (but attenuated with respect to P-AES without DLDO) peak corresponding to encryption clock frequency ( $F_{ENC}$ ), its harmonics and a small peak at the DLDO clock frequency ( $F_{DLDO}$ ) and (c) output waveform ( $V_{OUT}$ ) for the digital LDO under load changes due to encryption operation 114 |

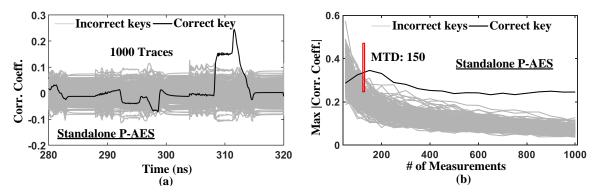

| 7.10 | CPA attack results on the standalone P-AES core at local supply node $(V_{ENC})$ for subkey/byte 9: (a) correlation plot with 1000 simulations/traces and (b) MTD plot shows correct subkey 9 can be recovered with only 150 simulations/traces                                                                                                                                                                                                                                    |

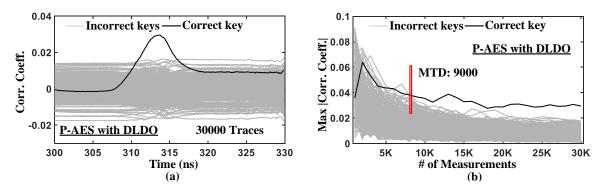

| 7.11 | CPA attack results on the DLDO powered P-AES core at the input of DLDO ( $V_{IN,DLDO}$ ) for subkey/byte 9: (a) correlation plot with 30000 simulations/traces and (b) MTD plot shows correct subkey 9 can be recovered with 9000 simulations/traces, indicating an increase of $60 \times$ with respect to standalone P-AES core                                                                                                                                                  |

| 7.12 | Effect of PID compensator gains on the DLDO transient response to the encryption current.                                                                                                                                                                  | 16  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

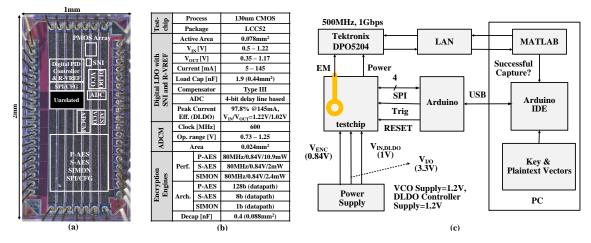

| 7.13 | (a) Die photo, (b) details of the testchip and (c) measurement setup 1                                                                                                                                                                                     | 19  |

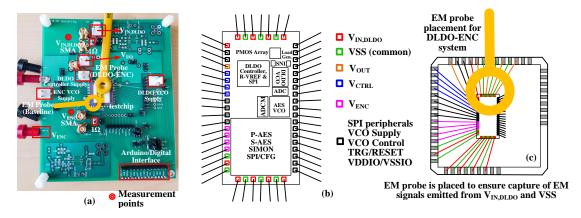

| 7.14 | (a) Test-board manufactured to measure side channel activity, (b) pinout specifications for the testchip showing the power, ground pins critical for EM signature acquisition with respect to probe placement and signal isolation.                        | .19 |

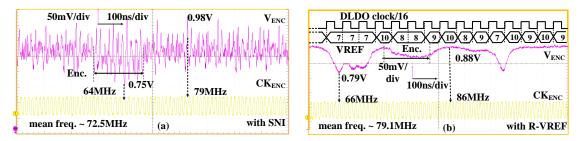

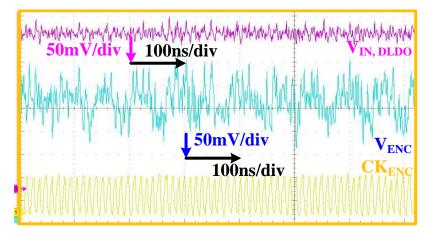

| 7.15 | Measured circuit operation for (a) SNI and (b) R-VREF with respect to supply voltage ( $V_{ENC}$ ) and clock ( $CK_{ENC}$ ) inputs to encryption cores. SNI is enabled with highest possible width for pulse out and R-VREF is run at DIV16 of DLDO clock. | 21  |

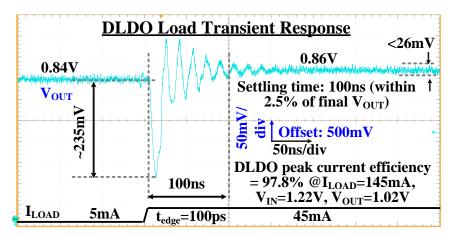

| 7.16 | Measured load transient response for the nominal DLDO with $\Delta I_L$ =40mA/100p<br>@V <sub>IN</sub> =1.0V, V <sub>OUT</sub> =0.84V                                                                                                                      |     |

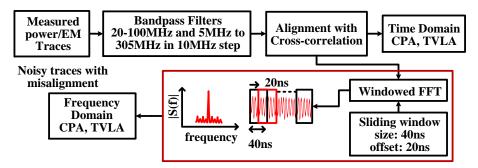

| 7.17 | Postprocessing including filtering and alignment of captured signatures and SCA analysis in time and frequency domains                                                                                                                                     | 22  |

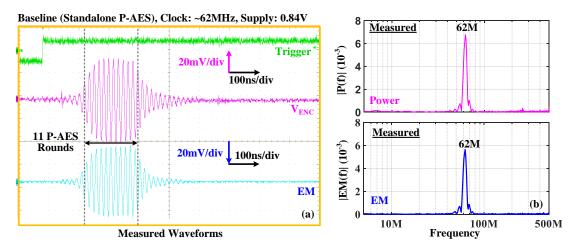

| 7.18 | Baseline (standalone P-AES) system: (a) measured waveforms captured at/near $V_{ENC}$ and (b) their spectral characteristics. Both DLDO and ADCM circuits are turned off                                                                                   | .22 |

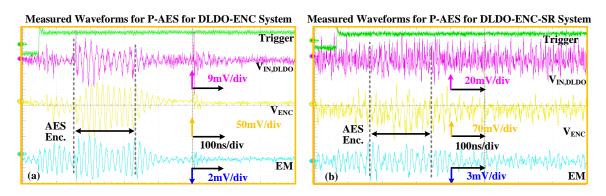

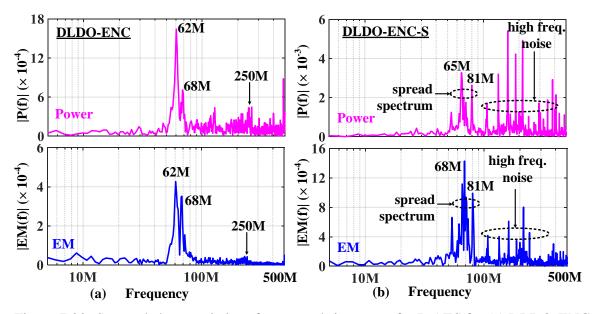

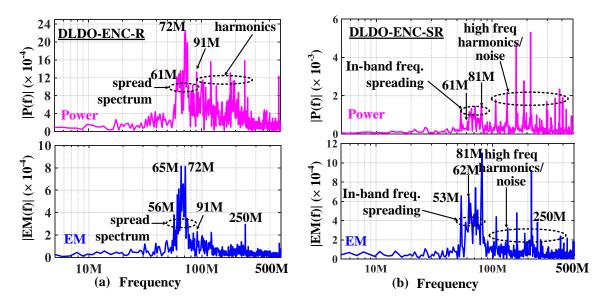

| 7.19 | Measured power/EM signatures for P-AES for (a) DLDO-ENC and (b) DLDO-ENC-SR systems                                                                                                                                                                        | .23 |

| 7.20 | Spectral characteristics of measured signatures for P-AES for (a) DLDO-ENC and (b) DLDO-ENC-S systems                                                                                                                                                      | 23  |

| 7.21 | Spectral characteristics of measured power/EM signatures for P-AES for DLDO-ENC with (a) R-VREF enabled and (b) with both SNI & R-VREF enabled                                                                                                             | 24  |

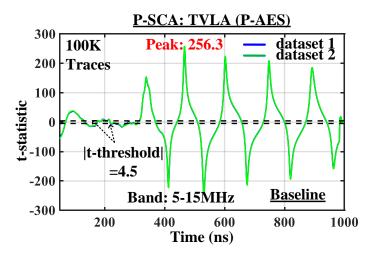

| 7.22 | TVLA analysis for P-AES for baseline (standalone) system                                                                                                                                                                                                   | 24  |

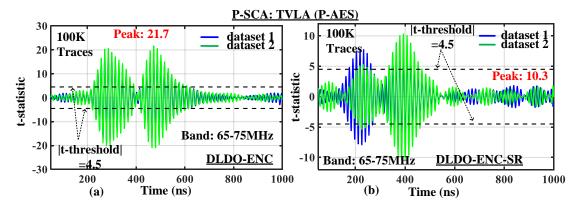

| 7.23 | TVLA analysis for P-AES for (a) DLDO-ENC and (b) DLDO-ENC-SR systems.                                                                                                                                                                                      | 25  |

| 7.24 | TVLA peak vs filter bands show reduced leakage across all bands for DLDO-<br>ENC system which further reduces for DLDO-ENC-SR system 1                                                                                                                     | 27  |

| 7.25 | CPA attack results for P-AES for Byte 9 for baseline system in (a) time domain, (b) freq. domain with 10K traces                                                                                                                                           | 28  |

| 7.26 | Freq. domain CPA attack results for Byte 9 for P-AES for (a) baseline system with MTD of 400 traces in (MTD=800 in time domain) and (b) correlation vs freq. for DLDO-ENC system                                           | . 129 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7.27 | Effect of test-control power gate and on-chip decoupling capacitance on CPA/CEMA results (a) measurement configuration and (b) MTD for 80% SR for the baseline P-AES shows small impact of on-chip decap (0.4nF vs 2.3nF). | . 129 |

| 7.28 | Freq. domain CPA attack results for P-AES for Byte 9 for (a) DLDO-ENC-SR system and (b) SR vs # of measurements                                                                                                            | . 130 |

| 7.29 | CR plotted against filter band shows large leakage in all bands for baseline system which reduces for DLDO-ENC and DLDO-ENC-SR systems                                                                                     | . 130 |

| 7.30 | TVLA leakage vs filter bands for EM-SCA shows reduced leakage for DLDO-ENC-SR system, however, leakage is higher than P-SCA                                                                                                | . 131 |

| 7.31 | CR plotted against filter bands for EM-SCA shows similar peak value as P-SCA for DLDO-ENC-SR system however the highest leaking bands are different.                                                                       | . 132 |

| 7.32 | SR plotted against # of measurements shows subkeys are easier to recover with respect to CEMA than CPA for DLDO-ENC-SR system. However, it still takes 7.2M measurements to reveal 80% of the subkeys                      | . 133 |

| 7.33 | Measured power waveforms at $V_{ENC}$ , $V_{IN,DLDO}$ and encryption clock under LCO at $V_{ENC}$ =0.88V at a base current of 5mA. ADCM is on                                                                              | . 133 |

| 7.34 | Effect of LCO on TVLA leakage time time/freq. domains at light load current (I <sub>base</sub> $\sim$ 5mA) and different V <sub>ENC</sub> settings                                                                         | . 134 |

| 7.35 | Measured power/EM signatures for DLDO-ENC-SR system for (a) S-AES and (b) SIMON encryption cores. For SIMON core, only initial 3 rounds (3R) of encryption are shown                                                       | . 135 |

| 7.36 | SR plotted against # of measurements for baseline and proposed systems with respect to power (P) and EM SCA for (a) S-AES (b) SIMON cores.                                                                                 | . 136 |

#### SUMMARY

The rapid growth in the number of devices connected to the network has transformed the computing paradigm in all walks of human life, from autonomous vehicles to healthcare, industrial and home automation. The internet of things (IoT) devices help in achieving higher energy-efficiency, accuracy, speed and faster design cycles compared to general purpose computing devices. Security and privacy of critical and sensitive data is a major challenge for all computing systems, however, these network-connected devices have been overlooked with respect to device-related security risks owing to lack of resources at IoT edge nodes. Moreover, encryption algorithms implemented in hardware on these devices to secure inter-device communication emit information about the key through physical side channels leading to research challenges in designing energy-efficient, compact and side channel attack (SCA) resistant cryptographic hardware for IoT applications. This thesis investigates alternative hardware architectures for SIMON for higher energyefficiency and design of lightweight SCA countermeasures utilizing on-chip integrated power-management and clocking techniques.

We propose alternative hardware architectures for lightweight cipher SIMON, at bit-/round-level parallelism, implemented in ASIC and FPGA platforms. Round unrolling (round-level parallelism) not only improves the energy-efficiency at small area, power overheads but also increases SCA resistance with deeper diffusion of the key, reduced signalto-noise ratio (SNR) and increased complexity in modeling true leakage. The optimized SIMON engine is applied to a low-power image sensor node to analyze the overheads for secured communication.

Power management and low-power techniques employed in modern high-performance and low-power systems for improved energy-efficiency modulate/modify power and electromagnetic (EM) side-channel leakage and therefore it is essential to understand their role in improving SCA resistance. We propose lightweight countermeasures utilizing on-chip fully-integrated inductive voltage regulator (FIVR) and digital low-dropout (DLDO) regulator along-with all-digital clock modulation (ADCM) circuit to improve SCA resistance of SIMON and advanced encryption standard (AES) encryption engines.

A random fast voltage dithering (RFVD) scheme with FIVR and ADCM is developed to randomize side channel signatures to improve SCA resistance for the local supply node of the AES cores which is exposed outside for bondwire or package based inductors. To eliminate the need for large passives (L, C), a major drawback for FIVR, a side channel protection scheme is proposed using DLDO and ADCM circuits. DLDO transforms the encryption patterns when measured at the input supply node and therefore enhances the SCA resistance. Two additional circuit techniques, namely, switching noise injector (SNI) and random reference word (R-VREF) generator are proposed to induce more randomness. The proposed FIVR, DLDO, randomization circuits along with 128-bit AES and SIMON cores are prototyped in two testchips in 130nm CMOS process and SCA measurements demonstrate improved resistance with respect to test vector leakage assessment (TVLA) and correlation power and EM analysis (CPA & CEMA) attacks. Due to all-digital nature of the proposed circuits, they easily integrate into digital design flows and are scalable across process nodes. Additionally, the overheads associated with these circuits are minimal compared to existing SCA countermeasures.

# CHAPTER 1 INTRODUCTION

The emergence of pervasive computing has led to exponential growth of IoT devices from smart homes to smart wearables and toys, smart healthcare, autonomous vehicles and industrial equipment [1, 2]. For remote monitoring and processing, most of these devices are connected to the internet communicating sensitive information over the insecure wireless channels requiring encryption and authentication protocols to ensure safety and confidentiality [3]. Even though these security protocols have been proven secure against bruteforce or cryptanalysis attacks, their hardware or software implementations leak certain information via physical and architectural side channels such as power consumption [4], electromagnetic (EM) emissions [5], timing [4], acoustic signals [6], speculative execution [7–9], cache timing [10] etc. Side channel attacks, considered to be one of the seven properties defined for the highly secure devices by Microsoft Researchers [11], are very critical for the security for the modern computing devices. These side channels are part of the hardware design itself and therefore are notoriously difficult to defeat.

Several side channel analysis (SCA) attacks have been demonstrated to extract secret key used during the security operations by exploiting data-dependent information leaked through power, EM, timing side channels [4, 5, 12]. Modern computing systems are built using digital gates and the current drawn by these gates when they switch is dependent on the input vectors. An adversary can exploit the correlation between measured current signature and the input vectors to reveal the secret key. Various statistical analysis methods are used to exploit this data dependency, namely, differential power analysis (DPA) [12], correlation power analysis (CPA) [13], and template attacks (TA) [14]. Several countermeasures [15–29] have been developed in past two decades to either mask or hide information leak-age through these side channels. However, due to high development costs, the hardened

security protocols are only limited to high-cost or high-margin devices [11]. For example, ARM Cortex instruction set architecture (ISA) offers TrustZone technology where trusted and untrusted operations are executed in two different worlds, namely, secure and normal operatig systems (OS), simultaneously running on a single core. Similarly, Intel's x86 ISA defines Software Guard Extensions (SGX) instructions to increase the security of application code and data, offering more isolation and protection to the sensitive operations using secure enclaves.

IoT devices drive huge economic efficiencies, however, due to severe resource constraints and price-sensitivity, they are ill-prepared for the security challenges of internet connectivity, exposing consumers and society to the perils of device security and privacy failures. To incorporate appropriate security features on IoT edge nodes, several lightweight cryptographic algorithms and primitives are being considered with PRINCE [30], PRESENT, [31], CLEFIA [32], Keccak [33], Whirlpool [34] and SIMON/SPECK [35] being few of the recently proposed candidates for lightweight encryption and authentication protocols. SIMON, introduced by National Institute of Standards and Technology (NIST) and optimized for hardware implementations, is an attractive option as it has been reported to be most compact implementation among all candidates [36]. However, for battery-operated IoT devices, energy-efficiency is another aspect which must be considered along with area. Most compact implementations may not be the most energy-efficient due to various tradeoffs. Additionally, accelerated hardware implementations should also be considered to ensure cryptographic blocks not being the bottleneck for the whole system.

At the circuit and architecture level, several power management and low-power techniques exist to improve the system energy-efficiency as well as performance such as distributed on-chip voltage regulation, dynamic voltage scaling (DVS) [37], dynamic voltage and frequency scaling (DVFS) [38] and clock and power gating [39]. Integration of voltage regulation modules on-chip [39–41] provides very fast response to transient events and reduces the overheads associated with switching of power states and therefore facilitates fine-grain power management for multiple DVFS domains. Adaptive clocking is another technique which eliminates timing/supply margins under variations, therefore improving system performance or reducing the total power [42, 43]. These techniques modulate/modify power side-channel leakage and therefore it is essential to understand their interaction with side-channel security of underlying cryptographic hardware. DVFS enabled with external VR and clock source has been demonstrated to improve SCA resistance [44, 45]. However, due to slower voltage-frequency transitions, there is a limited randomization that can be introduced, specifically for hardware accelerated encyrption engines. Impact of FIVR and switched capacitor voltage regulators (SCVR) has been previously investigated [46–52] and demonstrated to improve the SCA resistance at the input supply node of the chip. However, on-chip integration of large passives (L, C) is very expensive and generally not desired for low-cost applications. Consequently, for on-package or printed circuit board (PCB) based inductors/capacitors where local supply node for the encryption engine is exposed outside, these countermeasures provide negligible or little SCA resistance. Linear regulators, especially, low dropout regulators which do not require any large passives, can be implemented digitally, are scalable across process nodes, and can potentially replace IVR or SCVR. A very fast simultaneous supply and clock modulation enabled with on-chip LDO and all-digital clock modulation (ADCM) circuit can facilitate increased randomization of side channel signatures to provide both point of load (PoL) regulation [40, 41] and security [53], therefore, simultaneously addressing the challenges of energy-efficiency and security for low-power IoT devices and high-performance computing systems.

#### **1.1 Problem Statement**

The objective of the proposed research is to explore energy-efficient and side channel attack resistant architectures for lightweight ciphers and design of generic low-overhead SCA countermeasures for cryptographic hardware by leveraging on-chip power management and clocking techniques. This includes:

- Development of energy-efficient and SCA resistant datapath architectures for 128-bit SIMON engine; which are subsequently characterized and quantified with respect to ASIC and FPGA implementations.

- Design of random fast voltage dithering (RFVD) scheme to enable side channel security for FIVRs which use on-package or bondwire based inductors.

- Characterization of power-supply glitch or temperature variation induced fault injection attack resistance offered by all-digital clock modulation (ADCM) circuit.

- Modeling and identification of different transformations induced by digital LDO which help in suppressing information leakage.

- Integration of hiding circuits into digital LDO control loop to improve SCA resistance.

- Characterization and quantification of power, EM and fault attack resistance through measurement from two prototype testchips.

#### **1.2** Organization of this Thesis

**Chapter 2** provides a brief background on several topics which are essential to comprehend the scope and contributions of this dissertation including lightweight cryptography, on-chip power management techniques, adaptive clocking, side channel attacks and countermeasures.

**Chapter 3** describes side channel analysis methods and metrics employed in this dissertation to quantify SCA resistance. Also, presents the architecture for 128-bit AES (parallel AES: P-AES and serial AES: S-AES) and SIMON cores.

**Chapter 4** explores different datapath architectures for SIMON for improved energy efficiency as well increased SCA resistance. Several datapath architectures utilizing bit-level and round-level parallelism are implemented on ASIC to investigate power, performance, area (PPA) and energy tradeoffs. Proposed datapaths for 128-bit SIMON core are subsequently implemented on Sakura-G FPGA board to quantify side channel leakage. Optimized SIMON architectures are then applied to a low-power image sensor node to demonstrate the applicability and efficiency of the engine for IoT edge devices.

**Chapter 5** presents lightweight countermeasures utilizing a FIVR and ADCM circuit to protect 128-bit AES cores against side channel attacks. The architecture of ADCM circuit is presented and various sources of randomization induced from ADCM including instantaneous frequency randomization (FR) in conjunction with FIVR loop randomization (LR) are discussed. SCA measurements from a testchip prototype consisting of FIVR, ADCM and AES cores designed and fabricated in 130nm CMOS process are presented and improvement in SCA resistance with respect to CPA & CEMA and TVLA analysis is discussed alongwith the limitations of the proposed countermeasures.

**Chapter 6** explores fault injection attack (FIA) resistance offered by ADCM circuit for S-AES. A simple measurement setup is developed to inject power supply glitch and temperature variations based faults for the standalone S-AES and protected S-AES (with ADCM) systems. Faults are characterized and analyzed for FIA under different glitch settings and role of ADCM to tolerate these glitches is discussed and experimentally demonstrated.

**Chapter 7** explores on-chip LDO regulators as countermeasures to side channel attacks for 128-bit AES and SIMON cores. Additional circuit techniques, namely switching noise injector (SNI) and random reference word generator (R-VREF), to randomize side channel signatures are described. Measurement results from a testchip consisting of all-digital LDO, SNI & R-VREF, AES and SIMON cores developed in 130nm CMOS process are presented and improvement in SCA resistance with respect to CPA & CEMA and TVLA analysis is discussed.

Chapter 8 highlights the contributions of this dissertation and discusses future research work and directions.

# CHAPTER 2 BACKGROUND

### 2.1 Lightweight Cryptography

Even though IoT edge devices are miniscule and perform only important processing to reduce the communication from a device to the host machine, the processing of the data and communication need to be secured to prevent the edge device from becoming the entry point into the network for a potential hacker [Fig. 2.1]. Due to stringent resource requirements, conventional encryption schemes such as AES or DES cannot be used for IoT-edge nodes, giving rise to the field of lightweight cryptography . On one hand, researchers are exploring compact and low-power realization of AES engines, for example, using serial implementations [54–56], on the other hand, there is a growing interest in ultra-lightweight but cryptanalytically secure encryption algorithms that can be realized in very small area footprint and consume minimal energy. For example, lightweight cryptographic algorithms such as CLEFIA [32], PRESENT [31] and PRINCE [30] have been proposed and studied

Figure 2.1: Security threats of the interconnected world where security (in terms of security protocols and defenses against physical attacks) must be the first priority and not optional.

Figure 2.2: SIMON provides much higher flexibility when choosing an encryption algorithm for a target IoT application with respect to security parameters and with its resourceefficiency compared to other lightweight ciphers as well as compact implementations of AES algorithm.

for area, performance, and energy tradeoffs. More recently, National Institute of Standards and Technology (NIST) has proposed SIMON and SPECK [35], two sister lightweight cryptographic algorithms, tailored for IoT edge devices. SIMON is optimized for hardware implementations while SPECK is optimized for software implementations. The SIMON algorithm is based on feistel networks. Very simple round function and key expansion hardware makes SIMON suitable for lightweight cryptography. The high degree of algorithmic flexibility enables SIMON hardware to be optimized based on the application security requirement [Fig. 2.2].

Side channel attacks (SCA), a major threat to security of all cryptographic devices, have been shown to be very successful to extract the secret key. Many countermeasures which have been proposed to inhibit SCA in AES engines at significant area, power and/or performance overheads may not be suitable for lightweight cryptographic primitives. Moreover, there is an inherent tradeoff between compact implementation and SCA resistance of encryption engines. For example, serial implementation, a common approach for compact/lowpower encryption engines, reduces algorithmic noise from parallel computation, thereby increasing SCA vulnerability. The bit-serial nature can reduce the SCA resistance of lightweight encryption algorithms even further. Consequently, there is a need to characterize the tradeoff between area, performance, energy/power and side-channel security of encryption engines. While such analysis has been performed for AES engines, there is a lack of studies on how to design compact resource-efficient as well as SCA secure hardware engines for lightweight encryption algorithms like SIMON.

#### 2.2 **On-Chip Power Management**

Computing systems have traditionally been optimized for performance driving technological innovations and shrinking the transistors to fit more and more devices on the same die for better integration and speeds. However, it was achieved at the cost of increased power consumption and resulting thermal and reliability concerns. To address these challenges, designs were optimized with respect to a power budget and at the same time several power management techniques were developed to reduce power consumption in order to improve system energy-efficiency. Among these techniques, dynamic power management (DPM) techniques such as dynamic voltage scaling (DVS) [37], dynamic votlage frequency scaling (DVFS) [38], power and clock gating [57, 58], multiple power domains are more popular. However, to fully utilize these techniques, voltage regulators (VRs) must be integrated on-chip to facilitate fine-grained and point of load regulation [39–41]. VRs are the basic building blocks of any low-power system and can be categorized into switching DC-DC converters and linear regulators [Fig. 2.3]. Switching DC-DC converters can further be divided into inductive or capacitive based on the passive used to store the energy during switching cycles while low-dropout (LDO) regulators are the most common implementations of linear regulators which are used for a low-power systems on chip (SoC). LDOs can be categorized into analog or digital LDOs based on the type of feedback loop (continuous or discrete). We employ inductive VR and digital LDO (DLDO) regulator in this research. These are briefly described below:

#### 2.2.1 Fully Integrated Inductive Voltage Regulators (FIVR)

Modern processor systems switch between multiple power states quite frequently to save power under varying workload conditions. For off-chip VRs, parasitics of PCB and package PDN reduce the power conversion efficiency and limit the transient performance (settling time for load and reference transients). Therefore, to tackle these challenges, VRs are increasingly integrated on-chip to improve performance and energy-efficiency [39]. Relatively smaller parasitics (higher resonance frequency) for the on-chip PDN allows use of smaller passives for the FIVR increasing the power-density offered by these passives. Additionally, the control loop for the FIVR can be run at much faster speed. This not only improves the system performance but also drastically simplifies the integration of smaller passives [59] on the same chip. An all-digital implementation of the feedback controller can be chosen to simplify FIVR design [60–62].

Figure 2.3: Categorization of different types of integrated voltage regulators used in modern power management systems.

#### 2.2.2 All-Digital Low Dropout Regulators (DLDO