## ADVANCING CYBER SECURITY WITH A SEMANTIC PATH MERGER PACKET CLASSIFICATION ALGORITHM

A Thesis Presented to The Academic Faculty

by

J. Lane Thames

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2012

Copyright  $\bigodot$  2012 by J. Lane Thames

## ADVANCING CYBER SECURITY WITH A SEMANTIC PATH MERGER PACKET CLASSIFICATION ALGORITHM

Approved by:

Dr. Randal Abler, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Henry Owen School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. George Riley School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Raghupathy Sivakumar School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Dirk Schaefer School of Mechanical Engineering Georgia Institute of Technology

Date Approved: September 27, 2012

To Linda, my wife and best friend, forever plus infinity

## ACKNOWLEDGEMENTS

First and foremost, I give special thanks to my advisor, Dr. Randal (Randy) Abler, who has been a great friend and mentor. I began working with Dr. Abler while I was an undergraduate student at Georgia Tech. He introduced me to the world of computer networking, information technology, and cyber security, and I am indefinitely grateful for the support, guidance, and knowledge he has given to me throughout the years.

I would like to thank Dr. George Riley, Dr. Henry Owen, Dr. Raghupathy Sivakumar, and Dr. Dirk Schaefer for taking time from their busy schedules to serve as my thesis committee. Their feedback, support, and guidance played an invaluable role in my dissertation research. I am truly honored to have studied under the guidance of my advisor and committee.

I am grateful to all of my friends, classmates, and colleagues from Georgia Tech for all of their support and encouragement. I am thankful for each and every one of the wonderful Georgia Tech faculty and staff who have helped me during my time as a student. I would like to extend a special thanks to Ms. Marilou Mycko, Mrs. Pat Potter, and Dr. Daniela Staiculescu for all of their administrative support during my time as a graduate student. I would like to express my sincere gratitude to Dr. David Frost for being such a great friend and mentor to me. Special thanks goes to Gail Wells. Gail allowed me to work with her as an undergraduate teaching assistant. It was during my time as a teaching assistant that I discovered a burning desire to teach, and it was this desire that influenced my decision to pursue a graduate degree. Several years ago, Dr. Schaefer and my colleagues in the Systems Realization Laboratory invited me to do collaborative research with them. Our research together over the last few years has been very rewarding, and, for this, I am deeply grateful.

Finally and with immeasurable gratitude, I want to thank my wife, Linda, whose love and encouragement made this achievement possible.

# TABLE OF CONTENTS

| DED                 | ICAT | TION                                                                           | iii  |

|---------------------|------|--------------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS iv |      |                                                                                |      |

| LIST                | OF ' | TABLES                                                                         | viii |

| LIST                | OF   | FIGURES                                                                        | х    |

| NOM                 | IENC | ZLATURE                                                                        | ciii |

| SUM                 | MAR  | XY                                                                             | vii  |

| Ι                   | INT  | RODUCTION                                                                      | 1    |

| II                  | CON  | NCEPTS                                                                         | 6    |

|                     | 2.1  | Terminology                                                                    | 6    |

|                     | 2.2  | Firewalls                                                                      | 7    |

|                     | 2.3  | Intrusion Detection                                                            | 11   |

|                     | 2.4  | Intrusion Prevention                                                           | 14   |

|                     | 2.5  | Packet Classification                                                          | 15   |

|                     | 2.6  | Summary                                                                        | 18   |

| III                 | BAC  | KGROUND                                                                        | 19   |

|                     | 3.1  | Distributed security architectures and defense systems                         | 19   |

|                     | 3.2  | Software-Based Packet Classification Algorithms                                | 25   |

|                     |      | 3.2.1 One Dimensional Packet Classification Algorithms                         | 26   |

|                     |      | 3.2.2 Multidimensional Packet Classification Algorithms                        | 36   |

|                     | 3.3  | Hardware-based Packet Classification                                           | 41   |

|                     | 3.4  | Cyberattack Detection Algorithms with Intelligent Systems                      | 46   |

|                     | 3.5  | Summary                                                                        | 50   |

| IV                  |      | BERATTACK DEFENSE WITH THE DISTRIBUTED FIREWALL AND TIVE RESPONSE ARCHITECTURE | 51   |

|                     | 4.1  | Motivation                                                                     | 51   |

|                     | 4.2  | Functional Characteristics of Distributed Network Defense Mechanisms .         | 54   |

|                     |      | 4.2.1 The Firewall Collaboration Framework                                     | 54   |

|                     | 4.3  | The Distributed Firewall and Active Response Architecture                      | 58   |

|     |     | 4.3.1 High-level Description                                                                                                                                                 |

|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |     | 4.3.2 Architectural Description                                                                                                                                              |

|     |     | 4.3.3 Firewalls, Blacklisting, and the Packet Classification Problem 68                                                                                                      |

|     | 4.4 | Summary                                                                                                                                                                      |

| V   | A N | OVEL THEORY OF SEMANTIC ASSOCIATION SYSTEMS 72                                                                                                                               |

|     | 5.1 | A Compositional Computing Model of Semantic Association Systems 73                                                                                                           |

|     | 5.2 | Formal Model of the Semantic Association System                                                                                                                              |

|     | 5.3 | Hypergraph Representation of the Semantic Association Network 80                                                                                                             |

|     | 5.4 | Characteristics and other Transformations of the Semantic Association<br>System                                                                                              |

|     | 5.5 | Summary                                                                                                                                                                      |

| VI  |     | RDWARE-BASED MULTIDIMENSIONAL PACKET CLASSIFICATION WITH<br>E SEMANTIC PATH MERGER ALGORITHM                                                                                 |

|     | 6.1 | The SPM multidimensional packet classification algorithm $\dots \dots \dots$ |

|     | 6.2 | Simulation Methodology                                                                                                                                                       |

|     |     | 6.2.1 The Cacti Integrated Memory Simulator                                                                                                                                  |

|     |     | 6.2.2 Simulation performance metrics and parameters                                                                                                                          |

|     | 6.3 | Simulation Results                                                                                                                                                           |

|     | 6.4 | Summary                                                                                                                                                                      |

| VII |     | VANCED CYBERATTACK DETECTION WITH COMPUTATIONAL IN-<br>LLIGENCE SYSTEMS                                                                                                      |

|     | 7.1 | Datasets and Performance Metrics for Evaluating Cyberattack Detection<br>Systems                                                                                             |

|     |     | 7.1.1 Datasets                                                                                                                                                               |

|     |     | 7.1.2 Performance Metrics                                                                                                                                                    |

|     | 7.2 | Cyberattack Detection with Hybrid Intelligent Systems 122                                                                                                                    |

|     |     | 7.2.1 The HBSOM Classification Algorithm                                                                                                                                     |

|     |     | 7.2.2 Simulation Results $\ldots \ldots 127$                                      |

|     | 7.3 | Cyberattack Detection with Ensembles of Computational Intelligence Systems                                                                                                   |

|     |     | 7.3.1 The NNO Classification Algorithm                                                                                                                                       |

|     |     | 7.3.2 Simulation Results                                                                                                                                                     |

| 7.4 Summ      | ary                                        | 136 |

|---------------|--------------------------------------------|-----|

| VIII CONCLUSI | ON                                         | 138 |

| APPENDIX A    | CACTI 6.5 CONFIGURATION EXAMPLE            | 141 |

| APPENDIX B    | CACTI 6.5 SIMULATION OUTPUT                | 145 |

| APPENDIX C    | CACTI 6.5 CONFIGURATION EXAMPLE WITH MCPAT | 148 |

| APPENDIX D    | CACTI 6.5 SIMULATION OUTPUT WITH MCPAT     | 152 |

| APPENDIX E    | RAW CACTI SIMULATION DATA                  | 155 |

| REFERENCES .  |                                            | 159 |

| VITA          |                                            | 172 |

## LIST OF TABLES

| 1  | A real-world firewall filter-set                                                                                   | 10  |

|----|--------------------------------------------------------------------------------------------------------------------|-----|

| 2  | An example of points, prefixes, and ranges used by packet filters                                                  | 10  |

| 3  | An example of SNORT detection rules (filters)                                                                      | 13  |

| 4  | An example of a simple 2-dimensional packet classifier                                                             | 17  |

| 5  | A one-dimensional routing table of prefixes                                                                        | 27  |

| 6  | An example of prefix expansion                                                                                     | 30  |

| 7  | Resolving prefix collisions with prefix capture                                                                    | 31  |

| 8  | Generic model for the data structure of a trie node                                                                | 31  |

| 9  | Data represented by the trie of Figure 20                                                                          | 45  |

| 10 | The ideas of data, information, semantics, knowledge, and perspectives. $\ . \ .$                                  | 74  |

| 11 | The meta-language of the semantic data structure                                                                   | 75  |

| 12 | Conceptual typing production rules of the semantic space                                                           | 77  |

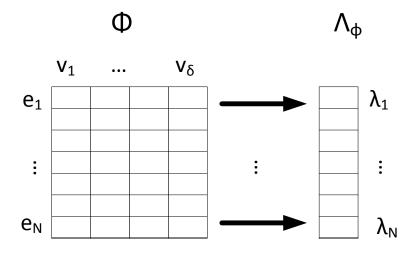

| 13 | The path matrix for the CPHG from Figure 30                                                                        | 82  |

| 14 | Theoretical space-time bounds for packet classification algorithms                                                 | 90  |

| 15 | Line rates, packets per second, and classification rates                                                           | 91  |

| 16 | Two dimensional packet filters                                                                                     | 94  |

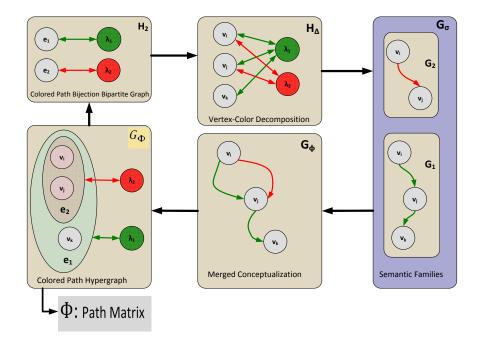

| 17 | Correspondences between the path merger processes and the semantic association network.                            | 100 |

| 18 | Parameters for a 3-dimensional packet classifier illustrating the construction of the SPM hypergrid                | 102 |

| 19 | A set of packet filters with parameters given by Table 18. $\ldots$                                                | 104 |

| 20 | Partitioned path matrix corresponding to the colored paths from the semantic association network of Figure 41      | 106 |

| 21 | Metrics used to evaluate the performance of the SPM hardware algorithm                                             | 111 |

| 22 | Perspectives of the positive and negative classes for mixed detection binary classification.                       | 122 |

| 23 | Basis parameters of the performance metrics defined in Table 24                                                    | 122 |

| 24 | Definitions and nomenclature of the performance metrics used to evaluate<br>the proposed classification algorithms | 123 |

| 25 | Classification results produced by simulations of the HBSOM and NBLN algorithms.                                   | 128 |

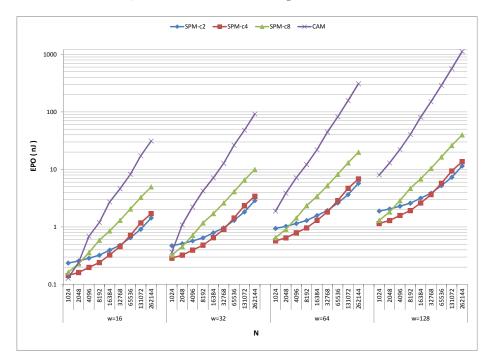

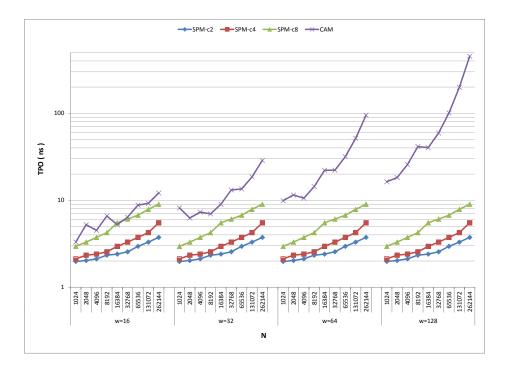

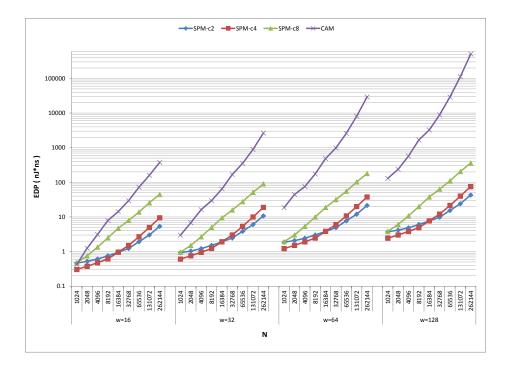

| 26 | EPO, TPO, and EDP data for $w = (16, 32)$                           | 156 |

|----|---------------------------------------------------------------------|-----|

| 27 | EPO, TPO, and EDP data for $w = (64, 128)$                          | 157 |

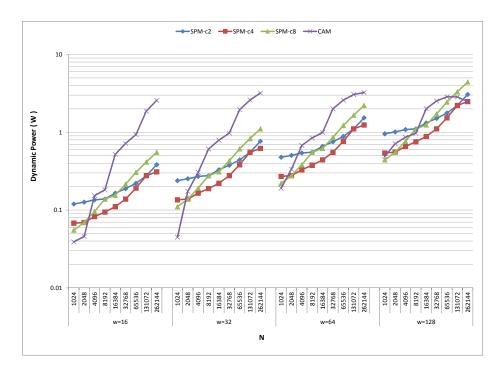

| 28 | Dynamic, static, and total power consumption data in units of Watts | 158 |

# LIST OF FIGURES

| 1  | The inside-outside topology-dependent firewall perspective                                   | 8  |

|----|----------------------------------------------------------------------------------------------|----|

| 2  | A simple network system with a firewall and its filter-set                                   | 9  |

| 3  | The behavioral overlap of legitimate users and intruders                                     | 12 |

| 4  | A taxonomy of intrusion response systems [141]                                               | 15 |

| 5  | The geometric perspective of packet classification.                                          | 17 |

| 6  | Primary functional components of the autonomous distributed firewall archi-<br>tecture.      | 20 |

| 7  | The DIADEM firewall architecture                                                             | 21 |

| 8  | The firewall network system for worm defense.                                                | 23 |

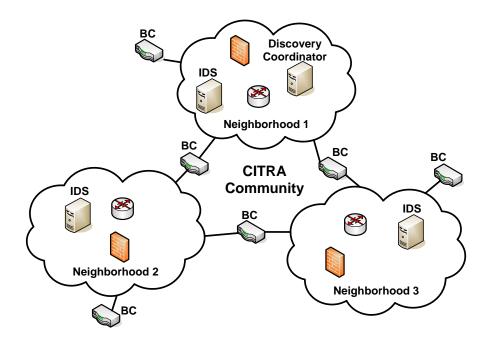

| 9  | The cooperative intrusion traceback and response architecture                                | 24 |

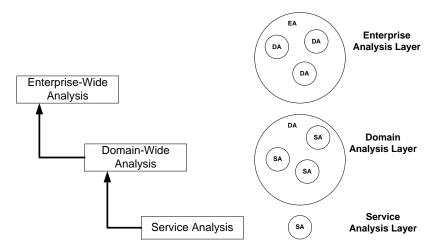

| 10 | Three-layer analysis within EMERALD                                                          | 25 |

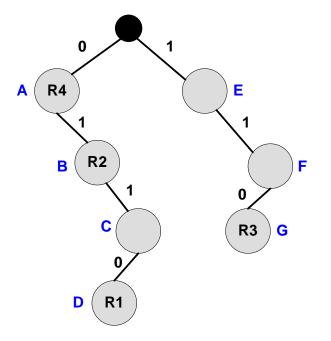

| 11 | A unibit trie for the prefixes from Table 5                                                  | 27 |

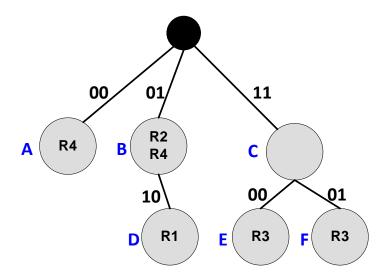

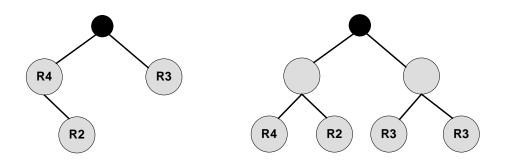

| 12 | A multibit trie with stride of two for the prefixes from Table 5                             | 29 |

| 13 | Pushing information fields to the leaf nodes in a trie                                       | 32 |

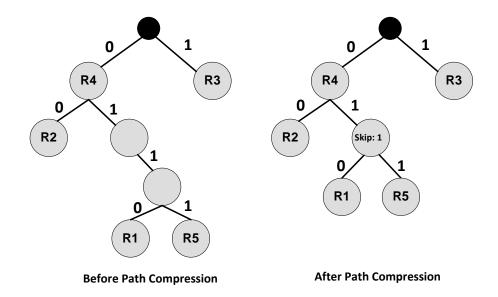

| 14 | Illustration of the path compression concept.                                                | 33 |

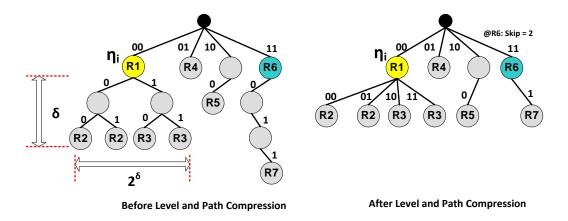

| 15 | Level and path compression techniques of the LC-trie algorithm                               | 34 |

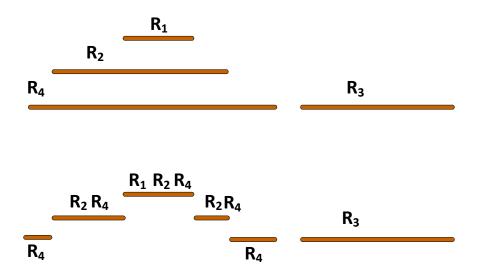

| 16 | Creating disjoint ranges from the filter-set of Table 5                                      | 35 |

| 17 | Assigning the best matching prefixes to the basic intervals from Table 5                     | 36 |

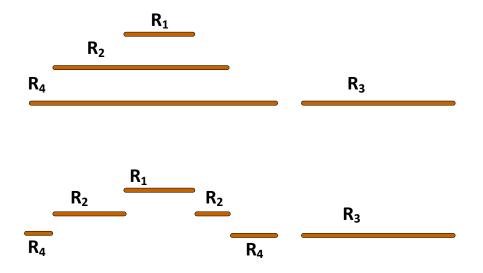

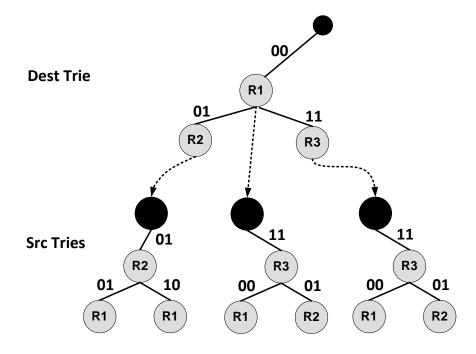

| 18 | A two dimensional source/destination prefix trie                                             | 38 |

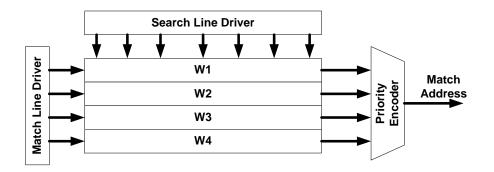

| 19 | Block diagram of a content addressable memory and its main functional components             | 41 |

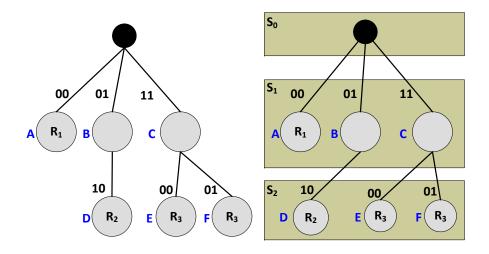

| 20 | Generic trie-to-hardware mapping techniques                                                  | 45 |

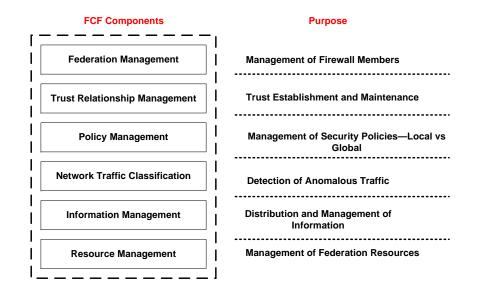

| 21 | The FCF functional components.                                                               | 56 |

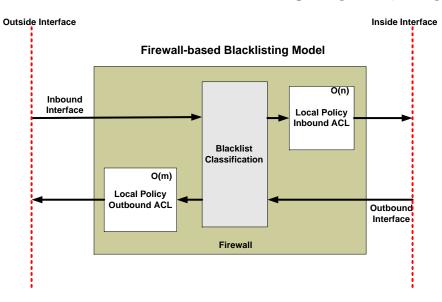

| 22 | The DFAR firewall-based blacklist enforcement model                                          | 59 |

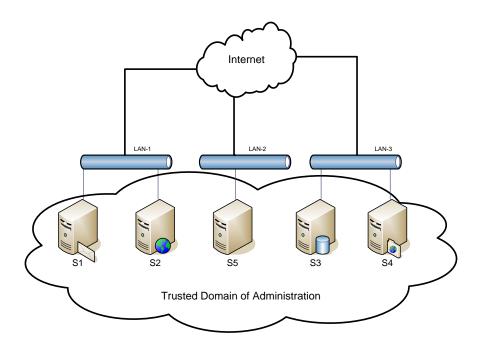

| 23 | A trusted domain of administration.                                                          | 60 |

| 24 | Quasi-quarantine process with DFAR                                                           | 61 |

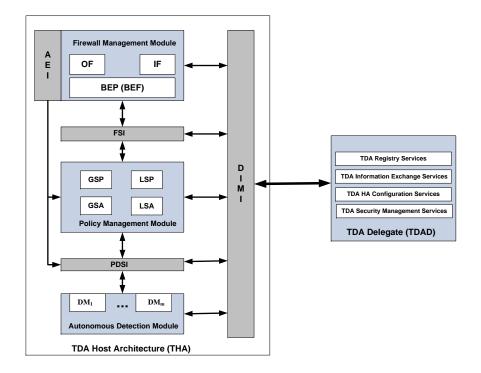

| 25 | The distributed firewall and active response architecture                                    | 62 |

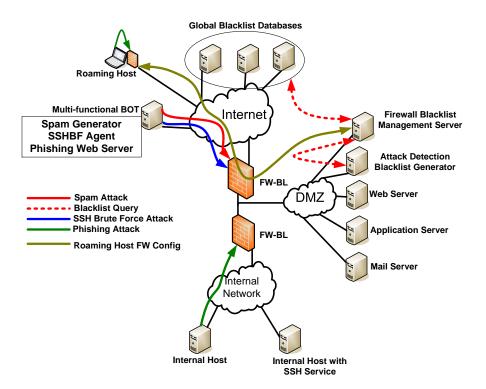

| 26 | Distributed blacklisting systems with DFAR                                                   | 69 |

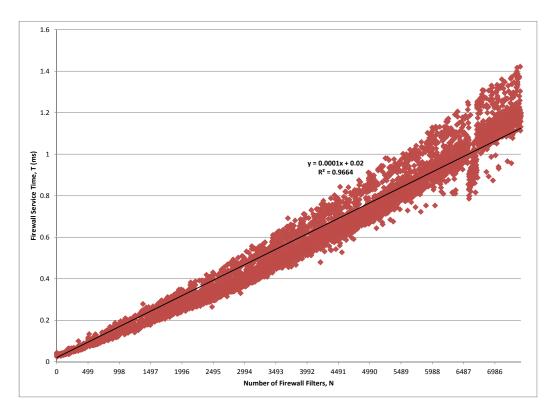

| 27 | Experimental results of firewall service time versus N for an enterprise-class email server. | 71 |

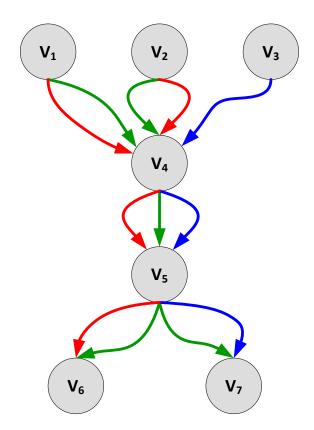

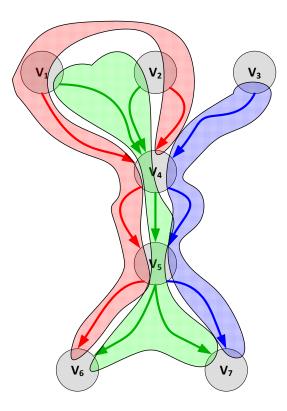

| 28 | A simple edge-colored multi-digraph                                                                                             | 79  |

|----|---------------------------------------------------------------------------------------------------------------------------------|-----|

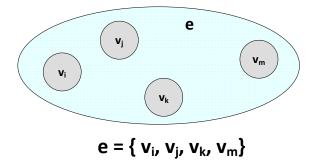

| 29 | A hyperedge enclosing three vertices                                                                                            | 80  |

| 30 | A colored path hypergraph                                                                                                       | 81  |

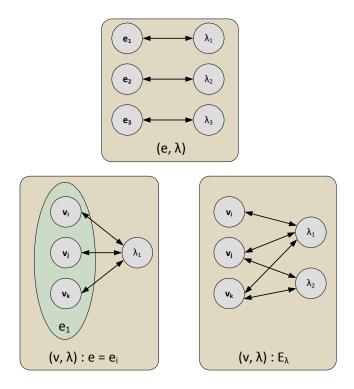

| 31 | A correspondence relationship between the vertices and edges of the CPHG and the semantic colors.                               | 82  |

| 32 | General <i>m</i> -to- <i>n</i> relationships between the vertices, edges, and colors of the CPHG                                | 83  |

| 33 | The family of graph transformations of the semantic association system                                                          | 88  |

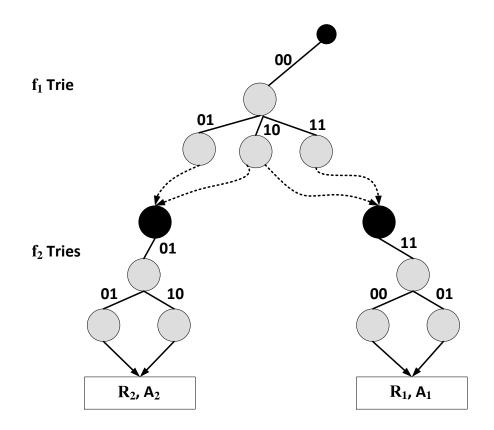

| 34 | Two dimensional MBT representation of the packet filters from Table 16. $% \left( {{{\rm{T}}_{{\rm{T}}}}_{{\rm{T}}}} \right)$ . | 95  |

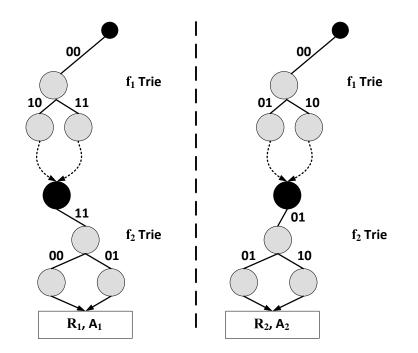

| 35 | Independent MBT encodings of the packet filters from Table 16 with each filter having its own collection of prefix tries.       | 96  |

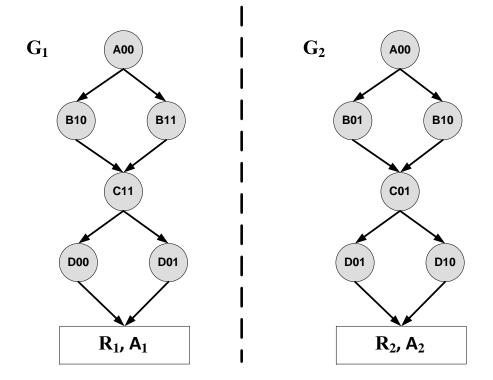

| 36 | Labeled directed acyclic graph transformation of the MBTs from Figure 35.                                                       | 97  |

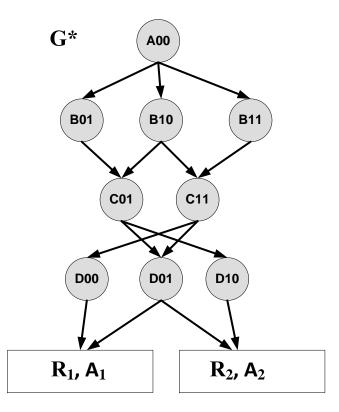

| 37 | The directed acyclic graph produced by merging the filter graphs of Figure 36                                                   | 98  |

| 38 | A path-merged DAG containing induced transitivity                                                                               | 100 |

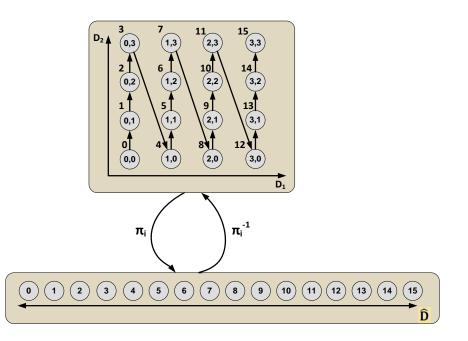

| 39 | Dimensional folding as the cross-product of subinterval domains generated<br>by $W_c = (w, c)$                                  | 102 |

| 40 | The hypergrid generated from the parameters in Table 18                                                                         | 104 |

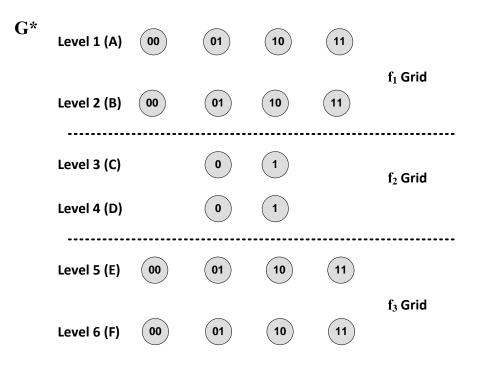

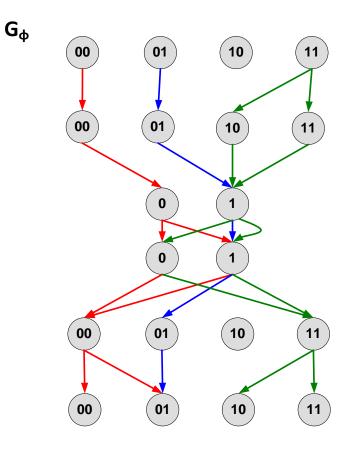

| 41 | The semantic association network encoding the filters from Table 19                                                             | 105 |

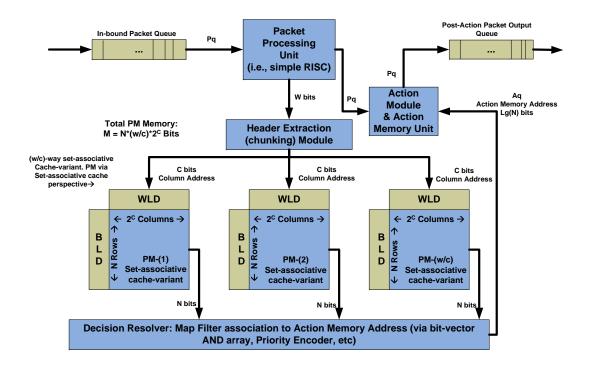

| 42 | Block diagram illustrating a hardware-based implementation of the SPM algorithm.                                                | 108 |

| 43 | Comparing EPO versus $(N, w, c)$ for the SPM algorithm and the content addressable memory.                                      | 112 |

| 44 | Comparing TPO versus $(N, w, c)$ for the SPM algorithm and the content addressable memory                                       | 113 |

| 45 | Comparing EDP versus $(N, w, c)$ for the SPM algorithm and the content addressable memory.                                      | 114 |

| 46 | Comparing dynamic power versus $(N, w, c)$ for the SPM algorithm and the content addressable memory.                            | 115 |

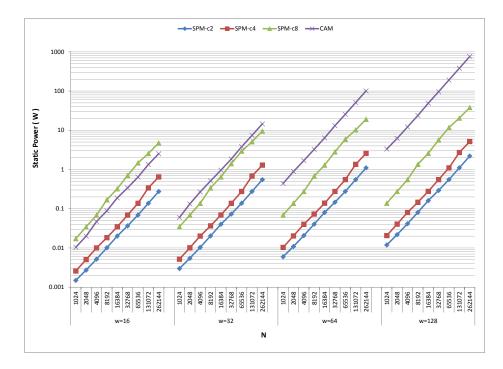

| 47 | Comparing static power versus $(N, w, c)$ for the SPM algorithm and the content addressable memory.                             | 115 |

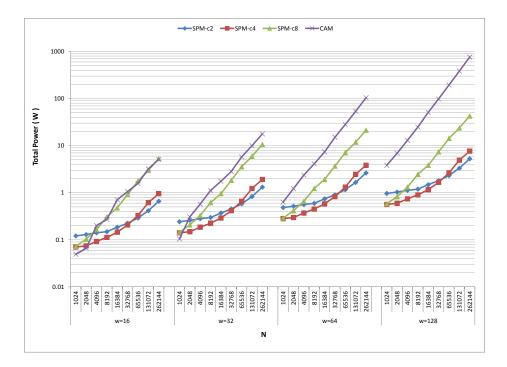

| 48 | Comparing total power versus $(N, w, c)$ for the SPM algorithm and the content addressable memory.                              | 116 |

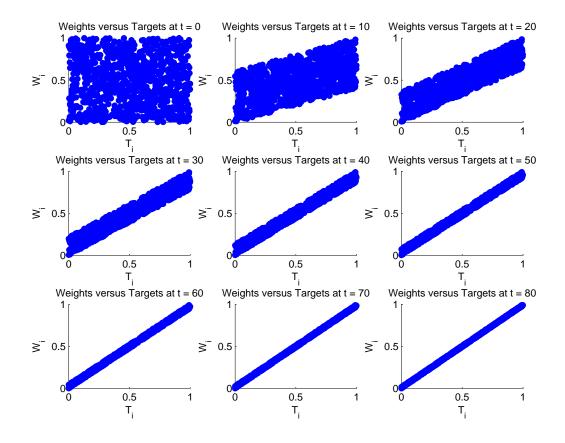

| 49 | Learning weights.                                                                                                               | 126 |

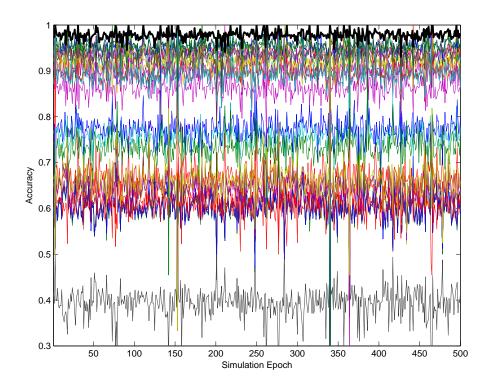

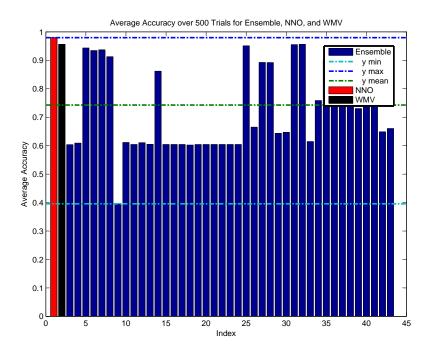

| 50 | Accuracies of the individual ensemble members and the neural network oracle over the 500 trials.                                | 132 |

| 51 | Bar chart revealing the average accuracies produced over the 500 trials 133           |

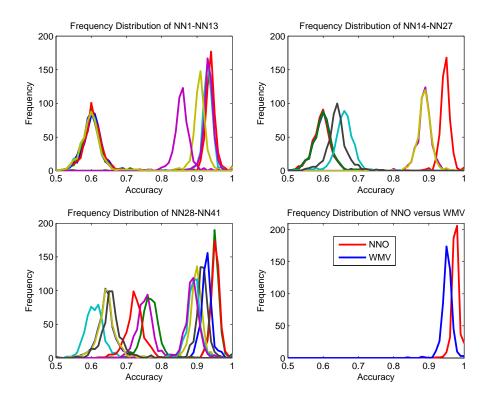

|----|---------------------------------------------------------------------------------------|

| 52 | Frequency distribution of the accuracies for each system over 500 simulation trials   |

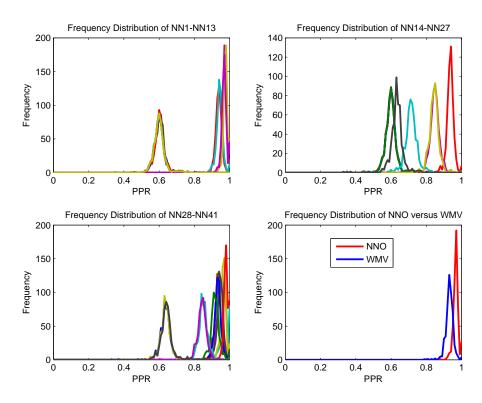

| 53 | Frequency distribution of the PPR for each system over 500 simulation trials. $134$   |

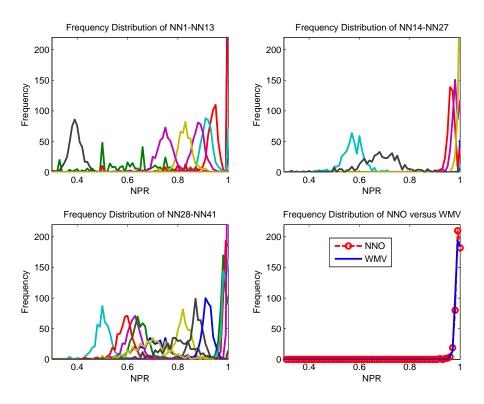

| 54 | Frequency distribution of the NPR for each system over 500 simulation trials. 135     |

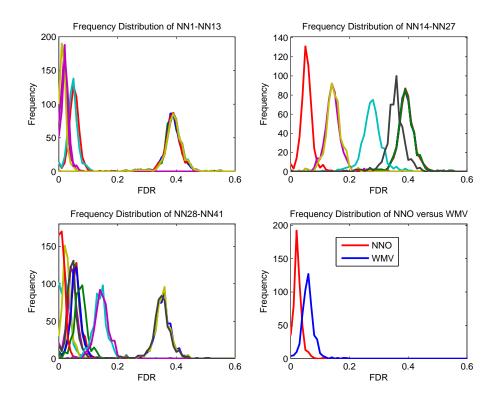

| 55 | Frequency distribution of the FDR for each system over 500 simulation trials. 135 $$  |

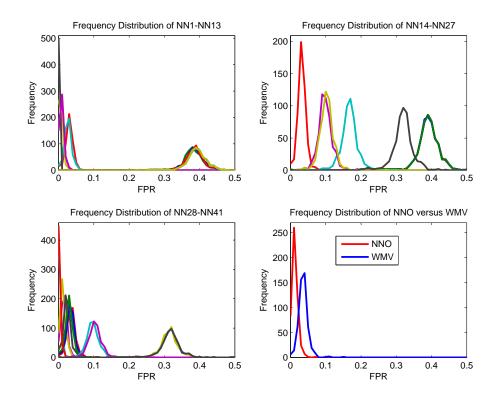

| 56 | Frequency distribution of the FPR for each system over $500$ simulation trials. $136$ |

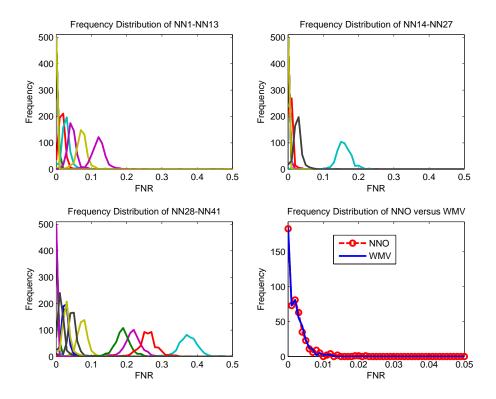

| 57 | Frequency distribution of the FNR for each system over $500$ simulation trials. $137$ |

## NOMENCLATURE

| ACL   | Access Control List.                                   |

|-------|--------------------------------------------------------|

| ADF   | Autonomic Distributed Firewall.                        |

| ADM   | Autonomous Detection Module.                           |

| AEI   | Audit Export Interface.                                |

| ANN   | Artificial Neural Network.                             |

| BC    | Boundary Controller.                                   |

| BEF   | Blocking Enforcement Filter.                           |

| BLN   | Bayesian Learning Network.                             |

| ВМР   | Best Matching Prefix.                                  |

| BMU   | Best Matching Unit.                                    |

| САМ   | Content Addressable Memory.                            |

| СВТ   | Complete Binary Tree.                                  |

| CIDR  | Classless Interdomain Routing.                         |

| CIS   | Computational Intelligence System.                     |

| CMS   | Central Management Server.                             |

| СР    | Cross Producting.                                      |

| СРВ   | Colored Path Bijection.                                |

| СРЕ   | Controlled Prefix Expansion.                           |

| CPHG  | Colored Path Hypergraph.                               |

| DAG   | Directed Acyclycic Graph.                              |

| DARPA | Defense Advanced Research Projects Agency.             |

| DDoS  | Distributed Denial of Service.                         |

| DFAR  | Distributed Firewall and Active Response Architecture. |

| DIMI  | Distributed Infrastructure Management Interface.       |

| DM    | Detection Modules.                                     |

| DT    | Destination Trie.                                      |

| EDP   | Energy Delay Product.                                  |

|       | וו ידו וו ד                                        |

|-------|----------------------------------------------------|

| EFW   | Embedded Firewall.                                 |

| EGoT  | Extended Grid of Tries.                            |

| ENN   | Evolutionary Neural Networks.                      |

| EPO   | Energy Per Operation.                              |

| FCF   | Firewall Collaboration Framework.                  |

| FDAG  | Filter Directed Acyclic Graph.                     |

| FDR   | False Discovery Rate.                              |

| FMM   | Firewall Management Module.                        |

| FN    | False Negative.                                    |

| FNR   | False Negative Rate.                               |

| FP    | False Positive.                                    |

| FPR   | False Positive Rate.                               |

| FSI   | Filter Specification Interface.                    |

| GA    | Genetic Algorithm.                                 |

| GoT   | Grid of Tries.                                     |

| GPP   | Global Preemptive Protection.                      |

| HBSOM | Hybrid Bayesian and Self-organizing Map Algorithm. |

| НРВ   | Highly Predictive Blacklisting.                    |

| IBS   | Interval Binary Search.                            |

| IDS   | Intrusion Detection System.                        |

| IF    | Inbound Filters.                                   |

| IP    | Internet Protocol.                                 |

| IPv4  | Internet Protocol version 4.                       |

| IPv6  | Internet Protocol version 6.                       |

| IRS   | Intrusion Response System.                         |

| ISP   | Internet Service Provider.                         |

| ITR   | Induced Transitive Relations.                      |

| ITU-T | International Telecommunication Union.             |

| KDD   | Knowledge Discovery in Data.                       |

|       |                                                    |

| LAN   | Local Area Network.                         |

|-------|---------------------------------------------|

| LC    | Level Compression.                          |

| LPM   | Longest Prefix Match.                       |

| LSA   | Local Security Audits.                      |

| LSP   | Local Security Policy.                      |

| МВТ   | Multibit Trie.                              |

| MDT   | Multidimensional Trie.                      |

| MVQ   | Multivalence Vertex Query.                  |

| NAE   | National Academy of Engineering.            |

| NBLN  | Naive Bayesian Learning Network.            |

| NIC   | Network Interface Card.                     |

| NMOS  | N-type Metal Oxide Semiconductor.           |

| NN    | Neural Network.                             |

| NNO   | Neural Network Oracle Algorithm.            |

| NPR   | Negative Prediction Rates.                  |

| OC    | Optical Carrier.                            |

| OF    | Outbound Filter.                            |

| PC    | Packet Classification.                      |

| PDS   | Policy Description Specification.           |

| PDSI  | Policy Description Specification Interface. |

| РМ    | Path Matrix.                                |

| PMDAG | Path Merged Directed Acyclic Graph.         |

| РММ   | Policy Management Module.                   |

| РМР   | Path Merger Process.                        |

| PPR   | Positive Prediction Rate.                   |

| RBP   | Resilient Back Propagation.                 |

| RFC   | Recursive Flow Classification.              |

| RPN   | Resilient Propagation Neural Network.       |

| SAN   | Semantic Association Network.               |

|       |                                             |

| SAS   | Semantic Association System.               |

|-------|--------------------------------------------|

| SCADA | Supervisory Control and Data Acquisition.  |

| SDS   | Search Data Structure.                     |

| SOM   | Self-organizing Map.                       |

| SPM   | Semantic Path Merger.                      |

| SRAM  | Static Random Access Memory.               |

| SSH   | Secure Shell.                              |

| SVM   | Support Vector Machine.                    |

| ТСАМ  | Ternary Content Addressable Memory.        |

| ТСР   | Transmission Control Protocol.             |

| TDA   | Trusted Domain of Administration.          |

| TDAD  | Trusted Domain of Administration Delegate. |

| ТНА   | TDA Host Architecture.                     |

| TN    | True Negative.                             |

| ТР    | True Positive.                             |

| тро   | Time Per Operation.                        |

| TRM   | Trust Relationship Management.             |

| ттн   | Trie to Hardware.                          |

| UBT   | Unibit Trie.                               |

| UDP   | User Datagram Protocol.                    |

| VLP   | Vertex Labeled Path.                       |

| VST   | Variable Stride Trie.                      |

| WMV   | Weighted Majority Vote.                    |

### SUMMARY

Internet security continues to be a complex and challenging problem. Security mechanisms such as authentication, data integrity, and data confidentiality along with intrusion detection, intrusion prevention, and firewall systems have traditionally provided respectable levels of protection. However, malicious actors and their associated attack technologies have advanced significantly. Moreover, Internet-enabled platforms such as cyber-physical infrastructures, advanced mobile voice communication systems, the mobile Internet, voiceover-Internet Protocol (VoIP), cloud computing, the Internet-of-Things, vehicular networks, aerospace networks, intelligent transportation systems, and smart-home environments will provide countless new attack vectors and opportunities for malicious actors. Consequently, advanced security mechanisms and defense methodologies are needed for the continual protection of traditional Internet systems along with these emerging Internet-enabled platforms.

However, existing security systems and architectures have a foundation based on the concepts of topological perimeters, non-cooperative and isolated operation, reactive reconfiguration, and human advisory. Perimeter-based, isolated, non-cooperative, and administratively reactive techniques are becoming ineffective, and this is especially true for emergent platforms such as the mobile Internet and cloud computing in which the constituent computational and networking resources reside outside of enterprise topologies and perimeters. Isolated and non-cooperative security mechanisms operate within a *confined awareness domain*, and knowledge related to new security occurrences are not shared outside of the awareness domain. Isolated is implied by confinement, and non-cooperative is implied by not sharing knowledge with other awareness domains. This imposes a significant impediment in terms of efficient, global-scale Internet security. Lastly, administratively reactive relates to techniques whereby a human security administrator reacts to newly discovered security events instead of automated, computer-driven reactions. Human reaction and remediation times are far too slow to counter the impact of many classes of high-speed, large-scale cyberattacks.

According to the National Academy of Engineering (NAE), securing the Internet and its associated cybersystems is one of the most complex engineering challenges ever faced by the engineering community. The NAE claims that cybersecurity cannot be achieved with traditional perimeter defenses, that new methods of authentication for hardware, software, data, and users are needed, that new approaches to the design of secure software should be considered, and that new methods are required for monitoring, detecting, and responding to cyberattacks. Consequently, the NAE and its committee on Engineering Grand Challenges has identified cyberspace security as one of fourteen Grand Challenges faced by engineers in the  $21^{st}$  century.

This dissertation provides novel algorithms, theories, and supporting frameworks to significantly improve the growing problem of Internet security. A premise forming a basis for the objectives and contributions of this dissertation is that distributed, collaborative, and autonomic defense methodologies are needed in order to achieve reliable Internet security because the sheer volume of modern day cyberattacks, their permutation capabilities, their sophistication, and their speed cause isolated, non-collaborative, administratively-reactive response and remediation methods to be ineffective. Consequently, the objectives of this dissertation research were (1) to study the characteristics needed for reliable distributed Internet security architectures and infrastructures, (2) to design a modular, adaptive, and integrable framework for distributed Internet security infrastructures, (3) to develop robust solutions addressing the fundamental packet classification problem, and (4) to develop new classification algorithms for advanced cyberattack detection systems.

As a result of these objectives, the contributions provided by this dissertation are the following:

- A distributed firewall and active response architecture.

- A firewall-based blacklist classification and enforcement model.

- A theory of semantic association systems.

- A semantic path merger packet classification algorithm and its hardware implementation.

- Advanced cyberattack detection algorithms based on computational intelligence systems.

The distributed firewall and active response architecture is a modular, adaptive, and integrable distributed security framework that enables cyber devices within an organization's cyber infrastructure to participate in the detection of and response to cyberattacks. The architecture is a supporting contribution that establishes the foundation upon which the core contributions of this dissertation are framed. Particularly, the distributed firewall and active response architecture requires (1) efficient packet classification algorithms to enable its novel firewall-based blacklist classification and enforcement model and (2) effective classification algorithms for cyberattack detection. While studying packet classification and cyberattack detection algorithms, the theory of semantic association systems was devised and formulated. The theory of semantic association systems was inspired by the emerging field of semantic computing. The theory defines a compositional model and a family of graph theoretic constructs supporting the notion of merged conceptualization. From this theory and the notion of merged conceptualization, the semantic path merger packet classification algorithm was derived along with its hardware-based implementation. The theory of semantic association systems, the semantic path merger algorithm, and the hardware implementation of the semantic path merger algorithm as a packet classification system are the core contributions of this dissertation. Finally, two novel cyberattack detection algorithms have been developed. The first detection algorithm is a hybridization of self-organizing maps and naive Bayesian learning networks. The second detection algorithm is a neural network ensemble coupled with a parametrically optimized neural network oracle that combines ensemble classification results. The oracle's network configuration is parametrically optimized with genetic algorithms.

#### CHAPTER I

## INTRODUCTION

Internet security continues to be a complex and challenging problem. Security mechanisms such as authentication, data integrity, and data confidentiality services along with intrusion detection, intrusion prevention, and firewall systems have traditionally provided respectable levels of protection. However, malicious actors and their associated attack technologies have advanced significantly. Moreover, Internet-enabled platforms such as cyber-physical infrastructures [30, 32, 40, 35, 168], advanced mobile voice communication systems [29], the mobile Internet [109, 122], voice-over-Internet Protocol (VoIP) [22], cloud computing [34, 46, 126], the Internet-of-Things [44], vehicular networks [65, 78, 165], aerospace networks [91], intelligent transportation systems [75], and smart-home environments [103, 169] will provide countless new attack vectors and opportunities for malicious actors. Consequently, advanced security mechanisms and defense methodologies are needed for the continual protection of traditional Internet systems along with these emerging Internet-enabled platforms [24, 130, 23, 125, 163, 117, 160, 43].

In a recent study, Kim et al. [81] claim that modern day cyberattacks are increasingly sophisticated, coordinated, and financially motivated. A report by Symantec [143] reveals that attacks are increasingly targeting enterprises, are increasingly Web-based, and are increasingly driven by financial gains available within the Internet underground economy. Their report also reveals an increasing usage of openly available attack tools. According to the Institute for Security Technologies Studies at Dartmouth college [66], over ten thousand attack tools were freely available on the Internet in 2004. In a recent report provided by the Georgia Tech Information Security Center [47], over 100,000 new malware samples are discovered each day.

Designers of Internet security architectures suggest that security cannot be provided by monolithic perimeter-based processes within a computational or networking system and advocate the incorporation of security mechanisms into each primary element contributing to a computing and communication framework [110]. Moreover, utilization of highly coordinated and cooperating security mechanisms are considered to be one of the most effective ways to prevent large-scale, persistent, targeted attacks [129]. Further, the exchange of information describing the attributes of attacks and malicious actors have been shown to significantly enhance security defense mechanisms [124, 161]. Consequently, security architectures and infrastructures that support methodologies for automatically detecting and responding to cyberattacks are needed to enable effective defense-in-depth strategies and robust cybersecurity systems [9, 63, 72, 123, 132]. However, existing security systems and architectures have a foundation based on the concepts of topological perimeters, non-cooperative and isolated operation, reactive reconfiguration, and human advisory. Perimeter-based, isolated, non-cooperative, and administratively reactive techniques are becoming ineffective, and this is especially true for emergent platforms such as the mobile Internet and cloud computing in which the constituent computational and networking resources reside outside of enterprise topologies and perimeters. Isolated and non-cooperative security mechanisms operate within a *confined awareness domain*, and knowledge related to new security occurrences are not shared outside of the awareness domain. Isolated is implied by confinement, and non-cooperative is implied by not sharing knowledge with other awareness domains. This imposes a significant impediment in terms of efficient, global-scale Internet security. Lastly, administratively reactive relates to techniques whereby a human security administrator reacts to newly discovered security events instead of automated, computer-driven reactions. Human reaction and remediation times are far too slow to counter the impact of many classes of high-speed, large-scale cyberattacks.

According to the National Academy of Engineering (NAE), securing the Internet and its associated cybersystems is one of the most complex engineering challenges ever faced by the engineering community [106]. The NAE claims that cybersecurity cannot be achieved with traditional perimeter defenses, that new methods of authentication for hardware, software, data, and users are needed, that new approaches to the design of secure software should be considered, and that new methods are required for monitoring, detecting, and responding to cyberattacks [106].

This dissertation provides novel algorithms, theories, and supporting frameworks to significantly improve the growing problem of Internet security. A premise forming a basis for the objectives and contributions of this dissertation is that distributed, collaborative, and autonomic defense methodologies are needed in order to achieve reliable Internet security because the sheer volume of modern day cyberattacks, their permutation capabilities, their sophistication, and their speed cause isolated, non-collaborative, administratively-reactive response and remediation methods to be ineffective. Consequently, the objectives of this dissertation research were (1) to study the characteristics needed for reliable distributed Internet security architectures and infrastructures, (2) to design a modular, adaptive, and integrable framework for distributed Internet security infrastructures, (3) to develop robust solutions addressing the fundamental packet classification problem, and (4) to develop new classification algorithms for advanced cyberattack detection systems.

As a result of these objectives, the contributions provided by this dissertation are the following:

- A distributed firewall and active response architecture.

- A firewall-based blacklist classification and enforcement model.

- A theory of semantic association systems.

- A semantic path merger packet classification algorithm and its hardware implementation.

- Advanced cyberattack detection algorithms based on computational intelligence systems.

The distributed firewall and active response architecture is a modular, adaptive, and integrable distributed security framework that enables cyber devices within an organization's cyber infrastructure to participate in the detection of and response to cyberattacks. The

architecture is a supporting contribution that establishes the foundation upon which the core contributions of this dissertation are framed. Particularly, the distributed firewall and active response architecture requires (1) efficient packet classification algorithms to enable its novel firewall-based blacklist classification and enforcement model and (2) effective classification algorithms for cyberattack detection. While studying packet classification and cyberattack detection algorithms, the theory of semantic association systems was devised and formulated. The theory of semantic association systems was inspired by the emerging field of semantic computing. The theory defines a compositional model and a family of graph theoretic constructs supporting the notion of merged conceptualization. From this theory and the notion of merged conceptualization, the semantic path merger packet classification algorithm was derived along with its hardware-based implementation. The theory of semantic association systems, the semantic path merger algorithm, and the hardware implementation of the semantic path merger algorithm as a packet classification system are the core contributions of this dissertation. Finally, two novel cyberattack detection algorithms have been developed. The first detection algorithm, which is referred to as HBSOM, is a hybridization of self-organizing maps and naive Bayesian learning networks. The second detection algorithm, which is called NNO, consists of a neural network ensemble coupled with a parametrically optimized neural network oracle that combines ensemble classification results. The oracle's network configuration is parametrically optimized with genetic algorithms.

The remainder of this dissertation is organized as follows. Chapter 2 provides an overview of the basic technological concepts underlying the primary research thrusts presented in this dissertation. Chapter 3 contains background material and discussion of related work in distributed Internet security architectures, packet classification algorithms, and cyberattack detection with classification algorithms implemented by computation intelligence systems. In chapter 4, the distributed firewall and active response architecture is presented. Chapter 5 introduces the novel theory of semantic association systems. In chapter 6, a new packet classification algorithm based on semantic path merger is introduced. Further, chapter 6 provides the implementation details of the semantic path merger

algorithm as a hardware-based packet classification system. In Chapter 7, the HBSOM and NNO algorithms are introduced as new classification algorithms for the cyberattack detection problem. Finally, the dissertation concludes with chapter 8.

### CHAPTER II

#### CONCEPTS

In this chapter, the basic concepts underlying firewalls, intrusion detection, intrusion prevention, and packet classification are introduced.

## 2.1 Terminology

The International Telecommunication Union (ITU) and its ITU-T X.1205 Overview of Cybersecurity [67] provides the following definition of cybersecurity:

"Cybersecurity is the collection of tools, policies, security concepts, security safeguards, guidelines, risk management approaches, actions, training, best practices, assurance and technologies that can be used to protect the cyber environment and organization and user's assets. Organization and user's assets include connected computing devices, personnel, infrastructure, applications, services, telecommunications systems, and the totality of transmitted and/or stored information in the cyber environment. Cybersecurity strives to ensure the attainment and maintenance of the security properties of the organization and user's assets against relevant security risks in the cyber environment. The general security objectives comprise the following: Availability, Integrity (which may include Authenticity and Non-repudiation), and Confidentiality"

Three key concepts form the core of cybersecurity problems: vulnerabilities, threats, and attacks. A vulnerability is any weakness contained within a computing or networking system that can be exploited. A threat is defined as any process that can potentially violate the security policies of a system. An attack is considered to be any active process that deliberately seeks to violate the security polices of a system.

Organizations seek to protect their computational and networking infrastructures based on defense-in-depth strategies. The objectives of this strategy are to reduce the impact of attacks that successfully exploit vulnerabilities within the system and to reduce the number of threats within the system. The design of systems using defense-in-depth strategies should be founded on the ideas of security architectures and security management infrastructures. These two concepts have been defined by Shirey [135] as follows. A security architecture is a plan and set of principles that describe (a) the security services that a system is required to provide to meet the needs of its users, (b) the system elements required to implement the services, and (c) the performance levels required in the elements to deal with the threat environment. A security management infrastructure includes system elements and activities that support security policy by monitoring and controlling security services and mechanisms, distributing security information, and reporting security events.

### 2.2 Firewalls

Firewalls are security mechanisms that control the flow of network traffic, i.e., communication packets, into or out of a communication system [26]. The flow of network traffic through a firewall is governed by *security policies*, which are defined by a collection of N*packet filters* (or filters for short) written in the native language of a particular firewall technology. Sometimes, packet filters are referred to as firewall rules.

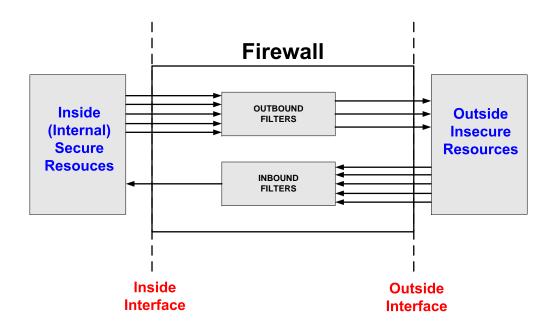

Firewalls are dependent on network topology such that filters are assigned to the direction of traffic flow relative to the orientation of the firewall with respect to the virtual resources it protects. In particular, a firewall provides an interface between *secure resources* and *insecure resources*. Secure resources reside behind an *inside interface* of the firewall, whereas insecure resources reside beyond an *outside interface* of the firewall. Figure 1 illustrates the idea of a firewall and its inside-outside topology-dependent perspective.

Firewall designs are constructed by the *Principle of Least Privilege*, which is expressed as follows:

All communication traffic attempting to traverse a firewall must be explicitly permitted by a security policy. Otherwise, the traffic must be denied.

In other words, if a packet is processed by a firewall and does not match an explicitly defined filter, then the firewall must deny the packet's access into or out of the communication

Figure 1: The inside-outside topology-dependent firewall perspective.

system. The filtering process provided by firewalls is demonstrated by the arrows of Figure 1, which represent packet flows entering and leaving the outbound and inbound filter collections. The arrows leaving out of the inbound/outbound filter collections represent packet flows that matched one or more packet filters. Packet denial is represented by more arrows entering a filter collection (inbound or outbound) than ones leaving. The suppressed arrows represent packet flows that are denied by the firewall.

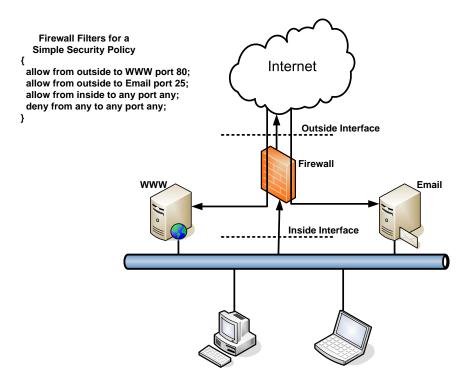

Figure 2 illustrates a simple perimeter firewall system. As can be seen in Figure 2, the collection of packet filters assigned to the firewall state that packets from the 'outside' and destined to the inside host named *WWW* with destination port 80 as well as those destined to the inside host named *Email* with destination port 25 are *explicitly* permitted (allowed). Further, the filter written as allow from inside to any port any provides unrestricted access from inside users/resources to any external Internet resource. The last filter, *deny from any to any port any*, is the default filter blocking any packets that do not match the first three filters, which enforces the principle of least privilege.

Table 1 shows a snippet of packet filters from a real-world enterprize-class Cisco PIX

Figure 2: A simple network system with a firewall and its filter-set.

firewall. The filters shown in Table 1 have a structure based on the so-called 5-tuple firewall filter, which includes *header field specifications* from the network and transport layers of the TCP/IP protocol stack. In particular, the 5-tuple includes the *(protocol type, source IP address, destination IP address)* from the network layer of the TCP/IP stack and the *(source port, destination port)* from the transport layer of the TCP/IP stack. In general, firewall packet filters can describe any value permissible by the specifications of the associated TCP/IP headers. For example, IPv4 addresses are contained in the source/destination IP headers in the network layer of the TCP/IP stack. Since IPv4 specifies 32 bits for IP addresses, then any one or more of the possible  $2^{32}$  IP addresses can be used for the source or destination IP addresses of a packet filter. In most cases, firewall filters specify the tuples as a collection of *points, prefixes,* or *ranges*. A 'point' is a single numeric value, a prefix is an expression based on the first *x*-bits of a value followed by wildcards in the remaining w - x bits where w is the number of bits allocated to the particular header field in the

| Intf       | Action                  | Proto                | SrcIP             | DestIP            | SrcPort | DestPort        |

|------------|-------------------------|----------------------|-------------------|-------------------|---------|-----------------|

| in         | permit                  | gre                  | 130.207.134.9     | 128.61.209.0/26   | any     | any             |

| in         | $\operatorname{permit}$ | $\operatorname{tcp}$ | 130.207.134.9     | 128.61.209.0/26   | any     | eq pptp         |

| in         | $\operatorname{permit}$ | gre                  | 130.207.134.9     | 128.61.209.128/26 | any     | any             |

| in         | $\operatorname{permit}$ | $\operatorname{tcp}$ | 130.207.134.9     | 128.61.209.128/26 | any     | eq pptp         |

| in         | $\operatorname{permit}$ | $\operatorname{tcp}$ | 128.61.252.110    | 143.215.254.64/29 | any     | eq https        |

| $_{ m in}$ | $\operatorname{permit}$ | $\operatorname{tcp}$ | 128.61.252.110    | 143.215.254.64/29 | any     | eq www          |

| in         | $\operatorname{permit}$ | $\operatorname{tcp}$ | 128.61.252.110    | 143.215.254.64/29 | any     | range $22$ $23$ |

| in         | $\operatorname{permit}$ | $\operatorname{tcp}$ | 128.61.5.0/24     | 143.215.254.64/29 | any     | eq https        |

| in         | $\operatorname{permit}$ | $\operatorname{tcp}$ | 128.61.5.0/24     | 143.215.254.64/29 | any     | eq www          |

| in         | $\operatorname{permit}$ | $\operatorname{tcp}$ | 128.61.5.0/24     | 143.215.254.64/29 | any     | range $22$ $23$ |

| in         | deny                    | ip                   | any               | any               | any     | any             |

|            |                         |                      |                   |                   |         |                 |

| out        | $\operatorname{permit}$ | ip                   | 128.61.210.0/24   | any               | any     | any             |

| out        | $\operatorname{permit}$ | ip                   | 128.61.211.0/24   | any               | any     | any             |

| out        | $\operatorname{permit}$ | ip                   | 128.61.212.0/24   | any               | any     | any             |

| out        | $\operatorname{permit}$ | ip                   | 128.61.213.0/24   | any               | any     | any             |

| out        | $\operatorname{permit}$ | ip                   | 143.215.254.8/29  | any               | any     | any             |

| out        | $\operatorname{permit}$ | ip                   | 143.215.254.56/29 | any               | any     | any             |

| out        | $\operatorname{permit}$ | ip                   | 143.215.254.64/29 | any               | any     | any             |

| out        | deny                    | ip                   | any               | any               | any     | any             |

Table 1: A real-world firewall filter-set.

TCP/IP stack, and a range is of the form [L, U] where L is the lower endpoint and U is the upper endpoint of a range. Table 2 gives an example of each. Prefixes are specified

Table 2: An example of points, prefixes, and ranges used by packet filters.

| Point        | Prefix         | Range      |

|--------------|----------------|------------|

| 128.61.208.3 | 128.61.55.0/24 | [20, 22]   |

| TCP          | 01000*         | [000, 110] |

| http = 80    | 10.20.*.*      | > 1023     |

by a certain number of most significant bits and are always inherently tied to the number of bits specified by a particular header field. For example, if the value 01000\* from the second row of Table 2 represents an IP address field, then an IP address where the first 5 bits equal 01000 will match the expression regardless of the remaining 32 - 5 = 27 bits. In this case, the first 5 bits are the most significant bits of the filter specification 01000\* and the remaining 27 bits are the least significant don't care bits with respect to the filter expression. The range specification of the last row of Table 2 specifies any value greater than 1023. However, since the header fields of the TCP/IP stack are specified by a particular number of w bits, the range specification > 1023 implies that the range is interpreted as  $[1024, 2^w - 1] = (1023, 2^w - 1]$ . For instance, if the range is based on the 16 bits of the TCP port number specification, then the range above is [1024, 65535].

### 2.3 Intrusion Detection

In general, cyberattack detection mechanisms are processes that collect data from within the cyber environment and utilize classification algorithms to determine the legitimacy of events associated with the data. A cyberattack detection system is a security mechanism that utilizes one or more cyberattack detection algorithms. A cyberattack prevention mechanism seeks to apply countermeasures that prevent adverse impacts caused by cyberattacks. A cyberattack prevention system employs one or more cyberattack detection mechanisms along with the associated techniques required to implement countermeasures.

An intrusion is defined as any unauthorized attempt to access cyber resources. Intrusion detection and intrusion detection systems are particular cases of the more general categories of cyberattack detection and cyberattack detection systems. The same is true for intrusion prevention and intrusion prevention systems. Consequently, intrusion detection/prevention and cyberattack detection/prevention will be used interchangeably throughout this dissertation.

Intrusion detection is concerned with the discovery of intruders attempting to gain unauthorized access to an organization's computing, networking, and information resources [8]. Intrusion detection is a process performed by an intrusion detection system (IDS) where events within a cyber environment are analyzed via audit data and sequences of events that indicate violations of an organization's security policies trigger alerts that notify security administrators of the abnormal system activities.

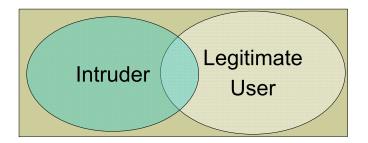

The fundamental premise underlying the design of an IDS is based on the idea of *behavior*. Understanding the behavior of computer users and processes is a central idea underlying the design of detection algorithms for intrusion detection systems. Particularly, the behavior of an intruder (human or agent) is assumed to be significantly different from the behaviors of legitimate users [142]. For example, in *most* cases, a legitimate user will not attempt to read to the contents of a system's password database. However, an intruder will *usually* attempt to retrieve the contents of the password database. The terms 'most' and 'usually' are highlighted to illustrate the *statistical* nature that actually underlies the *behavioral premise* of IDS design. But, the behaviors are not always different. In other words, a behavioral *overlap* exists whereby activities of legitimate users versus intruders (equivalently, legitimate cyber activities versus cyberattacks) cannot be perfectly differentiated at all points in time. The aforementioned behavioral overlap is illustrated by Figure 3. The preceding arguments imply that an intrusion detection system and its detection

Figure 3: The behavioral overlap of legitimate users and intruders.

algorithm(s) must compensate for their inherent *false negative* and *false positive* detection rates [12].

An IDS is commonly categorized by two types of algorithmic approaches, which include anomaly detection and signature detection. Anomaly detection applies statistical analysis to real-time data based on historical archives of data representing legitimate (normal) user activity. Behavior deviating from the statistical profiles of normal activities is considered abnormal (anomalous), and these deviations are used as the basis for detecting intrusions. Signature detection utilizes a collection of rules derived from data and patterns related to known profiles of particular types of intrusive behavior. Activities that generate content with patterns matching one or more signatures within the rule-base are indicative of an intrusion. A special case of signature detection is known as *blacklisting*. A blacklist is a collection of distinct identifiers associated with well-known malicious sources. Blacklists can be composed of values such as IP addresses, application types, filenames, or transport layer port numbers. The primary distinction between these two intrusion detection approaches is the following. Anomaly detection is concerned with the behavioral (or activity) profiles of legitimate users, whereas signature detection is based on the behavioral or activity patterns (profiles) of intruders.

Intrusion detection systems require packet classification algorithms. For example, intrusion detection systems process data from TCP/IP header fields along with content belonging to application payloads during the detection process. Table 3 contains three signature detection rules similar to those found in the SNORT intrusion detection system [137]. The

| Action | TCP/IP Header Filter             | Payload Filter                                                                                                                                                                                                                                                                                                                    |

|--------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| alert  | tcp any any $- >$ any 7070       | (msg: "IDS411/dos-realaudio";<br>flags:AP;                                                                                                                                                                                                                                                                                        |

|        |                                  | content: " fff4 fffd 06 ";<br>reference:arachnids,IDS411;)                                                                                                                                                                                                                                                                        |

| alert  | tcp any any $-> 128.61.14.57$ 21 | (msg:"IDS287/ftp-wuftp260-linux";<br>flags:AP;                                                                                                                                                                                                                                                                                    |

|        |                                  | content: " 31c0db 31c9b0 31c0db ";<br>reference:cve,CAN-2000-1574;)                                                                                                                                                                                                                                                               |

| drop   | tcp any any $- >$ any 80         | <pre>(msg: "Unauthorized Access";<br/>flags:AP;<br/>content: " 21daff 03cf1a0 ";<br/>react: HTTP/1.1 403 Forbidden<br/>Connection: close<br/>Content-Type: text/html; charset=utf-8<br/><head><br/><title>Access Denied</title><br/></head> <body><br/><h1>Access Denied</h1><br/>Unauthorized Access<br/></body> ; sid:4;)</pre> |

Table 3: An example of SNORT detection rules (filters).

first two rules shown in Table 3 are *alert* rules. The first rule will be triggered for packets specified with TCP as the transport layer protocol and destined to any internal machine

with a destination TCP port of 7070. Once the rule is triggered by a match on this particular TCP/IP header tuple, a second phase process will inspect the the TCP flag fields and the payload data. If the TCP flags are set to ACK (A) or PUSH (P) and if the content contains the hexadecimal string "fff4 fffd 06", then the packet matches the entire rule and an alert will be sent to a system administrator. The third rule is an *active response* rule. If a packet matches the TCP/IP header specifications along with the flags and content payload data as given in the third row of the table, then the IDS will actively *terminate* the communication flow by *dropping* (i.e., blocking) the packet.

## 2.4 Intrusion Prevention

Intrusion prevention can be categorized by two primary security mechanisms related to intrusion activities: (1) proactive mechanisms and (2) reactive mechanisms. *Proactive* intrusion prevention mechanisms enforce security policies with services such as authentication, authorization, and access control. For example, password systems and firewalls are proactive intrusion prevention systems. These systems implement security policies designed to prevent unauthorized access to cyber resources. *Reactive* intrusion prevention mechanisms function synergistically with intrusion detection systems and provide functionality that aims to stop intrusion occurrences in real-time and/or to recover from any adverse effects caused by a successful system penetration. Intrusion prevention systems capable of both detecting intrusions and reacting with countermeasures to intrusion occurrences are referred to as *active response systems*.

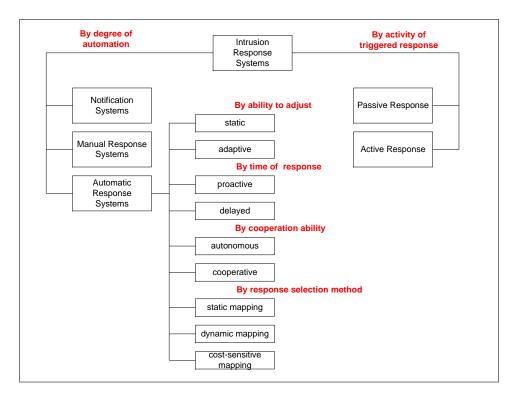

Collectively, intrusion detection and prevention systems are categorized as intrusion response systems (IRS). In [141], Stakhanova et al. propose an intrusion response system taxonomy, which is illustrated graphically by Figure 4. In their taxonomy, an IRS is classified by two top-level characteristics indicating the system's degree of automation and the system's response activity. IRS automation is categorized by notification systems, manual response systems, and automatic response systems, whereas response activity comprises passive and active response. Passive response systems are notification-based systems. Active response systems, as described above, provide real-time countermeasures to intrusions

Figure 4: A taxonomy of intrusion response systems [141].

and attacks. Active response includes countermeasures such as disabling user accounts, terminating system processes, and traffic filtering. Automatic response systems are further partitioned by its adjustment ability, response time, cooperation ability, and response selection method.

## 2.5 Packet Classification

Packet classification (PC) provides the basis for network functionality such as Internet protocol (IP) routing, virtual private networks, firewalls, access control lists, quality of service, policy based routing, network traffic accounting, and network traffic billing. In essence, PC is the process of mapping packets into network traffic *flows*. From a theoretical perspective, PC is equivalent to the multidimensional point location problem from computational geometry whereby the fields of a packet represent a point in *d*-dimensional space, and the *packet filters* of a packet classifier represent *d*-dimensional hyperrectangles. Flows are defined by hyperrectangles, and a packet matches a flow if it is contained within the boundaries of a hyperrectangle. A *flow* is the set of all packets contained within a hyperrectangle. Packet classification is formally described by the following. Let P be the set of all packets, R be a set of filters, and A be a collection of filter actions. A d-dimensional packet classification system implements a multivalence mapping  $\mathcal{F}$  defined by the following relationship:

$$\mathcal{F}: R \times P \to A \tag{1}$$

A d-dimensional packet classifier  $\mathcal{F}$  is specified by a set  $R = \{R_1, R_2, \ldots, R_N\}$  of N packet filters where  $R_i$  is the  $i^{th}$  packet filter of  $\mathcal{F}$ . Each filter is specified over a set of d field descriptors where  $R_i = \{r_{ij}\}, 1 \leq i \leq N$ , and  $1 \leq j \leq d$ . Each field descriptor,  $r_{ij}$ , is associated with a header field  $f_j$  from an underlying network protocol stack, where each  $f_j$ is allocated  $w_j$  bits based on its definition within the protocol stack. Further, each  $f_j$  is interpreted as a  $w_j$  bit, unsigned, binary number. Therefore, each  $f_j$  has a finite domain,  $D_j$ , where  $D_j = [0, 2^{w_j} - 1]$ . In other words, a field's domain is a finite range over the positive integers. In turn, each field descriptor  $r_{ij}$  can be specified in  $R_i$  as a range such that  $r_{ij} \subseteq D_j$ , where  $r_{ij} = [l_{ij}, u_{ij}]$  and  $0 \leq l_{ij} \leq u_{ij} \leq 2^{w_j} - 1$ .

The semantics of packet classification can be described as follows. A packet classifier  $\mathcal{F}$  receives a packet P from the network and extracts the associated d fields from the packet, and these d fields form the input field set  $p = \{p_1, p_2, \ldots, p_d\} \subseteq P$ . A packet matches the filter  $R_i$  if and only if  $p_j \in r_{ij}, \forall j, 1 \leq j \leq d$ . In other words, a packet matches the  $i^{th}$  filter if and only if  $l_{ij} \leq p_j \leq u_{ij}, \forall j, 1 \leq j \leq d$ . If a packet matches a filter  $R_i$ , then an associated action  $A_i$  shall be applied to the packet.

In general, a packet can match multiple filters specified by a packet classifier. In certain applications such as multi-match packet classification, the packet classifier will perform a set of actions on the packet for each of the matched filters. However, the semantics of most packet classifiers is such that a priority is assigned to the packet filters. In these cases, the packet classifier will perform the action of the highest priority matching filter. Priority, denoted by Pri(x), is measured such that  $Pri(R_i) = i$  and  $i < j \implies Pri(R_i) > Pri(R_j)$ . Particularly,  $Pri(R_1) > Pri(R_2) > \ldots > Pri(R_N)$ .

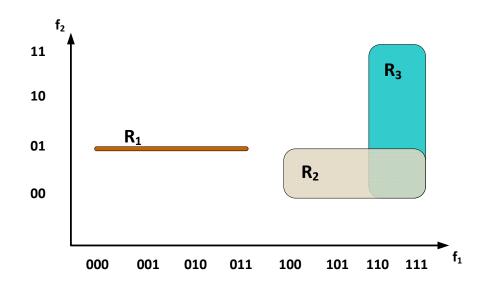

Table 4 provides an example of a d = 2 dimensional packet classifier  $\mathcal{F}$  with N = 3 filter-action tuples. The number of bits for header fields  $f_1$  and  $f_2$  are specified as  $w_1 = 3$

and  $w_2 = 2$ . The last three rows of Table 4 are binary range representations of the first

| ${\mathcal F}$ | $f_1: w_1 = 3$ | $f_2: w_2 = 2$ |       |

|----------------|----------------|----------------|-------|

| $R_1$          | 0*             | 01             | $A_1$ |

| $R_2$          | 1*             | 0*             | $A_2$ |

| $R_3$          | 11*            | *              | $A_3$ |

| $R_1$          | [000,011]      | [01,01]        | $A_1$ |

| $R_2$          | [100,111]      | [00,01]        | $A_2$ |

| $R_3$          | [110,111]      | [00, 11]       | $A_3$ |

Table 4: An example of a simple 2-dimensional packet classifier.

three rows, which are expressed with prefix notation.

In general, the field descriptors of a packet filter are ranges bound together over d dimensions. As a result, filters can be viewed geometrically as hyperrectangles. Figure 5 illustrates the geometry described by the filters of Table 4. The fields  $(f_1, f_2)$  generate a

Figure 5: The geometric perspective of packet classification.

two-dimensional plane given by  $[000, 111] \times [00, 11]$ . Filter  $R_1$  represents a line, whereas filters  $R_1$  and  $R_2$  are interpreted as rectangles. Observe that  $R_2$  and  $R_3$  overlap within the region  $[110, 111] \times [00, 01]$ . Regions with overlap encompass multi-match locations.

# 2.6 Summary

In this chapter, the basic concepts underlying the three primary research thrusts of this dissertation were discussed. In the next chapter, an overview of related works from within these research areas will be provided.

# CHAPTER III

# BACKGROUND

This chapter provides an overview of related works in distributed security architectures, packet classification algorithms, and cyberattack detection techniques with computational intelligence systems.

### 3.1 Distributed security architectures and defense systems

Bellovin [17, 64] introduced the concept of distributed firewalls. Perimeter firewalls enforce security policies at the ingress/egress locations of a network. With Bellovin's distributed firewall, security policies are centrally defined by administrators. However, policy enforcement is implemented by the local firewall of each host within an organization's network. Contrary to perimeter firewalls, distributed firewalls do not depend on network topology. As a result, distributed firewalls alleviate issues such as insider threats, provide security to mobile hosts that roam beyond organizational perimeters, and reduce configuration challenges associated with complex communication protocols.

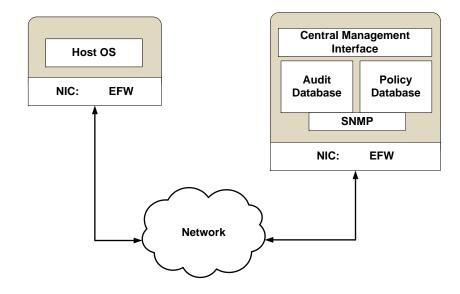

Meredith et al. [97, 94] developed the autonomic distributed firewall (ADF). ADF is a distributed firewall architecture with independent (autonomic) firewalls residing at each host of the network and implementing a centrally defined security policy. The design objectives of ADF are similar to Bellovin's distributed firewall. However, ADF implements the firewall functionality within the host's network interface card (NIC). Meredith et al. claim that host-based firewalls controlled by operating systems software fail to meet the security requirements as defined by the *Trusted Computer System Evaluation Criteria* [37]. Particularly, they claim that software-based firewalls do not satisfy the *non-bypassable* and *tamper-resistant* properties of the trusted computer system criteria. To satisfy these criteria, ADF detaches the host-based firewall from the host's operating system and moves it to the host's NIC. The idea is to view the host-based firewall as an embedded firewall (EFW) within the network interface card. Figure 6 illustrates the main components of the ADF

architecture. ADF has a central management server (CMS) responsible for audit collection

**Figure 6:** Primary functional components of the autonomous distributed firewall architecture.

and security policy management. Security policy is defined by security administrators, and the central management interface *pushes* the policy to the EFW. Each EFW has logging capabilities, whereby the firewall filters can can be configured to trigger alerts for various match conditions. For example, any packet attempting to traverse the firewall that gets denied can be logged, and the log data can be subsequently delivered to the CMS to be stored as security audit data.

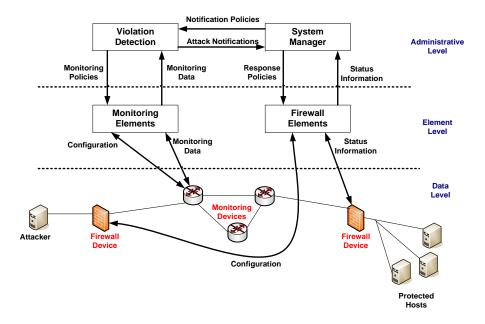

In [102], Munz et al. present the DIADEM firewall architecture as a distributed approach to integrating intrusion detection systems and firewalls. The DIADEM firewall architecture, which is illustrated by Figure 7, is partitioned into three levels: the data level, the element level, and the administrative level. The data level is composed of routers, network monitors, and firewalls that are responsible for network monitoring and intrusion response. The element level provides an abstraction layer between the data and administrative levels and is composed of two components: monitoring elements and firewall elements. The administrative level components communicate with the data level devices via an application

Figure 7: The DIADEM firewall architecture.

programming interface provided by the monitoring and firewall elements. The administrative level contains a violation detection unit and a system manager. The violation detection unit receives Internet Protocol Flow Information Export (IPFIX) [128] data from the network monitoring units, and it uses this data to perform intrusion detection analysis. Once an intrusion is observed, event information is delivered to the system manager. Once events are received by the system manager, it issues response policies to the network's perimeter firewalls. The response policies are firewall actions such as connection blocking, connection redirection, or connection rate-limiting. Once the violation detection system determines that an intrusion is no longer active, it sends new event information to the system manager. The system manager then removes the response policies from the firewall units.

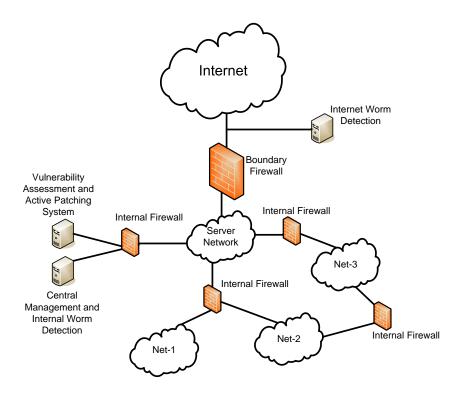

Zou et al. proposed a firewall network system for worm defense [170]. Their architecture extends the classical perimeter firewall configuration whereby an enterprise network is divided into sub-networks that are isolated and protected by internal firewalls. Their system is designed for the purpose of defending against internal worm attacks and internal worm propagation. The architecture has the following components:

• Perimeter Firewalls

- Internal Network-Based Firewalls

- Internal Worm Detection System

- Vulnerability Assessment and Active Patching System

- Central Management Station