# DESIGN OF A LOW-POWER INTERFACE CIRCUITRY FOR A

# **VESTIBULAR PROSTHESIS SYSTEM**

A Dissertation Presented to The Academic Faculty

by

Hakan Töreyin

In Partial Fulfillment of the Requirements for the Degree PhD in the School of Electrical and Computer Engineering

> Georgia Institute of Technology August 2014

# COPYRIGHT 2014 BY HAKAN TÖREYİN

## **DESIGN OF A LOW-POWER INTERFACE CIRCUITRY FOR A**

## **VESTIBULAR PROSTHESIS SYSTEM**

Approved by:

Dr. Pamela T. Bhatti, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. David V. Anderson School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Robert J. Butera School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Omer T. Inan School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Rusell K. Gore School of Medicine *Emory University*

Date Approved: June 24, 2014

### ACKNOWLEDGEMENTS

I would like to express my immense gratitude to my advisor, Pamela T. Bhatti, for her continuous support and guidance. I am very grateful for the knowledge and insight she shared with me.

I would like to thank Dr. Omer T. Inan and Dr. Robert J. Butera for their time and consideration in reviewing my dissertation and serving as reading committee members. I would like to thank the other members of my committee, David V. Anderson and Russell K. Gore for serving on my defense committee and providing me valuable feedback.

I thank all my friends.

Lastly, I thank my family for their endless love and invaluable support.

# TABLE OF CONTENTS

|                                                               | Page  |

|---------------------------------------------------------------|-------|

| ACKNOWLEDGEMENTS                                              | iii   |

| LIST OF TABLES                                                | ix    |

| LIST OF FIGURES                                               | X     |

| SUMMARY                                                       | xviii |

| CHAPTER                                                       |       |

| 1 INTRODUCTION                                                | 1     |

| 1.1. Peripheral Vestibular Organs                             | 3     |

| 1.1.1. SCCs                                                   | 3     |

| 1.1.1.1. Canal Macromechanics                                 | 3     |

| 1.1.1.2. Canal Hair Cell and Afferent Properties              | 4     |

| 1.1.1.3. Canal Directional Properties                         | 6     |

| 1.1.2. Otolith Organs                                         | 8     |

| 1.1.2.1. Otolith Macromechanics                               | 8     |

| 1.1.2.2. Otolith Hair Cell and Afferent Properties            | 9     |

| 1.1.2.3. Otolith Directional Properties                       | 10    |

| 1.2. A System-Level Description of a VP                       | 11    |

| 1.3. State-of-the-art VP Systems                              | 14    |

| 1.3.1. The Johns Hopkins University Group                     | 15    |

| 1.3.2. University of Cyprus-Imperial College Group            | 16    |

| 1.3.3. Closed-Loop Neural Prosthesis for Vestibular Disorders |       |

| (CLONS) Project                                               | 17    |

| 1.3.4. The UC Irvine Group                                    | 18    |

# 2 VESTIBULAR PROSTHESIS SIGNAL PROCESSING ON A FIELD-

# PROGRAMMABLE ANALOG ARRAY (FPAA) DEVELOPMENT

| PLATFORM                                                    | 20 |

|-------------------------------------------------------------|----|

| 2.1. FPAA Architecture                                      | 21 |

| 2.1.1. Signal Processor                                     | 22 |

| 2.1.1.1. Voltage-to-Current Converter Block                 | 25 |

| 2.1.1.2. Current-to-Frequency Converter and Clock Generator |    |

| Blocks                                                      | 26 |

| 2.1.2. Measurement Results                                  | 28 |

| 2.1.3. Neural Stimulator                                    | 32 |

| 2.1.4. Analysis of Results from the FPAA Implementation     | 34 |

| 3 A VP SIGNAL PROCESSING ASIC                               | 36 |

| 3.1. Vector-Matrix Multiplier                               | 37 |

| 3.1.1. Design Considerations                                | 38 |

| 3.1.2. The VMM Architecture                                 | 40 |

| 3.1.3. Design Details                                       | 41 |

| 3.1.3.1. Sensor and Weight Voltages Multiplexing            | 41 |

| 3.1.3.2. Multiplier                                         | 42 |

| 3.1.3.3. Transimpedance Amplifier                           | 44 |

| 3.1.3.4. Voltage Averaging and Demultiplexing               | 47 |

| 3.1.3.5. Reconstruction Filters                             | 48 |

| 3.1.3.6. Clock Generation Block                             | 48 |

| 3.1.4. Measurement Results                                  | 50 |

| 3.1.4.1. Testing Procedure                                  | 51 |

| 3.1.4.2. Bias Generation Circuitry                          | 52 |

| 3.1.4.3. Linearity                                      | 53 |

|---------------------------------------------------------|----|

| 3.1.4.4. Bandwidth                                      | 54 |

| 3.1.4.5. Noise                                          | 55 |

| 3.1.4.6. Power                                          | 56 |

| 3.1.5. Discussion                                       | 56 |

| 3.2. Neural Dynamics Filters                            | 58 |

| 3.2.1. Design Considerations                            | 59 |

| 3.2.2. Selection of the Filter Architecture             | 60 |

| 3.2.2.1. Time Constants                                 | 61 |

| 3.2.2.2. Energy-Efficiency                              | 61 |

| 3.2.2.3. Area                                           | 61 |

| 3.2.2.4. Input/Output Voltage Range                     | 63 |

| 3.2.2.5. Noise                                          | 64 |

| 3.2.3. Design of the Vestibular Neural Dynamics Filters | 67 |

| 3.2.3.1. SCC Filter                                     | 68 |

| 3.2.3.2. Otolith Filter                                 | 70 |

| 3.2.4. Measurement Results                              | 72 |

| 3.2.4.1. Testing Procedure                              | 72 |

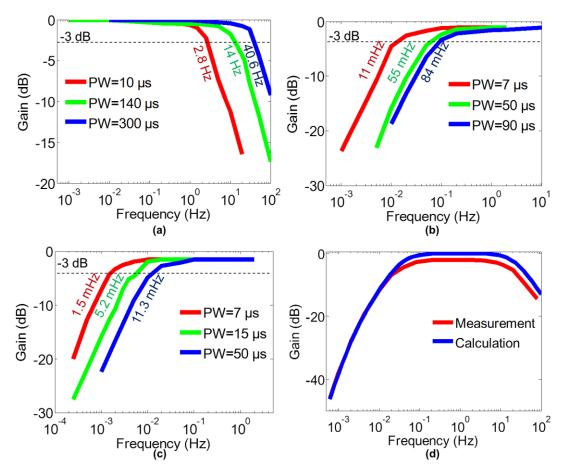

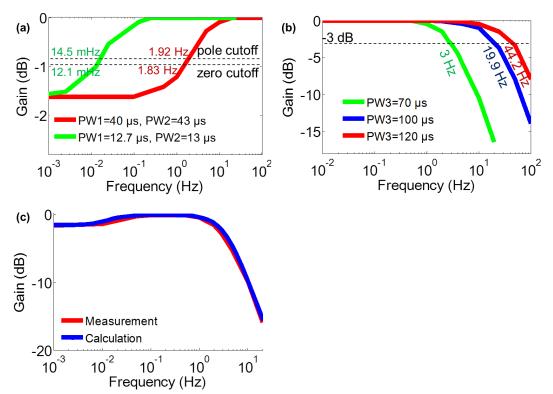

| 3.2.4.2. Functionality                                  | 74 |

| 3.2.4.3. Noise                                          | 76 |

| 3.2.4.4. Power                                          | 76 |

| 3.2.5. Discussion                                       | 77 |

| 3.3. Voltage-to-Frequency Block                         | 79 |

| 3.3.1. Design Considerations                            | 80 |

| 3.3.2. System-Level Design of the V-to-F                | 81 |

| 3.2.2.1. Achieving Sigmoid Frequency vs. Voltage Relationship |     |

|---------------------------------------------------------------|-----|

| with Tunable Parameters in an Energy-Efficient Manner         | 81  |

| 3.3.2.2. Input Voltage Range                                  | 82  |

| 3.3.2.3. Noise                                                | 82  |

| 3.3.3. Design Details of the V-to-F                           | 83  |

| 3.3.3.1. Variable-Gain OTA                                    | 83  |

| 3.3.3.2. Asymmetric Current Mirror                            | 89  |

| 3.3.3.3. Current-to-Frequency Block                           | 92  |

| 3.3.3.4. Clock Generation Block                               | 93  |

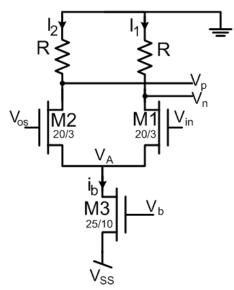

| 3.3.3.5. Variable-Gain Amplifier                              | 94  |

| 3.3.4. Measurement Results                                    | 97  |

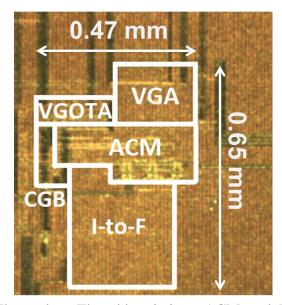

| 3.3.4.1. Testing Procedure                                    | 98  |

| 3.3.4.2. Functionality                                        | 99  |

| 3.3.4.3. Noise                                                | 103 |

| 3.3.4.4. Power                                                | 105 |

| 3.3.5. Discussion                                             | 105 |

| 4 VESTIBULAR PROSTHESIS SIGNAL PROCESSING ON AN               |     |

| ULTRA-LOW POWER MICROCONTROLLER                               | 108 |

| 4.1. A/D Conversion                                           | 109 |

| 4.2. Vector-Matrix Multiplication (VMM)                       | 110 |

| 4.3. IIR Filters                                              | 110 |

| 4.4. Pulse Generation                                         | 111 |

| 4.5. Performance Parameters                                   | 112 |

| 4.5.1. Power                                                  | 112 |

| 4.5.2. Area                                                   | 112 |

| 4.5.2. Noise                                            | 112 |

|---------------------------------------------------------|-----|

| 4.6. The MSP430 vs. the ASIC                            | 113 |

| 5 CONCLUSION AND FUTURE WORK                            | 115 |

| 5.1. Three Approaches                                   | 115 |

| 5.1.1. FPAA Implementation                              | 115 |

| 5.1.2. ASIC                                             | 116 |

| 5.1.3. Microcontroller Implementation                   | 118 |

| 5.2. Comparison of the Three Approaches                 | 118 |

| 5.3. Future Directions                                  | 120 |

| 5.3.1. Signal Processing ASIC Performance               | 120 |

| 5.3.2. A Complete VP Interface Circuitry                | 120 |

| 5.3.3. Reflecting the Biology                           | 121 |

| APPENDIX A: A FINITE ELEMENT ANALYSIS OF A BIOMIMETIC   |     |

| ANGULAR VELOCITY SENSOR FOR A VESTIBULAR PROSTHESIS     | 122 |

| APPENDIX B: MATLAB CODE USED TO GENERATE THE IIR FILTER |     |

| COEFFICIENTS                                            | 124 |

| APPENDIX C: C CODE IMPLEMENTED ON MSP430                | 126 |

| REFERENCES                                              | 134 |

# LIST OF TABLES

|                                                                              | Page |

|------------------------------------------------------------------------------|------|

| Table 1: State-of-the-art Vestibular Prostheses Circuitry                    | 15   |

| Table 2: FPAA Current Stimulator Outputs                                     | 34   |

| Table 3: Bias Current Generation Circuitry Resistance Values for VMM         | 53   |

| Table 4: Summary of Performance Parameters of the 3-by-2 and the 3-by-3 VMMs | 57   |

| Table 5: SCC Filter Circuit Parameters and Time Constant Ranges              | 70   |

| Table 6: Otolith Filter Circuit Parameters and Time Constant Ranges          | 71   |

| Table 7: Summary of Performance Parameters of the Neural Dynamics Filters    | 77   |

| Table 8: Summary of Performance Parameters of the V-to-F                     | 105  |

| Table 9: Performance Comparison of the ASIC and the MSP430                   | 114  |

| Table 10: Summary of the Three Approaches                                    | 115  |

### **LIST OF FIGURES**

Page

8

12

15

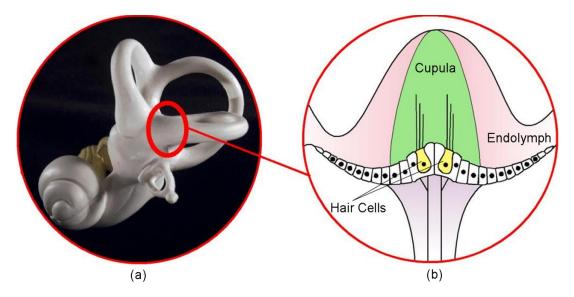

- Figure 1: Semicircular Canal (SCC) Structure (a) Three SCCs are (almost) orthogonal to each other. (b) Cross sectional view of the ampulla. The hair cell hairs are embedded inside a jelly-like structure, namely the cupula. The cupula occludes the canal which is filled with a fluid, endolymph. 4

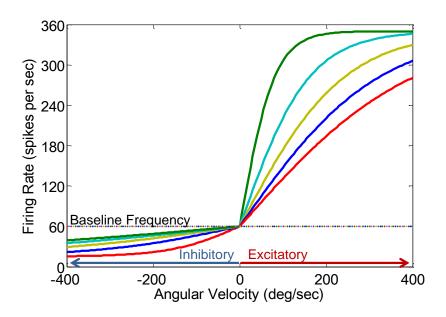

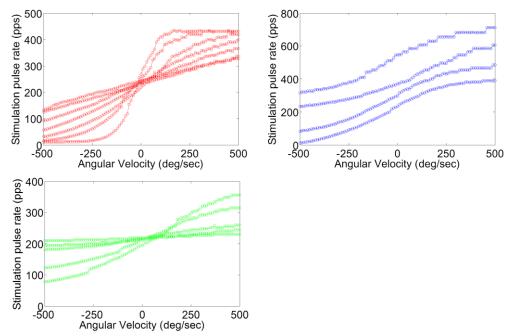

- Figure 2: SCC afferents firing rate-angular velocity. Curves having different gains are plotted. 5

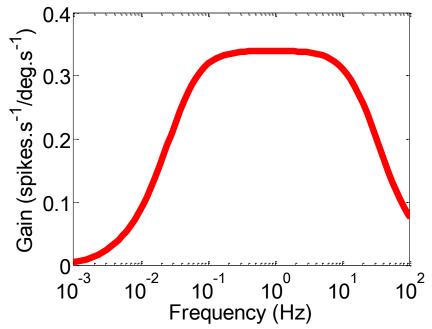

- Figure 3: Frequency response of SCC afferents. The plot is drawn based on (1). Typical values of  $A_V$ ,  $\tau_1$ ,  $\tau_2$ ,  $\tau_A$  are 0.34 spikes.s-1/deg.s-1, 4.37 s, 7 ms, and 80 s, respectively. 6

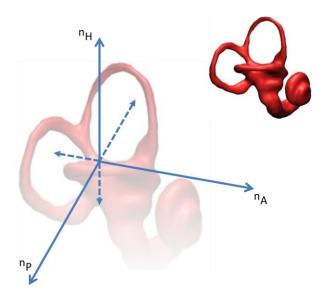

- Figure 4: The prime directions (**n**<sub>H</sub>, **n**<sub>A</sub>, and **n**<sub>P</sub>) corresponding to the horizontal, anterior, and posterior canals. The labyrinth image is adapted from [10].

- Figure 5: The otoconial membrane [1].

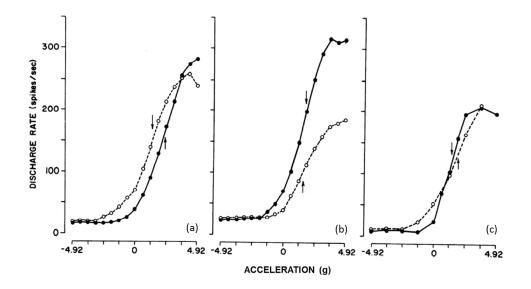

- Figure 6: Otolith afferents firing rate-linear acceleration ([11]). The input acceleration is in units of *g*, the gravitational acceleration. Each pair of curves in each plot are used to signify the variation of different curve properties seen in the otolith afferent. These properties are (a) the location of the curve along the x-axis, (b) the dynamic range of the discharge rate, and (c) the gain in the linear region 9

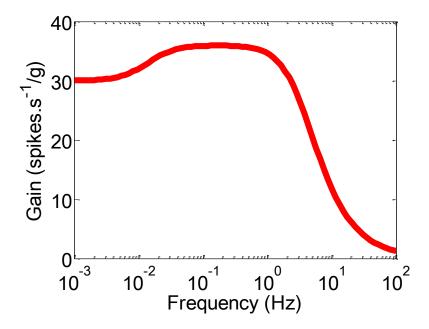

- Figure 7: Frequency response of otolith afferents. The plots are drawn based on (2). Typical values for  $A_V$ ,  $\kappa_A$ ,  $\tau_A$ , and  $\tau_M$  are 30 spike.s-1/g, 1.2, 11 s, and 46 ms, respectively. 10

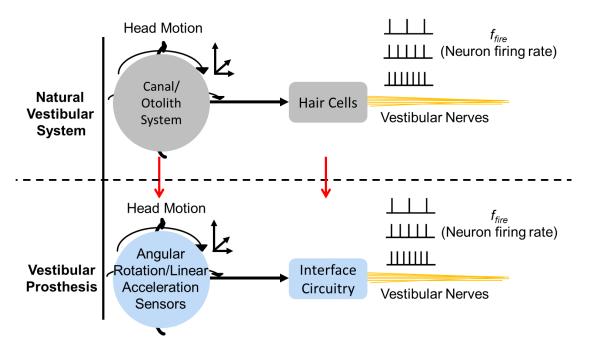

- Figure 8: A vestibular prosthesis needs to replace the vestibular organ functions. Canal/otolith system and the hair cells are replaced with rate sensors and an interface circuitry, respectively. 11

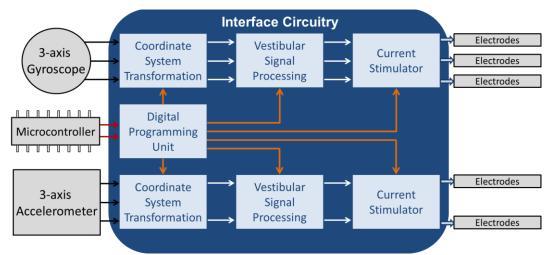

- Figure 9: The interface circuitry block diagram.

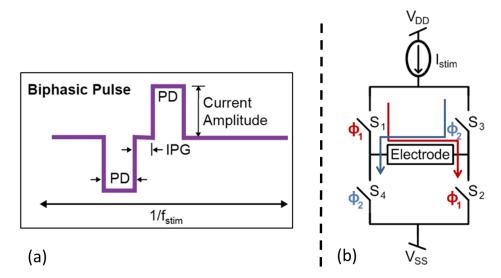

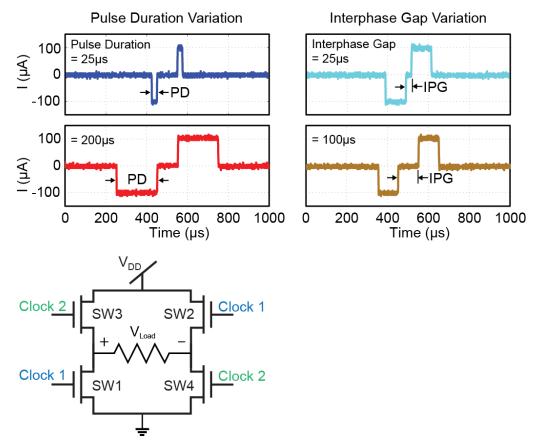

- Figure 10: Biphasic waveform is used to in electrical stimulators to prevent harmful electrochemical processes at the tissue sites. (a) Biphasic current pulse. The cathodic phase is followed by an anodic phase. The two phases are separated by an interphase gap (IPG) to ensure the neuron firing. (b) Biphasic current pulses can be generated across an electrode by an H-bridge circuit. Four switches are operated in pairs to switch the flow direction of the stimulation current across the electrode. 13

Figure 11: A representation of an implanted VP system.

- Figure 12: Single Canal Vestibular Prosthesis System Diagram.

- Figure 13: Floating-gate FPAA architecture. (a) The FPAA consists of an 8 x 4 matrix of Computational Analog Blocks (CABs) interconnected through crossbar networks. (b) Circuit elements/blocks are distributed among CAB1 and CAB2. 22

20

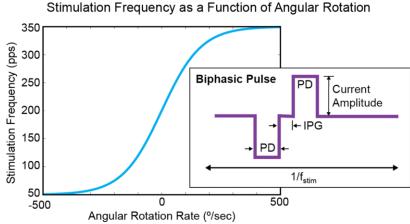

- Figure 14: Non-linear relationship between the angular velocity and the firing rate. A representative biphasic pulse is shown inside the graph. 23

- Figure 15: Circuit schematic of the signal processor. The bias voltages  $V_{gyro, ref}$ ,  $V_{control}$ , V<sub>bias1</sub>, V<sub>bias2</sub>, V<sub>pulse1</sub> and V<sub>pulse2</sub> are generated using an off-chip DAC housed on a development board. (a) The voltage-to-current converter block transfers the voltage signal from the gyroscope,  $V_{gyro,out}$ , into a current signal,  $I_3$ . The current I<sub>3</sub> is related to angular velocity through a *tanh* function. The minimum level of I<sub>3</sub> is controlled by  $V_{control}$ . By adjusting  $V_{gyro,ref}$  an offset can be added to  $V_{gyro,out}$ . This serves to translate the  $I_3$  along the x-axis of the  $I_3$  vs.  $V_{gyro,out}$  curve. (b) The current-to-frequency converter block converts the current signal,  $I_3$ , into the pulse train output  $V_{PT}$ . Linearly related to  $I_3$ , the frequency of  $V_{PT}$  determines  $f_{stim}$ . (c) Two similar fully digital Clock Generation stages create Clock 1 and Clock 2. The pulse width of Clock 1 is controlled by  $V_{pulse1}$  and a similar relationship exists for Clock 2. (d) The FGOTA is the core of the voltage-tocurrent converter block. In the sub-threshold region, the output current, Iout, of the FGOTA is related to its differential input voltage,  $V_p$ - $V_n$ , through a *tanh* function. Ibias is the bias current which determines the region of operation and is set up during the programming stage by V<sub>bias</sub>. 24

- Figure 16: Pulse timing control. The signal  $V_{PT}$  is output from the current-to-frequency converter block with a pulse rate of  $f_{stim}$ . The rising edge of  $V_{PT}$  triggers Clock 1 in the clock generation block. The clock generation block also controls the PD, the duration of each clock. The delay between the clocks, thigh, less the PD is the IPG. 26

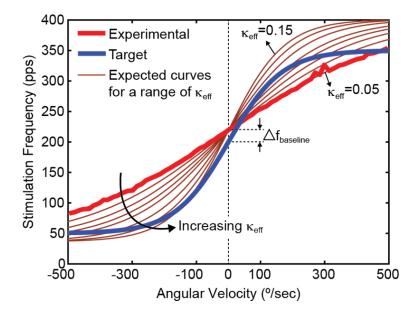

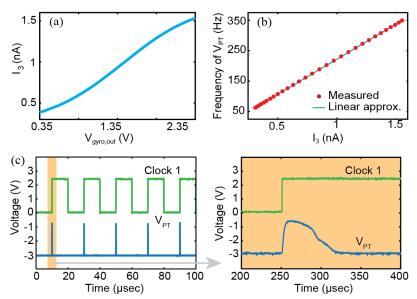

- Figure 17: Stimulation frequency vs. angular velocity. The experimental stimulation frequency (pulse rate) as a function of angular velocity is shown. Superimposed on the plot is a a series of curves illustrating  $f_{stim}$  vs angular velocity for  $\kappa_{eff}$  (0.05–0.15). The steepness of the curve is controlled by the  $\kappa_{eff}$  of the FGOTA The baseline frequency difference between the experimental and the target curves,  $\Delta f_{baseline}$ , can be adjusted by decreasing  $I_1$  (controlled by  $V_{control}$ ). To control the stimulation frequency range, the following values can be adjusted: the bias current of the FGOTA,  $I_{bias}$  in (4), and the current ratio of the mismatched current mirror,  $I_3/I_2$ , and the capacitance C2 in (6).

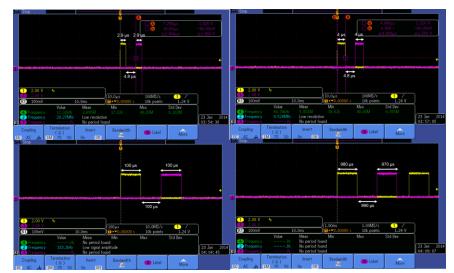

- Figure 18: Summary of signal processor block level outputs. (a) Non-linear response to  $V_{gyro,out}$  generated by the voltage-to-current conversion block. (b) Linear  $f_{stim}$  vs. I3 response is exhibited by the current-to-frequency conversion block with  $t_{high} = 200 \ \mu$ s. (c) Triggering of Clock 1 by the rising edge of  $V_{PT}$ . Note that a long (10ms) clock pulse was created in the clock generation block to illustrate the relationship between the rising edge of  $V_{PT}$  and Clock 1. In practice the pulse duration of Clock 1 would be less than the duration of  $V_{PT}$ . 30

- Figure 19: Biphasic pulse control. Using a 1 kΩ resistive load placed across an H-bridge circuit, Clock 1 and Clock 2 serve to control a cathodic-first, symmetric, biphasic pulse. Representative values of the PD and IPG are demonstrated.

31

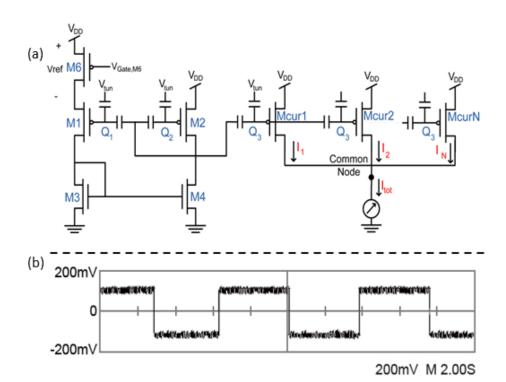

- Figure 20: Current Source Circuit. (a) Two matched nFETs, M3 and M4, form a current mirror (gate voltage of M6 at zero). Equal currents pass through M1 and M2. Unlike a conventional bootstrap circuit where  $V_{ref}$  is generated by setting the size of M1 larger than M2, programming the gates of M1 and M2 at different charge levels, Q1 and Q2, generates  $V_{ref}$ . Assuming perfect matching of M1 and M2,  $V_{ref}$  is directly proportional to the charge difference Q1-Q2. Floating-gate pFETs, Mcur1-McurN, reflects the current generated inside the core circuit to an outside pin. The charge level (Q3) programmed onto the gates of Mcur1-McurN changes the respective effective gate voltages, thus I1 is dependent on Q3. Multiple current branches can boost the current level with N copies. To linearly span a range of currents M6 is controlled to act as a variable resistor thereby providing current increments of 2%. (b) The oscilloscope trace illustrates an 116  $\mu$ A biphasic charge-balanced pulse output across a 1k $\Omega$  load resistor in parallel with a 10 nF capacitor.

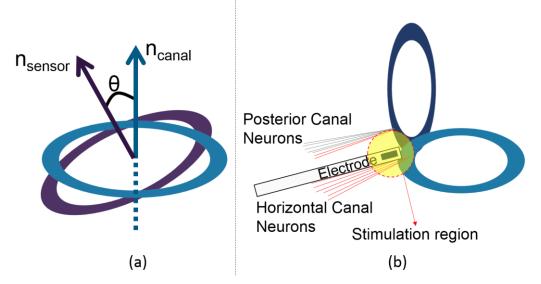

- Figure 21: Vector Matrix Multiplication (VMM). For simplicity, the necessity for the VMM block is explained for the canals only. (a) To align the primary axes of implanted sensors and peripheral vestibular sense organs, a VMM can perform a coordinate system transformation between the implanted sensors and natural organs. (b) When an electrode is placed to stimulate only horizontal canal neurons, a portion of posterior canal neurons can be stimulated erroneously. To eliminate false representations of motion due to current spread a VMM can precompensate, or adjust, for the effect.

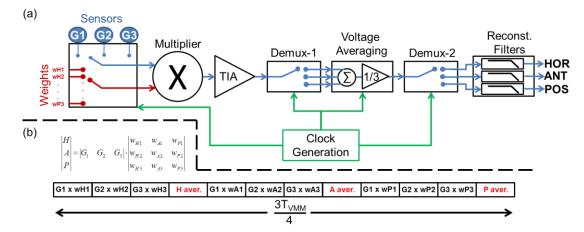

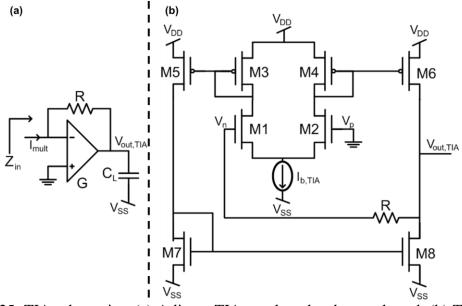

- Figure 22: VMM operation. (a) Block Diagram. (b) The time sequence of each arithmetic operation, where TVMM is the VMM cycle time. HOR, ANT, and POS are the corrected signals for the horizontal, anterior, and posterior canals, respectively. G1, G2, and G3 denote the output signals from the gyroscopes and *w<sub>j,i</sub>* denotes the weight voltage corresponding to the canal *j*, and the gyroscope number *i*.41

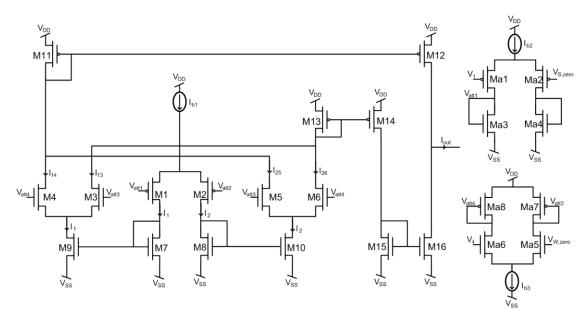

- Figure 23: Multiplier schematics. Attenuation stages are used to increase the linear range.

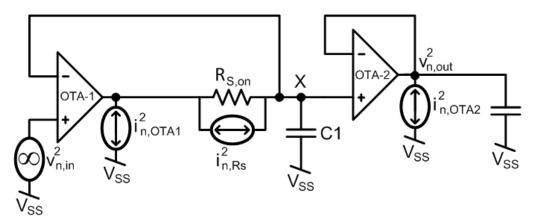

Figure 24: Multiplier noise model.

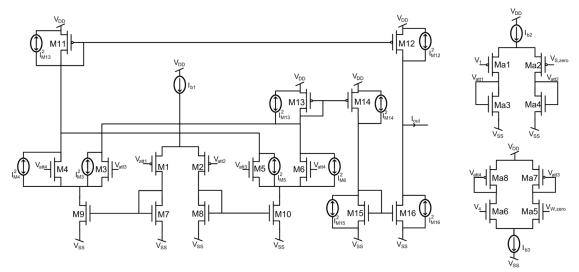

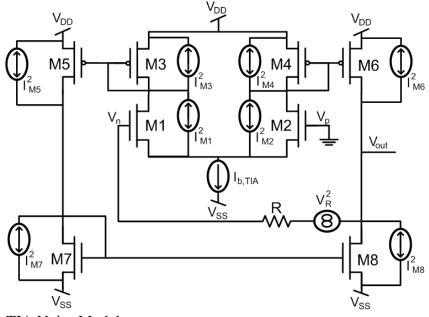

| Figure 25: TIA schematics. (a) A linear TIA topology has been selected. (b) The TIA utilizes and OTA in subthreshold region.45                                                                                                                                                                                                                                                                           | The TIA<br>45         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Figure 26: TIA Noise Model. 46                                                                                                                                                                                                                                                                                                                                                                           | 46                    |

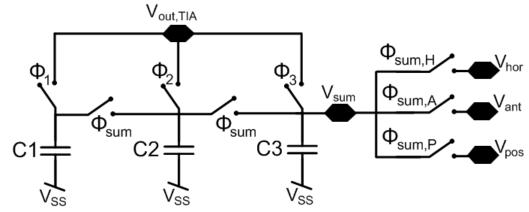

| Figure 27: Voltage averaging and demultiplexing schematics. 47                                                                                                                                                                                                                                                                                                                                           | 47                    |

| Figure 28: Reconstruction filter schematics.48                                                                                                                                                                                                                                                                                                                                                           | 48                    |

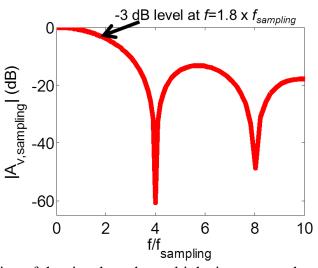

| Figure 29: Sampling of the signals at the multiplexing stage reduces the magnitudes of the sensor signals by means of a sinc function, which limits the minimum allowable input clock frequency.                                                                                                                                                                                                         |                       |

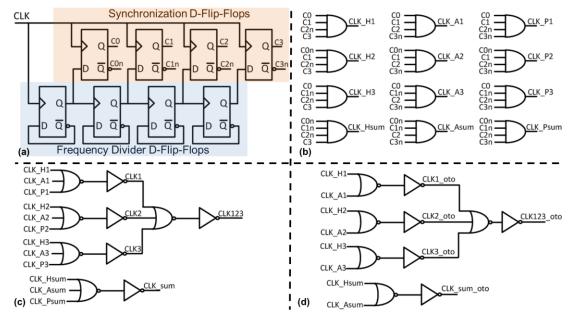

| <ul> <li>Figure 30: Clock Generation Block Circuitry. (a) Frequency of the input clock, CLK, i divided into 2/4/8/16. The resulting clocks are then synchronized. (b) Clocks of the sensor and weight multiplexing stage for both 3-by-3 and 3-by-2 VMM operations. (c) Demultiplexer clocks of 3-by-3 VMM operation (SCC). (d Demultiplexer clocks of 3-by-2 VMM operation (otolith).</li> </ul>        | Clocks of 2 VMM       |

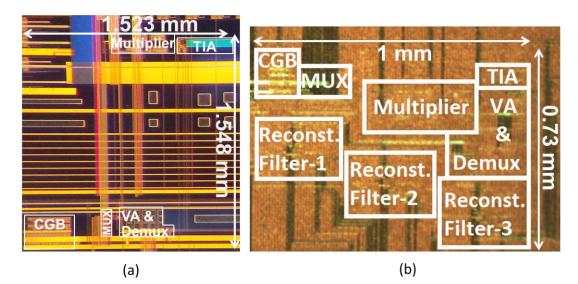

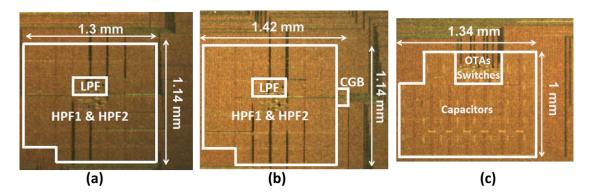

| <ul> <li>Figure 31: VMM Floor Plans. The abbreviation VA refers to the voltage averaging block</li> <li>(a) 3-by-2 VMM fabricated with TSMC 0.35-µm 4P2M n-well CMOS process</li> <li>(b) 3-by-3 VMM fabricated with TI LBC7 0.35-µm 3P2M n-well CMOS process.</li> </ul>                                                                                                                                | process.<br>CMOS      |

| Figure 32: VMM Test-bench schematics.52                                                                                                                                                                                                                                                                                                                                                                  | 52                    |

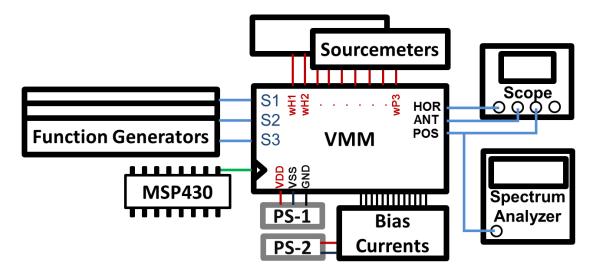

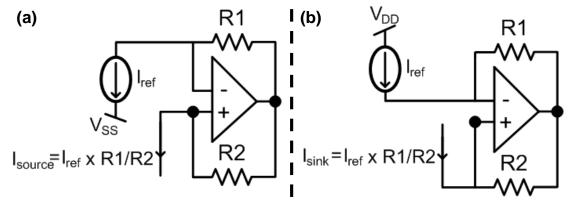

| Figure 33: Off-chip bias current generation circuitry. (a) Source. (b) Sink.52                                                                                                                                                                                                                                                                                                                           | 52                    |

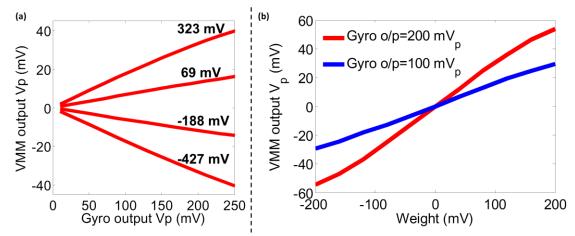

| <ul> <li>Figure 34: Linear dependence of the VMM output (y-axis) with respect to the input signal magnitudes (x-axis). (a) The results from the TSMC 3-by-2 VMM chip ar parameterized by weight voltage (-427 mV to 323 mV, equal weighting applied to all gyro outputs). (b) The results from the TI 3-by-3 VMM chip ar parameterized by gyroscope output voltages (200 mVp and 100 mVp). 53</li> </ul> | chip are<br>g applied |

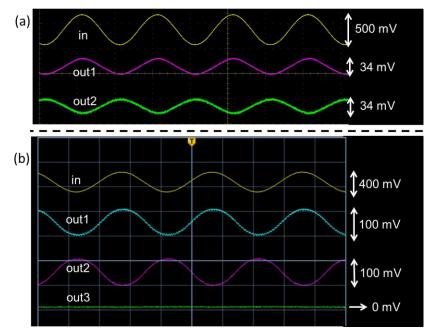

| Figure 35: The output waveforms. (a) TSMC 3-by-2 VMM measurements. Out1-out2 ar obtained when the input voltage is multiplied by the weight matrix $W_{3-by-2} = 10.2 = 0.441$                                                                                                                                                                                                                           |                       |

$\begin{vmatrix} 0.2 & -0.44 \\ 0.2 & -0.44 \\ 0.2 & -0.44 \end{vmatrix}$  (b) TI 3-by-3 VMM measurements. Out1-out3 are obtained when the input voltage is multiplied by the weight matrix  $W_{3-by-3} = \begin{vmatrix} 1 & -1 & 1 \\ 1 & -1 & 0 \\ 1 & -1 & -1 \end{vmatrix}$ . 54

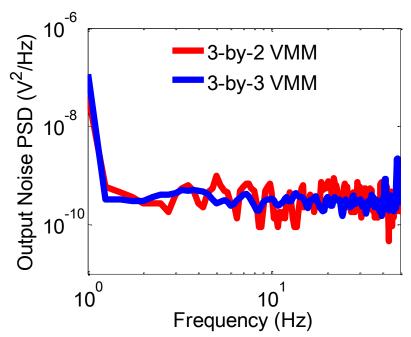

Figure 36: Output noise voltage PSDs of the 3-by-2 and 3-by-3 VMMs. 55

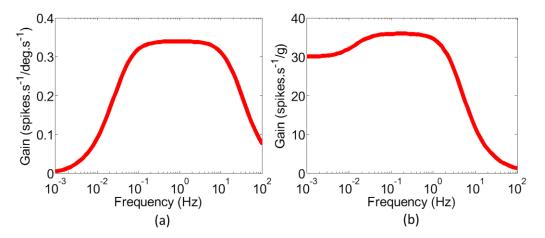

Figure 37: Neural dynamics of peripheral vestibular organs. (a) SCC neural dynamics. (b) Otolith neural dynamics. 59

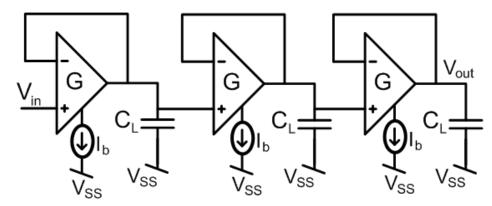

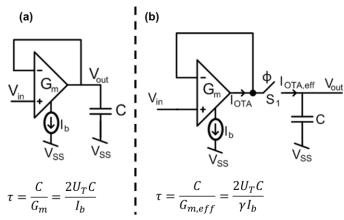

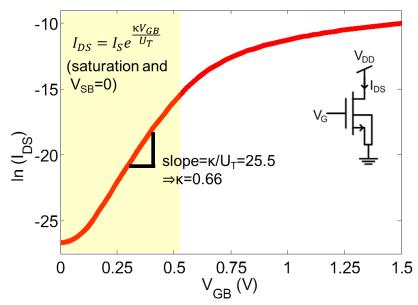

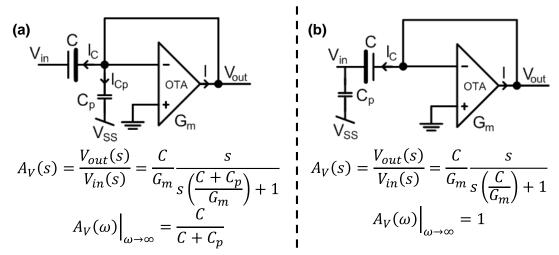

- Figure 38: First order OTA-C filters. (a) Regular configuration. (b) A switch at the output limits the OTA current, thereby reducing the effective transconductance [58].

- Figure 39: Actual implementation of the 1st order clocked transconductor OTA-C integrator. 62

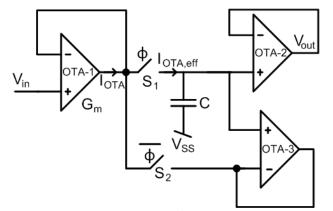

- Figure 40: Wide-range OTA schematic. All OTAs of the filters are designed as wide-range OTAs. To improve the output impedance, current mirrors are cascode MOS devices. 63

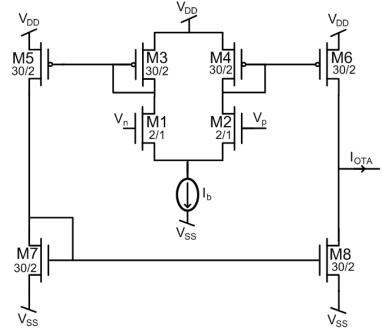

- Figure 41:  $V_{GB}$  sweep simulation for an nMOS in 0.35 µm TI LBC7 process. ln( $I_{DS}$ ) vs  $V_{GB}$  plot is used to extract the process-dependent  $\kappa$  value. 64

- Figure 42: The LPF noise sources during the sampling phase. 65

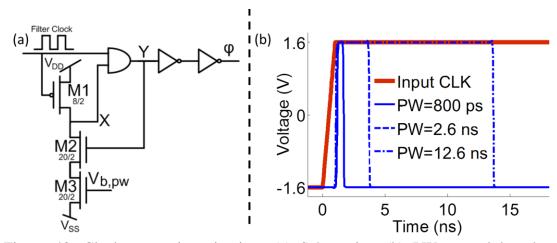

- Figure 43: Clock generation circuitry. (a) Schematics. (b) PW control based on simulation results. PW=800 ps is obtained when  $V_{b,pw}$ =-90 mV. 68

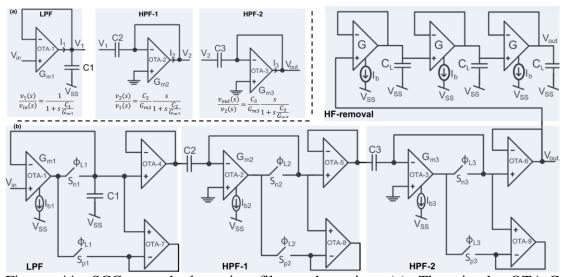

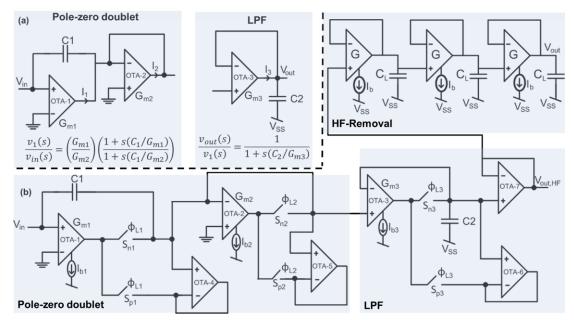

- Figure 44: SCC neural dynamics filter schematics. (a) The simple OTA-C implementation of the SCC transfer function shown in (23). (b) The implementation of the SCC transfer function filter using clocked OTAs. The design includes switches and buffer stages.

- Figure 45: Otolith neural dynamics filter schematics. (a) The simple Gm-C implementation of the otolith transfer function shown in (20). (b) Actual implementation of the SCC transfer function filter using clocked OTAs. 71

- Figure 46: Filter floor plans. (a) SCC-v1. (b) SCC-v2. (c) Otolith. 72

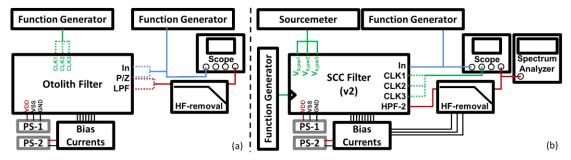

- Figure 47: Filter Test-bench Schematics. (a) For ease of characterization, SCC-v1 and otolith filter use externally generated clocks. For simplicity, the schematics is drawn for the case only the otolith filter is under test. (b) Clocks are generated internally at SCC-v2.

- Figure 48: SCC neural dynamics filter measurements. (a) LPF measurements (b) HPF-1 measurements (c) HPF-2 measurements. (d) The complete transfer function measurements. 74

- Figure 49: Otolith neural dynamics filter measurements. (a) Pole-zero doublet stage measurements. (b) LPF measurements. (c) The complete transfer function measurements. 75

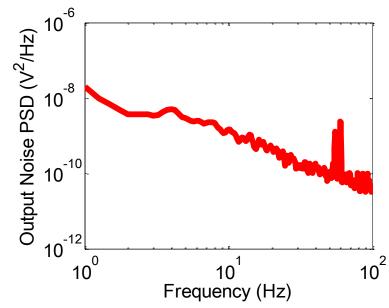

Figure 50: Output voltage noise PSD of the SCC filter. 76

- Figure 51: The effect of bottom-plate parasitic capacitance,  $C_p$ , on the gain of the HPF stage. (a) Because the bottom-plate (thick plate on the schematics) is connected to  $V_{out}$ , the maximum gain is less than 1. (b) To eliminate the effect of  $C_p$ , the bottom plate should be connected to  $V_{in}$ . 78

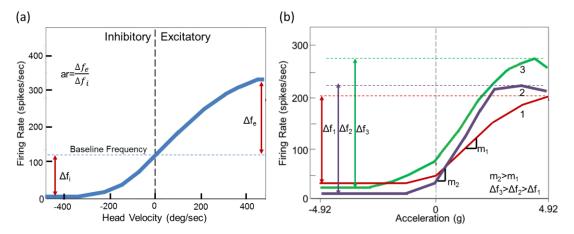

- Figure 52: Firing rate angular velocity/linear acceleration relationship. (a) Data from an SCC neuron (Redrawn from [56]) Baseline frequency is the neuron firing rate when there is no head motion. The asymmetry ratio, ar, is defined as the ratio of firing rate spans of excitatory and inhibitory head motions. (b) Data from otolith neurons (redrawn from [11]). Three plots correspond to different otolith neurons. The firing rate ranges,  $\Delta f$ , and the gains, m, of the curves are different. 79

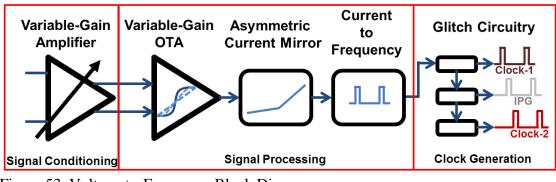

| Figure 53: | Voltage-to-Fi | equency Bl | ock Diagram. | 8 | 33 |

|------------|---------------|------------|--------------|---|----|

|------------|---------------|------------|--------------|---|----|

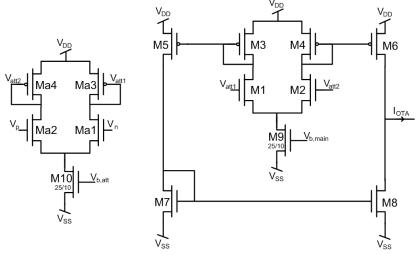

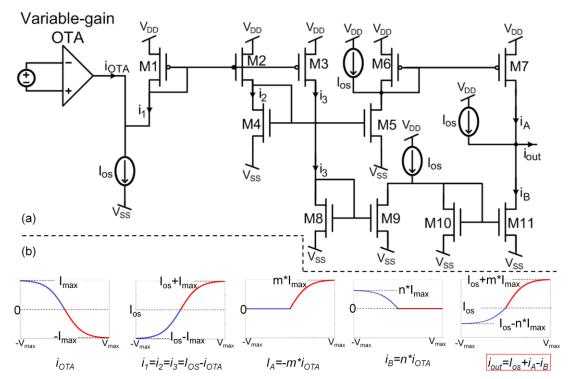

Figure 54: Variable-gain OTA.

84

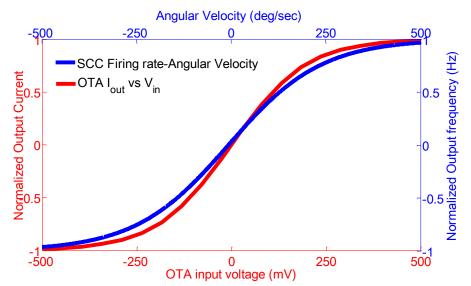

- Figure 55: The sigmoid firing rate-head angular velocity relationship based on (33) and the tanh curve calculated based on (28) for the maximum attenuation factor of  $\alpha$ =0.4, when the input voltage range is ±500 mV.

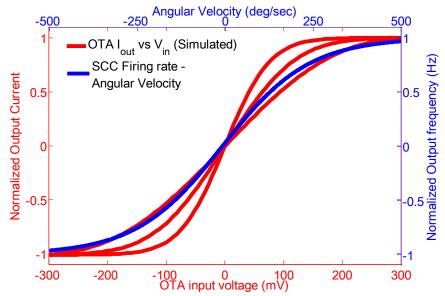

- Figure 56: The sigmoid firing rate-head angular velocity relationship based on [6] and the tanh curves based on simulation results of the variable gain OTA designed. 88

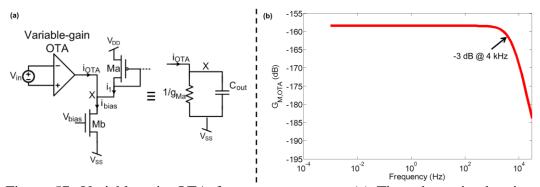

- Figure 57: Variable-gain OTA frequency response. (a) The schematic showing the connections at the output node of the OTA and its small signal equivalent. (b) Simulation result. 88

- Figure 58: Asymmetric current mirror. (a) Schematic. The input to the block is the current output of the Variable-gain OTA,  $i_{OTA}$ . The offset current, IOS, is generated as the drain current of a long-channel nMOS, gate voltage of which is controlled by a bias voltage. The  $I_{OS}$  is replicated by a series of pMOS current mirrors. For simplicity, the nMOS and the current mirrors are not shown in the figure. (b) Variations of currents with respect to input voltage of the variable-gain OTA are illustrated by the plots at the bottom. 90

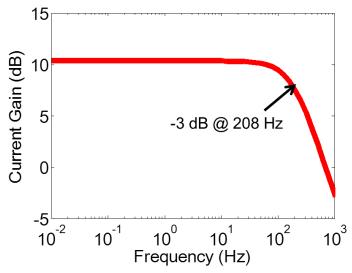

- Figure 59: Frequency response of the asymmetric current mirror based on simulations.91

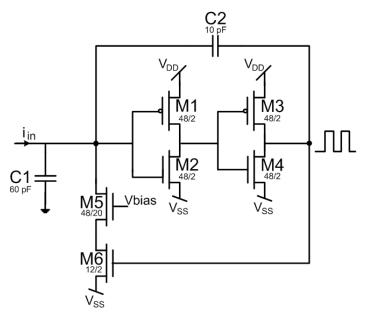

Figure 60: Current to frequency conversion block schematics. 93

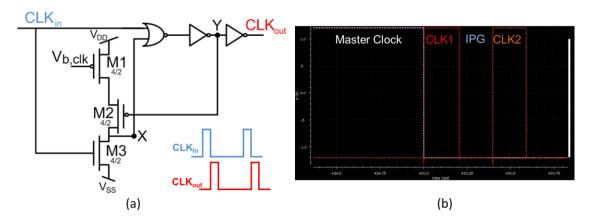

Figure 61: Clock-generation-circuitry (a) Schematics.  $V_{b,clk}$  controls the pulse width of the CLK<sub>out</sub>. CLK<sub>out</sub> is generated at the falling edge of CLK<sub>in</sub>. (b) Three clock-generation circuitry are cascaded to generate CLK1 and CLK2 with an interphase gap (IPG). Simulated waveforms of CLK1 and CLK2 generated from a Master Clock. 94

Figure 62: Variable-gain amplifier schematics.

95

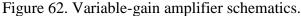

Figure 63: V-to-F Floor plan. The abbreviations ACM and VGOTA refer to the Asymmetric Current Mirror and the Variable-gain OTA blocks. 98

99

- Figure 64: V-to-F Test-Bench Schematics.

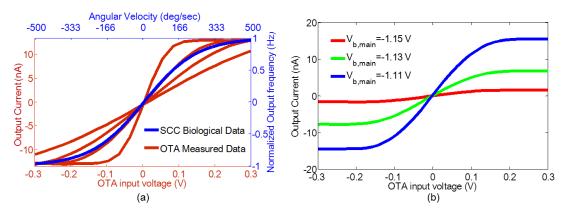

- Figure 65: Variable-gain OTA measured data. (a) Slope control and SCC neuron firing rate from [58]. (b) Current range control. 99

- Figure 66: Asymmetric current mirror measurement results. (a) The order of asymmetry control. (b) Output current when variable-gain OTA feeds the asymmetric current mirror. 100

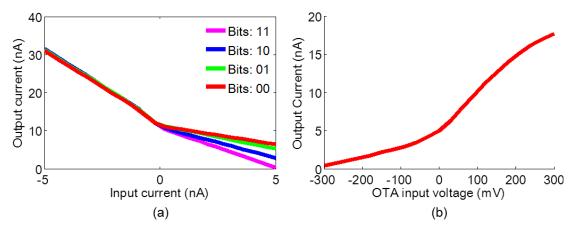

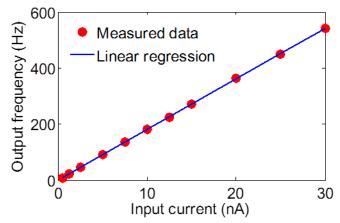

- Figure 67: Measurement results of the current to frequency conversion block. 101

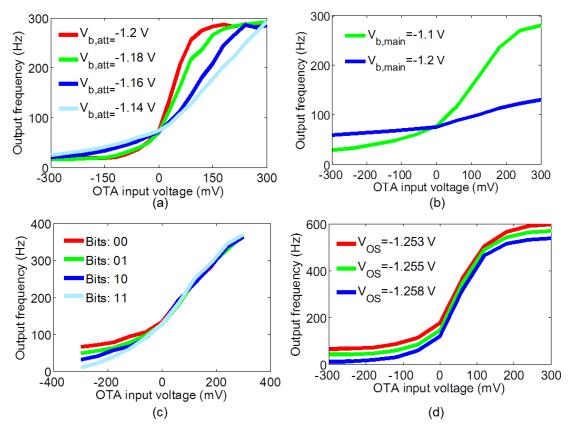

- Figure 68: Measurement results of the current to frequency conversion block. (a) Slope control. (b) Frequency range control. (c) The order of asymmetry control. (d) Baseline frequency control. 102

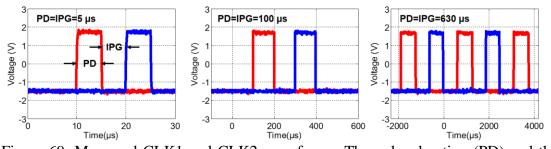

- Figure 69: Measured CLK1 and CLK2 waveforms. The pulse duration (PD) and the interphase gap (IPG) can be varied from <1 μs to the maximum possible value for that particular frequency (630 μs when PD=IPG and clock frequency is 400 Hz). For PD=5 μs, 100 μs, and 630 μs, V<sub>b,clk</sub> values are ~1.184 V, ~1.287 V, and ~1.354 V, respectively.

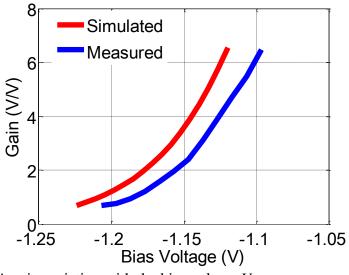

| Figure 70: VGA | gain variation | with the bias | voltage $V_h$ . | 103 |

|----------------|----------------|---------------|-----------------|-----|

|                |                |               |                 |     |

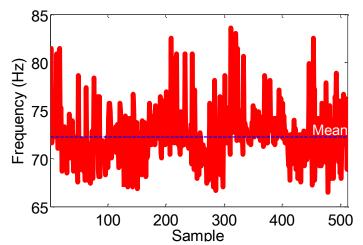

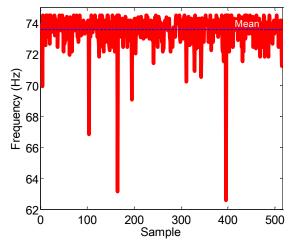

Figure 71: Noise of the V-to-F is observed as jitter at the output in the time domain. 103

- Figure 72: Noise of the V-to-F is observed as jitter at the output in the time domain. 104

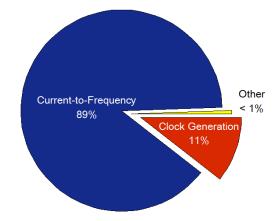

- Figure 73: Power breakdown of the V-to-F. 105

- Figure 74: Current to frequency conversion block static power consumption simulations. 106

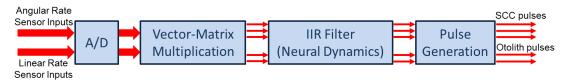

- Figure 75: Block diagram of the vestibular signal processing functions implemented on a TI MSP430 microcontroller. 109

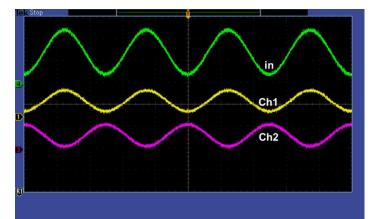

- Figure 76: Output signals on Ch1 and Ch2 when a sinusoidal signal is multiplied with [1 1 1] and [-1 -1 -1] matrices, respectively. 110

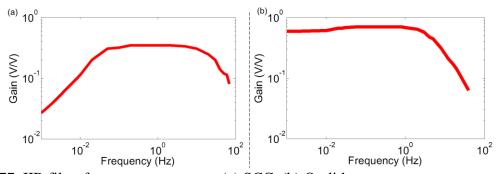

- Figure 77: IIR filter frequency responses. (a) SCC. (b) Otolith. 110

- Figure 78: Illustration of control of the parameters in (51).

- Figure 79: Illustration of control of time-related parameters of the two clocks. 112

- Figure 80: Fluctuation in the output frequency of the MSP430. 113

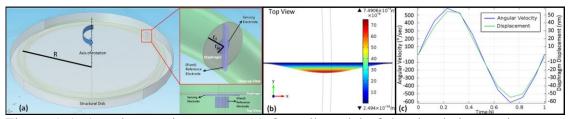

Figure A.1: Angular rotation sensor. (a) Overall model of the simulation environment and sensing and reference electrode. (b) A typical displacement of the diaphragm in response to disk rotation. In this figure  $t_d=1 \mu m$ , and at that instant the maximum displacement, which occurs at the center of the diaphragm, is ~749 nm. (c) The diaphragm displacement in response to a 1 Hz of sinusoidal angular velocity input for  $t_d=5 \mu m$ .

### **SUMMARY**

The objective of this research is to design and validate a signal processing interface circuitry for a vestibular prosthesis (VP) system.

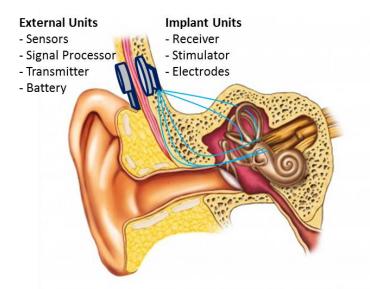

The human vestibular system is responsible for maintaining balance and orientation, and stabilizing gaze during head motion. Head motion is sensed by vestibular sensors and encoded via the firing rate of vestibular neurons. Vestibular disorders can result in dizziness, imbalance, and disequilibrium. Currently there are no therapeutic options for individuals suffering from bilateral vestibular dysfunction. A potential solution is a vestibular prosthesis (VP). This device serves to replace peripheral vestibular organs by sensing angular motion, detected by semicircular canals (SCCs), and linear head motion, detected by the otolith, and selectively stimulating the corresponding vestibular afferents. An ideal VP will not only mimic the patient-dependent vestibular neural dynamics, but also consume low power.

In this study, three energy-efficient ways to implement the motion encoding function required in a vestibular prosthesis are presented: (1) signal processing circuit implementation on an experimental field-programmable analog array (FPAA), (2) a fully-custom design of signal processing circuitry that extensively makes use of subthreshold analog signal processing techniques, and (3) signal processing functions implementation on an ultra-low power microcontroller. This way, both analog and digital signal processing techniques to implement the vestibular signal processing functions are investigated.

### **CHAPTER 1**

### **INTRODUCTION**

In human body, the vestibular system is responsible for helping the body to keep balance, to have a perception of orientation, and to stabilize the vision during head movements [1]. Using motion sensors that constitute the peripheral vestibular organs, the vestibular system detects angular velocities and linear accelerations. Vestibular afferents provide the detected motion information to the vestibular nuclear (VN) complex where not only vestibular but also related information such as visual or somatosensory information are gathered. The vestibular and vestibular related information are processed at the VN to give rise to vestibulocular (VOR) or vestibulospinal reflex pathways as well as pathways to the central nervous system (CNS). The VOR causes the eyes to move in a direction opposite to the direction of head motion, which stabilizes images on the retina. The vestibulospinal reflex provides information to the limb and head muscles to maintain the posture and balance. The CNS uses cues from the VN to interpret the body orientation.

The motion sensors of the body are located inside the inner ear and the information from the sensors is transmitted to the VN along the cochleovestibular nerve. The vestibular sensors, which are a series of tubes and sacs, form the membranous vestibular labyrinth. The angular rotations are sensed by the semicircular canals (SCCs). In each ear, there are three SCCs that are located (almost) orthogonal to each other. The transducer cells located in the SCCs encode the angular velocity information into the firing rate of the vestibular neurons. The linear accelerations are sensed by the otolith organs, namely the saccule and the utricle. While the saccule is sensitive to up and down movements, the utricle is sensitive to horizontal movements. In both the SCCs and the otolith organs, conversion of motion to vestibular neuron firing is done by the transducer cells, namely the hair cells.

Disorders that affect the vestibular labyrinth result in dizziness, imbalance, and disequilibrium. Research based on data collected from more than 5000 individuals between

the years 2001 and 2004 reveals that 35.4% of the participants aged 40 and older had vestibular dysfunction, which corresponds to 69 million Americans [2]. In patients over the age of 65 years, these problems often result in falls which may cause fatal or non-fatal injuries. When the vestibular dysfunction is in one ear (unilateral), vestibular rehabilitation therapy can help a patient reduce imbalance and dizziness [3]. However, for bilateral vestibular dysfunction, there are not any therapeutic options. Bilateral vestibular dysfunction may occur primarily due to ototoxic drugs, trauma, or infection that inhibits the functioning of the peripheral vestibular organs. It is estimated that there are 50,000 individuals in the U.S. that would benefit from bilateral vestibular dysfunction treatment [4].

A treatment option that would increase the quality of life for individuals suffering from bilateral vestibular dysfunction is an implantable prosthesis. Such a device would replace the functions of the peripheral vestibular organs by sensing angular and linear head motions and selectively stimulating the corresponding vestibular afferents. In this dissertation I describe my doctoral research toward building a state-of-the-art signal processing circuitry for a VP system that can be used in vestibular studies on animals and for ultimate use in human patients having bilateral vestibular dysfunction.

This document begins by describing the biological properties of the peripheral vestibular organs, namely the SCCs and the otolith organs. Then, a VP that would replace the functions of the peripheral vestibular organs is presented from a system-level perspective. Chapter 1 is concluded by a review of the state-of-the-art VP systems to summarize the efforts and highlight the major challenges towards building a VP. The necessity for building a state-of-the-art signal processing circuitry for a VP is justified at the end of Chapter 1. Different signal-processing implementations that make use of analog and digital domains are presented in the following sections. In Chapter 2, a Field-Programmable Analog Array (FPAA) implementation of a neural stimulator and part of the signal processing functions that process signals in the analog domain is presented. In

Chapter 3, a full-custom design VP signal processing circuit that utilize energy-efficient analog-signal processing techniques is presented. In Chapter 4, a digital domain implementation of the VP signal processing functions on an existing commercial solution is presented. Lastly, in Chapter 5, conclusion of the study and the future directions are discussed.

#### **1.1 Peripheral Vestibular Organs**

The vestibular organs are grouped into two categories based on the types of motions they detect; the SCCs and the otolith organs. Angular motions are sensed by the three SCCs, namely horizontal, posterior, and anterior canals. Linear motions are sensed by the two otolith organs, namely the saccule and the utricle. Macromechanics; the transducer cell (hair cell) properties; neuron types, dynamics, and firing rate encodings; and directional properties corresponding to the SCCs and the otoliths are presented below.

#### 1.1.1 SCCs

In a human body, inside each ear, there are three SCCs positioned (almost) mutually orthagonal to each other as shown in Figure 1(a). SCCs in one ear work complementarily with those in the other ear forming a pair of SCCs. This way, the common mode rejection ratio of the sensory information increases.

#### 1.1.1.1. Canal Macromechanics

An SCC is essentially a circular canal that is filled with a fluid called endolymph. The three SCCs have curvature radii of  $3.17\pm0.21$  mm, and the lumen of the canal has an elliptic cross section [5]. The region of the canal where the cross section widens to a bulb shape is called the ampulla (Figure 1(b)). A jelly-like structure called the cupula, which resides at the ampulla, divides the circular canal into two sections. When the SCC rotates, the endolymph moves at a slower speed relative to the canal walls causing the cupula to experience a deflection in the opposite direction of rotation. In fact, studies of the cupula

suggest that for the mid-range frequency band that defines the normal head movements, the cupula is attached along the ampullary wall at its entire perimeter and deforms like a diaphragm [6].

Figure 1. Semicircular Canal (SCC) Structure (a) Three SCCs are (almost) orthogonal to each other. (b) Cross sectional view of the ampulla. The hair cell hairs are embedded inside a jelly-like structure, namely the cupula. The cupula occludes the canal which is filled with a fluid, endolymph.

#### 1.1.1.2. Canal Hair Cell and Afferent Properties

The end of the cupula that is fixed at the ampulla is populated with sensory cells, namely hair cells. The hair cells are the transducer cells of the vestibular organs. A series of biochemical reactions inside the hair cells cause the innervating afferents to fire. If hair cell cilia are deflected, depending on the direction and the magnitude of inclination, the chemical reaction rate increases or decreases. Hair cell cilia are embedded inside the cupula. Thus, the cilia of a hair cell deflect in response to motion, modulating the afferent firing rate. It is known that under no motion vestibular neurons fire at a constant rate, namely baseline rate, which is ~60 spikes/s. Increasing angular velocity, depending on its direction of rotation, increases (excitatory rotation) or decreases (inhibitory rotation) the neuron firing rate. Because the dynamic range for firing rate in response to inhibitory

stimuli (from ~15 spike.s<sup>-1</sup> to ~60 spike.s<sup>-1</sup>) is smaller compared to that in response to excitatory stimuli (from ~60 spike.s<sup>-1</sup> to ~350 spike.s<sup>-1</sup>), there is an asymmetry between the excitatory and inhibitory responses. Furthermore, although the gain remains almost constant for a range of excitatory input angular velocities, when the angular velocity is increased further, the gain decreases, causing saturation of the angular velocity-firing rate curve for large excitatory and inhibitory angular velocities. The asymmetry and the saturation effects result in an asymmetric sigmoid firing rate-angular velocity relationship. Rough representations of the firing rate vs. head velocity relationships observed in chinchillas for various gain values have been shown in Figure 2 [7].

Figure 2. SCC afferents firing rate-angular velocity. Curves having different gains are plotted.

The afferent SCC dynamics are best described by the following transfer function

[7]:

$$H_{SCC}(s) = A_V \left( \frac{\tau_1 s}{(1 + \tau_1 s)(1 + \tau_2 s)} \right) \left( \frac{\tau_A s}{1 + \tau_A s} \right), \tag{1}$$

where  $\tau_1$  and  $\tau_2$  are the long and the short time constants associated with the band-pass characteristics of the SCC mechanical model, respectively. In (1),  $A_v$  is the gain in spike.s<sup>-1</sup>/deg.s<sup>-1</sup> at a mid-band frequency of 0.2 Hz and  $\tau_A$  is the time constant associated with the adaptation of the afferents for small frequency inputs.<sup>1</sup> The gain plot corresponding to (1) is shown in Figure 3.

Figure 3. Frequency response of SCC afferents. The plot is drawn based on (1). Typical values of  $A_{V_1} \tau_{I_1} \tau_{Z_2} \tau_A$  are 0.34 spikes.s<sup>-1</sup>/deg.s<sup>-1</sup>, 4.37 s, 7 ms, and 80 s, respectively.

#### 1.1.1.3. Canal Directional Properties

Historically, it has been assumed that 3D angular movements are resolved into three separate vector components and each component is carried to the VN by the afferents of one SCC. Thus, rotation about one of these three vector components is expected to excite afferents of a single canal. However, more recent studies to predict the directions about

<sup>&</sup>lt;sup>1</sup> Adaptation is defined as the reduction in neuron firing rates during prolonged stimulation [1].

which the vestibular labyrinth resolves 3D angular movements into separate vector components, have revealed that the rotations about the directions normal to the anatomical planes of the canals do not give maximum responses [8],[9]. This is partly because the cross-section area of the canal is not fixed everywhere on the canal, and partly because of the interdependence of canal responses due to the same single mass fluid flowing inside all three-canals. These directions about which maximum responses occur are called the maximum response directions. Since rotations about the maximum response directions also result in afferent activation in the other canals, the maximum response directions cannot be the separate vector components that 3D angular movements are resolved into. Thus, a set of different directions, namely prime directions (**n**<sub>H</sub>, **n**<sub>A</sub>, and **n**<sub>P</sub>) corresponding to each of the three SCCs. Prime direction for one canal is obtained by intersecting the maximum response planes of the other two canals. Thus, rotation about the prime direction of one canal response planes in the other two canals.

Figure 4. The prime directions ( $\mathbf{n}_{H}$ ,  $\mathbf{n}_{A}$ , and  $\mathbf{n}_{P}$ ) corresponding to the horizontal, anterior, and posterior canals. The labyrinth image is adapted from [10].

#### 1.1.2. Otolith Organs

There are two otolith organs that sense linear accelerations in the vestibular labyrinth, namely the saccule and the utricle. The saccule and the utricle senses vertical and horizontal accelerations, respectively.

#### 1.1.2.1. Otolith Mechanics

The otoconial membrane is a flat jelly-like structure that covers the neural tissue of the otolith organs. Three layers constitute the otoconial membrane: the otoconial layer, the gelatinous layer, and the columnar layer (Figure 5) [1].

Figure 5. The otoconial membrane [1].

The otoconial layer is occupied with calcium carbonate crystals in the form of a loose fiber network. Beneath the otoconial layer is the gelatinous layer, which is a dense and cross-linked filamentous network. Linear forces, which displace the otoconial layer, are coupled to the columnar layer by the gelatinous layer. Shearing displacements of the columnar layer result in displacements in the stereocilia of the hair cells.

#### 1.1.2.2. Otolith Hair Cell and Afferent Properties

The anisotropic structure of the columnar layer causes the cilia of the hair cells bend in response to shear motion only. Similar to the hair cell operation in SCCs, bending of the cilia controls the rate of a series of biochemical reactions inside the cell that cause firing of the innervating afferents. Depending on the bending of the cilia, the rate of the chemical reactions increase or decrease, which in turn modulates the firing rate of the action potential train carried to the vestibular nucleus (VN) by the afferents. Similar to the canal afferents, the firing rate-acceleration dependence of the otolith afferents is a sigmoid function. Figure 6 shows firing rate-linear acceleration relationships of six otolith afferent neurons. Each plot illustrates a different kind of variation observed among afferents, namely the position on the horizontal axis (a), dynamic range of the discharge rate (b), and linear-region gains (c).

Figure 6. Otolith afferents firing rate-linear acceleration ([11]). The input acceleration is in units of g, the gravitational acceleration. Each pair of curves in each plot are used to signify the variation of different curve properties seen in the otolith afferent. These properties are (a) the location of the curve along the x-axis, (b) the dynamic range of the discharge rate, and (c) the gain in the linear region.

The otolith afferent dynamics are best described by the following transfer function [12]:

$$H_{oto}(s) = A_{\nu} \left( \frac{1 + k_A \tau_A s}{1 + \tau_A s} \right) \left( \frac{1}{1 + \tau_M s} \right), \tag{2}$$

where  $\tau_A$  and  $\tau_M$  are the adaptation and mechanical related time constants, respectively. In (2),  $A_v$  is the gain in spike.s<sup>-1</sup>/g at a mid-band frequency of 0.2 Hz, where g is the gravitational acceleration. The gain plot corresponding to (2) is shown in Figure 7.

Figure 7. Frequency response of otolith afferents. The plots are drawn based on (2). Typical values for  $A_V$ ,  $\kappa_A$ ,  $\tau_A$ , and  $\tau_M$  are 30 spike.s<sup>-1</sup>/g, 1.2, 11 s, and 46 ms, respectively.

#### 1.1.2.3. Otolith Directional Properties

Each hair cell in the otolith organs has a polarization direction. While deflections in the polarization direction increases the afferent discharge rate, those in the opposite of the polarization direction decreases the discharge rate. The otolith directional properties were determined by understanding both how the otoconial membrane of each otolith organ is oriented in the head and how the polarization directions of the hair cells inside an otolith organ are distributed. Studies reveal that while the utricle provides a two-dimensional representation of linear accelerations in the horizontal plane, the saccule provides the vertical acceleration information.

Below, the functions of a VP that could replace the aforementioned vestibular organ functions is described. Then an overview of the state-of-the-art VP systems is presented.

### 1.2 A System-Level Description of a VP

In designing a VP, it is aimed to replace the functions of the peripheral vestibular organs. Therefore, the VP needs to sense angular and linear head motions and selectively stimulate the corresponding vestibular neurons. An analogy between the natural vestibular system and the VP is illustrated in Figure 8.

Figure 8. A vestibular prosthesis needs to replace the vestibular organ functions. Canal/otolith system and the hair cells are replaced with rate sensors and an interface circuitry, respectively.

3D angular and linear head motions need to be sensed by rate sensors. Interface circuitry is needed to encode head motion information measured by the sensors into current

pulse rates and stimulate the vestibular neurons. A block diagram of the interface circuitry is shown in Figure 9.

Figure 9. The interface circuitry block diagram.

The interface circuitry needs to perform a coordinate system transformation for two reasons. One is to align the primary axes of angular and linear rate sensors with the SCC and otolith alignments. This way, the implantation operation time is reduced thereby reducing the risks and the costs of the operation. The other reason is related to current spread at the stimulation sites. Small distances between adjacent canals/otolith organs (~ 6  $\mu$ m) cause stimulation current targeted for a particular canal/otolith to excite another canal/otolith, thereby creating erroneous representation of head motion. The coordinate system transformation can be used to implement a precompensation strategy to reduce erroneous representation of head motion due to current spread.

The vestibular signal processing block is needed to implement the canal/otolith dynamics as well as the firing rate encoding observed at the vestibular neurons.

Lastly, the interface circuitry needs to stimulate the vestibular neurons. Based on clinical studies, current stimulation is proven to be successful for a VP [1]. The charge accumulation at the tissue site during electrical stimulation is harmful for the tissue in the long-term [13]. To prevent long-term harms in the tissue, electrical neuro-stimulators use

biphasic waveforms to initiate action potential at the neurons (Figure 10(a)). The first (cathodic) phase initiates the action potential, and the second (anodic) phase takes back the charge delivered to the tissue during the cathodic phase.

An H-bridge circuitry can be used to generate biphasic current pulses (Figure 10(b)) [14]. The current through a stimulation electrode is controlled by four switches that are controlled by two clocks in pairs. This way, the current flow direction across the electrode is switched. Pulse widths of the clocks  $\Phi_1$  and  $\Phi_2$  determine the phase durations of the biphasic waveform. The phase difference between the clocks determine the interphase gap, IPG, of the two phases.

Figure 10. Biphasic waveform is used to in electrical stimulators to prevent harmful electrochemical processes at the tissue sites. (a) Biphasic current pulse. The cathodic phase is followed by an anodic phase. The two phases are separated by an interphase gap (IPG) to ensure the neuron firing. (b) Biphasic current pulses can be generated across an electrode by an H-bridge circuit. Four switches are operated in pairs to switch the flow direction of the stimulation current across the electrode.

Most parameters of the aforementioned functions are patient-dependent. For instance, the general characteristics of the neural dynamics presented in Figures 3 and 7 are fixed. However, the exact locations of the poles/zeros not only vary from neuron to neuron but also from patient to patient. Similarly, firing rate values as well as current phase-widths are needed to be set to optimum values that create the stimuli that best represent the head motions in a particular patient.

To quantify the efficiency of the stimuli, the vestibular system provides an easily accessible and reliable path, namely vestibuloocular reflex (VOR). When the head is moved in one direction, the VOR moves the eye pupils in the opposite direction at the same speed to obtain a stable vision. Therefore in clinical studies, the efficiency of the stimuli delivered to vestibular neurons is assessed by monitoring the motions of the eye pupils of the subject. One of the methods that monitors eye pupil motions uses a camera to track markers that are affixed to the eyes of the subject [15]. The patient-dependent parameter values that move the eye pupils in the right directions at the correct magnitudes are the optimal values for that particular patient. After the implantation operation, the characterization of the implanted VP can be performed by monitoring the eye pupil motions in response to a series of stimuli. Based on the matrix that relates the stimuli to responses, a new matrix that would correct the sensor orientations as well as minimize the erroneous stimuli due to current spread could be obtained [16]. In practice this could be accomplished via a programming unit whereby all needed patient-dependent parameters can be programmed onto the interface circuitry.

A representation of an implanted VP system is shown in Figure 11. Besides the blocks shown in Figure 9, the complete system needs to have a wireless link to perform data and power transfer between the external and the implanted units.

#### **1.3 State-of-the-art VP Systems**

To formulate a baseline for existing VP systems, I investigated the four research groups/projects building VP systems; which are the Johns Hopkins University Group, University of Cyprus-Imperial College Group, Closed-Loop Neural Prosthesis for Vestibular Disorders (CLONS) Project, and the UC Irvine Group. In Table 1, the state-ofthe-art VP systems are summarized. In the following subsections each VP system is assessed with respect to technology, function, physical dimensions and power consumption.

Figure 11. A representation of an implanted VP system.

| Group/Project                                                                                                                           | Technology                               | Functions                         |                                           |                         | Area                    | Power                              |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------|-------------------------------------------|-------------------------|-------------------------|------------------------------------|--|

| Johns Hopkins<br>University                                                                                                             | PCB with off-<br>the-shelf<br>components | 3 Canals<br>Multipolar            | Coordinate<br>System<br>Transformation    | 8<br>current<br>sources | 841<br>mm <sup>2</sup>  | Circuitry:<br>~5 mW<br>(estimated) |  |

| University of<br>Cyprus/<br>Imperial College                                                                                            | ASIC<br>(AMS 0.35µm)                     | 3 Canals+<br>2 Otolith<br>Bipolar | NO Coordinate<br>System<br>Transformation | 3<br>current<br>sources | $6 \text{ mm}^2$        | Circuitry:<br>~120 µW              |  |

| CLONS                                                                                                                                   | ASIC<br>(X-Fab 0.6 μm<br>HV CMOS)        | 3 Canals<br>Bipolar               | Coordinate<br>System<br>Transformation    | 3<br>current<br>sources | 2.27<br>mm <sup>2</sup> | Circuitry:<br>1.1 mW               |  |

| Data for the CLONS Project correspond to per one canal stimulator. The signal processor of the CLONS Project has not been reported yet. |                                          |                                   |                                           |                         |                         |                                    |  |

Table 1. State-of-the-art Vestibular Prostheses Circuitry

### 1.3.1 The Johns Hopkins University Group

The VP system developed by this group restores SCC functions to create a normal 3D angular-VOR (aVOR) [17]. The device includes gyroscopes to detect angular velocities and MEMS linear accelerometers to detect linear accelerations. Yet, this system has been reported to process only the outputs of the gyroscopes. For electrical stimulation, the device contains four pairs of current sources that can be used as current sinks and sources. Thus, it allows implementation of simultaneous multipolar neural stimulation techniques. These

techniques are usually used to perform focused stimulation of afferents when different types of afferents are located within a small region as in the case of the vestibular afferents. The inputs from the three gyroscopes are also processed to reduce the misalignment caused by current spread at the stimulation sites. Use of a microcontroller as the signal processing unit provides the device with the capability of implementing different signal processing schemes to the sensor output signals. To do *in-vivo* measurements of electrode impedances, the system also includes an instrumentation amplifier that takes as inputs the potentials of any electrode pairs, amplifies the differential voltage, and outputs to the microelectrode. Through the microcontroller, the device interfaces with an external computer for data analysis.

Despite its capabilities, this VP system is simply integration of off-the-shelf components on a PCB. Thus, in terms of device size (29 mm x 29 mm x 5 mm) the device requires significant scaling and integration to approach the space needed for implantation. Furthermore, although low-power microcontroller and sensors have been used in the system, the power consumption is significantly high for a battery-powered implant. It was reported that the sensor power consumption (~45 mW for triaxial sensing) dominates the total power consumption of the system. Thus, this device is more suitable for animal studies rather than use as an implant.

#### 1.3.2 University of Cyprus-Imperial College Group

Similar to the Johns Hopkins Group, the system developed by this group also aims to sense angular and linear motions, process the signals from the sensors, and provide artificial stimulus to the afferents of three SCCs and two otolith organs [14], [18-20]. MEMS sensors are used in the system to sense motion in six degrees of freedom (three angular, three linear). Unlike the Johns Hopkins system, the signal processor and the stimulation circuitry have been developed as an application-specific integrated circuit (ASIC). The circuitry interfaces to either a custom-design or an off-the-shelf accelerometer. However, it can only interface to an off-the-shelf gyroscope. The sensor outputs are fed to the otolith and the SCC processors, which are implemented as inherently tunable switched capacitor filters. The current stimulator has five current sources, which can only be used in bipolar stimulation configuration [14]. The current magnitudes and the pulse widths of each of the five sources can be controlled independently. Patient-dependent parameters that vary the filter cut-off frequencies are programmed onto the device using a microcontroller. Of the circuit blocks constituting this VP system, only the tilt-processing circuitry that is used to estimate the tilt angle using an accelerometer [18] and the current stimulator circuitry [14] have been fabricated and tested separately.

This system meets the minimum requirements expected from a VP such as sensing 3D motion, processing the signals from the sensors to match the afferent dynamics, and stimulating the afferents. The reported power consumption values are 48.84  $\mu$ W, 4.963  $\mu$ W, and ~65.6  $\mu$ W for the SCC signal processor, the Tilt-processing unit, and (static power consumption of) the Current Stimulator, respectively. The footprint of the system is 3mm x 2mm. Yet, there are two deficiencies of this system that affect the performance of the device as an implant. One of them is that the system does not allow reduction of axis misalignment due to current spread. The other is that the system does not allow correction of discrepancies between the orientations of the implanted sensors and the SCCs after the implantation process.

#### 1.3.3 Closed-Loop Neural Prosthesis for Vestibular Disorders (CLONS) Project

This project, which is conducted by a consortium of eight partners, is based upon the early work of a major partner, D. Merfeld, the inventor of the first VP [21]. Unlike the first VP device, the CLONS project aims to restore vestibular information by electrically stimulating all three SCC afferents. The research steps of this project have been explained in various papers [22-26]. These steps include designing implanted and external components, building systems performing control algorithms, anatomical modeling, and animal/human experiments. The external components are the gyroscopes and the internal components are the stimulation electrodes [24]. Control algorithms of the system are reported to perform angular velocity-to-firing rate encoding and gyroscope-SCC orientation transformation [23]. The current version of the system built under CLONS project uses an off-the-shelf three-axis gyroscope to sense 3D angular velocity. The stimulator circuitry consists of a management unit and an output stage. The management unit receives command frames from the external signal processor unit and manages the output stage, which is a current DAC. The stimulator can deliver currents to electrodes in bipolar configuration [22]. Since it has been reported that an ASIC is going to be designed, the dimension of the system is expected to be small. On the other hand, a signal processor circuitry has not been designed yet. Thus, it cannot be estimated how close the system will mimic the natural vestibular afferent dynamics.

#### **1.3.4 The UC Irvine Group**

The focus of this group was to demonstrate a single-axis gyroscope customized for a vestibular prosthesis [27]. In summary, all the blocks of the system; namely the sensing unit; the signal processing unit, which consists of transfer-function and voltage-tofrequency converter units; and the current stimulation unit are implemented on a PCB. Being an off-the-shelf demonstration, the device was not designed as an implant device. Because off-the-shelf resistors, capacitors, and potentiometers are used, this system does not allow precise tuning of transfer-function or current-pulse related parameters, making the device inconvenient for animal studies. Given the rudimentary nature of the VP interface circuitry, we do not include the UC Irvine Group as state-of-the-art.

As mentioned in the Introduction, a vestibular prosthesis (VP) can be a therapeutic option for those having bilateral vestibular dysfunction. Although there have been four research groups that have built a VP system at different complexities and properties, none of those systems have been implanted in a human patient yet. However, there are two prosthetic devices that have been implanted in human subjects [28],[29]. Both of these devices are revised versions of commercial cochlear implants. While, the first device is operated by the patient to reduce the deleterious effects of dizziness caused by the Meniere's disease, the second device was used in a case study to see the feasibility of a vestibular implant for humans. Thus, neither of the devices aimed to replace malfunctioning peripheral vestibular organs.

The motivation behind my PhD research is to improve the energy-efficiency of a VP interface circuit. Considering the VP interface circuitry blocks presented in Figure 9, the lower limit for the current stimulator power consumption is limited by the stimulation current and stimulation electrode headroom voltage limitations that are imposed by the vestibular clinical studies. Therefore, the focus in this work is given to designing coordinate system transformation and vestibular signal processing blocks that make use of energyefficient signal processing techniques. To explore those techniques, part of the vestibular signal processing functions for one SCC were implemented on an experimental fieldprogrammable analog array (FPAA) platform, which is explained in Chapter 2. To investigate the limits of the FPAA as a VP interface circuit platform, a current stimulation circuit on an FPAA is also presented in Chapter 2. Then a custom design solution that meets the small area and the energy-efficiency requirements of an implantable VP system is presented in Chapter 3. The custom design includes coordinate system transformation blocks for three SCCs and two otoliths and vestibular signal processing blocks for two SCCs and one otolith. To compare the custom-design with an existing low-power signal processing system and a promising state-of-the-art VP system developed by the Johns Hopkins Group, a Texas Instruments MSP430 series ultra-low power microcontroller implementation of the VP functions is explained in Section 4.

## **CHAPTER 2**

# VESTIBULAR PROSTHESIS SIGNAL PROCESSING ON A FIELD-PROGRAMMABLE ANALOG ARRAY (FPAA) DEVELOPMENT PLATFORM

As mentioned in previous sections, *in-vivo* studies indicate a pressing need for optimizing current stimulation paradigms as well as reducing spurious stimulation. Thus, refining and optimizing encoding of angular velocity, and processing of angular velocity signals, is an essential step to achieving the clinical efficacy of a vestibular prosthesis. To investigate a potential reconfigurable, low-power option for angular velocity encoding, we explored an experimental Field Programmable Analog Array (FPAA) development platform [30].

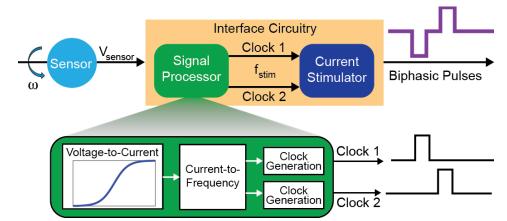

Accomplished completely in the analog domain, the signal processing circuitry generates a non-linear signal that codes angular velocity into a pulse rate for a single SCC (Figure 12).

Figure 12. Single Canal Vestibular Prosthesis System Diagram.

Producing two out-of-phase clocks, the circuit can control all of the timing features of a biphasic pulse and ultimately drive a current stimulator for targeted activation of vestibular nerve fibers. Below, a brief description of the FPAA and the procedure for realizing circuitry on the FPAA is presented.

#### 2.1. FPAA Architecture

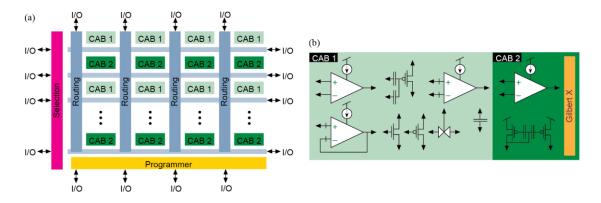

The FPAA used is an experimental chip; the Reconfigurable Analog Signal Processor (RASP) 2.8 designed by the Integrated Computational Electronics Laboratory, Georgia Institute of Technology [30]. Although a commercial FPAA could also serve as a development platform [31], we chose the RASP 2.8 since its floating gate architecture provides greater functionality through the ability to program the switches with variable impedance. In addition, by operating the circuitry in weak inversion, considerable power saving can potentially be realized.

Fabricated with the Taiwan Semiconductor Manufacturing Company (TSMC) 0.35 µm 2P3M CMOS process and operating with a 2.4 V power supply, the RASP 2.8 is comprised of computational analog blocks (CABs) and an interconnect network (Figure 13(a)). A total of 32 CABs (CAB1 or CAB2) consist of circuit elements and blocks at different levels of complexity. Circuit elements/blocks such as transconductance amplifiers (OTAs), multi-input floating gates, nFET/pFET transistors, floating capacitors, Gilbert Multipliers, and floating-gate current mirrors are distributed among CAB1 and CAB2 (Figure 13(b)). The role of the interconnect network, which consists of switches (floating-gate pFETs) and interconnect lines, is to sensitize connections between CAB elements/blocks. In addition, global interconnect lines are also connected to input/output pins for voltage/current measurements.

Figure 13. Floating-gate FPAA architecture. (a) The FPAA consists of an 8 x 4 matrix of Computational Analog Blocks (CABs) interconnected through crossbar networks. (b) Circuit elements/blocks are distributed among CAB1 and CAB2.

To implement a particular circuit on the FPAA, connections are made by programming the necessary switches in the interconnect network. An automated placement and routing tool, the Generic Reconfigurable Array Specification and Programming Environment (GRASPER), determines which switches to activate. GRASPER converts a user-generated SPICE netlist describing the circuit into a netlist of switches [30]. To program a floating-gate pFET, negative charge is injected onto the floating-gate of the transistor. The amount of the charge trapped at the floating-gate affects the effective gate potential of the transistor and thus directly controls the conductance of the device. Briefly, the charge injection mechanism is accomplished by applying a high potential difference (~15 V) between the drain and the source terminals. As a result, a programming current,  $I_{prog}$ , passes across the two terminals.  $I_{prog}$  can be varied between 1 nA-32 µA, with higher  $I_{prog}$  causing more negative charge to be trapped at the floating-gate. The communication between the PC and the FPAA is achieved through a microprocessor-based board.

#### 2.1.1. Signal Processor

For each SCC, the encoding of angular velocity into a pulse rate is based on a relationship validated in animal models [32]. This non-linear relationship between the angular velocity and the firing rate is represented as (Figure 10):

$$f_{stim} = 200 + 150 \tanh\left(\frac{\omega}{500/3}\right),\tag{3}$$

where  $\omega$  is the angular velocity in °/sec, and  $f_{stim}$  is the pulse rate in pulses per second (pps). The offset value in the equation conveys a baseline pulse rate corresponding to zero angular velocity.

A biphasic current scheme (Figure 14) is generated to prevent any charge accumulation at the tissue site that can cause long-term adverse effects [33]. The amplitude and pulse duration (PD) of the cathodic pulse determines how much charge is delivered to the neural tissue. Similarly, the PD and the amplitude of the anodic pulse determine how much charge is returned from the tissue. The interphase gap (IPG) separates the two pulse periods to ensure the firing of the neuron. This control is essential for optimizing stimulus waveforms to reduce threshold, improve spatial selectivity, and reduce spurious stimulation.

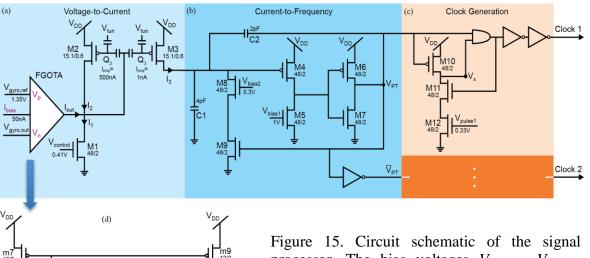

Figure 14. Non-linear relationship between the angular velocity and the firing rate. A representative biphasic pulse is shown inside the graph.

The signal processor provides the user with the freedom to control all timing features of a biphasic current pulse. The signal processor senses an analog voltage output from an inertial sensor,  $V_{gyro,out}$ , and converts this voltage into two out-of-phase clocks (Clock 1 and Clock 2) each with a frequency of  $f_{stim}$ . In turn, Clock 1 and Clock 2 serve as control signals for a stimulator. The respective pulse duration of the two clocks determine

the cathodic and the anodic PD of the biphasic current waveform. The phase difference between Clock 1 and Clock 2, less the PD, determines an IPG. The three blocks constituting the signal processor are the voltage-to-current converter block, the current-to-frequency converter block, and the clock generation block (Figure 15). Each block is described in detail below.

Figure 15. Circuit schematic of the signal processor. The bias voltages  $V_{gyro,ref}$ ,  $V_{control}$ ,  $V_{bias1}$ ,  $V_{bias2}$ ,  $V_{pulse1}$  and  $V_{pulse2}$  are generated using an off-chip DAC housed on a development board.

(a) The voltage-to-current converter block transfers the voltage signal from the gyroscope,  $V_{gyro,out}$ , into a current signal,  $I_3$ . The current  $I_3$  is related to angular velocity through a *tanh* function. The minimum level of  $I_3$  is controlled

by  $V_{control}$ . By adjusting  $V_{gyro,ref}$  an offset can be added to  $V_{gyro,out}$ . This serves to translate the  $I_3$  along the x-axis of the  $I_3$  vs.  $V_{gyro,out}$  curve.

m8

m5

m6

(b) The current-to-frequency converter block converts the current signal,  $I_3$ , into the pulse train output  $V_{PT}$ . Linearly related to  $I_3$ , the frequency of  $V_{PT}$  determines  $f_{stim}$ .

(c) Two similar fully digital Clock Generation stages create Clock 1 and Clock 2. The pulse width of Clock 1 is controlled by  $V_{pulsel}$  and a similar relationship exists for Clock 2.

(d) The FGOTA is the core of the voltage-to-current converter block. In the sub-threshold region, the output current,  $I_{out}$ , of the FGOTA is related to its differential input voltage,  $V_p$ - $V_n$ , through a *tanh* function.  $I_{bias}$  is the bias current which determines the region of operation and is set up during the programming stage by  $V_{bias}$ .

#### 2.1.1.1. Voltage-to-Current Converter Block

The first block of the Signal Processor transfers the analog voltage output from an inertial sensor, gyroscope, into a current signal (Figure 15(a)). As indicated in (3), the stimulation frequency is related to angular velocity through a hyperbolic tangent function. In the spirit of biomorphic circuit design, we followed an integrate-and-fire neuron scheme utilizing a floating-gate OTA (FGOTA) [34]. In the sub-threshold region, the output current,  $I_{out}$ , of the FGOTA is related to its differential input voltage,  $V_p$ - $V_n$ , through a *tanh* function:

$$I_{out} = I_{bias} \tanh\left(\frac{\kappa\alpha(V_p - V_n)}{2U_T}\right),\tag{4}$$

where  $\kappa$  is a constant relating the surface potential of a transistor to its gate voltage,  $\alpha$  is the attenuation factor due to the capacitive divider at the input differential pair,  $I_{bias}$  is the bias current which determines the region of operation of the transistors, and  $U_T$  is the thermal voltage. Thus, an FGOTA is at the core of the voltage-to-current converter block.

In our implementation,  $V_{gyro,out}$ , the output of the gyroscope, is connected to  $V_n$  input of the FGOTA.  $V_p$  is tied to  $V_{gyro,ref}$ , the reference voltage for the gyroscope. To ensure that  $I_{out}$  is positive, M1, drawing  $I_1$  from the output node of the FGOTA, adds a DC offset. The current  $I_1$  is controlled by  $V_{control}$  and  $I_2$  is the DC shifted version of  $-I_{out}$ . To ensure that  $I_2$ maintains  $f_{stim}$  within the 50-350 Hz interval,  $I_2$  is scaled and mirrored using a mismatched current mirror circuit. The mirror circuit is formed by two floating-gate pFETs, M2 and M3, thereby creating  $I_3$ . Since device sizes are fixed in the FPAA, the mismatch between M2 and M3 is controlled by programming varying amounts of charges (Q2 and Q3) onto their respective floating gates. For the  $I_{prog}$  values of M2 and M3 shown in Figure 15, the  $I_2/I_3$  ratio is measured to be ~80. The minimum level of  $I_3$  is controlled by  $V_{control}$ . By adjusting  $V_{gyro,ref}$  an offset can be added to  $V_{gyro,out}$ . This serves to translate the  $I_3$  along the x-axis of the  $I_3$  vs.  $V_{gyro,out}$  curve.

#### 2.1.1.2. Current-to-Frequency Converter and Clock Generator Blocks

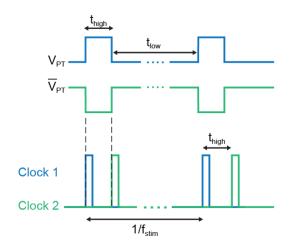

Since these two blocks function in an integrated fashion to provide control signals for a current stimulator, we begin by describing the main signals of interest followed by a detailed description of each block. The main output of the current-to-frequency converter block is  $V_{PT}$ , a frequency modulated pulse train with an adjustable pulse-width. Figure 16 depicts the duration that  $V_{PT}$  is high and low,  $t_{high}$  and  $t_{low}$  respectively.

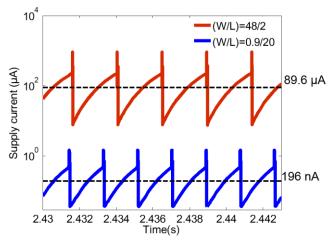

Figure 16. Pulse timing control. The signal  $V_{PT}$  is output from the current-to-frequency converter block with a pulse rate of  $f_{stim}$ . The rising edge of  $V_{PT}$  triggers Clock 1 in the clock generation block. The clock generation block also controls the PD, the duration of each clock. The delay between the clocks,  $t_{high}$ , less the PD is the IPG.