# SYSTEM ABSTRACTIONS FOR RESOURCE SCALING ON HETEROGENEOUS PLATFORMS

A Thesis Presented to The Academic Faculty

by

Vishal Gupta

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology December 2013

Copyright  $\bigodot$  2013 by Vishal Gupta

# SYSTEM ABSTRACTIONS FOR RESOURCE SCALING ON HETEROGENEOUS PLATFORMS

Approved by:

Dr. Karsten Schwan, Advisor School of Computer Science Georgia Institute of Technology

Dr. Sudhakar Yalamanchilli School of Electrical & Computer Engineering Georgia Institute of Technology

Dr. George Cox School of Computer Science Georgia Institute of Technology Dr. Scott Hahn Systems Architecture Lab Intel Labs

Dr. Ricardo Bianchini Department of Computer Science *Rutgers University*

Date Approved: September 5, 2013

om ajnāna-timirāndhasya jnānānjana-śalākayā cakṣur unmīlitam yena tasmai śrī-gurave namaḥ

## ACKNOWLEDGEMENTS

There are many people who have been instrumental in helping me complete my Ph.D. I would like to take this opportunity to formally thank them for their support.

I would like to sincerely thank my thesis advisor Dr. Karsten Schwan for his guidance and support during my doctoral studies. He always encouraged exploring ideas, giving me his feedback, and thus, nudging me along at each step from finding a research topic to shaping this thesis till its completion. I am especially thankful to him for allowing me to change my research area in the second year of my Ph.D. I also thank him for for providing excellent lab facilities, hardware equipments, travel assistance, and support for doing internships which gave me valuable industry exposure.

I feel indebt while expressing my immense gratitude towards Dr. Krishnan for making me understand the purpose behind doing a Ph.D and giving me the right focus. His guidance made my graduate studies a wonderful experience which otherwise felt like a difficult journey at times. His teachings on principle-centered life affected both my professional and personal life deeply. I dedicate this thesis to him without whose well-wishes and encouragement, this work would not have completed.

I owe special thanks to Mr. Ganapati Srinivasa and Dr. Scott Hahn for giving me the opportunity to do internships at Intel Labs which helped me gain momentum in my Ph.D. The projects initiated and the resources made available at Intel provided me the building blocks to develop this thesis further. I am also thankful to other team members including Paul Brett, Dheeraj Reddy, David Koufaty, Eugene Gorbatov, and Karthik Gururaj for all the insightful discussions regarding internals of Linux kernel and Intel architecture. Also, many thanks to Intel for donating the QuickIA system and their financial support through ISTC grants and fellowship award. I am grateful to my thesis committee members Dr. Sudhakar Yalamanchili, Dr. George Cox, Dr. Scott Hahn, and Dr. Ricardo Bianchini for their feedback which was critical in developing a more coherent thesis. In addition, I wish to thank Dr. Ada Gavrilovska and Dr. Hyesoon Kim for giving their valable guidance at various junctures during Ph.D. I would also like to acknowledge my MS advisor Dr. Montek Singh for supporting my decision to move to Georgia Tech for doctoral studies.

I am thankful to my friends Sanket and Vishal for their association, not letting me lose focus of life beyond academics. I would also like to acknowledge all of my labmates for their assistance in overcoming various obstacles at work. My special thanks to Hrishi and Ripal who have been of great help and good friends to me over the years. I am thankful to my roommates Balaji, Partha, and Pushkar for their companionship making my stay in Atlanta pleasant. I also thank Susie McClain for taking care of all the administration work and the devotees for providing us with 'prasadam' lunch on-campus, relieving me from cooking on time-constrained days.

Foremost and above all, I thank Lord for His grace and blessings for giving me the opportunity and ability to get to this point, and His mercy in the form of countless other things in life for which I feel undeserving. Last but not the least, I would like to express my deep gratitude towards my parents and brother for their constant love, guidance, and support all these years. I owe this degree to them without whose selfless sacrifices, it would not have been possible for me to reach this juncture.

# TABLE OF CONTENTS

| DE            | DIC | ATIOI  | N                               | iii          |

|---------------|-----|--------|---------------------------------|--------------|

| AC            | KNO | OWLE   | DGEMENTS                        | iv           |

| LIS           | T O | F TAE  | BLES                            | $\mathbf{x}$ |

| LIS           | T O | F FIG  | URES                            | xi           |

| $\mathbf{SU}$ | MM. | ARY .  |                                 | xiii         |

| Ι             | INT | ROD    | UCTION                          | 1            |

|               | 1.1 | Motiv  | ation                           | 1            |

|               |     | 1.1.1  | Resource Scaling                | 1            |

|               |     | 1.1.2  | Platform Heterogeneity          | 2            |

|               | 1.2 | Challe | enges & Approach                | 4            |

|               | 1.3 | Thesis | s Statement and Contributions   | 6            |

|               | 1.4 | Thesis | s Organization                  | 8            |

| II            | HE  | ΓERO   | GENEOUS CORES: BRAWNY VS. WIMPY | 9            |

|               | 2.1 | Introd | luction                         | 9            |

|               | 2.2 | Why l  | heterogeneity?                  | 11           |

|               |     | 2.2.1  | Why wimpy cores?                | 11           |

|               |     | 2.2.2  | Why not wimpy cores?            | 12           |

|               | 2.3 | Workl  | oad Description                 | 13           |

|               |     | 2.3.1  | Client Workload Suite           | 13           |

|               |     | 2.3.2  | Server Workloads                | 14           |

|               | 2.4 | Evalua | ation                           | 15           |

|               |     | 2.4.1  | Experimental Platform           | 15           |

|               |     | 2.4.2  | Performance Monitoring          | 16           |

|               |     | 2.4.3  | Power Measurement               | 16           |

|               |     | 2.4.4  | Methodology                     | 16           |

|               |     | 2.4.5  | Limitations                     | 17           |

|     | 2.5 | Exper  | imental Results                 | 17 |

|-----|-----|--------|---------------------------------|----|

|     |     | 2.5.1  | Client Workload Evaluation      | 18 |

|     |     | 2.5.2  | Server Workload Analysis        | 22 |

|     |     | 2.5.3  | Opportunity Analysis            | 24 |

|     | 2.6 | Relate | d Work                          | 26 |

|     | 2.7 | Summ   | ary                             | 28 |

| III | BE  | YOND   | CORE: UNCORE & MEMORY SUBSYSTEM | 30 |

|     | 3.1 | Uncor  | e subsystem                     | 30 |

|     |     | 3.1.1  | What is uncore?                 | 32 |

|     |     | 3.1.2  | Idle State Coordination         | 32 |

|     |     | 3.1.3  | Impact of uncore                | 33 |

|     | 3.2 | Exper  | imental Evaluation              | 34 |

|     |     | 3.2.1  | Testbed                         | 34 |

|     |     | 3.2.2  | Client Workloads                | 35 |

|     |     | 3.2.3  | Methodology                     | 36 |

|     |     | 3.2.4  | Power Model                     | 36 |

|     |     | 3.2.5  | Results                         | 38 |

|     | 3.3 | Hetero | ogeneous Memory Organization    | 40 |

|     | 3.4 | Impler | mentation                       | 43 |

|     |     | 3.4.1  | Memory Access Tracking          | 43 |

|     |     | 3.4.2  | Memory Allocation Policy        | 45 |

|     | 3.5 | Exper  | imental Evaluation              | 46 |

|     |     | 3.5.1  | Heterogeneous Memory Emulation  | 46 |

|     |     | 3.5.2  | Workloads                       | 47 |

|     |     | 3.5.3  | Results                         | 48 |

|     | 3.6 | Relate | ed Work                         | 50 |

|     | 3.7 | Summ   | ary                             | 52 |

| IV |     |        | MATES: PROVIDING HIGH DYNAMIC RANGE ON PLATFORMS | 53      |

|----|-----|--------|--------------------------------------------------|---------|

|    | 4.1 | Introd | luction                                          | 53      |

|    | 4.2 | Motiv  | ation                                            | 54      |

|    |     | 4.2.1  | Client Workloads                                 | 55      |

|    |     | 4.2.2  | Client Devices                                   | 57      |

|    | 4.3 | Dynar  | mic Power Range                                  | 58      |

|    | 4.4 | Hetero | oMates Design                                    | 59      |

|    |     | 4.4.1  | Core Groups                                      | 59      |

|    |     | 4.4.2  | H-state Controller                               | 61      |

|    |     | 4.4.3  | Uncore-aware Operation                           | 63      |

|    |     | 4.4.4  | Remote Behavior Prediction                       | 64      |

|    | 4.5 | Imple  | mentation                                        | 66      |

|    | 4.6 | Exper  | imental Evaluation                               | 67      |

|    |     | 4.6.1  | Experimental Platform                            | 67      |

|    |     | 4.6.2  | Workloads                                        | 68      |

|    |     | 4.6.3  | Methodology                                      | 68      |

|    | 4.7 | Exper  | imental Results                                  | 69      |

|    |     | 4.7.1  | Performance-driven Policy                        | 69      |

|    |     | 4.7.2  | Power-driven Policy                              | 71      |

|    | 4.8 | Relate | ed Work                                          | 73      |

|    | 4.9 | Summ   | nary                                             | 74      |

| V  |     |        | VISOR: ELASTIC RESOURCE SCALING ON HETERO        | -<br>75 |

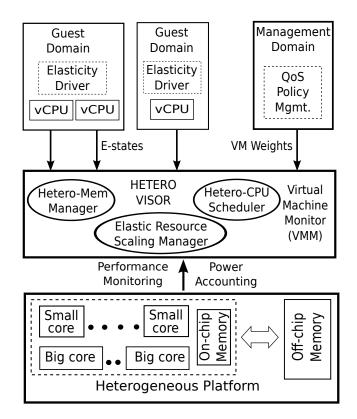

|    | 5.1 | Introd | luction                                          | 75      |

|    | 5.2 | Elasti | city using Heterogeneity                         | 77      |

|    |     | 5.2.1  | Elasticity in Clouds                             | 77      |

|    |     | 5.2.2  | Exploiting Heterogeneity                         | 79      |

|    | 5.3 | Desig  | n                                                | 80      |

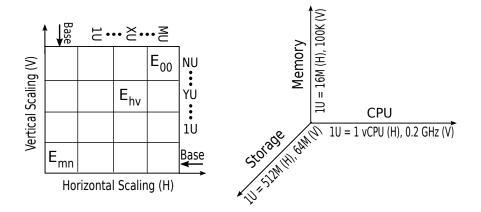

|    |     | 5.3.1  | Elasticity States                  | 82  |

|----|-----|--------|------------------------------------|-----|

|    |     | 5.3.2  | Elasticity Manager                 | 83  |

|    |     | 5.3.3  | Elasticity Driver                  | 86  |

|    |     | 5.3.4  | Discussion                         | 88  |

|    | 5.4 | Impler | nentation                          | 88  |

|    | 5.5 | Evalua | ation                              | 89  |

|    |     | 5.5.1  | Experimental Setup                 | 89  |

|    |     | 5.5.2  | Workloads                          | 90  |

|    | 5.6 | Result | s                                  | 91  |

|    | 5.7 | Relate | d Work                             | 97  |

|    |     | 5.7.1  | Resource Management in Clouds      | 97  |

|    |     | 5.7.2  | Heterogeneous Processor Scheduling | 98  |

|    | 5.8 | Summ   | ary                                | 98  |

| VI | CO  | NCLU   | SIONS & FUTURE WORK                | 100 |

|    | 6.1 | Conclu | usions                             | 100 |

|    | 6.2 | Future | e Work                             | 103 |

| AP | PEN | DIX A  | A — CLIENT WORKLOAD SUITE          | 106 |

| AP | PEN | DIX E  | B — VIRTUAL CORE SCALING MODELS    | 109 |

| RE | FER | ENCE   | $\mathbf{S}$                       | 112 |

| VI | ГА. |        |                                    | 124 |

# LIST OF TABLES

| 1  | Client workload suite                                                                  | 13 |

|----|----------------------------------------------------------------------------------------|----|

| 2  | Server workload summary                                                                | 14 |

| 3  | Performance and power comparison for Xeon, Atom, and Heteroge-<br>neous configurations | 26 |

| 4  | Core and package idle state coordination                                               | 33 |

| 5  | Client workload summary                                                                | 35 |

| 6  | Workload summary                                                                       | 47 |

| 7  | Modern client workloads                                                                | 68 |

| 8  | Thresholds for performance- and power-driven policies                                  | 69 |

| 9  | Mechanisms for elastic resource scaling in clouds                                      | 78 |

| 10 | Thresholds for QoS- and resource-driven scaling policies                               | 90 |

# LIST OF FIGURES

| 1  | Platforms consisting of heterogeneous resources                                                           | 3  |

|----|-----------------------------------------------------------------------------------------------------------|----|

| 2  | Resource scaling on heterogeneous platforms                                                               | 5  |

| 3  | Best of both latency and throughput using heterogeneous cores $% \mathcal{A} = \mathcal{A} = \mathcal{A}$ | 12 |

| 4  | QuickIA heterogeneous multicore platform                                                                  | 15 |

| 5  | A comparison of CPU usage profile of client vs. server workloads                                          | 18 |

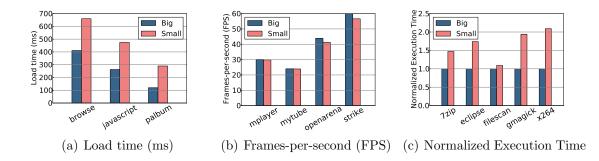

| 6  | Performance and energy impact of using small vs. big cores for client workloads                           | 19 |

| 7  | A comparison of the behavior of client workloads on big vs. small cores                                   | 20 |

| 8  | User-perceived performance for client applications                                                        | 21 |

| 9  | Performance and Performance/Watt comparison of server workloads<br>on Xeon vs. Atom CPUs                  | 23 |

| 10 | Core and uncore in multicore processors                                                                   | 32 |

| 11 | Effect of uncore power on the energy-efficiency of heterogeneous cores                                    | 34 |

| 12 | Experimental heterogeneous platform                                                                       | 35 |

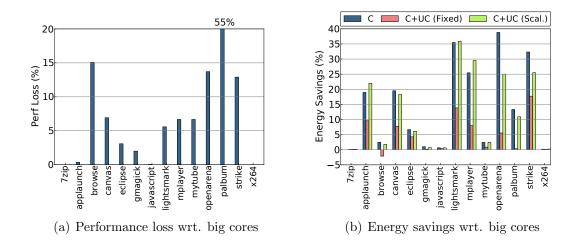

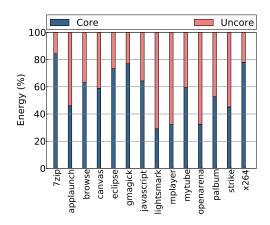

| 13 | A comparison of the behavior of several client workloads on big vs. small cores                           | 38 |

| 14 | Application performance comparison on big and small cores                                                 | 39 |

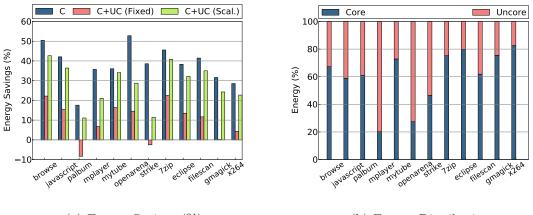

| 15 | Uncore evaluation showing energy savings and energy distribution $\ .$ .                                  | 39 |

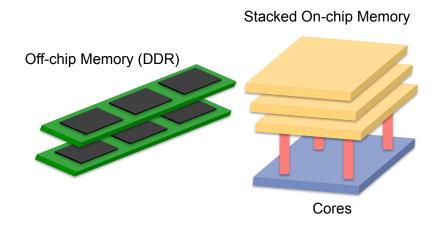

| 16 | Heterogeneous memory organization consisting of a combination of on-<br>chip and off-chip memories.       | 41 |

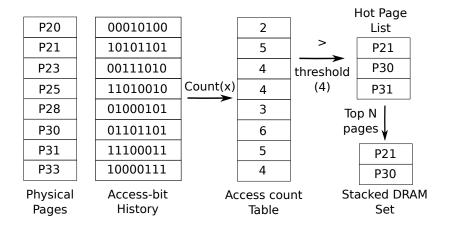

| 17 | Hot page detection using a-bit history                                                                    | 44 |

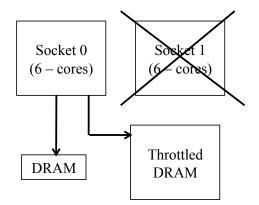

| 18 | Emulated heterogeneous memory platform                                                                    | 46 |

| 19 | Bandwidth and latency comparison for different memory configurations                                      | 47 |

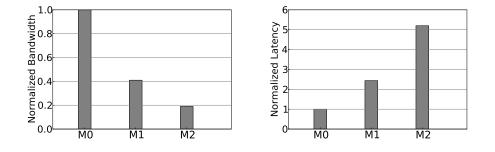

| 20 | WSS curve for SPEC CPU2006 applications (x-axis = time (s), y-axis = WSS (MB)). $\ldots$                  | 48 |

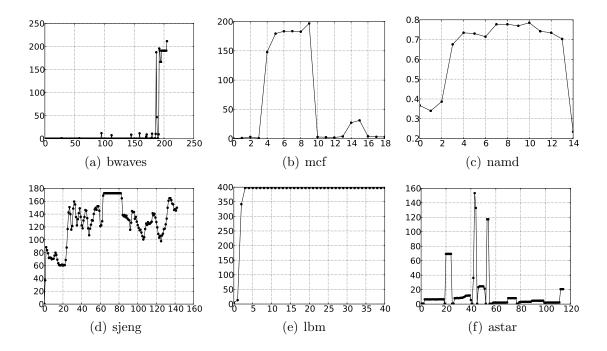

| 21 | Comparison of performance impact of memory slow down with different memory configurations                 | 49 |

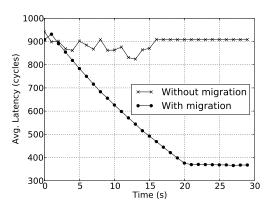

| 22 | Micro-benchmark results: Memory access latency with and without hot-page migration                        | 50 |

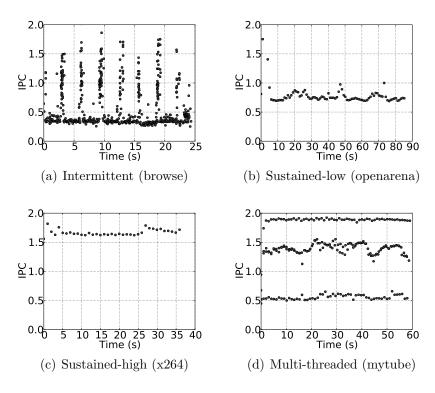

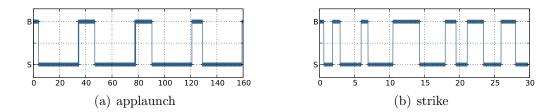

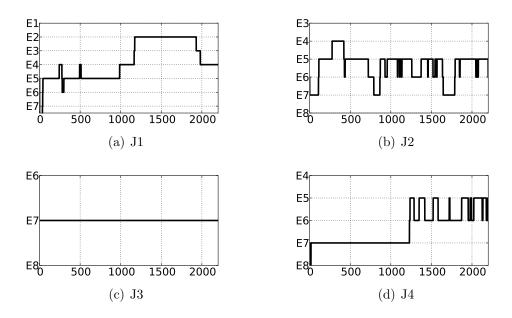

| 23 | Diverse client workload profiles (IPC vs. Time)                                                                                               | 56 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

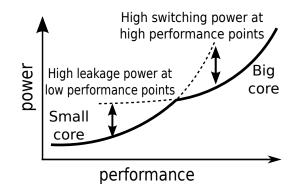

| 24 | Using a heterogeneous processor provides a wide dynamic power range.                                                                          | 58 |

| 25 | A core groups consisting of three heterogeneous cores: a big (B), a small (S), and a tiny (T) core exposed as three H-states. $\ldots$        | 60 |

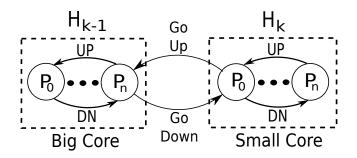

| 26 | H-state and P-state transition state machines. H-state determine the core for execution, while P-states determine the frequency on that core. | 61 |

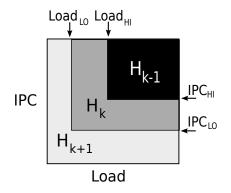

| 27 | H-state scaling operations in response to application IPC and CPU load.                                                                       | 62 |

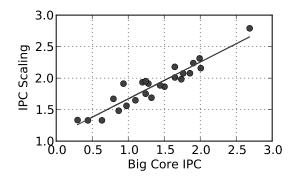

| 28 | Modeling IPC scaling as a function of IPC                                                                                                     | 65 |

| 29 | Experimental heterogeneous platform                                                                                                           | 67 |

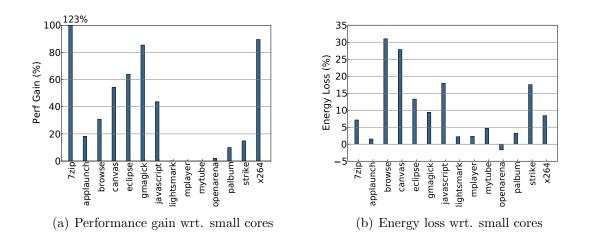

| 30 | Comparison of performance-driven policy with big core execution                                                                               | 69 |

| 31 | Core and uncore energy distribution                                                                                                           | 70 |

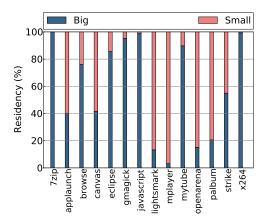

| 32 | Comparison of power-driven policy with small core execution                                                                                   | 71 |

| 33 | Residency on big and small cores                                                                                                              | 72 |

| 34 | Big (B) and small (S) core usage profile (x-axis: time(s)) $\hdots$                                                                           | 73 |

| 35 | Using heterogeneity to enable resource scaling                                                                                                | 79 |

| 36 | System architecture for HeteroVisor                                                                                                           | 81 |

| 37 | Elasticity state abstraction for resource scaling                                                                                             | 82 |

| 38 | Models for vCPU scaling using heterogeneity                                                                                                   | 84 |

| 39 | Virtual core scaling using heterogeneous cores                                                                                                | 85 |

| 40 | Workload traces based on Google cluster data [40]                                                                                             | 91 |

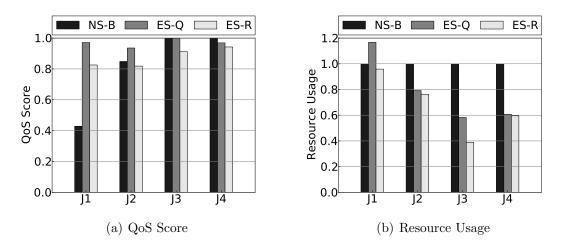

| 41 | Performance comparison of heterogeneous configurations with the na-<br>tive platform                                                          | 92 |

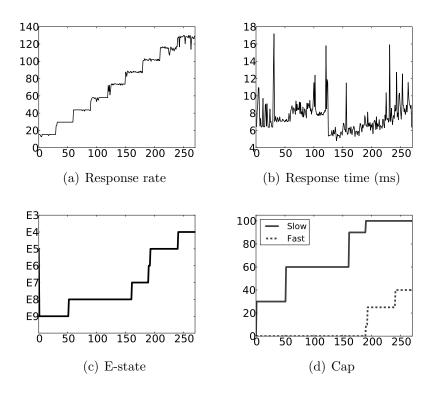

| 42 | QoS variation with different E-states                                                                                                         | 93 |

| 43 | Elastic scaling experiment using the webserver workload $(x-axis = time (s))$                                                                 | 94 |

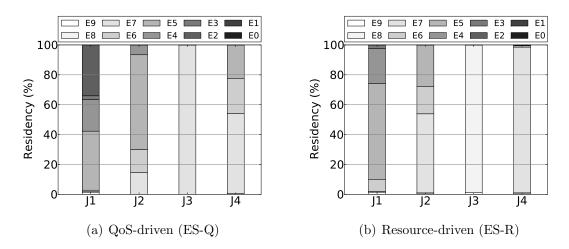

| 44 | Experimental results for CPU E-state scaling                                                                                                  | 95 |

| 45 | E-state residencies for different scaling policies                                                                                            | 96 |

| 46 | E-state switch profiles showing usage of various states $(x-axis = time (s), y-axis = E-states)$                                              | 97 |

## SUMMARY

The increasingly diverse nature of modern applications makes it critical for future systems to have dynamic resource scaling capabilities which enable them to adapt their resource usage to meet user requirements. Such mechanisms should be both fine-grained in nature for resource-efficient operation and also provide a high scaling range to support a variety of applications with diverse needs. To this end, heterogeneous platforms, consisting of components with varying characteristics, have been proposed to provide improved performance/efficiency than homogeneous configurations, by making it possible to execute applications on the most suitable component. However, introduction of such heterogeneous architectural components requires system software to embrace complexity associated with heterogeneity for managing them efficiently. Diversity across vendors and rapidly changing hardware make it difficult to incorporate heterogeneity-aware resource management mechanisms into mainstream systems, affecting the widespread adoption of these platforms.

Addressing these issues, this dissertation presents novel abstractions and mechanisms for heterogeneous platforms which decouple heterogeneity from management operations by masking the differences due to heterogeneity from applications. By exporting a homogeneous interface over heterogeneous components, it proposes the scalable 'resource state' abstraction, allowing applications to express their resource requirements which then are dynamically and transparently mapped to heterogeneous resources underneath. The proposed approach is explored for both modern mobile devices where power is a key resource and for cloud computing environments where platform resource usage has monetary implications, resulting in HeteroMates and HeteroVisor solutions. In addition, it also highlights the need for hardware and system software to consider multiple resources together to obtain desirable gains from such scaling mechanisms. The solutions presented in this dissertation open ways for utilizing future heterogeneous platforms to provide on-demand performance, as well as resource-efficient operation, without disrupting the existing software stack.

## CHAPTER I

## INTRODUCTION

### 1.1 Motivation

#### 1.1.1 Resource Scaling

The diversity in the behavior of modern applications, both across applications and within applications, keeps growing. For instance, users perform a wide variety of tasks on mobile devices, ranging from low activity audio playback to compute-intensive gaming and media editing. Concerning server systems, the behavior of various applications can also be highly variable, either due to various phases in the application or variation in input load at different durations. Apart from the applications, the demands from the users of these platforms can be highly variable as well. For instance, a user may desire high energy-efficiency when operating the device on battery which may be less relevant when running on wall-power. Similarly, elastic resource scaling is a core feature for cloud platforms, due to the cost implications of used resources, particularly in the IaaS (infrastructure-as-a-service) environments like Amazon Elastic Compute Cloud (EC2) [5] and Google Compute Engine (GCE) [28].

This diverse nature of applications and user preferences demands systems that support various operating modes in order to meet their dynamic needs, thus, providing both high-performance and resource-efficient operation. However, balancing between these conflicting goals of on-demand performance and resource-efficiency can be challenging. For instance, supporting high levels of performance on a mobile system may affect its battery life negatively. Therefore, these systems should support dynamic resource scaling capabilities to address both of the requirements. Without such capabilities, a system has to either sacrifice performance for under allocation scenarios or waste resources as in the case of over allocation. Further, it is non-trivial to figure out the right resource allocations statically which may require profiling the application under different configurations.

There are two key features for the resource management methods to be effective. First, they should be *fine-grained* in nature, implying that they should allow scaling resources in small quantities at short timescales for efficient operation. Second, the mechanisms should provide a *large scaling range* to meet the requirements of highly diverse applications. Various scaling mechanisms are already prevalent in existing systems including dynamic voltage scaling for processors [82], ballooning for memory [9], and virtual machine (VM) scaling, i.e., varying the number of VM instances used by an application as done by Amazon EC2 AutoScale [3]. While techniques like voltage scaling are fine-grained in nature but have limited scaling range, VM-level scaling options are rather a coarse-grained and heavy-weight operation.

#### 1.1.2 Platform Heterogeneity

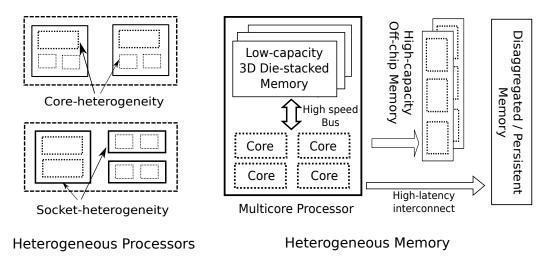

The approach used in this work exploits resource heterogeneity to enhance the scaling capabilities of modern platforms. Heterogeneity can exist in various platform subsystems such as processor, memory, and storage.

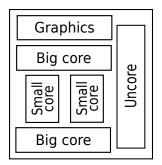

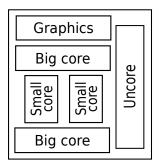

Heterogeneous processors, consisting of CPU cores that different in their performance/power capabilities, have been proposed as an energy-efficient alternative to homogeneous configurations [23, 30, 55]. This form of performance heterogeneity can exist at both levels: cores within a socket or across sockets as shown in Figure 1. There are several commercial implementations of such heterogeneous CPU architecture [18, 29, 45, 78]. Several studies have shown that different processor architectures are suited for different applications. For example, prior work has discussed the utility of low-powered cores for the design of datacenters [6, 48] as well as the need for highperformance brawny cores [10, 59]. Various scheduling methods for heterogeneous

Figure 1: Platforms consisting of heterogeneous resources

cores have also been investigated [32, 54, 64, 92].

Similarly, introduction of new memory technologies such as die-stacked 3D memories, non-volatile memories, in addition to traditional DRAM, can result into a hierarchy of heterogeneous memory organization shown in Figure 1. 3D stacked memories can provide lower latency and higher bandwidth, in comparison to traditional offchip memories [67]. However, the capacity of such memories is likely to be limited to only a few hundreds of megabytes [69]. Thus, a combination of both fast on-chip memory with additional slower off-chip memory is needed for higher capacity and expansion capabilities, specially for high-end enterprise machines. Further, addition of disaggregated memory or persistent memory technologies can also result in memory heterogeneity [21, 88, 49, 65].

Similar heterogeneity can exist in storage subsystem as well composed of persistent memory, flash memory, and hard disk based components. In this work, we focus on heterogeneous processors and memories, but the approach is applicable to other resources as well.

# 1.2 Challenges & Approach

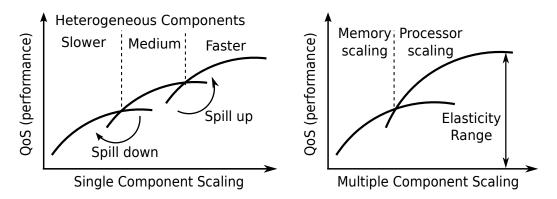

The aim of this dissertation is to enable fine-grained scaling mechanisms on such heterogeneous platforms taking user requirements into account for intelligent and efficient allocation. To this end, it provides a scalable resource interface using heterogeneous components such that it uses various heterogeneous components dynamically, according to the scaling requirements expressed by the user. A scale up operation results into using a larger proportion of the faster resource for execution (a thread or a page). Similarly, a scale down operation would imply using the slower resource. This component level scaling enables a fine-grain scaling interface. Moreover, such scaling can be applied to various platform resources such as processor, memory, and storage subsystem to provide a highly scalable platform with large scaling range.

However, introduction of heterogeneity on the platforms raises new resource management challenges regarding the interface for exposing heterogeneity and mechanisms for allocation of heterogeneous resources to applications. There are two ways to approach this problem. For instance, in a virtualized environment, both hypervisor and guest operating system run their resource management operations. One option would be to expose the heterogeneous components and delegate the responsibility of heterogeneity-aware resource management to guest VMs. This choice, though giving more flexibility to applications, can be too disruptive requiring changes across the stack. An alternative approach would be to manage heterogeneous platforms in the hypervisor, thus, hiding heterogeneity for easier adoption of these systems. However, this approach can be too restrictive, not providing user and applications the ability to express their allocation preferences.

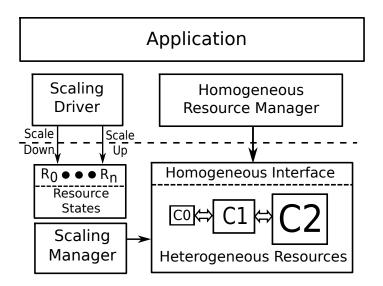

The techniques proposed in this dissertation aim to achieve the advantages of both the approaches: having flexibility of resource allocation but not overloading the applications with complexity. The proposed interface, as depicted in Figure 2, is inspired by the P-state (performance state) abstraction used by modern operating systems to

Figure 2: Resource scaling on heterogeneous platforms

perform dynamic voltage and frequency scaling (DVFS). Leveraging this, it presents a 'resource-state' interface, defining multiple-levels of resource allocations which can be requested by the application using a scaling driver, similar to the CPU governor as in the case of P-states. The input from the scaling driver is used by a scaling manager to perform heterogeneity-aware resource allocation. Thus, differences due to component heterogeneity are handled by the manager hidden from the remaining system. There are several advantages to the proposed abstractions:

- The resource state interface decouples heterogeneity management handled by the scaling manager from policy management which is handled by the scaling driver. Thus, it provides a way to hide heterogeneity which is critical to support legacy software and applications for wider adoption of such platforms.

- The scaling driver mechanism provides a way for each application to guide resource allocation to suit its own needs by using a driver customized to its own needs. For example, an application may use a power or cost-driven policy while the other application which is more sensitive to performance can employ a performance-driven policy.

• The interface shown is generic to be used across different components. Thus, it can be used to perform resource scaling across processor, memory, and storage subsystem. Further, it is also applicable to systems involving multiple levels of heterogeneity such as using stacked DRAM, off-chip DRAM, and persistent memory.

In this dissertation, we analyze the impact of heterogeneity by considering several use cases for both server systems and client devices and develop resource management methods to intelligently map heterogeneous resources to different workloads. Approaches, associated methods, and their implementation are evaluated experimentally using representative heterogeneous platforms and workloads from the mobile and the enterprise spaces.

## 1.3 Thesis Statement and Contributions

This dissertation aims to support the following hypothesis:

Novel resource management abstractions can exploit platform heterogeneity to enhance resource scaling capabilities on future systems, without disrupting the existing software stack.

To this end, this dissertation makes the following specific contributions:

We first perform a comparative analysis of heterogeneous multicores on the performance and energy efficiency of mobile devices and server systems. Using several real-world workloads from both the mobile and enterprise domains, experimental evaluations are carried out on a unique experimental testbed comprised of real heterogeneous CPUs that differ in both their core architecture and cache sizes, comparing the performance and efficiency for these applications. The experimental results presented in this study provide platform and system software designers a perspective on the trade-offs involved with these architectures and thus make optimal design choices. Extending the analysis on heterogeneous cores, we also consider the 'uncore' subsystem, which in modern platforms, is an increasingly important contributor to total SoC power. Using a unique testbed comprised of heterogeneous cores with a shared uncore, we highlight the need for uncore-awareness and uncore scalability to maximize intended efficiency gains from heterogeneous cores. Next, going beyond the processor by considering the memory subsystem, we present an analysis and description of techniques for managing the heterogeneous memory resources of next generation multicore platforms with fast 3D die-stacked memory and slow off-chip memory. The resulting ability to characterize the memory behavior of representative server workloads demonstrates the feasibility of software-managed heterogeneous memory resources.

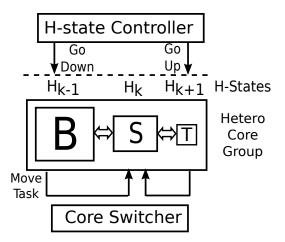

We then present **HeteroMates**, a solution that uses heterogeneous processors to extend the dynamic power/performance range of client devices. By using a mix of different processors, HeteroMates offers both high performance and reduced power consumption. The solution uses *core groups* as the abstraction that groups a small number of heterogeneous cores to form a single execution unit. Group heterogeneity is exposed as multiple *heterogeneity* (H) states, an interface similar to the P-state interface already used for frequency scaling. An H-state controller governs H-state transitions based on dynamic policies maximizing performance or minimizing power consumption, while a 'core switcher' transparently migrates tasks to the appropriate core, i.e., the one matching the chosen H-state. Thus, HeteroMates decouples heterogeneity from scheduling and provides a seamless way for adoption of such platforms in mobile devices.

Finally, we present **HeteroVisor**, a heterogeneity-aware hypervisor, that exploits resource heterogeneity to enhance the elasticity of cloud systems. Introducing the notion of 'elasticity' (E) states, HeteroVisor permits applications to manage their changes in resource requirements as state transitions that implicitly move their execution among heterogeneous platform components. Masking the details of platform heterogeneity from virtual machines, the E-state abstraction allows applications to adapt their resource usage in a *fine-grained* manner via VM-specific 'elasticity drivers' encoding VM-desired policies. The approach is explored for the heterogeneous processors evolving for modern server platforms, leading to mechanisms that can manage these heterogeneous resources dynamically and as required by the different VMs being run. HeteroVisor is implemented for the Xen hypervisor, with mechanisms to perform elastic core scaling. Evaluation on an emulated heterogeneous platform uses workload traces from real-world data, demonstrating the ability to provide high ondemand performance while also reducing resource usage for these workloads.

In addition, we also present the description of a client workload suite used in this work along with its implementation details in Appendix A. These workloads include a diverse set of real-world client applications, representing the usage model of modern client devices.

## 1.4 Thesis Organization

The remainder of this dissertation is organized as follows. Chapter 2 begins by providing an overview of processor heterogeneity and presents experimental evaluation of modern client and server workloads on a unique heterogeneous multicore platform. This evaluation is extended beyond CPU cores by analyzing the impact of uncore subsystem and evaluating heterogeneous memory organization in Chapter 3. Next, Chapter 4 describes the HeteroMates solution for mobile platforms to enable extended resource scaling modes. Chapter 5 presents the HeteroVisor system for enhancing the elasticity of cloud platforms. Finally, Chapter 6 summarizes the conclusions from the dissertation, along with several directions for future work.

## CHAPTER II

## HETEROGENEOUS CORES: BRAWNY VS. WIMPY

### 2.1 Introduction

Energy efficiency remains a critical concern for both mobile devices and server systems. Since the battery capacities of mobile devices are severely restricted due to constraints on size and weight, energy efficiency is critical to their usability. Similarly, due to cost implications of power and cooling, energy-efficient operation is a core issue for server systems as well. Desired energy efficiency, however, is challenged by ever-increasing demands of high-performance from these platforms. To continue scaling performance, the industry has made a shift towards multicore architectures for both mobile and enterprise platforms. While thus far these architectures have incorporated symmetric computational components, heterogeneous processors have been proposed as a possible alternative to improve power efficiency [23, 42, 55, 73].

This work focuses on heterogeneous processors consisting of a mix of cores that expose the same instruction-set-architecture (ISA), but differ in their power and performance characteristics. Examples of such platforms include Variable SMP from NVIDIA [78], Big.LITTLE from ARM [18, 29], and Xeon Phi architecture from Intel [45]. Such heterogeneous platforms make it possible for different applications within a diverse mix of workloads to be run on the most appropriate cores. For example, applications that do not produce a result that is time critical to the user can be run on low-power wimpy cores, while applications with their output visible to the user can be allocated to high-performance cores. Similar arguments have been made to utilize low-powered cores for the design of datacenters [6, 48], while others have discussed the need for high-performance brawny cores as well [10, 59]. This chapter investigates the opportunities and limitations in using such heterogeneous multicores on the performance and energy efficiency of modern workloads from both the mobile and enterprise domains. Our goal is to better allow system designers to assess the trade-offs and merits of moving from homogeneous systems, which are already well supported, to heterogeneous architectures that require changes across both hardware and software. We begin by providing the motivation for employing fast brawny cores and slow wimpy cores and describe advantages and limitations of using each of them. We then provide a description of the workloads used in our analysis which consists of a diverse mix of server benchmarks and a client benchmark suite targeted towards modern end-user devices like smartphones and tablets. We characterize the behavior of these applications and compare the performance and power trade-offs of using different types of processors. While previous studies either relied on simulators or emulated heterogeneous platforms, this chapter presents real performance and power data from a real heterogeneous platform.

Experimental evaluations are carried out using a unique, experimental heterogeneous multicore platform 'QuickIA', comprised of both high and low power CPUs operating in a coherence domain under shared memory. The processors differ in both their core architecture and last-level-cache (LLC) sizes. A key element of our analysis includes an evaluation of the power overhead of shared system components such as memory on the energy efficiency of heterogeneous cores which have been ignored in prior work. The QuickIA platform allows us to separate the effects of processor heterogeneity from the rest of the system which is shared by both the processors. Experimental results demonstrate that heterogeneous architectures can provide performance improvements while also lowering energy consumption for a diverse set of applications when compared to homogeneous processor configurations. They also indicate the need for novel resource management approaches for heterogeneous CPUs accounting for non-CPU components and user-perceived performance.

# 2.2 Why heterogeneity?

Users perform a wide variety of tasks on mobile devices, resulting in diverse platform demands. Similarly, various applications hosted in a datacenter also exhibit highly diverse behavior in their processor usage and performance requirements. The presence of virtualization technologies and server consolidation only exacerbate such diversity. Therefore, underlying platforms hosting these applications should be designed to accommodate such software diversity. However, modern processors are typically designed to satisfy only one of the two conflicting requirements: performance vs. energy efficiency. This chapter explores whether and to what extent the hardwarebased arguments for heterogeneity stated above lead to realistically achievable gains for modern client devices and server systems. The remainder of this section describes various scenarios under which different types of processors can be useful.

#### 2.2.1 Why wimpy cores?

Slow wimpy cores can provide higher energy efficiency than the larger high-performance cores, and thus, they can be used for applications not requiring high performance to save energy. For example, a small core can be used for background tasks like email update checks and normal user operation to ensure longer battery life, while the big core is reserved for performance-critical tasks. Similarly, wimpy cores can be used for I/O bound applications which consume low levels of CPU resources.

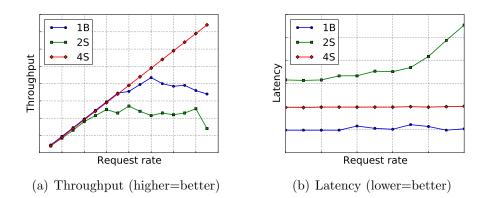

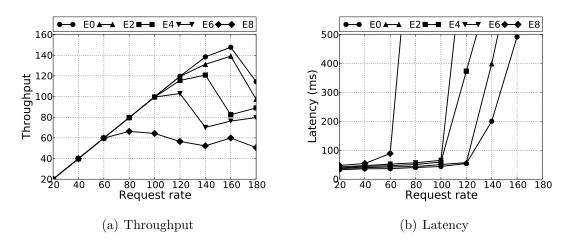

Wimpy cores can also be used to improve application throughput. Since a larger number of wimpy cores can be employed under a fixed power envelope in comparison to power-hungry big cores, they can provide higher throughput for parallel applications which can make use of such cores. For example, Figure 3(a) compares the response throughput of a web-server microbenchmark as a function of request rate for three different processor configurations consisting of one big (1B), two small (2S), and four small (4S) cores on an emulated heterogeneous platform. As seen in the figure, the 4S configuration provides the highest throughput among these configurations at high request rates.

Figure 3: Best of both latency and throughput using heterogeneous cores

#### 2.2.2 Why not wimpy cores?

Due to the limited performance of wimpy cores, they may not be suitable for latencysensitive applications. For example, user-facing tasks which are CPU-intensive such as browsing and gaming may require a high-performance processor. Various datacenter applications also have associated latency SLAs (service-level-agreements) and a wimpy core may not be suitable for these applications. For example, Figure 3(b) compares the response time of the web-server microbenchmark for the three CPU configurations (1B, 2S, and 4S) where the big core (1B) provides the lowest latency. Thus, brawny cores may win over wimpy cores when latency matters.

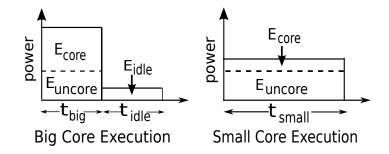

In addition to such latency improvements, brawny cores may also provide higher energy efficiency than their low-power counterparts for certain applications. Due to the power overhead of various system components such as memory, execution on fast cores may allow various platform components to quickly enter low power modes, resulting in lower energy consumption. This phenomenon is also known as 'race-toidle' [72] and is particularly prominent for modern systems with deeper idle states.

## 2.3 Workload Description

A diverse set of applications from mobile and enterprise domain are included in this study. This section provides an overview of these workloads.

#### 2.3.1 Client Workload Suite

| Category     | tegory Workload Description            |                          | Metric    |

|--------------|----------------------------------------|--------------------------|-----------|

|              | browse                                 | Web-page rendering       | Load time |

| Browser      | javascript Javascript operations       |                          | Load time |

|              | palbum                                 | Photo album application  | Load time |

| Gaming       | chess                                  | 2D chess game            | Time      |

| Gaining      | $\operatorname{strike}$                | 2D browser gaming        | FPS       |

|              | animate                                | Image sequence animation | Time      |

| Multimedia   | convert                                | Image resize             | Time      |

| Wutthileula  | mencoder                               | Video encoding           | Time      |

|              | mplayer                                | Video playback           | FPS       |

|              | calc                                   | Spreadsheet operations   | Time      |

| Productivity | uctivity impress Power-point slideshow |                          | Time      |

|              | writer Document editing                |                          | Time      |

|              | 7zip                                   | File compression         | Time      |

|              | diskscan                               | Disk I/O operations      | Time      |

| Utility      | gtkperf                                | GUI operations           | Load time |

| Contry       | pguard File encryption                 |                          | Time      |

|              | sqlite                                 | Database access          | Time      |

|              | wget                                   | File download            | Time      |

Table 1: Client workload suite

To assess the viability of using heterogeneity on client devices, it is useful to refer to prior server-centric research on heterogeneous processors [8, 54, 64, 92], but such server-centric investigations do not directly address the needs and processor usage models seen on typical client devices. This section presents representative and typical client workloads used in our analysis and summarized in Table 1, along with relevant performance metrics. The benchmarks consists of the following components: browser, gaming, multimedia, productivity, and utility which we briefly describe below. All of these workloads are implemented in Linux and completely automated using scripts. Browser workloads are run using the open-source Chromium browser. A more detailed description along with relevant implementation details is provided in Appendix A.

#### 2.3.2 Server Workloads

| Category Workload Description            |            | Description                                |

|------------------------------------------|------------|--------------------------------------------|

|                                          | lusearch   | Text search against Lucene search engine   |

| Transaction                              | tomcat     | Webpage retrieval using Tomcat server      |

| processing                               | tradebeans | Online stock trading system (Java Beans)   |

| (OLTP)                                   | tradesoap  | Online stock trading system (SOAP)         |

|                                          | hsqldb2    | Transactions against a banking application |

|                                          | histogram  | RGB histogram in a set of images           |

| Data                                     | linreg     | Compute the best fit line from points      |

| processing                               | revindex   | Build reverse index from HTML files        |

| (MapReduce)                              | strmatch   | Search word in a file with keys            |

|                                          | wordcount  | Determine frequency of words in a file     |

|                                          | kmeans     | Clustering algorithm for classification    |

| Analytics                                | matrix     | Dense integer matrix multiplication        |

|                                          | pca        | Principal components analysis on a matrix  |

| Other benchmarks                         |            |                                            |

| ST-CPU SPECCPU Single-threaded CPU bench |            | Single-threaded CPU benchmarks             |

| MT-CPU                                   | PARSEC     | Multi-threaded application kernels         |

Table 2: Server workload summary

A large body of prior work on heterogeneity has relied on high-performance benchmarks such as SPEC CPU2006 and NAS parallel benchmarks for evaluation [55, 54, 64, 92]. However, applications running on modern servers are more sophisticated and diverse in their characteristics such as search engines, MapReduce, key-value stores, etc. In order to evaluate the impact of heterogeneity on the server workloads, therefore, a diverse set of server-centric workloads are included in the analysis which are summarized in Table 2. These workloads include several transactional applications such as the Lucene search engine, the Tomcat application server, an online trading system, several MapReduce data processing benchmarks (reverse index, word count, etc.), and data analytics kernels. In addition, CPU-intensive SPEC CPU2006 benchmarks [41] and multi-threaded PARSEC benchmarks [11] are also evaluated. MapReduce and analytics benchmarks use the shared-memory Phoenix implementation of MapReduce [89].

## 2.4 Evaluation

#### 2.4.1 Experimental Platform

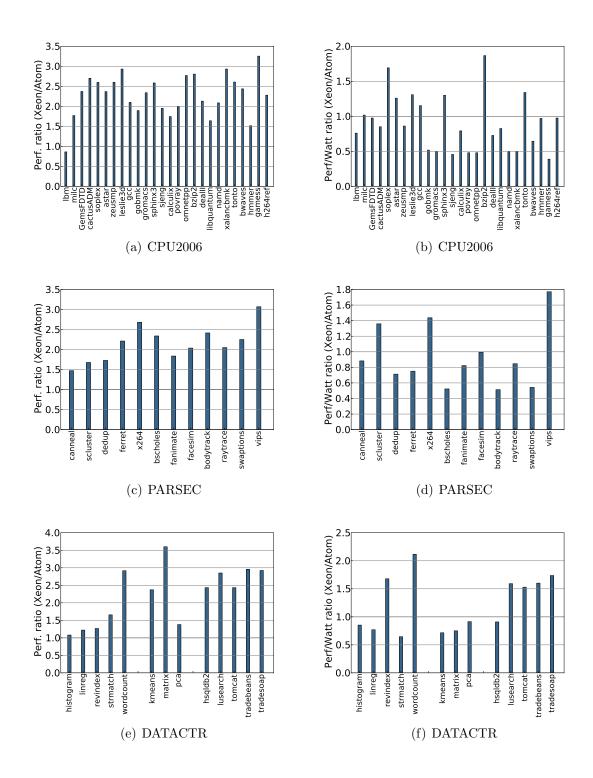

The QuickIA heterogeneous multicore platform is used for experimental evaluation [16]. The QuickIA platform is based on a dual socket Intel Xeon 5400 series platform that has a real Xeon 5450 CPU in one socket and a real Atom N330 CPU in the other socket (see Figure 4). Both the sockets are fully cache coherent with full access to the shared platform services like memory and I/O. The processors differ in their core architecture (in-order vs. out-of-order) as well as LLC sizes, making it a unique experimental platform for evaluating the impact of CPU heterogeneity. Since various platform components such as motherboard, memory, disks, etc. are common, it allows us to isolate the effect of differences in CPU power/performance. the system is configured to run with 4GB of DRAM for client workloads and 16GB for server workloads. Figure 9(a) shows a performance comparison of the two processors for SPEC CPU2006 workloads showing an average performance difference of 2.27x.

|            | Shared Memory     |                        |             |   |  |

|------------|-------------------|------------------------|-------------|---|--|

| Socket 0   | ÛÛ                | $\widehat{\mathbb{I}}$ | Socket 1    |   |  |

| (          | < í               |                        |             | ì |  |

| Small Core |                   | Large Cache            | Big<br>core |   |  |

| Small Core | Cache<br>Coherent |                        | Big<br>core |   |  |

|            | ι,                |                        |             | 1 |  |

| Processor     | Atom N330          | Xeon 5450          |

|---------------|--------------------|--------------------|

| Cores         | 2                  | 2                  |

| H/W Threads   | OFF                | N/A                |

| CPU Frequency | $1.60\mathrm{GHz}$ | $1.60\mathrm{GHz}$ |

| L1 Inst Cache | 32KB               | 32KB               |

| L1 Data Cache | 24KB               | 32KB               |

| L2 size       | 512 KB/core        | 2MB/2 cores        |

| C states      | N/A                | ON                 |

Figure 4: QuickIA heterogeneous multicore platform

#### 2.4.2 Performance Monitoring

We modified the Linux kernel to add performance monitoring support for heterogeneous cores. Since the QuickIA system contains heterogeneous cores with different CPUIDs, standard performance monitoring tools available do not work on this platform. We added a kernel module which periodically reads appropriate performance monitor counters from the system, taking into account the differences in core architectures.

#### 2.4.3 Power Measurement

The Wattsup power meter is used to obtain system power/energy consumption data. It provides instantaneous voltage and current data with a measurement accuracy of 1.5% of reading values. Data is logged to disk using the USB interface available on the power meter with the help of a Linux driver. Since this work focuses on analyzing the impact of processor heterogeneity, we use a difference of total system power and system idle power to obtain active power used by the workload and report in the results.

#### 2.4.4 Methodology

Experimental evaluation and analysis are carried out as the multiple steps summarized below.

- Each workload is first evaluated on a system configured to use only Xeon cores. Multi-threaded applications are configured for a one to one mapping of threads to cores used.

- Next, the same workloads are run using only Atom processor.

- The metrics collected include: application performance, power, and various performance counters including instructions retired, unhalted core cycles, LLC misses, MPERF, and timestamp counters.

• With the help of data collected in previous steps, we calculate the performance improvement provided by Xeon over Atom cores, and the energy savings or performance/watt that can be obtained by using these processors.

The analysis currently uses Xeon or Atom cores for the entire execution of the application. In practice, an application can dynamically switch between different types of cores and achieve higher gains, but the implementation and evaluation of a dynamic scheduling algorithm remains part of our future work.

#### 2.4.5 Limitations

There are few limitations to the study performed in this work. First, the processors available on the QuickIA platform may not represent the latest high-performance and low-power CPUs available in the market. However, these two processors belong to the same generation. The performance/power profiles of both Intel Xeon and Atom processors have improved so we expect the relative trends to be comparable to the results obtained from the QuickIA platform. Second, the network connection used in the experiments is through the ethernet port available on QuickIA machine. However, mobile devices commonly use wireless connections which can affect the results for browser workloads.

### 2.5 Experimental Results

This section presents experimental results and the analysis of heterogeneous multicores for all of the client and server workloads described in Section 2.3. Results for the client workloads are presented first in Section 2.5.1, followed by the server workload evaluation (Section 2.5.2).

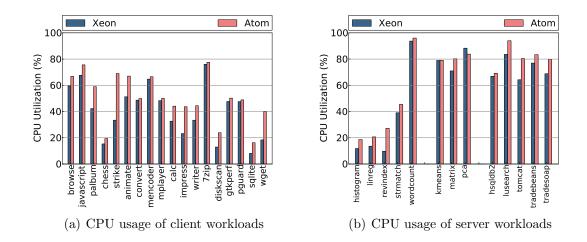

Figure 5: A comparison of CPU usage profile of client vs. server workloads

#### 2.5.1 Client Workload Evaluation

#### 2.5.1.1 Application Behavior

The results shown in Figure 5(a) show the average CPU utilization of all of the client applications in Table 1 for execution on Xeon and Atom CPUs. As seen in the figure, applications exhibit diverse behavior in their CPU usage. 7zip, mencoder, and javascript have high CPU utilization, while other applications like productivity apps (calc, impress, writer), chess, wget make light use of CPU resources. This behavior is in contrast to that of typical server applications used by earlier work on heterogeneity [54, 55, 64, 92] which exhaust the CPU. It can also be noticed that the average CPU utilization is higher on small cores due to their simpler core architecture, requiring more processing time for the same task.

For comparison, Figure 5(b) shows the CPU utilization profile of the transactional, MapReduce, and analytics workloads in Table 2 which we collectively call 'DATACTR' workloads. These workloads either almost saturate the CPU (transactional applications and analytics kernels) or have much lower CPU-usage as in the case of MapReduce workloads due to their I/O-bound nature. In comparison, client applications exhibit much more diverse behavior.

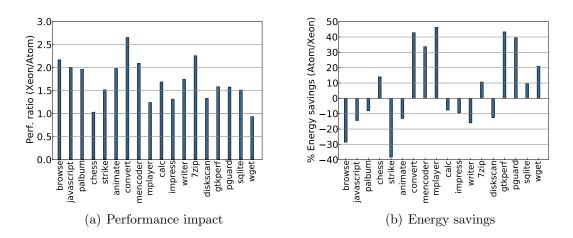

#### 2.5.1.2 Performance Analysis

Figure 6(a) evaluates the impact on client application performance of using heterogeneous processors. Specifically, it shows the performance ratio of using only Xeon CPU over using only small Atom for these applications. As evident from the figure, Xeon provides significant performance improvement for several applications like 7zip, convert, javascript, browse, etc. Application convert shows the highest gain of 2.67x. On the other hand, wget, diskscan, mplayer, impress, and chess show only small gains. The average performance gain for all the applications is observed to be 1.7x.

**Figure 6:** Performance and energy impact of using small vs. big cores for client workloads

#### 2.5.1.3 Power Analysis

Results comparing energy consumption on the big and small cores are shown in Figure 6(b). The results provide energy savings (%) of using Atom cores over Xeon cores. These results are particularly interesting. Several workloads like pguard, gtkperf, mplayer, convert, etc. show significant savings by using Atom CPU (maximum 46% for mplayer). However, many other applications show negative savings during execution on Atom cores. For example, strike game consumes 38% more energy when running on small cores while also providing lower performance, in comparison to big core execution. This implies that Xeon provides both higher performance and energy efficiency for these applications.

Figure 7: A comparison of the behavior of client workloads on big vs. small cores

This behavior is contrary to popular understanding that small cores are more energy-efficient and can be attributed to the increased execution time and increased power of non-CPU components. It can be verified using Figure 7(a) and 7(b) which respectively compare average IPC (instructions-per-cycle) and MPI (misses-per-instruction) for these workloads on two types of CPUs. Most of the applications observe a significant decrease in their IPC when running on the small core as compared to the big core. This reduction in IPC results in the small core being active for longer durations, thereby either causing an increase in core utilization or longer execution time. Further, Figure 7(b) shows a significant increase in cache miss rate (MPI) for several applications when run on the small cores, indicating a large increase in the memory access rate and thus memory power consumption. For example, application browse and strike have the worst energy impact in Figure 6(b), while they also have a large increment in their MPI rate in Figure 7(b). The overall behavior is a combination of several factors including big/small core power ratio, performance difference, and the application behavior.

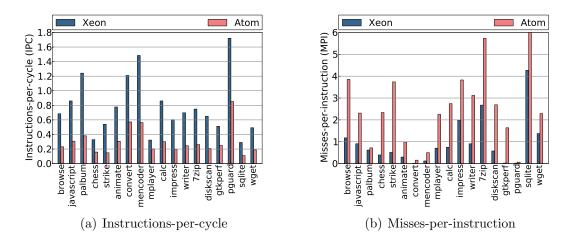

Figure 8: User-perceived performance for client applications

In comparison to server systems where typically total work done is used as a performance metric, user-perceived performance counts on consumer devices. If an application performs better than what a user wants or can notice, it may not be useful work. For example, Figure 8(a) shows the average load-time for various web-pages within the *browse* workload. It can be seen that the page-load latency is significantly decreased for these applications when using a big core. For example, the average page-load time for facebook page is decreased from 841ms to 346ms on the big core. However, a user may or may not perceive such a change in load-time. If 500ms is considered as the load-time threshold for the user, various sites like apple, google, yahoo can be rendered using a small core as well without exceeding the tolerance limit. On the other hand, other websites like cnn, digg, mtv, etc. strictly require a big core to be used to meet the desired performance requirement.

Similarly, Figure 8(b) shows the frames-per-second (FPS) metric for the mplayer workload when playing videos with different resolution quality (480p, 720p, 1080p). In the case of low resolution 480p video, the small core is able to perform comparable to the big core by sustaining the 23 FPS rate. Therefore, it can be run on a small core, with only minor performance loss and a decrease in energy consumption. However, the playback quality degrades for higher resolution videos, demanding a big core for maintaining the desired quality. Thus, both these examples highlight the challenge of user-perceived performance associated with client applications which need to be taken into account for scheduling operations on heterogeneous processors.

#### 2.5.2 Server Workload Analysis

Under the server workload analysis, we first present results for SPEC CPU2006 and PARSEC applications followed by the DATACTR workloads.

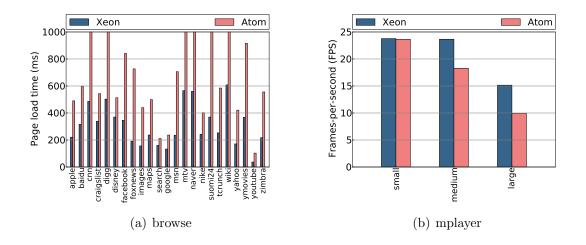

Figure 9(a) shows the performance ratio for SPEC CPU2006 workloads on two QuickIA processors. The benchmarks are sorted in the order of increasing IPC (left to right), with average performance gain of 2.27x. The corresponding performance/watt ratio of Xeon over Atom is shown in Figure 9(b). A ratio greater than one signifies that the Xeon consumes less energy for the same amount of work, while a ratio lower than one implies Atom consuming less energy. As evident in the figure, different applications show affinity towards different processor for energy-efficient execution. Several applications like bzip2, soplex, sphinx3 etc. take less energy on the big core, while gamess, namd, sjeng, etc. run more efficiently on the big core. These results show the need for heterogeneity for these CPU-bound workloads to maximize system performance/watt.

Further, many applications with low IPC (on left) such as soplex, astar, gcc run more efficiently on the Xeon core, as opposed to typical understanding that memoryintensive applications with low IPC can be offloaded to smaller cores. However, these memory-intensive applications perform better on the Xeon core with larger cache size. Our ongoing work is further investigating the performance and power predictors which can be used to make optimal scheduling decisions for such heterogeneous multicores.

**Figure 9:** Performance and Performance/Watt comparison of server workloads on Xeon vs. Atom CPUs.

Similar results are obtained for several multi-threaded applications from the PAR-SEC benchmark suite, as shown in Figure 9(c) and 9(d). The performance improvement of using the big cores for these applications is 2.15x. The energy profile of these workloads shows that most of the applications (except fluidanimate, vips, and x264) consume less energy when run on the Atom cores.

Finally, results comparing the performance and performance-per-watt of the DAT-ACTR workloads on Xeon vs. Atom processors are presented in Figure 9(e) and 9(f) respectively. Applications under the transactional and analytics category see large performance gains from the faster CPUs. The kmeans application kernel observes a sharp decline in its IPC when run on small cores causing a performance degradation. Similarly, performance gains for applications like wordcount, tomcat, tradesoap, tradebeans and matrix kernel can be attributed to high increase in the LLC miss rate on small cores. In comparison, data processing MapReduce applications (except wordcount) observe only minor performance gains from large Xeon cores, due to their low CPU requirement.

Comparing the performance/watt ratio of these workloads in Figure 9(f), almost all the transactional applications show lower energy consumption on the Xeon cores, thus, favoring them for both performance and energy-efficiency. On the contrary, analytics applications and many data processing MapReduce applications (except revindex and wordcount) take less energy when run on small cores. These results again confirm the original hypothesis that small cores are not always most efficient and by provisioning the appropriate server configuration for each application, a datacenter can be optimized for energy-efficient operation.

#### 2.5.3 Opportunity Analysis

A summary of the experimental results for all the workloads is presented in Table 3, showing the relative performance and power on Xeon and Atom configurations. The

results are categorized by workload suites namely SPECCPU, PARSEC, DATACTR, and CLIENT. We observe that the Xeon processor provides average performance gains of 2.28x and 2.15x over Atom for SPECCPU and PARSEC workloads. The corresponding increase in energy consumption is 1.35x and 1.25x. On the other hand, DATACTR workloads exhibit a performance gain of 2.24x as well as a reduction in energy consumption (4%) from Xeon over Atom cores. Finally, workloads from the mobile domain show an average 68% performance gain on the faster CPU, with a 17% increase in energy consumption. The average performance improvement from big cores for all the workload categories is 2.09x with 18% higher energy consumption.

| 1: | if | Energy | gain | > | 10% | (wrt. | Xeon) | $\operatorname{then}$ |

|----|----|--------|------|---|-----|-------|-------|-----------------------|

|----|----|--------|------|---|-----|-------|-------|-----------------------|

- $2: \quad \text{CPU} \leftarrow \text{Atom}$

- 3: else

- 4: CPU  $\leftarrow$  Xeon

- 5: **end if**

#### Algorithm 2: Hetero-B Policy

| 1: <b>if</b> Energy gain | > 10% AND | Perf. loss | < 50% | (wrt. | Xeon) | $\operatorname{then}$ |

|--------------------------|-----------|------------|-------|-------|-------|-----------------------|

|--------------------------|-----------|------------|-------|-------|-------|-----------------------|

- 2: CPU  $\leftarrow$  Atom

- 3: else

- 4: CPU  $\leftarrow$  Xeon

- 5: **end if**

An opportunity analysis is performed to estimate the benefits of using heterogeneous processors for these workloads. The analysis assumes knowledge of relative performance/power of each workload on two processors. Two CPU assignment policies are evaluated as shown in Algorithm 1 and 2. Hetero-A policy is an energy-centric policy which selects the CPU for each workload that is more energy efficient, irrespective of its performance impact. On the other hand, Hetero-B policy is also sensitive to performance and selects Atom only if it is energy efficient and does not degrade performance by more than 50% when compared to Xeon.

Results from the analysis are shown in Table 3 with several observations. First, Hetero-A policy provides large energy savings when compared to homogeneous configurations. When compared to Atom-only execution, it provides both higher performance (average 47%) as well as power savings (11%) by opportunistically using the big core when it is more efficient for all the workload categories. In comparison to Xeon only execution, it reduces both energy consumption and performance of the system. On the other hand, Hetero-B policy provides high performance at the cost of increased energy consumption. Overall, it provides 2x performance with only a 8% increased energy with respect to Atom, and 8.5% energy savings with a performance degradation of 4.3% with respect to Xeon-only results.

**Table 3:** Performance and power comparison for Xeon, Atom, and Heterogeneous configurations

| Workload | Performance |       |          |          | Energy |       |          |          |

|----------|-------------|-------|----------|----------|--------|-------|----------|----------|

| suite    | Atom        | Xeon  | Hetero-A | Hetero-B | Atom   | Xeon  | Hetero-A | Hetero-B |

| SPECCPU  | 1.00x       | 2.28x | 1.42x    | 2.15x    | 1.00x  | 1.35x | 0.93x    | 1.20x    |

| PARSEC   | 1.00x       | 2.15x | 1.37x    | 2.09x    | 1.00x  | 1.25x | 0.92x    | 1.21x    |

| DATACTR  | 1.00x       | 2.24x | 1.72x    | 2.17x    | 1.00x  | 0.96x | 0.81x    | 0.90x    |

| CLIENT   | 1.00x       | 1.68x | 1.35x    | 1.60x    | 1.00x  | 1.16x | 0.93x    | 1.02x    |

| Average  | 1.00x       | 2.09x | 1.47x    | 2.00x    | 1.00x  | 1.18x | 0.89x    | 1.08x    |

These results show that heterogeneous multicores can be employed to improve energy-efficiency of mobile devices and server systems.

## 2.6 Related Work

Heterogeneous processors have been proposed to provide higher energy-efficiency than symmetric multicore processors. Using a mix of different types of cores, different phases within an application can be mapped to the core which can run them most efficiently [23, 42, 55, 56, 73]. Experimental studies have been performed to analyze the impact of such performance asymmetry on several server workloads [8, 14]. Similar studies also exist for the mobile domain, characterizing the behavior of several client applications on heterogeneous multicore platform [32, 35]. However, earlier work relied on either simulators or emulated heterogeneous platforms for their evaluation using mechanisms like throttling (T) states, dynamic voltage and frequency scaling (DVFS), or proprietary techniques like core de-featuring. Such emulations do not realistically represent the behavior of a real heterogeneous system [54]. Also, the power data reported was obtained from models instead of real measurements. In comparison, QuickIA system used in our work contains real heterogeneous processors, allowing us to obtain real power data.

Several scheduling algorithms for efficient execution of applications on asymmetric multicore processors have also been proposed [33, 54, 58, 63, 64, 92, 99]. In addition, several techniques have been described to accelerate critical sections [42, 97] and virtual machine monitors [52, 57] using heterogeneous cores. Similarly, prior work has also investigated asymmetric cache-aware scheduling algorithms [50]. A study of several server workloads was performed by using processors with different cache sizes [7]. In comparison, our work involves processors with different core architecture in addition to cache asymmetry. Further, previous work has relied on throughputoriented server workloads for evaluating the impact of heterogeneity, while this study targets server domain as well as client devices where energy is a premium resource, application behavior and performance metrics are diverse. We also motivate the need for novel energy-aware scheduling approaches for heterogeneous multicores.

Various benchmark suites for embedded devices are available including MiBench [38] and EEMBC [85]. However, MiBench was developed during a different era of embedding computing. Modern CPUs found in consumer devices like smartphones and tablets and the applications run on these platforms have become quite sophisticated. EEMBC suite is proprietary and is not freely available to academics. Recent work has characterized the behavior of several Android applications on ARM-based mobile devices [39, 60]. However, their work deals with only homogeneous multicore platforms.

Concerning the datacenter environment, arguments have been made in favor of low-powered cores for the design of datacenters (e.g., FAWN [6]), while others have questioned the wisdom of using such cores for server systems [10]. Specific applications like database and web-search have been analyzed and compared on Atom and Xeon-based platforms [48, 59]. In this work, we look at a wider range of server applications from the point of view of server consolidation. Also, we use an evaluation platform which differs only in CPU configuration, with other components being shared, thus, allowing us to quantify the effect of processor heterogeneity and isolate it from differences in other components. Further, Polfliet et al. performed a cost analysis for provisioning datacenters with heterogeneous servers [84]. However, their work relied on models and simulators. Finally, several techniques have been proposed to optimize execution of datacenter applications on inherent heterogeneity due to servers from multiple generations [2, 74, 107]. Our results support their conclusions stressing the importance of employing heterogeneity for datacenter applications.

## 2.7 Summary

This chapter investigates the use of heterogeneous, i.e., low-power wimpy and high performance brawny, processors in modern mobile devices and server platforms. A unique experimental heterogeneous platform consisting of real Xeon and Atom processors with shared system resources is used to study and analyze a diverse mix of real-world applications from mobile and enterprise domain. Client applications represent the typical usage of end-user devices such as smartphones, tablets, while server applications include transactional applications, data processing MapReduce benchmarks, and data analytics kernel. The behavior of these applications is characterized on heterogeneous CPUs and a power-performance analysis is carried out to quantify the benefits of using heterogeneity for these applications. Results show that heterogeneous CPUs can be used to provide a superior solution for these platforms by enabling energy-efficient execution of various applications. The importance of power consumed by non-CPU components, the challenges of user-perceived performance for mobile devices, and its implication on the energy-efficiency of heterogeneous processors are also highlighted.

# CHAPTER III

## **BEYOND CORE: UNCORE & MEMORY SUBSYSTEM**

This chapter extends the analysis performed in Chapter 2 on heterogeneous cores by including the uncore and memory subsystem. A large fraction of CPU resources is dedicated to uncore on modern multicore platforms which is shared by all the cores. In this work, we first describe the relevance of uncore in the context of heterogeneous processors and study the effect of uncore using an experimental heterogeneous platform. Going beyond the processor, we also analyze heterogeneity in the memory subsystem consisting of fast on-chip and slow off-chip memory and discuss mechanisms required to support them. Specific contributions include hypervisor-level mechanisms to detect guest memory access patterns using access bit information and transparency support for managing heterogeneous memory for virtual machines, implemented by the hypervisor. We also present an evaluation of the sensitivity of several server workloads to the performance of heterogeneous memory subsystems from an emulated heterogeneous platform.

In the remaining chapter, Sections 3.1 and 3.2 provide details on discussions related to uncore, followed by mechanisms for heterogeneous memory management in Sections 3.3 - 3.5. Finally, related work and conclusions are described in Section 3.6 and 3.7 respectively.

## 3.1 Uncore subsystem

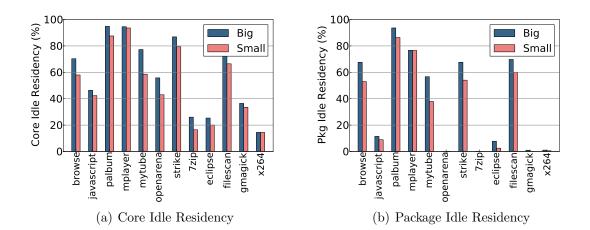

Energy efficiency remains a critical concern for both mobile devices and server systems. To improve energy efficiency while providing high performance, chip vendors have adopted heterogeneous multicore processors. Previous work on heterogeneous processors has primarily focused on core power [42, 55], but modern multicore processors also contain an *uncore* subsystem (see Figure 10), with components like the last level cache, integrated memory controllers, etc. With growing cache sizes, increasing complexity of the interconnection network, various core power optimizations, and the integration of SoC (system-on-a-chip) components on the CPU die, the uncore is becoming a significant power component in total SoC power [68]. For energy efficient operation, therefore, it becomes increasingly important to account for uncore while executing on heterogeneous cores.

This work investigates the importance of uncore power on the energy efficiency of heterogeneous multicore platforms. Unlike previous work on heterogeneous processors focused on server workloads [23, 54, 55], it targets client devices where energy is a premium resource and workload profiles are diverse. Since server workloads are not representative of the usage model of client devices, it characterizes the behavior of a diverse set of real-world client applications which are typical of end-user mobile devices and describes different ways in which they can exploit heterogeneity. Using these workloads, it further analyzes the impact of heterogeneity on workload performance and energy-efficiency, including both core and uncore components.

Experimental evaluations use a unique, experimental, heterogeneous multicore platform, comprised of both high and low power cores operating in a shared coherence domain. Results demonstrate that heterogeneous core architectures can provide significant performance improvements while also lowering energy consumption for a diverse set of applications when compared to homogeneous processor configurations. They also demonstrate that potential savings are strongly affected by the 'uncore' contribution, which motivates the need for uncore-awareness in managing heterogeneous multicore platforms and a scalable uncore design to completely realize the intended gains.

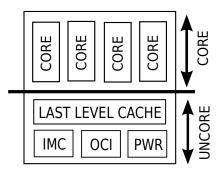

#### 3.1.1 What is uncore?

The uncore is a collection of components of a processor not in the core but essential for core performance. The CPU core contains components involved in executing instructions, including execution units, L1 and L2 cache, branch prediction logic, etc. Uncore functions include the last level cache (LLC), integrated memory controllers (IMC), on-chip interconnect (OCI), power control logic (PWR), etc. as shown in Figure 10. With growing cache sizes and the integration of various SoC components on CPU die, the uncore is becoming an increasingly important contributor to total SoC power.

Figure 10: Core and uncore in multicore processors

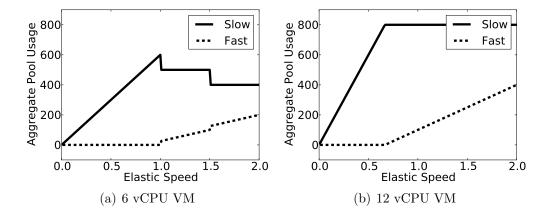

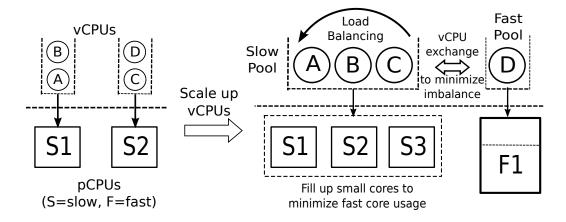

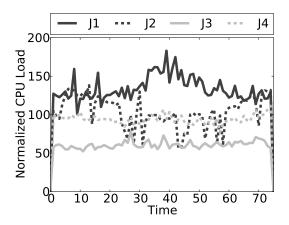

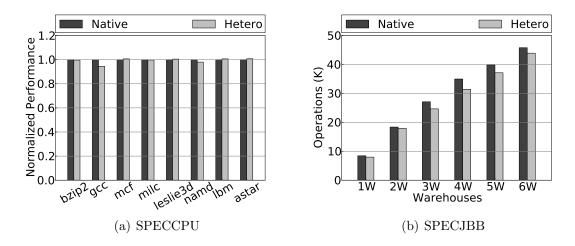

#### 3.1.2 Idle State Coordination