# Next Generation of $100-\mu\mathrm{m}$ -Pitch Wafer-Level Packaging and Assembly for Systems-on-Package

Andrew A. O. Tay, Mahadevan K. Iyer, *Senior Member, IEEE*, Rao R. Tummala, *Fellow, IEEE*, V. Kripesh, *Member, IEEE*, E. H. Wong, Madhavan Swaminathan, *Senior Member, IEEE*, C. P. Wong, *Fellow, IEEE*, Mihai D. Rotaru, *Member, IEEE*, Ravi Doraiswami, Simon S. Ang, and E. T. Kang

Abstract-According to the latest ITRS roadmap, the pitch of area array packages is expected to decrease to 100  $\mu m$  by 2009. Simultaneously, the electrical performance of these interconnections needs to be improved to support data rates in excess of 10 Gbps, while guaranteeing thermomechanical reliability and lowering the cost. These requirements are challenging, thus, needing innovative interconnection designs and technologies. This paper describes the development of three interconnection schemes for wafer-level packages (WLPs) at 100- $\mu$ m pitch, involving rigid, compliant, and semicompliant interconnection technologies, extending the state of the art in each. Extensive electrical and mechanical modeling was carried out to optimize the geometry of the interconnections with respect to electrical performance and thermomechanical reliability. It was found that the requirements of electrical performance often conflict with those of thermomechanical reliability and the final "optimum" design is a tradeoff between the two. For the three interconnection schemes proposed, it was found that the electrical requirements can be met fairly well but acceptable mechanical reliability may require organic boards with coefficient of thermal expansion of 10 ppm/K or lower.

## I. INTRODUCTION

NFORMATION technology (IT) is more than a trillion dollar industry. It includes hardware, software, services, and applications. Contrary to perception, hardware accounts for more than two-thirds of the IT industry, and the single most important building block of this hardware, of course, is semiconductor devices such as CMOS, GaAs, SiGe, and silicon-on-insulator (SOI) for a variety of computing, communication, consumer, automotive, and other applications. The total worldwide annual market for these devices is approximately \$150 B. These devices, the technology for which is at the threshold of nanoscale (100 nm), are typically fabricated into wafers as big as 300 mm in diameter and are subsequently diced into individual integrated circuits (ICs). They are then packaged, tested, and burnt into individual IC devices, ready to be surface mount bonded onto system level boards. The total number of ICs produced in 2003 was about 375 billion units, each packaged at some cost, typically US\$0.01 per I/O. The

Manuscript received February 12, 2004; revised April 20, 2004.

A. A. O. Tay, S. S. Ang, and E. T. Kang are with the Nano/Microsystems Laboratory, National University of Singapore, Singapore (e-mail: mpetayao@nus.edu.sg).

M. K. Iyer, V. Kripesh, E. H. Wong, and M. D. Rotaru are with the Institute of Microelectronics, Singapore.

R. R. Tummala, M. Swaminathan, C. P. Wong, and R. Doraiswami are with the Packaging Research Center, Georgia Institute of Technology, Atlanta, GA 30332 USA.

Digital Object Identifier 10.1109/TADVP.2004.830351

#### Today: Million Operations for 1000 Chips each at 1000 I/Os

\*IC photo courtesy of Intel

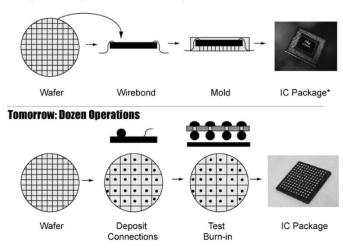

Fig. 1. WLP versus conventional packaging.

# 100 Micron Pitch:

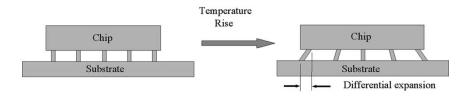

Fig. 2. Proposed 100- $\mu m$ -pitch interconnections.

total packaging market, which includes IC packaging, as well as systems packaging, is almost as big as the semiconductor market, together accounting for 25% of the IT industry.

The semiconductor industry is racing toward a historic transition—nanochips with less than 100-nm features. The first set of such chips reached production in 2003. Some of these chips have several hundred million transistors which require I/Os in excess of 10 000 and power in excess of 150 W, providing computing speed at terabits per second. These requirements, together with digital and wireless systems around 20 GHz (in 2010), require new approaches to IC and systems packaging in general and IC-to-package interconnections in particular.

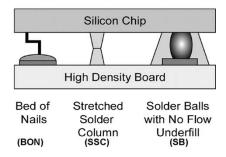

Fig. 3. Flip-chip package.

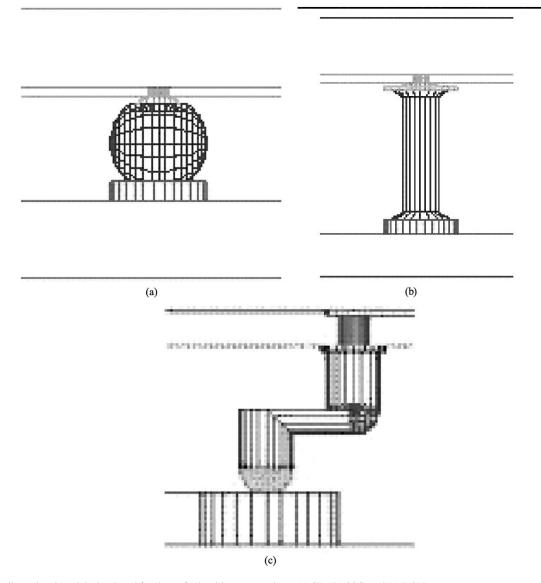

Fig. 4. Three-dimensional models developed for the wafer level interconnections: (a) SB, (b) SSC, and (c) BON.

# A. Finer Pitch Need and Technology Barriers

The latest ITRS roadmap clearly states the need for finer pitch area array package and assembly technologies calling for 100- $\mu m$  pitch by 2009. Simultaneously, the electrical performance of these interconnections need to be improved to support data rates in excess of 10 Gb/s, while guaranteeing thermomechanical reliability and lowering cost. These drivers present enormous barriers. The current approach of lead-free solders with underfill present major challenges in both dispensing the underfill and guaranteeing fatigue resistance as the height of solder bumps is lowered. The currently available compliant in-

terconnections, on the other hand, present electrical challenges due to their higher inductance and resistance.

This paper proposes to understand the limits, as well as propose new ways of extending the state of the art of in three IC-to-package interconnection technologies:

- 1) current solder bumps by extension to stretched-solder column (SSC);

- 2) current compliant interconnections by extension to lower cost and higher compliancy;

- 3) current lead-free with organic underfills by extension to improvements in underfill technology.

In 2002, an international collaboration program between the National University of Singapore, the Institute of Microelectronics, Singapore, and the Packaging Research Center, Georgia Institute of Technology, was initiated with a vision is to develop interconnection technologies spanning from 100- $\mu$ m pitch in the short term to nanoscale in the long term, as wafer level technologies, for the best electrical properties and lowest cost, while guaranteeing mechanical reliability. This paper reviews the progress by this team in the 100- $\mu$ m-pitch interconnection technologies.

## B. What is Wafer Level Packaging?

As illustrated in Fig. 1, a wafer-level package (WLP) is one in which the die and "package" are fabricated and tested on the wafer prior to singulation. This process eliminates many of the packaging processes required using conventional packaging resulting in drastic reduction in manufacturing cost. The benefits of WLP are as follows:

- smallest IC package size as it is a truly a chip-size package (CSP);

- 2) lowest cost per I/O because the interconnections are all done at the wafer level in one set of parallel steps;

- lowest cost of electrical testing, as this is done at the wafer level:

- 4) lowest burn-in cost, as burn-in is done at the wafer level;

- 5) enhances electrical performance because of the short interconnections;

- 6) ease of cooling through the fully exposed back of the die. In this paper, three basic interconnection technologies for WLPs at 100- $\mu$ m pitch are pursued, each extending the state of the art (Fig. 2):

- lead-free solder ball (SB) with underfill, a rigid interconnection;

- 2) bed of nails (BON), a compliant interconnection;

- 3) SSC, semicompliant interconnection.

The following are the main electrical and mechanical design parameters considered in this paper:

size of chip:  $20 \text{ mm} \times 20 \text{ mm}$ ; pitch of interconnections:  $100 \mu \text{m}$ ; number of I/Os:  $10\,000 \text{ per cm}^2$ ; temperature cycling range:  $-40 \text{ to } 150\,^{\circ}\text{C}$ ; thermal cycle fatigue life: 1000 cycles (target); signal frequency: 20 GHz; interconnection parasitics: dc resistance:  $25 \text{ m}\Omega$ ; inductance: 50 pH; capacitance: 10-15 fF.

#### C. Electromechanical Design of Interconnections

While the primary function of interconnections between chip and substrate (Fig. 3) is to provide electrical connections, mechanical integrity guarantees this electrical connection. At the assembly temperature, the stress in the interconnections is zero. However, during the operation of the chip, the interconnections experience temperature changes which result in differential expansion between chip and substrate due to the difference in the coefficient of thermal expansion (CTE) between the silicon chip

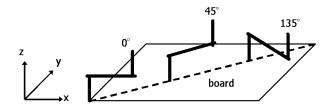

Fig. 5. Schematic illustration of three BON orientations to be investigated.

Fig. 6. (a) Plan view of package. (b) Slim sector model for the package with SB interconnections.

(CTE = 3 ppm/K) and the substrate (typically 18 ppm/K for FR4 board material). This is illustrated in Fig. 3. This causes stress to be induced in the interconnections which, if excessive, can result in structural failure which leads eventually to electrical failure of the chip. This is considered the single biggest barrier to fine-pitch interconnections, requiring novel designs.

Two broad classes of interconnections have been proposed in this program, namely, compliant and rigid interconnections. With a compliant interconnection, the mechanical stress in the interconnection for the same CTE mismatch is reduced. However, compliant interconnections are usually accompanied by higher values of electrical resistance and inductance. With a rigid interconnection, on the other hand, electrical resistance and inductance can be lowered but stresses will be increased. Thus, electrical and mechanical design requirements are often conflicting and the final design is a tradeoff between the two.

Thus, before the three types of 100- $\mu m$ -pitch interconnections were fabricated, extensive electrical and mechanical modeling and simulations were carried out to optimize the geometry of the interconnections. The final dimensions of the interconnections are a tradeoff between the satisfaction of the electrical performance requirements and the mechanical performance requirements. Details of these simulations are given in Sections II–VI. This will be followed by descriptions of fabrication methods and discussion of the results.

Fig. 7. Micromodels used in fatigue life estimation. (a) BON. (b) SSC. (c) SB.

# II. ELECTRICAL MODELING OF PROPOSED INTERCONNECTION SCHEMES

The interconnection schemes presented in Section I-C had to fulfill stringent electrical requirements. These requirements were based on the fact that the package using such interconnects had to support high frequency performance applications (e.g., microprocessors, high pin count logic devices, etc.). The ITRS road map [1] stated that in 2005 the high end microprocessor would have a 5-GHz clock frequency, consume 170 W of power and the operating voltage would be 0.9 V. It had been shown [2] that to support the requirements given by the ITRS road map the interconnection of the package had to fulfill some basic electrical properties such as dc resistance  $\leq\!25\,\mathrm{m}\Omega$ , inductance  $\leq\!50\,\mathrm{pH}$ , and capacitance  $\leq\!10$ –15 fF. These valued were

Fig. 8. Solder bump specifications for 100- $\mu m$  pitch.

Fig. 9.  $100-\mu\mathrm{m}$ -pitch lead-free solder bumps.

set as targets for the interconnection schemes described in this paper.

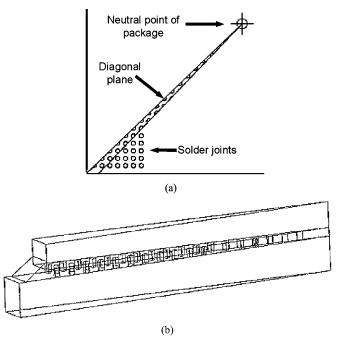

The basic electrical characteristics of interconnects under study had been modeled using three-dimensional (3-D) full-wave solver, high-frequency structure simulator (HFSS) [3]. The models developed are shown in Fig. 4. The assumptions made in the 3-D models are that all the dielectric materials in the models are considered to be lossless and the signal traces are considered perfect conductors. With these assumptions, the S-parameters of the models were extracted with the signal lines deembedded and thereafter an impedance parameter extraction was done. An equivalent circuit model for each interconnection was then obtained through a parameter fitting using the circuit simulation software -ADS.

Furthermore, to achieve the targeted values for the resistance, inductance and capacitance an optimization was done. Through geometrical variation (height, width, diameter, etc.) an optimum design for each of the interconnection schemes was obtained. The following table summarizes the geometrical parameters and electrical characteristics of the optimized interconnection schemes.

# III. MECHANICAL MODELING OF PROPOSED INTERCONNECTION SCHEMES

For a 20 mm  $\times$  20 mm package with 100- $\mu$ m pitch, there would be 40 000 interconnectiions. Even after taking advantage of symmetry, it would be computationally impractical to perform 3-D simulations using adequately-sized elements for all the solder joints. Hence, a macro–micro modeling approach was adopted [5], [6] which used the displacement results from a coarse mesh of the entire structure (i.e., the macromodel) as boundary conditions of a fine mesh of the region of interest (i.e., the micromodel). The response of the region of interest might then be studied using small 3-D solid elements without potentially prohibitive computational requirements.

Two approaches had been taken for the macromodels. In the macromodels of packages with either BON interconnections or SSC interconnections, the interconnections were modeled by equivalent beams [5] while the chip and substrate were modeled

Fig. 10. Underfill coated on the bumped wafer.

as shell elements. An equivalent beam is one which gives approximately the same compliance in the x, y and z directions as the actual interconnection. As the compliance of the BON was not isotropic, the orientation of the BON (illustrated in Fig. 5) is expected to have a significant effect. The equivalent beam model is ideal for this situation, since the beam can easily be rotated without affecting the mesh thus obviating creation of different meshes for different orientations of the BON. However, for packages with underfill, this approach would not be possible. Hence, a second approach was adopted for the macromodel of packages with SB interconnections, where a very slim sector of the package was modeled using 3-D solid elements (Fig. 6) [6]. This was possible since it would be reasonable to assume that as the number of interconnections became very large, the displacement of points on the chip and substrate would tend to be directed radially. This fact had also been confirmed by 3-D finite element analysis of WLPs. The macromodel of a package with SSC interconnections only modeled an eighth of the package, while that of the BON interconnections modeled a quarter. The prerequisite planes of symmetry were assumed. Typical BON, SSC, and SB micromodels, built using 3-D solid elements, are illustrated in Fig. 7.

Fig. 11. Process flow of BON interconnections.

The efforts to date had been focused on predicting the fatigue lives of the interconnections with 100- $\mu m$  pitch. The 20 mm  $\times$  20 mm package with 100  $\mu m$  pitch was assumed to be fully populated with interconnections. Fatigue life had been

estimated under thermal cycling between 150 and -40 °C with the stress-free temperature being 150 °C. To predict the fatigue life of the interconnections, a relatively simple correlation by Solomon [7] based on maximum strain range was

used. Solomon's correlation relate fatigue life  $N_f$  to applied maximum plastic shear strain range  $\Delta \gamma_p$

$$\Delta \gamma_p N_f^{0.51} = 1.14.$$

(1)

$\Delta \gamma_p$  was obtained from a finite element simulation of the temperature cycling process.

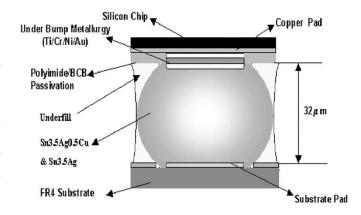

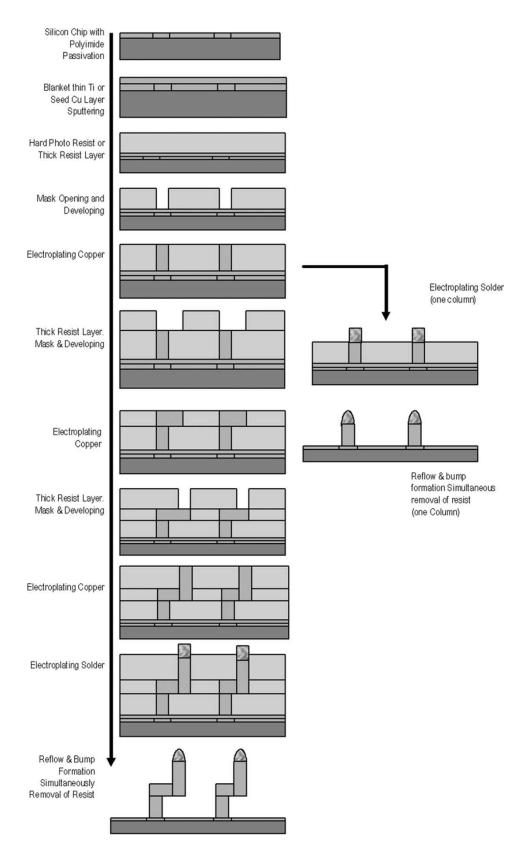

#### IV. FABRICATION OF PROPOSED INTERCONNECTION SCHEMES

Lead-Free SB With No-Flow Underfill: The detailed specifications of the solder bump is illustrated in Fig. 8. A  $100-\mu\mathrm{m}$ -pitch lead-free solder (Sn3.5Ag0.7Cu and Sn3.5Ag) bumping process was developed using Harima Chemical's Super Solder process as shown in Fig. 8. An extensive testbed was designed and fabricated to study different pad metallurgies and passivations for the Super Solder bumping process. The results suggest that Ti/Ni/Cr/Au was the optimal under bump metallurgy (UBM) and that polyimide was an ideal wafer passivation. (See Fig. 9.)

A unique wafer level underfill material was developed for this lead-free application. It contains an epoxy resin mix, a phenolic hardener, and a latent catalyst. The curing behavior of the underfill was characterized using a modulated differential scanning calorimeter (DSC). One important requirement for a successful wafer level underfill process was that the underfill should not gel before the solder melted and wetted the substrate. In order to identify the gel point of the underfill, the time to gel was obtained in the isothermal curing experiments performed using the stress rheometer. Compared to the degree of cure (DOC) change in the isothermal curing experiments from the DSC measurement, the DOC at gelation at different curing temperatures was calculated. It was found that the DOC at gelation for the underfill is around 0.85. Therefore, the underfill can be B-stage cured to DOC of 0.7 without pre-gel in the reflow process.

The unique process of the wafer level underfill required the  $T_g$  of the B-staged underfill to be around or above room temperature, so that the material would be sufficiently solid to facilitate dicing and prevent further reaction at room temperature storage. The  $T_g$  and the DOC of the underfill after B-stage at 130  $^{\circ}{\rm C}$  for different times were determined using the DSC.

The assembly of WLP with wafer level underfill was carried out on a 6" wafer. The underfill was spin-coated on the wafer and B-stage cured at 130 °C for 30 min. Then the wafer was diced into 5 mm  $\times$  5 mm individual chips. Fig. 10 shows the bumped wafer with B-staged underfill after dicing. The B-staged underfill did not show any cracking or delamination after dicing. The thickness of the underfill was about the height of the bumps (i.e., around 50  $\mu m$ ). The chip with wafer level underfill could be considered as a WLP, since no additional underfilling step was needed in the assembly process.

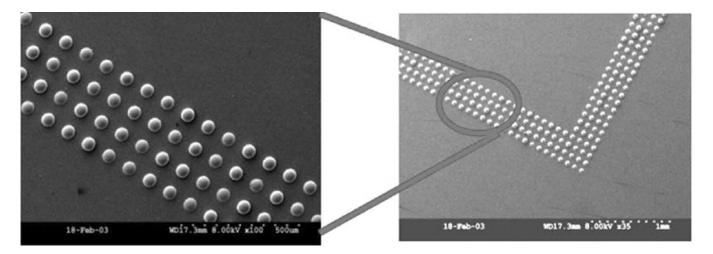

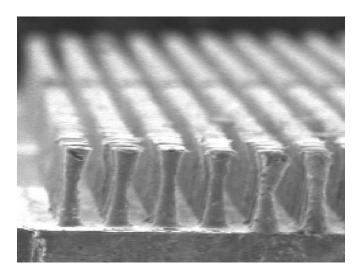

BON Interconnections: The BON interconnection is a novel compliant interconnect, extending beyond compliant interconnects previously reported. Two variations are being pursued: a single layer and a three layer structure. Their geometry and the process flow for fabricating the BON interconnections are illustrated in Fig. 11. Since a higher column height would result in higher compliance, lower stress, and hence, longer fatigue life, interconnections as high as 50  $\mu$ m were developed.

Fig. 12. Optical micrograph of the single layer BON on test die.

Fig. 13. Array of SSC interconnections.

TABLE I ELECTRICAL CHARACTERISTICS OF OPTIMIZED INTERCONNECTION SCHEME

| Interconnection scheme           | DC          | resistance | Inductance | Capacitance (fF) |

|----------------------------------|-------------|------------|------------|------------------|

|                                  | $(m\Omega)$ |            | (pH)       |                  |

| Solder Bump                      | 5           |            | 32         | 17               |

| (diameter = $50 \mu m$ )         |             |            |            |                  |

| Bed of Nails                     | 28          |            | 46         | 18               |

| (diameter = 15 $\mu$ m, total    |             |            |            |                  |

| height = $50 \mu m$ )            |             |            |            |                  |

| Stretched solder column          | 33          |            | 51         | 21               |

| (diameter = 30 $\mu$ m, height = |             |            |            |                  |

| 100 μm)                          |             |            |            |                  |

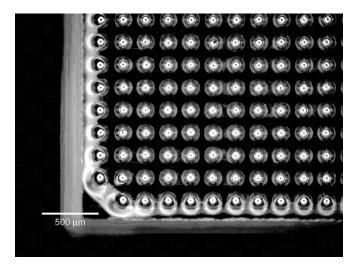

A single layer BON wafer level interconnection had been successfully fabricated with a nail height of 50  $\mu m$ . The thick photoresist process with high aspect ratio and good vertical profile was developed after analyzing various commercially available photoresist materials. Copper columns of 50  $\mu m$  were electroplated, followed by Sn/Pb solder plating to 15  $\mu m$  thickness. The plating process was optimized for copper nail plating in 12 min and solder plating in 4 min, achieving a coplanarity of

| Cases  | Bump          | Height | Ball Diameter (µm) | Substrate | CTE | With Underfill | Fatigue Life |

|--------|---------------|--------|--------------------|-----------|-----|----------------|--------------|

|        | ( <i>μ</i> m) |        |                    | (ppm/K)   |     |                |              |

| Case 1 | 50            |        | 70                 | 5         |     | Yes            | 2108         |

| Case 2 | 50            |        | 70                 | 10        |     | Yes            | 1749         |

| Case 3 | 32            |        | 45                 | 10        |     | Yes            | 1597         |

| Case 4 | 50            |        | 70                 | 5         |     | No             | 741          |

| Case 5 | 50            |        | 70                 | 10        |     | No             | 138          |

TABLE II FATIGUE LIFE OF SB JOINT

TABLE III

FATIGUE LIFE ESTIMATES OF BON USING SOLOMON'S CORRELATION

| chip thickness (µm)   | 250 | 640 | 640 | 640  |

|-----------------------|-----|-----|-----|------|

| substrate CTE (ppm/K) | 18  | 18  | 10  | 5    |

| orientation = 0°      | 10  | 21  | 60  | 1575 |

| orientation = 45°     | 16  | 41  | 71  | 1228 |

| orientation = 135°    | 200 | 11  | 348 | 4037 |

Fig. 14. Typical strain distribution in SSC of high aspect ratio.

$\pm 2\text{--}3~\mu\mathrm{m}$ . For this process optimization study, a  $10\times10~\mathrm{mm}$  test chip with 3332 I/Os, as shown in Fig. 12, was designed and fabricated.

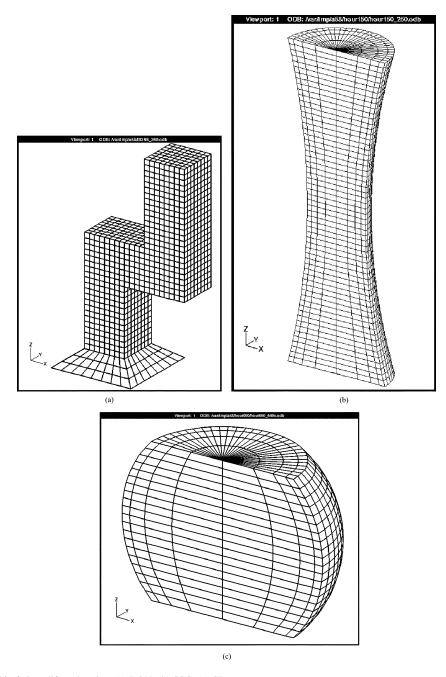

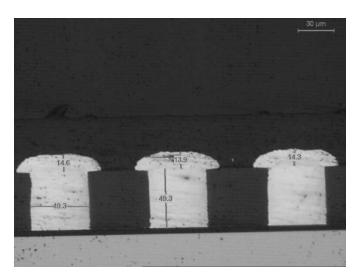

SSC Interconnections: In terms of mechanical compliance, the SSC interconnection is somewhere between the rigid SB and the compliant BON, and may be regarded as a semicompliant interconnection. In this interconnection design, an amount of high-lead solder is first deposited on all the die-pads on wafers. The solder is then melted, stretched, and cooled to form a unique hourglass shape (Fig. 13) on the entire wafer. Details of the

TABLE IV

FATIGUE LIFE ESTIMATES OF SSC INTERCONNECTIONS

| Chip thickness (µm)   | 250 | 640 | 640 | 640  |

|-----------------------|-----|-----|-----|------|

| substrate CTE (ppm/K) | 18  | 18  | 10  | 5    |

| Height=50 μm          | 81  | -   | 171 | 3237 |

| Height=100 μm         | 97  | 27  | 276 | 3124 |

| Height=150 μm         | 134 | 31  | 518 | 4405 |

| Height=200 μm         | 74  | 38  | 273 | 5772 |

Fig. 15. Test vehicle developed for electrical measurements.

process cannot be given as the process is being patented. To demonstrate the process, a full array of 2000 SSC eutectic solder interconnections on a 10  $\times$  10 mm test die at 200- $\mu m$  pitch and die-pad diameter of 100  $\mu m$ , was developed. This is shown in Fig. 13.

# V. RESULTS AND DISCUSSION

#### A. Thermomechanical Simulations

SB Interconnections: The chip thickness was kept constant at 640  $\mu m$  while the height and width of the SB were varied. Estimates of the fatigue life based on the finite element simulations using the slim sector model are given in Table II. It can be seen that increasing solder height and decreasing substrate CTE will increase the fatigue life. The use of underfill also increases fatigue life dramatically.

*BON Interconnections:* The cross section of the BON was fixed at 20  $\mu m$  square and the pad at 40  $\mu m$  square. The equivalent beam macro model was employed and it was assumed that

Fig. 16. Eye diagram simulation response for three different interconnection schemes. (a) SB  $L=32~\mathrm{pH}, C=17~\mathrm{fF}, R=5~\mathrm{m}\Omega$ . (b) BON  $L=46~\mathrm{pH}, C=17~\mathrm{fF}, R=5~\mathrm{m}\Omega$ . (c) Stretched solder  $L=51~\mathrm{pH}, C=21~\mathrm{fF}, R=33~\mathrm{m}\Omega$ .

failure of the interconnection occurred at the solder joining the interconnection to the substrate. The results of fatigue life estimates based on the finite element simulations of some BON with various heights and lengths were obtained and those for the "best" BON are given in Table III. As can be seen, a BON oriented at  $135^{\circ}$  usually has a higher fatigue life than one oriented at  $0 \text{ or } 45^{\circ}$ . This is probably due to the fact that the BON is most compliant when oriented at  $135^{\circ}$  and stiffest at  $0^{\circ}$ . The effect of chip thickness is not so clear. As expected, smaller values of substrate CTE give longer fatigue lives due to smaller CTE mismatch between chip and substrate. The fatigue lives with a FR4 substrate are very short suggesting that it might not be suitable for use with BON interconnections at 100- $\mu$ m pitch.

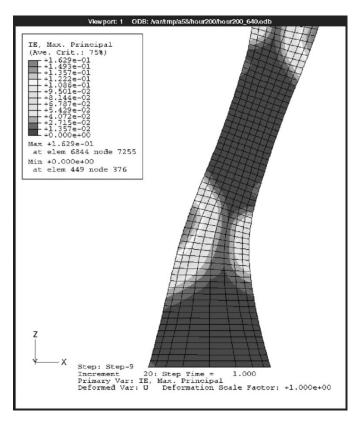

SSC Interconnections: The effect of the height of the SSC was studied. The volume was kept constant at  $1.63 \times 10^{-13} \, \mathrm{m}^3$  and the pad diameter at  $50 \, \mu \mathrm{m}$ . The distribution of the maximum principal strain in the SSC of height  $200 \, \mu \mathrm{m}$  is shown in Fig. 14. A significant finding is that, with the proposed unique shape of the SSC and for high aspect ratios, the location of maximum strain, and hence, the failure site, is shifted away from the usual location at the solder/pad interface toward the center of the interconnection. This can be seen in Fig. 14. This is also confirmed by fatigue experiments conducted on the SSC interconnection which will be described in Section VI.

The results of fatigue life estimates based on the simulations are given in the Table IV. For these simulations, no underfill is considered. As expected, fatigue life increases with height. Reducing either board CTE or chip thickness is beneficial to fatigue life, with board CTE having a greater effect.

#### B. Electrical Testing

As shown earlier the interconnection schemes had promising electrical parameters, but to demonstrate further their ability to support very high speed signals with minimum deterioration and to provide adequate power supply, a more complex test vehicle and test methodology were needed. The board, the chip, and the interface between them were studied and the electrical performance of the wafer level interconnect schemes were evaluated through the proposed test methodology.

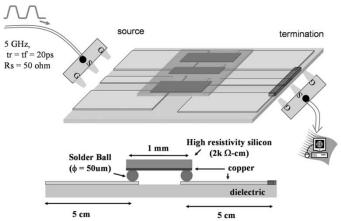

As the ultimate goal of this paper was to demonstrate the ability of the wafer level off-chip interconnections to support speeds and power comparable with that on-chip, this required careful design of the test structure. The test vehicle consisted of coplanar wave guided (CPW) lines on high resistive silicon substrate interfaced with a CPW line on a low dielectric constant and low dielectric loss board [2], [4]. The transition between the chip and the board was completed through the interconnect schemes proposed earlier (BON, SSC, SB), as shown in Fig. 15. Both of the CPW lines had been characterized using time domain reflectometry (TDR) and vector network analyzer (VNA) based measurements.

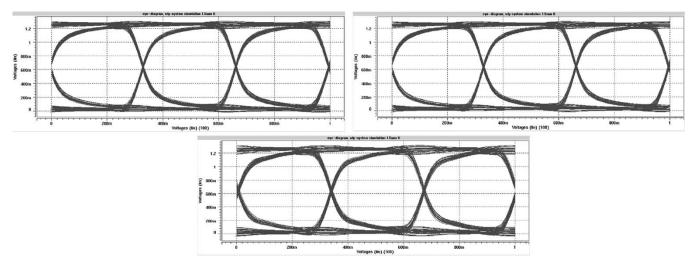

The synthesized models extracted from the measurement results were used together with the equivalent circuit extracted for the interconnect schemes and a data transmission at 5-GHz speed had been simulated. The methodologies used for model extraction was as described in [2]. The data transmission at 5 GHz was simulated using HSPICE model. A random pulse source with 200 ps period and a rise time of 20 ps was used. The output impedance of the pulse source was 50  $\Omega$  and the high-level and low level voltages of the pulse were 2 and 0 V, respectively. The transient signal at the far end termination was simulated from 50 to 100 ns, and converted to the eye diagrams (Fig. 16). All the combinations used for the simulations showed clean and wide open eyes demonstrating that high-speed signal transmission could be achieved off chip through this kind of interconnection. It must be mentioned here that the choice of the board, the design of CPW lines, as well as the design of the chip /interconnect/ board interfaces were very important for the overall system performance.

#### C. Mechanical Testing

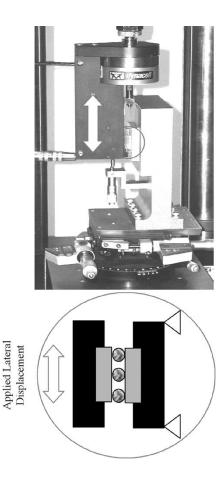

Static tensile tests, as well as mechanical cyclic loading fatigue tests, had been conducted on the SSC interconnection to determine its strength and fatigue life at room temperature [8]. The SSC specimens had base diameters of  $100~\mu\mathrm{m}$  and had been stretched to varying heights (aspect ratios) between two silicon pieces. The experimental setup for the fatigue tests is shown in Fig. 17. The specimen was attached to a specially designed fix-

Fig. 17. Experimental setup of mechanical cyclic loading fatigue test.

ture which allowed a sinusoidal cyclic lateral displacement to be applied as shown in Fig. 17.

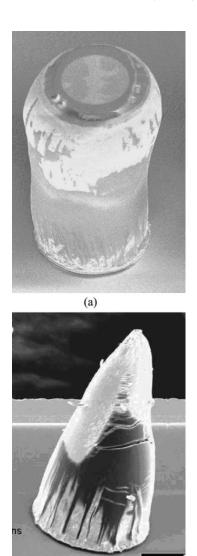

The experimental test results are given in Table V. In the fatigue tests, specimens were subjected to a cyclic lateral sinusoidal displacement of amplitude of 2.8  $\mu m$  and frequency 5 Hz. As can be seen from Table V, as the aspect ratio is increased the static strength decreased. This is expected since the solder volume was kept constant and a higher aspect ratio will result in a smaller minimum cross-sectional area of the interconnection and hence, a smaller axial strength. On the other hand, the fatigue life of the interconnections increased with the aspect ratio (height) of the solder column. This is expected as a higher aspect ratio leads to lower shear strains in the interconnection and, hence, a higher fatigue life. Another interesting finding is that at low aspect ratios the site of the fatigue failure is located at the solder/pad interface as is usually the case. However, as the aspect ratio is increased, the failure site moves toward the middle of the interconnection. Fig. 18(a) shows a specimen of aspect ratio 2.2 where the failure occurred at the UBM while Fig. 18(b) shows a specimen of aspect ratio 3.9 where the fatigue failure occurred near the mid-height of the interconnection. This experimental result is consistent with the numerical simulation described earlier (Fig. 14). A significant advantage of shifting the failure location away from the solder/substrate interface to within the bulk material is that fatigue failure should be more consistent and, hence, a more consistent fatigue model should be possible.

Fig. 18. Fatigue failure mode for SSC at aspect ratios of (a) 2.2—intermetallic failure at UBM and (b) 3.9—bulk solder failure at midlength.

# VI. EVALUATION OF PROPOSED INTERCONNECTION SCHEMES

The main objective of the electrical and mechanical simulations described above is to optimize each of the three proposed  $100\text{-}\mu\text{m}$ -pitch interconnections and compare them in terms of how well they satisfy the electrical and mechanical requirements. From the aforementioned electrical and mechanical simulations, the best tradeoffs for SB, BON, and SSC interconnections were determined.

A template has been constructed to perform a comparative evaluation of the three proposed interconnections. This is shown in Table VI. As can be seen, all the three interconnections are generally able to meet the electrical requirements. Without underfilling, the SSC has the highest fatigue life followed by the SB and the BON. Assuming Solomon's correlation is correct and without underfilling, all three interconnections are expected to fail to meet a fatigue life of 1000 cycles even with the most advanced organic substrates having a CTE of 10 ppm/K which are commercially available presently. However, with underfilling

| Aspect ratio          | 0.9         | 1.8   | 2.2   | 2.8   | 3.9            |

|-----------------------|-------------|-------|-------|-------|----------------|

| Static strength (N)   | 35          | 23    | 17    | 12    | 8              |

| Fatigue life (cycles) | 600         | 1,800 | 2,700 | 3,600 | 8,600          |

| Fatigue failure mode  | Solder near | UBM   | UBM   | UBM   | Solder at mid- |

|                       | and         | I     |       | 1     | haight         |

TABLE V

MEASURED FATIGUE LIFE AND STATIC STRENGTH OF SSC INTERCONNECTIONS

TABLE VI Comparison of Three 100  $\mu \mathrm{m}$  Pitch Interconnection Schemes

|                        |              |                   |                     | Mechanical Requirements |                                        |         |                   |      |      |

|------------------------|--------------|-------------------|---------------------|-------------------------|----------------------------------------|---------|-------------------|------|------|

|                        | Electrical   |                   |                     | Fatigu                  | e Life                                 | without | Fatigue Life with |      |      |

| EVALUATION             | Requirements |                   | Underfill (cycles)  |                         | Underfill (cycles) [1000] <sup>1</sup> |         |                   |      |      |

| TEMPLATE               |              |                   | [1000] <sup>1</sup> |                         |                                        |         |                   |      |      |

|                        | С            | L                 | R                   | CTE of substrate        |                                        |         | CTE of substrate  |      |      |

| 100 μm pitch           | (fF)         | (pH)              | $(m\Omega)$         | (ppm/K)                 |                                        |         | (ppm/K)           |      |      |

| interconnection scheme | [15]         | [50] <sup>1</sup> | [25] <sup>1</sup>   |                         |                                        |         |                   |      |      |

|                        |              |                   |                     | 18                      | 10                                     | 5       | 18                | 10   | 5    |

| Solder Ball (height 50 | 17           | 32                | 5                   | -                       | 417                                    | 2223    | 1320              | 1749 | 2108 |

| μm, diameter 70 μm)    |              |                   |                     |                         |                                        |         |                   |      |      |

| BON (height 100 μm,    |              |                   |                     |                         |                                        |         |                   |      |      |

| length 50 μm)          | 18           | 46                | 28                  | 11                      | 348                                    | 4037    | -                 | -    | -    |

| SSC (height 150 µm,    |              |                   |                     |                         |                                        |         |                   |      |      |

| diameter 50 μm)        | 21           | 51                | 33                  | 31                      | 518                                    | 4405    | 1484              | 3328 | 6886 |

<sup>&</sup>lt;sup>1</sup> Target values

both SSC and SB can meet mechanical requirements with a substrate CTE of 10 ppm/K. Again, it must be emphasized that the above conclusions are dependent on the accuracy of Solomon's correlation. Also, the solder material currently used in the simulations is eutectic solder. In actual interconnections to be developed eventually, the solder to be used for the SB will be lead-free solder while that used for the SSC will be high-lead solder. Furthermore, the upper limit of the temperature cycling range of 150 °C is more extreme than the usual limit of 125 °C. Reliability tests which are currently being conducted will determine if acceptable fatigue lives will be achieved. However, the simulations do provide a good indication of the relative merits of the three proposed interconnection schemes in terms of mechanical reliability.

### VII. CONCLUSION

A Nano Wafer Level Packaging program has been initiated to demonstrate future IC-package interconnections that meet the electrical, mechanical, cost, and pitch requirements. The initial focus, however, has been on 100- $\mu m$  pitch. Three interconnection designs and technologies at  $100~\mu m$  pitch such as rigid lead-free SB with no-flow underfill, compliant BON and semicompliant SSC interconnection have been developed. It was noted that the optimum geometry for electrical requirements often conflict with that for mechanical requirements. Hence, extensive electrical and mechanical simulations have been carried out to optimize their designs in order to satisfy both the elec-

trical and mechanical design parameters. The results indicate that the electrical requirements can be met but for meeting the mechanical requirements, it is necessary to use organic boards with a CTE of 10 ppm/K or lower. Of the three interconnection schemes proposed, the scheme which best meets the electrical requirements is the SB interconnection while the scheme which best meets the mechanical requirements is the SSC.

#### REFERENCES

- (2001) International Technology Roadmap for Semiconductors. Semiconductor Industry Association, San Jose, CA. [Online]. Available: http://public.itrs.net/

- [2] W. Kim et al., "Electrical design of wafer level package on board for gigabit data transmission," in 5th Electronics Packaging Technology Conf. (EPTC2003), Dec. 2003, pp. 150–159.

- [3] ANSOFT—HFSS Version 8.5 Manual, 2002.

- [4] J. Mao, M. Swaminathan, J. Libous, and D. O'Connor, "Effect of substrate resistivity on switching noise in on-chip power distribution network," in *Conf. Proc.* 2003 Electrical Performance of Electonic Packaging, Oct. 2003, pp. 33–36.

- [5] A. C. Chng, A. A. O. Tay, K. M. Lim, E. H. Wong, and K. Vaidyanathan, "Fatigue life estimation of a bed-of-nails ultra-fine-pitch wafer level package using the macro-micro modeling approach," in *Conf. Proc.* EPTC 2003, 2003, pp. 675–682.

- [6] B. Zhao, A. A. O. Tay, R. R. Tummala, C. P. Wong, Z. Q. Zhang, and R. Doraiswami, "Simulation of the fatigue life of solder ball joint of an ultra-fine pitch wafer level package," in *Proc. EPTC 2003*, 2003, pp. 683–687.

- [7] H. D. Solomon, "Fatigue of 60/40 solder," IEEE Trans. Compon., Hybrids, Manufact. Technol., vol. 9, pp. 423–432, 1986.

- [8] R. Rajoo, E. H. Wong, K. T. Tsai, T. L. Yap, and A. A. O. Tay, "Micro-fatigue characterization of wafer level stretched solder columns," in First Int. Workshop in Nano Bio-Packaging, Atlanta, GA, Mar. 2004, pp. 22–23.

Andrew A. O. Tay (M'91) received the B.E. degree in mechanical engineering with First Class Honors and University Medal from the University of New South Wales, Australia, and the Ph.D. degree from the same university, in 1970 and 1974, respectively.

He is a Professor with the Department of Mechanical Engineering and Director of the Nano/Microsystems Integration Laboratory, National University of Singapore. His research interests include thermomechanical failure of IC packages (delamination, effects of moisture, reliability),

measurement of adhesion strength, wafer level packaging (WLP), solder joint reliability, cooling of electronic systems, wire bonding, and wire sweep.

Dr. Tay is a member of the Editorial Board of *Microelectronics Journal*, a former Associate Editor of the ASME *Journal of Electronic Packaging*, and a former member of the editorial board of *Finite Elements in Analysis and Design*. He was the General Chairman of the First and the Second IEEE Electronic Packaging Technology Conference (EPTC'97 and EPTC'98), Singapore. He is also serving on the International Advisory Board and Organizing committees of several international packaging conferences such as EPTC, ECTC, InterPack, EuroSime, EMAP, IPFA, DTIP, MicroMat, and HDP. He is also in the Education Committee of the IEEE CPMT Society.

**Mahadevan K. Iyer** (M'96–SM'02) received the Ph.D. degree in electronics and communication engineering from Loughborough University of Technology, U.K.

He has 20 years of R&D experience in the area of design and development of electronic packages and high-frequency design and modeling. His research interests are in the development of new design and modeling stratgies and enabling technologies for system integration. Currently, he is heading the Microsystems, Modules and Components Laboratory

of Institute of Microelectronics, Singapore. He has more than 80 research papers and holds five U.S. patents.

Dr. Iyer and has won three Best Paper Awards in International Conferences. He is a Member of IMAPS.

**Rao R. Tummala** (M'81–SM'84–F'92) received the B.E. degree in metallurgical engineering from the Indian Institute of Science, Bangalore, and the Ph.D. degree in materials science and engineering (MSE) from the University of Illinois, in 1969.

He is an Endowed Chair Professor in electrical and computer engineering and MSE with the Georgia Institute of Technology (Georgia Tech), Atlanta. He is also the Founding Director of the Microsystems Packaging Research Center (PRC). The PRC is currently the largest and most

comprehensive microsystems packaging center involving 250 students, 30 faculty, and 50 global companies, and was funded by the National Science Foundation (NSF) as one of its Engineering Research Centers in the United States, the Georgia Research Alliance, and the electronics industry, where he is pioneering the system-on-a-package (SOP) vision for mixed-signal systems of the next decade. He is also a Temasek Professor, NUS, Singapore. Prior to joining Georgia Tech, he was an IBM Fellow where he invented a number of major technologies for IBM's products for packaging, displaying, printing, and magnetic storage that include LTCC and scale-up of multilayer alumina ceramic. He was also part of the pioneering team that developed the industry's first flat panel display based on gas discharge display. He was the Director of the Advanced Packaging Technology Laboratory for all of IBM in 14 labs across the United States, Europe, and Japan. He edited the first undergraduate textbook Fundamentals of Microsystems Packaging (New York: McGraw-Hill, 2001) currently used by 43 universities around the world. He edited the first modern book in packaging Microelectronic Packaging Handbook (1988) which began to catalyze the academic research and educational programs. During this time, he began to lecture and advise universities in this area throughout the United States. Three notable examples are: Chairman of Advisory Board at the Massachusetts Institute of Technology, Cambridge, from 1988 to 1993, at the University of California at Berkeley from 1984 to 1987, and at the University of Illinois, Urbana, from 1983 to 1986. He left IBM in October 1993 and, two weeks later, he wrote the winning NSF proposal for an NSF-Engineering Research Center on SOP. He has published 350 papers and holds 71 U.S. patents.

Dr. Tummala received 16 technical, outstanding, and corporate awards from IBM, the highest Faculty Award at Georgia Tech, alumni awards from the University of Illinois and IISc, the David Sarnoff award from the IEEE for MCM, the Dan Hughes Award from IMAPS, the Engineering Materials Award from ASME, the Total Quality Manufacturing Award from SME, and the IEEE's Major Educational Innovation award. He is a member of NAE, IMAPS, and the American Ceramic Society, and Past President of the IEEE CPMT and IMAPS societies.

V. Kripesh (M'01) received the M.S. degree in physics from University of Madras, Madras, India in 1987. He carried out his doctoral degree at the Max–Planck Institute for Metalforschung, Stuttgart, Germany, in the area of thick and thin film passives for microelectronics modules in 1995.

He has 16 years research experience in the area of advance packaging. He worked as a Visiting Scientist at Infineon Technologies, Corporate Research, Munich, Germany, in the area of 3-D-integrated circuits. Since March 2000, he has been with the Insti-

tute of Microelectronics, Singapore, heading a group of researchers in the area of 3-D-stacked silicon micro modules and wafer level packaging process. He has authored more than 40 journal and conference publications and holds 12 patents to his credit. His research interests are 3-D-silicon stacked modules, Cu/low-k packaging and wafer level packaging. He is also an Adjunct Faculty Member at National University of Singapore, where he teaches Microelectronics Packaging.

Dr. Kripesh is a member of IMAPS and he is currently the President of IMAPS, Singapore Chapter.

**E. H. Wong** received the M.Sc. degree in mechanics from the University of Manchester Institute of Science and Technology, U.K., in 1989.

He has spent a decade in the defense industry specializing on product and process development prior to joining the Institute of Microelectronics, Singapore, in 1996, where he is responsible for reliability modeling and material characterization for electronic packaging.

**Madhavan Swaminathan** (A'01–M'95–SM'98) received the M.S. and Ph.D. degrees in electrical engineering from Syracuse University, Syracuse, NY.

He is currently a Professor with the School of Electrical and Computer Engineering, Georgia Institute of Technology (Georgia Tech), Atlanta, and the Deputy Director of the Packaging Research Center (PRC), Georgia Tech. He is the cofounder of Jacket Micro Devices, a company specializing in integrated passive devices for RF applications where he serves as the Chief Scientist. Prior to

joining Georgia Tech, he was with the Advanced Packaging Laboratory, IBM, working on packaging for super computers. While at IBM, he reached the second invention plateau. He has more than 150 publications in refereed journals and conferences, has coauthored three book chapters, has nine issued patents, and has nine patents pending. His research interests are in digital, RF, optoelectronics, and mixed-signal packaging with emphasis on design, modeling, characterization, and test.

Dr. Swaminathan is the recipient of the 2002 Outstanding Graduate Research Advisor Award from the School of Electrical and Computer Engineering, Georgia Tech and the 2003 Outstanding Faculty Leadership Award for the advisement of GRAs from Georgia Tech. He is also the recipient of the 2003 Presidential Special Recognition Award from IEEE CPMT Society for his leadership of TC-12. He has also served as the coauthor for a number of outstanding student paper awards at EPEP'00, EPEP'02, EPEP'03, ECTC'98, and the 1997 IMAPS Education Award and is the recipient of the Shri. Mukhopadyay best paper award at the International Conference on Electromagnetic Interference and Compatibility in 2003. He served as the Co-Chair for the 1998 and 1999 IEEE Topical Meeting on Electrical Performance of Electronic Packaging (EPEP), the Technical and General Chair for the IMAPS Next Generation IC & Package Design Workshop, and the Co-Chair for the 2001 IEEE Future Directions in IC and Package Design Workshop. He serves as the Chair of TC-12, the Technical Committee on Electrical Design, Modeling and Simulation within the IEEE CPMT society. He is the cofounder of the IMAPS Next Generation IC & Package Design Workshop and the IEEE Future Directions in IC and Package Design Workshop. He also serves on the Technical Program Committees of EPEP, Signal Propagation on Interconnects Workshop, Solid State Devices and Materials Conference (SSDM), Electronic Components and Technology Conference (ECTC), and Interpack. He has been a Guest Editor for the IEEE TRANSACTIONS ON ADVANCED PACKAGING and the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES. He was the Associate Editor of the IEEE TRANSACTIONS ON COMPONENTS AND PACKAGING TECHNOLOGIES.

C. P. Wong (SM'87–F'92) received the B.S. degree in chemistry from Purdue University, West Lafayette, IN, and the Ph.D. degree in inorganic/organic chemistry from the Pennsylvania State University. After his doctoral study, he was awarded a two-year Post-doctoral Fellowship with Nobel Laureate Professor Henry Taube at Stanford University, Stanford, CA, where he conducted studies on electron transfer and reaction mechanism of metallocomplexes.

He joined AT&T Bell Laboratories in 1977 as a Member of Technical Staff and has been involved

with the research and development of the polymeric materials (inorganic and organic) for electronic and photonic applications. He became a Senior Member of Technical Staff in 1982, and a Distinguished Member of Technical Staff in 1987. Since 1996, he has been a Professor with the School of Materials Science and Engineering and a Research Director at the NSF-funded Packaging Research Center, Georgia Institute of Technology (Georgia Tech), Atlanta. He was named a Regents Professor in July 2000. His research interests are in the fields of polymeric materials, high Tc ceramics, materials reaction mechanism, IC encapsulation, in particular, hermetic equivalent plastic packaging, electronic manufacturing packaging processes, interfacial adhesions, PWB, SMT assembly, components reliability, and nanofunctional materials. He holds more than 40 U.S. patents, numerous international patents, has published more than 400 technical papers and 350 key notes and presentations in the related area.

Dr. Wong was elected as an AT&T Bell Laboratories Fellow (the most prestigious award bestowed by Bell Labs) in 1992 for his fundamental contributions to low-cost high-performance plastic packaging of semiconductors. He received the Best Paper Award in 1981 at the International Society for Hybrids and Microelectronics Annual Meeting, the AT&T Engineering Research Center Technical Achievement Award in 1983, the AT&T Bell Laboratories Distinguished Technical Staff Award in 1987, a 1992 AT&T Bell Laboratories Fellow Award, the IEEE Components, Packaging and Manufacturing Technology (CPMT) Society's Outstanding and Best Paper Awards in 1990, 1991, 1994, 1996, and 1998, the IEEE-CPMT Society Board of Governors Distinguished Contributions Award in 1991, the IEEE Technical Activities Board (TAB) Distinguished Service Award in 1994, the 1995 IEEE CPMT Society's Outstanding Sustained Technical Contributions Award (the Highest Society Honor), the Outstanding Faculty Research Program Development Award, the NSF-ERC Packaging Research Center Faculty of the Year Award from Georgia Tech in 1999, the IEEE millenium medal in 2000, the University Press (London) Award of Excellence in 2000, the Georgia Tech Sigma Xi Faculty Paper in 2000, the IEEE Educational Board Activities Meritorious Educational Award 2001, and the IEEE Exceptional Technical Contribution Award 2002.

Mihai D. Rotaru (M'01) received the B.S. and M.S. degrees in electrical engineering from the Technical University of Cluj, Romania, in 1996 and 1997, respectively, and the Ph.D. degree in electrical engineering from the University of Southampton, U.K., in 2000. His doctoral research was on modeling and computation of ac losses and electromagnetic fields in high-temperature superconductors tapes using an E-J characteristic diffusion model.

From 2000 to 2001, he was with the School of Engineering and Mathematical Science, City

University London, U.K., where he worked in simulation and modeling of electromagnetic problems. Since May 2001, he has been with the Institute of Microelectronics, Singapore, Microsystems, Modules and Components Laboratory, working on design, simulation, and analysis of advanced packaging solution for microelectronics. Presently, he is involved in designing, modeling, and characterization of system-in-package solutions for wireless applications, as well as electromagnetic modeling of 3-D stack modules. His professional interest includes efficient modeling techniques for complex electromagnetic problems and system-in-package integration solution for RF front end.

Ravi Doraiswami received the M.S. degree in applied sciences in 1986, and the Master of Technology degree in lasers and electrooptical engineering in 1987 from the College of Engineering, Madras, India. He received the Ph.D. degree in mechatronics from the Indian Institute of Technology, Delhi.

He was a Senior Scientific Officer II with the Indian Institute of Technology, New Delhi, from August 1990 to July 1995. From December 1995 to September 1999, he was a Research Fellow with Nanyang Technological University, Singapore. From

September 1999 to September 2000, he was a Lecturer with North Dakota State University, Fargo. Currently, he is a full-time research faculty member with the Packaging Research Center (PRC), Georgia Institute of Technology (Georgia Tech), Atlanta. Since September 2000, he has been a faculty member with the Electronics and Computer Engineering Department, Georgia Tech. He teaches a hands-on module course "Design Build and Operate II" and coteaches "Fundamentals of Microsystems Packaging" at Georgia Tech. He is the wafer-level packaging test bed leader at the PRC, Georgia Tech. He also has written several publications on electronics packaging.

Simon S. Ang received the B.S.E.E. degree from the University of Arkansas, Fayetteville, in 1980, the M.S.E.E. degree from the Georgia Institute of Technology (Georgia Tech), Atlanta, in 1981, and the Ph.D. degree in electrical engineering from Southern Methodist University in 1985.

He was with Texas Instruments, Dallas, from 1981 to 1988. He joined the University of Arkansas in 1988. From 2001 to 2002, he was with the National University of Singapore. He is currently at the University of Arkansas, where he is a Professor of

electrical engineering. He has authored and coauthored more than 190 journal and proceeding papers.

**E. T. Kang** received the B.S. degree in chemical engineering from the University of Wisconsin, Madison, in 1978, and the Ph.D. degree in chemical engineering from the State University of New York at Buffalo, in 1983.

He joined the Department of Chemical and Biomolecular Engineering at the National University of Singapore in 1984, and is currently a Professor in the same department. His research interests include the applications of polymers in microelectronics, nano-level electronics, molecular electronics, and

biomolecular engineering.