# ENERGY-EFFICIENT DIGITAL HARDWARE PLATFORM FOR LEARNING COMPLEX SYSTEMS

A Dissertation

Presented to

The Academic Faculty

By

Jae Ha Kung

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology

May 2017

Copyright © Jae Ha Kung 2017

# ENERGY-EFFICIENT DIGITAL HARDWARE PLATFORM FOR LEARNING COMPLEX SYSTEMS

# Approved by:

Dr. Saibal Mukhopadhyay, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Sudhakar Yalamanchili School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Arijit Raychowdhury School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Hyesoon Kim School of Computer Science Georgia Institute of Technology

Dr. Sek Chai Center for Vision Technologies SRI International

Date Approved: March 16, 2017

#### **ACKNOWLEDGEMENTS**

I sincerely appreciate my advisor Professor Saibal Mukhopadhyay for the full support in every aspect of my doctoral studies. He has been a great academic mentor, and his research vision and guidance let me grow as an independent researcher. Having discussion with him significantly improved the quality of my research work and developed my ability to approach and solve fundamental problems that have great impact. Beside being the academic advisor, he helped me when I was having personal difficulties as if that was his own. It was always been a pleasure to personally talk with him and I will remain thankful.

I also want to thank my thesis committee members, Professor Sudhakar Yalamanchili, Professor Arijit Raychowdhury, Professor Hyesoon Kim and Dr. Sek Chai for their time, efforts and suggestions in improving the quality of the dissertation.

I thank the former and the current colleagues in GREEN Lab at Georgia Tech for providing me an enjoyable environment and going through the hard times together. I am thankful to work with and to know Dr. Minki Cho, Dr. Kwanyeob Chae, Dr. Denny Lie, Dr. Sergio Carlo, Dr. Wen Yueh, Dr. Amit Trivedi, Dr. Boris Alexandrov and Dr. Zakir Ahmed who had graduated before me. Also, it was great to spend time with the future PhDs, Monodeep Kar, Jong Hwan Ko, Taesik Na, Faisal Amir, Arvind Singh, Yun Long and Burhan Mudassar. Especially, I am thankful to Duckhwan Kim for being a great teammate for many research works and being a sincere friend. I will never forget the moments spent with my colleagues and hope everything goes well with their future studies and other plans.

Finally, I greatly appreciate my beloved wife and children, Hana Kang, Jiho and Jia Kung, for supporting my back in all aspects of my life. I also thank my family members in South Korea for all the sacrifices they have made for me.

# TABLE OF CONTENTS

| Acknov  | vledgm   | ents                                                           | iii |

|---------|----------|----------------------------------------------------------------|-----|

| List of | Tables   |                                                                | ix  |

| List of | Figures  |                                                                | X   |

| Chapte  | r 1: Int | roduction                                                      | 1   |

| Chapte  | r 2: Ba  | ckground on System Learning Methods                            | 4   |

| 2.1     | Model    | l-based Learning                                               | 4   |

|         | 2.1.1    | Scientific Modeling: Formulation of Dynamical Systems          | 4   |

|         | 2.1.2    | Hardware Platform for Model-based Learning                     | 5   |

|         | 2.1.3    | Computing Model for Simulating Dynamical Systems               | 5   |

| 2.2     | Data-c   | driven Learning                                                | 6   |

|         | 2.2.1    | Fundamentals of Neural Networks                                | 6   |

|         | 2.2.2    | Impact of Noise on Neural Networks                             | 9   |

|         | 2.2.3    | Neuromorphic Hardware                                          | 11  |

| Chapte  | •        | ghly-Efficient Model-based System Learning Integrated Circuits | 14  |

| 3.1     | Backg    | ground: Thermal Analysis of ICs                                | 15  |

|         | 3.1.1  | Need for Post-silicon Thermal Analysis                                          | 15 |

|---------|--------|---------------------------------------------------------------------------------|----|

|         | 3.1.2  | Related Work on Full-chip Temperature Estimation with Limited Number of Sensors | 15 |

|         | 3.1.3  | Thermal System Identification (TSI)                                             | 17 |

| 3.2     | MIMC   | Thermal Filter                                                                  | 19 |

|         | 3.2.1  | Superposition Principle                                                         | 19 |

|         | 3.2.2  | Definition of MIMO Thermal Filter                                               | 21 |

| 3.3     | Test C | hip: Thermal Emulator                                                           | 22 |

|         | 3.3.1  | Extraction of MIMO Thermal Filter                                               | 22 |

| 3.4     | Experi | mental Results                                                                  | 24 |

|         | 3.4.1  | Extraction of MIMO Thermal Filter                                               | 24 |

|         | 3.4.2  | Accuracy of the Temperature Prediction Using MIMO Thermal Filter                | 26 |

| 3.5     | Tempe  | erature Estimation at Locations Without Temperature Sensors                     | 29 |

|         | 3.5.1  | Interpolated Thermal Filter                                                     | 29 |

|         | 3.5.2  | Experimental Validation                                                         | 31 |

| 3.6     | Hardw  | rare Design of MIMO Thermal Filter                                              | 34 |

| 3.7     | Summ   | ary of the Chapter                                                              | 36 |

| Chapter |        | Generic and Energy-Efficient Accelerator for Simulating Dynam-                  | 38 |

| 4.1     | Comp   | utation Model                                                                   | 40 |

|         | 4.1.1  | Mapping Linear Systems                                                          | 41 |

|         | 4.1.2  | Mapping Nonlinear Systems                                                       | 42 |

| 4 2     | Onerat | ion of DE Solver                                                                | 44 |

| 4.3    | Systen  | n Architecture                                                                      | 46 |

|--------|---------|-------------------------------------------------------------------------------------|----|

|        | 4.3.1   | Real-Time Template Weight Update                                                    | 46 |

|        | 4.3.2   | Storage of States, Inputs, and Templates                                            | 49 |

|        | 4.3.3   | Processing Engine Architecture                                                      | 50 |

| 4.4    | Datafle | ow in Proposed DE Solver                                                            | 50 |

|        | 4.4.1   | Exploration of Different Dataflow Schemes                                           | 50 |

|        | 4.4.2   | OS Dataflow in Proposed DE Solver                                                   | 53 |

| 4.5    | Systen  | n Analysis of DE Solver                                                             | 55 |

|        | 4.5.1   | Benchmark Differential Equations                                                    | 55 |

|        | 4.5.2   | Miss Rate Analysis for Weight Update                                                | 57 |

|        | 4.5.3   | Performance Comparison                                                              | 58 |

|        | 4.5.4   | Integration with High-bandwidth Memory                                              | 59 |

|        | 4.5.5   | Power Consumption of DE Solver                                                      | 60 |

| 4.6    | Relate  | d Work                                                                              | 61 |

| 4.7    | Summ    | ary of the Chapter                                                                  | 62 |

| Chapte |         | wer-Aware Digital Feedforward Neural Network for Learning Static<br>nlinear Systems |    |

| 5.1    | Backg   | round                                                                               | 64 |

|        | 5.1.1   | Feedforward Neural Network                                                          | 64 |

|        | 5.1.2   | Prior Work on Neural Network Hardware                                               | 65 |

| 5.2    | Power   | Analysis of Processing Engines                                                      | 66 |

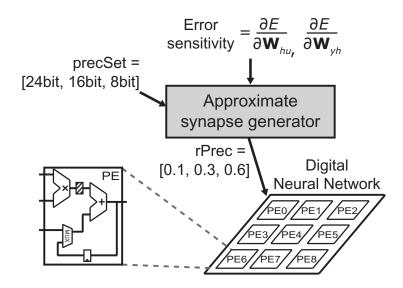

| 5.3    | Appro   | ximate Synapses Selection                                                           | 68 |

|        | 5.3.1   | Design Methodology                                                                  | 68 |

|        | 5.3.2   | Greedy Algorithm for Low-Power Design                            | 73  |

|--------|---------|------------------------------------------------------------------|-----|

| 5.4    | Full S  | ystem Power Analysis                                             | 76  |

| 5.5    | Summ    | ary of the Chapter                                               | 80  |

| Chapte | r 6: En | ergy-Efficient Learning of Dynamic Nonlinear Systems             | 81  |

| 6.1    | Prelim  | ninaries                                                         | 82  |

|        | 6.1.1   | Recurrent Neural Network                                         | 82  |

|        | 6.1.2   | Training of Recurrent Neural Network                             | 83  |

|        | 6.1.3   | Approximate Feedforward Neural Network                           | 84  |

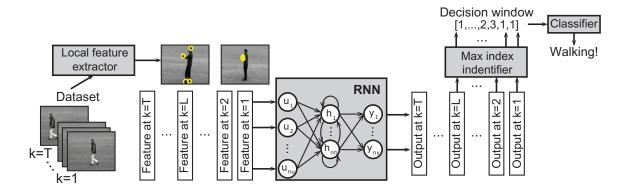

|        | 6.1.4   | Sequence Classification Using RNN                                | 85  |

| 6.2    | Appro   | ximate Computing in RNN                                          | 86  |

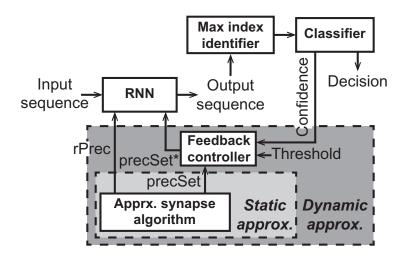

|        | 6.2.1   | Static Approximation in RNN                                      | 86  |

|        | 6.2.2   | Dynamic Approximation in RNN                                     | 87  |

|        | 6.2.3   | Feedback Controller in Digital RNN                               | 88  |

| 6.3    | Simula  | ation Results                                                    | 91  |

|        | 6.3.1   | Benchmark: Human Activity Recognition                            | 91  |

|        | 6.3.2   | Operation of Dynamic Approximation                               | 91  |

|        | 6.3.3   | Digital RNN with Dynamic Approximation                           | 94  |

|        | 6.3.4   | Energy-Accuracy Trade-off                                        | 95  |

| 6.4    | Summ    | ary of the Chapter                                               | 98  |

| Chapte |         | alysis of Energy-Accuracy Tradeoff in Digital Cellular Nonlinear | 00  |

|        |         | twork                                                            |     |

| 7 1    | Racko   | round                                                            | 101 |

|         | 7.1.1    | Fundamentals of Cellular Nonlinear Network (CeNN)101 |

|---------|----------|------------------------------------------------------|

|         | 7.1.2    | Dynamic Route of CeNN                                |

| 7.2     | Impact   | of Error on CeNN                                     |

|         | 7.2.1    | Impact of Error on Cell Dynamics                     |

|         | 7.2.2    | Convergence Time Constraints                         |

|         | 7.2.3    | Experimental Characterization of Error Propagation   |

| 7.3     | Design   | of a Digital CeNN                                    |

|         | 7.3.1    | Hardware Design of CeNN                              |

|         | 7.3.2    | Power and Bit Error Rate Analysis of Digital CeNN    |

| 7.4     | Energy   | 7-Accuracy Tradeoff in CeNN                          |

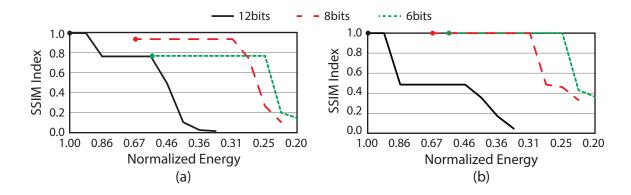

|         | 7.4.1    | Analysis of Image Quality                            |

|         | 7.4.2    | Energy-Accuracy Tradeoff                             |

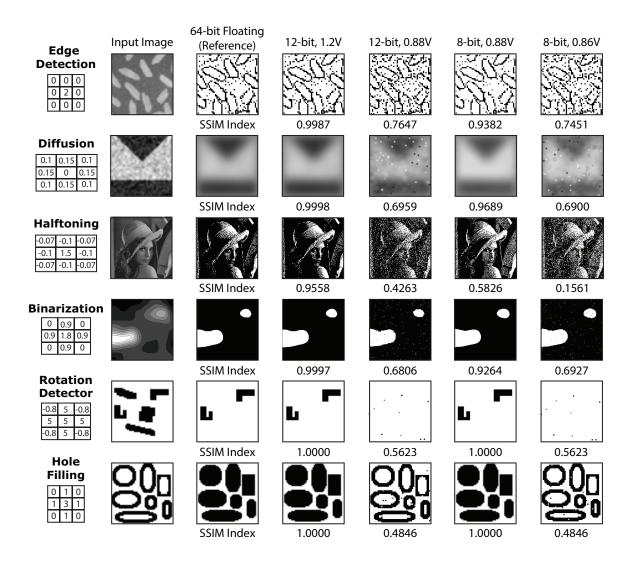

| 7.5     | Impact   | of Applications                                      |

|         | 7.5.1    | Simple Image Processing Applications                 |

|         | 7.5.2    | Case Study: Fingerprint Preprocessing Application    |

| 7.6     | Discus   | sions                                                |

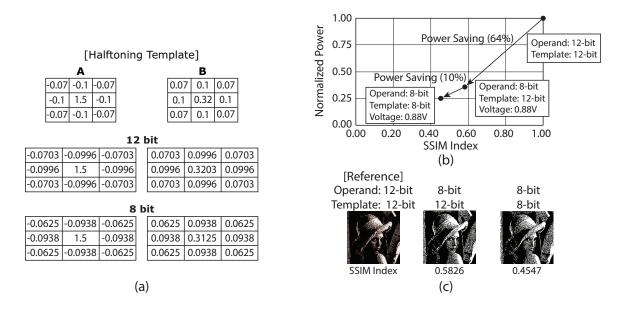

|         | 7.6.1    | Effect of Truncation in the Templates                |

|         | 7.6.2    | Adaptive Precision Control                           |

| 7.7     | Summ     | ary of the Chapter                                   |

| Chapte  | r 8: Coi | nclusion                                             |

| Defener |          | 144                                                  |

# LIST OF TABLES

| 3.1 | Verification of the superposition principle by using the RC-based thermal simulator [119]                | 20  |

|-----|----------------------------------------------------------------------------------------------------------|-----|

| 4.1 | The power consumption of modules in PE array having 64 (PEs-L1 LUT) pairs                                | 61  |

| 4.2 | The overall power consumption including PE array and global buffer (data banks + shared template buffer) | 61  |

| 4.3 | The comparison of the proposed DE solver to previous hardware platforms for cellular nonlinear network.  | 62  |

| 5.1 | The system analysis in terms of power, area, and recognition accuracy                                    | 79  |

| 6.1 | The classification of each dataset into training, validation and inference sets                          | 92  |

| 6.2 | Power consumption and area breakdown of the proposed RNN hardware with dynamic approximation             | 96  |

| 7.1 | SSIM Index by Running an Edge Detection Algorithm with Different Precision Bit-width                     | 115 |

| 7.2 | Simulation Results on Adaptive Precision Control                                                         | 123 |

# LIST OF FIGURES

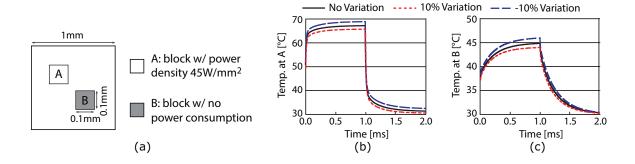

| 3.1  | An illustrative simulation result using RC-based thermal simulator [119] of the thermal coupling with variations on thermal conductivity of TIM; (a) an example floorplan used for the simulation, (b) transient temperature of power consuming block A, and (c) that of non-power consuming block B. | 16 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

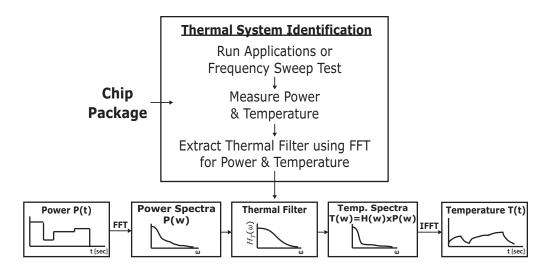

| 3.2  | The basic concept of Thermal System Identification (TSI) method [3]. The method requires FFT/IFFT computation                                                                                                                                                                                         | 17 |

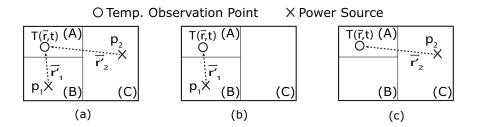

| 3.3  | Superposition of heat energy from two power sources at a certain temperature observation point                                                                                                                                                                                                        | 20 |

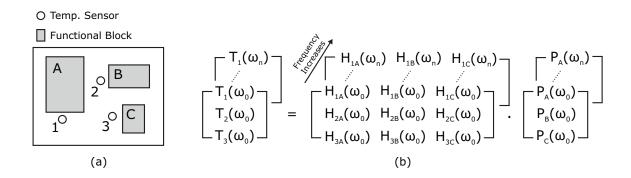

| 3.4  | (a) A simple floorplan example with multiple power sources and temperature sensors and (b) the corresponding matrix equation of the MIMO thermal filter.                                                                                                                                              | 21 |

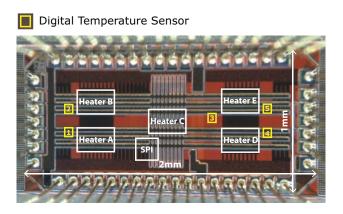

| 3.5  | The die photo of the test chip; five digitally controllable heaters, five digital sensors, and SPI registers [134]                                                                                                                                                                                    | 22 |

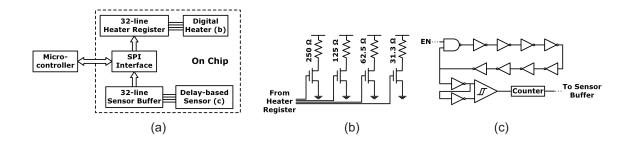

| 3.6  | (a) A block diagram of the test chip and the microcontroller, (b) a schematic of resistor banks to control power (heat) generation, and (c) a schematic of a delay-based digital temperature sensor                                                                                                   | 23 |

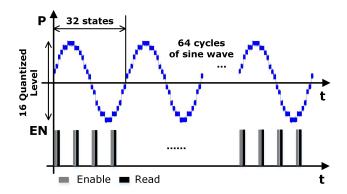

| 3.7  | The 'EN' signal for the digital sensor reading with 64 cycles of sinusoidal power pattern applied at the heater                                                                                                                                                                                       | 24 |

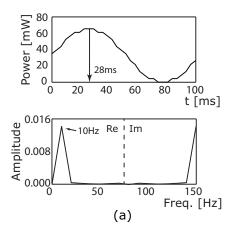

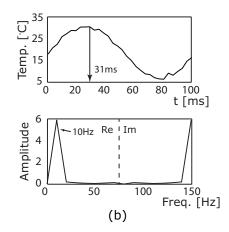

| 3.8  | (a) The heater power and (b) the measured temperature both in time- and frequency-domain at $10$ Hz. Note that the temperature has some delay to follow power transition ( $\sim 3$ ms)                                                                                                               | 25 |

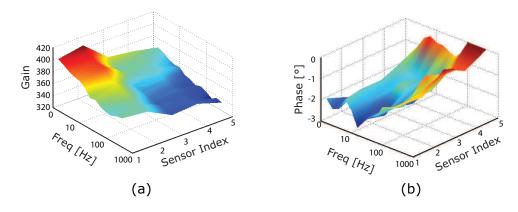

| 3.9  | (a) The amplitude response and (b) the phase response of the MIMO thermal filter extracted from our test chip when heater 'B' is turned on                                                                                                                                                            | 26 |

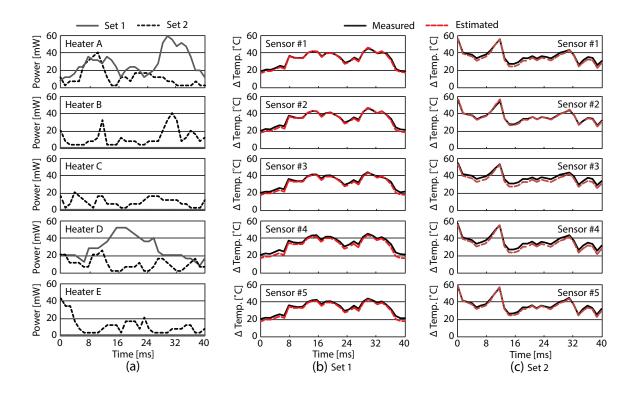

| 3.10 | (a) Two sets of tested input power pattern at each heater and (b-c) the comparison between the measured temperature and the estimated one when input power pattern is set 1 (b) and set 2 (c)                                                                                                         | 27 |

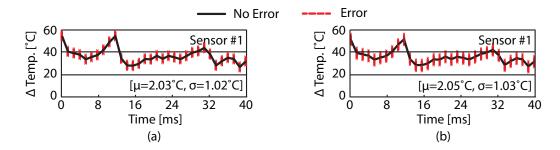

| 3.11 | #1 for brevity) without sensor error and with sensor error (100 simulations) for (a) normal power and (b) low power temperature sensor case                                                                                                                                                     | 28      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

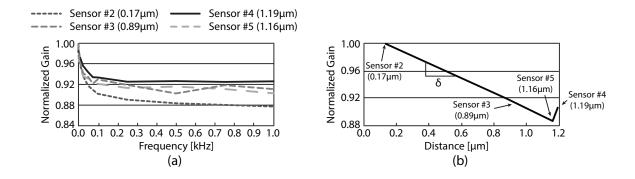

| 3.12 | (a) The normalized gain of each sensor (except sensor #1) at different frequencies of the heater 'B'; the distance from the heater to each sensor is denoted inside the parentheses and (b) the normalized gain of each sensor (except sensor #1) as a function of the distance from heater 'B' | 31      |

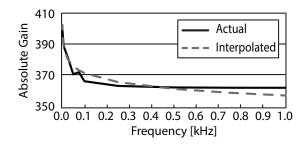

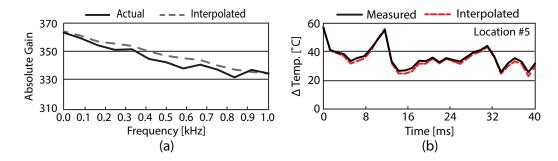

| 3.13 | The comparison between the actual thermal filter response and the interpolated one at sensor location #1 when heater 'B' is on                                                                                                                                                                  | 32      |

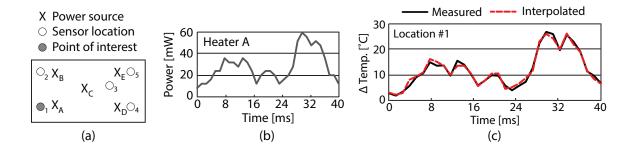

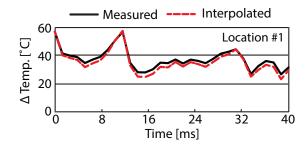

| 3.14 | (a) A tested floorplan assuming sensor #1 is not available, (b) applied power pattern at heater 'A' (no power consumption elsewhere), and (c) the accuracy of temperature estimation at location #1 using the proposed interpolated thermal filter.                                             | 33      |

| 3.15 | The accuracy of temperature estimation at location #1 (assuming there is no temperature sensor at #1) when power pattern set 2 is used from Fig. 3.10(a).                                                                                                                                       | 33      |

| 3.16 | (a) The comparison between the actual thermal filter response and the interpolated one at sensor location #5 when heater 'B' is on and (b) the accuracy of temperature estimation at location #5 when power pattern set 2 is used from Fig. 3.10(a)                                             | 34      |

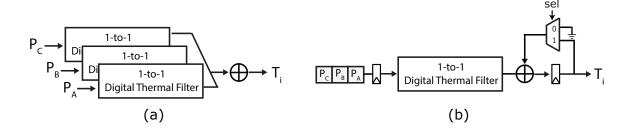

| 3.17 | On-chip time-domain MIMO thermal filter implementation: (a) the thermal filter banks and (b) the pipelined thermal filter                                                                                                                                                                       | 35      |

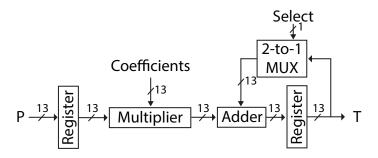

| 3.18 | A block diagram of an on-chip digital thermal filter implementation                                                                                                                                                                                                                             | 36      |

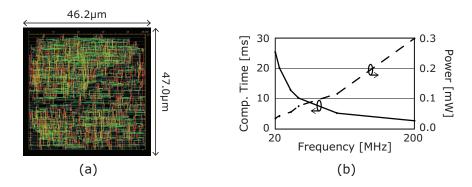

| 3.19 | (a) The layout of the on-chip thermal filter after the physical synthesis and (b) its dynamic power consumption and the computation time                                                                                                                                                        | 37      |

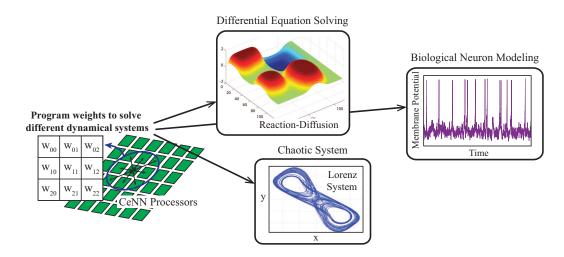

| 4.1  | Programmable computing model by using <u>Cellular Nonlinear Network</u> (CeNN) with some dynamical systems that can be modeled by CeNN                                                                                                                                                          | )<br>39 |

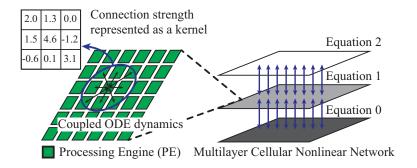

| 4.2  | A 2-dimensional CeNN processing array having cell states locally coupled. This structure can be extended to a multilayer CeNN platform to handle coupled systems.                                                                                                                               | 41      |

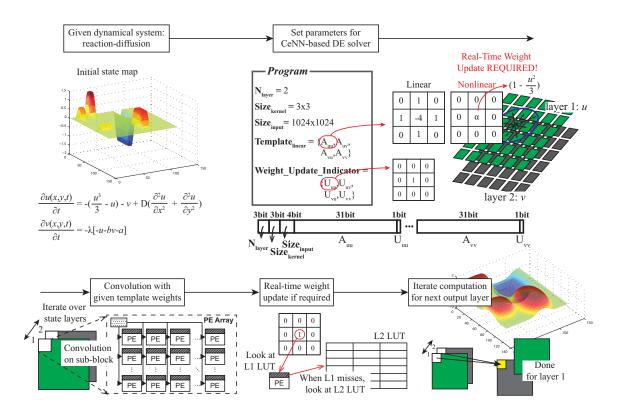

| 4.3  | The overall operation of the proposed CeNN-based differential equation (DE) solver. With a given dynamical system, template weights and other parameters are set to program the DE solver (binary bit stream is used to program). Then, a sub-block in each state map (each layer) is fed into PE array to perform convolution on them. When real-time weight update is required, it looks at LUTs at different levels | 44 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

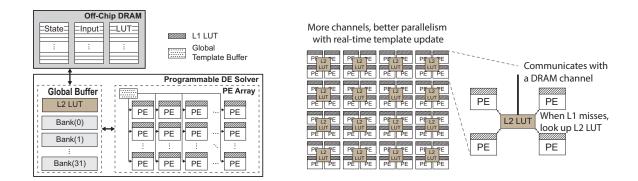

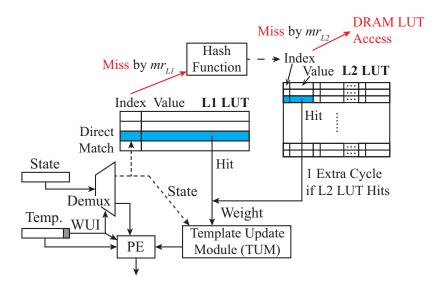

| 4.4  | The overall architecture of CeNN-based DE solver. Look-up Tables (LUTs) allow nonlinear and real-time weight updates with complex functions                                                                                                                                                                                                                                                                            | 47 |

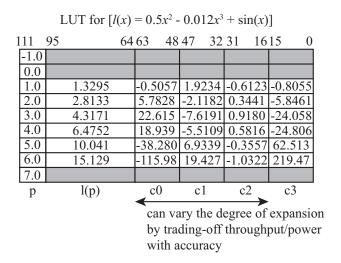

| 4.5  | The data format stored in off-chip LUT of an examplary nonlinear function required for real-time weight update                                                                                                                                                                                                                                                                                                         | 47 |

| 4.6  | The operation of real-time weight update to compute state nonlinear template $\hat{\mathbf{A}}.$                                                                                                                                                                                                                                                                                                                       | 49 |

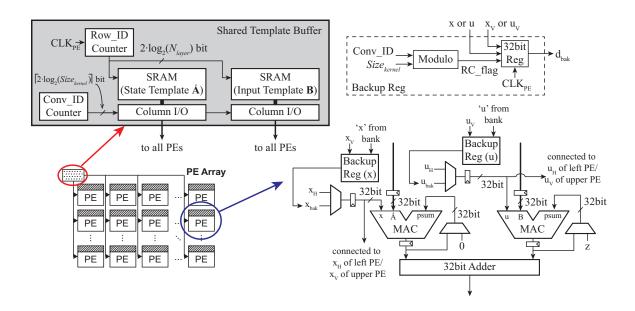

| 4.7  | The detailed circuit block diagram of a global template buffer and a processing element                                                                                                                                                                                                                                                                                                                                | 51 |

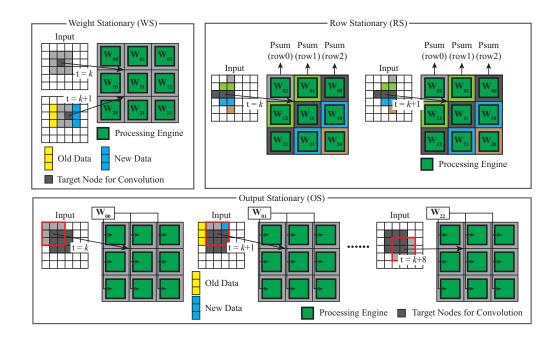

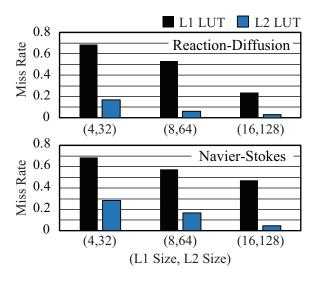

| 4.8  | The comparison between different dataflow schemes for consecutive time steps with $3\times3$ template (kernel). Other than OS dataflow, entire template weights are used during the convolution operation                                                                                                                                                                                                              | 52 |

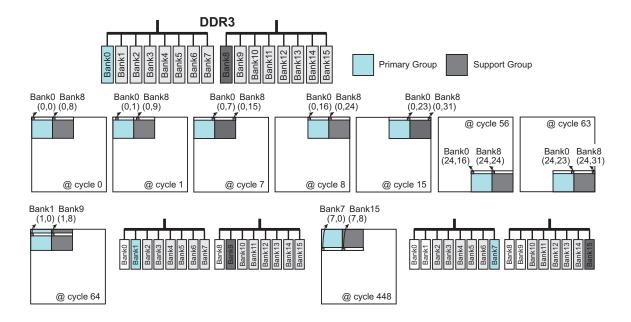

| 4.9  | Data prefetching from off-chip DRAM to on-chip global buffer for $32\times32$ input. There are two bank groups (primary and support) to utilize intra-PE data transfer                                                                                                                                                                                                                                                 | 54 |

| 4.10 | Dataflow modes from data banks to PE array during convolution operation. A proper mode selection for the convolution operation with $3\times3$ template is shown as an example                                                                                                                                                                                                                                         | 55 |

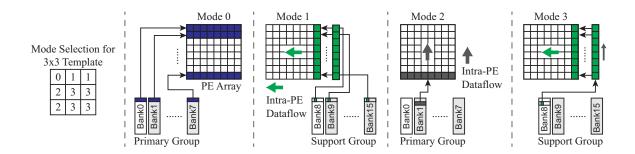

| 4.11 | The accuracy comparison between GPU (64bit floating-point) and CeNN-based solver (32bit fixed-point)                                                                                                                                                                                                                                                                                                                   | 56 |

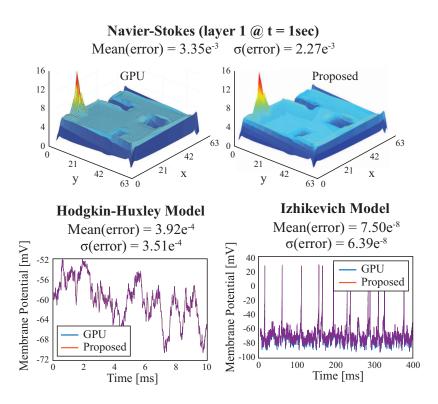

| 4.12 | The miss rate depending on the size of on-chip LUTs for two different dynamical systems                                                                                                                                                                                                                                                                                                                                | 57 |

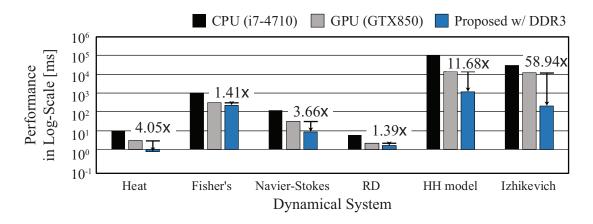

| 4.13 | The performance comparison on six different benchmark differential equations. The speed-up using the proposed CeNN-based solver with DDR3 is shown compared to the performance using GPU (GTX 850)                                                                                                                                                                                                                     | 59 |

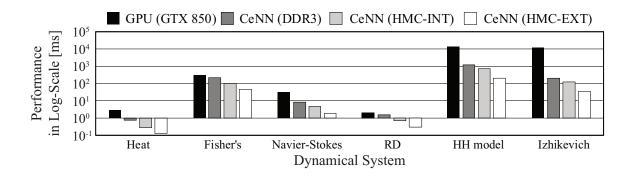

| 4.14 | The performance improvement by using 3D memory stack with higher memory bandwidth                                                                                                                                                                                                                                                                                                                                      | 60 |

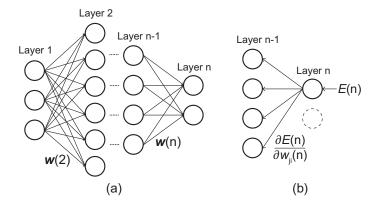

| 5.1 | (a) The operation of feedforward neural network. (b) The backpropagation training algorithm computing the error sensitivity $(\partial E/(\partial w_{ji}))$                                                                                                                                                                                                                    | 64 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

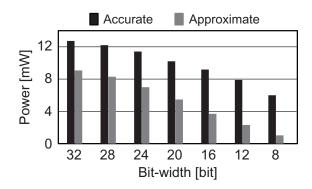

| 5.2 | The power dissipation of the accurate multiplier (black) and the approximate multiplier (gray)                                                                                                                                                                                                                                                                                  | 67 |

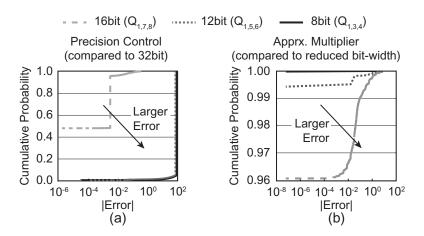

| 5.3 | The cumulative probability of (a) quantization error due to precision control and (b) the additional error induced by using an approximate multiplier with error correction of 20 MSBs ( $x$ -axis is logarithmic scale)                                                                                                                                                        | 68 |

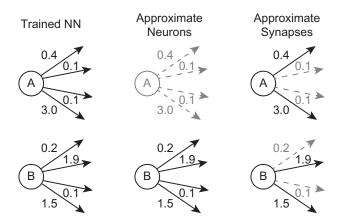

| 5.4 | Diagram illustrating the advantage of approximating synapses over approximating neurons on a given trained feedforward NN                                                                                                                                                                                                                                                       | 69 |

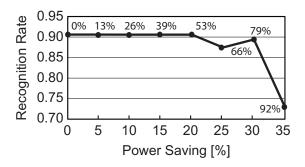

| 5.5 | Recognition rate from MNIST dataset when approximation of synapses ( <i>only precision control</i> ) is allowed to meet a set of given power constraints. The percentage of approximate synapses to meet each power constraint is provided in the plot as well. The analysis assumes only two precision levels.                                                                 | 71 |

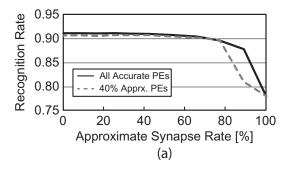

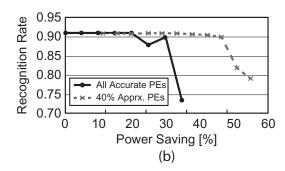

| 5.6 | MNIST recognition rate with accurate (100% accurate) and approximate (40% approximate, 60% accuarte) PEs (a) at different rates of approximate synapses and (b) at different power constraints                                                                                                                                                                                  | 73 |

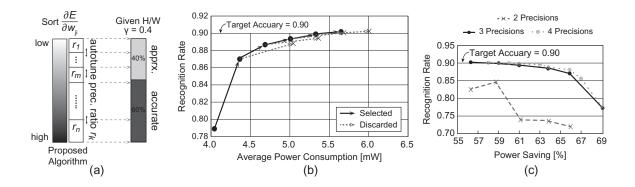

| 5.7 | (a) Overview of the proposed greedy algorithm with $\gamma=0.4$ . (b) Experimental result on quality-aware low-power design methodology. This method dynamically selects (solid line) precision bit-widths which increase accuracy with less power increase. (c) Recognition rate comparison between two, three, and four different bit-precisions at varying power constraints | 74 |

| 5.8 | Comparison of the proposed algorithm to just doing software (reduced bit-precisions) or hardware (approximate PEs) approach. Proposed approach couples both reduced bit-preciosn and approximate PE                                                                                                                                                                             | 77 |

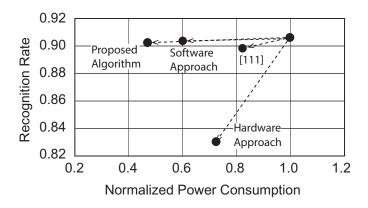

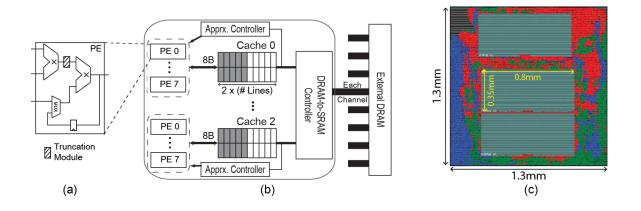

| 5.9 | A system diagram: (a) a processing engine (PE), (b) the overall NN system including PEs, caches and controllers and (c) the layout of the components connected to each channel; 3 SRAMs and 24 PEs (40% approximate and 60% accurate) with required controllers                                                                                                                 | 78 |

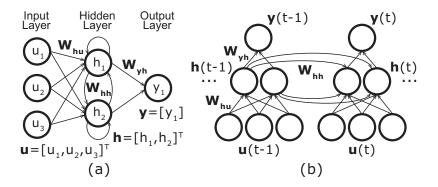

| 6.1 | Overview of RNN: (a) RNN with one hidden layer where recurrent connections ( $\mathbf{W}_{hh}$ ) are established between hidden neurons. (b) The same topology unfolded in time                                                                                                                                                                                                 | 82 |

| 6.2 | Overview of approximate synapse for low-power operation of digital neuromorphic hardware. Here, <i>p</i> recSet represents the fixed bit-precision set and <i>r</i> Prec is the ratio of each bit-precision                                                                                                                                                                                 | 85  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3 | Block diagrams of video classification using RNN. Local feature extractor is used to recognize important local features to obtain an input sequence for RNN. Then, RNN outputs a sequence which can be post-processed to decide which activity a subject in the video is performing                                                                                                         | 86  |

| 6.4 | The proposed approximation algorithm for RNN in video (or sequence) classification                                                                                                                                                                                                                                                                                                          | 88  |

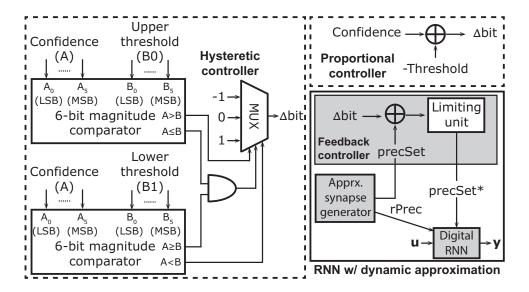

| 6.5 | The proposed feedback controllers to implement dynamic approximation for RNN in hardware                                                                                                                                                                                                                                                                                                    | 90  |

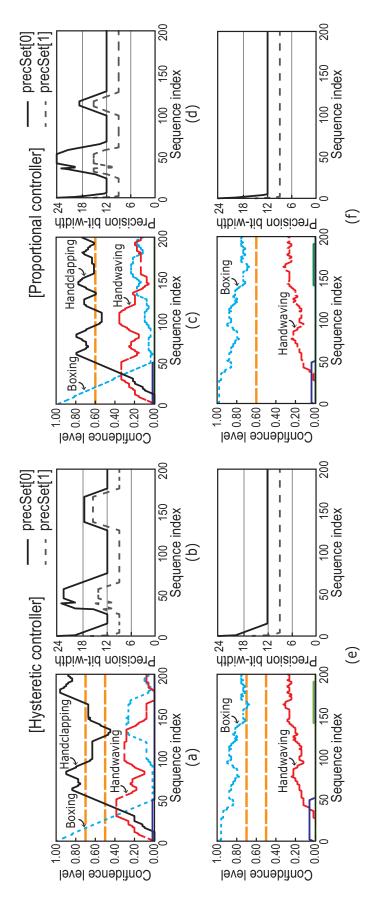

| 6.6 | The operation of the dynamic approximation to adaptively change bit-precision of synapses. (a) Confidence level of each activity and (b) the resulting prec-Set by using hysteretic controller. (c) Confidence level of each activity and (d) the resulting precSet by using proportional controller (handclapping). (e-f) The same set of experiment for different human activity (boxing) | 93  |

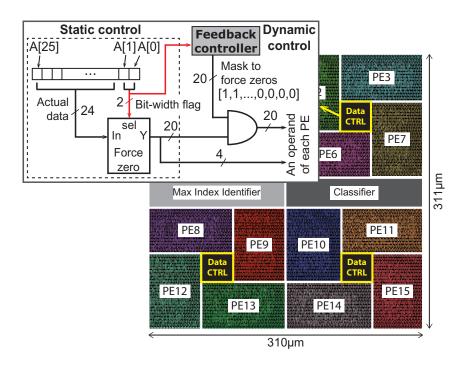

| 6.7 | Synthesis and placement of the RNN hardware with dynamic approximation. A small data controller is placed near the center                                                                                                                                                                                                                                                                   | 95  |

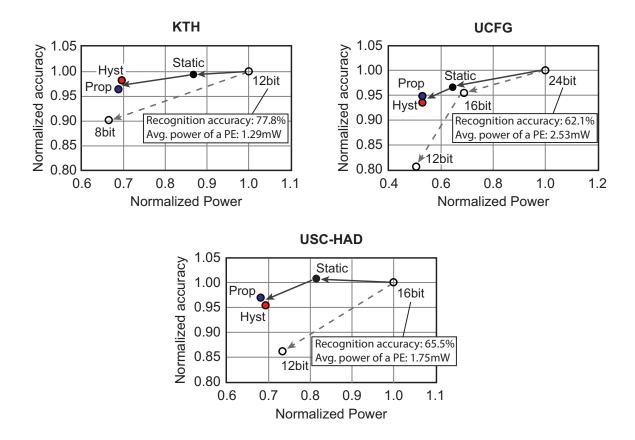

| 6.8 | Simulation results showing normalized accuracy vs. normalized power for each benchmark with different computation methods: single fixed point, static approximation and dynamic approximation (hysteretic or proportional).                                                                                                                                                                 | 97  |

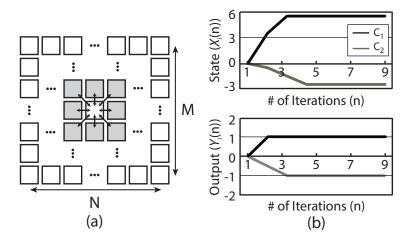

| 7.1 | (a) Structure of a $M \times N$ CeNN with a cell locally connected to neighbor (gray) cells and (b) dynamic behavior of the state $(X_i)$ and the output $(Y_i)$ of two randomly selected cells $(C_i)$                                                                                                                                                                                     | 100 |

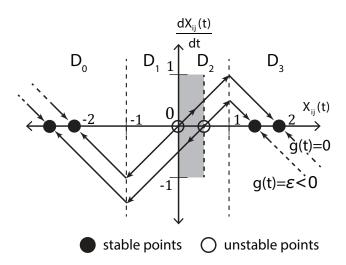

| 7.2 | Dynamic routes and two equilibrium points of the state $x_{ij}(t)$ when $g(t) = 0$ [188]; dynamic route of a cell changes due to error $\epsilon$ (direction reverses in the shaded area)                                                                                                                                                                                                   | 103 |

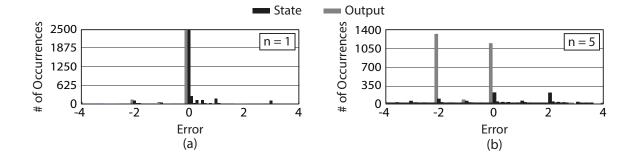

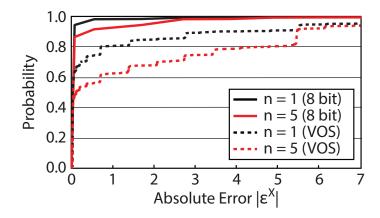

| 7.3 | Histogram of error in CeNN state and CeNN output at time step (a) $n=1$ and (b) $n=5$ . The analysis is shown with the hole filling at 5% bit error rate.                                                                                                                                                                                                                                   | 108 |

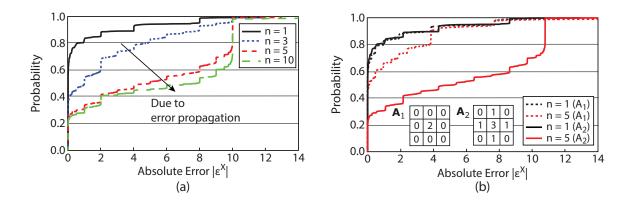

| 7.4 | Impact of the feedback template $A$ on error propagation by looking at empirical CDF with $P_b = 5\%$ : (a) detailed trajectory of error propagation for hole filling algorithm and (b) comparison of the error propagation between two different templates ( $A_1$ : edge detection and $A_2$ : hole filling)                                                                              | 109 |

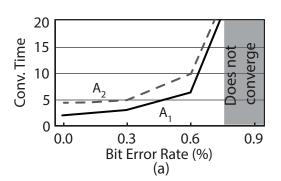

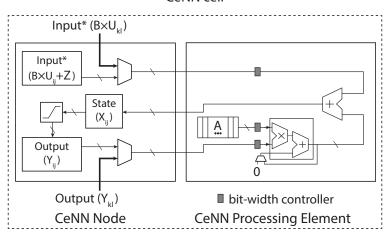

| 1.5  | (a) Convergence time increase due to error and (b) accuracy degradation in terms of SSIM of the CeNN output when number of iterations is fixed for real-time CeNN under different $P_b$ 's                                                                                                        | . 110 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

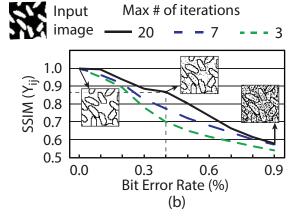

| 7.6  | Digital CeNN implementation of a single cell consists of a CeNN node and a processing element (PE)                                                                                                                                                                                                | . 111 |

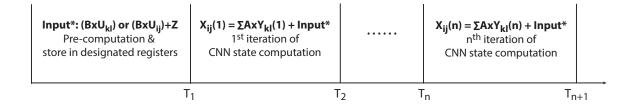

| 7.7  | Simple timing diagram showing CeNN computation steps using the hardware with one ALU as shown in Figure 7.6                                                                                                                                                                                       | . 112 |

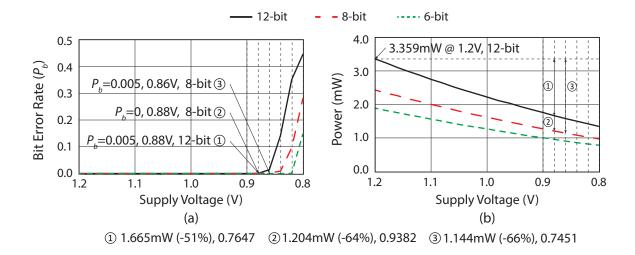

| 7.8  | (a) Bit error rate $(P_b)$ at different supply voltages and precision bit-widths and (b) the corresponding power dissipation. The various options for energy-accuracy trade are shown with selected target $P_b$                                                                                  | . 114 |

| 7.9  | The comparison of empirical CDF of the absolute state error between reduced precision and voltage over scaling (VOS)                                                                                                                                                                              | . 115 |

| 7.10 | Energy-accuracy tradeoff plot using (a) edge detection and (b) hole filling applications                                                                                                                                                                                                          | . 117 |

| 7.11 | The impact of voltage scaling and precision control on output image quality for various applications                                                                                                                                                                                              | . 118 |

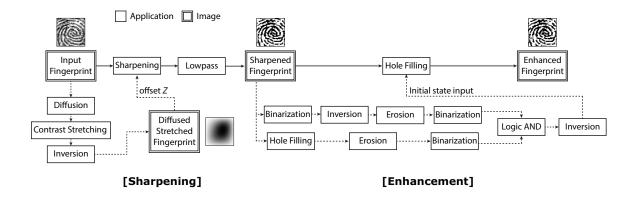

| 7.12 | Overall block diagram of the fingerprint preprocessing application [197], which can be divided into two main algorithms (sharpening and enhancement). Solid lines represent the main flow while dotted lines represent the sub-flow of the application                                            | . 119 |

| 7.13 | Allocation of energy reduction schemes for each algorithm in the finger-print preprocessing application depending on the strength of feedback template $\mathbf{A}.$                                                                                                                              | . 120 |

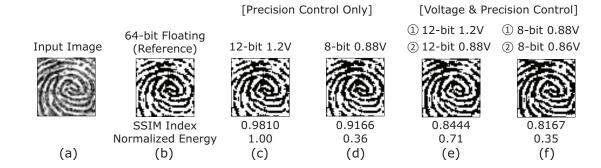

| 7.14 | (a) Input fingerprint image and enhanced fingerprint images with (b) 64-bit floating point representation, (c) 12-bit precision without error, (d) 8-bit precision without error, (e) 12-bit precision with 0.5% bit error, and (f) 8-bit precision with 0.5% bit error                           | . 121 |

| 7.15 | Impact of template truncation on the output quality of CeNN considering the halftoning example: (a) the halftoning templates depending on the precision bit-width, (b) the power versus quality for template and operand truncation, and (c) images comparing SSIM index with template truncation | . 122 |

#### **CHAPTER 1**

#### INTRODUCTION

System learning is the most fundamental research area in the engineering domain. It is a modeling method to map external stimulations (inputs) to the corresponding measurements (outputs) with/without physically analyzing the system between them. Applications of the system learning method are electical circuit analysis (two-port network [1]), acoustic signal processing [2], thermal analysis (power-temperature relation [3]), particle physics [4], aircraft engine analysis [5], neural function characterization [6], to name a few. The system can be simple enough, such as a linear time-invariant system, to be easily identified by a simple mathematical model, i.e. a transfer function or a physical equation. However, it can be a quite complex system, such as a nonlinear dynamic system, which is highly difficult to understand with a mathematical representation. Even further, the presence of noise in the system or in input signals makes the learning process more challenging.

Historically, for some engineering or real-world problems, systems of interest were formulated by a set of mathematical equations; *model-based learning*. A variety of physical, biological, chemical behaviors around us are modeled by differential equations. For instance, heat propagates through a medium described by the well-known Poisson's equation [7]. Biological evolution of a species can be modeled by the reaction-diffusion equation [8]. In the engineering domain, joint movements of bipedal robots [9] or path planning of drones [10] can be modeled by coupled differential equations (DE). The model-based learning is efficient in that there is no need to process large volume of data. Yet, numerical simulation of physical models takes long time to run, e.g. Newtons method, finite element method (FEM), or Runge-Kutta method. Thus, many researchers have presented different reduction methods to simplify the learning of physical models [11, 12].

In many other applications, however, physical understanding of the system is not straight-

forward. For those applications, black box model is utilized for the system learning process. Black box modeling is the method assuming the system as a black box and only utilizes the input and output data from a set of experiments; *data-driven learning*. Neural network is a good substitute in representing that black box. The strength of the neural network comes from the nonlinear activation function (mostly, sigmoid type functions) associated with each neuron in the network. The nonlinear function allows the neural network to express or approximate nonlinear functions [13]. Depending on the type of connections, neural network is able to express a static nonlinear system (feedforward) or a dynamic nonlinear system (both feedforward and recurrent).

There connected portable devices through the network is ever increasing, called Internet of Things (IoT), and they communicate and exchage a bulk of data. The overflowing data are collected from sensors, embedded devices, and personal electronics and they can be processed on-line to understand some unknown systems. Thus, the advantage of neural networks in evaluating those unknown systems related to collected data can be utilized in mobile platforms. Although, application of a neural network as an embedded processing platform has received significant interest [14, 15], low operating power with feasibility of dynamic scaling of energy, performance, and quality-of-result is of critical importance to make it viable as an accelerator in mobile SoCs.

In this thesis, the primary objective is to present the energy-efficient operation of digital hardware to identify a physical system in real-world applications. This is done by first presenting the highly-efficient digital hardware to identify a thermal system of an integrated circuit (IC) where frequency-domain analysis is utilized for the learning process (Chapter 3). This is followed by the design of generic and energy-efficient solver for simulating wide classes of dynamical systems; equivalently, coupled differential equations as a physical model (Chapter 4). To deal with more complex systems, a neural network is selected as the data-driven learning method. The widely-accepted training algorithm of neural networks is being analyzed to develop an energy-efficient hardware platform during

the inference of a target neural network, either feedforward or recurrent (Chapter 5, 6). At last, the algorithmic analysis of the impact of error (hardware induced error for achieving low-power operation) on performance for one class of neural networks, called Cellular Nonlinear Network (CeNN), is performed to achieve better energy-efficiency (Chapter 7). The detailed analysis on this computing model is essential in that it is capable of serving as either model-based or data-driven learning method.

#### **CHAPTER 2**

#### **BACKGROUND ON SYSTEM LEARNING METHODS**

#### 2.1 Model-based Learning

## 2.1.1 Scientific Modeling: Formulation of Dynamical Systems

Scientific modeling is the process of understanding and predicting specific behaviors of objects or systems. The established model is used to develop fundamentals of science for a long time, from physics and chemistry to earth science and social science. As some systems in real life is extremely complex, scientists make many assumptions to simplify the model to ease the analysis. These assumptions may cause inaccurate estimation of the underlying object/system, for instance the classical Bohr's atomic model. Also, a single modeling may not be sufficient to fully describe the system (or the object) of interest. In that case, multiple models can be coupled together to represent the system with better accuracy.

The dynamical system, represented as coupled ordinary/partial differential (continuous time) or difference (discrete time) equations (ODE/PDE), is a scientific model for describing systems varying in time. The solution of dynamical systems is an important computing problem. The scientific simulations, a key driver for high-performance computing, are defined by solution of coupled ODEs/PDEs. There are many real-time control problems such as bipedal robotic walking, UAV path planning, or aircraft control that necessitates real-time ODE/PDE solution for fast actions [9, 16, 17, 18].

More recently, there is a growing interest in computing with dynamical systems, e.g. reaction-diffusion equations or oscillatory networks [19, 20, 21, 22, 23]. The concept of building a Turing complete machine using reaction-diffusion equations has been proposed [20]. The coupled oscillators based dynamical systems are being explored as a platform for solving complex problems [24, 25, 26, 27]. Computing with biophysical neuron with dy-

namics modeled using coupled PDEs is another well-known example of dynamical system based computing [22, 23]. The dynamical system based computing is showing promise in solving complex problems in computer vision, graph theory, optimization, to name a few [22, 23, 26, 27].

# 2.1.2 Hardware Platform for Model-based Learning

There are three major trends in designing hardware platforms for accelerating solution of coupled ODE/PDE to support dynamical system analysis. First, the Graphical Processor Unit (GPU) helps accelerate ODE/PDE solution for scientific computation [28, 29]. The GPU-based platforms provide the advantage of programmability, but in general are more power hungry and less energy-efficient. Second, the FPGA-based coprocessors have also been developed to speed up the computation of conventional numerical analysis methods [30, 31, 32]. However, FPGAs only accelerate the numerical algorithms, do not provide a different computing model. Finally, there is significant effort in exploring ASICs and non-CMOS devices to accelerate specific dynamical systems, for example, simple first/second order equations, oscillatory networks, and spiking systems [22, 23, 25, 26, 27, 33, 34]. The ASIC-based approach provides high energy-efficiency, but lack the capability of solving different types of dynamical systems in a single platform. Likewise, directly using the internal dynamics of a device to build a computing platform does not provide the ability to 'program' a required dynamical behavior.

#### 2.1.3 Computing Model for Simulating Dynamical Systems

A fundamentally different computing model for dynamical system analysis is Cellular Non-linear Network (CeNN) [35]. The CeNN is composed of an array of cells where each cell follows an ODE based dynamics [35]. Each cell in CeNN is connected to (local) neighboring cells resulting in a system of coupled ODEs. The weight of local connections, referred to as the templates, defines the coupling and hence, the nature of the system of the equa-

tions. A multilayer CeNN can realize a system defined by multiple coupled PDEs, where each layer represents the 'first-order' equation. The advantage of CeNN based computation originates from the inherent ODE-based cell dynamics, the high-degree of parallelism, local connectivity, and programmability to solve wide classes of 'system of equations'.

Although the CeNN platform is most widely known for image processing, several past efforts have shown that a multilayer CeNN with linear and nonlinear templates can be used to solve different types of coupled differential equations [36, 37, 38, 39, 40, 41]. There are many studies on how to map a scientific model to CeNN algorithm [38, 39, 41, 42, 43]. Significant research efforts have also been directed to design digital and analog CeNN chips for image processing applications [44, 45, 46, 47]. However, the mapping algorithms developed in prior studies mostly focused on *specific equations* and/or *linear templates*. Likewise, the hardware acclerators were designed for image processing applications with *spatially* and/or *temporally invariant templates*. Therefore, the prior efforts are not sufficient to develop a generic dynamical system simulator with *nonlinear interactions* between equations leading to *space and time variant templates*.

# 2.2 Data-driven Learning

#### 2.2.1 Fundamentals of Neural Networks

A neural network (NN) is an algorithmic approach for statistical learning of unknown complex functions or systems with large dataset. Various types of NN have been developed over last few decades and utilized in a wide range of applications [48, 49, 50, 51, 52]. NNs have high-degree of parallelism providing opportunities for high system performance with large number of simple processing engines (PEs). The hardware engines for the neural network have received attention for embedding in mobile platforms to perform various applications, for example, medical diagnosis [53], mobile robot motion control [54] and vision systems [55].

In general, NN is composed of nodes (i.e. neurons) and directed edges (i.e. synaptic

weights). Each node has activation functions which compute the output of the node with respect to the state of a neuron. This activation function is typically a sigmoid type function or Rectified Linear Unit (ReLU). Depending on the connectivity of neurons, the behavior of the neural network changes significantly (either static or dynamic). In the following subsections, different types of neural networks will be discussed along with their learning algorithms and applications.

#### A) Feedforward Neural Network

Having unidirectional connections between two nodes at different layers, the network is called a feedforward neural network. The most simplest structure of the feedforward NN is a perceptron proposed by Rosenblatt [56]. In Rosenblatt's perceptron, the output of a neuron is computed by the linear sum of inputs followed by the hard limiter (activation function). In general, a feedforward NN is multiple layers of these perceptrons called multilayer perceptron (MLP) [48]. Due to the nonlinearity of each neuron, MLP is suitable for estimating or identifying any *static* nonlinear system [57].

The learning (or training) of a feedforward NN is a challenging optimization problem (parameter and/or structure optimization). There are two methods on training the feedforward NN: 1) iterative gradient descent (backpropagation algorithm) [58, 59, 60, 61] and 2) evolutionary algorithm (e.g. genetic algorithm) [62, 63, 64]. Mostly, the backpropagation algorithm is used for training due to its lower computational complexity compared to the genetic algorithm. However, it normally tends to settle at a local minima while the genetic algorithm is better at finding the global minimum. Since each optimization method has its pros and cons, hybrid training algorithms are proposed as well for better training performance in terms of the accuracy and the complexity [65, 66].

The applications of interest for the feedforward NN are image recognition (or classification) [60, 67, 68] and function approximation [69, 70, 71]. As explained, the feedforward NN is a good candidate for approximating static nonlinear functions (or systems). That is

why it is suitable for classifying images. Basically, the classification problem is equivalent to approximating a nonlinear function that separates the state space into desired number of regions. Thus, for the system learning problem, if a system that we are trying to approximate is desribed by a static nonlinear equation can be identified by utilizing the feedforward NN.

#### B) Recurrent Neural Network

Given a MLP, if there are additional recurrent connections (forming any cycles in the network), the neural network becomes a recurrent neural network (RNN) [51]. Over several decades, various types of recurrent NNs have been proposed depending on where recurrent connections are established. Nonlinear AutoRegressive with eXogenous inputs (NARX) model has only recurrent connections (delayed by arbitrary time steps) from the output to the input layer (no recurrent connections within the network) [13]. If there are recurrent connections from a single hidden layer to the input layer delayed by unit time step, the network is called Simple Recurrent Network (SRN) [72]. The network is known as a Recurrent MultiLayer Perceptron (RMLP) when recurrent connections are from multiple hidden layers to their previous layers [73]. Owing to the recurrent connections in the network, RNN is capable of approximating any *dynamic* nonlinear systems in theory [74].

As can be expected, training RNN is more complicated than that of the feedforward NN due to its learning capaility of temporal information. There are two conventional training algorithms: 1) BackPropagation Through Time (BPTT) [75] and 2) Real-Time Recurrent Learning (RTRL) [76]. The BPTT algorithm is simply the extension of the (standard) backpropagation algorithm in that it unfolds the temporal behavior of RNN to form a layered feedforward NN. The number of layers of the constructed multilayer feedforward NN linearly increases by an additional time step involved in the training. Also, the memory space required to perform BPTT algorithm increases as the length of a training sequence increases [48].

To overcome these limitations, truncated BPTT algorithm has been proposed by Williams and Peng [75]. Another critical problem that BPTT-type algorithms have is vanishing (or exploding) gradient problem pointed out by Bengio [77]. To deal with this concern, Long Short-Term Memory (LSTM) architecture [52] and Hessian-free training method [78] are proposed. These two novel idea shed light on RNN as a promising NN architecture again.

Because of the limited memory space in hardware, BPTT-type algorithms are suitable for off-line training of RNN. For on-line training, RTRL algorithm can be performed which updates the synaptic weights while operating the network [76]. To train RNN in real-time, the RTRL algorithm approximates the gradient of total error with respect to weight changes by an instantaneous estimate of the gradient for each time step [48]. This deviation from the actual gradient can be minimized by reducing the learning rate  $\eta$ , which determines how fast the gradient descent algorithm evolves. However, the computational complexity of the RTRL algorithm is high since it requires the weight update at every time steps.

As explained, RNN is capable of dealing with systems having nonlinear temporal behaviors which depend on external input sequences. There have been extensive studies on applications of the RNN owing to its ability to utilize the history of past inputs or states. They include appproximation of dynamic systems [79, 80, 81], mapping finite state machines [82, 83], language modeling [84, 85], and associative memory [86, 87], to name a few. Since RNN is more general definition of neural network compared to feedforward NN, detailed understanding of its behavior is required for further development. Finding a good application using RNN is still an open problem by many scientists and RNN has a great amount of potential due to the ability to approximate nonlinear systems.

# 2.2.2 Impact of Noise on Neural Networks

Understanding the impact of noise on training and/or operation of feedforward NNs is an important research topic to implement them in hardware [88]. When the given network is prone to error from either connection weights or neuron states, the output accuracy of

the network will degrade significantly by small perturbations. Thus, error tolerant training methods or guidelines to allow well-defined level of noise (not sacrificing accuracy much) have to be studied. Towards this direction, fault-tolerant training methods [89, 90, 91] have been proposed to realize feedforward NN tolerant to errors to some extent. The effects of noise from the synaptic arithmetic unit during neural network training are studied and noise injection training scheme is proposed [89]. Limiting the absolute value of each connection weight during training, when the value exceeds certain threshold, to flatten the distribution of the magitude of weights enhanced the error tolerance of a feedforward NN [90]. In [91], the convergence of fault injection-based training algorithm has been provided.

Apart from the feedforward NN, neural networks with recurrent connections may have stability (or convergence) issues under noise even at the operation of the network. There have been a number of works on providing sufficient conditions for the global stability of various classes of RNNs [92, 93, 94, 95, 96, 97, 98, 99]. It has been shown that a controlled amount of additive errors can improve the convergence and regularization in training RNNs [92]. Recently, the stability condition of RNNs considering transmission delays has been studied [93]. Moreover, the global exponential stability of RNNs considering random noise as well as time delays has been explored [94]. In [94], upper bounds of delays and additive noise for maintaining global exponential stability are mathematically shown. Similar stability criteria studies have been done for other classes of (recurrent) neural networks as well [95, 96, 97, 98, 99]. Many researches have provided the mathematical estimation of the upper limit of connection weight matrices in delayed neural networks (DNNs), which guarantees global stability of DNNs [95, 96, 97]. Most recently, a new criteria for global stability of DNN is shown considering parameter uncertainties on the delayed connection weight matrix [98]. In addition, the stability analysis on Hopfield neural networks (HNNs) with time delays has been done [99].

# 2.2.3 Neuromorphic Hardware

Neuro-inspired architecture is increasingly recognized as a new paradigm since it is capable of dealing with applications that a conventional von Neumann architecture could not solve efficiently. To accelerate NN computations, many research scientists focused on designing neuromorphic hardware accelerators [100, 101, 102, 103, 104, 105, 106, 107]. Specifically, digital implementation of NNs provide the advantage of easier integration, higher scalability (can handle variable input size), and better programmability.

#### A) Digital Implementation of Neuromorphic Hardware

The most efficient feedforward NN in image classification and object recognition is a convolutional neural network (ConvNet) [108, 109]. Naturally, its promising performance in those applications led research on hardware implementation of ConvNet accelerators. A group led by Yann LeCun, a ConvNet pioneer, first demonstrated FPGA-based ConvNet based on parallel filter banks to detect objects in real-time [15, 100]. FPGA demonstration was followed by ASIC design of a ConvNet processor, named NeuFlow, developed by a hardware group at Yale University [101]. The computation in NeuFlow is done by parallel processing units where required data stream is provided by Smart Direct Memory Access (Smart DMA) module.

The dataflow model used in NeuFlow limits its energy efficiency since it requires explicit data transfer between processing units. To lower energy consumption in designing ConvNet, a standalone neuromorphic hardware (DaDianNao) with localized memory banks (eDRAM) for each computing unit is proposed [102]. To compensate memory latency and wire congestion, the proposed architecture has a mesh structure with distributed on-chip memory. Recently, another type of energy-efficient ConvNet engines (Hardware Convolution Engine (HWCE) [103] and Origami [104]) was presented. Both accelerators are streaming-based engines integrated with a shared-memory (shared-L1) cluster of RISC processors. They reduce memory access pattern by making only one pixel value to be

changed during 2D convolution.

Apart from the ConvNet, Researchers at IBM initiated SyNAPSE project to build a brain-like chip which realizes a spiking neural network (SNN) which is known to have the most similar behavior with human brain. Along the way, *neurosynaptic core*, having 256 digital spiking neurons, has been fabricated in 45nm process; here, spiking neurons can have either 0 or 1 as a state value [105]. This neuromorphic chip locally stores and computes the state of each neuron (utilizing crossbar synapses) and each neuron consumes only 45pJ. Most recently, an advanced version of such low-power spiking neural network engine, named *TrueNorth*, was presented [106]. This brain-like chip is composed of 4,096 parallel processors which represents one million spiking neurons [107].

#### B) Approximate Computation in Neuromorphic Hardware

Approximate and accuracy-aware computing has emerged as an attractive approach for low-power neuromorphic hardware by trading-off energy and quality-of-result under performance constraints [110, 111, 112, 113]. The most common way to approximate computation is reducing the bit precision of operands [110, 111, 112]. By carefully forcing some LSBs to zero, effective power saving can be achieved with slight degradation in output quality. Most recently, stochastic rounding during training of ConvNet to effectively reduce the bit precision is proposed [112]. Another method to approximate NN hardware is by implementing approximate multipliers as processing engines [113]. An approximate multiplier is designed with iterative logarithmic multiplier having computation error less than 1%. However, having only approximate PEs is limited in saving power while maintaining the output quality.

Even though there have been some level of research on the impact of approximation in neural computation, most research works only deal with feedforward NNs. Having recurrent connections in the network will show completely different error behavior due to the error propagation in temporal direction. Also, having both reduced precision and

approximate processing units is not evaluated yet. Thus, the impact of hardware-induced error in recurrent-type networks and the approximation methods utilizing both precision control and approximate hardware will be addressed in the thesis.

#### **CHAPTER 3**

# HIGHLY-EFFICIENT MODEL-BASED SYSTEM LEARNING ON INTEGRATED CIRCUITS

For an integrated circuit (IC), thermal behavior of the chip is a critical design factor as scaling of device technology significantly increases the dynamic and leakage power of silicon ICs [114, 115]. Higher power density elevates junction temperature and triggers higher leakage current which leads to thermal runaway. Higher temperature also degrades circuit reliability and performance and increases cooling and packaging cost [116]. The thermal problem becomes more intriguing in multi-core processors due to the thermal coupling between neighboring cores and components [117]. Even if a specific core/component is in a low power mode, its temperature can increase when a neighboring core is in the high-power mode due to thermal coupling. For example, measurements on an AMD Fusion processor executing a compute intensive CPU workload demonstrated up to a 13°C rise in temperature in the adjacent idle CPU and GPU cores [118]. As the workload/power pattern of a processor dynamically changes, so does the effect of the thermal coupling and hence, the junction temperature.

The effective thermal management of multicore processors requires on-line estimation of the full-chip thermal patterns. The design-time thermal modeling methods ([119, 120, 121, 122]), although highly accurate for pre-fabrication analysis, are less effective for on-line analysis. It is in principle difficult for design-time modeling to account for post-fabrication (chip-to-chip and potentially time dependent) variations in leakage power, thermal properties of the package, and workload dependent power patterns [123, 124, 125, 126]. On-chip temperature sensors are used in recent processors to sense runtime temperature changes, but they only provide current temperature at specific locations. Several spatial reconstruction methods on temperature distribution have been proposed [127, 128,

129, 130] that can predict full-chip (spatial) temperature distribution including at locations without sensors but only at a given time. These methods do not estimate transient temperature variations at locations without sensors; therefore, has limited ability to estimate spatiotemporal temperature variations.

# 3.1 Background: Thermal Analysis of ICs

# 3.1.1 Need for Post-silicon Thermal Analysis

The design-time thermal analysis methods do not account for the post-fabrication variations in electrical or thermal properties. For example, leakage power can experience significant variations. Specifically, the process variations affect the leakage power considerably; leakage current varies 23% to 30% on average [123]. This amount of variation is noticeable since the leakage power is more than half of total power consumption in recent technology nodes. Likewise thermal properties of the package components, e.g. heat spreader, heat sink, and thermal interface materials (TIM), are difficult to extract. The extraction of such properties requires complex measurements and characterizations [124]. These properties can also have chip-to-chip or time dependent variations; for example, the properties of interface materials can vary due to the delamination [125] or the quality of interface adhesion [126]. Fig. 3.1 illustrates how the variations in the thermal properties of a chip can change temperature variations including thermal coupling showing the need for post-silicon thermal analysis.

#### 3.1.2 Related Work on Full-chip Temperature Estimation with Limited Number of Sensors

On-chip temperature sensors are placed in developing recent processors to relieve the performance degradation or reliability hazard caused by elevated chip junction temperature [131, 132]. Temperature sensors, however, are limited to providing current temperature at specific locations where the sensors are placed. Moreover, if the sensors were placed at distant locations from actual hotspot due to placement or routing problems, temperature

Figure 3.1: An illustrative simulation result using RC-based thermal simulator [119] of the thermal coupling with variations on thermal conductivity of TIM; (a) an example floorplan used for the simulation, (b) transient temperature of power consuming block A, and (c) that of non-power consuming block B.

readings may be lower than the actual maximum temperature (optimistic).

Several thermal analysis methods have been proposed to reconstruct spatial temperature variations of an IC from limited sensor data [127, 128, 129, 130]. Spatial reconstruction methods are proposed to establish full-chip temperature distribution based on reasonable number of on-chip sensors. Interpolation scheme is used to estimate temperature at locations without sensors [127]. To achieve energy efficiency, only a subset of sensors is activated using a dynamic sensor selection mechanism. For more accurate hotspot temperature estimation, thermal characterization using signal reconstruction techniques has been proposed [128]. This technique uses space-domain filters to characterize spatial distribution of temperature. To deal with uncertainties in real-time power consumption, temperature estimation using a linear estimator, approximating power density as a Gaussian random variable, has been proposed [129]. Also, a runtime temperature estimation method using Kalman filter has been proposed [130]. This work provides methodology dealing with noisy sensor readings and process variations. However, these methods only provide full-chip temperature distribution at a given time [127, 128, 129] or next time step [130] (limited to *reactive* thermal management).

Figure 3.2: The basic concept of Thermal System Identification (TSI) method [3]. The method requires FFT/IFFT computation.

#### 3.1.3 Thermal System Identification (TSI)

A post-silicon thermal analysis methodology - *Thermal System Identification (TSI)* - has been proposed to estimate temperature considering inherent variations after fabrication of the chip [3]. Fig. 3.2 briefly describes the entire process of the TSI method. TSI characterizes the relation between power and temperature of a packaged IC in the frequency domain using on-chip power and temperature measurements. Then, this relation is being used to predict temperature variations in time at one location with a given power pattern using transformation between time and frequency, such as Fast Fourier Transform (FFT). This method enables *proactive* thermal management; future temperature estimates can be utilized in dynamic thermal management (DTM) techniques such as workload allocation in advance.

TSI exploits the well-known analogy between electrical current and heat conduction. By using this analogy, temperature is analogous to voltage, heat flow is analogous to current, thermal conductivity is analogous to electrical conductivity ( $\propto 1/R$ ), and heat capacity is analogous to capacitance (C). This analogy forms the basis of thermal analysis using distributed RC networks [119]. The first-order RC circuit is a simple low-pass filter which

makes it possible to think of a thermal system as a complex low-pass filter. Further, an RC network is a linear system which enables the application of superposition principle.

For a simple understanding of TSI, assume a single point (x, y) on a given chip. Power consumption, P(t), at location (x, y) is also assumed to be given. Temperature increase from ambient temperature,  $\triangle T(t)$ , is then obtained by performing a convolution between power and the impulse response of a thermal system,  $h_T(t)$ . It can be written as

$$\Delta T(t) = h_T(t) * P(t). \tag{3.1}$$

The convolution operation is simply multiplication in the frequency domain. Hence, Fourier Transform of (3.1) becomes

$$\Delta T(\omega) = H_T(\omega) * P(\omega), \tag{3.2}$$

where  $H_T(\omega)$  is the thermal filter response between the power generation and the temperature observation point (one-to-one). Here, TSI can be defined as a method to learn  $H_T(\omega)$  in the relation of (3.2). TSI exploits the presence of on-chip temperature sensors at various locations of a chip. Essentially one can apply a periodic power pattern with varying frequency and estimate the associated temperature variation from the sensors at different locations. The measured results can be used to construct the amplitude and phase response of thermal filters between the locations of power dissipation to the locations of temperature sensors.

The method presented in this thesis advances the state-of-the-art of post-silicon thermal analysis over the prior work. First, unlike the prior work, in this thesis, the MIMO thermal filters that consider multiple power sources and multiple temperature sensors were considered and experimentally verified. The experimental verification of the MIMO filter makes TSI more applicable for multi-core processors with thermal coupling between different components (power sources, e.g. cores). The experimental verifications are performed us-

ing a 130nm test chip that emulates arbitrary power (and hence, thermal) patterns. Second, the prior work only presented the ability to estimate transient temperature variations at the specific sensor locations. The work reported here overcomes this limitation and developed methods to predict temporal variation in temperature even at locations without sensors.

#### 3.2 MIMO Thermal Filter

# 3.2.1 Superposition Principle

The power consumption of each functional block generates a certain amount of heat on a silicon die. The heat is naturally being conducted via silicon substrate. This physical phenomenon of generated heat is well described by the Fourier's heat conduction equation, which is

$$\rho C_p \frac{dT(\vec{r}, t)}{dt} = \kappa \nabla^2 T(\vec{r}, t) + p(\vec{r}, t). \tag{3.3}$$

where  $\rho$ ,  $C_p$ , and  $\kappa$  are material properties,  $\vec{r}$  is the location of interest, and t is time.  $\vec{r}$  could be (x,y) or (x,y,z) depending on the dimension of heat conduction. Here,  $T(\vec{r},t)$  is temperature and  $p(\vec{r},t)$  is power density at  $\vec{r}$ .

Among several approaches solving (3.3), the Green's function approach well describes the temperature change at  $\vec{r}$  with respect to power sources at different locations,  $\vec{r_j} = (\vec{r} - \vec{r_j'})$  [133]. Using the Green's function, temperature at  $\vec{r}$  can be computed by

$$T(\vec{r},t) = \iint g(\|\vec{r'}\|, f_0) \cdot p(\vec{r} - \vec{r'}, t) \cdot \vec{r'} dr' d\theta'$$

(3.4)

where  $g(\|\vec{r'}\|, f_0)$  is the Green's function which is a function of distance  $\|\vec{r'}\|$  and the frequency  $f_0$  of the power source. Consider two power sources  $p_1(\vec{r} - \vec{r'_1}, t)$  and  $p_2(\vec{r} - \vec{r'_2}, t)$  on the chip (Fig. 3.3(a)). Computation of (3.4) assuming there exists one power source gives us the temperature increase due to that heat energy as depicted in Fig. 3.3(b) and (c). Since the integral is a linear operator in (3.4), actual  $T(\vec{r}, t)$  can be computed by adding

Figure 3.3: Superposition of heat energy from two power sources at a certain temperature observation point.

Table 3.1: Verification of the superposition principle by using the RC-based thermal simulator [119]

| On  | T↑ at A | On  | T↑ at B        | On  | T↑ at C        |

|-----|---------|-----|----------------|-----|----------------|

| В   | 8.63°C  | A   | 2.84°C         | A   | 1.31°C         |

| С   | 1.10°C  | С   | 1.07°C         | В   | 3.89° <b>C</b> |

| B,C | 9.77°C  | A,C | 3.94° <b>C</b> | A,B | 5.23°C         |

each temperature result;  $T_1(\vec{r},t)$  and  $T_2(\vec{r},t)$ . This simple example gives us the insight of the superposition principle of the heat conduction.

The superposition principle is being verified by using a RC-based thermal simulator with a simple example [119]. The same floorplan is used as shown in Fig. 3.3(a). Assume each block consumes 2.44W (A), 7.37W (B), and 3.07W (C). These numbers are merely random power numbers. Two functional blocks (B and C) are turned on and temperature is observed at the remaining block (A). It is compared with the temperature estimate, which is the addition of temperature increase when each functional block (B or C) is turned on in isolation. Table 3.1 shows the simulation results and it verifies the superposition principle very well. The first two rows represent the temperature increase at a certain location when one functional block is operating. The last row represents the temperature rise due to the operation of two functional blocks. Additive increase of the first two temperatures is about the same as the temperature increase in the last row.

Figure 3.4: (a) A simple floorplan example with multiple power sources and temperature sensors and (b) the corresponding matrix equation of the MIMO thermal filter.

#### 3.2.2 Definition of MIMO Thermal Filter

On the basis of the superposition principle, a MIMO thermal filter can be extracted and utilized in estimating spatiotemporal temperature variations. Each thermal filter response  $(H_{ij}(\omega))$  equivalent to  $H_T(\omega)$  in (3.2)) between one power source and a sensor location at a given frequency  $\omega_k$  can be extracted by

$$H_{ij}(\omega_k) = \Delta T_i(\omega_k) / P_j(\omega_k),$$

(3.5)

where i is the sensor index, j is the power source index, and k is the frequency index. Recall that a sine- or square-wave power pattern with a fixed frequency  $\omega_k$  is applied during the thermal filter characterization step. Assume there are three power sources (A, B, and C) and three temperature sensors (1, 2, and 3) on the chip (Fig. 3.4(a)). In this case, nine different thermal filter responses should be extracted to establish MIMO thermal filter.

By the superposition principle, temperature at one location can be estimated by summing temperature changes due to multiple power sources. Thus, temperature increase at sensor i when the fundamental frequency of a power source is  $\omega_k$  becomes

$$\Delta T_i(\omega_k) = \sum_{j \in \{A, B, C\}} H_{ij}(\omega_k) \cdot P_j(\omega_k). \tag{3.6}$$

Figure 3.5: The die photo of the test chip; five digitally controllable heaters, five digital sensors, and SPI registers [134].

Then, the relation between power and temperature can be written in a 3-dimensional matrix equation:

$$\Delta \mathbf{T}(\omega) = \mathbf{H}_{\mathbf{T}}(\omega) \cdot \mathbf{P}(\omega), \tag{3.7}$$