# INTEGRATED, DYNAMICALLY ADAPTIVE SUPPLIES FOR LINEAR RF POWER AMPLIFIERS IN PORTABLE APPLICATIONS

A Dissertation Presented to The Academic Faculty

By

Biranchinath Sahu

In Partial Fulfillment

Of the Requirements for the Degree

Doctor of Philosophy in Electrical and Computer Engineering

Georgia Institute of Technology November 2004

Copyright © 2004 by Biranchinath Sahu

# INTEGRATED, DYNAMICALLY ADAPTIVE SUPPLIES FOR LINEAR RF POWER AMPLIFIERS IN PORTABLE APPLICATIONS

# APPROVED:

Prof. Gabriel A. Rincón-Mora, Chairman

Prof. Phillip E. Allen

Prof. J. Stevenson Kenney

Prof. W. Marshall Leach

Prof. Paul A. Kohl

Date Approved: November 4, 2004

### **PREFACE**

This research focuses on the design and development of a high-efficiency linear radio frequency (RF) power amplifier (PA) with a dynamically adaptive power supply and bias current control targeted for state-of-the-art and next generation, highperformance wireless handsets. The use of spectrally efficient modulation schemes, e.g., code-division-multiple-access (CDMA) and wide-band CDMA (WCDMA) has resulted in challenging requirements of a highly linear PA while maximizing its efficiency over a wide loading range for longer battery life. In this work, an integrated circuit primarily consisting of a noninverting, dynamic, buck-boost converter is conceived and experimentally verified. The approach adopted is to develop circuit techniques that allow use of a low-cost, complementary metal-oxide-semiconductor (CMOS) process while ensuring the design to be operational in a low voltage environment permitted by the threshold voltages of transistors. The functionality of the overall system is verified over a wide range of input supply voltage 1.4 - 4.2 V, which enables the design to be useful over a wide spectrum of portable power sources, e.g., single cell Li-ion battery, double cell nickel cadmium (NiCd) and nickel metal hydride (NiMH) batteries, and the promising alternative of direct-methanol fuel cell (DMFC). The dissertation is organized as a logical sequence of efforts that has gone into the design and development of the linear, efficient RF PA system with dynamically adaptive supply and bias current control.

Chapter 1 introduces the role of portable power management in modern handheld devices and the importance of highly efficient linear RF PAs. The requirements imposed by wireless standards are briefly discussed, which is followed by introduction of various linearity and efficiency specifications pertinent to PA design. The characteristic of portable power sources, rechargeable batteries and DMFC are described in this section.

Various power supply circuits used in portable devices are introduced and compared. Lastly, the chapter concludes by identifying and defining the research objective.

Chapter 2 discusses various PA circuit topologies highlighting their efficiency and linearity aspects. State-of-the-art linearization and efficiency enhancement techniques are critically analyzed pertaining to their suitability for handheld applications, where circuit complexity and low-cost are of prime importance. A comparative evaluation of the linearization and efficiency-enhancement methods is offered. A novel, power-tracking PA with both supply voltage and bias current control is developed and its characteristics are analyzed. The use of buck-boost converter for supply voltage control is adopted to maximize the battery voltage range.

In Chapter 3, various switching regulator topologies suitable for both step-up and -down conversion have been analyzed and compared. Because of its suitability towards IC implementation with minimal number of external components, the single inductor non-inverting buck-boost converter was selected as the adaptive power supply for the PA. The buck-boost converter was analyzed and various system design considerations are offered in this chapter. An intuitive, non-mathematical procedure for deriving small-signal models of the converter is also described, which can be readily extended to other converter topologies. Analysis of converter transfer function for various loading conditions and converter power loss analysis have also been derived in this chapter.

Chapter 4 deals with prototype implementation and experimental verification of the power-tracking PA system developed at the end of Chapter 2. The primary goal of prototyping is to verify the system functionality and subsequently identify potential improvements, which are addressed and implemented in the IC solution. The design details and experimental results of the noninverting buck-boost converter discussed in Chapter 3 are presented in this chapter. Experimental results of a CDMA PA with a power-tracking buck-boost power supply operating at 915 MHz center frequency and 27 dBm peak output power is offered.

Chapter 5 brings about the concepts and extensions made to the basic buck-boost converter to achieve high efficiency over wide loading conditions. The modified buck-boost converter operating in pulse-width modulation (PWM) mode is discussed. An

adaptive on time based pulse-frequency modulation (PFM) mode converter operating in discontinuous conduction-mode (DCM) suitable for maintaining high efficiency during light-loading conditions is presented. Overall, by operating the converter in dual-mode, not only higher system efficiency is maintained throughout the PA loading range but also the controller's quiescent power dissipation is lowered, which improves the PA's standby performance. The concept of spread-spectrum clocking used for reducing the peak-value of switching noise in a buck-boost converter and its implication on CDMA-based wireless systems is discussed.

Based on the conclusions of prototype implementation and subsequent circuit improvements developed in Chapter 5, the details of power management system design and circuit blocks of the buck-boost converter are discussed in Chapter 6. A top-down design approach is followed for deriving specifications for the individual building blocks from the top-level system requirements. The circuit blocks whose design, implementation and experimental results offered are: error amplifier op-amp, PWM and PFM comparators, triangular waveform generator, bandgap reference, supply voltage adaptive on time generation for PFM, and dynamic gate/base bias for the RF PA.

Chapter 7 details the system the experimental evaluation of the adaptive supply IC and WCDMA PA system. The buck-boost converter IC was tested individually for its performance specifications. Later, the IC is used as an adaptive supply for a discrete HBT PA and overall system was tested with a 1.96 GHz HPSK modulated signal with 3.84 MHz bandwidth, as specified by the WCDMA standard. Finally, a summary of the performance specifications of the system as well as those targeted are discussed and illustrated in a table.

Chapter 8 provides a summary of the research presented in the dissertation and conclusions derived thereof. The concepts developed and adopted in the design of the integrated power management system are discussed. The implications of the research on the current and future market demand of linear RF PAs and development of their power management systems is highlighted. The chapter ends with recommendations for future work in this area, addressing the issues of calibration and integration with the transceiver system in a real-word application platform.

## **ACKNOWLEDGMENTS**

I express my deepest sense of gratitude and thanks to Prof. Gabriel A. Rincón-Mora for allowing me to work with him for my Ph.D. dissertation. His advice, suggestions, and encouragement throughout my doctoral research have been a lifetime learning opportunity and experience. The energy and enthusiasm he infuses during each and every discussion over the entire program has been instrumental in successful completion of this dissertation. His insightful and thought-provoking comments in every possible opportunity have been immensely helpful, not only for the graduate experience, but will also be of tremendous help in my future endeavors. The fine art of intuitive analysis and design of analog integrated circuits from a system perspective that I learned over the years working with Prof. Rincón-Mora is the hallmark of my graduate education at Georgia Tech.

In the same token, I am grateful to Prof. Phillip E. Allen for his timely help, support and recommendations, without which this dissertation would perhaps have never been realized. His time and effort in serving in my qualifier, proposal, and dissertation reading and defense committees is greatly appreciated. My thanks to Professors J.S. Kenney, G.T. Zhou, W.M. Leach, and Paul A. Kohl for serving at various stages of proposal, dissertation reading, and defense committees. I am obliged to Prof. J. A. Connelly, Prof. W.M. Leach, Prof. A. Chatterjee, Prof. J. Cressler and others whose classes have helped me to garner an ever-lasting invaluable wealth of knowledge.

The stimulating research environment in the Georgia Tech Analog and Power IC Design Laboratory is definitely worth mentioning. The useful discussions, debates, arguments, and disagreements starting from research, life-styles to world politics during any time of the day have been simply superb, and I take this opportunity to thank my

fellow colleagues for enriching my graduate school experience at Georgia Tech. The association with Georgia Tech Analog Consortium has not only helped to broaden my analog integrated circuit exposure, but it also provided a platform for reaching out to the other frontiers of analog and RF technology. The help of Margaret H. Boehme, our administrative support, during my graduate research is gratefully acknowledged. Graduate school without friends is always devoid of an important facet of life. All of those whom I met inside and outside the Georgia Tech campus, inside and outside the work environment, deserve a special mention for their generous and brave smiling faces in spite of many different obstacles, which inspired me to march towards a goal, which once the famous Robert Frost termed as "Miles to go before I sleep."

This place is not enough to mention names of all the people who have contributed financially or morally to my graduate program endeavor at Georgia Tech. The support of Siddhartha, Basuri, Pinak, and Prasant are especially appreciated. All of my roommates during the graduate study have been very friendly and supportive, which made the out-of-school life extremely enjoyable. Amongst all, my sincere thanks to Kapil for his willingness, time and effort to reach out to others whenever there was a need.

Above all, the program would not have been successful without the support and encouragement of my family members and friends. All the credits for whatever I have accomplished professionally goes to my elder brother for his never-ending moral support, insurmountable belief in my abilities, and constantly keeping me motivated and focused. My parents have been a source of inspiration and pillar of strength and wisdom throughout my career for their unimaginable guts, modern outlook and confidence in my abilities, not to mention with their very limited opportunity to interact with the world of the 21<sup>st</sup> century. At the same token, I wish to thank all the other family members whose prayers and blessings have always helped me overcome many hurdles during the course of graduate research.

# **TABLE OF CONTENTS**

| Pref    | face                                                         | iv    |

|---------|--------------------------------------------------------------|-------|

| Ack     | nowledgments                                                 | vii   |

| List    | of Tables                                                    | xvi   |

| List    | of Figures                                                   | xix   |

| Glos    | ssary                                                        | xxxi  |

| Summary |                                                              | xxxiv |

| I       | Introduction                                                 | 1     |

|         | 1.1 Role of Efficient Linear RF Power Amplifiers in Portable | 2     |

|         | Applications                                                 | _     |

|         | 1.2 Role of Portable Power Management                        | 4     |

|         | 1.3 Wireless System Considerations                           | 7     |

|         | 1.3.1 High Peak-to-Average Ratio                             | 7     |

|         | 1.3.2 Power Control                                          | 9     |

|         | 1.4 RF PA Performance Specifications                         | 10    |

|         | 1.4.1 Linearity                                              | 10    |

|         | 1.4.2 Efficiency                                             | 14    |

|         | 1.5 Portable Power Sources                                   | 15    |

|         | 1.5.1 Rechargeable Batteries                                 | 16    |

|         | 1.5.2 Micro Fuel Cells                                       | 17    |

|         |                                                              |       |

|    | 1.6 Introduction to Dynamically Adaptive Power Supplies          | 18 |

|----|------------------------------------------------------------------|----|

|    | 1.6.1 Power Supply Specifications                                | 19 |

|    | 1.6.2 Power Supply Circuit Classification                        | 21 |

|    | 1.6.3 Efficiency and Bandwidth Perspective in Adaptive Switching | 26 |

|    | Regulators                                                       |    |

|    | 1.7 Research Objective                                           | 28 |

|    | 1.8 Summary                                                      | 31 |

| •• |                                                                  |    |

| II | Efficient Linear RF Power Amplifier Design                       | 32 |

|    | 2.1 RF PA Topologies                                             | 33 |

|    | 2.2 Linearization Techniques of RF PAs                           | 37 |

|    | 2.2.1 Direct Feedback                                            | 38 |

|    | 2.2.2 Envelope Feedback                                          | 38 |

|    | 2.2.3 Polar Loop Feedback                                        | 39 |

|    | 2.2.4 Cartesian Feedback Loop                                    | 40 |

|    | 2.2.5 Predistortion                                              | 41 |

|    | 2.2.6 Feedforward System                                         | 43 |

|    | 2.2.7 Linear Amplifications with Nonlinear Components            | 44 |

|    | 2.2.8 Envelope Elimination and Restoration (EER)                 | 45 |

|    | 2.2.9 Comparative Evaluation of PA Linearization Techniques      | 46 |

|    | 2.3 Efficiency Enhancement Techniques                            | 48 |

|    | 2.3.1 Doherty Amplifier                                          | 48 |

|    | 2.3.2 Envelope Enhancement of Linear Power Amplifiers            | 48 |

|    | 2.3.3 Comparative Evaluation of Efficiency Enhancement           | 50 |

|    | Techniques                                                       |    |

|    | 2.4 Proposed Power-Tracking, Dual-Bias Controlled Linear RF PA   | 51 |

|   | 2.4.1 System Description                                         | 52 |

|---|------------------------------------------------------------------|----|

|   | 2.4.2 Efficiency Enhancement Analysis                            | 54 |

|   | 2.4.3 Effect of Supply Voltage and Bias Current Adjustment on PA | 58 |

|   | 2.4.4 Effect of Power Supply Ripple                              | 60 |

|   | 2.4.5 Effect of Power Supply Transient Response                  | 68 |

|   | 2.5 Summary                                                      | 69 |

| Ш | Dynamically Adaptive Buck-Boost Power Supply                     | 70 |

|   | 3.1 Regulator Topologies                                         | 71 |

|   | 3.1.1 Flyback Converters                                         | 71 |

|   | 3.1.2 Boost/Linear Regulator Combination                         | 72 |

|   | 3.1.3 Inverting Buck-Boost Converter                             | 73 |

|   | 3.1.4 Cuk Converter                                              | 74 |

|   | 3.1.5 Single-Ended-Primary-Inductance Converter                  | 75 |

|   | 3.1.6 Noninverting Buck-Boost Converter                          | 76 |

|   | 3.2 Noninverting, Synchronous Buck-Boost Converter               | 77 |

|   | 3.2.1 Circuit Topology and Operation                             | 77 |

|   | 3.2.2 Steady-State Analysis                                      | 80 |

|   | 3.2.3 Implications of Dynamic Output Voltage                     | 82 |

|   | 3.3 Small-Signal Modeling and Analysis                           | 84 |

|   | 3.3.1 Small-Signal Model with Respect to Duty Cycle              | 84 |

|   | 3.3.2 Small-Signal Model with Respect to Line (Input) Voltage    | 86 |

|   | Change                                                           |    |

|   | 3.3.3 Transfer Function Analyses under Different Loads           | 88 |

|   | 3.4 Power Stage Design                                           | 89 |

|   | 3.4.1 Selection of Power Inductor                                | 89 |

|   | 3.4.2 Selection of Output Capacitor                              | 91 |

|   | 3.4.3 Selection of Input Capacitor                               | 92 |

|   | 3.5 Control Loop Design                                          | 92 |

|              | 3.5.1 Control Scheme and Frequency Compensation                 | 92  |

|--------------|-----------------------------------------------------------------|-----|

|              | 3.5.2 Duty Cycle Limiting                                       | 95  |

|              | 3.5.3 Dead-time Control                                         | 97  |

|              | 3.5.4 Start-up Circuit                                          | 98  |

|              | 3.6 Buck-Boost Converter Power Losses                           | 98  |

|              | 3.7 Summary                                                     | 100 |

| IV           | Prototype CDMA RF PA with a Power-Tracking, Dynamically         | 102 |

|              | Adaptive Buck-Boost Supply                                      |     |

|              | 4.1 System Implementation                                       | 103 |

|              | 4.2 Noninverting Buck-Boost Converter Design                    | 104 |

|              | 4.2.1 Specifications                                            | 104 |

|              | 4.2.2 Implementation                                            | 106 |

|              | 4.3 Experimental Results – Prototype Buck-Boost Supply          | 111 |

|              | 4.4 Experimental Results – Prototype CDMA PA System             | 118 |

|              | 4.5 Summary                                                     | 126 |

| $\mathbf{V}$ | High-Performance, Buck-Boost Adaptive Supply                    | 128 |

|              | 5.1 PWM Control with Buck, Buck-Boost, and Boost Mode Operation | 129 |

|              | 5.1.1 Motivation                                                | 129 |

|              | 5.1.2 Control Scheme and Operation                              | 130 |

|              | 5.2 Implications of Low Supply Voltage                          | 134 |

|              | 5.3 PFM Control with Adaptive On-Time Control                   | 139 |

|              | 5.3.1 Motivation                                                | 139 |

|              | 5.3.2 Operation and Control Scheme                              | 140 |

|              | 5.3.3 Design Equations                                          | 143 |

|              | 5.3.4 Adaptive On-Time Control                                  | 145 |

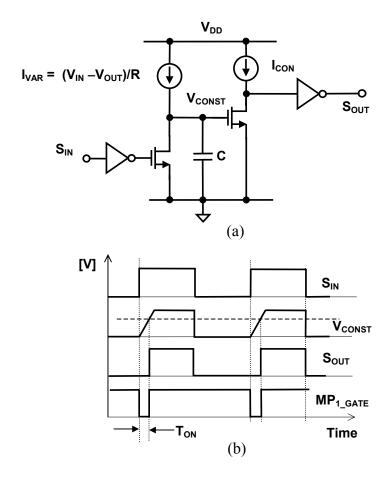

|    | 5.3.5 Asynchronous Versus Synchronous Switching in PFM         | 147 |

|----|----------------------------------------------------------------|-----|

|    | 5.4 Advanced Dead-Time Control Schemes                         | 149 |

|    | 5.4.1 Motivation                                               | 149 |

|    | 5.4.2 Adaptive Dead-Time Control                               | 149 |

|    | 5.4.3 Predictive Dead-Time Control                             | 152 |

|    | 5.5 Switching Noise Reduction Using Spread-Spectrum Clocking   | 153 |

|    | 5.6 Summary                                                    | 154 |

| VI | Integrated Circuit Design                                      | 156 |

|    | 6.1 Linear RF PA Power Management System                       | 157 |

|    | 6.1.1 The System                                               | 157 |

|    | 6.1.2 Adaptive Power Supply Design Considerations              | 158 |

|    | 6.1.3 Calibration Requirement and Alternate Control Strategies | 162 |

|    | 6.2 Dynamically Adaptive Buck-Boost Supply System Design       | 164 |

|    | 6.2.1 System Specifications                                    | 164 |

|    | 6.2.2 Power Stage Design                                       | 165 |

|    | 6.2.3 PWM Control Loop Design                                  | 167 |

|    | 6.2.4 PFM Controller Design                                    | 173 |

|    | 6.3 Power Transistor and Gate Drive Circuit Design             | 175 |

|    | 6.3.1 Design Considerations                                    | 175 |

|    | 6.3.2 Integrated Circuit Design                                | 178 |

|    | 6.4 Error Amplifier Op-amp                                     | 182 |

|    | 6.4.1 Topologies                                               | 182 |

|    | 6.4.2 Slow-Start Circuit                                       | 185 |

|    | 6.4.3 Integrated Circuit Design                                | 186 |

|    | 6.4.4 Simulation and Experimental Results                      | 189 |

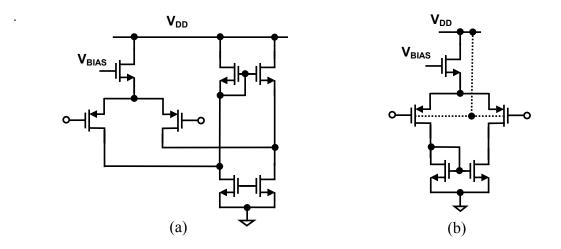

| 6.5 PWM Comparator                         | 190 |

|--------------------------------------------|-----|

| 6.5.1 Circuit Topology                     | 190 |

| 6.5.2 Integrated Circuit Design            | 190 |

| 6.5.3 Simulation and Experimental Results  | 193 |

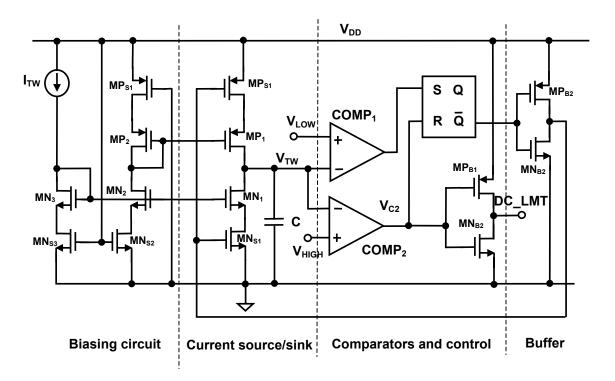

| 6.6 Triangular-Wave Generator              | 194 |

| 6.6.1 Circuit Topology                     | 194 |

| 6.6.2 Integrated Circuit Design            | 195 |

| 6.6.3 Simulation and Experimental Results  | 196 |

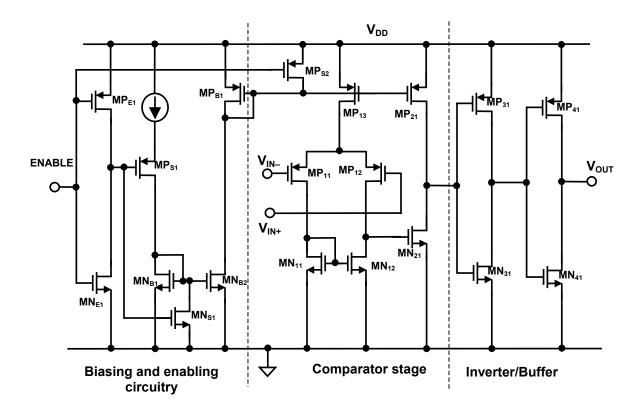

| 6.7 PFM Comparator                         |     |

| 6.7.1 Circuit Topology                     | 197 |

| 6.7.2 Integrated Circuit Design            | 198 |

| 6.7.3 Simulation and Experimental Results  | 200 |

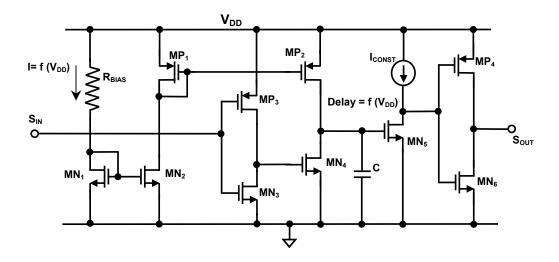

| 6.8 Variable Delay Generator for PFM       |     |

| 6.8.1 Integrated Circuit Design            | 201 |

| 6.8.2 Simulation and Experimental Results  | 203 |

| 6.9 Bandgap Reference Circuit              | 203 |

| 6.9.1 Circuit Topology                     | 203 |

| 6.9.2 Integrated Circuit Design            | 205 |

| 6.9.3 Simulation and Experimental Results  | 207 |

| 6.10 PA Dynamic Gate/Base Bias Circuit     | 211 |

| 6.10.1 Circuit Topology                    | 211 |

| 6.10.2 Integrated Circuit Design           | 212 |

| 6.10.3 Simulation and Experimental Results | 214 |

| 6.11 Summary                               | 216 |

| VII   | Integrated Buck-Boost Supply and Efficient WCDMA RF PA System | 218 |

|-------|---------------------------------------------------------------|-----|

|       | 7.1 Integrated Buck-Boost Supply                              | 218 |

|       | 7.2 Chip Layout                                               | 222 |

|       | 7.3 Experimental Results of the Integrated System             | 224 |

|       | 7.3.1 PFM Mode                                                | 227 |

|       | 7.3.2 PWM Mode                                                | 234 |

|       | 7.4 WCDMA RF PA System                                        | 243 |

|       | 7.5 PA System Experimental Results                            | 245 |

|       | 7.6 Battery Life Improvement                                  | 253 |

|       | 7.7 Summary                                                   | 259 |

| VIII  | Conclusions                                                   | 261 |

|       | 8.1 Challenges                                                | 262 |

|       | 8.2 Original Research Contributions                           | 263 |

|       | 8.3 Future Work                                               | 267 |

|       | 8.4 Summary                                                   | 270 |

| Appe  | ndix I                                                        | 272 |

| Appe  | ndix II                                                       | 274 |

| Refer | rences                                                        | 276 |

| Vita  | Vita                                                          |     |

# LIST OF TABLES

| Гable |                                                                                                        | Page No |

|-------|--------------------------------------------------------------------------------------------------------|---------|

| 1.1.  | Comparison of energy densities of rechargeable batteries [20].                                         | 17      |

| 1.2.  | Comparative evaluation of basic power-supply circuits.                                                 | 26      |

| 1.3.  | Summary of trade-offs involved in designing wide-bandwidth and high-efficiency switching converters.   | 28      |

| 1.4.  | Key specifications of CDMA IS-95 and WCDMA power amplifiers in portable handsets.                      | 30      |

| 2.1.  | Summary of RF PA classification and characteristic based on their operation.                           | 36      |

| 2.2.  | Efficiency comparison of Class A and B PAs for single-tone and variable envelope signal amplification. | 37      |

| 2.3.  | Comparative evaluation of the PA linearization schemes.                                                | 47      |

| 2.4.  | Comparative evaluation of the PA efficiency enhancement schemes.                                       | 51      |

| 3.1.  | Comparative evaluation of regulator topologies suitable for noninverting buck-boost conversion.        | 77      |

| 3.2.  | Small-signal transfer function parameters of the non-inverting buck-boost converter.                   | 88      |

| 3.3.  | Summary of power losses in the buck-boost converter.                                                   | 100     |

| 4.1.  | Prototype buck-boost converter specifications.                                                         | 105     |

| 4.2.  | Experimental results of the prototype buck-boost converter.                                            | 117     |

| 4.3.  | Comparison of the proposed and reported efficiency enhancement schemes.                                            | 125 |

|-------|--------------------------------------------------------------------------------------------------------------------|-----|

| 6.1   | Gain calibration and dynamic converter's accuracy and transient response requirements for various control schemes. | 163 |

| 6.2.  | Integrated, dynamically adaptive buck-boost supply's specifications in PWM and PFM mode.                           | 165 |

| 6.3.  | Simulation results of the power transistors' switch on-resistance.                                                 | 180 |

| 6.4.  | Simulation and measurement results of the drive stage's propagation delays.                                        | 181 |

| 6.5.  | Component parameters of the designed error amplifier.                                                              | 187 |

| 6.6.  | Simulation and experimental results of the error amplifier op-amp.                                                 | 189 |

| 6.7.  | Component parameters of the two-stage comparator.                                                                  | 191 |

| 6.8.  | PWM comparator's simulation and experimental results summary.                                                      | 193 |

| 6.9.  | Component parameters of the triangular wave generator.                                                             | 196 |

| 6.10. | Summary of the simulated and experimental results of the triangular wave generator.                                | 197 |

| 6.11. | PFM comparator's component parameters.                                                                             | 200 |

| 6.12. | Summary of the PFM comparator's simulation and experimental results.                                               | 201 |

| 6.13. | Component parameters of the bandgap reference circuit.                                                             | 207 |

| 6.14. | Simulation and experimental results summary of the bandgap reference.                                              | 211 |

| 6.15. | Component parameters of the dynamic bias circuit.                                                                  | 213 |

| 6.16. | Summary of simulation and experimental results of the PA dynamic bias generation circuit.                          | 216 |

| 7.1.  | Pin description of the buck-boost converter and bias control chip.                                                 | 226 |

| 7.2   | Experimental buck-boost converter's PFM mode results summary                                                       | 234 |

| 7.3. | Summary of the integrated buck-boost converter's experimental results.                        | 242 |

|------|-----------------------------------------------------------------------------------------------|-----|

| 7.4. | Comparison of the proposed and reported efficiency enhancement scheme using dynamic supplies. | 253 |

| 7.5. | Comparison of the average efficiencies of alternate control schemes.                          | 254 |

| 8.1. | Summary of original research contributions.                                                   | 268 |

# LIST OF FIGURES

| Figure |                                                                                                                       | Page No |

|--------|-----------------------------------------------------------------------------------------------------------------------|---------|

| 1.1.   | Block-level representation of a typical wireless handset transmitter section with a digital modulation scheme.        | 3       |

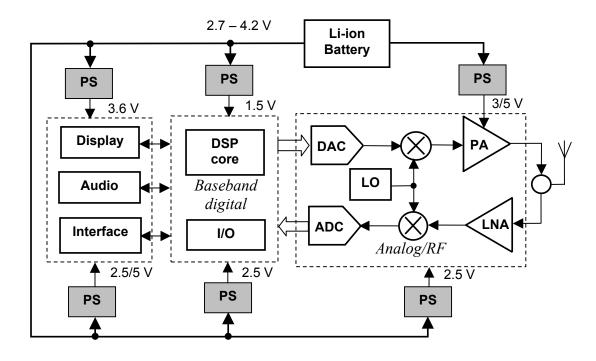

| 1.2.   | Block diagram representation of various power supply units in a wireless handset [7].                                 | 6       |

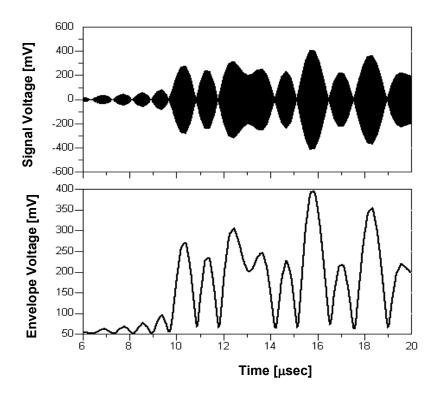

| 1.3.   | Time domain CDMA waveform and its envelope, illustrating high peak-to-average-ratio characteristics.                  | 8       |

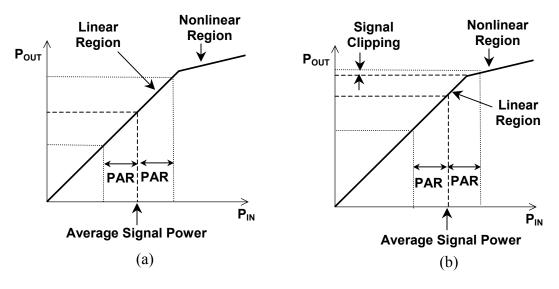

| 1.4.   | Illustration of the peak-to-average signal implication on the PA (a) linear operation, (b) operation with clipping.   | 8       |

| 1.5.   | Probability curves for transmit power level in urban and suburban environments [3], [12].                             | 10      |

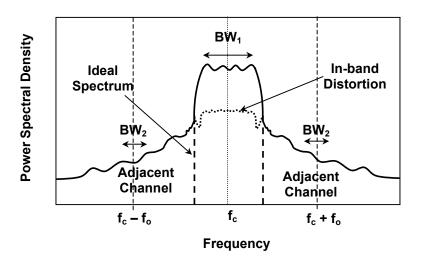

| 1.6.   | Spectrum of the ideal transmitted modulated signal and the distorted signal illustrating ACPR and in-band distortion. | 11      |

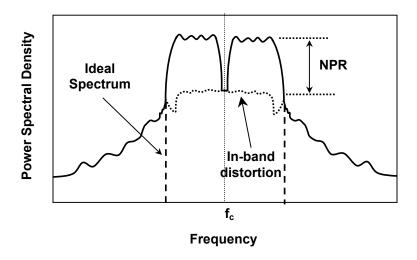

| 1.7.   | Illustration of noise power ratio of an RF PA because of in-band signal distortion.                                   | 12      |

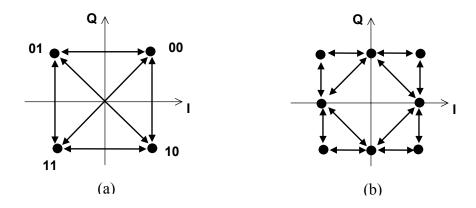

| 1.8.   | Constellation (state) diagram of (a) QPSK, and (b) OQPSK modulation schemes.                                          | 13      |

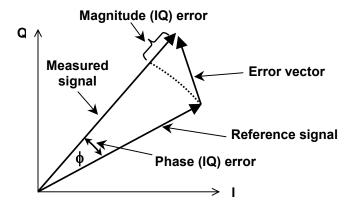

| 1.9.   | Illustration of error vector magnitude (EVM) and related quantities.                                                  | 13      |

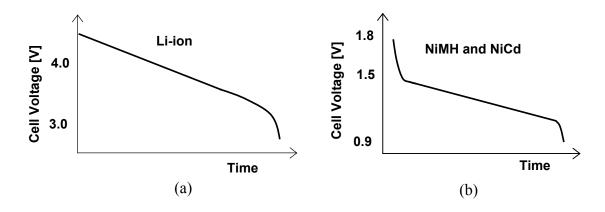

| 1.10.  | Approximate discharge characteristics of (a) Li-ion and (b) NiMH and NiCd batteries [20].                             | 16      |

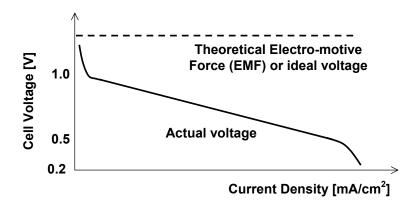

| 1.11.  | Ideal and actual fuel cell voltage/current characteristic [21].                                                       | 18      |

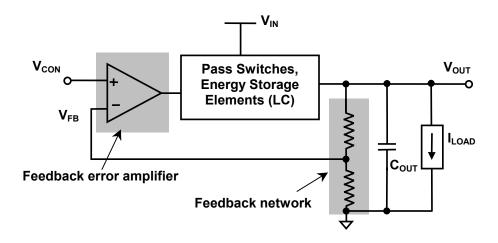

| 1.12. | Schematic of a generic power supply circuit.                                                                                      | 19 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|----|

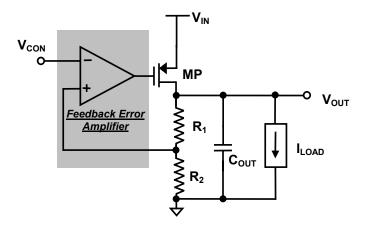

| 1.13. | Schematic of a linear regulator.                                                                                                  | 22 |

| 1.14. | Schematic of a step-down switching regulator with a simplified feedback control circuit.                                          | 23 |

| 1.15. | Schematic of a switched-capacitor voltage doubler and its respective control circuit.                                             | 25 |

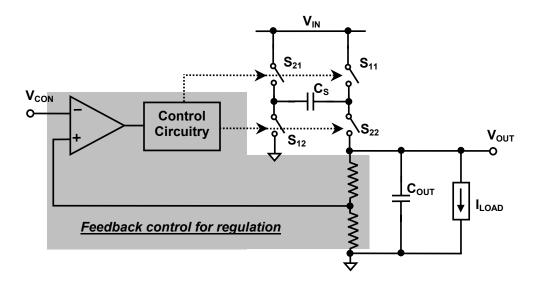

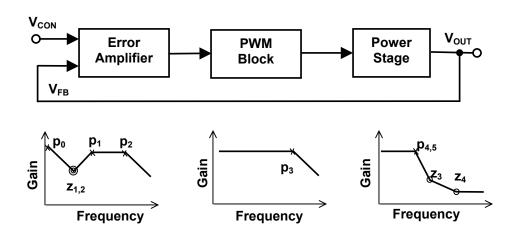

| 1.16. | Block diagram of a switching regulator illustrating key building blocks along with their representative frequency responses.      | 27 |

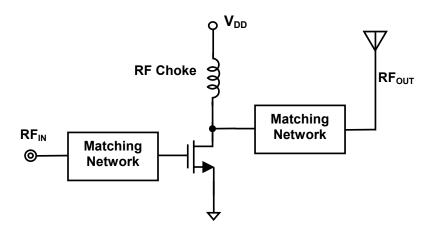

| 2.1.  | Simplified output stage of an MOS RF PA.                                                                                          | 33 |

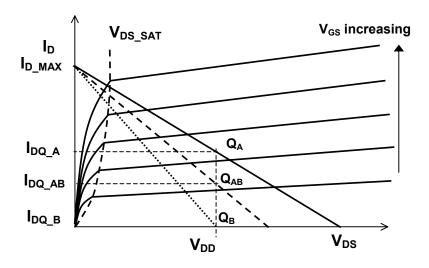

| 2.2.  | Load line in MOS RF PA for Class-A, -AB, and -B mode operation.                                                                   | 34 |

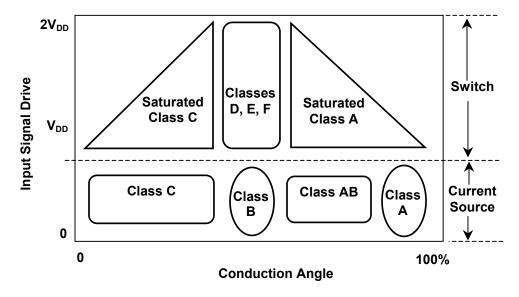

| 2.3.  | Classical definition of RF PAs based on conduction angle and input signal overdrive [30].                                         | 35 |

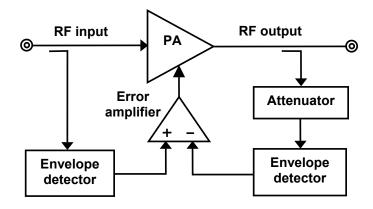

| 2.4.  | Linearization of an RF PA using envelope feedback.                                                                                | 39 |

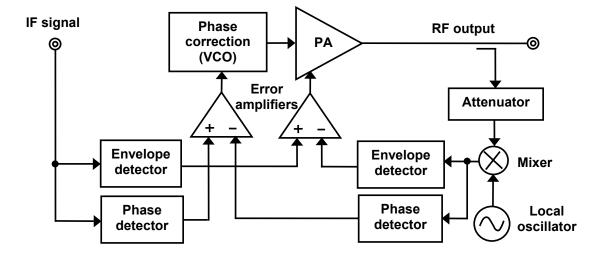

| 2.5.  | Linearization of an RF PA using polar signal feedback.                                                                            | 40 |

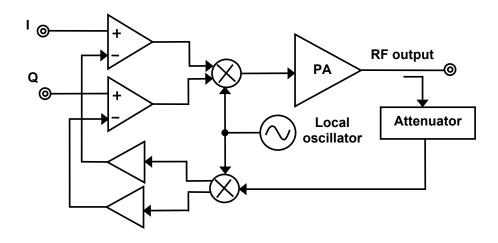

| 2.6.  | Linearization of an RF PA using Cartesian feedback.                                                                               | 41 |

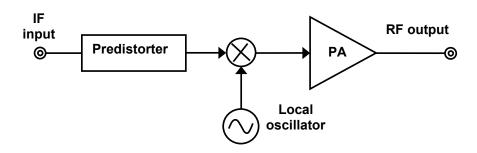

| 2.7.  | Linearization of an RF PA using predistortion method.                                                                             | 42 |

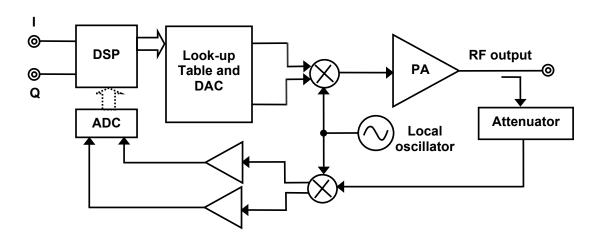

| 2.8.  | Digital adaptive predistortion system.                                                                                            | 42 |

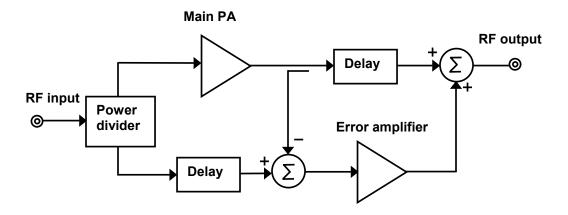

| 2.9.  | Simplified schematic of a feedforward PA scheme.                                                                                  | 43 |

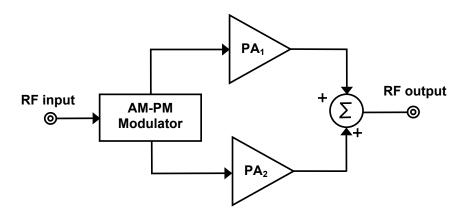

| 2.10. | Schematic of linear amplification with nonlinear components (LINC) scheme.                                                        | 44 |

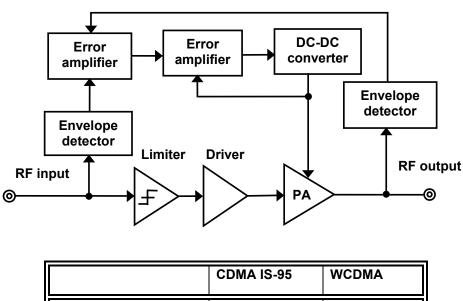

| 2.11. | Kahn envelope elimination and restoration scheme and requirements of the dc-dc converter for CDMA IS-95 and WCDMA specifications. | 46 |

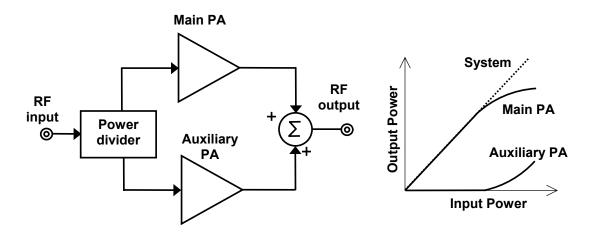

| 2.12. | Basic Doherty amplifier configuration.                                                                                            | 48 |

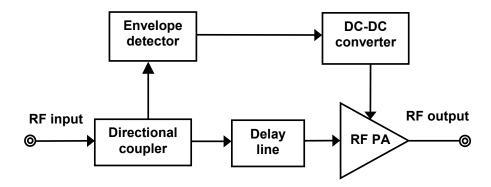

| 2.13. | Generalized functional block diagram of the envelope-follower linear PA.                                                          | 49 |

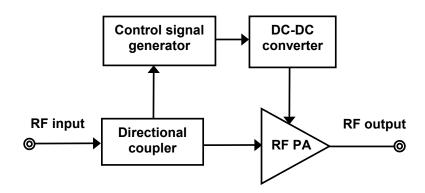

| 2.14. | Generalized functional block diagram of the envelope-tracking linear PA.                                                          | 50 |

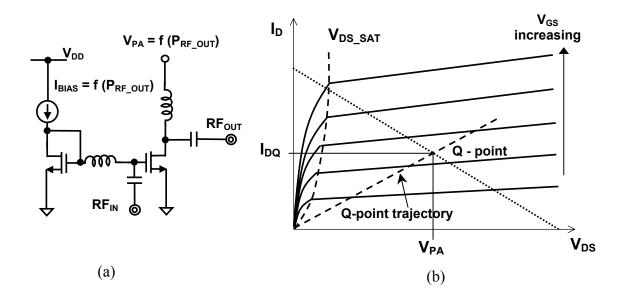

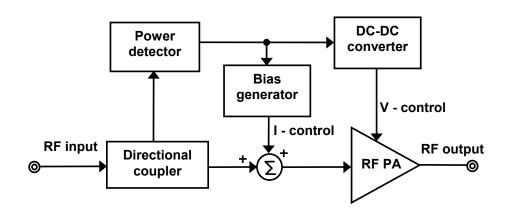

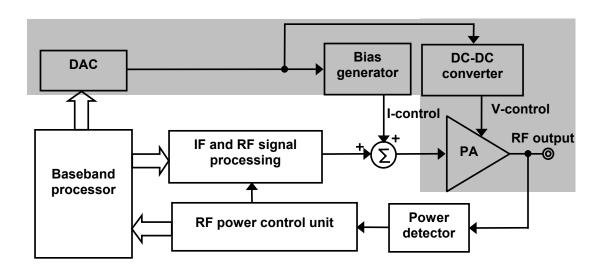

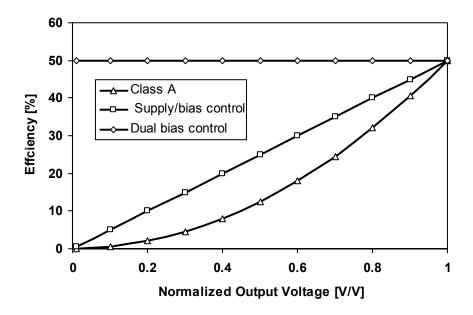

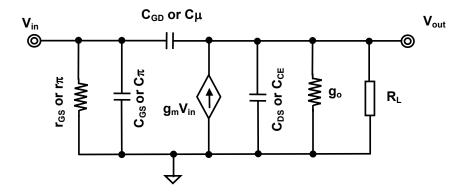

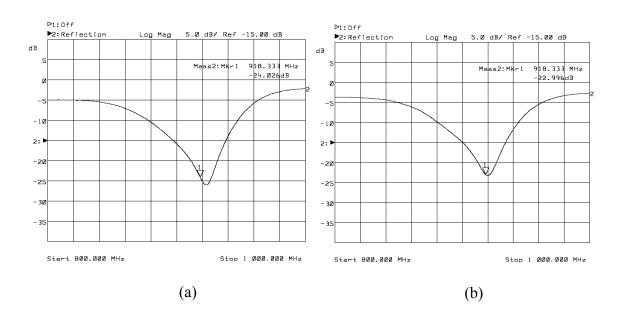

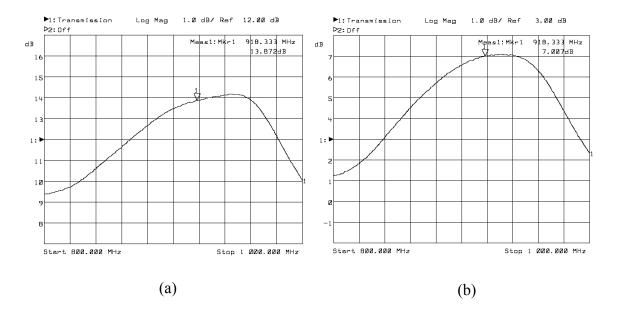

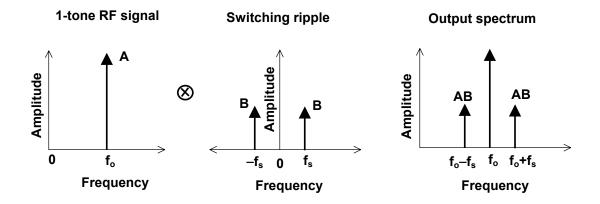

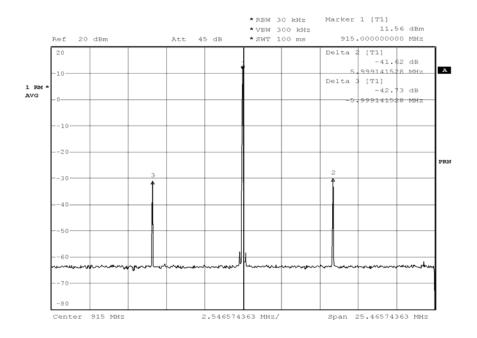

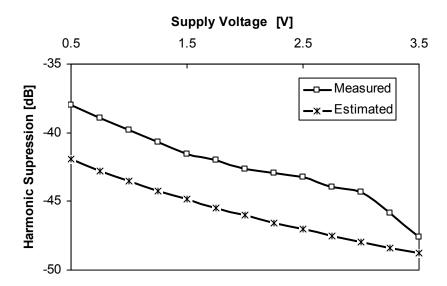

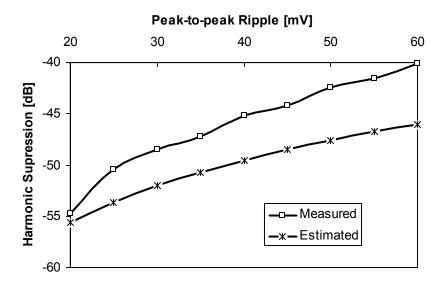

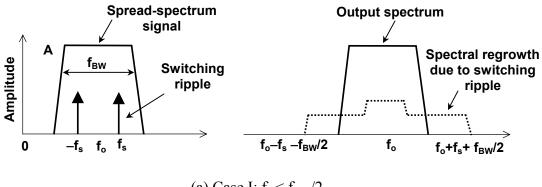

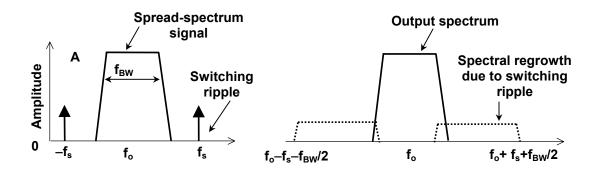

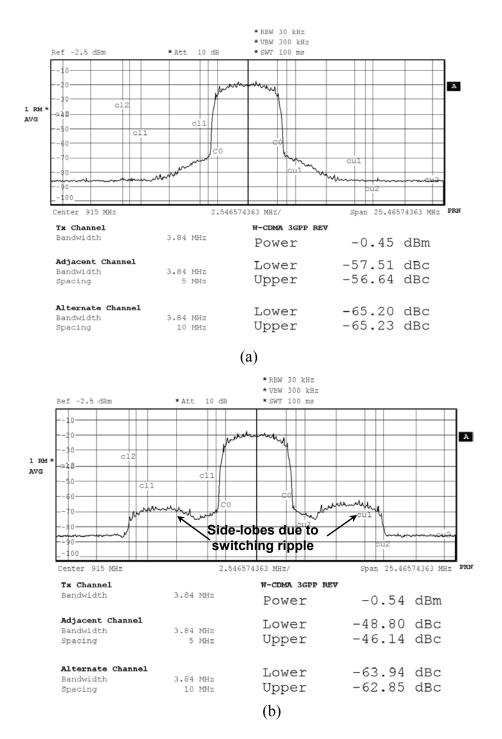

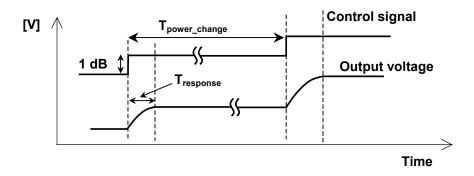

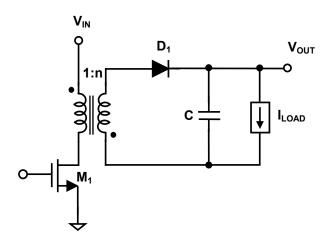

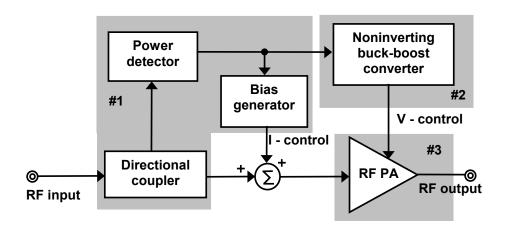

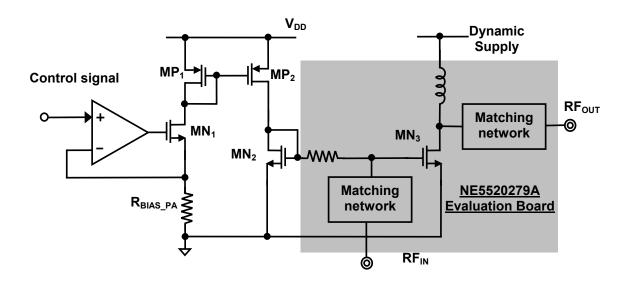

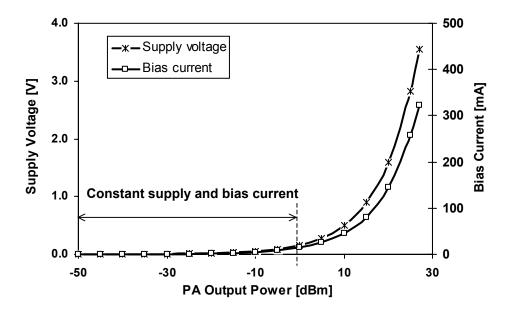

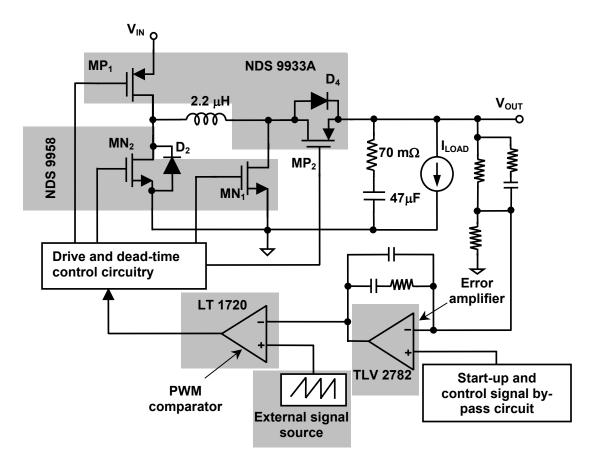

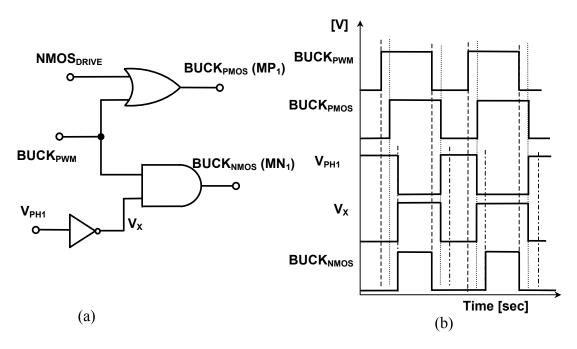

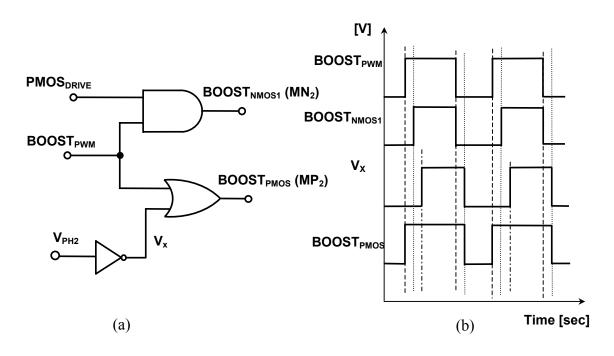

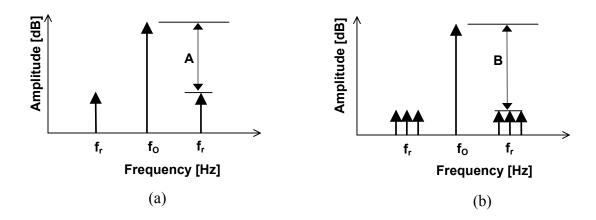

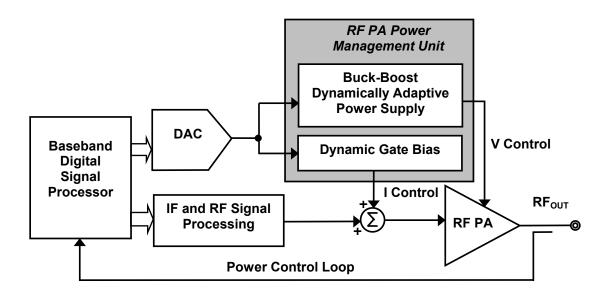

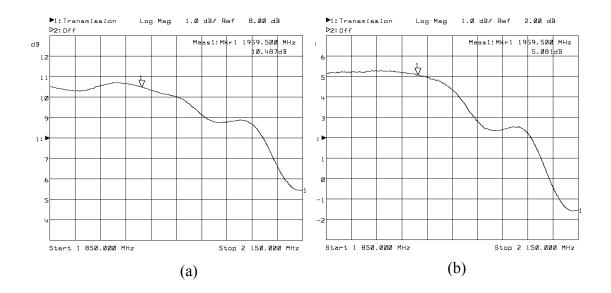

(a) Simplified schematic of a MOS PA with dynamic supply voltage 52 and bias current adjustment and (b) its operating point trajectory. 53 Functional block diagram of the proposed power-tracking, dual-bias controlled linear RF PA as a stand-alone solution. 54 Functional block diagram of the proposed power-tracking, dual-bias controlled linear RF PA within the complete transmitter. Efficiency enhancement plots of an RF PA under various bias control 57 schemes of a class-A amplifier. 58 2.19. Simplified small-signal model of an MOS or bipolar transistor without parasitic elements. 2.20. Input matching characteristics of an LDMOS PA with bias current 59 and supply voltage variation. The  $S_{11}$  parameter of the PA with (a)  $V_{DD} = 3.6 \text{ V}, I_D = 300 \text{ mA}, \text{ and (b) } V_{DD} = 0.5 \text{ V}, I_D = 40 \text{ mA}.$ Power gain variation of a LDMOS RF PA with supply voltage and 60 2.21. bias current adjustment. The  $S_{21}$  parameter of the PA with (a)  $V_{DD}$  =  $3.6 \text{ V}, I_D = 300 \text{ mA}, \text{ and (b) } V_{DD} = 0.5 \text{ V}, I_D = 40 \text{ mA}.$ 2.22. Effect of the power-supply ripple voltage on single-tone signal 63 amplification. 2.23. Measured single-tone signal amplification in the presence of a 6 MHz 63 power supply ripple. 2.24. Comparison of the measured and first-order estimated harmonic 64 suppression as a function of supply voltage. 2.25. Comparison of the measured and first-order estimated harmonic 64 suppression as a function of peak-to-peak ripple voltage in the supply. Power supply ripple effect on the spread-spectrum signal 66 amplification by the RF PA with ripple frequency (a) within baseband bandwidth, and (b) outside baseband bandwidth. Measured output spectrum of a PA with a 915 MHz center frequency 67 and 3.84 MHz HPSK signal (a) without power supply ripple, (b) with power supply ripple of 6 MHz. 2.28. Illustration of the power supply's transient response during a PA's 68 supply voltage adjustment.

| 3.1.  | Schematic of a Flyback converter.                                                                                        | 71 |

|-------|--------------------------------------------------------------------------------------------------------------------------|----|

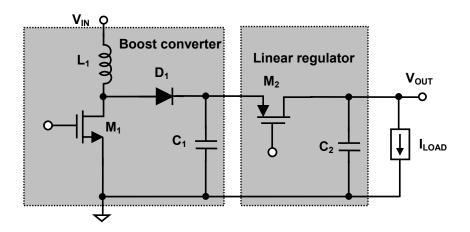

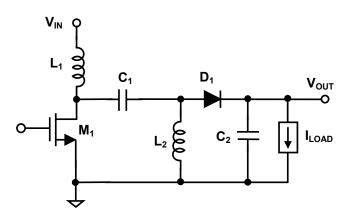

| 3.2.  | Schematic of a boost converter with a series linear regulator for realizing buck-boost conversion.                       | 72 |

| 3.3.  | Schematic of an inverting buck-boost converter.                                                                          | 73 |

| 3.4.  | Schematic of a charge-pump inverter.                                                                                     | 74 |

| 3.5.  | Schematic of Cuk converter.                                                                                              | 74 |

| 3.6.  | Schematic of single-ended-primary-inductance converter.                                                                  | 75 |

| 3.7.  | Schematic of noninverting buck-boost converter.                                                                          | 76 |

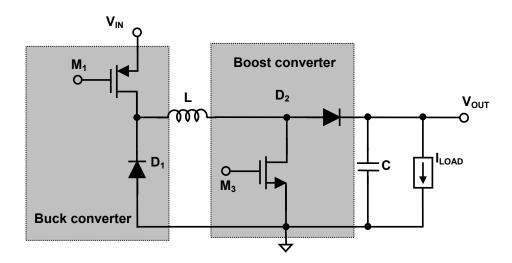

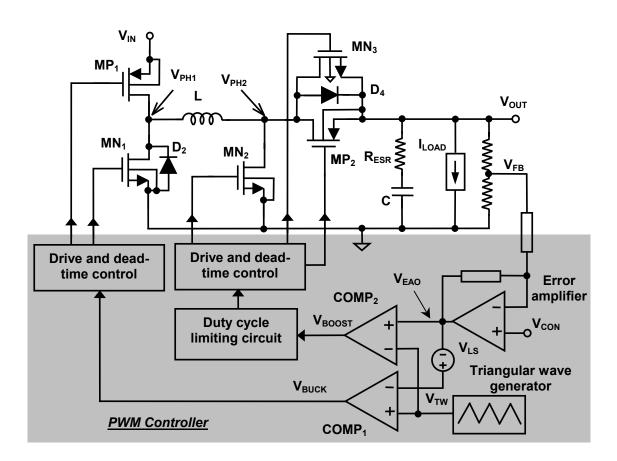

| 3.8.  | Schematic of a noninverting, synchronous buck-boost converter.                                                           | 78 |

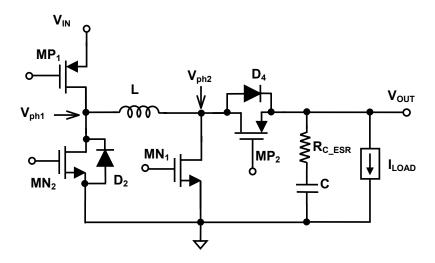

| 3.9.  | Key waveform of the noninverting synchronous buck-boost dc-dc converter.                                                 | 79 |

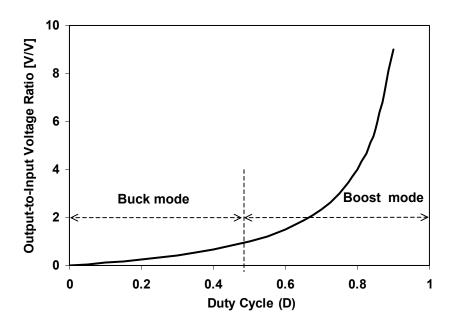

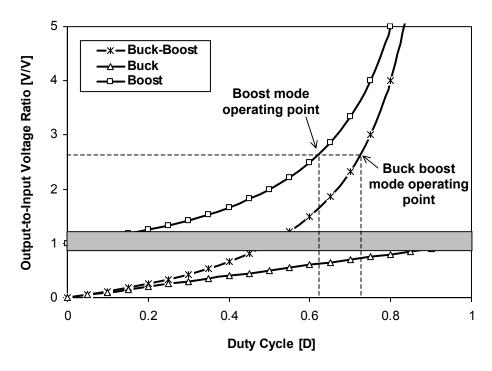

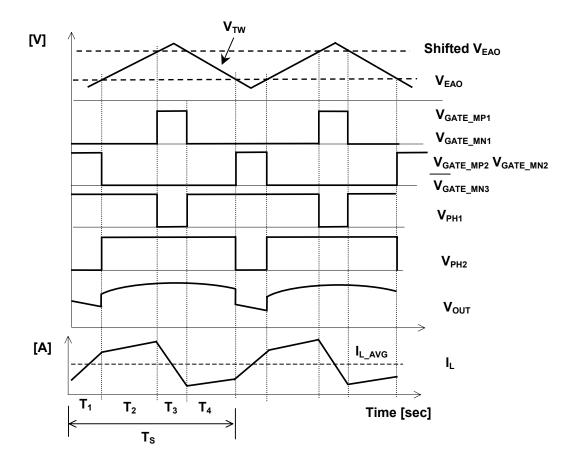

| 3.10. | Output-to-input voltage ratio of a noninverting buck-boost converter as a function of its duty cycle.                    | 81 |

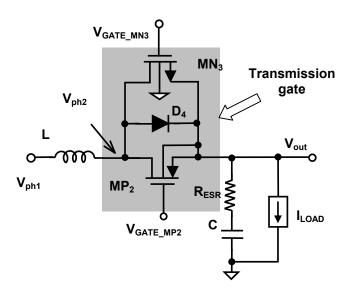

| 3.11. | Schematic of the transmission-gate output stage of the buck-boost converter for dynamic output voltage considerations.   | 83 |

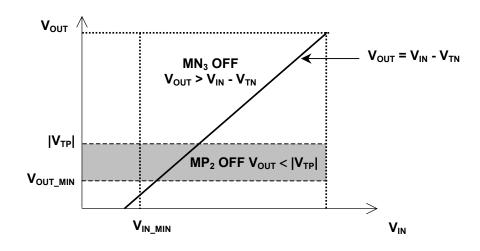

| 3.12. | Illustration of the effect of low supply voltage on buck-boost converter with a transmission-gate output stage.          | 83 |

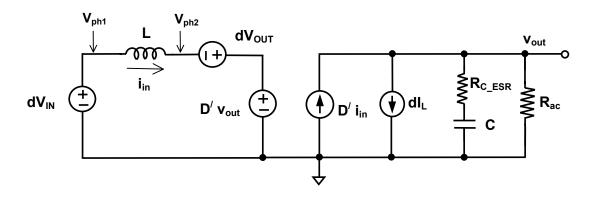

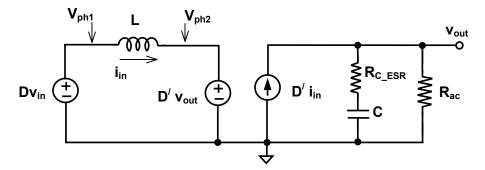

| 3.13. | Time averaged small-signal model of the buck-boost converter power stage with respect to change in duty cycle.           | 85 |

| 3.14. | Time averaged small-signal model of the buck-boost converter power stage with respect to change in line (input) voltage. | 87 |

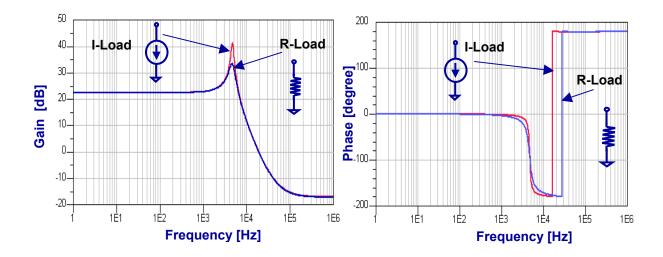

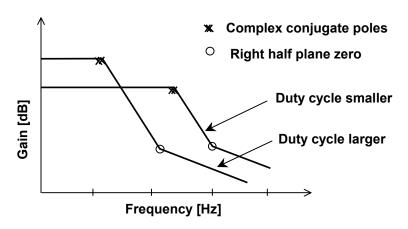

| 3.15. | Power stage frequency response of the noninverting buck-boost converter with respect to change in duty cycle.            | 89 |

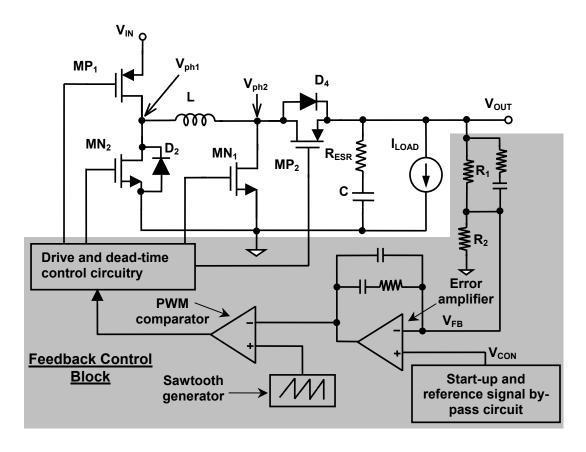

| 3.16. | Voltage-mode, PWM controlled, noninverting, synchronous buck-boost dc-dc converter.                                      | 93 |

| 3.17. | Frequency response of the buck-boost converter's power stage with for two duty cycle values                              | 95 |

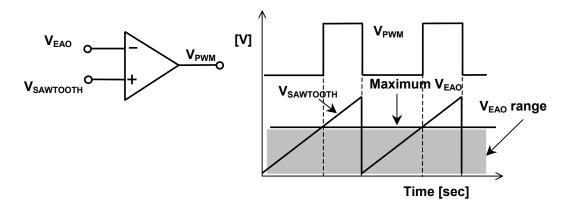

| 3.18. | Duty-cycle limiting of the buck-boost converter with restricted error                                                    | 96 |

amplifier supply voltage.

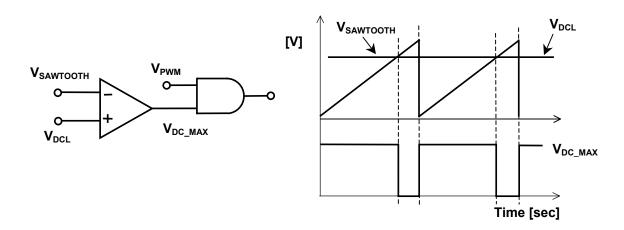

| 3.19. | Duty-cycle limiting in the buck-boost converter for low supply voltage environment.                                                                  | 96  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

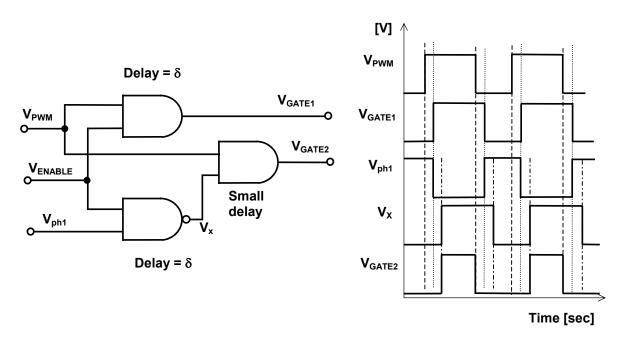

| 3.20. | Fixed dead-time control scheme and its relevant waveforms for the buck-boost converter.                                                              | 97  |

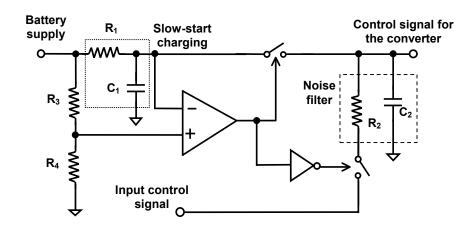

| 3.21. | Slow-start circuit schematic suitable for the buck-boost converter.                                                                                  | 98  |

| 4.1.  | Schematic of the prototype CDMA PA system.                                                                                                           | 103 |

| 4.2.  | Schematic of RF PA along with dynamic gate bias circuit.                                                                                             | 104 |

| 4.3.  | Approximate loading profile (supply voltage and bias current) of the CDMA RF PA with output power variation from –50 to 27 dBm.                      | 106 |

| 4.4.  | Voltage-mode, noninverting synchronous buck-boost dc-dc converter implementation.                                                                    | 107 |

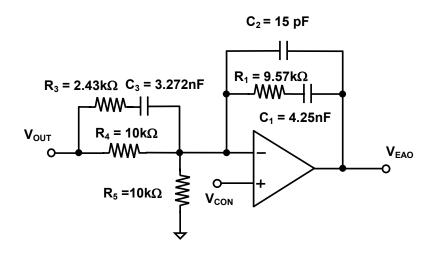

| 4.5.  | Type –III (2-zeros and 3-poles) designed for compensating the buckboost converter.                                                                   | 109 |

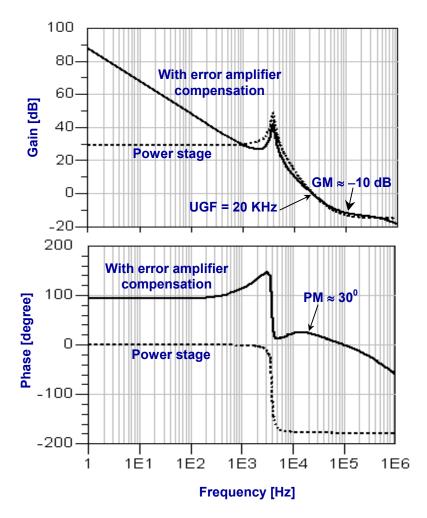

| 4.6   | Gain and phase plots of the open-loop control-to-output transfer function of the buck-boost converter with and without error amplifier compensation. | 110 |

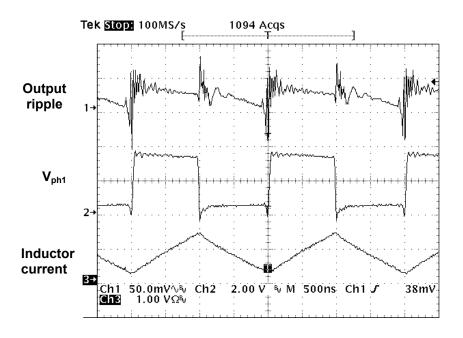

| 4.7.  | Experimental buck-boost converter waveforms: output ripple, node voltage $V_{\text{ph1}}$ , and inductor current waveforms.                          | 111 |

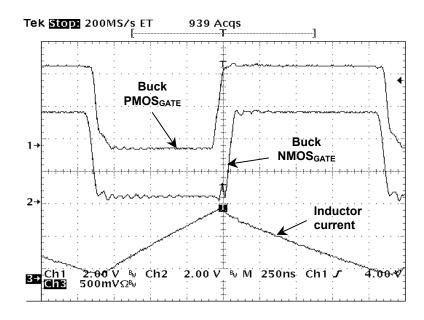

| 4.8.  | Experimental buck-boost converter waveforms: gate drive signals illustrating dead time control.                                                      | 112 |

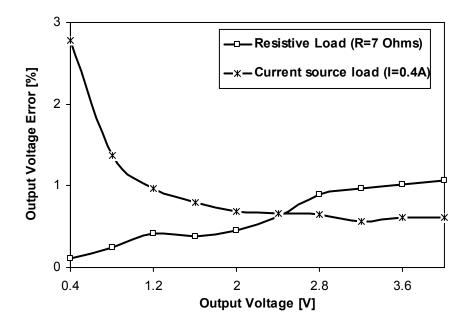

| 4.9.  | Percentage output voltage error of the dynamic buck-boost converter.                                                                                 | 113 |

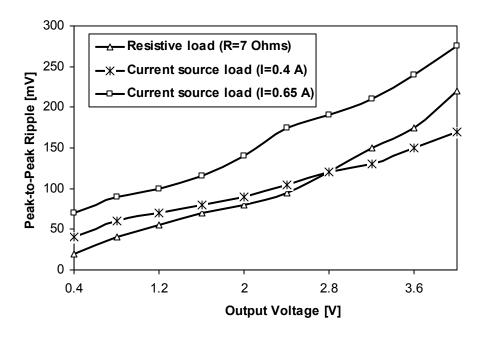

| 4.10. | Peak-to-peak ripple voltage of the prototype dynamic buck-boost converter.                                                                           | 113 |

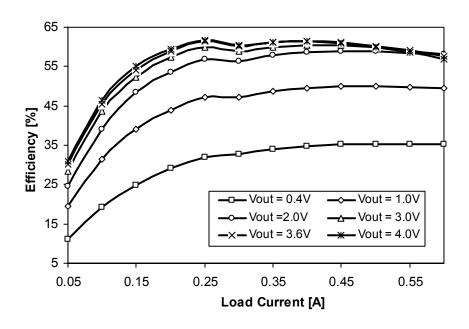

| 4.11. | Efficiency curves of the buck-boost converter.                                                                                                       | 115 |

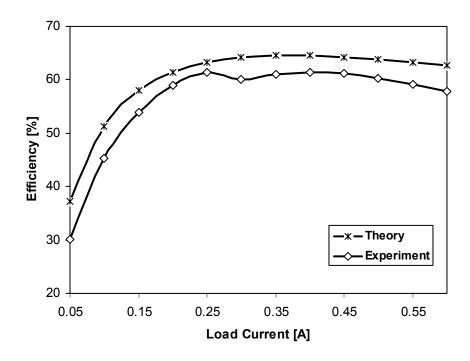

| 4.12. | Comparison of the theoretical and experimental efficiency results for output voltage of 3.6 V from an input supply of 3 V.                           | 115 |

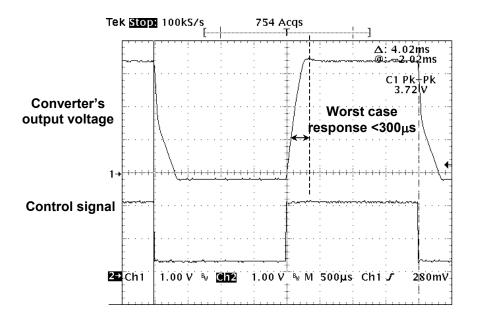

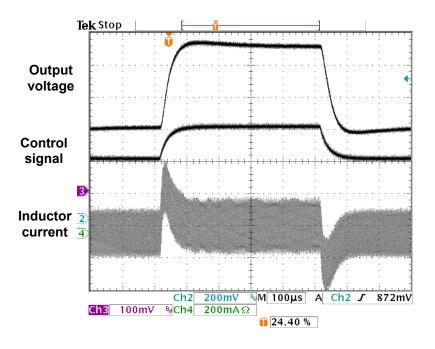

| 4.13. | Prototype buck-boost converter's response to a worst-case step change in control signal.                                                             | 116 |

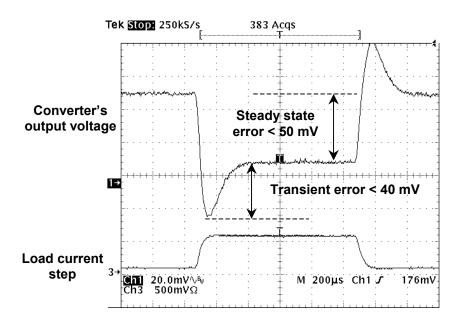

| 4.14. | Prototype buck-boost converter's response to a 0 to 0.5 A step-change in load current.                                                                                                 | 117 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

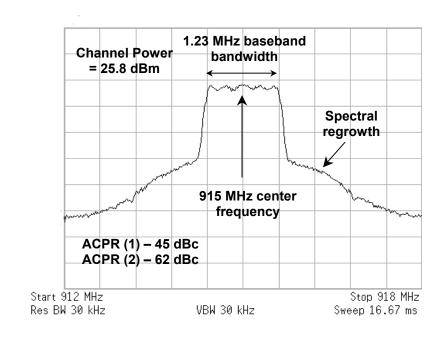

| 4.15. | Measured output spectrum if the RF PA showing channel power in a 1.23 MHz bandwidth with a 915 MHz center frequency.                                                                   | 118 |

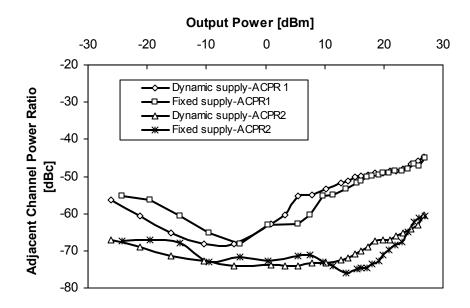

| 4.16. | First and second ACPR comparison of the dynamic- and fixed-supply PA.                                                                                                                  | 119 |

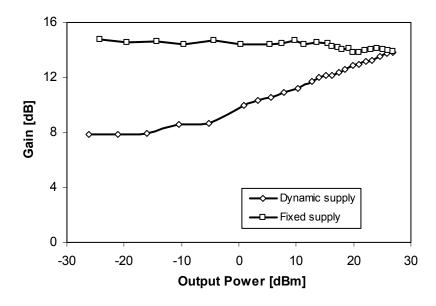

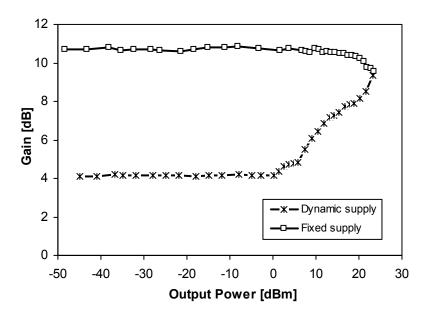

| 4.17. | Gain comparison of the dynamic- and fixed-supply PA.                                                                                                                                   | 120 |

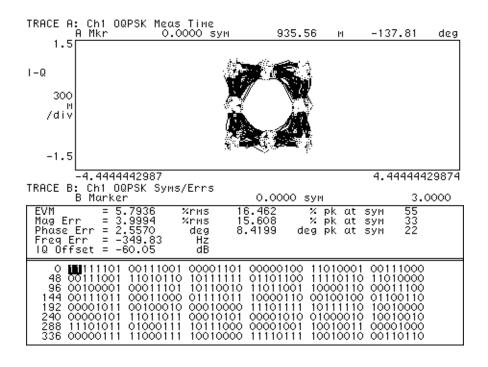

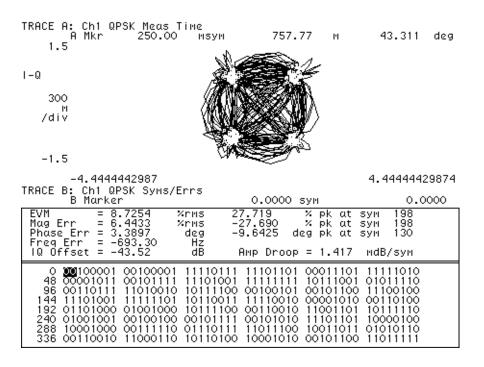

| 4.18. | Measured error vector magnitude and constellation of the OQPSK CDMA signal at the maximum PA output power of 27 dBm.                                                                   | 121 |

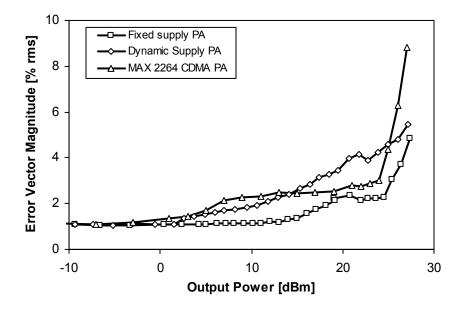

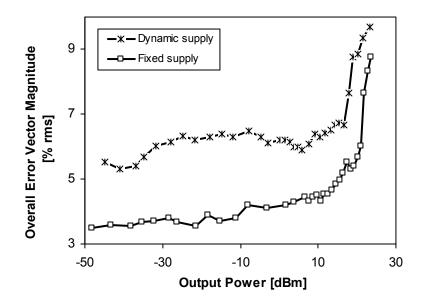

| 4.19. | Error vector magnitude (EVM) results comparison of the dynamicand fixed-supply PA.                                                                                                     | 121 |

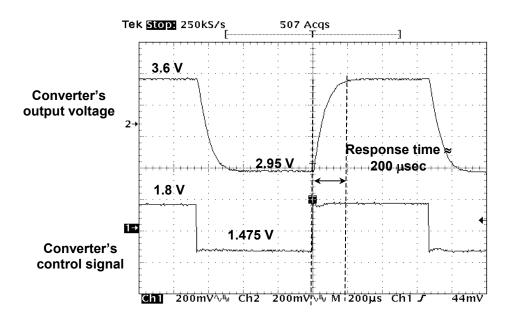

| 4.20. | Dynamic converter's response to a worst-case power adjustment from 26 to 27 dBm with a corresponding change in its output voltage from 2.95 to 3.6 V.                                  | 122 |

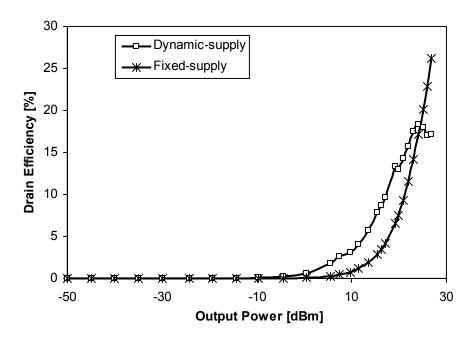

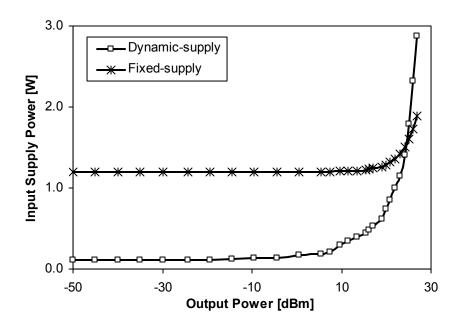

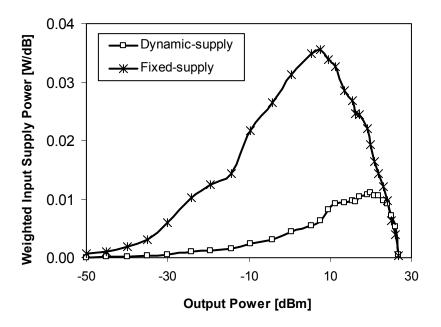

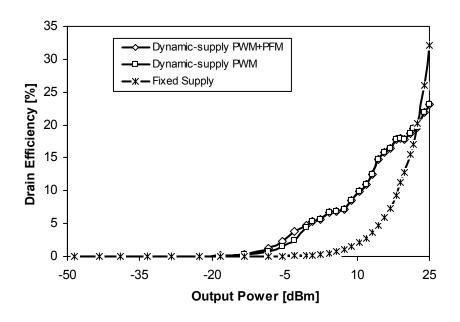

| 4.21. | Drain efficiency comparison of the dynamic- and fixed-supply PAs.                                                                                                                      | 123 |

| 4.22. | Input power comparison of the dynamic- and fixed-supply PAs.                                                                                                                           | 124 |

| 4.23. | Weighted input power comparison of the dynamic and fixed-supply PAs                                                                                                                    | 125 |

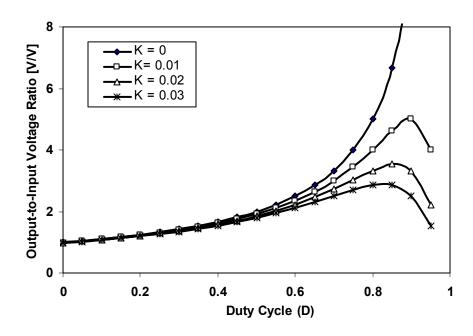

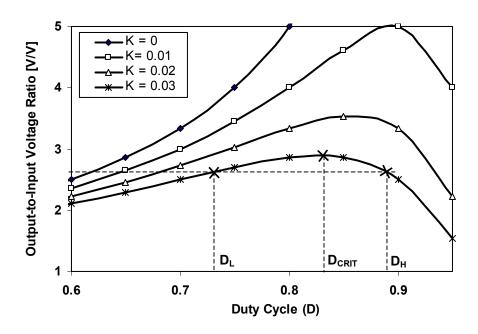

| 5.1.  | Output-to-input voltage ratio in buck, buck-boost, and boost mode operation and their band overlap.                                                                                    | 130 |

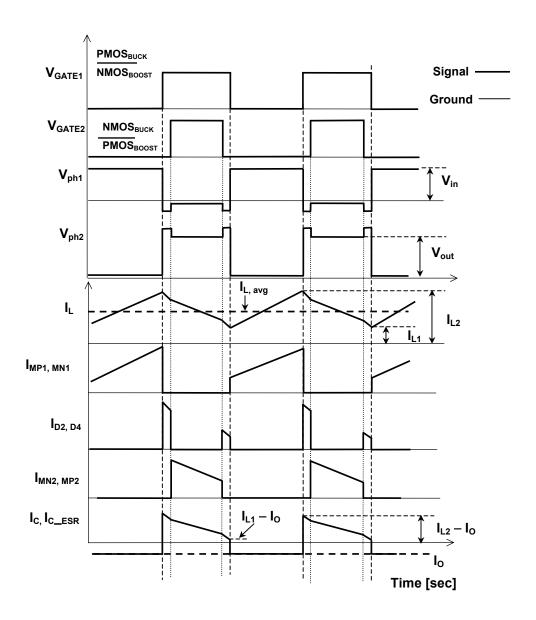

| 5.2.  | Block diagram representation of the modified back-boost converter with buck, buck-boost, and boost mode operation.                                                                     | 131 |

| 5.3.  | Key waveforms of the modified noninverting buck-boost converter operating on buck-boost mode.                                                                                          | 133 |

| 5.4.  | Output-to-input voltage ratio the boost converter with power switches and inductor resistances.                                                                                        | 137 |

| 5.5.  | Zoomed output-to-input voltage ratio plot of the boost converter in presence of nonidealities illustrating the existence of two operating points for a given voltage conversion ratio. | 138 |

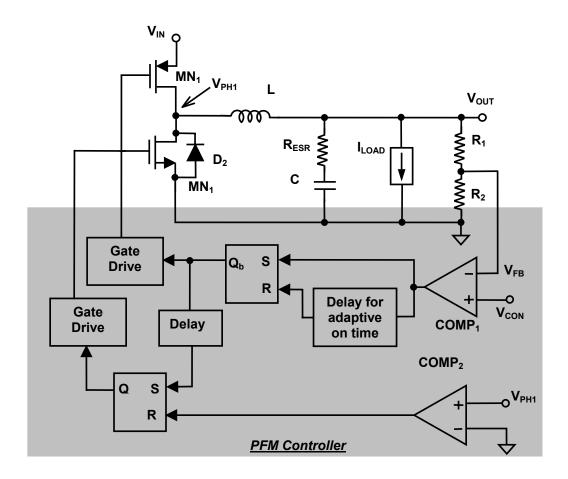

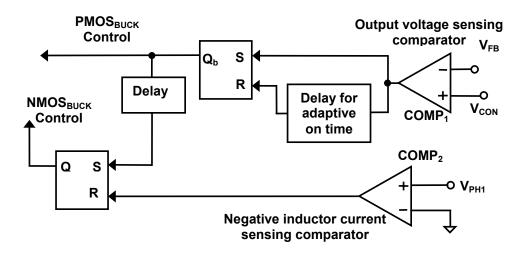

| 5.6.  | Block diagram representation of the PFM controller with buck operation.                                                                                                            | 141 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.7.  | Buck-boost converter's PFM mode steady-state waveforms.                                                                                                                            | 142 |

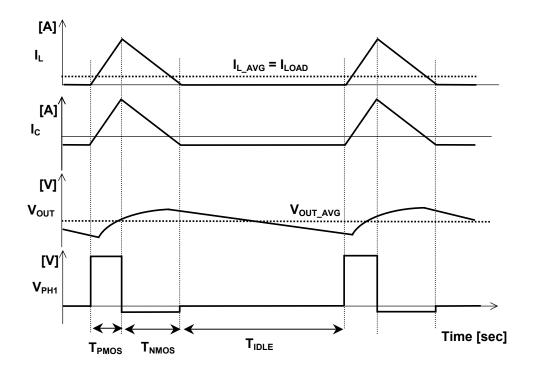

| 5.8.  | (a) Conceptual representation of adaptive on time generation for PFM control, and (b) timing diagram.                                                                              | 146 |

| 5.9.  | Inductor current waveform of one switching cycle with asynchronous and synchronous operation in PFM control.                                                                       | 148 |

| 5.10. | (a) Logic-level representation of the adaptive dead-time control circuit for the buck stage of the PWM buck-boost converter and (b) its timing diagram.                            | 151 |

| 5.11. | (a) Logic-level representation of the dead-time control circuit for the boost stage of the PWM buck-boost converter and (b) its timing diagram.                                    | 152 |

| 5.12. | Illustration of the single-tone RF PA output: (a) without spread-spectrum clocking, and (b) with spread-spectrum clocking.                                                         | 153 |

| 6.1.  | Simplified system-level representation of the dynamically adaptive RF PA power management system.                                                                                  | 158 |

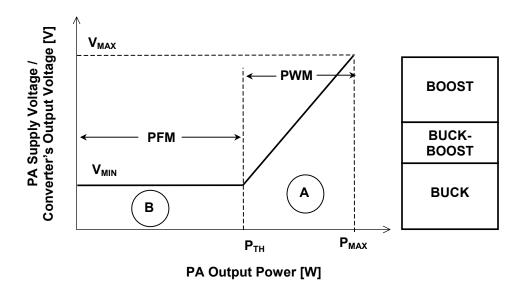

| 6.2.  | Adaptive supply's output voltage profile and illustration of a dual mode (PWM/PFM) converter operation.                                                                            | 160 |

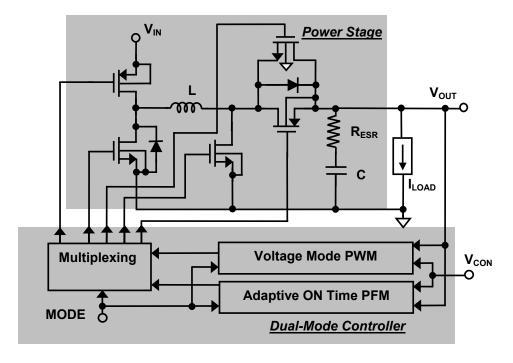

| 6.3.  | Schematic of the dual-mode, buck-boost converter.                                                                                                                                  | 161 |

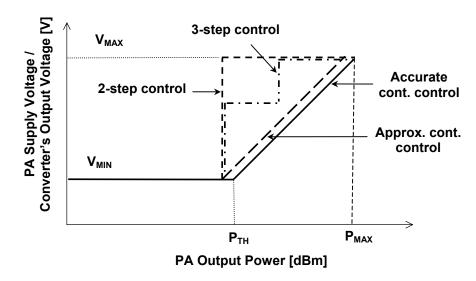

| 6.4.  | PA supply voltage variation profile with transmitter output power for alternate control schemes.                                                                                   | 163 |

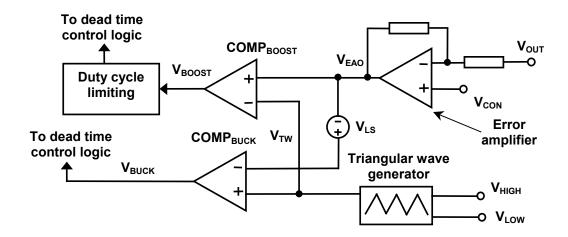

| 6.5.  | Schematic of the voltage-mode PWM controller for the buck-boost converter.                                                                                                         | 168 |

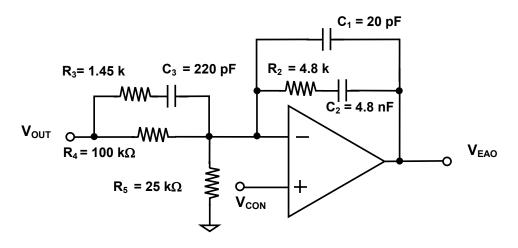

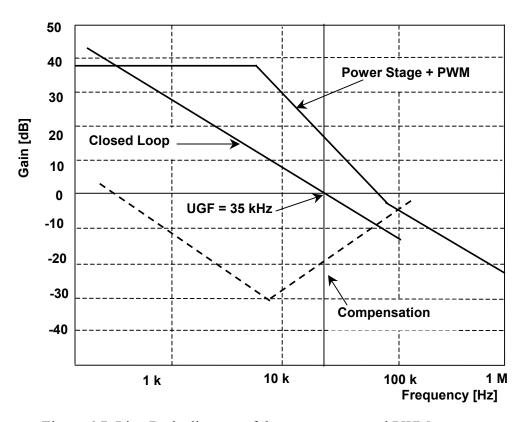

| 6.6.  | Error amplifier with the compensation network component values.                                                                                                                    | 169 |

| 6.7.  | Line Bode diagram of the power stage and PWM generator, error amplifier compensation, and closed-loop transfer function of the buck-boost converter.                               | 169 |

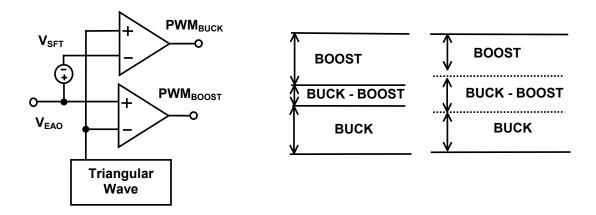

| 6.8   | Simplified schematic of the PWM block, (b) regions of operation under ideal conditions, and (c) modified region of operation under comparators with input-referred offset voltage. | 171 |

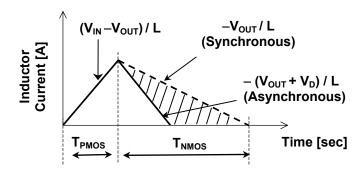

| 6.9.  | Schematic of the PFM controller.                                                                                                                                                                                                          | 173 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

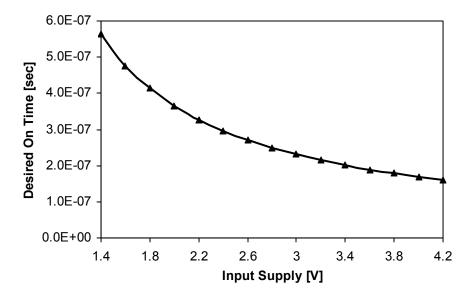

| 6.10. | Desired on time of the PFM controller over the input supply voltage range.                                                                                                                                                                | 174 |

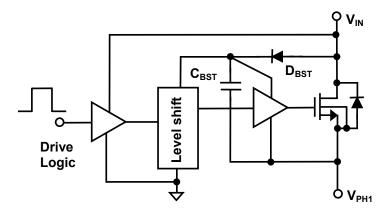

| 6.11. | Schematic of the bootstrap circuit for the NMOS high-side drive.                                                                                                                                                                          | 176 |

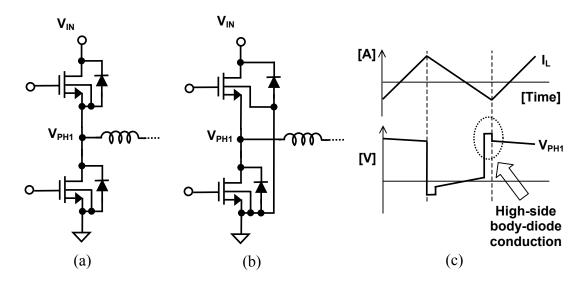

| 6.12. | High-side NMOS transistor's body-diode in (a) discrete implementation, (b) n-well integrated circuit implementation. (c) Illustration of the high-side body diode conduction for negative inductor current in continuous-conduction mode. | 177 |

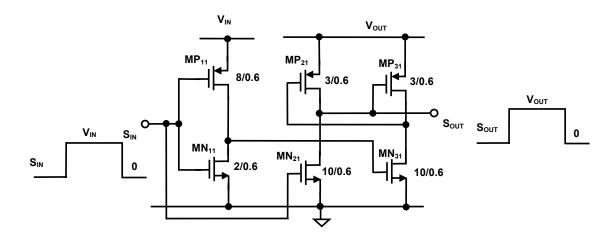

| 6.13. | Schematic of logic-level converter (level-shifter) circuit (device sizes are in $\mu m$ ).                                                                                                                                                | 178 |

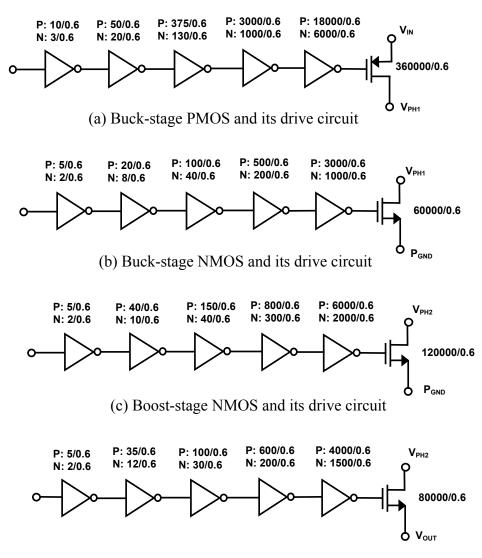

| 6.14. | Schematic of the power transistors and their drive circuits with their respective aspect ratios and dimensions (in $\mu$ m).                                                                                                              | 179 |

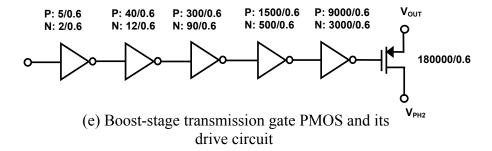

| 6.15. | Illustration of the additional propagation delay in the boost-stage PMOS transistor resulting from higher gate resistance.                                                                                                                | 181 |

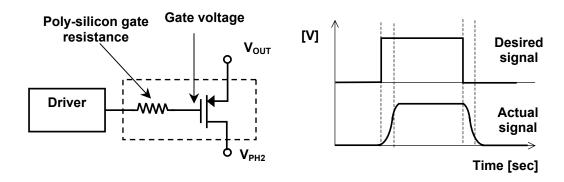

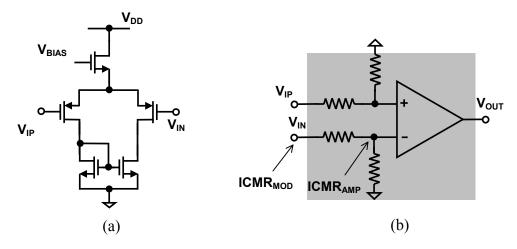

| 6.16. | NMOS input stage differential amplifiers with (a) a simple current mirror, (b) a low voltage current mirror load, (c) and folder mirror load architecture.                                                                                | 182 |

| 6.17. | (a) PMOS input stage differential amplifier and (b) increasing the ICMR of the PMOS input stage with a resistive divider.                                                                                                                 | 183 |

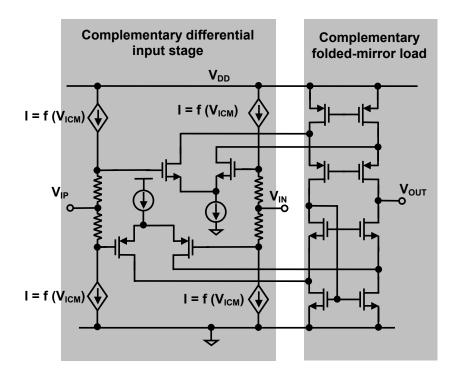

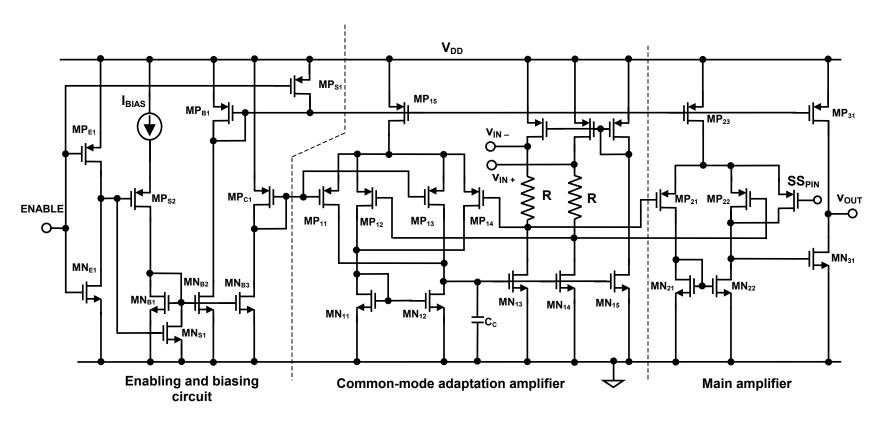

| 6.18. | Complementary (PMOS and NMOS) pair input stage with level shifting resistor divider to realize a large ICMR op-amp.                                                                                                                       | 184 |

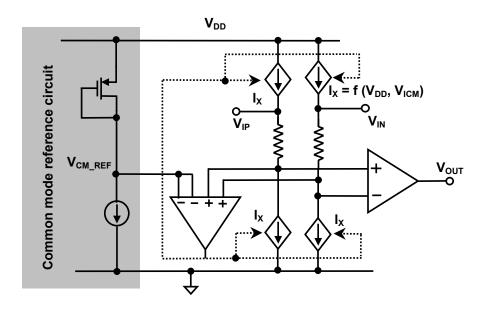

| 6.19  | Supply voltage dependant adaptive input common-mode feedforward based amplifier operation with PMOS input stage.                                                                                                                          | 185 |

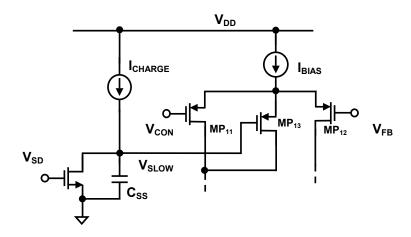

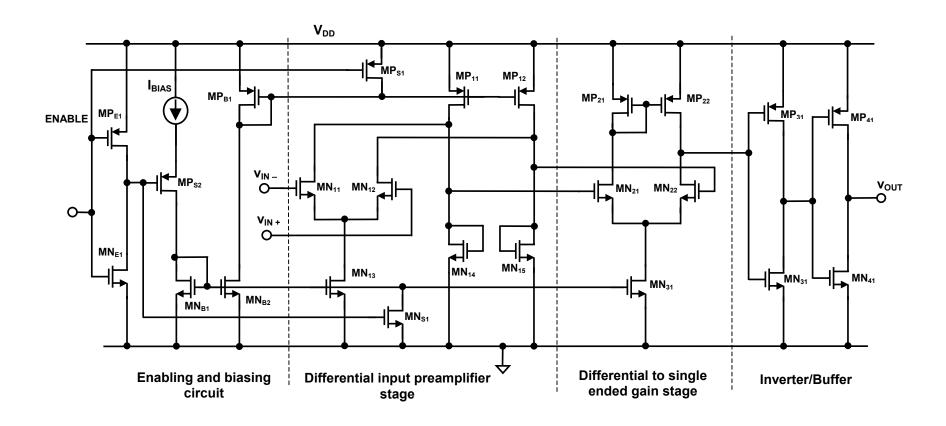

| 6.20. | Illustration of the slow-start circuit as a part of the error amplifier design [96].                                                                                                                                                      | 186 |

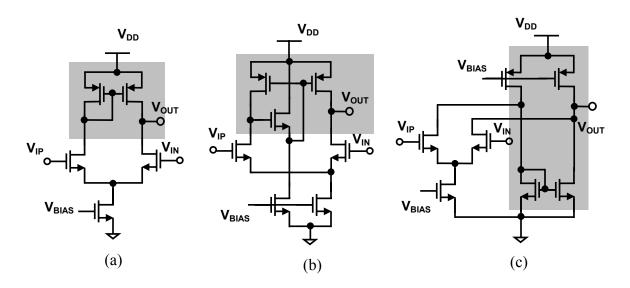

| 6.21. | Complete schematic of the error amplifier op-amp with large input common-mode range (ICMR).                                                                                                                                               | 188 |

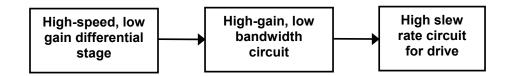

| 6.22. | Conceptual representation of the low voltage, high resolution, fast comparator circuit [67].                                                                                                                                              | 190 |

| 6.23. | Complete schematic of the high-speed, two-stage comparator circuit.                                                                                                                                                                       | 192 |

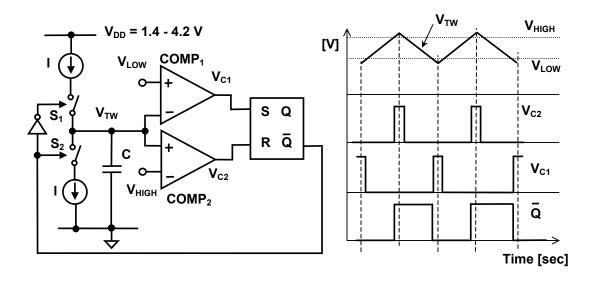

| 6.24. | Basic principle of the triangular wave generator.                                                                                                                  | 194 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.25. | Complete schematic of the triangular wave generator.                                                                                                               | 195 |

| 6.26. | PMOS input stage with (a) folded-mirror load (b) current mirror load with input transistors' bodies connected to power supply for extending the ICMR below ground. | 197 |

| 6.27. | Complete schematic of the PFM-mode comparator.                                                                                                                     | 198 |

| 6.28  | Complete schematic of adaptive on time circuit for the PFM controller.                                                                                             | 202 |

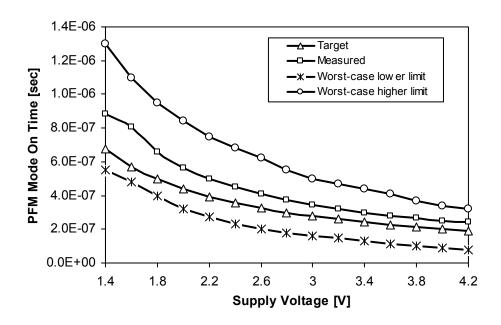

| 6.29. | Simulated and measured on-time characteristic of the adaptive on-time circuit with supply voltage variation.                                                       | 203 |

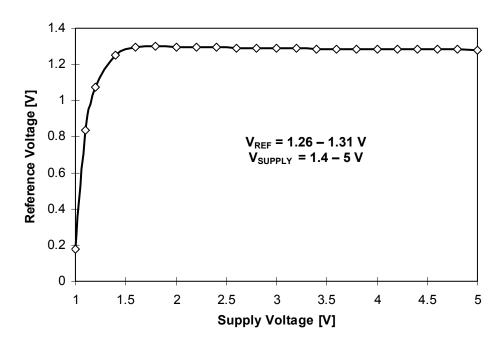

| 6.30. | Conceptual representation of the low voltage, bandgap reference circuit.                                                                                           | 204 |

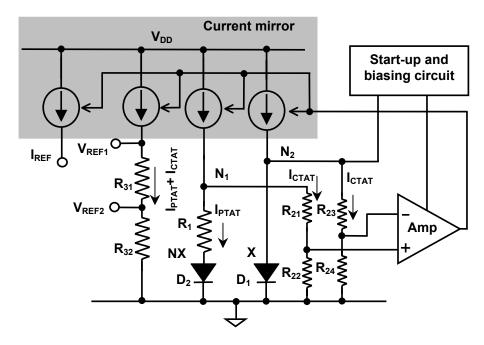

| 6.31. | Complete schematic of the low voltage bandgap-based voltage and current reference.                                                                                 | 206 |

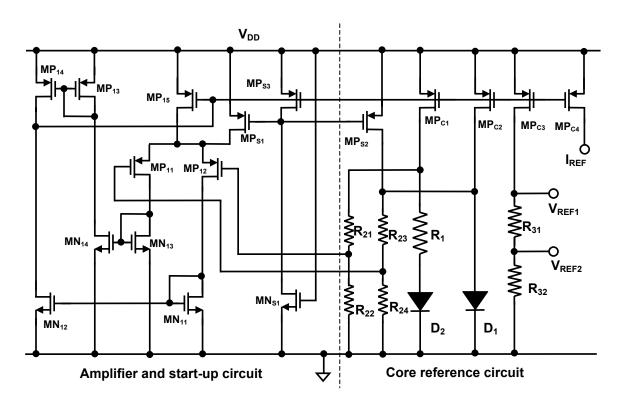

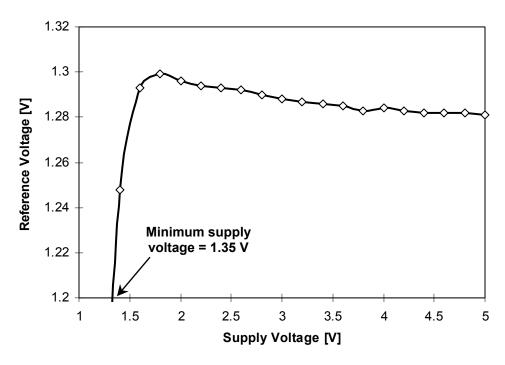

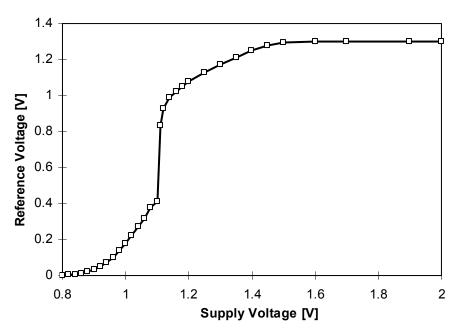

| 6.32. | Measured line regulation performance of the bandgap reference.                                                                                                     | 208 |

| 6.33. | Measured minimum input supply voltage for the bandgap reference.                                                                                                   | 208 |

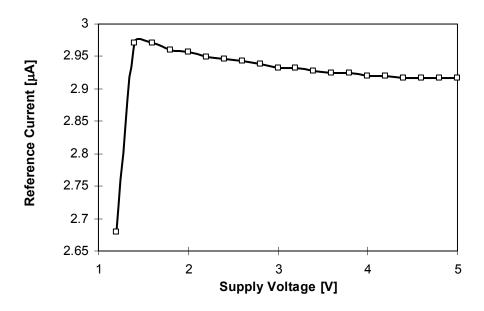

| 6.34. | Measured reference current generated from the bandgap circuit.                                                                                                     | 209 |

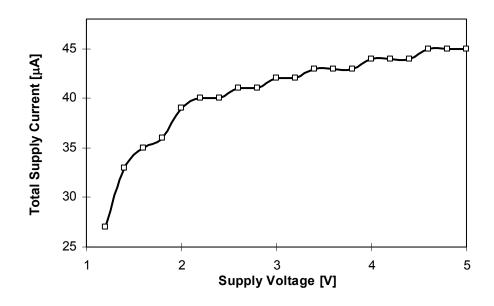

| 6.35. | Measured supply current drawn by the bandgap reference.                                                                                                            | 210 |

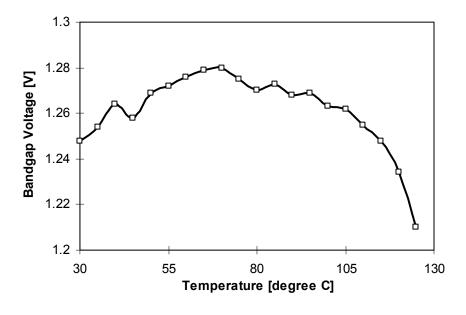

| 6.36. | Measured temperature characteristics of the bandgap reference for an input supply of $1.4\ V.$                                                                     | 210 |

| 6.37. | Measured start-up characteristic of the bandgap reference circuit.                                                                                                 | 211 |

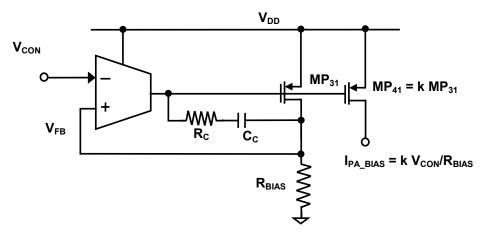

| 6.38. | Schematic of the dynamic gate (base) bias circuit for MOS (BJT/HBT) RF PA.                                                                                         | 212 |

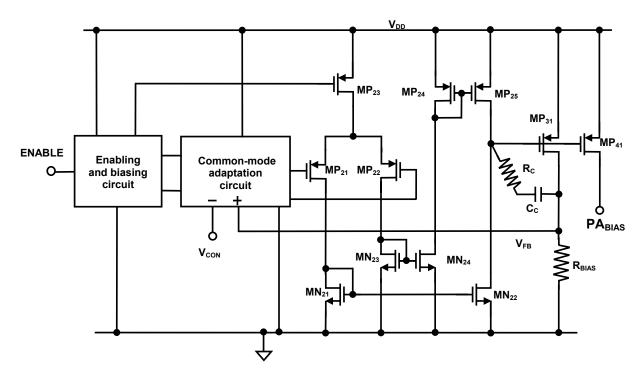

| 6.39. | Schematic of the dynamic bias circuit.                                                                                                                             | 213 |

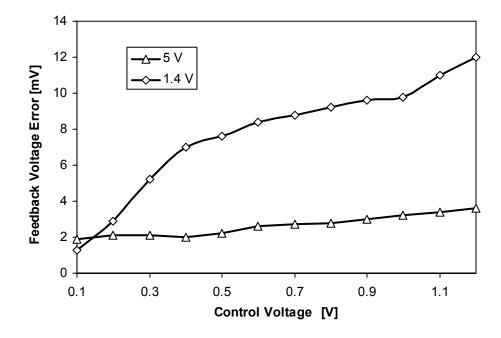

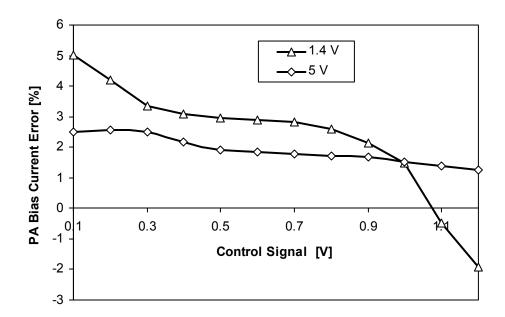

| 6.40. | Measured feedback node error voltage compared to the control voltage of the dynamic bias circuit.                                                                  | 214 |

| 6.41  | Measured accuracy of the dynamic bias circuit's output current                                                                                                     | 215 |

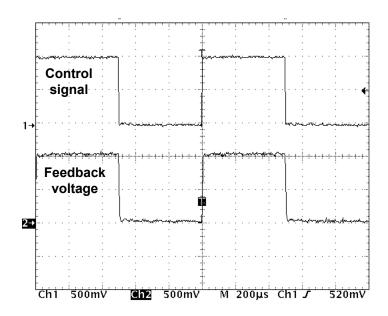

| 6.42. | Measured $0.1 - 1$ V control-step transient response.                                                                                                | 216 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

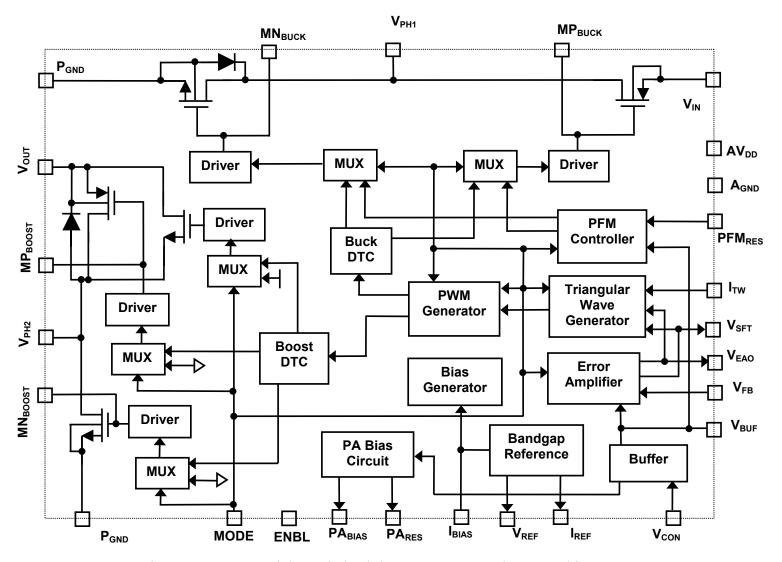

| 7.1.  | Integrated dynamic buck-boost converter and PA gate-bias system.                                                                                     | 219 |

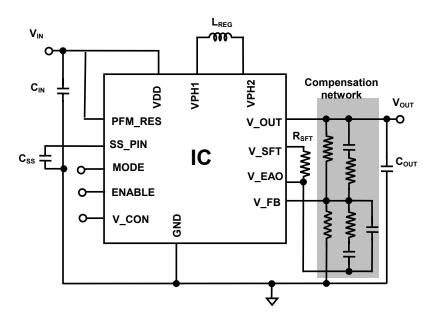

| 7.2.  | Schematic of the chip-level integrated system with its respective external passive components.                                                       | 220 |

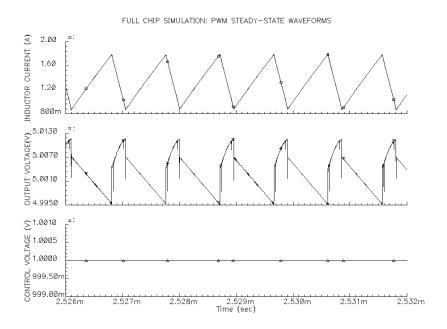

| 7.3.  | Full chip PWM mode simulation results - Steady-state waveforms ( $V_{\rm IN}$ = 1.5 V, $V_{\rm OUT}$ = 5 V).                                         | 221 |

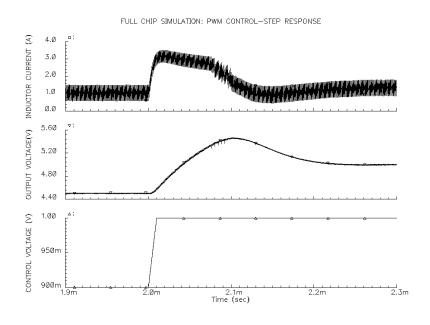

| 7.4.  | Full chip PWM mode simulation result: Transient control-step response.                                                                               | 221 |

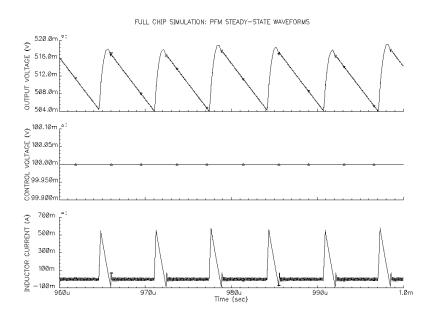

| 7.5.  | Full chip PFM mode simulation result: Steady-state waveforms.                                                                                        | 222 |

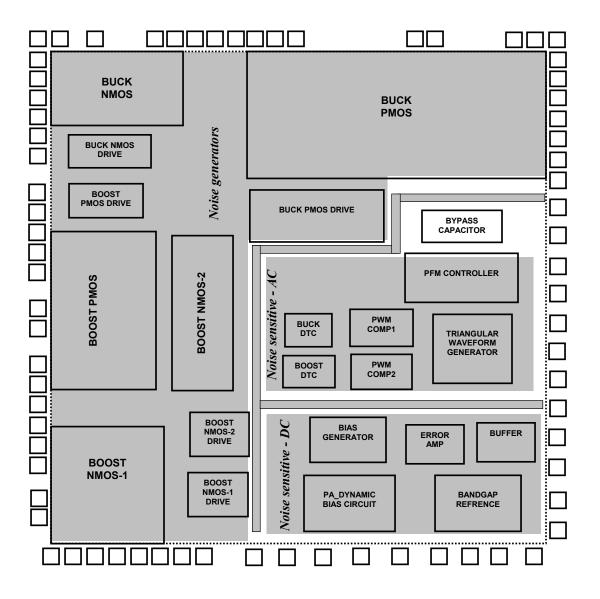

| 7.6.  | Integrated system floor plan.                                                                                                                        | 223 |

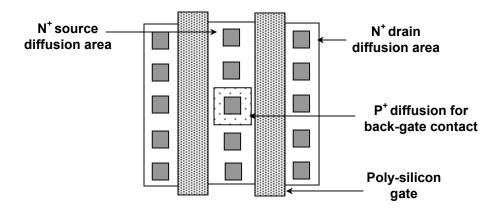

| 7.7.  | Illustration of integrated back-gate contact of an NMOS transistor.                                                                                  | 224 |

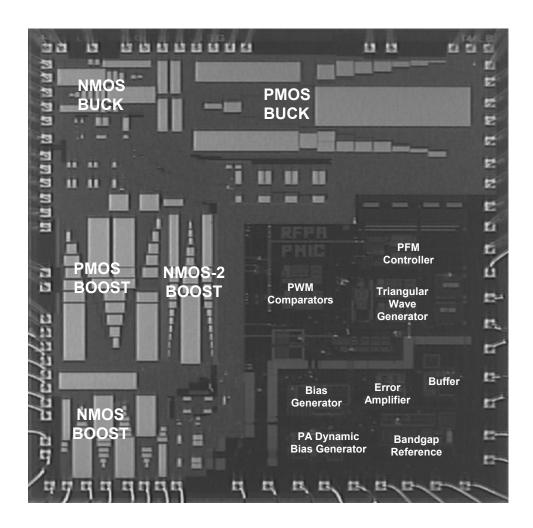

| 7.8.  | Die plot of the buck-boost converter and PA dynamic gate bias control chip.                                                                          | 225 |

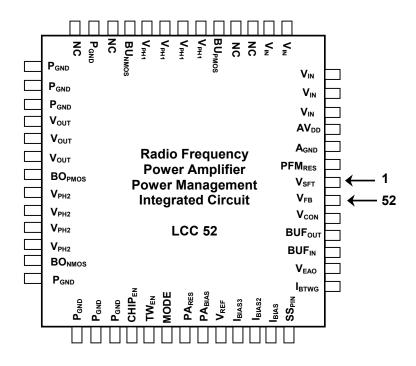

| 7.9.  | Pin diagram of the buck-boost converter and bias control chip.                                                                                       | 226 |

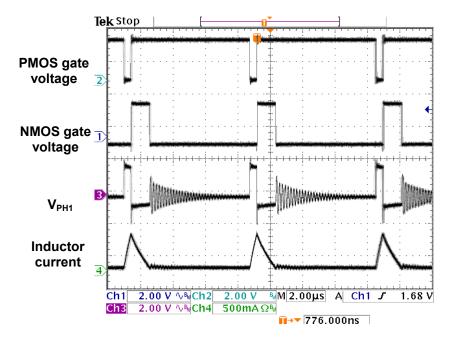

| 7.10. | Experimental buck-boost converter IC PFM mode functionality: Power transistors' gate voltage, $V_{\text{PH}1}$ node, and inductor current waveforms. | 227 |

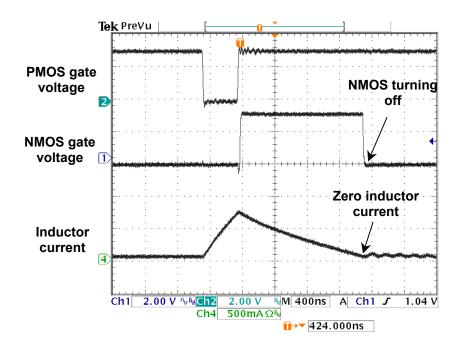

| 7.11. | Experimental buck-boost converter IC results: Synchronous NMOS turning off when the inductor current becomes zero.                                   | 228 |

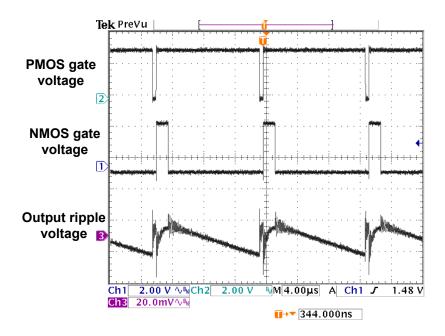

| 7.12. | Experimental buck-boost converter IC results: Gate drive and output ripple voltage waveforms.                                                        | 229 |

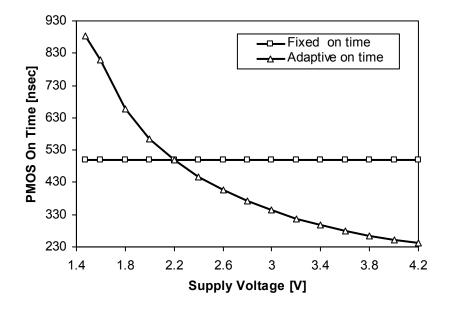

| 7.13. | Fixed and adaptive on time of the experimental buck-boost converter IC in PFM mode.                                                                  | 229 |

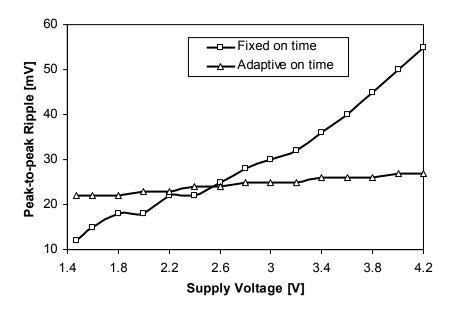

| 7.14. | Experimental peak-to-peak output voltage ripple of the buck-boost converter IC for fixed and adaptive on time PFM mode control.                      | 230 |

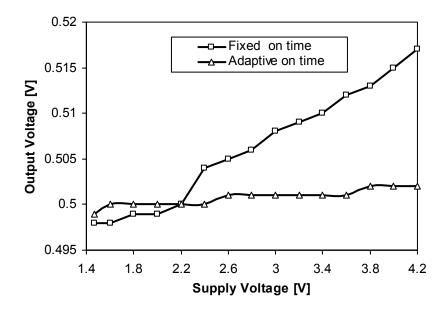

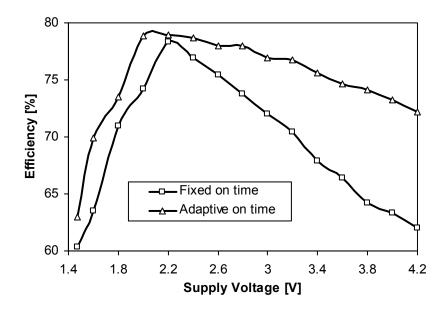

| 7.15. | Experimental average output voltage of the buck-boost converter IC for fixed and adaptive on time PFM mode control.                                  | 230 |

| 7 16  | Measured switching frequency of the buck-boost converter IC for                                                                                      | 231 |

fixed and adaptive on time PFM mode control.

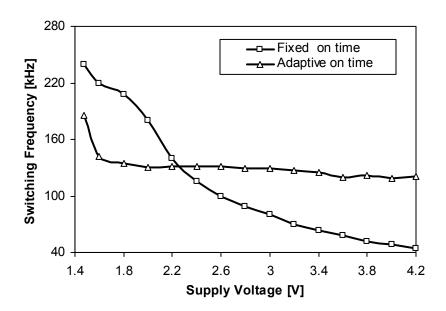

| 7.17. | Measured efficiency characteristics of the buck-boost converter IC in fixed and adaptive on time PFM control.                                                                                                                      | 232 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

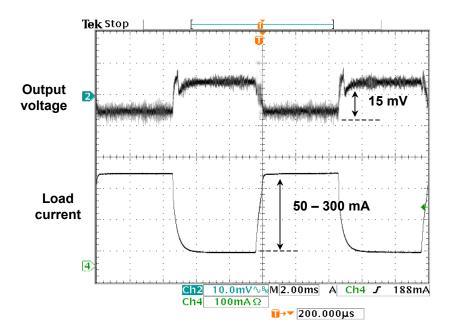

| 7.18. | Experimental load-step response of the PFM-mode converter with adaptive on time control.                                                                                                                                           | 233 |

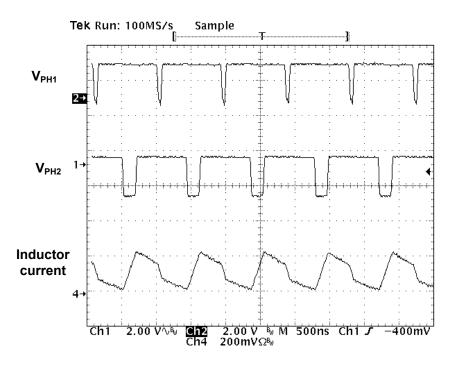

| 7.19. | Experimental buck-boost converter waveforms in buck-boost mode: $V_{\text{PH1}},V_{\text{PH2}},$ and inductor current.                                                                                                             | 235 |

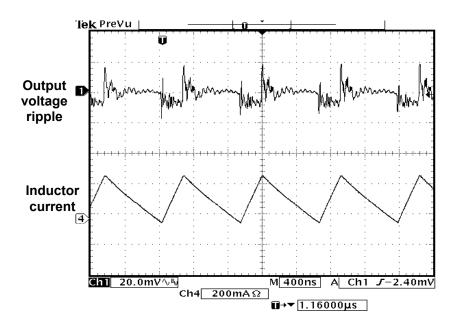

| 7.20. | Experimental buck-boost converter waveforms in boost mode: output ripple and inductor current.                                                                                                                                     | 235 |

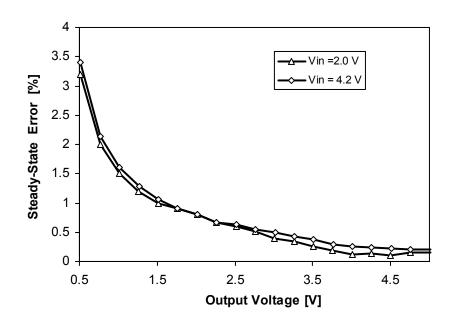

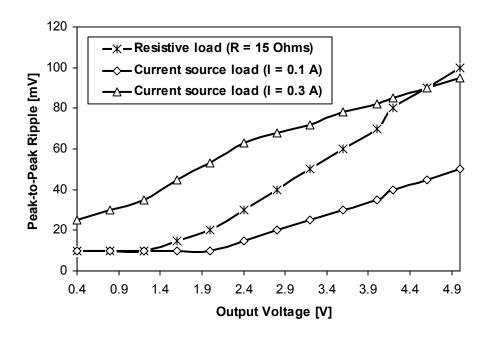

| 7.21. | Percentage output voltage error of the integrated dynamic buck-boost converter ( $V_{OUT}$ = 2.5 V, $R_{LOAD}$ = 15 $\Omega$ ).                                                                                                    | 236 |

| 7.22. | Peak-to-peak output ripple voltage of the integrated dynamic buck-boost converter.                                                                                                                                                 | 237 |

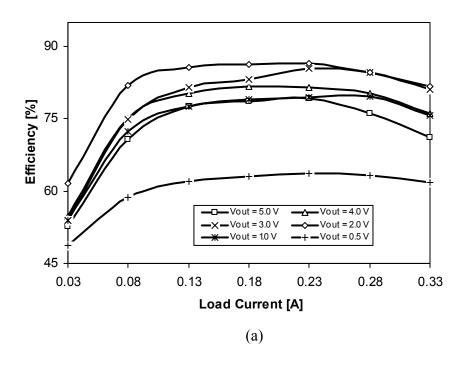

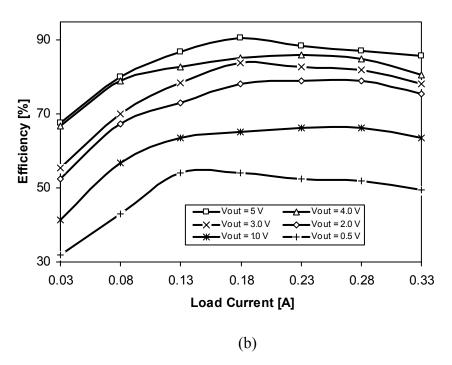

| 7.23. | Measured efficiency characteristic of the integrated buck-boost converter (a) $V_{IN}$ = 2.5 V and (b) $V_{IN}$ = 4.2 V.                                                                                                           | 238 |

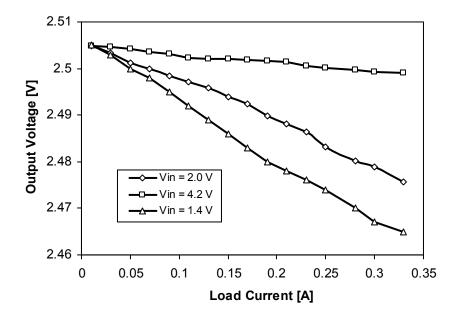

| 7.24. | Measured load (LDR) and line regulation (LNR) characteristics of the integrated buck-boost converter.                                                                                                                              | 239 |

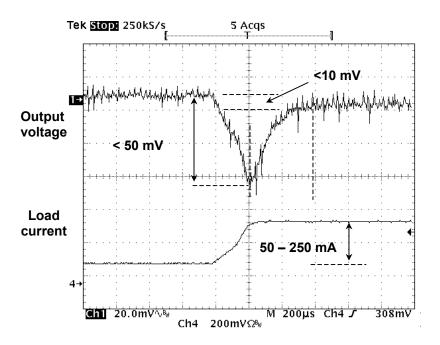

| 7.25. | Measured load transient response of the integrated buck-boost converter.                                                                                                                                                           | 240 |

| 7.26. | Control step-response of the buck-boost converter operating in buck-mode with 1.4 V input supply.                                                                                                                                  | 241 |

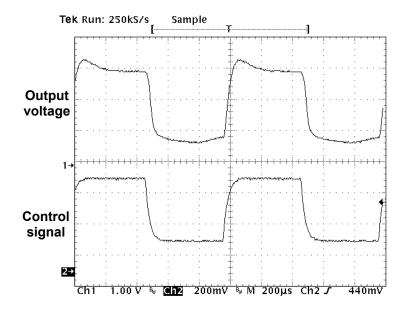

| 7.27. | Control step-response of the buck-boost converter transitioning through buck, buck-boost, and boost mode with a 1.4 V input supply.                                                                                                | 241 |

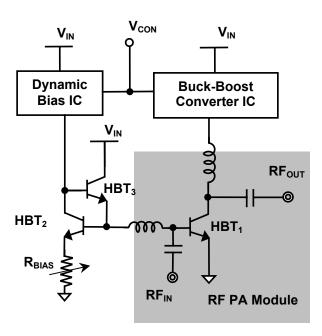

| 7.28. | Schematic of the HBT RF PA with a dynamically adaptive buckboost supply and gate-bias circuit.                                                                                                                                     | 243 |

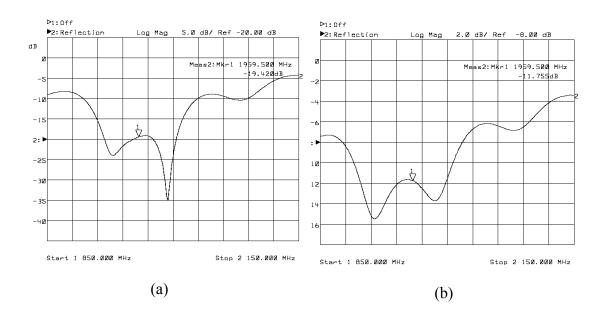

| 7.29. | Input matching characteristics of the 1.96 GHz HBT RF PA with bias current and supply voltage adjustment. The $S_{11}$ parameter of the PA with (a) $V_{DD}$ = 4.5 V, $I_D$ = 220 mA and with (b) $V_{DD}$ = 0.5 V, $I_D$ = 25 mA. | 244 |

| 7.30. | Power gain variation of the 1.96 GHz HBT RF PA with supply voltage and bias current adjustment. The $S_{21}$ parameter of the PA with                                                                                              | 245 |

- (a)  $V_{DD} = 4.5 \text{ V}$ ,  $I_D = 220 \text{ mA}$  and with (b)  $V_{DD} = 0.5 \text{ V}$ ,  $I_D = 25 \text{ mA}$ .

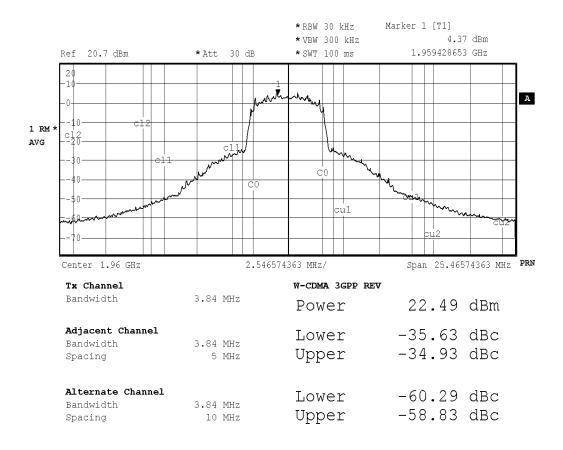

- 7.31. Output spectrum of the experimental WCDMA PA with dynamically adaptive buck-boost supply and bias current control.

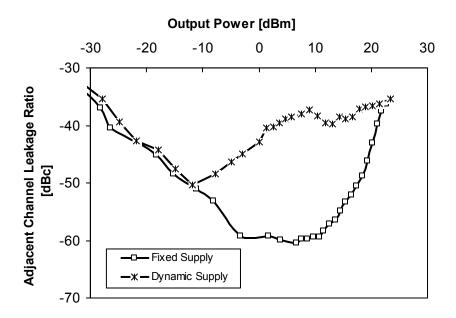

- 7.32. Comparison of adjacent channel leakage ratio of the dynamic- and fixed- supply WCDMA PA.

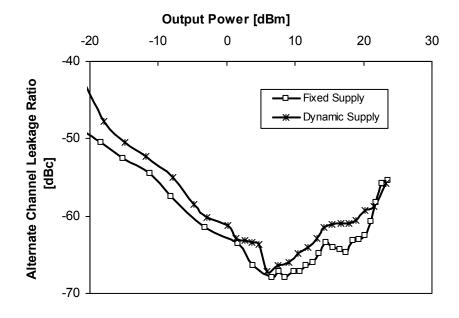

- 7.33. Comparison of alternate channel leakage ratio of the dynamic- and fixed- supply WCDMA PA.

- 7.34. Power gain of the dynamic- and fixed- supply WCDMA PA. 248

- 7.35. Error vector magnitude (EVM) plot of the WCDMA RF PA with a 249 dynamically adaptive buck-boost supply and bias control IC.

- 7.36. Error vector magnitude (EVM) of the dynamic- and fixed-supply PA 250 with QPSK-modulated signal.

- 7.37. Drain efficiency of the dynamic- and fixed-supply WCDMA PA. 251

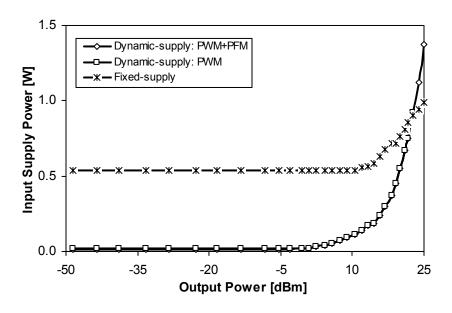

- 7.38. Input supply power of the dynamic- and fixed-supply WCDMA PA. 251

- 7.39. Weighted input power comparison of the dynamic- and fixed-supply WCDMA PA.

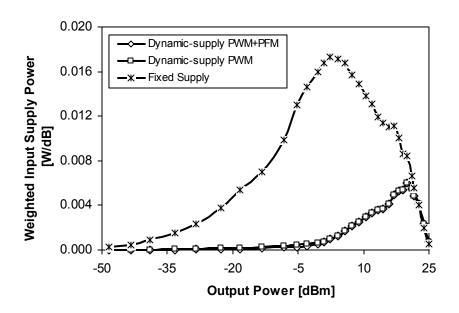

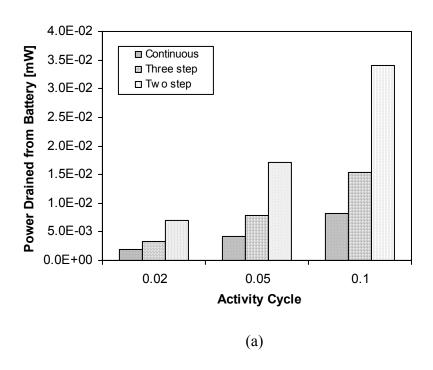

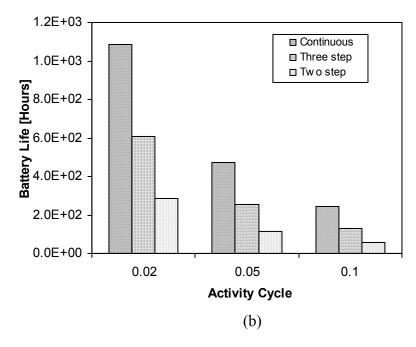

- 7.40. (a) Power drained from the battery and (b) battery life of the dynamic- and fixed-supply PAs for various activity cycles.

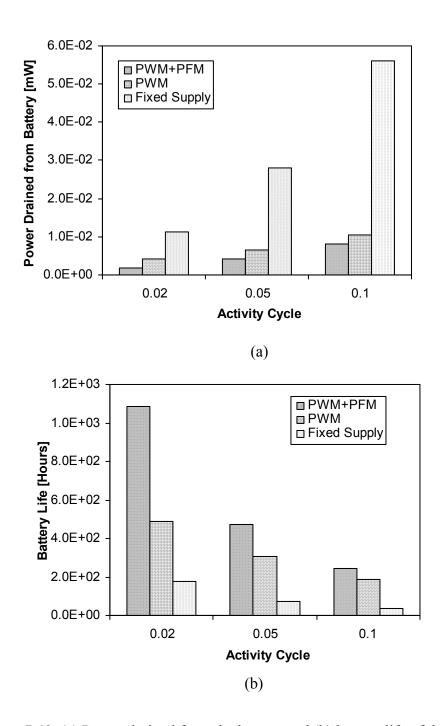

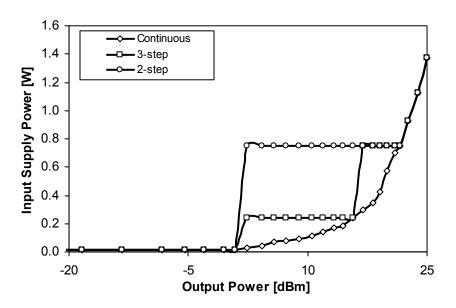

- 7.41. Input power profiles of the continuous 1-dB, discrete two- and three-step control schemes.

- 7.42. Weighted input power profiles of the continuous 1-dB, discrete two-and three-step control schemes.

- 7.43. (a) Power drained from the battery and (b) battery life for alternate control methods for various activity cycles.

### **GLOSSARY**

**2G/3G** Second Generation Third Generation

**ACPR** Adjacent Channel Power Ratio

**ACLR** Adjacent Channel Leakage Power Ratio

**BER** Bit Error Rate

**BJT** Bipolar Junction Transistor

BS Base StationBW Bandwidth

**CCM** Continuous Conduction Mode

**CDMA** Code Division Multiple Access

CTAT Complementary to Absolute Temperature

**DAC** Digital-to-Analog Converter

**DAT** Distributed Active Transformer

**DCM** Discontinuous Conduction Mode

**DMFC** Direct Methanol Fuel Cell

**EDGE** Enhanced Data Rate for GSM Evolution

**EER** Envelope Elimination and Restoration

**ESL** Equivalent Series Inductance

**ESR** Equivalent Series Resistance

**EVM** Error Vector Magnitude

**GaAs** Gallium Arsenide

**GSM** Global System for Mobile Communications

**HBT** Hetero-junction Bipolar Transistor

**HPSK** Hybrid Phase Shift Keying

InP Indium PhosphiteIC Integrated Circuit

ICMR Input Common Mode Range

IF Intermediate Frequency

LAN Local Area Network

**LDMOS** Laterally Diffused Metal Oxide Semiconductor

LDO Low Dropout

LDR Load regulation

LHP Left-half plane

LINC Linear Amplification with Nonlinear Control

**LNR** Line regulation

NADC North American Digital Cellular

**OFDM** Orthogonal Frequency Division Multiplexing

**MOSFET** Metal Oxide Semiconductor Field Effect Transistor

MS Mobile Station

**NPR** Noise Power Ratio

**OCOPSK** Orthogonal Complex Quadrature Phase Shift Keying

**OQPSK** Offset Quadrature Phase Shift Keying

**PA** Power Amplifier

PAR Peak-to-Average Ratio

PCB Printed Circuit Board

**PDF** Probability Density Function

**PM** Phase Margin

**PMU** Power Management Unit

**PTAT** Proportional to Absolute Temperature

**PWM** Pulse Width Modulation

**PFM** Pulse Frequency Modulation

**QPSK** Quadrature Phase Shift Keying

**RF** Radio Frequency

RHP Right-half plane

**SEPIC** Single-ended Primary Inductance Converter

SiGe Silicon-Germanium

SOP System-on-Package

SIP System-in-Package

SOC System-on-Chip

UGF Unity-gain frequency

VCO Voltage Controlled Oscillator

VGA Variable Gain Amplifier

VLSI Very Large Scale Integration

VRM Voltage Regulator Module

WCDMA Wideband Code Division Multiple Access

## **SUMMARY**

Energy-efficient radio frequency (RF) power amplifiers (PAs) are critical and paramount to achieve longer battery life in state-of-the-art portable systems, e.g., cellular phones and multimedia terminals with wireless connectivity, because they typically dominate the power consumption of such devices. The conflicting requirements of higher linearity and increased power efficiency impose an enormous challenge for the PA designers. While many complex schemes are employed to improve the linearity of PAs in base-station applications, handheld devices typically require a different approach, where circuit complexity and form-factor of the device are crucial. When a dedicated power supply is used for the PA, incorporating smart power management functions in the converter supply provides unique possibility of prolonging battery life without any significant increase in circuit complexity, when compared to other approaches requiring RF and intermediate frequency (IF) signal processing.

In this research, a high efficiency linear RF PA with a dynamically adaptive supply and bias current control targeted for code division multiple access (CDMA) and wideband CDMA (WCDMA) is conceived, simulated and experimentally demonstrated with a discrete PCB-level design as well as in integrated circuit (IC) form. The efficiency of the PA is improved by dynamically adjusting its supply voltage and bias current, there by minimizing the quiescent power drained from the source. The supply voltage of the PA is derived from the battery by a noninverting synchronous buck-boost switching regulator, because of its flexible functionality and high efficiency. Investigations conducted in this research concluded that changing the PA supply voltage and current by tracking the input power, instead of following the complete envelope in large bandwidth

wireless applications, can be achieved by a converter with a lower switching frequency and consequently higher light-load efficiency, which translates to prolonged battery life. Experimental results of the discrete prototype implementation of the linear PA system with dynamically adaptive supply shows *more than four times improvement in average efficiency* over a fixed-supply PA.

The dynamically adaptive power management system for a WCDMA RF power amplifier is designed, simulated and experimentally evaluated. AMI's 0.5-µm CMOS process technology through MOSIS is utilized for the fabrication of the integrated system. The integrated buck-boost converter was experimentally verified for functionality with a wide input voltage range, 1.4 – 4.2 V, the lower value of which is limited by the threshold voltage of the process technology and input common-mode range (ICMR) requirements of low-voltage circuits. The converter IC generates an output voltage of 0.4 – 5 V in pulse width modulation (PWM) mode from an input supply of 1.8 – 4.2 V with a maximum output current of 330 mA, while exhibiting a peak efficiency of 90 %. The converter operating in pulse frequency modulation (PFM) mode generates an output voltage of 0.5 V with 50 mA load current, while accurately controlling the output ripple voltage to less than 25 mV over an input supply range of 1.4 – 4.2 V using adaptive on time control. A top-down design approach was followed for deriving the circuit specifications from the system requirements and subsequently various circuit blocks were designed and developed for low voltage operation.

A 25-dBm, 1.96 GHz center frequency, 3.84 MHz baseband bandwidth hybrid-phase-shift-keying (HPSK) modulated WCDMA RF PA is experimentally demonstrated with a dynamically adaptive integrated CMOS dual-mode buck-boost supply and bias current control IC. The dual-mode (i.e., PWM and PFM) converter increased the battery life performance of the PA system as much as *five times* compared to a fixed-supply system and *twice* compared to a converter operating in only PWM control, assuming that the PA remains in active mode for 2 % of the total time and remains in the standby mode otherwise. The experimental PA system developed in this research is verified for functionality and performance over a 1.8 – 4.2 V supply voltage range, rendering its suitability for single-cell state-of-the-art Li-ion batteries and two-cell stacked low-cost

NiCd/NiMH battery, thus providing a truly generic and low voltage solution. Furthermore, the low voltage circuit design techniques developed in this research are also applicable beyond the realm of integrated power management applications and can be used in the general arena of analog integrated circuit design.

#### **CHAPTER I**

#### INTRODUCTION

In the next generation, high-performance, portable hand-held devices there is a great interest in accommodating the challenging demands of high-speed data transmission, e.g., software, screen technology, and data-processing bandwidth [1]. Consequently, the higher bandwidth and increased power requirement at the antenna in these systems demand efficient power management solutions to prolong battery life. The power amplifier (PA) in a portable radio frequency (RF) transmitter drives the load (antenna) with sufficient energy such that the resulting electromagnetic signals reach the base station with higher power level than the noise floor. Energy-efficient PAs are critical to increase battery life in state-of-the-art RF transceivers used in portable communication devices, e.g., cellular phones, because they typically dominate and determine the power consumption characteristics of such devices. Unlike the second-generation (2G) systems employing Global Systems for Mobile Communications (GSM) where nonlinear PAs are used, the spectrally efficient digital modulation schemes, e.g., code-division-multiple-access (CDMA), require linear PAs to preserve the fidelity of the transmitted signal without causing unnecessary interference in the adjacent channels.

Linearity of a PA is typically achieved by increasing its bias current, thereby drawing more power from the supply for a fixed output power and consequently degrading its power efficiency. On the other hand, PAs exhibiting high efficiency are nonlinear in nature [2]. Therefore, the design of an energy-efficient PA remains an extremely challenging frontier in wireless communication research. This chapter brings about the role and requirements of energy-efficient linear PAs in the domain of portable

power management with the aim of improving battery life in feature-rich handheld devices. The performance specifications of RF PAs, especially linearity and efficiency are introduced. A brief summary of state-of-the-art rechargeable batteries and the highly promising fuel cells are also discussed, while presenting an overview of dynamically adaptive power supplies. The objectives of the research are then identified according to the state-of-the-art and future portable market demands for wireless handsets using CDMA and Wide-band CDMA (WCDMA) wireless standards.

# 1.1 Role of Efficient Linear RF Power Amplifiers in Portable Applications

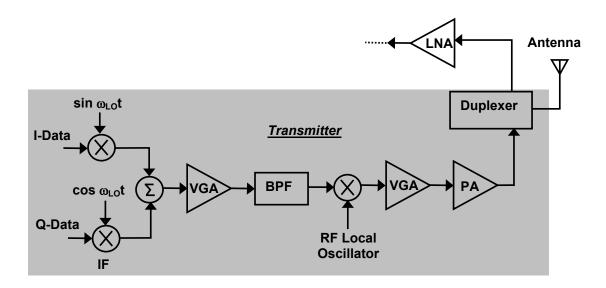

Portable devices with wireless connectivity require a radio frequency transmitter to send information to the nearest base station, which subsequently resends the data to the desired destination via another wired or wireless network. In the wireless transmitters, the RF PA is the final interface between the baseband and RF signal processing components and the antenna. Figure 1.1 offers a simplified block-level schematic of a radio transmitter employing a digital modulation scheme. The baseband in-phase (I) and quadrature-phase (Q) data are modulated to generate an intermediate frequency (IF) signal, which is subsequently amplified by a variable gain amplifier (VGA). The resulting signal is processed through a band pass filter (BPF) and up-converted into an RF signal by using a mixer and a local oscillator. The PA amplifies the modulated RF signal and increases the transmitted signal power level at the antenna such that faithful reception is accomplished at the base station. The variable gain amplifiers, by adjusting their gains, control the signal level at the PA input, thereby ultimately controlling the antenna power level.

Conceptually, the role of a PA appears to be rather simple, to amplify the input signal and to deliver the resulting power to the antenna. However, RF PAs are extremely critical components in the radio transmitters used in the wireless communication systems because they determine the final quality of the waveform. The PA in a RF transmitter drives the load (antenna) with sufficient energy to ensure the resulting electromagnetic signals reach the base station with enough strength, that is to say, well above the noise

level. This must be done with minimum distortion to the RF signal to prevent spurious signals from interfering with other channels. Therefore, the RF PAs used in transmitters require very high linearity to preserve modulation accuracy and limit the spectrum regrowth. PAs typically dissipate more power than any other circuit block in a mobile radio [3]. The PA is therefore a key block, as far as cost, power consumption, reliability, and system performance requirements are concerned [2].

Figure 1.1. Block-level representation of a typical wireless handset transmitter section with a digital modulation scheme.

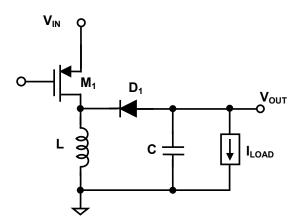

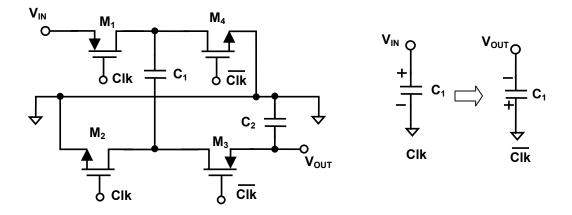

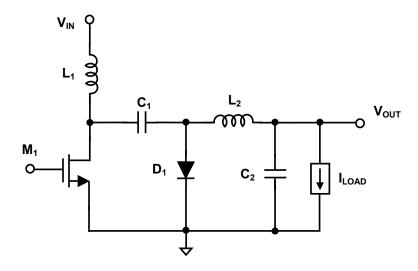

To improve operational time of a battery-powered wireless transceiver, it is desirable to have a transmitter section that works at its highest possible efficiency. Unfortunately, as one strives to increase power efficiency by operating the PA in different regions of its load-line, the output distortion produced by the solid-state device nonlinearities often becomes excessive and a limiting factor for the overall design. Nonlinear PAs achieve higher efficiency at the expense of degraded linearity. The required linearity level desired for the PA is highly dependant on the application environment. Wireless standards employing modulation schemes with constant envelope RF signals, e.g., GSM, use nonlinear PAs because the information is transmitted in the phase of the signal, and accurate transmission of amplitude is therefore not required. On