## DESIGN AND RELIABILITY OF HIGH DYNAMIC RANGE

## **RF BUILDING BLOCKS IN**

# SOI CMOS AND SIGE BICMOS TECHNOLOGIES

A Thesis Presented to The Academic Faculty

by

Anuj Madan

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2011

# **COPYRIGHT 2011 BY ANUJ MADAN**

## DESIGN AND RELIABILITY OF HIGH DYNAMIC RANGE

## **RF BUILDING BLOCKS IN**

# SOI CMOS AND SIGE BICMOS TECHNOLOGIES

Approved by:

Dr. John D. Cressler, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. John Papapolymerou School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Sudipto Chakraborty Adjunct Faculty School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Bruno Frazier School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Rosario Gerhardt School of Materials Science and Engineering *Georgia Institute of Technology*

Date Approved: October 7<sup>th</sup>, 2011

# Dedicated to the Divine's Creation

BLISS, LOVE & JOY

## ACKNOWLEDGEMENTS

At the very outset, I would like to express my deepest gratitude to my advisor, Prof. John D. Cressler for his guidance and support in research and personal life. I am especially appreciative of the amount of freedom he has extended to me over the years, in terms of research topics and areas of investigation.

I would like to sincerely thank the other members of my thesis advisory committee, Dr. John Papapolymerou and Dr. Sudipto Chakraborty.

I would like to acknowledge the support of Defense Threat Reduction Agency (DTRA) and Semiconductor Research Consortium (SRC) for sponsoring part of this research. I would also like to thank Mike McPartlin, Greg Babcock, Christophe Masse, Ray Lam, Bill Vaillancourt, Steve Kovacic, and Peter Gammel at SiGe Semiconductor for providing me the opportunity to complete my thesis and supporting odd hours at work during thesis writing days. I would also like to thank Dr. Greg Freeman and Dr. Alvin Joseph at IBM Microelectronics for providing devices and design support. My work has significantly improved from their inputs and suggestions too.

I am grateful to the ECE staff, especially Lisa Gardner and Joi Adams for providing logistics support to enable this research. Special thanks to my colleagues Dr. Lance Kuo, Dr. Jon Comeau, Dr. Ramkumar Krithivasan, Dr. Tushar Thrivikraman, Dr. Aravind Appaswamy, Dr. Marco Bellini, Dr. Akil Sutton, Dr. Peng Cheng, Dr. Jiahui Yuan, Dr. Curtis Grens, Dr. Laleh Najafizadeh, Sachin Seth, Rajan Arora, John Poh, Ted Wilcox, Stan Phillips, Ryan Diestelhorst, , Kurt Moen, Steven Finn, Nand Jha, Prabir Saha, Gustavo Espinel, Steven Horst, Rob Schmidt, Partha Chakraborty, Adilson Cardoso, Duane Howard, Subu Shankar, Nelson, Richie Mills and other members of SiGe research team.

Finally, I would like to thank my family for their support and encouragement. I am grateful to my father who always plays an encouraging role in my research.

# TABLE OF CONTENTS

|                                               | Page       |

|-----------------------------------------------|------------|

| ACKNOWLEDGEMENTS                              | iv         |

| LIST OF TABLES                                | viii       |

| LIST OF FIGURES                               | ix         |

| SUMMARY                                       | xvi        |

| <u>CHAPTER</u>                                |            |

| 1 INTRODUCTION                                | 1          |

| Motivation                                    | 1          |

| Technology                                    | 3          |

| Switch and LNA Design                         | 8          |

| 2 THE ROLE OF BODY CONTACTS IN SOI            | 14         |

| Introduction                                  | 14         |

| Radiation Reliability                         | 15         |

| Impact on Linearity                           | 26         |

| 3 INTEGRATED S-PARAMETER AND LINEARITY CHARAC | TERIZATION |

|                                               | 29         |

| Introduction                                  | 29         |

| Measurement Results                           | 32         |

| Simulations and Calculations                  | 36         |

| 4 HIGH LINEARITY RF SWITCH DESIGN             | 38         |

| CMOS RF Switch Design                         | 38         |

| SiGe HBT RF Switch Design                     | 44         |

| 5 RF SWITCH RELIABILITY: CMOS VS SIGE BICMOS  | 55         |

| CMOS RF Switch Reliability             | 55  |

|----------------------------------------|-----|

| SiGe BiCMOS RF Switch Reliability      | 65  |

| 6 HIGH DYNAMIC RANGE SOI CMOS LNA      | 71  |

| Introduction                           | 71  |

| Design of the CMOS LNA                 | 72  |

| Experimental Results                   | 73  |

| Summary                                | 79  |

| 7 SWITCH AND LNA INTEGRATION FOR FEICs | 80  |

| Introduction                           | 80  |

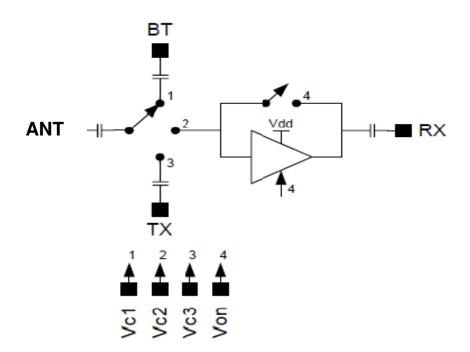

| 180 nm CMOS Technology                 | 82  |

| RF Front-End IC Architecture           | 83  |

| Design Methodology                     | 85  |

| Circuit Implementation                 | 93  |

| Results and Discussions                | 94  |

| Summary                                | 102 |

| FUTURE WORK                            | 104 |

|                                        |     |

| REFERENCES                             | 105 |

| VITA                                   | 119 |

# LIST OF TABLES

|                                                                 | Page |

|-----------------------------------------------------------------|------|

| Table 1: Performance comparison between recently published LNAs | 74   |

| Table 2: Controller logic for FEIC operation                    | 80   |

| Table 3: Summary of 2.4 GHz CMOS switches                       | 97   |

# LIST OF FIGURES

| Figure 1. Block diagram of a typical wireless transceiver depicting the RF front-          |

|--------------------------------------------------------------------------------------------|

| end                                                                                        |

| Figure 2. Dynamic range of a typical transceiver or wireless communication system.         |

|                                                                                            |

| Figure 3. Illustration of price-performance comparison between BiCMOS (HBTs) and           |

| CMOS (NFETs)                                                                               |

| Figure 4. CMOS scaling parameters showing the concepts of "ideal" and "real"               |

| scaling5                                                                                   |

| Figure 5. Top view schematic and cross-section of two widely used body contacting          |

| schemes in SOI MOSFETs7                                                                    |

| Figure 6. Section of a RF front-end, highlighting the key performance metrics for a front- |

| end switch                                                                                 |

| Figure 7. Comparison of (a) non-isolated switch and (b) triple-well isolated n-MOSFET      |

| switch with floating body11                                                                |

| Figure 8. Major processes responsible for inducing TID damage in MOSFET 14                 |

| Figure 9. Transfer characteristics of the devices at different accumulated dose points for |

| 63 MeV protons                                                                             |

| Figure 10. Possible radiation-induced leakage paths along the (a) surface of BOX, (b) STI  |

| sidewalls                                                                                  |

| Figure 11. Enhanced degradation in off-state leakage when gate was biased at 1.0 V         |

| during proton irradiation                                                                  |

| Figure 12. Normalized change in off-state leakage as a function of total accumulated     |

|------------------------------------------------------------------------------------------|

| proton dose                                                                              |

| Figure 13. Transfer characteristics of a body-contacted device at different accumulated  |

| proton doses                                                                             |

| Figure 14. Back-gate characteristics of body-contacted device at different accumulated   |

| proton doses                                                                             |

| Figure 15. Impact of CMOS scaling on the device linearity27                              |

| Figure 16. Comparison of linearity between floating-body and body-contacted devices in   |

| a 45nm CMOS on SOI technology                                                            |

| Figure 17. Block diagram of a conventional two-tone linearity measurement setup with     |

| spectrum analyzer                                                                        |

| Figure 18. Block diagram of the test-setup proposed for two-tone linearity measurements  |

| integrated with S-parameter measurements                                                 |

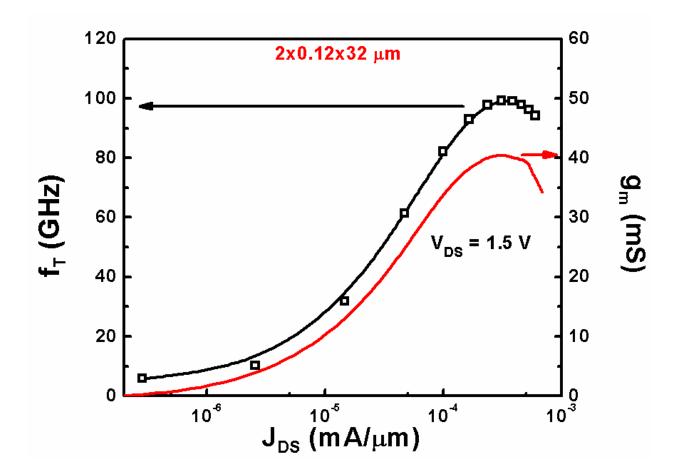

| Figure 19. Peak $f_T$ performance of the device under test and its correlation with gm33 |

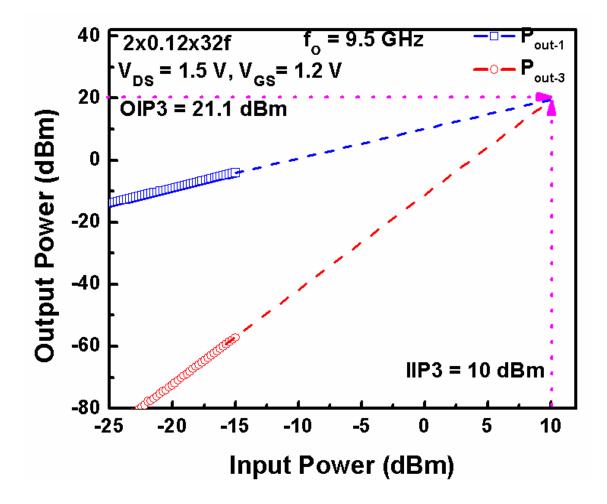

| Figure 20. Measured fundamental and third-order harmonics for the device. IIP3 and       |

| OIP3 are extrapolated for a fixed bias                                                   |

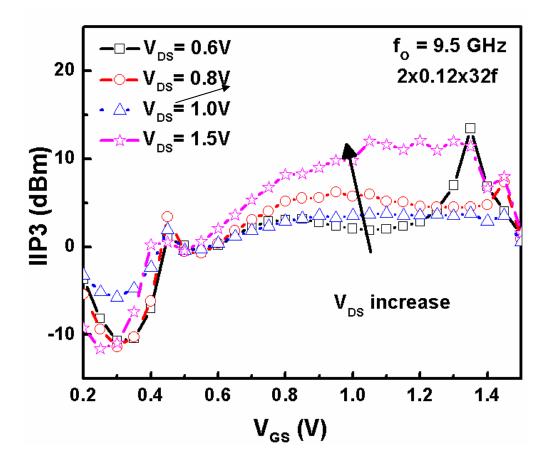

| Figure 21. Measured bias dependence of IIP3 as a function of gate voltage, at different  |

| drain voltages                                                                           |

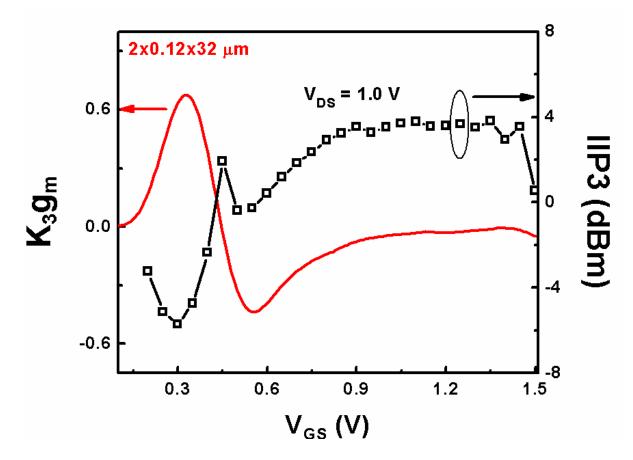

| Figure 22. K3gm and its correlation with linearity sweet spot                            |

| Figure 23. Comparison of measured IIP3 with harmonic balance simulations run using     |

|----------------------------------------------------------------------------------------|

| ADS simulation tool                                                                    |

| Figure 24. Schematic of single-pole single-throw (SPST) switch using triple-well n-    |

|                                                                                        |

| MOSFET as series device                                                                |

| Figure 25. On-state S21 of series-shunt Single-Pole Single-Throw (SPST) RF switches    |

| optimized for X-band operation                                                         |

|                                                                                        |

| Figure 26. Off-state S21 of series-shunt Single-Pole Single-Throw (SPST) RF switches   |

| optimized for X-band operation                                                         |

|                                                                                        |

| Figure 27. Record P1dB compression point of a CMOS based SPST switch at 9.5            |

| GHz43                                                                                  |

| Eigen 20 HD2 - 6.25 dD m is many a family should start the barry CDCT - 4.0.5 CH - 4.4 |

| Figure 28. IIP3 of 25 dBm is measured for a series-shunt stack type SPST at 9.5 GHz44  |

| Figure 29. Schematic of the inverse-mode bipolar transistor as an RF switch            |

|                                                                                        |

| Figure 30. Insertion Loss of the SiGe BiCMOS RF switches in both forward- and          |

| inverse-mode orientation48                                                             |

|                                                                                        |

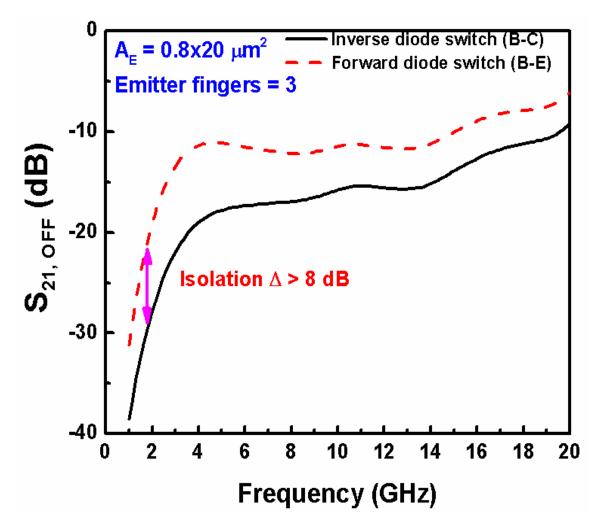

| Figure 31. Improved isolation in the inverse-mode switch compared to the forward-mode  |

| switch across a wide frequency range                                                   |

|                                                                                        |

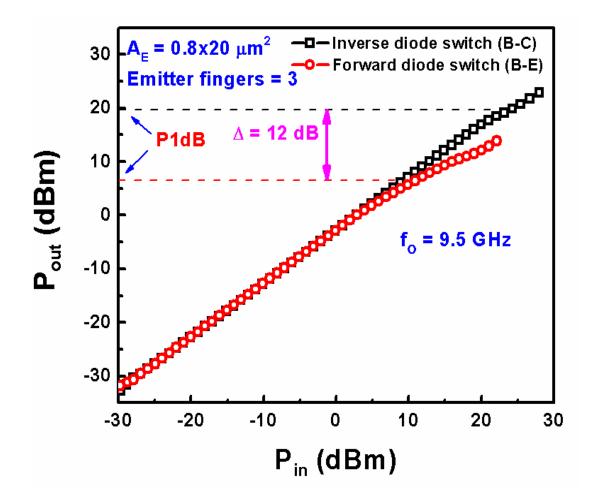

| Figure 32. A 12 dB improvement in P1dB compression point of the switch through         |

| inverse-mode operation is obtained                                                     |

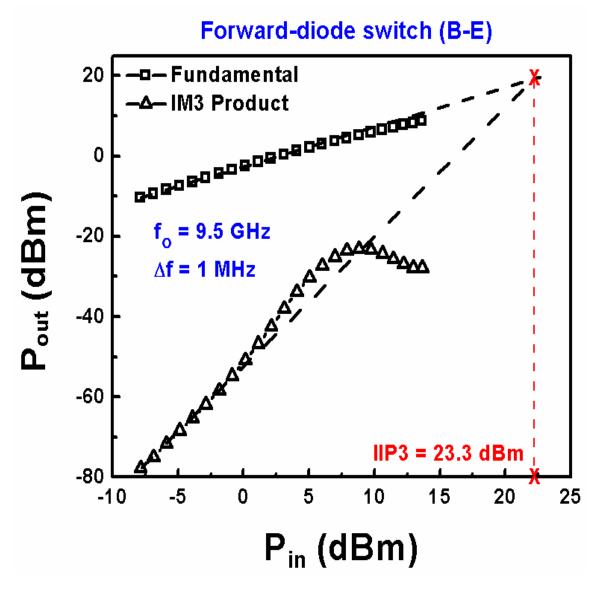

| Figure 33. Extrapolated IIP3 using two-tone characterization of the forward-mode RF      |

|------------------------------------------------------------------------------------------|

| switch                                                                                   |

|                                                                                          |

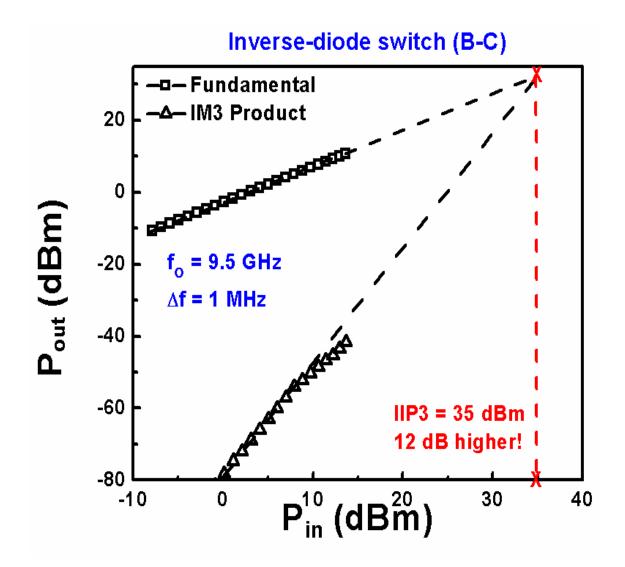

| Figure 34. Using the inverse-mode switch topology, 12 dB improvement in IIP3 is          |

| measured over standard switch                                                            |

|                                                                                          |

| Figure 35. Single-Pole Double-Throw (SPDT) RF switch design topology used for            |

| reliability analysis                                                                     |

|                                                                                          |

| Figure 36. Block diagram of the setup used for applying RF stress and measuring S-       |

| parameters                                                                               |

|                                                                                          |

| Figure 37. Insertion Loss of standalone DUT after RF-Stress. Degradation is observed at  |

| 33 dBm (inset) before device fails                                                       |

|                                                                                          |

| Figure 38. Isolation of the Series Transistor (M2) increases after RF stressing up to 36 |

| dBm input power                                                                          |

|                                                                                          |

| Figure 39. Input matching of the series transistor (M2) changes until the transistor     |

| behaves as an electrical "open" terminal after 36 dBm of RF stressing is applied60       |

|                                                                                          |

| Figure 40. Output Matching of the DUT changes with RF stress                             |

|                                                                                          |

| Figure 41. Gate-Breakdown induced by high RF power at the drain of the device            |

| produces failure of the transistor as an RF switch                                       |

|                                                                                          |

| Figure 42. Impact of RF stress on isolation of SPDT switch in 180nm and 130nm CMOS       |

| technologies                                                                             |

| Figure 43. RF stress degrades the insertion loss of the SPDT switch in 180nm and          |

|-------------------------------------------------------------------------------------------|

| 130nm CMOS technologies64                                                                 |

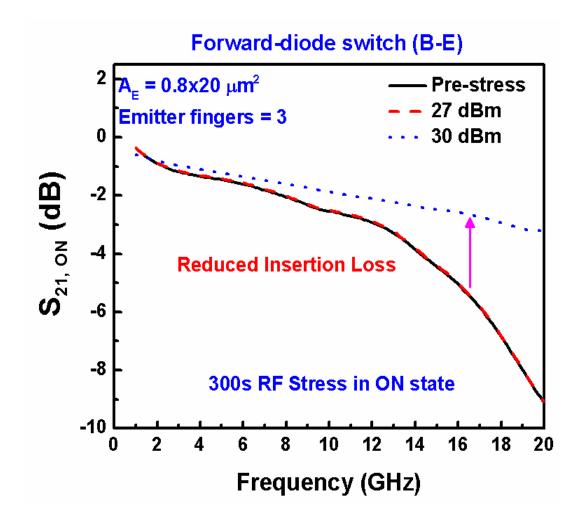

| Figure 44. The insertion-loss of forward-mode switch improves after stressing at 30 dBm   |

| RF power for 300 seconds                                                                  |

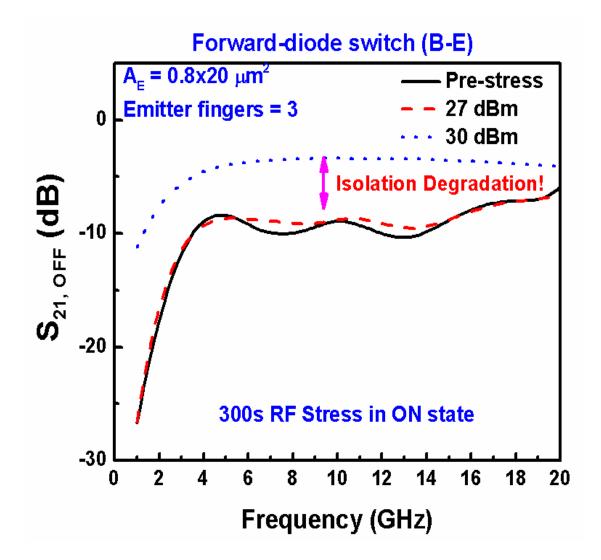

| Figure 45. The isolation of the switch is considerably degraded after stressing at 30 dBm |

| RF power due to the junction damage at the base-emitter interface                         |

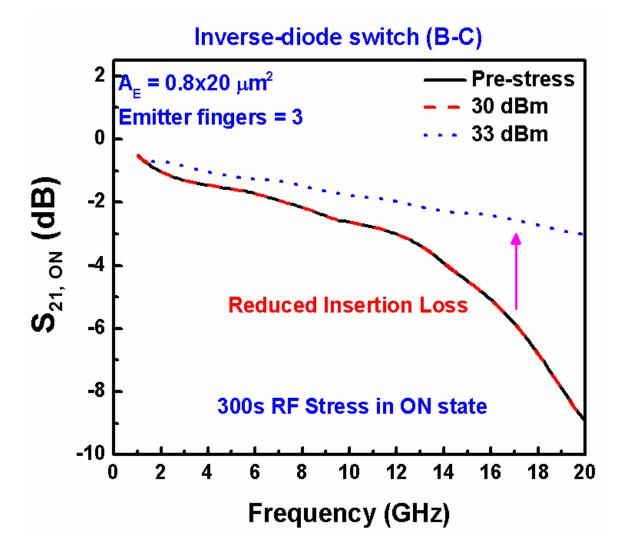

| Figure 46. Insertion loss of inverse-mode switch improves, but after stressing at 33 dBm  |

| RF power for 300 seconds. There is no change after stressing at 30 dBm RF power68         |

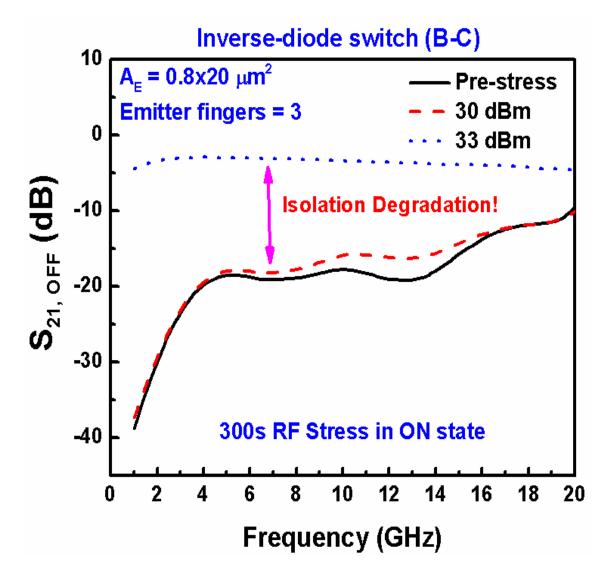

| Figure 47. Isolation degradation similar to forward-mode switch is observed, indicating   |

| failure of the switch at 33 dBm RF input power                                            |

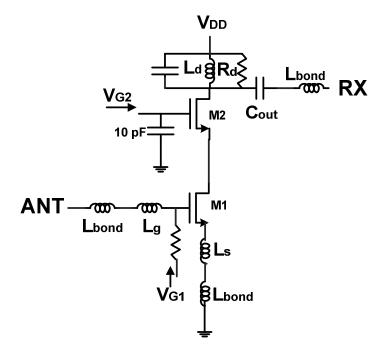

| Figure 48. Circuit schematic of the inductively-degenerated cascode LNA73                 |

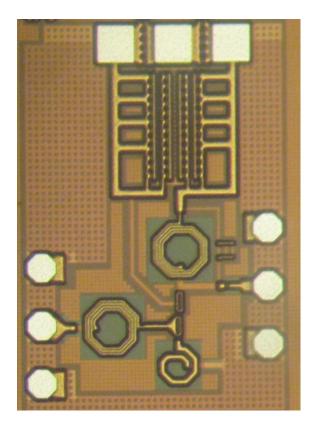

| Figure 49. Die photograph of the fabricated LNA74                                         |

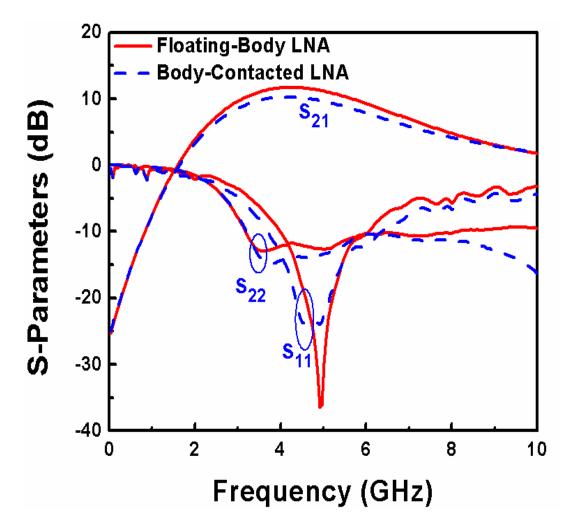

| Figure 50. S-parameters of floating-body and body-contacted LNA with integrated input     |

| and output matched to 50 $\Omega$                                                         |

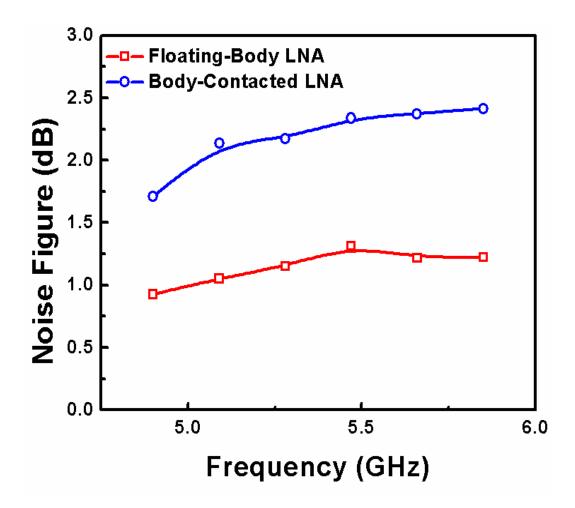

| Figure 51. Measured NF of the LNA after de-embedding the input board loss76               |

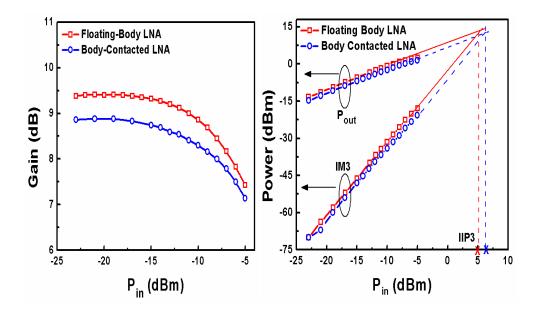

| Figure 52. (a) Measured input P1-dB compression point of LNAs, and (b) comparison of      |

| measured harmonics and IIP3 of the floating-body and body-contacted, single-stage,        |

| inductively degenerated, cascode LNA77                                                    |

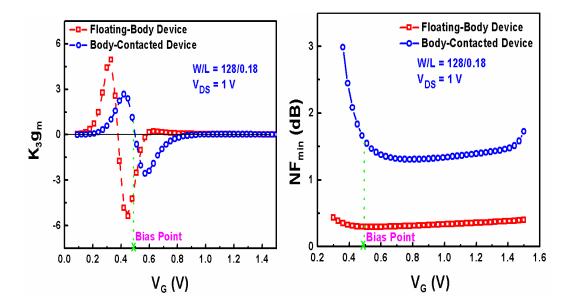

| Figure 53. (a) Simulated K3gm, and (b) $NF_{min}\ comparison$ of the floating-body and body- |

|----------------------------------------------------------------------------------------------|

| contacted input device of the LNA77                                                          |

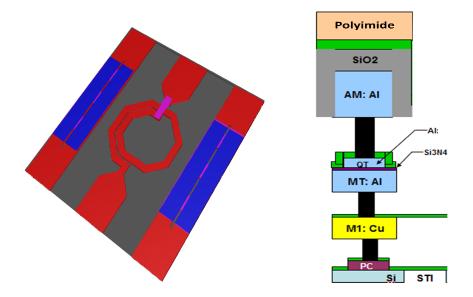

| Figure 54(a). 3-D EM view of the inductor, and (b) back-end-of-line metal layers used in     |

| the three metal layer process                                                                |

| Figure 55. Architecture of a switch-LNA WLAN front-end with integrated bluetooth             |

| functionality                                                                                |

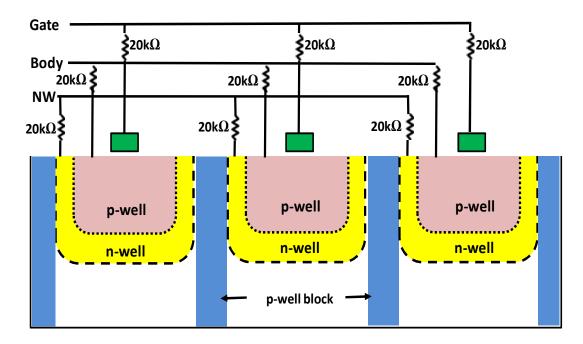

| Figure 56. A stack of three series transistors with isolated gate, p-well and n-well using   |

| $20 \text{ k}\Omega$ polysilicon resistors                                                   |

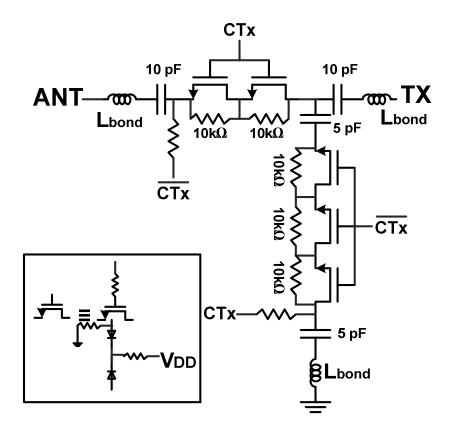

| Figure 57. Series-shunt stacked FET switch topology with cross-biasing for the transmit      |

| switch                                                                                       |

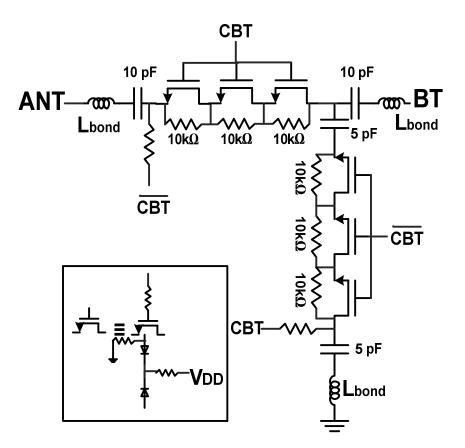

| Figure 58. Series-shunt stack topology of the bluetooth switch with 3-series and 3-shunt     |

| stack of FETs90                                                                              |

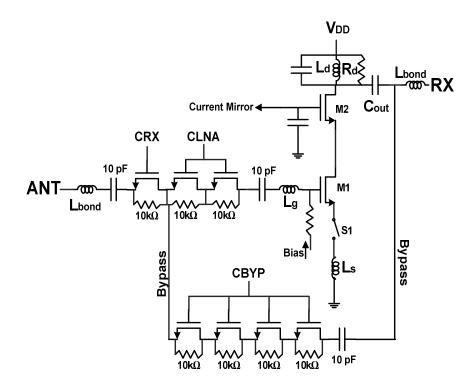

| Figure 59. Schematic of the receive path with high-gain mode (switch + LNA) and              |

| bypass mode                                                                                  |

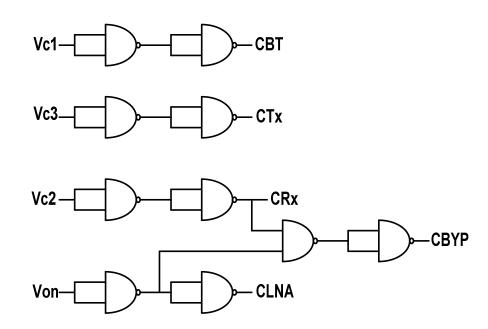

| Figure 60. NAND gate based logic-decoder for switching between FEIC states93                 |

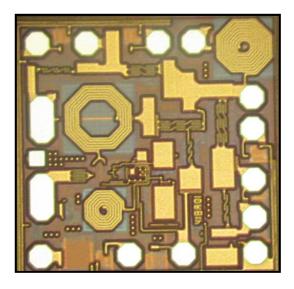

| Figure 61. Die micrograph of the FEIC94                                                      |

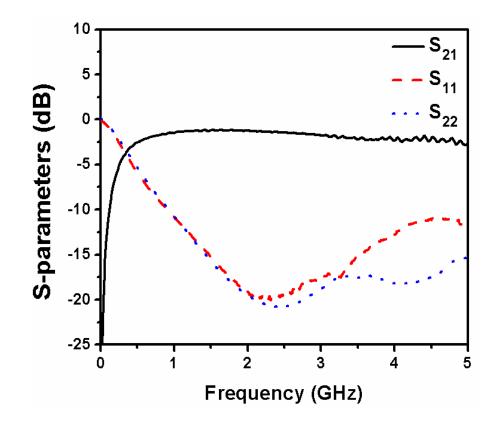

| Figure 62. S-parameters of the transmit switch95                                             |

| Figure 63. S-parameters of the bluetooth switch96                                            |

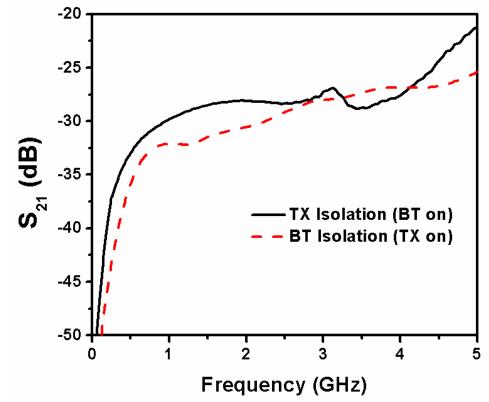

| Figure 64. Isolation between transmit and bluetooth throws                                   |

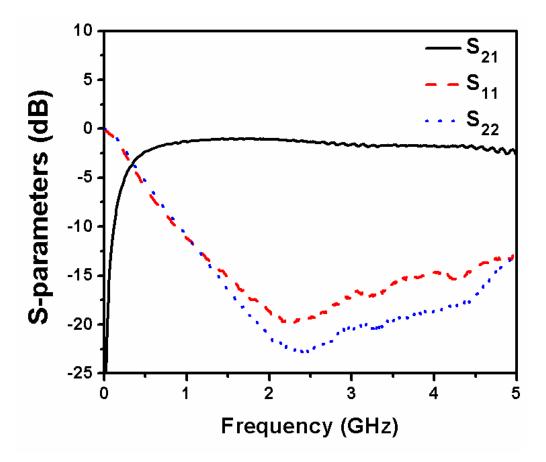

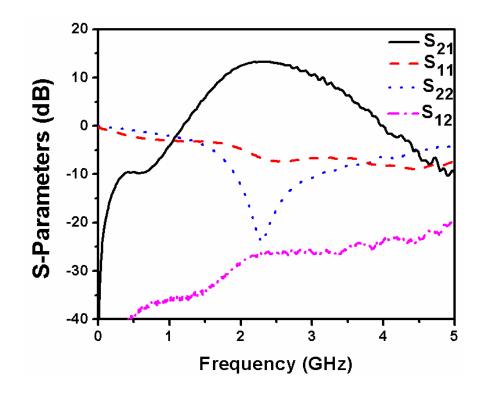

Figure 65. Measured small-signal parameters of the receive path in high gain mode......97

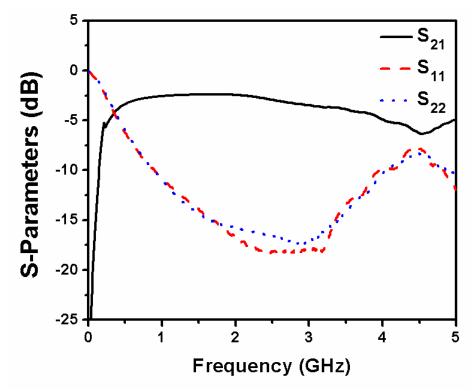

| Figure 66. Measured small-signal parameters of the receive path in bypass or low-gain  |

|----------------------------------------------------------------------------------------|

| mode97                                                                                 |

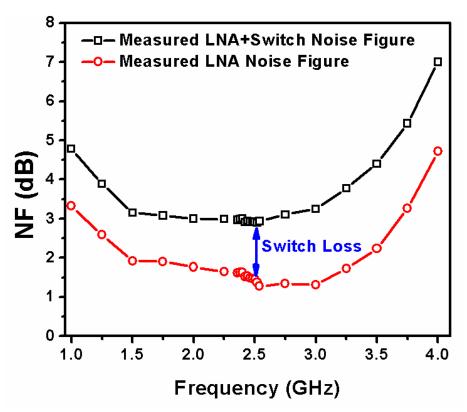

| Figure 67. Noise Figure of the full receive path and the LNA. The LNA NF is 1.5 dB at  |

| 2.4 GHz                                                                                |

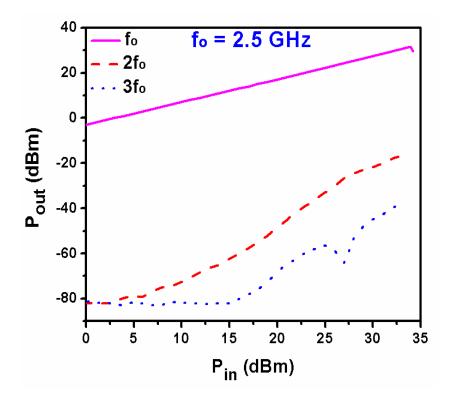

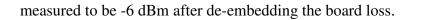

| Figure 68. Measured 1-dB compression point and harmonics of the transmit switch99      |

| Figure 69. Measured 1-dB compression point and harmonics of the bluetooth switch100    |

| Figure 70. Measured 1-dB compression point and harmonics of the receive switch100      |

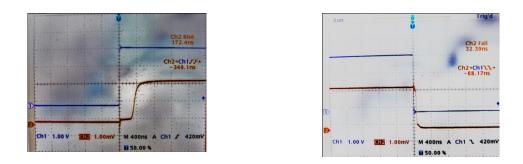

| Figure 71. (a) Turn-on, and (b) turn-off time measurements for the switch paths at 2.5 |

| GHz with an input power of +5 dBm101                                                   |

## SUMMARY

The objective of the proposed research is to understand the design and reliability of RF front-end building blocks using SOI CMOS and SiGe BiCMOS technologies for high dynamic-range applications. This research leads to a comprehensive understanding of dynamic range in SOI CMOS devices and contributes to knowledge leading to improvement in overall dynamic range and reliability of RF building blocks.

While the performance of CMOS transistors has been improving naturally with scaling, this work aims to explore the possibilities of improvement in RF performance and reliability using standard layouts (that don't need process modifications). The totalionizing dose tolerance of SOI CMOS devices has been understood with extensive measurements. Furthermore, the role of body contacts in SOI technology is understood for dynamic range performance improvement. In this work, CMOS low-noise amplifier design for high linearity WLAN applications and its integration with RF switch on the same chip is presented. The LNA and switches designed provide state-of-the-art performance in silicon based technologies.

Further, the work aims to explore applications of SiGe HBT in the context of highly linear and reliable RF building blocks. The RF reliability of SiGe HBT based RF switches is investigated and compared with CMOS counterparts. The inverse-mode operation of SiGe HBT based switches is understood to give considerably higher linearity.

A significant portion of this research has been published in peer-reviewed literature [7, 36, 38, 72, 73, 74, 75, 76].

xvi

### CHAPTER 1

## **INTRODUCTION**

#### 1.1 Motivation

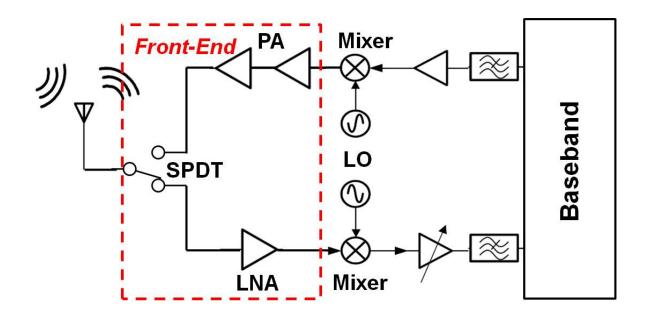

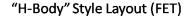

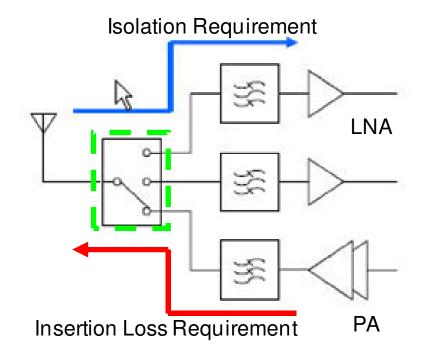

Radio-frequency (RF) front-end is a key building block in any wireless or communication system. A typical RF front-end includes an RF switch for transmit and receive mode switching, low-noise amplifier on the receive side, and power amplifier on the transmit side. The push for increasingly higher data rates, low-cost technology, and compact design drives much of the demand in wireless and supporting technologies that comprise the front-end. The challenging RF circuits, in particular, the RF front-end prove to be a limiting factor in reducing bandwidth, dynamic range, and sensitivity of the wireless communication system.

The basic topology of a RF transceiver is shown in Figure 1. A crucial component of the transceiver architecture is the RF front-end. For example, the power handling capability of the RF switch limits the amount of power that can be transmitted through the system. Moreover, the insertion loss of the switch also adds to the noise-figure of the receiver. The LNA has a direct impact on the receiver signal-to-noise ratio (SNR) and thus can restrict the maximum data rate, receiver sensitivity, and other receiver parameters. For wireless receivers, the SNR limits the minimum detectable signal and therefore limits the receiver dynamic range.

Figure 1. Block diagram of a typical wireless transceiver depicting the RF front-end.

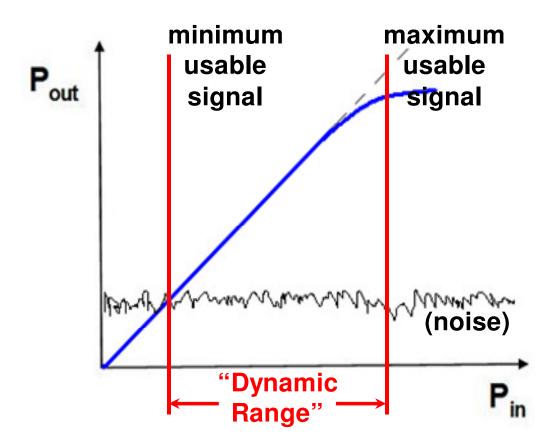

"Dynamic Range" is defined as the power spanning from minimum to maximum usable signal levels in any wireless communication system. In a RF transceiver or frontend, the upper bound of dynamic range is typically limited by the functional block distortion characteristics and the lower bound is limited by the noise floor (or noise figure) of the system, as illustrated in Figure 2.

Figure 2. Dynamic range of a typical transceiver or wireless communication system.

#### **1.2 Technology**

CMOS technology has, in recent years, emerged as a genuine contender for RF and analog applications. These markets have traditionally been outside the scope of the relatively low-cost silicon-based technologies, and have been dominated by III-V and SiGe BiCMOS technologies. With the need for low-power and low-cost wireless solutions for consumer electronics, the historical demand for compound semiconductors and high-performance processes has been largely reduced for consumer applications. Instead, the focus of industry has moved towards using CMOS technology for analog baseband and RF front-end modules by integrating multiple functions on the same chip and package, using System-on-Chip (SoC) and System-on-Package (SoP) approaches, respectively. CMOS technology allows the integration of digital functionalities which can control high-frequency and high-speed analog circuits and digital compensation for non-ideal effects.

**Relative Price**

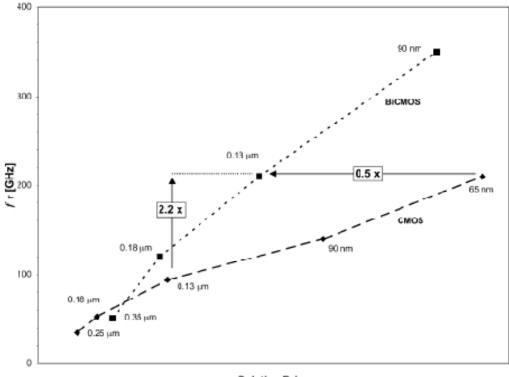

Figure 3. Illustration of price-performance comparison between BiCMOS (HBTs) and CMOS (NFETs) [12].

RF-CMOS remains the optimal choice for low-cost RF applications where the SiGe HBT performance is not fully required, due to thr lower mask count in CMOS process. A typical RF-CMOS technology can be considered primarily as an enhancement on the base of digital CMOS with improved RF models, design automation, and passive devices built from the existing base process. There may be additional process adders (masks) to improve the FET performance from a RF standpoint. Typically, higher resistivity or SOI substrate is another enhancement introduced in the RFCMOS process relative to the base CMOS technology. High-performance features such as MIM capacitor, thick analog metal for inductors, high-gain FETs, hyperabrupt varactors, etc., are modularly introduced and can be utilized with appropriate cost-performance tradeoff considerations. Integrating a bipolar transistor with CMOS adds masks and processing steps which necessarily raises the cost of producing the wafer. Figure 3 compares the relative cost and performance of BiCMOS and CMOS technologies by looking at the of the NFET and SiGe NPN for various technology nodes [12].

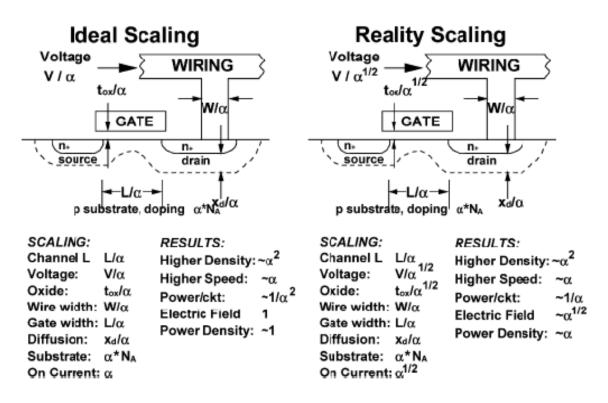

Figure 4. CMOS scaling parameters showing the concepts of "ideal" and "real" scaling [12].

Figure 4 summarizes the "ideal" and "real" CMOS scaling methodology. All dimensions of the device are scaled with the same scaling factor ' $\alpha$ ' in ideal scaling methodology to ensure that the electric field remains constant from one generation to the other. The reality scaling guidelines in Figure 4 illustrate the two departures from ideal scaling methodology i.e. supply voltage (V<sub>DD</sub>) and gate-oxide thickness (t<sub>ox</sub>). Thus, both performance and density increase but at a cost of the power density.

As a result of CMOS, the high-frequency performance of CMOS devices has undergone considerable improvement, resulting in devices with peak cutoff frequency (f<sub>T</sub>) currently greater than 450 GHz [1]. This impressive improvement in speed provides RF enablement to a simple digital CMOS technology, while being a low-cost adder. A combination of process innovations and lithographic scaling has been used to improve CMOS performance. These innovations include SOI substrates, strained silicon layers for mobility enhancement, double gated devices and fully-silicided or metal gates [2, 3]. Among available choices, SOI technology provides added advantages over bulk CMOS technology by minimizing parasitic, improving isolation, decreasing leakage, improving short-channel effects, and enhancing single event upset (SEU) tolerance. This performance improvement, combined with high-density integration capability, cost effectiveness and process maturity makes SOI CMOS technology attractive for integrating both RF front-ends and base-band analog/digital circuitry onto a single chip. In this thesis, we evaluate two commercially available CMOS technologies from IBM. While the 65 nm CMOS technology is evaluated more from a radiation standpoint [72, 73], the 180 nm bulk and SOI CMOS technologies are used to design RF front-end circuits [75, 76].

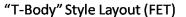

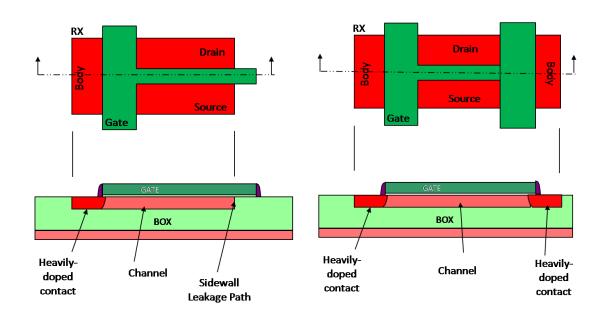

The operation of SOI CMOS devices in the floating-body and body-tied mode has been thoroughly investigated for digital applications. In the digital world, the body-tied operation was used to control the floating-body effects in digital logic, where the transistors showed kink-effect [4]. In addition to the area penalty, the high-frequency performance of body-contacted SOI CMOS devices is degraded due to additional parasitic from different body-contacting schemes. However, as is demonstrated in Chapter 2, an auxiliary benefit of using body-contacting schemes has been the simultaneous improvement in the total-dose radiation tolerance of SOI CMOS devices, which to date has been largely ignored in the literature due to the widely perceived performance shortcomings in body-contacted SOI devices. In the present context, different body contacts refer to the T-body, and H-body orientations for accessing the thin silicon body [Figure 5].

Figure 5. Top view schematic and cross-section of two widely used body contacting schemes in SOI MOSFETs.

The impact of floating-body effects on the analog performance of SOI devices has also been investigated before [5]. It was found that third-order harmonic distortion and noise are very sensitive to floating-body induced kink or deviation of output conductance and a body tie was necessary to maintain comparable distortion performance with the bulk counterparts. With aggressive scaling, however, the linearity performance of the transistors degrades (as will be shown). It is therefore logical to revisit the use of body contacts in a state-of-the-art SOI CMOS technology (45 nm), to quantitatively assess the impact of generational scaling and role of body contacts for improved high-frequency performance. The significance of using body-contacts to maintain a fixed body potential in these devices is explored from a dynamic range standpoint. The addition of body contacts to the compact layout of the 45 nm n-MOSFETs degrades the linearity at lower bias. Finally, improved understanding of the linearity should potentially lead to better circuit design for high dynamic-range using SOI CMOS technology, which is clearly relevant to a number of small-signal and large-signal circuits.

#### **1.3 Switch and LNA Design**

Multi-standard radio integration requires complex transmit/receive switching capabilities as highlighted in Section 1.1. Key switch performance parameters include not only insertion loss and isolation, but power handling capability as well. Typical switch performance parameters and their importance is highlighted below and illustrated in Figure 6:

- **Insertion Loss** (dB) is the measure of power lost due to the switch. A higher insertion loss implies lower overall power amplifier efficiency. The insertion loss of a switch is proportional to the on-resistance (R<sub>on</sub>) of the FET.

- **Isolation** (dB) is the measure of power coupled form one node to the other. Higher isolation is required to protect LNA while PA is transmitting. This parameters is proportional to the off-capacitance ( $C_{off}$ ) of the FET.

- Power Handling P1dB (dBm) of the switch can be converted to the drain to source breakdown voltage (BV<sub>DSS</sub>) of the FET. A large number of FETs are stacked to handle the large peak voltage swing. For example, in a typical GSM environment, the peak voltage can be up to 30V under 6:1 mismatch.

Figure 6. Section of a RF front-end, highlighting the key performance metrics for a frontend switch.

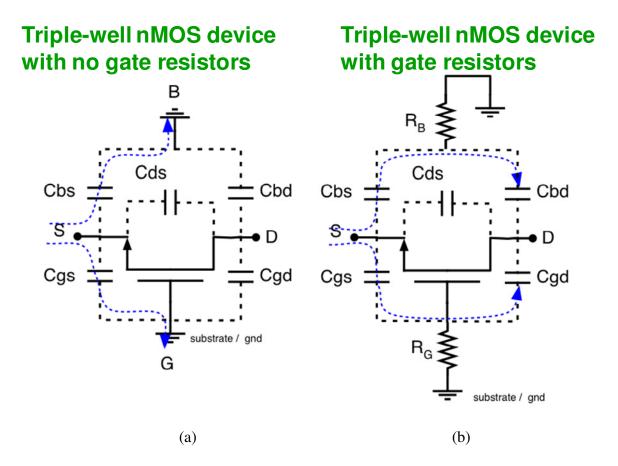

High linearity and constant group delay over modulation bandwidth in RF switches are critical to ensure that the amplitude and phase information of the modulated signal is maintained, and to prevent intermodulation distortion. While the addition of body contacts may be crucial for high linearity RF amplifiers on SOI, floating body devices are generally used in RF switch design to minimize the  $C_{ds}$  [8]. SOI technology is particularly interesting for RF switch design since parasitic junction capacitances are lower than the bulk CMOS technology. However, high linearity performance can be achieved in bulk CMOS switches (as will be demonstrated here) by layout optimization and careful treatment of parasitic in the switch design and layout, without any design rule violations, as demonstrated in Chapter 4. Triple-well CMOS devices are generally added to a standard technology to improve switch insertion loss. The trade-off of using a triple-well technology is better understood by a comparison of parasitic capacitances between a standard n-MOSFET device and an isolated triple-well device as shown in Figure 7 [9].

In addition, SiGe HBT technology is rapidly entering the world of wireless and radar applications, particularly at higher frequencies. RF switches have been realized in SiGe BiCMOS technology by incorporating diode-connected HBTs as series elements, and pMOS pull-up transistors to act as shunting elements [10]. Due to higher non-linearity in SiGe HBTs compared to CMOS transistors, systems with high linearity or dynamic range requirements typically employ CMOS-based RF switches. However, when the SiGe HBT is operated in inverse-mode as a switch, it is shown in Chapter 4 that considerable improvement in linearity and compression point of the switch is obtained. The proposed circuit enables a wide variety of RF and mm-wave applications where high power levels are needed.

Figure 7. Comparison of (a) non-isolated switch and (b) triple-well isolated n-MOSFET switch with floating body [9].

Currently, the majority of front-end radar and wireless modules use p-HEMT based switches, which are fabricated on III-V technologies [11]. The idea of a high dynamic range silicon-based RF switch with high power handling capability is clearly desirable for low-cost integration. Even though we show that high linearity can be achieved in both CMOS and SiGe HBT based switches, the high RF power handling capability and robustness of silicon-based switches has not been addressed in the literature. Both CMOS and SiGe-BiCMOS based switch designs are investigated and compared for their power handling capability under RF stress in Chapter 5. Improved understanding of the breakdown mechanism will potentially lead to better design of CMOS switches operating under high power conditions, clearly relevant to a number of large-signal circuits.

The learning from improved linearity in body-contacted devices is applied to SOI low-noise amplifiers in Chapter 6. The LNA design involves tradeoffs between noise-figure (NF), gain, power dissipation, input matching, and linearity in the output signal. The standard cascode topology design is applied to LNA design using both floating-body and body-contacted devices at 5 GHz. The floating-body device based LNA delivers state-of-the-art performance with sub-1.0 dB noise figure, while maintaining high linearity. The body-contacted FET LNA performance is compared with the floating-body LNA. Due to the extra gate resistance and better control of body potential relative to source, the body-contacted FET based LNA is seen to have higher NF, but marginally better intermodulation performance. The improvement in the intermodulation performance is explained using third-order derivatives of DC characteristics, also used in Volterra analysis.

Due to extensive CMOS scaling (sub-100 nm) and integration of the RF transceiver with the baseband, it has become extremely difficult to integrate the RF frontend on the same chip to obtain the desired performance. Thus, a standalone front-end module is typically used, which includes performance critical blocks such as the RF switch, the low-noise amplifier on the receive side, and the power amplifier on the transmit side. This approach necessitates RF front-end modules with switch and LNA functionality on the same chip, for use with WLAN chipsets. WLAN front-ends have been historically dominated by GaAs platforms because of their superior high power handling capability and semi-insulating substrate. Owing to low mobility, high substrate conductivity, low breakdown voltage, and various parasitic parameters of CMOS processes, it is very challenging to design CMOS switches and LNA to simultaneously achieve low-insertion loss, high isolation, wide bandwidth, high power handling and low-noise comparable to their GaAs counterparts. In Chapter 7, the first implementation of a single-chip fully-integrated SP3T and LNA front-end on 0.18  $\mu$ m CMOS is reported for 802.11b/g WLAN applications at 2.5 GHz. The integrated solution includes on-chip dc blocking, bypass-mode, matching network and ESD protection and drives the die-size (0.64 mm<sup>2</sup>) towards a low-cost, fully-integrated solution.

.

### **CHAPTER 2**

## THE ROLE OF BODY CONTACTS IN SOI

#### **2.1 Introduction**

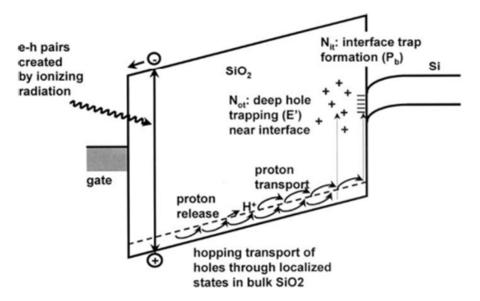

In this chapter, we discuss the role of body contacts in mitigating total ionizing damage in SOI CMOS technology. Ionization damage in semiconductor devices is initiated when electron-hole-pairs (ehps) are generated along the track of secondary electrons emitted via photon-material interactions. Protons and other charged particles also generate ehps that lead to ionization damage. The total amount of energy deposited by a particle that results in ehp production is commonly referred to as total ionizing dose (TID). The typical unit of TID is rad, which denotes the energy absorbed per unit mass of a material. The possible physical processes leading to the creation of ionization defects are depicted in Figure 8 below. Since electrons have much higher mobility than holes in oxides, they are rapidly swept out of the dielectric [12].

Figure 8: Major processes responsible for inducing TID damage in MOSFET [13].

In modern CMOS technologies, susceptibility of gate oxide to radiation-induced damage is reduced primarily due to the fact that defect buildup in gate oxides scales with  $t_{ox}$  [14]. Gate oxide hardness trends have continued to be observed in 0.25µm ( $t_{ox} = 6$ nm), 0.18µm ( $t_{ox} = 3.2$ nm), and 0.13µm ( $t_{ox} = 2$ nm) respectively [15], [16]. However, defect buildup in thicker isolation oxides is the major cause of radiation-induced degradation in modern CMOS devices. The STI oxide thickness is typically greater than 300nm in advanced CMOS technologies. The thick buried oxide (BOX) in SOI technologies is also susceptible to radiation damage.

#### 2.2 Radiation Reliability

Advances in CMOS technology have enabled system-on-a-chip applications through the integration of analog and radio-frequency (RF) circuit blocks with conventional digital CMOS. This combination of a traditional digital CMOS technology with RFoptimized process elements (e.g., n- and p-channel transistors, passive elements, and thick top metal) is commonly termed RF-CMOS. Importantly, RF-CMOS transistors typically employ very large numbers of gate fingers (50 – 200) in order to boost transconductance and frequency response to >200 GHz levels. A combination of new materials, strain-engineering, and lithographic scaling is used to further improve performance to support demanding RF circuit functions [17]. The scaling trends in digital CMOS have a strong influence on the RF CMOS roadmap. For example, the  $f_{MAX}$  scaling and broadband noise can benefit from the lower resistance of fully silicided gates, but the flicker (1/f) noise may require added attention as new gate materials are introduced.

RF-CMOS on SOI technology provides additional advantages over bulk RF-CMOS,

by decreasing leakage and improving short-channel effects. In the RF context, SOI helps by minimizing parasitics and also improves device-to-device isolation at high frequencies. From a radiation perspective, SOI is known to enhance single event upset (SEU) tolerance. This performance improvement, coupled with its high-density integration capability, cost effectiveness, and process maturity, makes RF-CMOS on SOI technology attractive for integrating both RF front-ends and base-band analog/digital circuitry onto a single chip for emerging space-based systems.

The proton tolerance of 180 nm and 130 nm bulk CMOS technology has been previously studied from both dc and RF standpoints [18, 19]. High-quality ultra-thin gate oxides in aggressively-scaled CMOS technologies are known to exhibit reduced sensitivity to total dose irradiation. However, isolation-oxide and buried-oxide damage (in CMOS on SOI) can potentially impact the total dose tolerance. The total dose radiation response of partially depleted RF-CMOS on SOI transistors has been investigated using X-ray and proton sources [20]. Although the radiation tolerance of a 90 nm SOI technology has been reported [21], the radiation response of more advanced SOI CMOS technology nodes has not been understood, especially from a RF standpoint. The total ionizing dose-induced degradation mechanisms in high-gate-finger-count 65 nm RF-CMOS on SOI devices are investigated for the first time. Both S-parameters and dc characteristics are employed to characterize the radiation damage and understand the underlying damage mechanisms in 65 nm SOI devices. The devices selected were laid out as multi-finger structures and padded out to enable on-wafer high-frequency measurements.

#### **2.2.1 Experimental Details**

Strain-engineered, partially-depleted RF-CMOS on SOI devices are investigated here for total ionizing dose radiation tolerance. The stress memorization technique (SMT) has been applied to a fully-integrated 65 nm RF-CMOS on SOI technology, complete with high Q on-chip inductors and capacitors, to enable system-on-chip integration of RF blocks with digital blocks [22]. A relaxed pitch layout for the RF devices yields peak  $f_t$  of 360 GHz and 260 GHz for the nFET and the pFET, respectively [23]. Fully silicided (FUSI), low resistance polysilicon gates were used with a thermally grown gate oxide of thickness 1.05 nm. The devices are designed for an operating  $V_{DD}$  of 1.0 V using a dualwell CMOS technology on p-type SOI substrate. For our analysis, we used 60 nm gate length, standard threshold voltage nFETs.

The devices selected were laid out as multi-finger structures and padded out to enable on-wafer high-frequency measurements. An Agilent 4156C Semiconductor Parameter Analyzer was used to perform dc device characterization at room temperature. For twoport S-parameter measurements, an Agilent E8361B network analyzer was used for RF measurements up to 40 GHz, both before and after irradiation. The conventional openshort de-embedding technique was used on the raw S-Parameters of the devices to deembed the effects of pad parasitics. All measurements were performed at room temperature before and after the devices were exposed to a given proton radiation dose. These devices were also packaged into 28-pin DIP packages for cumulative total ionizing dose radiation testing. The dc characteristics of the devices were measured at room temperature. All terminals were grounded for nominal bias conditions, while the gate was biased at 1.0 V (V<sub>DD</sub>) for worst-case conditions during exposure. The dc characteristics of the devices were measured immediately after each cumulative dose was reached. All irradiated devices were of a multi-finger geometry, with different total width (1  $\mu$ m, 2  $\mu$ m, and 4  $\mu$ m) and number of gate fingers.

Two separate ionizing radiation experiments were conducted to analyze the role of shallow-trench isolation in the device response. First, the samples were irradiated with 63 MeV protons at Crocker Nuclear Laboratory, at the University of California at Davis. A five-foil secondary emission monitor calibrated against a Faraday cup was used for dosimetry measurements. The radiation source (Ta scattering foils) was located several meters upstream of the target, and this established a beam spatial uniformity of about 15% over a 2.0 cm radius circular area. Beam currents from about 10 nA to 50 nA allow testing with proton equivalent gamma doses up to 2 Mrad(SiO<sub>2</sub>). The dosimetry system has been previously described and is accurate to about 10% [24]. Additionally, devices were irradiated on-chip with all terminals floating using a 10 keV X-ray source at Vanderbilt University. A dose rate of 31.5 krad(SiO<sub>2</sub>)/s was used to obtain equivalent gamma doses up to 2 Mrad( $SiO_2$ ). Since radiation damage can depend on device bias conditions during exposure, the results obtained from 10 keV X-ray exposure with floating terminals may not represent worst-case conditions. While X-ray exposure of packaged devices would be better to compare the response with proton radiation, packaging related electro-static discharge (ESD) issues allowed only floating terminal conditions in this experiment.

#### **2.2.2 Impact on DC performance**

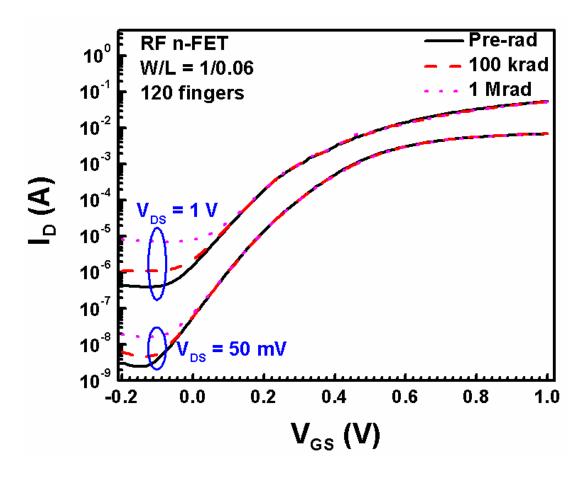

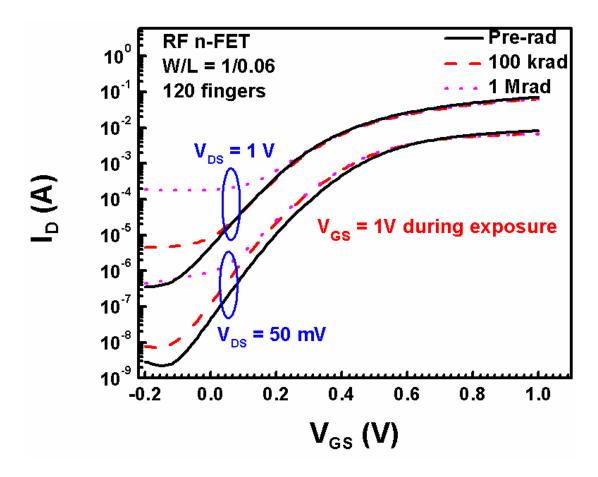

Figure 9 shows typical  $I_D$ - $V_{GS}$  transfer characteristics as a function of total accumulated dose for a 120-finger nFET with width and length dimensions of W/L=1.00/0.06 µm, after 63.5 MeV proton exposures. Even though we show the off-state leakage degradation in a 120-finger nFET, the device with 20-fingers also showed considerable degradation in off-current. Observe that the off-state leakage current is significantly degraded, even at a low  $V_{DS}$  of 50 mV. Thus, the impact ionization-induced floating-body effect (also referred to as 'total-dose latch' or 'snap-back effect') in these SOI devices can be ruled out [25]. Moreover, this effect is known to be more predominant in fully-depleted SOI transistors [26, 27].

Figure 9. Transfer characteristics of the devices at different accumulated dose points for 63 MeV protons.

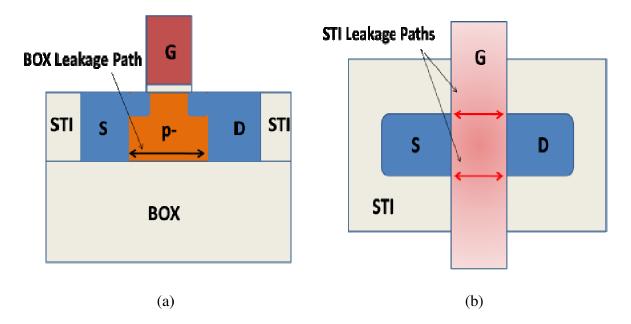

There are two possible radiation-induced parasitic conduction paths which can induce off-state leakage degradation consistent with what we observe. As shown in Figure 10(a), hole trapping in the much thicker buried-oxide (BOX) layer could result in a sheet of mobile electrons at the bottom of the active silicon layer, thus causing radiation-induced back-channel conduction between the source and drain, which reach to the BOX in these partially-depleted devices. On the other hand, the increase in radiationinduced leakage could potentially be a manifestation of a parasitic inversion channel where the gate overlaps the shallow trench isolation (STI), as shown in Figure 10(b).

Figure 10. Possible radiation-induced leakage paths along the (a) surface of BOX, (b) STI sidewalls.

In Figure 11, it is observed that the same device has more off-state leakage degradation when the gate was biased at 1.0 V ( $V_{DD}$ ) during exposure. The effect of parasitic inversion channel along the STI is aggravated in nFETs since one applies a positive front-gate bias during irradiation [28]. Moreover, one would expect the BOX

surface channel to be insensitive to front-gate bias during exposure. This result is highly suggestive of a STI-induced degradation mechanism in these multi-finger RF-CMOS devices, because each finger adds extra parasitic conduction paths along the STI edge, thereby contributing to the observed total radiation-induced leakage enhancement. These conduction paths may enhance the total drain current at high drain bias and make the floating body effect more pronounced, as shown in Figure 11.

Figure 11. Enhanced degradation in off-state leakage when gate was biased at 1.0 V during proton irradiation.

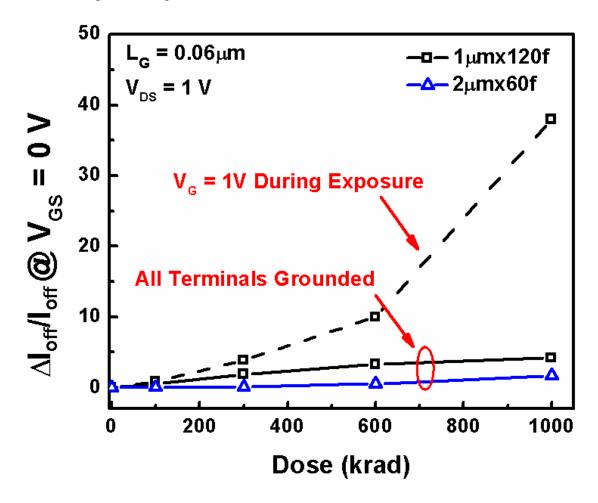

Figure 12 shows the normalized change in off-state leakage as a function of accumulated dose. The enhancement in degradation with applied gate-bias during

irradiation is clearly visible. This is because each additional finger creates extra parasitic conduction paths along the STI edge, thus contributing to the total radiation-induced leakage enhancement. Additionally, it is shown that the damage can be reduced by decreasing the number of fingers. This reduction can be achieved by increasing the width of each finger, while maintaining the same total width of the device. However, gate resistance may start to dominate the small-signal RF response for longer finger-widths, thus reducing the RF figures-of-merit of the transistor.

Figure 12. Normalized change in off-state leakage as a function of total accumulated proton dose.

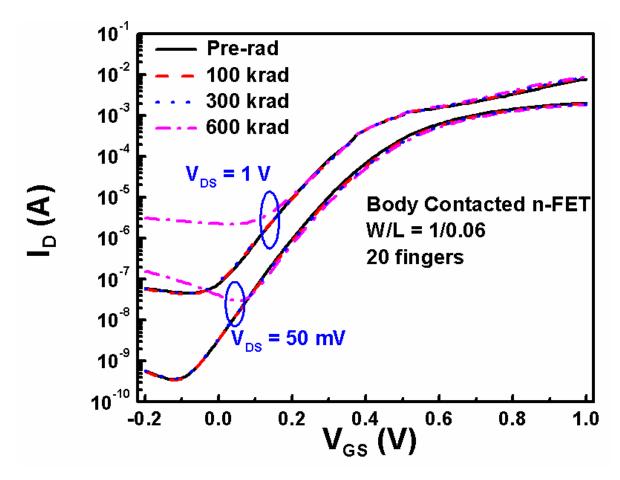

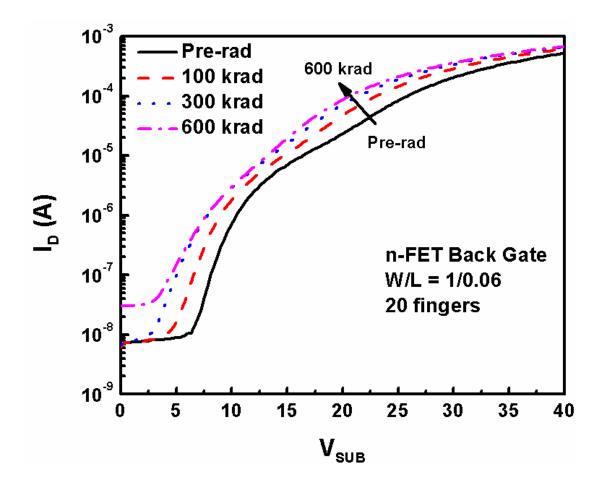

Interestingly, the T-body contact eliminates the STI edge from only one end of the channel, while an H-body contact results in a completely edgeless device. We observed negligible degradation of a T-shaped body-contacted device, as shown in Figure 14. The effect of sidewall leakage at one end of a T-body contacted device is observed at a cumulative dose of 600 krad(SiO<sub>2</sub>). Additionally, the back-gate characteristics of irradiated T-body devices indicate the presence of trapped charge in the buried oxide (Figure 14), which has negligible impact on the front-gate characteristics of the device in Figure 13.

Figure 13. Transfer characteristics of a body-contacted device at different accumulated proton doses.

Figure 14. Back-gate characteristics of body-contacted device at different accumulated proton doses.

Radiation tolerance of edgeless devices (no STI) and H-gate topology available in a 90 nm SOI CMOS technology has been analyzed [21]. It was observed there that even though the back-gate threshold voltage was shifted due to BOX charge accumulation, the front-gate characteristics of the transistor remained unaffected up to a total dose of 300 krad. Thus, the observed radiation damage is understood to be dominated by an STI parasitic conduction path.

#### 2.2.3 Impact on RF Performance

To achieve better RF performance (i.e., peak  $f_T$  and  $f_{MAX}$ ), finger width in a multifinger device plays a key role. Cut-off frequency ( $f_T$ ) is seen to scale very well with inverse gate length, and is independent of finger width to a certain minimum value. This minimum value is dictated by the technology node, when the parasitic capacitance,  $C_{gs}$ and  $C_{gd}$ , dominate the device  $f_T$ , as indicated in equation (1) below:

$$f_T = \frac{g_m}{2\pi (C_{gs} + C_{gd})} \tag{1}$$

A strong indicator of usable power-gain of the transistor is its  $f_{MAX}$ .  $f_{MAX}$  has a peak value at some optimum width, above which it is limited by physical gate resistance, and below which it is limited by parasitic losses in the FET structure, as shown in equation (2). The optimum device width shrinks as the unit gate resistance increases with smaller gate length in advanced technologies [12].

$$f_{MAX} = \frac{f_T/2}{\sqrt{g_{ds}(R_g + R_i + R_s) + 2\pi f_T R_g C_{gd}}}$$

(2)

The total dose radiation tolerance is shown here to be worse for smaller finger width devices. This result potentially represents a fundamental tradeoff between achievable RF performance and total dose radiation tolerance. Moreover, high finger count is required for acceptable power-gain, which degrades the total dose tolerance due to extra parasitic conduction paths along the sidewalls of each finger. If the designer decides to use devices with longer finger width to accommodate total dose tolerance in the circuit, the resulting lower power-gain or  $f_{MAX}$  of the device will impose a penalty on the achievable RF performance.

As discussed in Section 1.3.1, body-contacts can mitigate the effect of STI sidewall conduction. However, body contacting schemes come not only with an added area penalty, but with extra gate polysilicon strapping around the active region of the device. This gate polysilicon around the edges adds extra parasitic capacitance between gate-source ( $C_{gs}$ ) and gate-drain ( $C_{gd}$ ), respectively, thus degrading the high frequency performance of the device. Hence, the choice between longer finger width devices and body-contacted devices for total dose tolerance will depend on the technology performance and desired circuit specifications.

#### **2.3 Impact on Linearity**

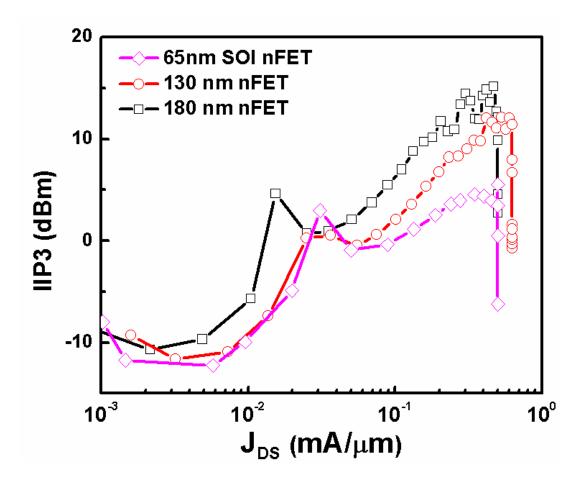

To enable integration of scaled CMOS in wideband communication systems, it is important to ensure that the linearity of these scaled devices will be able to satisfy the expected demands of high P1dB compression point and low IMD product. It is shown in Figure 15 that the linearity of CMOS devices worsens with scaling. The 180 nm channel length n-MOSFET has the highest IIP3, followed by the 130 nm and 65 nm devices, respectively. However, the device noise-figure is expected to improve with CMOS scaling [12]. It is therefore important to investigate the impact of scaling on overall dynamic range of scaled CMOS devices.

Figure 15. Impact of CMOS scaling on the device linearity.

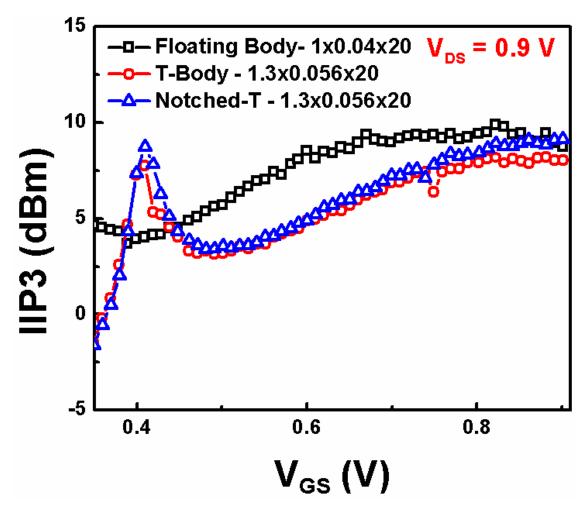

Device linearity in the state-of-the-art, commercially available 45 nm SOI CMOS technology is investigated. As shown in Figure 16, the floating-body device linearity is compared with two different body-contacted devices. The notched-T body contacting scheme is used to reduce the extra gate-to-source and gate-to-drain capacitance in a T-body device, while controlling the body potential. The floating-body device provides the highest linearity in this technology. The body potential was tied to the ground during the linearity measurements of body-contacted devices. It should be noted that the body-contacted devices have a longer channel length (56 nm) than the floating-body device (40 nm), which may potentially be the reason for improved linearity in body-contacted

devices. However, the use of body-contacting schemes for high dynamic range LNA design will be investigated in Chapter 6.

Figure 16. Comparison of linearity between floating-body and body-contacted devices in a 45nm CMOS on SOI technology.

# CHAPTER 3 INTEGRATED S-PARAMETER AND LINEARITY CHARACTERIZATION

#### **3.1 Introduction**

A new and simpler linearity characterization approach is described, in which the power levels of the fundamental and the IM3 products are measured using a network analyzer, thus eliminating the need for the spectrum analyzer. The network analyzer used is capable of performing power sweeps at the desired frequencies along with S-parameter measurements. Measurements were performed on MOSFETs in a commercially-available 0.13  $\mu$ m SiGe BiCMOS technology using this novel test setup. Harmonic balance simulations and IP3 analysis are performed to validate the measured results.

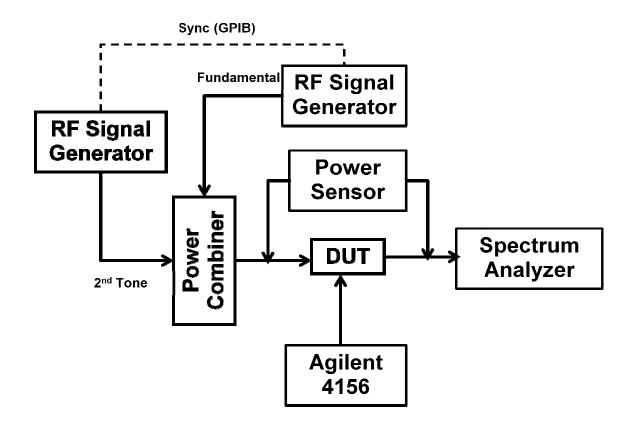

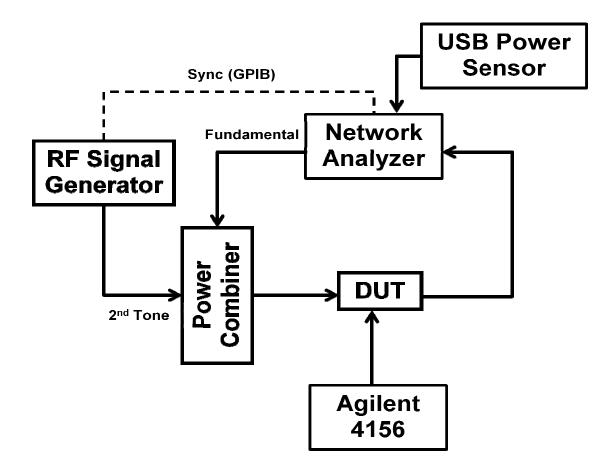

Figure 17 shows the block diagram of a conventional two-tone measurement setup. The two-tone signal is obtained by power combining the two RF signal generators which supply the fundamental and the second tone, respectively. Figure 18 shows the block diagram of the proposed setup. The measurement setup uses the power sweep feature of the network analyzer to measure non-linear distortion across bias in both transistors and integrated circuits. The setup shown in Figure 18 eliminates the need for a spectrum analyzer and an additional RF signal generator. Thus, the setup facilitates easy integration of linearity measurements with S-parameter measurement setup with minimal cost overhead.

Figure 17. Block diagram of a conventional two-tone linearity measurement setup with spectrum analyzer.

Figure 18. Block diagram of the test-setup proposed for two-tone linearity measurements integrated with S-parameter measurements.

The continuous-wave (CW) signal at the fundamental frequency is provided by the network analyzer. The network analyzer (here, an Agilent PNA E8361C) is synchronized in the time-domain with an external Analog Signal Generator, which provides the CW signal for the second tone. The signals are then fed into a power combiner and a two-tone signal is obtained at the input of the DUT. The device or circuit is biased using an Agilent 4156 Parameter Analyzer or with external DC supplies. The network analyzer is used to measure the power of the fundamental frequency, 2<sup>nd</sup> tone, and third-order harmonics at the output of DUT. The power sensor (Agilent U2002H) used for the power calibration is connected to the USB port of the network analyzer.

#### **3.2 Measurement Results**

Source power calibration is performed at four different frequencies (i.e., fundamental, 2<sup>nd</sup> tone, IM3 low and IM3 high) using the power sensor. The output is received at the network analyzer. Four separate channels are set up in the network analyzer to receive the fundamental, 2<sup>nd</sup> tone, IM3 low, and IM3 high signals, respectively. The source and receiver power calibration for each of these frequencies are loaded onto their respective channels. When the DUT is biased and input RF power is applied as a two-tone signal, the output power sweep for all four frequencies (channels) are then measured. For linearity characterization, minimum channel length n-MOSFETs with maximum supply voltage of 1.5 V and a total width (W) of 64 µm was chosen from a 0.13 µm SiGe BiCMOS technology for validation purposes [29]. The peak cut-off frequency  $(f_T)$ performance and transconductance of the device are shown in Figure 19. The fundamental frequency chosen for the linearity analysis is 9.5 GHz, with 10 MHz spacing for the 2<sup>nd</sup> tone. The input power on the device was swept from -27 dBm to -15 dBm. IIP3 was measured as a function of gate bias (V<sub>GS</sub>) at four different drain bias values (0.6 V to 1.5 V).

Figure 19. Peak f<sub>T</sub> performance of the device under test and its correlation with g<sub>m</sub>.

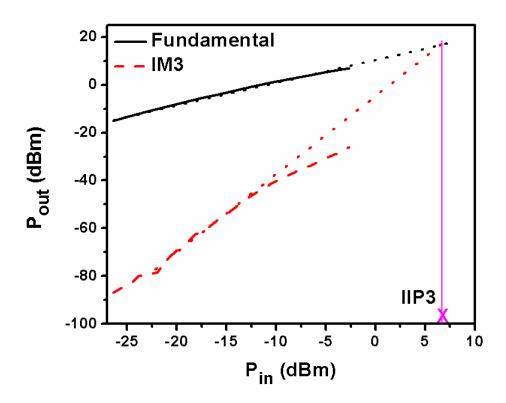

Figure 20 shows the measured power sweep on the device at a fixed bias. The IP3 point was extrapolated from the experimental  $P_{out}$  and IM3 curves and approximate 1:3 slope ratios were obtained, as expected. The measured IIP3 and OIP3 values are also shown in Figure 20.

Figure 20. Measured fundamental and third-order harmonics for the device. IIP3 and OIP3 are extrapolated for a fixed bias.

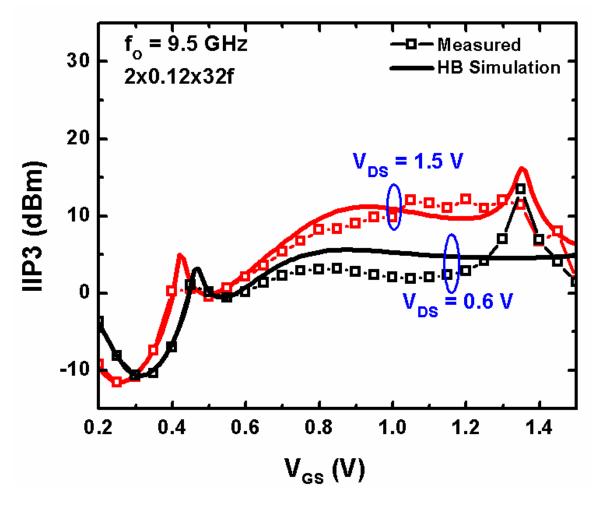

Figure 21 shows IIP3 obtained from measurements at four different  $V_{DS}$  values ranging from 0.6 V to 1.5 V. At each of these  $V_{DS}$  values, the gate voltage was swept from 0.2 V to 1.5 V. With  $V_{DS}$  increasing from 0.6 to 1.5 V, IIP3 increases by a large factor, particularly at higher  $V_{GS}$ . The measured value of K3g<sub>m</sub> (third-order derivative of  $I_D$  with respect to  $V_{GS}$ ) is plotted in Figure 22 to explain the "sweet spot" and  $V_{GS}$ dependence of IIP3. The zero K3g<sub>m</sub> point corresponds closely to the sweet spot (maximum linearity) of IIP3 for  $V_{DS} = 1$  V.

Figure 21. Measured bias dependence of IIP3 as a function of gate voltage, at different drain voltages.

Figure 22. K3g<sub>m</sub> and its correlation with linearity sweet spot.

## **3.3 Simulations and Calculations**

The harmonic balance (HB) technique was used for simulating distortion in the devices. For simulating analog and RF circuits, harmonic balance offers frequency-domain analysis, and is typically the method-of-choice for linearity simulations. The direct solver method was used for HB simulations, with a fine bias step size (10 mV). This method allows one to minimize the oscillations in the extraction of third-order derivatives, which is necessary for understanding the nonlinear response of transistors. For a fundamental frequency of 9.5 GHz, IIP3 was calculated by extrapolating the P<sub>out</sub> and IM3 terms at -27 dBm, assuming 1:3 slopes. Figure 23 shows the IIP3 dependence on

bias obtained from the harmonic balance simulations, using the standard design kit compact models. It is observed that the simulation results are in agreement with the measured data using our new simplified linearity measurement setup.

Figure 23. Comparison of measured IIP3 with harmonic balance simulations run using ADS simulation tool.

This integrated approach to measure linearity and S-parameters is currently used in the lab to characterize a number of devices and circuits.

#### **CHAPTER 4**

# **HIGH LINEARITY SWITCH DESIGN**

#### 4.1 CMOS Switch Design

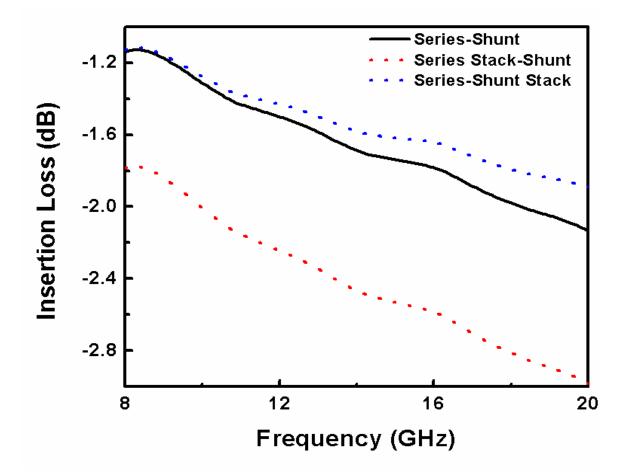

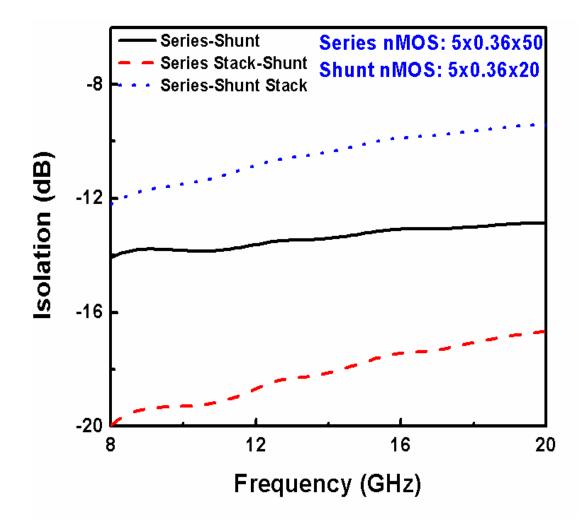

In this chapter, we explore RF single-pole single throw (SPST) n-MOSFET switch designs in a commercially available 0.35  $\mu$ m SiGe BiCMOS technology (5PAe), particularly used for power-amplifier (PA) applications. The focus of this work is to design high linearity, low-loss switches for integration with PA in wireless front-end applications. The challenge is to design a low loss switch using a longer channel length technology (0.35  $\mu$ m), while maintaining adequate isolation, and pushing for higher linearity.

The SPST switches were designed using the topology highlighted in Figure 24. To improve insertion loss, an isolated triple-well n-MOSFET device is used as the series switch. The isolated p-well is achieved by floating the deep n-well of the triple-well n-MOSFET device, reducing parasitic losses by increasing the effective substrate resistance in the body of the device. The shunt n-MOSFET device increases isolation while only minimally degrading the insertion loss. Both the source and drain of the device were held at the same *dc* potential, and therefore only leakage current is dissipated, enabling these switches to consume virtually no power. As shown in the schematic in Figure 24, the 20 k $\Omega$  resistors on the gate and body of the device isolate the gate and body nodes from RF ground, thus improving the insertion loss of the switch. However, the switch isolation is

degraded due to these floating nodes, allowing RF power to leak from the source to the drain, even when the switch is in the off state.

Figure 24. Schematic of single-pole single-throw (SPST) switch using triple-well n-MOSFET as series device.

The optimization of switches for a particular application (in this case, X-band) involves appropriate selection of device geometry. The geometry selection provides a balance in trade-offs between the on-state device resistance ( $R_{on}$ ) and the off-state parasitic device capacitances ( $C_{off}$ ).  $R_{on}*C_{off}$  product is a common benchmark for FET switch designs where the multiplier for 1 mm of gate width is often used to compare the quality of the FET used in the switch. For example, a transistor with a larger width will

provide a small Ron, but will also increase overlap and source/drain to body capacitances, thus increasing the overall switch performance metric product. The switches in the present work were realized to achieve optimum linearity and insertion loss at 9.5 GHz. Linearity is dominated by the device parasitic capacitances which can be reduced by optimally sizing the device, but at the cost of higher Ron. The optimal gate widths for the series and shunt devices were chosen as 200  $\mu$ m and 100  $\mu$ m, respectively. It is worth mentioning that the optimal width for switch design is technology dependent [30]. Series or shunt devices are stacked to distribute the large signal swing across multiple transistors, thus preventing high potential across the gate of a single device. The following three switch configurations were built to analyze the performance trade-off associated with stacking the series or shunt devices in series:

- 1. Series-Shunt: Single series device and single shunt device.

- 2. Series Stack-Shunt: Two similar devices stacked in series arm and a single shunt device.

- 3. Series-Shunt Stack: Single series device and two stacked devices in the shunt leg.

The two-port S-parameter characterization for switches was performed using an Agilent E8363 PNA. Switch 1 dB compression point (P1dB) measurements were performed using a novel high power test setup which allows us to apply +33 dBm RF power at the DUT input. The setup is described in detail in Sec 1.3.5. IIP3 of the switches was calculated using a conventional two-tone measurement setup.

As shown in Figure 25, the switch shows an insertion loss of < 1.5 dB across the X-band while maintain an isolation of about 14 dB (Figure 26). As one would expect, an additional series device degrades the switch insertion loss while improving the isolation

at the same time. However, the shunt stacked switch degrades the isolation by reducing the total resistance offered by the shunt leg to the ground.

Figure 25. On-state  $S_{21}$  of series-shunt Single-Pole Single-Throw (SPST) RF switches optimized for X-band operation.

Figure 26. Off-state  $S_{21}$  of series-shunt Single-Pole Single-Throw (SPST) RF switches optimized for X-band operation.

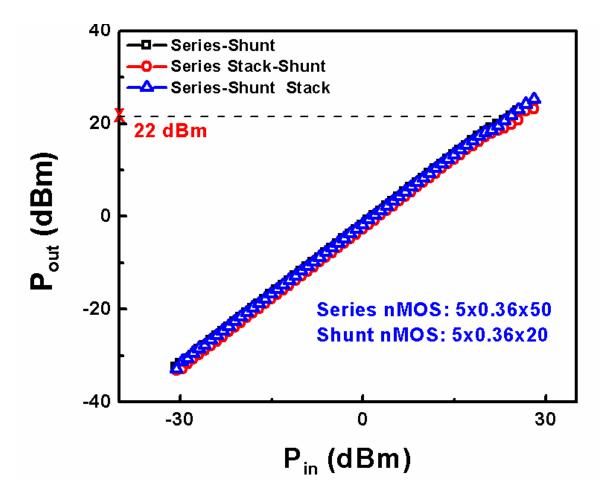

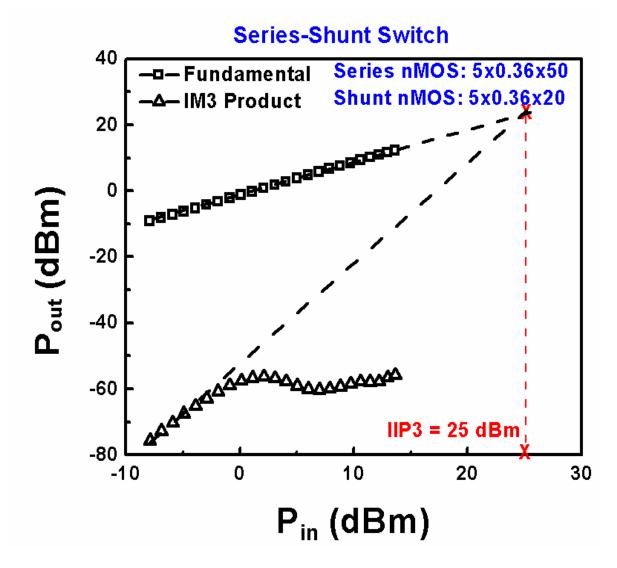

The power sweep curve of the series-shunt switch gives a P1dB compression point of 22 dBm, as shown in Figure 27. This compression point is the record performance for any CMOS based switch at X-band. For the series-shunt stack switch, two-tone measurements in Figure 28 showed IIP3 performance of 25 dBm at 9.5 GHz.

Figure 27. Record P1dB compression point of a CMOS based SPST switch at 9.5 GHz

Figure 28. IIP3 of 25 dBm is measured for a series-shunt stack type SPST at 9.5 GHz.

#### 4.2 SiGe HBT Switch Design

Highly-integrated, low-cost circuits have fueled the growth of BiCMOS technology for radio-frequency (RF) applications. Aggressive technology scaling and the integration of bandgap-engineered Silicon-Germanium (SiGe) technologies have resulted in dramatic performance improvements of silicon-based RF integrated circuits, thus providing cost advantages over III-V technologies [31]. RF switches are crucial for operation of any radar or wireless transceiver. In addition to transmit/receive functionality, RF switches can be used for digital gain control and phase state selection in a typical RF front-end. Technology scaling and layout optimization has resulted in low insertion loss CMOS RF switches [32]. However, shorter channel length and thinner oxide limit the dynamic range and high power handling capability of the CMOS switches.

Near one watt X-band power amplifiers (PA) in SiGe BiCMOS technology have been demonstrated, thus highlighting the need for high power handling silicon RF switches [33]. Since solutions are already available for integrating the balun and high power PA on a single chip, a high power and high linearity T/R switch becomes the last external component (excluding the crystal oscillator) that needs to be integrated on chip to provide the most cost-efficient system-level solution. With SiGe HBT device performance constantly improving (with  $f_T$  now routinely above 200 GHz and even now approaching 500 GHz), it is possible to design a robust switch based on a diode-connected SiGe HBT [34]. In the present work, we focus on building low insertion loss and high-linearity RF switches, using SiGe HBTs, to enable integration with power amplifiers designed in the same technology platform.

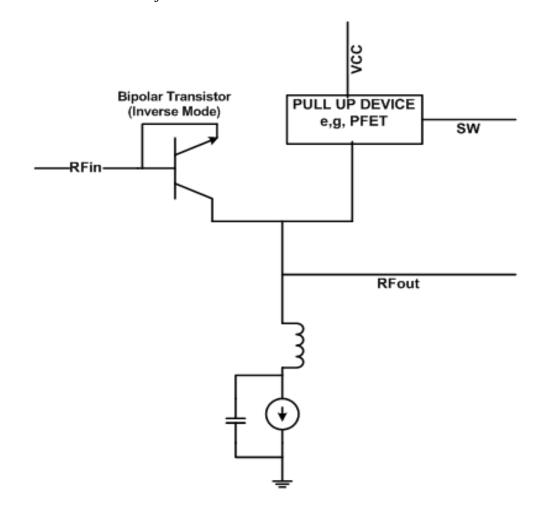

The single-pole, single-throw (SPST) RF switches were designed using SiGe HBTs from a commercially available, 0.35  $\mu$ m SiGe BiCMOS technology. Thru-Silicon Via (TSV) technology is used in this platform to provide a low ground plane inductance, which is highly desirable for power-amplifier applications [35]. The SiGe HBT acts as the series switching element, while a pFET is used to pull-up the circuit in the OFF state, as shown in Figure 29. When the switch is ON, the switching junction (B-E in forward

mode, B-C in inverse-mode) is forward-biased and the current flows from the collector (emitter) into the emitter (collector), in forward-mode (inverse-mode) operation. The schematic in Fig. 1 highlights the operation of the SiGe BiCMOS RF switch in inverse mode, in which the base-collector junction is used as the switching diode, instead of the conventional base-emitter junction.

Figure 29. Schematic of the inverse-mode bipolar transistor as an RF switch.

When the switch is turned OFF, the pFET pulls the collector voltage of the SiGe HBT to the  $V_{CC}$  rail and eliminates any dc current flow through the device. Compared to CMOS RF switches, higher dc power is dissipated in SiGe HBT switches due to the bias

current flowing through the bipolar transistor in the ON state. The dimensions of the SiGe HBT chosen were  $0.8x20\mu m^2$  with three emitter stripes, with a peak  $f_T$  of 33 GHz. The *npn* SiGe HBTs in the technology support only up to three-stripe emitter geometries. This is because at high current densities allowed in the technology (for PA applications) center fingers of a multi-finger device would be at a higher temperature than the outer fingers, causing potential reliability concerns. However, the RF switch current density is low enough to ignore this effect. The switches were optimized for operation in the X-band. For the three-stripe device, a *c-b-e-b-e-b-c*-three-stripe layout is used.

#### 4.2.1 Results and Discussions

#### A. Switch Performance

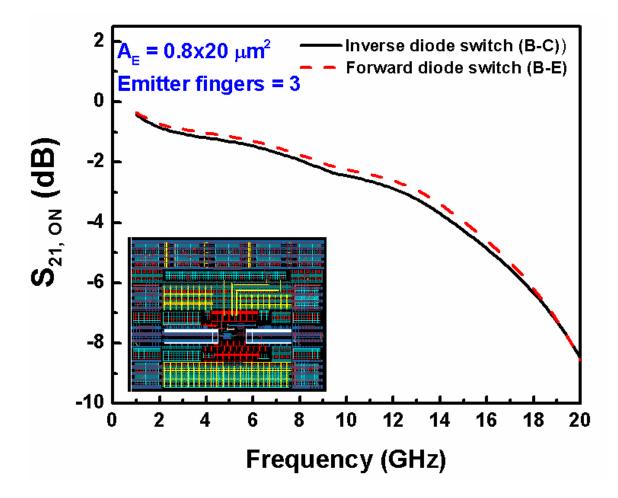

Figure 30 shows the measured insertion loss of both forward- and inverse-mode SiGe BiCMOS switches, and the SPST die picture (inset). The insertion loss of the inversemode switch is slightly higher than the forward-mode switch. Identical pFETs were used as shunt devices in both of the designs. The high intrinsic collector resistance is likely responsible for higher insertion loss in the inverse-mode switch, compared to the low emitter resistance in the forward-mode operation.

Figure 30. Insertion Loss of the SiGe BiCMOS RF switches in both forward- and inverse-mode orientation.

As seen in Figure 31, the isolation of the switch improves considerably when the basecollector junction is used as the switching diode. This improvement is observed across the whole frequency spectrum, with about 8 dB improvement at 2 GHz, and a 6 dB improvement around the center of X-band (9.5 GHz), respectively. When the switch is turned OFF, negligible leakage current flows through the diode and the junction is reverse-biased. The base-collector junction has a longer depletion region and thus, smaller depletion capacitance than the base-emitter junction. Hence, this smaller capacitance allows for better isolation in inverse-mode switch.

Figure 31. Improved isolation in the inverse-mode switch compared to the forward-mode switch across a wide frequency range.

Figure 32. A 12 dB improvement in P1dB compression point of the switch through inverse-mode operation is obtained.

To evaluate the large-signal potential of SiGe BiCMOS switches, 1 dB compression point measurements were performed at 9.5 GHz on both forward-mode and inverse-mode switches. As shown in Figure 32, the inverse-mode switch gives a P1dB compression point of about 20 dBm, which is a 12 dB improvement over the forward-mode switch. This is a significant result. The improvement in power handling capability of the inversemode switch is due to the longer depletion width of the base-collector junction, thus allowing for a larger swing before the switch goes into compression. The transistors were biased at 9 mA, which is well below the peak  $f_T$  current of the forward-mode device. This is done to ensure that the device is biased below peak  $f_T$  in the inverse-mode operation as well, to avoid other non-linear contributions from high-injection.

Two-tone measurements are used to calculate the input third-order intercept (IIP3) of the RF switches. The center frequency was kept at 9.5 GHz with a tone spacing of 1 MHz. Figure 33 shows the extrapolated IIP3 of the forward-mode switch. The linearity of inverse-mode switch was also 12 dB higher than the forward-mode switch, as shown in Figure 34. To the best of author's knowledge, an IIP3 of 35 dBm represents record linearity performance for a SiGe BiCMOS switch at X-band [36].

Figure 33. Extrapolated IIP3 using two-tone characterization of the forward-mode RF switch.

Figure 34. Using the inverse-mode switch topology, 12 dB improvement in IIP3 is measured over standard switch.

#### 4.2.2 Summary

The inverse-mode RF switch operation of the SiGe HBTs is investigated for highlinearity and high-power handling capability. We find that the inverse-mode switch gives superior linearity performance, while maintaining reasonable insertion loss. High power and high dynamic range switches on silicon necessitate careful reliability analysis to correlate device failure with circuit reliability. We find that high RF input power induces junction damage in SiGe HBTs, leading to degradation or failure of the RF switches. Insertion loss and isolation of forward-mode switch begin degrading at 30 dBm RF input power, while the inverse-mode switches can withstand 30 dBm of RF power.

## CHAPTER 5

# **RF SWITCH RELIABILITY**

# 5.1 CMOS RF Switch Reliability

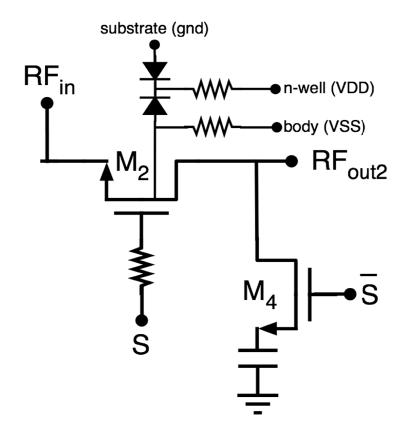

The use of conventional MOS transistors for front-end building blocks of RF transceivers raises issues related to MOSFET reliability, particularly under RF and mixed-signal stress conditions. RF single-pole, double-throw (SPDT) n-MOSFET switch designs are explored for their power handling capability and robustness under RF stress. The series-shunt SPDT switches were designed using n-MOSFETs from 180 nm and 130 nm SiGe BiCMOS technology nodes [37]. A series-shunt topology, highlighted in Figure 35, was chosen for all of the switches.

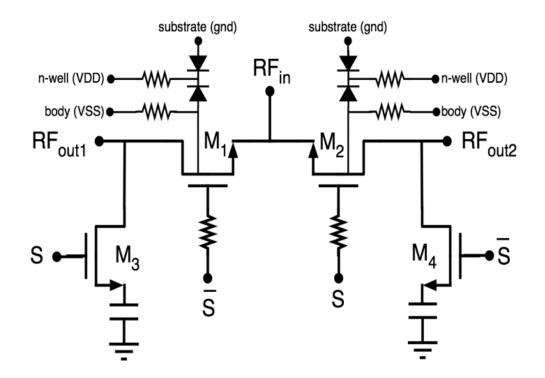

Figure 35. Single-Pole Double-Throw (SPDT) RF switch design topology used for reliability analysis.

An isolated triple-well n-MOSFET device was used as the series switch to improve insertion loss. The standard n-MOSFET device is used in the shunt leg to improve the isolation. The shunt devices M3 and M4 (Figure 35) cause a minimal degradation in insertion loss of the switch. The switching control is provided by a digital signal, S. When S is high, M2 is on and M4 is off, allowing the RF signal to pass from RF<sub>in</sub> to RF<sub>out2</sub>. Similarly, the signal flows from RF<sub>in</sub> to RF<sub>out1</sub> when S is low. Separate test structures with only the series transistor, M1 or M2 as a switch, were also tested to better understand the exact failure mechanisms of the RF switches under high RF drive.

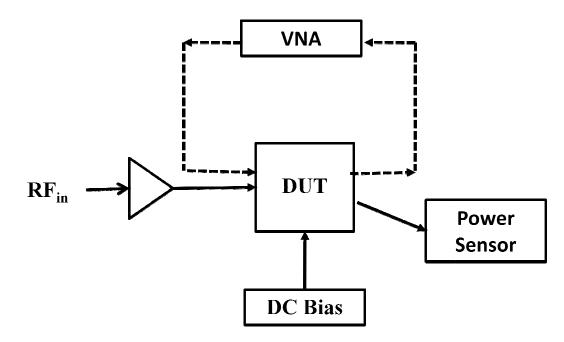

Figure 36. Block diagram of the setup used for applying RF stress and measuring S-parameters.

Figure 36 shows the test setup for high power RF reliability analysis of the switches. RF stress is applied at 9.5 GHz (in the middle of X-band) for 300 seconds when the switch is 'ON' by using a RF source and a traveling wave tube (TWT) amplifier with maximum gain of 40 dB at 9.5 GHz. For stressing at high input power, a separate RF

source becomes necessary to avoid reflected power at the network analyzer input. All losses were calibrated using a power sensor to de-embed the RF power applied to the DUT. S-parameters were measured while sweeping frequency from 1 GHz to 40 GHz with an applied input power of -17 dBm. Five different switches and device test structures were stressed at input power levels between 24 and 36 dBm, in 3 dBm steps. No DC biasing was used to accelerate oxide degradation.

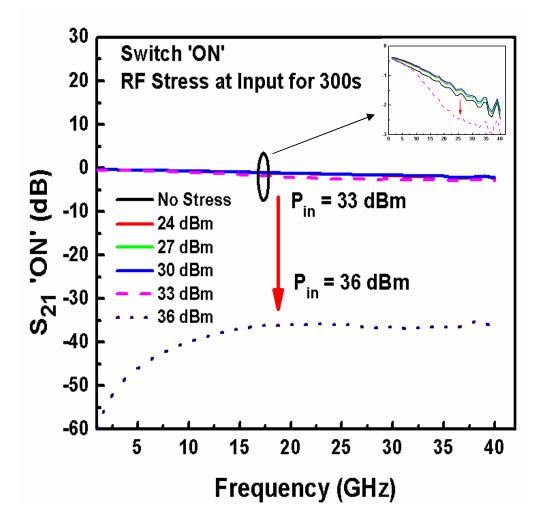

Figure 33 shows the insertion loss degradation of the series transistor structure. No degradation was observed up to RF input power of 30 dBm. However, the insertion loss degraded at 33 dBm RF stress (inset) before the series transistor failed catastrophically during stressing at 36 dBm input power.

Figure 37. Insertion Loss of standalone DUT after RF-Stress. Degradation is observed at 33 dBm (inset) before device fails.

Figure 38. Isolation of the Series Transistor (M2) increases after RF stressing up to 36 dBm input power.

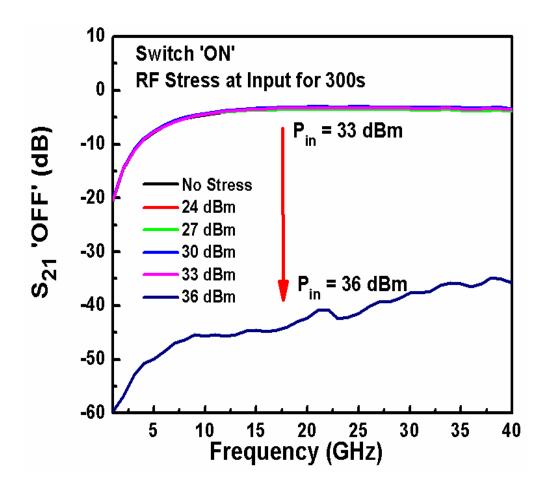

As shown in Figure 38, similar behavior was observed for transistor isolation or  $S_{21}$  when the switch was turned 'OFF'. Figure 39 shows the impact of RF stress on  $S_{11}$  of the device in the 'ON' state. The input matching conditions for the device change with RF stress and the device starts behaving as an electrical "open" after being subjected to 36 dBm input RF power. Similar behavior of  $S_{22}$  in Figure 40 implies that both ports (source, drain) behave as "open's" for small-signal power. The shunt transistor was not analyzed in detail, but we expect the device to show similar degradation when the switch is operated in the transmit state. Stacking of shunt devices at the transmit leg and series

devices at the receiving leg of the switch can help in improving breakdown voltage by distributing the large signal swing [38].

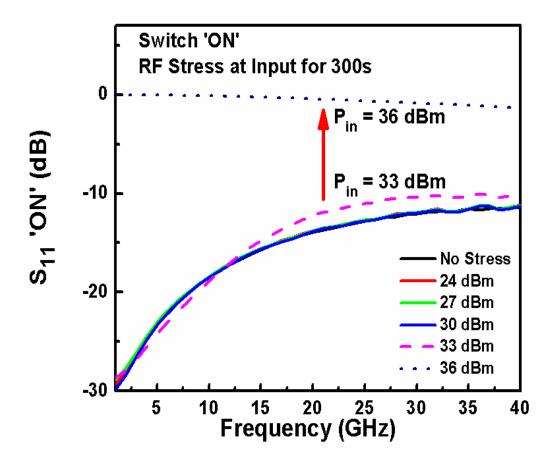

Figure 39. Input matching of the series transistor (M2) changes until the transistor behaves as an electrical "open" terminal after 36 dBm of RF stressing is applied.

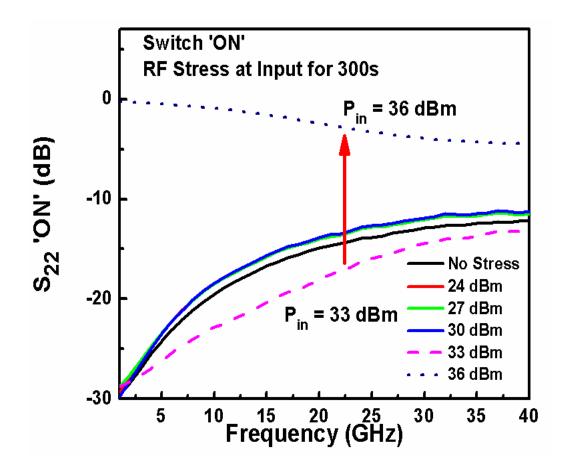

Figure 40. Output Matching of the DUT changes with RF stress.

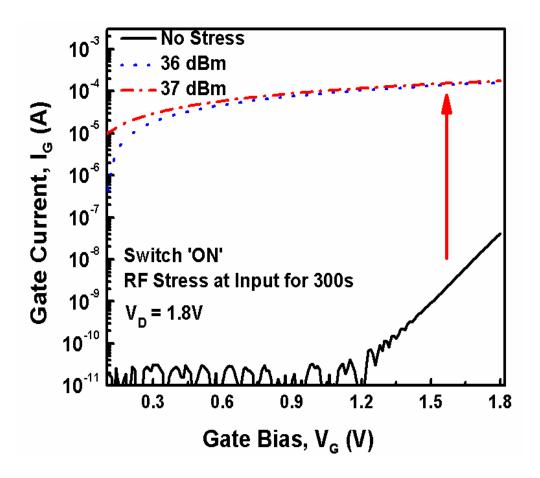

To understand the failure mechanisms in the transistor, we performed DC sweeps on the transistor after RF stressing. Device failure was observed in the transfer characteristics of the device, which can be attributed to gate-oxide breakdown. As shown in Figure 41, the gate current of the device degrades considerably after 33 dBm of RF stress (and above). The devices exhibit typical breakdown current characteristics with very high current levels at low field. Similar gate current behavior has been observed for high voltage 0.28 µm CMOS devices used in power amplifiers [39]. No difference in gate current was observed when the source and drain terminals were swapped after gate breakdown. This observation may be attributed to the fact that no DC drain bias is applied to the device during its operation as an RF switch (hence, no localized field). Instead, the transistor acts as a pass-gate switch without any DC bias on the drain and source terminals. Thus, hot carrier effects are negligible. The current flowing to the reverse biased n-well did not change after RF stressing (~175 pA). This observation eliminates the possibility of breakdown of the reverse-biased p-n junction between the body and n-well of triple-well process.

Figure 41. Gate-Breakdown induced by high RF power at the drain of the device produces failure of the transistor as an RF switch.

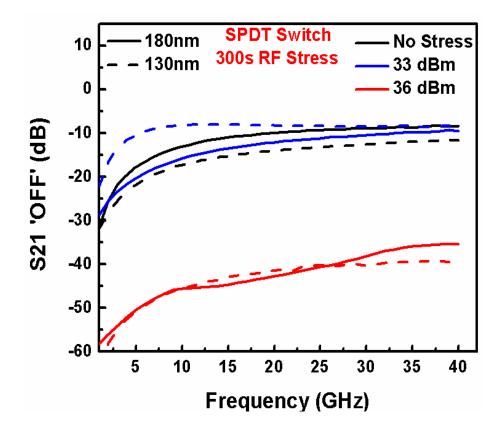

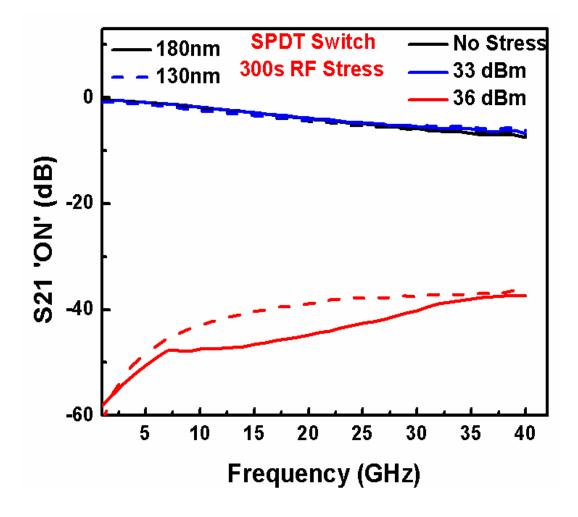

Reliability measurements were performed on RF switches designed in two different CMOS technology generations to assess the impact of node scaling. All switches were series-shunt SPDT switches with similar sized series and shunt transistors. Figure 42 shows that an RF switch designed in 130 nm CMOS shows degradation in isolation after stressing at 33 dBm input power, before it fails completely after 36 dBm stress. This degradation is presumably due to the damage in smaller sized shunt transistor, M4 (Figure 35) which reduces isolation of the switch since the shunt transistor is connected to AC ground. Notice that the effect of the shunt device can only be observed during the full operation of the switch. However, independent treatment of shunt device reliability needs attention.

Figure 42. Impact of RF stress on isolation of SPDT switch in 180nm and 130nm CMOS technologies.