# A Fully-Integrated All-Digital Outphasing Transmitter

## for Wireless Communications

A Dissertation Presented to The Academic Faculty

by

Kwan-Woo Kim

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2009

Copyright 2009 by Kwan-Woo Kim

## A Fully-Integrated All-Digital Outphasing Transmitter

## for Wireless Communications

Approved by:

Dr. Joy Laskar, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Chang-Ho Lee School of Electrical & Computer Engineering Georgia Institute of Technology

Dr. Ravi V. Bellamkonda Department of Biomedical Engineering *Georgia Institute of Technology*  Dr. Emmanouil M. Tentzeris School of Electrical & Computer Engineering *Georgia Institute of Technology*

Dr. David E. Schimmel School of Electrical & Computer Engineering Georgia Institute of Technology

Date Approved: Nov. 06, 2009

## ACKNOWLEDGEMENTS

First, I would like to appreciate the enthusiastic supervision of my research advisor, Professor Joy Laskar. He has always supported my research with great motivation and provided an excellent research environment. Without his guidance and support, this research would not be completed.

I am also grateful to my committee members, Professor Emmanouil M. Tentzeris, Professor Chang-Ho Lee, Professor David E. Schimmel, and Professor Ravi V. Bellamkonda for their time in reviewing my thesis.

I would like to specially thank Dr. Kyutae Lim for his helpful guidance, deep discussion through the research work. I also would like to thank Dr. Chang-Ho Lee again for his generous support for my research. I am greatly indebted my colleague members in Microwave Application Group (MAG) for making good environment as a team supporting each other. I owe special thanks to the cognitive radio (CR) team and the Samsung Design Center (SDC) members for their numerous technical discussions in circuit and system design.

I also thank Dr. Edward Gebara, Dr. Debasis Dawn, and Dr. Stephan Pinel for their technical discussion and guidance for the research directions.

I am deeply grateful to my parents, Joong Kon Kim and Duck Hyun Cho for their endless love and support throughout my life. I have to acknowledge my beloved wife, Yejee Ha for her love and encouragement.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTSII                                                    |

|-----------------------------------------------------------------------|

| LIST OF TABLES                                                        |

| LIST OF FIGURES                                                       |

| SUMMARYX                                                              |

| CHAPTER I 1                                                           |

| CHAPTER II                                                            |

| 2.1 PRINCIPLE OF OUTPHASING AMPLIFICATION                             |

| 2.2 CHALLENGES                                                        |

| 2.2.1 MATCHING REQUIREMENTS AND MISMATCH ERROR COMPENSATION           |

| 2.2.2 EFFICIENCY ENHANCEMENT VS. LINEARITY                            |

| 2.3 PRIOR ART                                                         |

| 2.3.1 QUADRATURE MODULATOR BASED OUTPHASING TRANSMITTER WITH MISMATCH |

| CALIBRATION                                                           |

| 2.3.2 Analog Phase Shifter based Outphasing Transmitter               |

| 2.3.3 CHIREIX POWER COMBINER FOR EFFICIENCY ENHANCEMENT               |

| CHAPTER III                                                           |

| 3.1 MAIN ARCHITECTURE                                                 |

| 3.2 System Requirements                                               |

| 3.3 KEY BUILDING BLOCKS                                               |

| 3.3.1 DIGITAL PHASE MODULATOR                                         |

| 3.3.2 Power Amplifier                                                 |

| 3.3.3      | Power Combiner                                     | . 31 |

|------------|----------------------------------------------------|------|

| 3.4 Die    | GITAL MISMATCH COMPENSATION ALGORITHMS             | . 34 |

| 3.4.1      | Foreground Mismatch Compensation Algorithms        | . 36 |

| 3.4.2      | BACKGROUND MISMATCH COMPENSATION ALGORITHMS        | . 40 |

| 3.4.3      | Simulation Results                                 | . 41 |

| CHAPTER IV | 7                                                  | . 46 |

| 4.1. IC    | Implementation                                     | . 46 |

| 4.2. Bu    | ILDING BLOCKS                                      | . 47 |

| 4.2.1.     | DIGITAL PHASE MODULATOR                            | . 47 |

| 4.2.2.     | Voltage-Controlled Oscillator                      | . 51 |

| 4.2.3.     | Frequency Synthesizer                              | . 52 |

| 4.3. ME    | EASUREMENT RESULTS                                 | . 55 |

| CHAPTER V  |                                                    | . 64 |

| 5.1. Po    | WER COMBINER                                       | . 66 |

| 5.2. DE    | SIGN CONSIDERATIONS                                | . 72 |

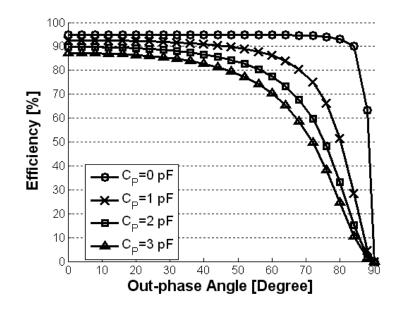

| 5.2.1.     | Efficiency                                         | . 72 |

| 5.2.2.     | Linearity                                          | . 80 |

| 5.3. CII   | RCUIT IMPLEMENTATION                               | . 81 |

| 5.4. Ke    | Y BUILDING BLOCKS                                  | . 83 |

| 5.4.1.     | Low Power Digital Phase Modulator                  | . 83 |

| 5.4.2.     | CLASS E POWER AMPLIFIER WITH ISOLATED COMBINER     | . 86 |

| 5.4.3.     | CLASS D POWER AMPLIFIER WITH NON-ISOLATED COMBINER | . 86 |

| 5.5. ME    | EASUREMENT RESULTS                                 | . 87 |

| 5.5.1.     | Measurement Setup   |     |

|------------|---------------------|-----|

| 5.5.2.     | Measurement Results |     |

| CHAPTER V  | [                   |     |

| REFERENCES | 5                   |     |

| PUBLICATIO | NS                  |     |

| VITA       |                     | 101 |

# LIST OF TABLES

| TABLE 4.1. PERFORMANCE SUMMARY OF OUTPHASING MODULATOR | 6 | 52 | 2 |

|--------------------------------------------------------|---|----|---|

|--------------------------------------------------------|---|----|---|

# LIST OF FIGURES

| FIGURE 1.1. EVOLUTION OF WIRELESS COMMUNICATIONS.                                                              | 1    |

|----------------------------------------------------------------------------------------------------------------|------|

| FIGURE 1.2. SIGNAL PROFILE OF OFDM-WIRELESS LAN. (A) TIME-DOMAIN SIGNAL                                        |      |

| WAVEFORM, (B) PDF OF OUTPUT POWER                                                                              | 2    |

| FIGURE 1.3. MAXIMUM EFFICIENCY OF IDEAL CLASS A AND CLASS B PAS.                                               | 3    |

| FIGURE 1.4. COMPARISON OF LINEAR AMPLIFICATION TECHNIQUES.                                                     | 4    |

| FIGURE 1.5. COMPARISON OF EFFICIENCY WITH DIFFERENT LINEAR AMPLIFICATION                                       |      |

| TECHNIQUES                                                                                                     | 5    |

| EXCURE 2.1 OUTPUT ONLY OF COMPOSITION                                                                          | 0    |

| FIGURE 2.1. OUTPHASING SIGNAL DECOMPOSITION.                                                                   |      |

| FIGURE 2.2. VECTOR REPRESENTATION OF OUTPHASING SIGNAL DECOMPOSITION.                                          |      |

| FIGURE 2.3. COMBINER ARCHITECTURE: ISOLATED AND NON-ISOLATED COMBINER                                          |      |

| FIGURE 2.4. CONVENTIONAL ANALOG OUTPHASING TRANSMITTER WITH I/Q QUADRATU<br>MODULATORS                         |      |

| FIGURE 2.5. ANALOG PHASE SHIFTER-BASED OUTPHASING TRANSMITTER.                                                 |      |

| FIGURE 2.6. CHIREIX POWER COMBINER.                                                                            |      |

|                                                                                                                | 17   |

| FIGURE 3.1. BLOCK DIAGRAM OF PROPOSED ALL-DIGITAL OUTPHASING TRANSMITTER                                       | 19   |

| FIGURE 3.2. EFFECTS OF NUMBER OF BITS IN DPM ON IEEE 802.16E MODULATION                                        | 22   |

| FIGURE 3.3. BLOCK DIAGRAM OF N-BIT DIGITAL PHASE MODULATOR.                                                    | 24   |

| FIGURE 3.4. TIMING DIAGRAM OF 8-BIT DIGITAL PHASE MODULATOR                                                    | 26   |

| FIGURE 3.5. RELATIVE PHASE SHIFT CORRESPONDING TO INPUT SIGNALS.                                               | 27   |

| FIGURE 3.6. DLL-BASED DIGITAL PHASE MODULATOR.                                                                 | 28   |

| FIGURE 3.7. BASIC TOPOLOGY OF CLASS E AMPLIFIER                                                                | 30   |

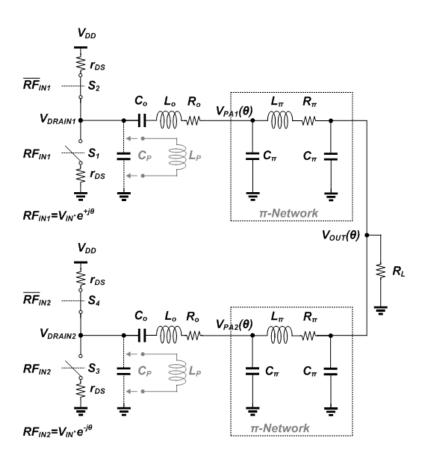

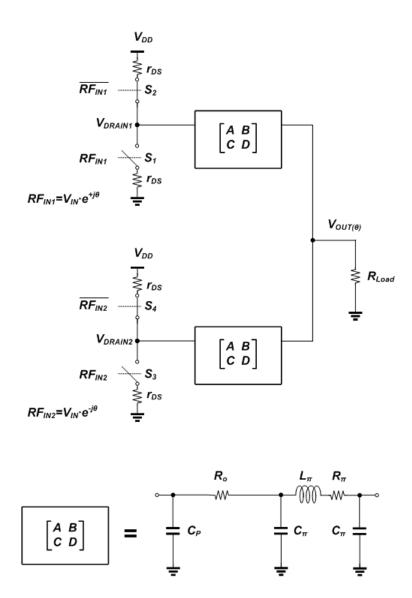

| FIGURE 3.8. ARCHITECTURE OF GENERAL NON-ISOLATED COMBINER.                                                     | 32   |

| FIGURE 3.9. ERRORS OF OUTPHASING AMPLIFICATION.                                                                | 35   |

| FIGURE 3.10. SEQUENCE OF STEPS FOR STATIC MISMATCH COMPENSATION.                                               | 37   |

| FIGURE 3.11. SEQUENCE OF STEPS FOR DYNAMIC MISMATCH COMPENSATION. (A) DYNA                                     | AMIC |

| ERROR MEASUREMENT WITH TEST VECTORS, (B) DYNAMIC MISMATCH COMPENSAT                                            | ΓION |

| WITH LOOK-UP TABLES.                                                                                           | 40   |

| FIGURE 3.12. EVM AND SPECTRUM OF OUTPUT SIGNAL BEFORE MISMATCH CALIBRATIC                                      |      |

|                                                                                                                | 43   |

| FIGURE 3.13. SUMMARY OF LOOK-UP TABLES                                                                         | 44   |

| FIGURE 3.14. EVM AND SPECTRUM OF OUTPUT SIGNAL AFTER MISMATCH CALIBRATION                                      | v 44 |

|                                                                                                                | 47   |

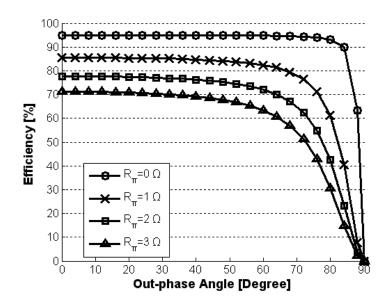

| FIGURE 4.1. BLOCK DIAGRAM OF ALL-DIGITAL OUTPHASING TRANSMITTER.                                               |      |

| FIGURE 4.2. BLOCK DIAGRAM OF PROPOSED 9-BIT DIGITAL PHASE MODULATOR.                                           |      |

| FIGURE 4.3. CIRCUIT IMPLEMENTATION OF 5-BIT DIGITAL PHASE INTERPOLATOR.                                        |      |

| FIGURE 4.4. MEASUREMENT RESULTS AND CALIBRATION OF DIGITAL PHASE INTERPOLA                                     |      |

| FIGURE 4.5. TIMING DIAGRAM OF 9-BIT DIGITAL PHASE MODULATOR                                                    |      |

| FIGURE 4.5. THMING DIAGRAM OF 9-BIT DIGITAL PHASE MODULATOR<br>FIGURE 4.6. SCHEMATIC OF ON-CHIP QUADRATURE VCO |      |

| FIGURE 4.7. BLOCK DIAGRAM OF INTEGRATED FREQUENCY SYNTHESIZER.                                                 |      |

| I IGORE T. 7. DEOCR DIAGRAM OF INTEGRATED PREQUENCE STIMILESIZER.                                              | 55   |

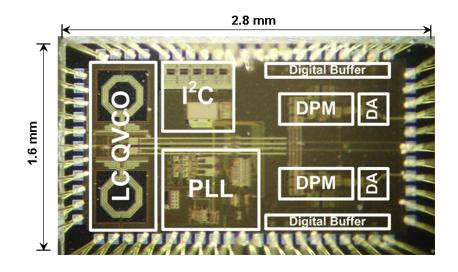

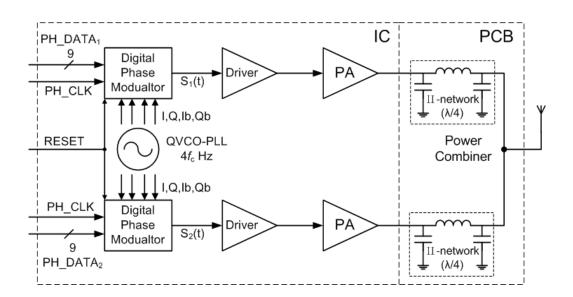

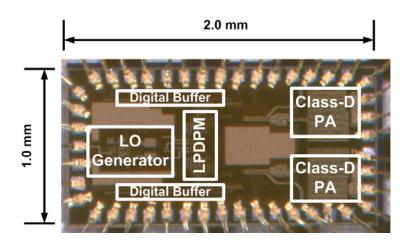

| FIGURE 4.8. CHIP MICROPHOTOGRAPH.                                                              | 56   |

|------------------------------------------------------------------------------------------------|------|

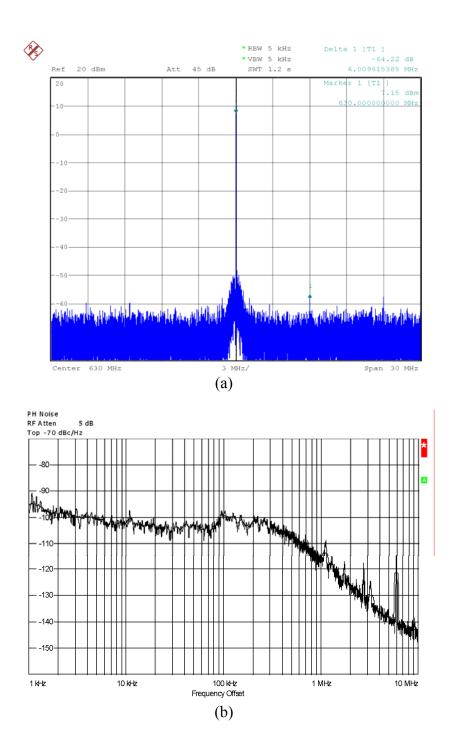

| FIGURE 4.9. PLL MEASUREMENT RESULTS. (A) OUTPUT SPECTRUM, (B) PHASE NOISE                      |      |

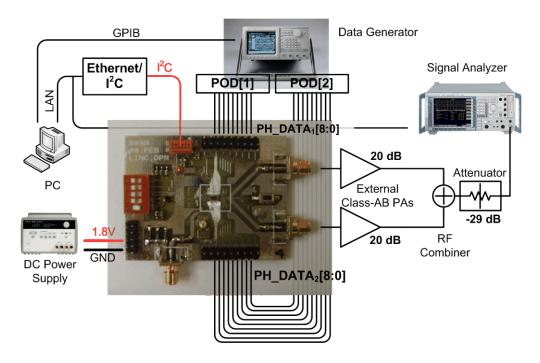

| FIGURE 4.10. MEASUREMENT SETUP.                                                                |      |

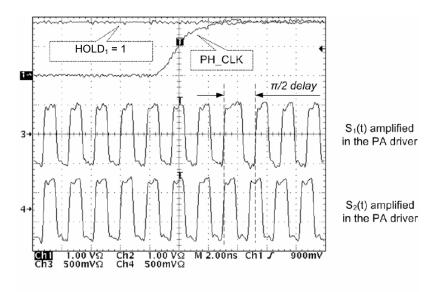

| FIGURE 4.11. PHASE MODULATED $S_1(T)$ with HOLD <sub>1</sub> and PH_CLK.                       | 59   |

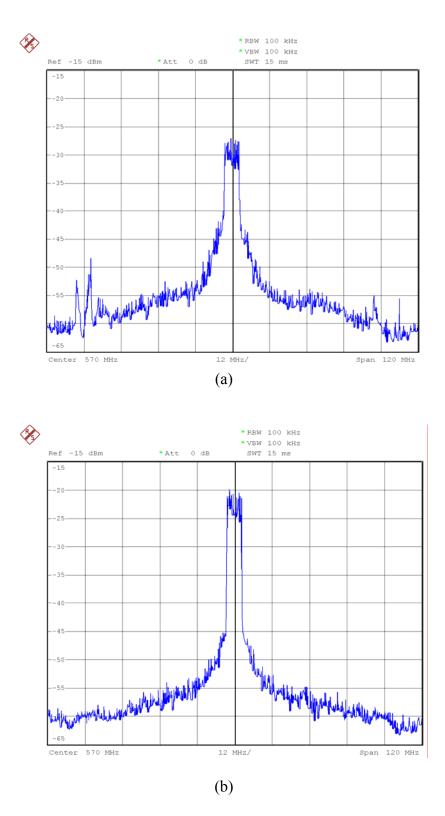

| FIGURE 4.12. SPECTRUM OF OUTPUT SIGNAL BEFORE AND AFTER MISMATCH                               |      |

| COMPENSATION. (A) BEFORE MISMATCH COMPENSATION WITH $F_B$ =48 MHz, (B) AF                      | TER  |

| MISMATCH COMPENSATION WITH $F_{\rm B}$ =80 MHz.                                                | 61   |

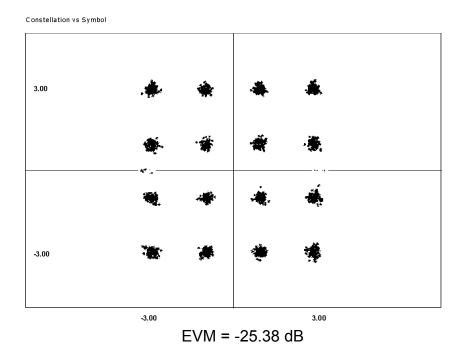

| FIGURE 4.13. EVM measurement after mismatch compensation with $F_{\rm B}$ =80 MH               | ĺZ.  |

|                                                                                                | 62   |

| FIGURE 5.1. WILKINSON POWER COMBINER.                                                          | 65   |

| FIGURE 5.2. NON-ISOLATED POWER COMBINER.                                                       |      |

| FIGURE 5.3. COMPARISON OF POWER EFFICIENCY WITH DIFFERENT COMBINER AND PA                      |      |

| STRUCTURE                                                                                      | 66   |

| FIGURE 5.4. NON-ISOLATED COMBINER WITH TRANSMISSION LINES.                                     |      |

| FIGURE 5.5. SIMPLE SCHEMATIC OF VM CLASS D PA.                                                 | 70   |

| FIGURE 5.6. SIMPLE SCHEMATIC OF CLASS E PA.                                                    | 70   |

| FIGURE 5.7. SIMPLE SCHEMATIC OF CLASS F PA.                                                    | 70   |

| FIGURE 5.8. EFFICIENCY COMPARISON BETWEEN ISOLATED AND NON-ISOLATED COMBIN                     | JER. |

|                                                                                                | 71   |

| FIGURE 5.9. LINEARITY COMPARISON BETWEEN ISOLATED AND NON-ISOLATED COMBINI                     |      |

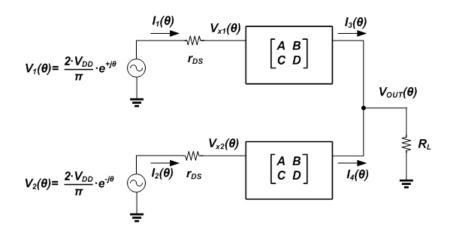

| FIGURE 5.10. SCHEMATIC OF VM CLASS D MODEL WITH NON-ISOLATED COMBINER                          |      |

| FIGURE 5.11. SIMPLIFIED SCHEMATIC OF VM CLASS D MODEL WITH NON-ISOLATED                        |      |

| COMBINER.                                                                                      | 75   |

| FIGURE 5.12. EQUIVALENT SCHEMATIC OF VM CLASS D MODEL WITH NON-ISOLATED                        |      |

| COMBINER                                                                                       | 76   |

| FIGURE 5.13. EFFICIENCY RESULTS WITH DIFFERENT CP VALUES                                       | 78   |

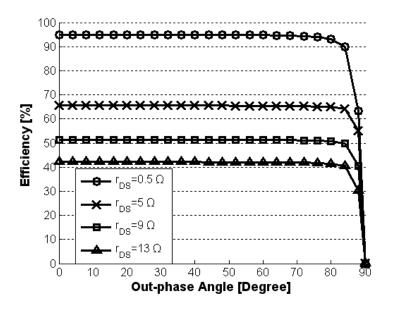

| FIGURE 5.14. EFFICIENCY RESULTS WITH DIFFERENT RDS VALUES.                                     | 79   |

| FIGURE 5.15. Efficiency results with different $R_0$ values                                    | 79   |

| Figure 5.16. Efficiency results with different $R_{\mbox{\tiny II}}$ values                    | 80   |

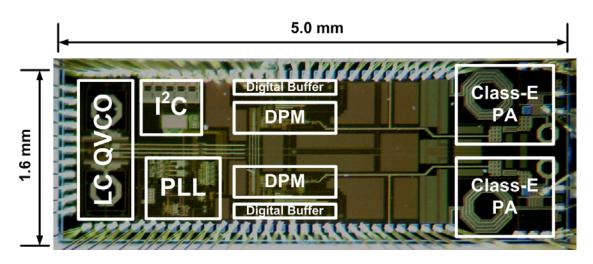

| FIGURE 5.17. BLOCK DIAGRAM OF FULLY-INTEGRATED ALL-DIGITAL OUTPHASING                          |      |

| TRANSMITTER                                                                                    | 81   |

| FIGURE 5.18. CHIP MICROGRAPH (FULLY-INTEGRATED ALL-DIGITAL OUTPHASING                          |      |

| TRANSMITTER WITH CLASS E PAS)                                                                  |      |

| FIGURE 5.19. CHIP MICROGRAPH (ALL-DIGITAL OUTPHASING TRANSMITTER WITH LPDF<br>AND CLASS D PAS) |      |

| FIGURE 5.20. BLOCK DIAGRAM OF PROPOSED LOW POWER DIGITAL PHASE MODULATOR.                      | 84   |

| FIGURE 5.21. BLOCK DIAGRAM OF PROPOSED LOW POWER DIGITAL PHASE MODULATOR.                      | 85   |

| FIGURE 5.22. BUILDING BLOCKS FOR LPDPM. (A) SCHEMATIC OF TSPC D-FLIPFLOP, (E                   |      |

| DIGITAL PI                                                                                     |      |

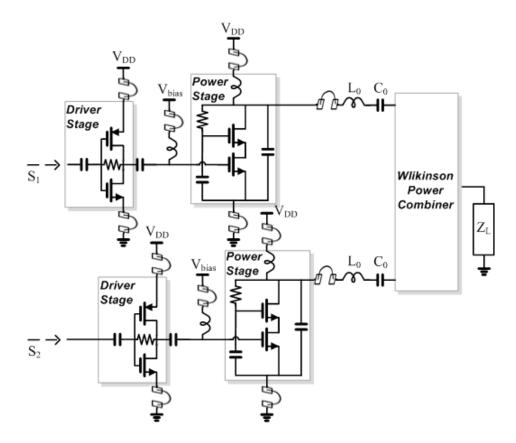

| FIGURE 5.23. SCHEMATIC OF IMPLEMENTED CLASS E PAS AND COMBINER                                 |      |

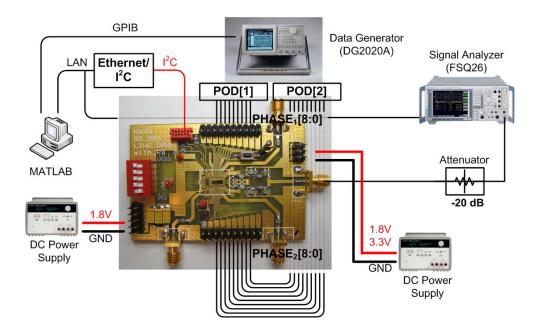

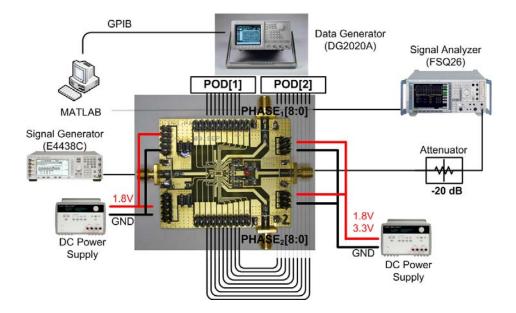

| FIGURE 5.24. IC MEASUREMENT SETUP FOR FULLY-INTEGRATED ALL-DIGITAL OUTPHAS                     |      |

| TRANSMITTER WITH CLASS E PAS.                                                                  |      |

| FIGURE 5.25. IC MEASUREMENT SETUP FOR ALL-DIGITAL OUTPHASING TRANSMITTER W                     |      |

| CLASS D PAS                                                                                    | 88   |

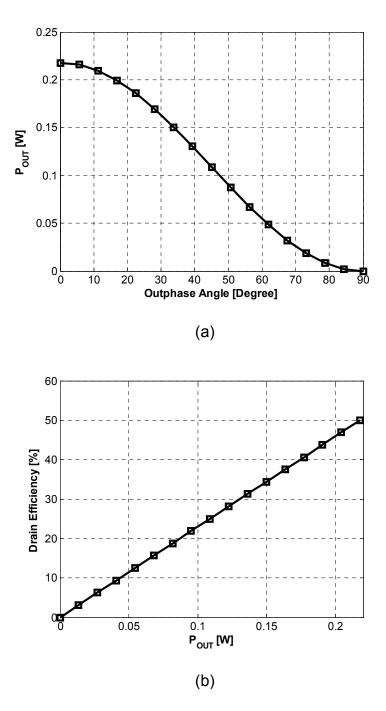

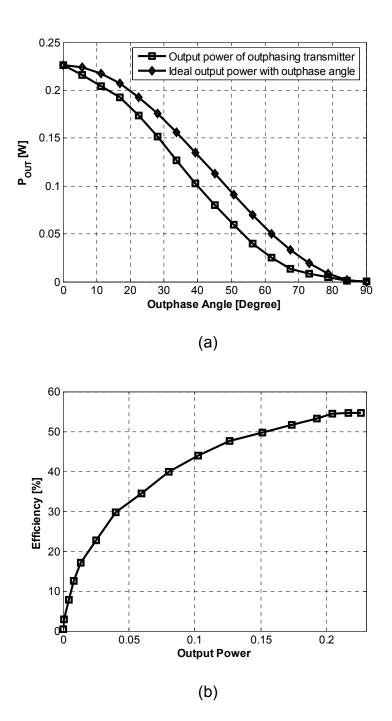

| FIGURE 5.26. OUTPUT POWER AND EFFICIENCY MEASURED WITH DIFFERENT OUTPHASE |    |

|---------------------------------------------------------------------------|----|

| ANGLE IN OUTPHASING TRANSMITTER WITH CLASS E PAS. (A) OUTPUT POWER, (B)   |    |

| DRAIN EFFICIENCY.                                                         | 89 |

| FIGURE 5.27. OUTPUT POWER AND EFFICIENCY MEASURED WITH DIFFERENT OUTPHASE |    |

| ANGLE IN OUTPHASING TRANSMITTER WITH CLASS D PAS. (A) OUTPUT POWER, (B)   |    |

| DRAIN EFFICIENCY.                                                         | 90 |

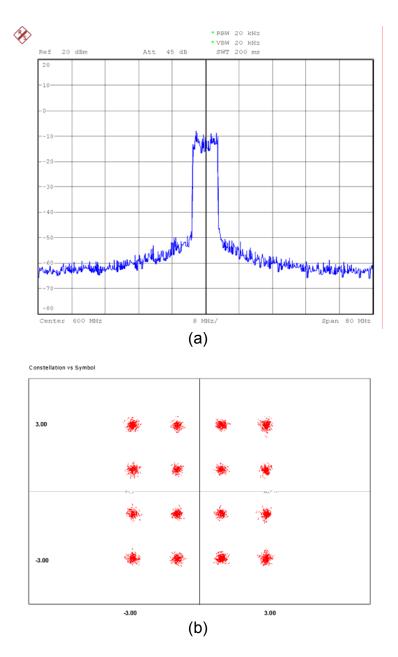

| FIGURE 5.28. OUTPUT SPECTRUM AND EVM MEASURED IN OUTPHASING TRANSMITTER   |    |

| WITH CLASS E PAS. (A) OUTPUT SPECTRUM, (B) CONSTELLATION (EVM=-26.7 DB).  |    |

|                                                                           | 91 |

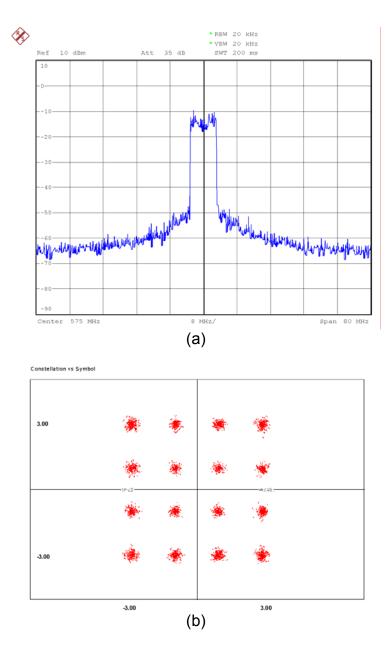

| FIGURE 5.29. OUTPUT SPECTRUM AND EVM MEASURED IN OUTPHASING TRANSMITTER   |    |

| WITH CLASS D PAS. (A) OUTPUT SPECTRUM, (B) CONSTELLATION (EVM=-25.5 DB).  |    |

|                                                                           | 92 |

# **SUMMARY**

The objective of the proposed research is to present a new all-digital outphasing transmitter IC, a comprehensive explanation of its operation, and its performance characterization. The all-digital transmitter chip leverages flexible digital phase modulators (DPMs) to adaptively compensate for amplifier mismatches. As the DPM uses a digital input to directly modulate the RF phase of each path, the phase control becomes very simple and accurate for power amplifier (PA) gain/phase mismatch compensation. Furthermore, this digital phase modulation scheme also facilitates minimizing the distortion of an RF combiner. It is newly proposed that two distinct digital predistortion algorithms are required for perfect compensation for both PAs and a combiner. All phase calibration values can be adaptively calculated as a function of outphase angle and saved in digital look-up tables to predistort the phase inputs of two DPMs.

Various types of PAs and combiners are investigated to further enhance the performance of the outphasing transmitter. These features are implemented in a chip fabricated in a 0.18-µm CMOS process and evaluated with IEEE 802.16e baseband symbols.

# **CHAPTER I**

## **INTRODUCTION**

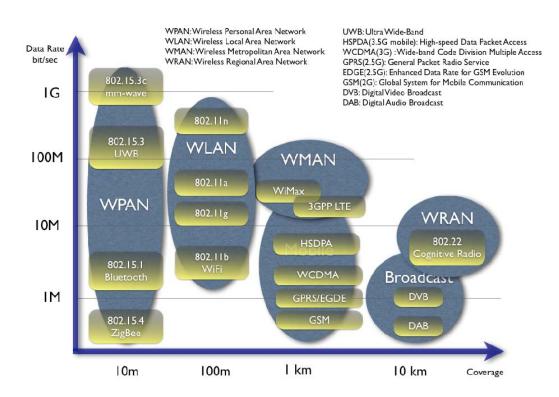

The demand for higher data throughput in wireless communications has been increasing at a tremendous rate over the past decade. Figure 1.1 shows the evolution of wireless communication trends with various coverage ranges.

Figure 1.1. Evolution of wireless communications.

As shown in the figure, every new emerging wireless standard requires a higher data rate with more stringent user connectivity. To deal with these requirements, both spectral and power efficiencies are important factors in modern wireless communication for high-speed data connection and long battery life, respectively.

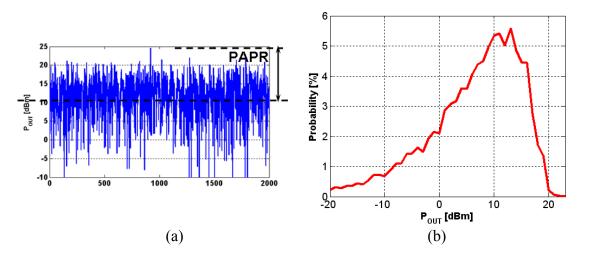

However, an intrinsic trade-off exists between these two PA design metrics. To increase the spectral efficiency, baseband signals should have complex I/Q symbols, which require both amplitude and phase modulation. Since most amplitude modulated signals have high peak-to-average-power ratio (PAPR), a substantial back-off is generally needed to ensure adequate amplifier linearity; thus the average power efficiency is significantly degraded. For example, orthogonal frequency division multiplexing (OFDM) is very spectrally efficient and mitigates multi-path fading due to its long symbol duration, but one of the major drawbacks of the OFDM system is its sensitivity to nonlinear distortion due to its wide variation in signal envelope and low average power efficiency. Figure 1.2 shows the time-domain waveform of an IEEE802.11g OFDM-Wireless local area network (LAN) signal and its probability density function (PDF) of output power [1].

Figure 1.2. Signal profile of OFDM-Wireless LAN. (a) Time-domain signal waveform, (b) PDF of output power.

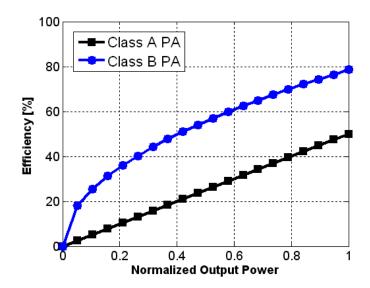

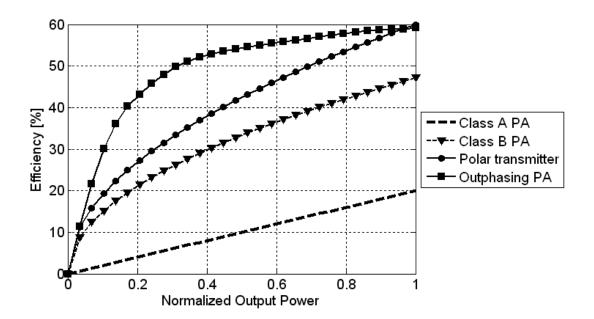

As shown in the figure, the output power of the OFDM signal is much less than the peak output power at most times. However, PAs, which consumes the largest amount of power in a typical wireless transmitter, tend to be most efficient only when delivering peak output power, while the efficiency degrades with reduced output power. Figure 1.3 shows typical linear PA efficiency graphs.

Figure 1.3. Maximum efficiency of ideal Class A and Class B PAs.

Therefore, to support the large PAPR in the OFDM systems, the PAs unfortunately have to spend most of their time in back-off where the efficiency is poor. The average power efficiency of an OFDM system using linear PAs can be calculated by multiplying the PDF of output power by the efficiency profile of linear PA and it is typically much less than 15% in most CMOS PAs; thus most of the system power is dissipated in PA to meet the linearity requirements of an OFDM signal [2].

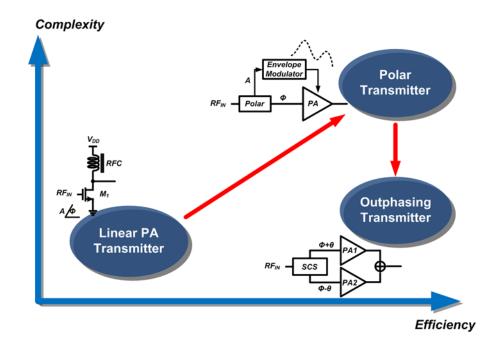

To resolve efficiency degradation problems in linear PAs, various efficiency enhancement technologies have been proposed. Figure 1.4 compares three major linear amplification techniques. A polar transmitter, also called envelope elimination and restoration (EER), is one of the most promising techniques for improving efficiency. Compared to a Class A PA, the polar transmitter demonstrates a much higher power efficiency. The polar transmitter basically operates by converting complex I/Q symbols into envelope and constant envelope phase signals. The constant envelope signal is amplified through a highly efficient nonlinear PA with a separate envelope control path. However, despite the efficiency improvement, the separate amplitude modulation through a low dropout (LDO) regulator, DC/DC converter,  $\Sigma\Delta$  modulator, or PWM has significant bandwidth limitation and efficiency degradation problems in commercial wideband systems [3]-[11].

Figure 1.4. Comparison of linear amplification techniques.

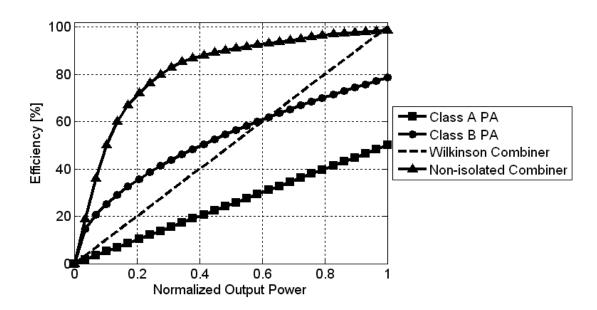

The outphasing power amplification, also called linear amplification using nonlinear components (LINC), was proposed as another solution that may offer high efficiency with good linearity [12]. LINC eliminates the high linearity demands on a single PA by summing the outputs of two nonlinear PAs via a power combiner to amplify non-constant envelope signals. This technique produces an amplifier with the linearity of a moderate back-off linear PA at an efficiency approaching that of a switching amplifier. Also, the outphasing transmitter, which uses two simple wideband switching PAs, can be a good solution for highly power efficient and wideband operation. Figure 1.5 shows the efficiency comparison of different linear amplification techniques.

Figure 1.5. Comparison of efficiency with different linear amplification techniques.

The power efficiency of a Class A amplifier decreases with output power  $P_{out}$  (relative to its peak value  $P_{out,max}$ ) proportional to  $P_{out}/P_{out,max}$ . Similarly, for a Class B amplifier, the efficiency varies as  $(P_{out}/P_{out,max})^{0.5}$ . Class AB amplifiers have output power

variation intermediate between these values. Thus, there is customarily an inherent tradeoff between linearity and efficiency in a typical amplifier design [2]. The peak efficiency of a polar transmitter is much higher than that of linear PAs and overall efficiency is mainly determined by the efficiency of the envelope modulator, such as a LDO and DC/DC converter. Also, the outphasing transmitter can provide comparable efficiency with the polar transmitter through PA and combiner optimization. The efficiency curve of the outphasing transmitter will be analyzed in detail.

The goal of this research is to enhance the efficiency at back-off and thus reduce the average power consumption of such systems operating with large PAPR through the outphasing amplification techniques. In this dissertation, a new architecture for an alldigital outphasing transmitter is presented. The transmitter employs a novel DPM, which enables all transmitter blocks other than the switching PAs to operate via digital signals. By modulating the outphase signals digitally, mismatches caused by PAs and the combiner are detected and stored in digital look-up tables for each frequency channel. Furthermore, by modulating phase directly, the proposed outphasing transmitter needs only two kinds of test algorithms for complete mismatch compensation, which is very simple compared to an outphasing transmitter based on a quadrature modulator as used in prior work.

The original contributions and main focus of this dissertation include:

1. Development of a new all-digital outphasing transmitter architecture with detailed system requirements and error compensation algorithms.

6

First all-digital outphasing modulator with a 0.18-μm CMOS technology for OFDM signals.

3. First to introduce a fully-integrated all-digital outphasing transmitter IC with thorough PA and combiner analysis.

This dissertation is organized as follows:

Chapter 1 is an introduction of this dissertation and demonstrates the necessity of highly efficient linear power amplifiers in wireless communications. Following that, the organization of the dissertation is described. In chapter 2, a brief historical background and origin of the problems of an outphasing amplification technique is introduced. In chapter 3, a behavioral model for a new all-digital outphasing transmitter, consisting of dual DPMs and switching power amplifiers, is described in detail. This transmitter architecture not only provides linear amplification of OFDM modulation, but also permits fine phase control for error calibration. The effects of phase quantization on digital modulation error performance are studied. The study confirms the feasibility of an all-digital amplifier approach and demonstrates that modulation specifications can be met using quite modest digital work lengths.

Chapter 4 focuses on real circuit implementation of the all-digital outphasing modulator with a 0.18-µm CMOS technology. Each building block is described with its detailed operating principles. Also, the overall modulator IC performances, such as total power consumption, phase noise results of a frequency synthesizer, and modulation errors, are demonstrated. Chapter 5 describes and analyzes the effects of switching power amplifiers on overall outphasing transmitter efficiency. The average system efficiency mainly depends on the characteristics of power amplifiers; thus various nonlinear

switching PAs are analyzed numerically in an outphasing transmitter. In addition, a fullyintegrated all-digital outphasing transmitter IC is presented to verify the PA analysis. Two types of PAs, Class D and Class E, are implemented and integrated with the outphasing modulator presented in chapter 4.

Finally, chapter 6 summarizes the dissertation and provides guidance towards future research possibilities.

# **CHAPTER II**

# **OUTPHASING AMPLIFICATION**

## 2.1 Principle of Outphasing Amplification

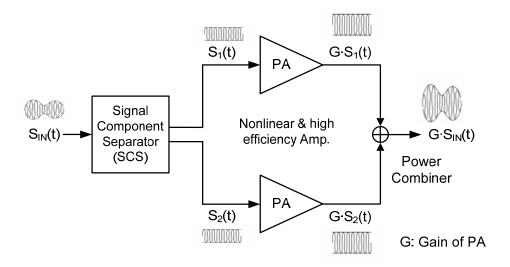

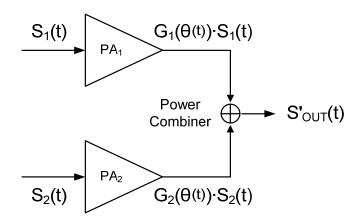

The outphasing amplification technique basically operates by representing an amplitude and phase modulated signal,  $S_{IN}(t)$ , as the difference of two constant amplitude, phase modulated signals,  $S_I(t)$  and  $S_2(t)$  [13]. These two signals can then be amplified separately through high efficiency nonlinear switching PAs and recombined to produce the amplified original signal, as shown in Figure 2.1.

Figure 2.1. Outphasing signal decomposition.

A complex polar representation of the original signal can be written as

$$S_{IN}(t) = \left[S_{I}(t) + j \cdot S_{Q}(t)\right] \cdot e^{j\omega_{c}t} = \left|S_{IN}(t)\right| \cdot e^{j\left[\omega_{c} \cdot t + \phi(t)\right]},$$

(2.1)

where

$$\left|S_{IN}(t)\right| = \sqrt{S_{I}^{2}(t) + S_{Q}^{2}(t)}$$

(2.2)

$$\phi(t) = tan^{-1} \left( \frac{S_{\mathcal{Q}}(t)}{S_{\mathcal{I}}(t)} \right).$$

(2.3)

The original signal can also be expressed by a sum of two phase modulated signals as

$$S_{IN}(t) = S_1(t) + S_2(t)$$

(2.4)

$$S_1(t) = A_{\max} \cdot e^{j\left[\omega_c \cdot t + \phi(t) + \theta(t)\right]}$$

(2.5)

$$S_2(t) = A_{\max} \cdot e^{j\left[\omega_c \cdot t + \phi(t) - \theta(t)\right]}$$

(2.6)

$$S_{OUT}(t) = G \cdot S_{IN}(t) = G \cdot \left[S_1(t) + S_2(t)\right], \qquad (2.7)$$

where G is the gain of each PA and  $\theta(t)$  is the outphase angle given by

$$\theta(t) = \cos^{-1}\left(\frac{\left|S_{IN}(t)\right|}{2 \cdot A_{\max}}\right)$$

(2.8)

and  $(2 \cdot A_{max})$  is the peak of the  $S_{IN}(t)$  envelope.

From (2.5) and (2.6), both  $S_1(t)$  and  $S_2(t)$  have only phase information,  $\varphi(t)$  and  $\theta(t)$ .  $\varphi(t)$  is the phase of the original baseband symbol and  $\theta(t)$  is the additional phase modulated angle related to the outphasing amplification. The block, which calculates this

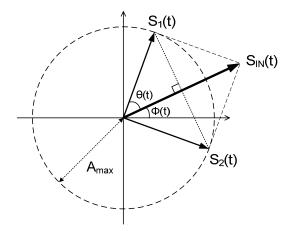

outphase angle calculation, is called a signal component separator (SCS). The outphasing decomposition and reconstruction can easily be represented by a vector diagram, as shown in Figure 2.2.

Figure 2.2. Vector representation of outphasing signal decomposition.

For an ideal outphasing amplifier, the two PAs should have identical gain and phase response for linear amplification and operate at saturation, yielding maximum amplifier efficiency. Simultaneously, the power combiner, which is used to combine the output of both PAs, should operate linearly over all the frequency bands of interest with perfect isolation between both inputs. However, both the non-identical responses of PAs and the power combiner's imperfect isolation distort the output signal of the outphasing transmitter. Thus, compensation algorithms for minimizing such distortion are necessary for a useful practical implementation. In this research, simple digital calibration methods using look-up tables are presented, which replace the conventional quadrature modulator with a handy DPM.

### 2.2 Challenges

Despite the efficiency enhancement, the outphasing topology has not been widely used in commercial amplifiers due to its strict matching requirements both in the phase and amplitude of each path [14][15] and non-isolation distortion and efficiency degradation caused by the RF power combiner [16][17].

#### 2.2.1 Matching Requirements and Mismatch Error Compensation

For an ideal outphasing amplifier, the two PAs should have identical gain and phase response for linear amplification and operate at saturation, yielding maximum amplifier efficiency. Simultaneously, the power combiner, which is used to combine the output of two PAs, should operate linearly over all the frequency bands of interest with perfect isolation between both inputs. However, both the non-identical responses of PAs and the non-isolation properties of a power combiner distort the output signal of the outphasing transmitter. The mathematical analysis to evaluate the effects of the imbalances and the non-isolation distortion on the performance of the outphasing transmitter shows that only a gain imbalance of  $0.3 \sim 0.4$  dB or the phase imbalance of  $2 \sim 3^\circ$  can be tolerated [18]. Thus, extremely precise compensation algorithms for minimizing such errors are necessary for a useful practical implementation.

#### 2.2.2 Efficiency Enhancement vs. Linearity

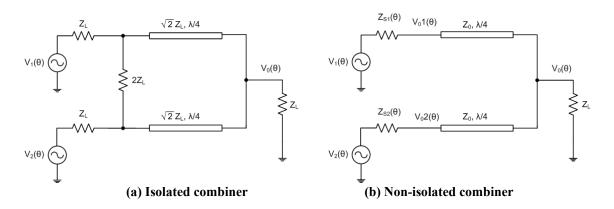

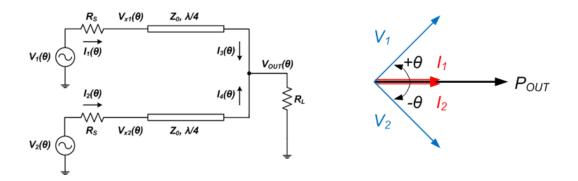

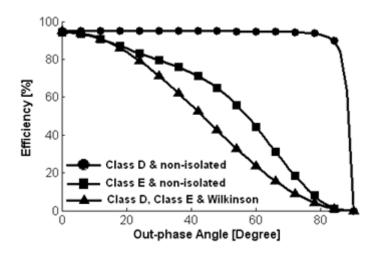

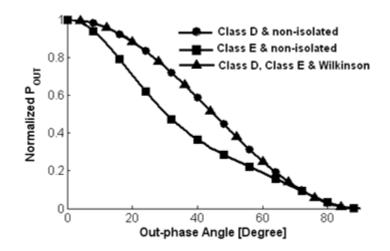

The key advantage of an outphasing system is the ability to maintain a high efficiency and the efficiency mainly depends on the configuration of a power combiner, which adds the outputs of two nonlinear PAs. There are two kinds of combiner architectures, isolated and non-isolated, as shown in Figure 2.3. An isolated combiner, such as a Wilkinson combiner, provides good linearity, but the out-of-phase components of the combined signals are directed to the isolated resistor load and dissipated when the output power decreases. On the contrary, a non-isolated combiner, such as a Chireix combiner, is a lossless combining structure, which provides much higher combining efficiency than the isolated combiner at the cost of linearity due to the lack of isolation. Thus, to take advantage of the high efficiency, an outphasing system requires the use of a non-isolated combiner with the improved linearity through appropriate calibration algorithms.

Figure 2.3. Combiner architecture: isolated and non-isolated combiner.

#### 2.3 Prior Art

#### 2.3.1 Quadrature Modulator based Outphasing Transmitter with Mismatch Calibration

Figure 2.4 shows a conventional analog outphasing transmitter based on I/Q quadrature modulators [19]. In the transmitter, the two outphasing signals,  $S_1(t)$  and  $S_2(t)$ ,

are modulated separately by I/Q quadrature modulators. Also, a digital error detection block measures any gain and phase mismatches between the two paths and combiner through a demodulation feedback path, and calibrates the errors by the predistortion of digital baseband symbols. The conventional outphasing transmitter consists of many analog blocks, such as baseband filters, I/Q generation blocks, mixers, driver amplifiers, and so on. Those analog blocks make the system bulky and more susceptible to process and temperature variations than digital blocks in integrated circuits.

Figure 2.4. Conventional analog outphasing transmitter with I/Q quadrature modulators.

Several mismatch calibration schemes have been proposed in [20] and [21], but the method of predistorting baseband symbols requires extremely complex calculations in conjunction with a digital-to-analog converter (DAC) and analog quadrature modulator, which may not be suitable for commercial products.

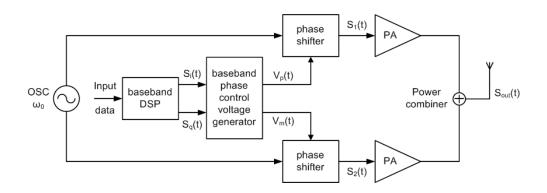

#### 2.3.2 Analog Phase Shifter based Outphasing Transmitter

An outphasing transmitter using two analog phase shifters is presented in Figure 2.5 [14]. In the transmitter, the essence of the outphasing modulation techniques lies in the analog phase shifters that vary the phases of the incoming clock with respect to baseband outphase angles. In the baseband DSP block of the transmitter, the input data are coded and mapped according to the in-phase and the quadrature-phase components, and the data are converted into analog signals with baseband filters. Then, the baseband phase control voltage generator of the transmitter generates the output signals,  $V_p(t)$  and  $V_m(t)$ , proportional to the outphase angle,  $\varphi(t)+\theta(t)$ ,  $\varphi(t)-\theta(t)$  in (2.5) and (2.6), respectively.

Figure 2.5. Analog phase shifter-based outphasing transmitter.

There are no mixers to upconvert baseband signals to RF or downconvert the RF signals to the baseband for reference feedback signals compared to the quadrature modulator-based outphasing transmitter. Elimination of the analog blocks and the feedback path in the phase-shifter-based outphasing transmitter results in high-speed, wideband operation, as well as no I/Q mismatches. The simple architecture of the

transmitter facilitates the phase modulation of the outphasing system and makes it more robust on circuit variations than the previous quadrature modulator-based transmitter. However, the analog control of the phase shifter degrades the accuracy of output phases, and the open loop structure is also not adequate for the flexible calibration of path mismatches and combiner errors.

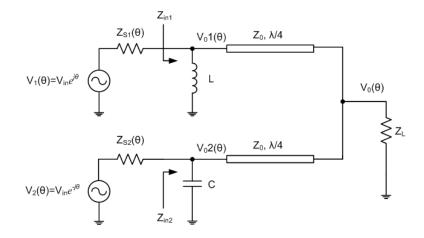

### 2.3.3 Chireix Power Combiner for Efficiency Enhancement

A Chireix power combiner, made of  $\lambda/4$  transmission-line sections with shunt reactances, is a lossless combining structure that offers substantially higher combining efficiencies [22]. In Figure 2.6, the input impedances of the Chireix combiner,  $Z_{in1}$  and  $Z_{in2}$ , can be represented as

$$Re[Z_{in1}] = \frac{2\left(\frac{Z_L}{Z_0^2}\right)cos^2(\theta)}{4\left(\frac{Z_L^2}{Z_0^4}\right)cos^2(\theta) + \frac{1}{\omega^2 L^2} - \frac{\left(4Z_L \cos(\theta)\sin(\theta)\right)}{Z_0^2 \omega L}}$$

(2.9)

$$Im[Z_{in1}] = \frac{\frac{1}{\omega L} - \left(\frac{2Z_L}{Z_0^2}\right) sin(\theta) cos(\theta)}{4\left(\frac{Z_L^2}{Z_0^4}\right) cos^2(\theta) + \frac{1}{\omega^2 L^2} - \frac{\left(4Z_L cos(\theta) sin(\theta)\right)}{Z_0^2 \omega L}}$$

(2.10)

$$Re[Z_{in2}] = \frac{2\left(\frac{Z_L}{Z_0^2}\right)\cos^2(\theta)}{4\left(\frac{Z_L^2}{Z_0^4}\right)\cos^2(\theta) + \omega^2 C^2 - \frac{\left(4Z_L\cos(\theta)\sin(\theta)\right)\omega C}{Z_0^2}}$$

(2.11)

$$Im[Z_{in2}] = \frac{-\omega C - \left(\frac{2Z_L}{Z_0^2}\right) sin(\theta) cos(\theta)}{4\left(\frac{Z_L^2}{Z_0^4}\right) cos^2(\theta) + \omega^2 C^2 - \frac{\left(4Z_L cos(\theta) sin(\theta)\right) \omega C}{Z_0^2}}.$$

(2.12)

Figure 2.6. Chireix power combiner.

The basic idea of the Chireix combiner is to add parallel reactive elements to cancel the reactive parts of the loads,  $Im[Z_{in1}]$  and  $Im[Z_{in2}]$ , at a certain predefined phase offset value, thereby allowing maximum efficiency to also be achieved at a phase difference value other than  $\theta=0$  [23]. However, those reactives are optimized at one outphase angle and not adaptive for all outphase angles. Also, both efficiency and linearity are degraded at other phase angles because each PA does not operate as an ideal voltage source. Therefore, the Chireix combiner requires an adaptive compensation scheme for the variable input impedance of each port to improve linearity over all outphase angles.

# **CHAPTER III**

## **ALL-DIGITAL OUTPHASING TRANSMITTER SYSTEM**

Recent advances in digital processing capabilities and VLSI technology scaling, fueled by Moore's law, have widened the gap between digital and analog circuits in terms of their performance/complexity/cost trade-offs. This trend is projected to become even more significant in the future. The proposed all-digital outphasing transmitter extends the outphasing concept from its analog origins to a digital form based on a baseband DPM, which operates solely via digital signals. Compared to the previous analog approaches, the digital modulation scheme can accommodate many signal types and provide fine phase control for error calibration.

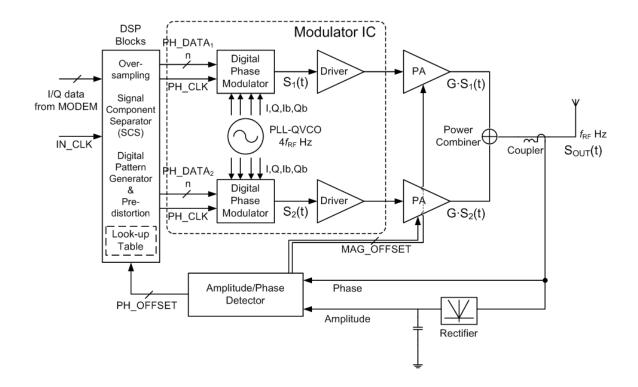

#### 3.1 Main Architecture

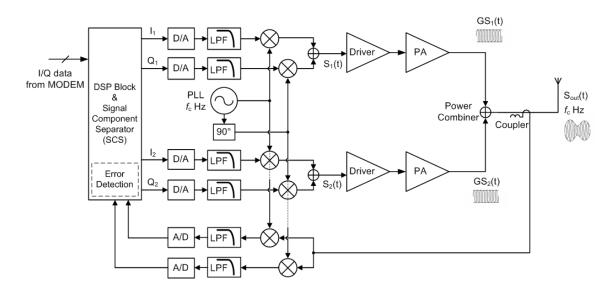

A block diagram of the proposed all-digital outphasing transmitter is shown in Figure 3.1. The transmitter consists of a DSP block, phase locked loop (PLL), two DPMs, two nonlinear switching PAs, an RF power combiner, and an amplitude/phase detection block for mismatch compensation loops. First, the oversampling part of the DSP block oversamples I/Q data from the MODEM with interpolation for image suppression. Since the transmitter operates with digital baseband inputs, the baseband images, which appear at multiples of the sampling rate, can violate the spectral mask if not properly oversampled [24]. The SCS converts the oversampled I/Q data into two phase-only data by (2.5) and (2.6). Then, the digital pattern generator block creates bit streams,  $PH_DATA_1[n]$  and  $PH_DATA_2[n]$ , to control the DPMs according to the phase information from the SCS. The pattern generator can also take calibration values into account for baseband predistortion. The DPMs use the clock signals from the PLL and the digital phase data,  $PH_DATA_i[n]$ , to generate two phase modulated signals,  $S_1(t)$  and  $S_2(t)$ . Both phase modulated signals from the DPMs are then amplified by driver amplifiers (DAs) and nonlinear switching PAs, respectively, and finally combined to create the amplified version of the original signal,  $S_{OUT}(t)$ .

Figure 3.1. Block diagram of proposed all-digital outphasing transmitter.

Additionally, the amplitude/phase detection block measures and calculates path mismatches and distortion caused by both PAs and the combiner. Simple single-tone RF test signals synthesized by the DPM can reveal these artifacts via the detector; thus the amplitude/phase detector is enough for the measurements. This topology is much simpler than using a demodulator and analog-to-digital converters (ADCs) proposed in [25] in the feedback path for error detection.

The most noticeable difference from a conventional outphasing system is that conventional DACs, baseband filters, and I/Q modulators are replaced by DPMs. In general, a conventional I/Q modulator consists of two mixers and an RF sumer. The mixer uses baseband analog inputs, I and Q, from the DAC with reconstruction filters; thus the precise phase control for predistortion requires intricate complex number calculations. However, in the proposed digital outphasing transmitter, as the DPM operates with digital baseband inputs, the complex calculation for the phase calibration is substituted by simple bit additions or subtractions because the calibration values can be stored in look-up tables for each frequency channel. Thus, the predistortion block can be easily implemented by simple DSP blocks integrated with the SCS.

The actual implementation of the DPM, the digital pattern generator, and the detailed operation algorithms for the mismatch detection and calibration are presented as follows.

#### 3.2 System Requirements

20

Some digital modulation schemes, such as quadrature phase shift keying (QPSK) and quadrature amplitude modulation (QAM), have discrete phase values in modulated RF signals. However, modulators that can generate continuous phase values at RF are often required for oversampled baseband symbols or more complex modulation schemes. For example, in OFDM systems, as frequency-domain baseband data have been converted to time-domain data by an inverse fast Fourier transform (IFFT), the phases of baseband symbols can be any values between -180° and +180°. To support such modulation schemes, the phase modulator must produce continuous phase values. Moreover, the outphasing transmitter also requires fine phase tuning for mismatch compensation.

In the digital transmitter, each DPM modulates the clock signal according to a digital phase input, thus it has a finite resolution in phase. Phase quantization may degrade modulation accuracy, as measured by error vector magnitude (EVM) because the finite resolution generates quantization noise at each phase angle of the outphasing amplifier. Therefore, it is necessary to determine the minimum number of bits required for a given modulation scheme, which will ensure compliance with the appropriate specification. The relation between signal to noise ratio (SNR<sub>q</sub>) and the word length of signal quantization has been well discussed in many textbooks and papers [26][27]. The SNR<sub>q</sub> after a  $b_s$ -bit quantization is given by

$$SNR_q = 6.02 \cdot b_s + 1.76 - 20 \cdot \log_{10} k \,[\text{dB}],$$

(3.1)

where  $b_s$  denotes the number of bits and k denotes the peak factor, the ratio of the peak amplitude to the mean amplitude of the signal.

Every additional bit in signal quantization increases  $SNR_q$  by 6.02 dB and its absolute value depends on the PAPR of the original signal. To avoid signal quality degradation due to quantization, the  $SNR_q$  should be larger than the SNR of the original signal. Therefore, the number of bits of a DPM,  $b_{DPM}$ , should be

$$b_{DPM} \ge \frac{SNR - 1.76 + PAPR}{6.02},$$

(3.2)

where both SNR and PAPR are from the original signal in dB before the phase quantization.

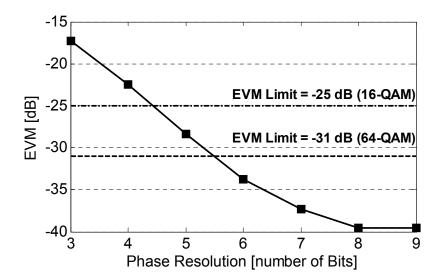

To evaluate the quantization effects on OFDM signals, the EVM values of IEEE 802.16e signals were tested with different phase resolution [1]. Figure 3.2 shows the simulation results.

Figure 3.2. Effects of number of bits in DPM on IEEE 802.16e modulation.

The original signal has the SNR of 40 dB before phase quantization. From the graph, it is seen that the EVM decreases by 6 dB with an each additional bit until it reaches the original EVM value. Therefore, the DPM of the system must provide at least 5 and 6-bit phase resolution to meet required EVM limit of 16-QAM and 64-QAM, respectively, and 8-bits to avoid significant SNR degradation.

#### 3.3 Key Building Blocks

#### 3.3.1 Digital Phase Modulator

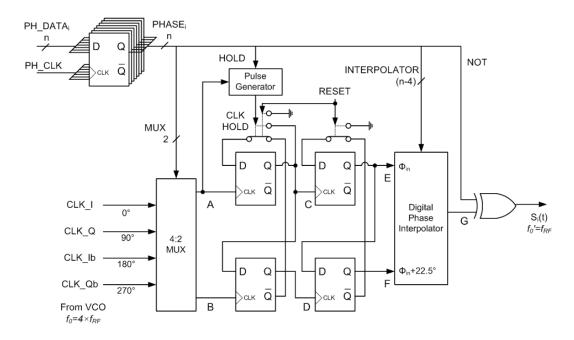

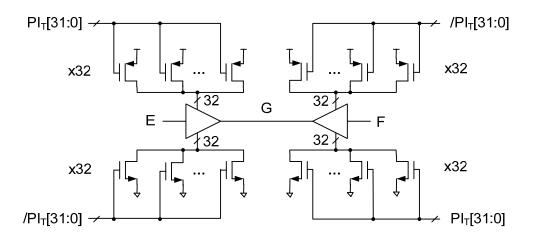

In general, most DPMs have 3 or 4 bits of resolution within a small phase range [28][29]. To implement a DPM with high phase resolution and a wide phase control range  $(-\pi \sim +\pi)$  for the outphasing modulator, a special DPM architecture adopting frequency dividers with quadrature phase clock is preferred, as has been suggested in prior work [30]. A clock frequency four times higher than the RF, provides two phase control bits through the frequency dividers and two additional control bits are obtained by selecting one of the quadrature signals of the clock. Finer phase control can be accomplished by a phase interpolator. An exemplary DPM design is shown in Figure 3.3.

It consists of a quadrature voltage-controlled oscillator (VCO) with four times higher frequency than RF, an input register, a 4:2 multiplexer (MUX), frequency dividers, a fine digital phase interpolator, and a XOR gate. Once loaded into the input register, the phase data,  $PHASE_i[n]$ , controls each building block for phase modulation: 2-bit for the 4:2 MUX, 1-bit for the pulse generator, 1-bit for the XOR gate, and the remaining (n-4)-bit for the digital PI for fine phase control.

Figure 3.3. Block diagram of n-bit digital phase modulator.

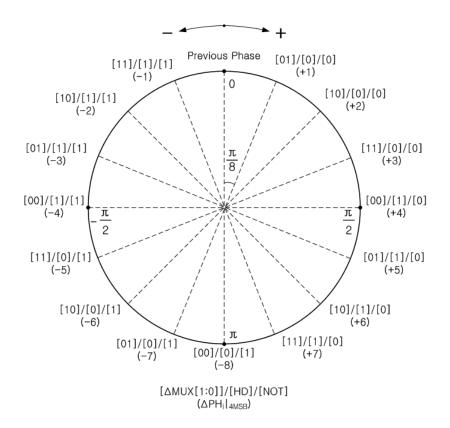

The 4:2 MUX selects one pair of clock signals from four phase I/Q clock signals so that A leads B by  $\pi/2$ , i.e., (A, B)  $\in$  { (CLK\_I, CLK\_Q), (CLK\_Q, CLK\_Ib), (CLK\_Ib, CLK\_Qb), (CLK\_Qb, CLK\_I) }. Since the frequency of the LC quadrature VCO is four times that of the phase modulated signal,  $S_i(t)$ , the 4:2 MUX rotates phase with the step size of  $\pi/8$  from 0 to  $\pi/2$ . The following two D-flipflops (DFFs) divide the clock signals, A and B, by two and delay phase by holding the upper DFF from toggling for one period of the clock signal, if needed. The pulse signal, *HOLD*, is turned on for one period of the clock signal when it is high. The next two DFFs just divide the clock signals, C and D, by two. Thus, the four DFFs divide the clock signals by four and rotate phase by 0 or  $\pi/2$ with the resolution of  $\pi/8$ . The digital PI interpolates between the two clock signals, E and F, with (n-4) bit resolution and outputs the phase modulated signal to the XOR gate. The input signals of the interpolator, E and F, always have a phase difference of  $\pi/8$ . Therefore, the output signal,  $S_i(t)$ , has a phase value between the two signals corresponding to its control input. Lastly, the XOR gate can invert the clock signal, G, which is equivalent to the phase of  $-\pi$ , and output signal is fed into PA driver amplifier. As a result, the *n*-bit DPM modulates phase from  $-\pi$  to  $\pi$  with the minimum step size of  $(2\pi)/2^n$ .

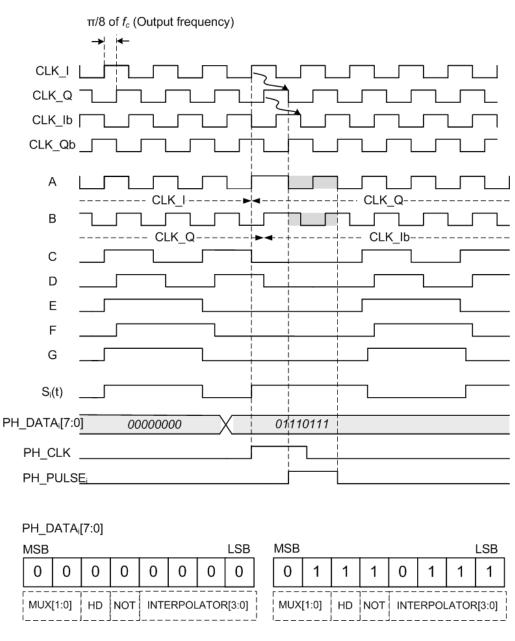

The timing diagram describing the phase shift mechanism with 8-bit resolution is shown in Figure 3.4 as an example. As seen in the figure, each bit should be carefully calculated to generate a desirable phase output. When  $S_i[k]$  is *k*-th baseband symbol including calibration of a certain path, the 8-bit quantized phase of the symbol can be represented as

$$PH_{i}[k] = \left[ \angle \left( \boldsymbol{S}_{i}[k] \right) \times \frac{2^{8} - 1}{2\pi} + 0.5 \right], \text{ where } -\pi < \angle \left( \boldsymbol{S}_{i}[k] \right) \le \pi.$$

(3.3)

The bits, *MUX[1:0]*, *HD (HOLD)* and *NOT*, are from the relative phase difference between a previous symbol and a current symbol. The four most significant bits (4 MSB) of the relative phase difference between the symbols are calculated as

$$\Delta PH_i[k]|_{4MSB} = \left\{ \left( \left\lfloor \frac{PH_i[k]}{2^4} \right\rfloor - \left\lfloor \frac{PH_i[k-1]}{2^4} \right\rfloor + 8 \right) \mod 16 \right\} - 8.$$

(3.4)

Figure 3.4. Timing diagram of 8-bit digital phase modulator.

$\Delta PH_i[k]|_{4MSB}$  is an integer value between -8 and +7 showing the phase shift between (*k*-1)-th and *k*-th symbol with the resolution of  $\pi/8$ . The DPM phase control bits at *k*-th symbol,  $\Delta MUX[1:0]$ , *HD* and *NOT*, can be determined by the  $\Delta PH_i[k]|_{4MSB}$  where  $\Delta$ MUX[1:0] is the incremental difference of MUX[1:0] between a previous and a current symbol. Figure 3.5 shows the relative phase shifting diagram, and each bit value is summarized according to the relative phase differences,  $\Delta PH_i|_{AMSB}$ .

Figure 3.5. Relative phase shift corresponding to input signals.

In addition, the input bits of the phase interpolator, *INTERPOLATOR[3:0]*, at the *k*-th symbol are from the four least significant bits (4 LSB) of the current phase value as shown in (3.5).

$$INTERPOLATOR[3:0] = \left\{ \left( PH_i[k] + 2^7 \right) \mod 16 \right\}$$

(3.5)

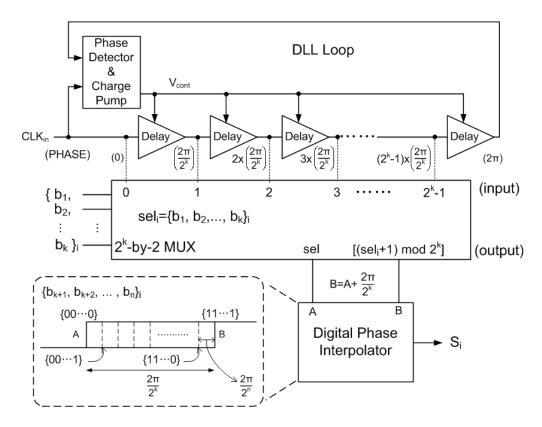

Another possible DPM design is using a simple delay locked loop (DLL) block, as shown in Figure 3.6. The n-bit DPM modulates the phase of incoming clock by two steps, coarse and fine steps. It is composed of a delay locked loop (DLL) with  $2^k$  delay stages and a  $2^k$ -by-2 multiplexer for the coarse phase step ( $k \le n$ ) and a digital phase interpolator (DPI) for the fine step. Up to achievable minimum delay for a given device process, we can obtain  $2^k$  different phases with the resolution of  $(2\pi)/2^k$  from the delay stages of the DLL. The two signal paths,  $S_1$  and  $S_2$ , in outphasing modulation can share the delay stages. Finer phase control is accomplished by the DPI, which generates intermediate phases between the two inputs with a phase difference of  $(2\pi)/2^k$ .

Figure 3.6. DLL-based digital phase modulator.

The phase control bits,  $PH\_DATA_{1,2}[n] = \{b_1, b_2, \dots, b_n\}_{1,2}$ , at time, *t*, are made in the digital pattern generator and used to control the phase of each signal for phase modulation. The  $b_1$  is the most significant bit (MSB), and  $b_n$  is the least significant bit (LSB) on phase control. Then, the bits are given by

$$\left\{b_1, b_2, \dots, b_k\right\}_i = \left\lfloor \frac{PH_i(t)}{2^{n-k}} \right\rfloor \qquad (k \le n)$$

(3.6)

$$\{b_{k+1}, b_{k+2}, \dots, b_n\}_i = (PH_i(t) \mod 2^{n-k}),$$

(3.7)

where

$$PH_i(t) = \left[ \angle \left(S_i(t)\right) \cdot \frac{\left(2^n - 1\right)}{2\pi} + 0.5 \right]$$

(3.8)

and  $0 \leq \angle (S_i(t)) < 2\pi$ .

The simple phase control of the DPM facilitates the phase calibration for various mismatch and error correction algorithms. Moreover, the proposed digital transmitter, implemented without conventional analog mixers and filters, is suitable for a wide variety of modulation schemes and signal bandwidths.

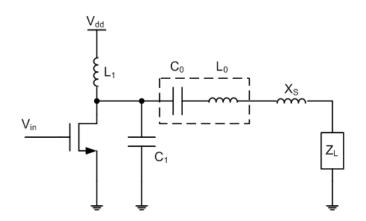

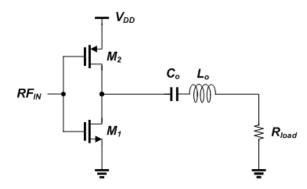

# 3.3.2 Power Amplifier

The load-sensitive properties of the PA can influence the performance of the outphasing transmitter. In [31] and [32], various types of switching PAs, such as Class D,

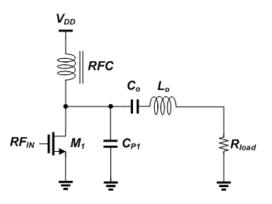

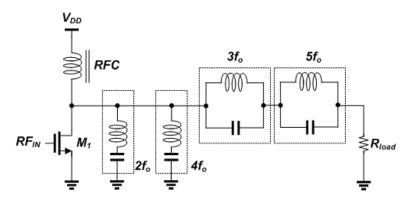

E, F, were evaluated to find the optimum candidates for an outphasing transmitter. In [32], each input impedance of a combiner varies due to the non-isolation effects of a combiner, and can be represented by a function of the outphase angle,  $\theta$ . Likewise, PAs were substituted by ideal voltage or current sources with output impedance,  $Z_{\theta}$ . The results showed that voltage-mode Class D (VMCD) and Class F PAs are good choices for an outphasing transmitter because they have an output current – a voltage relationship that is similar to the ideal voltage source, but the sensitive characteristics in load impedance of Class E PA render it a poor candidate for an outphasing transmitter [33]. To demonstrate this sensitivity of a Class E PA, the basic topology of the PA is shown in Figure 3.7 [34]. The circuits include a transistor, shunt capacitor  $C_I$ , RF chock  $L_I$ , and series tuned output circuit  $L_{\theta}$ ,  $C_{\theta}$ . Ideally, the tuned output circuit does not impact the output impedance of the PA, but there exists a residual series reactance due to the circuit because the series resonant circuit is usually not perfectly tuned at the operating frequency. This feature makes the Class E PA highly reactive and load impedance-sensitive.

Figure 3.7. Basic topology of Class E amplifier.

However, every PA operates as a non-ideal voltage or current source, and therefore they are all influenced by load impedance to some degree. Thus, precise compensation for the time-varying load impedance is required to optimize the performance of the outphasing transmitter. Proper calibration can even improve the linearity of the outphasing transmitter using a Class E PA. The output impedance of each PA,  $Z_0(\theta)$ , consists of both amplitude and phase elements. Therefore, the phase error in the impedance can be cancelled by shifting the phase of an input signal in the opposite direction, and the amplitude error can be compensated by adjusting the supply voltage of the PA.

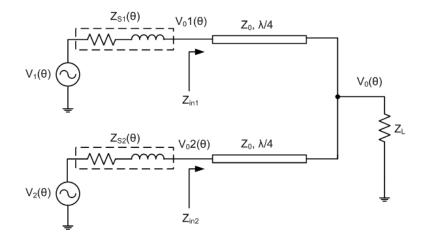

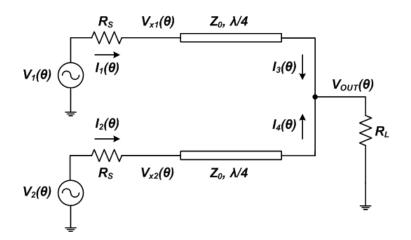

#### 3.3.3 Power Combiner

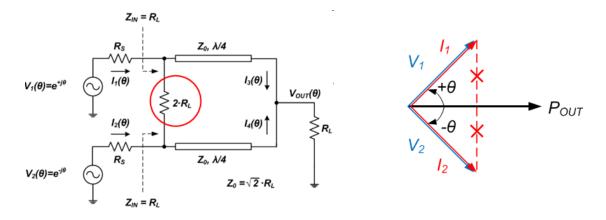

In the outphasing technique, there are two kinds of power combiners: isolated and non-isolated combiners. The isolated combiner, such as a Wilkinson combiner, has all matched input and output ports independent of the amplitude and phase of input signals. This feature has the advantage of low distortion, but most of the energy can be dissipated in the combiner when the outphase angle,  $\theta$ , is close to 180°, which corresponds to significant efficiency degradation. On the contrary, in a non-isolated combiner, the equivalent input impedance of each input port varies depending on the amplitude and phase of the input. A Chireix combiner is one of the non-isolated combiners using the load modulation technique [33]. A Chireix combiner is a lossless combining structure that provides much higher combining efficiency than that of the isolated combiner at the cost of linearity due to non-isolation characteristics. In a general Chireix combiner, two reactive shunt elements are inserted to mitigate the reactive input impedances of the combiner, thus improving overall efficiency [23], but those susceptances are optimized at one outphase angle and are not adaptive for all outphase angles. Thus, both efficiency and linearity are degraded at other phase angles. Therefore, adaptive compensation of the input impedance of each input can improve both combining efficiency and linearity over all outphase angles. To track the input impedances of a combiner with respect to all outphase angles, the detailed power combiner architecture needs to be analyzed. Figure 3.8 shows a general non-isolated combiner topology.  $Z_{SI}(\theta)$  and  $Z_{S2}(\theta)$  are the output impedances of PA, and  $Z_{inI}(\theta)$  and  $Z_{in2}(\theta)$  are input impedances of the combiner at port 1 and port 2, respectively. Each impedance value is represented by a function of the outphase angle,  $\theta$ , to take non-isolation effects into account.

Figure 3.8. Architecture of general non-isolated combiner.

From (2.5) and (2.6), the input voltages of the power combiner,  $V_1(\theta)$  and  $V_2(\theta)$ , are defined as follows.

$$V_1(\theta) = 0.5r_{\max}e^{j\theta}$$

(3.9)

$$V_2(\theta) = 0.5r_{\max}e^{-j\theta}$$

(3.10)

The original signal angle,  $\varphi(t)$ , and dependence of  $\theta$  on time are suppressed since it does not affect the mismatch analysis [20]. If one assumes that the output impedances of two PAs remain constant as  $Z_s$  overall the outphase angle such as an ideal voltage source, then the reflection coefficient,  $\Gamma(\theta)$ , between the PA output and the combiner input will be

$$\Gamma(\pm\theta) = \frac{Z_{in}(\pm\theta) - Z_s}{Z_{in}(\pm\theta) + Z_s}$$

(3.11)

where

$$Z_{in}(\pm\theta) = \frac{1}{\frac{Z_L}{Z_0^2} \left[ 2\cos^2\theta \mp j\sin(2\theta) \right]}$$

(3.12)

$\Gamma(\theta)$  takes into account the lack of isolation between both branches, as each branch is seen as a dynamic load to the other. With equation (3.9) and (3.10), the following output voltage expression is obtained as derived in [35].

$$V_0 1(\theta) = G V_1(\theta) [1 + \Gamma] = |V_0 1| e^{j\theta'}$$

(3.13)

$$V_{0}2(\theta) = GV_{2}(-\theta)[1+\Gamma] = |V_{0}2|e^{-j\theta}$$

(3.14)

$$V_0(\theta) = 2G\left(\frac{Z_L}{Z_0}\right)\left(\frac{r_{\text{max}}}{2}\right)\left|1 + \Gamma(\theta')\right|\cos(\theta')$$

(3.15)

where  $\theta = \theta' - \angle (1 + \Gamma(\theta'))$  and *G* is the gain of each PA.

It is seen that despite the non-isolation effects in a combiner, only the output signal amplitude is distorted if the PA output impedance remains constant. However, because the PA does not behave as an ideal voltage source, there exists one more circuit parameter that causes distortions in the combiner. The output impedances of PAs,  $Z_{in1}(\theta)$  and  $Z_{in2}(\theta)$ , are also a function of the outphase angle, and they are not identical, which means that the phase of the output signal can also be distorted. The only way to estimate the effects on the output signal is to measure it in actual circuits. In [33], a load-pull analysis method was proposed to measure output signal phase distortion on a Class E PA, but this method is not adequate for commercial products. Thus, the method of applying test vectors and measuring their responses was adopted for calibration in this preliminary research. Fortunately, because the DPM in the proposed transmitter has a finite number of test vectors, calibration is much easier than with the methods using conventional predistortion for both measurement and compensation.

# 3.4 Digital Mismatch Compensation Algorithms

As long as the two signal paths of the transmitter are perfectly symmetrical and isolated, the output of the outphasing amplifier is linear, as shown in (2.7). However,

process, voltage and temperature (PVT) variations in real circuits can generate path mismatches, and thereby degrade signal path linearity. Figure 3.9 shows a general power combiner topology of the outphasing transmitter. In the previous mismatch analysis methods in [36]-[39], the gain of each PA is always regarded as a constant. Thus, they could not compensate for imperfect isolation in the combiner. Here, the gain of each path is represented as a function of outphase angle,  $\theta(t)$ , as shown in (2.5) and (2.6) to include the effects of imperfect combiner isolation. The distortion due to the combiner is determined by the relative angle differences between the two input vectors. Thus, the original signal angle,  $\varphi(t)$ , and dependence of  $S_1$ ,  $S_2$ ,  $S_{OUT}$  and  $\theta$  on time are suppressed since it does not affect the mismatch analysis.

Figure 3.9. Errors of outphasing amplification.

The most significant advantage of the proposed DPM-based transmitter is that the calibration is much easier and simpler than the methods using the conventional calculation-based predistortion presented in [20] and [39]. Any mismatches caused by circuits can be detected and stored in digital look-up tables for each frequency channel

because the DPM has a finite number of vectors to represent all available output amplitudes.

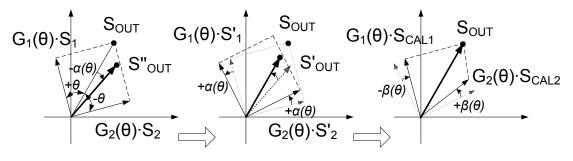

## 3.4.1 Foreground Mismatch Compensation Algorithms

Foreground mismatch compensation algorithm detects and calibrates any gain and phase mismatches between the two branches and the distortion due to the combiner during initialization. For the calibration, the two DPMs generate and inject various test vectors into PAs, and then the combiner output is measured when power is turned on. The calibration results will be stored in digital look-up tables as a function of outphase angle,  $\theta$ . The algorithm consists of static mismatch compensation and dynamic mismatch compensation.

## A. Static Mismatch Compensation

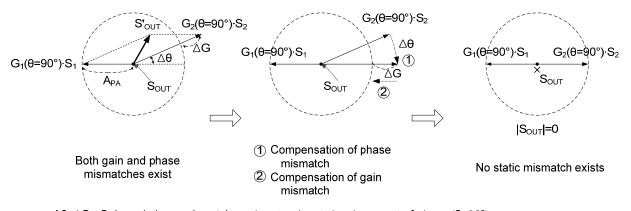

The static mismatch compensation method is used to compensate for unbalanced PAs and any path or load mismatches between the two signal paths when they are out-ofphase or  $\theta$ =90°. Figure 3.10 demonstrates the steps in the gain/phase mismatch compensation algorithm. Gain/phase mismatches are detected by simply letting two test vectors,  $S_1$  and  $S_2$ , have equal amplitude and opposite phases, and then monitoring the amplitudes of  $S_{OUT}$ . As shown in the figure, if gain/phase mismatches exist,  $S'_{OUT}$  is not zero and has an amplitude as shown in (3.16).

$\Delta\theta$ ,  $\Delta G$ : Gain and phase mismatches when two input signals are out-of-phase ( $\theta$ =90°) S'<sub>OUT</sub>: Output signal with gain and phase mismatches S<sub>OUT</sub>: Ideal output signal

Figure 3.10. Sequence of steps for static mismatch compensation.

$$|S'_{OUT}| = \left\{ \left[ \left( A_{PA} + \Delta G \right) \cdot \cos\left( \Delta \theta \right) - A_{PA} \right]^2 + \left[ \left( A_{PA} + \Delta G \right) \cdot \sin\left( \Delta \theta \right) \right]^2 \right\}^{\frac{1}{2}} = \sqrt{\Delta G^2 + 2 \cdot A_{PA} \cdot \left( A_{PA} + \Delta G \right) \cdot \left[ 1 - \cos\left( \Delta \theta \right) \right]}$$

$$(3.16)$$

where

$$\Delta \theta = \angle \left( G_1 \left( \theta = 90^\circ \right) \cdot S_1 \right) + \angle \left( G_2 \left( \theta = -90^\circ \right) \cdot S_2 \right), \tag{3.17}$$

$$\Delta G = \left| \left| G_1 \left( \theta = 90^\circ \right) \cdot S_1 \right| - \left| G_2 \left( \theta = -90^\circ \right) \cdot S_2 \right| \right|$$

(3.18)

and  $A_{PA}$  is the output amplitude of the PA<sub>1</sub>.

The gain mismatch is corrected after first compensating for phase difference in the two branches.

Phase mismatch,  $\Delta \theta$ , is first compensated by initializing the amplitude offset to be zero and by selecting the phase offset that minimizes  $|S'_{OUT}|$  or  $\Delta G$ . Amplitude mismatch,

$\Delta G$ , is then compensated by setting *PH\_OFFSET* to the selected value and by finding the *MAG\_OFFSET* that makes  $|S_{OUT}|$  as small as possible. The selected offset values, *PH\_OFFSET* and *MAG\_OFFSET*, are provided to the SCS and nonlinear PAs, respectively, for gain/phase adjustment, as shown in Figure 3.1. *PH\_OFFSET* is added or subtracted from DPM control bits at the digital pattern generator for constant phase mismatch cancellation and *MAG\_OFFSET* is used to control the bias of each nonlinear PA to produce the same gain in each branch.

## **B.** Dynamic Mismatch Compensation

Dynamic mismatch compensation method is used for the compensation of combining errors and losses in the outphasing transmitter. To compensate for those errors and losses, the two test vectors that have the opposite outphase angles,  $\pm \theta$  ( $0 \le \theta < 90^{\circ}$ ), are used, as shown in Figure 3.11(a). If there are no path mismatches and no combiner errors, the net combiner output impedance is purely real with an amplitude corresponding to the outphase angles,  $\pm \theta$ , due to their symmetries on the real axis. However, the combining errors can cause imperfect phase cancellation in the combiner, which generates phase and amplitude errors in the combiner output. Figure 3.11(a) shows the exemplary combiner response to the conjugate phase test signals. Suppose that at some outphase angle,  $\theta$ , the output vector is no longer on the horizontal axis but rather its angle is negative. Then, both input signals should be calibrated in the same direction,  $+\alpha(\theta)$ , to cancel the phase offset of the output. This is called common phase compensation.

Simultaneously, the amplitude of the combined output signal is also diminished due to the losses in passive components. This is also shown in Figure 3.11(a). To remove

the effects of losses, both input signals should be calibrated in the opposite direction,  $\pm\beta(\theta)$ , to reduce the angle between the two vectors corresponding to the outphase angle,  $\theta$ . This is called differential phase compensation.

Dynamic mismatch compensation consists of: first, common phase compensation; then, differential phase compensation. These steps are summarized in Figure 3.11(a).

Again, the original baseband symbol angle,  $\varphi$ , in (2.3) does not affect the compensation of mismatch, since the phase and amplitude distortion is only a function of the outphase angle,  $\theta$  ( $0 \le \theta < 90^{\circ}$ ). The total number of test vectors for the dynamic mismatch compensation is  $2^{n}/4=2^{(n-2)}$ , which is the number of possible phases in the first quadrant of an n-bit DPM in Figure 3.11(a). Also, the static mismatch compensation can be performed before the dynamic mismatch compensation is performed because the static compensation only measures a minimum output amplitude, which is independent of the dynamic compensation. Both compensation angles,  $\alpha(\theta)$  and  $\beta(\theta)$ , can be saved in digital look-up tables for each channel and calibrate the input bit streams of DPMs with simple digital addition or subtraction operations.

Finally, after the completion of the look-up tables, the calibrated baseband symbols,  $S_{CAL1}$  and  $S_{CAL2}$  shown in Figure 3.11(b), including the static and dynamic mismatch compensation can be represented as

$$S_{CAL1} = S_1 \cdot e^{j\left[\alpha(\theta) - \beta(\theta)\right]}$$

(3.19)

$$S_{CAL2} = S_2 \cdot e^{j\left[\alpha(\theta) + \beta(\theta) - \Delta\theta\right]}.$$

(3.20)

Output with test vector 1. Common phase compensation 2. Differential phase compensation  $+\alpha(\theta) \qquad \pm\beta(\theta)$

$S_{1t},\,S_{2t}\,\,$  : Test signals for dynamic mismatch compensation

$S_{\text{OUTt}}$  : Ideal output signal from test signals

S<sub>OUTt</sub><sup>e</sup> : Distorted output signal due to gain and phase errors at combiner

$+\alpha(\theta)$  : Common phase compensation as a function of out-phase angle,  $\theta$   $\pm\beta(\theta)$  : Differential phase compensation

(a)

Original input vector 1. Common phase compensation 2. Differential phase compensation  $+\alpha(\theta) \pm \beta(\theta)$

| S" <sub>OUT</sub> | : Output signal with gain and phase errors at combiner |

|-------------------|--------------------------------------------------------|

| S' <sub>OUT</sub> | : Output signal after phase error calibration          |

| $S_{\text{OUT}}$  | : Output signal after gain and phase calibration       |

|                   | (b)                                                    |

Figure 3.11. Sequence of steps for dynamic mismatch compensation. (a) Dynamic error measurement with test vectors, (b) Dynamic mismatch compensation with look-up tables.

## 3.4.2 Background Mismatch Compensation Algorithms

The foreground mismatch compensation is the initial characterization of the outphasing system before communication. Thus, it requires a series of test vectors and an empty time slot. However, the mismatches and variations change over time. Also, the calibration and data transmission cannot operate simultaneously. Therefore, the only way to calibrate the time-varying effects is to measure the errors from data signals and compensate them continuously.

In the foreground compensation, the digital look-up tables summarize the calibration values as a function of the outphase angle,  $\theta$ . As each data symbol has an outphase angle value as in (2.5) and (2.6), it is possible to update the calibration information by monitoring and comparing the relationship between the outphase angle of the data and its combiner output signal at the amplitude/phase detector with the same manners of the foreground compensation. Thus, the background mismatch compensation is also available during data transmission.

## 3.4.3 Simulation Results

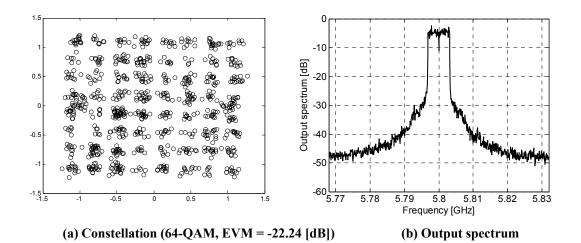

To validate the proposed compensation algorithms above, two sets of simulation setups have been designed using the ADS simulator [40] with various WiMax modulation schemes. The first setup was developed to measure the mismatch effects caused by both PAs and a combiner to test vectors, and the second setup is an entire 5.8 GHz WiMax transmitter testbed system to demonstrate the performance of the compensation algorithms. The testbed consists of a digital baseband generation part with 8-bit DPMs, an error calibration block, an outphasing amplifier block, and a measurement block. The outphasing amplifier is composed of two Class E PAs and a non-isolation combiner using circuit co-simulation environments. The measurement block is used for calculating an EVM, system efficiency, and output signal spectrum. In the setup, Class E PAs with a non-isolation combiner are selected to maximize the effects of the non-isolation distortions.

For the Class E PA, a 0.18- $\mu$ m standard CMOS process library is used for circuit design. The PA consists of a driver stage and a power stage, and its tuned output circuits are designed to operate at 5.8 GHz for WiMax applications. The maximum available output power of the PA is 22 dBm with an efficiency of 73%. The architecture of the non-isolation combiner is the same as that of a general Chireix without shunt elements, and the characteristic impedance of the quarter-wave transformer is 40  $\Omega$  to transform the output impedance of the PA, 16  $\Omega$ , to 100  $\Omega$ . In practice, it may be difficult to design a DPM that operates at 5.8 GHz because its internal frequency must be four times higher than the carrier frequency. In this simulation setup, the operating frequency of 5.8 GHz is chosen to verify the calibration performance in the WiMax-OFDM modulation scheme. Also, the proposed transmitter architecture is applicable to other wireless standards, which use different frequency bands.

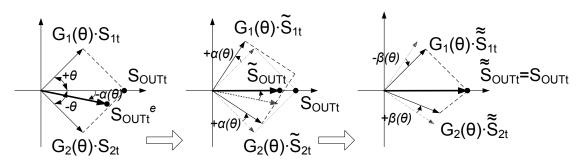

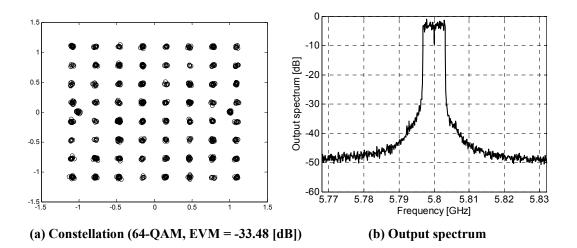

Figure 3.12 shows the EVM and the output signal spectrum for an 8-bit all-digital outphasing transmitter without error compensation. The gain and phase mismatches were 5% and  $6^{\circ}$ , respectively. As expected, the output signals cannot meet the EVM requirements of the transmitter due to the distortions from PAs and a combiner.

Figure 3.12. EVM and spectrum of output signal before mismatch calibration.

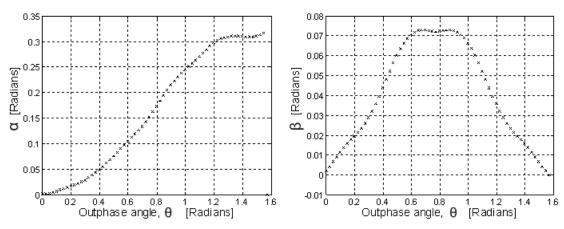

To reduce the distortion through calibration, the static and dynamic compensation values are generated with the responses of the test vector, as demonstrated in Figure 3.10 and Figure 3.11. The gain/phase mismatches between the two PAs are detected through the static mismatch measurement. In addition, the test vectors for the dynamic mismatch compensation create 64-by-2 calibration look-up tables for the 8-bit DPMs. Each row has two compensation parameters,  $\alpha$  and  $\beta$ , and they are recorded according to the outphase angle,  $\theta$ , with a resolution of  $\pi/2^7$  from 0 to $\pi/2$ . The calibration tables are summarized in Figure 3.13.

Finally, Figure 3.14 shows the EVM and the signal spectrum of the output signal after calibration. The EVM value and the shape of the output spectrum are similar to the results from the quantization effects in Figure 3.2, as the compensation mechanisms can improve the performance up to the resolution of DPMs.

1. Static mismatch compensation

$$\Delta \theta_1 = 0, \Delta r_1 = 1$$

$\Delta \theta_2 = 6^\circ, \Delta r_2 = 0.95$

2. Dynamic mismatch compensation

Figure 3.13. Summary of look-up tables.

Figure 3.14. EVM and spectrum of output signal after mismatch calibration.

In this chapter, a new all-digital outphasing transmitter architecture was presented. As the DPM modulates each outphase angle directly in the digital domain, any phase mismatch caused by PAs or an RF combiner can be easily compensated within the resolution of the DPM. For complete error compensation, two distinct mismatch compensation algorithms are used. One is static mismatch compensation for unbalanced paths, and the other one is for dynamic mismatch compensation. The dynamic error compensation is composed of common and differential phase calibration for error caused by the non-ideal behavior of both PAs and an RF combiner. The compensation can also be easily accomplished by using digital look-up tables. The simulation results show that the methods can improve the linearity.

# **CHAPTER IV**

# ALL-DIGITAL OUTPHASING MODULATOR IC IMPLEMENTATION

# 4.1. IC Implementation

The architecture of the proposed all-digital outphasing transmitter was discussed in the previous chapter with system requirements and digital mismatch compensation algorithms. To verify the functionality of the all-digital outphasing transmitter technique and the mismatch compensation algorithms in real circuit implementation, a test chip of the digital modulator is designed and fabricated.

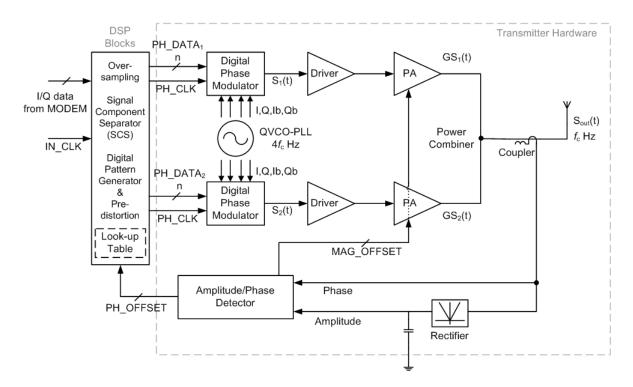

Figure 4.1 shows a block diagram of an all-digital outphasing transmitter. The chip consists of an on-chip PLL with a quadrature LC VCO, an I<sup>2</sup>C block, two DPMs, and two driver amplifiers. The frequency range of the VCO is from 2.6 to 3.0 GHz, and it is controlled by 4-bit capacitor banks. Thus, the corresponding output frequency of DPM is from 650 to 750 MHz. The I<sup>2</sup>C block sets various digital registers, such as the division number of PLL, capacitor tanks for the VCO, debugging ports, and so on. The target application of the modulator IC is a UHF band white space cognitive radio system, which is an emerging wireless communication standard based on the concept of opportunistic spectrum sharing [41].

Figure 4.1. Block diagram of all-digital outphasing transmitter.

# 4.2. Building Blocks

## 4.2.1. Digital Phase Modulator

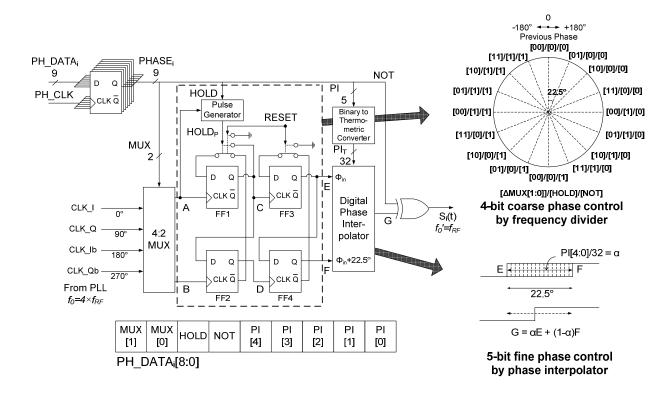

A clock frequency four times higher than the RF, provides two phase control bits for the two frequency dividers and two additional control bits are obtained by selecting one of the two quadrature signals of the clock. Finer phase control can be accomplished by a digital phase interpolator (PI).

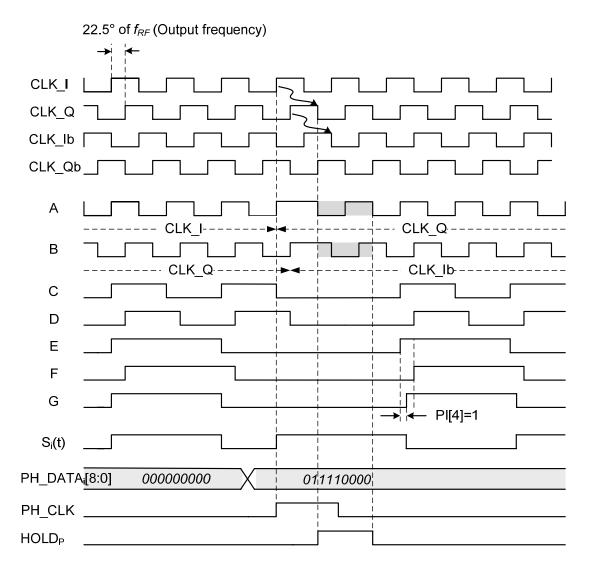

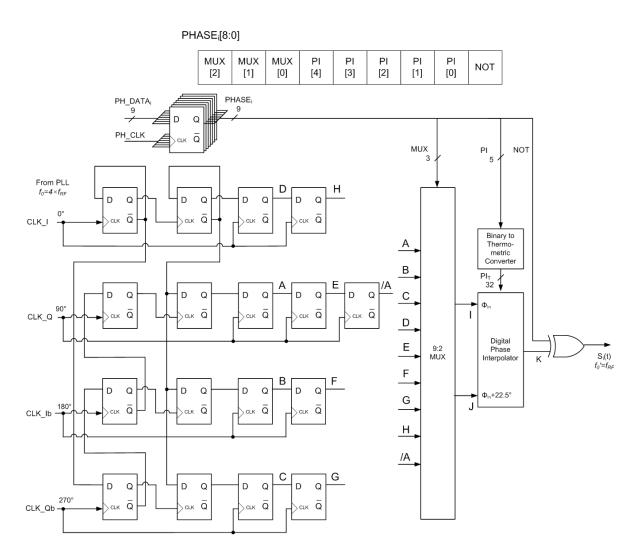

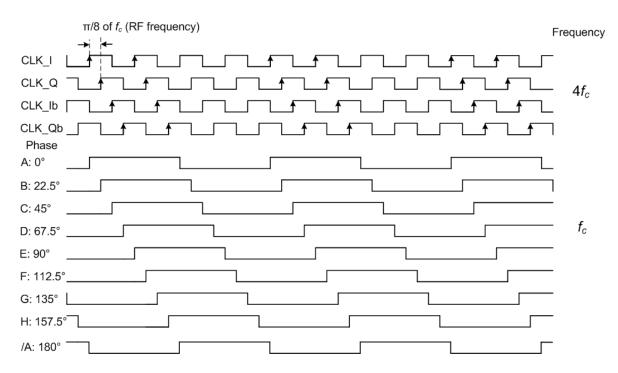

Figure 4.2 shows a block diagram of the proposed DPM. The 9-bit phase data,  $PH\_DATA_i[8:0]$ , control each building block for phase modulation: 2-bit for the 4:2 multiplexer (MUX), 1-bit for the 90°-pulse generator HOLD line, 1-bit for the XOR gate, and the remaining 5-bit for the digital PI.

Figure 4.2. Block diagram of proposed 9-bit digital phase modulator.

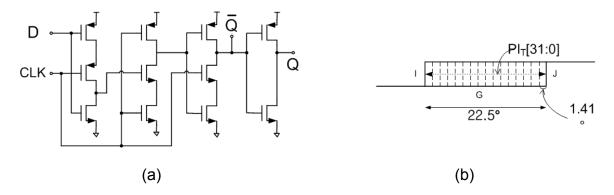

The 4:2 MUX selects one pair of clock signals among four phase I/Q clock signals so that A leads B by 90°, i.e., (A, B)  $\in$  { (CLK\_I, CLK\_Q), (CLK\_Q, CLK\_Ib), (CLK\_Db, CLK\_Qb, CLK\_I) }. Since the frequency of the quadrature VCO is four times that of the phase modulated signal,  $S_i(t)$ , the 4:2 MUX rotates phase with a step size of 22.5° from 0 to 90°. The following two D-flipflops (DFFs), FF1 and FF2, divide the clock signals, A and B, by two and delay the phase of 90° by holding the FF1 from toggling for one period of the clock signal when HOLD is high. The next two DFFs, FF3 and FF4, just divide the clock signals, C and D, by two. Thus, the four DFFs divide the clock signals by four and rotate the phase from 0 to 180° with a resolution of 22.5°. Then, the digital PI interpolates between the two clock signals, E and F, with 5-bit resolution. The digital PI, shown in Figure 4.3, consists of 32 unit gain cells in both paths

and the weighting of each path is controlled by the digital inputs of the PI, PI[4:0], through a binary to thermometric converter. The XOR gate inverts the output of the digital PI, G, if NOT is high, which is equivalent to the additional phase of 180°. As a result, the DPM modulates phase from -180° to 180° a the step size of  $360^{\circ}/(2^{9})$  or  $0.703^{\circ}$ .

Figure 4.3. Circuit implementation of 5-bit digital phase interpolator.

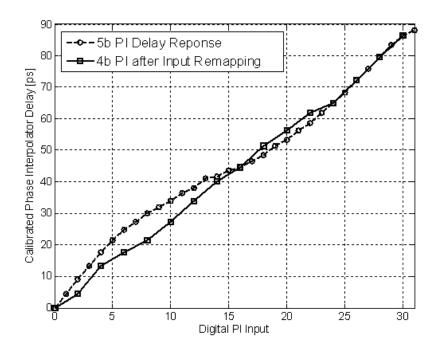

The 5-bit PI may not have linear responses with respect to its input bits due to its open-loop structure. Figure 4.4 shows the delay measurement of the 5-bit PI. To get a better linearity, the input of the PI is calibrated by 4-bit input remapping and the PI has a 4-bit effective resolution after the remapping. As the 5-bit PI is designed to have an effective 4-bit resolution, the DPM has an 8-bit resolution and modulates the phase from  $-\pi$  to  $\pi$  with the minimum step size of  $\pi/2^8$  or 1.41°.

Figure 4.4. Measurement results and calibration of digital phase interpolator.

An exemplary timing diagram of the 9-bit DPM is shown in Figure 4.5.

Figure 4.5. Timing diagram of 9-bit digital phase modulator.

The simple DPM phase control facilitates phase calibration for various mismatch and error correction algorithms. Moreover, the proposed digital transmitter, implemented without conventional analog mixers and filters, is suitable for a wide variety of modulation schemes and signal bandwidths.

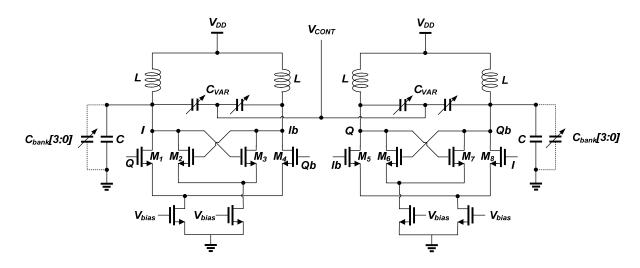

# 4.2.2. Voltage-Controlled Oscillator

Figure 4.6 shows the schematic of the quadrature VCO used in the modulator. The on-chip 2.2~2.8 GHz LC quadrature VCO generates differential I/Q clock signals for the proposed DPM. The LC-type VCO is used for low phase noise at clock outputs. By using large coupling transistors between two LC oscillators, the phase error between I/Q clock signals is kept low to not degrade the phase resolution of the DPM even if mismatch exists. The frequency band of the VCO is selected by a 4-bit control word,  $C_{bank}/3:0/$ , for both low VCO gain and wide frequency range.

Figure 4.6. Schematic of on-chip quadrature VCO.

## 4.2.3. Frequency Synthesizer

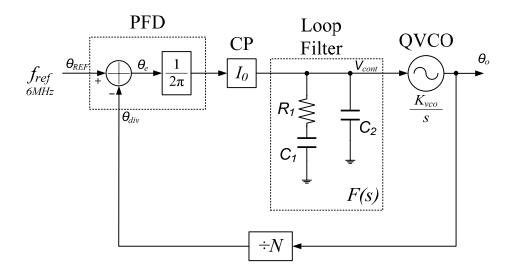

The integrated PLL is a basic type-II,  $3^{rd}$  order integer-N PLL, as shown in Figure 4.7. It consists of a phase frequency detector (PFD), a charge pump (CP), a  $2^{nd}$  order loop filter, a quadrature LC VCO, and a dual modulus frequency divider. The frequency of the reference signal,  $f_{ref}$ , is 6 MHz and VCO frequency ranges from 2.2 to 2.8 GHz. The  $2^{nd}$  order loop filter consists of series  $R_1$  and  $C_1$  in parallel with  $C_2$ .  $C_2$  is added to suppress

the ripples in the  $V_{cont}$  signal and is only about one-tenth of C<sub>1</sub> to not change the frequency response of the filter [42].

Figure 4.7. Block diagram of integrated frequency synthesizer.

The transfer function of the loop filter in the PLL is