### POST-CMOS MEMORY TECHNOLOGIES AND THEIR APPLICATIONS IN EMERGING COMPUTING MODELS

A Dissertation Presented to The Academic Faculty

By

Insik Yoon

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology

August 2019

Copyright © Insik Yoon 2019

### POST-CMOS MEMORY TECHNOLOGIES AND THEIR APPLICATIONS IN EMERGING COMPUTING MODELS

Approved by:

Dr. Arijit Raychowdhury, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Asif Islam Khan School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Shimeng Yu School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Suman Datta Department of Electrical Engineering University of Notre Dame

Dr. Titash Rakshit Advanced Logic Lab Samsung Semiconductor

Date Approved: May 20, 2019

### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my research advisor Dr. Arijit Raychowdhury for his support and guidance throughout my doctoral research. Without his encouragement, I would not be able to overcome the difficulties that I faced in the course of research.

I would also like to thank my committee members – Dr. Madhavan Swaminathan, Dr. Asif Khan, Dr. Shimeng Yu, Dr. Suman Datta, Dr. Titash Rakshit and Dr. Suman Datta for providing me guidance and insight to my research.

I would like to thank my research group members, Dr. Samantak Gangophadyay, Dr. Saad Bin Nasir, Dr. Anvesh Amaravati, Abhinav Parihar, Ningyuan Cao, Muya Chang, Aqeel Anwar, Bitan Bhar, Brian Crafton, Anupam Golder, Foroozan Karimzade and Rakshith Saligram, Dr. Kaushik Bhattacharyya, Dr. Yan Fang and Dr, Jong-Hyeok Yoon. Your help, support, input and friendship was a crucial part of my experience as a graduate student.

I would like to thank my family and friends. I am extremely grateful to my parents for their support. Lastly, I would like to thank my wife, Dr. Hyo-Jin Nam for unlimited support and patience.

### SUMMARY

The objective of this proposed research is to take a holistic approach to the post-CMOS in/near-memory processing system design for machine learning and optimizations. We first address the current issues of Spin-Transfer Torque Magnetic Random Access Memory(STT-MRAM) and multi-bit ferroelectric FET in the device level. At the circuit level, the research shows how these issues shape the peripheral circuit of STT-MRAM and ferroelectric FET memory arrays. Lastly, at the system level, the research leads to the efficient memory architecture and system design that maximizes the benefits of STT-MRAM and ferroelectric FET while mitigating the current limitations of these devices. In the proposed research, we apply the in/near memory processing system design with STT-MRAM and ferroelectric FETs to various applications such as reinforcement learning with a drone, image classification with Deep Neural Network and least square minimization for image reconstruction. For the remaining part of this research, we will focus on near-memory processing system with STT-MRAM for reinforcement learning of a drone and evaluate the system to quantify how much benefits are expected in terms of latency, power and energy. From this project, we would like to show that near-memory processing system with nonvolatile devices is a key enabler for real-time learning systems with stringent power and energy constraints.

# TABLE OF CONTENTS

| List of ' | Tables   | ix                                                                  |

|-----------|----------|---------------------------------------------------------------------|

| List of ] | Figures  | х                                                                   |

| Chapte    | r 1: Int | roduction                                                           |

| 1.1       | Motiva   | ation                                                               |

| 1.2       | Prior w  | vorks                                                               |

|           | 1.2.1    | Post CMOS memory: Spin Transfer Torque Magnetic RAM (STT-<br>MRAM)2 |

|           | 1.2.2    | Post CMOS memory: Ferroelectric FET                                 |

|           | 1.2.3    | Challenges with STT-MRAM and FerroFET based system 7                |

| 1.3       | Key co   | ontributions of the research                                        |

| 1.4       | Disser   | tation overview                                                     |

| Chapte    | r 2: Ma  | gnetic Coupling Across Bit-Cells of STT-MRAM 14                     |

| 2.1       | Model    | ing of STT-MRAM and external magnetic field                         |

|           | 2.1.1    | MTJ physical dimension modeling                                     |

|           | 2.1.2    | Modeling the H field                                                |

| 2.2       | Role o   | f Magnetic coupling in dense arrays                                 |

|           | 2.2.1    | Impact of Magnetic Coupling on Write and Retention                  |

| 2.3    | Effect of Magnetic Coupling on Static Characteristics of the Victim Cell                  | 24 |

|--------|-------------------------------------------------------------------------------------------|----|

|        | 2.3.1 Effect of Magnetic Coupling on Thermal stability                                    | 26 |

|        | 2.3.2 Effect of Magnetic Coupling on Retention Time                                       | 33 |

| 2.4    | Magnetic coupling effect on thermal stability with synthetic anti-ferromagnet fixed layer | 34 |

| 2.5    | Summary                                                                                   | 36 |

| Chapte | r 3: Retention test Challenges of STT-MRAM Arrays                                         | 37 |

| 3.1    | Test and Characterization of cell Retention                                               | 37 |

|        | 3.1.1 Challenges in Retention and Thermal Stability Tests                                 | 38 |

|        | 3.1.2 Test patterns for retention test: Role of Magnetic Coupling                         | 40 |

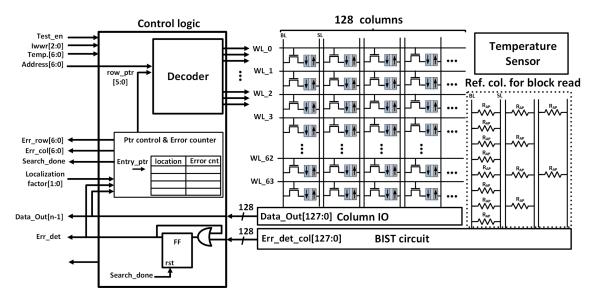

| 3.2    | Proposed MBIST for Retention Testing                                                      | 41 |

|        | 3.2.1 EMACS System Architecture for Statistical Retention Tests                           | 42 |

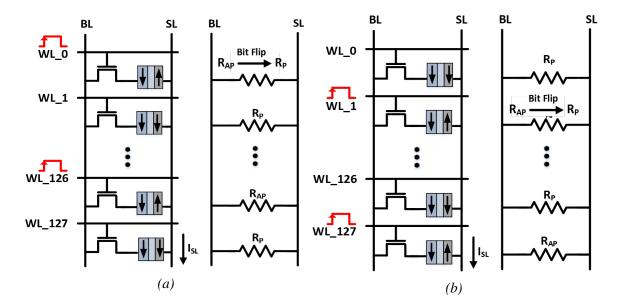

|        | 3.2.2 Error Detection (ED)                                                                | 43 |

|        | 3.2.3 Error Search and Localization                                                       | 49 |

|        | 3.2.4 Overhead of internally storing data                                                 | 52 |

| 3.3    | Performance analysis                                                                      | 53 |

|        | 3.3.1 Test time Comparison                                                                | 53 |

|        | 3.3.2 Area overhead                                                                       | 54 |

| 3.4    | Array Level Testing and Challenges                                                        | 54 |

| 3.5    | Summary                                                                                   | 55 |

| Chapte | r 4: FerroFET based In-memory processing architecture                                     | 56 |

| 4.1    | CONVEX LEAST SQUARE MINIMIZATION                                                          | 57 |

| 4.2    | FerroF  | Fet PIM Architecture and End-to-end Tool Chain Development | 59 |

|--------|---------|------------------------------------------------------------|----|

|        | 4.2.1   | FerroFET cell structure                                    | 60 |

|        | 4.2.2   | Core Architecture                                          | 61 |

|        | 4.2.3   | System Architecture                                        | 63 |

| 4.3    | Design  | n Space Exploration                                        | 64 |

| 4.4    | APPL    | ICATIONS                                                   | 71 |

| 4.5    | Summ    | ary                                                        | 71 |

| Chapte | r 5: ST | T-MRAM based system for reinforcement learning on a drone  | 74 |

| 5.1    | Introd  | uction                                                     | 74 |

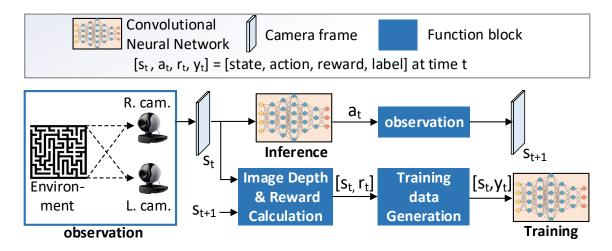

| 5.2    | Reinfo  | preement Learning for Drone Navigation                     | 78 |

|        | 5.2.1   | Basics of Reinforcement Learning                           | 78 |

|        | 5.2.2   | RL in Camera Based Navigation in Drones                    | 79 |

|        | 5.2.3   | Challenges of End-to-End(E2E) RL in Embedded Systems       | 81 |

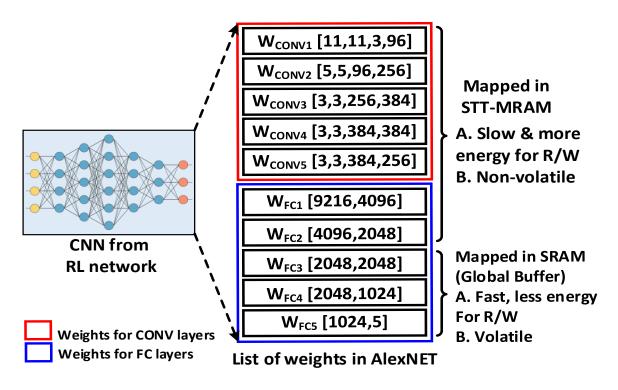

| 5.3    | Propos  | sed Approach Using Transfer Learning(TL) with Real-Time RL | 82 |

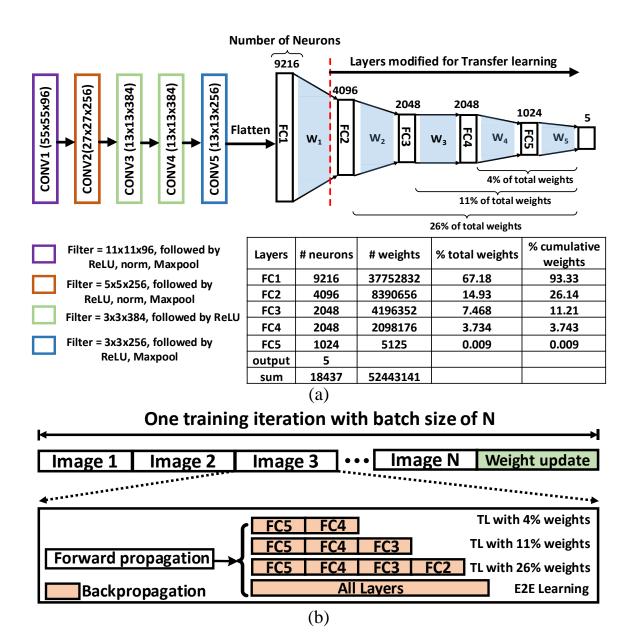

| 5.4    | Propos  | sed System Architecture                                    | 84 |

|        | 5.4.1   | Off-chip to On-chip Data Movement                          | 84 |

|        | 5.4.2   | On-chip System Architecture with Stacked STT-MRAM          | 85 |

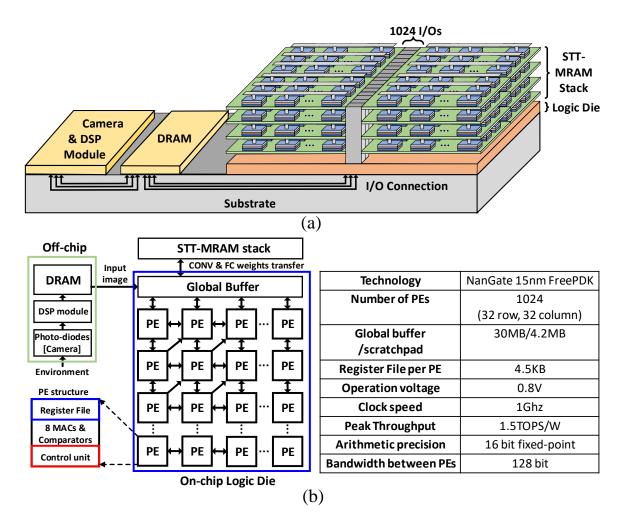

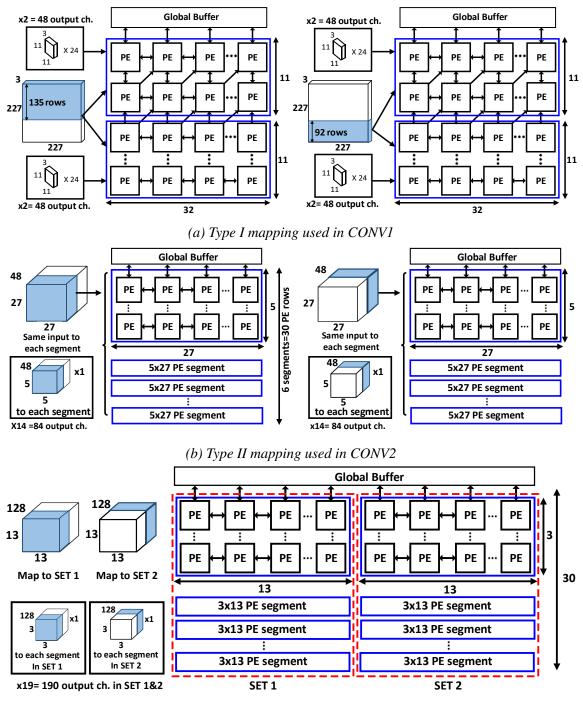

|        | 5.4.3   | Mapping the CNN Model to the Memory System                 | 86 |

| 5.5    | Forwa   | rd Propagation Through the CNN                             | 87 |

|        | 5.5.1   | Forward Propagation in Convolution (CONV) layers           | 87 |

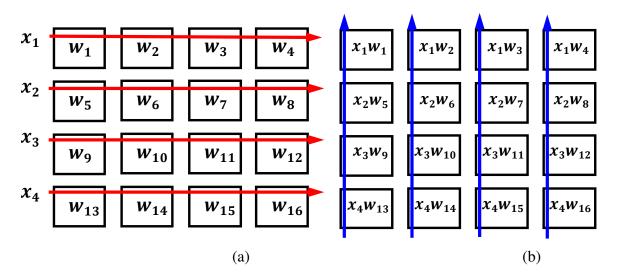

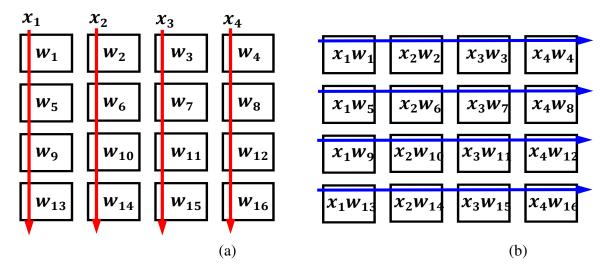

|        | 5.5.2   | Forward Propagation in Fully Connected(FC) Layers          | 90 |

| 5.6    | Backp   | ropagation and Gradient Descent                            | 91 |

|         | 5.6.1    | Backpropagation architecture of Fully-Connected Layer 91 |

|---------|----------|----------------------------------------------------------|

|         | 5.6.2    | Backpropagation architecture of CONV                     |

| 5.7     | Simula   | ation Setup                                              |

|         | 5.7.1    | Hardware Architecture Simulation                         |

|         | 5.7.2    | Simulation Setup                                         |

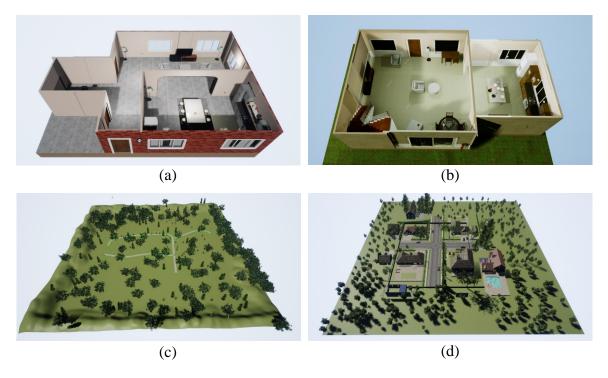

|         | 5.7.3    | Training on Meta Environments                            |

|         | 5.7.4    | Training on Test Environments                            |

| 5.8     | Hardw    | are Power-Performance Results                            |

| 5.9     | Summ     | ary                                                      |

| Chapter | r 6: Coi | <b>nclusion</b>                                          |

| Referen | ces      |                                                          |

# LIST OF TABLES

| 1.1 | Comparison between STT-MRAM [7][5] and competing technologies (EFlash [8][9][10], RRAM[11][12], PCRAM[13][14] |     |

|-----|---------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | STT-MRAM array parameters as compiled from [5][4][17]                                                         | 5   |

| 2.1 | Physical dimensions of MTJ in STT-MRAM bit-cells across technology generations                                | 15  |

| 2.2 | Design parameters for maintaining a target $\Delta$                                                           | 26  |

| 4.1 | Specifications of baseline Von Neumann architecture in 28nm CMOS process                                      | 63  |

| 4.2 | Compute time and energy comparison in different architectures                                                 | 71  |

| 5.1 | List of hyper parameters for training                                                                         | 97  |

| 5.2 | STT-MRAM[104][105][3] and HBM[126] energy parameters used in the system                                       | 102 |

# LIST OF FIGURES

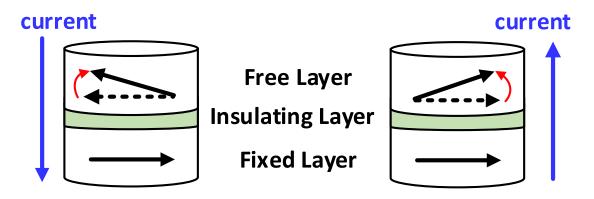

| 1.1 | The direction of magnetic moment in free layer changes from (a)anti-parallel<br>to parallel (b) parallel to anti-parallel to the direction of magnetic moment<br>of fixed layer. The arrow in the free/fixed layer indicates the direction of                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | magnetic moment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4  |

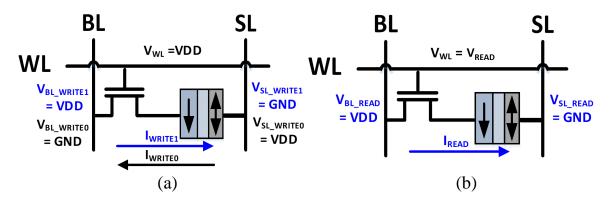

| 1.2 | The STT-MRAM cell schematic of (a) write (b) read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5  |

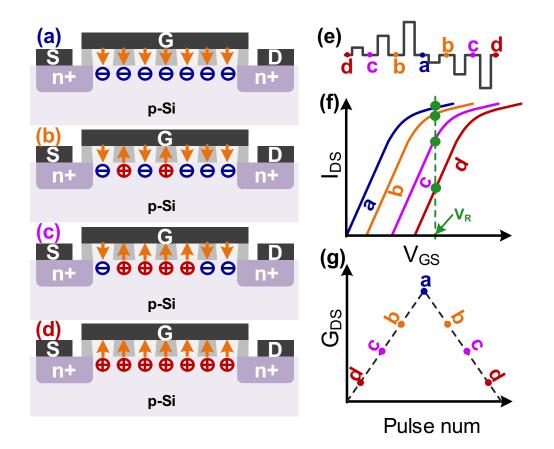

| 1.3 | (a) – (d) show different FerroFET states, corresponding to different portions of ferroelectric domain switching. The yellow arrows indicate the polarization direction. The blue/red circles represent electron/hole, respectively. (e) shows the applied pulse amplitude modulation scheme. The states after each pulse are also illustrated. The initial state is assumed to be all polarizations are pointing toward the gate. (f) shows the $I_{DS}$ - $V_{GS}$ characteristics after each pulse. (g) shows the measured drain to source conductance as a function of applied pulse number. Here ideal case is presented, which shows linear and symmetrical potentiation and depression. | 7  |

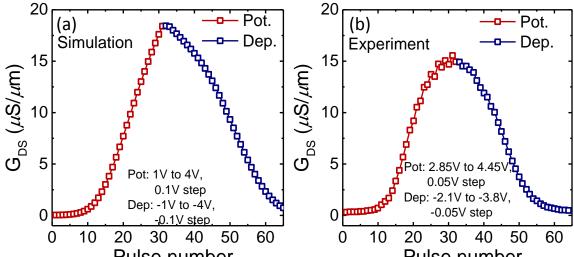

| 1.4 | (a) simulated FerroFET channel conductance (b)Measured FerroFET channel conductance ( $G_{DS}$ ) as a function of pulse number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8  |

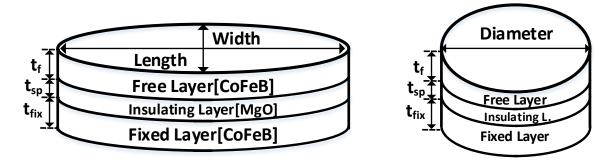

| 2.1 | (a) In-plane MTJ (b) Perpendicular MTJ Physical dimensions of MTJ cell types. The perpendicular MTJ can be Bulk or Interface perpendicular MTJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

| 2.2 | Schematic representation of current loops in the nanomagnet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16 |

| 2.3 | Solenoid representation of current loops in IMTJ and PMTJ to model mag-<br>netic field around MTJs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17 |

| 2.4 | Finite element representation of biot savart law                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17 |

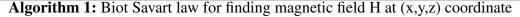

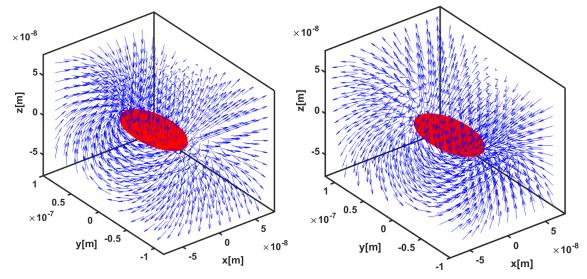

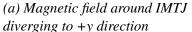

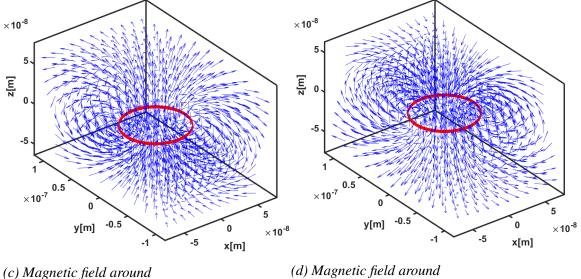

| 2.5  | Magnetic field around IMTJ and PMTJ when current is applied to current loops.(a) current flowing from +y to -y direction (b) current flowing from -y to +y direction (c) current flowing from -z to +z direction (d) current flowing from +z to -z direction                                                                                                                           | 19 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

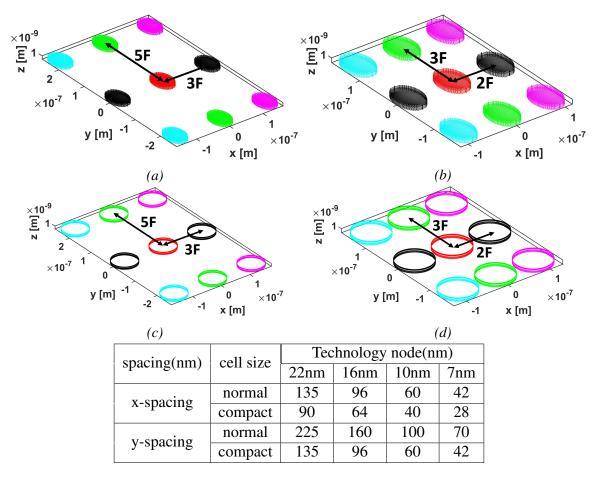

| 2.6  | (a) IMTJ default cell array (b) IMTJ compact cell array (c) PMTJ normal default array (d) PMTJ compact cell array                                                                                                                                                                                                                                                                      | 20 |

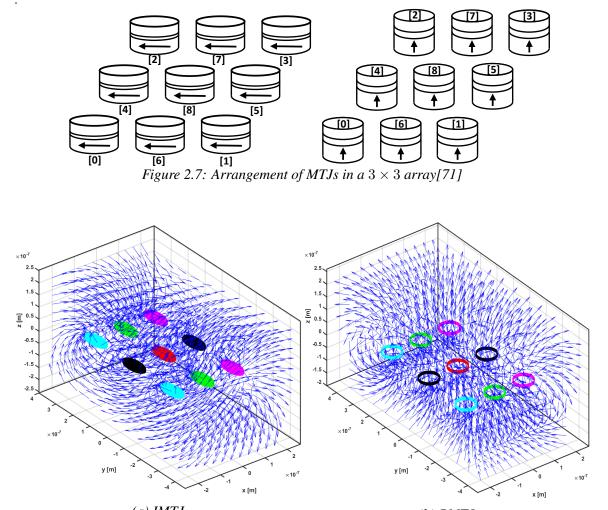

| 2.7  | Arrangement of MTJs in a $3 \times 3$ array[71]                                                                                                                                                                                                                                                                                                                                        | 21 |

| 2.8  | Magnetic field visualization of IMTJ and PMTJ $3 \times 3$ arrays for the worst data pattern[71]                                                                                                                                                                                                                                                                                       | 21 |

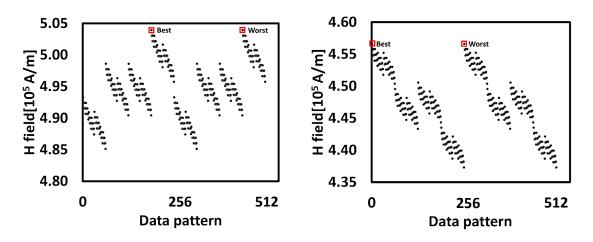

| 2.9  | Residual H field vs. data pattern in IMTJ and PMTJ[71]                                                                                                                                                                                                                                                                                                                                 | 22 |

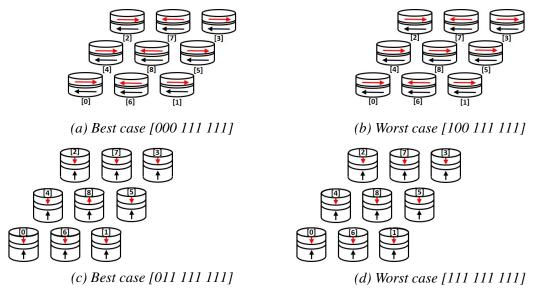

| 2.10 | Magnetic coupling induced worst-case data pattern for thermal stability[71]                                                                                                                                                                                                                                                                                                            | 23 |

| 2.11 | MTJ best/worst data pattern[71]                                                                                                                                                                                                                                                                                                                                                        | 24 |

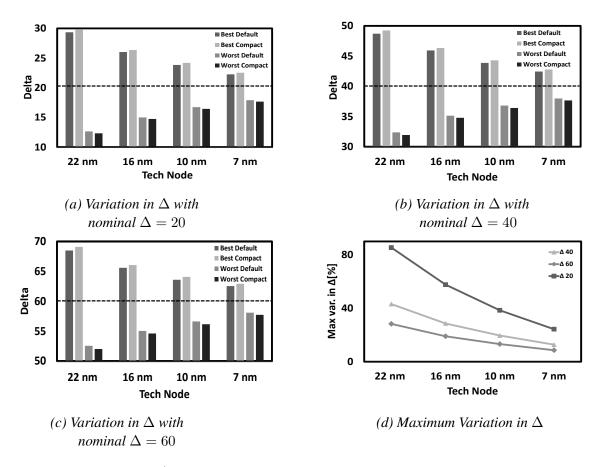

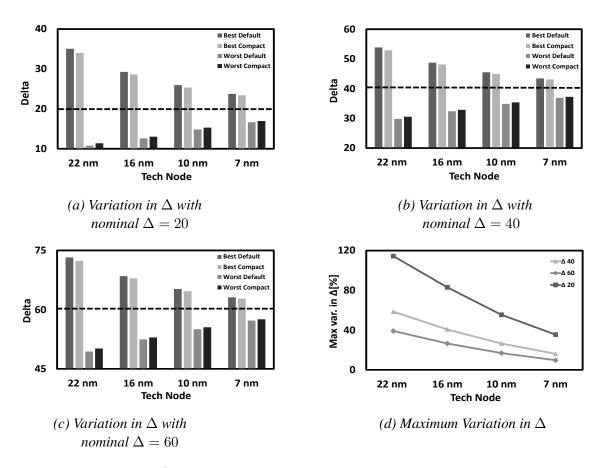

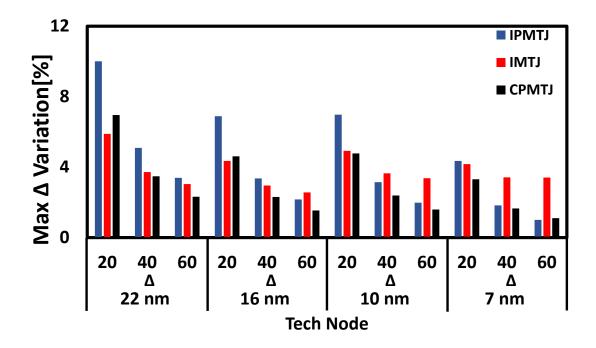

| 2.12 | Variation of $\Delta$ in IMTJ with respect to technology nodes, data patterns and cell array configuration (a) Variation with nominal $\Delta = 20$ (b) Variation with nominal $\Delta = 40$ (c) Variation with nominal $\Delta = 60$ (d) Maximum variation of $\Delta$ across combinations of data pattern and cell array configuration in technology node.                           | 27 |

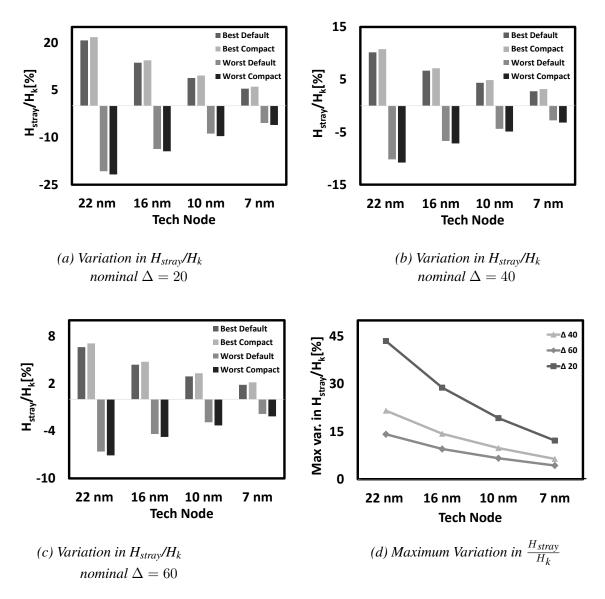

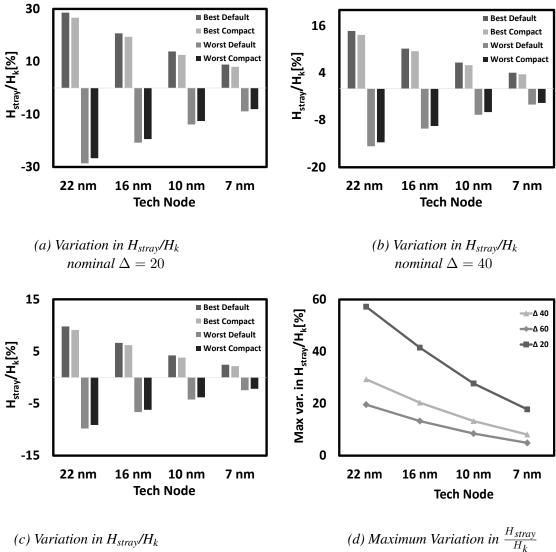

| 2.13 | Variation of $H_{stray}/H_k$ in IMTJ with respect to technology nodes, data patterns and cell array configuration (a) Variation with nominal $\Delta = 20$ (b) Variation with nominal $\Delta = 40$ (c) Variation with nominal $\Delta = 60$ (d) Maximum variation of $H_{stray}/H_k$ across combinations of data pattern and cell array configuration in technology node.             | 28 |

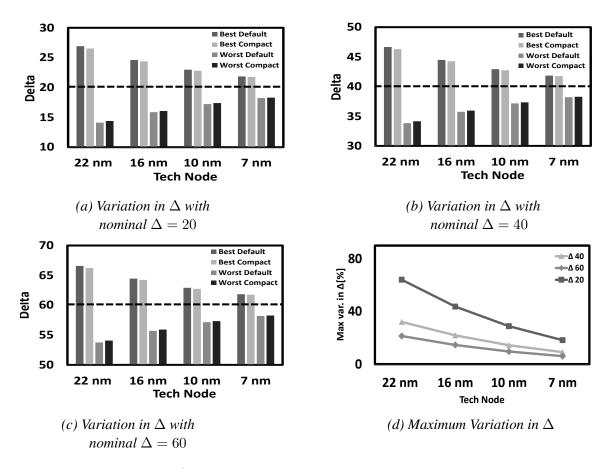

| 2.14 | Variation of $\Delta$ in CPMTJ with respect to technology nodes, data patterns<br>and cell array configuration (a) Variation with nominal $\Delta = 20$ (b) Variation<br>with nominal $\Delta = 40$ (c) Variation with nominal $\Delta = 60$ (d) Maximum vari-<br>ation of $\Delta$ across combinations of data pattern and cell array configuration<br>in technology node.            | 30 |

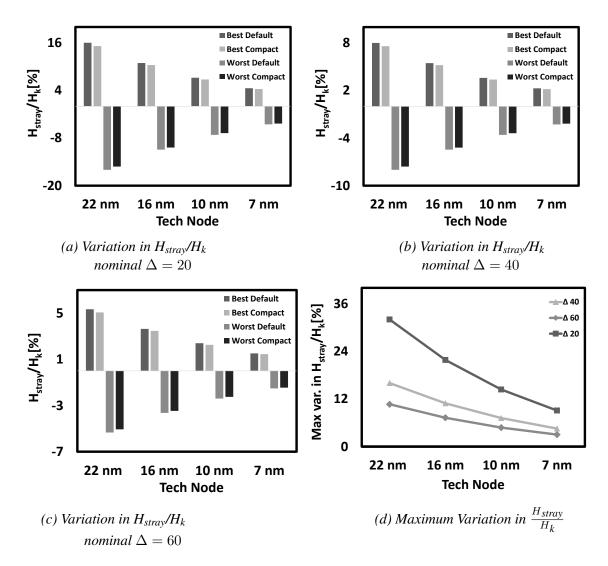

| 2.15 | Variation of $H_{stray}/H_k$ in CPMTJ with respect to technology nodes, data<br>patterns and cell array configuration (a) Variation with nominal $\Delta = 20$<br>(b) Variation with nominal $\Delta = 40$ (c) Variation with nominal $\Delta = 60$ (d)<br>Maximum variation of $H_{stray}/H_k$ across combinations of data pattern and<br>cell array configuration in technology node | 31 |

| 2. | 16 Variation of $\Delta$ in IPMTJ with respect to technology nodes, data patterns<br>and cell array configuration (a) Variation with nominal $\Delta = 20$ (b) Varia-<br>tion with nominal $\Delta = 40$ (c) Variation with nominal $\Delta = 60$ (d) Maximum<br>variation of $\Delta$ across combinations of data pattern and cell array configu-<br>ration in technology node            | . 32 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2. | 17 Variation of $H_{stray}/H_k$ in CPMTJ with respect to technology nodes, data<br>patterns and cell array configuration (a) Variation with nominal $\Delta = 20$<br>(b) Variation with nominal $\Delta = 40$ (c) Variation with nominal $\Delta = 60$ (d)<br>Maximum variation of $H_{stray}/H_k$ across combinations of data pattern and<br>cell array configuration in technology node. | . 33 |

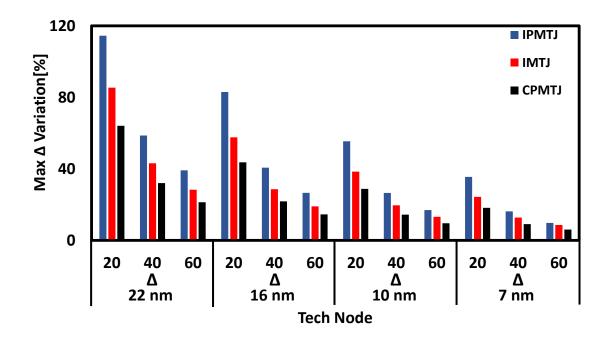

| 2. | 18 Maximum variation of $\Delta$ in IMTJ, CPMTJ and IPMTJ across combinations<br>of data pattern and cell array configuration in technology node and nominal<br>$\Delta$ .                                                                                                                                                                                                                 | . 34 |

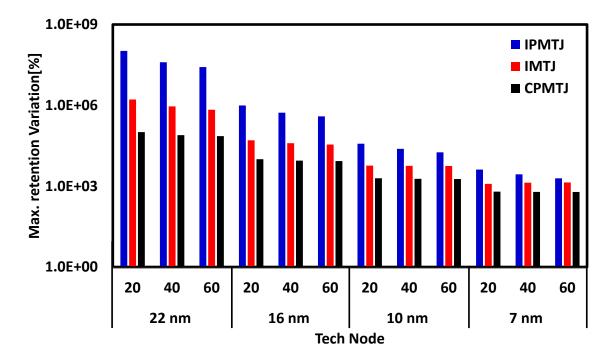

| 2. | 19 Maximum variation of retention time in IMTJ, CPMTJ and IPMTJ across combinations of data pattern and cell array configuration in technology node and nominal $\Delta$ .                                                                                                                                                                                                                 | . 35 |

| 2. | 20 Maximum variation of $\Delta$ in IMTJ, CPMTJ and IPMTJ across combinations of data pattern and cell array configuration in technology node and nominal $\Delta$ .                                                                                                                                                                                                                       | . 36 |

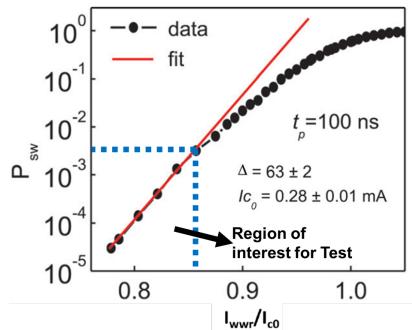

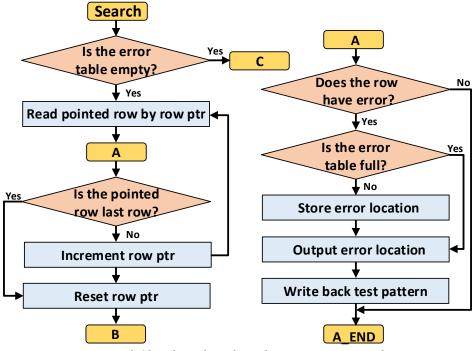

| 3. | 1 Experimental data of $P_{SW}$ vs. Iwwr[7] showing the region of operation for test where the exponential thermal model is valid                                                                                                                                                                                                                                                          | . 40 |

| 3. | 2 IMTJ worst case data patterns for retention shown in a $5 \times 5$ grid. For PMTJ the worst case pattern is all-ones.                                                                                                                                                                                                                                                                   | . 41 |

| 3. | 3 System architecture of EMACS MBIST applied to a $64 \times 128$ array. EMACS is capable of read, write and statistical retention tests.                                                                                                                                                                                                                                                  | . 41 |

| 3. | 4 Multiple word-lines simultaneously turned ON to detect bit-flips according to worst case patterns identified in Fig.10 for IMTJ. (a) Simultaneous testing with block data pattern A applied to C1,C3,, (b) Simultaneous testing with block data pattern B applied to C0,C2, For PMTJ the worst case pattern is all-ones so all word-lines are turned on simultaneously                   | . 44 |

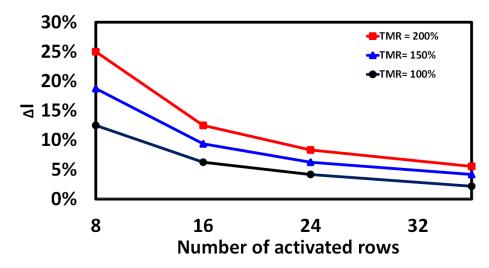

| 3. | 5 $\Delta I_{SL}$ vs. number of rows activated as a function of TMR                                                                                                                                                                                                                                                                                                                        | . 45 |

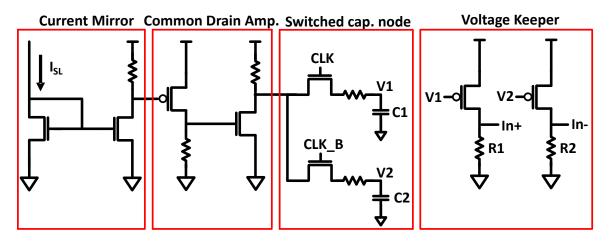

| 3. | 6 Error Detection circuit for a column with 16 rows                                                                                                                                                                                                                                                                                                                                        | . 45 |

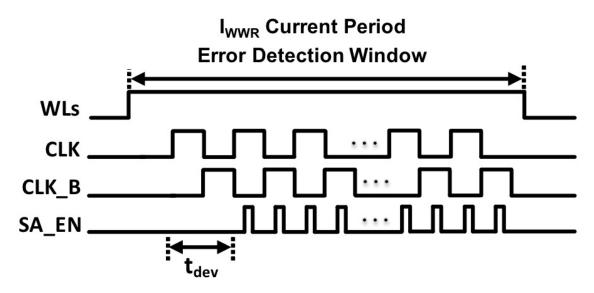

| 3. | 7 Timing Diagram illustrating the operation of the MBIST retention test                                                                                                                                                                                                                                                                                                                    | . 46 |

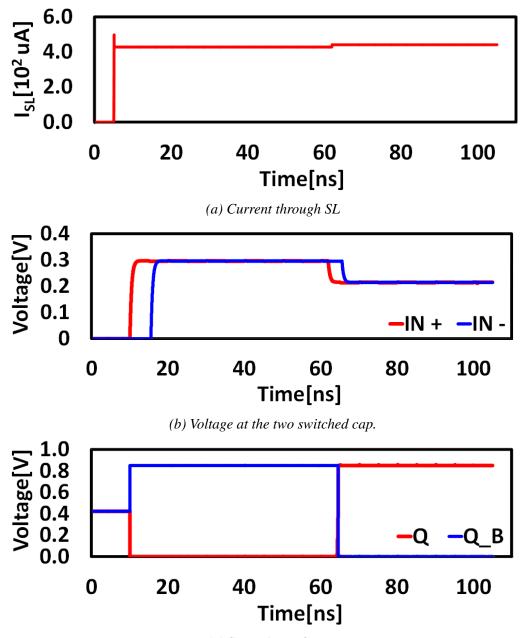

| 3.8  | Transient analysis for error detection                                                                                                                                                                                                                                                                             | 47 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

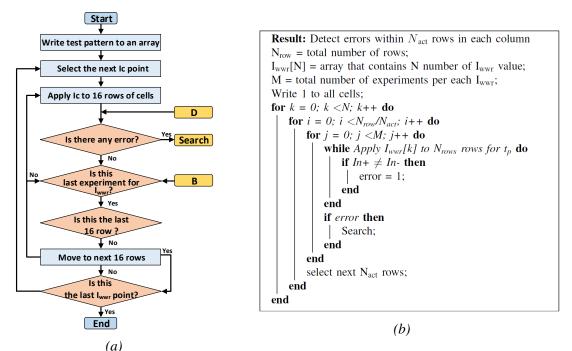

| 3.9  | (a) Flow chart (b) algorithm for bit-flip detection in a column                                                                                                                                                                                                                                                    | 48 |

| 3.10 | Estimating $P_{sw}$ and $\Delta$ through EMACS                                                                                                                                                                                                                                                                     | 48 |

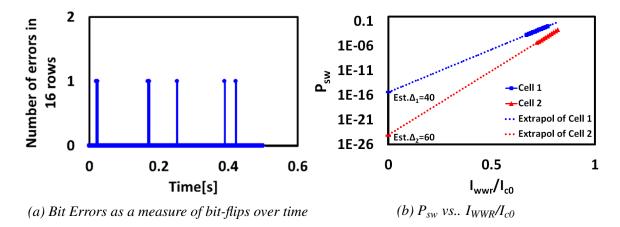

| 3.11 | $P_{sw}$ on a cluster of cells in an 8KB array showing a scatter which can be extrapolated to obtain $\Delta$                                                                                                                                                                                                      | 49 |

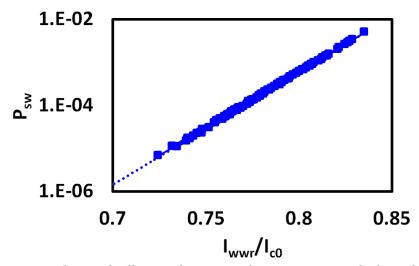

| 3.12 | Flow chart for exhaustive error search                                                                                                                                                                                                                                                                             | 50 |

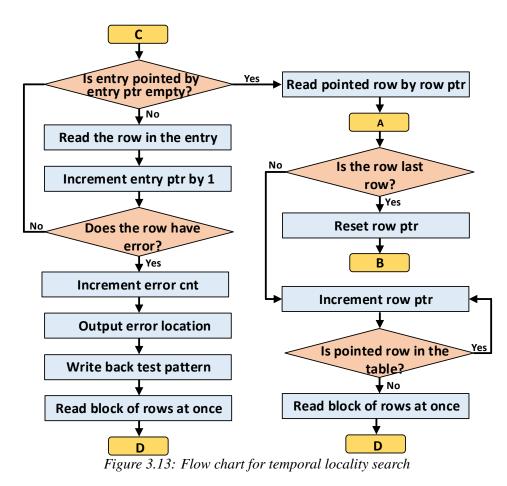

| 3.13 | Flow chart for temporal locality search                                                                                                                                                                                                                                                                            | 51 |

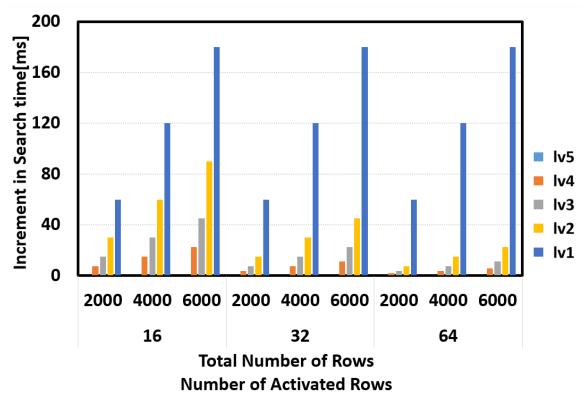

| 3.14 | Search time increment w.r.t. localization level                                                                                                                                                                                                                                                                    | 52 |

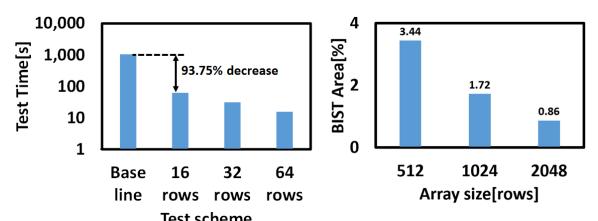

| 3.15 | (a) Retention time vs. localization level, (b) Area overhead w.r.t. array size .                                                                                                                                                                                                                                   | 53 |

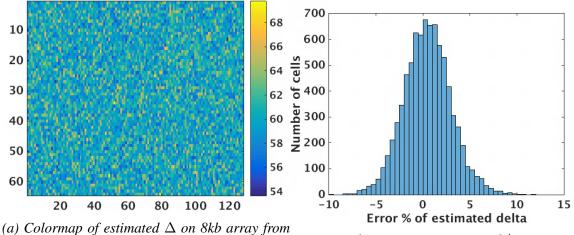

| 3.16 | Estimated $\Delta$ and Error of estimation from 8kb array using EMACS. The colormap represents cells in a $64 \times 128$ array.                                                                                                                                                                                   | 55 |

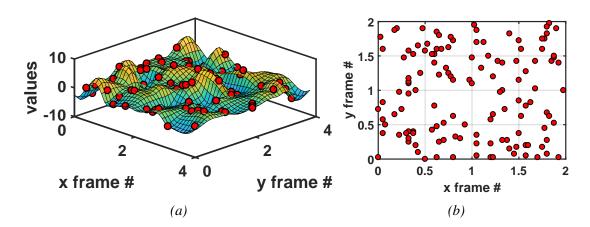

| 4.1  | (a) 2D continuous function $f(u,v)$ with non-uniform samples. (b) Spatial location of the non-uniform samples.                                                                                                                                                                                                     | 57 |

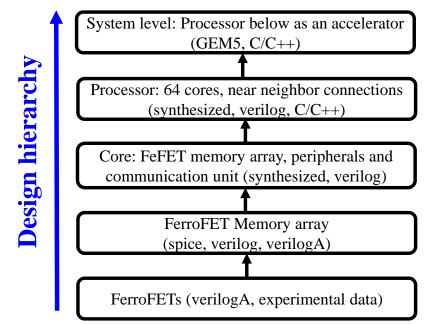

| 4.2  | Flow-chart of design hierarchy from device to system                                                                                                                                                                                                                                                               | 59 |

| 4.3  | FerroFET cell schematic (a) Conceptual (b) Transistor level implementa-<br>tion                                                                                                                                                                                                                                    | 60 |

| 4.4  | Schematic of a typical core                                                                                                                                                                                                                                                                                        | 62 |

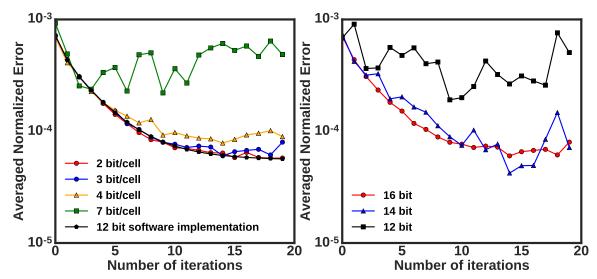

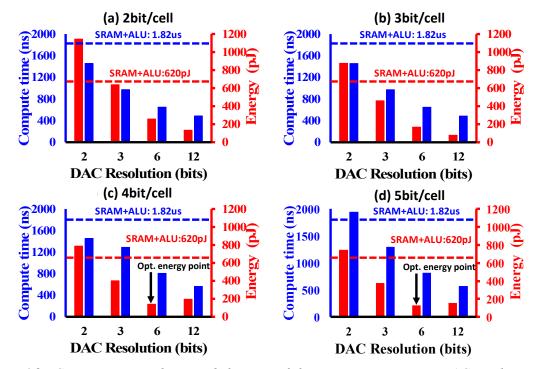

| 4.5  | (a) Average normalized error in signal reconstruction via distributed least-<br>squares method as a function of the number of bits/cell of FerroFET. The<br>ADC bit resolution is fixed to 16 (b) Average normalized error of Z in non-<br>uniform sampling algorithm with respect to different ADC bit resolution | 65 |

| 4.6  | (a) Nonlinear conductance of 4bit/cell FerroFET (b) Average normalized error of as a function of the nonlinear conductance of FerroFETs. (4 bits/cell FerroFET and 16 bit ADCs are considered)                                                                                                                     | 67 |

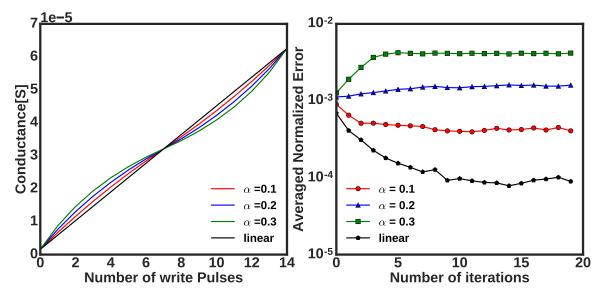

| 4.7  | Compute time and energy behaviour of the compute unit versus DAC resolution for the parallel-computation approach and storage per FerroFET memory cell is (a) 2bit/cell (b) 3bits/cell (c) 4bits/cell and (d) 5bits/cell                                                                                           | 68 |

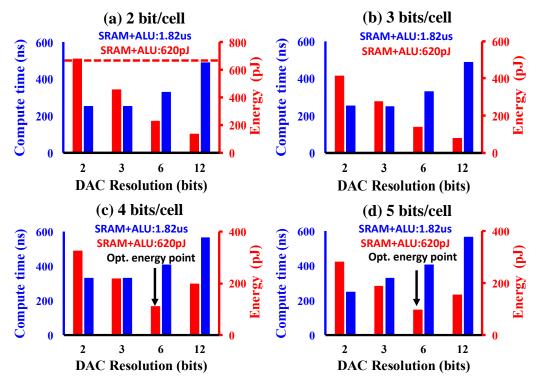

| 4.8  | Compute time and energy behaviour of the compute unit versus DAC resolution for the sequential-computation approach and storage per FerroFET memory cell is (a) 2bit/cell (b) 3bits/cell (c) 4bits/cell and (d) 5bits/cell                                                                                                                                         | 69 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

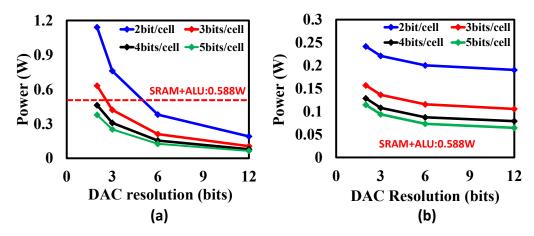

| 4.9  | Power consumption of the compute unit when bits/memory cell and DAC resolution are varied for (a) parallel-computation (b) sequential-computation.                                                                                                                                                                                                                 | 70 |

| 4.10 | Estimated area of the compute unit when bits/memory cell and DAC resolution are varied for (a) parallel-computation (b) sequential-computation                                                                                                                                                                                                                     | 70 |

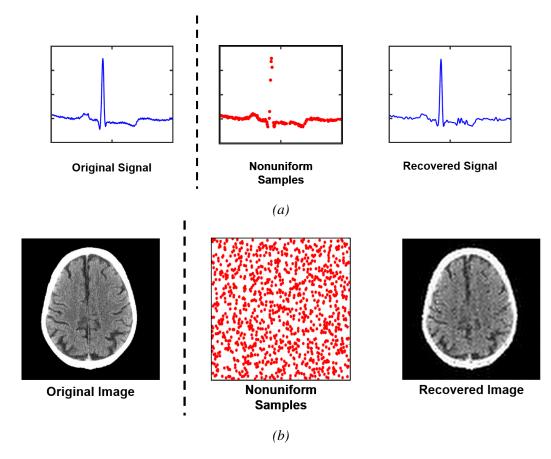

| 4.11 | Reconstruction steps. (a) 1D Example: Recovery of EEG Signal Profile.<br>(b) 2D Example: Brain Computed Topography Recovery                                                                                                                                                                                                                                        | 72 |

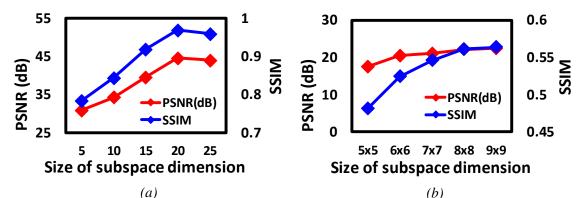

| 4.12 | Peak signal-to-noise ratio (PSNR) & Structural similarity (SSIM). (a) 1D<br>Example: Recovery of a non-uniformly sampled 1D signal from an EEG<br>probe. (b) 2D Example: Recovery of a sampled image from the CT scan of<br>a brain.                                                                                                                               | 72 |

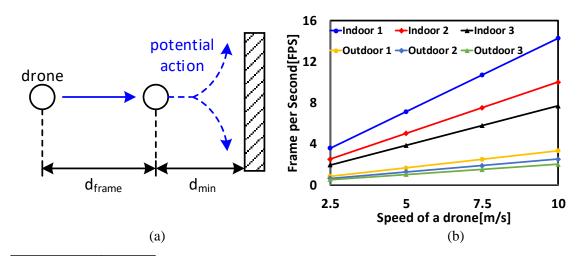

| 5.1  | (a) Definition of minimum distance required for obstacle avoidance $(d_{min})$ .<br>$d_{frame}$ = distance that drone moves between frames. (b) Frame per second<br>vs. speed of a drone for sample indoor and outdoor environments (c) $d_{min}$<br>setting for different environment and minimum FPS needed for obstacle<br>avoidance for different environments | 75 |

| 5.2  | Reinforcement Learning(RL) network architecture for camera based navi-<br>gation in drones                                                                                                                                                                                                                                                                         | 80 |

| 5.3  | Reinforcement Learning(RL) network architecture for camera based navi-<br>gation in drones. (a) Modified AlexNET [112] for the proposed system (b)<br>3 configurations where 4,11 and 26% weights are learnt in real-time. This<br>is in contrast to E2E RL, where the entire network is learnt in real-time                                                       | 81 |

| 5.4  | (a) 3D view of the hardware platform (b) System architecture and parameters as extracted post-synthesis in 15nm Nangate PDK                                                                                                                                                                                                                                        | 85 |

| 5.5  | Mapping the weights of the proposed CNN (modified AlexNET) to stacked-STT-MRAM and on-die SRAM in the system                                                                                                                                                                                                                                                       | 86 |

| 5.6  | Strategies for mapping weights and data for processing the convolutional layers                                                                                                                                                                                                                                                                                    | 89 |

| 5.7  | (a) Row-wise vector propagation in PE array for calculating pSUM (b) Ver-<br>tical pSUM accumulation for vector-matrix multiplication in forward prop-<br>agation of FC layers                                                                                                                                                                                     | 91 |

| 5.8  | (a) Column-wise vector propagation in PE array for calculating pSUM (b)<br>Row-wise pSUM accumulation for vector-transposed matrix multiplication<br>in backpropagation of FC layers                                                                                   | 92  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.9  | Screenshots of the complex meta environments developed using UE 4                                                                                                                                                                                                      | 93  |

| 5.10 | Screenshots of the test environments (a)Indoor Apartment (b)Indoor House (c)Outdoor Forest (d)Outdoor Town developed using UE 4                                                                                                                                        | 94  |

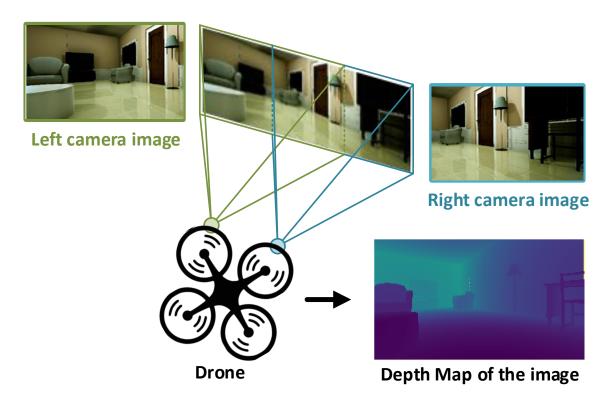

| 5.11 | Stereo Vision based Depth Map Generation                                                                                                                                                                                                                               | 95  |

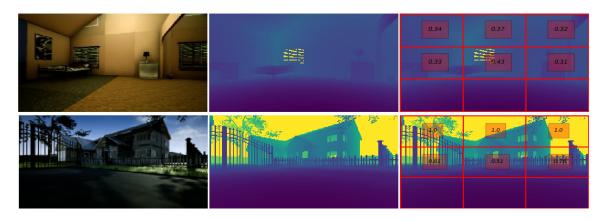

| 5.12 | Feature extraction for SVM Classifier – On the left, the actual camera frame is shown. The depth map (in the center) is divided into windows and the top 6 windows are used towards feature extraction (right image)                                                   | 95  |

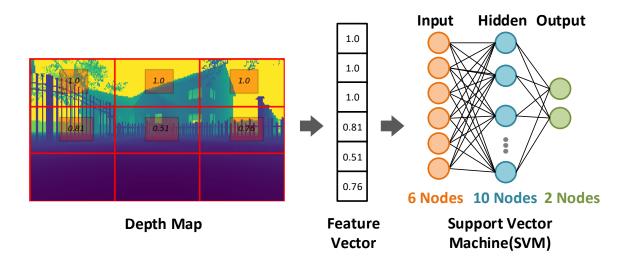

| 5.13 | SVM Classifier Block Diagram                                                                                                                                                                                                                                           | 96  |

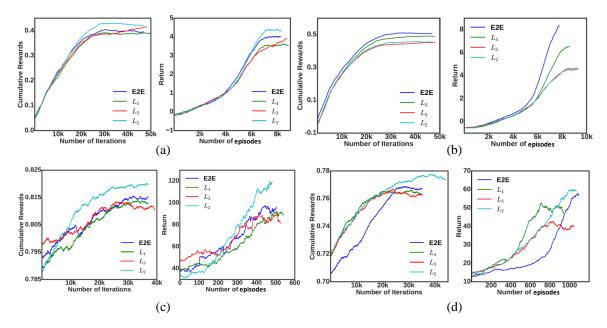

| 5.14 | Cumulative rewards and return results in indoor (a)apartment (b)house and outdoor (c)forest (d)town test environments. The legend $L_i$ indicates TL with last i-layers. All the algorithms show convergence and improving return loss indicating successful learning. | 98  |

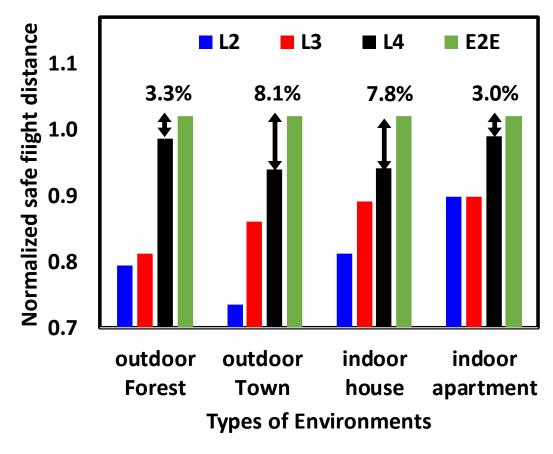

| 5.15 | Normalized safe flight distance (SFD) with respect to different environments.                                                                                                                                                                                          | 99  |

| 5.16 | Latency, power and energy of each layers in forward and backward propa-<br>gation                                                                                                                                                                                      | 100 |

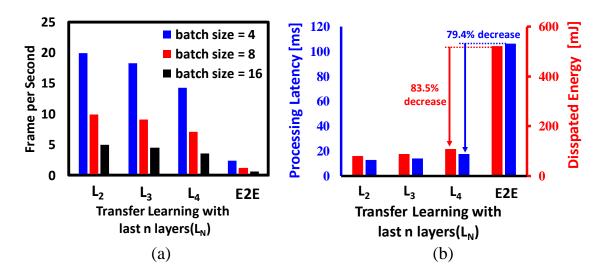

| 5.17 | (a) Maximum fps supported by different algorithms as a function of batch size. (b) Estimated processing latency and energy dissipation                                                                                                                                 | 101 |

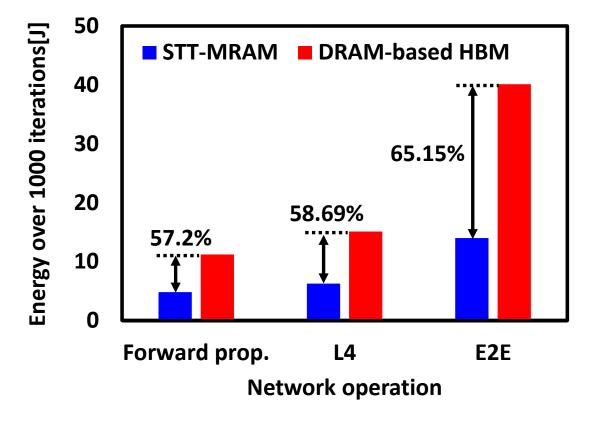

| 5.18 | : Energy dissipation from DRAM-based HBM and STT-MRAM memory stack (off-chip) in case of Forward propagation, last 4 layer training $(L_4)$ and E2E learning                                                                                                           | 102 |

# CHAPTER 1 INTRODUCTION

### 1.1 Motivation

In recent years, Post-CMOS memory technologies are extensively explored as the importance of deep neural network based machine learning and distributed optimization accelerators increases. Among other post-CMOS memory technologies, spin torque transfer magnetic Random Access Memory (STT-MRAM) and ferroelectric Field Effect Transistor(FerroFET) are viable candidates for deep learning and distributed optimization accelerators. Spin Transfer Torque Magnetic Random Access Memory (STT-MRAM) is an emerging memory technology which exhibits non-volatility, high density, high endurance and nano-second read and write times with no refresh operations. These attributes of STT-MRAM make it suitable as a DRAM replacement in near-memory architecture of deep learning based accelerator. Since STT-MRAM shows short read latency and no refresh power, application such as deep learning based Unmanned Aerial Vehicles (UAVs) with small power-constraints is a perfect application for STT-MRAM.

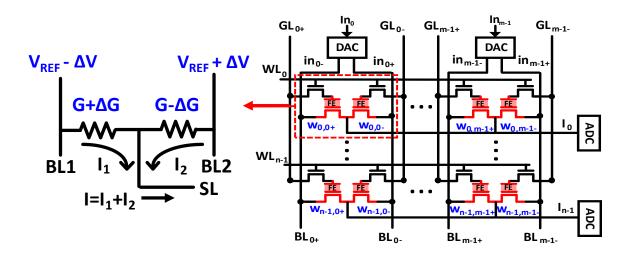

FerroFET device can be used as a analog multiplier by measuring current across Ferro-FET after applying voltage between the source and drain of the device. By embedding FerroFET, a processing element, in the memory subarray itself in so called processing-inmemory architecture, the system can solve memory bottleneck, a problem due to a large amount of data traffic between logic and memory blocks, of deep learning and optimization accelerators.

In the dissertation, we propose in/near-memory processing system design with post-CMOS devices such as STT-MRAM and FerroFET for machine learning and optimization accelerators. First, we introduce the properties and characteristics of STT-MRAM and FerroFET and show why using these technologies can improve systems for deep learning and optimization. Then we identify the challenges of STT-MRAM and FerroFET in device & circuit level and provide potential solutions to the challenges. Lastly, we demonstrate the implementation of;

- 1. Near-memory system with STT-MRAM for Reinforcement Learning algorithm for a drone

- 2. In-memory system with FerroFET for distributed convex optimization via least squares method

to compare the system performance in latency, power and energy with state-of-the-art conventional system. In the conclusion, we show whether post-CMOS based in/near-memory system exhibits better performance compared to conventional system even with the limitations in post-CMOS devices.

In the next section, we present prior works on post-CMOS devices(mainly STT-MRAM and FerroFET) and challenges of STT-MRAM & FerroFET based system with in/near memory architectures.

### 1.2 Prior works

#### 1.2.1 Post CMOS memory: Spin Transfer Torque Magnetic RAM (STT-MRAM)

It is well understood that next-generation memory-intensive ultra low power learning-based systems require a memory technology which shows;

- 1. high-density

- 2. low-standby power (hence eNVM)

- 3. acceptable R/W speeds

4. compatibility with a logic process both in terms of process thermal budget and voltage domains

This is required to ensure that the design, along with an eNVM, can take advantage of the numerous scaled high performance, low power digital logic blocks that are essential for any area and power constrained design like the one we have described in this paper. Compared to other NVMs such as Phase-change memory or resistive RAM, STT-MRAM exhibits better read/write latency [1][2] and is more mature than Ferroelectric FET based RAMs. Recent publications from leading foundries [3][4][5] have demonstrated MBs of STT-MRAM arrays with necessary peripheral circuits. Compared to STT-MRAMs, RRAMs show larger device-to-device and cycle-to-cycle variations making it hard to commercialize [6].

Table 1.1: Comparison between STT-MRAM [7][5] and competing technologies (EFlash[8][9][10], RRAM[11][12], PCRAM[13][14]

|                 | SRAM                 | Eflash           | STT-MRAM         | RRAM             | PCRAM     |

|-----------------|----------------------|------------------|------------------|------------------|-----------|

| Cell size       | 80~100F <sup>2</sup> | ~6F <sup>2</sup> | >6F <sup>2</sup> | $>4F^{2}$        | $>4F^{2}$ |

| Non-volatility  | No                   | Yes              | Yes              | Yes              | Yes       |

| Program voltage | < 1V                 | <~10V            | < 1.5V           | < 3V             | < 1V      |

| Write speed     | ~1ns                 | 660 µs           | ~30ns            | $\sim 1 \ \mu s$ | ~80ns     |

| Read speed      | ~1ns                 | 45 μs            | ~10ns            | ~1 µs            | ~10ns     |

| Endurance       | 1016                 | $10^4 \sim 10^6$ | 1015             | $10^{10}$        | 1012      |

| Retention       | N/A                  | 10 yrs           | 10 yrs           | 10 yrs           | 10 yrs    |

Although our study investigates STT-MRAM based stacks, all eNVM suffer from high write latency and energy; and hence the algorithm-hardware co-design that we propose is applicable to similar other platforms. The STT-MRAM model parameters are summarized in Table 1.1.

The STT-MRAM bitcell consists of one access transistor and one Magnetic Tunnel Junction (MTJ) where a single bit of information is stored[15]. Typical MTJ stacks comprise of an insulator (MgO) which is sandwiched between a "fixed" ferromagnetic layer (typically CoFeB based) whose magnetic moment is pinned to one direction and a "free" ferromagnetic layer whose moment changes direction based on applied external current or magnetic field. Since MTJ exhibits TMR (Tunneling magnetoresistance)[16], the resis-

tance of the stack changes depending on the orientation of the "free" layer, which in turn stored the data of the bit-cell. When the direction of the magnetic moment inside the free layer of an MTJ is anti-parallel to the fixed layer, the MTJ has high resistance and its state is defined as bit "1" [15]. Likewise, when the direction of the magnetic moment in an MTJ is parallel to the magnetic moment of the fixed layer, the MTJ exhibits low resistance and it is defined as bit "0".

Figure 1.1: The direction of magnetic moment in free layer changes from (a)anti-parallel to parallel (b) parallel to anti-parallel to the direction of magnetic moment of fixed layer. The arrow in the free/fixed layer indicates the direction of magnetic moment.

Fig. 1.1 describes how the direction of magnetic moment in the free layer changes based on the current across the MTJ. Fig. 1.1 shows how the direction of magnetic moment in the free layer changes from (a) anti-parallel to parallel and (b) parallel to anti-parallel direction compared to the direction of magnetic moment in fixed layer. Since the fixed layer acts as a spin polarizer, the spin polarized electrons that pass the fixed layer exerts the torque on the magnetic moment in the free layer and causes a flip in the direction of the magnetic moment in fixed layer as shown in Fig. 1.1(a). When the current flows from the fixed layer to the free layer as shown in Fig. 1.1(b), the electrons with opposite spin are reflected back from the fixed layer and exerts a torque that changes the direction of the magnetic moment of the free layer to an anti-parallel direction with respect to the magnetic moment in the fixed layer. The alignment of the magnetic moment in the fixed and free layers determine the resistance across the MTJ. When the magnetic moments in the two

layers are anti-parallel to each other, the resistance across MTJ is high.

Figure 1.2: The STT-MRAM cell schematic of (a) write (b) read operation

| Technology         | 22nm FFL FinFET    |  |  |

|--------------------|--------------------|--|--|

| TMR                | 180%               |  |  |

| RA                 | $9 \Omega \mu m^2$ |  |  |

| Density            | 8Mb                |  |  |

| Cell architecture  | 1T 1MTJ            |  |  |

| unit cell size     | $9F^2$             |  |  |

| Power supply(core) | 1.0V               |  |  |

| MTJ size           | 60~80nm            |  |  |

| MTJ type           | Perpendicular MTJ  |  |  |

Table 1.2: STT-MRAM array parameters as compiled from [5][4][17]

A low resistance is achieved when both the magnetic moments are parallel to each other. The high/low resistance is mapped to 1/0. The bias conditions applied for the write and read operations are shown in Fig. 1.2. As shown in Fig. 1.2(a), the write operation is bi-directional. In case of writing a 1, the bit-line and the source line are set to VDD and GND and the write current flows from the fixed layer to the free layer of the MTJ. The biasing condition for writing a 0 is the opposite and is shown in Fig. 1.2(a). In case of read operations, the word-line is asserted to VREAD and the bitline and the source line are set to VDD and GND. This causes a weak current to flow across the MTJ and the resistance

state is sensed using either a constant current scheme or a BL discharge scheme [18]. Table 1.2 shows STT-MRAM array parameters from the silicon implementation of STT-MRAM.

### 1.2.2 Post CMOS memory: Ferroelectric FET

We explore FerroFETs as the technology of choice for implementing resistive cross-bar architectures that can accelerate linear algebraic operations. In particular, HfO<sub>2</sub> based Ferroelectric FETs (FerroFETs) have recently received great interest for its application in non-volatile memory (NVM) [19]. It is CMOS compatible and retains ferroelectricity for thin films with thickness around 10nm. By tuning the portion of switched ferroelectric domain, a FerroFET can exhibit multiple intermediate states, which has been used in neuromorphic computing [20, 21].

The operation of FerroFET as an multi-valued eNVM storage is different from a traditional binary memory [19] in that a series of weak pulses are applied to set the device in a desired state [20, 21]. Various pulse schemes are proposed to tune the state, including identical pulse schemes[22], pulse-width modulation schemes[23], and pulse-amplitude modulation schemes [21][24]. For illustration, Fig. 1.3 illustrates the operation with pulseamplitude modulation scheme, which is used in this paper. Fig. 1.3(e) shows the applied pulse waveform. After each pulse, the percentage of switched ferroelectric domains is modified. The device states are shown in Fig. 1.3 (a)-(d). The device  $I_{DS}$ -V<sub>GS</sub> corresponding to different states are shown in Fig. 1.3 (f), which shows the intermediate states. The different states could be sensed by applying a read pulse, V<sub>R</sub>, the corresponding drain-tosource conductance, G<sub>DS</sub>, can be sensed. Fig. 1.3 (g) shows the ideal G<sub>DS</sub> as a function of applied pulse numbers. G<sub>DS</sub> increases/decreases linearly with pulse number during potentiation/depression, respectively. A symmetrical potentiation/depression is necessary for high accuracy computation. The FerroFET model includes atomistic simulation of domain dynamics with a drift-diffusion based FET model. The simulation results closely match the experimental data and is shown in Fig. 1.4 where the different conductance levels are

Figure 1.3: (a) – (d) show different FerroFET states, corresponding to different portions of ferroelectric domain switching. The yellow arrows indicate the polarization direction. The blue/red circles represent electron/hole, respectively. (e) shows the applied pulse amplitude modulation scheme. The states after each pulse are also illustrated. The initial state is assumed to be all polarizations are pointing toward the gate. (f) shows the  $I_{DS}$ - $V_{GS}$  characteristics after each pulse. (g) shows the measured drain to source conductance as a function of applied pulse number. Here ideal case is presented, which shows linear and symmetrical potentiation and depression.

shown as a function of the number of programming pulses.

### 1.2.3 Challenges with STT-MRAM and FerroFET based system

### Magnetic Coupling Across Bit-Cells in STT-MRAM

As STT-MRAM arrays become dense and the cell dimensions become smaller, the magnetic field coupling from ferromagnetic layers of one MTJs affect write and read operation of its neighboring bits. As shown in [25], scaling MTJ in a densely packed array causes program errors due to large stray field coupling. When MTJ scales down and they are

Figure 1.4: (a) simulates Penoper performance conductance (b) Measured Penoper Performance conductance ( $G_{DS}$ ) as a function of pulse number.

densely packed in an array, magnetic coupling of MTJs could become a significant problem since the distance of the ferromagnets, free and fixed layer of MTJs, reduces to cause even stronger magnetic coupling. Therefore, there is an urgent need to identify how magnetic coupling affects properties of STT-MRAM and analyze whether magnetic coupling will pose as a scaling challenge in further scaling of STT-MRAM dimensions.

There is limited prior work on the analysis of magnetic coupling on STT-MRAM arrays. Observation of  $H_{stray}$  in victim MTJ with four neighboring MTJs in technology scaling was presented by one of the authors in [26]. However, detailed models of magnetic coupling, the role of technology scaling on stray field and their effect on the electrical characteristics has not been discussed. On the other hand, there is ample research that analyzes how static and dynamic properties of MTJ are affected by technology scaling. [27][28] presents a scaling roadmap of MTJ that contains trends for thermal stability, switching current density ( $J_{c0}$ ), critical switching current ( $I_c$ ), Resistance-Area product (RA), etc. The effect of technology scaling on the dynamic properties of MTJs is also well explored; [29],[30] present how write current( $I_c$ ) and critical current density( $J_{c0}$ ) change with technology nodes. While scaling MTJ dimension, the authors calibrate  $H_k$  to maintain a target thermal stability of the MTJ. [31] presents changes in write current density ( $J_{c0}$ ) across different MTJ types.

Further, [32][33] proposes a scaling trend of anisotropy energy ( $K_u$ t) for single and dual interface MTJs. The authors also present models of thermal stability as a functions of MTJ dimensions. [34] examined how  $P_{fail}$  of a chip, which relates to thermal stability, changes with technology node. We also explore the case where the fixed layer is an anti-ferromagnet and the magnetic fields are closed. In this case, the free layer nanomagnets create the magnetic field which affects the performance and stability of the victim cell.

#### Retention test Challenges of STT-MRAM Arrays

STT-MRAM arrays are expected to suffer from read and write failures which are induced by electrical defects and process variations. The role of variations in read and write have been extensively studied, including prior work by the authors[35]. However, the role of resistive and capacitive defects and coupling faults is relatively unexplored (except for preliminary work in [36]). Apart from read and write faults, STT-MRAMs can also suffer from retention failures. The non-volatility (or retention characteristics) of the bit can be measured by the thermal stability factor. [37][38] describe retention failure as a bit-flip in a cell caused by thermal noise. The thermal activation model of STTMRAM in [37] suggests that a bit flip has a poisson distribution with time constant of  $\tau .e^{\Delta}$  where  $\tau \approx 1ns$ . Due to this fact, conventional test methods for retention have very large number of test times and there is a strong need for implementing a retention test scheme of STT-MRAM arrays that has low testing latency.

#### Challenges in FerroFET based In-memory processing architecture

Modern computing systems based on the Von-Neumann architecture rely on a clear distinction between logic and memory, and processes information by executing a sequence of precise atomic instructions with periodic uploads to the memory. Such systems are the foundation of the digital revolution which began with the demonstration of the self-aligned planar-gate silicon MOSFET in the sixties and was accelerated by rapid advances in transistor technology. However, in the last one decade, the volume of data collected by distributed sensors and networks has grown exponentially. Ingesting, processing and extracting actionable intelligence out of this abundant data requires large amount of data traffic between logic and memory blocks leading to the problem of memory bottleneck. This requires novel ways of architecting the compute platform. For example, by embedding processing elements in the memory sub-array itself in so called Processing-In-Memory (PIM) architectures [39, 40, 41, 42, 43], the traditional Von-Neumann bottleneck can be addressed and significant acceleration and improved power-efficiency can be achieved.

HfO<sub>2</sub> based Ferroelectric FETs (FerroFETs) have recently received great interest for its non von-neumann application in nonvolatile memory (NVM) [19]. Among all of post CMOS memories, the developments in FerroFET technology is a rather recent occurrence; thanks to the breakthrough discovery of the underlying physical phenomenon: ferroelectricity in CMOS compatible Hf based binary oxides in 2011 [44][45] [46] a flurry of research activities on FerroFETs has ensued worldwide [47] [48][49]. FerroFET are also the most energy efficient among all eNVM technologies. This is due to the fact that, in contrast to the other non-volatile memories which are all current driven, the FerroFETs relies on electric field-effect for memory state switching. While non-Von-Neumann architectures based on other emerging eNVM technologies are being explored in depth [50] [51][52][53][54], the FerroFET technology provides unique features for adoption in such emerging architectures and applications.

However, Using FerroFET as a computation device in subarray for in-memory computing architecture has major challenge. Since the increase in conductance level with respect to the amplitude of write pulse to the gate of FerroFET is non-linear, the output of analog multiplication(current across FerroFET, the product of conductance and voltage across FerroFET) contains error. Also, when analog multiplication output is transferred to digital domain by using Analog to Digital Converter(ADC), quantization errors from ADC will exacerbate the error. Therefore, in order to implement FerroFET based in-memory computing architecture, we must quantify the effect of these limitations of FerroFET on system performance and present the device requirements that enables in-memory computing architecture.

#### Challenges of STT-MRAM based system for reinforcement learning on a drone

Over the past decade, there has been considerable success in using Unmanned Aerial Vehicles (UAVs) or drones in varied applications such as reconnaissance, surveying, rescuing and mapping. Irrespective of the application, navigating autonomously, particularly with camera based inputs, is one of the key desirable features for small drones, both indoors and outdoors. In recent years, reinforcement learning (RL) has been extensively explored for different type of robotic tasks, including drone navigation and collision avoidance. RL, in spite of its biomimetic approach, is computationally challenging [55][56]. The agent (drone) needs to collect visual data and train a neural network based model in real-time [56][57]. For a given velocity of the drone, the corresponding distance traveled between two frames ( $d_{frame}$ ), and the minimum distance between obstacles (a measure of clutter in the environment), we can calculate the minimum number of frames/second (fps) required for collision avoidance. Since the drone needs to train on acquired data at least at the same rate as the fps, the amount of computation that needs to be performed is prohibitively large for embedded systems that can be mounted on small drones. Further, the emergence of STT-MRAM [58][59][60] technologies that exhibit high-density and low-standby-power aims to disrupt the design of embedded systems. In spite of their advantages, STT-MRAM technologies shows high write latency and energy. This makes them unsuitable for storing model weights in real-time RL systems such as drones, both in terms of meeting an fps (or, velocity) requirement and energy target.

### **1.3** Key contributions of the research

In the research, we classify the challenges listed above into device, circuit, memory array and system level.

At the device level, we analyze the magnetic coupling across bit-cells of STT-MRAM and show whether this challenge prohibits the STT-MRAM memory scaling. First, we present a model of magnetic field induced coupling between adjacent bits in an STT-MRAM array. A comprehensive analysis, across four technology nodes and different MTJ technologies, has been presented and we have analyzed the role of the magnetic coupling on electrical performance, both static and dynamic. We conclude that for MTJ technologies with dense memory bits and lower stored energy, the coupling field can cause significant change in the average retention time. Data patterns that activate the worst and best case scenarios have also been explored. Dynamic analysis reveals that critical current densities are weakly disturbed by the coupling field. It should be noted that the research explores ultra-dense memory bit cells with cell sizes which are  $15F^2$  and  $6F^2$ . The state-of-the art bit-cells are significantly larger (3X larger) and effects such as magnetic coupling will be reduced. However, key observations such as the data pattern dependence of retention, will remain unchanged and as the technology matures and denser bit-cells are enabled, magnetic field induced coupling will play a key role in both design and test.

At the circuit level, we present a comprehensive test methodology that solves the retention test challenges of STT-MRAM arrays. We identify electrical defects and magnetic coupling induced data pattern dependence on tests for read, write and retention and propose an MBIST architecture (EMACS) capable of collecting statistical data in an STT-MRAM subarray to estimate the thermal stability and retention. The proposed MBIST shows 93.75% improvement in test-time compared to a brute-force approach [37] with less that 5% estimation error.

At the memory array level, we analyze the challenges of FerroFET based in-memory

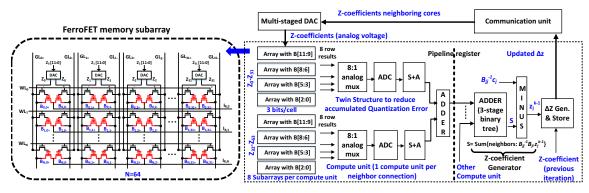

computing architecture and present a systolic processing-in-memory(PIM) architecture based on analog FerroFet pseudo-crosspoint arrays with in-situ computation to enable distributed convex optimization(non-uniform sampling) via least square minimization. The system demonstrated  $21 \times$ ,  $3 \times$  improvement in energy efficiency and compute time compared to an SRAM based Processing- In-Memory (PIM) architecture.

At the system level, we present a hardware-algorithm frame-work for STT-MRAM based embedded systems for application to small drones. we present a hardware-algorithm frame-work for STT-MRAM based embedded systems for application to small drones. We show that TL followed by RL on the last few layers of a deep CNN provides comparable performance compared to an E2E RL system, while reducing latency and energy by 79.4% and 83.45% respectively.

### **1.4 Dissertation overview**

In the next chapters, we first address the current issues of Spin-Transfer Torque Magnetic Random Access Memory(STT-MRAM) and multi-bit ferroelectric FET in the device level. At the circuit level, the research shows how these issues shape the peripheral circuit of STT-MRAM and ferroelectric FET memory arrays. Lastly, at the system level, the research leads to the efficient memory architecture and system design that maximizes the benefits of STT-MRAM and ferroelectric FET while mitigating the current limitations of these devices. Lastly, we applies the in/near memory processing system design with STT-MRAM and ferroelectric FETs to various applications such as reinforcement learning with a drone, image classification with Deep Neural Network and least square minimization for image reconstruction. we focus on near-memory processing system to quantify how much benefits are expected in terms of latency, power and energy. we would like to show that near-memory processing system with non-volatile devices is a key enabler for a real-time learning systems with stringent power and energy constraints.

### **CHAPTER 2**

### MAGNETIC COUPLING ACROSS BIT-CELLS OF STT-MRAM

In this chapter, we analyze how magnetic coupling affects both static and dynamic properties of MTJs with in-plane anisotropy,[61] Bulk perpendicular anisotropy[62] and interface induced perpendicular anisotropy [63] across different technology nodes. In modeling section, we present a compact model of MTJs and show the effect of magnetic field coupling as a function of MTJ dimensions and spacings. Then the data pattern dependence of magnetic coupling is analyzed in a  $3 \times 3$  array and the worst case data pattern for each of the MTJ stacks is discussed. In the analysis section, we present how static properties ( $\Delta$ ,  $\tau$ ) are affected by different scenarios of magnetic field induced coupling.

### 2.1 Modeling of STT-MRAM and external magnetic field

### 2.1.1 MTJ physical dimension modeling

From [62][64], dimensions of in-plane, bulk and interface-induced perpendicular MTJ are retrieved. For more details on the three types on MTJs and their relative merits/demerits and role in the technology development, interested readers are pointed to [65][26][66][67]. in-plane MTJ (IMTJ) is modeled as an elliptical pillar and perpendicular MTJs (PMTJ) are modeled as cylinders.

Fig. 2.1 illustrates the physical dimensions of in-plane and perpendicular MTJ cells. In Fig.2.1  $t_f$ ,  $t_{sp}$  and  $t_{fix}$  represent thickness of free layer, insulating layer and fixed layer respectively. Length of in-plane MTJ is determined by the product of aspect ratio (AR) and the width of the in-plane MTJ. Since aspect ratio is one of the factors that determines  $H_k$  and thermal stability, its value changes with target thermal stability. In order to observe how magnetic coupling of MTJ cell array change with respect to technology node, we scale

*Figure 2.1:* (a) In-plane MTJ (b) Perpendicular MTJ Physical dimensions of MTJ cell types. The perpendicular MTJ can be Bulk or Interface perpendicular MTJ

physical dimensions of MTJs. Table2.1 shows physical dimensions at different technology node. Saturation magnetization remains constant in all the technology nodes. Similar to aspect ratio in IMTJ, free layer thickness ( $t_f$ ) of Interface PMTJ is also an important design variable that determines thermal stability. Therefore, AR and  $t_f$  are scaled appropriately to maintain a constant thermal stability in all the technology nodes. From [62][29], device parameters of Table 2.1 were chosen.

| Cell type      | Dimension        | Technology node(nm)         |      |      |      |

|----------------|------------------|-----------------------------|------|------|------|

|                | Parameter(nm)    | 22nm                        | 16nm | 10nm | 7nm  |

| IMTJ           | width            | 50                          | 35   | 24.5 | 17.2 |

|                | length           | AR*width                    |      |      |      |

|                | t <sub>f</sub>   | 3                           |      |      |      |

|                | t <sub>fix</sub> | 5                           |      |      |      |

|                | t <sub>sp</sub>  | 1.2                         |      |      |      |

| Bulk PMTJ      | diameter         | 40                          | 28   | 19.6 | 13.7 |

|                | t <sub>f</sub>   | 3                           |      |      |      |

|                | t <sub>fix</sub> | 5                           |      |      |      |

|                | t <sub>sp</sub>  | 1.2                         |      |      |      |

| Interface PMTJ | diameter         | 40                          | 28   | 19.6 | 13.7 |

|                | t <sub>f</sub>   | variable dependent on delta |      |      |      |

|                | t <sub>fix</sub> | 3                           |      |      |      |

|                | t <sub>sp</sub>  | 0.9                         |      |      |      |

Table 2.1: Physical dimensions of MTJ in STT-MRAM bit-cells across technology generations

#### 2.1.2 Modeling the H field

The magnetic field of a single MTJ is first modeled to observe the net magnetic field coupling between adjacent cells. In an STT-MRAM array we consider a cell in the center of a  $3 \times 3$  lattice as the victim cell and the eight neighbors as aggressors. Under the assumption of uniform magnetization of the the MTJ material, the magnetic dipoles inside MTJs cancel out and finally the magnetic dipoles on the edges of the MTJ are unpaired.

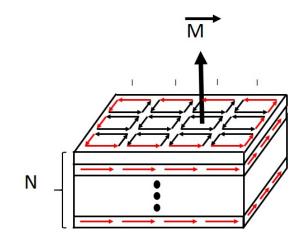

Figure 2.2: Schematic representation of current loops in the nanomagnet

Magnetic dipoles can be in turn modeled as current loops following[68]. Fig. 2.2shows how magnetic dipoles inside an MTJ cancels each other's internal current loops [68]. Hence we model an MTJ as a solenoid which has bound current paths wrapped around itself to produce the saturation magnetization ( $M_s$ ) of an MTJ as described in [62].

Since magnetic moment is derived from the volume and  $M_s$  of an MTJ ( $M_s = \frac{Magnetic moment}{Volume of MTJ}$ ) and it is the product of the bound current, the cross sectional area of the MTJ and the number of coils, the amount of current needed to produce the magnetic field can be calculated. The current is expressed as  $\frac{M_s t}{no.of coils}$ , t is the thickness of an MTJ layer.

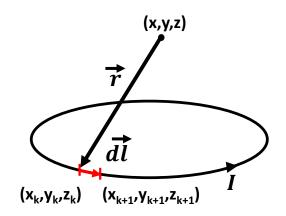

Fig. 2.3 shows the IMTJ and PMTJ with the corresponding solenoid model for evaluating the resultant magnetic field. The current loop around an MTJ is wrapped around in a direction that generates the net  $M_s$ . Finally, we can calculate the magnetic field at any specific point in space by applying the Biot-Savart law [68], as:

(a) Solenoid modeling of free and fixed layer of(b) Solenoid modeling of free and fixed layer of IMTJ PMTJ

*Figure 2.3: Solenoid representation of current loops in IMTJ and PMTJ to model magnetic field around MTJs*

Figure 2.4: Finite element representation of biot savart law

$$\vec{H}(x,y,z) = \frac{I}{4\pi} \int_{C} \frac{d\vec{l} \times \vec{r}}{|\vec{r}|^{3}}$$

(2.1)

where,  $d\vec{l}$  is defined by  $\{d\vec{x}, d\vec{y}, d\vec{z}\}$ , which is equal to  $\{\vec{x}_{k+1} - \vec{x}_k, \vec{y}_{k+1} - \vec{y}_k, \vec{z}_{k+1} - \vec{z}_k\}$  from Fig.2.4.

Algorithm. 2 shows the pseudo-code for a discrete finite element representation of Biotsavart law, which is used to calculate magnetic field at coordinate (x,y,z). For each segment in the model, Algorithm. 2 computes dHx,dHy and dHz, x,y,z components of  $d\vec{l} \times \vec{r}$ , and stores it in an array. After computing  $d\vec{l} \times \vec{r}$  for all segments, we can find the magnetic field in x,y,z direction at point (x,y,z) by summing up dHx, dHy and dHz and multiplying by the coefficient  $\frac{I}{4\pi}$

**Result:** Calculate H<sub>stray</sub> from MTJs at coordinate (x,y,z) N = number of points in MTJ model;  $x_{p}[N] = array of x$ -coordinates of MTJ model; y<sub>p</sub>[N] = array of y-coordinates of MTJ model;  $z_{p}[N] = array of z$ -coordinates of MTJ model; **for** *k* = 1; *k* <*N*-1; *k*++ **do**  $r_mag = sqrt((x-x_p[k])^2 + (y-y_p[k])^2 + (z-z_p[k])^2);$  $dx[k] = x_p[k+1] - x_p[k];$  $dy[k] = y_p[k+1] - y_p[k];$  $dz[k] = z_p[k+1]-z_p[k];$  $dHx[k] = (dy[k]*(z-z_p[k])-dz[k]*(y-y_p[k]))/(r_mag)^3;$  $dHy[k] = (dz[k]*(x-x_p[k])-dx[k]*(z-z_p[k]))/(r_mag)^3;$  $dHz[k] = (dx[k]*(y-y_p[k])-dy[k]*(x-x_p[k]))/(r_mag)^3;$ end Hx = (I/(4\*pi))\*sum(dHx);Hy = (I/(4\*pi))\*sum(dHy);Hz = (I/(4\*pi))\*sum(dHz);

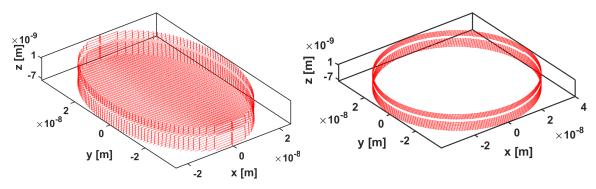

By using Biot-Savart law and finite element method as above, we find magnetic field at a set of coordinates in 3D space and Fig. 2.5 shows the complete magnetic field modeling for free layer of IMTJ and PMTJ in space. In Fig. 2.5, The magnetic field direction between Fig. 2.5(a) and Fig. 2.5(b), Fig. 2.5(c) and Fig. 2.5(d) are opposite to each other because direction of bound current into the coil is opposite.

We expect that the magnetic coupling between aggressor cells and a victim cell would be affected by the distance between the cells 2.1. In order to observe the difference in  $\vec{H}$ with respect to distance between cells, we consider two types of MTJ cells: (1) a nominal cell of size  $5F \times 3F$  and (2) a compact cell size as  $3F \times 2F$ . Here F is the half-pitch of the poly-silicon layer for a given technology node.

Fig. 2.6 shows the nominal and compact cells in array configurations. The MTJ at the center of an array in Fig. 2.6 is the victim MTJ and distance labeled in Fig. 2.6 is the center to center distance between the victim cell and its aggressor neighboring cells. For each cell, we model the net magnetic field generated by both the free layer and the fixed layers. Then

(b) Magnetic field around IMTJ diverging to -y direction

*PMTJ diverging to +z direction*

(d) Magnetic field around PMTJ diverging to -z direction

Figure 2.5: Magnetic field around IMTJ and PMTJ when current is applied to current loops.(a) current flowing from +y to -y direction (b) current flowing from -y to +y direction (c) current flowing from -z to +z direction (d) current flowing from +z to -z direction

we calculate the net magnetic field from each MTJ and compute the total magnetic field at the victim node. Although the fixed layer has its magnetic moment pointing in a specific direction, the direction of the magnetic moment in the free layer is data dependent. Hence, the net field generated by the neighboring cells on the victim, depends on the over-all data pattern of the  $3 \times 3$  array. In the next section, we explore the effect of data pattern on the

*Figure 2.6: (a) IMTJ default cell array (b) IMTJ compact cell array (c) PMTJ normal default array (d) PMTJ compact cell array*

coupling field on the victim node and determine the worst and best data patterns that can reduce magnetic coupling. It should be noted that our discussion in this paper is limited to the nanomagnet. The access transistor in the bit-cell plays an important role in the cell dynamics[69][70], especially the write properties. The retention properties of the cell are not disturbed by the access transistor, at least to the first order. However, the aim of this paper is to explore the performance and retention behavior of bit-cells with and without magnetic coupling from the neighboring cells. Hence, we have not considered the role of the access transistor in our discussions.

### 2.2 Role of Magnetic coupling in dense arrays

(a) IMTJ Figure 2.8: Magnetic field visualization of IMTJ and PMTJ  $3 \times 3$  arrays for the worst data pattern[71]