# Design of Process and Environment Adaptive Ultra-Low Power Wireless Circuits and Systems

A Doctoral Dissertation Presented to The Academic Faculty

By

**Shreyas Sen**

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology December, 2011

Copyright © 2011 by Shreyas Sen

# Design of Process and Environment Adaptive Ultra-Low Power Wireless Circuits and Systems

#### Approved by:

Dr. Abhijit Chatterjee, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. David Keezer School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Bonnie Heck Ferri School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Satish Kumar School of Mechanical Engineering Georgia Institute of Technology

Date Approved: August 15, 2011

#### **ACKNOWLEDGEMENTS**

First and foremost I would like to express my heartfelt gratitude to my research advisor Prof. Abhijit Chatterjee, without whom I would not have been here. I thank him for his able guidance in my research and for his advice and support on other aspects which have helped me immensely. I'm thankful for all the discussions we've had over last five years. He is one of the most wonderful human being I've ever met. PhD under him seemed like a journey that I enjoyed from the core of my heart. He was always there in every step of my way advising me towards the right direction as I grew as a researcher and as a human being. I sincerely thank him for that.

I take this opportunity to thank faculty members, Prof. Bonnie H. Ferri, Prof. David Keezer, Prof. Saibal Mukhopadhyay and Prof. Satish Kumar for agreeing to serve on my committee and offering valuable suggestions and recommendations. I would also like to thank Prof. Linda Milor for serving on my proposal committee. I would like to thank Semiconductor Research Corporation (SRC), Gigascale Systems Research Center (GSRC), and National Science Foundation (NSF) for the support during various stages of my graduate studies at Georgia Tech. I thank Intel Corporation and IEEE Microwave Theory and Techniques Society for the encouragement and motivation they provided through the graduate fellowship programs. I am grateful to Dr. Marian Verhelst, my industry mentor during the Intel PhD Fellowship, for helping me thoroughly in issues of research and otherwise during the final phase of my PhD.

I'm extremely grateful to my mother Mrs. Suprity Sen and my father Mr. Dilip Kumar Sen for their countless sacrifices, unconditional love and their unshakable trust. I

have always found strength and encouragement in their love and support. I owe everything to them. My dream of being a PhD was partially intertied from my mother, who could do anything for my well-being and my studies. I remember all those countless nights that you were awake during my school days just so that I do not feel lonely while I study. I could never forget you giving up your job to give me more time and make me a better human being. You have always been there for me. I developed my desire for excellence and knowledge from you. You taught me how to be honest, hardworking and righteous while striving for excellence. Mom, I dedicate my PhD to you.

There has been one other person without whom I would not have been in a PhD, at least not this soon in my life. I would like to thank Prof. Kausik Chatterjee for showing me the beauty of doctoral research during my undergraduate studies. I thank him for walking me through the ins and outs of graduate studies in USA, the application and admission process and mainly for helping me develop the thirst for research at a very early age.

From my undergraduate days at Jadavpur University, I would like to thank Prof. Debidas Mukhopadhyay for making me interested in semiconductor device physics. I thank Prof. Amit Konar for teaching me how to think out of the box in research and Prof. Tarun Kanti Bhattacharyya (IIT Kharagpur) and Prof. Navakanta Bhatt (IISC Bangalore) for allowing me to be exposed to cutting edge research facilities during my undergraduate, which fascinated me and helped me decide that I want to do a PhD. From my graduate studies, I would especially like to thank Prof. Gabriel A. Rincon-Mora and Prof. Paul Hasler for teaching us how beautiful, intuitive and fun analog IC design could be.

I would like to thank Prof. Saibal Mukhopadhyay, Dr. Arijit Raychowdhury and Dr. Soumendu Bhattacharyya for their guidance during the initial phases of my PhD. The excellent work you did in your PhD have always served as a motivation to me.

I sincerely appreciate what I learnt from Dr. Susanta Sengupta, Harish Muthali and Manas Behera during my internship in Qualcomm Inc. and from Dr. Farshid Aryanfar during my internship in Rambus Inc. The experience on real world IC design that I gathered from you helped me a lot in my doctoral research.

I'm thankful for the professional and personal support I received from my colleagues in our research group over the years. I thank Soumendu Bhattacharya, Donghoon Han, Ganesh Srinivasan, Selim Sermet Akbay, Rajarajan Senguttuvan, Vishwanath Natarajan, Hyun Choi, Mudassar Nisar, Sehun Kook, Shyam Kumar Devarakond, Jayaram Natarajan, Aritra Banerjee, Debashis Banerjee, and Joshua Wells for their wonderful company. I was lucky to cross paths with many interesting people who have enriched my life through the years at Georgia Tech.

I made some great friends at Georgia Tech and in Atlanta. Without them last five years of my life would have been colorless. I thank Debrup Das, Ananda Barua, Ayan Chakrabarti, Payel Chatterjee, Subho Chatterjee, Prabir Saha, Atri Dutta, Mrinmoy Ghosh, Saikat Sarkar, Payel Paul, Padmanava Sen, Tapobrata Bandyopadhyay, Priya Kundu, Koushik Kundu and Gopal Jha, whose constant company has kept me afloat all along my journey. Your friendship means a lot to me.

Finally, I would also like to thank Seetharam Narasimhan and Angik Sarkar for all his support and friendship. You have always been there through my ups and downs.

## TABLE OF CONTENTS

| ACKNOWL     | EDGEMENTS                                                 | IV   |

|-------------|-----------------------------------------------------------|------|

| LIST OF TA  | BLES                                                      | XII  |

| LIST OF FIG | GURES                                                     | XIII |

| SUMMARY     |                                                           | XX   |

| CHAPTER 1   | . INTRODUCTION                                            | 1    |

| 1.1. OF     | RIGIN AND HISTORY OF THE PROBLEM                          | 2    |

| 1.2. CC     | ONVENTIONAL WIRELESS SYSTEMS                              | 3    |

| 1.3. NE     | EED FOR ENVIRONMENT AND PROCESS ADAPTIVE WIRELESS         |      |

| SYSTEMS     | S                                                         | 3    |

| 1.3.1.      | Low Power Requirements in Wireless/Portable Systems       | 3    |

| 1.3.2.      | Process Variation in Mixed Signal Circuits and Yield Loss | 4    |

| 1.4. PR     | IOR WORK IN ADAPTIVE WIRELESS SYSTEMS                     | 5    |

| 1.4.1.      | Adaptivity in Low Noise Amplifiers (LNA)                  | 5    |

| 1.4.2.      | Adaptivity in Power Amplifiers (PA)                       | 6    |

| 1.4.3.      | Adaptivity in Analog to Digital Converters (ADC)          | 9    |

| 1.4.4.      | System Level Adaptivity in Transceivers                   | 10   |

| CHAPTER 2   | . DESIGN FOR PROCESS VARIATION TOLERANCE                  | 12   |

| 2.1. PR     | OBLEMS WITH PROCESS VARIATION: YIELD LOSS                 | 12   |

| 2.2. CI     | RCUIT LEVEL APPROACH: A SELF-HEALING LNA EXAMPLE          | 12   |

| 2.2.1.      | Minimal Intrusion Sensing                                 | 13   |

| 2.2.2.      | Non-Intrusive Mixing                                      | 15   |

| 2.2.3.      | Process Variation Tolerant LNA                            | 16   |

| 2.2.4.      | Yield recovery through process variation tolerant LNA     | 17   |

| 2.3. SY   | STEM LEVEL APPROACH                                           | 19  |

|-----------|---------------------------------------------------------------|-----|

| 2.3.1.    | Effect of Process Variation and Built in Tunability           | 19  |

| 2.3.2.    | System Level Healing Framework                                | 21  |

| 2.3.3.    | Need for Process Identification through testing               | 22  |

| CHAPTER 3 | LOW COST TESTING FOR IDENTIFICATION OF PROCESS-               |     |

| VARIATION | V                                                             | 24  |

| 3.1. PR   | EVIOUS WORK                                                   | 24  |

| 3.1.1.    | Alternate Testing                                             | 24  |

| 3.1.2.    | Need for Phase Distortion Testing                             | 26  |

| 3.1.3.    | AM-AM & AM-PM and its Effect on Communication Systems         | 28  |

| 3.2. LC   | W COST TESTING FOR PHASE DISTORTION                           | 31  |

| 3.2.1.    | Phase to Amplitude Transformation: Basics                     | 31  |

| 3.2.2.    | AM-AM & AM-PM Measurement Using Phase to Amplitude Conversion | 33  |

| 3.2.3.    | Single Setup AM-AM & AM-PM Measurement                        | 41  |

| 3.2.4.    | Experimental Validation                                       | 54  |

| 3.3. AM   | MPLITUDE AND PHASE DISTORTION FROM SINGLE DATA                |     |

| ACQUISI   | ΓΙΟΝ                                                          | 57  |

| 3.3.1.    | AM-AM and AM-PM from AM Stimulus                              | 57  |

| 3.3.2.    | Implementation                                                | 60  |

| 3.3.3.    | Experimental Setup and Results                                | 62  |

| 3.3.4.    | Discussions about Low-Cost Phase Distortion Testing           | 65  |

| 3.4. IQ   | MISMATCH MEASUREMENT AND COMPENSATION                         | 69  |

| 3.4.1.    | Transmitter IQ Imbalance Measurement                          | 70  |

| 3.4.2.    | Receiver IQ Imbalance Measurement                             | 71  |

| 3.4.3.    | DSP Assisted IQ Mismatch Compensation                         | 72  |

| 3.4.4.    | Experimental Validation                                       | 73  |

| 3.5. BI   | ST/DIGITAL COMPATIBLE DISTORTION MODEL EXTRACTION             |     |

| DRIVENT   | FESTING OF DE DEVICES                                         | 7.4 |

| 3.5.1.     | Distortion Model based Testing using Modulated RF Stimulus           | 76  |

|------------|----------------------------------------------------------------------|-----|

| 3.5.2.     | Digital/BIST Compatible Distortion Model based Testing using Digital |     |

| Pulse Sec  | juences                                                              | 86  |

| 3.5.3.     | Hardware Validation                                                  | 95  |

| 3.5.4.     | Discussions                                                          | 98  |

| CHAPTER 4. | ENVIRONMENT-ADAPTIVE ZERO MARGIN LOW-POWER                           |     |

|            | RANSMITTERS                                                          | 101 |

|            |                                                                      |     |

|            | VIOUS WORK                                                           |     |

| 4.1.1.     | Background                                                           |     |

|            | APTATION FRAMEWORK                                                   |     |

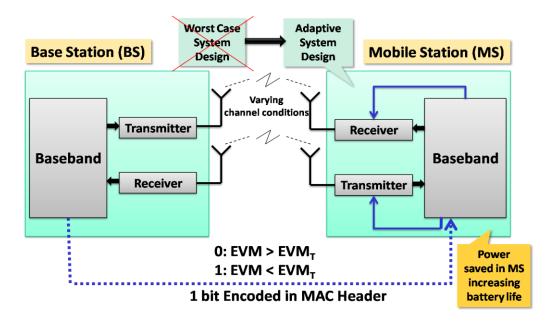

| 4.3. CHA   | ANNEL QUALITY ESTIMATION AND FEEDBACK                                | 109 |

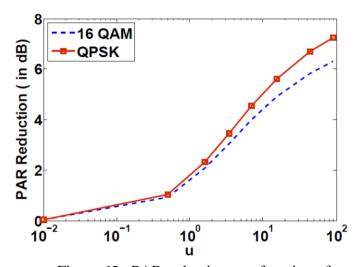

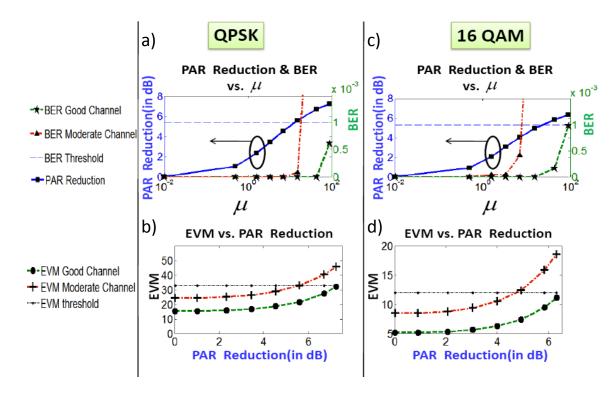

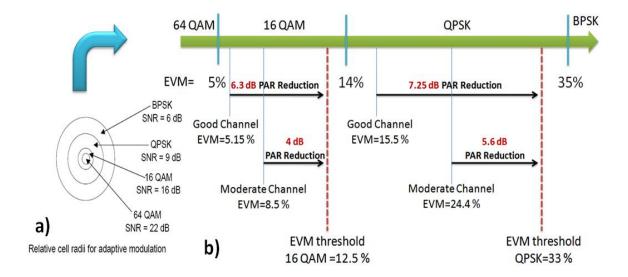

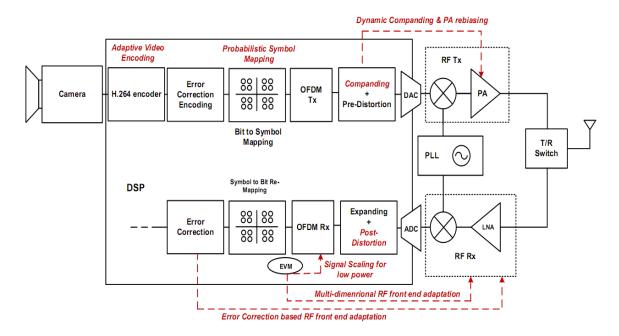

| 4.4. ENV   | VIRONMENT DEPENDENT PAR REDUCTION                                    | 111 |

| 4.4.1.     | Traditional Static PAR reduction techniques                          | 112 |

| 4.4.2.     | Adaptive PAR reduction                                               | 113 |

| 4.4.3.     | Radio Link Quality                                                   | 114 |

| 4.4.4.     | Maximum Achievable PAR reduction under different environmental       |     |

| condition  | s                                                                    | 115 |

| 4.4.5.     | PAR Reduction: A closer look                                         | 119 |

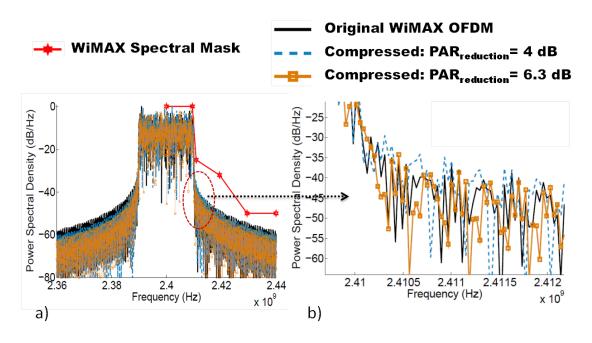

| 4.4.6.     | Out of band emission characterization                                | 121 |

| 4.5. ADA   | APTIVE POWER AMPLIFIER                                               | 122 |

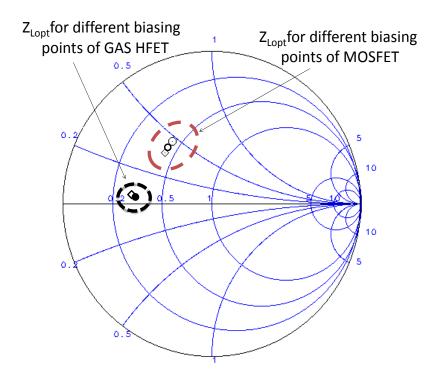

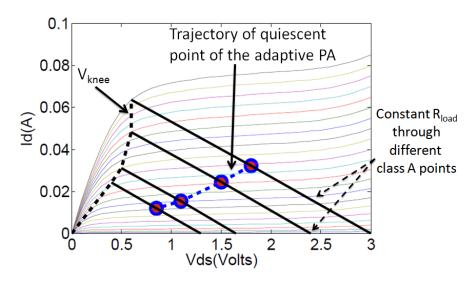

| 4.5.1.     | Adaptivity of Power Amplifiers                                       | 122 |

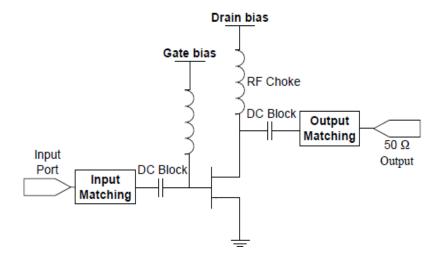

| 4.5.2.     | Adaptive CMOS PA Design                                              | 123 |

| 4.5.3.     | Power savings                                                        | 124 |

| 4.6. HAI   | RDWARE VALIDATION                                                    | 127 |

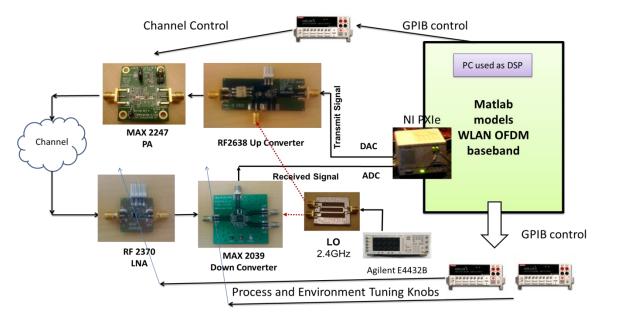

| 4.6.1.     | Experimental Setup                                                   | 127 |

| 4.6.2.     | Results                                                              | 128 |

| 463        | Discussions and Summary                                              | 131 |

### CHAPTER 5. ENVIRONMENT ADAPTIVE VIRTUALLY ZERO MARGIN

| LOW POWI | ER RF (VIZOR) RECEIVER SYSTEMS                            | 133 |

|----------|-----------------------------------------------------------|-----|

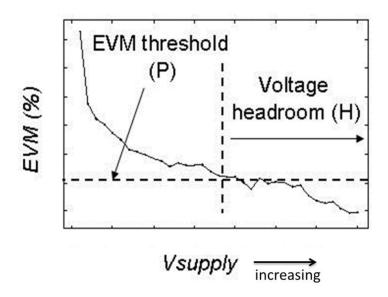

| 5.1. VI  | ZOR RECEIVER                                              | 137 |

| 5.1.1.   | Low Power Adaptation Framework                            | 137 |

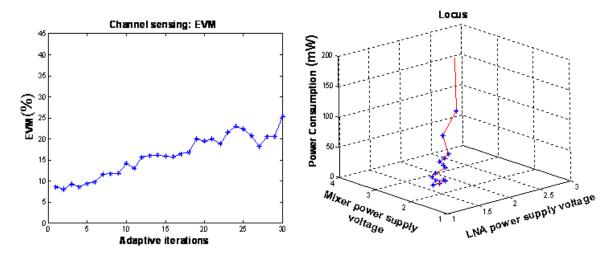

| 5.1.2.   | A Suitable Adaptation Metric: EVM                         | 139 |

| 5.1.3.   | Adaptive Receiver Design Framework                        | 143 |

| 5.1.4.   | Design Phase Optimization                                 | 144 |

| 5.1.5.   | Run Time Operation of the Device                          | 146 |

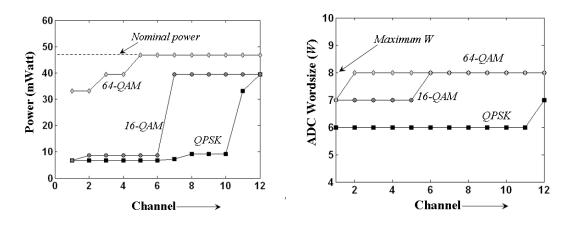

| 5.1.6.   | Power Savings through Receiver Adaptation                 | 147 |

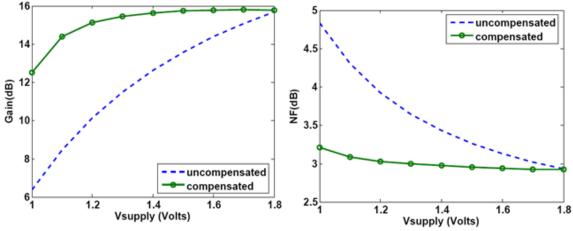

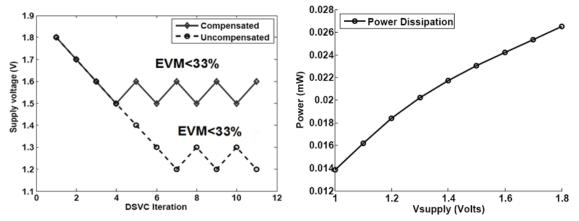

| 5.1.7.   | Extra Power Savings through Adaptive Biasing for DSVC     | 149 |

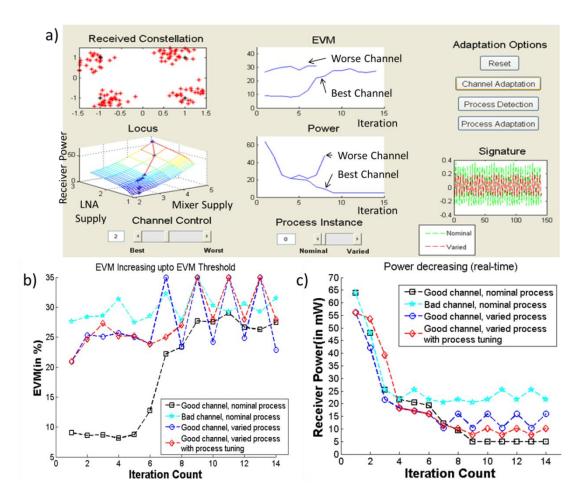

| 5.1.8.   | Live Demonstration: VIZOR Receiver                        | 155 |

| 5.2. BU  | JILT-IN ORTHOGONAL TUNABILITY FOR OPTIMAL ADAPTATION      | 157 |

| 5.2.1.   | Need for Orthogonal/Independent Tunability in RF Circuits | 158 |

| 5.2.2.   | Inductorless LNA                                          | 160 |

| 5.2.3.   | Design of Orthogonal Tuning Knobs                         | 164 |

| 5.2.4.   | Results: Orthogonally Tunable RF LNA                      | 168 |

| 5.2.5.   | Adaptive Receiver with Orthogonally Tunable LNA           | 173 |

| 5.3. LC  | OW-POWER JAMMER DETECTOR FOR ADAPTATION TO CHANNEL        |     |

| BLOCKE   | RS                                                        | 180 |

| 5.3.1.   | Need for Receiver Adaptation to Jammer                    | 180 |

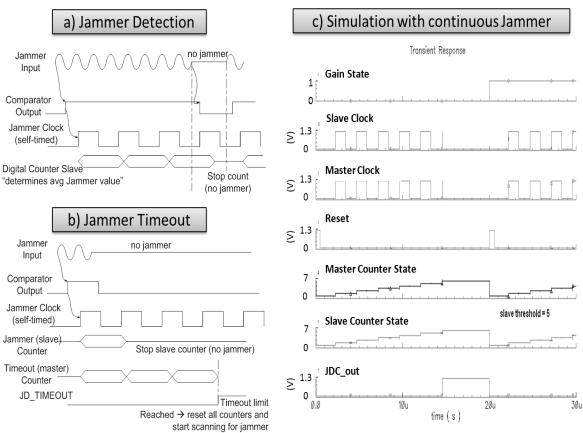

| 5.3.2.   | Background and Overview of Jammer Detector                | 182 |

| 5.3.3.   | Motivation & Working Principle                            | 183 |

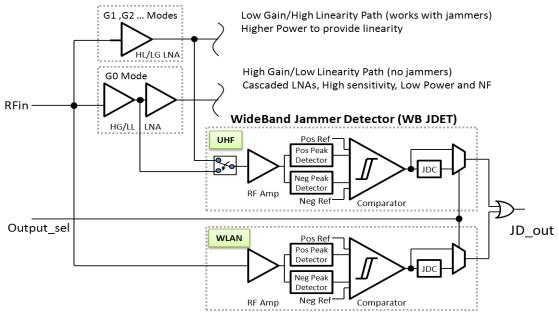

| 5.3.4.   | WBJD Architecture & Circuit Design                        | 184 |

| 5.3.5.   | Fabricated Chip and Measurement Results                   | 191 |

| 5.4. VI  | ZOR RECEIVERS FOR MULTIPLE INPUT MULTIPLE OUTPUT (MIMO)   |     |

| SYSTEMS  | S                                                         | 194 |

| 5.4.1.   | MIMO: Basics                                              | 194 |

| 542      | MIMO VIZOR                                                | 196 |

| 5.4    | .3.           | Extra Power Saving using MIMO VIZOR Mode       | 197 |

|--------|---------------|------------------------------------------------|-----|

| CHAPTI | ER 6.         | PRO-VIZOR: PROCESS VARIATION TOLERANT VIZOR    | 200 |

| 6.1.   | COI           | MPONENTS OF PROCESS TOLERANT VIZOR (PRO-VIZOR) | 201 |

| 6.2.   | PRO           | OCESS SENSING USING TEST                       | 202 |

| 6.3.   | LOV           | W POWER ADAPTATION UNDER PROCESS VARIATION     | 206 |

| 6.4.   | LOV           | W POWER ADAPTATION UNDER PROCESS VARIATION     | 208 |

| 6.5.   | EXI           | PERIMENTAL VALIDATION                          | 209 |

| 6.5    | .1.           | System Implementation of Adaptive Receiver     | 209 |

| 6.5    | .2.           | Results: Pro-VIZOR Live Demonstration          | 212 |

| CHAPTI | E <b>R 7.</b> | CONCLUSIONS AND FUTURE WORK                    | 216 |

| REFERI | ENCE          | S                                              | 221 |

## LIST OF TABLES

| Table 1 Variation of parameters considered                                          | 18  |

|-------------------------------------------------------------------------------------|-----|

| Table 2 Comparison of Both LNA                                                      | 18  |

| Table 3 Maximum error in phase deviation measurement over different experiments (in |     |

| degrees)                                                                            | 68  |

| Table 4 Error value for different input test stimulus                               | 94  |

| Table 5 Hardware measurement results                                                | 98  |

| Table 6: Channel Definition                                                         | 118 |

| Table 7: Comparison of this work with traditional methods                           | 119 |

| Table 8: Optimum load impedance with adaptive biasing                               | 122 |

| Table 9: Extra Power Savings under different channel                                | 130 |

| Table 10 Comparison with existing inductorless LNA                                  | 163 |

| Table 11 Comparison with other Jammer detectors                                     | 193 |

| Table 12 Summary of Process and Environment Adaptive Low Power Receiver             |     |

| Experimental Setup                                                                  | 211 |

## LIST OF FIGURES

| Figure 1: Feed-forward AM-PM correction using varactor tuning [28]                                                     | 8  |

|------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2: Reconfigurable ADC as a part of a wireless receiver that reduces its power                                   |    |

| consumption when interference is not high [29].                                                                        | 9  |

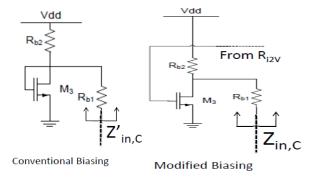

| Figure 3: a) Conventional cascoded LNA b) Minimal intrusion sensing circuit                                            | 13 |

| Figure 4: Non-intrusive mixing using modified biasing technique                                                        | 15 |

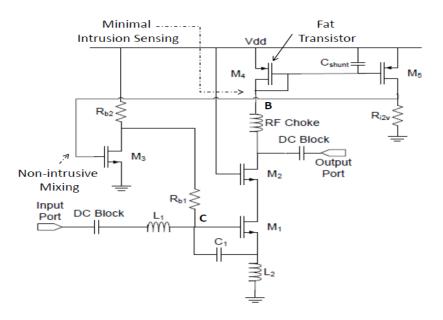

| Figure 5: Complete circuit diagram of process variation tolerant LNA                                                   | 16 |

| Figure 6 Variation of Gain, NF and S11 of the process variation tolerant LNA and                                       |    |

| conventional LNA                                                                                                       | 18 |

| Figure 7: a) $P_{out}$ vs $P_{in}$ for a PA over $V_{dd}$ variation. b) $P_{out}$ vs. $P_{in}$ over all combination of |    |

| tuning knobs (supply and bias) for 4 process instances c) Gain of a transmitter over all tuning                        |    |

| knob combinations for 2 process instances. [46]                                                                        | 20 |

| Figure 8: System Level Power Conscious Self-Healing Framework                                                          | 21 |

| Figure 9: Alternate test framework                                                                                     | 24 |

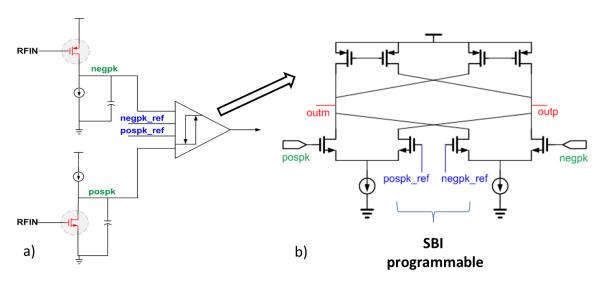

| Figure 10: Production test implementation of alternate tests                                                           | 26 |

| Figure 11: Gain Compression and Phase deviation [73]                                                                   | 28 |

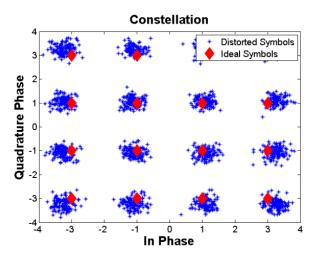

| Figure 12: Effect of AM-AM on 16 QAM OFDM: it spreads the received constellation                                       |    |

| depending on the gain compression                                                                                      | 29 |

| Figure 13: Effect of frequency independent AM-PM on 16 QAM OFDM: it rotates and                                        |    |

| spreads the received constellation; the rotation depends on the average power (refer Figure                            |    |

| 11) whereas the spread depends on the slope of phase deviation curve at the operating point                            |    |

| (S1 vs. S2 in Figure 11)                                                                                               | 29 |

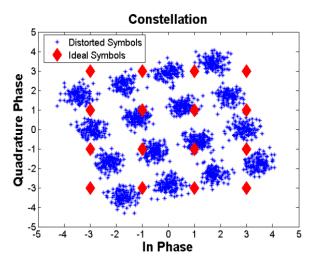

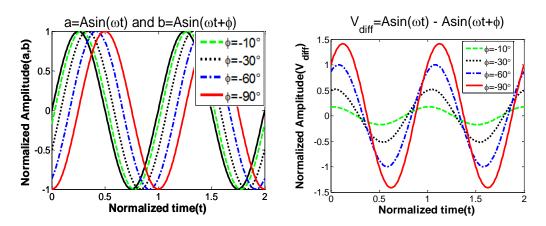

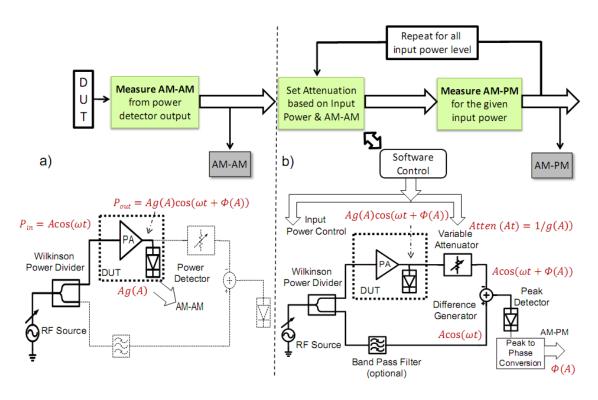

| Figure 14: a) $A\sin(\omega t)$ and $A\sin(\omega t + \phi)$ for different $\phi$ . b) Difference wave showing         |    |

| amplitude proportional to the phase difference of the two waves in a).                                                 | 33 |

| Figure 15: Block diagram two step measurement technique utilizing PAC and using RF                                     |    |

| difference generator                                                                                                   | 35 |

| Figure 16: a) Schematic of Power Amplifier used for this work b) Schematic of RF                                       |    |

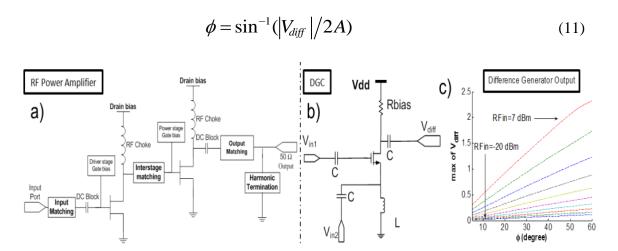

| difference generator circuit c) DGC output increases with increasing $\phi$                                            | 37 |

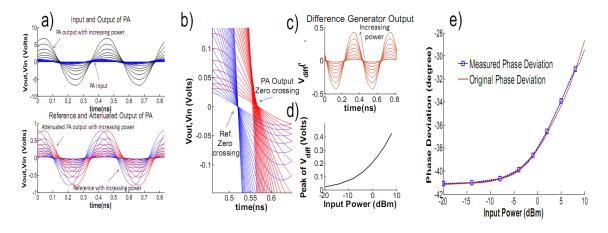

| Figure 17: a) Original PA output and Reference, normalized PA out and reference b)               |    |

|--------------------------------------------------------------------------------------------------|----|

| Zoomed in version of fig a, showing phase distortion in RF out c) difference waveform d)         |    |

| peak detector output e) Original and measured phase deviation.                                   | 39 |

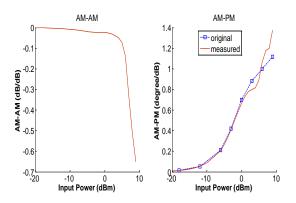

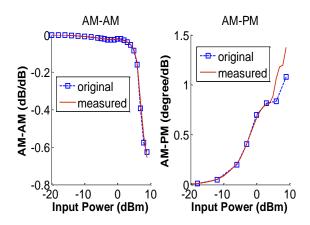

| Figure 18: a) Measured AM-AM and Measured and actual AM-PM                                       | 41 |

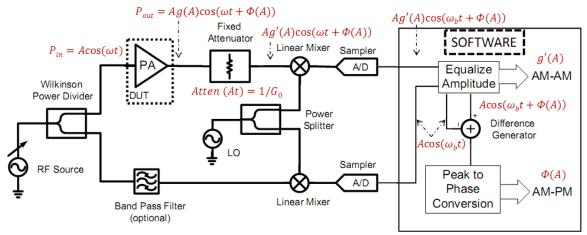

| Figure 19: Block diagram of one shot AM-AM and AM-PM measurement setup using down                |    |

| conversion and sampling                                                                          | 42 |

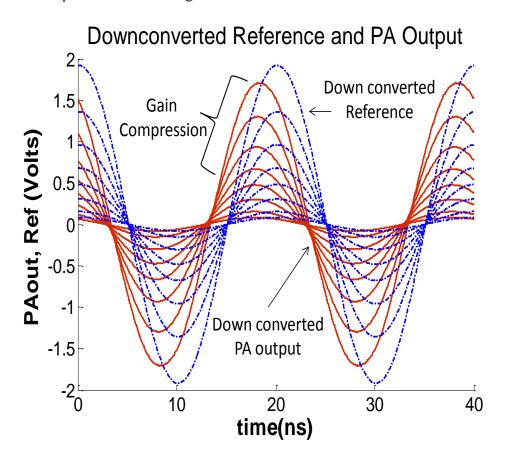

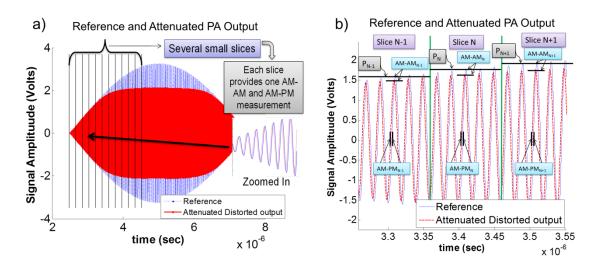

| Figure 20: Down converted PA output and reference                                                | 46 |

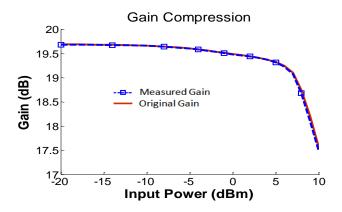

| Figure 21: Gain compression: original and measured                                               | 47 |

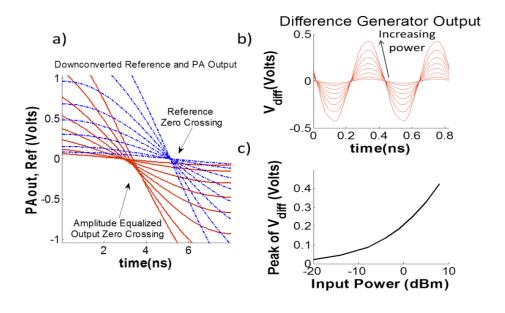

| Figure 22: a) Zoomed in version signal and reference, showing the effect of phase distortion     |    |

| in RF out zero crossings b) difference waveform c) peak detector output.                         | 48 |

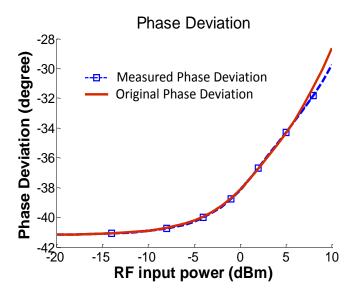

| Figure 23: Phase deviation: Original and measured                                                | 48 |

| Figure 24: a) Measured AM-AM b) Measured and actual AM-PM                                        | 49 |

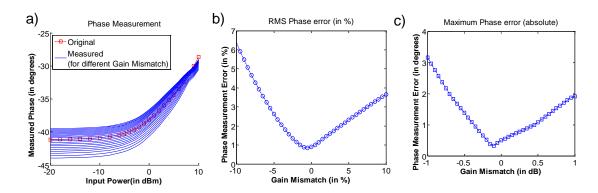

| Figure 25: a) Actual and measured Phase deviation with different amount of errors in             |    |

| compensation for gain mismatch b) RMS Phase error with Gain mismatch in % c) Absolute            |    |

| Maximum Phase measurement error ( in degree) with Gain Mismatch in dB                            | 51 |

| Figure 26: Gain adjustment for Process variation                                                 | 51 |

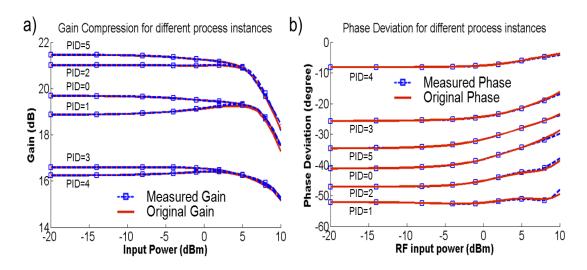

| Figure 27: a) Gain Compression b) Phase deviation for different process instances                | 53 |

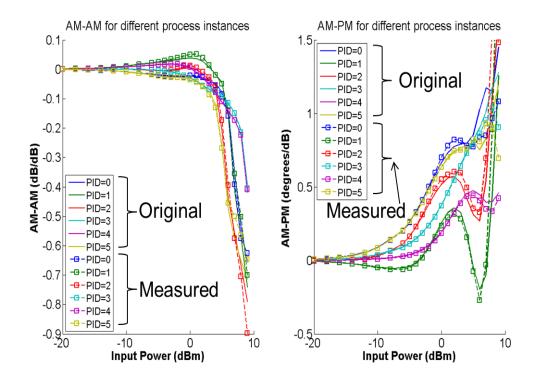

| Figure 28: AM-AM and AM-PM measured and original over 6 process instances                        | 53 |

| Figure 29: Single setup measurement setup of AM-AM and AM-PM on MAX 2247 WLAN                    |    |

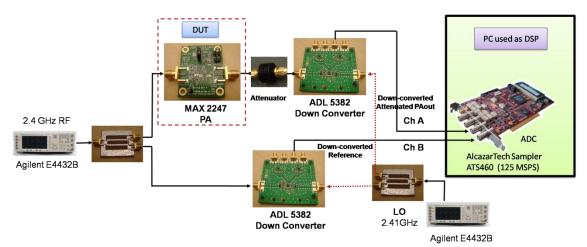

| High Power Amplifier (HPA)                                                                       | 54 |

| Figure 30: Measurement using low cost method and VNA a) Gain Compression and b)                  |    |

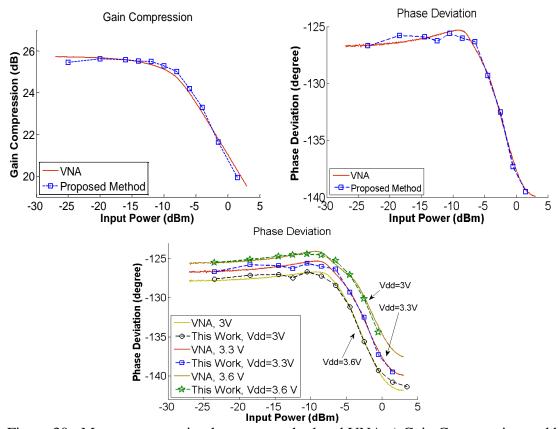

| Phase deviation measurement for MAX 2247 HPA for nominal instance c) Phase deviation             |    |

| for 3 supply voltages of the PA                                                                  | 55 |

| Figure 31: Measurement using low cost method and VNA for a) Gain Compression and b)              |    |

| Phase deviation for 2 process instances (nominal and varied) of MAX 2247 PA and c) Gain          |    |

| Compression and d) Phase deviation for RF2411 Amplifier                                          | 56 |

| Figure 32: a) One Cycle of down converted PA <sub>out</sub> and Reference b) Expanded view of a) |    |

| showing 3 slices having 5 cycles each. The average power of each cycle is taken as the           |    |

| power of that slice. The AM-AM and AM-PM provides a data point on the complete              |    |

|---------------------------------------------------------------------------------------------|----|

| distortion curve at the average power level.                                                | 57 |

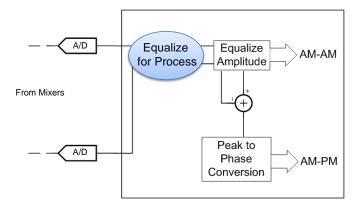

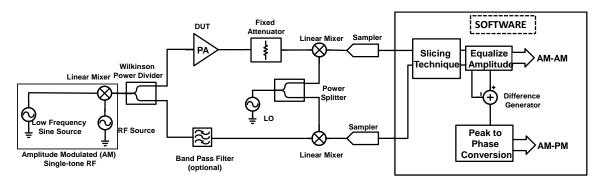

| Figure 33: Amplitude and Phase Distortion measurement setup                                 | 60 |

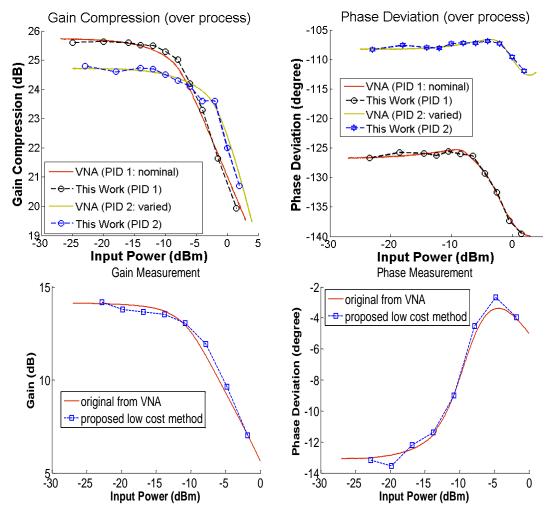

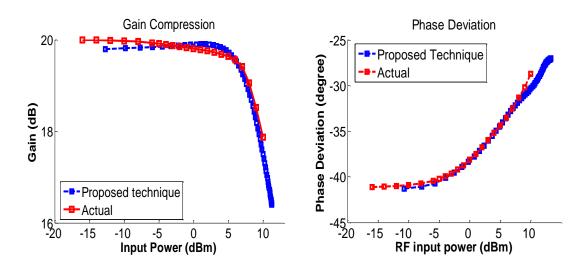

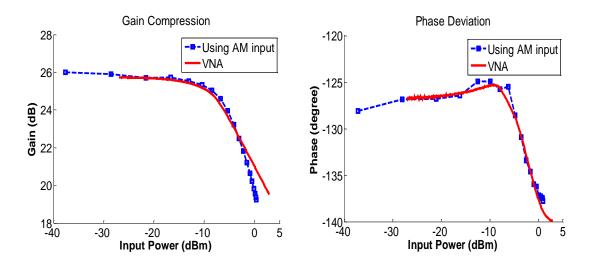

| Figure 34: Gain Compression and Phase Deviation measurement                                 | 62 |

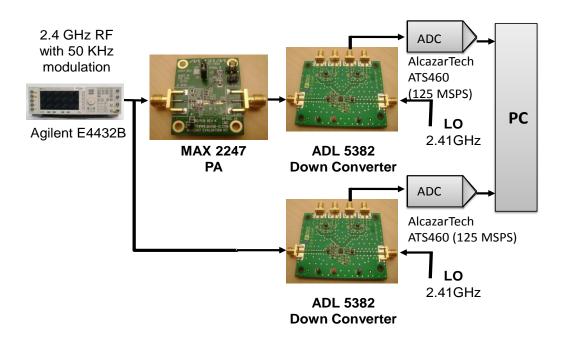

| Figure 35: Experimental setup                                                               | 64 |

| Figure 36: Comparison of a) Gain b) Phase deviation measured using single-tone AM           |    |

| stimulus without any power sweep and a standard VNA.                                        | 65 |

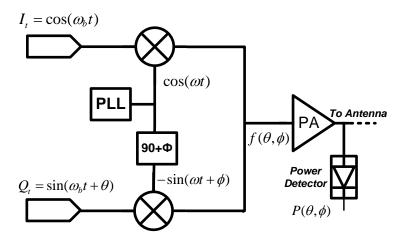

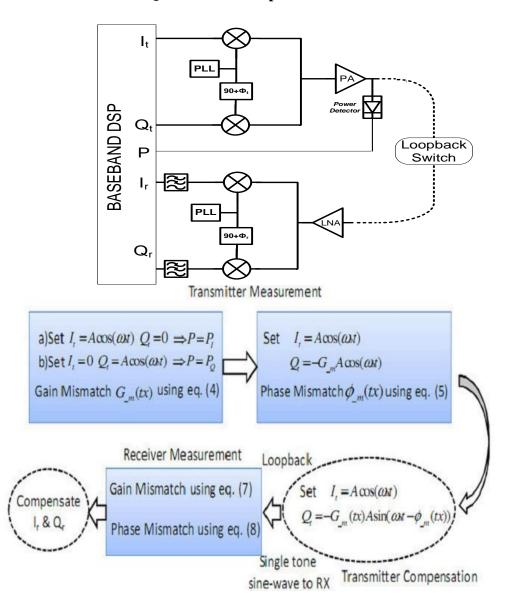

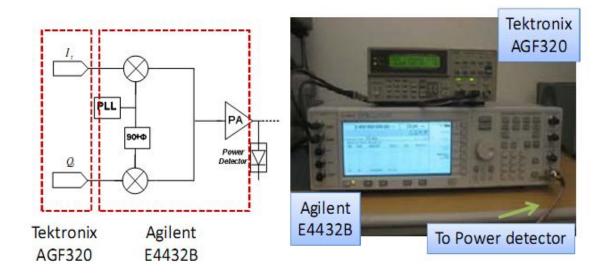

| Figure 37: IQ transmitter system with envelope detector                                     | 70 |

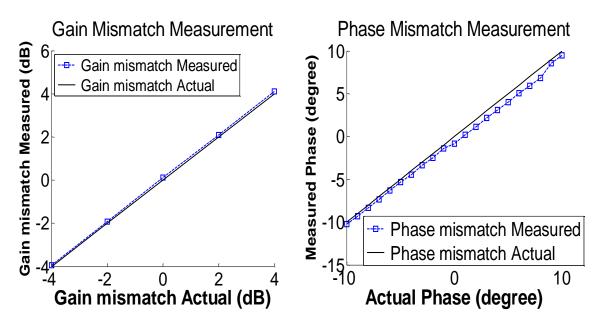

| Figure 38: IQ transmitter a) Gain mismatch measurement b) Phase mismatch for two gain       |    |

| mismatches                                                                                  | 71 |

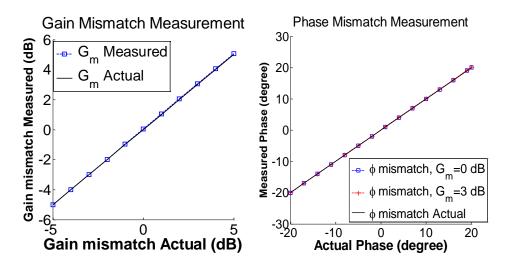

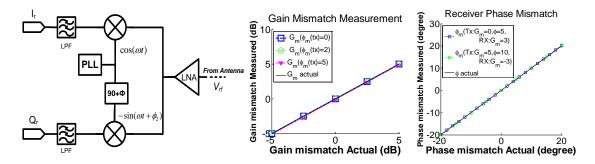

| Figure 39: a) Receiver IQ imbalance b) Gain mismatch measurement for compensated and        |    |

| uncompensated transmitter c) Phase mismatch for two sets of compensated transmitter and     |    |

| receiver parameter                                                                          | 71 |

| Figure 40: a) System block diagram with both Transmitter and Receiver with built in power   |    |

| detector b) Measurement and Compensation methodology                                        | 72 |

| Figure 41: a) Experimental Setup Measured and Actual b) Gain mismatch c) Phase mismatch     | 74 |

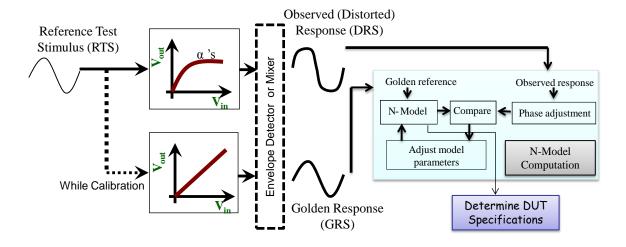

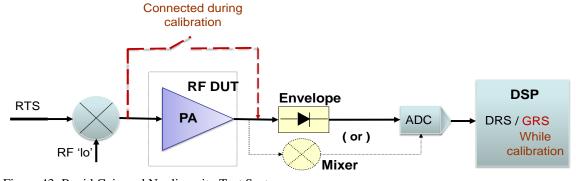

| Figure 42: Conceptual block diagram.                                                        | 76 |

| Figure 43: Rapid Gain and Nonlinearity Test System                                          | 80 |

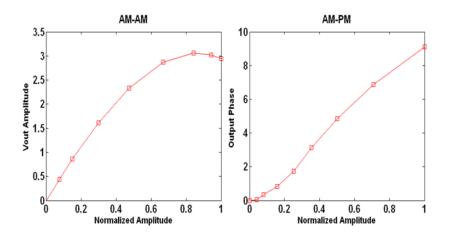

| Figure 44: AM-AM and AM-PM characteristics of the PA DUT from Agilent-ADS                   |    |

| simulations                                                                                 | 84 |

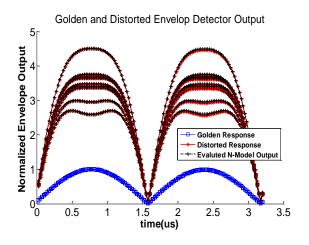

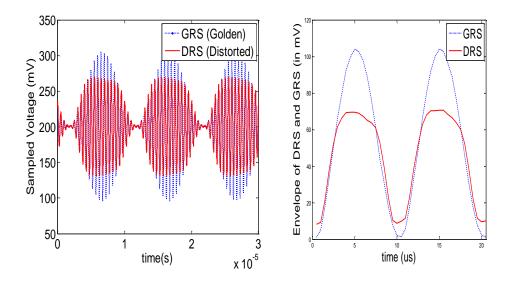

| Figure 45: DRS for several instances and GRS                                                | 84 |

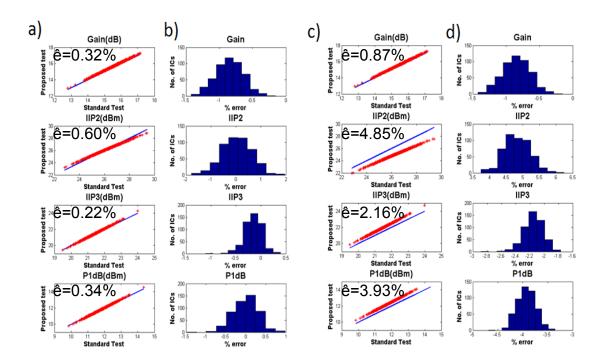

| Figure 46: Comparison of low-cost test with actual test for 500 instances a) absolute specs |    |

| (Gain, IIP2, IIP3 and P1dB), b) RMS error histogram for a, c) absolute specs without        |    |

| correction for AM-PM, d) RMS error histogram for c (ê = RMS Error in %).                    | 86 |

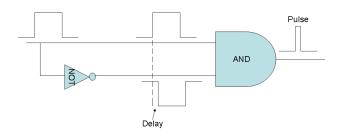

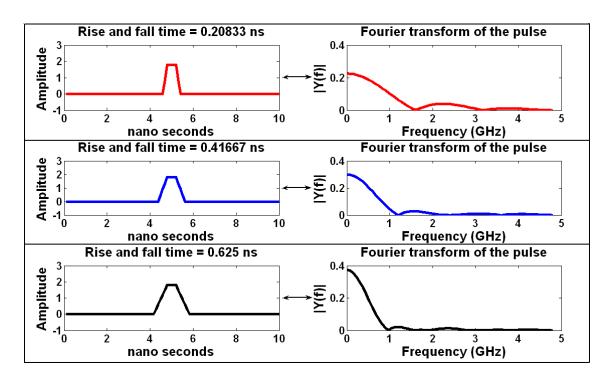

| Figure 47: Pulse generation using AND gate and inverter                                     | 88 |

| Figure 48: Pulse generation using OR gate and inverter                                      | 88 |

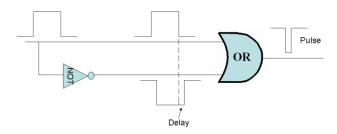

| Figure 49. Variation in frequency spectrum with change in pulse width                       | 89 |

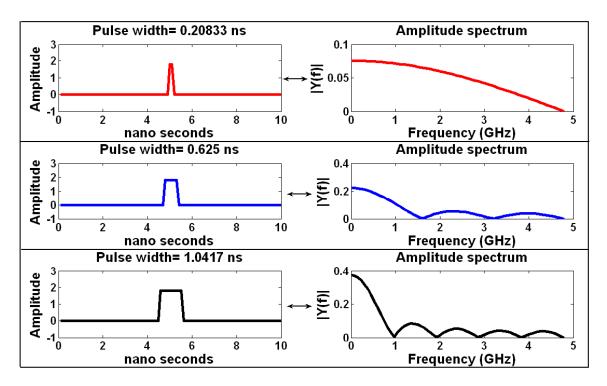

| Figure 50. Change in frequency component distribution with different rise and fall time of      |     |

|-------------------------------------------------------------------------------------------------|-----|

| the pulse                                                                                       | 90  |

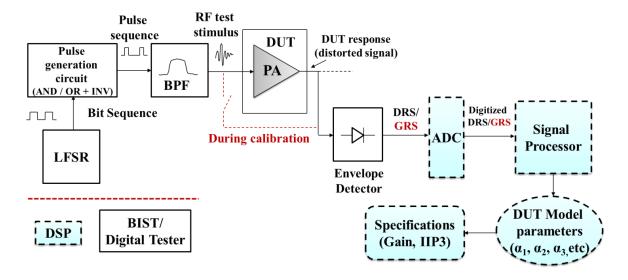

| Figure 51. Digital/BIST Compatible Test Setup                                                   | 91  |

| Figure 52. a) Frequency domain representation (FFT) of the optimized pulse sequence b)          |     |

| Band pass filtered test stimulus in freq. domain                                                | 92  |

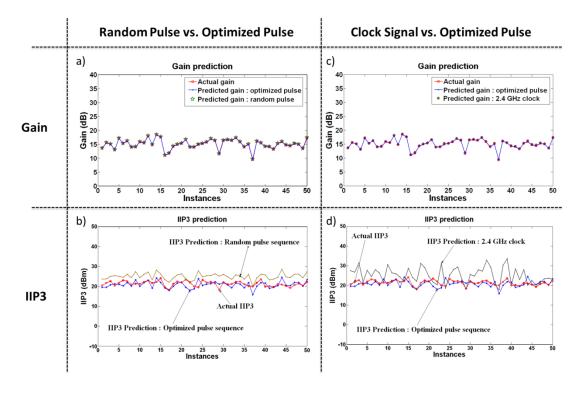

| Figure 53: Simulation results using digital stimulus for distortion model based testing a) Gain |     |

| b) IIP3 for random pulse vs. optimized pulse c) Gain d) IIP3 for clock signal vs. optimized     |     |

| pulse                                                                                           | 93  |

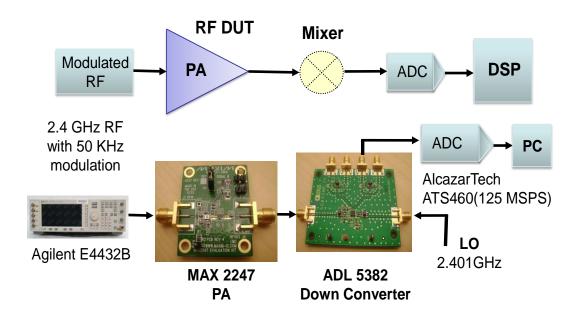

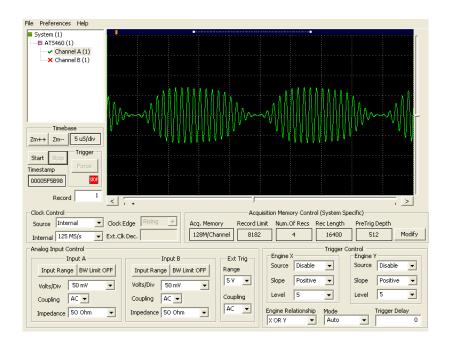

| Figure 54: Experimental setup                                                                   | 96  |

| Figure 55: Captured down converted distorted response signal using AlazarTech Sampler           | 97  |

| Figure 56: a) Measured GRS and DRS b) Envelope of both                                          | 97  |

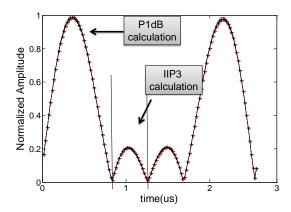

| Figure 57: Proposed test for P1dB and IIP3 calculation for high power devices                   | 100 |

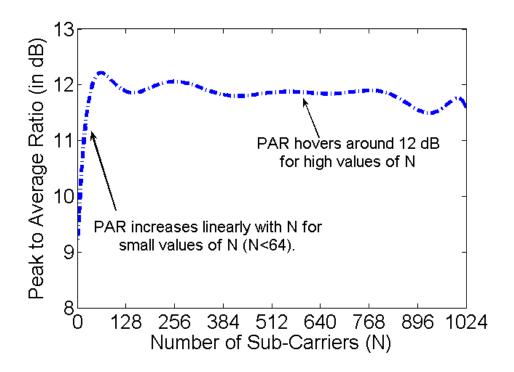

| Figure 58: PAR of OFDM Signal with no. of Subcarriers [102]                                     | 102 |

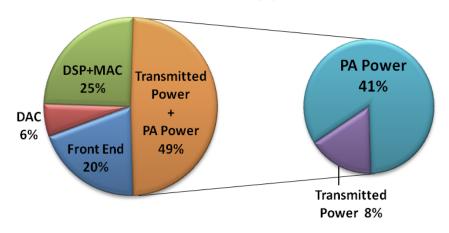

| Figure 59: Typical transmitter power consumption breakdown                                      | 103 |

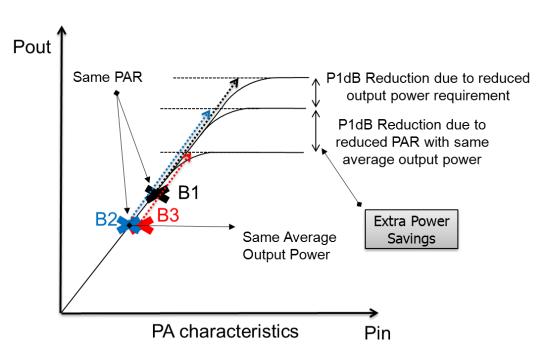

| Figure 60: Extra Power savings through dynamic PAR reduction                                    | 105 |

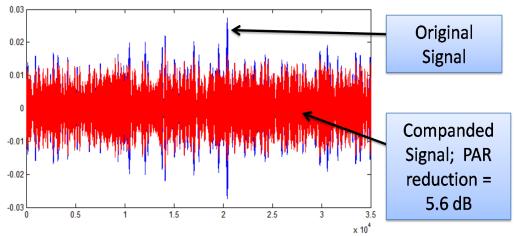

| Figure 61: Original and Companded OFDM signal                                                   | 106 |

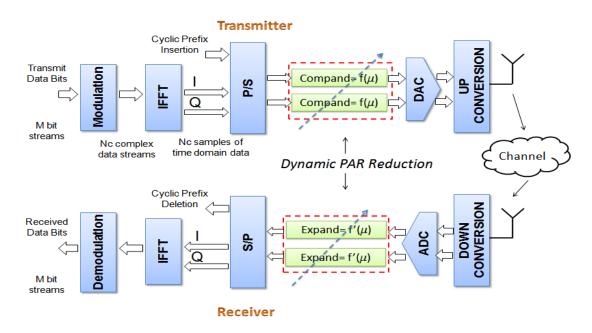

| Figure 62: An OFDM transceiver and dynamic companding in baseband for PAR adaptation            | 108 |

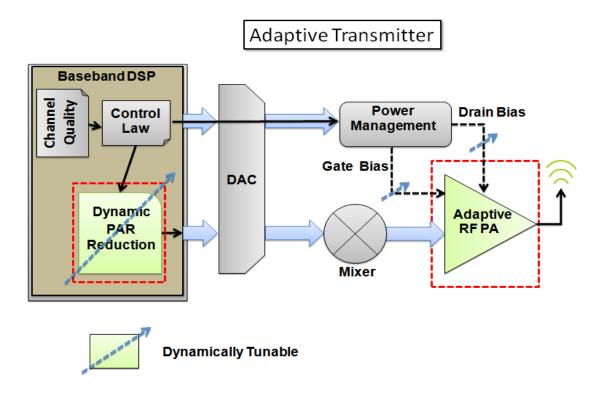

| Figure 63: Low-power adaptation of mobile transmitter through concurrent dynamic                |     |

| companding and adaptation of RF PA (Concurrent PAR and PA adaptation)                           | 108 |

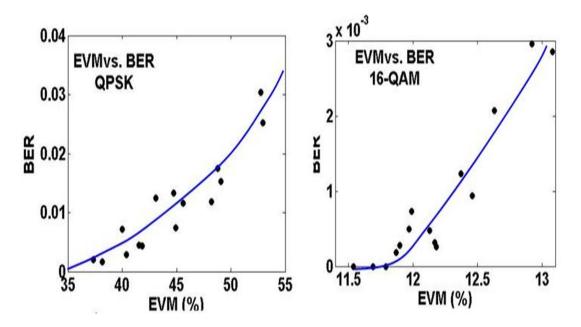

| Figure 64: Correlation between EVM and BER                                                      | 111 |

| Figure 65: PAR reduction as a function of $\mu$                                                 | 115 |

| Figure 66: Maximum achievable PAR reductions under different channel conditions for             |     |

| QPSK and 16 QAM modulations                                                                     | 117 |

| Figure 67: A closer look at the adaptation process                                              | 120 |

| Figure 68: a) Out of band emission characterization b) Zoomed In                                | 121 |

| Figure 69: Z <sub>Lopt</sub> for different bias conditions                                      | 123 |

| Figure 70: Simplified schematic of 1-stage PA                                                   | 124 |

| Figure 71: Trajectory of hias points of adaptive PA                                             | 124 |

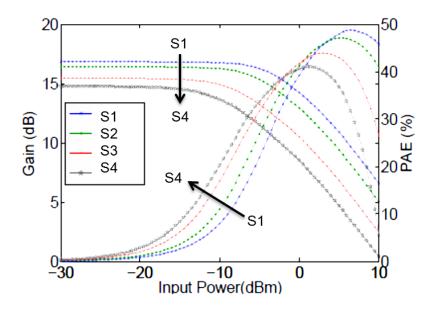

| Figure 72: Gain and PAE in different states of the adaptive PA                              | 126 |

|---------------------------------------------------------------------------------------------|-----|

| Figure 73: Power savings through PA adaptation                                              | 126 |

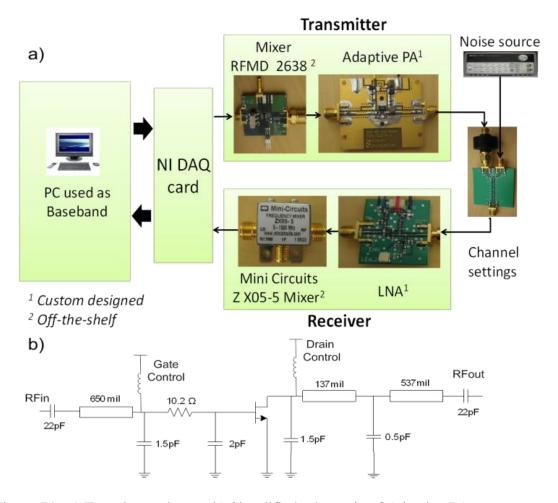

| Figure 74: a) Experimental setup b) Simplified schematic of Adaptive PA                     | 128 |

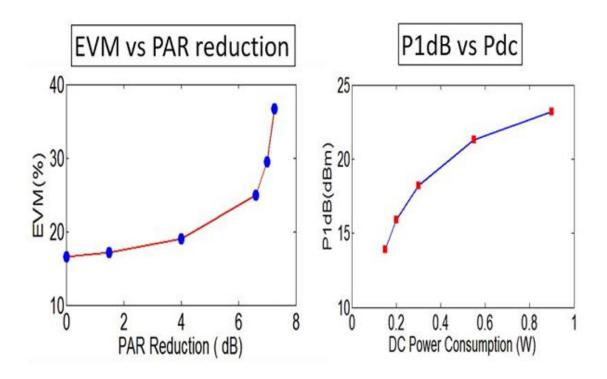

| Figure 75: Experimental results: a) EVM vs. PAR b) P1dB vs. Pdc                             | 130 |

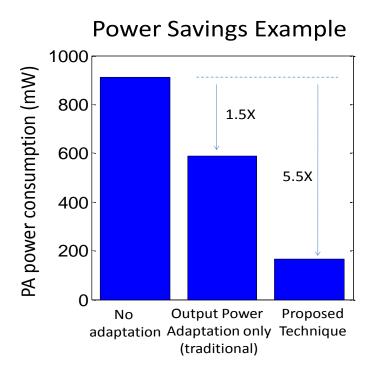

| Figure 76: Comparison of power savings                                                      | 131 |

| Figure 77: Mobile Radio Transmitter and Receiver                                            | 133 |

| Figure 78:. Adaptation approach: Dynamic Supply Voltage Control (DSVC)                      | 135 |

| Figure 79:.EVM vs. supply voltage variation.                                                | 136 |

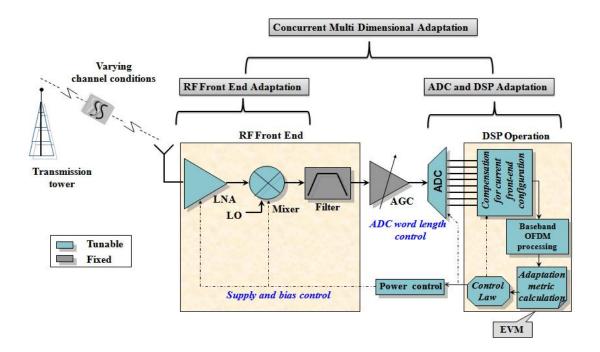

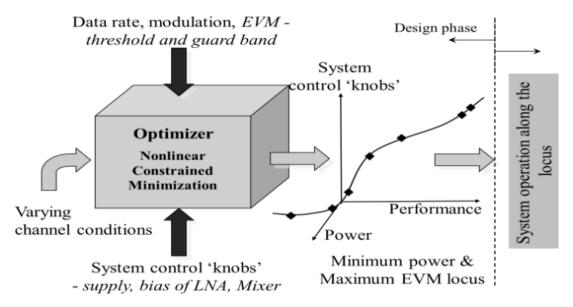

| Figure 80: System Level Adaptation Framework                                                | 137 |

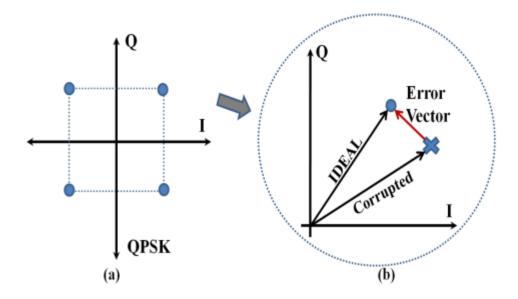

| Figure 81: (a) Constellation plot for QPSK, (b) Error vector for a transmitted and received |     |

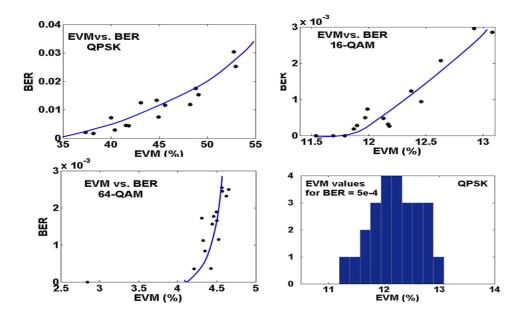

| symbol in the 1st quadrant, the rms of the error vectors over several symbols provides EVM  | 140 |

| Figure 82: EVM vs. BER relations for QPSK, 16-QAM, 64-QAM and EVM threshold                 |     |

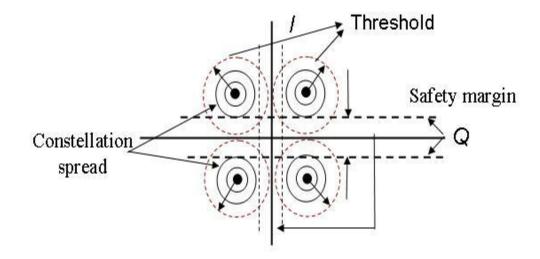

| estimation for QPSK                                                                         | 141 |

| Figure 83: Feedback control: QPSK constellation viewpoint                                   | 142 |

| Figure 84: Adaptive Receiver Framework                                                      | 143 |

| Figure 85: Receiver Power Optimization                                                      | 145 |

| Figure 86: a) EVM variation with time b) Operation along the locus showing power savings    |     |

| compared to the static case (highest point on the locus)                                    | 147 |

| Figure 87: a) Power consumption for different modulations b) Optimal ADC wordsize (W)       |     |

| along the locus for different modulations                                                   | 148 |

| Figure 88: Gain and NF change as supply voltage is scaled down.                             | 150 |

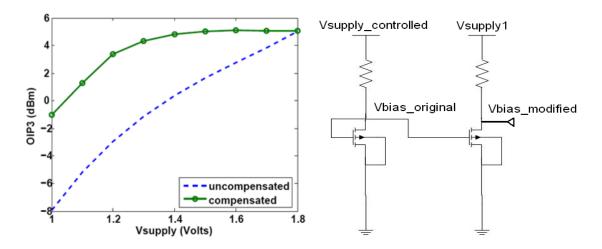

| Figure 89: a) OIP3 degradation with supply voltage scaling b) Adaptive biasing circuit      | 150 |

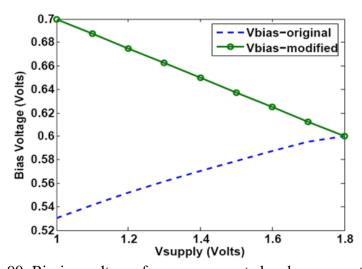

| Figure 90: Biasing voltages for uncompensated and compensated case                          | 151 |

| Figure 91: a) DSVC of the LNA for the compensated and uncompensated case b) Power           |     |

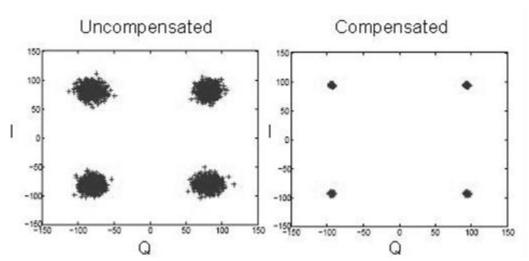

| dissipation with supply voltage                                                             | 153 |

| Figure 92: Received constellation plots (uncompensated and compensated)                     | 154 |

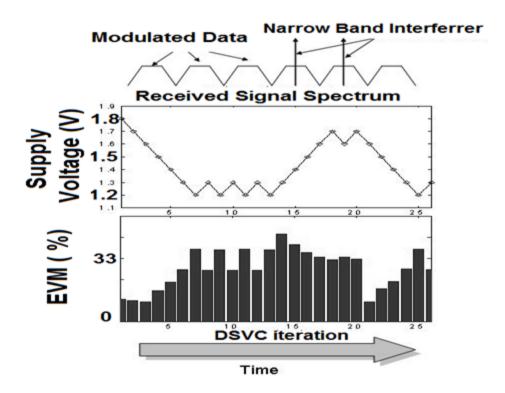

| Figure 93: Simulation study of the DSVC operation of the system under narrow-band           |     |

| interference                                                                                | 155 |

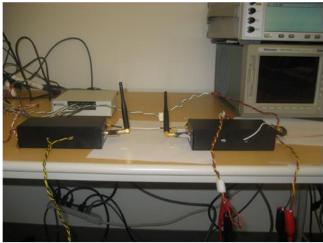

| Figure 94: Setup for live demonstration of a VIZOR receiver                                  | 156 |

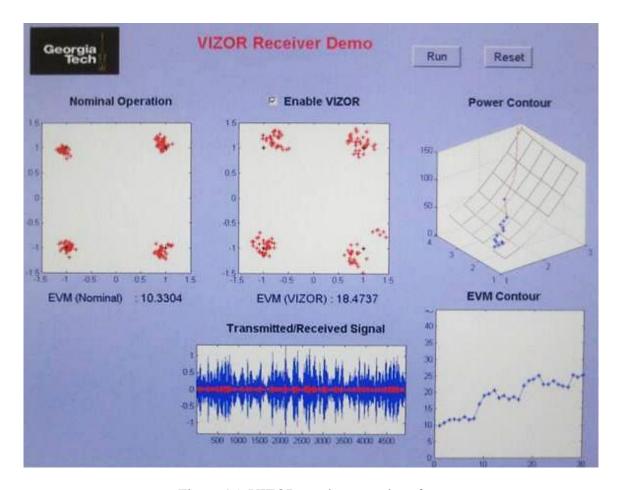

|----------------------------------------------------------------------------------------------|-----|

| Figure 95: VIZOR receiver user interface                                                     | 157 |

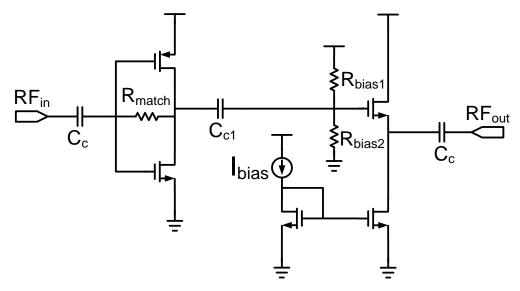

| Figure 96: Inductorless two stage LNA                                                        | 161 |

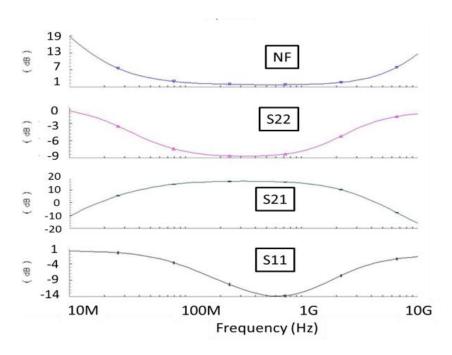

| Figure 97: Noise Figure and S-parameters of the designed LNA                                 | 163 |

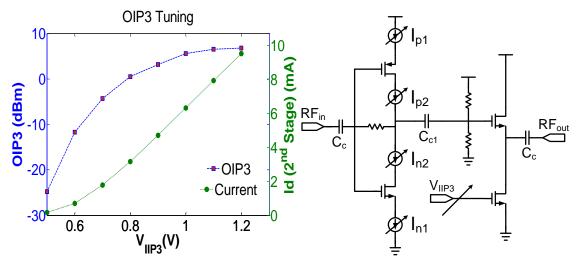

| Figure 98: a) OIP3 tuning b)Possible Gain and NF tuning knob choices                         | 165 |

| Figure 99: Performance comparsison for different gain control knobs                          | 167 |

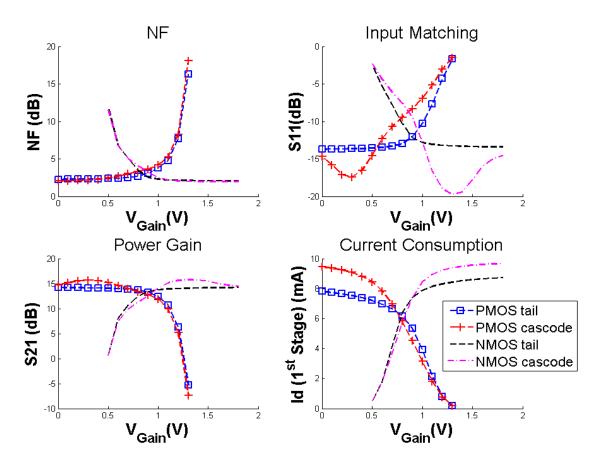

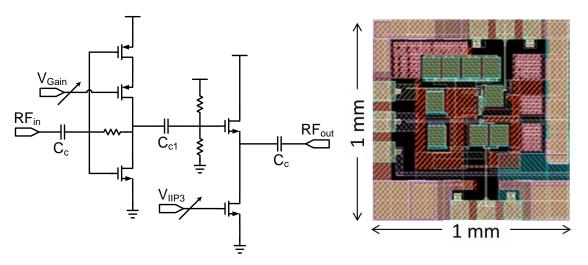

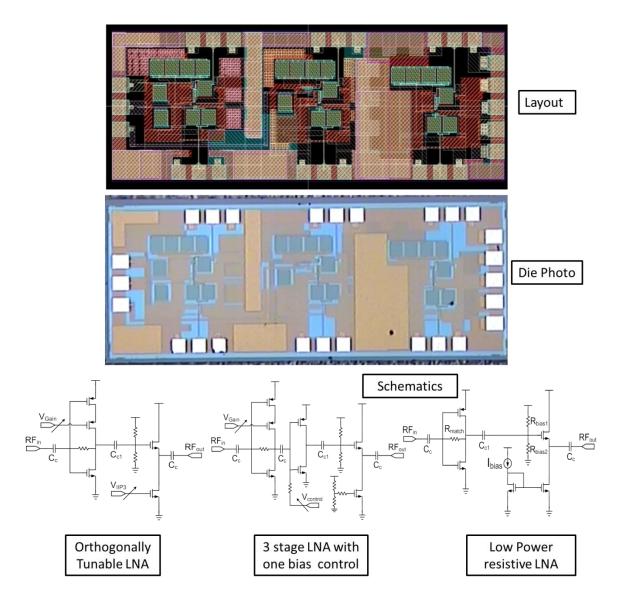

| Figure 100: a) Schematic b) Layout of orthogonally tunable LNA                               | 167 |

| Figure 101: Layout and Die Micrograph and schematics of the orthogonally tunable LNA         |     |

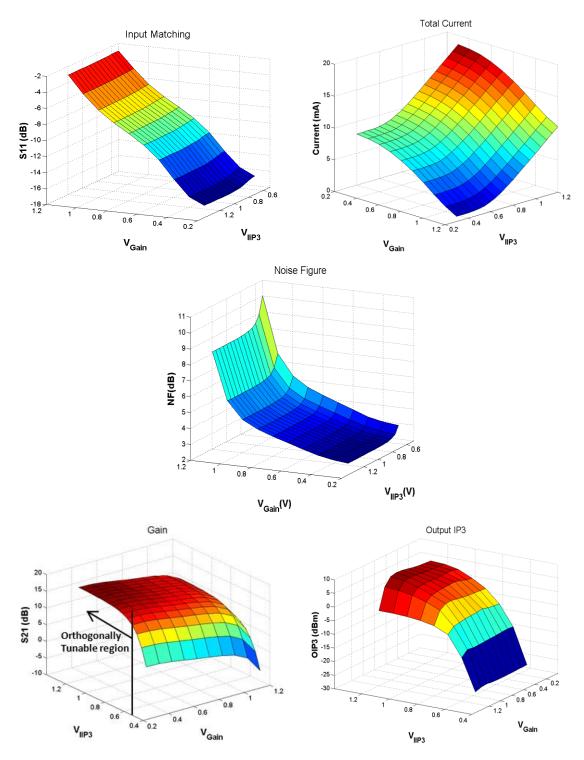

| and two other LNA for comparison purposes                                                    | 168 |

| Figure 102: a) Variation of S11 with tuning knobs, Orthogonal Tunability in b) Total         |     |

| current c) NF d) S21(gain) e) OIP3(linearity)                                                | 170 |

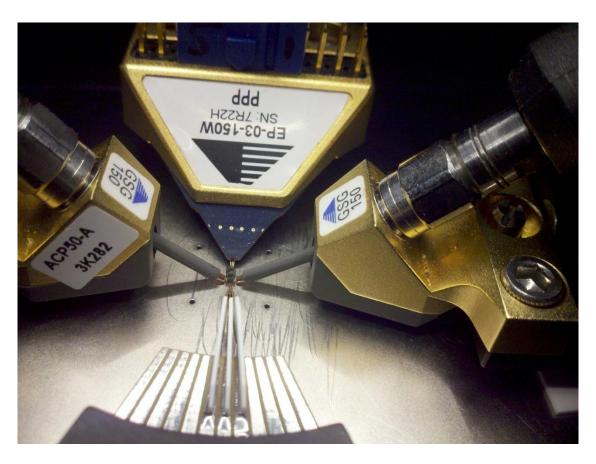

| Figure 103: Measurement setup                                                                | 171 |

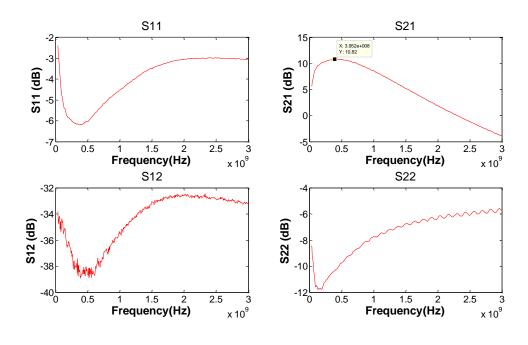

| Figure 104: Measured result for orthogonally tunable LNA at 22mA bias current                | 171 |

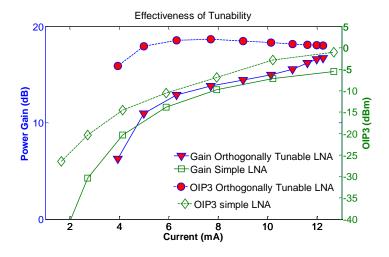

| Figure 103: Effectiveness of Orthogonal Tunability                                           | 172 |

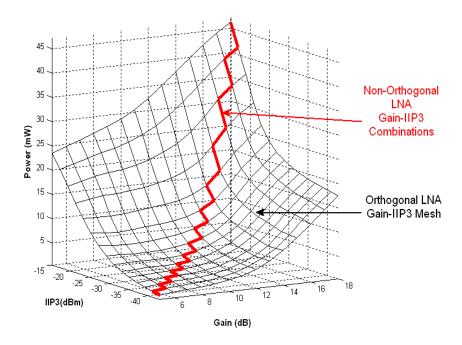

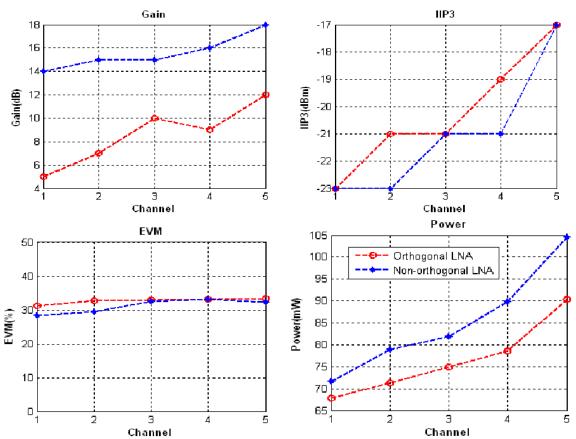

| Figure 104: Power profile for orthogonal and non-orthogonal LNA                              | 174 |

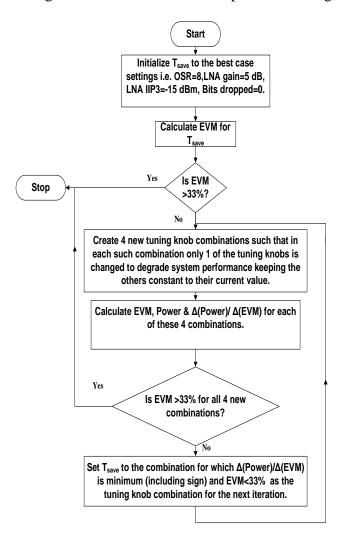

| Figure 105: Flowchart of optimization algorithm used                                         | 176 |

| Figure 106: Gain settings, IIP3 settings, EVM and Power for channels with progressively      |     |

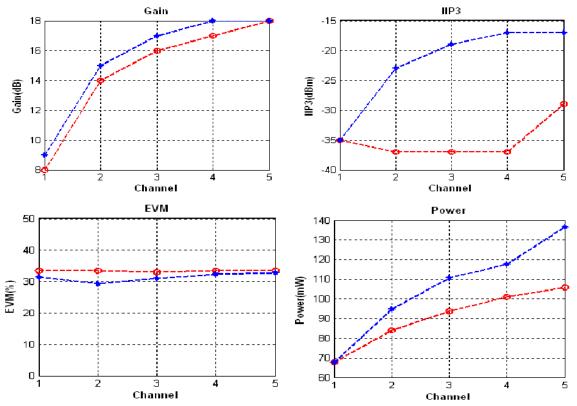

| increasing path loss (attenuation) but constant high output SNR                              | 177 |

| Figure 107: Gain settings, IIP3 settings, EVM and Power for constant path loss (attenuation) |     |

| and progressively noisier channels                                                           | 179 |

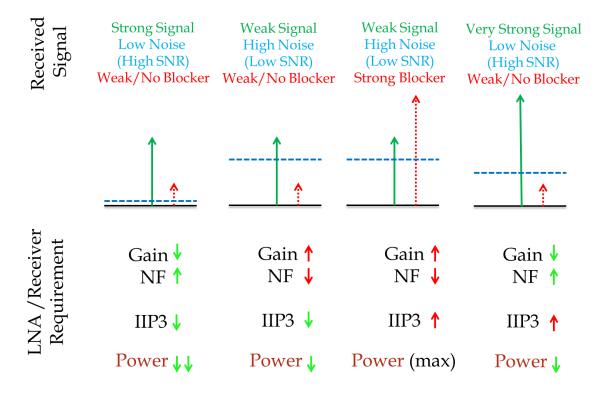

| Figure 108: Possible important cases of the channel receiver/LNA requirements for each       |     |

| channel along with the power consumption that should be expected for each case if the        |     |

| receiver is adapted.                                                                         | 182 |

| Figure 109: Wide Band Jammer detector(WBJD) architecture within the DVB-H receiver           | 185 |

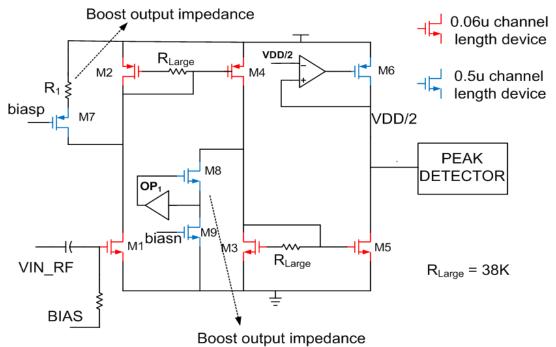

| Figure 110: Peaking Current Mirror based low power RF amplifier                              | 186 |

| Figure 111: a) Peak detector and b) Analog Comparator                                        | 187 |

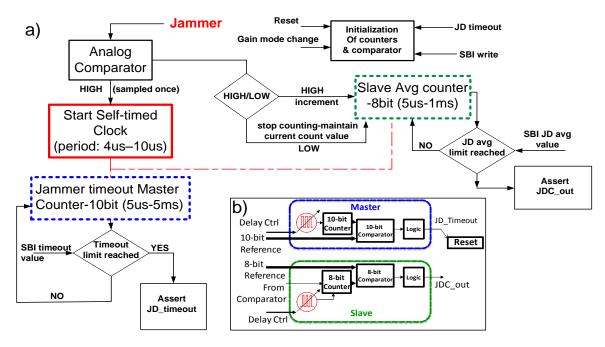

| Figure 112: a) Jammer detect decision scheme b) Master counter maintains timeout whereas     |     |

| slave counter finds out the average jammer value and asserts JDC out                         | 189 |

| Figure 113: a) Slave counter provides average value of jammer b) Master Counter                |     |

|------------------------------------------------------------------------------------------------|-----|

| determines time window within which jammers are counted once the first jammer comes. At        |     |

| the end of this window it provides a timeout which resets all JDC states. c) Simulation result |     |

| and timing diagram with continuous jammer present (JDC_out goes high, gain mode changes        |     |

| and resets all JDC states)                                                                     | 190 |

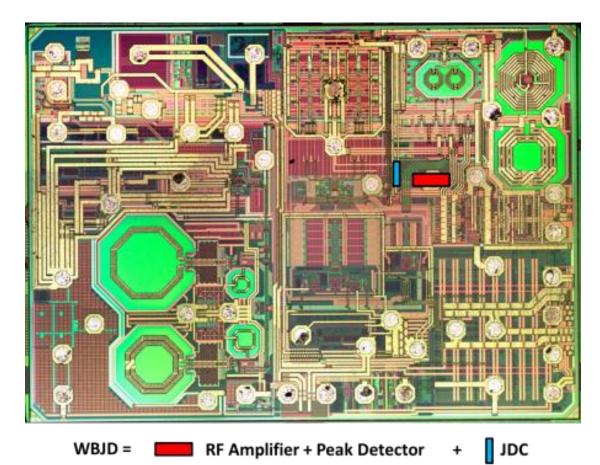

| Figure 114: Die photo of complete multi-band adaptive DVB-H receiver including the Wide        |     |

| Band Jammer Detector (WBJD)                                                                    | 191 |

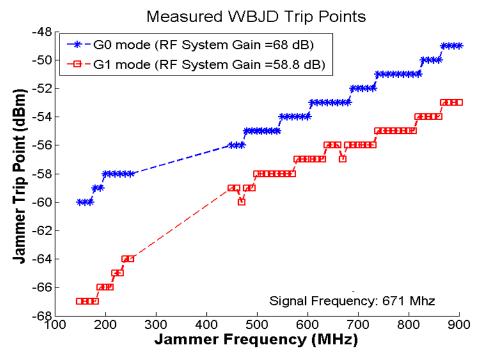

| Figure 115: a) Measured WBJD trip points over frequency in G0 mode and G1 mode (with           |     |

| DVB-H signal at 671 MHz)                                                                       | 192 |

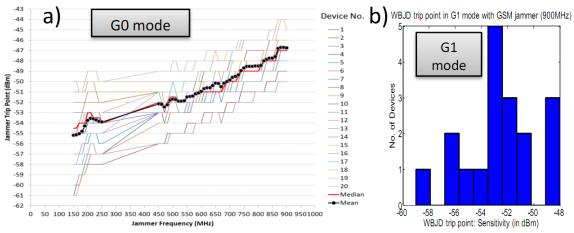

| Figure 116: a) Measured WBJD trip points over frequency for 20 devices in G0 mode b)           |     |

| Measured WBJD trip point histogram with GSM jammer in G1 mode (both in presence of             |     |

| desired DVB-H signal at 671 MHz)                                                               | 193 |

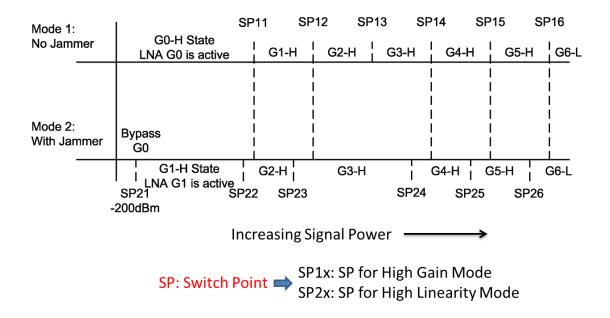

| Figure 117: Operation of the adaptive receiver with and without jammer [162]                   | 194 |

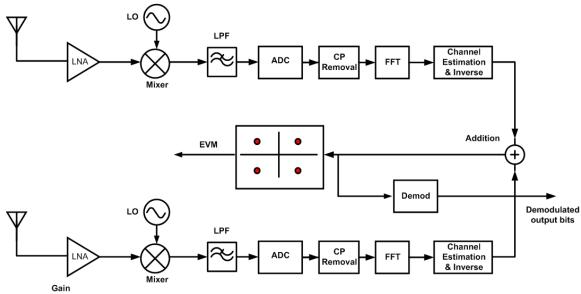

| Figure 118: Basic MIMO 1×2 receiver system                                                     | 196 |

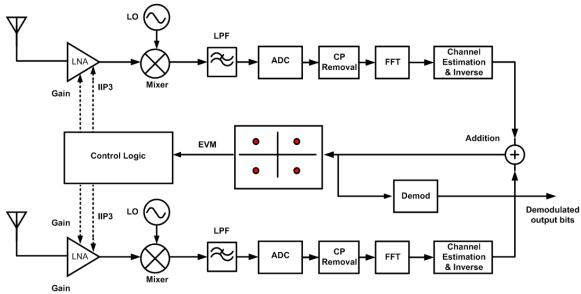

| Figure 119: MIMO VIZOR 1×2 receiver system                                                     | 197 |

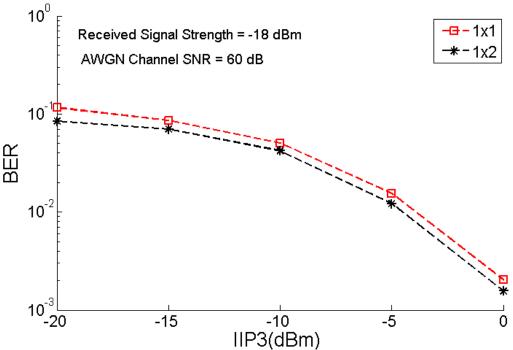

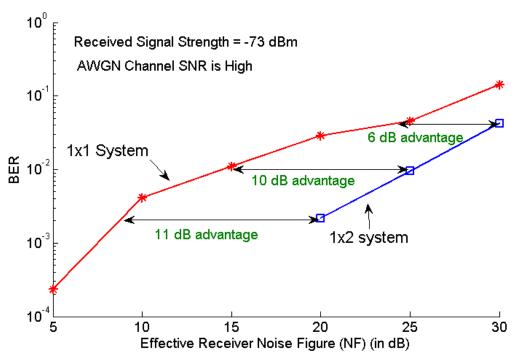

| Figure 120: BER for 1×1 and 1×2 systems with different LNA IIP3                                | 198 |

| Figure 121: BER for 1×1 and 1×2 systems with different receiver Noise Figure (NF)              | 199 |

| Figure 122: ACT based loopback testing approach                                                | 202 |

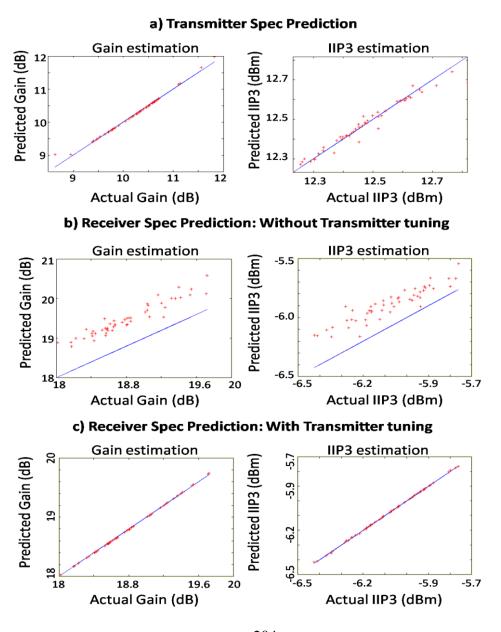

| Figure 123: Estimation plots for system specifications                                         | 205 |

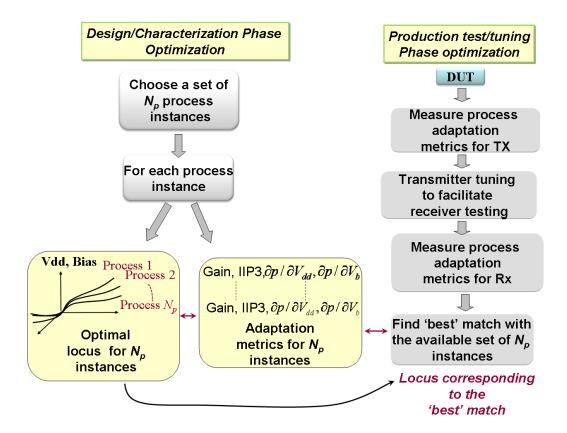

| Figure 124: Process sensing and estimation of optimal locus for minimum power operation        |     |

| of the DUT under process variation                                                             | 206 |

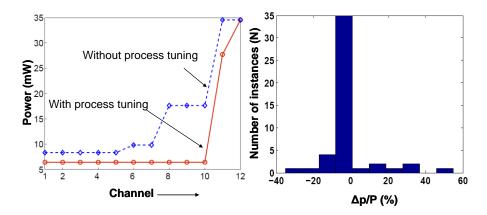

| Figure 125: a) Power Savings obtained with process tuning b) Optimality of locus selection:    |     |

| Histogram of $\Delta p/P$ in %                                                                 | 208 |

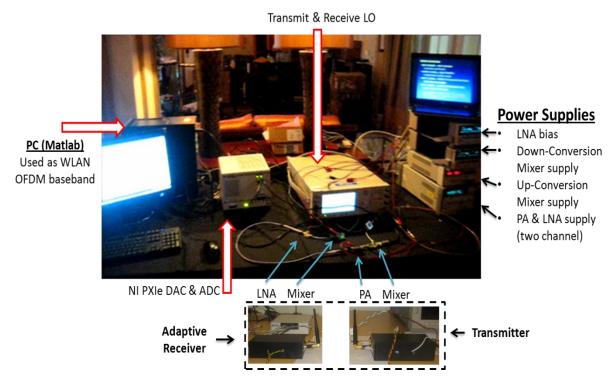

| Figure 126: Real-time demonstration hardware setup                                             | 209 |

| Figure 127: Block diagram of the adaptive receiver within OFDM transceiver                     | 209 |

| Figure 128: a) demonstration interface b) real-time EVM c) real-time power                     | 214 |

| Figure 129: Adaptation of wireless transceiver to workload and variability with the key        |     |

| adaptation mechanisms highlighted [164]                                                        | 219 |

#### **SUMMARY**

The explosive growth of portable battery operated devices has mandated design of low power circuits and systems to prolong battery life. These devices fabricated in modern nanoscale CMOS technologies suffer from severe process variation due to the reduced controllability of the fabrication process, causing yield loss. This calls for integrated low power and process tolerant design techniques, or design of systems that can adapt to its process and environment to maintain its performance while minimizing power consumption.

Currently, most of the wireless circuits are designed to meet minimum quality-of-service requirements under worst-case wireless link conditions (interference, noise, multi-path effects), leading to high power consumption when the channel is better than worst-case. In this research, we develop a multi-dimensional adaptation approach for wireless transmitters and receivers that optimally trades-off power vs. performance across temporally changing operating conditions by concurrently tuning control parameters in the RF front end to lower power consumption. Tunable circuits (e.g. LNA) with built-in tuning knobs providing independent controllability of important specifications allow optimal adaptation. Process sensing using intelligent test and calibration facilitates yield improvement and the design of process tolerant environment adaptive systems.

### **Chapter 1. INTRODUCTION**

The objective of the proposed research is to investigate the design of Self-Aware Radio Frequency Circuits and Wireless Communication Systems that can adapt to environmental and process variations to always operate at minimum power levels possible, extending battery life.

The explosive growth of portable battery operated devices has mandated design of low power circuits and systems to prolong battery life. These devices are designed in modern nanoscale CMOS technologies to allow integration of mega functionalities per chip. The reduced controllability of the fabrication process at these nano dimensions requires the design of process variation tolerant components and systems. This calls for integrated low power and process tolerant design techniques, or design of systems that can adapt to its process and environment to maintain its performance while minimizing power consumption.

Currently, wireless circuits are designed to meet minimum quality-of-service requirements under worst-case wireless link conditions (interference, noise, multi-path effects), leading to high power consumption when the channel is better than worst-case. In the proposed research work, we develop a multi-dimensional adaptive power management approach that optimally trades-off power vs. performance across temporally changing operating conditions by concurrently tuning control parameters in the RF and digital baseband components of the wireless transmitter and receiver. This adaptation is performed in real-time for low power operation.

Low cost testing methodologies are developed for identification of the *health* of the wireless circuit/system. These are used in conjunction with tuning algorithms that tune a

wireless system under process variation to meet performance specifications and recover yield loss. This testing and adaptation is performed once during the post manufacture test/tune phase to compensate for manufacturing variations. This can also be applied periodically during in field operation of a device to account for performance degradation due to ageing. Finally, *process tolerant environment adaptive* systems are designed.

#### 1.1. Origin and History of the Problem

The number of transistors in an Integrated Circuit (IC) has been doubling every 18 months following Moore's Law for last few decades. This has allowed the sustained growth of the IC industry by increasing the functionality per chip in every generation. However, increasing functionality per unit area has increased the power consumption per unit area (power density) significantly. According to data published by Intel in early 2000's [1] the power density of the microprocessors would reach that of a nuclear reactor if low power techniques are not employed. Hence a significant amount of research in VLSI in the first decade of 21st century has been targeted towards low power IC designs.

The doubling of transistor per unit area has been achieved by technology scaling, i.e. reducing the dimensions of the transistors. Scaling reduces the area as well as the capacitance associated with each node making the circuits faster. However, with continued scaling the IC industry is past the sub-micron dimensions and has reached the nanometer regime. The controllability of the fabrication process has reduced significantly due to these nanoscale dimensions of the transistors. This causes variability in fabrication resulting in undesired variation in the circuit and system performance. The traditional static circuits fail to meet the demand of the stringent system requirements due to the underlying variation of the transistors. This calls for a new paradigm of variability aware

circuit and system design, where the circuits/systems are intelligent enough to understand the underlying variation and able to heal itself by compensating appropriately (self-healing circuits/systems).

Low Power and Variation tolerant Analog/Mixed Signal/RF circuits' require a new/different set of design techniques that adapt the wireless transceiver systems and underlying circuits to simultaneously meet low power and high performance requirements with minimum power.

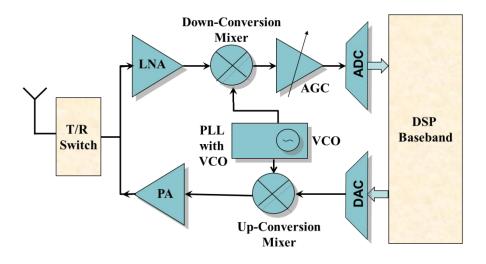

## 1.2. Conventional Wireless Systems

Conventional wireless circuits/systems are designed for the worst case channel, environment and process corner. Each of the variations is dealt by incorporating significant built in design margin which results in high power consumption. The sub blocks are designed for their respective specifications with enough design margins such that they work by themselves over channel, environment and process variations. The system and underlying circuits are not aware (for the most part) of their health and surroundings, i.e. they are so called *static* circuits.

## 1.3. Need for Environment and Process Adaptive Wireless Systems

#### 1.3.1. Low Power Requirements in Wireless/Portable Systems

With the projected explosion in the number of multimedia wireless applications in the consumer electronics market, power consumption will be a critical metric in future designs of multi-mode multi-standard wireless devices, as most of these devices are portable (battery operated) and battery lifetime is a key demand among consumers. At the physical layer level, low-power design methodologies for digital systems have been studied extensively but relatively fewer techniques have been proposed for Mixed Signal (MS) and Radio Frequency (RF) systems. However a lot of the Mixed Signal/RF circuits (e.g. an Analog to Digital Converter (ADC), a Power Amplifier (PA)) are power hungry and are generally have to be overdesigned to work across different operating environments, process and temperature. Due to the sensitive nature of analog circuits and variety of specifications that needs to be satisfied simultaneously, low power techniques for analog/RF systems are required that adapts the system to always operate at the minimum power level possible.

#### 1.3.2. Process Variation in Mixed Signal Circuits and Yield Loss

With aggressive scaling of CMOS the controllability of the fabrication process is decreasing with each technology node. In the nanometer design regime, high performance Analog/RF circuits are expected to be increasingly susceptible to process variations. It is becoming increasingly impossible to keep the 3σ variations of the process parameters within 10% bound [2][3]. The variability in the nanometer regime is making circuits less reliable and resulting in significant yield (% of non-faulty chips) loss.

Modern Wireless circuits are designed to be extremely high performance as demanded by the consumer. This requires designing the circuits at the "edge", making the circuits very sensitive to any process variation. In the nanometer regime, the increased variation in the process causes these high performance systems to vary allot from its desired specifications, resulting in throwing away of the device. This causes yield loss and results in reduced profit for the IC design company. With static design techniques, if we try to address this issue by leaving an increased guard band, the power consumption goes up. Hence there is a pressing need for variation tolerant circuits which are also low

power. Significant research work has been done in recent years in variability aware design of digital circuits. Important techniques include adaptive body biasing [4], dynamic supply voltage scaling [5][6] and variable size keepers [7]. Radio Frequency (RF) circuits are very sensitive to the increasing process variation. To make RF design successful in the nanometer regime with acceptable yield there is an increasing demand for variability tolerant RF circuit design techniques, similar to their digital counterpart.

One way to address this issue is to have intelligent circuits and systems that can understand the process corner it is in and tune itself to meet the required specifications, while minimizing power consumption. This requires built in tunability in Analog/Mixed Signal/ RF circuits which is traditionally not that common due to the sensitive nature of these circuits.

### 1.4. Prior work in Adaptive Wireless Systems

In this section we summarize the prior efforts in adaptive wireless circuits as well as system design for low power and process variation tolerance.

#### **1.4.1.** Adaptivity in Low Noise Amplifiers (LNA)

There have been few efforts on designing an adaptive LNA for process variation tolerance. These are summarized as follows. Tuning of the input match frequency can be achieved using several-tap tunable inductors [8]. Another way to control only the non-linearity of the LNA is to add an extra current stealing path (Inter-Modulation Distortion or IMD sinker) to a traditional LNA design [9]. The gain of an LNA can be stabilized using damped LC loads [10]. Though this takes care of gain variation to some extent it is not able to compensate for noise figure (NF) and input reflection co-efficient (S11). Also

this technique is specific to tuned amplifiers. The input and output matching is a critical requirement to ensure proper transfer of signal in RF Amplifier. These matching networks can be made process variation insensitive by breaking then from one step to two step and choosing the components values such that the sensitivity to process variation is minimized [11]. A process and temperature variation tolerant Bluetooth RFIC was designed in [12] by using bandgap references, current compensation circuit and active loads.

#### **1.4.2.** Adaptivity in Power Amplifiers (PA)

A PA is the last block in a wireless transmitter that drives the signal to be transmitted to the antenna. Due to high transmission power requirements the PA tends to be the most power hungry block in the transceiver. It needs to provide gain to the signal while delivering high output power, i.e. process signals with extreme large swing (typical swing is close to 1.7 to 2 times the supply voltage). The key specifications include Gain, Non-linearity (IIP3), input and output matching, Adjacent Channel Power Ratio (ACPR), bandwidth (BW) and efficiency. Since the signal levels in a PA are very high the tunability achieved by gate and drain bias control are minimal. Voltage based tuning can be aided by dynamically companding in the digital to reshape the signal to reduce its peak to average ratio [13]. Output of the PA has to conform to stringent spectrum requirements set by the Federal Communications Commission (FCC). This requires highly linear operation of the PA, which reduces its efficiency or makes it power hungry. A pre-distortion function, i.e. the inverse of the PA nonlinearity is used in the baseband DSP to increase the overall linearity of the system even with low power consumption.

In the system level, to reduce interference and increase efficiency, output power of the Mobile Station (MS) is varied depending on the channel condition and distance from the Base Station (BS). Using power control information (based on received signal strength) sent by the BS to MS through the BCH (Broadcast channel) [14][15], the PA average output power is varied. If the DC power consumption is kept fixed (i.e. static PA) the efficiency of the PA is very low for the time that it is not transmitting at the maximum average output power level. An approach to increase the operational efficiency of RF transmitters has been to use a tunable PA (such as Agilent ACPM-7891[16]) in the frontend. A MS power controller (such as National Semiconductor LMV243[17]) uses the information from BS to control the output power of the PA by applying proper control voltages and sometimes using a control loop[15][18]. Output power is varied in a wide range as described in [19]. For example, output power could be varied from 5 -39 dBm for GSM 900MHz band. This recovers some of the efficiency loss due to variable distance between the BS and MS.

To increase the efficiency of PAs using circuit level techniques, the supply voltage of the PA is changed according to the envelope of the signal. These PAs can be broadly divided into 3 categories [20], namely slow tracking, envelope tracking and polar modulation PAs. A slow tracking PA [21] supplies the PA with a voltage slightly greater than the largest peaks of the envelope. Hence it can only recover the efficiency loss due to power-control back-off. An envelope following or envelope tracking PA [22]-[24] have been developed in which the supply voltage is dynamically modulated by the estimated or tracked envelope to keep drain efficiency high. Hence it allows recovery of lost efficiency due to both modulation and power-control back-off. In these methods, the

envelope amplitude information has to be extracted from the signal and incurs extra complexity and increased hardware overhead. In polar modulated PAs [25], [26] the supply modulator applies the required envelope signal directly onto the carrier through a saturating PA. Though the use of saturated PAs increase efficiency, the bandwidth requirements of the AM path is significantly high and the noise requirements of the supply modulator makes this implementation impractical. A power management block presented in [27] provides good efficiency while providing variable output voltages. This on-chip block can generate drain and gate bias for a PA using inputs from DSP making adaptation of PAs easier. This work also shows adaptation of a PA with varying average output power to maintain high efficiency, using the above mentioned PMU.

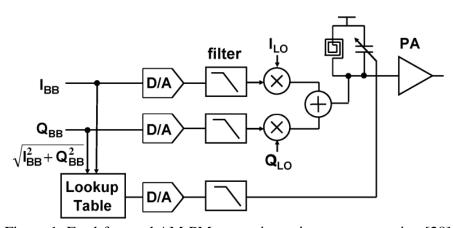

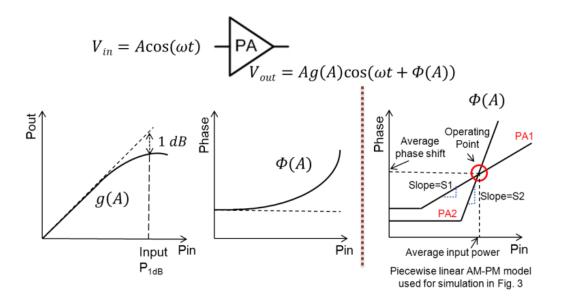

Figure 1: Feed-forward AM-PM correction using varactor tuning [28]

Another significant effect in the PA is input power dependent gain compression and phase distortion. AM-PM distortion can be corrected by introducing an opposite phase shift to cancel the signal power dependent phase shift of the PA. Figure 1 shows a schematic that achieves this goal. A varactor is placed across one of the inductors in the mixer or the PA. By changing the control voltage of the varactors [28], the resonance frequency of the tank can be changed, thus modifying the phase shift incurred by the signal. The control voltage changes according to the amplitude of the input signal in such

a way as to cancel the AM-PM distortion of the PA. This shows a real-time technique to correct for AM-PM. Under process shift, the AM-PM curve changes for a PA. This can also be compensated for using this technique just by changing the way control voltages are applied.

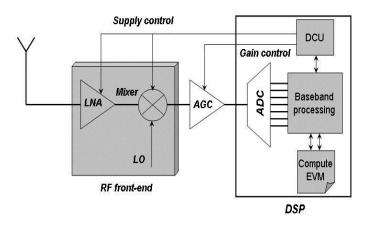

#### **1.4.3.** Adaptivity in Analog to Digital Converters (ADC)

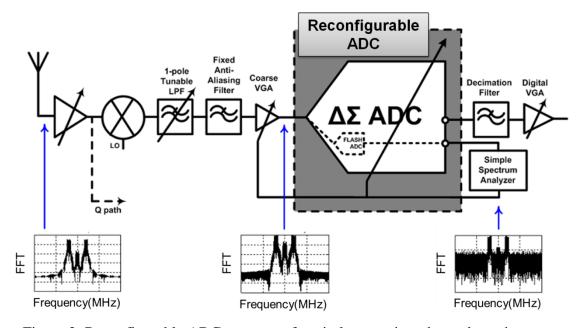

Figure 2: Reconfigurable ADC as a part of a wireless receiver that reduces its power consumption when interference is not high [29].

ADCs or Analog to Digital Converter is an important sub block in a wireless receiver. It converts the analog signal to digital domain for further processing by the DSP. There has been some effort to make ADCs low power by using them in an environment adaptive manner. To reduce power consumption the order of the loop filter can be reduced dynamically depending on the interference environment in a sigma delta ADC [29]. This could be achieved as shown in Figure 2. The reconfigurable ADC consists of several modes allowing power versus performance tradeoff. As the

interference to signal ratio goes down the requirement of the ADC dynamic range is relaxed and hence a lower power mode can be used. A low resolution flash ADC is used for spectrum sensing. A simple spectrum Analyzer is used for spectrum sensing from the flash ADC output and the mode of the ADC is set based on the sensed spectrum. This allows power savings by choosing lesser performance when interference in the received signal is low.

#### 1.4.4. System Level Adaptivity in Transceivers

Several techniques for low power operation of wireless circuits have been proposed in the literature. At the physical layer, low-power design methodologies for digital systems [30][31] and analog/RF systems [32][33] have been studied extensively. The issue with these approaches though is that circuit designs incorporate margins to account for worst-case estimates of process variability, and thermal effects in the RF front-end, and channel conditions corresponding to different modes (data rates) of transmission. However, for most of the time a wireless device is powered up for operation, it is not in a worst case environment and hence, consumes more power than necessary under the majority of operating conditions. The need for dynamically adapting RF front-end, baseband and digital circuits to save power and enable multi-mode operability in future wireless devices was discussed in [34][35][36]. There exist media access control (MAC) and network-level dynamic power management schemes [37] that conserve power by adapting the data rate (modulation and coding rates) based on certain channel quality metrics derived from the analysis of training symbols. Present-day wireless devices also feature high-power, low-power, and shut-down modes, that are activated on the basis of prevailing channel conditions. Though these approaches are effective in reducing the power consumption levels, they do so in a few discrete steps, and hence do not fully exploit the design margins through fine-grained system-level adaptation. In a recently published work [38], an energy scalable RF transmitter was proposed, where the frontend is dynamically tuned (supply, bias, resistances) for each data rate modulation set by the higher-level link layer protocol. The tuning is driven by channel quality as determined by channel estimation metrics and relies on simulation of a large number of channel and RF front-end settings. In [40], the authors show a reconfigurable LNA based on DSP assisted testing and self-tuning.

## Chapter 2. DESIGN FOR PROCESS VARIATION TOLERANCE

#### 2.1. Problems with Process Variation: Yield Loss

The continued scaling following Moore's law has resulted in feature sizes in the nanometer regime. The reduced controllability of sub-wavelength lithography has resulted in severe manufacturing variations. This in turn results in parametric variation in the specifications of the circuits, resulting in more and more devices failing the required performance threshold. This results in significant yield loss which directly affects the profit margin. Hence, design techniques that are robust to manufacturing variations are required. In the prosed research, we tackle this issue in two ways. First circuit level process tolerance is demonstrated using an LNA as a test vehicle. These circuits inherently show robustness to process variation. A second approach is to tackle process variation using system level control. These *self-healing* systems would consist of a way to sense the process corner or health of the system. Using this information and built in tuning knobs a system level algorithm tunes the device back until it comes back within its acceptable specification bound. The next two sections describe such circuit level and system level process tolerance, respectively.

## 2.2. Circuit Level Approach: A Self-healing LNA example

Design of a *self-compensating process variation tolerant RF Low Noise Amplifier* (*LNA*) is described here [40]. A novel non–intrusive mixing technique is described which enables minimal intrusion negative feedback in RF circuits making them process variation tolerant. The following design technique provides 18% yield improvement over comparable conventional LNA under severe process variation.

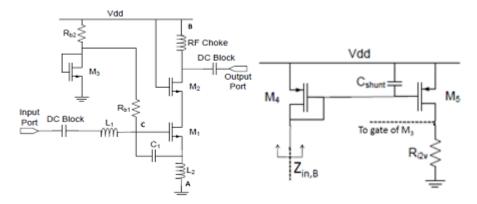

A well-known and widely used method for process variation tolerance in analog circuits is negative feedback. This can also provide a formal methodology in designing process variation tolerant RF circuits. But this technique is not very common in RF circuits, as any type of conventional sensing and mixing in highly sensitive RF nodes changes the RF circuit performance significantly. So, loss due to performance degradation becomes greater than the gain achieved by stabilization using negative feedback. The techniques described here address this problem by developing a non-intrusive mixing technique as well as minimizing the intrusion of the sensing circuit. This enables use of negative feedback in RF circuits and helps in designing process variation tolerant RF front ends. Figure 3a shows a conventional cascoded LNA typically used in RF receiver front ends. Next, the minimal intrusion sensing and non-intrusive mixing technique is described.

Figure 3: a) Conventional cascoded LNA b) Minimal intrusion sensing circuit

#### 2.2.1. Minimal Intrusion Sensing

In the LNA of Figure 3a the most important single parameter that could give the information about effect of process variation on it, is the bias current flowing through the main branch (containing M1 and M2, L2 and RF choke) (Id). For ensuring proper RF

operation, the LNA needs to be biased up "properly" under any process condition. So emphasis is placed on sensing Id to acquire information about the process. To acquire true information of Id it has to be sensed directly from the main branch. The problem now, is to minimize the intrusion, i.e. to minimize the effect of the sensing circuitry on the RF performance of the LNA. The two likely sensing points are A and B (Figure 3a). In [41] sensing from A has been proposed by inserting a small resistance (7 $\Omega$ ) in between L2 and ground. But this increases noise figure (NF) of the LNA severely. Another approach is shown in [42] where the RF voltage across L2 is sensed and is processed in baseband using a 'three tonal' approach to find out information about the LNA. However, it can only be used for testing the LNA with known test input signal. Figure 3b shows the sensing circuit which is to be inserted at point B. This is essentially a PMOS current mirror with an additional C<sub>shunt</sub>. The resistance looking into the transistor M<sub>4</sub> without C<sub>shunt</sub> is 1/g,<sub>m,M4</sub>. This impedance should be minimized to minimize the loading on the LNA. Hence (W/L)<sub>M4</sub> is made as large as possible to minimize the resistance looking into the diode connected transistor. Also  $C_{shunt}$  is added in parallel with  $C_{gs,M4}$  and  $C_{gs,M5}$ . This capacitance is big enough to short at RF frequencies, almost shorting the impedance looking into sensing network ( $Z_{in,B}$ ). At RF frequencies it could be written as follows:

$$Z_{in,B} = \frac{1}{Y_{in,B}} = \frac{1}{g_{m,M_4} + j\omega_{RF}(C_{shunt} + C_{gs,M_4} + C_{gs,M_5})}$$

(1)

$(W/L)_{M4}$  and  $C_{shunt}$  are maximized to maximize the denominator in (1) and hence make  $Z_{in,B} \rightarrow 0$  at RF frequencies. This minimizes the amount of loading on the LNA due to the sensing circuitry. Also  $(W/L)_{M4}/(W/L)_{M5}$  is designed to be 100 to make  $I_{M5}$  very low compared to  $I_d$ . This ensures *insignificant additional power consumption* compared to the

original LNA.  $R_{i2v}$  converts this sensed current into a voltage which would be used for mixing.

#### 2.2.2. Non-Intrusive Mixing

Traditional analog mixing techniques (shunt and series mixing) fail in RF frequencies as the feedback network is directly connected to the gate or source of  $M_1$ . Connection to the gate (point C in Figure 3a) changes the input impedance significantly, whereas connecting to the source increases NF and also degrades input matching.

Figure 4: Non-intrusive mixing using modified biasing technique

Figure 4 shows a novel mixing arrangement by modifying the biasing transistor. Instead of biasing M1 from a diode connected M3 (conventional biasing), it is biased from the drain voltage of M3, where M3 is biased by the voltage generated across Ri2v (modified biasing). This doesn't load node C at all and still provides the required mixing capability. The impedance looking into Rb1 (Zin,C) should be as high as possible, such as the biasing arrangement has no effect on RF performance. This impedance could be written as follows:

$$Z'_{in,C} = R_{b1} + R_{b2} || \frac{1}{g_{m,M_3}}$$

(2)

$$Z_{in, C} = R_{b1} + R_{b2} || r_{o, M_3}$$

(3)

Where,  $g_{m,M3}$  and  $r_{o,M3}$  are the transconductance and output resistance of the biasing transistor  $M_3$  respectively.  $Z'_{in,C}$  is the impedance looking into conventional biasing circuit whereas  $Z_{in,C}$  is the impedance looking into the modified biasing/mixing circuit. Since

$$r_{o,M_3} >> \frac{1}{g_{m,M_3}} => Z_{in,C} > Z'_{in,C}$$

(4)

Hence, the modified biasing circuit improves the RF performance and hence it's completely non-intrusive.

#### 2.2.3. Process Variation Tolerant LNA

Figure 5: Complete circuit diagram of process variation tolerant LNA

The concepts described in the previous sections are used to build a process variation tolerant Low Noise Amplifier as shown in Figure 5. The analysis of the circuit could be understood by following the feedback loop. Due to process variation, say  $I_d$  has

increased from its nominal designed value. This results in similar increase in the mirrored current  $I_{M5}$  and hence increases the voltage across  $R_{i2v}$ . This acts as the gate to source voltage of  $M_3$  ( $V_{G,M3}$ ). As  $V_{G,M3}$  goes up drain voltage of  $M_3$  goes down reducing the biasing voltage (point C) of the transconductance stage, in turn reducing  $I_d$ . Thus through this negative feedback loop this circuit keeps the  $I_d$  constant (as close as possible to the nominal designed value of  $I_d$ ) or in other words keeps the LNA biased "properly" even under severe process variation. Under RF operation since  $Z_{in,B} \rightarrow 0$  it doesn't have much effect on the circuit and keeps the RF performance of the circuit intact.

(5) and (6) shows the dependence of  $V_{G,M1}$  on  $I_d$ . As  $I_d$  increases  $V_{G,M1}$  decreases and vice versa showing the validity of the negative feedback. The parameters in these equations are used in their traditional sense and they are optimized in the design to maximize the sensitivity of the feedback loop.

$$V_{G, M_3} = I_d \times \frac{(W/L)_{M_5}}{(W/L)_{M_4}} \times R_{i2\nu}$$

(5)

$$V_{G, M_1} = V_{dd} - \frac{\mu_n C_{ox}}{2} \left(\frac{W}{L}\right)_{M_3} \left(V_{G, M_3} - V_{tn}\right)^2 \times R_{b2}$$

(6)

# 2.2.4. Yield recovery through process variation tolerant LNA

The results of the design are presented in this section. For comparison purposes a conventional LNA and a process variation tolerant LNA has been designed in TSMC  $0.25\mu$  technology, working at 1.8 GHz with similar gain, noise figure (NF) and input return loss (S11) (Refer Table 2). Simulations have been performed using Agilent ADS design tools. Severe process variations have been introduced to important process parameters as shown in Table 1. The parameters considered are minimum channel length ( $L_{eff}$ ), oxide thickness ( $T_{ox}$ ), threshold voltage ( $V_t$ ), capacitances (C) and inductances (C).

Table 1 Variation of parameters considered

| Process Parameter | L <sub>eff</sub> | Tox | V <sub>t</sub> | С  | L  |

|-------------------|------------------|-----|----------------|----|----|

| 3σ variations (%) | 60               | 30  | 30             | 30 | 30 |

|                   |                  |     |                |    |    |

**Table 2 Comparison of Both LNA**

| Design                 | Nominal  | Nominal | Nominal | Yield |

|------------------------|----------|---------|---------|-------|

|                        | Gain(dB) | NF(dB)  | S11(dB) | (%)   |

| LNA (conventional)     | 15.072   | 1.131   | -22.85  | 64    |

| LNA (process-tolerant) | 15.019   | 1.136   | -23.05  | 82    |

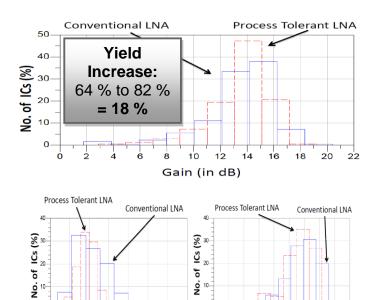

Figure 6 Variation of Gain, NF and S11 of the process variation tolerant LNA and conventional LNA

S11(in dB)

2.0 2.2

1.6

Noise Figure (in dB)

1.0

Yield analysis has been performed with the following performance constraint: 11dB<Gain<17dB, S11<-10dB and NF<1.35dB. The yield of the variation-tolerant circuit is found to be a significant 18% higher than its conventional counterpart. Fig. 6 shows the distribution of % of ICs based on gain, NF and S11 obtained from yield analysis. It can be seen that for all the specs process-tolerant LNA performs better than the conventional one (less variation around its nominal spec). Hence the above described techniques lets us design a process variation tolerant LNA which self-compensates under variation. This technique can very easily be extended to other RF components opening up the paradigm of variability aware RF front end design.

# 2.3. System Level Approach

### 2.3.1. Effect of Process Variation and Built in Tunability

As described in previous sections the reduced controllability of the fabrication process in the nanometer regime reflects as significant variation of the important specifications from chip to chip. The yield of a system design gets affected severely as variation in the subsystems directly affects the system specifications. We have discussed circuit level techniques to address this issue. In this section we investigate requirements and possibility of system level healing. The general methodology of 'healing' a process skewed system is to have built in tunability in the system and intelligently tune the system under variation such the system specifications come back within acceptable bounds[43][44][45][46].

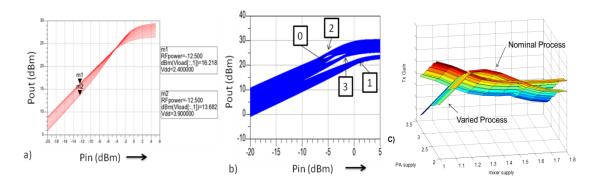

Figure 7: a)  $P_{out}$  vs  $P_{in}$  for a PA over  $V_{dd}$  variation. b)  $P_{out}$  vs.  $P_{in}$  over all combination of tuning knobs (supply and bias) for 4 process instances c) Gain of a transmitter over all tuning knob combinations for 2 process instances. [46]

This calls for identifying proper tuning knobs in a design such that the tunable range obtained of the specifications concerned is close to or more than the variations of the same for a 3 sigma variation of the process parameters. This fact is illustrated for a PA in Figure 7. Figure 7a shows the  $P_{out}$  vs.  $P_{in}$  for a PA with  $V_{dd}$  (supply voltage) varying within its tuning range. It can be seen that for higher supply voltages gain is lower (due to g<sub>m</sub> being lower at high values of I<sub>d</sub>), P<sub>1dB</sub> is higher and vice versa. So gain vs. P<sub>1dB</sub> tradeoff can be achieved by using supply as a tuning knob. Similarly even more tuning capability is achieved by using supply and bias of the PA as two tuning knobs simultaneously. Figure 7b plots the Pout vs. Pin for the PA over all combinations of supply and bias knob settings for 4 process instances, 0 being the nominal instance. It is to be noted that some of them (namely 2 & 3) exhibit 'small parameter variation' [46] and can be tuned back completely by choosing the right tuning knob values. On the other hand there are instances (like 1) which exhibit 'large parameter variation' and can only be tuned for its Gain and not P1dB. To understand how a specification changes with process and how it can be tuned back the Gain of an illustrative Transmitter (with tunable PA and

Mixer) is shown in Figure 7c for the nominal process and a varied process instance. For the nominal case the transmitter is to be biased at maximum gain. However, under variation this setting is not optimum for gain. So the job of the *healing algorithm* is to find out a new tuning knob setting such that the gain is closest to its nominal value for the varied process instance. Now there could be several such knob settings that provide the same gain. A *power conscious* self-healing system would choose the setting with minimum hit in power consumption. A *system level* power conscious self-healing framework would find a new setting that optimizes all the specifications for the system simultaneously while minimizing power.

### 2.3.2. System Level Healing Framework

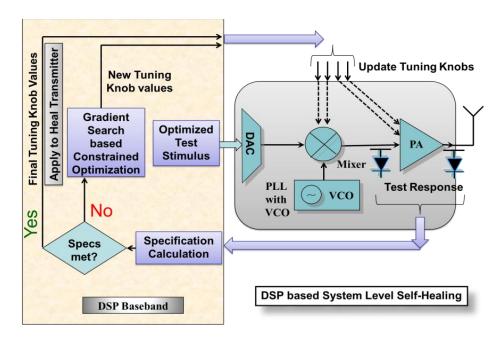

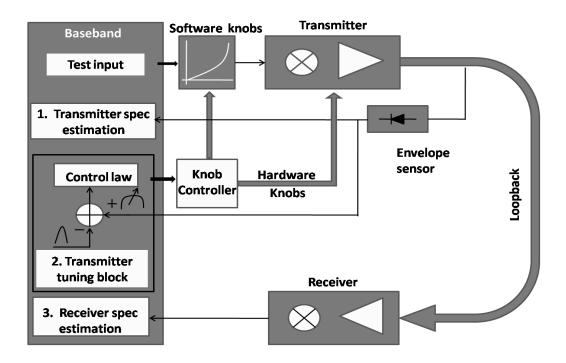

Figure 8: System Level Power Conscious Self-Healing Framework

The framework for power conscious system level self-healing is described below and is shown in Figure 8. The methodology consists of the following key steps:

• The system is made up of tunable components with built in tuning knobs.

- During production test/characterization/tune phase any instance with non-nominal specifications are tuned to be as close as possible to the nominal one.

- An optimized test stimulus is applied to the system with nominal tuning knob settings.

Important specifications are calculated from the test response using standard methods or alternate test methods [47] using built in sensors (as shown in Figure 8) for faster response time.

- If the specifications are within the preset bounds the device passes and the current knobs settings are to be applied while operation.

- If not, the device would have failed in static sense and should now be healed to try to pass it, so that the yield increases.

- A power conscious constraint optimization algorithm updates the knobs settings and repeats this procedure until the best knob setting for the given process is achieved.

- The final setting found from the optimizations is applied to the system during runtime operation.

- At the end of the optimization a significant number of instances are expected to meet all of the specifications (as 2 & 3 in Figure 7b), however there would be some that would still not meet all the specifications (as 4 in Figure 7b).

The detailed of this system level self-healing methodology is to be found in a co-authored work titled "Self-Healing RF SoCs: Low Cost Built-In Test and Control Driven Simultaneous Tuning of Multiple Performance Metrics" [50].

### 2.3.3. Need for Process Identification through testing

One aspect of achieving complete self-healing systems is to be able to test for the health of the RF system. Identifying the process corner of the manufactured device

requires low cost fast test techniques targeted towards key specifications. To make tuning/self-healing realistic or implementable in real production test phase it is important to tune the system within the time it takes to test the system using present techniques. This calls for orders of magnitude improvement in test times compared to standard testing methodologies. The process information gathered from the testing phase is then used by an algorithm to tune the system back to recover yield loss.

There have been significant efforts for developing fast and accurate test techniques. The most important being Alternate Test [47] that uses regression based techniques to map the response of a device to carefully crafted test stimulus to its specifications. This technique, though very useful in fast and accurate prediction of most of the specifications, does not perform well for some key specifications like amplitude to phase distortion (AM-PM) etc. Hence low cost test techniques targeted towards such key specifications are required. In this work we address this by developing a low cost rapid test methodology for AM-PM and IQ mismatch testing. The next chapter will first highlight the Alternate Test and then describe the development of new test techniques.

# Chapter 3. LOW COST TESTING FOR IDENTIFICATION OF PROCESS-VARIATION abcdeffwwgre

### 3.1. Previous Work

# 3.1.1. Alternate Testing

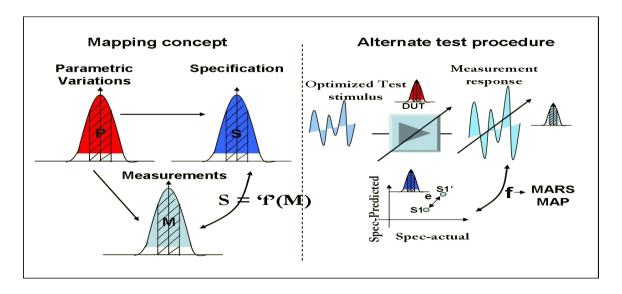

Conventional test strategies for mixed-signal, analog and RF circuits are based upon specification based testing techniques where the DUT specifications are measured and compared against pre-defined specification bounds to make pass/fail decisions for each specification. This requires a different test set-up for each specification resulting in an increase in test time and test cost. Alternate test [51]-[52] & [53], (as shown in Figure 9) on the other hand makes use of a single test configuration and predicts *all of the specifications of interest with a single input stimulus*, thereby, reducing the overall test time and test cost.

Figure 9: Alternate test framework