## SILICON-BASED RF/MM-WAVE POWER AMPLIFIERS AND TRANSMITTERS FOR FUTURE ENERGY-EFFICIENT AND BROADBAND COMMUNICATION SYSTEMS

A Dissertation Presented to The Academic Faculty

by

Song Hu

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology May 2017

## COPYRIGHT © 2017 BY SONG HU

### SILICON-BASED RF/MM-WAVE POWER AMPLIFIERS AND TRANSMITTERS FOR FUTURE ENERGY-EFFICIENT AND BROADBAND COMMUNICATION SYSTEMS

Approved by:

Dr. Hua Wang, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. John D. Cressler School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Maysam Ghovanloo School Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Gee-Kung Chang School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Haomin Zhou School of Mathematics *Georgia Institute of Technology*

Date Approved: March 30, 2017

To my family and friends

To the loving memory of my maternal grandfather

#### ACKNOWLEDGEMENTS

Time flies. It has been fifty-six months since I came to the United States and started the journey of my doctoral study. These fifty-six months turn out to be an important part of my life, which blend the memorable moments of excitement, accomplishments, and anxieties. As Mencius said, what a person can achieve is highly determined by the surrounding people. I could never reach this far without the insightful guidance and generous help from many people during this journey.

First, I'd like to express my sincerest gratitude to my doctoral advisor, Professor Hua Wang. Being a knowledgeable and wise person, Hua not only taught me technical skills and knowledge but also helped me establish and develop passionate, independent, creative yet principled minds in tackling challenges throughout my life. Hua's wisdom, vision, and enthusiasm will have a lifelong and profound influence on my future career. I cannot feel more proud to be your first doctoral student.

I am also very grateful to Professor John D. Cressler, Professor Maysam Ghovanloo, Professor Gee-Kung Chang, and Professor Haomin Zhou for being on my dissertation committee. I appreciate all your valuable feedback, which helped me improve this dissertation.

I feel very fortunate to have worked with world-renowned experts from industry in my field. I appreciate the inspiring technical discussions and meetings with Dr. Shouhei Kousai and Dr. Kohei Onizuka at Toshiba Corporation. I also would like to extend my appreciation to Toshiba for the generous support of silicon chip fabrication. I feel honored to be a member of Georgia Tech Electronics and Micro-System (GEMS) Lab. From every GEMS member and visiting scholar that I interacted with, including Jong Seok Park, Taiyun Chi, Tso-Wei Li, Fei Wang, Min-Yu Huang, Doohwan Jung, Moez Karim Aziz, Sensen Li, Edgar Garay, Huy Thong Nguyen, Bert Zhu, Choongsoon Kim, Michael Kroger, Juan Pablo Caram, Manoj Aripirala, Stefan Lepkowski, Chi-Hsien Chiu, Mohan Yang, Dr. Jun Luo, and Dr. Venkatesh Ramalingam, I learned a lot, including skills from BBQ to swimming and knowledge from English language to global cultures.

I'd like to thank all the other friends, especially Ming Yi, Yue Zhang, Chao Weng, Kehuang Li, Lingchen Zhu, Jason Chen, and Jialing Tong at Georgia Tech, who helped me during my early time in the United States.

In addition, I'd like to thank Professor Zhiliang Hong at Fudan University, who led me to the world of circuits and always supports me.

I owe my deepest gratitude to my family. My parents give me unconditional love and support at any time. No words in any languages can express my love to you. My dear maternal grandfather, I miss you from the bottom of my heart. I wish I could have been around you when you left us in 2015. I am sure you will be proud of my accomplishments.

> Song Hu Atlanta, GA Mar. 25, 2017

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                                                       | iv    |

|------------------------------------------------------------------------|-------|

| LIST OF TABLES                                                         | ix    |

| LIST OF FIGURES                                                        | X     |

| LIST OF SYMBOLS AND ABBREVIATIONS                                      | xviii |

| SUMMARY                                                                | xxi   |

| CHAPTER 1. Introduction                                                | 1     |

| 1.1 Background                                                         | 1     |

| <b>1.2 Efficiency Enhancement Techniques for CMOS RF PAs</b>           | 3     |

| <b>1.3 Linearization Techniques for CMOS RF PAs</b>                    | 10    |

| CHAPTER 2. A Transformer-Based Reconfigurable Digital Polar Doherty PA |       |

| Fully Integrated in Bulk CMOS                                          | 12    |

| 2.1 Digital Polar Doherty PA Architecture                              | 12    |

| 2.1.1 Digital Polar Doherty Architecture                               | 12    |

| 2.1.2 PA Core and Driver Design                                        | 14    |

| 2.2 Passive Network Designs in A Fully Integrated Doherty PA           | 15    |

| 2.2.1 Doherty Input Passive Network Design                             | 15    |

| 2.2.2 Doherty Output Passive Network Design                            | 17    |

| 2.3 Experimental Results                                               | 27    |

| 2.3.1 Continuous-Wave (CW) Measurement                                 | 27    |

| 2.3.2 Modulated Signal Measurement                                     | 30    |

| 2.4 Summary                                                            | 35    |

| CHAPTER 3. Antenna Impedance Variation Compensation By Exploiting A    | •     |

| Digital Doherty PA Architecture                                        | 36    |

| 3.1 Theoretical Modeling and Analysis of Digital Doherty PAs           | 37    |

| 3.1.1 A Behavioural Model for Doherty PAs                              | 37    |

| 3.1.2 The Doherty PA Model with a Lossy Output Network                 | 40    |

| 3.1.3 The Doherty PA Model with a Lossless Output Network              | 42    |

| <b>3.2</b> Antenna Impedance Variation Compensation and PA Performance |       |

| Enhancement by Exploiting the Digital Doherty PA Architecture          | 48    |

| 3.2.1 PA Performance Enhancement Examples                              | 49    |

| 3.2.2 Antenna Mismatch Compensation and PA Performance Enhancement by  |       |

| Utilizing the Digital Doherty PA Architecture                          | 51    |

| 3.2.3 Extending the Non-Clipping Antenna Impedance Region              | 64    |

| <b>3.3</b> Simulation Results                                          | 67    |

| 3.3.1 Effects of the Output Network Loss                               | 67    |

| 3.3.2 PA Efficiency Enhancement and Optimum PA Configurations for the  |       |

| Symmetric Doherty PA Design                                            | 69    |

|                                                                        |       |

| 3.3.3 Asymmetric Digital Doherty Design                                                                                      | 75                |

|------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 3.3.4 Incorporating Peak PBO                                                                                                 | 76                |

| 3.4 Experimental Results                                                                                                     | 77                |

| 3.4.1 CW Measurement                                                                                                         | 77                |

| 3.4.2 Modulated Signal Measurement                                                                                           | 80                |

| 3.5 Summary                                                                                                                  | 85                |

|                                                                                                                              | G                 |

| CHAPTER 4. A Broadband Mixed-Signal CMOS PA with a Hybrid Clas                                                               |                   |

| Doherty Efficiency Enhancement Technique                                                                                     | 86                |

| 4.1 Hybrid Class-G Doherty Efficiency Enhancement and CW Efficience<br>Measurement                                           | .y<br>86          |

| 4.1.1 Hybrid Class-G Doherty PA Architecture                                                                                 | 86                |

| 4.1.1 Hybrid Class-G Doherty PA Implementation                                                                               | 80<br>91          |

| 4.1.2 Tryona class-o Donerty FA Implementation<br>4.1.3 CW Measurement Results                                               | 97                |

| 4.2 Mixed-Signal Linearization and CW AM-PM Measurement                                                                      | 99                |

| 4.2.1 Amplitude Distortion Minimization in the Hybrid Class-G Doherty PA                                                     |                   |

| 4.2.2 Phase Distortions in the Hybrid Class-G Doherty PA                                                                     | 100               |

| 4.2.3 Introduced AM-PM Linearization Technique                                                                               | 100               |

| 4.2.4 CW Phase Measurement Results                                                                                           | 101               |

| 4.3 Doherty PA RF Bandwidth Extension and CW Bandwidth Measure                                                               |                   |

| 4.3.1 RF Bandwidth Extension Technique for Doherty PA                                                                        | 107               |

| 4.3.2 CW Measurement for Doherty PA RF Bandwidth Extension                                                                   | 108               |

| 4.4 Modulation Measurement Results                                                                                           | 110               |

| 4.4.1 PA Dynamic AM-PM Linearization                                                                                         | 111               |

| 4.4.2 Broadband Doherty PA Operation                                                                                         | 112               |

| 4.4.3 PA Efficiency Enhancement in Deep PBO                                                                                  | 113               |

| 4.5 Summary                                                                                                                  | 116               |

|                                                                                                                              | •41               |

| CHAPTER 5. A Compact Broadband Mixed-Signal PA in Bulk CMOS w                                                                |                   |

| Hybrid Class-G and Dynamic Load Trajectory Manipulation                                                                      | 118               |

| <b>5.1 Mixed-Signal Hybrid Class-G and DLTM PA Architecture</b><br>5.1.1 DLTM Scheme that Achieves PA PBO Efficiency Peaking | <b>118</b><br>118 |

| 5.1.2 Mixed-Signal Hybrid Class-G and DLTM PA Architecture                                                                   | 118               |

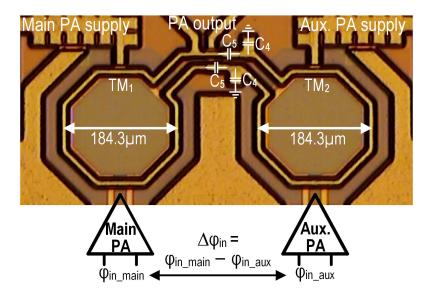

| 5.2 PA Implementation Details                                                                                                | 122<br>126        |

| 5.2.1 RF Power DAC and Class-G Supply Modulator                                                                              | 120               |

| 5.2.2 On-Chip Transformer-Based LM Network                                                                                   | 120               |

| 5.3 Experimental Results                                                                                                     | 133               |

| 5.3.1 CW Measurement                                                                                                         | 134               |

| 5.3.2 Modulation Measurement                                                                                                 | 138               |

| 5.4 Summary                                                                                                                  | 148               |

| -                                                                                                                            |                   |

| CHAPTER 6. A 28GHz/37GHz/39GHz Multiband Linear Doherty PA fo                                                                |                   |

| Massive MIMO Applications                                                                                                    | 149               |

| 6.1 A Broadband and Low-Loss On-Chip Doherty Output Network                                                                  | 150               |

| 6.2 Power-Dependent Doherty PA Uneven-Feeding Scheme                                                                         | 154               |

| 6.3 Experimental Results                                                                                                     | 155               |

| 6.4 Summary                                                                                                                  | 160               |

| CHAPTER 7. Conclusions                     | 161 |

|--------------------------------------------|-----|

| 7.1 Research Summary                       | 161 |

| 7.2 Key Research Contributions             | 162 |

| 7.3 Research Publications                  | 163 |

| 7.3.1 First-Author Journal Publications    | 163 |

| 7.3.2 Co-Author Journal Publications       | 164 |

| 7.3.3 First-Author Conference Publications | 165 |

| 7.3.4 Co-Author Conference Publications    | 166 |

| 7.3.5 Book Chapter                         | 167 |

| 7.4 Research Awards                        | 167 |

| 7.5 Future Research                        | 168 |

| REFERENCES                                 |     |

# LIST OF TABLES

| Table 1  | - Measurement results with different control code optimization methods                                                                                           | 33  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2  | <ul> <li>Performance summary and comparison with other CMOS Doherty PAs</li> </ul>                                                                               | 34  |

| Table 3  | <ul> <li>Modulation performance comparison with CMOS PAs using other<br/>back-off efficiency enhancement techniques</li> </ul>                                   | 34  |

| Table 4  | – Summary of the analytical results on antenna impedance variation compensation and PA performance enhancement by exploiting the digital Doherty PA architecture | 63  |

| Table 5  | - Minimally required peak PBO for the clipping load condition                                                                                                    | 66  |

| Table 6  | - Measured efficiency optimum configurations in various load conditions                                                                                          | 80  |

| Table 7  | - Measured efficiency and linearity with mismatched loads using different code sets for the QPSK signal                                                          | 84  |

| Table 8  | <ul> <li>Measured efficiency and linearity with mismatched loads using<br/>different code sets for the 16-QAM signal</li> </ul>                                  | 84  |

| Table 9  | - Performance comparison with other PBO efficiency enhanced CMOS PAs                                                                                             | 117 |

| Table 10 | - Performance comparison with other PBO efficiency enhanced CMOS PAs                                                                                             | 147 |

| Table 11 | - Dual varactor control settings that cover three mm-wave 5G bands                                                                                               | 156 |

| Table 12 | - Comparison with recently reported mm-wave silicon PAs                                                                                                          | 160 |

# LIST OF FIGURES

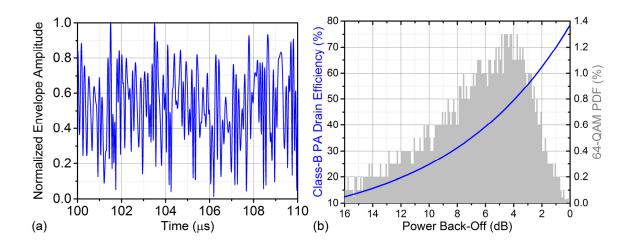

| Figure 1  | - (a) Normalized envelope amplitude and (b) power probability density function (PDF) for a 10MSym/s 64-QAM signal with $PAPR = 5.8$ dB. The efficiency curve of an ideal Class-B PA is also plotted in (b). | 2  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | - Summary and categorization of existing PA PBO efficiency enhancement techniques.                                                                                                                          | 4  |

| Figure 3  | <ul> <li>(a) Schematic of a Class-G PA with a 2-level (1-bit) supply<br/>modulator. (b) Theoretical PA efficiency behavior of a 2-level<br/>Class-G PA.</li> </ul>                                          | 5  |

| Figure 4  | <ul> <li>– (a) Schematic of a classic 2-way Doherty PA. (b) Theoretical PA efficiency behavior of a classic symmetric 2-way Doherty PA. (c) Concept of the active LM effect.</li> </ul>                     | 6  |

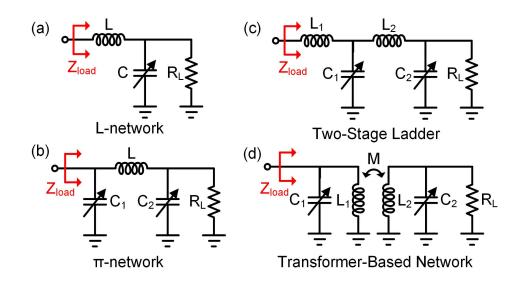

| Figure 5  | - Existing PA load tuning networks.                                                                                                                                                                         | 9  |

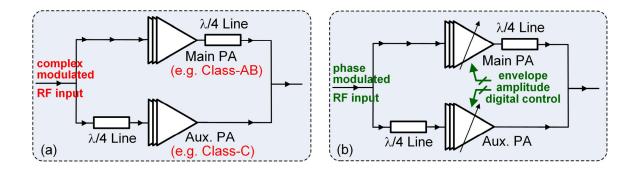

| Figure 6  | <ul> <li>– (a) Conventional analog Doherty PA. (b) Introduced digital polar<br/>Doherty PA architecture.</li> </ul>                                                                                         | 13 |

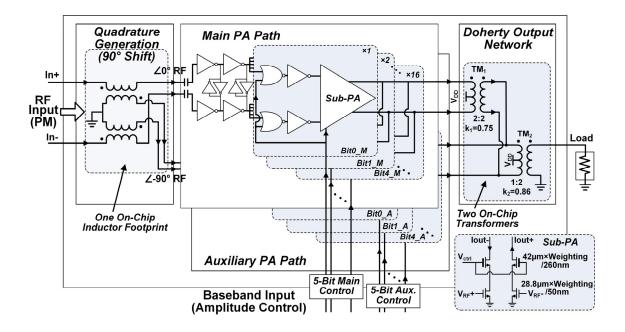

| Figure 7  | - Schematic of a digital polar Doherty PA.                                                                                                                                                                  | 15 |

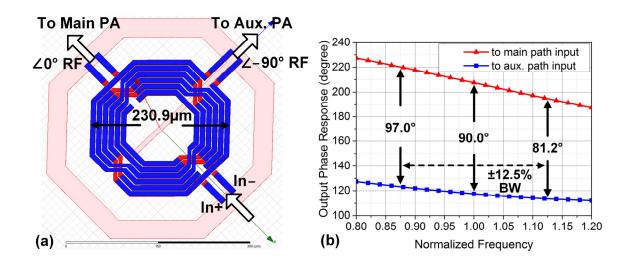

| Figure 8  | <ul> <li>(a) Six-port folded-transformer-based differential quadrature generation structure.</li> <li>(b) EM simulation results showing the wideband differential quadrature generation.</li> </ul>         | 16 |

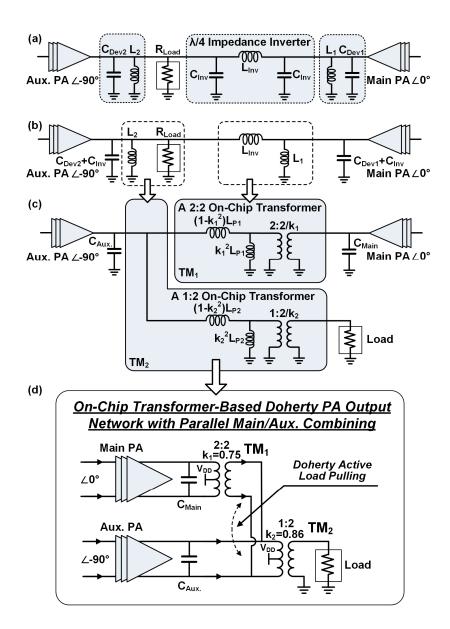

| Figure 9  | – Introduced parallel-combining-transformer-based Doherty output passive network.                                                                                                                           | 18 |

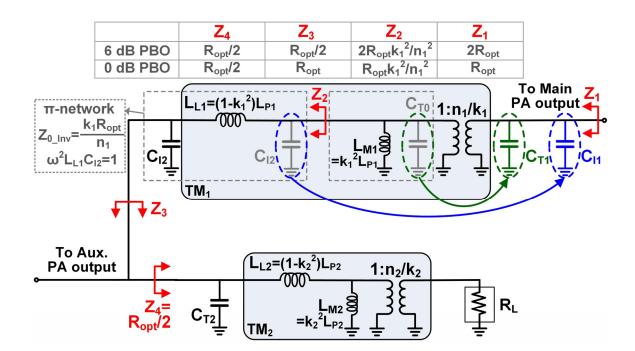

| Figure 10 | - Design methodology for the introduced PCT-based Doherty output network.                                                                                                                                   | 19 |

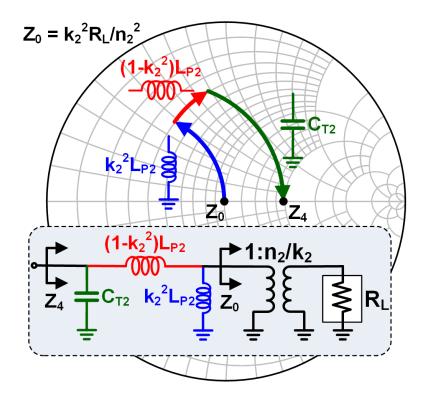

| Figure 11 | - Explanation on the Smith chart for the effects of the non-ideal magnetic coupling in the impedance down-scaling transformer.                                                                              | 21 |

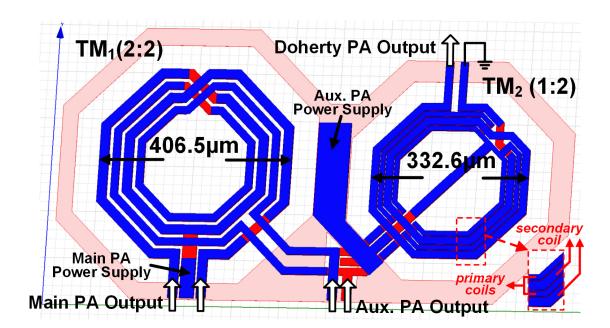

| Figure 12 | - Implementation of the introduced Doherty output passive network.                                                                                                                                          | 26 |

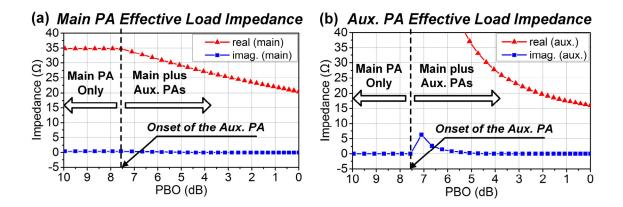

| Figure 13 | - Effective load impedance for the main and auxiliary PAs based<br>on the EM-simulated Doherty output passive network. Device<br>output parasitic capacitors and constant tuning capacitors are             | 26 |

|           | included. The two PA RF currents are assumed to follow ideal Doherty operation.                                                                                   |    |

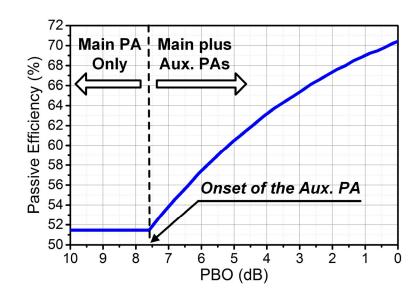

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 14 | – Simulation results of the PE with the EM-simulated Doherty output passive network.                                                                              | 27 |

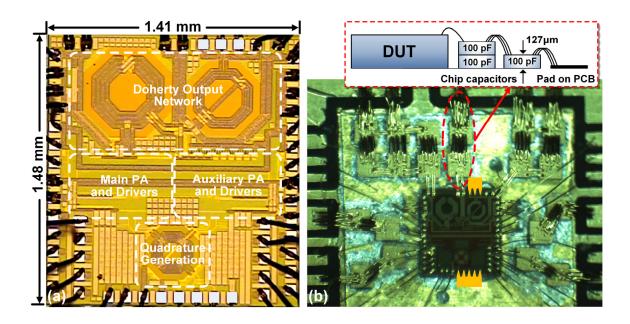

| Figure 15 | - (a) Chip microphotograph. (b) Chip assembly.                                                                                                                    | 28 |

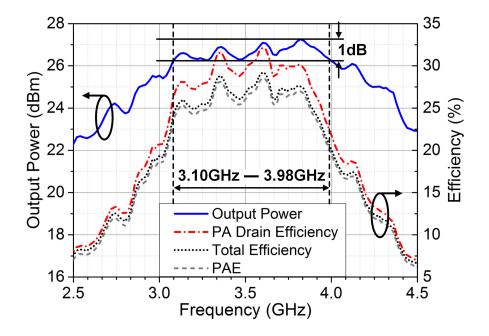

| Figure 16 | - Measured PA Pout and efficiencies.                                                                                                                              | 29 |

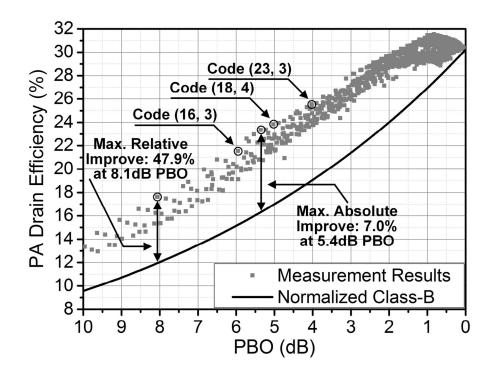

| Figure 17 | – Measured PA drain efficiency (DE) with the 50 $\Omega$ standard load.                                                                                           | 29 |

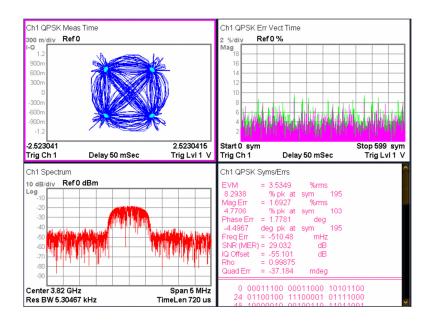

| Figure 18 | – Modulation test with 1MSym/s QPSK at +23.5dBm average $P_{out}$ and 26.8% PA DE.                                                                                | 30 |

| Figure 19 | – Modulation tests with 500kSym/s 16QAM when applying (a) efficiency optimum codes, and (b) linearity optimum codes for all the power levels.                     | 31 |

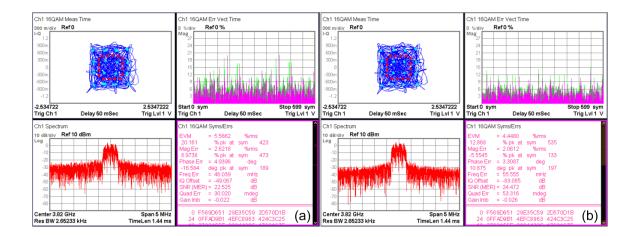

| Figure 20 | - (a) Measured large signal phase response referred to the value at the peak P <sub>out</sub> and (b) relative PA DE improvement over Class-B for LOCs and EOCs.  | 32 |

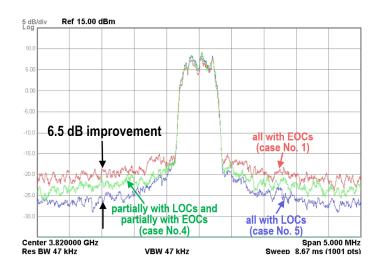

| Figure 21 | – OOB linearity comparison when applying different code selection strategies. See Table 1 for the configurations in different cases.                              | 33 |

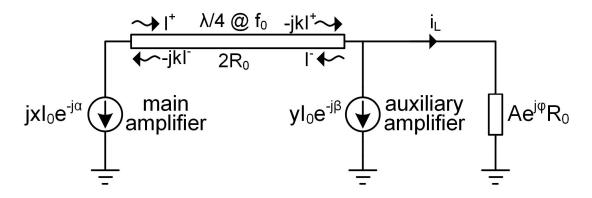

| Figure 22 | - Introduced Doherty PA model.                                                                                                                                    | 38 |

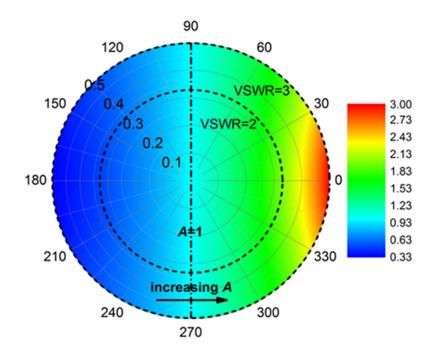

| Figure 23 | - Values of A for the impedance within the VSWR=3:1 circle.                                                                                                       | 39 |

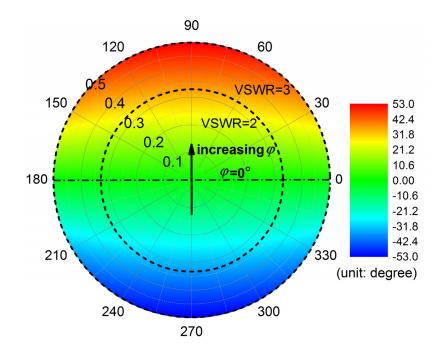

| Figure 24 | – Values of $\varphi$ for the impedance within the VSWR=3:1 circle.                                                                                               | 39 |

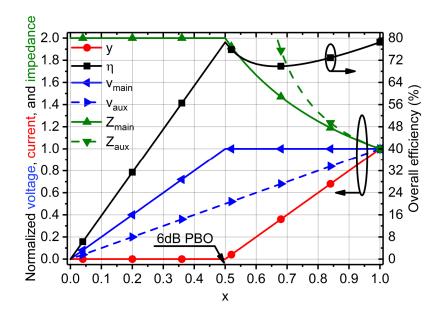

| Figure 25 | – Simulated performance for a conventional symmetric analog<br>Doherty PA based on the introduced model. The antenna<br>impedance is assumed to have no mismatch. | 46 |

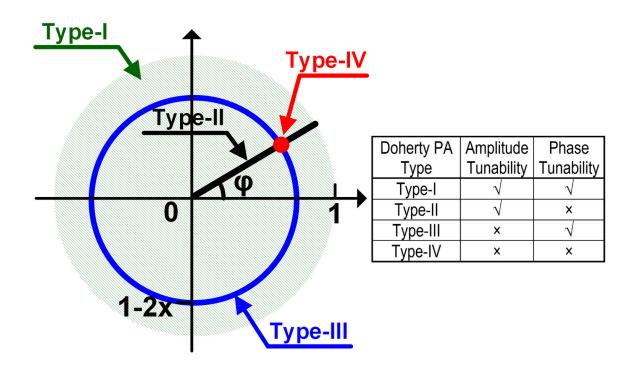

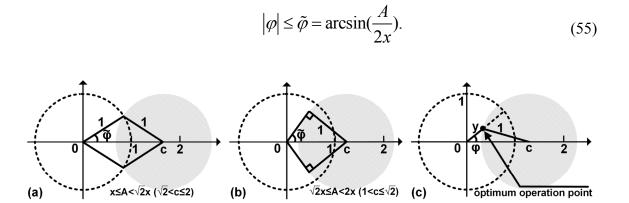

| Figure 26 | - Valid PA operation regions for the four Doherty PA types. (The main and auxiliary amplifiers are assumed to be symmetric in this plot.)                         | 54 |

| Figure 27 | - Unconditional clipping scenario for Type-I and II Doherty PAs.                                                                                                  | 56 |

| Figure 28 | - Unconditional clipping scenario for Type-III and IV Doherty PAs.                                                                                                | 56 |

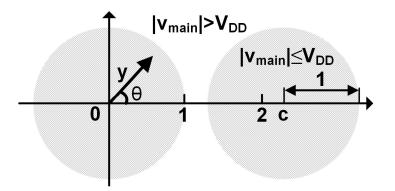

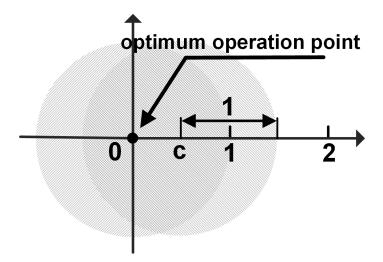

| Figure 29 | – Unconditional non-clipping scenario for Type-I and II Doherty PAs ( $0 \le c \le 1$ ).                                                                          | 57 |

| Figure 30 | – Unconditional non-clipping scenario for Type-I Doherty PA $(1 \le c \le 2)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

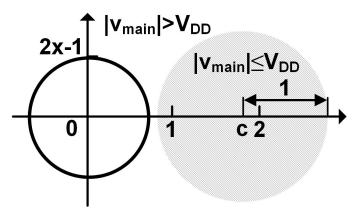

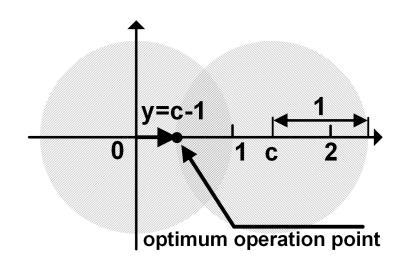

| Figure 31 | - Unconditional non-clipping scenario for Type-III Doherty PA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59 |

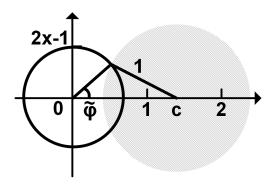

| Figure 32 | - Unconditional non-clipping scenario for Type-IV Doherty PA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60 |

| Figure 33 | - Conditional non-clipping scenario for Type-II Doherty PA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61 |

| Figure 34 | - Conditional non-clipping scenario for Type-IV Doherty PA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62 |

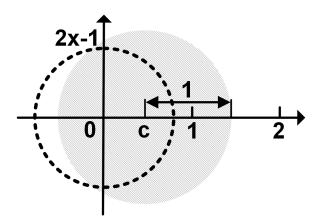

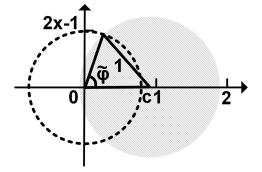

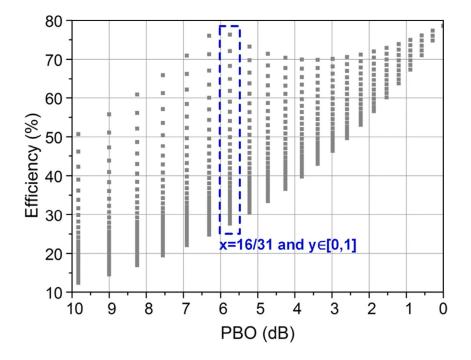

| Figure 35 | – Comparison of the required TMN in single-branch PA and digital Doherty PA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 65 |

| Figure 36 | – Simulated efficiency with a lossless output network ( $k=1$ in Figure 22).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68 |

| Figure 37 | - Simulated efficiency with a lossy output network ( $k=0.8$ in Figure 22).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 68 |

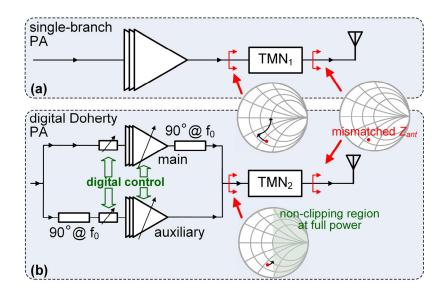

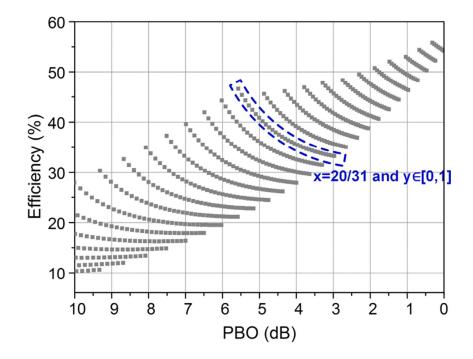

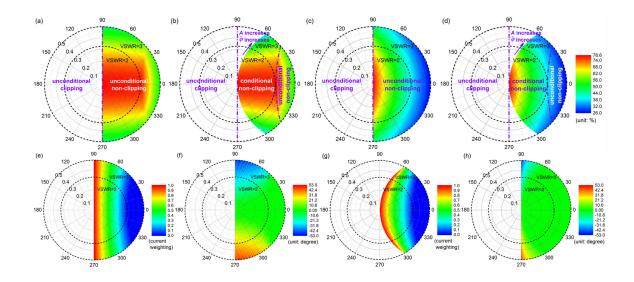

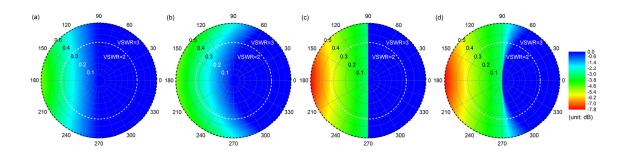

| Figure 38 | – Optimized PA efficiencies and the required PA tuning parameters<br>at the peak PA P <sub>out</sub> ( $x=1$ ) for different load conditions. (a)-(d) show<br>the PA drain efficiencies for Type-I to IV Doherty PAs. They share<br>the same color bar shown in (d). Due to the Class-B operation<br>assumption, the efficiency at the matched load is 78.5% for this<br>peak PA P <sub>out</sub> case. (e) and (f) are the required y and ( $\alpha-\beta$ ) for Type-<br>I Doherty PA to achieve the optimum PA efficiency; (g) is the<br>required y for Type-II Doherty PA; (h) is the required ( $\alpha-\beta$ ) for<br>Type-III Doherty PA. | 70 |

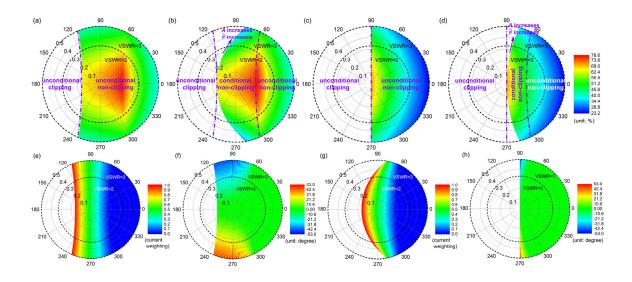

| Figure 39 | – Optimized PA efficiencies and the required PA tuning parameters<br>at 3 dB PBO ( $x=22/31$ ) for different load conditions. (a)-(d) are the<br>PA drain efficiencies for Type-I to IV Doherty PAs. They share the<br>same color bar shown in (d). Due to the Class-B operation<br>assumption, the efficiency at the matched load is 70.2% for this 3<br>dB PBO case. (e) and (f) are the required y and ( $\alpha-\beta$ ) for Type-I<br>Doherty PA to achieve the optimum PA efficiency; (g) is the<br>required y for Type-II Doherty PA; (h) is the required ( $\alpha-\beta$ ) for<br>Type-III Doherty PA.                                   | 71 |

| Figure 40 | - Optimized PA efficiencies and the required PA tuning parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76 |

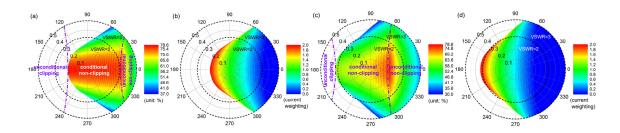

Figure 40 – Optimized PA efficiencies and the required PA tuning parameters for an asymmetrical (main/auxiliary = 1:2) Type-II Doherty PA at different load conditions. (a) and (b) show the PA efficiency and the required *y* at full power. (c) and (d) show the PA efficiency and the required *y* at 3 dB PBO.

| Figure 41 | - The minimally required peak PBO. (a)-(d) are the results for Type-I to IV Doherty PAs, respectively.                                                                                                                                                                                                                                                                                                                                            | 77 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 42 | – Measured PA efficiency with the 50 $\Omega$ standard load (3.6GHz, VSWR=1).                                                                                                                                                                                                                                                                                                                                                                     | 78 |

| Figure 43 | – Measured PA efficiency with the load at VSWR=2:1, phase( $\Gamma$ )=+60° (3.6GHz).                                                                                                                                                                                                                                                                                                                                                              | 79 |

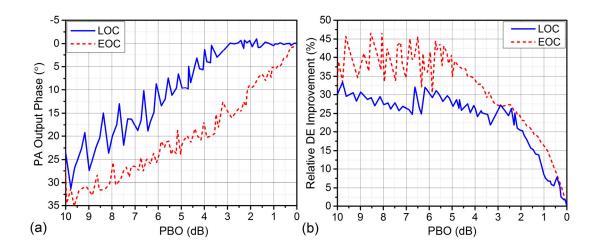

| Figure 44 | – Measured (a) EVM and (b) ACLR with the load at VSWR=2:1, phase( $\Gamma$ )=+60° at 3.6 GHz using the EOCS.                                                                                                                                                                                                                                                                                                                                      | 83 |

| Figure 45 | – Measured (a) EVM and (b) ACLR with the load at VSWR=2:1, phase( $\Gamma$ )=+60° at 3.6 GHz using the DCS.                                                                                                                                                                                                                                                                                                                                       | 83 |

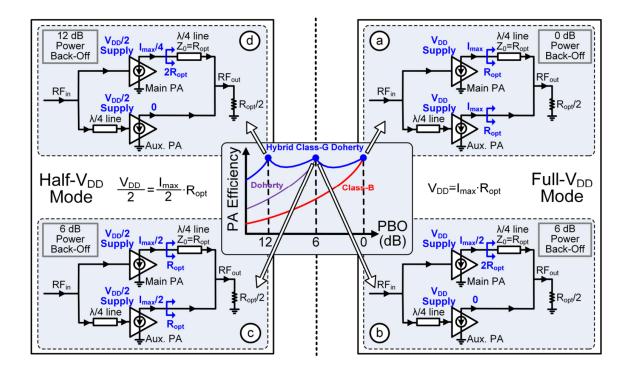

| Figure 46 | – Introduced hybrid Class-G Doherty operation and its theoretical PA efficiency behavior. The main and auxiliary PAs are assumed to be identical RF power DACs with zero knee voltages. All the harmonics are assumed to be terminated as short to ground.                                                                                                                                                                                        | 87 |

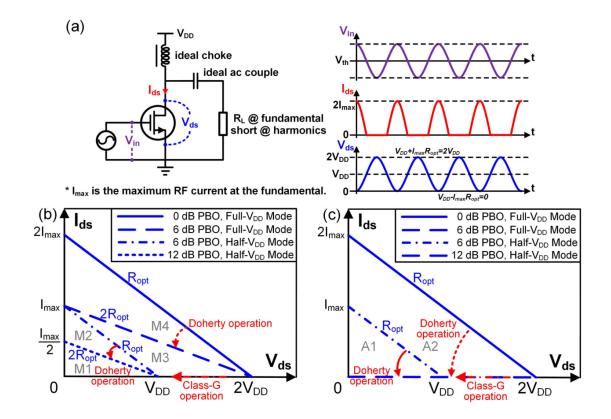

| Figure 47 | – The load-line analysis for the introduced hybrid Class-G Doherty PA operation. (a) The voltage and current definitions with their waveform illustrations at peak $P_{out}$ . (b) The main PA's load-line behavior. (c) The auxiliary PA's load-line behavior. Class-B operation with zero knee voltage is assumed for both PAs. PA $P_{out}$ can be calculated based on the area enclosed by the load lines and the $I_{ds}$ and $V_{ds}$ axes. | 90 |

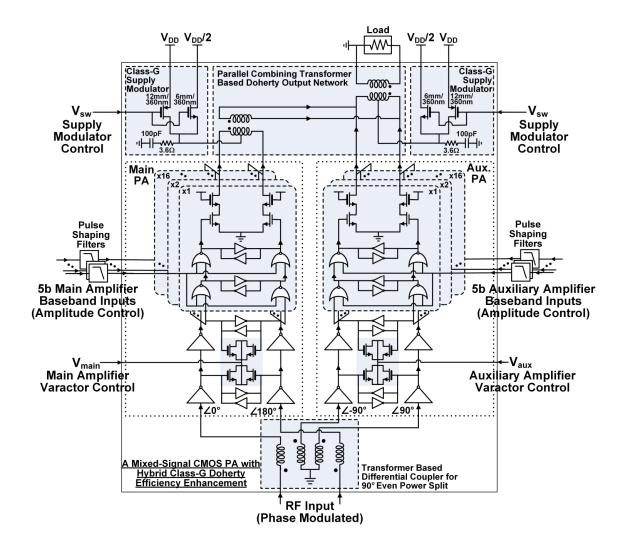

| Figure 48 | <ul> <li>Schematic of the proof-of-concept Class-G Doherty PA design<br/>fully integrated in a standard 65 nm bulk CMOS process.</li> </ul>                                                                                                                                                                                                                                                                                                       | 92 |

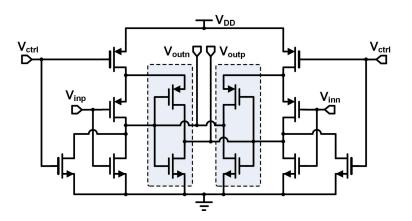

| Figure 49 | – Schematic of the NOR gate digital driver circuit, and similar circuits are used for the last two stage drivers. The cross-coupled inverters are highlighted in the dotted boxes.                                                                                                                                                                                                                                                                | 93 |

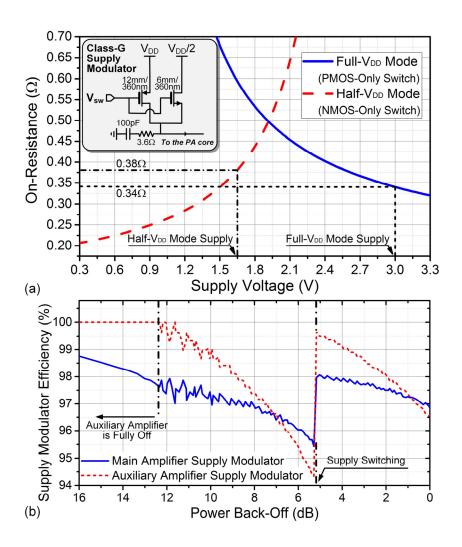

| Figure 50 | -(a) Simulated on-resistance for the Class-G supply modulator. (b) Simulated efficiency for the supply modulators of the main and auxiliary amplifiers.                                                                                                                                                                                                                                                                                           | 94 |

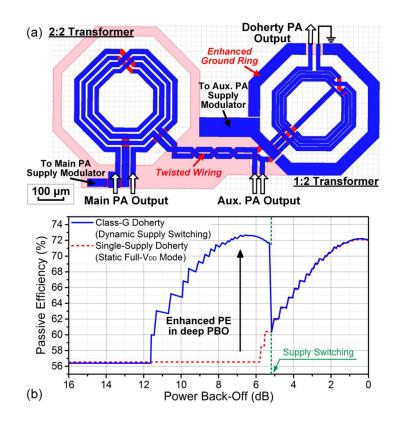

| Figure 51 | - (a) The Doherty output passive network implemented in hybrid<br>Class-G Doherty PA. (b) Simulated PE of the PCT Doherty output<br>network for the hybrid Class-G Doherty operation and the<br>conventional Doherty operation. The passive structures are 3D<br>EM-modelled, and the transistor-level PA cells program the PBO<br>and provide the parasitic loadings.                                                                            | 96 |

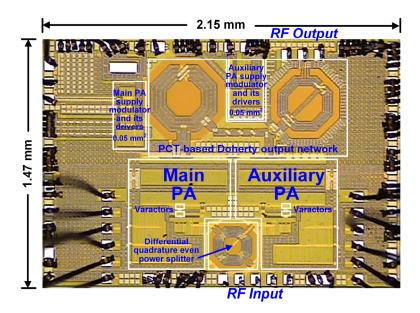

| Figure 52 | – Chip microphotograph                                                                                                                                                                                                                                                                                                                                                                                                                            | 97 |

Figure 52 – Chip microphotograph.

97

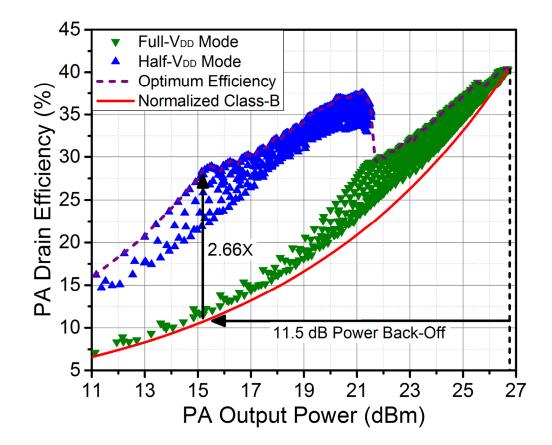

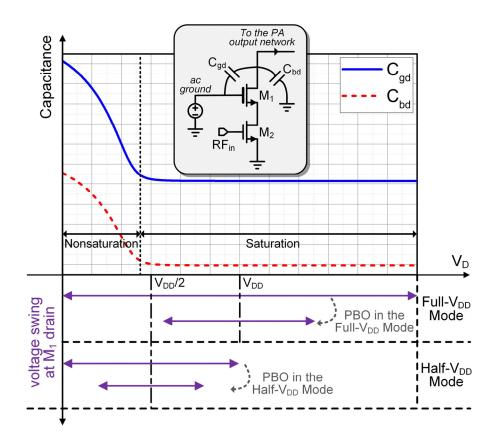

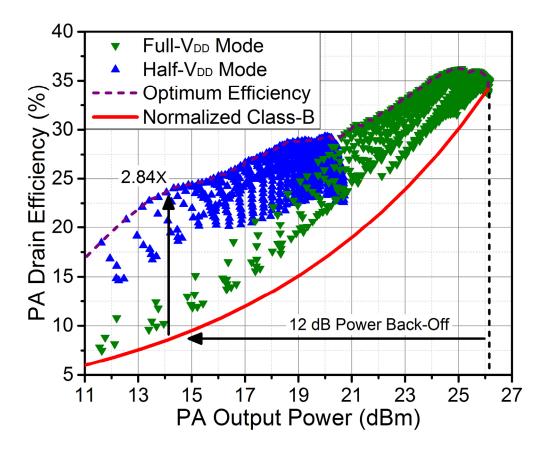

| Figure 53 | – Measured PA DE at 3.71 GHz versus PA $P_{\text{out}}$ in CW measurement.                                                                                                            | 98  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 54 | – Measured AM-AM error for the EOCs up to 12 dB PBO.                                                                                                                                  | 99  |

| Figure 55 | – Simulated AM-PM response of the PA digital driver chain (from Doherty PA input to $Class-D^{-1}$ PA core input).                                                                    | 101 |

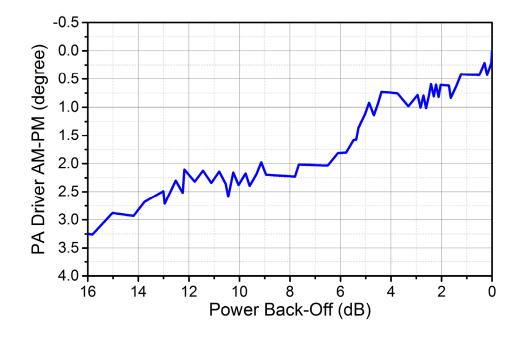

| Figure 56 | - Conceptual illustration for the drain output nonlinear capacitance<br>of a cascode PA during PBO and Class-G supply switching<br>operation. The knee voltage is assumed to be zero. | 102 |

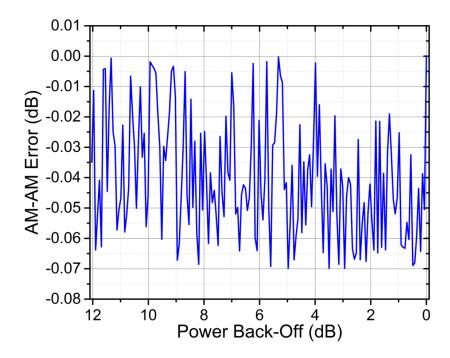

| Figure 57 | – Measured total PA AM-PM response for the efficiency-optimum codes at 3.71 GHz.                                                                                                      | 103 |

| Figure 58 | – Measured (a) PA phase response, (b) $P_{out}$ , and (c) DE when adjusting the varactor control voltages with all the power cells on at 3.71 GHz.                                    | 107 |

| Figure 59 | – Measured (a) PA P <sub>out</sub> and (b) DE for different varactor settings when all the power cells are on at different RF frequencies.                                            | 109 |

| Figure 60 | – Measured PA DE at 4.3 GHz showing Class-G Doherty operation and substantial PA PBO efficiency enhancement.                                                                          | 110 |

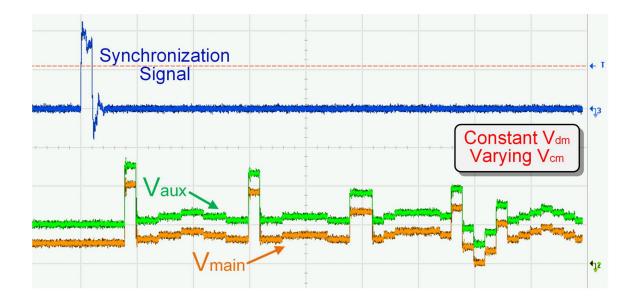

| Figure 61 | <ul> <li>Measured dynamically tuned varactor control voltages for AM-<br/>PM linearization in modulation measurements.</li> </ul>                                                     | 111 |

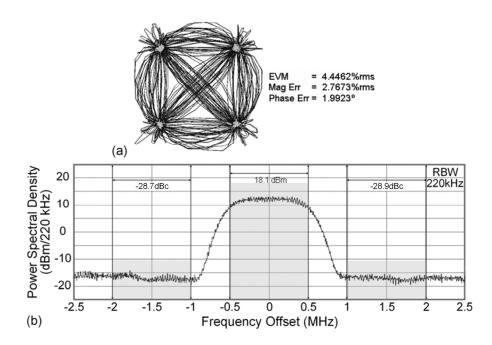

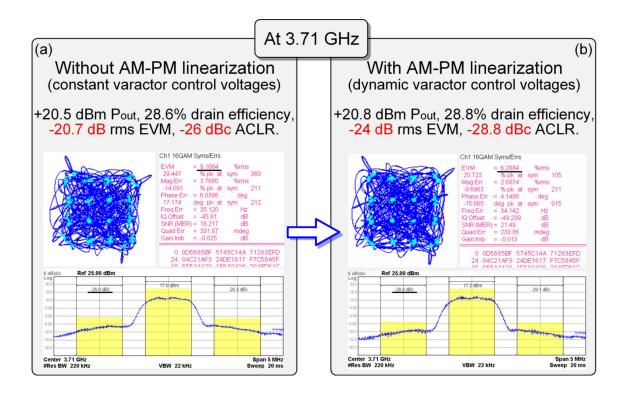

| Figure 62 | – Measured PA performance at 3.71 GHz (a) with and (b) without AM-PM linearization.                                                                                                   | 112 |

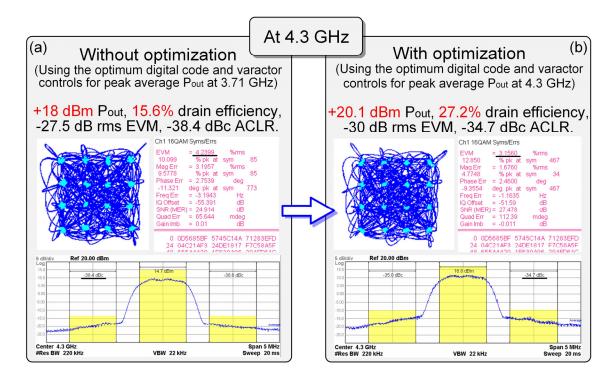

| Figure 63 | - Optimized broadband Doherty PA operation by mixed-signal reconfigurability.                                                                                                         | 113 |

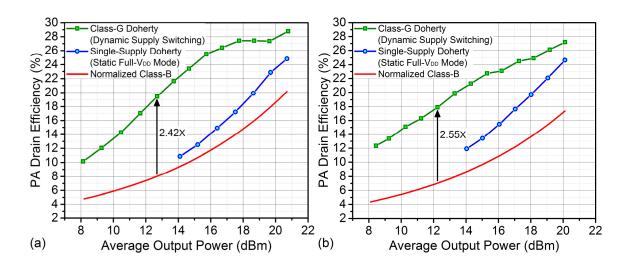

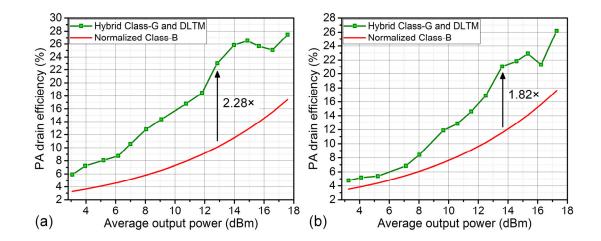

| Figure 64 | – Measured PA DE when backing-off the average $P_{out}$ in modulation tests at (a) 3.71 GHz and (b) 4.3 GHz.                                                                          | 114 |

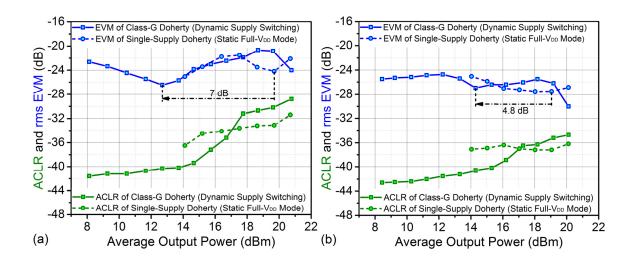

| Figure 65 | – Measured EVM (in-band linearity) and ACLR (OOB linearity) when backing-off the average $P_{out}$ in modulation tests at (a) 3.71 GHz and (b) 4.3 GHz.                               | 114 |

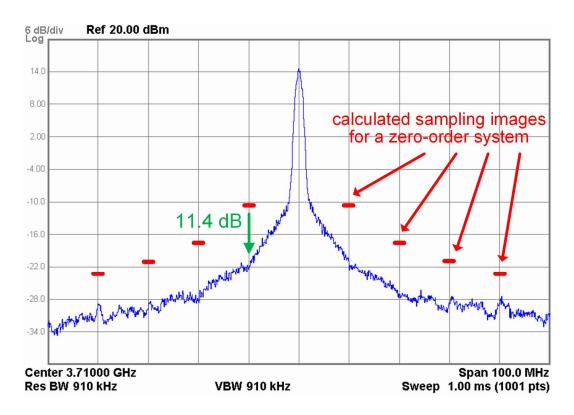

| Figure 66 | – Measured far-out-of-band spectrum for a $+20.8$ dBm 1MSym/s 16-QAM signal with $10 \times$ oversampling.                                                                            | 115 |

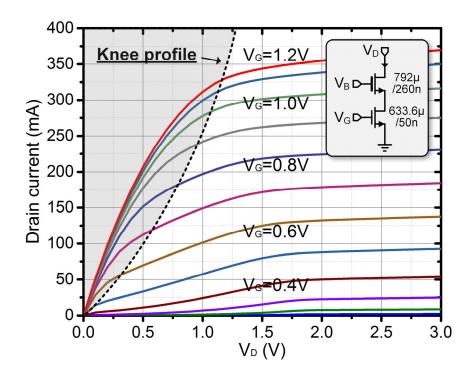

| Figure 67 | – Simulated I-V characteristic of a cascode MOSFET configuration.                                                                                                                     | 119 |

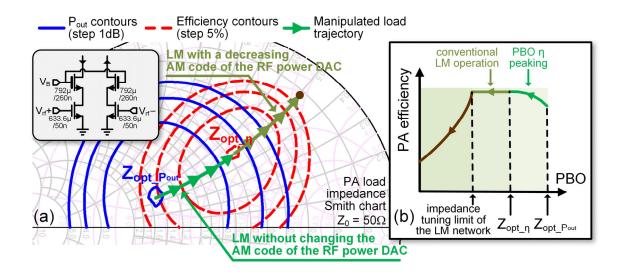

| Figure 68 | - (a) DLTM operation achieving PA PBO efficiency peaking and (b) its theoretical efficiency curve. The large-signal load-pull simulation result of the cascode circuit in Figure 67 is used here for illustration; it operates in a differential Class- $D^{-1}$ configuration at 2.4GHz.                                                                                                   | 120 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

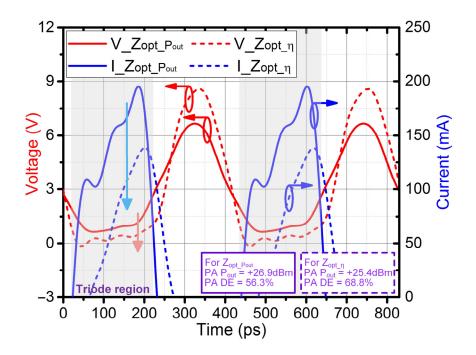

| Figure 69 | – Simulated drain current and voltage waveforms of the cascode circuit in Figure 67 when it operates in a differential Class- $D^{-1}$ configuration. Results for $Z_{opt_\eta}$ and $Z_{opt_Pout}$ as the fundamental load impedance are compared. Even and odd harmonics are terminated as open and short-to-ground up to the 6 <sup>th</sup> and 5 <sup>th</sup> harmonic, respectively. | 122 |

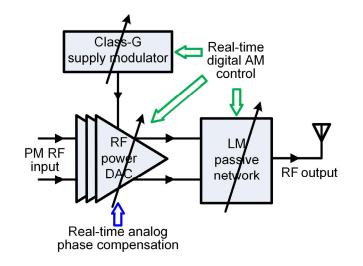

| Figure 70 | – Mixed-signal hybrid Class-G and DLTM PA architecture.                                                                                                                                                                                                                                                                                                                                     | 123 |

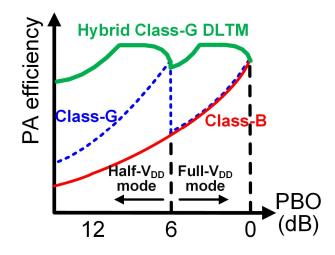

| Figure 71 | – Theoretical efficiency curve of the hybrid Class-G and DLTM PA.                                                                                                                                                                                                                                                                                                                           | 124 |

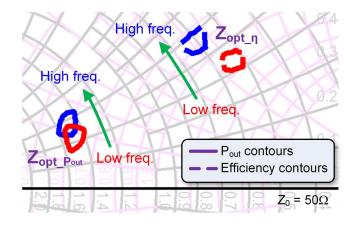

| Figure 72 | – Load-pull simulation results at different RF frequencies (2.1GHz and 2.8GHz) for the cascode circuit in Figure 67 when it operates in a differential Class- $D^{-1}$ configuration.                                                                                                                                                                                                       | 125 |

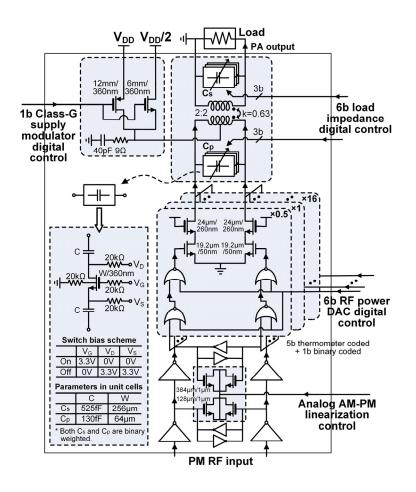

| Figure 73 | - Simplified schematic of the prototype PA implementation in a standard CMOS 65nm process.                                                                                                                                                                                                                                                                                                  | 126 |

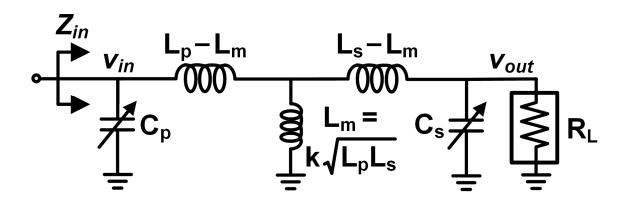

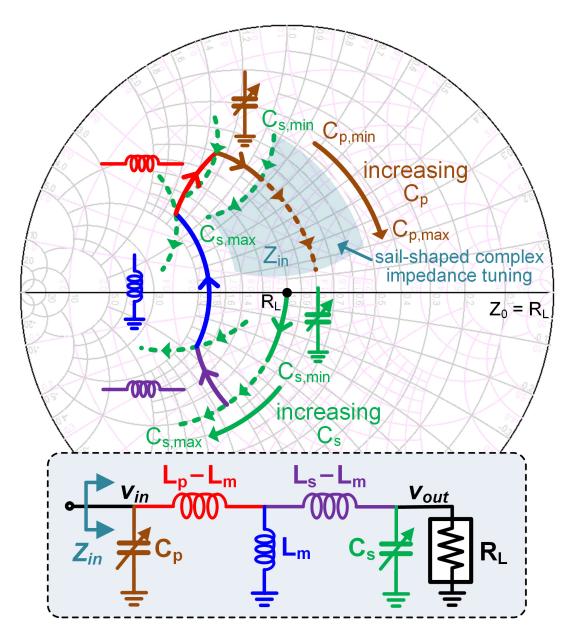

| Figure 74 | - Analysis model of the on-chip transformer-based LM network.                                                                                                                                                                                                                                                                                                                               | 128 |

| Figure 75 | – Smith chart illustration for the impedance tuning characteristic of the transformer-based LM network. The network is assumed to be lossless for simplicity in this figure.                                                                                                                                                                                                                | 129 |

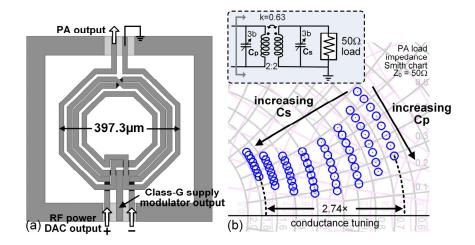

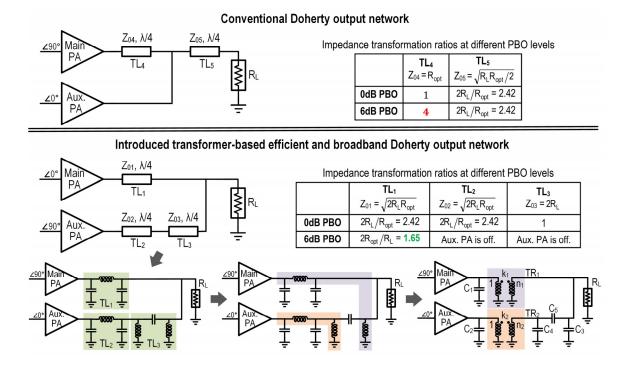

| Figure 76 | – (a) EM structure of the transformer and (b) simulated ITR of the LM network.                                                                                                                                                                                                                                                                                                              | 132 |

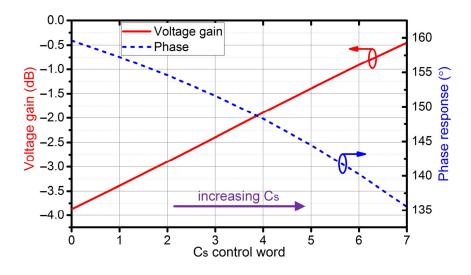

| Figure 77 | – Simulated voltage gain and phase response of the LM network when $C_s$ is tuned.                                                                                                                                                                                                                                                                                                          | 132 |

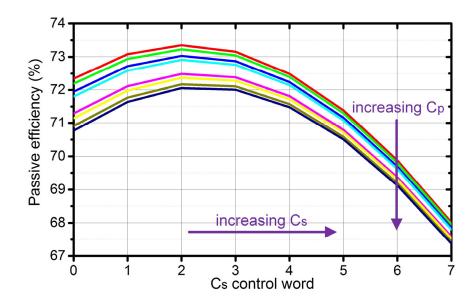

| Figure 78 | – Simulated PE of the LM network for all the settings.                                                                                                                                                                                                                                                                                                                                      | 133 |

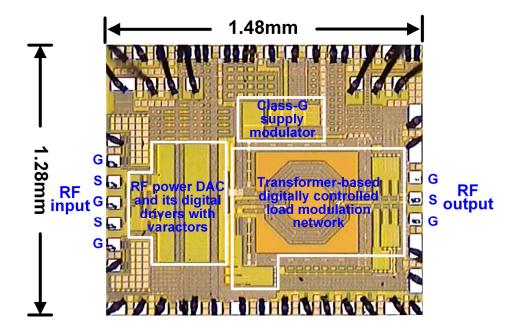

| Figure 79 | - Chip microphotograph.                                                                                                                                                                                                                                                                                                                                                                     | 133 |

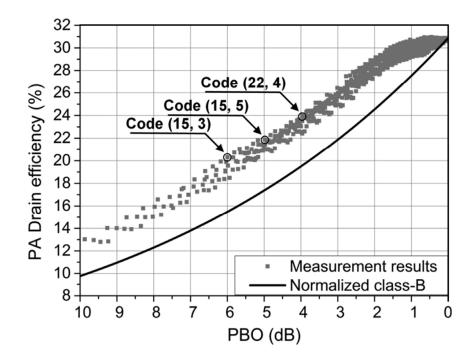

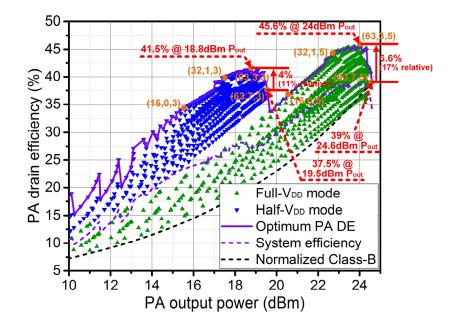

| Figure 80 | – Measured PA DE at 2.4GHz versus PA $P_{out}$ in CW measurement.<br>Representative control words are shown and they are formated as<br>(power DAC code, $C_s$ code, $C_p$ code).                                                                                                                                                                                                           | 135 |

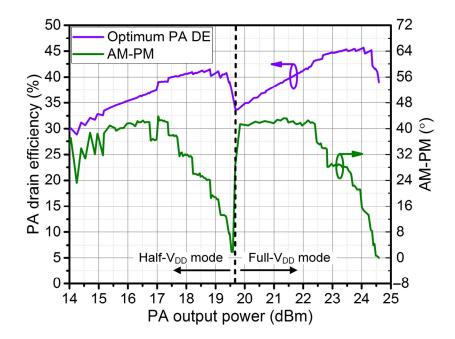

| Figure 81 | - Measured PA AM-PM of the efficiency-optimum settings at 2.4GHz.                                                                                                                                                                                                                                                                                                                           | 135 |

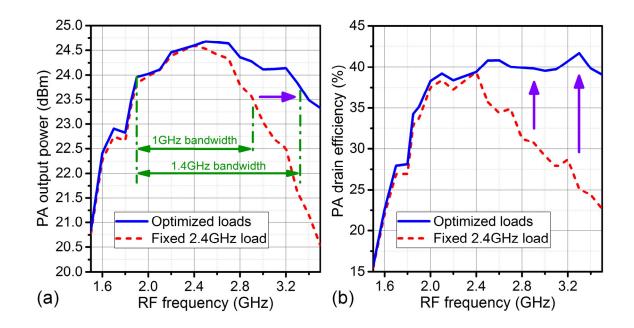

| Figure 82 | <ul> <li>– PA carrier bandwidth extension by LM in CW measurement for</li> <li>(a) PA P<sub>out</sub> and (b) PA DE.</li> </ul>                                                                                                                                                                          | 136 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

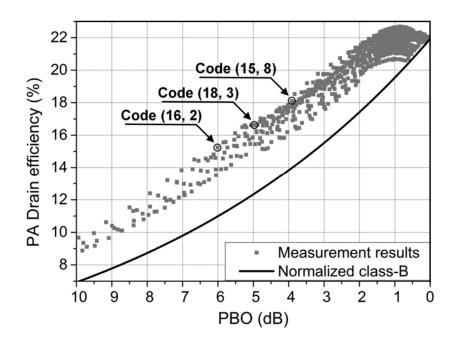

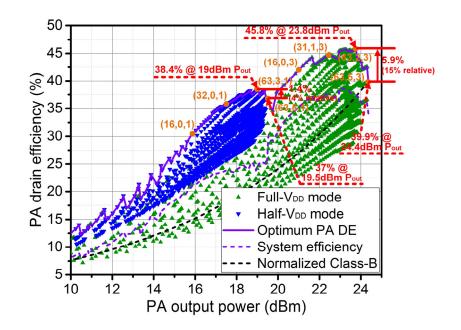

| Figure 83 | – Measured PA DE at 2.8GHz versus PA $P_{out}$ in CW measurement.<br>Representative control words are shown and they are formated as<br>(power DAC code, $C_s$ code, $C_p$ code).                                                                                                                        | 137 |

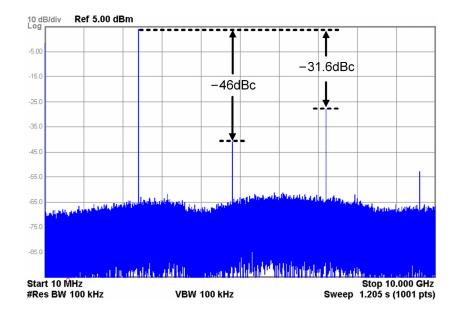

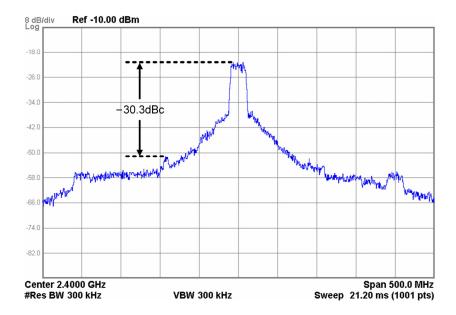

| Figure 84 | – Measured PA output spectrum for peak CW $P_{out}$ at 2.4GHz without any additional filtering. A 20dB attenuator is used at the PA output in this measurement.                                                                                                                                          | 137 |

| Figure 85 | - Simplified measurement setup for modulation measurement.                                                                                                                                                                                                                                               | 138 |

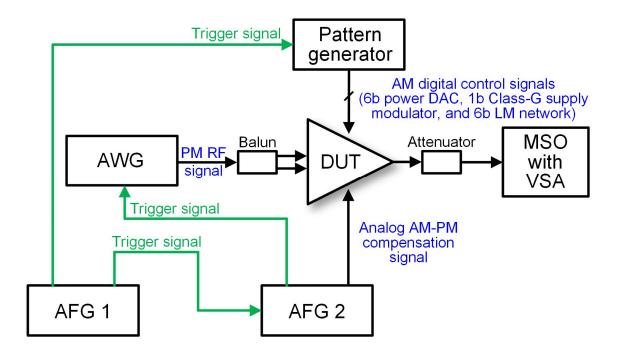

| Figure 86 | – Waveform examples of the synchronized PM RF signal, digital AM control signal, and dynamic varactor analog control signal at a sampling rate of 100MSa/s.                                                                                                                                              | 139 |

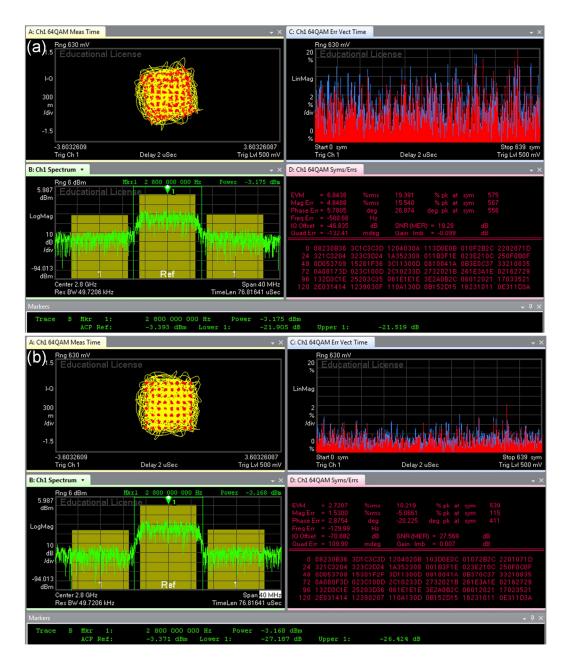

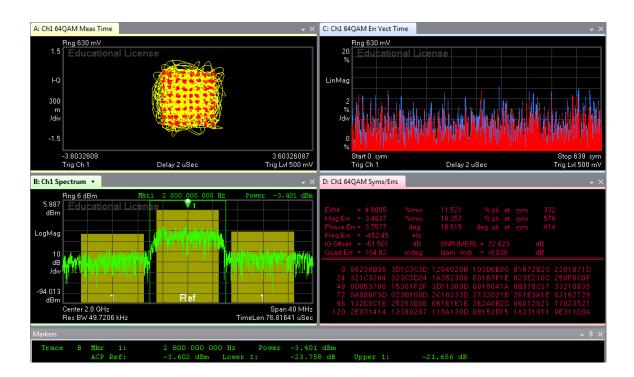

| Figure 87 | – Measurement results for 10MSym/s 64QAM at 2.8GHz: (a) with a constant varactor control voltage (+17.3dBm average PA $P_{out}$ , 25.5% PA DE) and (b) with the dynamic analog tuning of the varactor control voltage (+17.3dBm average PA $P_{out}$ , 26.2% PA DE).                                     | 141 |

| Figure 88 | <ul> <li>Measurement results for 5MSym/s 256QAM at 2.8GHz with<br/>+17dBm average PA P<sub>out</sub> by employing the dynamic analog tuning<br/>of the varactor control.</li> </ul>                                                                                                                      | 142 |

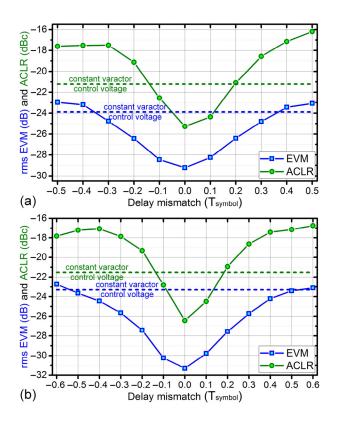

| Figure 89 | – Measurements with deliberately misaligned dynamic varactor analog control at (a) 2.4GHz and (b) 2.8GHz. The rms EVM/ACLR results for a constant varactor control voltage are shown as dashed lines. 64-QAM signals at 10MSym/s (symbol period $T_{symbol}$ =100ns) are used.                           | 142 |

| Figure 90 | – Measurement results for 10MSym/s 64QAM at 2.8GHz when<br>using LUTs for 2.4GHz. Comparison with the optimum<br>performance at 2.8GHz using 2.8GHz LUTs (Figure 87b) verifies<br>that the mixed-signal reconfiguration of the PA achieves<br>performance optimization at different carrier frequencies. | 143 |

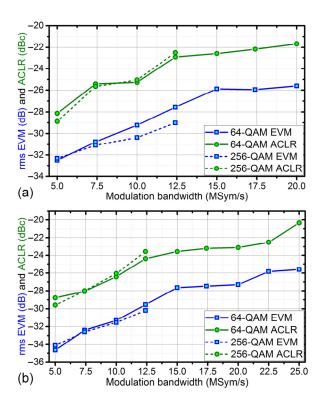

| Figure 91 | – Measurement results for 64QAM and 256QAM with different symbol rates at (a) 2.4GHz and (b) 2.8GHz.                                                                                                                                                                                                     | 144 |

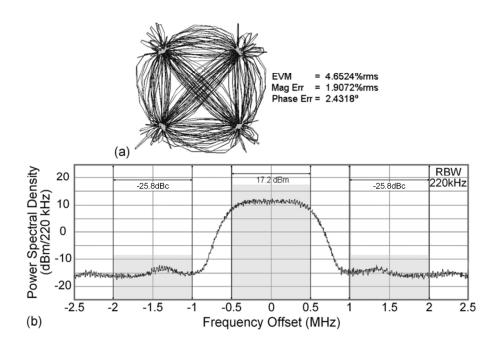

| Figure 92 | <ul> <li>Measured far-out-of-band spectrum for +17.5dBm 20MSym/s</li> <li>64QAM at 2.4GHz.</li> </ul>                                                                                                                                                                                                    | 145 |

| Figure 93 | – Measured PA DE when backing off the average $P_{out}$ for 10MSym/s 64QAM at (a) 2.4GHz and (b) 2.8GHz.                                                                                                                                                                                                 | 146 |

| Figure 94  | – Measured rms EVM (in-band linearity) and ACLR (OOB linearity) when backing off the average $P_{out}$ for 10MSym/s 64QAM at (a) 2.4GHz and (b) 2.8GHz.                                                                                                                                  | 146 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

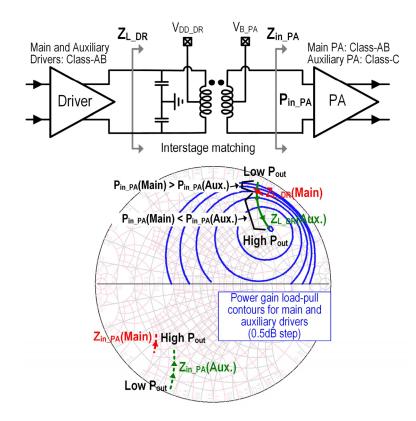

| Figure 95  | – Introduced transformer-based Doherty power combiner achieving reduced ITRs in PBO with the same peak $P_{out}$ ( $R_{opt} = 41.3\Omega$ ).– Introduced transformer-based Doherty power combiner achieving reduced ITRs in PBO with the same peak $P_{out}$ ( $R_{opt} = 41.3\Omega$ ). | 151 |

| Figure 96  | - Microphotograph of the implemented Doherty output network.                                                                                                                                                                                                                             | 152 |

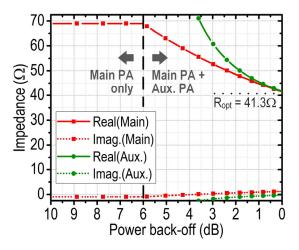

| Figure 97  | - Effective load impedance for the main and auxiliary PAs based<br>on the EM-simulated Doherty output passive network.                                                                                                                                                                   | 153 |

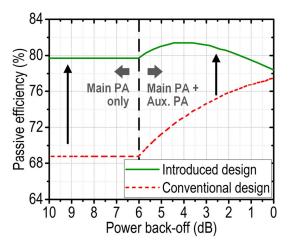

| Figure 98  | – Simulated PE of the introduced Doherty output network and comparison with a conventional design.                                                                                                                                                                                       | 153 |

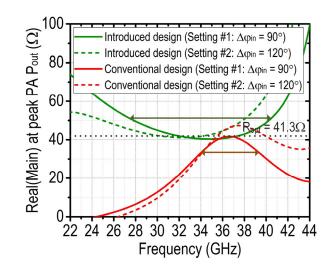

| Figure 99  | – Simulated bandwidth performance of the introduced Doherty output network and comparison with a conventional design.                                                                                                                                                                    | 154 |

| Figure 100 | - Introduced power-dependent Doherty PA uneven-feeding scheme.                                                                                                                                                                                                                           | 155 |

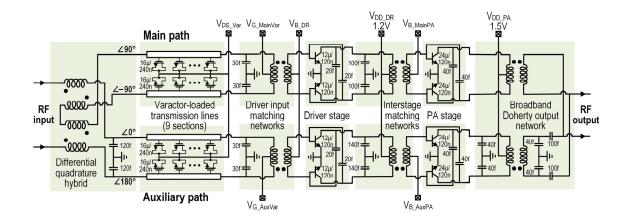

| Figure 101 | - Schematic of the implemented 28/37/39GHz linear Doherty PA                                                                                                                                                                                                                             | 156 |

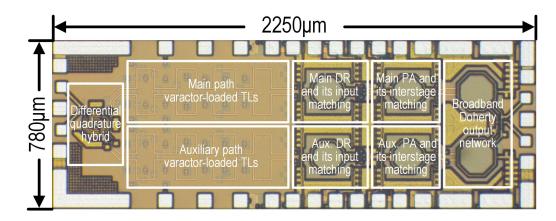

| Figure 102 | – Chip microphotograph.                                                                                                                                                                                                                                                                  | 157 |

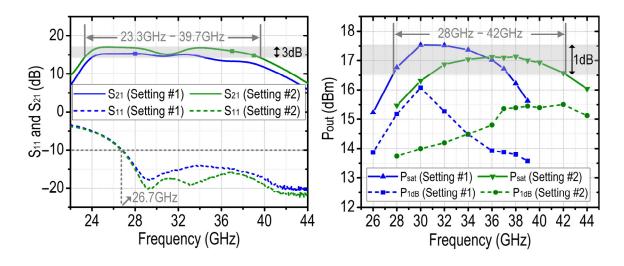

| Figure 103 | – Measured small-signal S-parameters and large-signal $P_{sat}/P_{1dB}$ .                                                                                                                                                                                                                | 157 |

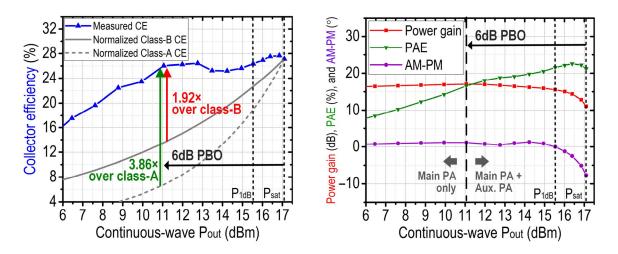

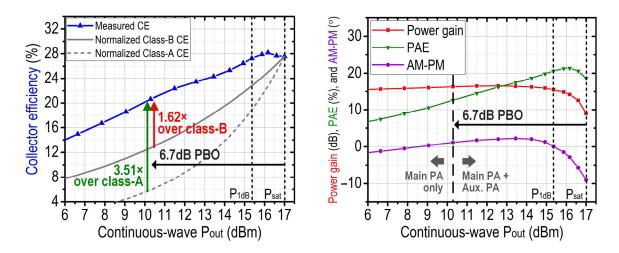

| Figure 104 | - Measured CW efficiency and linearity performance at 37GHz.                                                                                                                                                                                                                             | 157 |

| Figure 105 | - Measured CW efficiency and linearity performance at 39GHz.                                                                                                                                                                                                                             | 158 |

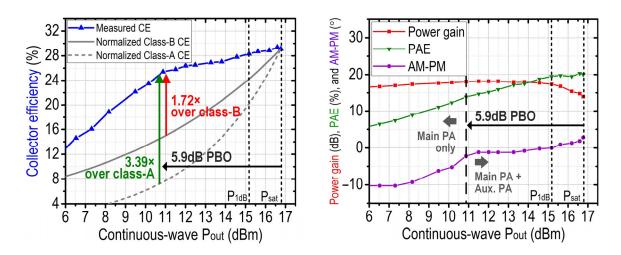

| Figure 106 | - Measured CW efficiency and linearity performance at 28GHz.                                                                                                                                                                                                                             | 158 |

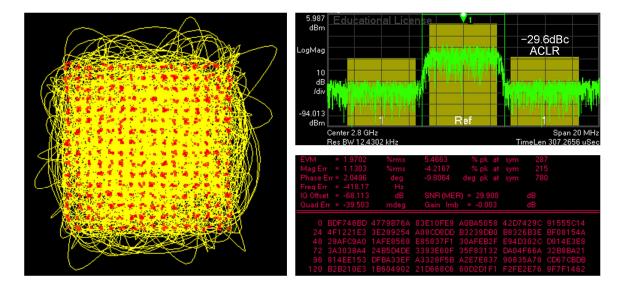

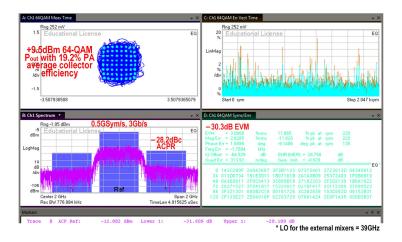

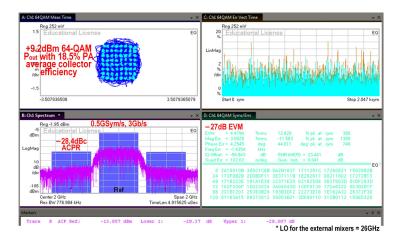

| Figure 107 | – Measured 500MSym/s 64QAM (3Gb/s) at 37GHz.                                                                                                                                                                                                                                             | 159 |

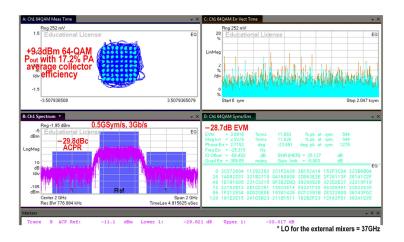

| Figure 108 | – Measured 500MSym/s 64QAM (3Gb/s) at 39GHz.                                                                                                                                                                                                                                             | 159 |

| Figure 109 | – Measured 500MSym/s 64QAM (3Gb/s) at 28GHz.                                                                                                                                                                                                                                             | 159 |

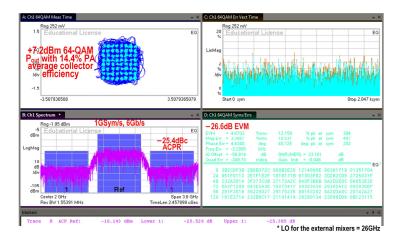

| Figure 110 | - Measured 1GSym/s 64QAM (6Gb/s) at 28GHz.                                                                                                                                                                                                                                               | 160 |

#### LIST OF SYMBOLS AND ABBREVIATIONS

- 5G Fifth-generation

- ACLR Adjacent channel leakage ratio

- AM Amplitude modulation

- AFG Arbitrary function generator

- AWG Arbitrary waveform generator

- CE Collector efficiency

- CMOS Complementary metal-oxide semiconductor

- CW Continuous-wave

- DCS Default code set

- DPD Digital predistortion

- DAC Digital to analog converter

- DE Drain efficiency

- DLTM Dynamic load trajectory manipulation

- EOC Efficiency optimum code

- EOCS Efficiency optimum code set

- EM Electromagnetic

- EER Envelope elimination and restoration

- ET Envelope tracking

- EVM Error vector magnitude

- FET Field-effect transistor

- FPGA Field-programmable gate array

- ITR Impedance tuning range

- P<sub>in</sub> Input power

- LOC Linearity optimum code

- LM Load-modulation

- LTE Long term evolution

- LUT Look-up table

- mm-wave Millimeter-wave

- OOB Out-of-band

- OFDM Orthogonal frequency division multiplexing

- PCT Parallel combining transformer

- PE Passive efficiency

- PM Phase modulation

- PAPR Peak-to-average power ratio

- Pout Output power

- PA Power amplifier

- PBO Power back-off

- PDF Probability density function

- PVT Process, voltage, temperature

- QoS Quality of service

- QAM Quadrature amplitude modulation

- QPSK Quadrature phase shift keying

- RF Radio frequency

- P<sub>sat</sub> Saturated output power

- SCT Series combining transformer

- SoC System-on-chip

- TDDB Time-dependent dielectric breakdown

- WLAN Wireless local area network

- ZVS Zero voltage switching

#### SUMMARY

Next-generation wireless networks pose unmet challenges for conventional communication circuits and systems. To satisfy the voracious demand for higher data rates using scarce spectrum resources, modern wireless networks often employ sophisticated modulations such as high-order quadrature amplitude modulation (QAM). They routinely require high-quality communication links. Consequently, energy efficiency is often compromised in conventional solutions. Current solutions also entail extraordinary challenges when extended to future civilian and defense electronics featuring wide bandwidth. My approaches to addressing these challenges fuse state-of-the-art mixed-signal techniques with large-signal radio frequency (RF)/millimeter-wave (mm-wave) and holistically design active circuits with on-chip electromagnetic (EM) structures. My research introduces new circuit topologies and system architectures that eliminate the tradeoffs and the limits of conventional solutions. In addition, my approaches are conducive to system-on-chip (SoC) integration in silicon.

A digital polar Doherty power amplifier (PA) fully integrated in a 65 nm bulk CMOS process is first introduced. The digital Doherty PA architecture optimizes the cooperation of the main and auxiliary amplifiers and achieves superior back-off efficiency enhancement. This digital intensive architecture also allows in-field PA reconfigurability which both provides robust PA operation against antenna mismatches and allows flexible trade-off optimization on PA efficiency and linearity. The active Doherty load modulation and power combining at the PA output are achieved by two transformers in a parallel configuration, which ensure an ultra-compact PA design and broad bandwidth. Both continuous-wave (CW) and modulation measurement results are demonstrated.

A comprehensive theoretical study on Doherty PAs under antenna impedance mismatch is performed. It is demonstrated for the first time that by varying the relative gain and phase of the main and auxiliary amplifiers, the PA performance degradation caused by the antenna impedance mismatch can be largely compensated. Such compensation effect is studied extensively for different antenna impedance conditions. Four types of Doherty PAs, i.e., three digital Doherty PAs with different degrees of flexibility and the classical analog Doherty PA, are covered in the complete theoretical analysis. To intuitively show the introduced concept, numerical simulation results based on the theoretical analysis are shown. In addition, measurement results on a fully integrated digital Doherty PA in 65nm bulk CMOS are demonstrated to verify the theoretical study.

In order to enhance the PA efficiency enhancement up to the deep power back-off (PBO) region, a broadband mixed-signal CMOS PA with a hybrid Class-G Doherty architecture is introduced. In addition, a mixed-signal linearization technique is introduced to ensure the PA's AM-AM linearity by digital PA operation and suppresses the PA's AM-PM nonlinearity by real-time analog phase compensation. A Doherty PA carrier bandwidth extension technique is also introduced. A proof-of-concept PA fully integrated in a standard 65 nm bulk CMOS process is demonstrated. Its measured CW and modulation performance advances the state-of-the-art CMOS PA PBO efficiency with superior broadband operation.

To further explore the potential of hybrid PAs, a mixed-signal PA architecture with the real-time hybrid operation of Class-G and dynamic load trajectory manipulation (DLTM) is introduced. This hybrid technique brings the following advantages. First, the Class-G operation substantially relaxes the required impedance tuning range of the loadmodulation (LM) network, allowing for a compact and low-loss transformer-based LM network that occupies only a single-transformer footprint. Secondly, DLTM enables PA efficiency enhancement in both Class-G supply modes. Furthermore, a new DLTM operation achieves PA efficiency peaking during PBO as well as PA carrier bandwidth extension. Mixed-signal digitally intensive PA operations ensure the PA output accuracy, including both amplitude and phase. A prototype PA is fully integrated in a standard 65nm bulk CMOS process and its CW and modulation measurement results are demonstrated.

In order to address the challenges in mm-wave 5G applications, a 28/37/39GHz multiband linear Doherty power amplifier is demonstrated. A broadband and low-loss transformer-based Doherty output network is introduced to enhance the Doherty PA efficiency and carrier bandwidth. The Doherty operation is further enhanced by a power-dependent Doherty PA uneven-feeding scheme based on a "driver-PA co-design" method. The PA fully integrated in 130nm SiGe delivers output power and linearity performance that meet the requirements of mm-wave 5G massive MIMO systems. Substantial efficiency enhancement is achieved in all three 5G bands, which advances the state of the art.

#### CHAPTER 1. INTRODUCTION

#### 1.1 Background

The last decade has witnessed an enormous surge of wireless devices. The mobile devices have earnt explosive popularity in human's daily life. Ubiquitous access to the internet with fast data streaming is desired in many existing applications. Moreover, applications supported by the mobile devices is ever increasing. These demand wireless systems with larger communication capacities and higher data rates. However, radio spectrum resources are limited for wireless communications. Radio frequency (RF) bands have already been densely allocated for different commercial and military applications. Therefore, spectrally efficient modulation methods are often deployed in modern wireless communication standards. For example, high-order quadrature amplitude modulation (QAM) and orthogonal frequency division multiplexing (OFDM) are utilized in Long Term Evolution (LTE) and Wireless Local Area Network (WLAN). Meanwhile, sophisticated power control schemes are often leveraged in modern wireless networks to maximize the system capacity. For example, base stations in modern wireless networks often set transmission power levels for the connected handsets. Different users with different wireless path conditions and requested data rates are required to transmit different power so that the overall system capacity is optimized. As a result, the transmitted signals of mobile devices often show large variations in the amplitude of the envelope (Figure 1a). In

other words, they have large peak-to-average power ratios (PAPRs) (Figure 1b). This presents design challenges for power amplifiers (PAs) in mobile devices.

PA is often the most power-hungry building block in a wireless transceiver. Achieving high PA energy efficiency is critical to extend the battery life of a mobile device and ease the thermal management. However, conventional PAs suffer significant efficiency drop in power back-off (PBO) [1], [2]. Classic PA efficiency enhancement techniques often offer very limited efficiency improvement in deep PBO. The average energy efficiency for a conventional PA when amplifying a high-PAPR signal is hence very low (Figure 1b).

Figure 1 – (a) Normalized envelope amplitude and (b) power probability density function (PDF) for a 10MSym/s 64-QAM signal with PAPR = 5.8dB. The efficiency curve of an ideal Class-B PA is also plotted in (b).

In parallel, it is essential for a PA to amplify the signal with high fidelity to ensure the quality of service (QoS) of a wireless link [1], [2]. This poses stringent requirements when the PA need to amplify a high-PAPR signal, in which case the PA nonlinearity need to be minimized across a wide power range. Both PA amplitude and phase responses, namely PA amplitude modulation to amplitude modulation (AM-AM) and AM to phase modulation (AM-PM), are often of concern in modern wireless systems.

The object of the introduced research is to achieve high-efficiency high-linearity PA in complementary metal-oxide semiconductor (CMOS) for modern wireless communications. New mixed-signal PA architectures and circuit techniques are introduced to address the design challenges posed by high-PAPR signals. Moreover, the introduced solutions should potentially benefit from the CMOS technology downscaling and be conducive to system-on-chip (SoC) integration.

#### 1.2 Efficiency Enhancement Techniques for CMOS RF PAs

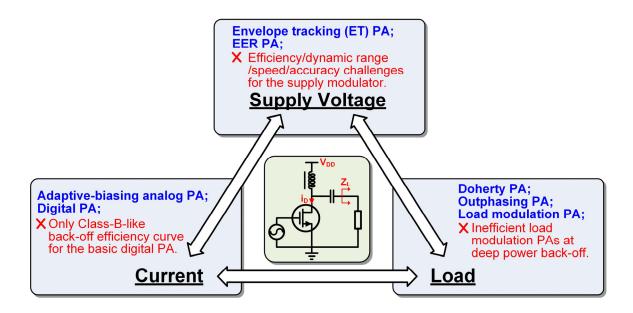

To improve the PA PBO efficiency, multiple PA architectures and circuit techniques have been presented in literatures. They can be grouped into three categories which essentially adjust the dc current, the supply voltage, or the PA load impedance during PBO (Figure 2). The advantages and limitations of each PA PBO efficiency enhancement technique will be discussed in details in this section.

The adaptive-biasing analog PA [3]-[5] and basic digital PA using RF power digital to analog converter (DAC) [6]-[11] reduce the PA dc current during PBO. However, they typically offer limited PBO efficiency improvement. For example, the basic digital PA only achieves Class-B-like PBO efficiency behavior.

Figure 2 – Summary and categorization of existing PA PBO efficiency enhancement techniques.

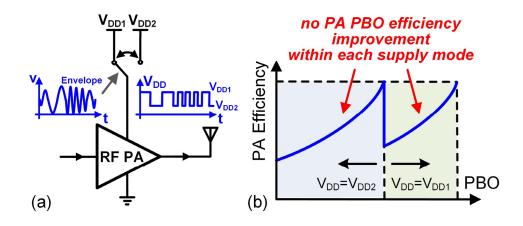

Envelope elimination and restoration (EER)/envelope tracking (ET) PAs [3], [12]-[20] save the PA dc power consumption in PBO by dynamic power supply [21]. However, the analog supply modulator often presents stringent design trade-offs among its efficiency, dynamic range, and speed [22]-[24]. This becomes particularly challenging for signals with large PAPRs and high modulation rates. As a compromised solution, the Class-G supply modulation [25] has recently become popular in PA implementations [26]-[28]. Different from analog supply modulators, Class-G supply modulators output discrete supply levels (Figure 3). This alleviates the supply modulator design trade-off and potentially allows high modulation rates. However, the existing Class-G PAs do not offer efficiency improvement within each supply mode (Figure 3). Moreover, significant design overhead is required to address the gain and phase discontinuities during mode switching in the analog Class-G PA [28].

Figure 3 – (a) Schematic of a Class-G PA with a 2-level (1-bit) supply modulator. (b) Theoretical PA efficiency behavior of a 2-level Class-G PA.

Outphasing [29]-[33], Doherty [34]-[53], and load modulation (LM) [54]-[64] PA architectures improve the PA PBO efficiency by modulating the effective PA load impedances in PBO. However, conventional silicon-based outphasing, Doherty, and load-modulation PAs often achieve compromised performance in practice and they offer very limited efficiency enhancement in deep PBO.

An outphasing PA need to generate two constant amplitude signals from the composite signal, which encode the amplitude modulation information as a differential phase shift. This process demands additional computation power in the digital baseband. Moreover, the efficiency of outphasing power combiners often degrades significantly in deep PBO. For an isolating outphasing combiner, e.g., a Wilkinson combiner, power is wasted in the isolation resistor in PBO. A non-isolating outphasing combiner, e.g., a Chireix combiner, is only effective for a small range of the outphasing angle, i.e., a limited PBO range.

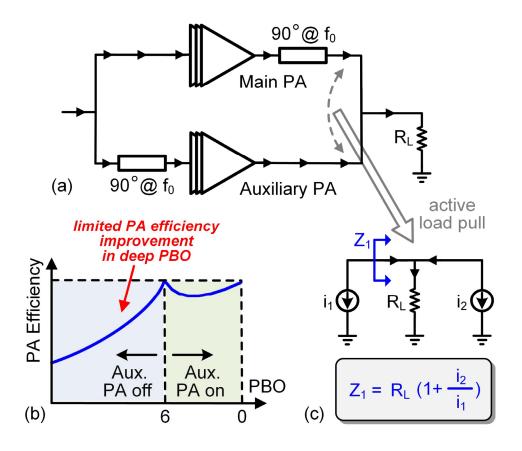

The Doherty PA configuration achieve enhanced PBO efficiency by leveraging the active load-pull effect (Figure 4). Compared with EER/ET and outphasing PAs, it potentially supports large modulation bandwidth without costly computation for the input signals. Doherty PAs have been widely employed in base stations. However, several key challenges exist for the CMOS integration of Doherty PAs [39]-[46]. Non-ideal cooperation between the main and auxiliary PA paths, together with large and lossy passive networks, often leads to compromised performance for the conventional analog Doherty CMOS PAs in practice.

Figure 4 – (a) Schematic of a classic 2-way Doherty PA. (b) Theoretical PA efficiency behavior of a classic symmetric 2-way Doherty PA. (c) Concept of the active LM effect.

The desired Doherty PA operation highly relies on the cooperation between the two PA paths, especially the turning-on point of the auxiliary PA and the relative gain relationship of the two PAs (Figure 4). However, it is challenging to satisfy these in analog Doherty PAs. Conventionally, to mimic Doherty operation, the auxiliary PA is often biased with a smaller conduction angle compared with the main PA. Additional analog techniques, including dynamic biasing [42] and asymmetrical main and auxiliary amplifiers [43] have been reported to enhance the analog Doherty PA performance. However, most techniques rely on dedicated tuning and lack the flexibility for in-field adjustment. Achieving desired cooperation between the two amplification paths remains elusive in practice.

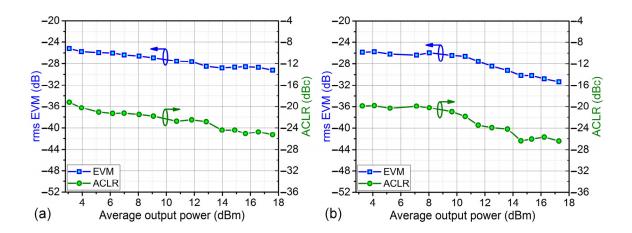

Moreover, a  $\lambda/4$  impedance inverter is needed in a Doherty PA to combine the main and the auxiliary PA outputs (Figure 4). Its compact and low-loss realization presents another major challenge for CMOS Doherty PAs. Conventionally, this impedance inverter is often approximated as a C-L-C low-pass  $\pi$ -network. The series inductor can be either a slab [39], [41], [42] or a spiral [40] inductor, which often requires a large area particularly in differential configurations. A series combining transformer (SCT) network has been employed in Doherty PA designs [43]. However, the efficiency of the SCT network intrinsically suffers from the non-zero output impedance of the auxiliary PA when it is turned-off in the low power region. Although switch controlled capacitors [44] or LC tuning networks [45] can be added at the auxiliary PA output to address this issue, these techniques requires additional complexity and chip area and may also degrade the reliability and passive loss. In addition, a variable balun transformer has been reported in a CMOS Doherty PA [46]. It also requires switch controlled capacitors at the PA output, and only discontinuous LM can be realized.

Furthermore, classic Doherty PAs offer limited efficiency enhancement in deep PBO. For example, marginal efficiency enhancement is achieved for a classic symmetric 2-way Doherty PA when PBO is larger than 6dB (Figure 4). Modified Doherty PA techniques have thus been presented in literatures, including asymmetric [35], [47], [48], multiway [49]-[51], and multistage Doherty PAs [35], [52], [53]. However, these techniques complicate cooperation among the multiple PA paths, require more complex and lossy passive networks, and often lead to extra PA efficiency penalty in practice.

In LM PAs, the PA load is adjusted by a reconfigurable passive network during the PBO to enhance the PA PBO efficiency. Conventional LM PAs face stringent design tradeoffs among the passive network complexity/area/loss and effective PBO range [54], especially when efficiency enhancement in deep PBO is required. For example, the Lnetwork (Figure 5a) has a limited impedance tuning range. With one more tuning component, the  $\pi$ -network (Figure 5b) extends the tuning range. However, it has significant loss in practice for large impedance tuning ratios, since it travels through high-Q impedance regions at the intermediate stages of the impedance transformation. This problem is alleviated in the two-stage ladder network (Figure 5c) but at the expense of additional loss and larger footprint. Although the transformer-based schemes (Figure 5d) could be a compact solution, it also experiences strong trade-off between tuning range and loss. Moreover, dramatic phase variations may present during impedance tuning for these networks, resulting in significant PA AM-PM distortions [63].

In summary, employing an individual PA efficiency enhancement technique often results in limited PA efficiency enhancements when deep PBO is needed.

Figure 5 – Existing PA load tuning networks.

Multiple PA efficiency enhancement techniques can be combined in one PA design to achieve hybrid operation. For example, the supplies of the outphasing and Doherty PAs are controlled by the analog supply modulators in [65]-[67]. The dc current or supply voltage is reduced in discrete steps for the outphasing PAs in [68] and [69]. Switch-based PA LM is combined with active load-pull based Doherty operation in [70]. However, these techniques increase the complexity but still demonstrate limited efficiency improvement in deep PBO.

#### 1.3 Linearization Techniques for CMOS RF PAs

Intensive research has been performed in the field of PA linearization [1], [2]. Techniques both in the system architecture and transistor levels have been presented. In general, the existing PA linearization techniques can be grouped into two types, i.e., linearizing the PA by making corrections at the PA input or output.

Both predistortion and feedback techniques linearize the PA by making suitable adjustment to the amplitude and phase of the PA input signal. Predistortion can be realized in the analog domain [71] or digital domain [72]. Digital domain predistortion often rely on look-up tables (LUTs). Feedback techniques often use analog loops to compute the input correction in real time. Both Cartesian and polar analog feedback loops have been demonstrated for PA linearization [1], [2].

Feedforward techniques linearize the PA by applying corrective signals at the PA output. For example, an auxiliary signal amplification path with a differently biased transistor can be combined with the main amplification path to cancel distortions [5].

In most cases, digital predistortion can be combined with other linearization techniques to achieve further improvement. Next, major concerns for feedback and feedforward techniques will be discussed.

Feedback techniques are robust to process, voltage, temperature (PVT) and PA load variations. However, most feedback techniques need to generate down-converted

derivatives. Therefore, feedback techniques are generally not considered as favorable solutions in wideband applications. A PA-closed loop technique is introduced recently to overcome the bandwidth issue of conventional feedback linearization techniques [73]. The amplitudes and phases of the PA output and the PA driver input are directly detected at RF and compared to control the gain and phase shift of the PA, respectively. Separate amplitude and phase feedback also helps with the PA stability. However, the effectiveness of the PA-closed loop technique in [73] is limited by the nonlinearity of the linearization circuits in the feedback loop.

Compared with feedback techniques, signal processing for linearization purposes is performed on the RF signal in feedforward techniques. Therefore, feedforward techniques fundamentally can support higher modulation rates. In practice, feedforward techniques require the accurate timing of various paths for optimum linearization. The LUTs also need to be updated when the PVT and PA load conditions change. It should be noted that the time-domain resolution of digital signals gets superior to the voltage resolution of analog signals in deep-submicron CMOS processes [6]. This offers the opportunity to facilitate the signal timing of the feedforward signals. In addition, the overhead for LUT update could be marginal for a SoC in a deep-submicron CMOS process.

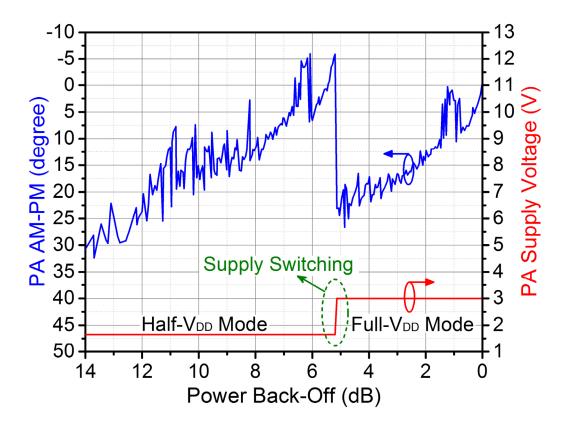

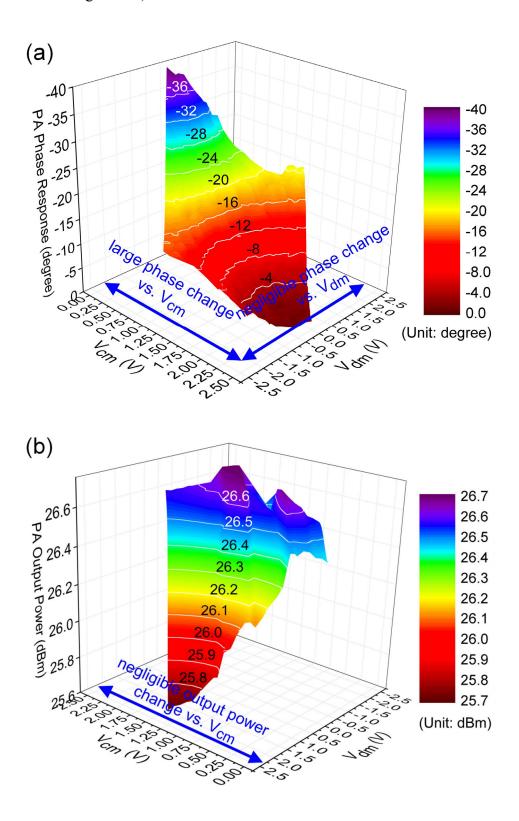

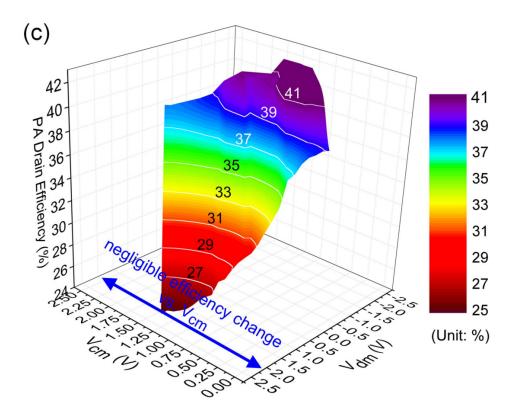

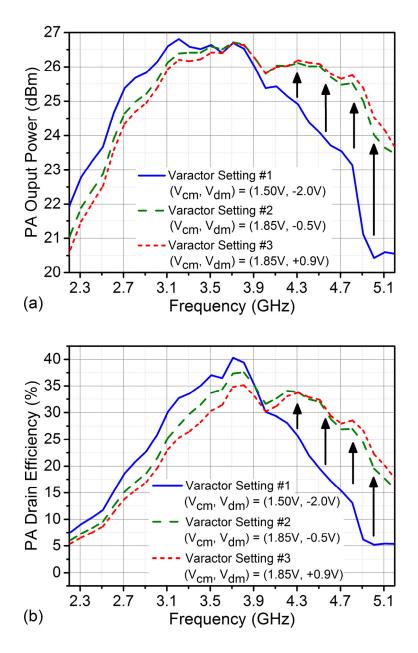

# CHAPTER 2. A TRANSFORMER-BASED RECONFIGURABLE DIGITAL POLAR DOHERTY PA FULLY INTEGRATED IN BULK CMOS