# MODELING, DESIGN, FABRICATION AND RELIABILITY CHARACTERIZATION OF ULTRA-THIN, GLASS BGA PACKAGE-TO-BOARD INTERCONNECTIONS

A Thesis Presented to The Academic Faculty

By

Bhupender Singh

In Partial Fulfillment Of the Requirements of the Degree Master of Science in the School of Materials Science and Engineering

Georgia Institute of Technology

May 2016

COPYRIGHT © Bhupender Singh 2016

# MODELING, DESIGN, FABRICATION AND RELIABILITY CHARACTERIZATION OF ULTRA-THIN, GLASS BGA PACKAGE-TO-BOARD INTERCONNECTIONS

Approved by:

Dr. Rao R. Tummala, Advisor School of Material Science and Engineering *Georgia Institute of Technology*

Dr. Suresh Sitaraman School of Mechanical Engineering *Georgia Institute of Technology*

Dr. Markondeya Raj Pulugurtha School of Material Science and Engineering *Georgia Institute of Technology*

Date Approved: April 8, 2016

In memory of my aunt, Late Indira Singh, Dedicated to parents and extended family...

#### ACKNOWLEDGEMENTS

I would like to express my humble gratitude to my advisor, Professor Rao R. Tummala for accepting me as his student and allowing me to pursue research and higher education. His vision and wisdom has encouraged and inspired my learning throughout the course of my thesis study.

I sincerely thank my mentors, Dr. Vanessa Smet and Dr. Raj Pulugurtha for keeping trust, patience and faith in my ability. I am indebted to their relentless support, supervision and technical consult in giving direction at every step along the way. I also thank Professor Suresh Sitaraman for serving on my committee and providing insightful feedback.

I would like to extend my heartfelt appreciation to the visiting engineers including Satomi Kawamoto, Makoto Kobayashi, Yutaka Takagi, Yoichiro Sato, Hiroyuki Matsuura, Tomonori Ogawa, Ryuta Furuya for their support and guidance on fabrication. I thank all the fellow GRAs for their help and involvement, with special mentions to Scott McCann for ANSYS modeling, and intern students for their experimental contributions. I would also like to acknowledge the PRC administration – Karen May, Patricia Allen, Chris White, Jason Bishop and all the student assistants for working keenly towards my interests and goals.

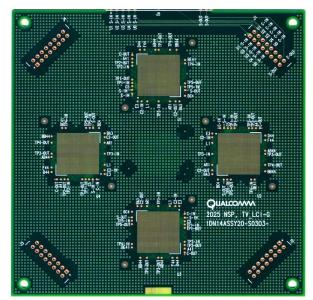

I thank our industry partners from Qualcomm, Atotech, Nanium, Namics, AGC, and Indium for their guidance and support on the experimental work.

Finally, I would like to thank my family, for their unconditional love and support and the Almighty, for giving me the strength and courage to achieve my ambitions.

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS i                                                                  | v  |

|-------------------------------------------------------------------------------------|----|

| TABLE OF FIGURES vi                                                                 | ii |

| TABLE OF TABLES xi                                                                  | v  |

| SUMMARYxv                                                                           | ⁄i |

| CHAPTER 1: INTRODUCTION                                                             | 1  |

| 1.1 Transistor scaling to system scaling trends in microelectronics packaging       | 1  |

| 1.2 Board-level Interconnections and Reliability Requirements                       | 4  |

| 1.3 Board-level reliability challenges with evolution of substrate technologies for |    |

| system scaling                                                                      | 6  |

| 1.4 Research objectives                                                             | 8  |

| 1.5 Unique approach addressing technical challenges                                 | 8  |

| 1.6 Thesis Tasks and Organization1                                                  | 3  |

| CHAPTER 2: LITERATURE REVIEW 1                                                      | 5  |

| 2.1 Evolution of IC packaging1                                                      | 5  |

| 2.1.1 Traditional packaging1                                                        | 5  |

| 2.1.2 Recent advances in multi-chip packaging 1                                     | 7  |

| 2.2 Recent material developments in board-level interconnections                    | 2  |

| 2.2.1 Advances in pad surface finishes                                              | 3  |

| 2.2.2 Advances in standard solders by doping 2                                      | 7  |

| 2.2.3 Advances in underfill materials                                               | 2  |

| 2.3 Strain-relief by compliant interconnections                                     | 3  |

| 2.4 Previous research at GT-PRC on package-to-board interconnections                 | 36 |

|--------------------------------------------------------------------------------------|----|

| 2.5 Summary                                                                          | 37 |

| CHAPTER 3: FINITE-ELEMENT MODELING FOR STRAIN-RELIEF MECHANI<br>WITH POLYMER COLLARS |    |

| 3.1 Geometric Model                                                                  | 38 |

| 3.2 Material Models and Stress-Free Temperatures                                     | 39 |

| 3.3 Thermal Loading Conditions for Thermomechanical Simulations                      | 42 |

| 3.4 Effect of Polymer Collars on Glass Package Warpage Behavior                      | 43 |

| 3.5 Effect of Polymer Collars on the Fatigue Life of Solders                         | 46 |

| CHAPTER 4: TEST VEHICLES DESIGN, FABRICATION AND ASSEMBLY                            | 51 |

| 4.1 Test Vehicle 1 (TV1) – Strain relief with polymer collars                        | 51 |

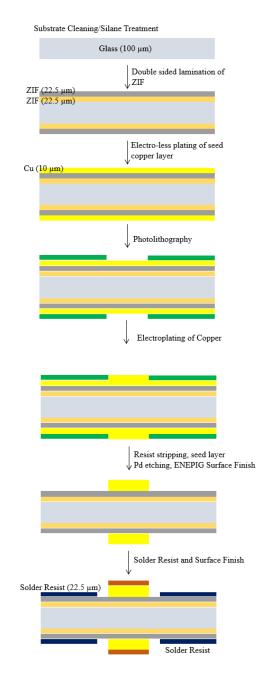

| 4.1.1 Design and Fabrication of Glass BGA Substrates                                 | 52 |

| 4.1.2 PCB Design for Thermal Cycling and Drop Test                                   | 55 |

| 4.1.3 Glass package pre-characterization                                             | 57 |

| 4.1.4 Polymer Collar Formation                                                       | 58 |

| 4.1.5 SMT Assembly Process                                                           | 59 |

| 4.2 Test Vehicle 2 (TV2) - TCT Evaluation of Mn-Doped Solder SACM <sup>TM</sup>      | 61 |

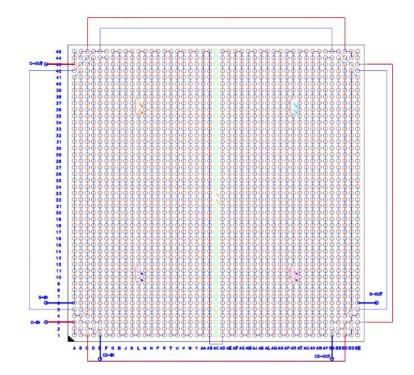

| 4.2.1 Design of Daisy-Chain Test Die                                                 | 61 |

| 4.2.2 Four Metal Layer Glass Package Design                                          | 62 |

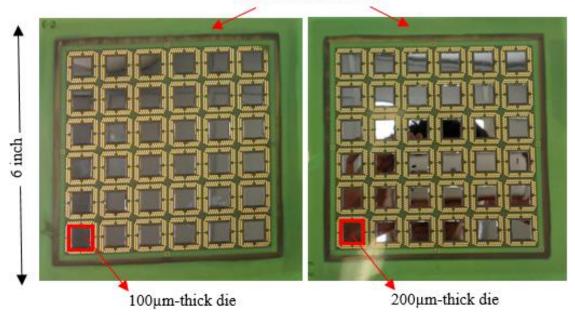

| 4.2.3 Chip-level assembly                                                            | 66 |

| 4.2.4 BGA Balling Process Development and Optimization                               | 67 |

| 4.2.5 Board-level assembly and yield evaluation                                      | 78 |

| 4.3 Test Vehicle 3 (TV3) – Evaluation of SACM, with Considerations of Surface        |    |

| Finishes                                                                             | 81 |

| 4.3.1 Test Vehicle Fabrication                                                    |

|-----------------------------------------------------------------------------------|

| CHAPTER 5: RELIABILITY TESTING AND FAILURE ANALYSIS                               |

| 5.1 TV1 Reliability Evaluation and Failure Analysis: Effect of Polymer Collars 86 |

| 5.1.1 Thermal Cycling Test Results                                                |

| 5.1.2 Drop Test Results                                                           |

| 5.2 TV2 Thermal Cycling Test: Evaluation of Mn-doped SAC solder 106               |

| CHAPTER 6: SUMMARY AND CONCLUSIONS 107                                            |

| 6.1 Research Summary 107                                                          |

| 6.1.1 Finite-Element Modeling 108                                                 |

| 6.1.2 Summary of Task 1 results 108                                               |

| 6.1.3 Summary of Task 2 results 110                                               |

| 6.1.4 Summary of Task 3 results and considerations for future work 112            |

| 6.2 Conclusions 113                                                               |

| REFERENCES                                                                        |

# **TABLE OF FIGURES**

| Figure 1.1: Gap between transistor and system scaling [3]                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Increasing functional densities for next-generation ultra-small systems: system scaling by System Moore (SM) for heterogeneous integration beyond More of Moore (MM) and More than Moore (MTM) [1]4 |

| Figure 1.3: Die-package-board interconnections with large LDNP and low stand-off height.                                                                                                                        |

| Figure 1.4: Traditional package approach (a) IC – organic BGA – PCB, current package (b) IC – low-CTE interposer – organic BGA – PCB, and new package approach (c) IC –large and thin glass package – PCB       |

| Figure 1.5: Unique approach for board-level reliability of large, thin glass BGA packages.                                                                                                                      |

| Figure 1.6: Optimization of collar thickness to provide best compromise of strain relief and reworkability [13]11                                                                                               |

| Figure 1.7: Contrasting solder requirements for drop test and thermomechanical reliability.                                                                                                                     |

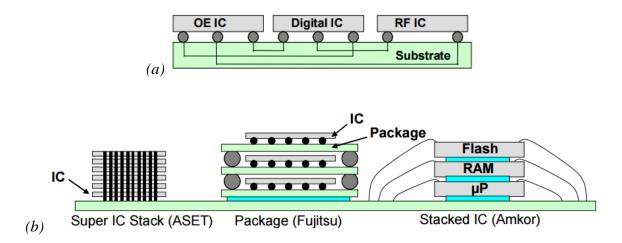

| Figure 2.1: Schematic representation of (a) multi-chip module, (b) stacked IC and package.                                                                                                                      |

| Figure 2.2: 2.5D silicon interposer from (a) Xilinx and (b) Hynix18                                                                                                                                             |

| Figure 2.3: Georgia Tech's 2.5D Glass Interposer Package                                                                                                                                                        |

| Figure 2.4: Conventional 2.5D assembly (left), Intel's EMIB assembly (right)20                                                                                                                                  |

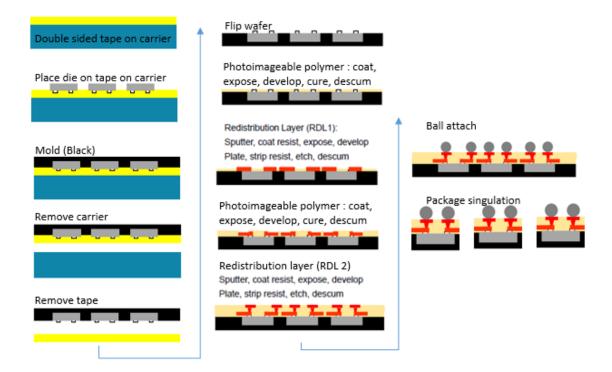

| Figure 2.5: Process flow to achieve FOWLP - Courtesy of Beth Keser (Qualcomm Inc.),<br>Guest Lecture on WLP, CPMT                                                                                               |

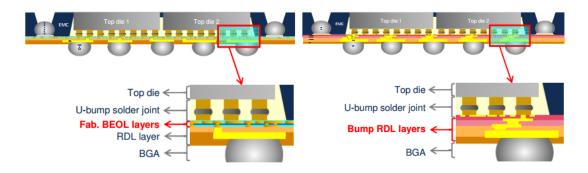

| Figure 2.6: Amkor Technology Inc's SLIM (left) and SWIFT (right)22                                                                                                                                              |

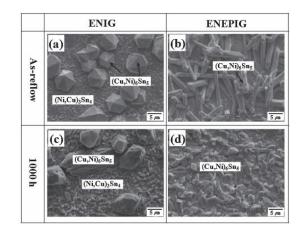

| Figure 2.7: IMC thickness for ENIG and ENEPIG after reflow (a) and (b); and after 1000 hours of thermal aging (c) and (d)25                                                                                     |

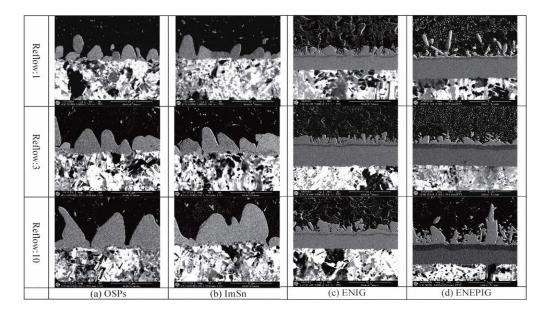

| Figure 2.8: Progression of IMC growth after multiple reflow cycles with various pad surface finishes                                                                                                            |

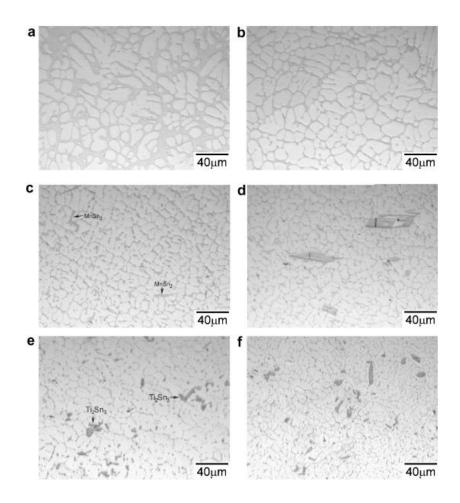

| Figure 2.9: Microstructures of (a) SAC305, (b) SAC105, (c) SAC105 + 0.15Mn, (d) SAC105 + 0.5Mn, (e) SAC105 + 0.15Ti and (f) SAC105 + 0.5Ti [ref]28                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.10: Cooling curve (a) for low Ag SAC solder and (b) simplified binary phase diagram with variation in undercooling                                                             |

| Figure 2.11: Drop test reliability of SAC solder with dopants                                                                                                                           |

| Figure 2.12: Thermal cycling results for SnPb, SAC105, SAC305 and SACM31                                                                                                                |

| Figure 2.13: IMC thickness on package and PCB side                                                                                                                                      |

| Figure 2.14: Delo's novel encapsulant that acts as underfill and overmold32                                                                                                             |

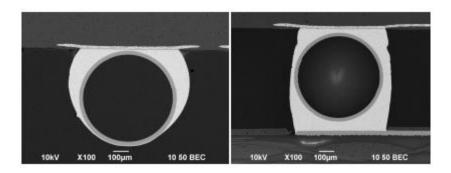

| Figure 2.15: Cross-section of polymer core solder ball after balling (left) and assembly (right)                                                                                        |

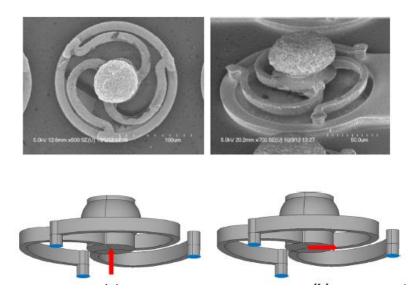

| Figure 2.16: Multi-path complaint structures - SEM image (top), simulations (bottom)35                                                                                                  |

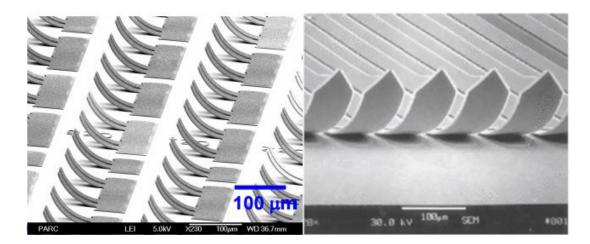

| Figure 2.17: Micro-spring (left) and stress-engineered compliant interconnections (right)                                                                                               |

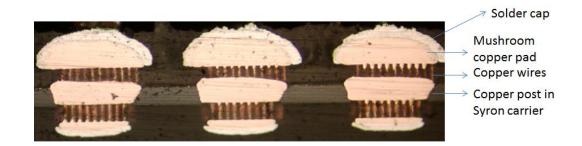

| Figure 2.18: Cross section of MWA interconnections                                                                                                                                      |

| Figure 3.1: Unit section of glass BGA package in 2D half-symmetry FE model                                                                                                              |

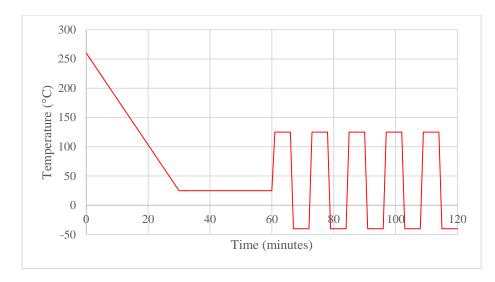

| Figure 3.2: Thermal loading applied in modeling of glass BGA package thermomechanical reliability                                                                                       |

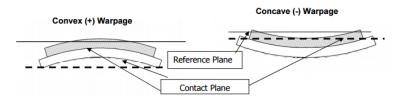

| Figure 3.3: JEDEC-defined package warpage convention                                                                                                                                    |

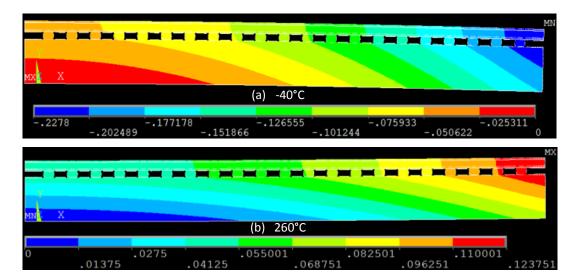

| Figure 3.4: (a) Convex warpage at -40°C, (b) concave warpage at 260°C44                                                                                                                 |

| Figure 3.5: Warpage behavior for low- and high-CTE BGA packages with and without circumferential collars                                                                                |

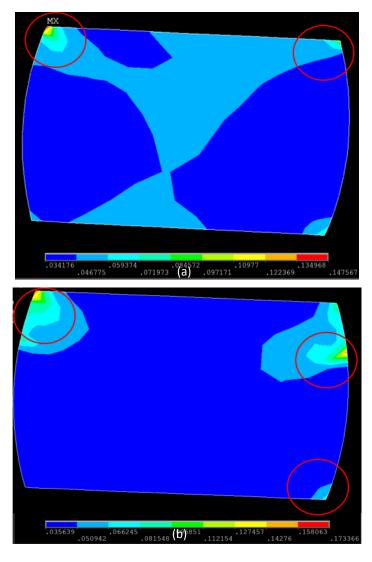

| Figure 3.6: (a) Plastic strain distribution in the outermost solder joint (a) without collars and (b) with collars. Show package side and board side on the figure. Thicker red circles |

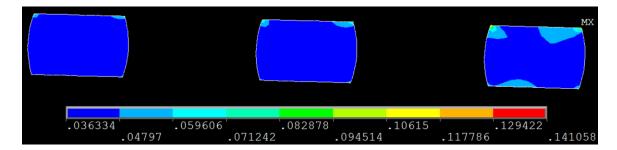

| Figure 3.7: Decreasing plastic strain in solder joints moving towards the package center                                                                                                |

| Figure 3.8: Fatigue life predictions using Coffin-Manson model                                                                                                                          |

| Figure 3.9: Fatigue life predictions using Engelmaier-Wild model                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.1: Glass BGA package stack-up of TV1                                                                                                                                                                                                                      |

| Figure 4.2: Glass BGA package design for board-level reliability evaluation                                                                                                                                                                                        |

| Figure 4.3: Glass BGA package TV1 fabrication process flow                                                                                                                                                                                                         |

| Figure 4.4: PCB board design with 4-point probing pads                                                                                                                                                                                                             |

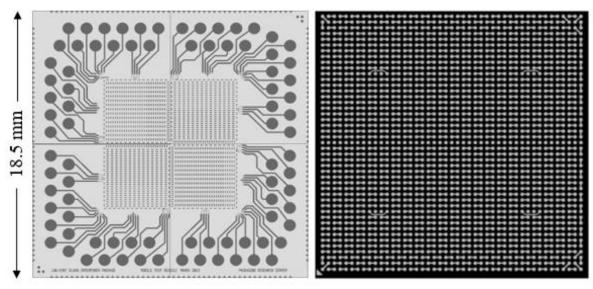

| Figure 4.5: Board design for drop testing of 18.5mm x 18.5mm glass packages56                                                                                                                                                                                      |

| Figure 4.6: Daisy-chain layout for drop test with corner daisy chain in red and inner daisy chain in blue                                                                                                                                                          |

| Figure 4.7: C-SAM image of a low-CTE glass package with suitable structural integrity                                                                                                                                                                              |

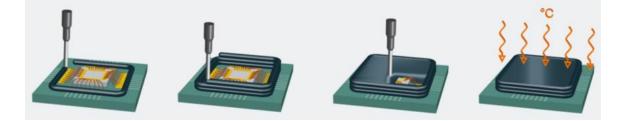

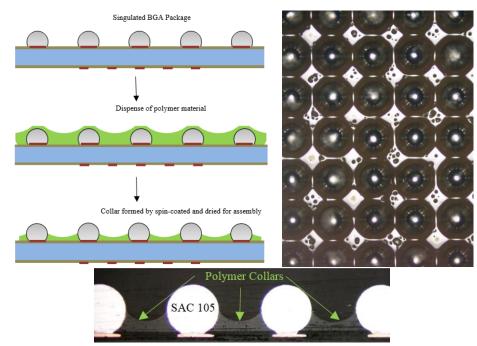

| Figure 4.8: Process flow of polymer collars formation (top left) and optical microscope image of spin-coated glass package (top right), cross-section of an 18.4mm interposer with uniform collar formation achieved after spin-coating profile optimization [13]. |

| Figure 4.9: X-ray characterization of non-yielded drop-test sample                                                                                                                                                                                                 |

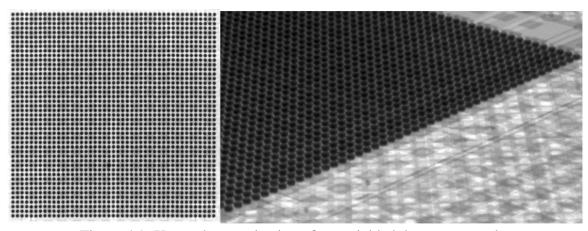

| Figure 4.10: Daisy-chain test die fabricated by ASE (left) and magnified view of the die corner (right) (Images courtesy of ASE)                                                                                                                                   |

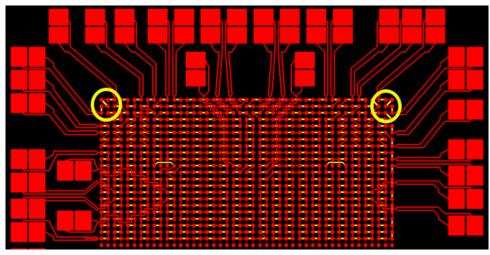

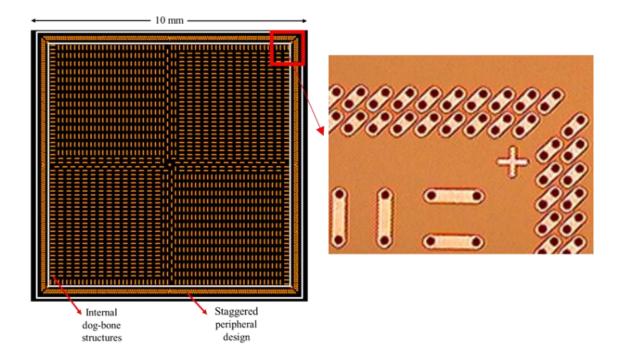

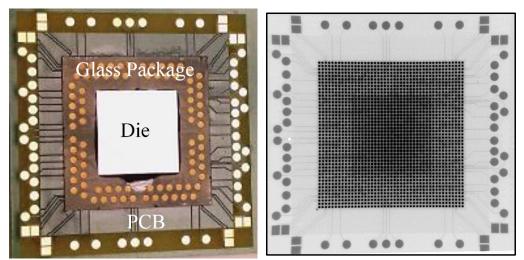

| Figure 4.11: Glass substrate test vehicle design with (left) die side, and (right) BGA side                                                                                                                                                                        |

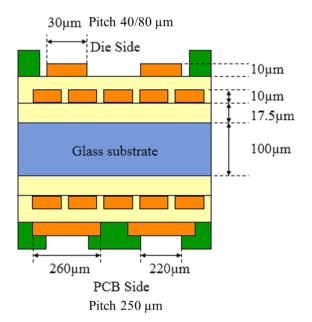

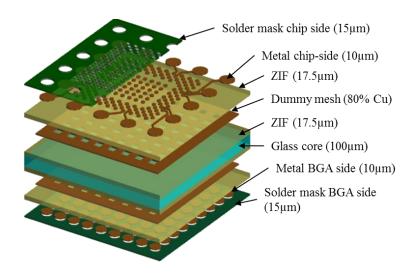

| Figure 4.12: TV2 glass package stack-up and design rules                                                                                                                                                                                                           |

| Figure 4.13: Expanded view of 18.5mm x18.5mm 4-metal layer glass substrates65                                                                                                                                                                                      |

| Figure 4.14: Chip-level assembly on low-CTE glass substrates by thermocompression bonding at panel level                                                                                                                                                           |

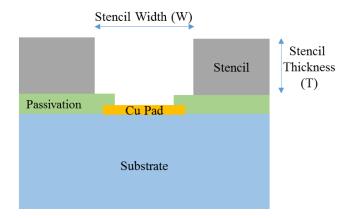

| Figure 4.15: Schematic of the stencil for BGA balling by paste printing                                                                                                                                                                                            |

| Figure 4.16: Optical inspection of as-printed BGAs with good paste release, uniform deposit, good paste-to-pad alignment and no observed bridging                                                                                                                  |

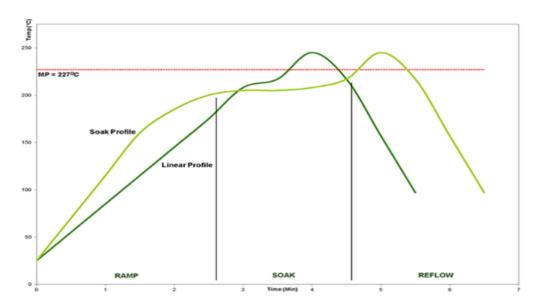

| Figure 4.17: Recommended reflow profile for SAC305 solder paste [65]70                                                                                                                                                                                             |

| Figure 4.18: X-ray characterization after BGA balling and reflow showing no solder voids, bridging or beading                                   | .72 |

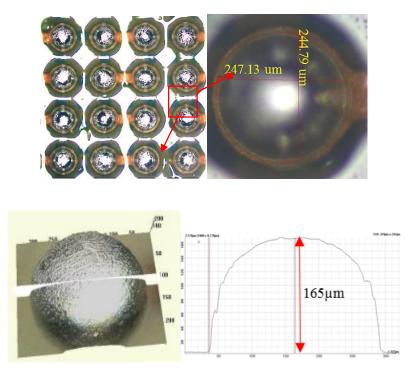

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.19: Optical inspection (top) and 3D profilometry (bottom) indicating precise dimensions of the paste printed solder balls after reflow | .72 |

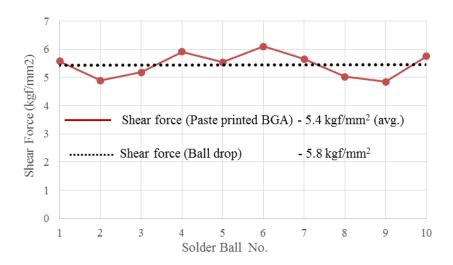

| Figure 4.20: Measured ball shear strength for the paste-printed vs. ball-drop BGA balls                                                         | .74 |

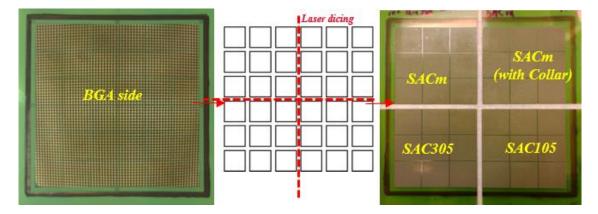

| Figure 4.21: Laser dicing of glass panels into quarters and BGA balling with SACM, SAC305 and SAC105                                            | .74 |

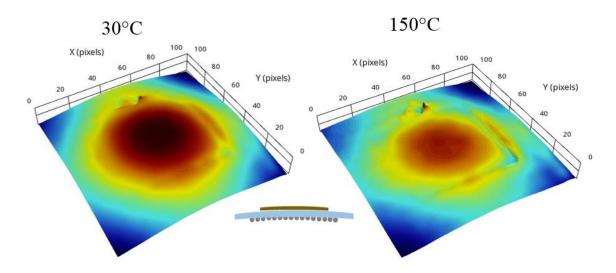

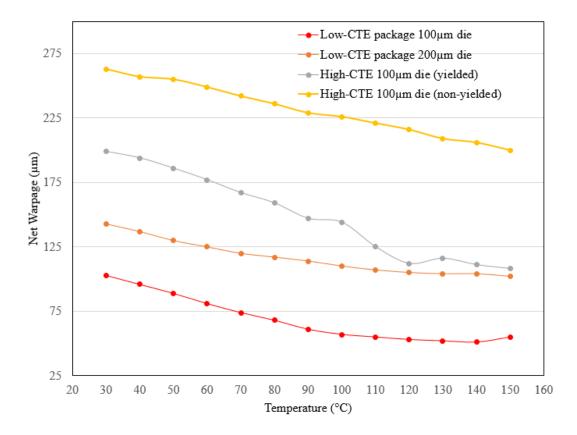

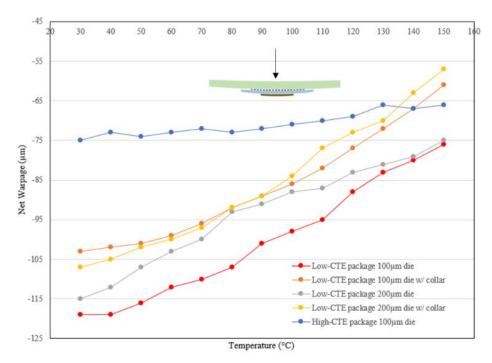

| Figure 4.22: Warpage behavior by Shadow-Moiré interferometry on a low-CTE glass package with a 100µm-thick die                                  | .76 |

| Figure 4.23: Net warpage temperature response of low- and high-CTE glass packages with considerations of BGA balling yield.                     | .77 |

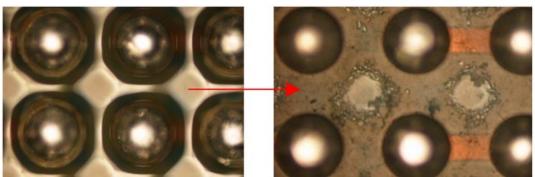

| Figure 4.24: BGA before (left) and after (right) paste flux residue removal                                                                     | .78 |

| Figure 4.25: Single-chip glass package mounted on PCB: (left) optical imaging, and (right) X-ray imaging                                        | 78  |

| Figure 4.26: Optical and SEM/EDS characterization of paste-printed BGA after board-<br>level assembly                                           |     |

| Figure 4.27: Net warpage response after board-level assembly, measured from PCB backside.                                                       |     |

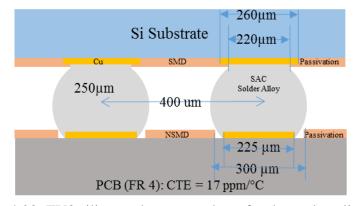

| Figure 4.28: TV3 silicon substrate stack-up for thermal cycling test                                                                            | .82 |

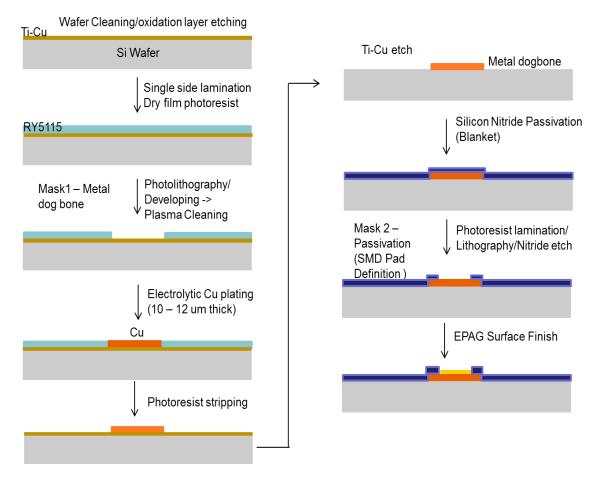

| Figure 4.29: Process flow for Si TV fabrication                                                                                                 | .83 |

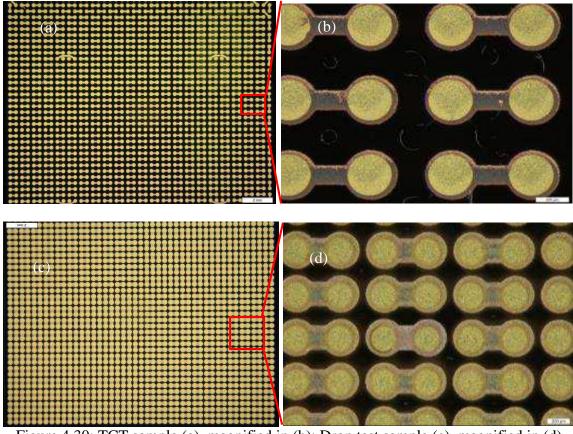

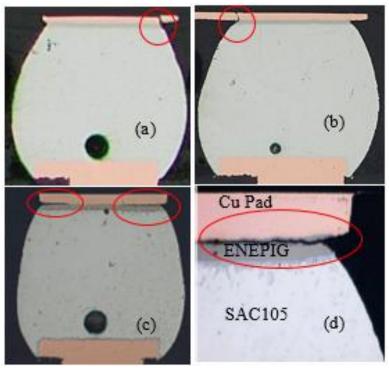

| Figure 4.30: TCT sample (a), magnified in (b); Drop test sample (c), magnified in (d).<br>[Images courtesy of Atotech GmbH, Germany]            | 84  |

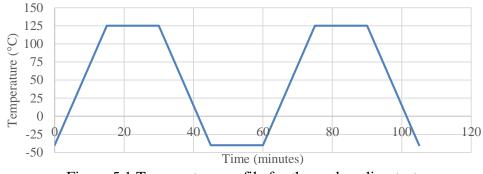

| Figure 5.1 Temperature profile for thermal cycling test                                                                                         | .87 |

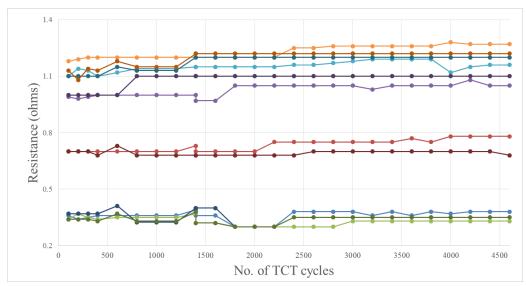

| Figure 5.2: Daisy-chain resistances of a high-CTE sample, stable across 4600 thermal cycles.                                                    | 88  |

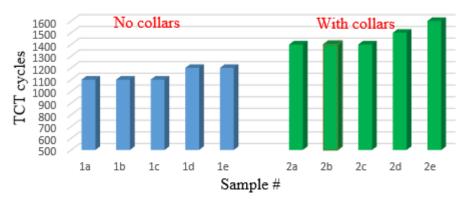

| Figure 5.3: Bar graph of first failure in low-CTE samples                                                                                       | .89 |

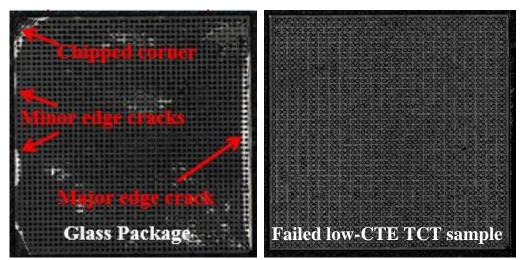

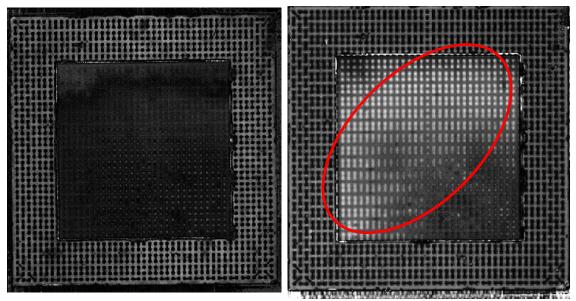

| Figure 5.4: C-SAM of reference sample (left) with defects, and failed low-CTE sample after 1400 cycles (right)90                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

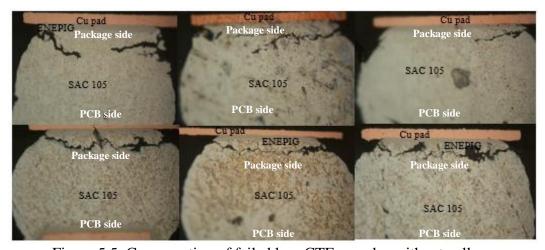

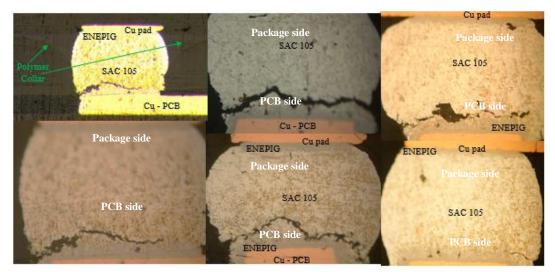

| Figure 5.5: Cross-section of failed low-CTE samples without collars                                                                                                                                                     |

| Figure 5.6: Cross-section of failed low-CTE samples with collars                                                                                                                                                        |

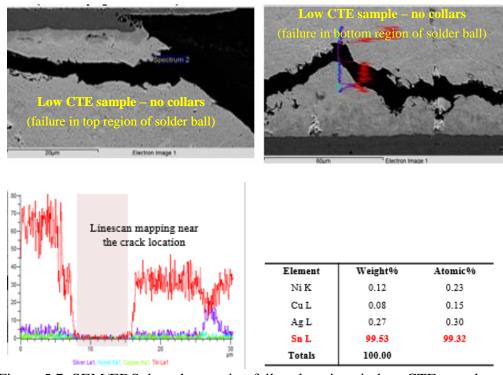

| Figure 5.7: SEM/EDS data showcasing failure locations in low-CTE samples92                                                                                                                                              |

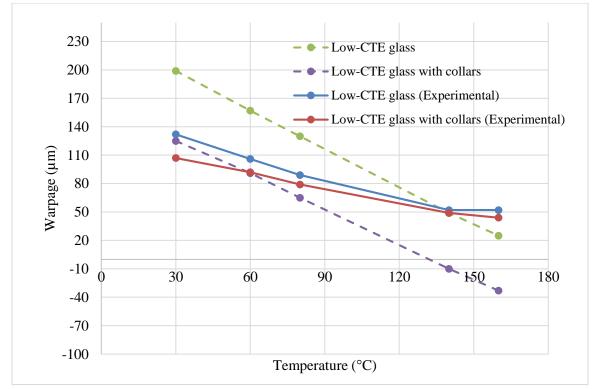

| Figure 5.8: Warpage trends for low-CTE samples with and without collars from (a) modeling, and (b) experiments                                                                                                          |

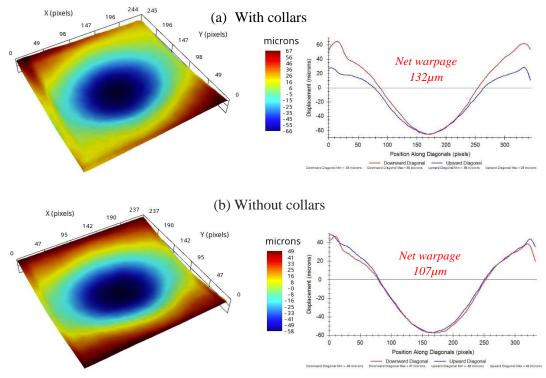

| Figure 5.9: Shadow-Moiré 3D contour plot at 30°C and corresponding displacements along the diagonals for low-CTE glass packages (a) with and (b) without collars94                                                      |

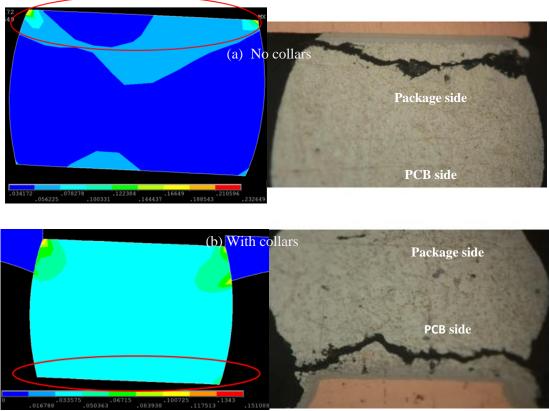

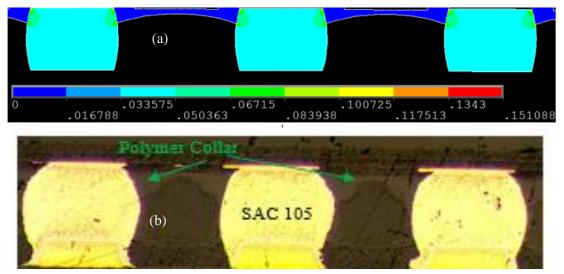

| Figure 5.10: Plastic strain distribution vs. crack location in failed low-CTE samples (a) without collars, and (b) with collars                                                                                         |

| Figure 5.11: Plastic strain distribution and cross-section of BGAs from the inner circuit in low-CTE samples with polymer collars                                                                                       |

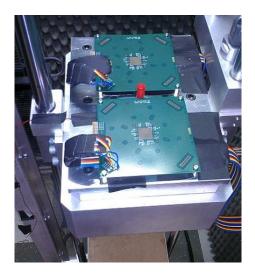

| Figure 5.12: Drop test boards mounted to the shock machine, wired for in-situ resistance monitoring                                                                                                                     |

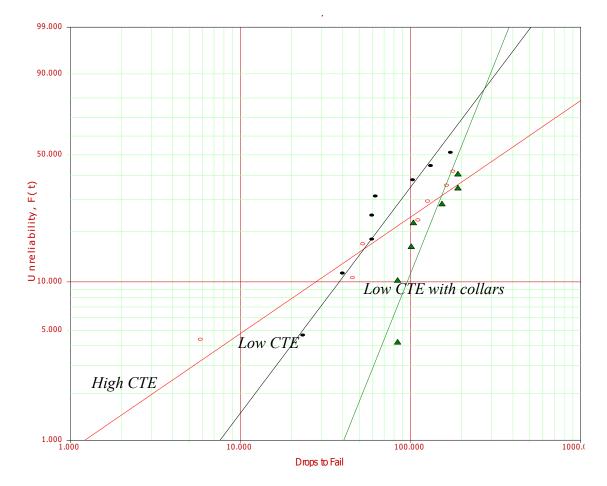

| Figure 5.13: Weibull failure distribution plot for drop testing of glass BGA packages99                                                                                                                                 |

| Figure 5.14: C-SAM characterization of drop test sample with 230 MHz (left) and 50 MHz (right) transducers                                                                                                              |

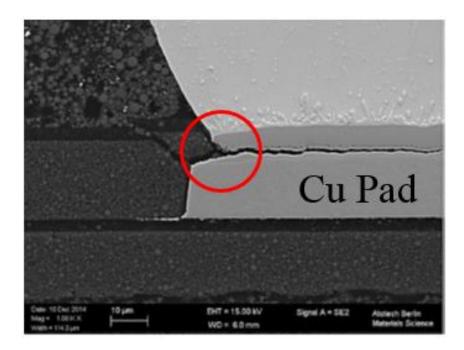

| Figure 5.15: Optical images of cross sections of failed drop test samples with: (a, b)<br>Mode 1 failure: crack in the Cu routing layer; and (c, d): Mode 2 failures: crack in<br>the Ni layer near the Cu-Ni interface |

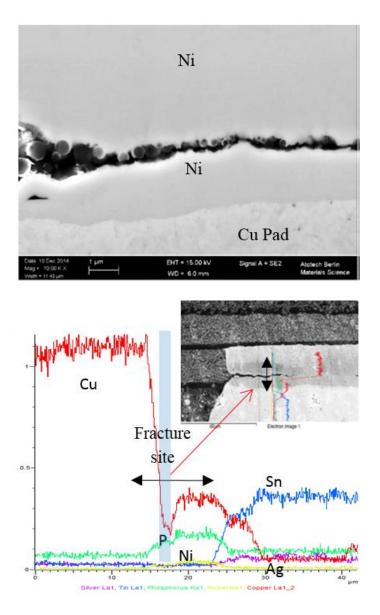

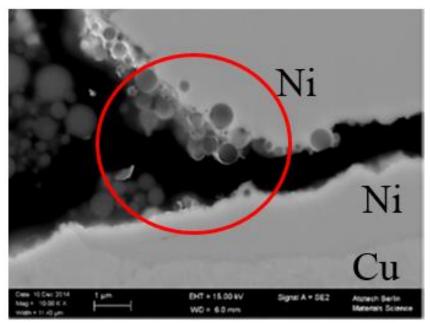

| Figure 5.16: SEM image (top, courtesy of Atotech) and EDX characterization of Mode 2 fracture (bottom)103                                                                                                               |

| Figure 5.17: Necking at pad edge tip (top), magnified view of fillers (bottom) indicating some ZIF residue on the copper pad. (Images courtesy of Atotech.)104                                                          |

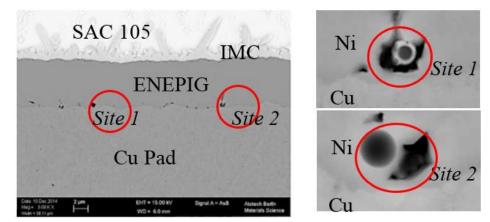

| Figure 5.18: ZIF fillers at central sites (left), magnified view of fillers - site 1 (top right), site 2 (bottom right). (Images courtesy of Atotech.)                                                                  |

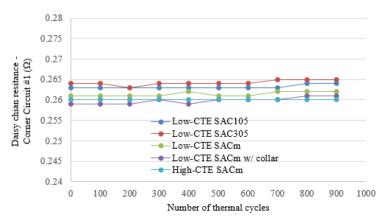

| Figure 5.19: Resistance measurements for corner daisy chain #1 in assemblies with 100µm-thick die                                                                                                                       |

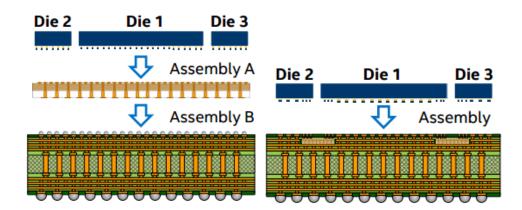

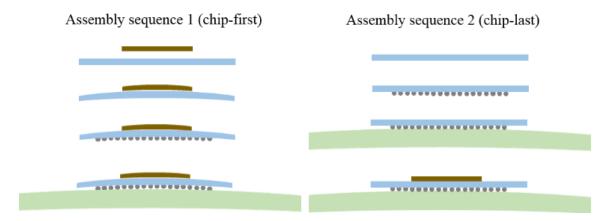

| Figure 6.1: Assembly sequen | ce modification fr | rom chip first | (left) to chip | last (right) for |

|-----------------------------|--------------------|----------------|----------------|------------------|

| high-CTE glass BGA pa       | ckages             |                |                |                  |

# TABLE OF TABLES

| Table 1.1: Research objectives beyond prior art.                                                                 | 8        |

|------------------------------------------------------------------------------------------------------------------|----------|

| Table 2.1: Summary of pros and cons of HASL, OSP, ImSn and Imag.                                                 | 24       |

| Table 2.2: Primary and secondary IMCs formed with common pad surface finishes                                    | 24       |

| Table 3.1: Properties of modeled materials [11].                                                                 | 40       |

| Table 3.2: Anand's model parameters for SAC105 solder [64].                                                      | 41       |

| Table 3.3: Plastic strain range values with and without collars.                                                 | 49       |

| Table 3.4: Material constants for SAC105 [16].                                                                   | 50       |

| Table 4.1: TV1 glass substrate stack-up.                                                                         | 55       |

| Table 4.2: SMT assembly yield for sample configurations in TCT and drop test                                     | 60       |

| Table 4.3: Fabrication parameters and materials description for fabrication of 4-metal layer glass BGA packages. | 65       |

| Table 4.4: Suggested parameters for stencil based paste printing (Indium Corporation)                            | . 69     |

| Table 4.5 Reflow optimization for minimization of solder voiding:                                                | 71       |

| Table 4.6: Ball diameter of paste printed BGAs: design vs. actual.                                               | 73       |

| Table 4.7: BGA balling yield on reliability glass substrates.                                                    | 75       |

| Table 4.8: Summary of SMT Assembly Yield and Thermal Cycling Test Plan.                                          | 80       |

| Table 4.9: Experimental plan for comprehensive reliability evaluation and benchmark SACm solder with TV3.        | of<br>84 |

| Table 5.1 Failure distributions in low-CTE glass samples.                                                        | 88       |

| Table 5.2: Fatigue life of SAC105 interconnections: calculations vs. experimental.                               | 94       |

| Table 5.3: Drop test evaluation plan.                 | 97  |

|-------------------------------------------------------|-----|

| Table 5.4: Summary of drop test results.              | 98  |

| Table 5.5: Failure distribution of drop test samples. | 101 |

| Table 6.1: Technical challenges vs. research tasks.   | 107 |

#### SUMMARY

The trend towards ultra-miniaturization, high interconnection densities with minimal power consumption at low cost is driving the need for large, thin, high-stiffness substrate technologies capable of lithographic design rules below 5µm and inducing low stress on ultra-low K dielectrics while retaining high dimensional stability. Low-CTE organic and silicon interposers have been proposed to address some of these concerns and achieve chip-level reliability at larger die sizes and reduced I/O pitches, below 40µm. However, such advanced substrates face critical reliability challenges at board level due to large CTE mismatch with the organic PCB. Glass substrates have emerged as a promising alternative to organic and silicon interposer packages due to their tailorable coefficient of thermal expansion (CTE), high dimensional stability and surface smoothness, outstanding electrical properties and low-cost panel-level processability.

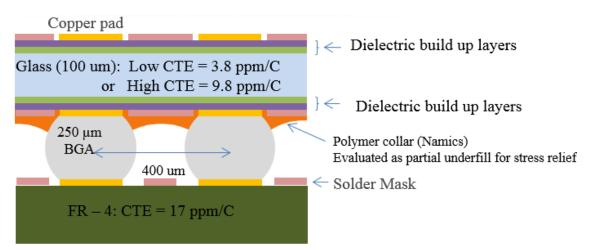

The primary focus of this thesis work is to: i) demonstrate for the first time drop and fatigue performances of large, thin, glass packages directly mounted on PCB with conventional BGAs at 400µm SMT pitch; and ii) evaluate scalability of solder-based interconnections to larger body sizes or finer BGA pitches with low- and high-CTE glass packages and the most advanced interconnection materials. In addition to glass packaging, two key innovations are introduced. First, in the form of reworkable circumferential polymer collars providing strain relief at critical locations of high strain concentration in the solder joint. Second, in the form of novel Mn-doped SACM<sup>TM</sup> solder to provide superior drop test performance without degrading thermomechanical reliability.

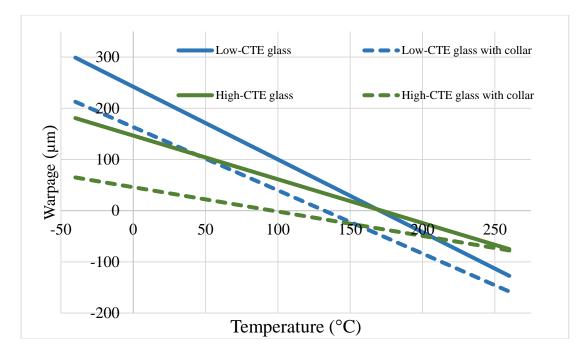

Finite-element modeling (FEM) was used to investigate the effectiveness of circumferential polymer collars as a strain-relief solution to improve fatigue performance. The models were built in 2D geometries to study the warpage response and predict the fatigue life of SAC105 interconnections at 400  $\mu$ m pitch with an 18.5mm × 18.5mm glass package that was SMT-assembled onto an organic printed circuit board. The assemblies

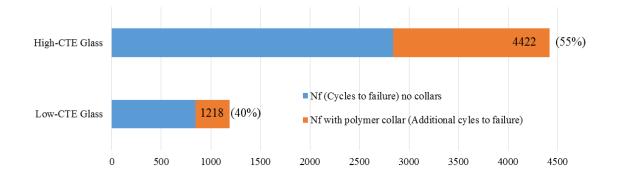

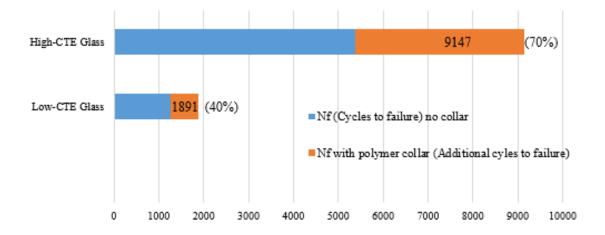

with polymer collars not only indicated lower net package warpage, but also showed between 40 - 70 % improvements in fatigue life, as predicted by Coffin-Manson and Engelmaier-Wild models.

Daisy-chain test vehicles were designed to carry out systematic evaluation of 1) polymer collars on reliability performance of low- and high-CTE glass packages; 2) thermomechanical reliability of SACM<sup>TM</sup> with system-level considerations, 3) drop and thermomechanical reliability of SACM<sup>TM</sup> with considerations of pad surface finishes.

Experimental results from the first test vehicle demonstrated a 2X improvement in drop performance and 30% improvement in fatigue life. Failure analysis was performed using characterization techniques such as confocal surface acoustic microscopy (C-SAM), optical microscopy, X-ray imaging, and scanning electron microscopy / energy dispersive spectrometry (SEM/EDS). Model-to-experiment correlation was performed to validate the effectiveness of polymer collars as a strain-relief mechanism. For the second test vehicle, a baseline stencil-based paste printing process for fabrication of 250µm BGAs at 400µm pitch had to be developed to evaluate the SACM<sup>TM</sup> solder which is currently available in paste form only. Shadow-Moiré warpage analysis was performed to explain the BGA balling and assembly yield. Thermal cycling test is ongoing, has reached 1000 thermal cycles, and will be pursued until failure. Fabrication of test wafers was completed on the third test vehicle and a systematic evaluation plan for comprehensive reliability testing was outlined for future work. These reliability studies demonstrated glass packaging as an ideal system integration platform for high performance, potentially enabling direct attach to the board of ultra-large, high-density 2.5D glass interposer packages.

#### **CHAPTER 1**

## **INTRODUCTION**

Transistor scaling, which began in 1949, has made electronics the largest global industry with a \$1.4T market in 2015 [1]. Advances in semiconductor technologies following Moore's Law have enabled integration of more than a billion transistors in a single integrated circuit (IC), resulting in rapid miniaturization of devices such as microprocessors that are used in today's servers, personal computers and mobile devices. While packaging of these devices was traditionally perceived as bringing minimal value to these applications, it now plays a key role in integration of heterogeneous functions as required by emerging electronic systems. Recent trends to miniaturized systems such as smartphones and wearables, as well as the rise of autonomous vehicles relying on smart incar systems, have brought unprecedented integration challenges with escalating performance, functionality, and cost requirements impossible to meet by transistor scaling alone. A novel system scaling approach has been proposed by Georgia Tech to address these challenges and to achieve complete integration of heterogeneous microsystems, starting the "System Moore" era [1].

## 1.1 Transistor scaling to system scaling trends in microelectronics packaging

Consumer and high-performance applications have been aggressively driving advances in device technologies over the last decades to meet the escalating needs for high bandwidth and transmission speeds at low power and low cost. Transistor scaling, following Moore's Law, has enabled continuous advancements in logic and memory integrated circuits (ICs), including the introduction of ultra-low-K dielectrics to minimize on-chip parasitics [2]. It also gave rise to the System-on-Chip (SOC) technology consisting of monolithic integration of multiple functions such as digital, analog, and radio-frequency circuitries in an IC. SOC focuses solely on the device integration and optimization of its performance, which means packaging brings little value and may be eliminated by wafer-level fan-out and embedding technologies. However, SOC integration faces many challenges from design and process complexity, bringing yield and cost issues, and limiting its applicability for complete system integration with many heterogeneous functions. Transistor scaling has also slowed down in recent years, diverging from Moore's Law, with no further cost reduction beyond the 14nm node, forcing the semiconductor industry to rethink its integration strategy.

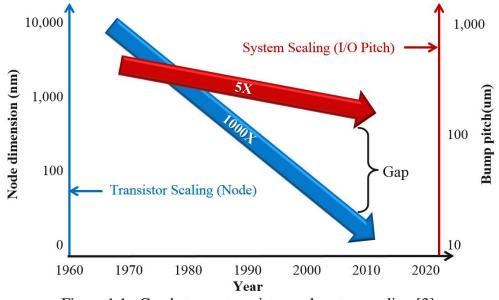

More-than-Moore technology was subsequently pursued to achieve higher functional densities and integrate components at module level, such as vertically stacked ICs and packages (SIP) technology. Vertical stacking of thinned silicon ICs using standard wire-bonding and flip-chip technologies was proposed to address design complexities and latency issues observed in SOC. In SIP, through-silicon vias (TSVs) were implemented to achieve 3D integration while providing design flexibility and miniaturization. This, however, means that the performance of the system relies on the processing power of the ICs. Subsequently, this approach faces the same integration limitations as SOC [2]. The gap between transistor scaling (qualified by the gate length of a transistor) and system scaling (represented by off-chip interconnection pitch), shown in Fig. 1.1, indicates the need for a new paradigm for system integration and miniaturization [3].

Figure 1.1: Gap between transistor and system scaling [3].

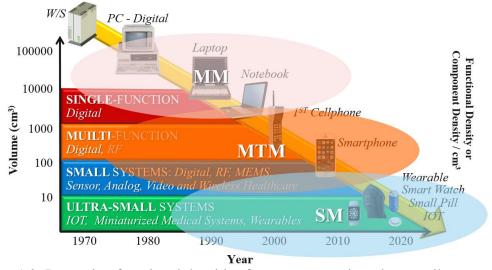

To address this fundamental challenge, the 3D Systems Packaging Research Center at Georgia Tech has been pioneering System-on-Package (SOP) to achieve complete system integration and miniaturization. The schematic of Fig. 1.2 introduces System Moore as the new frontier for system scaling, beyond Moore's and More than Moore's Laws. In the SOP approach, components, package, and system board are co-designed to realize all required heterogeneous functions of emerging electronic systems. Packaging now becomes a key enabler to reduce the overall system cost and size, thus it can add value to the system. An example reflecting this change is the recent trend of "die split" where large devices are split into multiple smaller ones to significantly improve yields and optimize cost [4]. Functionality is then reconstructed through the substrate with high-density die-to-die interconnections at pitches close to matching back-end-of-line (BEOL) technology. Advancing packaging technologies is therefore critical in the realization of SOP to enable next-generation ultra-miniaturized heterogeneous systems, from smartphones to autonomous vehicles and cloud computing.

Figure 1.2: Increasing functional densities for next-generation ultra-small systems: system scaling by System Moore (SM) for heterogeneous integration beyond More of Moore (MM) and More than Moore (MTM) [1].

## 1.2 Board-level Interconnections and Reliability Requirements

Typical packaging solutions in Moore's Law era consisted in integration of Si devices onto organic packages, then assembled onto a system board using low-cost, surface-mount (SMT) compatible technologies. For the last two decades, solder-based ball grid array (BGA) interconnections have been the primary technology of choice for SMT assembly of microprocessor packages to printed circuit boards (PCBs). Package-to-board interconnections in modern consumer electronic products such as smartphones have to meet both drop and thermomechanical reliability requirements, as defined by JEDEC standards [5, 6]. The drop performance is conditioned by the ability of the solder material to absorb shock energy, driving towards soft solders with lower elastic modulus and yield strength.

The mismatch in coefficients of thermal expansion (CTE) between package and board brings cyclic strains in solder joints with variations in temperature acting as thermal loading. These strains are given by the equation below [7]:

$$\Delta \gamma \alpha \frac{L_{\text{DNP}}(\alpha_{\text{PWB}} - \alpha_{\text{pack}})\Delta T}{h}$$

(Eq. 1.1)

in which  $L_{DNP}$  is the distance to the neutral point (DNP), between solder joint and the center of the package; h is the solder height;  $\Delta T$  is the temperature change during each loading cycle; and  $\alpha_{pack}$  and  $\alpha_{PWB}$  are the CTEs of the package and PCB, respectively, as illustrated in Fig. 3. Accumulation of plastic strains under thermal cycling results in crack initiation and propagation in solder joints and, ultimately, in fatigue failures. Thermomechanical reliability is therefore conditioned by the ability of the solder material to prevent and accommodate plastic deformation, which is superior in hard solders with higher elastic modulus and yield strength.

Figure 1.3: Die-package-board interconnections with large LDNP and low stand-off height.

Drop and thermal cycling reliabilities are consequently driving opposite material requirements for solders, but are equally critical to satisfy, bringing challenges for interconnection material design.

Reworkability is also highly desirable at board level, preventing the use of underfills, traditionally implemented to improve thermomechanical reliability at chip level.

# 1.3 Board-level reliability challenges with evolution of substrate technologies for system scaling

Demands for thinner consumer electronic products have led the trend for package thickness reduction. However, such reduction exacerbates substrate warpage, degrading SMT assembly yield and, subsequently, reliability. Further, increasing functional densities in emerging applications are driving the need for greater I/O count, and subsequently for larger die sizes at finer I/O pitches. Current packages are consequently expected to migrate to sizes larger than 20 mm x 20 mm with progressive reduction in pitch to below  $40\mu m$ . Organic and silicon substrates with CTEs matching to Si chips have, therefore, gained momentum to meet chip-level reliability requirements and minimize stresses on low-K dielectrics. Such large, low-CTE substrates still have to be mounted onto a PCB, displacing the CTE mismatch to board level. To accommodate the increase in I/O count, the BGA pitch also needs to reduce to  $400\mu m$  and below, further aggravating solder strains as per equation 1.1, and board-level reliability concerns. To address these challenges, an additional package layer was introduced between the low-CTE interposer and PCB to redistribute pitch and mitigate reliability. This 3-layer hierarchy, however, degrades electrical performance by increasing interconnect parasitics, and adds to the cost of the overall system. More recently, silicon interposers have gained importance in highperformance split-die applications as they satisfy sub-5µm lithographic design rules required for high-density die-to-die interconnections. These interposers frequently exceed 30mm x 40mm in body size, bringing unprecedented challenges for board-level thermomechanical reliability.

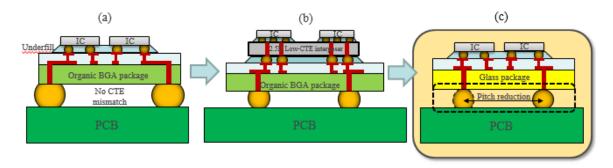

A novel 2-level packaging solution enabling direct, SMT interconnection of large and thin packages to the board is thus highly sought after by the semiconductor industry, as illustrated in Fig. 1.4.

Figure 1.4: Traditional package approach (a) IC – organic BGA – PCB, current package (b) IC – low-CTE interposer – organic BGA – PCB, and new package approach (c) IC – large and thin glass package – PCB.

Glass substrates have emerged as a promising alternative to organic and silicon substrates for system scaling, owing to their:

- Excellent electrical properties, including low-dielectric constant, high resistivity, and low insertion losses as compared to silicon;

- Superior dimensional stability as compared to organic, enabling micron-level lithographic design rules;

- Tailorable CTE from silicon (~3ppm/K) to organic (14-17 ppm/K);

- High modulus and intrinsic strength for lower warpage as compared to organic;

- Panel-level to roll-to-roll processability for low cost [8, 9].

Benefitting from these unique properties, glass packaging can potentially address all aforementioned challenges for system scaling. The tailorable CTE and high modulus can mitigate warpage introduced by thickness reduction. Further, the tailorable CTE can optimize chip- and board-level reliability. With glass, the desired 2-level hierarchy can therefore become possible, which has yet to be fully demonstrated.

#### **1.4 Research objectives**

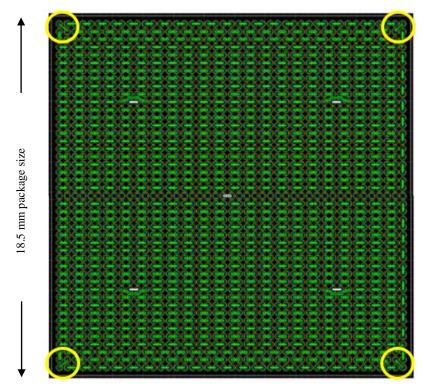

The primary goals of this work are to: 1) demonstrate board-level reliability of large, thin, low- and high-CTE glass packages directly mounted on PCB with conventional BGAs at 400µm SMT pitch; and 2) evaluate scalability of solder-based interconnections in a 2-level hierarchy to larger body sizes or finer BGA pitches. The critical performance metrics associated with the research objectives, beyond prior art, are summarized in Table 1.1.

| Table 1.1. Research objectives beyond phot art. |                            |                                       |                                    |  |

|-------------------------------------------------|----------------------------|---------------------------------------|------------------------------------|--|

| Metrics                                         | Conventional<br>package    | Current package                       | Research objectives                |  |

| Package size                                    | Small up to<br>15mm x 15mm | Medium to large:<br>up to 30mm x 40mm | 18.5 mm × 18.5 mm                  |  |

| SMT pitch                                       | > 500 µm                   | 400 – 500 μm                          | 400 µm                             |  |

| CTE mismatch                                    | None                       | Large                                 | Small to large                     |  |

| Hierarchy                                       | Two-level                  | Three-level                           | Two-level                          |  |

| Manufacturability                               | SMT-compatibility          | SMT-compatibility                     | SMT-compatibility<br>Reworkability |  |

Table 1.1: Research objectives beyond prior art.

## 1.5 Unique approach addressing technical challenges

The technical challenges faced by package-to-board interconnections in advanced package architectures can be summarized as follows:

- Aggravated solder strains and warpage with large, thin substrates at finer I/O SMT pitches, degrading thermomechanical reliability;

- Balanced drop and thermal cycling performances.

Proposed solutions also need to maintain SMT-compatibility and reworkability, as well as have minimal system-level impact.

Benefitting from its unique mechanical properties, glass is proposed to realize the research objectives and achieve, for the first time, board-level reliability of glass BGA packages at 18.5 mm x 18.5mm body size, 100µm thickness and 400µm SMT pitch. In GT-PRC's previous work at board level, superior thermal cycling reliability was demonstrated at 7.2mm x 7.2mm body size, passing up to 1300 thermal cycles with low-CTE glass [10]. This work was extended to 18.5mm x 18.5 mm but no clear conclusions could be reached from previous thermal cycling evaluation [13]. The drop test performance of glass BGA packages was never addressed.

In addition to glass packaging, two key innovations are introduced to further improve drop test and thermal cycling performances of glass BGA packages with minimal changes to current infrastructures and processes: 1) circumferential polymer collars; and 2) doped, lead-free solder alloys. The cross-section schematic of Fig. 1.5 illustrates the novelty of the proposed approach.

| Glass Package with tailorable CTE |                   |                           |  |

|-----------------------------------|-------------------|---------------------------|--|

|                                   | Polymer<br>Collar | Novel<br>Doped<br>Solders |  |

|                                   | PCB               |                           |  |

Figure 1.5: Unique approach for board-level reliability of large, thin glass BGA packages.

#### Circumferential polymer collars as reworkable underfills

Epoxy-based underfills with silica fillers have traditionally been used to improve thermomechanical reliability of solder-based interconnections at chip level. Underfills provide strain relief in solder joints by mechanically coupling device to package over the entire die footprint and mitigating their CTE mismatch. Application of underfills at board level is however undesirable as it compromises reworkability and has a strong system-level impact with alteration of substrate warpage and subsequent effect on chip-level reliability. Reinforced polymer collars have been proposed in wafer-level packaging (WLP) as a partial underfilling solution providing strain relief solely in locations of highest stress concentration, where failure would normally originate in the solder joints during thermal cycling. The Spheron<sup>TM</sup> technology has been demonstrated to effectively improve fatigue life of solders by 30-50% [11, 12].

Georgia Tech PRC and its industry partner Namics Corporation Inc. have recently extended this concept at board level with a new class of filler-free epoxies with low modulus and high CTE. Circumferential polymer collars can be formed with varied thicknesses around the BGA solder joints by a spin-coating process, as shown in Fig. 1.6. The collar thickness was optimized as a trade-off between providing effective strain relief and meeting assembly manufacturability constraints of SMT compatibility and reworkability [13].

Figure 1.6: Optimization of collar thickness to provide best compromise of strain relief and reworkability [13].

This work goes beyond previous empirical studies by investigating the fundamental strain-relief mechanisms through modeling and experimental validation, with considerations of plastic strain distributions in solder BGAs and of substrate warpage.

### Doped lead-free solder alloys

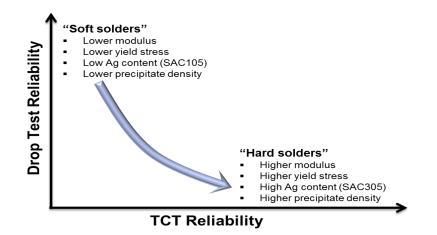

The ban of lead in 2006 by the Restriction of Hazardous Substances (RoHS) and the Waste Electrical and Electronic Equipment (WEEE) directives forced the semiconductor industry to drop their interconnection material of choice: eutectic tin-lead solder. Extensive research has been carried out to identify suitable lead-free replacements matching the outstanding physical properties, fatigue performance and manufacturability of eutectic tin-lead solder [14]. Among the potential candidates, SnAgCu (SAC) alloys have become prevalent over other lead-free solder systems benefitting from their low cost and superior properties such as relatively low melting point, excellent wettability, superior corrosion resistance and tailorable modulus and yield strength with variation of Ag content [15, 16]. Soft solders with low Ag content such as SAC105 are found more suitable for drop testing due to their lower yield strength, modulus, and higher ductility; while hard solders with higher Ag content such as SAC305, are more favorable to thermal cycling, as illustrated in Fig. 1.7 [17].

Figure 1.7: Contrasting solder requirements for drop test and thermomechanical reliability.

Improvements in fatigue life with standard SAC alloys thus come at the cost of the drop performance, which is equally critical in consumer products. Advances in solder materials are, therefore, required to achieve balanced thermomechanical and drop reliability. Solder properties are highly dependent on the alloy composition and microstructure, and can be selectively tailored by minor addition of other elements without affecting processability. Recently, Indium Corporation proceeded with systematic evaluation of dopants such as Ti, Ni, Bi, Y, Ni or Zn to optimize the properties of standard SAC alloys. This work resulted in the development of the Mn-doped SACM<sup>TM</sup> alloy, which enables improved drop test performance as compared to SAC 105 with similar fatigue life than SAC305 [18]. However, the SACM<sup>TM</sup> alloy is currently commercially available in paste form only, thus limiting its applicability to pitches of 500µm and above in high-volume manufacturing. In this work, the SACM<sup>TM</sup> solder is evaluated, for the first time, at 400µm SMT pitch.

The proposed unique approach realizes the research objectives with novel strainrelief mechanisms and innovations in solder materials to improve board-level reliability of ultra-thin glass BGA packages, and further extend the applicability of standard solderbased interconnections in package size and SMT pitch.

#### 1.6 Thesis Tasks and Organization

The research accomplished in this thesis work is organized into six chapters. Chapter 1 introduced the transistor and system scaling trends, recent evolution of substrate technologies bringing reliability challenges at board level, the research objectives and unique approach proposed to address the technical challenges.

Chapter 2 consists of a detailed review of the state-of-the-art of board-level interconnection technologies. Prior art on polymer collars as a strain-relief mechanism as well as solder doping for improved drop and thermal cycling performances is also reported.

Chapter 3 summarizes finite element modeling pursued to gain an understanding of the fundamental mechanisms by which polymer collars improve thermomechanical reliability, including warpage considerations. The solder fatigue life predicted with both Coffin-Manson and Engelmaier-Wild models is reported as guidelines for the experimental evaluation of Chapter 4.

Chapter 4 details the design, fabrication and assembly of three test vehicles. The specific research tasks associated to each test vehicle (TV) are:

- i) TV1: evaluation of the effect of polymer collars on the thermomechanical and drop performance of low- and high-CTE glass BGA packages;

- ii) TV2: evaluation of thermomechanical reliability of glass BGA packages with doped solder alloys, comparing SACM<sup>TM</sup> with standard SAC305 and SAC105;

iii) TV3: drop and accelerated thermal cycling tests with SACM<sup>TM</sup>, considering the effect of pad surface finish.

Chapter 5 reports the results of reliability evaluations on the three test vehicles, with detailed failure analysis using characterization techniques such as confocal surface acoustic microscopy (C-SAM), optical microscopy, X-ray imaging, and scanning electron microscopy/energy dispersive spectrometry (SEM/EDS). Model-to-experiment correlation highlighting the effectiveness of polymer collars in relieving solder strains is also detailed.

Chapter 6 gives a summary of the overall research, aligning results with the defined research objectives. The chapter concludes with suggestions for future work, towards system-level reliability.

#### **CHAPTER 2**

## LITERATURE REVIEW

This chapter starts with an overview of IC packaging and interconnection technologies along with an overview of the recent advances in multichip packaging with fine pitch and high I/O density. Material and process innovations to address fine-pitch challenges, such as advanced solders, pad surface finishes, and underfills for enhancing reliability performance are highlighted. Innovations to address reliability concerns through a variety of compliant interconnections pursued both in universities and industry are also briefly summarized. Finally, board-level reliability research previously accomplished at GT-PRC is reviewed.

#### 2.1 Evolution of IC packaging

This section summarizes the evolution of electronics packaging from traditional single-chip packages to the complex state-of-the-art multi-chip packages driven by miniaturization, functionality and a dramatic increase in bandwidth requirements in high-performance systems. With reduced interconnection pitches and increasing package sizes, need for advances in board-level interconnections is further reinforced.

#### 2.1.1 Traditional packaging

IC packaging evolved with small outline (SO) and single-chip packages (SCPs) that were individually attached to the PCB in order to meet the electrical, mechanical, and thermal requirements for low I/O applications. Dual-in-line (DIP) and quad-flat packages (QFN), later introduced for commercial use, consisted of metal leads that are distributed along the sides for interconnections. In the late 1980s, the limited I/O capability of DIP and QFN for very large scale systems integration (VLSI) applications in low-end microprocessor and memory devices, led to the developments in area-array packaging. In the pin grid array (PGA) packages, higher I/O count could be achieved by distributing the pins throughout the package surface [4]. IBM was the first to demonstrate high-aspect ratio PGA packages made of low-temperature co-fired ceramic (LTCC) modules that are still currently in use for some high-performance computing applications [17]. In the mid-1990s, Intel also manufactured computer chips using PGA packages [18]. However, with PGA, the interconnection pitch reached its practical manufacturing limit and could not be further scaled down below 1mm.

Alternatively, the pins were replaced with solder balls to form ball grid arrays (BGA), significantly boosting the interconnection density. Conventionally, with PGA, mounting was performed using the through-hole method, in which the leads are inserted into holes drilled in printed circuit boards and soldered to the other side. However, with BGA, surface-mount devices (SMD) could be directly mounted onto the system board with pre-defined solder pads (with surface finish) by a pick-and-place machine and reflow (melting and cooling the solder under a specific temperature profile) to create adherence and electrical connections. Thus, surface-mount technology (SMT) advanced as a primary technique to directly mount packages onto PCB. This method enables reliable assembly of smaller components with high I/O density at lower cost and increased high-volume production throughputs. Furthermore, other added benefits include higher alignment error tolerance, double-sided circuit board placement, and overall better mechanical attributes.

The escalating yield and manufacturability challenges with large ICs eventually led to their partitioning into multiple devices that are then packaged into a multi-chip package or multi-chip modules (MCM) as shown in Fig. 2.1 (a). IBM has pioneered the ceramicbased MCM for certain application-specific ICs (ASIC) and high-performance server systems [19]. Furthermore, Stacked ICs and Packages (SIP) enabled 3D stacking of multiple ICs for system miniaturization either by stacking of bare or packaged ICs by traditional wire-bonding or flip-chip technologies or by stacking of through silicon vias (TSVs) as shown in Fig 2.1 (b). TSV-enabled vertical chip-to-chip or chip-to-package interconnection reduces the interconnection length, thereby reducing signal latency. However, SIP has several limitations including heat generation, stress management, process integration, and fabrication of TSVs. Addressing the short-comings of SIPs, innovations in 2.5D and 3D package architectures are coming to the forefront.

Figure 2.1: Schematic representation of (a) multi-chip module, (b) stacked IC and package.

#### 2.1.2 Recent advances in multi-chip packaging

With emerging trends towards miniaturization and system scaling, over the last decade, 2.5D and 3D package integration are gaining prominence in the quest for low-latency, ultra-high I/O density, low-power interconnection, shorter off-chip interconnection pitch, large package sizes, and low cost.

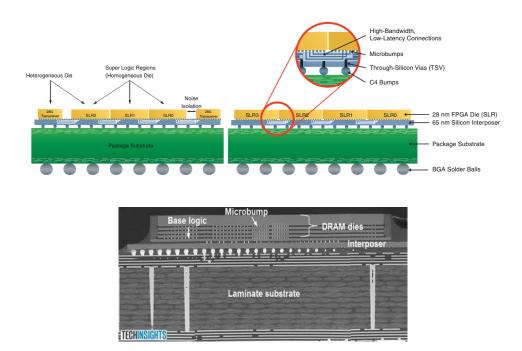

In a typical 2.5D architecture, the ICs are integrated side-by-side through multiple layers of intertwined copper wirings and metalized through package vias (TPVs) in the interposer or package. Copper traces featuring ultra-fine lines and spaces allow for short interconnections between ICs, enabling high-speed signal transmission. The dies are interconnected by standard reflow or thermocompression bonding (TCB) techniques on high-density interposers then assembled onto organic substrates. Finally, SMT assembly of the organic substrate connects the die to the system board. In 2010, Xilinx demonstrated successful 2.5D integration with heterogeneous dies on a Si interposer as shown in Fig. 2.2 (a) [20]. SK Hynix's HBM in Fig. 2.2 (b) also illustrates this 3-level hierarchy with 4HBM stacks and a GPU assembled on a 30mm x 38mm Si interposer [21].

Figure 2.2: 2.5D silicon interposer from (a) Xilinx and (b) Hynix.

Si, however, suffers from high signal losses due to dielectric and conductor losses and high cost due to small 300 mm size wafer processing and manufacturing. Further, in order to compensate for the CTE mismatch between Si and organic PCB, there is a need for an additional organic BGA package between interposer and system board. Low-CTE organic interposers are being developed to overcome the limitations of Si interposers, but are fundamentally limited in I/O density. In both cases, concerns over board-level thermomechanical reliability are further aggravated by the recent trends towards SMT pitch scaling, below 400µm, reduced substrate thicknesses and larger packages sizes.

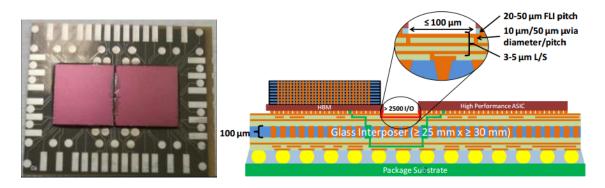

Glass substrates have emerged as a promising alternative to organic and silicon interposer packages due to their tailorable CTE, high dimensional stability and surface smoothness, outstanding electrical properties and low-cost panel-level processability. GT-PRC has been pioneering glass packaging research since the last six years and has demonstrated 2.5D packages (Fig. 2.3), composed of ultra-thin glass, 100µm in thickness. Glass substrates are readily available both in low-CTE (3.8 ppm/°C) and high-CTE (9.8 ppm/°C) in large panel sizes or roll-to-roll form. Through glass vias at as low as 30µm pitch and fine-pitch RDL with microvias at less than 10µm enable 40µm chip-level I/O pitches in development and 20 µm pitch in research [22].

Figure 2.3: Georgia Tech's 2.5D Glass Interposer Package.

The packaging industry has been innovating several other interconnection techniques including Intel's Embedded Multi-die Interconnect Bridge (EMIB), fan-out wafer-level packaging platform (FOWLP), Amkor's Silicon-Less Integrated Module (SLIM), and Silicon Wafer Integrated Fan-out Technology (SWIFT) which are also briefly reviewed.

## Intel EMIB (Embedded Interconnect Bridge)

EMIB simplifies the 2.5D approach for high-density interconnections between heterogeneous dies on a single package. The key innovation in this technology is that instead of utilizing a silicon interposer with TSVs, a small silicon bridge is embedded with multilayer RDL in the package, enabling very high density die-to-die interconnections. Intel announced availability of EMIB technology to 14nm foundry customers in 2015. EMIB aims at cost-effective fabrication by eliminating Si interposer with TSV while also reducing the number of assembly steps as shown in Fig. 2.4 [23].

Figure 2.4: Conventional 2.5D assembly (left), Intel's EMIB assembly (right).

## FOWLP (Fan-out Wafer-Level Packaging)

FOWLP provides a versatile platform for 2D, 2.5D and 3D integration with higher I/O density at low cost. It also offers advantages over conventional wafer-level packaging (WLP) such as more real estate for higher I/O counts, testability by probing pads on fan-out wafers to evaluate known good dies (KGD), protection from the mold compound that prevents die sidewalls from chipping/cracking during SMT assembly, heterogeneous integration with actives and passives with fine line and space for high-density routability. Therefore, FOWLP enables miniaturization with

smaller form factors, eliminating the need for chip-package interconnections and substrates, thereby enabling excellent electrical performance due to shorter interconnections, leading to lower parasitics. Steps to achieve FOWLP are shown in Fig. 2.5 (Courtesy of Beth Keser, Qualcomm) [24]. Companies such as TSMC, STATS ChipPac, Infineon and Nanium have developed their own variations of FOWLP [25].

Figure 2.5: Process flow to achieve FOWLP - Courtesy of Beth Keser (Qualcomm Inc.), Guest Lecture on WLP, CPMT

In 2015, Amkor Technology Inc. announced their SLIM and SWIFT technologies (Fig. 2.6). Like EMIB, SLIM is an alternative approach eliminating Si interposer, improving upon 2.5D and fan-out design. It is a dies-last package technology, offering compact form factors with highest level of integration, combining traditional back end of the line (BEOL) and assembly fan-out architectures. SWIFT, on the other hand, addresses shortcomings associated with conventional fan-out. High performance is attributed to integration of advanced polymer-based dielectrics, heterogeneous integration of multi-dies,

interconnection densities below 2/2μm line and space, Cu-pillar interconnections at 30μm pitch and capability of large package body sizes [26, 27].

Figure 2.6: Amkor Technology Inc's SLIM (left) and SWIFT (right).

#### 2.2 Recent material developments in board-level interconnections

With all the aforementioned state-of-the-art technologies, a common emerging trend is the aggressive scaling of interconnection pitches at chip level and shift to larger package body sizes. Therefore, improving thermomechanical performance at board level without degrading reliability at chip level is a grand engineering challenge. In parallel, with the SMT pitch scaling below 400µm, concerns over board-level reliability are further aggravated due to higher solder strains and warpage. Advances in material development in existing technologies at the board-level including pad surface finishes, standard SAC solders and underfills are studied in this section.

As mentioned in Chapter 1, BGAs generally composed of standard SAC alloys are used to form metallurgical joints between the copper pads on the package and the board. The copper pads are generally covered by a thin layer of surface finish providing a suitable surface for soldering and formation of intermetallics (IMCs). Upon reflow, the solder melts above its melting point, wetting the surface of the copper pad. During wetting, the melt partially dissolves the thin surface finish and the underlying elements, up to their solubility limits, forming IMCs due to diffusion phenomenon [28]. In this interfacial reaction, the growth kinetics that determine the IMC thickness are governed by the parabolic growth law:

$$L = (Dt)^{\frac{1}{2}}$$

(Eq. 2.1)

where 'L' is the average thickness of the IMC layer, D is the temperature dependent diffusion coefficient, and 't' represents the time. IMCs are generally composed of ordered alloy phases of two or more metals in a narrow compositional range. They are vital in providing mechanical joint strength and chemical stability [29].

# 2.2.1 Advances in pad surface finishes

Pad surface finishes play a critical role in determining reliable solder joint formation with excellent solderability and IMC formation. Some traditionally used surface finishes include hot air solder leveling (HASL), organic solderability preservative (OSP), immersion Sn (ImSn) and immersion Ag (ImAg).

HASL, despite its excellent solderability and low cost, is non-uniform and, hence, not suitable for fine-pitch applications. OSP has a short operating window between assembly stages and is highly prone to oxidation [30]. ImSn has concerns with tin whisker formation and ImAg requires special handling and is more expensive [31]. Table 2.1 highlights the critical attributes and summarizes the pros and cons of the above mentioned surface finishes.

| Surface finish attributes      | HASL | OSP | ImSn | ImAg |

|--------------------------------|------|-----|------|------|

| Solderability                  |      |     |      |      |

| Long shelf life                |      |     |      |      |

| Surface oxidation              |      |     |      |      |

| Tin whisker formation concerns |      |     |      |      |

| Applicability at fine-pitch    |      |     |      |      |

| Uniformity/flatness            |      |     |      |      |

| Low cost                       |      |     |      |      |

Table 2.1: Summary of pros and cons of HASL, OSP, ImSn and Imag [31].

Addressing the technical limitations of above-mentioned pad finishes, two popular technologies in practice today are electroless nickel immersion gold (ENIG) and electroless nickel electroless palladium immersion gold (ENEPIG). With these surface finishes, two predominant intermetallics are formed, Cu<sub>6</sub>Sn<sub>5</sub>, and Ni<sub>3</sub>Sn<sub>4</sub>. Table 2.2 summarizes the primary and secondary IMCs formed with SAC solders with OSP, ENIG and ENEPIG surface finishes [32].

| Surface Finish | Primary IMCs                                                      | Secondary IMCs                                                                        |

|----------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|                |                                                                   |                                                                                       |

| OSP            | $Cu_6Sn_5$                                                        | Cu <sub>3</sub> Sn                                                                    |

|                |                                                                   |                                                                                       |

| ENIG           | Cu <sub>6</sub> Sn <sub>5</sub> , Ni <sub>3</sub> Sn <sub>4</sub> | (Cu,Ni) <sub>6</sub> Sn <sub>5</sub> , Cu <sub>3</sub> Sn, Ni-Sn-P, Ni <sub>3</sub> P |

|                |                                                                   |                                                                                       |

| ENEPIG         | Cu <sub>6</sub> Sn <sub>5</sub> , Ni <sub>3</sub> Sn <sub>4</sub> | (Cu,Ni) <sub>6</sub> Sn <sub>5</sub> , Cu <sub>3</sub> Sn, Ni-Sn-P, Ni <sub>3</sub> P |

|                |                                                                   |                                                                                       |

Table 2.2: Primary and secondary IMCs formed with common pad surface finishes

During reflow, the solder dissolves the thin protective gold layer and some portion of the Ni (in ENIG and ENEPIG), which also acts as diffusion barrier between the solder and copper, retarding excessive IMC growth. Fig. 2.7 indicates the finer IMC thickness in cases of ENEPIG in comparison to ENIG after reflow and 1000 hours of thermal aging at 125°C. Several literature studies have indicated higher reliability with ENEPIG in comparison to ENIG, in both thermal cycling and drop test [33, 34, and 35]. In case of ENEPIG (and EPAG), the palladium (Pd) layer further acts as an advanced diffusion barrier [36].

Figure 2.7: IMC thickness for ENIG and ENEPIG after reflow (a) and (b); and after 1000 hours of thermal aging (c) and (d).

The thickness of the IMC formed is dependent on the reflow time and number of reflow cycles as shown in Fig. 2.8 [37]. According to the standards defined in JEDEC, JESD22-A104D, two additional reflows are required before initiating thermal cycling reliability testing [38]. The IMCs grow further during thermal ageing or cycling. Presence of continuous brittle IMC layers often serves as ideal initiation sites for crack origin and propagation leading to interfacial fractures [39].

IMC thickness is therefore a critical factor in determining the interfacial strength between the solder and the surface finish. Further, with the low % (1 - 4%) of silver in SAC alloys, brittle needle-shaped Ag<sub>3</sub>Sn are formed in addition to Cu<sub>6</sub>Sn<sub>5</sub>, which are

known to be detrimental to reliability performance [40]. Thus, lower IMC thickness is desired for both TCT and drop test reliability.

Figure 2.8: Progression of IMC growth after multiple reflow cycles with various pad surface finishes.

In emerging high-performance systems, the 'die split' trend is driving the need for high-density interconnections at sub-5um pitch. ENIG and ENEPIG, with nickel thicknesses, ~5 to 7 $\mu$ m, finishes impede their pitch scalability and applicability with sub-10 $\mu$ m gaps between traces. New, ultra-thin surface finish technologies with a fine control of extraneous plating are thus required to enable high-density wiring at finer pitches, and meet the integration and performance needs of tomorrow's computing systems. The electroless Pd autocatalytic Au (EPAG) finish has been developed by Atotech GmBH as a novel solution for fine-pitch applications. With thicknesses in the 50-150nm range, it enables a gap loss between traces of less than 5%, while improving insertion losses |S21| at 67 GHz by 1 dB [41]. EPAG therefore is an ideal finish for chip assembly, but its boardlevel reliability performance is yet to be qualified.

### 2.2.2 Advances in standard solders by doping

Besides the advances in pad surface finishes, developments in solders by refining microstructure with introduction of dopants have been extensively researched. Standard SAC alloys with doped alloying elements such as Germanium (Ge), Nickel (Ni), Manganese (Mn), Cerium (Ce), Bismuth (Bi), Titanium (Ti), and Yttrium (Y) have been recently studied due to their low melting points and low solid solubilities in the dominant phase within the rich  $\beta$ -Sn matrix [42]. After reflow and solidification, doping is reported to refine solder microstructure by making the grains finer, and improving the tensile and creep resistance in lead-free solders. Precipitation of heterogeneous intermetallic compounds along the interfaces can hinder dislocation motion, reduce grain boundary sliding and increase fracture resistance [43, 44].

Lin et al. have studied alloying modifications of SAC105 (Sn-1.0Ag-0.5Cu) with Mn and Ti to analyze the resulting microstructure and solidification behavior. It was found that the Mn and Ti dopants dramatically reduce the required undercooling for initiating crystal nucleation, and refine the extended volume fraction of pro-eutectic Sn. Addition of Mn and Ti refined the morphology of Sn dendrites by formation of heterogeneous IMCs such as MnSn<sub>2</sub> and Ti<sub>2</sub>Sn<sub>3</sub>, which also hindered the formation of detrimental intermetallics such as Ag<sub>3</sub>Sn and suppressed the thickness of Cu<sub>6</sub>Sn<sub>5</sub>. The microstructures of SAC305, SAC105, and SAC 105 with 0.15Mn, 0.5Mn, 0.15Ti and 0.5Ti are shown in Fig. 2.9 a–f. With dopants, finer precipitates with inclusions of heterogeneous IMCs along the grains can be observed in Fig. 2.9 c-f [45].

Figure 2.9: Microstructures of (a) SAC305, (b) SAC105, (c) SAC105 + 0.15Mn, (d) SAC105 + 0.5Mn, (e) SAC105 + 0.15Ti and (f) SAC105 + 0.5Ti [45].

Formation of heterogeneous IMC is attributed to reduction in undercooling by 4°. Consistent with classical thermodynamics explanation, with lower undercooling, the driving force or Gibbs free energy for formation of non-faceted heterogeneous IMC is lower than that of faceted or crystalline IMCs like Cu<sub>6</sub>Sn<sub>5</sub> and Ag<sub>3</sub>Sn. The cooling curve shown in Fig. 2.10 for low Ag SAC alloy and simplified pseudo-binary phase diagram illustrates the shift in eutectic and reduced undercooling ( $\Delta$ T) with introduction of Mn or Ti. The extended volume fraction of β-Sn, although by reducing the elastic modulus, benefits drop performance, distribution of hard heterogeneous MnSn<sub>2</sub> and Ti<sub>2</sub>Sn<sub>3</sub> provides a strengthening effect improving the fatigue life of the solder [45].

Figure 2.10: Cooling curve (a) for low Ag SAC solder and (b) simplified binary phase diagram with variation in undercooling.

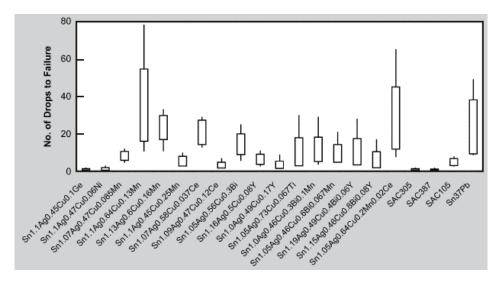

Liu and Lee (Indium Incorporation) have investigated various dopants in SAC alloys including Ge, Ni, Mn, Ce, Bi, Y, and Ti. With SAC305, SAC387, SAC105 and Sn37Pb as reference, the study of 17 different variations of SAC alloys with dopants revealed SAC105 + .13% Mn as the best proposition for balanced drop test and thermal cycling reliability. The drop test results for this study are detailed in Fig. 2.11 [46].

Figure 2.11: Drop test reliability of SAC solder with dopants.

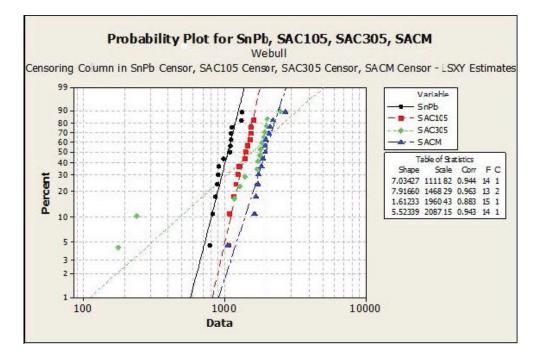

Based on their experimental findings, Indium commerciallized SACM<sup>TM</sup> in 2015 as an alternative low Ag content standard SAC solder, addressing the trade-offs between excellent thermal cycling fatigue life and drop shock resistance. Even with low Ag content (1%), SACM<sup>TM</sup> delivers better thermal cycling reliability than that of SAC305 while also offering upto 7x improvements in drop test reliability in comparision to SAC105. The Weibull distrubution plot for thermal cycling results achieved with SnPb, SAC105, SAC305 and SACM are shown in Fig. 2.12 [47]. The superior performance of SACM was attributed to refined microstructure and enhanced interfacial bond strength with inhibition of rapid IMC growth.

Figure 2.12: Thermal cycling results for SnPb, SAC105, SAC305 and SACM<sup>TM</sup>.

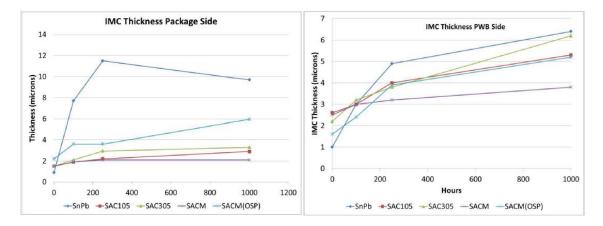

Lee et. al also confirmed lower IMC thickness in SACM on either sides of the solder joint as indicated in Fig. 2.13, with NiAu and OSP pad surface finishes [47]. SACM, however, is currently available in only paste form limiting its applicability at pitch sizes above 500µm.

Figure 2.13: IMC thickness on package and PCB side.

## 2.2.3 Advances in underfill materials

Underfills are primarily used to enhance reliability of chip-level interconnections by redistributing the stresses away from the solder joints. Underfills prevent reworkability, which is an important criterion for board-level assembly. Therefore, they are not widely used for board-level interconnections. Few recent advances in underfills that are of interest are briefly highlighted here.