## Adaptive Analog VLSI Signal Processing and Neural Networks

A Thesis Presented to The Academic Faculty

${\rm by}$

## Jeff Dugger

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

School of Electrical and Computer Engineering Georgia Institute of Technology November 2003

Copyright © 2003 by Jeff Dugger

## Adaptive Analog VLSI Signal Processing and Neural Networks

Approved by:

Professor Paul Hasler, Advisor

Professor David Anderson

Professor Mark Clements

Professor Steve DeWeerth

Professor Dieter Jaeger (Emory University)

Date Approved <u>24 November 2003</u>

To my father, Don Dugger, and to my mother, Shirley Dugger.

### PREFACE

While the digital world frantically pursues ever-faster clock speeds to satisfy demanding signal processing applications, a quiet revolution in analog computing has been brewing, which promises to do more with less - more sophisticated signal processing delivered at less power in a smaller space. Novel application of a digital memory technology, the floating-gate MOS-FET (used in EEPROMs), as an analog memory and computation device provides the basic building block of this technology. Utilization of inherent device physics provides the adaptivity and programmability needed to realize compact reconfigurable analog VLSI systems. Floating-gate charge storage provides non-volatile memory for a matrix of coefficients, while the nonlinear current-voltage relation of the MOSFET provides signal-coefficient multiplication. Summation of products is achieved simply using Kirckhoffs Current Law. Matrix coefficients adapt according to a correlation learning rule which utilizes physical device phenomena (electron tunneling and hot-electron injection) to program floating-gate charge. All of this functionality costs only four transistors per coefficient, each operating at nanowatts of power consumption. The resultant adaptive analog matrix-vector operations form the core of a novel analog VLSI signal-processing model, which is called computing in memory. Peripheral circuitry determines learning behavior, controls programmability, and expands core matrix functionality.

## ACKNOWLEDGEMENTS

I wish to thank my colleagues in the Integrated Computational Electronics lab for their encouragement and support, particularly Venkatesh Srinivasan for assistance with the design and construction of the adaptive test board, as well as producing some of the simulation results in Chapter 6.

## TABLE OF CONTENTS

| DI  | EDIC        | ATIO      | N                                                                   | iii          |

|-----|-------------|-----------|---------------------------------------------------------------------|--------------|

| PF  | REFA        | <b>CE</b> |                                                                     | iv           |

| AC  | CKN         | OWLE      | DGEMENTS                                                            | $\mathbf{v}$ |

| LI  | <b>ST O</b> | F TAI     | BLES                                                                | ix           |

| LIS | ST О        | F FIG     | URES                                                                | x            |

|     |             |           |                                                                     | xix          |

|     |             |           |                                                                     |              |

| Ι   |             |           | UCTION TO ADAPTIVE ELECTRONIC SYSTEMS                               | 1            |

|     | 1.1         | Basic     | Neural Network Theory                                               | 2            |

|     |             | 1.1.1     | Feedforward Computation                                             | 3            |

|     |             | 1.1.2     | Adaptation                                                          | 8            |

|     | 1.2         | VLSI      | Implementations of Neural Networks                                  | 9            |

|     |             | 1.2.1     | Neuron Design                                                       | 10           |

|     |             | 1.2.2     | Synapse Design                                                      | 11           |

|     |             | 1.2.3     | Analog vs. Digital Circuits                                         | 13           |

|     |             | 1.2.4     | Memories for VLSI Neural Networks                                   | 14           |

|     |             | 1.2.5     | Floating-Gate Technology for VLSI Neural Memories                   | 15           |

| II  | FL(         | DATIN     | IG-GATE SYNAPSE FUNDAMENTALS                                        | 17           |

|     | 2.1         | Floati    | ing-Gate Transistor Basics                                          | 18           |

|     | 2.2         | Charg     | ge Adaptation through Electron Tunneling and Hot-Electron Injection | 20           |

|     |             | 2.2.1     | Electron Tunneling                                                  | 20           |

|     |             | 2.2.2     | Hot-Electron Injection                                              | 22           |

|     | 2.3         | Invest    | igating Signal-Adaptive Behavior in Floating-Gate Circuits          | 23           |

|     |             | 2.3.1     | Separation of Timescales                                            | 24           |

|     |             | 2.3.2     | Fast-Timescale Behavior                                             | 25           |

|     |             | 2.3.3     | Slow Timescale Behavior                                             | 26           |

|     |             | 2.3.4     | The Autozeroing Floating-Gate Amplifier                             | 28           |

|     |             | 2.3.5     | Source-Degenerated pFET Devices: Modeling and Behavior              | 30           |

|     | 2.4         | Concl     | uding Comments                                                      | 35           |

| III           | TH  | E FLO             | ATING-GATE PFET CORRELATION LEARNING RULE                               | 36       |

|---------------|-----|-------------------|-------------------------------------------------------------------------|----------|

|               | 3.1 | Weigh             | t Update for the Continuously Adapting pFET Synapse                     | 36       |

|               | 3.2 | Effects           | s of Drain Voltage on the Equilibrium Weight                            | 37       |

|               | 3.3 | Effects           | s of Gate Voltage on the Equilibrium Weight                             | 39       |

|               | 3.4 | Equilil<br>Voltag | orium Weight is Determined by Correlations Between Gate and Drain<br>es | 41       |

|               | 3.5 | Hebbia            | an Learning Rule from Approximated Weight Dynamics                      | 43       |

|               | 3.6 | Conclu            | Iding Comments                                                          | 44       |

| IV            | FRO | OM FL             | OATING-GATE SYNAPSES TO FLOATING-GATE NODES                             | 46       |

|               | 4.1 | A Sim             | ple Two-Input Floating-Gate Node                                        | 47       |

|               |     | 4.1.1             | Simple Floating-Gate Learning Node Experiments                          | 50       |

|               |     | 4.1.2             | Learning a Square Wave from Sinusoidal Inputs                           | 51       |

|               | 4.2 | Remov             | val of Non-Ideal Effects in the Correlation Learning Rule               | 53       |

|               |     | 4.2.1             | Harmonic Distortion, Gate Variance, and Gate Pre-Distortion $\ . \ .$   | 54       |

|               |     | 4.2.2             | Drain Variance Effects, Drain Pre-Distortion, and Signal Correlations   | 57       |

|               |     | 4.2.3             | Cancelling Constant Offset and Gate Variance in the Weight              | 59       |

|               | 4.3 | Conclu            | Iding Comments                                                          | 61       |

| $\mathbf{V}$  |     |                   | L LEAST-MEAN-SQUARES LEARNING IN FLOATING-GA                            | TE<br>62 |

|               | 5.1 | Issue o           | of Weight Decay for Physical LMS computation structures                 | 62       |

|               | 5.2 | The L             | MS Floating-Gate Synapse Circuit                                        | 66       |

|               |     | 5.2.1             | Feedforward Synapse Computation                                         | 67       |

|               |     | 5.2.2             | Weight Adaptation and the Floating-Gate Correlation Learning Rule       | 70       |

|               |     | 5.2.3             | Amplitude Correlation Experiments                                       | 73       |

|               | 5.3 | The L             | east-Mean-Square (LMS) Learning Rule                                    | 76       |

|               | 5.4 | The T             | wo-Input Adaptive Node                                                  | 77       |

|               | 5.5 | Conclu            | Iding Comments                                                          | 81       |

| $\mathbf{VI}$ | FRO | OM SI             | MPLE NODES TO ADAPTIVE NETWORKS                                         | 82       |

|               | 6.1 | The n-            | Input Node                                                              | 82       |

|               | 6.2 | A Mul             | tiple-Input/Multiple-Node Adaptive Floating-Gate Integrated Circuit     | 84       |

|               |     | 6.2.1             | Hardware Test and Development System                                    | 85       |

| 6.3    | All-Transistor Synapse Circuit Model and Simulation | 87 |

|--------|-----------------------------------------------------|----|

| 6.4    | Fourier Series Example                              | 92 |

| 6.5    | Example Application: Adaptive Channel Equalization  | 93 |

| 6.6    | Concluding Comments                                 | 95 |

| VII CO | NCLUSIONS                                           | 96 |

| APPEN  | DIX A — OJA'S RULE DERIVATION                       | 98 |

## LIST OF TABLES

| Table 1 | Tunneling parameter, $V_x$ , versus IC fabrication process | 22 |

|---------|------------------------------------------------------------|----|

| Table 2 | Definition of constants in equations $(26)$ and $(30)$     | 32 |

## LIST OF FIGURES

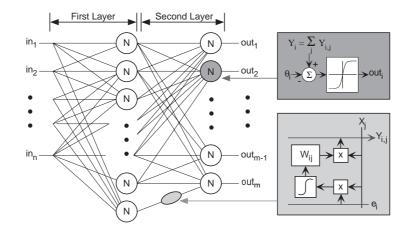

| Figure 1 | Classic picture of a two-layer neural network from the perspective of im-<br>plementating these networks in hardware. The neural networks are lay-<br>ers of simple processors, called neurons, interconnected through weighting<br>elements, called synapses. The neurons aggregate the incoming inputs<br>(including a threshold or offset) and are applied through a $tanh(\cdot)$ non-<br>linearity. The synapse elements, which in general are far more numerous<br>than neuron elements, must multiply the incoming signal by an internally<br>stored value, called the weight, and must adapt this weight based upon a<br>particular learning rule. Learning rules implemented in silicon are typically<br>functions of correlations of signals passing through each synapse processor.                                                                                                                                   | 2 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

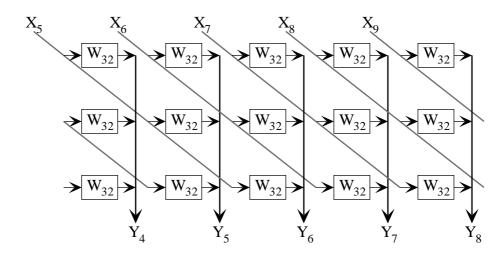

| Figure 2 | Typical architectures for neural network implementations. Although the routing looks complicated in Fig. 1, it can be easily implemented in a mesh architecture. Diagram of the Classic Mesh Architecture, typically used for fully-connected systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3 |

| Figure 3 | Typical architectures for neural network implementations. Although the routing looks complicated in Fig. 1, it can be easily implemented in a mesh architecture. Diagram of a Mesh processor architecture optimized for nearest-neighbor computations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4 |

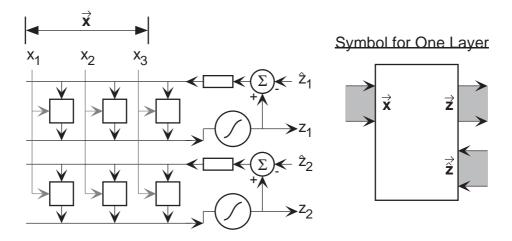

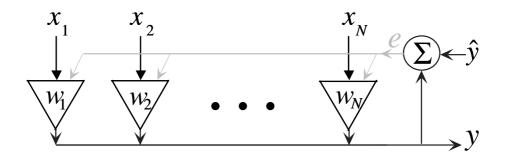

| Figure 4 | Learning in a single layer. We can build either supervised algorithms (LMS is explicitly shown) or unsupervised one-layer networks in this architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 |

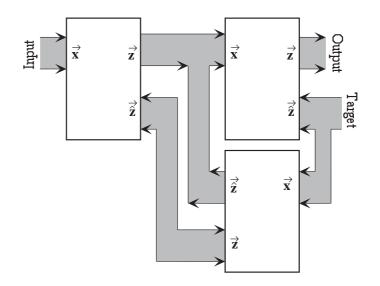

| Figure 5 | Building a multilayer architecture from one-layer mesh structures. Mul-<br>tiple layers can be directly combined to form multilayer neural networks;<br>each layer will rotate 90 degrees from the previous layer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6 |

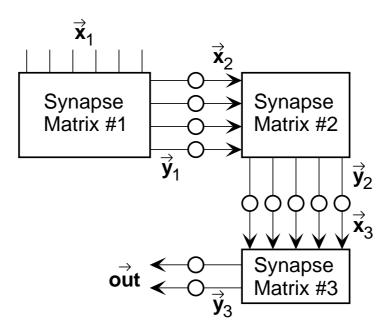

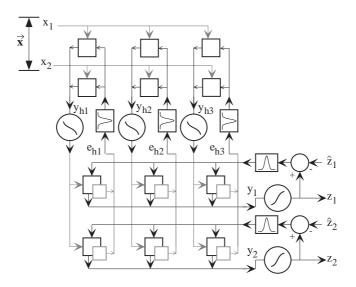

| Figure 6 | Possible architectures for adaptive multilayer neural networks. Implemen-<br>tation for Backpropagation networks. There are many forms and modifi-<br>cations, but from an implementation viewpoint, these approaches can be<br>modified towards this architecture. This approach significantly increases<br>synapse size, because one typically requires the complexity of two synapses<br>for weight feedback. Further, this approach limits some circuit approaches<br>to building dense synapses. The output from the hidden layer, or layer 1,<br>is $\mathbf{y}_h$ and the error signal given to the hidden layer is $\mathbf{e}_h$ . The synapses in<br>the second layer must also output a current proportional to the product of<br>the error and the stored weight; the sum of these currents along a column<br>is the error for the next layer. As a result, the synapses on the second layer<br>must be more complex | 7 |

| Figure 7  | Possible architectures for adaptive multilayer neural networks. Implemen-<br>tation using Helmholtz machine concepts. This approach requires twice as<br>many synapses for all but the first layer, which yields the same complexity<br>as the Backpropagation approaches. This approach will converge to the<br>same steady states, only requires a modular tiling of single layer networks,<br>and its reciprocal feedback has a similar feel to communication between<br>layers of cortical neurons.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

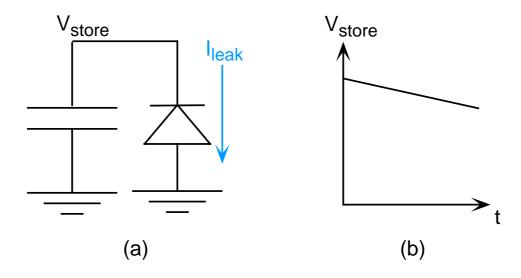

| Figure 8  | Dynamic storage of analog values on capacitors. (a) Circuit schematic illustrating voltage storage on a capacitor and leakage current through a pn junction. (b) Plot of the stored voltage versus time. The voltage decreases linearly over time since the leakage current is constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14 |

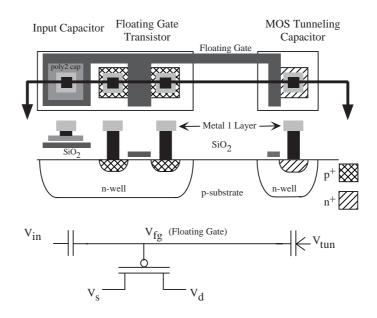

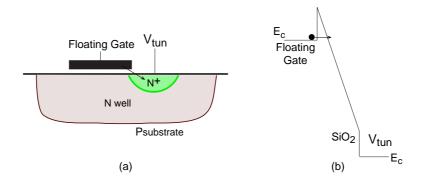

| Figure 9  | Layout, cross section, and circuit diagram of the floating-gate pFET in a standard double-poly <i>n</i> well MOSIS process. The cross section corresponds to the horizonatal line slicing through the layout (or top) view. The pFET transistor is the standard pFET transistor in the nwell process. The gate input capacitively couples to the floating-gate by either a poly-poly capacitor, a diffused linear capacitor, or a MOS capacitor, as seen in the circuit diagram (not explicitly shown in the other two figures). We add floating-gate charge by electron tunneling, and we remove floating-gate charge by hot-electron injection. The tunneling junction used by the single-transistor synapse is a region of gate oxide between the polysilicon floating-gate and <i>n</i> well (a MOS capacitor). Between $V_{tun}$ and the floating-gate is our symbol for a tunneling junction, a capacitor with an added arrow designating the charge flow. | 18 |

| Figure 10 | The tunneling junction is the capacitor between the floating gate and the $n$ well (a MOScap); we use high-quality gate oxide to reduce the effects of electron trapping. Over a wide range of oxide voltage, most of the tunneling occurs between the floating gate and $n^+$ diffusion region because this region is accumulated and the higher electric fields at the corner of the floating gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20 |

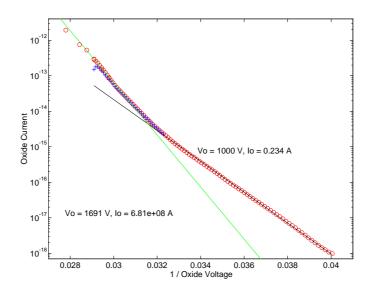

| Figure 11 | Electron tunneling current versus $1/\text{oxide voltage in a } 2.0\mu\text{m}$ process with 42nm gate oxide. The two straight line fits are to the classic Fowler-Nordheim expression in (6). The two different straight-line regions might be due to tunneling through intermediate traps, or due to initially tunneling through the junction edge for low oxide voltages and tunneling through the middle of the junction for high oxide voltages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21 |

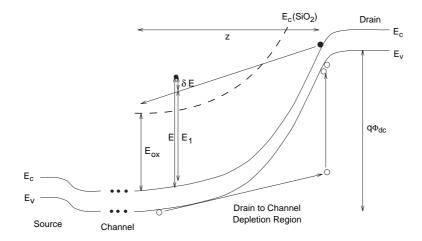

| Figure 12 | Band diagram of a subthreshold $p$ FET transistor under conditions favor-<br>able for hot-electron injection. $E_{ox}$ is the Si–SiO <sub>2</sub> barrier, which is 3.1eV<br>for no field across the oxide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23 |

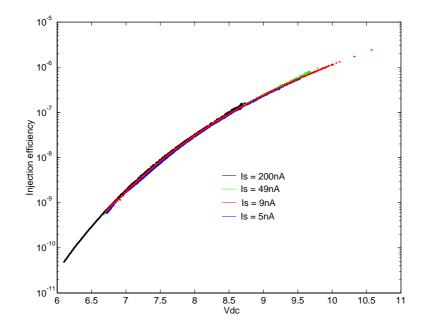

| Figure 13 | pFET hot-electron injection. Measured data of pFET injection efficiency<br>versus the drain-to-channel voltage for four source currents. Injection ef-<br>ficiency is the ratio of injection current to source current. The injection<br>efficiencies are nearly identical for the different source currents; therefore,<br>they appear to be indistinguishable on the plot. At $\Phi_{dc}$ equal to 8.2V,<br>the injection efficiency increases by a factor of $e$ for an increase in $\Phi_{dc}$ of<br>250mV.                      | 24 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 14 | The autozeroing floating-gate amplifier (AFGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27 |

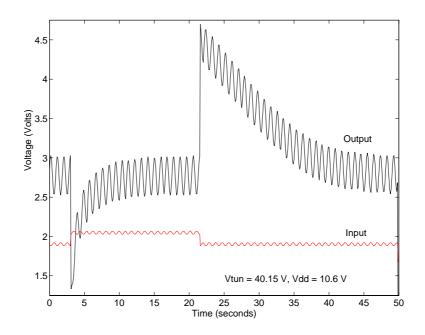

| Figure 15 | Response of the AFGA to a 1Hz sinewave superimposed on a 19s voltage pulse. The AFGA has a closed-loop gain of 11.2, and a low-frequency cutoff at 100 mHz. We see that the signal is amplified, but the much slower step is adapted away.                                                                                                                                                                                                                                                                                           | 29 |

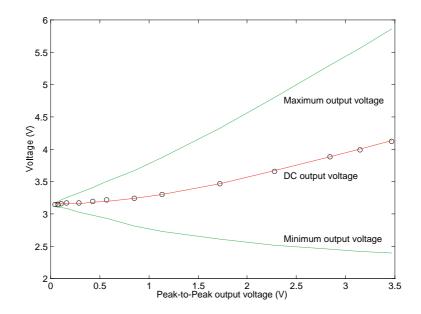

| Figure 16 | Minimum and maximum output voltages versus the peak-to-peak output-<br>voltage amplitude. The frequency of the input sine wave was 100Hz; the<br>AFGA had a gain of 146. For small input amplitudes, the minimum and<br>maximum output voltages symmetrically deviate from the steady-state<br>voltage; for large input amplitudes, however, the DC output voltage fol-<br>lows the maximum output voltage. The DC voltage was fit to the function<br>$0.5 \ln(I_0(V_{dc} / 1.0V))$ , which is equal to (25) with $V_{inj} = 500$ mV | 31 |

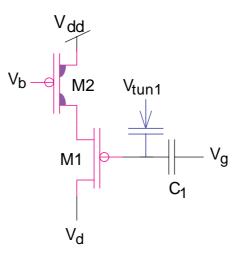

| Figure 17 | The source-degenerated (s-d) pFET synapse. The s-d pFET modifies the basic pFET dynamics by local negative-feedback; the device converges to a stable equilibrium for either a constant current or voltage. Circuit diagram of the s-d pFET synapse. The s-d pFET synapse is comprised of a floating-gate pFET synapse and a second ultra -short pFET, which provides feedback to the source terminal. We utilize the DIBL effect in short-channel MOSFETs to build a compact weakly exponential element.                            | 33 |

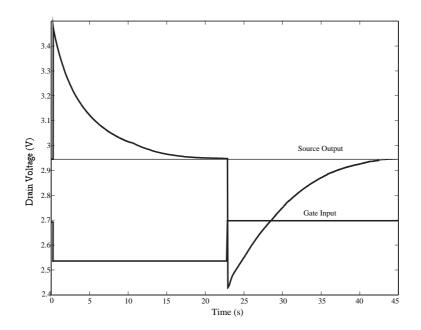

| Figure 18 | The behavior of the current autozeroing circuit using a source-degenerated pFET synapse. Unlike the pFET synapse, this circuit converges to its steady-state current. We use this data to measure weight changes versus time. The tunneling voltage was held at a constant value throughout this experiment; there was non-negligible tunneling and injection current throughout this experiment.                                                                                                                                    | 34 |

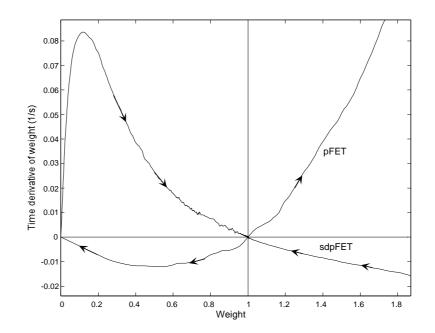

| Figure 19 | Plot of the time-derivative of w versus w for the pFET, and source-degenerated pFET synapses. The arrows show the direction that the differential equation will take. This data shows that the pFET synapse will diverge from the $w = 1$ steady state, but that source-degenerated synapses will stabilize to the $w = 1$ steady state. The s-d pFET modifies the basic pFET dynamics by local negative-feedback. We use zero $\Delta \hat{V}_g$ and zero $\Delta \hat{V}_g$ .                                                      | 35 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

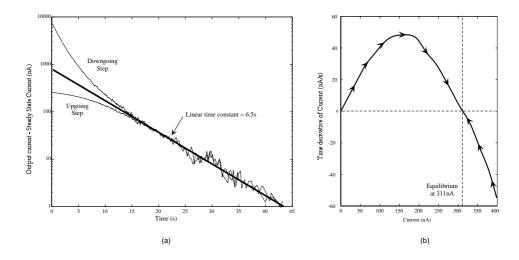

| Figure 20 | Experimental measurements of floating-gate dynamics from a $0.5\mu$ gate-<br>length process. The gate input is a step decrease in voltage followed later<br>by a step increase in voltage. We used a power supply voltage, $V_{dd} =$<br>$5.60V$ , and tunneling voltage, $V_{tun} = 15.65V$ , to set the operating point<br>for these experiments, as well as the other measurements in this paper. (a)<br>Convergence of the output current of a single synapse back to equilibrium<br>after the step perturbations. The response is nonlinear with asymmetries<br>between tunneling and injection. These nonlinear asymmetries are what<br>allow us to compute correlations. b Time derivative of the weight $(\dot{w})$ vs.<br>weight value $(w)$ . We graphically see that weight value converges toward<br>its equilibrium level. | 37 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

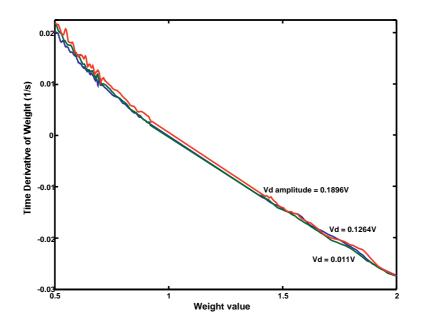

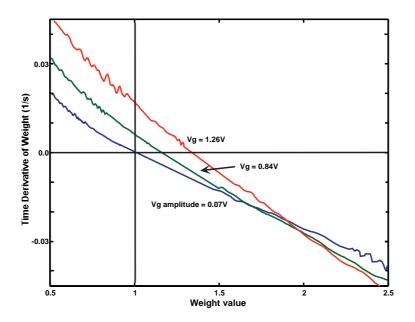

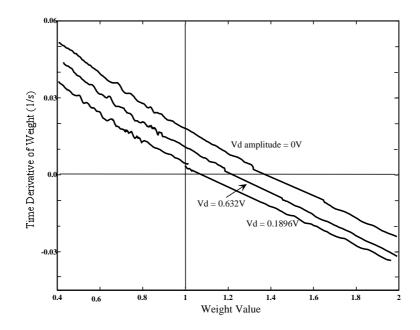

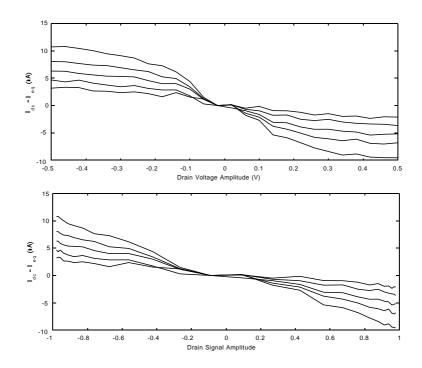

| Figure 21 | Change in the dynamical weight equation due to sinusoidal signal ampli-<br>tudes at only the drain terminal. The gate terminal is remaining at a<br>fixed voltage through this experiment. $\frac{dw}{dt}$ versus w for three drain input<br>amplitudes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38 |

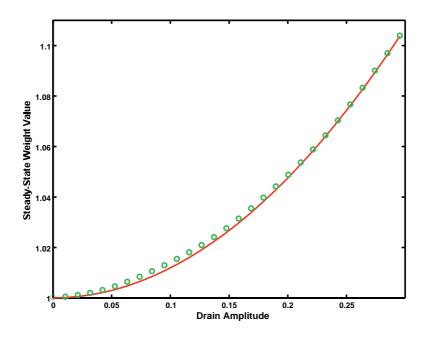

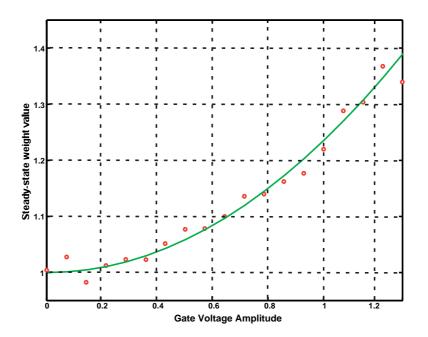

| Figure 22 | Change in the dynamical weight equation due to sinusoidal signal ampli-<br>tudes at only the drain terminal. The gate terminal is remaining at a fixed<br>voltage through this experiment. Equilibrium w $(w_{eq})$ versus drain input<br>amplitude                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39 |

| Figure 23 | Change in the dynamical weight equation due to sinusoidal signal amplitudes at only the gate terminal. The drain voltage is remaining at a fixed voltage through this experiment. $\frac{dw}{dt}$ versus w for three gate input amplitudes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40 |

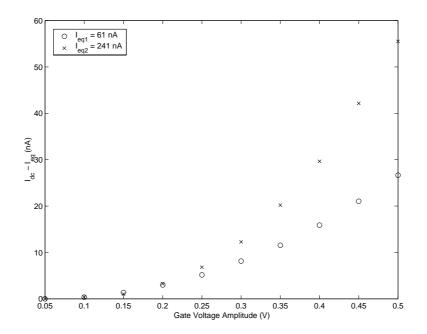

| Figure 24 | Change in the dynamical weight equation due to sinusoidal signal ampli-<br>tudes at only the gate terminal. The drain voltage is remaining at a fixed<br>voltage through this experiment. Equilibrium weight $(w_{eq})$ versus gate<br>input amplitude.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41 |

| Figure 25 | $dw/dt$ vs. $w$ for varying $\Delta V_d$ and fixed $\Delta V_g$ . This data gives strong evidence for our learning rule, $\tau' \frac{dw}{dt} = -w + \eta E[xy]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42 |

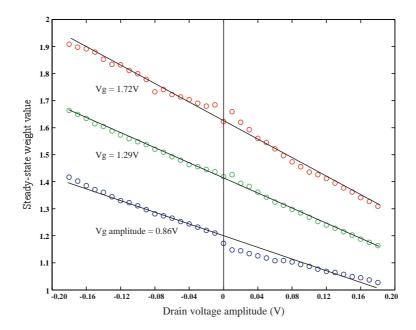

| Figure 26 | Change in the dynamical weight equation due to correlated sinusoidal sig-<br>nal amplitudes between the gate and drain terminals. Change in the dy-<br>namical weight equation due to different size drain amplitudes for three<br>different gate amplitudes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43 |

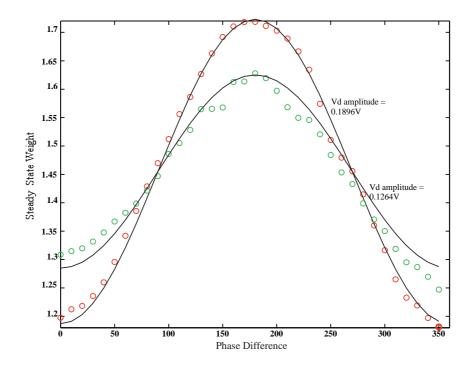

| Figure 27 | Change in the dynamical weight equation due to correlated sinusoidal sig-<br>nal amplitudes between the gate and drain terminals. Change in the dy-<br>namical weight equation due to various degrees of correlation (phase dif-<br>ference) between sinusoidal input signals at the gate and drain terminals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44 |

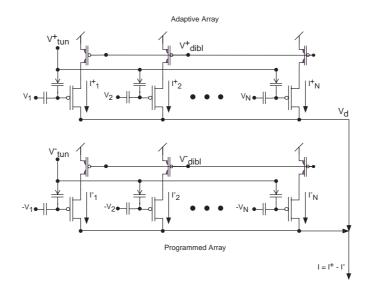

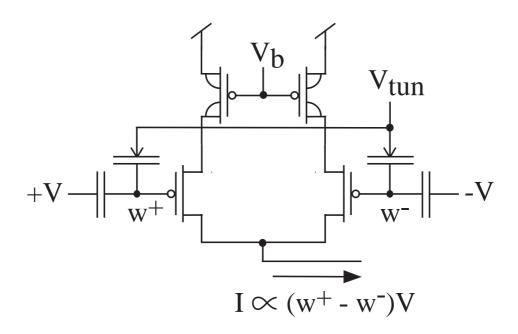

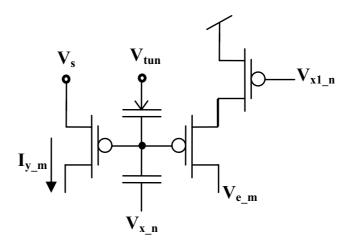

- Figure 28 The differential synapse array enables four quadrant multiplication of weights with inputs. Each floating-gate transistor behaves as a transistor amplifier with an adaptive gain. Adaption occurs through slow-timescale dynamics due to the tunneling and injection process at the floating-gates. We continuously adapt the synapses with the positive signals, and we program the synapses with negative signals to balance the steady-state current of the positive synapse. The network output is the total drain current, and the *learning* signal is the applied drain voltage. By applying the appropriate relationship between output drain current and the resulting drain voltage, we could get a variety of learning rules. Since pFET hot-electron injection is unstable when channel current is the free parameter, we stabilize each synapse element by incorporating DIBL transistors to provide source-degenerative feedback.

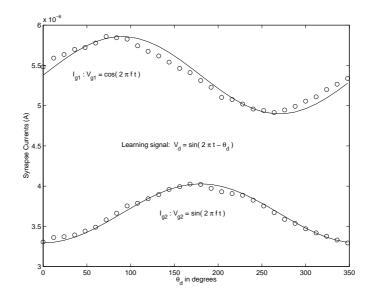

- Figure 29 Experimental measurements of positive synapse current phase correlations. We would program the negative synapses to currents of  $5.5\mu A~(w_1^-)$  and  $3.5\mu A~(w_2^-)$ , and therefore both weights are either positive or negative. These results show correlations between a specific gate and global drain terminal direct the convergence of that synapse's weight.

47

48

49

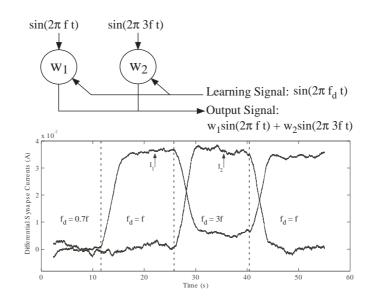

- Figure 30 Experimental measurements of frequency correlations for sinusoidal inputs to the two-input node given by  $V_{g1} = sin(2\pi 3ft)$  and  $V_{g2} = sin(2\pi ft)$ . The learning signal,  $V_d = sin(2\pi f_d t)$ , takes on three different frequencies  $f_d = 0.7f, f, 3f$ . Current outputs from our differential synapses. We programmed our negative weights to offset the positive synapse current measured with input signals with the same signal variance. We see that the synapse that has an identical synapse input frequency as the drain signal has a non-zero weight.

- Figure 31 Experimental measurements of a square wave learning signal applied to  $V_d$ Time course of steady-state currents showing convergence of weights. . . 50

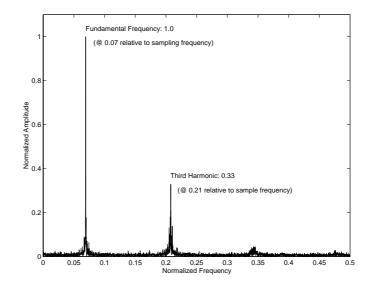

- Figure 32 Experimental measurements of a square wave learning signal applied to  $V_d$ Spectrum of output current shows amount of each node input frequency matched to frequency components in learning signal. The frequency axis is normalized; the frequency does not affect these results until it approaches the adaptation rate. We obtain 1 and 1/3 for the fundamental and third harmonics as expected. The fifth harmonic appears due to the drain voltage coupling into the floating gate through overlap capacitance. . . . . . 51

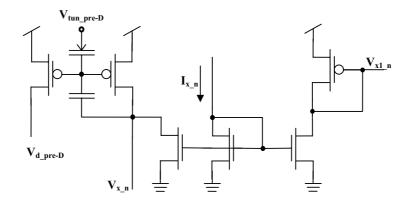

- Figure 33 The pre-distort circuit is a simple current mirror which implements  $\Delta V_g = V_{mq} \ln(1+x)$  to eliminate harmonic distortion in the output current. . . 52

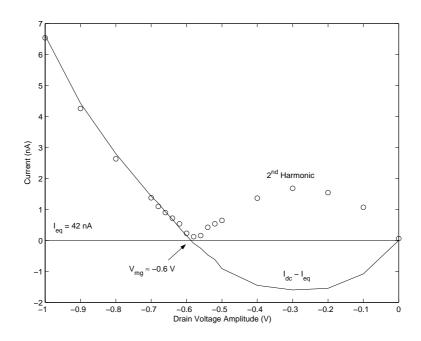

| Figure 35 | This plot shows the DC value (subtracting the equilibrium current) and $2^{nd}$ harmonic of the drain current vs. gate voltage pre-distort value. The gate pre-distortion is given by $\Delta V_g = V_{mg} \ln(1 + A \sin \omega t)$ for $\Delta V_d = 0$ . We find that the appropriate pre-distort factor ( $V_{mg} \approx -0.6V$ )to be that which makes the $2^{nd}$ harmonic to be zero and coincides with the non-zero root of $I_{dc} - I_{eq}$ . $I_{eq}$ is the value the drain current assumes when there is no signal input.                                                                                                                                             | 54 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

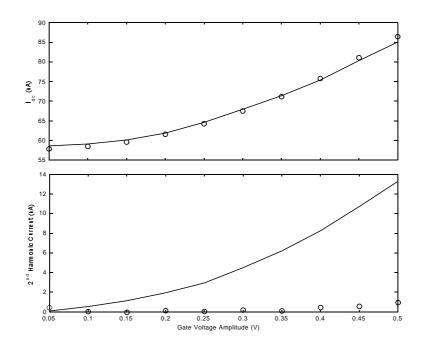

| Figure 36 | These plots compare the dc values and second-harmonic values of the drain<br>current vs. gate voltage amplitude both with and without pre-distortion.<br>We see that the dc value follows a similar quadratic form in both cases,<br>implying that there is still significant gate variance with pre-distortion for<br>a given pre-distort value. The second-harmonic plot shows that harmonic<br>distortion has been significantly reduced.                                                                                                                                                                                                                                         | 55 |

| Figure 37 | A plot of DC value of the drain current (weight) vs. drain voltage ampli-<br>tude for a pre-distorted sinusoid applied to the gate and a non-distorted<br>sinusoid applied to the drain. The gate variance contributes to constant<br>offsets in the data. The quadratic drain variance term masks the linear<br>correlation term.                                                                                                                                                                                                                                                                                                                                                   | 56 |

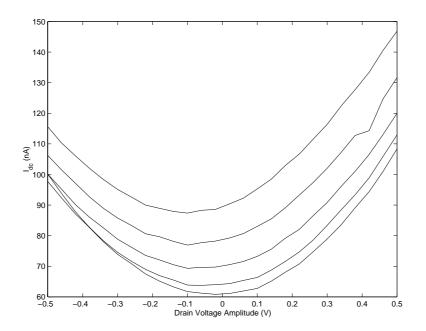

| Figure 38 | This plot shows the DC value of the drain current vs. drain voltage amplitude when $\Delta V_d = V_{md} \ln(1 + A \sin \omega t)$ with $\Delta V_g = 0$ . Here we have plots for several values of $V_{md}$ . We choose that value of $V_{md} = -0.22V$ (corresponding to the flattest curve) as the appropriate distortion factor to eliminate drain variance effects from the weight value.                                                                                                                                                                                                                                                                                        | 57 |

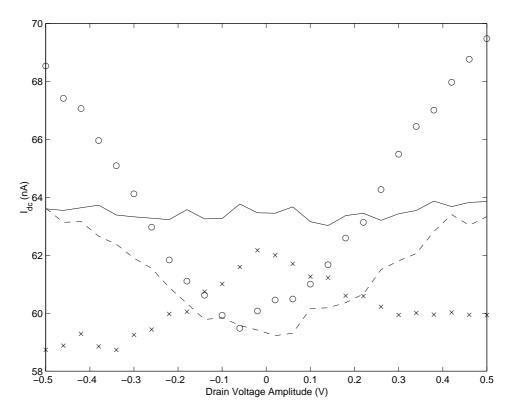

| Figure 39 | The top figure is a plot of the dc current (weight) minus the equilibrium current value and those current offsets due to gate variance vs. the amplitude of the drain voltage. We see that the quadratic effect due to drain variance has been eliminated. The curves presented have a $tanh$ form due to the relationship between the signal amplitude and drain voltage amplitude because of pre-distortion. The bottom figure shows the same data plotted vs. signal amplitude revealing linear correlations. Steeper slopes correspond to larger gate voltages. Thus, we see that $w \propto -E[xy]$ , where $x$ and $y$ are sinusoidal signals to be pre-distorted, is verified | 58 |

| Figure 40 | In the ideal situation of no mismatch, an adapting differential pair of floating-gate devices would cancel both the gate-variance and constant terms out of the correlation learning rule.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59 |

| Figure 41 | Plot of dc current values (weights) minus equilibrium values for two dif-<br>ferent source-degenerated floating-gate pFETs vs. gate voltage amplitude.<br>Tunneling junction mismatch leads to significant differences in the gate-<br>variance terms in the correlation learning rule. The legend demonstrates<br>the large variation of equilibrium current values also due to mismatch.                                                                                                                                                                                                                                                                                           | 60 |

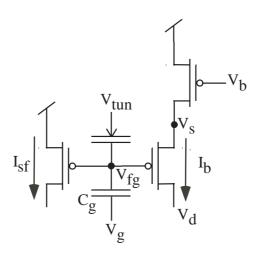

| Figure 42 | The Source-Follower Floating-Gate (SFFG) synapse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63 |

| Figure 43 | Block diagram of a single adaptive floating-gate node. Because the synapse elements far outnumber all of the other components, each synapse element must be as small as possible. Filters extract the output signal $(y)$ from its slow-timescale and DC bias currents. Program circuitry on the periphery allows us to set the initial conditions and / or to restart the weights in a known state when experimenting with various algorithms.                                                                                                                                                                               | 64 |

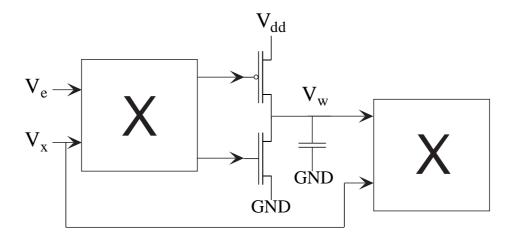

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

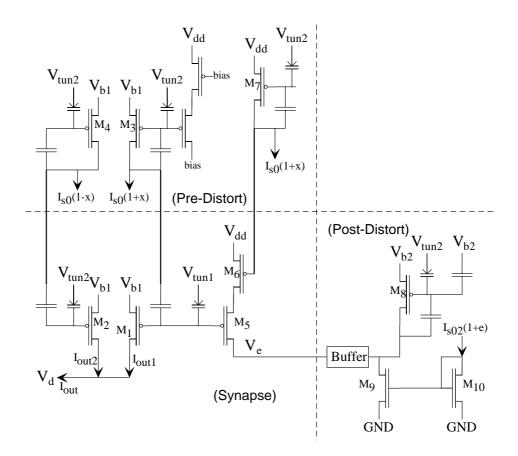

| Figure 44 | Basic block diagram for a weight update using transistors for the weight<br>update element. The result is either non-negligible weight decay or a dif-<br>ficult analytical system to control. Therefore in practice, we would design<br>our weight decay to be small enough for our algorithm but large enough<br>to achieve the desired level of stability.                                                                                                                                                                                                                                                                 | 65 |

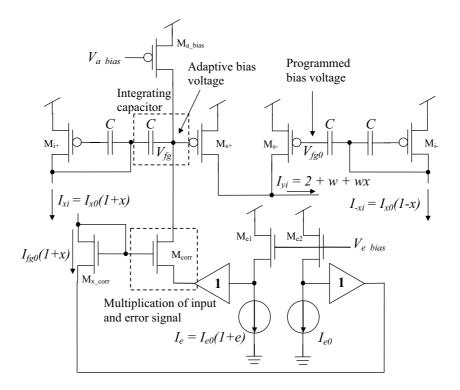

| Figure 45 | Building a node from a correlating synapse element. Full circuit with re-<br>quired peripheral interface circuitry. Interface circuitry linearizes synapse<br>computation and adaptation. The figure also shows programming circuitry<br>needed to set all of the floating-gate elements. $V_{tun1}$ is the tunneling line<br>for the adaptive and programmed floating-gate elements, where $V_{tun2}$ is<br>the tunneling line for the program only floating-gate elements                                                                                                                                                   | 67 |

| Figure 46 | 10.9513.6=1111The bandwidth of the pre-distort input current mirror lim-<br>its the speed of the feedforward computation. Bandwith depends on the<br>bias current, , and the total capacitance seen at the node, . One pre-distort<br>mirror feeds the input current to each column of the adaptive matrix, driv-<br>ing the capacitance on m-rows of the matrix.                                                                                                                                                                                                                                                             | 69 |

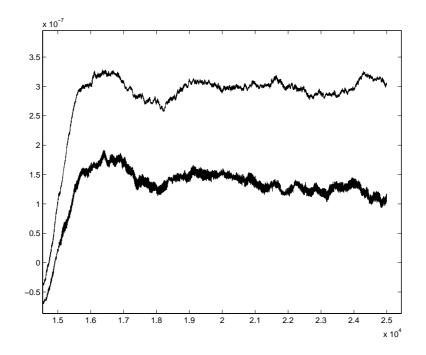

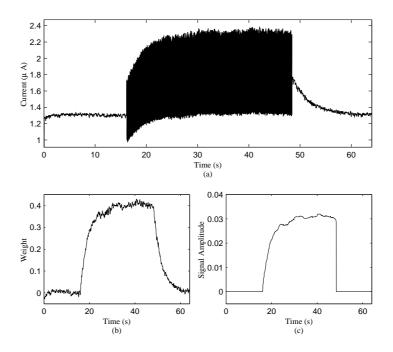

| Figure 47 | Amplitude correlation results for sinusoids of same frequency and phase<br>with input and error signal amplitudes of 0.3. (a) Synapse output current<br>vs. time. Sinusoidal signals are turned on at 16 seconds and turned off at<br>48 seconds. (b) Extracted dimensionless weight value vs. time, showing<br>convergence to steady-state due to correlations affected by weight decay<br>(c) Extracted dimensionless signal amplitude vs. time, which follows a<br>path similar to the weight, increasing from zero to a steady-state value.<br>Without an input signal, the output is zero due to multiplicative effects. | 73 |

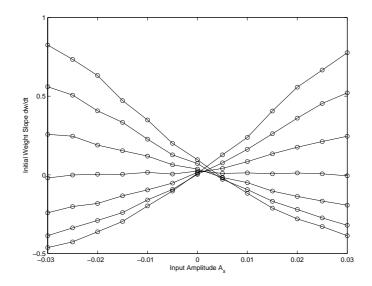

| Figure 48 | Basic correlating floating-gate synapse measurements for an individual iso-<br>lated synapse element. We measured the initial slope from this synapse<br>for multiple input (sinewave) amplitudes near the zero-input steady-state<br>condition. This initial slope shows the correlation function used by this<br>LMS synapse; steady-state solution has less meaning for an LMS synapse<br>with small weight decay.                                                                                                                                                                                                         | 74 |

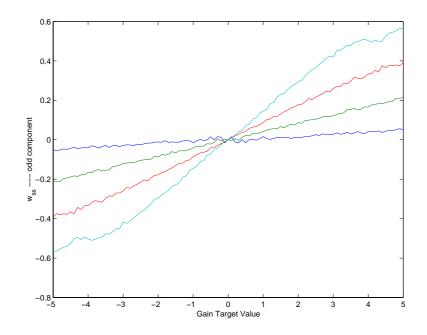

| Figure 49 | Results for a single-weight LMS experiment. The input signal is a sinusoid of fixed amplitude; the target signal has frequency and phase identical to the input, but varying amplitude. Steady-state weight values for the single-weight LMS experiment are plotted versus target signal amplitude. The steady-state weight value is a linear function of the target signal amplitude. We have plotted the results for several gain levels.                                                                                                                                                                                   | 75 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

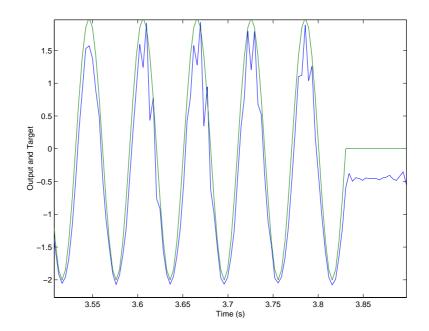

| Figure 50 | Results for a single-weight LMS experiment. The input signal is a sinusoid of fixed amplitude; the target signal has frequency and phase identical to the input, but varying amplitude. Transient solution for a given target signal amplitude of the single-weight LMS experiment shows the output signal for this trial tracking the target signal.                                                                                                                                                                                                                                                                                                                                                                                               | 76 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

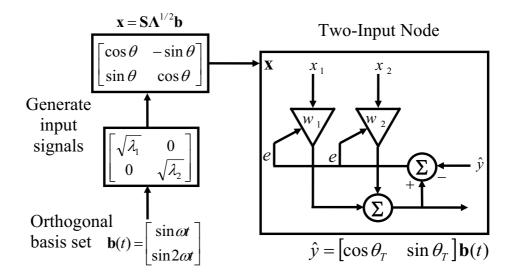

| Figure 51 | Experimental setup for examining Least-Mean-Squares behavior in a two-<br>input node. A scaling operation followed by application of a rotation ma-<br>trix to an orthogonal signal-space basis of harmonically related sinusoids<br>yields the system input signals; the fundamental sinusoid is chosen as the<br>target. The experiment runs for different values of $\theta$ , uniformly sampled<br>from a circle.                                                                                                                                                                                                                                                                                                                               | 77 |

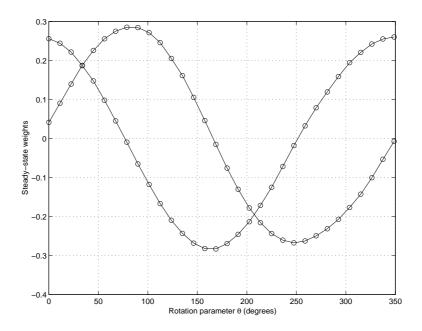

| Figure 52 | Two-input Least-Mean-Squares experimental results for the source-follower<br>floating-gate synapse circuit. Measured data for the case $\theta_T = 0$ and<br>$\lambda_1 = \lambda_2$ show steady-state weight dependence on the parameter, $\theta$ , of the<br>two-dimensional input mixing-matrix. As expected from equation (84),<br>we get a cosine curve for the first weight, and a sine curve for the second<br>weight.                                                                                                                                                                                                                                                                                                                      | 78 |

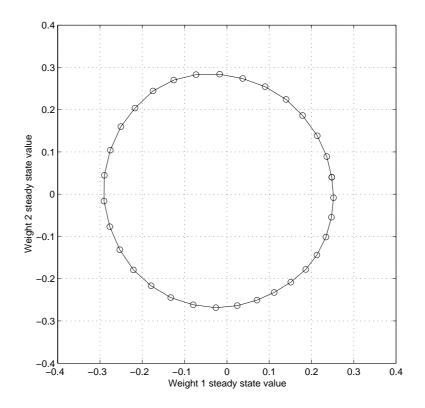

| Figure 53 | Two-input Least-Mean-Squares experimental results for the source-follower floating-gate synapse circuit. Measured data for the same case is plotted as one steady-state weight versus the other. An ideal LMS rule would produce a circle similar to our circuit results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79 |

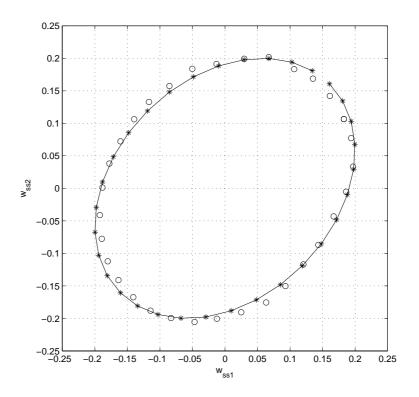

| Figure 54 | Two-input Least-Mean-Squares experimental results for the source-follower<br>floating-gate synapse circuit. Illustration of measured data compared with<br>model results computed from equation (83) assuming non-zero constant<br>weight decay for the case where $\lambda_1 = 1$ , $\lambda_2 = 2$ , and $\theta_T = \pi/3$ . The gain of<br>the filter and the amplitude of the input signals determine the scale of the<br>ellipse. The open circles show steady-state values measured from the actual<br>circuit. The asterisks and the corresponding fit-line illustrate computed<br>model results. We observe good agreement between the measured data<br>and the computed values. As predicted in the text, the results form an<br>ellipse. | 81 |

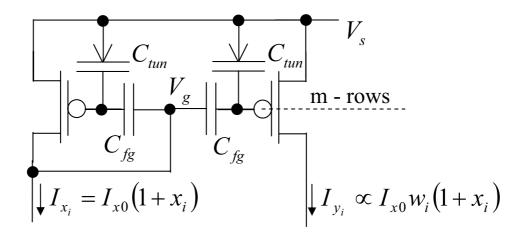

| Figure 55 | The source-follower floating-gate synapse (SFFG) that was introduced in the preceding chapter. The chip described in the text contains an array of 4 rows and 16 columns of this circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83 |

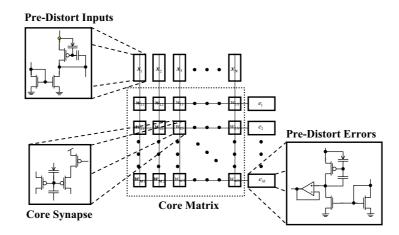

| Figure 56 | Functional diagram of the SFFG array chip described in this chapter. The chip, fabricated through MOSIS in a $0.5\mu m$ process, contains an array with 16 column inputs and 4 row outputs. Additional circuitry around the periphery allows for programming the array as desired. The pre- and post-distort circuitry particular to this design and the SFFG cell appear in the accompanying figures.                                                                                                                                                                                                                                                                                                                                              | 84 |

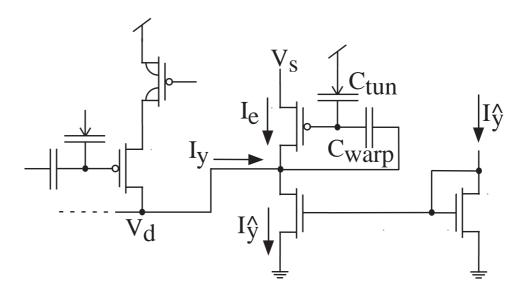

| Figure 57 | The pre-distort circuit for each column of the array includes an extra<br>floating-gate pFET for adjusting the charge on the charge on gate of the<br>pre-distort transistor. The nFET mirror provides the input signal to the<br>pre-distort circuit as well as feeds the pFET input to the source-follower<br>bias transistor in the SFFG synapse for the correlation learning rule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

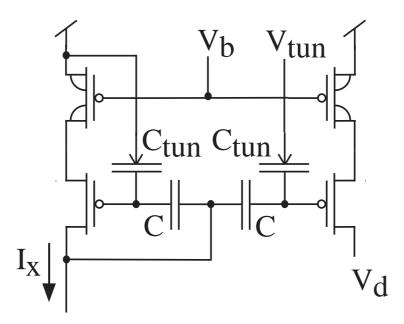

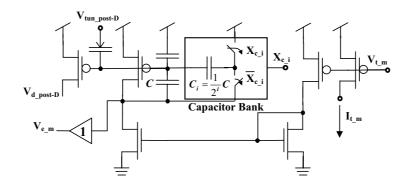

| Figure 58 | The post-distort circuit for each row of the array includes a switchable capacitor bank that allows for tuning the post-distort factor. The floating-gate pFET on the far left provides a means for setting the charge on the post-distort circuit gate node. The two pFET transistors and the nFET mirror on the right provide the error signal for the correlation learning rule.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 86 |

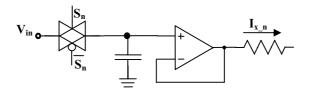

| Figure 59 | Sample-and-hold circuit formed by a capacitor and a unity-gain follower provides analog multiplexing allowing one input pin to drive sixteen synapse inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 87 |

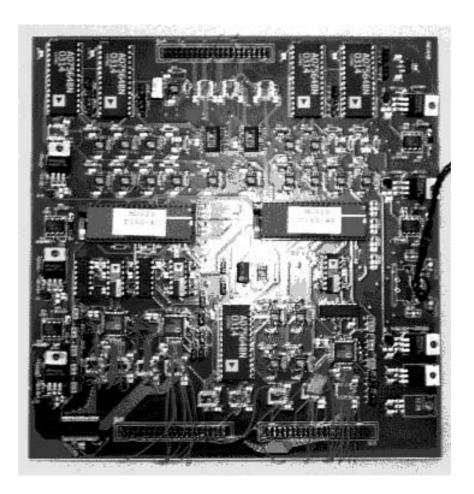

| Figure 60 | Photograph of the adaptive system test and measurment circuit board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88 |

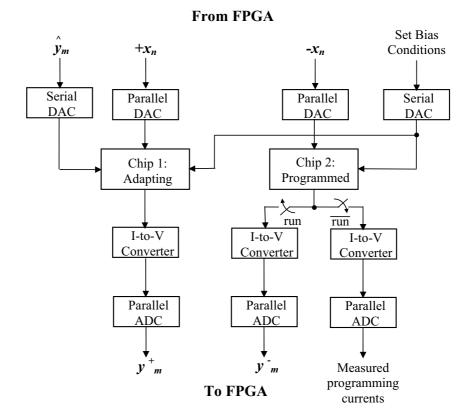

| Figure 61 | Functional diagram of the custom circuit board which appears in Fig. 60.<br>Two floating-gate synapse array chips form the heart of the test system.<br>One of the arrays has its floating-gate charge programmed to a bias point,<br>while the second array is allowed to adapt. The programmed array provides<br>a zero-point for for quadrant multiplication. The differential inputs, $+x_n$<br>and $-x_n$ are applied as a stream of time-division multiplexed samples from<br>the FPGA through the parallel DACS. The target signals for learning, $\hat{y}_m$ ,<br>are applied through through a serial DAC. The bias signals, including<br>power-supply and tunneling voltages, are also supplied from the DACs.<br>Finally, the output currents for each and programming currents are The<br>signals determining the mode of operation, $run$ and $r\bar{u}n$ are also provided<br>by the FPGA. | 89 |

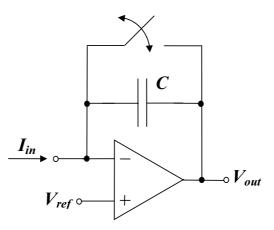

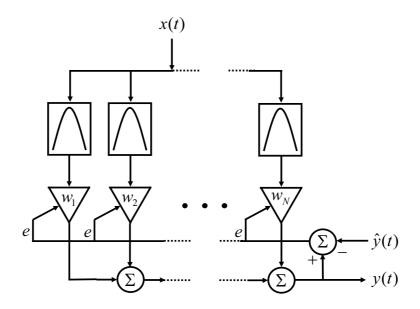

| Figure 62 | Integrator-based current-to-voltage converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90 |

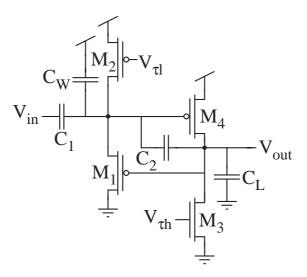

| Figure 63 | Schematic of the All-Transistor Synapse (ATS) model of the Source-Follower Floating-Gate (SFFG) synapse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 91 |

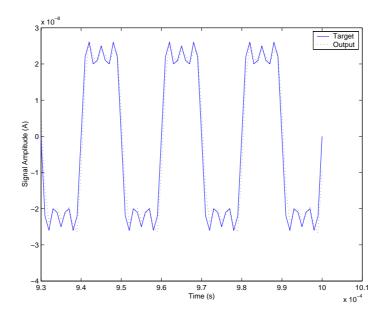

| Figure 64 | Comparison of system output and the square wave target signal for the ATS model Fourier LMS simulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 92 |

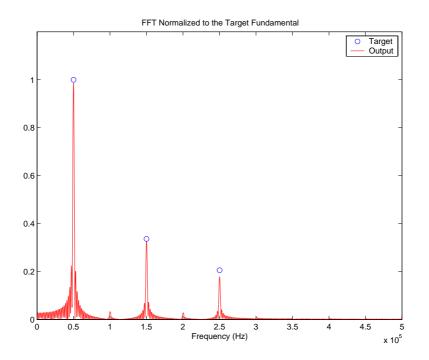

| Figure 65 | Fourier spectra comparing the learned system weights with the target sig-<br>nal square wave coefficients.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 93 |

| Figure 66 | Adaptive channel equalization filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 94 |

| Figure 67 | Circuit diagram of a capacitively coupled current conveyer (C <sup>4</sup> ). This is<br>a bandpass filter with electronically tunable corner frequencies (controlled<br>by $v_{\tau l}$ and $v_{\tau h}$ ) that can be moved independently of one another. The roll<br>offs are first-order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 95 |

### SUMMARY

Research presented in this thesis provides a substantial leap from the study of interesting device physics to fully adaptive analog networks and lays a solid foundation for future development of large-scale, compact, low-power adaptive parallel analog computation systems. The investigation described here started with observation of this potential learning capability and led to the first derivation and characterization of the floating-gate pFET correlation learning rule. Starting with two synapses sharing the same error signal, we progressed from phase correlation experiments through correlation experiments involving harmonically related sinusoids, culminating in learning the Fourier series coefficients of a square wave [13]. Extending these earlier two-input node experiments to the general case of correlated inputs required dealing with weight decay naturally exhibited by the learning rule. We introduced a source-follower floating-gate synapse as an improvement over our earlier source-degenerated floating-gate synapse in terms of relative weight decay [15]. A larger network of source-follower floating-gate synapses was fabricated and an FPGAcontrolled testboard was designed and built. This more sophisticated system provides an excellent framework for exploring applications to multi-input, multi-node adaptive filtering applications. Adaptive channel equalization provided a practical test-case illustrating the use of these adaptive systems in solving real-world problems. The same system could easily be applied to noise and echo cancellation in communication systems and system identification tasks in optimal control problems. We envision the commercialization of these adaptive analog VLSI systems as practical products within a couple of years.

### CHAPTER I

# INTRODUCTION TO ADAPTIVE ELECTRONIC SYSTEMS

Seeing, walking, and navigating an unknown environment are just a few of the sensory, motor, and cognitive abilities at which biological systems excel, but which are difficult for the best man-made computing systems. While a computer can prove theorems that tax the best human minds, a baby is superior to a digital computer in many respects. For example, a baby is better and faster at visually recognizing objects or faces than the most advanced AI algorithm running on the best supercomputer. Although the digital computer is very effective at giving precise answers to well-defined questions, the nervous system is better at interacting with the real world where sensory data is ambiguous and adaptation to the environment is required. Biological nervous systems have the advantage of being small, compact, and dissipating very little power, which is more than can be said for a supercomputer. They are also robust and fault-tolerant, degrade gracefully, and can learn to solve difficult problems on their own without specialized programming These advantages should inspire engineers to look at how biology has solved difficult sensory perception and motor control problems. Practical engineering examples of learning systems include adaptive filters which are used in cases where the desired signal processing is unknown, unknown and time-varying, or too complicated or costly to model Communication systems provide examples in adaptive channel equalization, and adaptive noise and echo cancellation. Control systems utilize adaptive filters to regulate processes where the system concerned is unknown or too costly to model. Adaptive electronics provide important tools for realizing these systems.

Figure 1: Classic picture of a two-layer neural network from the perspective of implementating these networks in hardware. The neural networks are layers of simple processors, called neurons, interconnected through weighting elements, called synapses. The neurons aggregate the incoming inputs (including a threshold or offset) and are applied through a  $tanh(\cdot)$  nonlinearity. The synapse elements, which in general are far more numerous than neuron elements, must multiply the incoming signal by an internally stored value, called the weight, and must adapt this weight based upon a particular learning rule. Learning rules implemented in silicon are typically functions of correlations of signals passing through each synapse processor.

### 1.1 Basic Neural Network Theory

Parameterized mathematical models form the basis of many systems studied by engineers and scientists. Scientists and engineers usually derive these models using basic principles and intuitive insight, determining parameters by fitting experimental data to the model. In many cases where difficult to construct from first principles, adaptivity allows a generic parameterized model to tune itself to the data.

Neural networks and adaptive filters represent the best known examples of generic parameterized models where parameters adjust through learning. Both neural networks and adaptive filters comprise a collection of nodes interconnected through a number of synapses. Figure 1 shows the basic feedforward structure typically used in neural network implementations. Most approaches focus on feedforward structures, since feedback systems and networks with time dynamics (e.g. time delays) are straightforward extensions for silicon implementation, although the algorithm design is considerably more difficult. In this model, we encode a neuron's activity as an analog quantity based on the mean spiking rate in a

$$X_{1} \qquad X_{2} \qquad X_{3} \qquad X_{4}$$

$$\Rightarrow W_{11} \qquad \Rightarrow W_{12} \qquad \Rightarrow W_{13} \qquad \Rightarrow W_{14}$$

$$\Rightarrow W_{21} \qquad \Rightarrow W_{22} \qquad \Rightarrow W_{23} \qquad \Rightarrow W_{24} \qquad \Rightarrow Y_{1} = \sum_{i} W_{1i} X_{i}$$

$$\Rightarrow W_{21} \qquad \Rightarrow W_{22} \qquad \Rightarrow W_{23} \qquad \Rightarrow W_{24} \qquad \Rightarrow Y_{2} = \sum_{i} W_{2i} X_{i}$$

$$\Rightarrow W_{31} \qquad \Rightarrow W_{32} \qquad \Rightarrow W_{33} \qquad \Rightarrow W_{34} \qquad \Rightarrow Y_{3} = \sum_{i} W_{3i} X_{i}$$

**Figure 2:** Typical architectures for neural network implementations. Although the routing looks complicated in Fig. 1, it can be easily implemented in a mesh architecture. Diagram of the Classic Mesh Architecture, typically used for fully-connected systems.

given time window. One can build linear or nonlinear filters at the input to the sigmoid function; typically, a low-pass filter is built or modeled since that will naturally occur for a given implementation. This model is excellent for describing biology if only mean-firing rate behavior with minimal dendritic interactions is considered.

Before considering circuit implementations of neurons and synapses, we first frame the overall architecture issues involved in implementing neural networks. In most implementations, a single layer of synapses are built as mesh architectures connected to a column of neuron processors to achieve the functionality illustrated in Fig. 1, because silicon ICs are two-dimensional and require routing schemes that optimally work with two-dimensional constraints.

#### 1.1.1 Feedforward Computation

A basic model synapse must be able to store a weight, multiply its input with the stored weight, and adapt that weight based upon a function of the input and a fed-back error signal. We model feedforward computation mathematically as

$$y_i = W_{ij} x_j \to \mathbf{y} = \mathbf{W} \mathbf{x} \tag{1}$$

**Figure 3:** Typical architectures for neural network implementations. Although the routing looks complicated in Fig. 1, it can be easily implemented in a mesh architecture. Diagram of a Mesh processor architecture optimized for nearest-neighbor computations.

where  $\mathbf{x}_j$  is the j<sup>th</sup> input (  $\mathbf{x}$  is a vector of inputs ),  $\mathbf{y}_i$  is the i<sup>th</sup> output (  $\mathbf{y}$  is a vector of outputs ), and  $\mathbf{w}_{ij}$  is the stored weight at position (i,j) ( W is a matrix of weights). The result of this output is passed through a nonlinear function,

$$z_i = \operatorname{out}_i = tanh(a(y_i - \theta_i)) \tag{2}$$

where we designate  $z_i$  or out<sub>i</sub> as the result of the computation, a is a gain factor, and  $\theta_j$  is a variable threshold value.

Figure 2 shows the typical implementations for feedforward computation for a single layer architecture. Currents are preferred for outputs, because the summation typically required for most connectionist models is easily performed on a single wire, and voltages are preferred for inputs because they are easy to broadcast. Figure 3 shows how to modify a mesh architecture when considering m-nearest neighbor connections. Figure 5 shows the multilayer architecture from one-layer mesh structures.

Synapses require both feedforward and adaptation computations; therefore architectural constraints imposed by the learning algorithm are an essential consideration for any neural network. Only learning algorithms that scale to large numbers of inputs and outputs are practical. A single layer architecture with a local supervised or unsupervised rule only requires communicating the error signal along each row, as seen in Fig. 4. The complexity

**Figure 4:** Learning in a single layer. We can build either supervised algorithms (LMS is explicitly shown) or unsupervised one-layer networks in this architecture.

of the synapse computation will depend upon the particular learning rule. Many complicated algorithms, like the generalized Hebbian Algorithm (GHA) [27] and Independent Component Analysis (ICA), require additional matrix-vector multiplications, but can be developed into a mesh architecture. Algorithms requiring matrix-matrix multiplications are not feasible in standard IC technologies.

For multilayer algorithms, the architecture gets more complicated, particularly for supervised algorithms such as multilayer backpropagation. To extend the basic silicon synapse to a backpropagating synapse, we need an additional function; we need an output current that is the product of the fedback error signal (drain voltage) and stored weight. We show this architecture in Fig. 6. This additional function results in two issues, one concerning the signal-to-noise ratio of the resulting error signal, and the other concerning the overall synapse size. The effect of these small error signals, even without the resolution issues, is a slow learning rate.

The neural network literature abounds with possible alternative approaches, but we will base our proposed research on the Helmholtz machine concept [11]. Our primary reason for this approach rests on our desire to use single layer networks as primitives for building larger networks, as well as the fact that this reciprocal adaptive single layer network architecture is seen in various models of sensory neurosystems, such as the pathways from

**Figure 5:** Building a multilayer architecture from one-layer mesh structures. Multiple layers can be directly combined to form multilayer neural networks; each layer will rotate 90 degrees from the previous layer.